# Active Input Current Shaper Without an Electrolytic Capacitor for Retrofit Lamps Applications

Diego G. Lamar, *Member, IEEE*, Manuel Arias, *Member, IEEE*, Arturo Fernandez, *Senior Member, IEEE*, Jose A. Villarejo, *Member, IEEE*, and Javier Sebastian, *Senior Member, IEEE*

Abstract—The evolution of solid-state lighting technology has transformed traditional solutions in lighting. High-brightness light-emitting diodes (HB-LEDs) have become very attractive light sources due to their excellent characteristics, namely high efficiency, a long lifetime, and low maintenance. It is evident that HB-LED drivers must be durable and efficient in order to enjoy these advantages. Moreover, to replace incandescent bulbs, the ac-to-dc HB-LED driver must be simple and have low size and comply with international regulations (i.e., injecting low-frequency harmonics into the mains supply). With the last modifications regarding low-power lighting equipment (i.e., <25 W), the authors have traditionally focused their efforts on increasing efficiency by sacrificing sinusoidal input current, yet all their solutions obviate the suppression of the traditional electrolytic capacitor of ac-to-dc converters, highlighting that this is the price to pay for a simple and low-size solution. This paper, however, puts forward the design of a simple and low-size ac-to-dc HB-LED driver for retrofit lamps without an electrolytic capacitor in order to extend its lifetime. The solution proposed here derives from a well-known technique used in the past, the active input current shaper (AICS), but without an electrolytic capacitor in this case. If the electrolytic capacitor of an AICS is removed, then low-frequency ripple arises at its intermediate dc bus, adding some distortion in the line input current over the proper natural one of an AICS. However, this addition is slight in comparison to the proper natural distortion of AICSs. Moreover, the low-frequency ripple at the intermediate bus is not transferred to the output with the help of the rapid output dynamic response of the AICS, which prevents flicker. This paper presents a theoretical analysis that guarantees a compromise between compliance with international regulations and the use of capacitor technologies other than the electrolytic design. Finally, a 24-W experimental prototype has been built and tested to validate the theoretical results presented in this paper.

*Index Terms*—AC-to-DC power conversion, harmonic distortion, light-emitting diodes (LEDs), lighting, power factor, switched mode power supplies.

Manuscript received February 15, 2016; revised April 26, 2016 and June 10, 2016; accepted July 10, 2016. Date of publication July 21, 2016; date of current version February 2, 2017. This work was supported by the Spanish Ministry of Education and Science under Project MINECO-13-DPI2013-47176-C2-2-R, by the Government of the Principality of Asturias under Project FC-15-GRUPIN14-143, and by European Regional Development Fund grants. Recommended for publication by Associate Editor M. Ponce-Silva.

- D. G. Lamar, M. Arias, and J. Sebastian are with the Grupo de Sistemas Electrónicos de Alimentación, Universidad de Oviedo, 33204 Gijón, Spain (e-mail: gonzalezdiego@uniovi.es; ariasmanuel@uniovi.es; sebas@uniovi.es).

- A. Fernandez is with European Space Agency, 22201 AZ, Noordwijk, Netherlands (e-mail: Arturo.Fernandez@esa.int).

- J. A. Villarejo is with the Departamento de Tecnologia Electronica, Universidad Politecnica de Cartagena, 30202 Cartagena, Spain (e-mail: jose.villarejo@upct.es).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TPEL.2016.2593868

### I. INTRODUCTION

IGH-BRIGHTNESS light-emitting diodes (HB-LEDs) are now recognized as a rapidly emerging technology, which is considered the true alternative to many mature technologies (i.e., incandescent bulbs, compact fluorescent lamps, etc.) due to their high efficiency, low maintenance, and durability. To enjoy these advantages, however, HB-LED drivers must be both durable and efficient.

As HB-LEDs are diodes, the default method for driving them is to control the dc forward current through this semiconductor device. If the primary energy source is the ac line, then some types of an ac-to-dc converter must be placed between the line and HB-LEDs. Furthermore, the low-frequency harmonic content of the line current must comply with specific standards (IEC 61000-3-2 [3]-[6] and the ENERGY STAR program [7]). Traditionally, as these regulations establish a very strict harmonic content for lighting (e.g., IEC 61000-3-2, Class C), only sinusoidal line waveforms are able to comply with these standards. Therefore, the only practical method to comply with these regulations is to use active high-power-factor (PF) converters. These converters, known as PF correctors, constitute expensive complex solutions. Two years ago, there was a modification for lighting equipment with power levels lower than 25 W. At this point, compliance with the IEC 61000-3-2 standard becomes more relaxed due to the fact that now low-power luminaries (i.e., <25 W) must comply with it but applying limits of Class D and not Class C [6]. Hence, new solutions can arise.

A possible application for replacing incandescent bulbs lamps is to use two strings of around  $10 \times 1$  W HB-LEDs in parallel connected to the output of an ac-to-dc driver to produce the same luminance flux as that produced by a 100-W incandescent bulb. These configurations supply output voltages of around 20 V and power levels below 24 W. The most widespread solution is to use a flyback converter operating in discontinuous conduction mode (DCM) with switching frequencies below 100 kHz in order to obtain efficiencies of around 82%. With the last modifications regarding low-power lighting equipment (i.e., <25 W), the authors have traditionally focused their efforts on increasing the efficiency by distorting the line input current of the ac-to-dc driver despite the increase in its cost and complexity. Some examples are solutions based on an asymmetrical half-bridge flyback converter [8], a two-stage resonant buck converter [9], or a tapped-inductor buck converter [10], [11]. However, all these proposals exhibit a major drawback: the use

of an electrolytic capacitor to reduce the low-frequency ripple of the output current reducing the lifetime of the equipment.

This paper presents a simple and low-size ac-to-dc HB-LED driver based on a well-known concept, namely the active input current shaper (AICS). The proposal of this solution arises from the latest modifications of the regulations for low-power lighting equipment (i.e., IEC 61000-3-2:2014 [6], Class D for <25 W), which are now more relaxed than previous standards (i.e., IEC 61000-3-2:2010 [5], Class C for <25 W), no longer requiring a sinusoidal input current. AICSs are topologies that recycle some amount of power from the output to the input of the converter in order to shape the line input current. Thus, they present a natural distortion of the line input current, which depends on the amount of power recycled (the larger value of power recycled the more sinusoidal input current and the lower efficiency). To carry out this natural operation of the AICS, an electrolytic capacitor is needed to stabilize its intermediate bus. If the electrolytic capacitor is replaced by another technology that leads to a decrease in its capacity, then some low-frequency ripple arises in the intermediate bus, thus adding some distortion over the proper natural one of line input current of the AICS. However, this added distortion is slight in comparison to the natural one of the AICS. Moreover, due to the help of its rapid dynamic response, the low-frequency ripple is not fully transferred to the output from the intermediate bus. As a result, an ac-to-dc HB-LED driver for retrofit lamps applications without an electrolytic capacitor (i.e., with extended lifetime) and no flicker is achieved which complies with regulations.

With this goal in mind, this paper is organized as follows. Section II reviews the basic concepts of the AICS applied to the flyback family of converters. In Section III, the experimental results of a 24-W AICS prototype without low-frequency ripple in the intermediate verify the conclusions of the review in Section II. Moreover, in Section III, the electrolytic capacitor is removed from the AICS prototype, allowing low-frequency ripple in the intermediate bus. As a result, the distortion of the line input current due to the low-frequency ripple in the intermediate bus is negligible compared to the distortion naturally generated by the operating of the AICS. Section IV presents a static analysis of the AICS with low-frequency ripple in the intermediate bus, including the modeling of input current distortion and its analysis in order to verify the conclusions drawn from the experimental results. Finally, Section V concludes this paper.

### II. REVIEW OF AICSS

### A. Basic Concepts of the AICS

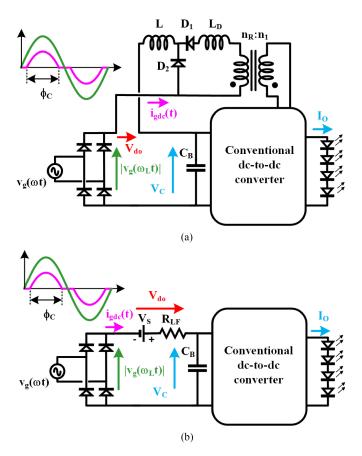

The concept of the AICS is very well known in the design of ac-to-dc switching-mode power supplies [14]–[18]. This solution is based on conventional dc-to-dc converters, with a slight modification: an additional output, obtained from the converter transformer [see Fig. 1(a)], is connected between the diode bridge and the bulk capacitor  $(C_B)$ .

This output, called "delayed output" in [12], was proposed in the context of two fully regulated outputs in dc-to-dc converters [13]. Although it seems similar to a conventional forward output, an extra inductor  $(L_D)$  is placed between one

Fig. 1. (a) AICS solution. (b) Equivalent circuit of an AICS.

terminal on the secondary side transformer and the diode  $D_1$  [see Fig. 1(a)]. With this extra inductor and with L working in continuous conduction mode (CCM, i.e.,  $L >> L_D$ ) or working in discontinuous conduction mode with moderated decreases of L (DCM, i.e.,  $L > 2L_D$ ), the Thévenin equivalent circuit of the "delayed output" becomes a voltage source  $[V_S;$  see Fig. 1(b)] with a loss-free resistor in series  $[R_{\rm LF};$  see Fig. 1(b)]. This "delayed output" recycles a certain amount of energy, redirecting it to the input in order to shape the line input current. The larger value of power recycled, the more sinusoidal input current and the lower efficiency, but by suitably choosing the values of these two elements (i.e.,  $V_S$  and  $R_L$ ), the AICS can achieve both high efficiency and a limited low-frequency harmonic content of the input current.

The current in a half cycle of input voltage can be easily deduced from the behavior of the AICS. The input rectifier starts to conduct when the input voltage (i.e.,  $v_g(t) = V_{\rm gp.} |\sin(\omega_L t)|$ ) reaches  $(V_S - V_C)$ . Thus, the expression of the rectified input current can be written as

$$i_{\rm gdc} (t) = \frac{V_{\rm gp} \cdot |\sin(\omega_L t)| - V_C + V_S}{R_{LF}}, \qquad (1)$$

where  $V_C$  is the voltage of the intermediate bus, and  $\omega_L$  and  $V_{\rm gp}$  are the angular frequency and the peak value of input voltage, respectively. Note that this expression is only valid for the interval  $[(\pi-\phi_{\rm C})/2,(\pi+\phi_{\rm C})/2]$ , where  $\phi_{\rm C}$  is the conduction angle (see Fig. 1). By equating (1) to zero, the expression for

TABLE I MINIMUM VALUE OF  $\phi_{\rm C}$  Complying With International Regulations

|                                                                                     | φ <sub>C m in</sub> (°) |

|-------------------------------------------------------------------------------------|-------------------------|

| EN 61000-3-2 Class C regulations                                                    | 140.49                  |

| EN 61000-3-2 Class D regulations                                                    | 63.12                   |

| ENERGY STAR for commercial applications<br>ENERGY STAR for residential applications | 55.59<br>103.87         |

the conduction angle can be easily calculated

$$\phi_C = 2\cos^{-1}\left(\frac{V_C - V_S}{V_{\rm gp}}\right). \tag{2}$$

Therefore, the line input current is defined by (1) within the  $[(\pi-\phi_{\rm C})/2,(\pi+\phi_{\rm C})/2]$  interval and by zero outside of this positive semicycle interval of the line input voltage. Likewise,  $i_{\rm g}(t)$  is similarly defined for the negative semicycle of the line input voltage (see Fig. 1). Note that the higher the  $\phi_{\rm C}$ , the greater the amount of energy recycled to the input, and therefore, the lower the efficiency.

From the expression of the input voltage, (1) and (2), the average input power will be

$$P_{g} = \frac{1}{\pi} \int_{(\phi_{C} - \pi)/2}^{(\phi_{C} + \pi)/2} \left[ i_{gdc} \left( t \right) \cdot V_{gp} \cdot \left| \sin \left( \omega_{L} t \right) \right| \right] dt$$

$$= \frac{V_{gp}^{2}}{2\pi R_{LF}} \left( \phi_{C} - \sin \left( \phi_{C} \right) \right). \tag{3}$$

The rectified input current can be rewritten as a function of the average input power, conduction angle, and peak value of the input voltage using (1)–(3)

$$i_{gdc}(t) = \frac{2\pi P_g}{V_{gp}} \left( \frac{|\sin(\omega_L t)| - \cos(\frac{\phi_C}{2})}{\phi_C - \sin(\phi_C)} \right).$$

(4)

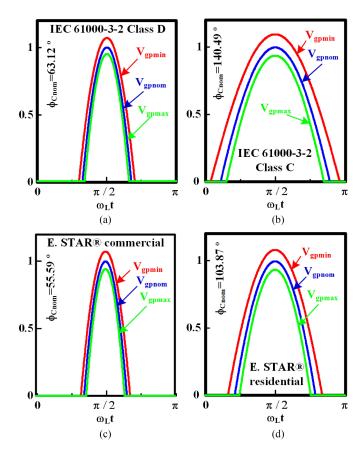

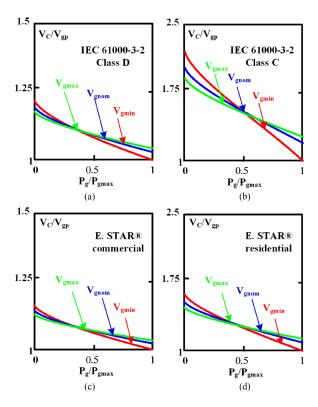

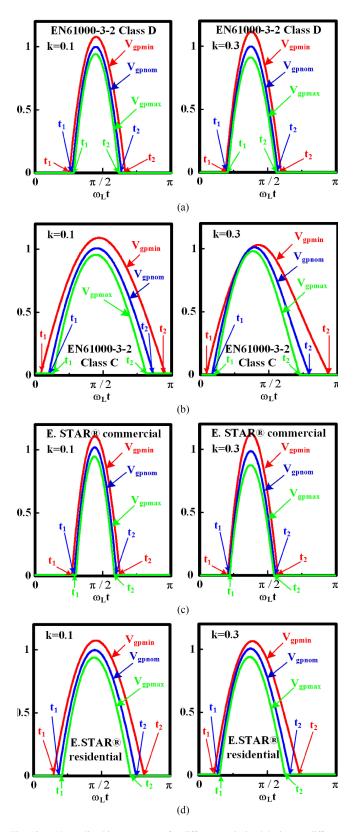

Moreover, from (4), it is straightforward to obtain the minimum  $\phi_{\rm C}$  value complying with international regulations for a given input voltage and input power (i.e., the minimum  $\phi_{\rm C}$  which introduces higher efficiency). Table I shows these minimum values (i.e.,  $\phi_{\rm Cmin}$ ), which are the same for both American and European mains supplies. Some of these values have been previously calculated in [15] and [18]. As can be seen in Table I, the more restrictive the standard, the higher the value of  $\phi_{\rm Cmin}$ . The input current of the AICS can now be represented. Fig. 2 shows the normalized input current for several optimized designs that meet international regulations at nominal input voltage in addition to maximizing efficiency. All the designs in Fig. 2 were carried out following the optimized design procedure proposed in [15] and [18].

## B. Implementation of the Voltage Source and the LFR With the Forward "Delayed Output"

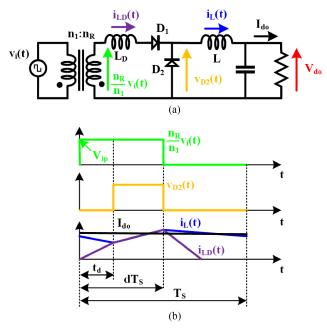

The analysis of the forward "delayed output" presented in [12] allows the calculation of  $V_S$  and  $R_{\rm LF}$ . Fig. 3 shows the equivalent circuit of the "delayed output." As can be seen, it is a forward output, but with an additional inductor,  $L_D$ , in

Fig. 2. Normalized input current for different optimized designs at different peak values of  $v_g(t)$ . (a) Class D European design. (b) Class C European design. (c) ENERGY STAR American design for commercial applications. (d) ENERGY STAR American design for residential applications.

Fig. 3. (a) Delayed output. (b) Main waveforms.

series with the rectifier diode,  $D_1$ . Due to the action of this inductor, there is a delay between the turn-off of  $D_2$  compared to the traditional forward output. In fact,  $D_2$  stops conducting later because  $L_D$  must be charged until  $i_L(t)$  [i.e., when  $i_{LD}(t)$  reaches  $i_L(t)$ ] via the action of the voltage reflected on the secondary side of the transformer of the forward "delayed output" [see Fig. 3(b)].

From Fig. 3(b), the delay time can be deduced by applying Faraday's law to the "delayed output"

$$t_d = \frac{i_L \left( t = t_d \right)}{\frac{n_R}{r_L} \cdot v_i \left( t \right)} \tag{5}$$

where  $v_i(t)n_R/n_1$  is the voltage reflected on the secondary side of the forward "delayed output,"  $n_R/n_1$  being the turns ratio of the transformer. The effective duty ratio applied to the output LC filter can be deduced from Fig. 3(b):

$$d' = d - t_d \cdot f_s. \tag{6}$$

where d is the duty cycle and  $f_S = 1/T_S$  is the switching frequency, with  $T_S$  being the switching period.

Assuming that there is no ripple through inductor L (for the sake of simplicity) because the forward "delayed output" operates in CCM (i.e.,  $L >> L_D$ ), the output voltage of the "delayed output" is

$$V_{\rm do} = \frac{n_R}{n_1} \cdot V_{\rm ip} \cdot d - L_D \cdot f_s \cdot I_{\rm od}, \tag{7}$$

where  $V_{\rm ip}$  is the peak value of  $v_i(t)$  and  $I_{\rm od}$  is the output current of the "delayed output". From Fig. 1, it can be deduced that the forward "delayed output" becomes a real source voltage. Equation (7) can thus be rewritten as follows:

$$V_{\rm do} = V_S - R_{\rm LF} \cdot I_{\rm od}, \tag{8}$$

where

$$V_S = \frac{n_R}{n_1} \cdot V_{\rm ip} \cdot d,\tag{9}$$

$$R_{\rm LF} = L_D \cdot f_s. \tag{10}$$

Note that no energy is dissipated in the  $R_{\rm LF}$  if all the components are ideal. Finally, it should be stressed that the  $L_D$  energy is transferred to the primary side of the transformer, in this case, to the equivalent voltage source,  $v_i(t)$ .

### C. Using a Flyback Converter to Design the AICS

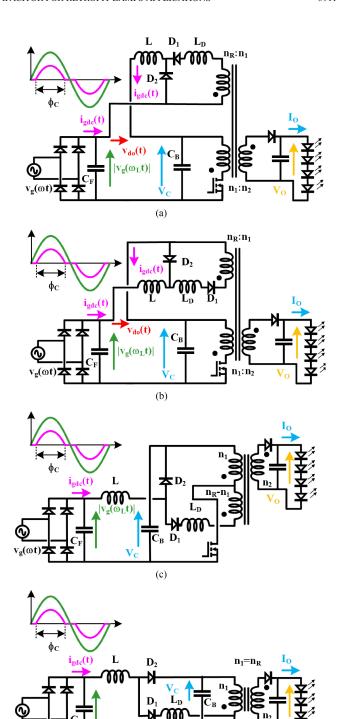

Fig. 4 shows the implementation of an AICS in a flyback converter (it will be the same in any other member of the flyback family of dc-to-dc converters: SEPIC, Cuk, and Zeta). First, Fig. 4(a) defines the basic implementation. Second, two modifications of this implementation are shown in Fig. 4(b) and (c), where the transformer becomes an autotransformer. Fig. 4(d) shows a particularization of the solution shown in Fig. 4(c). This is a straightforward implementation of the AICS by using a flyback converter, ideal for simple and low-size solutions. The price to pay is the loss of a degree of freedom in the design, as the autotransformer disappears (i.e.,  $n_R = n_1$ ). Finally, this implementation only introduces two extra inductors and two extra diodes with respect to the traditional flyback topology.

Fig. 4. Implementation of an AICS based on a flyback converter. (a) Basic scheme. (b) After moving  $L, L_D, D_1$ , and  $D_2$ . (c) Using an extra tap instead of "delayed output." (d) Using no extra tap  $(n_1 = n_R)$ .

(d)

$V_{\mathbf{g}}(\omega_{\mathbf{L}}\mathbf{t})$

By using a flyback topology to implement the AICS, the input voltage of the dc-to-dc converter becomes  $V_C$ . Taking into account CCM operation, the following equation can be written:

$$V_O = \frac{n_2}{n_1} \cdot V_C \cdot \frac{d}{1 - d},\tag{11}$$

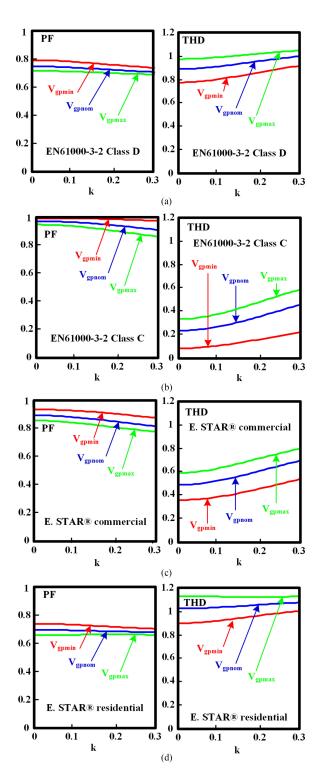

Fig. 5. Normalized voltage of the intermediate bus versus normalized power at different peak values of the input voltage for different optimized designs. (a) Class D European design. (b) Class C European design. (c) ENERGY STAR American design for commercial applications. (d) ENERGY STAR American design for residential applications.

where  $n_2$  is the number of turns of the secondary side of the transformer. Moreover, (9) becomes

$$V_S = \frac{n_R}{n_1} \cdot V_C \cdot d. \tag{12}$$

As shown in (12),  $V_S$  depends on  $V_C$ , the duty cycle, and the turn ratio of the "delayed output." In fact, suitably choosing  $n_R/n_1$  allows us to set  $V_S$  freely. Moreover,  $V_C$  and  $V_S$  are related by the fact that the output voltage of the AICS must be kept constant by the action of the feedback loop. A new equation must now be deduced using (2), (11), and (12)

$$V_C - \frac{n_R}{n_1} \cdot V_C \cdot \frac{V_O}{\frac{n_2}{n_1} \cdot V_C + V_O} = V_{\rm gp} \cdot \cos\left(\frac{\phi_C}{2}\right). \quad (13)$$

From (3) and (13), the evolution of  $V_C$  as a function of the design parameters (i.e., the conduction angle for nominal conditions and full load,  $\phi_{C\,\mathrm{nom}}$ , and the duty cycle for minimum peak value of the input voltage,  $d_{\mathrm{max}}$ ) can be calculated.  $V_C$  may be represented versus input power for different  $V_{\mathrm{gp}}$  values. Fig. 5 shows the voltage on the intermediate bus for different optimized designs following the design procedure in [16] and [18] (the same as the designs in Fig. 2). The optimized design procedures in [16] and [18] focused on minimizing the value of  $V_C$  and the amount of recycled energy, maintaining compliance with international regulations at nominal input voltage and full load. By suitably choosing  $n_R/n_1$ , the voltage drop across the series connection of  $V_S$  and  $R_{\mathrm{LF}}$  could be zero at the minimum input voltage,  $V_{\mathrm{gpmin}}$ , and full load,  $P_{\mathrm{gmax}}$ . Under these

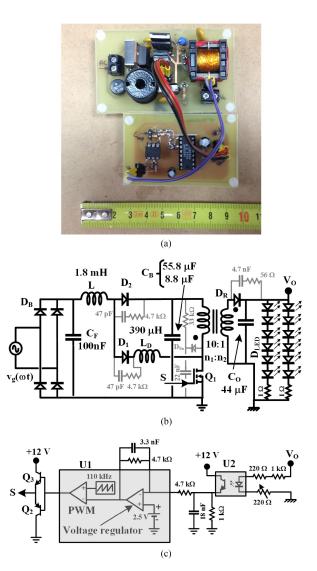

Fig. 6. Experimental prototype based on a flyback converter. (a) Picture. (b) Schematic of the power stage. (b) Schematic of the control stage.

conditions,  $V_C$  (i.e.,  $V_{C \min}$ ) becomes equal to  $V_{\rm gpmin}$ . Although  $V_C$  is minimized, it is not kept constant for different operating conditions (i.e.,  $P_g$  and  $V_{\rm gp}$  variations), at least if the flyback converter is operating at constant switching frequency, as can be seen in Fig. 5. This is the price to pay for the simplicity of this solution compared to a two-stage solution, in which the voltage across the intermediate bus is controlled, making no suitable regular AICS for wide input voltage range applications. Finally, it should be noted that, in the structure shown in Fig. 4(d),  $V_C$  prelimiting cannot be achieved due to the fact that  $n_R/n_1$  is set a priori.

## III. EXPERIMENTAL RESULTS: INCREASING LOW-FREQUENCY VOLTAGE RIPPLE OF THE AICS IN THE INTERMEDIATE BUS TO ELIMINATE THE ELECTROLYTIC CAPACITOR

A prototype of the proposed ac-to-dc HB-LED driver based on an AICS [see Fig. 6(a)] was designed to comply broadly with relaxed regulations (i.e., IEC 61000-3-2, Class D and ENERGY STAR program requirements for commercial applications), subsequently built and tested. A design was carried

|            | TABLE II            |                  |

|------------|---------------------|------------------|

| COMPONENTS | OF THE EXPERIMENTAL | <b>PROTOTYPE</b> |

| Fig. 6(b) and (c) reference | Value                |  |  |

|-----------------------------|----------------------|--|--|

| $\overline{D_1}$            | BYP08P140            |  |  |

| $D_2$                       | HFADBTB              |  |  |

| $D_B$                       | 3KBP04M              |  |  |

| $D_R$                       | 8TQ100               |  |  |

| $D_{Sn}$                    | MUR4100              |  |  |

| $D_{ m LED}$                | LXK2PW14T00 (Luxeon) |  |  |

| $Q_1$                       | NDF10N60ZH           |  |  |

| $Q_2$ and $Q_3$             | BD140 and BD139      |  |  |

| $U_1$                       | UC3825               |  |  |

| $U_2$                       | MCT2                 |  |  |

out in line with [16] and [18] for the following specifications:  $\phi_{C\,\mathrm{nom}} = 70^{\circ}, P_{g\,\mathrm{max}} = 24 \; \mathrm{W}, V_O = 19 \; \mathrm{V}, f_S = 110 \; \mathrm{kHz}$  (to provide a tradeoff between switching power losses and the size of the prototype), American design (i.e.,  $90\sqrt{2}$  $< V_{\rm gp} < 130\sqrt{2}$  and 60 Hz), CCM operation of the "delayed output" (i.e., L=1.8 mH), and  $d_{\rm max}=0.6$ . The circuit was designed according to the scheme shown in Fig. 6(a), where  $R_{\rm LF} = 43.45$  (i.e.,  $L_D = 0.39$  mH),  $n_S = n_1$ . The choice of the turns ratio of the transformer  $(n_2/n_1 = 0.1)$  is made according to a tradeoff between current and voltage stress in both the power transistor and diode, providing a duty cycle range at full load from 0.35 to 0.45. The prototype was controlled using a commercial IC, as shown in Fig. 6(b) (UC2825 manufactured by Texas Instruments). Finally, the converter output was connected to a matrix of two strings of six HB-LEDs in parallel using a  $1-\Omega$  resistor per string to equalize currents. Table II summarizes all the main components.

## A. AICS Without Low-Frequency Ripple in the Intermediate Bus ( $C_B = 55.8 \mu F$ )

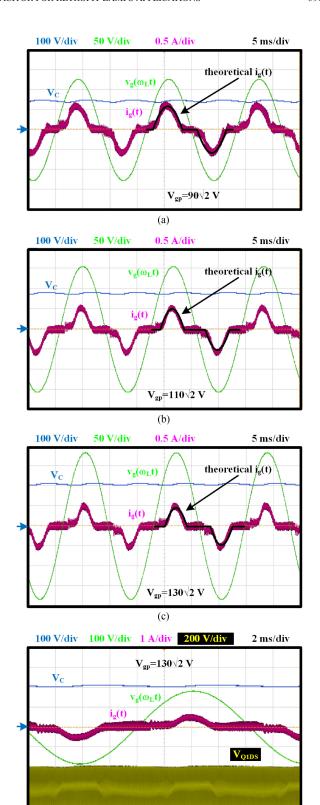

The prototype was tested until both its temperature and that of the HB-LEDs stabilized at the aforementioned specifications. The final operating temperature was reached after 45 min of operation. Fig. 7(a)–(c) shows the line input current, voltage in the intermediate bus, input voltage, and output voltage of the AICS, and Fig. 7(d) shows the drain-to-source voltage of  $Q_1$  MOSFET. As expected, the experimental results of  $i_g(t)$  match theoretical values. Furthermore, the voltage of the intermediate bus is between 150 and 200 V (depending on  $V_{\rm gp}$ ), as expected. In this implementation,  $V_C$  cannot be prelimited (i.e.,  $n_1=n_R$ ). However, this is the price to pay for using an implementation as simple as the one proposed here.

## B. AICS With Low-Frequency Ripple in the Intermediate Bus $(C_B = 8.8 \ \mu F)$

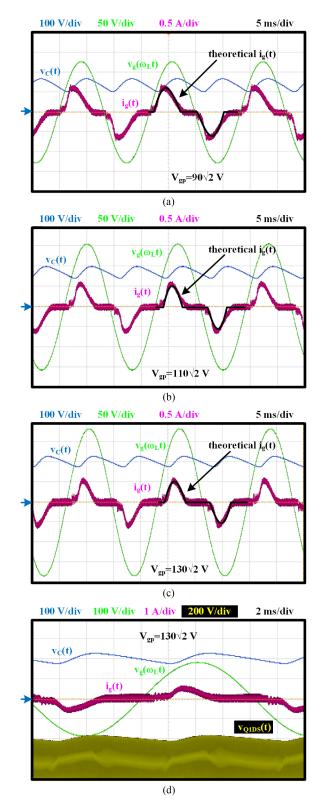

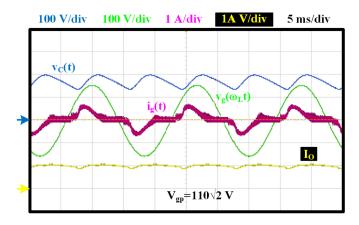

In this second test, the electrolytic capacitor of the intermediate bus ( $C_B=47~\mu\mathrm{F}$ ) has been removed and only the ceramic capacitor remains ( $C_B=4~\times~2.2~\mu\mathrm{F}$ ). As a result, some low-frequency ripple arises at the voltage of the intermediate bus (see  $v_C(t)$  in Fig. 8), adding some distortion over the proper natural one of the AICS line input current (i.e., the input current is now not sinusoidal during the conduction angle and  $\phi_C$  is

Fig. 7. Line input current  $(i_g(t))$ , voltage of the intermediate bus  $(V_C)$ , line input voltage  $(v_g(t))$ , and output voltage  $(V_O)$  of the AICS without a low-frequency ripple in the intermediate bus. (a)  $V_{\rm gp}=90~{\rm V_{rms}}$ . (b)  $V_{\rm gp}=110~{\rm V_{rms}}$ . (c)  $V_{\rm gp}=130~{\rm V_{rms}}$ . (d) Drain-to-source voltage of MOSFET  $Q_1(V_{\rm DSO1})$ .

Fig. 8. Line input current  $(i_g(t))$ , voltage of the intermediate bus  $(V_C)$ , line input voltage  $(v_g(t))$ , and output voltage  $(V_O)$  of the AICS with a low-frequency ripple in the intermediate bus. (a)  $V_{gp} = 90~\rm V_{rms}$ . (b)  $V_{gp} = 110~\rm V_{rms}$ . (c)  $V_{gp} = 130~\rm V_{rms}$ . (d) Drain-to-source voltage of MOSFET  $Q_1(V_{DSQ1})$ .

Fig. 9. Experimental harmonic content (a) with and (b) without an electrolytic capacitor for different line input voltages.

TABLE III

PF AND THD IN BOTH TESTS

| TEST                                                                      | $V_{ m gp}\left(V_{ m rms} ight)$ | PF    | THD(%) |

|---------------------------------------------------------------------------|-----------------------------------|-------|--------|

| AICS without low-frequency ripple in the intermediate bus                 | 90                                | 0.905 | 50.10  |

|                                                                           | 110                               | 0.854 | 64.83  |

| $(CB = 55.8 \mu\text{F})$                                                 | 130                               | 0.83  | 66.71  |

| AICS with low-frequency ripple in the intermediate bus (CB = $8.8 \mu$ F) | 90                                | 0.849 | 47.63  |

|                                                                           | 110                               | 0.812 | 57.49  |

|                                                                           | 130                               | 0.789 | 67.04  |

neither centered around nor equidistant from  $\omega_L t = \pi/2$ ). This added distortion seems slight in comparison to the proper natural distortion of the AICS [see  $i_q(t)$  in Fig. 8(a)–(c)]. Also, Fig. 8(d) shows the drain-to-source voltage of  $Q_1$  MOSFET. Moreover, this slight increase in input current distortion can be explicitly checked in comparison to the first test in Fig. 9, where the experimental harmonic content of  $i_q(t)$  is shown both for with and without an electrolytic capacitor. The experimental results corroborate the previous conclusion: the added distortion by eliminating the electrolytic capacitor is negligible in comparison to the proper natural one. As a consequence of this, compliance with the IEC 61000-3-2 Class D international standard is likewise achieved. Table III also shows compliance with ENERGY STAR program requirements for commercial applications and the slight increase in total harmonic distortion (THD) and slight decrease in PF.

Fig. 10. Line input current  $(i_g(t))$ , input line voltage  $(v_g(t))$ , output voltage  $(V_O)$ , and output current  $(I_o)$  of the AICS with a low-frequency ripple in the intermediate bus.

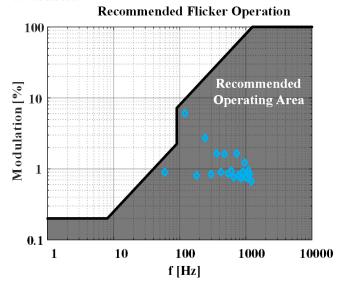

Fig. 11. Modulation (%) of the output current of the proposed design in the recommended operating area defined in [18].

Now, the question is how the low-frequency ripple of the intermediate bus is reflected at the output of the AICS. The answer is shown in Fig. 10. As can be seen, the low-frequency ripple of the output voltage  $(V_O)$  and output current  $(I_O)$  is very low because of the contribution of the rapid output voltage feedback loop [see Fig. 6(b)], which has been designed to eliminate flicker.

In order to validate the absence of flicker, the considerations in [19] have been followed. To limit the biological effects and detection of flicker in general illumination, modulation (%) should be kept within the shaded region defined in [19]. Modulation (%) must be calculated assuming perfect ac power line conditions, being

Modulation

$$(\%)_C = 100 \cdot \frac{(L_{\text{max}} - L_{\text{min}})}{(L_{\text{max}} + L_{\text{min}})},$$

(14)

where  $L_{\rm max}$  and  $L_{\rm min}$  correspond to the maximum and minimum luminance of each harmonic of the ac component of the output current, respectively. In this test, proportionality between luminance and the ac component of the output current has been

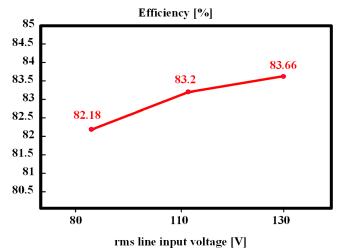

Fig. 12. Efficiency of the experimental prototype for different line input voltages.

assumed. The results of this analysis are shown in Fig. 11. As can be seen, all the ac harmonic content falls within the shaded region, and therefore, the absence of flicker is achieved.

Finally, the efficiency measured in both prototypes is the same, i.e., 83.2% at nominal input voltage. Fig. 12 shows the efficiency versus the line input voltage. This efficiency is lower than other proposed topologies for replacing incandescent bulb lamps [8]–[11], but expected in AISC based on flyback. Traditionally, the efficiency of AISC is relatively low, due to the fact that some amount of power is processed twice by the AICS in order to shape the line input current. However, the operation of the AICS allows the elimination of the electrolytic capacitor without flicker at the output current, which is the objective of this paper. Therefore, it could be said that the relatively low efficiency is the price to pay for replacing the electrolytic capacitor with a nonelectrolytic one with lower capacitance (i.e., with extended lifetime) without flicker at its output.

### IV. ANALYSIS OF THE AICS WITH LOW-FREQUENCY VOLTAGE RIPPLE IN THE INTERMEDIATE BUS

At this point, it is obvious that a theoretical analysis of the AICS solution with low-frequency ripple in the intermediate bus is required. This analysis should focus on the distortion of the line input current in order to validate the experimental results presented in the second test of the previous section.

If some ripple arises in the intermediate bus of the AICS due to the substitution of the electrolytic capacitor by another technology, the constant voltage,  $V_C$ , becomes  $v_C(t)$

$$v_C$$

(t) =  $V_{Cdc}$  -  $V_{Cac}$  sin (2 $\omega_L t$ )

=  $V_{Cdc}$  (1 -  $k$  sin (2 $\omega_L t$ ))

where  $V_{C\,\mathrm{dc}}$  and  $V_{C\,\mathrm{ac}}$  are, respectively, the dc component and ac component of the voltage across the intermediate bus, and k is the value of the relative ripple of  $v_C(t)$ . Note that only the component of twice the line frequency of  $v_C(t)$  has been taken into account for the sake of simplicity.

Fig. 13. Normalized input currents for different optimized designs at different peak values of  $v_g\left(t\right)$  and k values. (a) Class D European design. (b) Class C European design. (c) ENERGY STAR American design for commercial applications. (d) ENERGY STAR American design for residential applications.

The study is carried out for a flyback converter operating in CCM (or a member of the flyback family of dc-to-dc converters: SEPIC, Cuk, and Zeta). Equation (14) and a modification of (11) (i.e., changing d to d(t) and  $V_C$  to  $v_C(t)$ ) can be used to calculate the duty ratio

$$d(t) = \frac{Vo}{\frac{n_2}{n_1} \left( V_{Cdc} \left( 1 - k \sin \left( 2\omega_L t \right) \right) \right)} . \tag{15}$$

The duty ratio now varies with twice the line frequency due to the action of the output voltage feedback loop, which is designed to contribute either  $i_O(t)$  or  $v_O(t)$  to be constant. It is well known that the output voltage feedback loop of the AICS can be designed with a very rapid dynamic output response to contribute to the elimination of the low-frequency ripple, which now originates from the input of the flyback dc-to-dc converter (i.e., the intermediate bus of the AICS). This characteristic of the AICS [15]-[18] is the key to attenuate enough the lowfrequency ripple from  $v_C(t)$  to the output (keeping a nonlarge output capacitor) and to ensuring that the removal of the electrolytic capacitor at intermediate bus does not involve flicker. However, this variation in the duty cycle plus the low-frequency ripple of  $v_C(t)$  has consequences on  $V_S$  (which becomes  $v_S(t)$ in this analysis). From a modification of (12) (i.e., changing dto d(t),  $V_C$  to  $v_C(t)$ , and  $V_S$  to  $v_S(t)$  [see (14) and (15)], the expression of  $v_S(t)$  can be deduced as

$$v_S(t) = V_o \frac{\frac{n_R}{n_1}}{\frac{n_2}{n_1}} \frac{(1 - k \sin(2\omega_L t))}{(1 - k \sin(2\omega_L t)) + \frac{V_o}{\frac{n_2}{n_1} V_{Cdc}}}.$$

(16)

As shown in (16),  $v_S(t)$  is now not a constant voltage source, and therefore, the line input current will not be sinusoidal during the conduction of the diodes of the rectifier bridge. Using a modification of (3) [i.e.,  $V_C$  being  $v_C(t)$  and  $V_S$  being  $v_S(t)$ ] [see (14) and (16)], the line input current will be

$$i_{gdc}(t) = \frac{1}{R_{LF}} \left[ V_{gp} \left| \sin(\omega_L t) \right| + V_o \frac{\frac{n_R}{n_1}}{\frac{n_2}{n_1}} \frac{(1 - k \sin(2\omega_L t))}{(1 - k \sin(2\omega_L t)) + \frac{V_o}{\frac{n_2}{n_1} V_{Cdc}}} - V_{Cdc} \left( 1 - k \sin(2\omega_L t) \right) \right].$$

(17)

It should be noted that this expression is only valid for the interval in which  $v_g(t)$  is greater than  $v_C(t) - v_S(t)$ . This interval can be calculated by equating to zero (17)

$$V_{\rm gp} |\sin(\omega_L t_i)| + V_o \frac{n_S}{n} \frac{(1 - k \sin(2\omega_L t_i))}{(1 - k \sin(2\omega_L t_i)) + \frac{V_o}{n V_{C dc}}} - V_{C dc} (1 - k \sin(2\omega_L t_i)) = 0;, \quad i = 1, 2, \quad (18)$$

where the conduction angle becomes

$$\phi_C = 2\pi \frac{t_2 - t_1}{T}. (19)$$

As can be deduced from (17), the average input current of the AICS with ripple in the intermediate bus is nonsinusoidal during the interval  $[t_1, t_2]$ .

Fig. 14. Normalized  $\phi_C$  at different  $V_{\rm gp}$  values versus k for different optimized designs. (a) Class D European design. (b) Class C European design. (c) ENERGY STAR American design for commercial applications. (d) ENERGY STAR American design for residential applications.

Finally, the expression of  $R_{\rm LF}$  can be deduced from the input power using (18). For the sake of simplicity,  $R_{\rm LF}$  has been considered constant in this theoretical analysis

$$R_{\rm LF} = \frac{1}{P_g \cdot \frac{T}{2}} \int_{t_1}^{t_2} i_{gdc}(t) V_{\rm gp} |\sin(\omega_L t)| dt$$

$$= \frac{1}{P_g \cdot \frac{T}{2}} \int_{t_1}^{t_2} \left[ V_{\rm gp} |\sin(\omega_L t)| + V_o \frac{n_S}{n} \right]$$

$$\times \frac{(1 - k \sin(2\omega_L t))}{(1 - k \sin(2\omega_L t)) + \frac{V_o}{n V_{C dc}}} - V_{C dc}$$

$$\times (1 - k \sin(2\omega_L t)) V_{\rm gp} |\sin(\omega_L t)| dt. (20)$$

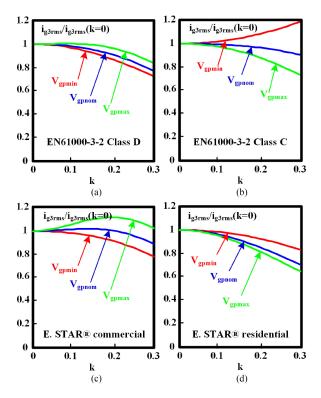

At this point, the line input current of the AICS with low-frequency ripple at intermediate bus can be plotted for a given specification. Fig. 13 shows the normalized input current for the same optimized designs presented in Fig. 2, though now introducing some ripple on  $v_{\rm C}(t)$  (i.e., k < 0.3).

As can be seen, slight distortion is introduced in  $i_g(t)$  as k increases in all the optimized American and European designs. It is obvious that the input current is now not sinusoidal during the conduction angle and also that the interval which defines the conduction angle (i.e.,  $[t_1,t_2]$ ) is neither centered around nor equidistant from  $\omega_L t = \pi/2$  as was introduced in experimental results of Section III-B. Although the expression of the conduction angle could be calculated from (18) and (19), no transcendent equation is thus obtained. Fig. 14 shows the evo-

Fig. 15. PF and THD at different peak values of  $v_g\left(t\right)$  versus k. (a) Class D European design. (b) Class C European design. (c) ENERGY STAR American design for commercial applications. (d) ENERGY STAR American design for residential applications.

lution of the normalized conduction angle (i.e., normalized to k=0 design) versus k for different  $V_{\rm gp}$  values k of the optimized American and European designs. As can be seen, the variation of  $\phi_C$  is not significant in any situation for moderate increases in k (i.e., k<0.3).

Fig. 16. Normalized third harmonic of  $i_g(t)$  versus k at different peak values of the input voltage for different optimized designs. (a) Class D European design. (b) Class C European design. (c) ENERGY STAR American design for commercial applications. (d) ENERGY STAR American design for residential applications.

At this point, however, no conclusion can be drawn regarding the distortion of the input current of the AICS by introducing low-frequency ripple in the intermediate bus of an optimized design. Thus, using (18)–(20), the PF and THD of  $i_g(t)$  can be calculated as a function of k for different  $V_{\rm gp}$  values (see Fig. 15). From Fig. 15, it can be concluded that the added the distortion of the line input current over proper natural one of the AICS due to moderate frequency ripple values (i.e., k < 0.3) in the intermediate bus is negligible. This means that compliance with ENERGY STAR regulations (due to the nonvariation of PF versus k) is still ensured for moderate values of k (i.e., k < 0.3) in traditional optimized designs.

For EN 61000-3-2 Class D regulations, however, the imposed limits refer to the power processed by the ac-dc HB-LED driver, while for Class C, the limits depends on the PF and on the rms value of the first harmonic. Fig. 16 shows the normalized rms value of the third harmonic of  $i_q(t)$  (i.e., normalized to a k=0design) for optimized designs. As can be seen, the variation in the rms value of the normalized third harmonic is not significant in any situation for moderate values of k (i.e., k < 0.3). Moreover, this analysis has been extended to all harmonic taken into account in the regulations with the same results: the rms value of each normalized harmonic is not significant, being the increase of the normalized third one the greatest. This means that compliance with EN 61000-3-2 is ensured for these k values (i.e., k < 0.3) if traditional optimized designs at k = 0 [16], [18] have been previously employed. Therefore, this last analysis corroborates previous conclusion: the added distortion of the line input current by allowing some low-frequency ripple at intermediate bus can be neglected in comparison to proper natural one of the AICS.

Therefore, the proposed conclusion of this analysis is to design a traditional AICS without ripple in the intermediate bus because this ensures both compliance with international regulations and higher efficiency. Subsequently, if the aim is to eliminate the electrolytic capacitor to extend the lifetime, then it is simply necessary to ensure that the ripple in the intermediate bus is moderate (i.e., k > 0.3).

Finally, the line input current of the experimental results of test B (i.e., k=0.2) can also be calculated using the theoretical model presented in this section. As can be seen in Fig. 10, the experimental results match theoretical values, thus validating the proposed model.

### V. CONCLUSION

This paper presents an ac-to-dc HB-LED driver with no electrolytic capacitor based on the AICS solution. The operation of the AICS provides the opportunity to eliminate the electrolytic capacitor at the intermediate bus. But, by replacing the electrolytic capacitor with a nonelectrolytic one with lower capacitance (extending its lifetime), some low-frequency ripple arises in the intermediate bus of the AICS. As a result, some distortion of the line input current is added over the proper natural one of the AICS. However, as theoretical and experimental results show, this added distortion is slight in comparison to that of a regular AICS and compliance with international regulations (i.e., EN 61000-3-2:2014 Class D) is achieved. Moreover, no low-frequency ripple is transferred to the output with the help of the rapid output dynamic response of the AICS, and hence, no flicker is obtained in the ac-to-dc one-stage topology without an electrolytic capacitor. However, the proposed solution presents two main drawbacks: no wide input voltage range performance and slightly lower efficiency compared to other solutions. The first drawback is not critical because wide input voltage range is not mandatory in ac-to-dc HB-LED driver for substituting incandescent bulb lamps. However, the second one is the price to pay for a simple and low-size solution without an electrolytic capacitor and extended lifetime, based on the use of an AICS.

### REFERENCES

- [1] I. L. Azevedo, M. G. Morgan, and F. Morgan, "The transition to solid-state lighting," *Proc. IEEE*, vol. 97, no. 3, pp. 481–510, Mar. 2009.

- [2] M. S. Shur and R. Zukauskas, "Solid-state lighting: Toward superior illumination," *Proc. IEEE*, vol. 93, no. 10, pp. 1691–1703, Oct. 2005.

- [3] Electromagnetic compatibility (EMC)-Part 3: Limits-section 2: Limits for harmonic current emissions (equipment input current<16A per phase), EN 61000-3-2: 1995.

- [4] Draft of the proposed CLC Common Modification to EN 61000-3-2, 2006.

- [5] Draft of the proposed CLC Common Modification to IEC 61000-3-2, 2010.

- [6] Draft of the proposed CLC Common Modification to EN 61000-3-2, 2014.

- [7] Revised ENERGY STAR Program Requirements for Solid-State Lighting Luminaires: Eligibility Criteria—Version 1.1, Dec. 2008.

- [8] S. Buso, G. Spiazzi, and F. Sichirollo, "Study of the asymmetrical half-bridge flyback converter as an effective line-fed solid-state lamp driver," *IEEE Trans. Ind. Electron.*, vol. 61, no. 12, pp. 6730–6738, Dec. 2014.

- [9] X. Qu, S.-C. Wong, and C. K. Tse, "Resonance-assisted buck converter for offline driving of power LED replacement lamps," *IEEE Trans. Power Electron.*, vol. 26, no. 2, pp. 532–540, Feb. 2011.

- [10] D. G. Lamar, M. Fernandez, M. Arias, M. M. Hernando, and J. Sebastian, "Tapped-inductor buck HB-LED AC–DC driver operating in boundary conduction mode for replacing incandescent bulb lamps," *IEEE Trans. Power Electron.*, vol. 27, no. 10, pp. 4329–4337, Oct. 2012.

- [11] D. G. Lamar, M. Arias, M. M. Hernando, and J. Sebastian, "Using the loss-free resistor concept to design a simple AC–DC HB-LED driver for retrofit lamp applications," *IEEE Trans. Ind. Appl.*, vol. 51, no. 3, pp. 2300–2311, May/Jun. 2015.

- [12] J. Sebastian and J. Uceda, "Two different types of fully regulated twooutput dc-to-dc converters with one switch," in *Proc. 2nd Int. Conf. Power Electron. Var. Speed Drives*, Birmingham, U.K., Nov. 1986, pp. 172–176.

- [13] J. Sebastian and J. Uceda, "An alternative method for controlling twooutput DC-to-DC converters using saturable core inductor," *IEEE Trans. Power Electron.*, vol. 10, no. 4, pp. 419–426, Jul. 1995.

- [14] L. Huber and M. M. Jovanovic, "Single-stage, single-switch, isolated power supply technique with input-current shaping and fast output-voltage regulation for universal input-voltage-range applications," in *Proc. 12th Annu. Appl. Power Electron. Conf. Expo.*, Feb. 23–27, 1997, vol. 1, pp. 272–280.

- [15] L. Huber and M. M. Jovanovic, "Design optimization of single-stage single-switch input-current shapers," *IEEE Trans. Power Electron.*, vol. 15, no. 1, pp. 174–184, Jan. 2000.

- [16] J. Sebastian, M. M. Hernando, A. Fernandez, P. J. Villegas, and J. Diaz, "Input current shaper based on the series connection of a voltage source and a loss-free resistor," *IEEE Trans. Ind. Appl.*, vol. 37, no. 2, pp. 583– 591, Mar./Apr. 2001.

- [17] J. Qian and F. C. Lee, "A high efficient single stage single switch high power factor AC/DC converter with universal input," in *Proc. 12th Annu. Appl. Power Electron. Conf. Expo.*, Atlanta, GA, USA, 1997, vol. 1, pp. 281–287.

- [18] J. A. Villarejo, J. Sebastian, F. Soto, and E. de Jodar, "Optimizing the design of single-stage power-factor correctors," *IEEE Trans. Ind. Electron.*, vol. 54, no. 3, pp. 1472–1482, Jun. 2007.

- [19] IEEE Recommended Practices for Modulating Current in High-Brightness LEDs for Mitigating Health Risks to Viewers, IEEE Std. 1789-2015, Jun. 5, 2015, pp. 1–80.

verters.

**Diego G. Lamar** (M'08) was born in Zaragoza, Spain, in 1974. He received the M.Sc. and Ph.D. degrees in electrical engineering from the University of Oviedo, Oviedo, Spain, in 2003 and 2008, respectively.

In 2003 and 2005, he became a Research Engineer and an Assistant Professor, respectively, with the University of Oviedo, where he has been an Associate Professor since September 2011. His research interests include switching-mode power supplies, converter modeling, and power-factor-correction con-

Manuel Arias (S'05–M'10) was born in Oviedo, Spain, in 1980. He received the M.Sc. and Ph.D. degrees in electrical engineering from the University of Oviedo, Oviedo, Spain, in 2005 and 2010, respectively.

Since February 2007, he has been an Assistant Professor in the Department of Electrical and Electronic Engineering, University of Oviedo. His research interests include ac–dc and dc–dc converters, uninterruptible power supply, and light-emitting-diode-based lighting.

**Arturo Fernandez** (M'98–SM'12) received the M.Sc. and Ph.D. degrees in electrical engineering from the Universidad de Oviedo, Gijon, Spain, in 1997 and 2000, respectively.

In 1998, he joined the Universidad de Oviedo as an Assistant Professor where since 2003 he has been an Associate Professor. In 2007, he joined the European Space Agency and is currently at the Power Systems Division. In 2015 he became the Head of the Power Management and Distribution Section in ESA. Since 1997, he has been involved in approximately 30

power electronics research and development projects, mainly developing highpower-factor rectifiers for Alcatel and Chloride Power Protection. His research interests include switching-mode power supplies, low output voltage, converter modeling, high-power-factor rectifiers, and power electronics for space applications. He has published more than 120 papers on those technical fields. Dr. Fernandez cooperates regularly with the IEEE and the IEEE-PELS Spanish Chapter.

Jose A. Villarejo (M'00) was born in Murcia, Spain, in 1972. He received the M.Sc. degree in electrical engineering from the University of Murcia, Murcia, in 1997, and the Ph.D. degree from Technical University of Cartagena, Cartagena, Spain, in 2004.

Since 1998, he has been an Assistant Professor with Technical University of Cartagena. His research interests include dc/dc converters and photovoltaic grid-connected microinverters.

**Javier Sebastian** (M'87–SM'11) was born in Madrid, Spain, in 1958. He received the M.Sc. degree in electrical engineering from Polytechnic University of Madrid, Madrid, and the Ph.D. degree in electrical engineering from the University of Oviedo, Oviedo, Spain, in 1981 and 1985, respectively.

He was an Assistant Professor and an Associate Professor at both Polytechnic University of Madrid and at the University of Oviedo. Since 1992, he has been with the University of Oviedo, where he is cur-

rently a Professor. His research interests include switching-mode power supplies, modeling of dc-to-dc converters, low-output-voltage dc-to-dc converters, high-power-factor rectifiers, dc-to-dc converters for envelope tracking techniques, and the use of widebandgap semiconductors in power supplies.