James Brian Romaine

Memoria presentada para optar al grado de Doctor por la Universidad de Sevilla

Director, Tutor: Manuel Delgado Restituto

Director: Ángel Rodríguez Vázquez

Departamento de Electrónica y Electromagnetismo

Universidad de Sevilla

May 2019

| I would like to dedicate this thesis to my family, friends and co-workers |              |                    |                 |                  |               |

|---------------------------------------------------------------------------|--------------|--------------------|-----------------|------------------|---------------|

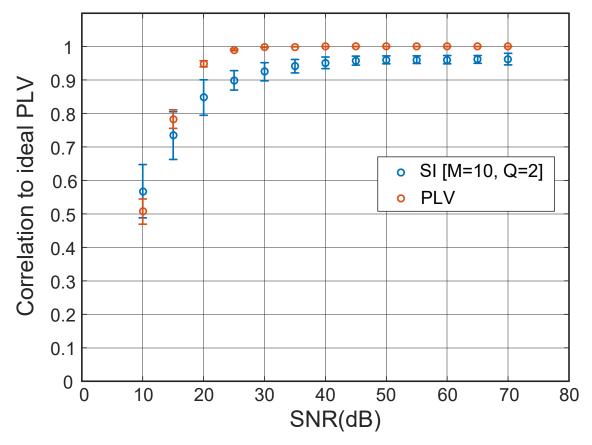

| I would like to dedicate this thesis to my family, friends and co-workers |              |                    |                 |                  |               |

|                                                                           | I would like | e to dedicate this | thesis to my fa | mily, friends ar | nd co-workers |

|                                                                           |              |                    |                 |                  |               |

|                                                                           |              |                    |                 |                  |               |

|                                                                           |              |                    |                 |                  |               |

|                                                                           |              |                    |                 |                  |               |

|                                                                           |              |                    |                 |                  |               |

|                                                                           |              |                    |                 |                  |               |

#### Declaration

I hereby declare that except where specific reference is made to the work of others, the contents of this dissertation are original and have not been submitted in whole or in part for consideration for any other degree or qualification in this, or any other university. This dissertation is my own work and contains nothing which is the outcome of work done in collaboration with others, except as specified in the text and Acknowledgements.

James Brian Romaine May 2019

#### Acknowledgements

Firstly, I would like to thank Manuel Delgado Restituto and Ángel Rodríguez Vázquez for their constant collaboration and intuitive guidance throughout my PhD.

Secondly, I would like to thank Miguel Angel Lagos Florido and Rafaella Fiorelli Martegani for their design guidence and help with test diagnostics and technical designs.

Last but not least, I would also like to thank Verónica Siles Santana and Marco Trevisi for their constant support, friendship and patients, throughout the course of this PhD.

This work has been supported by the Spanish Ministry of Science and Innovation under grant TEC2016-80923-P and the FEDER Program.

#### Abstract

The human brain is the most complex organ in the human body, which consists of approximately 100 billion neurons. These cells effortlessly communicate over multiple hemispheres to deliver our everyday sensorimotor and cognitive abilities.

Although the underlying principles of neuronal communication are not well understood, there is evidence to suggest precise synchronisation and/or de-synchronisation of neuronal clusters could play an important role. Furthermore, new evidence suggests that these patterns of synchronisation could be used as an identifier for the detection of a variety of neurological disorders including, Alzheimers (AD), Schizophrenia (SZ) and Epilepsy (EP), where neural degradation or hyper synchronous networks have been detected.

Over the years many different techniques have been proposed for the detection of synchronisation patterns, in the form of spectral analysis, transform approaches and statistical based studies. Nonetheless, most are confined to software based implementations as opposed to hardware realisations due to their complexity. Furthermore, the few hardware implementations which do exist, suffer from a lack of scalability, in terms of brain area coverage, throughput and power consumption.

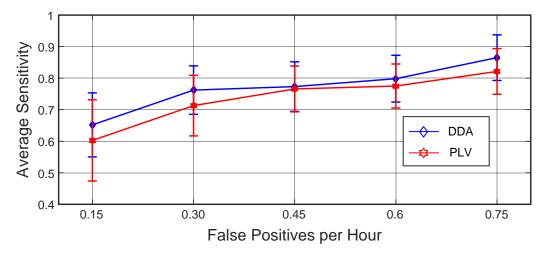

Here we introduce the design and implementation of a hardware efficient algorithm, named Delay Difference Analysis (DDA), for the identification of patient specific synchronisation patterns. The design is remarkably hardware friendly when compared with other algorithms. In fact, we can reduce hardware requirements by as much as 80% and power consumption as much as 90%, when compared with the most common techniques. In terms of absolute sensitivity the DDA produces an average sensitivity of more than 80% for a false positive rate of 0.75 FP/h and indeed up to a maximum of 90% for confidence levels of 95%.

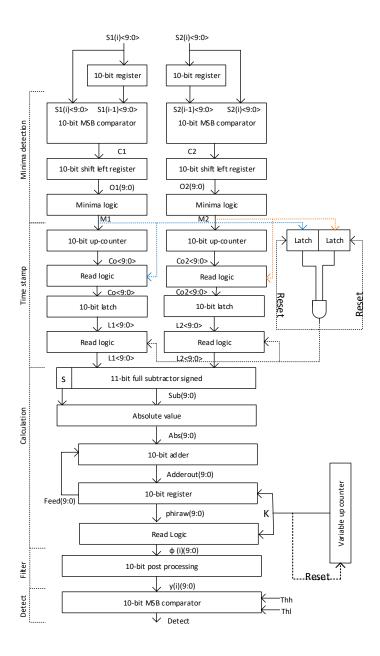

This thesis presents two integer-based digital processors for the calculation of phase synchronisation between neural signals. It is based on the measurement of time periods between two consecutive minima. The simplicity of the approach allows for the use of elementary digital blocks, such as registers, counters or adders. In fact, the first introduced processor was fabricated in a  $0.18\mu m$  CMOS process and only occupies  $0.05mm^2$  and consumes 15nW from a 0.5V supply voltage at a signal input rate of 1024S/s. These low-area and low-power features make the proposed circuit a valuable computing element in closed-loop neural prosthesis for the treatment of neural disorders, such as epilepsy, or for measuring functional connectivity maps between different recording sites in the brain.

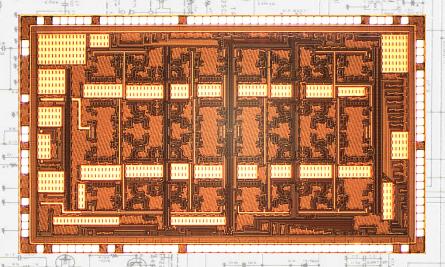

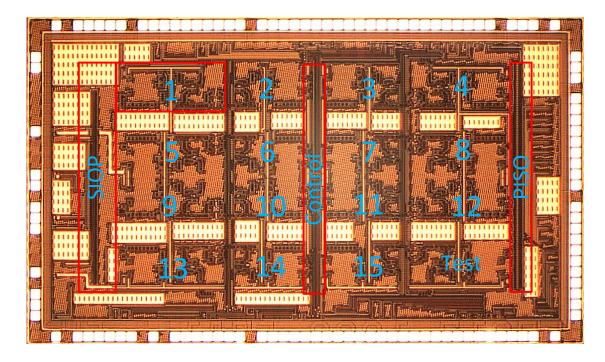

A second VLSI implementation was designed and integrated as a mass integrated 16-channel design. Incorporated into the design were 16 individual synchronisation processors (15 on-line processors and 1 test processor) each with a dedicated *training* and calculation module, used to build a specialised epileptic detection system based on patient specific synchrony thresholds. Each of the main processors are capable of calculating the phase synchrony between 9 independent electroencephalography (EEG) signals over 8 epochs of time totalling 120 EEG combinations. Remarkably, the entire circuit occupies a total area of only 3.64 mm<sup>2</sup>.

This design was implemented with a multi-purpose focus in mind. Firstly, as a clinical aid to help physicians detect pathological brain states, where the small area would allow the patient to wear the device for home trials. Moreover, the small power consumption would allow to run from standard batteries for long periods. The trials could produce important patient specific information which could be processed using mathematical tools such as graph theory. Secondly, the design was focused towards the use as an *in-vivo* device to detect phase synchrony in real time for patients who suffer with such neurological disorders as EP, which need constant monitoring and feedback. In future developments this synchronisation device would make an good contribution to a full system on chip device for detection and stimulation.

El cerebro humano es el órgano más complejo del cuerpo humano, que consta de aproximadamente 100 mil millones de neuronas. Estas células se comunican sin esfuerzo a través de ambos hemisferios para favorecer nuestras habilidades sensoriales y cognitivas diarias.

Si bien los principios subyacentes de la comunicación neuronal no se comprenden bien, existen pruebas que sugieren que la sincronización precisa y/o la desincronización de los grupos neuronales podrían desempeñar un papel importante. Además, nuevas evidencias sugieren que estos patrones de sincronización podrían usarse como un identificador para la detección de una gran variedad de trastornos neurológicos incluyendo la enfermedad de Alzheimer(AD), la esquizofrenia(SZ) y la epilepsia(EP), donde se ha detectado la degradación neural o las redes hiper sincrónicas.

A lo largo de los años, se han propuesto muchas técnicas diferentes para la detección de patrones de sincronización en forma de análisis espectral, enfoques de transformación y análisis estadísticos. No obstante, la mayoría se limita a implementaciones basadas en software en lugar de realizaciones de hardware debido a su complejidad. Además, las pocas implementaciones de hardware que existen, sufren una falta de escalabilidad, en términos de cobertura del área del cerebro, rendimiento y consumo de energía.

Aquí presentamos el diseño y la implementación de un algoritmo eficiente de hardware llamado "Delay Difference Aproximation" (DDA) para la identificación de patrones de sincronización específicos del paciente. El diseño es notablemente compatible con el hardware en comparación con otros algoritmos. De hecho, podemos reducir los requisitos de hardware hasta en un 80% y el consumo de energía hasta en un 90%, en comparación con las técnicas más comunes. En términos de sensibilidad absoluta, la DDA produce una sensibilidad promedio de más del 80% para una tasa de falsos positivos de 0,75 PF / hr y hasta un máximo del 90% para niveles de confianza del 95%.

Esta tesis presenta dos procesadores digitales para el cálculo de la sincronización de fase entre señales neuronales. Se basa en la medición de los períodos de tiempo entre dos mínimos consecutivos. La simplicidad del enfoque permite el uso de bloques digitales elementales, como registros, contadores o sumadores. De hecho, el primer procesador introducido se fabricó en un proceso CMOS de  $0.18\mu m$  y solo ocupa  $0.05mm^2$  y consume 15nW de un voltaje de suministro de 0.5V a una tasa de entrada de señal de 1024S/s.

Estas características de baja área y baja potencia hacen que el procesador propuesto sea un valioso elemento informático en prótesis neurales de circuito cerrado para el tratamiento de trastornos neuronales, como la epilepsia, o para medir mapas de conectividad funcional entre diferentes sitios de registro en el cerebro.

Además, se diseñó una segunda implementación VLSI que se integró como un diseño de 16 canales integrado en masa. Se incorporaron al diseño 16 procesadores de sincronización individuales (15 procesadores en línea y 1 procesador de prueba), cada uno con un *módulo de entrenamiento y cálculo* dedicado, utilizado para construir un sistema de detección epiléptico especializado basado en umbrales de sincronía específicos del paciente. Cada uno de los procesadores principales es capaz de calcular la sincronización de fase entre 9 señales de electroencefalografía (EEG) independientes en 8 épocas de tiempo que totalizan 120 combinaciones de EEG. Cabe destacar que todo el circuito ocupa un área total de solo 3.64 mm².

Este diseño fue implementado teniendo en mente varios propósitos. En primer lugar, como ayuda clínica para ayudar a los médicos a detectar estados cerebrales patológicos, donde el área pequeña permitiría al paciente usar el dispositivo para las pruebas caseras. Además, el pequeño consumo de energía permitiría una carga cero del dispositivo, lo que le permitiría funcionar con baterías estándar durante largos períodos. Los ensayos podrían producir información importante específica para el paciente que podría procesarse utilizando herramientas matemáticas como la teoría de grafos. En segundo lugar, el diseño se centró en el uso como un dispositivo *in-vivo* para detectar la sincronización de fase en tiempo real para pacientes que sufren trastornos neurológicos como el EP, que necesitan supervisión y retroalimentación constantes. En desarrollos futuros, este dispositivo de sincronización sería una buena base para desarrollar un sistema completo de un dispositivo chip para detección de trastornos neurológicos.

### Table of contents

List of figures

List of tables

Preface

#### Organisation

| 1 | Intr | roduction |                                         |    |  |  |

|---|------|-----------|-----------------------------------------|----|--|--|

|   | 1.1  | The la    | arger brain                             | 6  |  |  |

|   | 1.2  | Conne     | ectivity and the smaller brain          | 8  |  |  |

|   |      | 1.2.1     | Neurons                                 | 8  |  |  |

|   |      | 1.2.2     | Neural oscillations                     | 10 |  |  |

|   | 1.3  | Phase     | and Synchronisation                     | 13 |  |  |

|   |      | 1.3.1     | Basic concept                           | 13 |  |  |

|   |      | 1.3.2     | Synchronisation and phase locking       | 14 |  |  |

|   |      | 1.3.3     | Synchronisation in the brain            | 16 |  |  |

|   | 1.4  | Synch     | ronisation in pathological brain states | 17 |  |  |

|   |      | 1.4.1     | Synchrony in neurological disorders     | 19 |  |  |

|   | 1.5  | Phase     | synchronisation methods                 | 20 |  |  |

|   |      | 1.5.1     | Analytical measures                     | 20 |  |  |

|   |      | 1.5.2     | Numerical measures                      | 25 |  |  |

|   | 1.6 | VLSI implementations of PS estimators                        | 26 |

|---|-----|--------------------------------------------------------------|----|

|   | 1.7 | Thesis Objectives                                            | 28 |

| 2 | Del | ay Difference Analysis for Phase Synchronisation Computation | 31 |

|   | 2.1 | Proposed algorithm                                           | 32 |

|   | 2.2 | Parameters setting                                           | 37 |

|   |     | 2.2.1 Quantisation                                           | 37 |

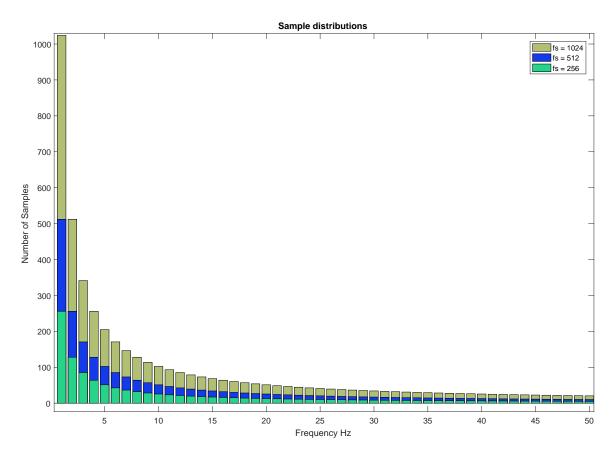

|   |     | 2.2.2 Sample distribution                                    | 37 |

|   |     | 2.2.3 Window length                                          | 39 |

|   | 2.3 | Verification                                                 | 40 |

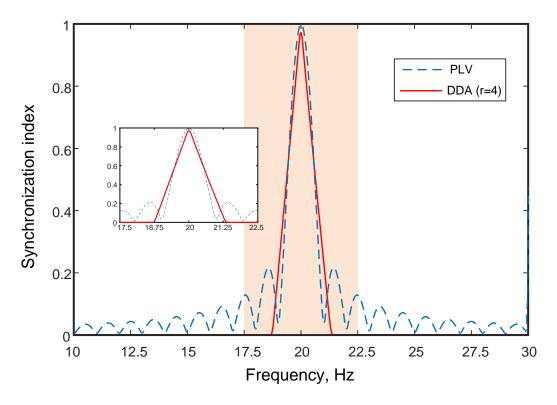

|   |     | 2.3.1 DDA-PLV correlation                                    | 43 |

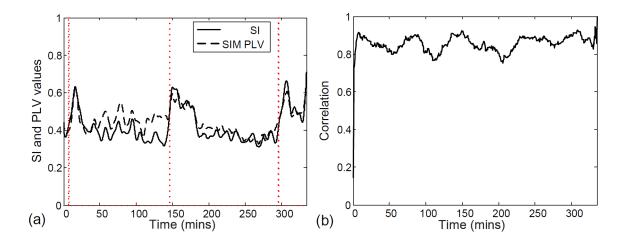

|   |     | 2.3.2 SNR                                                    | 44 |

|   |     | 2.3.3 Sensitivity                                            | 46 |

|   | 2.4 | Conclusions                                                  | 51 |

| 3 | Syn | chronisation Processor                                       | 53 |

|   | 3.1 | Overview                                                     | 54 |

|   | 3.2 | Design                                                       | 55 |

|   |     | 3.2.1 Minimum detection                                      | 55 |

|   |     | 3.2.2 Time stamp                                             | 57 |

|   |     | 3.2.3 Calculation                                            | 59 |

|   |     | 3.2.4 Filter                                                 | 60 |

|   |     | 3.2.5 Detect                                                 | 62 |

|   | 3.3 | Methods                                                      | 63 |

|   |     | 3.3.1 Design flow                                            | 63 |

|   |     | 0                                                            |    |

|   | 3.4 | Discussion                                                   | 68 |

|   | 3.4 |                                                              | 68 |

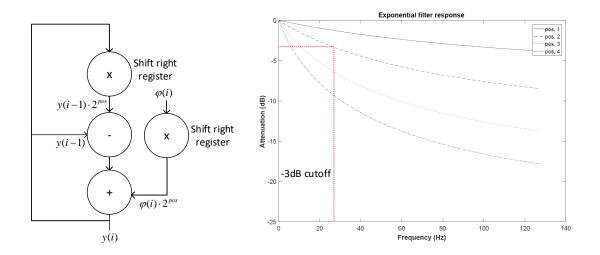

|                  |       | 3.4.3    | Filtering                                 | . 68  |

|------------------|-------|----------|-------------------------------------------|-------|

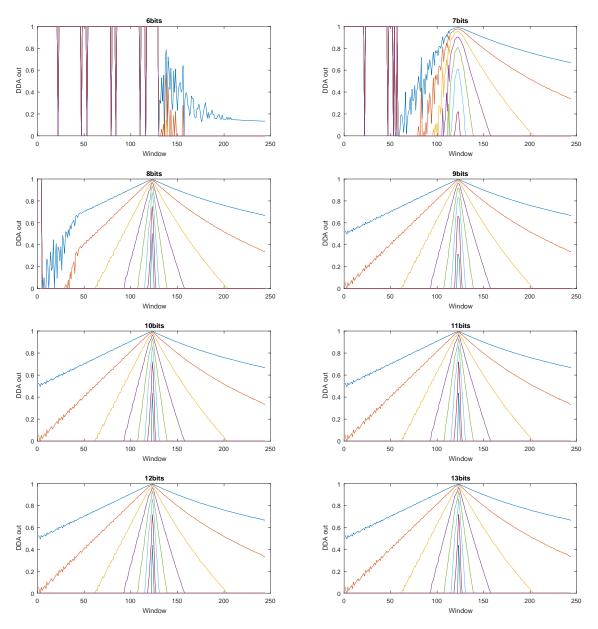

|                  |       | 3.4.4    | Power/Accuracy trade-off                  | . 69  |

|                  |       | 3.4.5    | Resource allocation                       | . 70  |

|                  | 3.5   | Experi   | mental results                            | . 72  |

|                  |       | 3.5.1    | Experimental Setup with Neural Recordings | . 74  |

|                  |       | 3.5.2    | Epilepsy Detection Results                | . 77  |

|                  |       | 3.5.3    | Functional Connectivity Results           | . 78  |

|                  | 3.6   | Conclu   | sion                                      | . 84  |

| 4                | Mu    | lti-char | nnel synchronisation processor            | 85    |

|                  | 4.1   | Overvi   | ew                                        | . 86  |

|                  | 4.2   | Design   |                                           | . 88  |

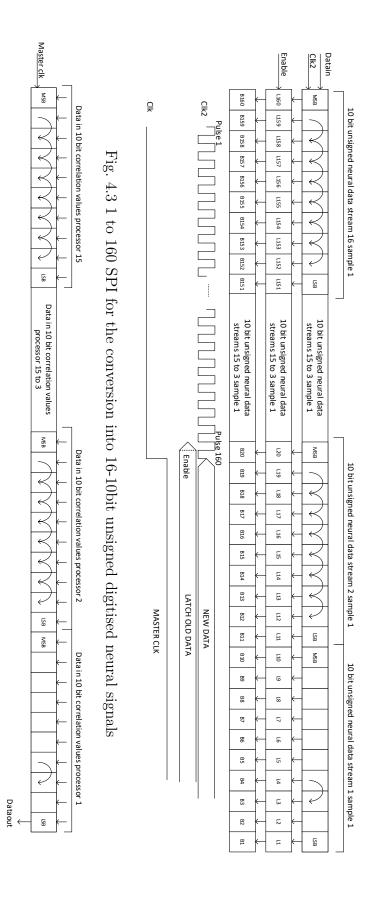

|                  |       | 4.2.1    | Input conversion SPI                      | . 88  |

|                  |       | 4.2.2    | Output conversion PSI                     | . 89  |

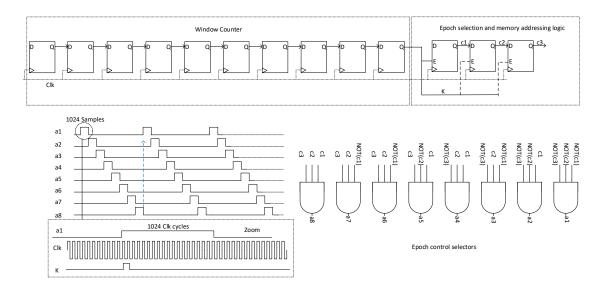

|                  |       | 4.2.3    | Epoch selection                           | . 91  |

|                  |       | 4.2.4    | Window, epoch and memory addressing logic | . 92  |

|                  |       | 4.2.5    | Flow                                      | . 93  |

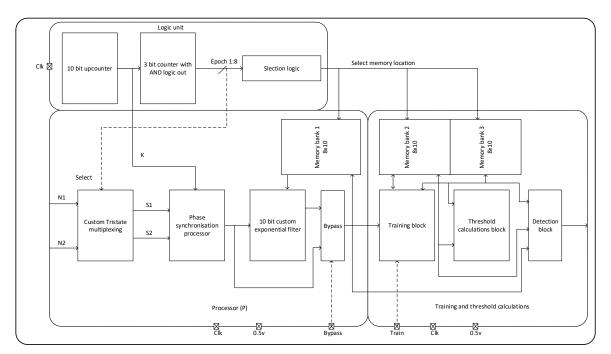

|                  |       | 4.2.6    | Neural multiplexing                       | . 94  |

|                  |       | 4.2.7    | Post processing                           | . 97  |

|                  |       | 4.2.8    | Training and Thresholds overview          | . 98  |

|                  | 4.3   | FPGA     | Implementation                            | . 104 |

|                  | 4.4   | Conclu   | sions                                     | . 110 |

| 5                | Cor   | clusior  | ns                                        | 111   |

|                  | 5.1   | Conclu   | sions                                     | . 112 |

| $\mathbf{R}$     | efere | nces     |                                           | 115   |

| $\mathbf{A}_{]}$ | ppen  | dix A    | Graph Theory concepts                     | 123   |

| Appen | dix B Code listings                                          | 129 |

|-------|--------------------------------------------------------------|-----|

| B.1   | Matlab Code DDA                                              | 129 |

| B.2   | Matlab Code Threshold                                        | 132 |

| В.3   | VHDL Code DDA                                                | 133 |

| B.4   | RTL-compiler                                                 | 148 |

| B.5   | MBED-C++ test platform code                                  | 149 |

| Appen | dix C Pseudo codes                                           | 155 |

| C.1   | Pseudo code DDA hardware flow                                | 155 |

| C.2   | Pseudo code for training and calculation hardware flow       | 157 |

| Appen | dix D Control signals for future 16-channel testing platform | 159 |

| Appen | dix E James Romaine, Publication list and curriculum         | 163 |

# List of figures

| 1.1  | Main lobes of the larger brain $\ldots \ldots \ldots \ldots \ldots \ldots$     | 7  |

|------|--------------------------------------------------------------------------------|----|

| 1.2  | Action potential and anatomy of the neuronal cell                              | 10 |

| 1.3  | Overview of common neuronal oscillatory bands                                  | 12 |

| 1.4  | Example of phase rotations around a stationary wave                            | 15 |

| 1.5  | Graph theory, application to real data                                         | 18 |

| 2.1  | Transition periods and approximated phases of two signals                      | 34 |

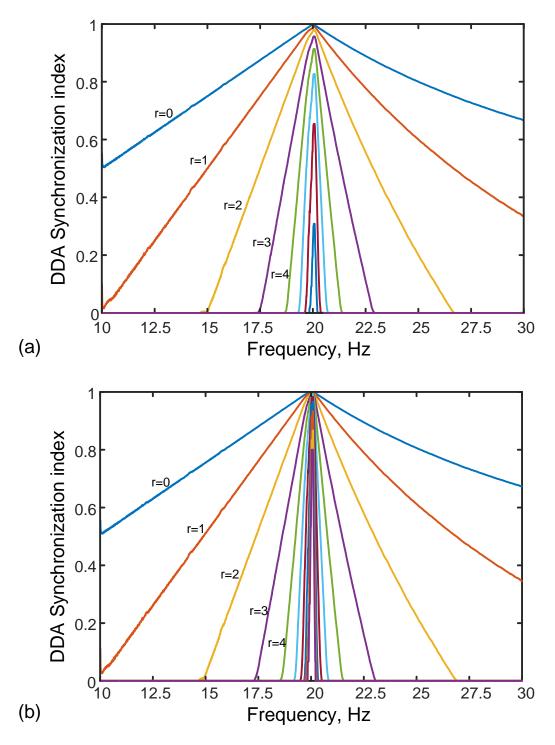

| 2.2  | Synchronisation indexes obtained through the DDA algorithm $\ \ldots \ \ldots$ | 35 |

| 2.3  | Results from DDA and Hilbert transform approaches $\ \ldots \ \ldots \ \ldots$ | 36 |

| 2.4  | Effects of quantisation on algorithm                                           | 38 |

| 2.5  | Effects of sample distribution on algorithm                                    | 39 |

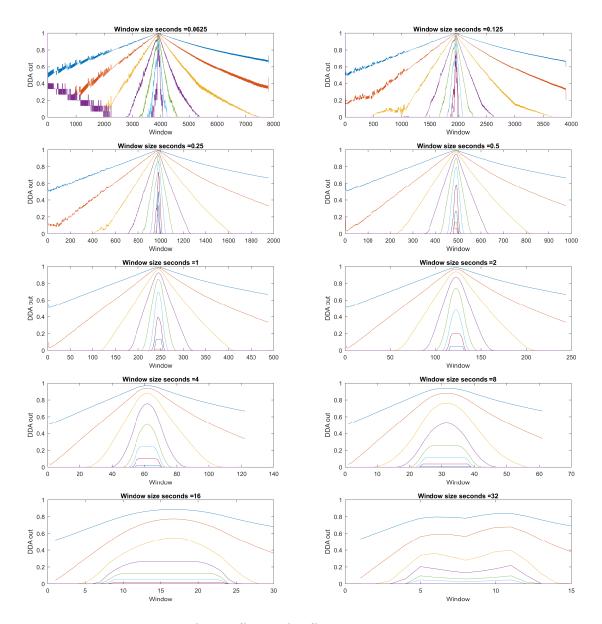

| 2.6  | Effects of window size on algorithm                                            | 41 |

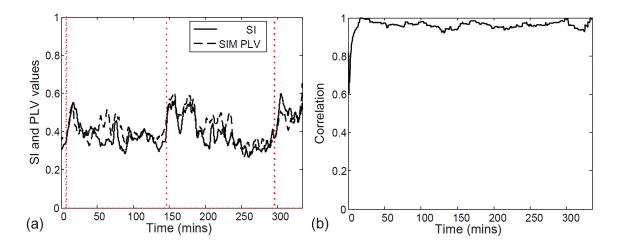

| 2.7  | $FR_1084_Block_0161, electrode positions M5$                                   | 43 |

| 2.8  | $FR_1084_Block_0161, electrode positions GA2 \dots \dots \dots \dots$          | 44 |

| 2.9  | SNR effects                                                                    | 45 |

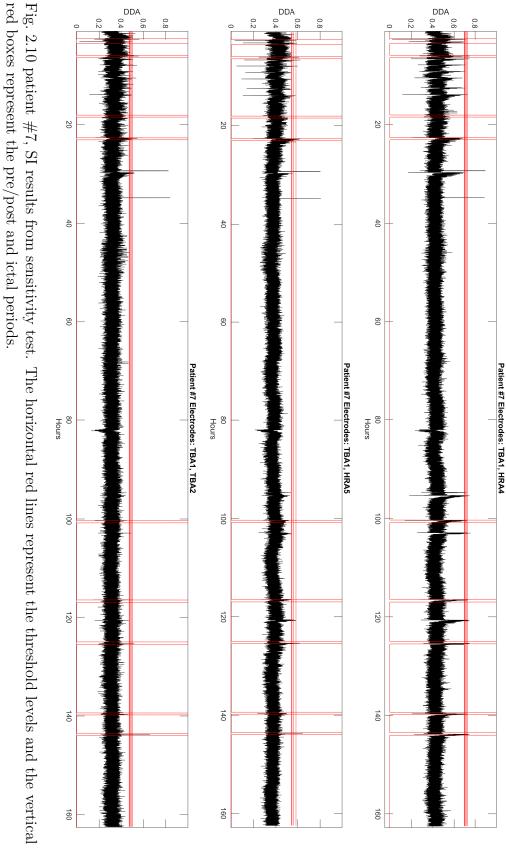

| 2.10 | patient #7, SI results from sensitivity test                                   | 48 |

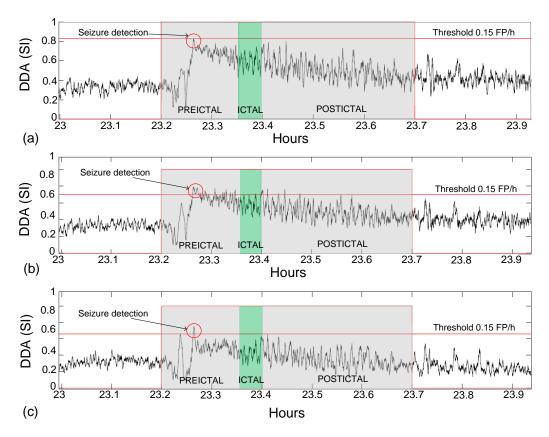

| 2.11 | Zoom synchronisation indexes for patient $\#7$                                 | 50 |

| 2.12 | Average Sensitivity against $FPR$ for DDA + SI and PLV + HT $ \dots  \dots$    | 50 |

| 3.1  | 2 channel synchronisation processor block diagram                              | 56 |

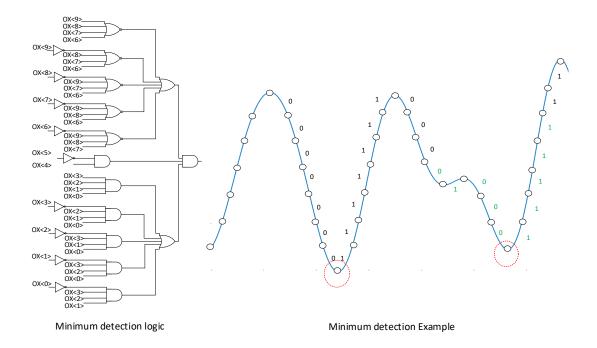

| 3.2  | Minama detection logic and application                                         | 58 |

| 3.3  | Exponential filter block diagram                                              | 62  |

|------|-------------------------------------------------------------------------------|-----|

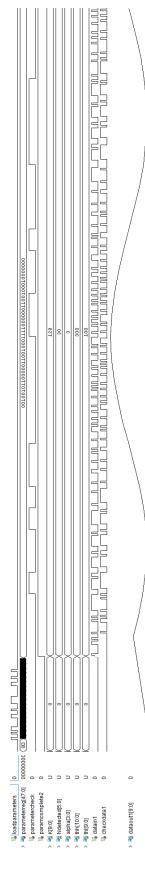

| 3.4  | VHDL simulation of parameters and verification                                | 65  |

| 3.5  | VHDL simulation of minima detection                                           | 65  |

| 3.6  | VHDL simulation showing the results for phi and detection                     | 65  |

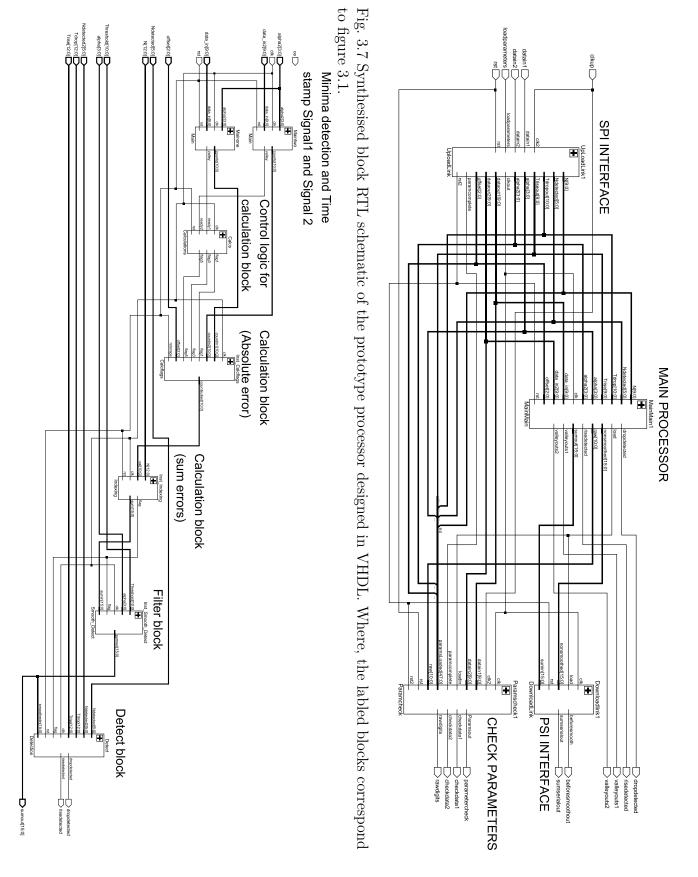

| 3.7  | VIVADO schematic of the prototype synchronisation processor                   | 66  |

| 3.8  | Detailed VIVADO schematic of the prototype synchronisation processor          | 66  |

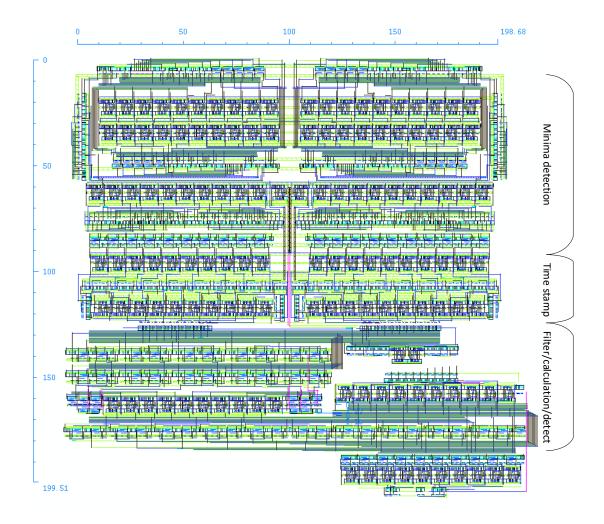

| 3.9  | CADENCE layout synchronisation processor                                      | 67  |

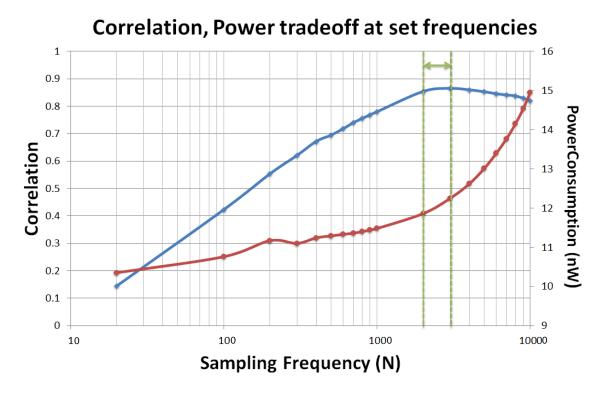

| 3.10 | 2 channel synchronisation processor correlation and power trade-off's $$ .    | 70  |

| 3.11 | Bar chart showing the FPGA resource allocation for the designed DDA algorithm | 71  |

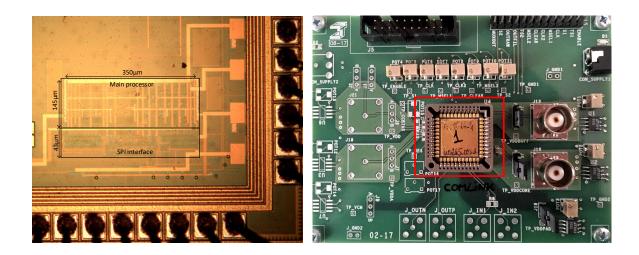

| 3.12 | AMS-0.18-micro microscopic view                                               | 72  |

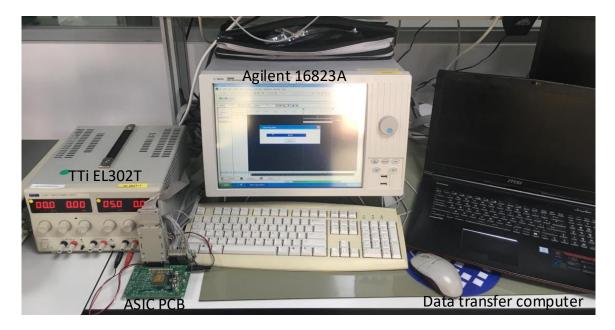

| 3.13 | test-setup                                                                    | 72  |

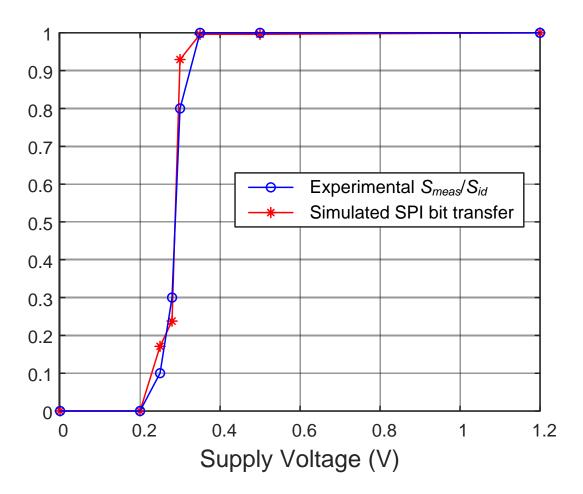

| 3.14 | spimeasurement                                                                | 73  |

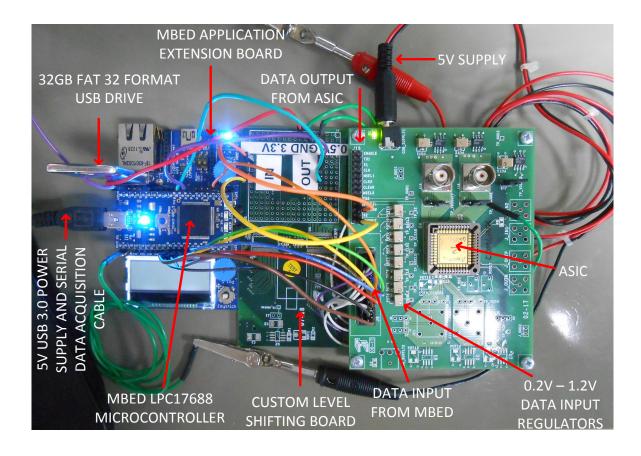

| 3.15 | mbed-setup                                                                    | 76  |

| 3.16 | $FR_1084_Block_0161, electrode positions M5$                                  | 77  |

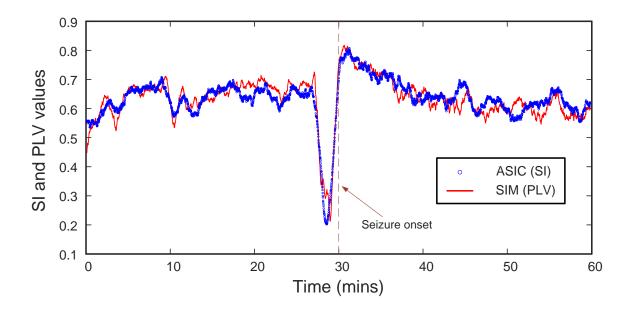

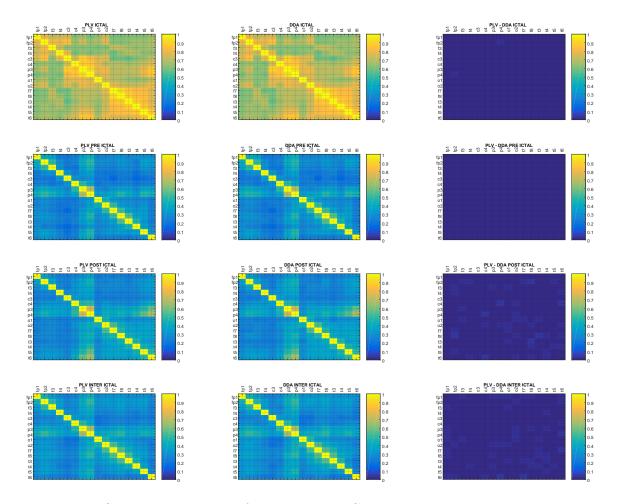

| 3.17 | EEG connectivity maps for patient #7                                          | 81  |

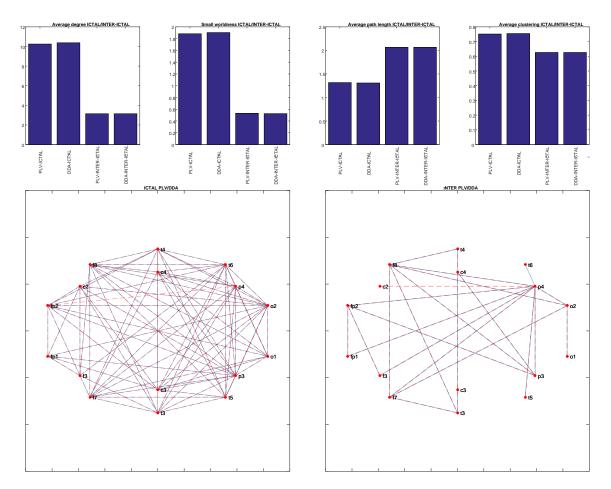

| 3.18 | Graph theory results for patient #7                                           | 82  |

| 3.19 | Graph theory contour map results for patient #7                               | 83  |

| 4.1  | 16-Channel ASIC implementation top level block diagram overview               | 87  |

| 4.2  | Microscopic view of 16-Channel ASIC                                           | 88  |

| 4.3  | 1 to 160 SPI for neural input data                                            | 90  |

| 4.4  | 160 to 1 SPI for captured synchronisation values                              | 90  |

| 4.5  | Control logic for 16-channel device                                           | 93  |

| 4.6  | 16-channel synchronisation processor flow                                     | 94  |

| 4.7  | Neural input multiplexing scheme and dedicated control logic                  | 96  |

| 4.8  | Modified exponential filter block diagram                                     | 98  |

| 4.9  | Training and calculation module block diagram                                 | 103 |

#### List of figures

| 4.10 | Dedicated control logic overview for memory latching               |   | 104 |

|------|--------------------------------------------------------------------|---|-----|

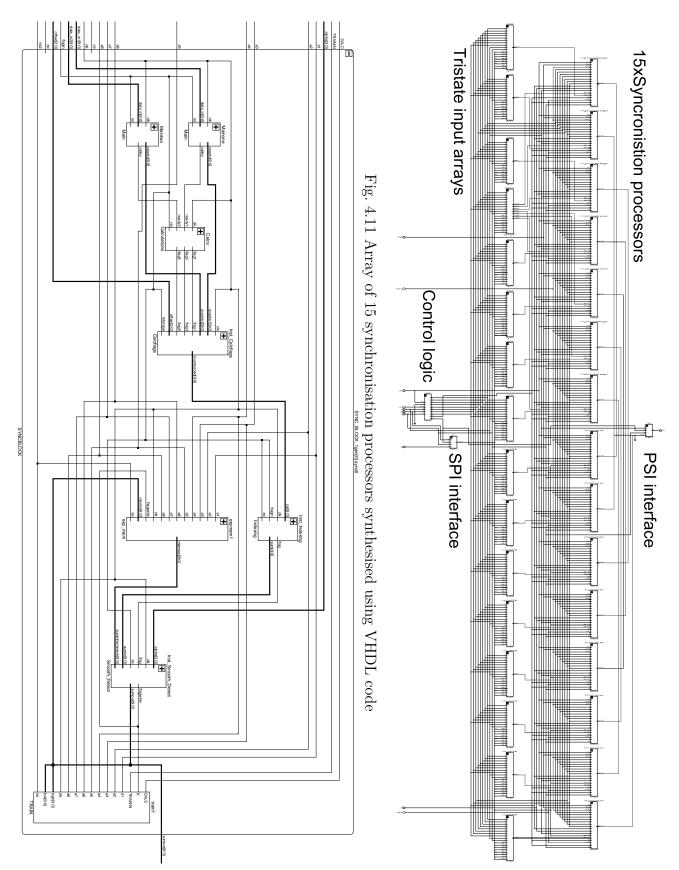

| 4.11 | Array of 15 synchronisation processors synthesised using VHDL code |   | 106 |

| 4.12 | Single synchronisation processor VHDL synthesis                    |   | 106 |

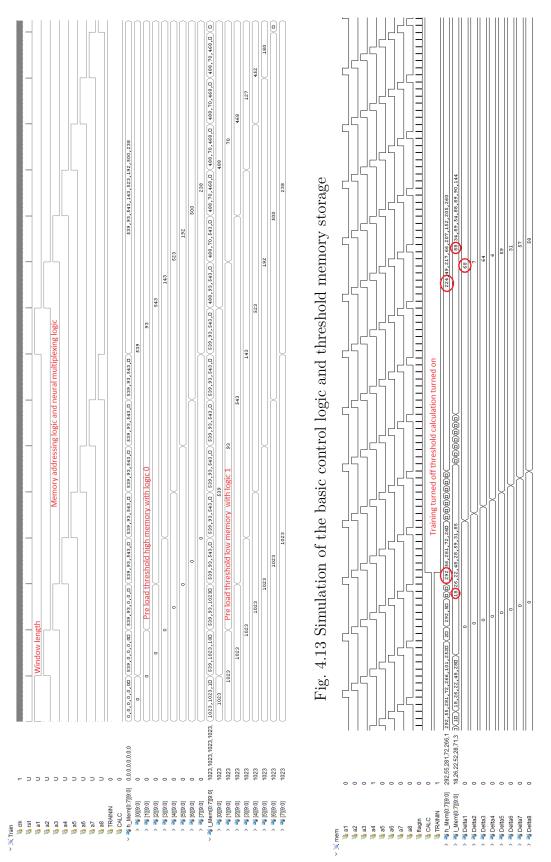

| 4.13 | Training logic VHDL simulation                                     |   | 107 |

| 4.14 | Training logic VHDL simulation2                                    | • | 107 |

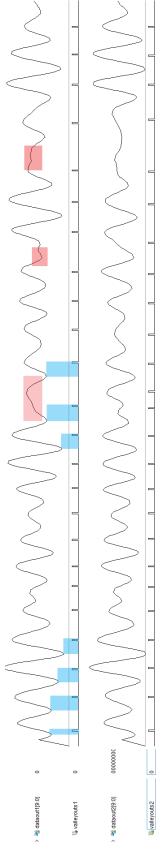

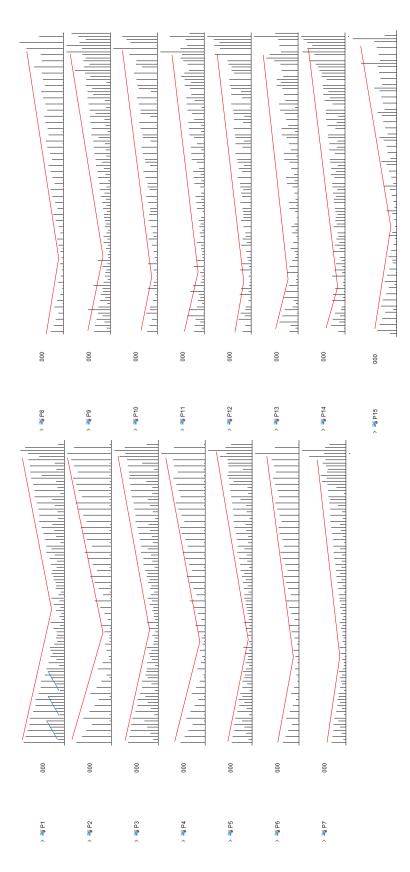

| 4.15 | Output results from VHDL simulation of 16-channel processor        |   | 109 |

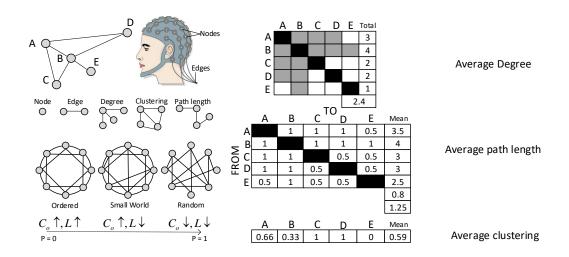

| A.1  | graphtheory basic concepts                                         | • | 127 |

## List of tables

| 1.1 | Basic overview of brain functions for specific lobes                                                            | 7   |

|-----|-----------------------------------------------------------------------------------------------------------------|-----|

| 1.2 | Synchrony in different neurological disorders                                                                   | 20  |

| 1.3 | State of the art comparison table                                                                               | 28  |

| 2.1 | Records used in the verification of the phase synchronisation processor                                         | 42  |

| 2.2 | DDA and PLV results sensitivity test                                                                            | 49  |

| 3.1 | Power breakdown of the synchronisation processor based on the blocks                                            |     |

|     | in Fig.3.1                                                                                                      | 75  |

| 3.2 | Normalised performance summary                                                                                  | 75  |

| 4.1 | Table showing which neural data streams are connected to specific processor during each of the 8 epochs of time | 92  |

| 4.2 | Table showing the memory allocation during calculation phase of the patient specific thresholds                 | 101 |

| 4.3 | Table showing the signals for processor 1 during VHDL simulation of 16-channel design                           | 108 |

| 4.4 | Table showing all design resource allocation for the DDA hardware implementation                                | 108 |

#### **Preface**

This thesis was written to give a broad overview of the work conducted during the doctoral scholarship over a period of approximately 5 years. The main goal during the life of the project was the design and implementation of low powered and lower resource consuming VLSI hardware, for the efficient and reliable detection of synchronisation between neural assemblies.

The work was conducted in several key stages:

Firstly, through the research of state of the art in the field of neurological disorders and synchronisation, we gathered a thorough understanding of the current limitations and design challenges faced in this field of study. Using this information, we then targeted the design of a new mathematical algorithm, which focused on solving the most commonly faced problems. Furthermore, to test the algorithmic design a MATLAB implementation was introduced which was compared against the state of the art in terms of comparable features and accuracy. At this point, important aspects are tested such as the signal-to-noise ratio, algorithmic sensitivity, sliding window size and sampling rate distribution to name a few.

To follow, the algorithm was implemented into a field programmable gate array (FPGA) using a hardware description language (VHDL), which allowed us to verify the algorithm running at the logic gate level. This also provided us with prototype metrics which could then be used to validate the scalability of the device compared to the state of the art.

The FPGA implementation of the design was later mapped into CADENCE as a register technology level (RTL) circuit. This design, operating at 1.2V, gave us a good estimation as to the real life functionality of the circuit and algorithmic design. Once the 1.2V design was verified at the RTL level in CADENCE, a 0.5V sub-threshold biased design was implemented using custom layout techniques. Afterwards, the ASIC design was tested in the laboratory using a mixture of test apparatus such as a logic analyser for basic variable verification and micro-controllers for longer in-depth neural signal simulations.

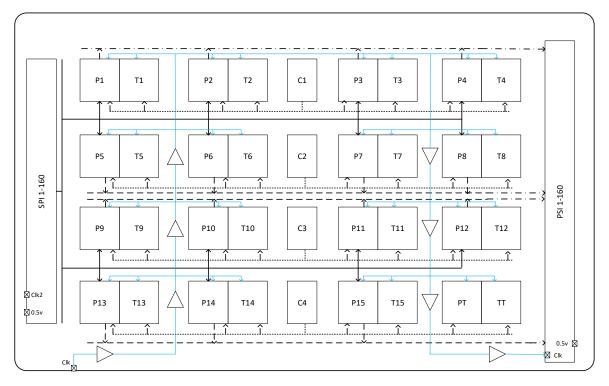

Later, a 16-channel mass VLSI implementation was integrated. This design incorporated 15 main synchronisation processors based on the previously integrated 2-channel processor. In order to integrate this design a similar method to that of the previous design was adopted. This included the FPGA implementation and verification before a CADENCE based custom layout and verification.

NOTE: Due to a change in the MPW policy of the selected foundry, AMS AG, regarding its 0.18µm CMOS process (MPWs were finally cancelled in 2018), the 16-channel VLSI DDA processor was received 13 months after the tape-out. The limited time that was available for the completion of the thesis meant that this design could not be tested in the laboratory. Nevertheless, FPGA simulations have been incorporated into the thesis as a verification of functionality.

#### Organisation

This thesis has been separated into five chapters.

Chapter 1 describes the most relevant principles needed for the rest of the Thesis. Starting with a brief overview of the anatomy of the brain at the system level ("the larger brain"), including its distinct regions and basic functions, we later go on to describe the anatomy of the brain at the cell level ("the smaller brain") and the electrical signals, such as action potentials (APs) and local field potentials (LFPs), which are involved.

Moving forward, we introduce the concept of phase and synchronisation in both stationary signals and neural signals. This includes the introduction of the most common methods of detection and how synchronisation is being treated as one of the most fundamental underlying principles for the encoding and transfer of information between neuronal clusters.

Afterwards, we give a small overview of some of the most common neurological disorders which suggests that synchronisation could be used as a tool for the detection of pathological states.

Finally, we introduce the most recent advances in hardware implementations for synchronisation detection algorithms.

Chapter 2 presents the proposed Delay Difference Analysis (DDA) algorithm for phase synchronisation computation. The chapter discusses the mathematical premises behind the algorithm and illustrates its functionality in real world scenarios. It also shows how parameters such as quantisation, sample distribution or window evaluation length, affect synchrony estimations.

Next the algorithm is verified in the Matlab environment using neural recordings from 10 epilepsy patients. These recordings sum in total over 1800 hours of neural data

List of tables 3

and contain over 60 annotated seizures. The noise tolerance and sensitivity performance of the DDA algorithm is evaluated and compared against more conventional techniques to give a true impression of the algorithms capabilities.

Chapter 3 introduce the design of a VLSI phase synchronisation processor based on the algorithm described in chapter 2. The chapter firstly gives a broad overview of the design including its strengths and weaknesses. Next, the steps followed towards the implementation of the VLSI design are presented. They included the design in an FPGA, followed by the synthesis with an RTL compiler and finally the custom layout in the CADENCE environment.

Then, the experimental results from the prototype are introduced. After describing the laboratory test setup, a breakdown of the design's power consumption is presented. Then, several measurements using neural recording data from the mentioned epilepsy dataset are presented. They include functional connectivity and graph theoretical results.

Chapter 4 includes the design and implementation of a multi-channel phase synchronisation processor based on the initial design in chapter 3. This section is laid out similar to the previous section in that firstly, all of the individual digital blocks and digital flow functionality is introduced. This is accompanied by many illustrations of the digital blocks as well an illustration of the overall flow and the implemented ASIC micro-photograph.

Next, a FPGA implementation of the VLSI circuit is introduced and system simulations are presented.

Finally, **Chapter 5** provides some final concluding comments and draw possible future work which will be conducted using the designed algorithm and VLSI implementations.

# Chapter 1 Introduction

#### 1.1 The larger brain

The human brain weighs approximately 1.5kg and accounts for only 2% the total weight of the average human. Nevertheless, it is the most diverse and complex organism known in the universe today. The brain is responsible for everything that we do in our everyday lives from basic motor functions such as, walking, eating or talking to sensory functions such as seeing, listening and touch. It is also responsible for our underlying cognitive abilities in the form of thinking, memories, attention, logical processing and reasoning. It also gives rise to consciousness, which is the state of being aware of one's surroundings and the ability to comprehend them. The brain also has some impressive attributes. It has been theorised that the brain has a storage capacity of upwards of a quadrillion bytes and can perform upwards of 10 quadrillion calculations per second. This complex organ has been extensively studied over the past centuries with new knowledge and understanding being discovered every day.

The larger brain is made up of the cerebrum, cerebellum and brain stem. The cerebrum itself is made up of two hemispheres, the left and right which make up the cerebral cortex. Although it is the largest and most distinguishable part of the brain it only consists of 16 billion of the estimated 100 billion total neurons.

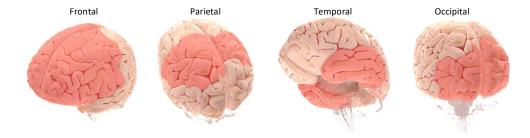

The cerebral cortex can be further broken down into four main lobes, namely, the frontal, parietal, temporal and occipital lobes.

The frontal lobe is the largest of the four main lobes and maintains connections to almost all other parts of the brain. Its main responsibilities include personality and decision making, as well as motor control. This lobe makes sense of the environment around us as well as making sense of memories and emotions. It also provides us with working memory which allows us to hold relative information for short periods in order to drive the attention span.

The parietal lobe interprets our sense of touch (somatosensation) and monitors the position of the body as well as the relative position of the limbs. It integrates information from senses in order to focus our attention on important tasks. It also receives information from the occipital lobe in terms of location, size and speed of objects and incorporates them into the sense of touch in order to interoperate our surroundings.

The temporal lobe is where memories, emotions and language comprehension are stored. It is also key to the recognition of objects, places and people.

| Frontal                      | Parietal                         | Temporal                  |

|------------------------------|----------------------------------|---------------------------|

| Regulation of personality    | Interoperates language and words | Understanding of Language |

| Behaviour and emotions       | Touch and pain                   | Long term Memory          |

| Judgement                    | vision                           | Hearing                   |

| Planning and problem solving | Hearing                          | Sequence and organisation |

| Speech                       | motor                            | Facial recognition        |

| Writing                      | sensory                          | Emotions                  |

| Smell                        | memory                           | Emotions                  |

| Intelligence                 |                                  |                           |

| Concentration                |                                  |                           |

| Self awareness               |                                  |                           |

| Emotional reactions          |                                  |                           |

Table 1.1 Table showing the basic control functions of the frontal, parietal and temporal lobes [1]

The occipital lobe is located at the far back of the cerebral cortex. It decodes information arriving from the retina. It mainly informs us of where, how and what we are seeing, via the detection of high contrast edges and their orientation and motion. This information is then passed to the parietal lobe for response mechanisms or to the temporal lobe to see if we recognise the object.

Fig.1.1 shows the relative positions and surface coverage of the four main lobes.[1], and Table 1.1 summarizes some of the basic functions for the frontal, parietal and temporal lobes.

The cerebellum is tucked underneath the occipital lobe and is actually small compared to the four main lobes. Nevertheless, the cerebellum contains approximately 70 billion neurons. This part of the brain is responsible for our talents from playing musical instruments to athletic agility. It does this by controlling complex movements, it detects errors and creates adjustments to compensate, which in turn strengthens neural circuits throughout the brain.

Fig. 1.1 Overview of the human brain including its four major regions of the cerebrum [1]

#### 1.2 Connectivity and the smaller brain

#### 1.2.1 Neurons

Neurons are the individual cells which make up the central nervous system. There exist many different types of neurons all of which are packed into small networks of upwards of 10000 neurons per network and are interconnected by kilometres of wiring per cubic millimetre. These are called individual neural circuits. Their main purpose is the transfer of information, which allows for the specific and complex movements, associated with human motor skills as well as allowing for cognitive perception and memory [2].

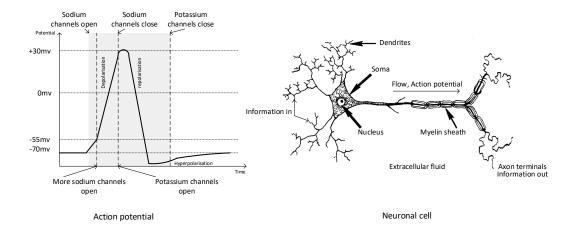

The basic neuron structure can be seen in Fig. 1.2. Consisting of three main parts. Firstly, the dendrites, which are the main collectors of information (they are analogous, to that of an input to a system).

The soma is the neuronal structure which is responsible for the central processing of the incoming information (similar to that of a systems function f(x)). The soma performs a non-linear threshold based comparison of the incoming information from the dendrites.

The axon, which is the final main component of the neuronal structure, is considered the main delivery system of information. This sends the soma generated information to other neurons within the network. At the end of each axon, there are axon terminals which connect to dendrites via synapses. In addition, there is a layer of fat which surrounds the axon known as the myelin sheath, which is an electrically insulating layer. The sheath regulates the proper transmission of electrical signals, helping speed up electrical transmission down the axon.

The transmitted information is referred to as an action potential (AP). The AP is a product of concentration gradients, which refers to the difference in ion concentrations inside and outside of the neuronal cell.

In general an AP is generated as follows. Firstly, neuronal cells are surrounded by an extracellular fluid (EF) which is full of positively charged sodium and potassium ions. While the inside of the neuronal cell there are also positively charged sodium and potassium ions. Nevertheless, the EF has many more positively charged ions than the inside of the neuronal cell. This leads to a high concentration gradient which causes a negative potential inside of the cell, known as a resting membrane potential (RMP).

The RMP is the state in which neurons spend most of their time, it is a negative concentration gradient of approximately -70 millivolts.

The membrane of the neuronal cell is very permeable to potassium ions, meaning that they leak out of the cell towards the EF via leakage channels. The membrane of the neuronal cell is also partially permeable to sodium ions which also flow out of the cell via sodium leakage channels. This creates instability within the cell. Nevertheless, a cell is constantly trying to to maintain its resting potential so it has tiny ion pumps which pump potassium back into the cell and sodium out.

In addition to the ion leakage channels and pumps, the neuronal cell also has two voltage controlled ion gates, one for sodium and the other for potassium. during RMP, these gates are always closed. When an event occurs at the dendrites of the cell, such as an AP sent from another neuron or a nerve input it causes the voltage-gated sodium channels to open, allowing sodium ions to flow into the cell which in turn causes a depolarisation in the current which tries to push the resting membrane potential towards 0 millivolts. If the membrane potential reaches a critical threshold, roughly speaking the threshold of approximately -55 millivolts an AP is formed. The AP itself is a positive electrical impulse which can push the membrane potential to +30 mV. Potassium channels then open and the sodium channels close in order to repolarise the cell. The basic overview of the AP can be seen in Fig. 1.2, which marks the opening and closing times of each voltage controlled gate. The potassium gate, however, stays open slightly too long creating a hyperpolarisation after the AP which then slowly moves back towards the resting potential [3, 4].

The interconnection between two neurons occurs at the synapse, which is an electro or chemical junction. The human brain contains anywhere between 100 and 500 trillion synapses of different varieties. Synapses are located at the dendrites (input terminals) and the axon terminals (output terminals).

In a chemical synapse, once the pre-synaptic (output terminal) AP or nerve impulse reaches the junction, a neurotransmitter chemical molecule is transmitted and diffused across a small space known as the synaptic cleft. These molecules then bind with neurotransmitter receptors on the postsynaptic (input terminal) neuron which opens or closes ion channels in the receiving neuron. This leads to a change in the membrane potential of the receiving neuron which can either lead to an AP or not. If the cell does fire it is what is known as an excitatory synapse, otherwise it is an inhibitory synapse. Since a neuronal cell has multiple synapse connections the firing of an AP is actually the combination or summation of all of the excitatory and inhibitory activity

at the input of the cell. If there are more excitatory signals, the membrane potential increase towards the AP threshold. For the signal to end, the synaptic cleft must then be cleaned of neurotransmitter.

Electrical synapse have a direct connection in the form of a gap junction, which allows current to flow extremely fast from one neuron to the next. This has the advantage of allowing neural circuits to synchronise rapidly. One of the benefits of an electrical synapse is the ability to allow current flow in both directions, meaning a bi-directional flow of information. It is believed that these types of synapses are used in fast response actions such as the 'fight or flight mode' in humans [5].

Fig. 1.2 Overview of neural connectivity, left, shows an example of an AP including approximate channel opening and closing times, right, shows the basic structure of a single neuron

#### 1.2.2 Neural oscillations

The term neuronal oscillation refers to periodic variations in neural activity. These variations can be measured at different scales such as the microscopic scale, which could consist of the measuring of direct synaptic currents which produce spike trains of AP's, the mesoscopic scale, which consists of the summation of many synaptic currents from a Local network, named a local field potential (LFP), or the macroscopic scale, in the form of electroencephalography (EEG) data, which is the measure of multiple local networks [6].

The history of neural oscillations started with the first ever recordings of individual microscopic recordings. First recorded by Richard Caton in 1875, a physician from

Liverpool, England, who used electrodes to probe the exposed surface of the brain in animals. Using a reflecting galvanometer, he was successful in monitoring signals in the microamperes range [7].

Nevertheless, it was the work of Berger in 1929, who first reported that he had identified oscillations of approximately 8-12Hz coming from the brain. Berger named this the alpha band since it was the first oscillation detected from such a source. This was early on in his pioneering work on the study of EEG. During one of his experiments Berger noticed that while the patients eyes were closed the prominent oscillations of the alpha band were visible. In the power spectrum the alpha waves produced a lone prominent peak of at approximately 12 Hz. However, when the patient opened their eyes the oscillations seemed to diminish in amplitude and become faster and more erratic, in a way the signals seemed to desynchronise and the prominent peak disappeared. This is known as the 'Berger effect'. Noting this, it was apparent that the alpha oscillations were attenuated by other more complex frequencies due to the visual stimuli originating from the occipital lobe.

Further observations of Hans Bergers works were carried out by W. Grey Walter in 1934, who devised an experiment entitled 'Thought and Brain: A Cambridge experiment', in Which one set of results was quoted as:

'When the eyes of a subject were open the lines were irregular, but when the subject's eyes were closed they showed as regular sinusoidal type signals occurring approximately every 10 seconds. Interestingly, When the subject closed their eyes and was asked to perform a simple arithmetic problem, the regular patterns disappeared, similar to that of when the patient's eyes were open. The lines continued to appear irregular until the simple problem was solved at which time the regular patterns reappeared'.

The fundamental observation by these pioneers revealed that the electrical fields recorded, must have been the combination of thousands of neurons firing in synchrony as stated by [8].

Since then, further advances in technology have led to the identification of multiple active frequency bands in which oscillations tend to occur. Namely,

- Infraslow (< 0.2Hz) and  $\delta = 0.2 3.5Hz$ . These wave patterns are usually seen during sleep of newborn infants or adults with serious brain diseases.

- $\theta = 4 7.5 Hz$ . These waves have been identified to mainly oscillate in the parietal and temporal regions of children's brains, and in healthy adults. Nonetheless, these slow varying oscillations are absent or indistinguishable under normal

conditions. Nevertheless, these oscillations do appear in healthy adults who show signs of emotional stress or frustration.

- $\alpha, \mu = 8 13Hz$ . These oscillations tend to occur during the period when a person is awake but in a very relaxed state, mainly with the eyes closed. The introduction of complex thought was proven to also diminish alpha waves causing alpha blocking due to complex thought.

- $\beta = 14 30Hz$ . The lower spectrum of the beta band usually falls into the same category as the alpha band, in that it can be disturbed by small amounts of complex activity or tension. The upper spectrum of the beta band is only affected by extreme thought processes, such as complex arithmetic. The beta band is usually considered as the awake and alert band, as we constantly process visual and auditory senses, as well as perform cognitive tasks throughout the day.

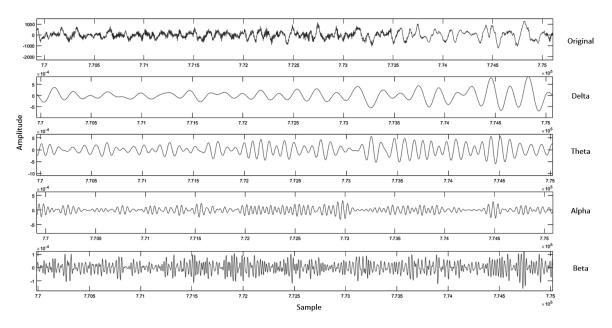

Other oscillatory bands include,  $\gamma = 30 - 90Hz$  and the upper limit of High Frequency Oscillations HFO > 90Hz. Recent research is, now starting to identify the gamma band as a communication layer between individual neural circuits [9]. Fig. 1.3, shows the decomposition of an original neural signal measured using EEG, into some common respective oscillatory bands.

Fig. 1.3 Example of the most common neuronal oscillatory bands

The interconnection of neurons forms several states of connectivity, three main types are as follows [10]:

- 1. structural connectivity, which refers to the anatomical connectivity via the structure of major tracts (i.e, white matter) connecting local and remote cortical regions of the brain.

- 2. functional connectivity, which is a statistical measure of the amount of connectivity in one region vs another and their dependence upon each other.

- 3. effective connectivity, the amount of connectivity in one cortical region which directly affects another cortical region by either activation or depression

#### 1.3 Phase and Synchronisation

#### 1.3.1 Basic concept

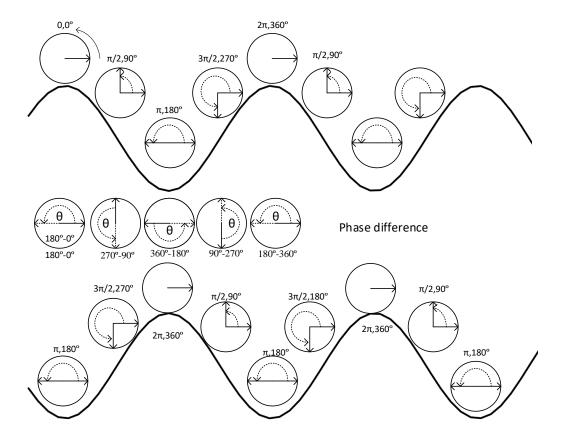

Phase is defined as the angular change in a signal over time. This can be represented as the anticlockwise rotation around the unit circle. Each adjustment is measured in terms of degrees, ranging from  $0^{\circ}$  to  $360^{\circ}$ , which indicates a full rotation around the unit circle. The rotation can also be measured in the SI unit radians, where  $360^{\circ} = 2\pi$ , radians.

A sinusoidal wave can be expressed as:

$$x(t) = A \cdot \sin(\omega t + \theta) \tag{1.1}$$

where, A is the amplitude,  $\theta$  (this has no relation to the theta oscillatory band described above) is the initial phase of the signal and  $\omega = 2\pi f$  denotes the rate of change of the vector rotation around the unit circle. The rate of change of phase increases or decrease as the frequency of the signal. If the frequency remains constant, the rate of change in phase will also remain constant. These types of signals are known as stationary signals.

Non-stationary signals, however, refers to a signal in which frequency changes over time, such as a synthetic sinusoidal chirp in which the rate of change in phase is constantly increasing. Another non-stationary source is that of EEG signals as LFP's tend to incorporate a wide range of frequencies.

Fig. 1.4, shows an example of the change in phase angle from a typical sinusoidal waveform and a cosine waveform. In this case, the first peak in the sine wave represents 0 radians and the first minimum in the cosine wave represents,  $\pi$  radians. As the two signals evolve, by the time the first minimum has appeared in the sine wave the phase angle has increased to  $\pi$  radians and the cosine has evolved to  $2\pi$  radians.

Since the sine wave and cosine wave are both stationary at 10Hz, the phase of both signals increases at a fixed rate. In comparative situations, it is desirable to take the phase difference between the two waveforms. This can give rise to information on their frequency offsets with respect to one another and can be calculated as:

$$\theta = \phi_{signal1} - \phi_{signal2} \tag{1.2}$$

Using specific markers in each signal such as minima or maxima, if the first derivative  $\frac{d(\phi_{signal1} - \phi_{signal2})}{dt}$ , is constant it can be said that the signals have a constant phase difference. Since the two signals in Fig. 1.4 are of a constant 10Hz, the phase difference between the two is constant. In this case, the constant phase change is  $\pi$  radians [11].

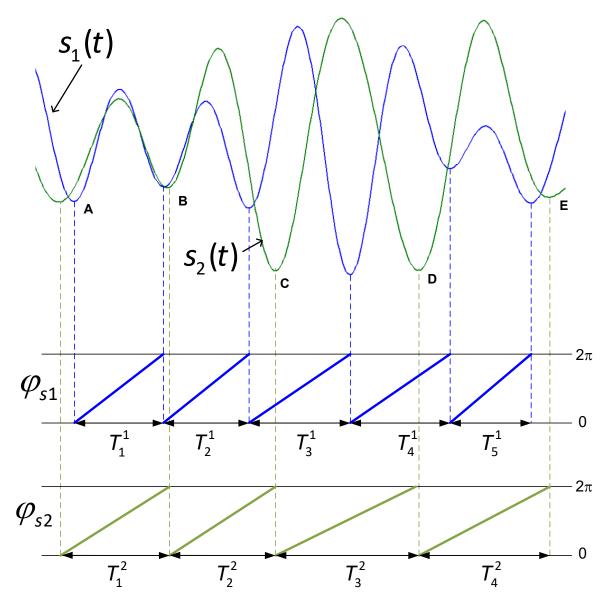

#### 1.3.2 Synchronisation and phase locking

In general terms, synchronisation is defined as any two-coupled (phase locked) oscillating systems, which have a relationship in both phase and frequency, but at the same time are independent of amplitudes. In non-disturbed and noise free systems synchronisation is usually described as the phase locking between instantaneous phase angles such that  $n \cdot \phi_{s1} - m \cdot \phi_{s2} = const$ , where  $\phi_{s1}$  and  $\phi_{s2}$  are the instantaneous phase angles of signal 1 and signal 2, respectively. m and n, are integer based weights which need adjusting based on the source of the oscillating system.

In the example in Fig. 1.4, although the two signals are in anti-phase there does exist a relationship between the two, in terms of phase locking.

In the case of non stationary signals, the phase locking condition should be considered as:  $|n \cdot \phi_{s1} - m \cdot \phi_{s2} - \delta| < const.$  Where  $\delta$ , is some average phase shift. This condition indicates that although the rate of change is not completely constant, it should reside (fluctuate) around a common constant [12].

Fig. 1.4 Phase: example of how phase rotates anti-clockwise around the unit circle in a stationary sine wave

In many cases of phase locking, the values m and n are usually set to a fixed 1:1 ratio. This is especially true if the signals originate from the same source such as the brain. Nevertheless, this phase locking attribute also holds true for signals of different frequencies, such as a stationary sine wave of 10Hz and a stationary sine wave of 20Hz. Although the frequencies are not the same there does exist a relationship in phase known as cross-frequency phase locking [13, 14].

#### 1.3.3 Synchronisation in the brain

The human brain seems to effortlessly communicate large quantities of information over multiple regions of the brain. However, one of the questions still unanswered is how neural communication between assembles throughout the larger brain actually works. That's to say, what decides what information is accepted or declined at the input of neural assemblies.

For many years it was assumed that general information processing was carried out by changes in firing patterns of so-called 'smart neurons'. which were dedicated to certain tasks and functions. Nevertheless, the work derived from Hans Berger and others has led to the question as to whether synchronisation of neural assemblies is the key to information processing and learning. The fact that neural oscillatory patterns exist, indicates that to some degree, neural synchrony at the given frequency must be intrinsic of some type of neural assembly collaboration.

Over recent years, new evidence is emerging that precise synchronisation and desynchronisation of neural assemblies may, in fact, be the key to the encoding of information transfer within the brain. This can be seen in various reviews and experimental results from [15–17]

Two main hypotheses have been suggested for the efficient transfer of information between neural circuits and brain regions. Namely, coherence, in the form of phase synchronisation and gating by inhibition.

Phase synchronisation could be used as an identifier between neural assemblies, similar to that of two radios set to the same frequency channel. If the presynaptic response from one neural circuit is oscillating at the correct excitability rate of the postsynaptic neurons, then the information is accepted. However, if the presynaptic response is oscillating at a different rate (different frequency), then the postsynaptic inputs of the second neural circuit then the information is blocked or diminished, as with a radios set at different frequencies.

In general terms, it is the phase of an oscillatory neuron population which determines their excitability, hence their spike timings. It is, therefore, the phase relationship between neuron populations which determines routing. This has been proposed to occur in the gamma band [18].

The flow of information is controlled by an increase of alpha oscillations which inhibit the neural population which is not firing in synchrony [19].

# 1.4 Synchronisation in pathological brain states

The topic of the synchrony between neural circuits for proper functional neuronal communication is a trending topic in neuroscience today.

When comparing brain states we like to consider the differences between normal and pathological brains, in order to identify the connectivity differences which may exist between them. Therefore, the data of pathological brain state patients is usually compared with that of a control subject (a patient with no medical history of neurological disorders). Nevertheless, in the case of neurological disorders such as epilepsy, the patients inter-ictal epileptic period can be associated with a non-pathological brain state, hence used in further analysis.

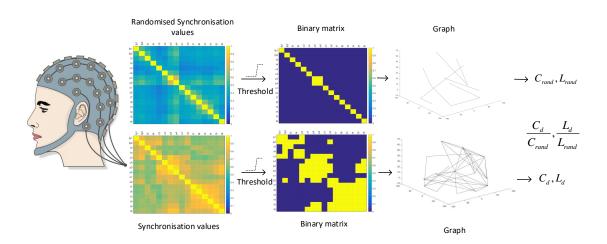

In order to distinguish between these two brain states, we use a common mathematical tool known as graph theory. This allows us to gather insight into the structural, functional and effective connectivity of the brain. It allows us to visualise the overall connectivity as a function of time.

For an in-depth look into the most common mathematical calculations and an overview of the steps required to calculate complex graph networks. Please see appendix A.

It is widely accepted that the brains neural communication is characteristic of a small world network where neural clusters are well connected and transfer information over small distances. Therefore comparing the small-worldness of a non-pathological brain state with that of pathological states can identify the changes which occur in terms of overall functional connectivity.

Fig. 1.5, shows an overview of the steps required for identifying small-worldness in epilepsy when taken from EEG sources.

Fig. 1.5 Example of how graph theory methods can be applied to real data. In this case, we compare an epileptic patients ictal period to that of their non ictal period. We then calculate M and A using an binary/undirected graph and calculate metrics as per needed

- 1. Firstly, all synchronisation values for every possible combination of electrode positions are computed, creating a O = NXM matrix. Where N corresponds to the electrode combination and M corresponds to each synchronisation value for the given electrodes over time.

- 2. Next, two matrices G1 = NXN For the non ictal period and G2 = NXN for the ictal period are constructed. This is done by creating a single mean representative value for each electrode combination from O such that:

$$G_{x(i,j)} = \frac{1}{M} \sum_{z=0}^{M} O_{i,j}$$

(1.3)

3. The next step is to apply thresholds to each matrix G, for the purpose of creating two binary based adjacent matrices  $A_x$ . The threshold which is applied is subject to the experimental data and the related subject at hand. In many cases, various thresholds are tested. This allows for the identification of the strongest connections and builds 3d topologies which give rise to information on C, L, k.

$$\begin{bmatrix} \phi_{11} & \phi_{12} & \phi_{13} & \dots & \phi_{1n} \\ \phi_{21} & \phi_{22} & \phi_{23} & \dots & \phi_{2n} \\ \vdots & \vdots & \vdots & \ddots & \vdots \\ \phi_{d1} & \phi_{d2} & \phi_{d3} & \dots & \phi_{dn} \end{bmatrix} = \begin{bmatrix} 0 & 0 & 1 & \dots & 0 \\ 1 & 0 & 1 & \dots & 1 \\ \vdots & \vdots & \vdots & \ddots & \vdots \\ 0 & 0 & 1 & \dots & 1 \end{bmatrix}$$

4. Finally, we can calculate  $\lambda$ ,  $\gamma$  and  $\eta$ , by calculating the mean clustering coefficients and the mean shortest path lengths to distinguish the small-world characteristics and small-worldness.

#### 1.4.1 Synchrony in neurological disorders

Although each neurological disorder has distinct causes and effects, synchrony has been found to manifest itself as an identifier, to distinguish between the normal and neurologically damaged brain. Table 1.2 [20], shows an overview of the most common neurological disorders as described above and how long and short-range communication is affected by increases or decreases in synchronisation. Other numerical methods such as graph theoretical analysis (please see appendix A) have also been shown to be a useful tool in the identification of both functional and structural connectivity.

In Alzheimer Disease (AD) synchronisation has been observed to increase in the  $\theta$  and  $\delta$  bands whilst, conversely, reducing in both the  $\alpha$  and  $\beta$  bands at resting state. Using a synchronisation likelihood (SL) measure, it was determined that these bands decreased in synchronisation over both long and short range recording sites [21–23]. Whilst global efficiency measures are higher in AD patients compared to the normal brain, the brain's ability to synchronise decreased significantly over multiple EEG bands in AD patients when their eyes were closed according to [24]. Synchronisation in AD patients has also been analysed in patients during memory working tasks. These include EEG and functional Magnetic Resonance imaging (fMRI) analysis of functional connectivity. Once again it was shown that a decrease in synchronisation was present when compared to control patients specifically in the  $\alpha$  and  $\beta$  bands [25].

The way our brain synchronises does not just affect cognitive functions. In fact, there is evidence which suggests that synchronisation in the  $\beta$  band is related to pre-motor movements (i.e preparation for movement). Nevertheless, once the actual movement takes place the  $\beta$  activity is replaced by  $\gamma$  activity [26, 27]. Moreover, there is evidence to suggest that an increase in  $\beta$  activity could be responsible for tremors in Parkinson Disease (PD) [28]. Where in patients who do not suffer from PD a short

| Disorder      | Neural synchrony                                                  |

|---------------|-------------------------------------------------------------------|

| Epilepsy      | Increase in local synchrony and evidence for long range reduction |

| Schizophrenia | Reduction in local and long range synchrony                       |

| Alzheimer     | Reduced synchrony, evidence for reduced functional connectivity   |

| Parkinson     | Increase in synchrony                                             |

Table 1.2 Synchrony in different neurological disorders.

period of  $\beta$  synchrony prior to a motor movement is replaced by fast  $\gamma$  bursts during the movement (where the  $\beta$  oscillations are dulled by inhibition), in patients with PD, however, the hypersynchronous  $\beta$  activity cannot be dulled and hence the  $\gamma$  oscillations responsible for the movement cannot take place [29].

It has been proposed that memory, attention and perceptual organisation are associated with synchronisation in the  $\beta$  and  $\gamma$  bands [30]. Various studies of Schizophrenia (SZ) show that a deficit in perceptual organisation is a common symptom and could be related to a reduction in synchrony in the  $\beta$  and  $\gamma$  bands [20].

Epilepsy (EP), on the other hand, is a well studied neurological disorder with overwhelming evidence suggesting that seizures occur due to hyper-synchronous networks. High-frequency oscillations in the  $\gamma$  band have especially been observed in EEG both during the ictal and pre-ictal periods [31]. It has also been observed that neurons synchronise with high precision in the  $\beta$  band pre seizures, however, synchronous activity is reduced during the ictal event [32]. Conversely, a decrease in synchronisation was proposed by Le Van Quyen et al. who examined the synchronous activity of eight patients finding a pre-ictal reduction in the  $\beta$  band in 77% of seizures [33].

## 1.5 Phase synchronisation methods

## 1.5.1 Analytical measures

Two main closed-form analytical approaches have been proposed for the estimation of phase angles. One is based on the Hilbert Transform and the other on the Wavelet Transform.

The Hilbert transform (HT) creates a projection of the original signal on to the imaginary plane in such a way that positive frequencies are phase shifted by  $-\pi/2$  and negative frequencies by  $+\pi/2$ , while keeping the amplitude unaffected. Analytically, the

Hilbert transform  $\tilde{s}(t)$  can be interpreted as the convolution of s(t) with the function  $h(t) = 1/(\pi t)$  and is given by [34]:

$$\tilde{s}(t) = \frac{1}{\pi} \cdot p.v \int_{-\infty}^{+\infty} \frac{s(\tau)}{t - \tau} \cdot d\tau \tag{1.4}$$

Where the integral is defined in terms of the Cauchy principal value p.v and  $\tilde{s}(t)$  is a (90°) phase shifted version of the original signal, s(t).

In continuous time signals the HT can be represented as the convolution of a real signal s(t) and a function  $h(t) = \frac{1}{\pi t}$ , such that  $\tilde{s}(t) = s(t) * \frac{1}{\pi t}$  [35].

In the frequency domain the HT can be written as:

$$\tilde{s}(f) = X(f) \times (-jsgn(f)).$$

(1.5)

Where (-jsgn(f)), is the HT of X(f) [35].

An analytical construct introduced by Gabor in 1946 utilises the HT, to create an analytical signal, given by:

$$s_a(t) = s(t) + j\tilde{s}(t) = A(t)e^{j\phi(t)}$$

(1.6)

The resulting complex signal  $s_a(t)$ , has the property that there exist no spectral components for negative frequencies, that's to say the Discrete Time Fourier transform of  $s_a(t)$ , is  $S_a(e^{j\omega}) = 0, -\pi < \omega < 0$ .

The instantaneous phase of the analytical signal  $s_a(t)$  can be calculated as:

$$\phi(t) = \tan^{-1} \left[ \frac{\tilde{s}(t)}{s(t)} \right] \tag{1.7}$$

Two other important metrics can be extracted from the HT. Firstly, the instantaneous amplitude of the signal, which can be extracted as [36]:

$$A(t) = (s(t)^{2} + \tilde{s}(t)^{2})^{\frac{1}{2}}$$

(1.8)

Secondly, the instantaneous frequency, which is given as the first derivative of the phase,

$$\omega(t) = \frac{d\phi}{dt} \tag{1.9}$$

The HT, however, is a linear function which in retrospect only works on stationary signals. Nevertheless, an adaptation of the HT can be used known as the Hilbert-Huang Transform (HHT).

The HHT incorporates an empirical mode decomposition (EMD) to the signals before taking the HT. The EMD consists of breaking down the signal into a finite number of components which are called Intrinsic Mode Functions (IMFs). These are extracted from an arbitrary time series x(t), by means of *sifting*. In order to sift all extrema, both maximum and minimum. The first IMF can be extracted as [37]:

$$h_1(t) = x(t) - m_1(t).$$

(1.10)

Where, x(t) is the time series in question and  $m_1(t)$ , is the mean of the upper and lower envelope derived from the extrema.

However,  $h_1(t)$ , is usually not sufficient to satisfy the constraints of an IMF and hence the process is repeated such that:

$$h_{11}(t) = h_1(t) - m_{11}(t). (1.11)$$

Where  $m_{11}(t)$ , is the mean of the upper and lower envelopes of  $h_1(t)$ .

In general, the process is as follows:

$$h_{1k}(t) = h_{1(k-1)}(t) - m_{1k}(t). (1.12)$$

where k is the number of iterations to find the first IMF  $C_1(t) = h_{1k}(t)$ .

Furthermore, the residual part the signal should be obtained from such that:

$$h_1(t) = x(t) - c_1(t).$$

(1.13)

at the end of the process the original signal can be represented as:

$$x(t) = \sum_{i=1}^{n} c_i(t) + r_n(t).$$

(1.14)

The HT is then performed on each IMF [38]:

$$c_{ai}(t) = c_i(t) + j\tilde{c}_i(t) \tag{1.15}$$

The instantaneous phase of the signal can be extracted as:

$$\phi_i(t) = \tan^{-1} \left[ \frac{\tilde{c}_i^2(t)}{c_i^2(t)} \right]$$

(1.16)

A similar approach for estimating phase angles [39] uses a definition based on the Wavelet Transform (WT). Here, the phase variable is defined as,

$$\varphi_s(t) = \arctan \frac{\operatorname{Im}(W(t))}{\operatorname{Re}(W(t))}$$

(1.17)

where  $\text{Im}(\cdot)$  and  $\text{Re}(\cdot)$  denote imaginary and real part, respectively, and W(t) is the convolution of the band-limited signal s(t) with a Morlet wavelet  $\psi(t)$ ,

$$W(t) = \int_{-\infty}^{+\infty} \psi(t - \tau) s(\tau) \cdot d\tau$$

$$\psi(t) = \exp\left(\frac{-t^2}{2\sigma^2}\right) \cdot \exp\left(j\omega_0 t\right)$$

(1.18)

where  $\sigma$  is the decay rate of the wavelet and  $\omega_0$  is the centre frequency of the signal band. Both analytical methods give similar results when applied to neurophysiological data [40].

The Phase Locking Value (PLV) or mean phase coherence usually accompanies the HT or WT methods as an index for quantifying the amount of synchronisation between two signals.

$$PLV = \left| \frac{1}{N} \sum_{k=0}^{N-1} e^{j\phi(t)} \right| = \frac{1}{N} \cdot \sqrt{\left[ \sum_{k=0}^{N-1} \cos(\Delta\phi_k) \right]^2 + \sum_{k=0}^{N-1} \sin(\Delta\phi_k)}^2$$

(1.19)

The PLV converts instances of the relative phase  $\Delta \varphi$  into unit vectors on the complex plane. If N of said vectors all have the same instantaneous phase (i.e the same vector direction) then the PLV will average out to 1 which equates to fully coupled oscillations for that period. However, in the case that the relative phase angles are very different the PLV will result in a value close to 0.

In some cases, a normalised PLV is more desirable than raw values as it gives a better approximation of the difference between normal state PLV and large changes, due to stimulus. The normalised values can be extracted as,

$$PLV_{norm} = \frac{PLV - mean(PLV_{ts})}{\sigma(PLV_{ts})}$$

(1.20)

Where ts, is a small baseline selection of samples taken before the episode. In this case,  $\sigma$ , represents the standard deviation of the baseline.

This metric is actually based on the Z-score and provides a zero mean offset.

#### 1.5.2 Numerical measures

Phase synchronisation measures can be alternatively derived from the phase space trajectories of the signals. Using time-delay embedding procedures [41], the phase space trajectory of a time series  $\{s(k)\}$  is obtained by constructing the vectors,

$$\vec{S}_i = \{s(j), s(j+d), \dots, s(j+(m-1)d)\}$$

(1.21)

where  $i = 1 \dots N$ , j = i + mod[N - (m-1)d],  $m \ge 1$  is the embedding dimension and  $d \ge 1$  is an arbitrary but fixed time increment.

Based on this topological representation, the phase synchronisation between two signals can be estimated by computing the cross-correlation between the probabilities of recurrence in their respective phase spaces [42]. This approach has been used recently for quantifying functional connectivity in EEG recordings [43]. The probability of recurrence of a signal measures the likelihood that each phase space vector returns to its neighbourhood after a time delay  $\tau$ . It is calculated as:

$$p_r(\tau) = \frac{1}{N - \tau} \sum_{i=1}^{N - \tau} \Theta(\epsilon - \|\vec{S}_i - \vec{S}_{i+\tau}\|)$$

(1.22)

where  $\epsilon$  is a pre-defined distance threshold,  $\|\cdot\|$  is a norm to calculate the distance between vectors and  $\Theta$  is the Heaviside function. The cross-correlation CPR of two trajectories is calculated as:

$$CPR = \frac{\left\langle (p_{r,1}(\tau) - m_1) \cdot (p_{r,2}(\tau) - m_2) \right\rangle}{\sigma_1 \cdot \sigma_2} \tag{1.23}$$

where  $m_1$  and  $m_2$  are the mean, and  $\sigma_1$  and  $\sigma_2$  are the standard deviations of  $p_{r,1}(\tau)$  and  $p_{r,2}(\tau)$ , respectively. If both signals are in synchrony, their probabilities of recurrence will peak at the same time and  $CPR \sim 1$ . Contrarily, if the signals are not synchronised, low values of CPR can be expected.

Numerical techniques have been also proposed for the quantification of synchrony, as an alternative to the PLV index in 1.19 [44]. Assuming that the phase angles of both signals have been previously estimated, a synchronisation index can be calculated based on the Shannon entropy of the phase difference distribution. Having an estimate  $P_{se}(l)$ , l = 1, ..., L of the relative frequency of finding a phase difference  $\Delta \varphi = \varphi_{s1} - \varphi_{s2}$  in a

certain bin l, the index is given by,

$$S_{se} = 1 + \frac{1}{\ln(L)} \sum_{l=1}^{L} P_{se}(l) \cdot \ln[P_{se}(l)]$$

(1.24)

where L is the number of bins. Note that  $S_{se}$  is comprised in the interval [0,1], where  $S_{se} = 0$  corresponds to a uniform distribution (no synchronisation) and  $S_{se} = 1$  corresponds to a distribution localised in one point. The estimate of this index heavily depends on L [44].

Another synchronisation index is based on the conditional probability  $P_{cp}(k, l)$  to find the phase of a first signal in a bin k when the phase of the second signal falls in the l-th bin, l = 1, ..., L. Denoting as  $M_l$  the number of hits of the second signal in the l bin, a synchronisation index can be defined as,

$$S_{cp} = \frac{1}{L} \sum_{l=1}^{L} \left| \frac{1}{M_l} \sum_{k=1}^{M_l} \exp[jP_{cp}(k, l)] \right|$$

(1.25)

It has been found that this index is particularly suitable for revealing weak interactions between signals [44–47].

# 1.6 VLSI implementations of PS estimators

As mentioned in Sec.1.5.1, one popular approach for the calculation of the instantaneous phase of a signal relies on the construction of the analytic representation  $s_a(t) = s(t) + j\tilde{s}(t)$ , where  $\tilde{s}(t)$  is the Hilbert Transform of s(t) [see 1.4]. Using time-frequency domain techniques, the Hilbert Transform can be derived by [48] (i) obtaining the Fourier transform of s(t), (ii) nulling the negative frequency components, (iii) calculating the inverse Fourier transform and (iv) taking the imaginary part of the result. Given the non-stationary nature of neural signals, the Fourier transform should be applied over short intervals. This suggests the use of the Short Time Fourier Transform (STFT) algorithm instead of the classical Fast Fourier Transform (FFT) [36]. 1.4 and 1.19

A simpler method for the generation of the analytic signal representation  $s_a(t)$  uses Hilbert Transformers based on digital filtering. These transformers can be implemented in complex domain or formed by the combination of two sub-components; a Hilbert filter with ideal transfer function -jsgn(f) for the generation of the imaginary part of  $s_a(t)$ , and a delay equal to that of the Hilbert filter for the real part. In both cases, the total group delay of the signal components should be kept constant to not cause phase errors. The vector analyzer presented in [49] follows the second implementation approach and employs 16-tap Hilbert finite impulse response (FIR) filters for obtaining  $\tilde{s}(t)$ , and 16-tap All-Pass FIR filters for implementing the delay. In a more recent implementation [50], the in-phase and quadrature components are directly provided by the mixed-signal acquisition front-end, and four 64-tap FIR filters are used for band selection.

Another transform-based approach for deriving the instantaneous phase of a signal uses Wavelets (see 1.18). In this case, the on-chip implementation of the method requires Multiply-and-ACcumulate (MAC) processors to correlate the input time series with the wavelet templates. As an example, [51] proposes a charge-recycling mixed-signal MAC processor for epilepsy detection in which time series of 1024 samples are serially loaded and correlated in parallel with all the Morlet wavelet templates (coded in 32 frequency bins with 4-bit coefficient resolution) stored in the on-chip memory.

The trigonometric functions involved in 1.7 and 1.17 as well as the computation of the phase locking value in 1.19 can be readily implemented by CORDIC (COordinate Rotation DIgital Computer) units. This is actually done in [52] where a digital signal processing (DSP) block formed by three 16-bit CORDIC cores and two 32-tap moving average FIR filters is used for computing the phase locking value (PLV) from the analytical signal  $s_a(t)$ .

Numerical methods for computing PS, such as the one based on probabilities of recurrence,  $p_r(\tau)$ , described in Sec. 1.5.2, typically use simpler logic than transform-based techniques at the price of increased latency and more memory resources. Thus, for instance, the evaluation of  $p_r(\tau)$  in 1.22 requires the collection and combination of phase space trajectories, demanding for a large memory allocation. Nevertheless, it is worth observing that, depending on  $\tau$ , there are coincident terms in the sum 1.22. This opens doors for reducing the computational complexity of the algorithm by avoiding recalculations. This is actually the approach followed in [53], where a differential scheduling for the computation of the correlation integral of a signal (similar to the calculation of recurrences) allows for a substantial reduction in complexity. Following the calculation of  $p_r(\tau)$ , a MAC unit should be used for the calculation of the cross-correlation in 1.23 to serve as a synchronization index.

As shown in 1.24 and 1.25, numerical methods can also be used for the computation of synchronization indexes. Although the computational complexity is relaxed as compared to PLV (in particular for the index based on Shannon entropy), long sliding

|      | Process               | Supply            | Core Area             | Input rate     | Clk Freq.             | Power cons.            | Computation capability                                     |

|------|-----------------------|-------------------|-----------------------|----------------|-----------------------|------------------------|------------------------------------------------------------|

| [49] | $0.13 \mu \mathrm{m}$ | 1.2 V             | $1.86~\mathrm{mm^2}$  | 7.2kHz (8-bit) | 10MHz                 | $400~\mu\mathrm{W}$    | 32 input-pairs multiplexed phase synchronization processor |

| [50] | $0.13 \mu \mathrm{m}$ | 1.2 V             | $1.27~\mathrm{mm^2}$  | NA             | NA                    | $260~\mu\mathrm{W}$    | 32 input-pairs multiplexed phase synchronization processor |

| [51] | $0.35 \mu \mathrm{m}$ | $1.65~\mathrm{V}$ | $16~\mathrm{mm}^2$    | NA             | 50 Hz                 | $NA^a$                 | 128×1024 binary MAC operator                               |

| [48] | $0.13 \mu \mathrm{m}$ | 1.2 V             | $1.18~\mathrm{mm^2}$  | 40kHz (16-bit) | $10.24\mathrm{MHz}$   | $3.64.4~\mu\mathrm{W}$ | 16-channel multiplexed 16-bit Hilbert Transform block      |

| [52] | $0.13 \mu \mathrm{m}$ | $0.85~\mathrm{V}$ | $0.178~\mathrm{mm^2}$ | 1.7kHz (8-bit) | $2.5 \mathrm{MHz}$    | $102~\mu\mathrm{W}$    | 10-bit <i>PLV</i> Processor                                |

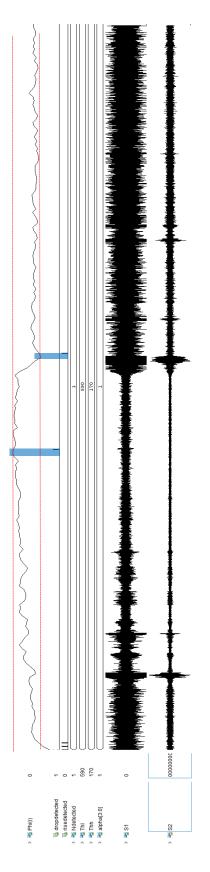

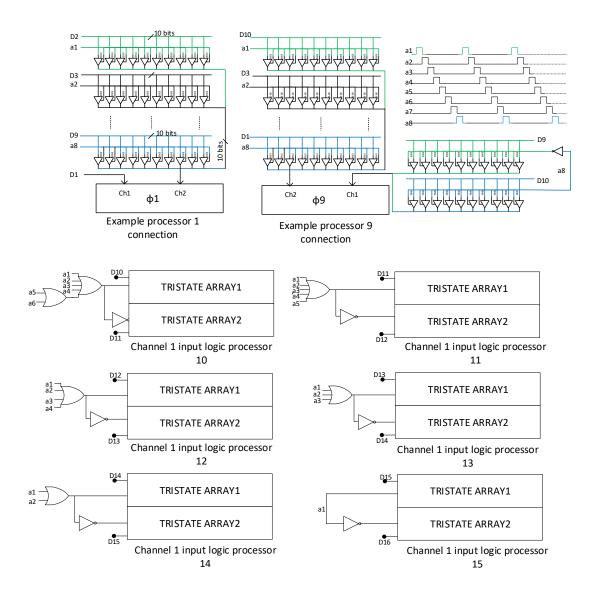

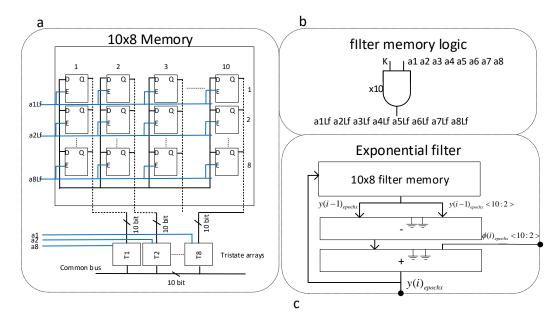

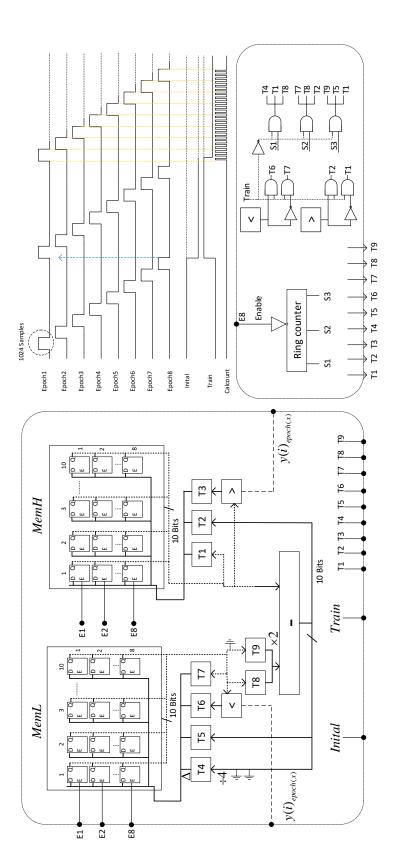

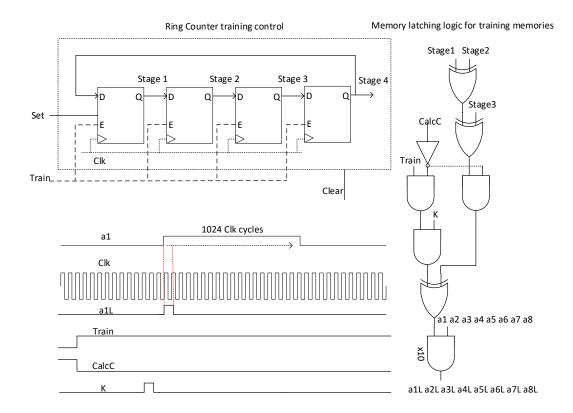

| [53] | 90nm                  | 1.0 V             | $0.143~\mathrm{mm^2}$ | 256Hz (9-bit)  | 4096 Hz               | $2.34~\mu\mathrm{W}$   | 16-channel Correlation Integral Processor                  |