# Trabajo Fin de Máster "Máster Universitario en Microelectrónica: Diseño y Aplicaciones de Sistemas Micro/Nanométricos"

# Study of the impact of lithography techniques and the current fabrication processes on the design rules of tridimensional fabrication technologies

Author: Miguel Gaitero Pérez

Advisor: Juan Antonio Leñero Bardallo

Date: June 26, 2019

This page intentionally left blank

# <u>INDEX</u>

- **Acknowledgments**

- **List of figures and tables**

- List of abbreviations

- List of equations

- Key words

#### 1. Introduction

- 1.1. **Motivation**

- 1.2. **Summary**

- 1.3. **Goal**

- 1.4. **Scope**

- 1.5. Methodology

- 1.6. Planning

# 2. State-of-the-art

- 2.1. Process evolution

- 2.2. Classification based on the source element

- 2.3. Market trends and cutting-edge

- 2.4. Physical limitations

- 2.5. Alternatives

# 3. Body

- 3.1. Photolithography

- 3.1.a. Physics

- 3.1.b. Optics: lens components, aberrations

- 3.1.c. Alignment and overlay: process and tool systematic errors

- 3.1.d. Throughput: cycle time breakdown

- 3.1.e. Current trends to improve accuracy

- 3.1.e.l. The Resolution Enhancement Techniques (RETs)

- 3.1.e.ll. <u>Immersion tools</u>

- 3.1.e.III. Extreme UltraViolet (EUV) lithography

# 3.2. <u>3D-integration</u>

- 3.2.a. Market and applications

- 3.2.b. Through Silicon Vias (TSVs)

- 3.2.b.l. Classification

- 3.2.b.II. Process description

- 3.2.b.III. Process characterization: yield and reliability concerns

- 3.2.c. Bonding

- 3.2.c.l. Classification and direct bonding description

- 3.2.c.ll. Process requirements/materials

- 3.2.c.III. Bonding quality characterization

- 3.2.d. 3D-patterning by modulated lithography

- 3.2.d.l. Tilted patterns by inclined/rotated lithography

- 3.2.d.II. Patterns by modulated exposure

- 3.2.d.III. Periodic 3D-patterns by holographic lithography

- 3.2.d.IV. Built-in lens mask lithography

- 4. Challenges

- 5. Conclusions

- **♦** Bibliography

#### Acknowledgments

I would like to thank first of all to my family for the continuous support during the whole master degree and specially throughout the thesis realization, always motivating me to keep on working on this interesting project with passion. Thanks Miguel Ángel, María del Rosario and Alicia for your smile always trying to get the best of me.

Second, let me thank the support of my friends. Especially two former student colleagues, Javi and Juan, who has been shown always interest in the project and keep on motivating me with their brilliant advice and successful careers.

Moving onto the institutional support, I would like to thank the University of Seville for the challenging master degree and, specially, to my tutor throughout the thesis, Mr. Juan Antonio Leñero, who has been always attentive providing the required help and feedback in an impressive lead time.

Last but not least, I want to thank my current employer, *ASML*, for having been an inspiration for me with the topic election at this master thesis and the knowledge sharing. The high tech work that they do contributes enormously to the technological progress and it is a great opportunity to take part of it.

#### List of figures and tables

Throughout the document some figures and tables are cross-referenced. The reader may find below an index with all the used figures and tables for convenience.

- Figure 1: Yearly sales for the semiconductor industry.

- Figure 2: History of transistor generations and logic styles.

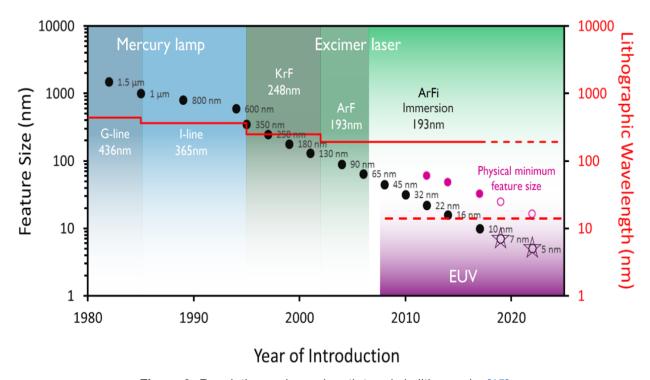

- Figure 3: Patterning size evolution throughout the years.

- Figure 4: Master thesis Gantt chart.

- Figure 5: Different approaches for printing tools.

- Figure 6: Stepper sketch.

- Figure 7: Photolithography tool classification depending on the source element.

- Figure 8: Ultraviolet light spectrum.

- Figure 9: Resolution and wavelength trends in lithography.

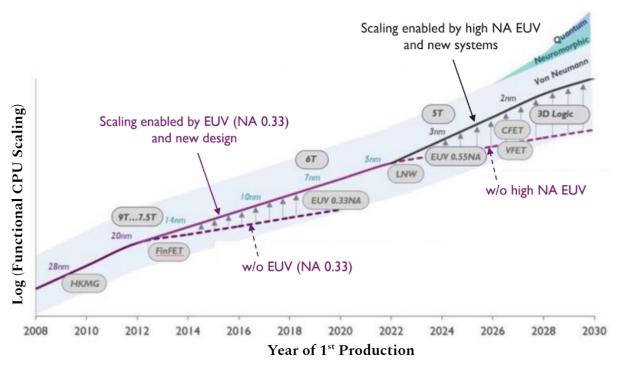

- Figure 10: Microprocessors scaling timeline.

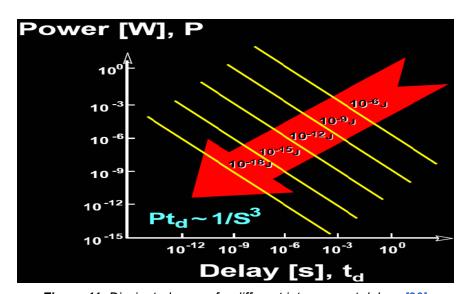

- Figure 11: Dissipated power for different interconnect delays.

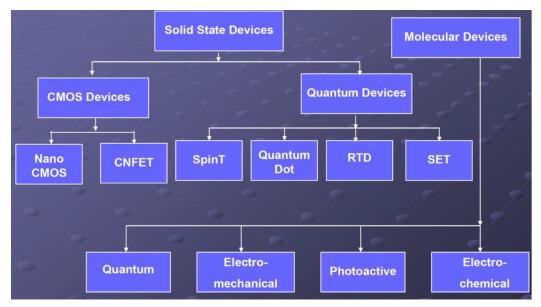

- Figure 12: New technologies and materials roadmap.

- Figure 13: 2D vs. 3D-Integrated Circuits cross section.

- Figure 14: 3D-ICs advantages.

- Figure 15: Reticle with pellicle and its rest of components.

- Figure 16: Major polymer platforms for the different photolithography generations.

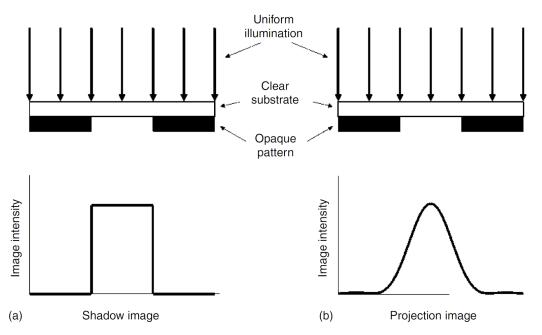

- Figure 17: Projection image. (a) Ideal situation. (b) Diffraction-broadened projection imaging.

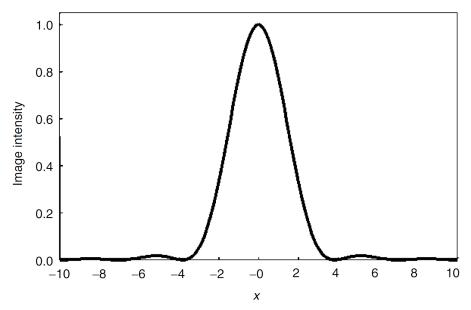

- **Figure 18:** Light intensity distribution from a point source projected through a circular imaging lens.

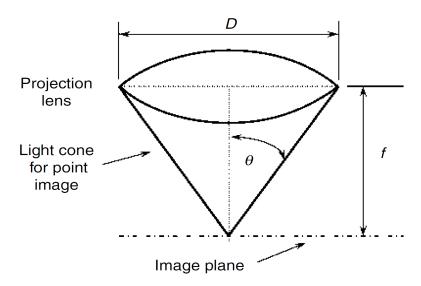

- Figure 19: Projection lens basic sketch.

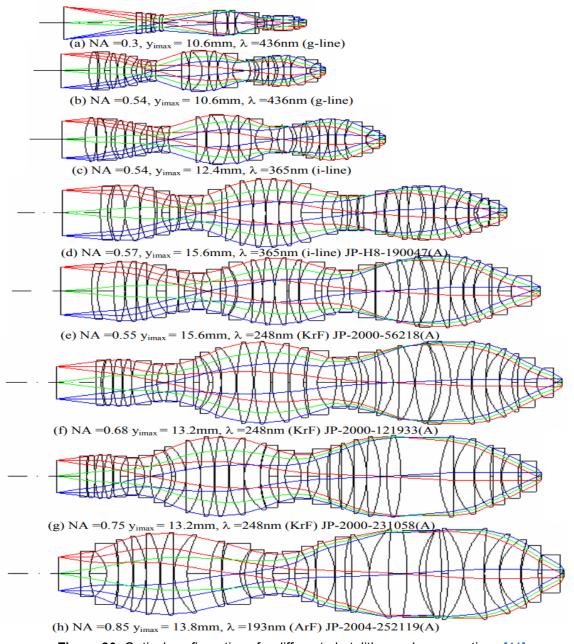

- Figure 20: Optical configurations for different photolithography generations.

- Figure 21: Rays and wavefront at a spherical lens.

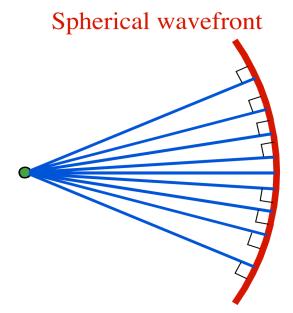

- Figure 22: Spherical aberration.

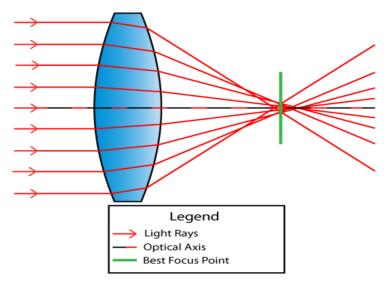

- Figure 23: Critical Dimension (linewidth) versus Exposure Energy for different focus.

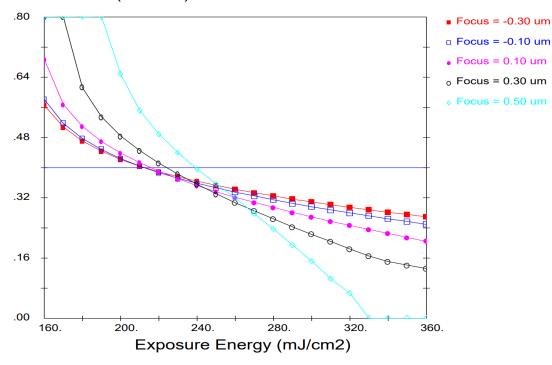

- Figure 24: Coma aberration and result.

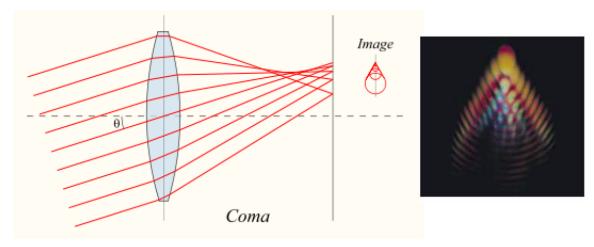

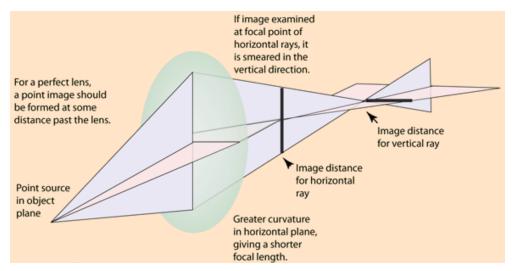

- Figure 25: Astigmatism aberration.

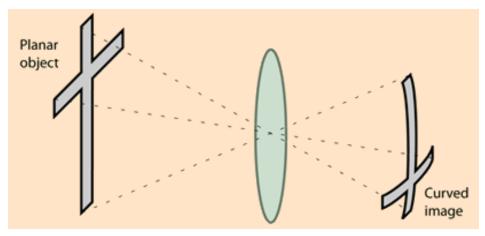

- Figure 26: Field curvature aberration and result.

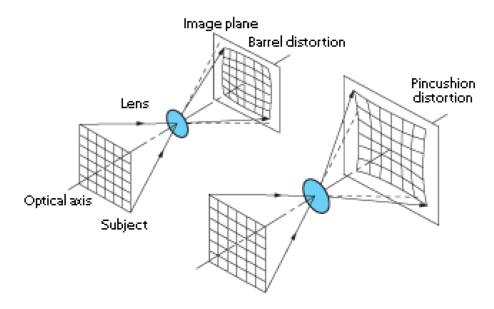

- Figure 27: Distortion aberration.

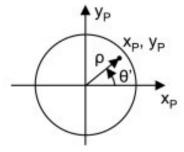

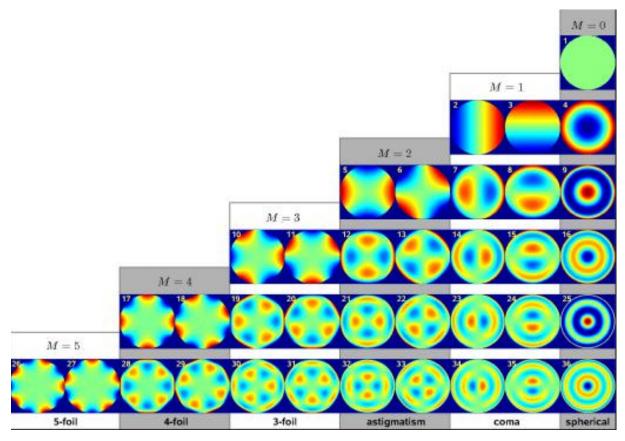

- Figure 28: Polar representation of Zernike polynomials.

- Figure 29: First five orders of Zernike coefficients and their related aberrations.

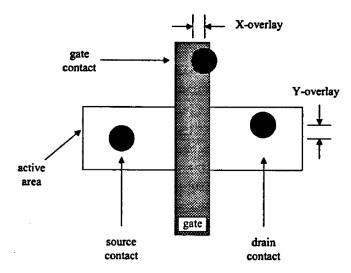

- Figure 30: Example of overlays errors in a transistor.

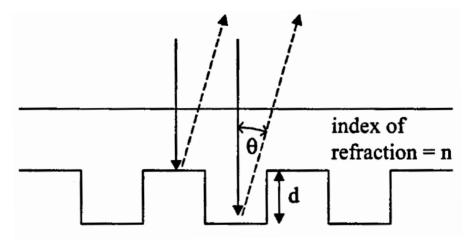

- Figure 31: Phase grating alignment mark.

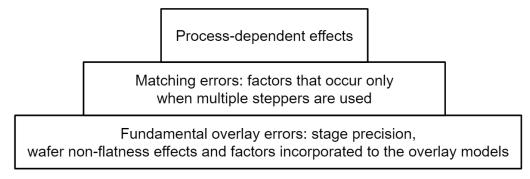

- Figure 32: Hierarchy of overlay errors.

- Figure 33: Effect of a contaminant particle in the image formation.

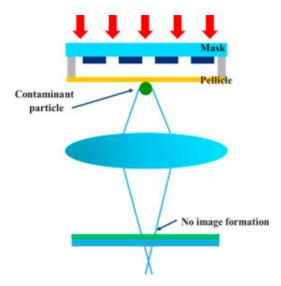

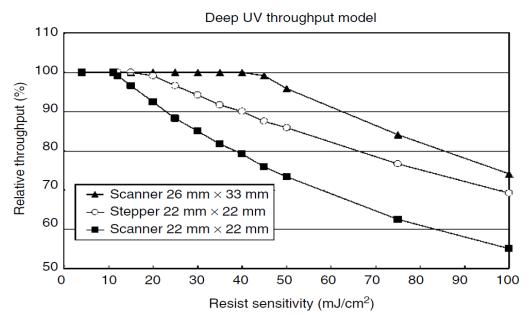

- **Figure 34:** Throughput model for steppers and scanners for different field sizes and resist sensitivities .

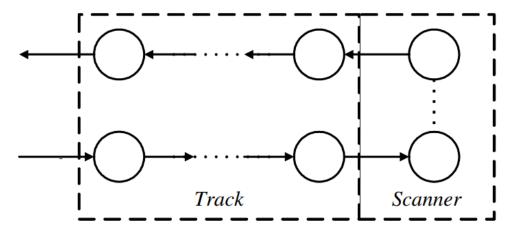

- Figure 35: Wafer cycle of life between the track and the photolithography tool (scanner).

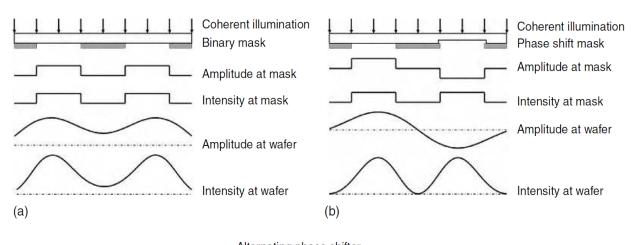

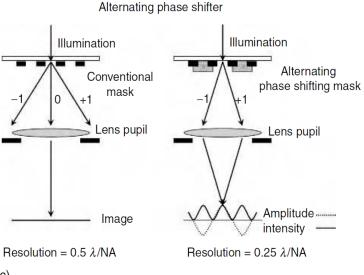

- Figure 36: Alternating phase shift masks. (a) Superposition of aerial images amplitude for conventional lithography. (b) Superposition of aerial images amplitude for PSM. (c) Comparison of conventional and PSM image and resolution.

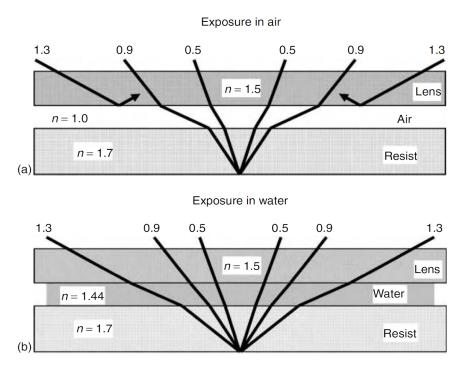

- Figure 37: Optical rays for different NAs. (a) Dry. (b) Wet environment.

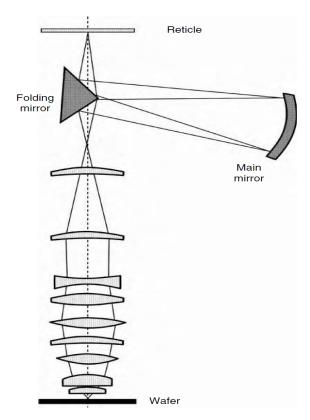

- Figure 38: Example of an advanced catadioptric projection lens.

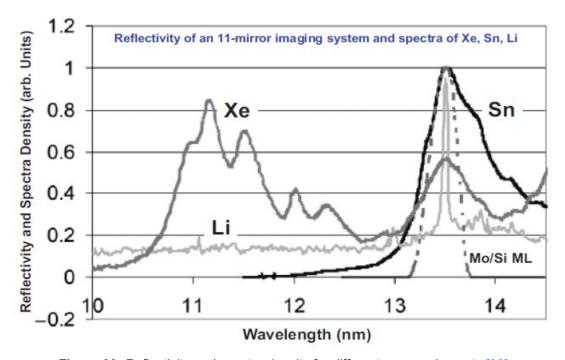

- Figure 39: Reflectivity and spectra density for different source elements.

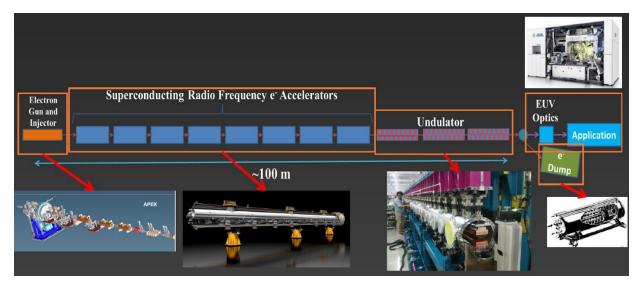

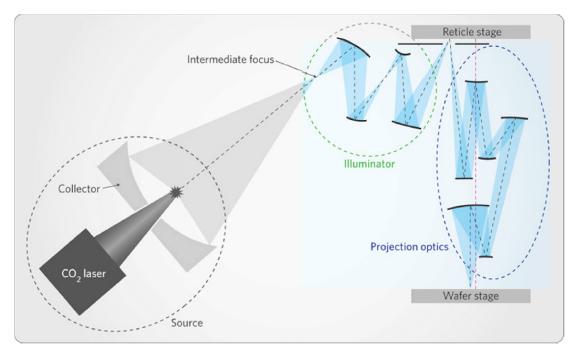

- Figure 40: EUV laser light source.

- Figure 41: EUV lithography light path.

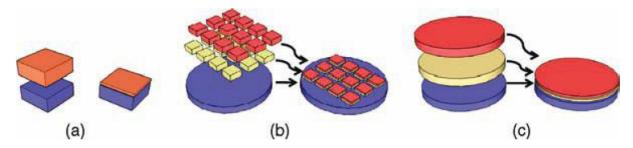

- Figure 42: Major 3D-integration technology platforms. (a) Chip-on-Chip (CoC). (b) Chip-on-Wafer (CoW). (c) Wafer-on-Wafer (WoW) vertical integration.

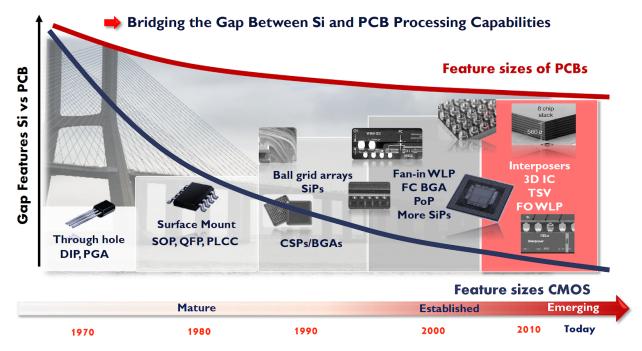

- Figure 43: Microelectronics packaging evolution.

- Figure 44: Features and schematic of the main 3D-integration processes/technologies.

- Figure 45: Market segments for advanced packaging (e.g. 3D-integration).

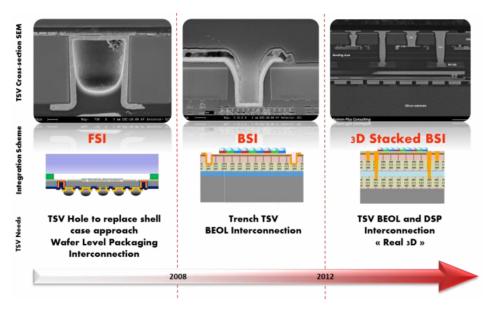

- Figure 46: Evolution of 3D-CMOS image sensors using TSVs.

- Figure 47: Bosch accelerometer package using TSV integration.

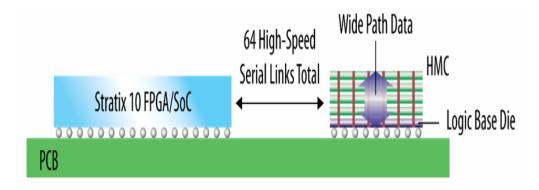

- Figure 48: Schematic of logic devices Arria 10 and Stratis 10 by Altera.

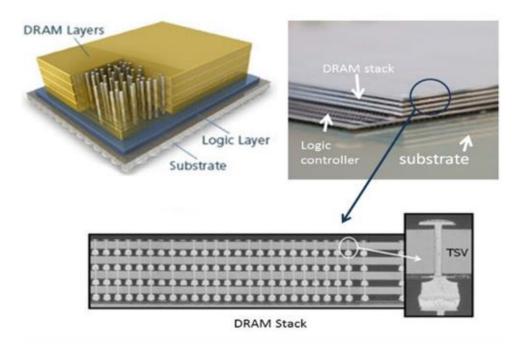

- Figure 49: Hybrid Memory Cube (HMC) by Micron.

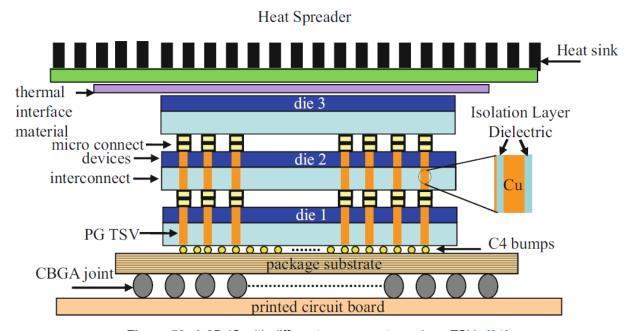

- Figure 50: A 3D-IC with different components such as TSVs.

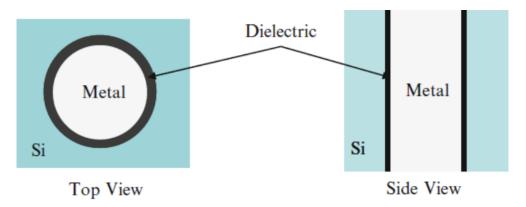

- Figure 51: Regular TSV top and side view.

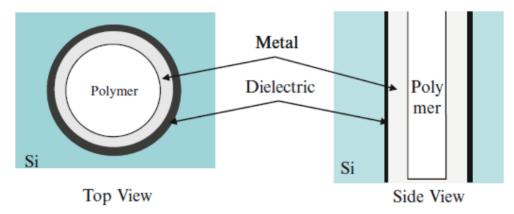

- Figure 52: Annular TSV top and side view.

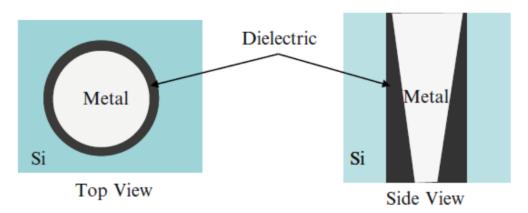

- Figure 53: Tapered TSV top and side view.

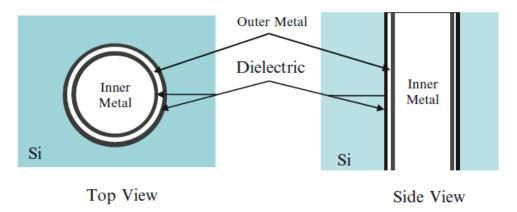

- Figure 54: Coaxial TSV top and side view.

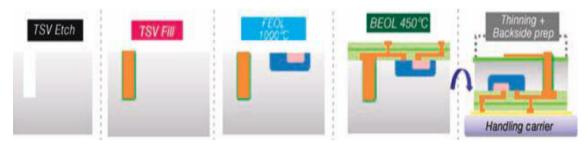

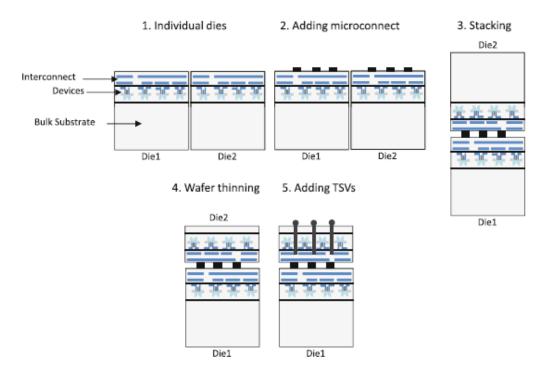

- Figure 55: TSV-first approach process flow.

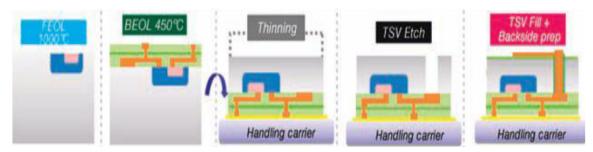

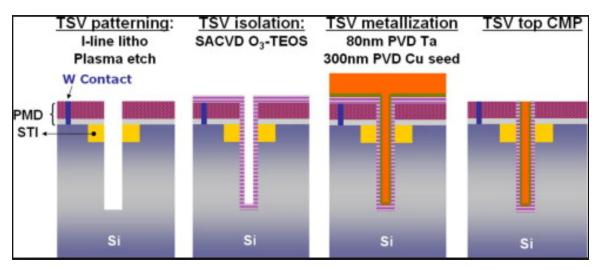

- Figure 56: TSV-middle approach process flow.

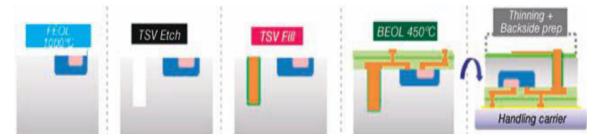

- Figure 57: TSV-last approach process flow.

- Figure 58: Backside TSV-last process flow.

- Figure 59: Frontside TSV-last process flow.

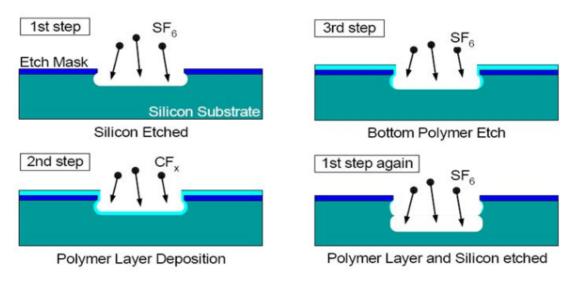

- Figure 60: DRIE process steps.

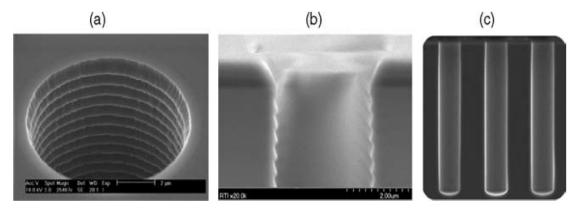

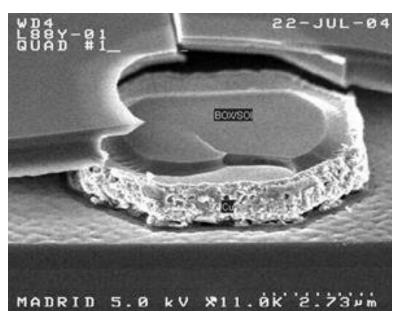

- Figure 61: DRIE features etched in Si. (a) Top view of TSV with sidewall scallops. (b) Cross section of scallops in Si trench. (c) "Scallop-free" TSV etch.

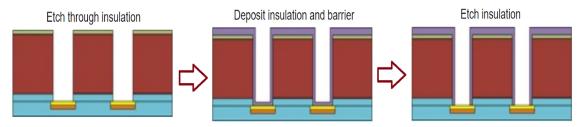

- Figure 62: TSV insulation process steps.

- Figure 63: Typical TSV formation process steps. Metallization comes after the isolation.

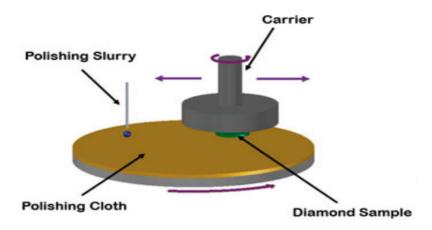

- Figure 64: CMP process.

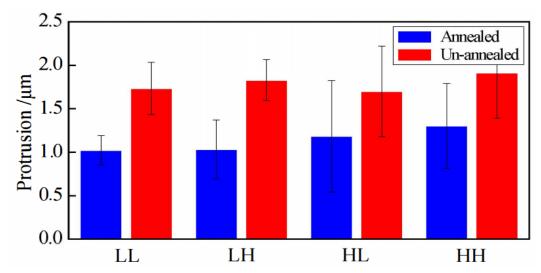

- Figure 65: Comparison of protrusions between annealed and unannealed TSV-Cu after ten thermal cycles.

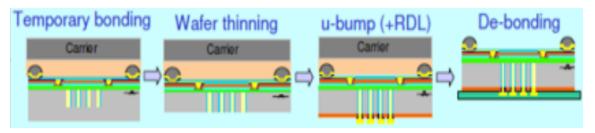

- **Figure 66:** Temporary bonding/bonding, wafer thinning and TSV reveal process flow for conventional 3D-integration.

- Figure 67: Electrical circuit model of TSV.

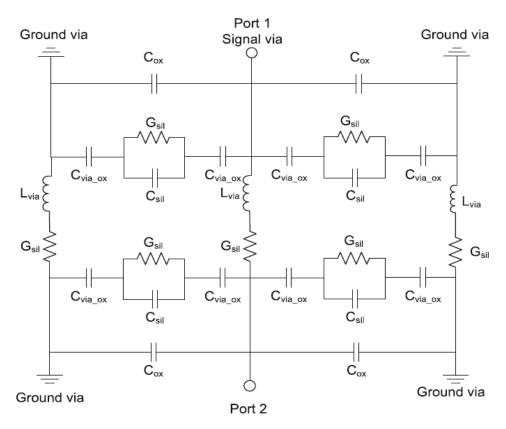

- Figure 68: Induced stress at TSV due to CTE mismatch.

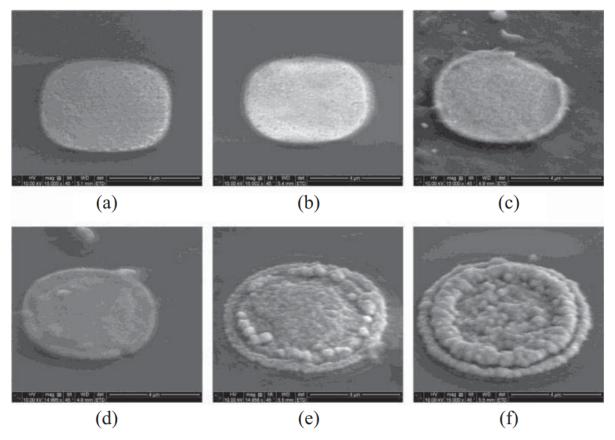

- Figure 69: SEM images showing Cu protrusion for different annealing conditions. (a) 25°C. (b) 250 °C. (c) 300 °C. (d) 350 °C. (e) 400 °C. (f) 450 °C

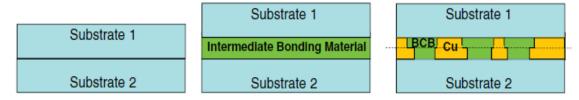

- Figure 70: Major 3D-bonding approaches: direct, indirect and hybrid bonding.

- Figure 71: Direct bonding between Au electrodes into SiO<sub>2</sub>. (a): Top view. (b): Cross section.

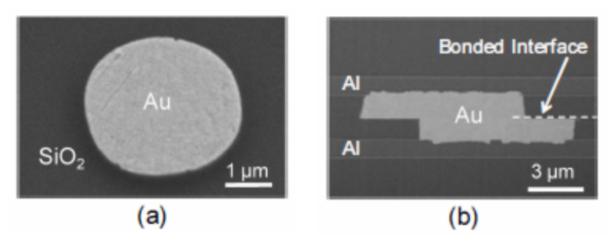

- Figure 72: Process flow of the 3D-Direct Bonding using Au electrodes to connect with SiO<sub>2</sub>.

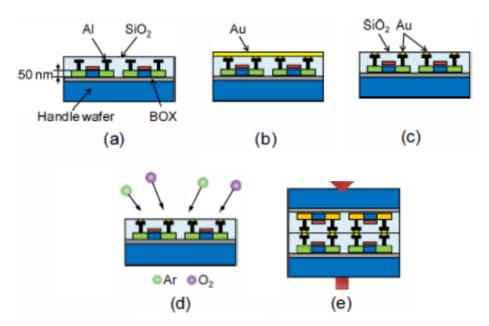

- Figure 73: Direct Bonding Interface (DBI) for a sensor.

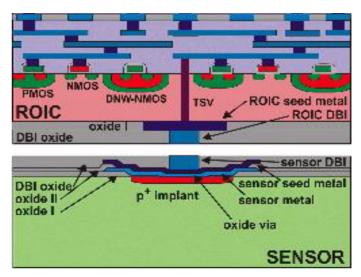

- Figure 74: Sensor manufacturing by using direct bonding, TSVs and DBI.

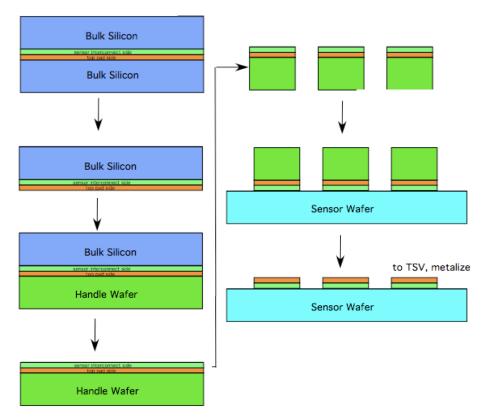

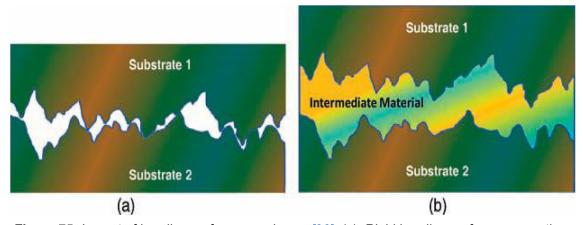

- Figure 75: Impact of bonding surfaces-roughness. (a): Rigid bonding surfaces preventing bonding. (b): Rigid bonding surfaces using an intermediate material to allow bonding.

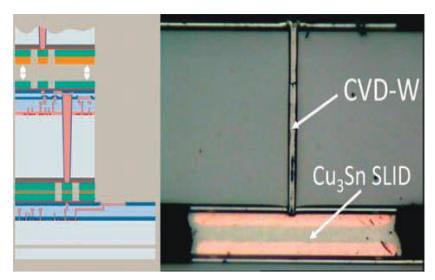

- Figure 76: Combination of SLID bonding process and TSVs.

- Figure 77: TEM cross section of Cu-Cu bonding at 40 degrees Celsius.

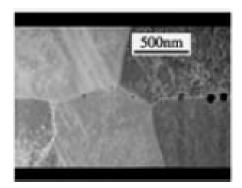

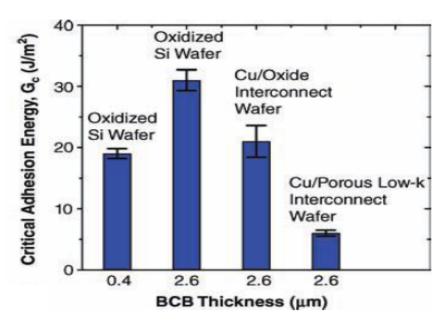

- Figure 78: Critical adhesion energy measured by a four-points bending technique for wafers with

- oxide, Cu-oxide and Cu-low-k interconnects, bonded to an oxidized Si wafer using BCB.

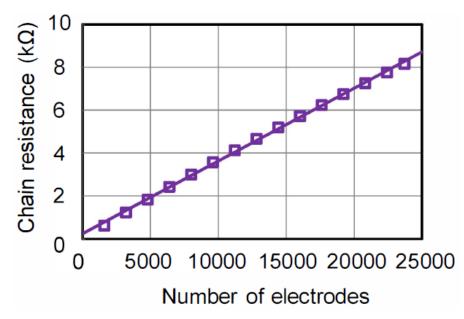

- **Figure 79:** Measured chain resistance by using daisy-chain device in an Au (electrodes)-SiO<sub>2</sub> junction.

- **Figure 80:** Cu-Sn IMC bonding cross section. Before (top) and after thermomechanical stressed (bottom), where voids can be seen to enlarge.

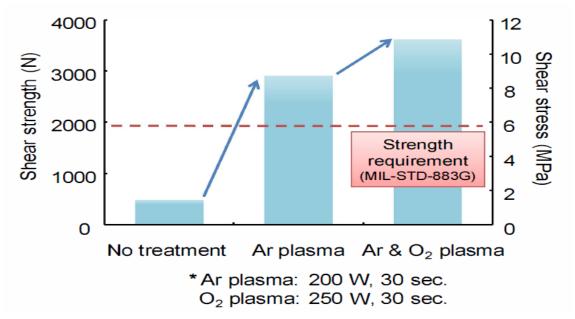

- Figure 81: Shear strengths for direct bonding Au/SiO<sub>2</sub> without and with plasma treatments.

- Figure 82: Tilted patterning by inclined lithography.

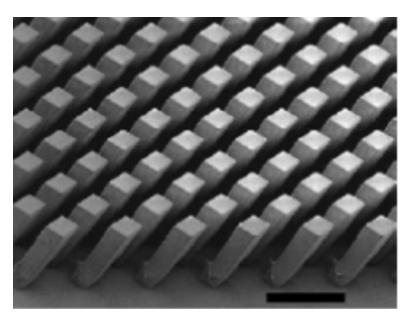

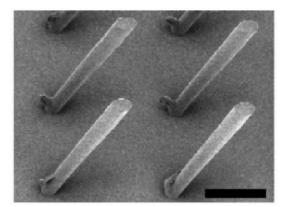

- Figure 83: Tilted pillars by inclined lithography. Scale bar corresponds to 100 μm.

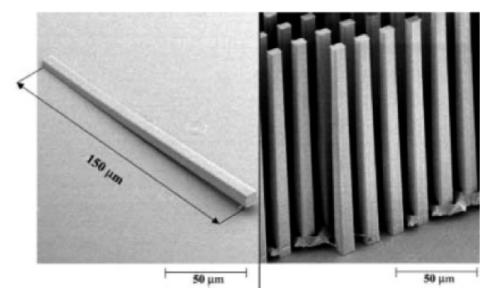

- **Figure 84:** Asymmetric pillars with aspect ratio=10 by combining X-ray vertical and tilted exposure.

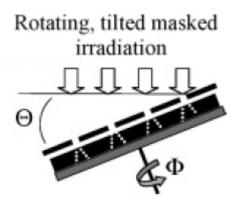

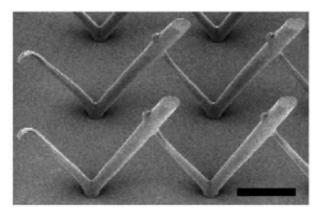

- Figure 85: Tilted and rotated patterning by inclined lithography.

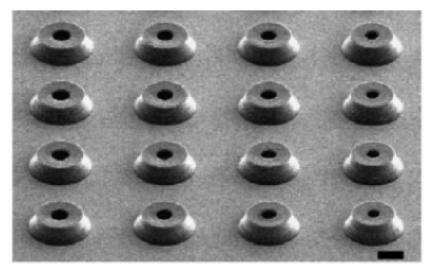

- **Figure 86:** Tapered structures by tilted and rotated UV exposure. Scale bar corresponds to 50 µm.

- **Figure 87:** Structures fabricated by tilted UV on nonreflective (silicon, left hand side), and reflective (aluminum-coated silicon, right hand side) substrates. Scale bar corresponds to 100 μm.

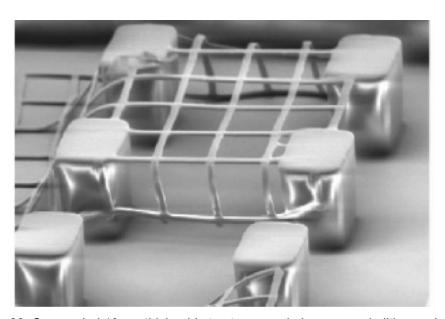

- Figure 88: Suspended 10 μm thick grid structures made by gray scale lithography.

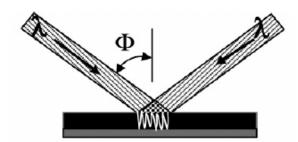

- Figure 89: Interference lithography with two laser beams.

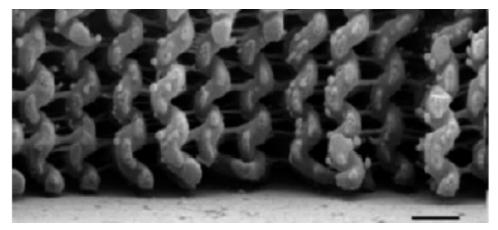

- **Figure 90:** Chiral 3D-structures (spirals) produced by holographic lithography. Scale bar corresponds to 1 μm.

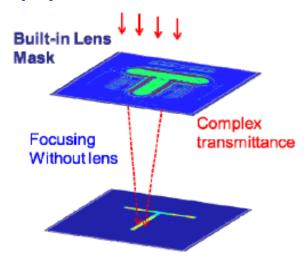

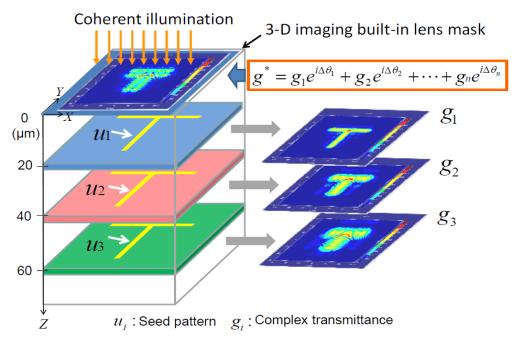

- Figure 91: Basic concept of the built-in lens mask having complex optical transmittance g\*.

- **Figure 92:** 3-dimensional imaging by superposing complex amplitudes of the seed patterns in various focal planes.

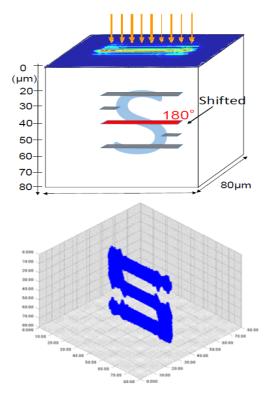

- Figure 93: 3-dimensional imaging of a pattern "S" by computational lithography.

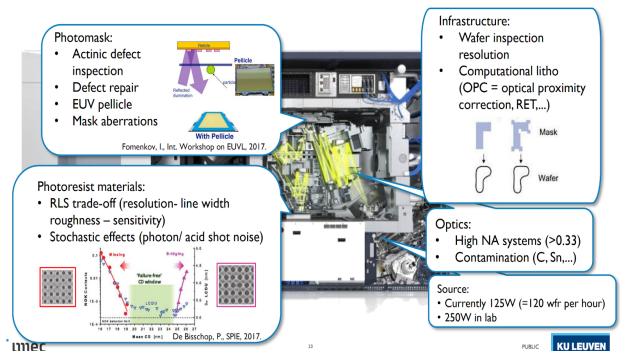

- Figure 94: Challenges for EUV lithography.

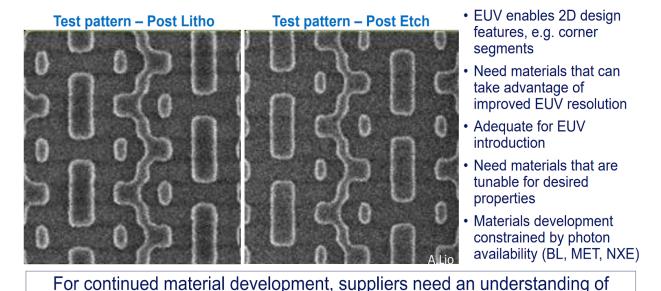

- Figure 95: Example of EUV materials and resolution concerns for a circuit manufacturer.

- Figure 96: Lithography tool supplier roadmap.

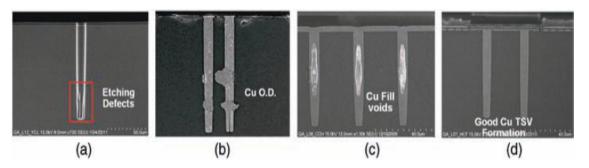

- Figure 97: TSV formation manufacturing defects. (a) Etching defects. (b) Cu out-diffusion. (c) Cu fill voids. (d) Good TSV formation.

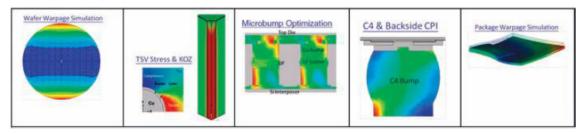

- Figure 98: 3D-integration simulation and optimization prior to the manufacturing.

- Table 1: Patterning resolution and photolithography source wavelength.

- Table 2: The Moore's law limits.

- **Table 3:** Basic relationships on photolithography technology generations.

- Table 4: Classification of alignment methods for photolithography.

- Table 5: Resolution Enhancement Techniques (RETs).

- Table 6: TSVs fabrication processes classification.

#### List of abbreviations

As other technical sectors, circuit manufacturing is full of abbreviations. A list of them (also the ones used at equations), properly sorted alphabetically with their signification, is included to allow the reader to always come back to check the meaning.

- %: per cent

- **2D:** Two Dimensional

- 3D-IC: Three Dimensional Integrated Circuit

- A<sub>eff</sub>: cross sectional area of the TSV

- Al: Aluminium

- AMD: Advanced Micro Devices (company)

- APA: American Psychological Association

- Ar: Argon

- ArF: Argon FLuoride

- **ASIC:** Application-Specific Integrated Circuit

- ASML: Advanced Semiconductors Materials Lithography (company)

- **Be:** Beryllium

- **BEOL:** Back-End-Of-Line

- **BGA:** Ball Grid Array

- BSI: Backside Imager

- C: capacitance

- c: light speed in vacuum

- C<sub>4</sub>F<sub>8</sub>: Octafluorocycloebutane

- CAD: Computer-Aided Design

- CaF,: Calcium Fluoride

- **CD:** Critical Dimension

- CFET: Complementary Field-Effect Transistor

- *cm*: centimeter

- *cm*<sup>2</sup>: square centimeter

- **CMOS:** Complementary Metal-Oxide-Semiconductor

- **CMP:** Chemical Mechanical Planarization

- CoC: Chip on Chip

- CoCoS: Chip on Chip on Substrate

- CoW: Chip on Wafer

- CoW: Chip on Wafer

- CoWoS: Chip on Wafer on Substrate

- CSP: Chip Scale Packaging

- CTE: Coefficient of Thermal Expansion

- Cu: copper

- **Cu**<sub>3</sub>**Sn**: no formal chemical name, represents the compound in the copper-tin phase diagram (Intermetallic Compound)

• CVP: Chemical Vapor Deposition

• D: diameter

• **D2D:** Die to Die

• **D2W**: Die to Wafer

• DB: Direct Bonding

• DBI: Direct BOnd Interface

• DfR: Design for Reliability

• **DfY:** Design for Yield

• **DoF:** Depth of Focus

• **DPP:** Discharge-Produced Plasma

• DR: Design Rule

• **DRAM:** Dynamic Random Access Memory

• DRIE: Deep Reactive Ion Etching

• **DUT:** Device Under Test

• **DUV:** Deep UltraViolet

• *E:* Energy

• **e.g.:** exempli gratia (for instance)

• ECD: Electrochemically Deposited

• **ECTS:** European Credit Transfer System

• ED: Electrical Discharge

• **EM**: Electromigration

• **EUV:** Extreme UltraViolet

• f: focal distance

• **f**: frequency

• FDSOI: Fully Depleted Silicon-On-Insulator

• FEOL: Front-End-Of-Line

• **fF:** femtofarad (s)

• FIB: Focused Ion Beam

• FPGA: Field Programmable Gate Array

• q\*: complex optical transmittance

• GaAs: Gallium Arsenide

• GB: GigaByte

• **GHz:** GigaHertz (s)

• **GPU:** Graphics Processing Unit

• h: Planck constant

• h: TSV height

• *H*<sub>2</sub>*O*: dihydrogen monoxide (water)

• **HBM:** High Bandwidth Memory

• HEBS: High-Energy Beam-Sensitive

• *Hg:* mercury

• HMC: Hybrid stacked Memory Device or Hybrid Memory Cube

• **HVM:** High-Volume Manufacturing

- *I/O:* Input/Output

- *i.e.:* id est (in other words)

- *IC:* Integrated Circuit

- ICP: Inductively Coupled Plasma

- **ID:** Identification

- *IF:* Intermediate Focus

- IH: Immersion Hood

- *IL:* Interference Lithography

- ILD: Interlayer Dielectric

- IMP: Ionized Metal Plasma

- *In:* Indium

- *IP:* Image Placement

- **J**: Joule

- *K:* Kelvin (s)

- **k**<sub>1</sub>: Rayleigh Resolution constant

- **k**<sub>2</sub>: Rayleigh Depth of Focus constant

- KOZ: Keep Out Zone

- KPI: Key Performance INdicator

- KrF: Krypton Fluoride

- LCD: Liquid Crystal Display

- LED: Light Emitter Diode

- LPP: Laser-Produced Plasma

- M<sub>1</sub>: first metal layer

- M<sub>2</sub>: second metal layer

- $m^2$ : square meter

- **MEMS:** Micro-Electro-Mechanical System

- MIT: Massachusetts Institute of Technology

- *mJ:* millijoule (s)

- **mK:** millikelvin (s)

- mm: millimeter

- Mo: Molybdenum

- MOCVD: Metallo-Organic Chemical Vapor Deposition

- MOSFET: Metal Oxide Semiconductor Field Effect Transistor

- **mW:** milli Watts

- $m\Omega$ : milliohm(s)

- *n*: index of refraction

- *n*: refraction index

- NA: Numerical Aperture

- NAND: type of flash memory based on NAND-gates (no real abbreviation)

- **N**<sub>f</sub>: number of exposure fields per wafer

- *nm:* nanometer

- O: overlay

- **O/O**<sub>2</sub>: oxygen

- O<sub>3</sub>: ozone

- OH: hydroxide

- **P**<sub>1</sub>: vector position of the corresponding point

- P<sub>2</sub>: vector position of a substrate geometry

- PCB: Printed Circuit Board

- **PECVD:** Plasma-Enhanced Chemical Vapor Deposition

- **pH**: picohenry (s)

- PMMA: Polymethyl Methacrylate

- poly-Si: Polysilicon

- PoP: Package-on-Package

- **PSM:** Phase Shift Mask

- R: resistor/resistance

- R: Resolution

- RC: Resistor Capacitor

- RET: Resolution Enhancement Technique

- **RF:** Radio Frequency

- RLC: Resistor Inductor Capacitor (refers to a the circuit modelling using those elements)

- RMS: Root Mean Square

- s: second (s)

- S<sub>a</sub>: sidewall area of a TSV

- **SACVD:** Subatmospheric Chemical Vapor Deposition

- SAM: Scanning Acoustic Microscopy

- **SEM**: Scanning Electron Microscopy

- SF<sub>6</sub>: Sulfur Hexafluoride

- Si: silicon

- SiO<sub>2</sub>: Silicon Dioxide

- SiP: System in Package

- SiP: System-in-Package

- SLID: Solid-Liquid Interdiffusion

- *Sn:* tin

- **Sn:** tin

- SoC: System on a Chip

- SOI: Silicon On Insulator

- SPIE: Society of Photographic Instrumentation Engineers

- *T:* throughput

- TaN: Tantalum Nitride

- **TEM:** Transmission Electron Microscopy

- TEOS: tetraethyl orthosilicate

- $t_{exp}$ : exposure time

- *t<sub>foh</sub>*: overhead time per exposure field

- **t**<sub>n,p</sub>: dielectric liner thickness

• TiN: Titanium Nitride

• **TSMC:** Taiwan Semiconductor Manufacturing Company

*TSV:* Through Silicon Via*TTL:* Through-The-Lens

• TTV: Total Thickness Variation

• **TV:** Television

•  $t_{woh}$ : overhead time per wafer

• UV: UltraViolet

• *V:* Volt (s)

• VFET: Vertical Field-Effect Transistor

Vs.: versusW: tungsten

• *W:* Watt (s)

• **W2W:** Wafer to Wafer

• WLCSP: Wafer Level Chip Scale Packaging

• WoW: Wafer on Wafer

• x: distance (typically in horizontal axis)

• **y**: distance (typically in vertical axis with two dimensions)

• **Z**: distance (typically in vertical axis with three dimensions)

• °: degree

• °C: degree Celsius

• *Θ*: angle

•  $\varepsilon_0$ : free space permittivity

• ε<sub>ε</sub>: relative permittivity

• λ: wavelength

• *µm:* micrometer/micron

•  $\rho$ : distance (in polar coordinates)

•  $\rho_m$ : material resistivity

#### List of equations

Throughout the document some formulae are used to illustrate the concept. They are number out with the section where they are mentioned and a number in latin numbers which is an ascendent counter.

- 3.1.1: Planck's equation

- 3.1.a.1: Rayleigh equation (Resolution of an optical system)

- 3.1.a.2: Rayleigh equation (Depth of Focus of an optical system)

- 3.1.a.3: Numerical Aperture of an optical system

- 3.1.a.4: Rayleigh equation for large angles (Resolution of an optical system)

- 3.1.a.5: Rayleigh equation for large angles (Depth of Focus of an optical system)

- 3.1.b.1: Strehl Ratio

- 3.1.b.2: Strehl Ratio in terms of wavelengths (RMS)

- 3.1.b.3: x coordinate of Zernike coefficients in polar coordinates

- 3.1.b.4: y coordinate of Zernike coefficients in polar coordinates

- 3.1.b.5: position vector of Zernike coefficients in polar coordinates

- 3.1.c.1: overlay definition

- 3.1.d.1: throughput of photolithography system (sprint rate)

- 3.1.d.2: wafer process time

- 3.1.e.l.1: mask thickness for PSM

- 3.1.e.ll.1: Rayleigh equation for immersion systems (Resolution of an optical system)

- 3.1.e.II.2: Rayleigh equation for immersion systems (Depth of Focus of an optical system)

- 3.2.b.III.1: TSV resistance

- 3.2.b.III.2: TSV capacitance

- 3.2.d.III.1: interference lithography pattern period

#### ❖ Key words

Some important concepts which will be used throughout the thesis are briefly defined, in order for the reader to get familiar with the most relevant and recurrent terms. The words are sorted alphabetically, thus providing an easy overview, always allowing the reader to come back to remember what the word means.

- **2D-circuits/devices:** conventional *ICs* which do not stack different layers.

- **2.5D-interposer:** predecessor of the *3D*-integration consisting on linking various layers by means of a silicon interposer.

- **3D-circuit/integration**: alternative to conventional circuits manufacturing, consisting on stacking various layers (also known as tiers) to increase the efficiency of the system and decrease the interconnection length.

- **(Optical) aberration**: flaw or distortion in the patterned image (at the wafer), compared to the original pattern. It is produced by the optical lens.

- Back-End-Of-Line (*BEOL*): term used at the manufacturing industry to describe the last processes during circuit manufacturing. It includes the process steps after the first metal layer, including the interconnections between layers for *3D*-Integrated Circuits.

- Chemical Mechanical Planarization (CMP): process used in circuit manufacturing, consisting in making the wafer more flat in order to avoid issues during expose, material deposition or etching.

- Chip-on Chip (CoC)/Die-to-Die (D2D): sort of 3D-bonding technique consisting of stacking a chip (die) into another chip (die).

- Chip-on Wafer (CoW)/ Die to Wafer (D2W): sort of 3D-bonding technique consisting of stacking a chip (die) into a wafer.

- Critical Dimension (CD)/Feature size/linewidth: refers to the size (width) of the pattern imaged onto the wafer. The control of the Critical Dimension is key in the photolithography process, since it defines the performance of the circuit.

- **Cu** protrusion: effect consisting on having hillocks formed during the heating process, being a reliability concern for thermomechanical failures in subsequent layers which is usually addressed by adding the extra process of *TSV* annealing.

- **Depth of Focus** (*DoF*): figure which represents the tolerance of the distance between the lens and the wafer that can be modified in order to still achieve a correct patterning process. It can be calculated with the Rayleigh equation.

- **Direct Bonding:** *3D*-circuits manufacturing process consisting on attaching two similar or dissimilar materials without anything between them.

- **Dry lithography/tool**: using air surrounding the lens instead of water. It is used by the conventional photolithography.

- **Etching:** process used in circuit manufacturing, consisting on removing by means of chemical products a layer or substance from the top surface of a wafer.

- Extreme UltraViolet (*EUV*) light/lithography: light with a wavelength in a range between 11 and 14 nanometers. In photolithography, it is used a wavelength of 13.5 *nm*

for EUV lithography, which has improved the resolution of the pioneer systems, in opposition to the conventional Deep UltraViolet (DUV) lithography, which typically uses wavelengths between 193 and 365 nm.

- **Fab/factory:** utility where the circuits are manufactured.

- Front-End-Of-Line (FEOL): term used at the manufacturing industry to describe the first processes during circuit manufacturing. It includes the process steps preceding the first metal layer.

- **Holographic/interference lithography:** alternative lithography technique consisting on using various coherent laser to create a interferences so that an inclined pattern is printed into the surface of the wafer. Used for *3D*-lithography novel techniques.

- **Hybrid bonding:** *3D*-circuits manufacturing process consisting on attaching two materials with the help of an added material in one of the bonding surfaces, forming the electrical connection.

- **Immersion (wet) lithography/tool**: using liquid -concretely water- surrounding the lens instead of air, in order to improve the resolution of the photolithography process.

- **Inclined mask/lithography:** alternative lithography technique consisting on tilting the reticle and the wafer so that inclined/3D-patterns can be printed into the wafer. Used for 3D-lithography novel techniques.

- **Indirect Bonding:** *3D*-circuits manufacturing process consisting on attaching two materials by means of an intermediate material which makes the connection.

- **Integrated Circuit (IC)**: electronic circuit formed on a small piece of semiconducting material (typically silicon) which performs different functionalities.

- **Keep Out Zone** (*KOZ*): area surrounding *TSV* to create a safe distance between *TSV*s and active devices in order to eliminate proximity effects.

- **Key Performance Indicator** (*KPI*): figure which specifies the quality/performance of a process. It is specific of the process, being the most common for photolithography the overlay.

- **(Excimer) laser**: ultraviolet light generator used in the production of microelectronics among others. It is the light source for the photolithography tool.

- (Optical/projection) lens: single, optically transparent device which enhances the transmission and refraction of light. In photolithography, it allows the light generated by the laser to pass through, so that the pattern can be imaged onto the wafer.

- (Alignment) marks/keys/targets/fiducials: distinguishable patterns used as reference point for the photolithography tool to establish the coordinate system at the wafer level.

- **Modulated/3D-lithography:** alternative lithography techniques not consisting on using optical means, but other processes able print 3D-patterns.

- Moore's law: observation and prediction made in 1965 by Gordon Moore, co-founder of Intel, postulating that the number of transistors per square inch on integrated circuits had doubled (and will double) every two years.

- **Multilayer Mirror/Bragg Mirror**: type of mirrors used at *EUV* lithography since they are able to reflect the light, thus achieving larger incident angles that conventional mirrors.

- **Numerical Aperture (NA)**: dimensionless number that measures the ability to gather light and to print a pattern at a fixed distance. It is a lens feature which is to be enlarged, in order to allow more light to pass through.

- **Overlay/alignment**: figure which indicates how well the stack-up between layers is done (in terms of relative position). The alignment is the process performed at the photolithography tool in order to achieve better overlay.

- **Pattern**: pre-defined model or shape which is used in photolithography to build the circuits by imaging it onto the wafer.

- **Pattern generator**: photolithography tool which uses as input data a database to directly create a physical image on the wafer.

- **Pattern replicator**: photolithography tool which creates a master pattern image in the form of a reticle and them replicates the pattern in a massively parallel fashion onto the wafer by means of a projection lens. It is the most common type of photolithography tool.

- **Phase Shift Mask** (*PSM*): a technique based on the principle of light interference with the goal of creating destructive interferences between the light from the adjacent openings, so that the resolution of the photolithography tool is improved.

- Photolithography/optical lithography/conventional/UV lithography: process of imaging a pattern onto a wafer by means of light. It is a key process in the electronic manufacturing, since its quality defines the performance of the circuit.

- (Wafer) processing: all the methods performed at the track. It includes coating and baking among others, which are needed to condition the wafer in order to perform the photolithography process.

- Rayleigh equation: mathematical relationship between the resolution of the photolithography process with respect to the Numerical Aperture of the lens and the wavelength of the inciding light. It also specifies the Depth of Focus used by the image lens.

- **Refraction index** *n*: dimensionless number which describes how fast the light propagates through the material. It is characteristic of each medium, thus defining the optical features in that environment.

- **Reliability:** concept to describe how well a product will behave in the long run. It is a key feature on a product, since has to be tested during product verification to guarantee the customer that the functionality will be kept throughout the time.

- (Photo)resist: organic material which consists of a polymer base resin. It is coated at the track to the wafer surface, allowing a certain wavelength to pass through to print the pattern into the wafer.

- **Resolution/accuracy**: figure which defines the ability to distinguish different components within a group of objects. Whereas the Critical Dimension or pattern size is more related to the circuit (the result of the photolithography process), the resolution/accuracy refers more to the photolithography tool itself.

- Resolution Enhancement Techniques (*RETs*): methodologies which improves the imaging performance (better resolution) by wavefront, mask or resist process engineering, thus reducing the Rayleigh constant  $k_t$ .

- **Reticle/photomask**: both terms are identical, defining an opaque element with a "written" pattern on it. Physically it is a thin sheet with some holes which allows the light to pass through, thus replicating the patterns into the wafer.

- **Scallop:** small ridges formed during *TSV* etching, being a well-known pattern as a result of that process.

- Scanner/step-and-scan tool/(photo) lithography tool/exposure tool: it is the system (machine) which performs the photolithography process. The three concepts will be used as synonyms throughout the thesis, consisting in the most advanced system types, where both the reticle and wafer are moving at the same time to improve accuracy and throughput.

- **Silicon** (*Si*): semiconductor material which is mainly used at the electronic industry due to its properties. It is provided to the factories in small rounded-pieces called wafers.

- System in Package (SiP): concept used to describe numeral ICs integrated in one single chip carrier package.

- **Throughput**: indicator of the amount of parts (in photolithography, wafers) that can be processed in a certain amount of time (typically one hour).

- Through Silicon Via (*TSV*): vertical electrical interconnection in the 3D-Integrated Circuits, which passes through the different layers of the die.

- **Tier/layer:** each of the strata for 3D-Integrated Circuit. Typically interconnected by TSVs.

- **Track**: system or machine which performs the processing of the wafer, *i.e.* the chemical treatments before and after the photolithography process to condition the wafer.

- **TSV-first:** process flow for 3D-Integrated Circuits, consisting on creating the via before the *FEOL*.

- **TSV-last:** process flow for 3D-Integrated Circuits, consisting on creating the via during or after the BEOL. Two variants exist depending on where the interconnection is done: backside or frontside.

- **TSV-middle:** process flow for 3D-Integrated Circuits, consisting on creating the via after the *FEOL* but before the *BEOL*.

- Voids: concept which describes the absence of material at 3D-bonding, being a reliability concern since the electrical connection and the junction robustness are degraded.

- **Wafer**: a thin slice of semiconductor used as substrate for electronics manufacturing. It is conventionally made on a circular shape with a diameter of 200 or 300 *mm*.

- Wafer-on-Wafer (WoW)/Wafer to Wafer (W2W): sort of 3D-bonding technique consisting on stacking a wafer into another wafer.

- Wavelength: physics feature which represents the distance between two consecutive points on a wave shape, where the same state is achieved. In photolithography, it is used to characterize the light source, thus defining the resolution of the tool by means of the Rayleigh equation.

- **Yield:** figure to show how well a process performs. Typically represents the ratio between the good (based on one or multiple criteria) manufactured parts out of the total manufactured parts.

• **Zernike coefficients**: mathematical invention which consists on numeral polynomials describing an optical tool. They are used to easily observe the aberrations in optical systems.

This page intentionally left blank

# 1. Introduction

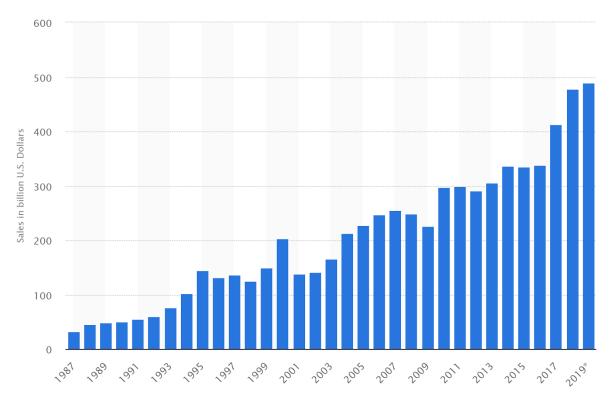

Electronic market has experienced an incredible growth during the past century, thus being nowadays one of the leading economies at the industry. The semiconductor companies, which customize the conductivity of the raw piece of silicon to fabricate the microchips, have generated sales in 2018 equivalent to 477.94 billion U.S. dollars [1], proving the increasing importance of the market as shown in figure 1.

Figure 1: Yearly sales for the semiconductor industry [1].

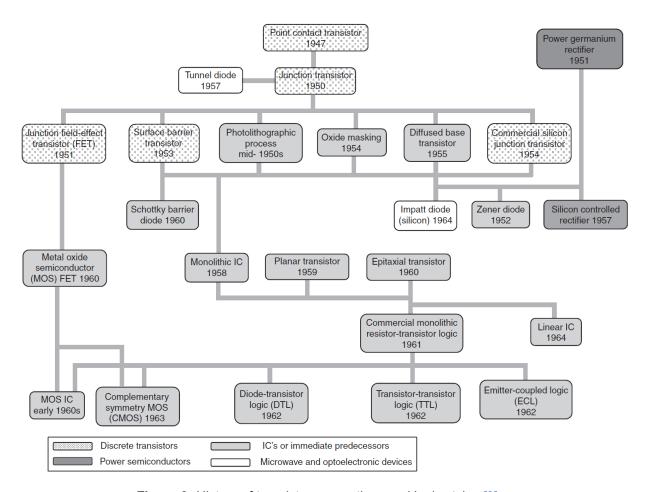

The origin of that revolution, the seed that caused this "big-bang" of electronics, was a grain of germanium on which the point contact transistor was fabricated for the first time in 1947 by J. Bardeen, W. Brattain, and W. Shockley [2]. That was the trigger for an unending race on continuous improvement to look for the "perfect transistor" which has the best physical and mechanical features to makes the chips of today. The evolution throughout history is depicted in figure 2, where different paths have been explored by the researchers community.

Figure 2: History of transistor generations and logic styles 3.

The boom of the robust *MOSFET* as preferred option, empowered the semiconductor market throughout the years, where the chips manufacturing was considerably advanced due to automation, reducing the cost and time to market and offering more reliable products, while increasing employee safety through highly sophisticated electronic security systems that can recognize and warn of critical equipment failures [4]. Electronics appeared then as an easy solution for storing media, making communication faster and better with each other (the Internet), improving medical procedures with noninvasive techniques or helping the science to advance by making computational tasks ultra fast.

Using electronics today is so much a part of our daily lives we hardly think of the way the world would be without electronics [5]. Everything from cooking to music uses electronics or electronic components in some way. Our family car has many electronic components, as does our cooking stove, laptop and cell phone. Cell phones are everywhere to take and send pictures, play music, text messages or just checking whe weather forecast. The Internet is used by almost everyone, from companies to send emails or store the information, to the personal usage such as online shopping or checking the bank statement. Music is a prime user of electronics, both in recording and in playback mode: music players, head- or earphones and speakers would not be existing without the electronic revolution. Television as main pastime fully incorporates the latest advances in electronics, being now able to get connected to the Internet and to other devices. Cameras of today are affordable, being included in the cell phone or as individual device, with the pictures easily to be easily edited through the marvel of electronics. Electronics devices are being used in the health field, not only to assist in diagnosis and determination of medical problems, but also to assist in the research that is providing treatment and cures for illnesses and even genetic anomalies, thus being pacemakers or similar equipment implanted in the body as almost a routine activity.

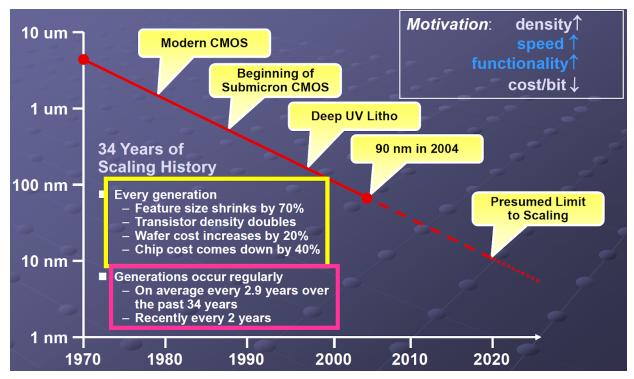

It is clear that today's lives are impossible to conceive without the electronics. How is that progress possible and for how long can withstand? Well, the electronic evolution through the years is known as the Moore's law, who stated that the amount of transistors on a chip doubles every two years. But the implication is not only about that figure, but also about the feature size, cost or power, as the <u>figure 3</u> suggests, resulting in smaller, cheaper and more power microchips, respectively.

Figure 3: Patterning size evolution throughout the years [6].

This is where the photolithography came to the play, being the main process of the chip manufacturing. Its process quality, cost and cycle time are the main figures for the factories to take into account at the chip production. The evolution of the transistor size has gone hand-by-hand with the photolithography progress: the smaller the feature size printed by the photolithography tool, the faster and smaller the microchip. Advances in lithography have been possible thanks to good understanding of the optics and physics behind the process, as well as material properties, making possible to keep Moore's law valid until nowadays.

However, the size shrinking can not long forever: even with the most advanced lithographic techniques, it is expected that physical limitations will impide the transistor size to be decreased. Some alternatives have appeared with the goal of replacing the conventional photolithographic process to drive the future of the semiconductor industry. Concretely, the approach of stacking-up different layers to create a 3D-integrated device, has recently gained a lot of weight at some electronic applications, since it allows to integrate different functionalities at a chip without increasing the power dissipation which is one of the main factors braking the scaling progress. 3D-integration seems as a valid candidate for certain applications, but it is not yet used for mass production due to some technological challenges.

The present is clear: using the photolithography breakthroughs is allowing to continue with the trends to improve our daily lives with smaller microchips. The future is uncertain though: will the 3D-integration the solution for the chip of tomorrow? It is difficult to predict the market evolution, but at least knowing the state-of-the-art of both technologies will help to have a better understanding of the current issues and how the industry is tackling them to improve our lives with better chips.

#### 1.1. Motivation

Working for the photolithography tool manufacturer leader sometimes gives me the impression of how complex and specific is the sector I am working on. This master thesis topic came with the goal of getting the overall picture of the state-of-the-art: stepping out and trying to get a helicopter view usually helps to understand where a process is in the productive chain, or what other firms and markets are doing to continue improving.

So, I came across with the idea of researching about the photolithography cutting edge, linking the particular vision I have from the company with the adds-on of the available literature. The ultimate goal was to allow the thesis reader to follow the progress of the photolithography throughout the history, understanding the basic concepts of the technology to explore how the industry is reinventing itself. On that way, it would also help to understand the overall picture: too often some concepts are daily used but we do not have the knowledge or know-how to grab what is behind or why it has revolutionized the market. With this thesis, I aim to understand those daily concepts and allow the thesis reviewer to get familiar with the background, so that a trajectory through the history can be easily followed. Take for instance a practical example, the news about faster microchips using Extreme UltraViolet (EUV) lithography (light source with wavelength of 13.5 nm): the user may have read that without really knowing what the breakthrough is about it. Rather than going directly to explain what the EUV is, through this thesis one can feel driven to need to know why it came up: the photolithography evolution, the basic equations and concepts, and the understanding of the more mature technologies. In that way, the EUV is considered a natural consequence -the evolution- of the photolithography history, having a solid know-how of how is working now at the industry, but also a subjective inside in the tool manufacturers which can help to understand how the market will evolve.

When I first proposed the topic for this thesis that was the main goal, getting the overall picture and being able to provide it: it is said that when you explain something it is finally when you understand it. But not only this, also my intention was to research some alternatives at the current market, and the professor has proposed to do that with the 3D-integration technology. Something that for me was quite new: I have sometimes heard about it but never worked or deepened into that. The goal thus was to understand the basics and see how mature the technology is, providing an objective and comprehensive knowledge that helps to grow a subjective point of view to "forecast" the technology roadmap. Information is power, therefore rather than saying that new technologies such as the 3D-integration will never work on the market, first let us try to understand what is behind, the current limitations and the different market solutions, to later say how good or bad they will fit in our lives.

I expect that after writing -and reading- this thesis, talking about photolithography and 3D-integration market trend will be based on facts and solid understanding of the basic concepts, rather than simply speculating without any criteria where the market goes.

# 1.2. Summary

The Moore's law has been driving the roadmap of the electronic manufacturing to reduce the transistor size, but now it seems about to hit their physical limitations. The main process that has allowed that progress is the photolithography, which consists on patterning by means of a light source into the wafer, thus creating the patterns in one layer which will form the transistors. The photolithography evolution through the history is key to understand the breakthroughs of today's industry. Describing the process concept, the physics and optics behind, allows to create a know-how of the standard lithography process, which is vital to understand the latest inventions by the tool manufacturers. From simple to complex, from standard to new, the concepts are being presented to lead to the two main technologies at the market: the immersion lithography and the *EUV* lithography. Those inventions are the responsible of keeping valid the Moore's law for the moment, being in different scales of maturity. The challenges to continue decreasing the patterning size are numerous, but the companies roadmaps are clearly defined to tackle those and keep on surprising the world with faster and smaller microchips.

On the other hand, other approach with a new process, called *3D*-manufacturing, is explored as an alternative to the conventional *2D*-manufacturing. By that emergent technology, wafers or tiers are vertically interconnected, thus decreasing the dissipated power and providing a solution to the current power increase. This approach is increasing the market share for some applications and sectors, which has the need to move into the *3D*-integration to find new or improved chip functionalities. Different alternatives are available at the market, having in common the main two processes: Through Silicon Vias forming and bonding. Their requirements, in terms of materials and process limitations, make the technology not yet implemented in mass production, but the good progress in the processes comprehension makes the *3D*-approach more than promising as an alternative, or maybe as an evolution, of the conventional photolithography-based circuit manufacturing.

3D-integration still needs from the photolithography process to form each circuit layer, but the enhancements of the lithography tool are not needed since the size is more limited by the specific integration processes. However, new alternatives at the market are appearing, which try to integrate both processes in the so-called 3D-lithography, which consists on having lithography variants to print 3D-patterns, not anymore only patterning one layer at a time. If that would work, the cycle time to manufacture a three dimensional-integrated circuit will drastically reduce and so, maybe, the 3D-approach will become cost-wise effective to be used in serial production.

#### 1.3. Goal

The ultimate goal of this thesis is to generate an opinion based on facts about the current status of the circuit manufacturing, particularly focused on the photolithography process, and how this one has overcome the challenges to be in its maturity phase currently with techniques such as immersion lithography. The future of the conventional lithography techniques is also discussed, particularly explaining why it is expected the usage of *EUV* lithography for the upcoming years and the current challenges of that technology. On the other hand, the conventional circuit manufacturing is expected to finish at some day, therefore an overview of one of the most appealing alternatives, the *3D*-integration, is discussed to keep the reader up to date with this potential solution, which would reduce the dissipated power and reduced the interconnect delays, among others. Researches about how lithography for generating 3D-patterns are included with the target of providing additional information of what the industry is considering as potential alternatives for the upcoming years.

To do so, an analysis of the historical evolution of photolithography is included, mainly pointing out the breakthroughs that allowed to continue the Moore's lay validity. The theory behind the process is also explained, highlighting the physics and optics nature of lithography tools. The remaining challenges for the upcoming years for the *EUV* are also discussed, thus providing the reader a view of what is the industry currently working on and how the process in some year is expected to be developed.

With regards to the *3D*-integration circuits, the goal is to provide a clear overview of which products and market segments may take advantage of its implementation. The main two processes, *TSV* formation and bonding are also described, since their understanding will allow the reader to figure out what the current challenges are and guess whether the technique may have a successful development in upcoming years. As information, the *3D*-lithography will provide the reader an interesting starting point for further investigations of novel techniques, which will enrich the knowledge and open the mind of the avid reader to look into different directions for the market evolution.

# 1.4. Scope

It is important to mention that this master thesis cannot cover the whole circuit manufacturing description, it is more aim to provide an overall vision of the cutting-edge for photolithography processes. Therefore, it is convenient to highlight what will be covered throughout the document and what will not be. It is **in scope**:

- Photolithography historic evolution

- Photolithography process description from physics and optics point of view

- Photolithography tool and process errors

- Photolithographic processes which enhances the accuracy, particularly focused on immersion lithography and EUV lithography

- Challenges for photolithography in the upcoming years

- 3D-integration market and applications

- TSV: classification, process description and challenges

- Bonding: classification, process description and challenges

- 3D-patterning by modulated lithography techniques examples and description

- Objective overview of what market trends

- Subjective opinion of present and future market trends

#### It is **not in scope**:

- Track processing description

- Overall circuit manufacturing flowchart

- Deepening on the transition from 2D to 3D-integration through the 2.5D-interposers

- Simulations or validations of a 3D-Integrated Circuit

- Design Rules for circuit manufacturing

# 1.5. Methodology

To successfully write this master thesis, the main task was to be based on the existing literature with the most up to-date papers and books to illustrate the current trends and challenges on the market. Since the University of Seville has some collaborations with important entities, e.g. the Society of Photographic Instrumentation Engineers (SPIE), and the online library allows the student to download some e-books, the collaborative work between the professor and the student consisted on looking for the right sources of information so that the student use the university rights to download the available documentation or the professor could send the student the information source via email.

Once that was available, the student has started to deep into the literature and then extract his own conclusions, which have been written in forms of a thesis previously having agreed with the professor about the content. The student has sent regularly his progress to the professor, who has quickly provided feedback about content and format, thus allowing the student for some improvements to achieve this final result.

To mention the usefulness of the online modality of the master, since otherwise the student could have not finished the thesis. The communication between professor and student have been via conference call (Skype) and email exchange, therefore a physical face-to-face was not needed (not possible either).

# 1.6. Planning

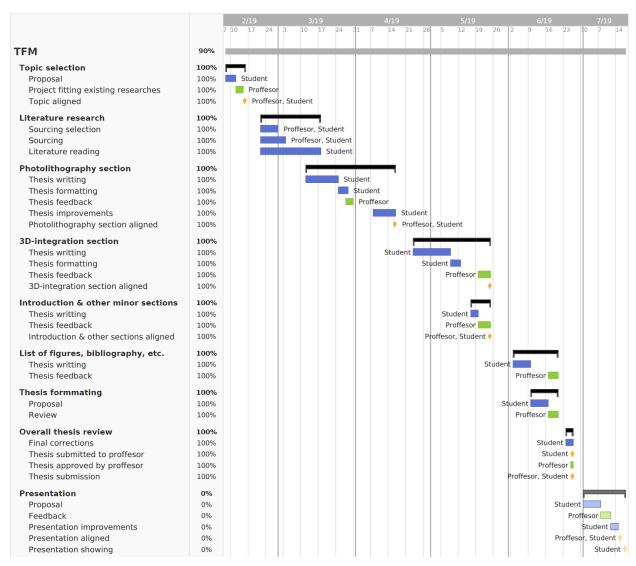

At the <u>figure 4</u> an overview of the overall planning is shown by means of a Gantt chart. The planning shows also the presentation preparation, even when it has not been done at the moment of submitting the master thesis. The past dates represented are the real ones, trying to stick as much as possible to the reality, where some gaps can be seen due to holidays or other business tasks.

Figure 4: Master thesis Gantt chart. Source: own, with Team Gantt tool.

The total realization of the master thesis comprehends 12.0 *ECTS* which are equivalent to 300 hours. The total spent time at the whole master thesis by the student was approximately 97 days, with an average of 3 hours/day, thus making a total of approximately 291 hours (only by the student), which is within the budget. In terms of cost, since there was no finished products to provide and the access to all the literature has been granted through the university collaborations and internal sources, it was limited to the amount of working time.

# 2. State-of-the-art

Since the beginning of the circuits manufacturing, the key process to determine the performance of the chip was to perform the patterning, *i.e.* to replicate a predefined pattern into the circuit so that the different regions are created. This process, called photolithography, continues with the natural trend of doubling the transistor size every two years predicted by Gordon Moore, thanks to the manufacturer innovations to continue decreasing the pattern size. Despite the fact that this process seems to crash soon against physical limitations of the conventional physics, based on analysis of various reports, press announcements, news stories, and technical articles written in the past 20 years, it has been forecasted that the optical lithography can long until 2024 [7].

#### 2.1. Process evolution

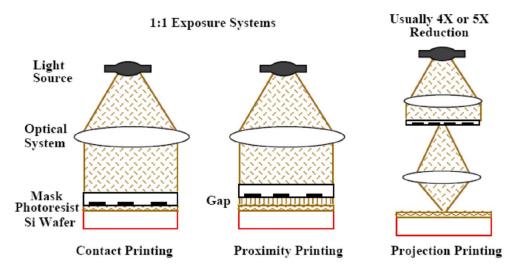

Up to the early 1970s, the most common process to perform the patterning was to use proximity printing or even printing by contact, in which blue and near UltraViolet (*UV*) light was passed through a photomask onto a photoresist-coated semiconductor substrate [8]. However, this fashion was replaced in the 1970s by the projection printing tools manufactured by Perkin-Elmer, the so-called Micralign projection aligners. The main difference for those tools was the performance enhancement, since they scan and image only a portion of the wafer, whereas the previous tools cover the whole wafer at the patterning, as shown in figure 5. Using this methodology, also the optical resolution was improved, since the printed details could be more specified having less field to expose.

Figure 5: Different approaches for printing tools 9.

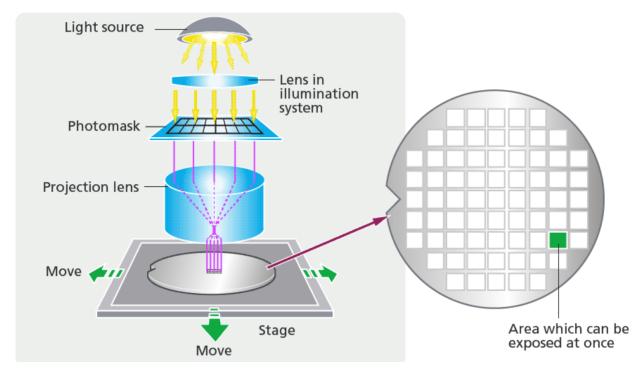

But the main breakthrough in terms of accuracy and performance happened in the early 1980s, where the **steppers** were introduced [10]. The revolution of those new systems was that only one single chip was patterned at a time, performing many times the "stepping-and-repeating" process to cover the whole wafer, which movement is easy to be understood by checking the stepper sketch in figure 6. This has a huge impact on the photomask (also called reticle throughout this thesis) and the lens, since the size of the first one could be enlarged whereas the lens would reduce the size (and thus the accuracy improves) by not augmenting the complexity of the reticle. Another implication of this new process is the improving overlay, in other words, the accuracy of a printed layer versus the previous one (how well they are stacked up), since the small printed areas are controlled independently from each other, allowing correction for wafer- and lens-induced distortion.

Figure 6: Stepper sketch [11].

So far it has been described the reticle movement (scanning) and the wafer movement (stepping), but what about mixing both methodologies? Well, that was the main idea introduced in the mid-1990s with the first tool Microscan by the manufacturer Silicon Valley Group, where both the reticle stage and the wafer stage moved at the same time, thus improving the accuracy and utmost the throughput of the tools. This is also called step-and-scan tool or simply scanner, which is nowadays the most common accepted strategy since it combines all the benefits of the previous invented processes.

#### 2.2. Classification based on the source element

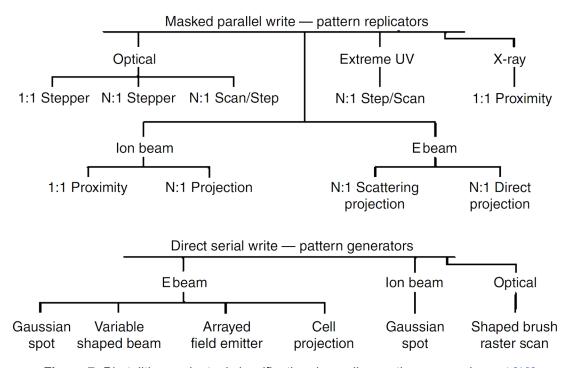

In terms of the element which creates the pattern, one differentiates between pattern generators and pattern replicators, which can be also subdivided depending on the source that they use, in accordance to <u>figure 7</u>.

Figure 7: Photolithography tool classification depending on the source element [12].

- -The **pattern generators** use as input data a database to directly create a physical image on the wafer. They utilize either charged particles or photons to create the image. The photomask fabrication is done with electron or photon beam tools, while the mask pattern defects are repaired with ion and photon beam tools. Their main disadvantage is the throughput (the speed to perform the process), only reaching one single 200 *mm*-wafer per hour, obviously not being that enough to cope with the actual chips demand.

- -The **pattern replicators**, on the other hand, create a master pattern image in the form of a reticle and then replicate the pattern in a massively parallel fashion onto the wafer by means of a projection lens. A variety of image transfer techniques can be used, such as photons and charged particles, having a throughput -depending on the accuracy and extra software packages- on the range of 220-260 wafers/hour for a 300 *mm*-wafer size (one can imagine the amount of difference in terms of money of producing one versus 240 wafers/hour). The most common pattern transfer agent is a well-conditioned beam of monochromatic photons, whose wavelength is in the range of ultraviolet spectrum. The wavelength, in fact, has been decreased in the photolithography history to achieve greater resolution or, in other words, better accuracy

by reducing the pattern size. This has to do with the <u>Rayleigh equation</u>, which will be further explained in the main body of the thesis. Throughout the photolithography history, one can differentiate different element sources, each one with a corresponding wavelength.

- ❖ The most basic approach uses mercury as source (also called as *g*-line of mercury), with a 436 *nm*-light source.

- ❖ The second generation reduces the wavelength until **365** *nm*, being called the *i*-line of mercury.

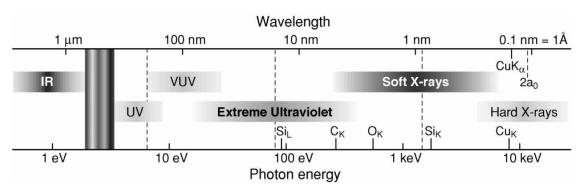

- The main change in terms of the source was to introduce the excimer lasers to replace the High Pressure lamps of mercury, having then very high intensity and a narrower bandwidth, thus reaching the 248 nm wavelength using Krypton Fluoride (KrF) as source element. This light wavelength -and the following generations with even smaller λ- is already at the ultraviolet region, which spectrum is shown in figure 8.

- ❖ The fourth generation uses an Argon Fluoride (ArF) excimer laser, with a wavelength of 193 nm.

- ❖ Some trends researched to go down to a source of 157 nm with Calcium Fluoride (CaF₂) as lens material. However, it needs as required environment the vacuum, and the CaF₂ large intrinsic birefringence complicates the design and manufacturing of high-quality optical lenses [13].

- ❖ The previous three sources are in the region of the Deep UltraViolet (DUV), whereas the new breakthroughs use vacuum and Extreme UltraViolet (EUV) light, reducing the wavelength to an impressive 13 nm (13.5 nm indeed).

Figure 8: Ultraviolet light spectrum [14].

The resolution of each generation has been improved by techniques which will be discussed in the body of this thesis, but one can already observe the correspondence between decreasing the wavelength with the improvement in resolution (the minimum feature size is reduced). The table 1 establishes the correspondence between the light source wavelength and the minimum feature size achieved with that lithography tool.

Table 1: Patterning resolution and photolithography source wavelength [14].

| Minimum feature | <b>5</b> 000 1000 | 1000 250     | 250 100   | 100.00    |              |

|-----------------|-------------------|--------------|-----------|-----------|--------------|

| size (nm)       | 7000–1000         | 1000–350     | 350–180   | 180–32    | 32 and below |

| Lithography     | 436 (G-line)      | 365 (I-line) | 248 (DUV) | 193 (DUV) | 13 (EUV)     |

| wavelength (nm) |                   |              |           |           |              |

# 2.3. Market trends and cutting-edge

The outstanding evolution of the photolithography, with impressive breakthroughs as the immersion lithography and now the EUV lithography, is continuing to reduce the pattern size. At the <u>figure 9</u> the trend can be easily identified, reducing from a pattern of 1.5 microns ( $\mu m$ ) in the early eighties, until the current 7 nm:

Figure 9: Resolution and wavelength trends in lithography [15].

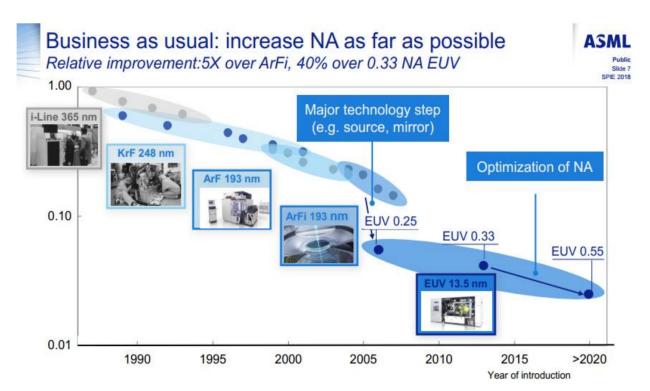

The trend is clear: the Moore's law remains applicable. Every time the microprocessor scaling trend was about to be cut off, anyhow new inventions -such as the *EUV* lithography- came up to continue reducing the patterning size, as sketched in figure 10. But what about the future? Well, the Numerical Aperture (*NA*) of the lens, which defines how good is the resolution at the printed pattern, has become a clear limitation: if the *NA* cannot be further improved (increased) for *EUV*, it is expected to reach a theoretical limitation at 3 *nm*. New devices, such as the Complementary Field-Effect Transistors (*CFETs*) or the Vertical Field-Effect Transistors (*VFETs*), or the integration of three-dimensional (*3D*)-logic at *EUV* lithography with higher *NA*, can make the Moore's law still valid with the von Neumann architecture.

Figure 10: Microprocessors scaling timeline [16].

What is currently in the market? The leading foundries are in mass production using both dry and wet tools (for the most demanding applications). Dry tools are the conventional ones, thus using air surrounding the lens, whereas the wet tools uses water to improve the resolution of the system even further.

But the revolution does not stop there: the transition into the *EUV* lithography is a reality: Samsung is using now the *EUV* light as source to manufacture nodes with 7 *nm* sizes, and it is rumoured [17] that their cell phones for 2021 will include a 3 *nm*-technology node.

The main manufacturer for microprocessors at the cell phone industry, the Taiwan Semiconductor Manufacturing Company (*TSMC*), is more than certain [17] of reducing their pattern size from their current 7 *nm* to 5 *nm*-nodes for the new iPhone to be released in 2020.

At the computer microprocessors, Intel is taking a more safe approach since Global Foundries is not going to use *EUV* in the near future. Intel current nodes of 14 *nm* are expected [18] to shift into *EUV* lithography by mid-2021, when they expect to introduce at the market a 7 *nm*-node.

Other foundries are not using the *EUV* yet (the cost of the tools is hundreds of million euros), since not all the market needs the ultra high accuracy of that technology. Even if a circuit requires that precision in the critical layers, conventional production lines accomplish multiple photolithography tools for different patterning sizes.

# 2.4. Physical limitations

Even with all the advances in lithography, the current manufacturing process as we know it nowadays must finish some day. The semiconductors physics applied to devices of few nanometers is no longer valid, but **quantum physics** has to be considered as well. The physical limitations are almost there:

- ❖ **High electrics fields:** they can create avalanche processes increasing the current passing through the transistor, and thus getting to a chip malfunctioning.

- ❖ Interconnection delays: the parasitic *RC*-network effect is huge for small dimensions, thus having problems with the signal integrity to operate at high frequencies.

- ❖ Heat/power dissipation: the faster the microchip, the more power is dissipated. The figure 11 illustrates that trend, showing that for smaller interconnect delays, the power is increased. Even using very powerful fans the generated heat it is a well-known issue, such as the incident with the batteries for the cell phone Samsung Galaxy Note 7. The only real solution is to completely rethink chip packaging and cooling, for instance having microfluidic channels that increase the effective surface area for heat transfer [19]. The power dissipation is one of the main bottlenecks for keeping on scaling the transistor size, thus the market looking already for packages alternatives such as the 3D-integration. In fact, even when that approach is considered as a potential alternative to mitigate the issue, the heat dissipation at each individual layer remains as one of the major headaches of the industry.

Figure 11: Dissipated power for different interconnect delays [20].

- ❖ Non-uniform doping: due to the small dimensions it is very difficult to control the amount of free electrons and electron holes. Obviously that affects the transistor performance and may drive to a failing device.

- ❖ Oxide thickness: the oxide thickness of the Metal Oxide Semiconductor Field Effect Transistor (MOSFET) determines the size and the leakage current of the transistor, which is approaching atomic levels, thus imposing a practical bound on the leakage current and hence limits transistor sizes [21, 22]. In fact, the maximum current per cross-sectional area generated by the transistor is inversely proportional to the oxide thickness, clearly showing that for small oxide thicknesses, the transistor current will reach an upper limit. The reduced oxide-thickness may also lead to the tunnel-effect at the transistor's gates.

- ❖ Reliability and fault tolerance: with decreasing size, some threats may affect the transistor life. Leakages are present at the nanometer level, particularly the gate and subthreshold leakage, since the transistor channel can no longer contain the electrical current for small dimensions. The device parameters utilized for modelling may also fluctuate, thus causing the device to fail unexpectedly. The signal integrity is also degraded for high-speed and high-integrated circuits due to the coupling, power-supply noise or the propagation delays.

The physical limitations are just referred to the devices themselves. But one has to think also about the manufacturing limitations: the cost to set up a foundry is exponentially increasing, thus posing a threat to the fiability of future technology scaling [23]. And obviously the cost of having less yield due to the beforehand reasons may cause a circuit manufacturing not to be cost-wise efficient. Every device limitation can be translated into extra money for the foundry to tackle the issue: from design and validation, passing by the cost of the equipment, and of course to the non-quality cost associated to devices malfunctioning. The table 2 summarizes the constraints at different levels threatening further development of the Moore's law.

Table 2: The Moore's law limits [24].

| Limits           | Engineering                                                                          | Design and<br>Validation                                          | Energy, time                                                                          | Space, time                                                                          | Information,<br>Complexity                                  |

|------------------|--------------------------------------------------------------------------------------|-------------------------------------------------------------------|---------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-------------------------------------------------------------|

| Funda-<br>mental | Abbe (diffraction)<br>Amdahl<br>Gustafson                                            | Error-corr. &<br>dense codes<br>Fault-<br>tolerance<br>thresholds | Einstein E=mc <sup>2</sup> Heisenberg ΔΕΔt Landauer kT ln2 Bremermann Adiabatic thrms | Speed of light<br>Planck scale<br>Bekenstein<br>Fisher T(n) <sup>1/(d+1)</sup>       | Shannon<br>Holevo<br>NC, NP, #P<br>Turing<br>(decidability) |

| Mate-<br>rial    | Dielectric constant<br>Carrier mobility<br>Surface morphology<br>Fabrication-related | Analytical &<br>numerical<br>modeling                             | Conductivity<br>Permittivity<br>Bandgap<br>Heat flow                                  | Propagation speed<br>Atomic spacing<br>No gravitational<br>collapse                  | Information<br>transfer<br>between<br>carriers              |

| Device           | Gate dielectric<br>Channel charge ctrl<br>Leakage, Latency<br>Crosstalk, Aging       | Compact<br>modeling<br>Parameter<br>selection                     | CMOS, quantum<br>Charge-centric<br>Signal to noise<br>Energy conversion               | Entropy density Entropy flow Interfaces & contacts Universali Size & delay variation |                                                             |

| Circuit          | Delay, Inductance<br>Thermal-related<br>Yield, Reliability, IO                       | Interconnect<br>Test<br>Validation                                | Cooling efficiency Interconnect comp                                                  |                                                                                      | Circuit<br>complexity<br>bounds                             |

| System<br>+SW    | Specification, Implementation<br>Validation, Cost                                    |                                                                   | Synchronization, Physical integration<br>Parallelism, <i>Ab initio</i> limits (Lloyd) |                                                                                      | The CAP<br>theorem                                          |

#### 2.5. Alternatives

Due to the physical limitations -and maybe due to the market dominance of the photolithography processes-, researches and small/medium companies have decided to go in different directions. It seems that in the current future, **new technologies** (such as spintronics [25]) **and/or different materials** (*GaAs*, carbon nanotubes, etc.) might be used: quantum dots [26] or neuromorphic networks can be some solutions to continue decreasing the size, not anymore using the photolithography and -maybe- without the silicon-based wafers that we know so far. A summary of the alternatives with regards to technologies and materials is plotted in figure 12.

Figure 12: New technologies and materials roadmap [20].

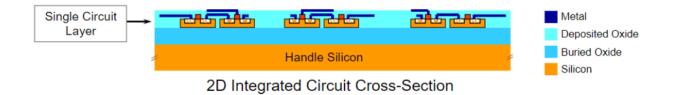

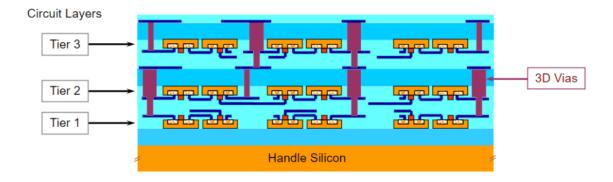

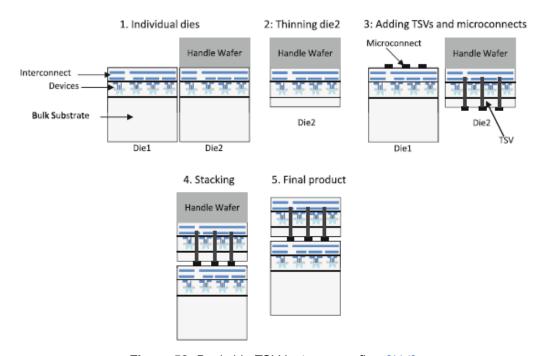

On the other hand, there is a totally different approach that will be addressed throughout this thesis, which is to integrate the conventional circuit in three dimensions. The also known as three-dimensional integrated circuits (3D-ICs) integrate multiple functional IC chips vertically, instead of packing a single chip or multiple chips into a 2D package, as the figure 13 suggests. The different chips are made at different layers, also known as tiers, being connected by vias which makes the connection between the different levels [27].

Figure 13: 2D vs. 3D-Integrated Circuits cross section [28].

3D Integrated Circuit Cross-Section

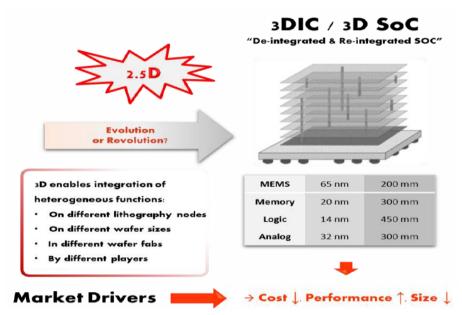

The advantages of this new technology is that it enables heterogeneous integration of materials, processes and functional *IC* chips [29]. In addition to that, the length of the longest interconnects across an integrated circuit is drastically decreased, thus offering unique opportunities for highly heterogeneous and multifunctional systems [30]. 3D-IC technology is not only capable of increase device-density [31], but also offers heterogeneous integration of dies from disparate technologies (analog, digital, mixed signal, sensors, antenna and power storage) and from different technology nodes (65, 32, 22 nm, etc.). Other advantages [32] versus the traditional Systems on a Chip (SoCs) are shown in figure 14, which include lower cost (if High Volume Manufacturing implemented), flexibility by manufacturing different devices by different organizations and higher performance, without unnecessary costs or yield losses due to complexity of simultaneous processing or need to increase silicon space to horizontally accommodate all the devices. On the other hand, also 3D-integration faces some challenges: current manufacturing cost, lack of design availability, lack of *DRAM* stack availability and thermal management (being the latest the reason why the most-consuming tiers are usually placed at both sides of the whole stacking).

The question is now: is the *3D*-integration the evolution of traditional methodologies or a revolution which will replace it?

Figure 14: 3D-ICs advantages [33].

# 3. Body

The main focus of this thesis is the photolithography process, which will cover the <u>main section</u> of the thesis.

Firstly, the process will be described using the <u>Rayleigh equations</u> as starting-point, thus providing the reader <u>the basic physics behind</u> to fully understand the core process. As photolithography is also called optical lithography, an extensive <u>section about optics</u> is needed: the lens behaviour will be explained and the main issues, the optical aberrations, will be addressed and described.

Once the basic concepts have been developed, the main Key Performance Indicator (*KPI*) for the process will be mentioned: the overlay. That figure will be fully explained and, the most important thing, the contributors to its potential failures will be described. The reader may then, by just reading the alignment and overlay subsection, come up with a critical perception of what the basic troubleshooting in moderne circuit manufacturing looks like. A small section about the photolithography tool throughput is also included, trying to convey the approach on the current industry of not only caring about quality but also time and cost.

To finish up the <u>lithography part</u>, an interesting <u>section about the current trends to improve accuracy</u> is added. The idea is to provide an understandable overview of the latest breakthroughs in the process, so that basic know-how of the latests techniques in circuit manufacturing is acquired. Concretely, based on the <u>Rayleigh equations</u>, advances in three fields will be distinguished: working on reducing the Rayleigh constant, increasing the Numerical Aperture and reducing the source wavelength, all of them with the goal of reducing the patterning size.

As mentioned in the <u>introduction</u>, even if the photolithography is the mainstream at the market, potential new solutions need to be used, therefore a <u>different part of the thesis</u> will review the *3D*-integration of the circuits as a serious alternative to the conventional *2D* manufacturing.

With respect to the *3D*-approach, the reader will be firstly presented the <u>market and applications</u>. After that, the main two processes will be described: the <u>Through Silicon Vias</u> (*TSVs*) formation and the <u>bonding</u>. Each process will be firstly described, continuing by highlighting their advantages versus the traditional *2D*-circuits (using photolithography). The cutting-edge of the two processes will be also shown, with a research in the latest applications and market trends.

Despite the fact that both trends seem to work in different directions, *i.e.* lithography on reducing the patterning size and 3D in reducing the dissipated power, the 3D-Integrated Circuits need of photolithography process for manufacturing, but not the latest techniques with the best accuracy. However, what would happen if the solution for the future is to combine both techniques to reduce cycle time and cost for 3D-circuits manufacturing? The last part of the thesis body will research about different novel techniques which are trying to merge both techniques.

# 3.1. Photolithography

Photolithography is the process of defining useful shapes on the surface of a wafer, thus creating the different regions where the physics will act -by means of electrons/holes balance-by building different functionalities and, in the end, composing the whole semiconductor device. The main component for the process is the reticle, which has the patterns to be printed into the substrate, also called wafer.

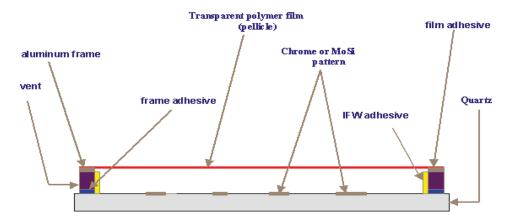

The **reticle** (also called photomask) is depicted in <u>figure 15</u>, being an opaque element with a "written" pattern on it. It consists of a thin sheet with some holes which allows the light to pass through, thus replicating the patterns into the wafer. As the reticle will be used to generate million of Integrated Circuits (*ICs*), one can imagine that if some contamination is found on it, the result will be that the patterned circuits will be wrong, therefore utmost cleanliness of the photolithography tool and, in particular, of the reticle, is mandatory for the circuit manufacturing. To ensure that, a transparent polymer film known as pellicle, protects the printed pattern.

Figure 15: Reticle with pellicle and its rest of components [34].

Not only perfection in terms of cleanliness for the reticle handling is needed but also, due to the fact that they are light sensitive, the lighting used at the clean rooms needs to be yellow (not absorbed by the reticle) in order to avoid chemical reactions with the film which may alter the pattern.

If handling and preservation are critical for the reticle life, one can also infer that the reticles manufacturing has to be at utmost perfection (in terms of accuracy) and taking into account the "well-known" issues which have been learned by trial-error and complex studies, therefore Design Rules (*DR*s) are common in its manufacturing. Reticle cost is therefore very expensive (not talking about its manufacturing lead times), thus being considered by the foundries as "holy" reticles.

A **wafer**, a thin slice of semiconductor *e.g.* crystalline silicon, whose conductivity properties are explained with the energy levels, which represents the silicon -and other semiconductors- as quantized levels of energy forming energy bands. One can differentiate between the conduction and the valence band, which represents the first and the last energy band to be filled by electrons, respectively [35]. Between them it appears the bandgap, where the electrons are forbidden to stay due to their energy. The difference in terms of energy between the conduction and the valence band represents the bandgap energy. An electron can step between levels if its energy is greater than the bandgap energy of the material. The energy is calculated with the Planck's equation, where *h* represents Planck's constant and *f* the incident light frequency, which is also related to *c* (the light speed in vacuum) and *lambda* (the light wavelength).

$$E = h\gamma = h\frac{c}{\lambda} \qquad (3.1.1)$$

On this way, a balance between generated electrons-holes can be chemically -artificially-implemented, where the properties of the silicon makes it ideal to build the electronics that is nowadays used.

The wafer is coated (covered) by a photosensitive material known as **photoresist**, which is an organic material which consists of a polymer base resin with additional components to provide photosensitivity and other properties. Its sensitivity range has to match the wavelength of the light source, thus absorbing only that wavelength allowing the pattern to trespass the coating, so that the pattern is replicated onto the wafer.

The main photoresist figures of merit are the resolution, the process latitudes and the reactive ion etch resistance. The previous features are also photolithography tool-dependent, therefore every change in the process parameters will affect the exposure, as well as using a different coating for the wafers [36]. Additional intrinsic parameters for the photoresist are the sensitivity, the compatibility with industrial standard developers, the adhesion to the substrate, the environmental stability and the shelf life. Obviously each generation of the photolithography process has implied a matching counterpart in the used photoresist, which is summarized at the figure 16.