TELKOMNIKA, Vol.17, No.5, October 2019, pp.2475~2480 ISSN: 1693-6930, accredited First Grade by Kemenristekdikti, Decree No: 21/E/KPT/2018 DOI: 10.12928/TELKOMNIKA.v17i5.11798

2475

# A temperature characterization of (Si-FinFET) based on channel oxide thickness

Yousif Atalla<sup>1</sup>, Yasir Hashim<sup>\*2</sup>, Abdul Nasir Abd Ghafar<sup>3</sup>, Waheb A. Jabbar<sup>4</sup>

<sup>1,3,4</sup>Faculty of Engineering Technology, University Malaysia Pahang (UMP), Lebuhraya Tun Razak, 26300, Pahang, Malaysia <sup>2</sup>Faculty of Engineering, Ishik University, Erbil, Iraq \*Corresponding author, e-mail: yasir.hashim@ieee.org

## Abstract

This paper presents the temperature-gate oxide thickness characteristics of a fin field-effect transistor (FinFET) and discusses the possibility of using such a transistor as a temperature nano-sensor. The investigation of channel oxide thickness–based temperature characteristics is useful to optimized electrical and temperature characteristics of FinFET. Current–voltage characteristics with different temperatures and gate oxide thickness values ( $T_{ox}=1$ , 2, 3, 4, and 5 nm) are initially simulated, and the diode mode connection is considered to measure FinFET's temperature sensitivity. Finding the best temperature sensitivity of FinFET is based on the largest change in current ( $\Delta I$ ) within a working voltage range of 0–5 V. According to the results, the temperature sensitivity of FinFET increases linearly with oxide thickness within the range of 1–5 nm, furthermore, the threshold voltage and drain-induced barrier lowering increase with increasing oxide thickness. Also, the subthreshold swing (SS) is close to the ideal value at the minimum oxide thickness (1 nm) then increases and diverges with increasing oxide thickness. So, the best oxide thickness (nearest SS value to the ideal one) of FinFET under the conditions described in this research is 1 nm.

Keywords: FinFET, nano-sensor, oxide thickness, temperature

## Copyright © 2019 Universitas Ahmad Dahlan. All rights reserved.

## 1. Introduction

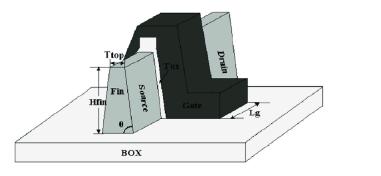

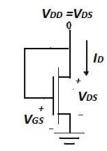

Many new field-effect transistor (FET) structures have been extensively explored [1-6] because metal oxide semiconductor FET (MOSFET) technology is approaching its downscaling limits. One of the relatively new FETs is the fin field-effect transistor (FinFET) as shown Figure 1 [7], a transistor-structured FET that is a popular research subject in the academe and semiconductor industry [8-10]. The ideal example of sensors for subsumed electronic applications (i.e., used within equipment) is the semiconductor temperature sensor [11-15]. Transistor-based temperature sensors are designed based on the temperature characteristics of the current–voltage (I–V) curves of FinFET transistors [16-20]. A bipolar transistor can be utilized as a temperature sensor by connecting its base and collector and operating them in diode mode. Similarly, a transistor with a MOSFET structure can be used as a temperature sensor by connecting oxide thickness to either the source or drain as shown in Figure 2. Electronic devices with nano-dimensions, such as diodes, transistors, capacitors, and resistors, have recently become popular in the electronics industry due to their extremely small electronic circuits.

The performance of new devices, which may correspond to various new applications, commonly depends on the nano-dimensional characteristics of such devices. The chip generation of these relatively new and powerful electronic devices with ultra-small transistors may even be regarded as trustworthy if new findings from future research are consolidated. However, new nano-dimensional FET designs and structures are still novel technologies and thus necessitate additional studies and improvements. Moreover, they require further innovations despite the limitations in MOSFET science.

Electronic device simulation has become increasingly important in understanding the physics behind the structures of new devices. Thus, simulation tools were adopted in this research for the analysis and evaluation of the performance limits of FinFET structures. Experimental work can be supported by simulation tools to explore further the development of

multiple-gate field-effect transistors (MuGFETs) for nano-dimensional characterization [21]. Simulation tools can also help identify device strengths, weaknesses, and retrenchment costs and illustrate the extensibility of these devices in the nm range [22, 23].

Figure 1. FinFET structure [7]

Figure 2. MOSFET as a temperature sensor (Vg=Vd=V<sub>DD</sub>)

## 2. Results and Discussion

In this research, MuGFET was utilized as the simulation tool to investigate the characteristics of FinFET. The output characteristic curves of the transistor under different conditions and parameters were considered. The effects of varying temperature and oxide thickness values on FinFET were determined based on the I–V characteristics derived from the simulation. The MuGFET [24, 25] simulation tool used for FET with a nano-dimensional structure was developed and designed by Purdue University.

MuGFET adopts either PADRE or PROPHET for simulation, both of which were developed by Bell Laboratories. The PROPHET is a partial differential equation profiler for one, two, or three dimensions, and PADRE is a device-oriented simulator for 2D or 3D devices with arbitrary geometry [24, 25]. The software can generate useful characteristic FET curves for engineers to help them fully explain the underlying physics of FETs. MuGFET also provides self-consistent solutions to Poisson and drift-diffusion equations [24, 25] and can be used to simulate the motion of transport objects when calculating FinFET characteristics as shown in Figure 1 [25].

In this research, the Id–Vg characteristics of FinFET at different temperatures of 250, 275, 300, 325, 350, 375, and 400 K were simulated with the following parameters: channel width = 40 nm, channel concentration (P-type) =10<sup>16</sup> cm<sup>-3</sup>, source and drain lengths = 50 nm, source and drain concentrations (N-type)=10<sup>19</sup> cm<sup>-3</sup>, and channel length=85 nm. The oxide thickness values were  $T_{ox}$ =1, 2, 3, 4, and 5 nm. The change in current ( $\Delta$ I) have been calculated when the temperature increased in the V<sub>DD</sub> range of 0–5 V at 0.25 V steps for T<sub>ox</sub> values of 1, 2, 3, 4, and 5 nm. The  $\Delta$ I was calculated depending on the relation:

$$\Delta I(T_{n+1}, Tox) = I(T_{n+1}, Tox) - I(T_n, Tox)$$

<sup>(1)</sup>

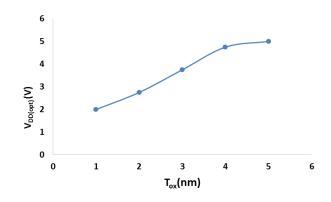

the maximum sensitivities (with max  $\Delta I$ ) became evident to relatively low temperatures, and the values decreased linearly as temperature increased for all V<sub>DD</sub>. The calculations of  $\Delta I$  show that the maximum temperature sensitivity values at V<sub>DD</sub>=2 V (with T<sub>ox</sub>=1 nm), V<sub>DD</sub>=2.75 V (with T<sub>ox</sub>=2 nm), V<sub>DD</sub>=3.75 V (with T<sub>ox</sub>=3 nm) and V<sub>DD</sub>=4.75 V (with T<sub>ox</sub>=4 nm), and V<sub>DD</sub>=5 V (with T<sub>ox</sub>=5 nm).

Figure 3 presents the optimized operating voltage  $V_{DD(opt)}$  based on the maximum temperature sensitivity and oxide thickness, in which the optimized  $V_{DD}$  is related to the temperature sensitivity peaks. Temperature sensitivity increased remarkably until oxide thickness reached 4 nm then increased only slightly from 4 to 5 nm. Hence, a linearly increasing relationship was observed between temperature sensitivity and oxide thickness up to about 5 nm.

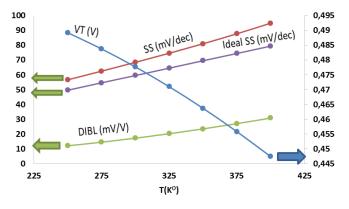

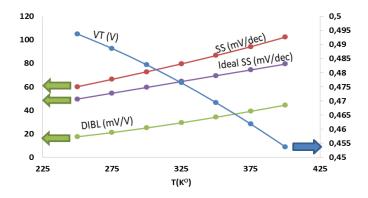

Figure 4 presents the threshold voltage ( $V_T$ ), subthreshold swing (SS), and drain-induced barrier lowering (DIBL) of FinFET. These temperature characteristics were obtained at T=250, 275, 300, 325, 350, 375, and 400 K at T<sub>ox</sub>=1 nm. As presented in this figure,

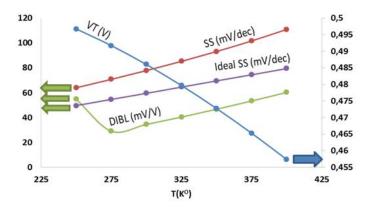

V<sub>T</sub> decreased linearly with increasing temperature, such that V<sub>T</sub>=0.48 V at a low temperature of 250 K and V<sub>T</sub>=0.44 V at a high temperature of 400 K. SS began at 56.63 mV/dec at the lowest temperature (the nearest value to the ideal SS at 49.6 mV/dec) at 250 K and increased until it reached 94.88 mV/dec (the farthest value from the ideal SS at 79.4 mV/dec) at 400 K. DIBL increased as temperature increased. Figure 5 presents the V<sub>T</sub>, SS, and DIBL of FinFET. These temperature characteristics were obtained at T=250, 275, 300, 325, 350, 375, and 400 K at T<sub>ox</sub>=2 nm. V<sub>T</sub> decreased linearly with increasing temperature. Hence, V<sub>T</sub>=0.49 V at a low temperature of 250 K and V<sub>T</sub>=0.45 V at a high temperature of 400 K. SS began at 60.12 mV/dec at the lowest temperature (the nearest value to the ideal SS at 49.6 mV/dec) at 250 K and increased until it reached 102.34 mV/dec (the farthest value from the ideal SS at 79.4 mV/dec) at 400 K. DIBL increased as temperature increased.

Figure 3. Optimized operating voltage V<sub>DD</sub> with different oxide thickness values on the basis of the best temperature sensitivity

Figure 4. V<sub>T</sub>, SS, and DIBL at  $T_{ox} = 1$  nm

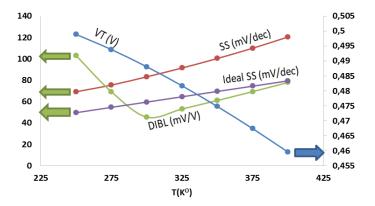

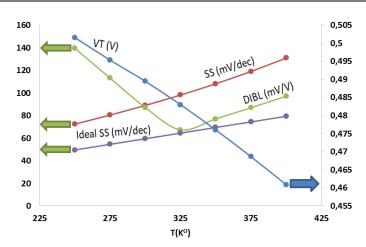

Figure 6 illustrates the V<sub>T</sub>, DIBL, and SS[ characteristics of the FinFET at T=250, 275, 300, 325, 350, 375, and 400 K at T<sub>ox</sub>=3 nm. Temperature increased with oxide thickness. This linear relationship implies that fat reduces fermentation from 250 K to 400 K. Hence, at 250 K and 400 K, V<sub>T</sub>=0.49 and 0.45 V, SS=63.95 and 110.90 mm/dec, and DIBL=54.73 and 60.23 mm/V, respectively. In addition, when temperature increased to 400 K, SS=63.95 mm/dec, which approached the ideal SS=49.6 mm/dec. Figure 7 presents the changes in V<sub>T</sub>, SS, and DIBL and their effects on FinFET properties when temperature was increased from 250 K to 400 K at T<sub>ox</sub>=4 nm. V<sub>T</sub> decreased linearly with increasing temperature. Hence, for 250 K and 400 K, V<sub>T</sub>=0.49 and 0.45 V, SS=69.20 and 120.44 mV/dec, and DIBL=103.06 and 79.4 mV/V, respectively. The figure also illustrates that the obtained value, SS=69.20 mV/dec, is close to the ideal SS = 49.6 mV/dec at 400 K.

Figure 8 shows the change in V<sub>T</sub>, SS, and DIBL and their effect on FinFET properties when temperature was increased from 250 K to 400 K at  $T_{ox}$ =5 nm. V<sub>T</sub>, SS, and DIBL decreased

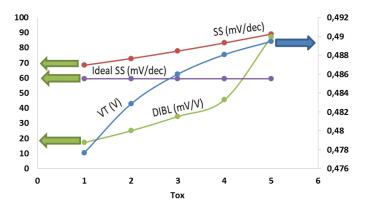

with increasing temperature. This figure particularly presents the limits of the decrease from 250 K to 400 K. Hence, for 250 K and 400 K,  $V_T$ =0.50 and 0.46 V, SS=72.43 and 130.91 mV/dec, and DIBL=139.52 and 97.11 mV/V, respectively. By contrast, the SS values decreased with increasing temperature until they approached the ideal values. Figure 9 presents the properties of  $V_T$ , SS, and DIBL with increasing oxide thickness of FinFET at T=300 K, with 1–5 nm at 1 nm steps,  $V_T$  increased hyperbolically, DIBL increased exponentially, and SS increased linearly with increasing oxide thickness. SS was close to the ideal value at 1 nm, beyond which it increased with increasing oxide thickness. So, according to these results, the best oxide thickness of FinFET under the conditions described in this research is 1 nm.

Figure 5. V<sub>T</sub>, SS, and DIBL at  $T_{ox} = 2 \text{ nm}$

Figure 6. V<sub>T</sub>, SS, and DIBL at  $T_{ox} = 3$  nm

Figure 7. V<sub>T</sub>, SS, and DIBL at  $T_{ox} = 4 \text{ nm}$

Figure 8. V<sub>T</sub>, SS, and DIBL at  $T_{ox} = 5 \text{ nm}$

Figure 9. VT, SS, and DIBL characteristics Tox

### 3. Conclusion

The effects of working temperatures (250, 275, 300, 325, 350, 375, and 400 K) on FinFET characteristics were studied by considering different oxide thickness values ( $T_{ox}$ =1, 2, 3, 4, and 5 nm). According to the results of optimized operating voltage V<sub>DD</sub> with respect to the best temperature sensitivity and oxide thickness, temperature sensitivity increased remarkably until oxide thickness reached 5 nm, then increased only slightly from 4 to 5 nm oxide thicknesses. Hence, a linearly increasing relationship was not observed between temperature sensitivity and oxide thickness beyond 5 nm. V<sub>T</sub> increased hyperbolically, DIBL increased exponentially, and SS increased linearly with increasing oxide thickness of FinFET from 1–5 nm at 1 nm steps. SS was close to the best value at 1 nm then increased with increasing oxide thickness. Therefore, the ideal oxide thickness (low SS) of FinFET under the conditions described in this research is 1 nm. The best oxide thickness of FinFET with excellent V<sub>T</sub>, DIBL and SS under the conditions described in this research is 1 nm.

## Acknowledgment

This research was supported by University Malaysia Pahang under the grant scheme No. (RDU1703284).

#### References

Hashim Y, Sidek O. Nanowire Dimensions Effect on ON/OFF Current Ratio and Sub-Threshold Slope in Silicon Nanowire Transistors. *Journal of nanoscience and nanotechnology*. 2012; 12(9): 7101-7104.

A temperature characterization of (Si-FinFET) based on channel oxide thickness (Yousif Atalla)

- [2] Hashim Y, Sidek O. Study and Simulation of Static Characteristics of Nanowire Inverter with Different Circuit Configurations. *Int. Rev. Model. Simul. (IREMOS).* 2012; 5(1): 93-98.

- [3] Hashim Y. A Review on Transistors in Nano Dimensions. International Journal of Engineering Technology and Sciences (IJETS). 2015; 4(1): 8-18.

- [4] Hashim Y, Sidek O. Dimensional Optimization of Nanowire-Complementary Metal Oxide Semiconductor Inverter. *Journal of nanoscience and nanotechnology*. 2013; 13(1): 242-249.

- [5] Hashim Y, Sidek O. Optimization of Nanowire-Resistance Load Logic Inverter. *Journal of nanoscience and nanotechnology*. 2015; 15(9): 6840-6842.

- [6] Hashim Y. Optimization of channel length nano-scale SiNWT based SRAM cell. AIP Conference Proceedings. 2016; 1774(1): 050020.

- [7] Wu X, Chan P, Chan M. Impacts of Nonrectangular Fin Cross Section on the Electrical Characteristics of FinFET. *IEEE Transactions on Electron Devices*. 2005; 52(1): 63-68.

- [8] Yu B, Chang L, Ahmed S, Wang H, Bell S, Yang C, Tabery C, Ho C, Xiang Q, King T, Bokor J, Hu C, Lin M, Kyser D. *FinFET Scaling to 10 nm Gate Length*. International Electron Devices Meeting (IEDM '02). 2002: 251-254.

- [9] Liu C, Sagong H., Kim H, Choo S, Lee H, Kim Y, Kim H, Jo B, Jin M, Kim J, Ha S, Pae S Park J. Systematical study of 14 nm FinFET reliability: From device level stress to product HTOL. IEEE International Reliability Physics Symposium. 2015: 2F.3.1-2F.3.5.

- [10] Mobarakeh M, Omrani S, Vali M, Bayani A, Omrani N. Theoretical logic performance estimation of Silicon, Germanium and SiGe nanowire Fin-Field Effect Transistor. *Superlattices and Microstructures*. 2018; 120: 578-587.

- [11] Meijer G, Wang G, Fruett F. Temperature sensors and voltage references implemented in CMOS technology. *IEEE Sensors J.* 2001; 1(3): 225-234.

- [12] Jackman J, Cho N, Nishikawa M, Yoshikawa G, Mori T, Shrestha L, Ariga K. Materials Nanoarchitectonics for Mechanical Tools in Chemical/Biological Sensing. *Chem. Asian J.* 2018; 13(22): 3366-3377.

- [13] Hashim Y, Sidek O. *Temperature effect on IV characteristics of Si nanowire transistor*. IEEE Colloquium on Humanities, Science and Engineering. 2011: 331-334.

- [14] Hashim Y, Sidek O. Characterization of Silicon Nanowire transistor as a temperature nano-sensor device. IEEE International Conference on Control System, Computing and Engineering. 2012: 1-4.

- [15] Hashim Y. Temperature effect on ON/OFF current ratio of FinFET transistor. IEEE Regional Symposium on Micro and Nanoelectronics (RSM). 2017: 231-234.

- [16] Liao C, Chen C, Tu K. Thermoelectric characterization of Si thin films in silicon-on-insulator wafer. J. Appl. Phys. 1999; 86(86): 3204-3208.

- [17] Doghish M, Ho F. A comprehensive analytical model for metal-insulator-semiconductor (MIS) devices. IEEE Trans. Electron Devices. 1992; 39(12): 2771-2780.

- [18] Hashim Y, Sidek O. Effect of temperature on the characteristics of silicon nanowire transistor. *Journal of nanoscience and nanotechnology*. 2012; 12(10): 7849-7852.

- [19] Hashim Y, Sidek O. *Temperature effect on IV characteristics of Si nanowire transistor*. IEEE Colloquium on Humanities, Science and Engineering (CHUSER). 2011: 331-334.

- [20] Mahmood A, Jabbar W, Hashim Y, Manap H. Electrical Characterization of Ge-FinFET Transistor Based on Nanoscale Channel Dimensions. *Journal of Nano and Electronic Physics*. 2019; 11(1): 01011.

- [21] Bescond M, Nehari K, Autran J, Cavassilas N, Munteanu D, Lannoo M. 3D quantum modeling and simulation of multiple-gate nanowire MOSFETs. IEDM Tech. Dig. 2004: 617.

- [22] Fahad H, Hu C, Hussain M. Simulation Study of a 3-D Device Integrating FinFET and UTBFET. *IEEE Transactions on Electron Devices*. 2015; 62(1): 83-87.

- [23] Alvarado J, Tinoco J, Salas S, Martinez-Lopez A, Soto-Cruz B, Cerdeira A, Raskin J. SOI FinFET compact model for RF circuits simulation. IEEE 13<sup>th</sup> Topical Meeting on Silicon Monolithic Integrated Circuits in RF Systems (SiRF). 2013: 87-89.

- [24] Hashim Y. Optimization of Resistance Load in 4T-Static Random-Access Memory Cell Based on Silicon Nanowire Transistor. *Journal of Nanoscience and Nanotechnology*. 2018; 18(2): 1199-1201.

- [25] Sung Geun K, Gerhard K, Sriraman D, Benjamin P. *MuGFET*. 2014. https://nanohub.org/resources/NANOFINFET.