Copyright by Ashay Rane 2019 The Dissertation Committee for Ashay Rane certifies that this is the approved version of the following dissertation:

# Broad-Based Side-Channel Defenses for Modern Microprocessors

Committee:

Calvin Lin, Supervisor

Mohit Tiwari, Co-Supervisor

Işil Dillig

Emmett Witchel

David Evans

## Broad-Based Side-Channel Defenses for Modern Microprocessors

by

Ashay Rane

#### DISSERTATION

Presented to the Faculty of the Graduate School of The University of Texas at Austin in Partial Fulfillment of the Requirements for the Degree of

### DOCTOR OF PHILOSOPHY

THE UNIVERSITY OF TEXAS AT AUSTIN May 2019

## Acknowledgments

Had it not been for the heroic efforts of Professor Dan Stanzione, Professor Jim Browne, and Professor Keshav Pingali in enabling me to come to UT Austin, I would never have been able to enroll as a PhD student and, therefore, work on this dissertation. Professor Browne and my PhD supervisor, Professor Calvin Lin, were both instrumental in helping me become acclimatized to the research environment. By virtue of the enthusiastic guidance of Professor Browne, Professor Lin, and my co-supervisor, Professor Mohit Tiwari, I have learned a great deal about various aspects of research, including skills such as picking the right research problems, being thorough with my work, and writing and presenting well. My committee members, Professor Işil Dillig, Professor Emmett Witchel, and Professor David Evans, have also been crucial in improving this dissertation.

Various colleagues have tirelessly provided feedback on my research, and I want to thank them for their contribution. The Spark lab members (Austin, Aydin, Casen, Mikhail, Pranav, Prateek, Riley, Rohith, Shijia, and Willy) and members from Professor Lin's research group (Akanksha, Anjana, Chirag, Curtis, Hao, Jia, Kai, Matthew, Molly, Pawan, and Zhan) have offered both valuable insights and technical assistance at various times throughout my term as a graduate student. Several fellow PhD students including Arthur, John, Rasheed, Roshan, Shilpi, Tyler, and Vance have provided both intellectual stimulation as well as social support through various times. I also thank Greg, Joshua, Raymond, and Varun for opting to work with me towards their Honors thesis.

Finally, and also most importantly, the contributions of my family and friends are invaluable. Without their support and their frequent reminders to stay sane and healthy, none of this work would have seen the light of the day.

## Broad-Based Side-Channel Defenses for Modern Microprocessors

Publication No.

Ashay Rane, Ph.D. The University of Texas at Austin, 2019

> Supervisors: Calvin Lin Mohit Tiwari

Private or confidential information is used in a wide variety of applications, not just including implementations of cryptographic algorithms but also including machine-learning libraries, databases, and parsers. However, even after using techniques such as encryption, authentication, and isolation, it is difficult to maintain the privacy or confidentiality of such information due to so-called side channels, with which attackers can infer sensitive information by monitoring program execution. Various side channels exist such as execution time, power consumption, exceptions, or micro-architectural components such as caches and branch predictors, and such side channels have been used to steal intellectual property, financial information, and sensitive document contents. Although numerous solutions exist for closing side channels, they are point solutions, since each solution closes an isolated set of side channels. In this dissertation, we present three compiler-based solutions—Raccoon, Escort, and VANTAGE—for closing digital side channels (such as the cache, address trace, and branch predictor side channels) that carry information over discrete bits, and for mitigating the a *non-digital* side channel, specifically, the power side channel. Additionally, our compilers are customizable, since they permit the defense to be tailored to the threat model, to the program, and to the microarchitecture.

More broadly, our solutions augment the compiler with information about the lower layers of the computing stack, so that the compiler is aware of potential side channels and so that the compiler can rewrite programs to avoid leaking information through those side channels. In doing so, our solutions define new abstractions that enable the compiler to reason about the program's impact on timing, power consumption, and other similar side channels. Through such abstractions, our compilers detect and prevent a broad set of digital and non-digital leakage on modern microarchitectures.

# Table of Contents

| Acknow  | wledgments                                               | iv        |

|---------|----------------------------------------------------------|-----------|

| Abstra  | act                                                      | vi        |

| List of | Tables                                                   | xii       |

| List of | Figures                                                  | xiv       |

| Chapte  | er 1. Introduction                                       | 1         |

| 1.1     | Inadequacy of Prior Solutions                            | 3         |

| 1.2     | Key Contributions of Our Research                        | 6         |

| 1.3     | Key Insight Used in Our Research                         | 7         |

| 1.4     | Organization of This Dissertation                        | 8         |

| Chapte  | er 2. Overview of This Dissertation                      | 9         |

| 2.1     | Key Ideas                                                | 9         |

| 2.2     | Threat Model                                             | 13        |

| 2.3     | Limitations of Our Approach                              | 16        |

| 2.4     | Related Work                                             | 18        |

|         | 2.4.1 Digital Side Channels                              | 18        |

|         | 2.4.2 Power Side Channel                                 | 21        |

| Chapte  | er 3. Closing Side Channels due to Source-Level Behavior | <b>24</b> |

| 3.1     | Background: Memory Trace Obliviousness                   | 27        |

| 3.2     | System Guarantees                                        | 28        |

| 3.3     | Raccoon Design                                           | 29        |

|         | 3.3.1 Key Properties of Our Solution                     | 30        |

|         | 3.3.2 Oblivious Store Operation                          | 32        |

|         | 3.3.3 Taint Analysis                                     | 33        |

|                            | 3.3.4                                                       | Transaction Management                                                                                                                                                                                                                                                                                                                                                                             | 33                                                                    |

|----------------------------|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

|                            | 3.3.5                                                       | Control-Flow Obfuscation                                                                                                                                                                                                                                                                                                                                                                           | 33                                                                    |

|                            | 3.3.6                                                       | Software Path ORAM                                                                                                                                                                                                                                                                                                                                                                                 | 36                                                                    |

|                            | 3.3.7                                                       | Limiting Termination Channel Leaks                                                                                                                                                                                                                                                                                                                                                                 | 37                                                                    |

|                            | 3.3.8                                                       | Putting It All Together                                                                                                                                                                                                                                                                                                                                                                            | 38                                                                    |

| 3.4                        | Secur                                                       | ity Evaluation                                                                                                                                                                                                                                                                                                                                                                                     | 41                                                                    |

|                            | 3.4.1                                                       | Security of Obfuscated Code                                                                                                                                                                                                                                                                                                                                                                        | 41                                                                    |

|                            | 3.4.2                                                       | Security of Obfuscation Code                                                                                                                                                                                                                                                                                                                                                                       | 45                                                                    |

|                            | 3.4.3                                                       | Termination Leaks                                                                                                                                                                                                                                                                                                                                                                                  | 49                                                                    |

|                            | 3.4.4                                                       | Defense Against Side-Channel Attacks                                                                                                                                                                                                                                                                                                                                                               | 50                                                                    |

| 3.5                        | Perfor                                                      | rmance Evaluation                                                                                                                                                                                                                                                                                                                                                                                  | 52                                                                    |

|                            | 3.5.1                                                       | Obfuscation Overhead                                                                                                                                                                                                                                                                                                                                                                               | 55                                                                    |

|                            | 3.5.2                                                       | Comparison with GhostRider                                                                                                                                                                                                                                                                                                                                                                         | 55                                                                    |

|                            | 3.5.3                                                       | Software Path ORAM                                                                                                                                                                                                                                                                                                                                                                                 | 58                                                                    |

| 3.6                        | Discu                                                       | ssion                                                                                                                                                                                                                                                                                                                                                                                              | 60                                                                    |

| 0.7                        | Concl                                                       | usions                                                                                                                                                                                                                                                                                                                                                                                             | 61                                                                    |

| 3.7                        | Conci                                                       |                                                                                                                                                                                                                                                                                                                                                                                                    | 01                                                                    |

| 3.7<br>Chapt               |                                                             | Closing Side Channels due to Floating-Point In-                                                                                                                                                                                                                                                                                                                                                    |                                                                       |

| Chapt                      | er 4.                                                       | Closing Side Channels due to Floating-Point In-<br>structions                                                                                                                                                                                                                                                                                                                                      | 63                                                                    |

| Chapte<br>4.1              | er 4.<br>Escor                                              | Closing Side Channels due to Floating-Point In-<br>structions<br>t's Guarantees                                                                                                                                                                                                                                                                                                                    | <b>63</b><br>67                                                       |

| Chapt                      | er 4.<br>Escor<br>Backş                                     | Closing Side Channels due to Floating-Point In-<br>structions<br>t's Guarantees                                                                                                                                                                                                                                                                                                                    | <b>63</b><br>67<br>68                                                 |

| Chapte<br>4.1              | er 4.<br>Escor<br>Backg<br>4.2.1                            | Closing Side Channels due to Floating-Point In-<br>structions<br>t's Guarantees                                                                                                                                                                                                                                                                                                                    | <b>63</b><br>67<br>68<br>68                                           |

| <b>Chapt</b><br>4.1<br>4.2 | er 4.<br>Escor<br>Backg<br>4.2.1<br>4.2.2                   | Closing Side Channels due to Floating-Point Instructions         t's Guarantees                                                                                                                                                                                                                                                                                                                    | <b>63</b><br>67<br>68<br>68<br>70                                     |

| Chapte<br>4.1              | er 4.<br>Escor<br>Backg<br>4.2.1<br>4.2.2<br>Our S          | Closing Side Channels due to Floating-Point Instructions         t's Guarantees                                                                                                                                                                                                                                                                                                                    | <b>63</b><br>67<br>68<br>68<br>70<br>70                               |

| <b>Chapt</b><br>4.1<br>4.2 | er 4.<br>Escor<br>Backg<br>4.2.1<br>4.2.2                   | Closing Side Channels due to Floating-Point Instructions         t's Guarantees                                                                                                                                                                                                                                                                                                                    | <b>63</b><br>67<br>68<br>68<br>70<br>70<br>71                         |

| <b>Chapt</b><br>4.1<br>4.2 | er 4.<br>Escor<br>Backg<br>4.2.1<br>4.2.2<br>Our S          | Closing Side Channels due to Floating-Point Instructions         t's Guarantees                                                                                                                                                                                                                                                                                                                    | <b>63</b><br>67<br>68<br>70<br>70<br>71<br>74                         |

| <b>Chapt</b><br>4.1<br>4.2 | er 4.<br>Escor<br>Backg<br>4.2.1<br>4.2.2<br>Our S<br>4.3.1 | Closing Side Channels due to Floating-Point In-<br>structions         t's Guarantees                                                                                                                                                                                                                                                                                                               | <b>63</b><br>67<br>68<br>70<br>70<br>71<br>74<br>74                   |

| <b>Chapt</b><br>4.1<br>4.2 | er 4.<br>Escor<br>Backg<br>4.2.1<br>4.2.2<br>Our S<br>4.3.1 | Closing Side Channels due to Floating-Point Instructions         t's Guarantees                                                                                                                                                                                                                                                                                                                    | <b>63</b><br>67<br>68<br>70<br>70<br>71<br>74                         |

| <b>Chapt</b><br>4.1<br>4.2 | er 4.<br>Escor<br>Backg<br>4.2.1<br>4.2.2<br>Our S<br>4.3.1 | Closing Side Channels due to Floating-Point In-<br>structions         t's Guarantees                                                                                                                                                                                                                                                                                                               | <b>63</b><br>67<br>68<br>68<br>70<br>70<br>71<br>74<br>74<br>74       |

| <b>Chapt</b><br>4.1<br>4.2 | er 4.<br>Escor<br>Backg<br>4.2.1<br>4.2.2<br>Our S<br>4.3.1 | Closing Side Channels due to Floating-Point In-<br>structionst's GuaranteesgroundSubnormal NumbersSubnormal NumbersFloating-Point Error MeasurementGolution: EscortElementary OperationsCompiling Higher-Level Operations4.3.2.1Step 1:Using Secure Elementary Operations4.3.2.2Step 2:Predicating Basic Blocks4.3.2.3Step 3:Linearizing Basic Blocks4.3.2.4Step 4:Controlling Side Effects        | <b>63</b><br>67<br>68<br>68<br>70<br>71<br>74<br>74<br>74<br>74<br>77 |

| <b>Chapt</b><br>4.1<br>4.2 | er 4.<br>Escor<br>Backg<br>4.2.1<br>4.2.2<br>Our S<br>4.3.1 | Closing Side Channels due to Floating-Point In-<br>structionst's GuaranteesgroundSubnormal NumbersSubnormal NumbersFloating-Point Error MeasurementGolution: EscortElementary OperationsCompiling Higher-Level Operations4.3.2.1Step 1: Using Secure Elementary Operations4.3.2.3Step 2: Predicating Basic Blocks4.3.2.4Step 4: Controlling Side Effects4.3.2.5Step 5: Transforming Array Accesses | <b>63</b><br>67<br>68<br>70<br>71<br>74<br>74<br>77<br>77<br>77       |

| <b>Chapt</b><br>4.1<br>4.2 | er 4.<br>Escor<br>Backg<br>4.2.1<br>4.2.2<br>Our S<br>4.3.1 | Closing Side Channels due to Floating-Point In-<br>structionst's GuaranteesgroundSubnormal NumbersSubnormal NumbersFloating-Point Error MeasurementGolution: EscortElementary OperationsCompiling Higher-Level Operations4.3.2.1Step 1:Using Secure Elementary Operations4.3.2.2Step 2:Predicating Basic Blocks4.3.2.3Step 3:Linearizing Basic Blocks4.3.2.4Step 4:Controlling Side Effects        | <b>63</b><br>67<br>68<br>70<br>70<br>71<br>74<br>74                   |

| 4.4               | Secur                                                                                                     | ity Evaluation                                                                                                                                                                                                      | 85                                                                                                                                                                     |

|-------------------|-----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                   | 4.4.1                                                                                                     | Experimental Setup                                                                                                                                                                                                  | 85                                                                                                                                                                     |

|                   |                                                                                                           | 4.4.1.1 Outlier Elimination $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                                                                                                                      | 86                                                                                                                                                                     |

|                   | 4.4.2                                                                                                     | Timing Assurance of Elementary Operations                                                                                                                                                                           | 87                                                                                                                                                                     |

|                   | 4.4.3                                                                                                     | Timing Assurance of Higher-Level Operations                                                                                                                                                                         | 91                                                                                                                                                                     |

|                   | 4.4.4                                                                                                     | Side-Channel Defense in Firefox                                                                                                                                                                                     | 93                                                                                                                                                                     |

|                   | 4.4.5                                                                                                     | Control- and Data-Flow Assurance                                                                                                                                                                                    | 93                                                                                                                                                                     |

|                   |                                                                                                           | 4.4.5.1 Non-Interference Using Inference Rules                                                                                                                                                                      | 95                                                                                                                                                                     |

|                   |                                                                                                           | 4.4.5.2 Defense Against Machine-Learning Attack                                                                                                                                                                     | 96                                                                                                                                                                     |

| 4.5               | Precis                                                                                                    | sion Evaluation                                                                                                                                                                                                     | 97                                                                                                                                                                     |

|                   | 4.5.1                                                                                                     | Comparison Using Unit of Least Precision                                                                                                                                                                            | 97                                                                                                                                                                     |

|                   | 4.5.2                                                                                                     | Comparison of Program Output                                                                                                                                                                                        | 98                                                                                                                                                                     |

| 4.6               | Perfor                                                                                                    | rmance Evaluation                                                                                                                                                                                                   | 100                                                                                                                                                                    |

|                   | 4.6.1                                                                                                     | Impact of Floating-Point Library                                                                                                                                                                                    | 100                                                                                                                                                                    |

|                   | 4.6.2                                                                                                     | Impact of Control Flow Obfuscation                                                                                                                                                                                  | 102                                                                                                                                                                    |

| 4.7               | Concl                                                                                                     | usions                                                                                                                                                                                                              | 104                                                                                                                                                                    |

|                   |                                                                                                           |                                                                                                                                                                                                                     |                                                                                                                                                                        |

| Chapt             |                                                                                                           | Mitimating Non Digital Side Channels                                                                                                                                                                                | 106                                                                                                                                                                    |

| Chapte            |                                                                                                           | Mitigating Non-Digital Side Channels                                                                                                                                                                                | <b>106</b>                                                                                                                                                             |

| 5.1               | Motiv                                                                                                     | ration                                                                                                                                                                                                              | 110                                                                                                                                                                    |

| 5.1               | Motiv<br>Open-                                                                                            | -Source Power Model: McPAT                                                                                                                                                                                          | 110<br>112                                                                                                                                                             |

| 5.1               | Motiv<br>Open-<br>5.2.1                                                                                   | vation          -Source Power Model: McPAT          Analysis of McPAT                                                                                                                                               | 110<br>112<br>112                                                                                                                                                      |

| 5.1               | Motiv<br>Open-<br>5.2.1<br>5.2.2                                                                          | ration                                                                                                                                                                                                              | 110<br>112<br>112<br>113                                                                                                                                               |

| 5.1               | Motiv<br>Open-<br>5.2.1<br>5.2.2<br>5.2.3                                                                 | ration          -Source Power Model: McPAT          -Analysis of McPAT          Our Findings          Validation of the Analysis Results                                                                            | <ol> <li>110</li> <li>112</li> <li>112</li> <li>113</li> <li>115</li> </ol>                                                                                            |

| 5.1<br>5.2        | Motiv<br>Open-<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4                                                        | ration          -Source Power Model: McPAT          -Source Power Model: McPAT          Analysis of McPAT          Our Findings          Validation of the Analysis Results          Design of the VANTAGE Compiler | <ol> <li>110</li> <li>112</li> <li>112</li> <li>113</li> <li>115</li> <li>116</li> </ol>                                                                               |

| 5.1<br>5.2        | Motiv<br>Open-<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>Closed                                              | ration                                                                                                                                                                                                              | <ol> <li>110</li> <li>112</li> <li>112</li> <li>113</li> <li>115</li> <li>116</li> <li>122</li> </ol>                                                                  |

| 5.1<br>5.2        | Motiv<br>Open-<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>Closed<br>5.3.1                                     | ration                                                                                                                                                                                                              | <ol> <li>110</li> <li>112</li> <li>113</li> <li>115</li> <li>116</li> <li>122</li> <li>123</li> </ol>                                                                  |

| 5.1<br>5.2        | Motiv<br>Open-<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>Closed<br>5.3.1<br>5.3.2                            | ration                                                                                                                                                                                                              | <ol> <li>110</li> <li>112</li> <li>113</li> <li>115</li> <li>116</li> <li>122</li> <li>123</li> <li>127</li> </ol>                                                     |

| 5.1<br>5.2<br>5.3 | Motiv<br>Open-<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>Closed<br>5.3.1<br>5.3.2<br>5.3.3                   | ration                                                                                                                                                                                                              | <ul> <li>110</li> <li>112</li> <li>113</li> <li>115</li> <li>116</li> <li>122</li> <li>123</li> <li>127</li> <li>127</li> </ul>                                        |

| 5.1<br>5.2        | Motiv<br>Open-<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>Closed<br>5.3.1<br>5.3.2<br>5.3.3<br>Evalue         | ration                                                                                                                                                                                                              | <ul> <li>110</li> <li>112</li> <li>113</li> <li>115</li> <li>116</li> <li>122</li> <li>123</li> <li>127</li> <li>127</li> <li>128</li> </ul>                           |

| 5.1<br>5.2<br>5.3 | Motiv<br>Open-<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>Closed<br>5.3.1<br>5.3.2<br>5.3.3<br>Evalu<br>5.4.1 | ration                                                                                                                                                                                                              | <ul> <li>110</li> <li>112</li> <li>112</li> <li>113</li> <li>115</li> <li>116</li> <li>122</li> <li>123</li> <li>127</li> <li>127</li> <li>128</li> <li>129</li> </ul> |

| 5.1<br>5.2<br>5.3 | Motiv<br>Open-<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>Closed<br>5.3.1<br>5.3.2<br>5.3.3<br>Evalue         | ration                                                                                                                                                                                                              | <ul> <li>110</li> <li>112</li> <li>113</li> <li>115</li> <li>116</li> <li>122</li> <li>123</li> <li>127</li> <li>127</li> <li>128</li> </ul>                           |

|       | 5.4.3.1 Security Evaluation $\ldots$ | 133 |

|-------|--------------------------------------|-----|

|       | 5.4.3.2 Performance Evaluation       | 135 |

| 5.5   | Discussion                           | 137 |

| 5.6   | Conclusion and Future Work           | 138 |

| Chapt | er 6. Conclusion and Future Work     | 139 |

|       |                                      |     |

| 6.1   | Future Work                          | 140 |

## List of Tables

| Entry-points of Raccoon's library                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 45                                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|

| Categorized list of x86 hardware exceptions                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 49                                          |

| Benchmark programs used for performance evaluation of Rac-<br>coon. The bottom eight programs are also used to evaluate<br>GhostRider. The remaining seven programs cannot be trans-<br>formed by GhostRider because these programs use pointers and<br>invoke functions in the secret context                                                                                                                                                                                                       | 52                                          |

| Latency (in cycles) of the SQRTSS instruction for various operands.                                                                                                                                                                                                                                                                                                                                                                                                                                  | 64                                          |

| Predicates per line for function in Figure 4.8b                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 83                                          |

| Number of discarded outliers from 100 million double-precision square-root operations. The results indicate that our outlier elimination process is statistically independent of the input operand values.                                                                                                                                                                                                                                                                                           | 87                                          |

| Comparison of standard deviation of running times of elemen-<br>tary operations across six types of values (zero, normal, sub-<br>normal, $+\infty$ , $-\infty$ , and not-a-number). Numbers in parenthesis<br>show the standard deviation as a percentage of the mean. The<br><b>-sp</b> suffix identifies single-precision operations while the <b>-dp</b><br>suffix identifies double-precision operations. Compared to SSE<br>operations, Escort exhibits negligible variation in running times. | 89                                          |

| Standard deviation of 10 million measurements for each type of value (normal, subnormal, and not-a-number). All standard deviation values are within 3.1% of the mean. Furthermore, the mean of these 10,000,000 measurements is always within 2.7% of the representative measurement.                                                                                                                                                                                                               | 90                                          |

| Inference rules for verifying the security of Escort's higher-level operations.                                                                                                                                                                                                                                                                                                                                                                                                                      | 94                                          |

| Floating-point difference for 10,000 operations on random in-<br>puts in terms of Unit of Least Precision (ULP) in <b>FTFP versus</b><br><b>Musl C library</b> . Since we observe zero ULP distance between<br>Escort's results and Musl's results, this table omits Escort's re-<br>sults.                                                                                                                                                                                                          | 97                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Categorized list of x86 hardware exceptions |

| 4.8  | Distribution of differences in answers produced by MINPACK-<br>FTFP and MINPACK-C. In all, 321 values differ between the<br>outputs of the two programs.                                                                                                                                                                  | 99  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.9  | Overhead of SPEC-ESCORT (SPECfp2006 using Escort oper-<br>ations) relative to SPEC-LIBC (SPECfp2006 using libc)                                                                                                                                                                                                           | 100 |

| 4.10 | Overhead of Escort on $\text{SVM}^{light}$ program                                                                                                                                                                                                                                                                        | 101 |

| 4.11 | Performance comparison of benchmarks compiled using Rac-<br>coon and Escort. We only compare the control flow obfuscation<br>overhead, since both Raccoon and Escort use the same tech-<br>nique for data access obfuscation.                                                                                             | 103 |

| 5.1  | Energy consumption (measured using Intel RAPL) while run-<br>ning the LibSVM classifier [20] that labels data from the KDD<br>Cup dataset [10]. We observe that energy consumption is a<br>reasonable indicator of the label of the input data                                                                            | 110 |

| 5.2  | x64 instructions whose operand values trigger variable number<br>of microcode operations.                                                                                                                                                                                                                                 | 114 |

| 5.3  | The 21 chosen performance events for computing the regression<br>between microarchitectural events and energy consumption and<br>their corresponding coefficients (after rounding to one decimal).                                                                                                                        | 125 |

| 5.4  | Accuracy of the new regression models based on 100 ms mea-<br>surements of a subset of the PARSEC benchmarks using Intel<br>RAPL. The remaining benchmarks failed to either compile or<br>run on our platform.                                                                                                            | 128 |

| 5.5  | Mean Area Under the Curve (AUC) and standard deviation for<br>ROC curves corresponding to non-secure and secure (VANTAGE)<br>execution over 500 summaries. We observe that six benchmark<br>applications are vulnerable to power channel attacks, and VAN-<br>TAGE thwarts the attack in the transformed (VANTAGE) execu- |     |

|      | tion                                                                                                                                                                                                                                                                                                                      | 134 |

# List of Figures

| 1.1 | Code fragment to demonstrate side channels                                                                                                                                                                                                                                                                                                                                                        | 2  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | In a point solution that adds dummy NOP instructions to ensure<br>that the instruction count does not leak information, the execu-<br>tion time can still leak information. A different point solution<br>that adds NOP instructions to balance the execution time will<br>need to add many more NOP instructions in the else path, thus<br>breaking the security guarantee of the former defense | 3  |

| 1.3 | A point solution that adds a dummy load instruction (to hide variations in the number of runtime load instructions) is susceptible to compiler optimizations (like Dead Code Elimination) which will break the solution's security guarantees.                                                                                                                                                    | 4  |

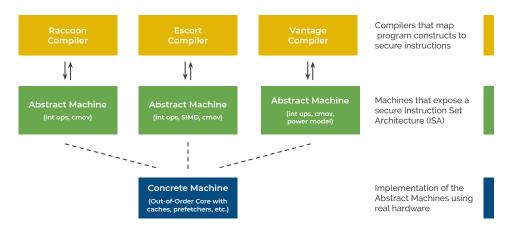

| 2.1 | Our compilers map various programming constructs to instruc-<br>tions of an abstract machine. We derive the abstract machine<br>by analyzing various ISAs and microarchitectures                                                                                                                                                                                                                  | 10 |

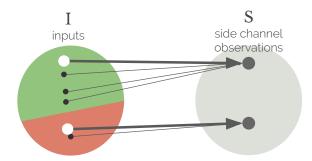

| 2.2 | If the input set can be partitioned based on the distinct side-<br>channel observations, then we can evaluate the user's compu-<br>tation on only one input per partition instead of evaluating it<br>once for each input, thus reducing the performance impact                                                                                                                                   | 12 |

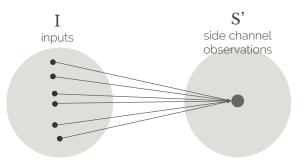

| 2.3 | Illustration of the leakage function of a computation whose in-<br>puts result in an identical side-channel observation                                                                                                                                                                                                                                                                           | 13 |

| 3.1 | Illustrating the importance of Property 2. This code fragment<br>shows how solutions that do not update memory along decoy<br>paths may leak information. If the decoy path is not allowed<br>to update memory, then the dereferenced pointer in line 7 will<br>access $a$ instead of accessing $b$ , which reveals that the statement<br>was part of a decoy path.                               | 30 |

| 3.2 | Source code to compute $m^s \mod n$ .                                                                                                                                                                                                                                                                                                                                                             | 31 |

| 3.3 | CMOV wrapper                                                                                                                                                                                                                                                                                                                                                                                      | 32 |

| 3.4 | Pseudocode for transaction buffer accesses. Equality checks are implemented using XOR operation to prevent the compiler from introducing an explicit branch instruction.                                                                                                                                                                                                                          | 34 |

| 3.5 | Sample code and transformed pseudocode                                                                                                                                                                                                                                                                                                                                                            | 39 |

|     |                                                                                                                                                                                                                                                                                                                                                                                                   |    |

| 3.6  | Typing rules and supporting functions that check security of Raccoon's code                                                                                                                                                                                                                                                                          | 46 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

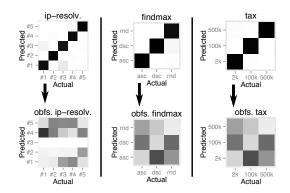

| 3.7  | Confusion matrices for ip-resolv, find-max and tax. The top matrices describe original execution. The bottom matrices describe obfuscated execution.                                                                                                                                                                                                 | 51 |

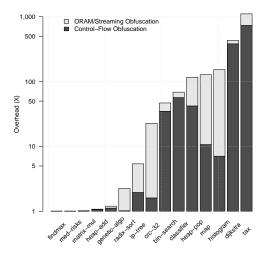

| 3.8  | Sources of obfuscation overhead                                                                                                                                                                                                                                                                                                                      | 54 |

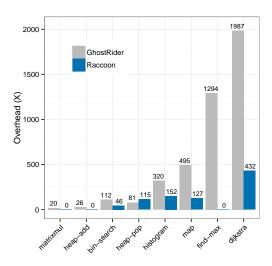

| 3.9  | Overhead comparison on GhostRider's benchmarks. Even when<br>we generously underestimate GhostRider's overhead, GhostRider<br>sees an average overhead of $195 \times$ , while Raccoon's overhead is<br>$21.8 \times \ldots \times $ | 54 |

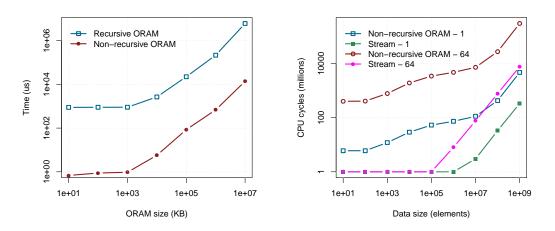

| 3.10 | Software ORAM performance                                                                                                                                                                                                                                                                                                                            | 58 |

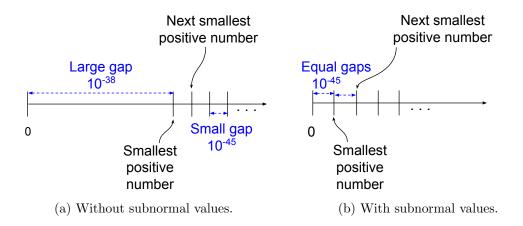

| 4.1  | Impact of allowing subnormal numbers. Without subnormal values, there exists a much larger gap between zero and the smallest positive number than between the first two smallest positive numbers. With subnormal numbers, the values are more equally spaced. (The figure is not drawn to scale.)                                                   | 68 |

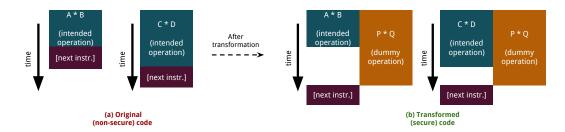

| 4.2  | The key idea behind Escort's secure elementary operations. The operation is forced to exhibit a fixed latency by executing a fixed-latency long-running operation in a spare SIMD lane                                                                                                                                                               | 71 |

| 4.3  | Escort's implementation of double-precision multiplication, using the AT&T syntax.                                                                                                                                                                                                                                                                   | 72 |

| 4.4  | Code for conditional data copy operation that does not leak<br>information over digital side channels. This function returns<br>t_val if pred is true; otherwise it returns f_val. The assembly<br>code uses AT&T syntax                                                                                                                             | 73 |

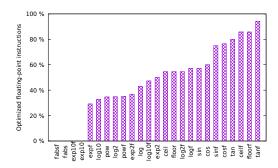

| 4.5  | Percentage of instructions that are left uninstrumented (without sacrificing security) after consulting the SMT solver                                                                                                                                                                                                                               | 74 |

| 4.6  | Algorithm for predicating basic blocks.                                                                                                                                                                                                                                                                                                              | 76 |

| 4.7  | The use of pointers can leak information. If store instructions are not allowed to access memory when the basic block's predicate is false, then pointer $p$ will dereference the address for $a$ instead of $b$ , thus revealing that <i>secret</i> is true                                                                                         | 78 |

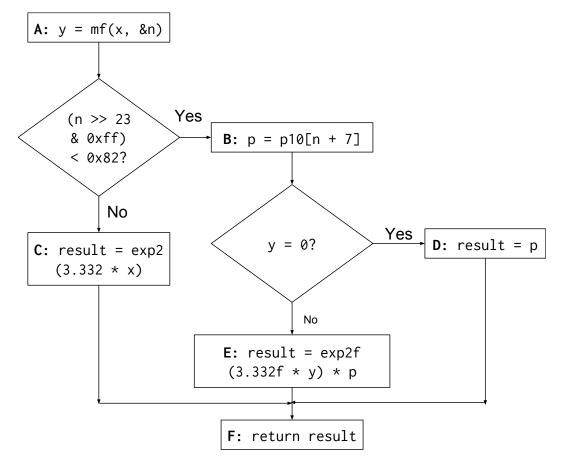

| 4.8  | Escort's transformation of explof()                                                                                                                                                                                                                                                                                                                  | 82 |

| 4.9  | Control flow graph with labeled statements for the code in Figure 4.8b. A, B, D, E, C, F is one possible sequence of basic blocks when linearized by the Escort compiler.                                                                                                                                                                            | 84 |

|      |                                                                                                                                                                                                                                                                                                                                                      |    |

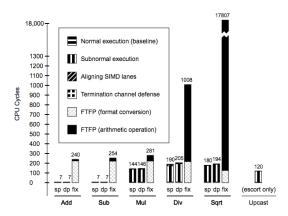

| 4.10 | Comparison of running times of elementary operations. <b>sp</b> iden-<br>tifies Escort's single-precision operations, <b>dp</b> identifies Escort's<br>double-precision operations, and <b>fix</b> identifies FTFP's fixed-<br>point operations. Numbers at the top of the bars show the total<br>cycle count. We see that Escort's execution times are dominated<br>by the cost of subnormal operations, and we see that FTFP's<br>overheads are significantly greater than Escort's | 88  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

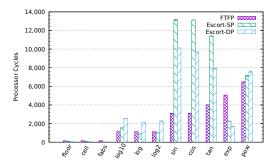

| 4.11 | Comparison of running times of commonly used higher-level functions. Error bars (visible for only a few functions) show the maximum variation in running time for different kinds of input values.                                                                                                                                                                                                                                                                                    | 91  |

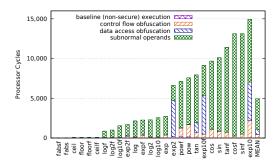

| 4.12 | Performance breakdown of Escort's commonly used higher-level<br>functions. The baseline (non-secure) execution and exception<br>handling together cost less than 250 cycles for each function,<br>making them too small to be clearly visible in the above plot.                                                                                                                                                                                                                      | 92  |

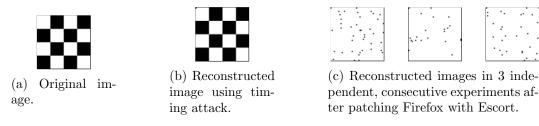

| 4.13 | Results of attack and defense on a vulnerable Firefox browser<br>using timing-channel information leaks arising from the use of<br>subnormal floating-point numbers                                                                                                                                                                                                                                                                                                                   | 92  |

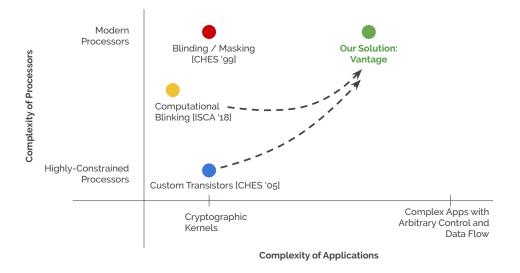

| 5.1  | Relative comparison of power side-channel defenses. Our solu-<br>tion, VANTAGE, enables protection for a broad class of applica-<br>tions running on modern microprocessors, by building on exist-<br>ing techniques like Computational Blinking or Custom Transis-<br>tors.                                                                                                                                                                                                          | 107 |

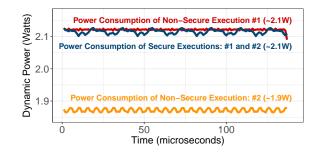

| 5.2  | Power consumption of the LibSVM classifier before and after<br>using our solution (measured using McPAT). The non-secure<br>executions (shown in red and orange), produce a visually dis-<br>tinct profile of power consumption, whereas after using our so-<br>lution, for all secrets, the power profiles are identical (shown as<br>a single line in blue), effectively mitigating the power channel<br>attack.                                                                    | 111 |

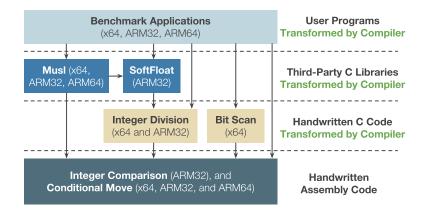

| 5.3  | Dependences among runtime components for compiling pro-<br>grams using VANTAGE                                                                                                                                                                                                                                                                                                                                                                                                        | 117 |

| 5.4  | Conditional move operation for x64, ARM 32, and ARM 64.<br>The code does not leak the secret condition through power con-<br>sumption.                                                                                                                                                                                                                                                                                                                                                | 119 |

| 5.5  | C Code for bit scan forward operation that is later transformed<br>using the VANTAGE compiler.                                                                                                                                                                                                                                                                                                                                                                                        | 120 |

| 5.6  | C Code for unsigned integer division that is later transformed<br>using the VANTAGE compiler. We mark the numerator and the<br>denominator inputs as secret.                                                                                                                                                                                                                                                                                                                          | 121 |

| 5.7  | Not-equals comparison without causing power variations                                                                                                                                                                                                                                                                                                                    | 122 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.8  | Unsigned greater-than comparison without causing power vari-<br>ations                                                                                                                                                                                                                                                                                                    | 123 |

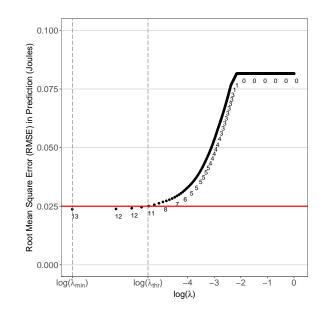

| 5.9  | The prediction error increases as $\lambda$ increases beyond $\lambda_{min}$ , which<br>produces the smallest prediction error. We are interested in the<br>value of $\lambda$ for which the prediction error is close to the smallest<br>prediction error. Digits on the curve indicate the number of<br>non-zero coefficients for the corresponding values of $\lambda$ | 126 |

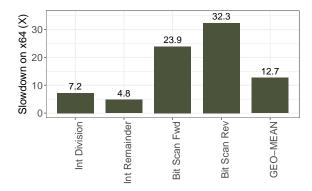

| 5.10 | Performance overhead of transformed 32-bit division, remain-<br>der, and bit scan code on the x64 target                                                                                                                                                                                                                                                                  | 130 |

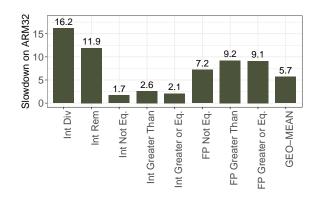

| 5.11 | Performance overhead of transformed 32-bit division, remain-<br>der, and comparison on ARM 32 target.                                                                                                                                                                                                                                                                     | 131 |

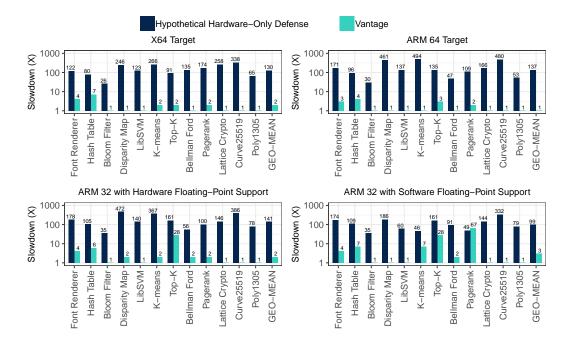

| 5.12 | Performance overhead of VANTAGE on x64, ARM 32, and ARM 64 targets.                                                                                                                                                                                                                                                                                                       | 132 |

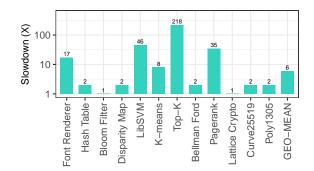

| 5.13 | Performance overhead of VANTAGE-RAPL                                                                                                                                                                                                                                                                                                                                      | 135 |

## Chapter 1

### Introduction

Private or confidential information is used by a wide variety of applications including machine-learning libraries, which analyze personal browsing histories to recommend products [60], social networking tools, which analyze graphs that represent connections between persons [82], and cloud services (such as online maps), which provide directions based on the location of their users [74]. Unfortunately, it is difficult to keep all of this sensitive information private, because although there exist many techniques such as encryption, access control, and isolation to prevent the accidental disclosure or leakage of sensitive information, these techniques are not sufficient. In particular, attackers can steal sensitive information through so-called side channels, which are means by which an attacker can monitor program execution to reveal sensitive information in the program.

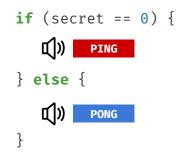

To understand side channels, consider the program shown in Figure 1.1, where the code emits a sound *ping* if **secret** is zero and it emits a sound *pong* otherwise. Given such a program, an attacker who hears the sound *ping* knows that **secret** must be equal to zero. Similarly, if the attacker hears the sound *pong*, then she knows that the secret must be not equal to zero. Thus the

Figure 1.1: Code fragment to demonstrate side channels.

presence or absence of the *ping* or *pong* sounds inadvertently leaks the value of the **secret** variable, and hence the audible sounds become side channels. Although programs do not typically emit audible sounds, they usually exhibit many kinds of *variations* that produce the same effect of leaking sensitive information.

More formally, a side channel is any variation in a system's behavior, such that the variation is (1) is visible to an attacker and (2) dependent on sensitive information. Thus, the variations reveal sensitive values, thus becoming side channels of sensitive information.

Numerous side channels exist, including execution time, memory access, instruction count, cache behavior, DRAM address trace, power consumption, and electromagnetic radiation. Side-channel attacks are significant because attackers have used side channels to break AES [80] and RSA [83] encryption schemes, to break the Diffie-Hellman key exchange [50], to fingerprint software libraries [123], and to reverse-engineer commercial processors [53].

```

if (secret == 0) {

x <- load ptr_1 // 5 cycles

y <- load ptr_2 // 5 cycles

} else {

NOP // 1 cycle

NOP // 1 cycle

}

total 2 cycles

for else path</pre>

```

Figure 1.2: In a point solution that adds dummy NOP instructions to ensure that the instruction count does not leak information, the execution time can still leak information. A different point solution that adds NOP instructions to balance the execution time will need to add many more NOP instructions in the else path, thus breaking the security guarantee of the former defense.

#### **1.1** Inadequacy of Prior Solutions

Numerous solutions exist for closing side channels [33, 34, 49, 61, 62, 65, 66, 73, 93, 96, 97, 99, 105, 108, 111, 112, 117–119], and we compare our solutions against them in Section 2.4 (Related Work). However, the common characteristic across these prior solutions is that they are *point* solutions, since they each close an isolated set of side channels. Consequently, there exist separate solutions for closing the execution time side channel [66, 73, 94], separate solutions for the branch predictor side channel [25, 56, 73], for the DRAM address trace side channel [4, 8, 61, 62], and so on.

Point solutions suffer from two major drawbacks, which we describe below.

Lack of Composability. Point solutions do not always compose with each

```

if (secret == 0) {

x <- load ptr_1

y <- load ptr_2

} else {

z <- load ptr_3

d < load dummy

}

Dead Code

Elimination</pre>

```

Figure 1.3: A point solution that adds a dummy load instruction (to hide variations in the number of runtime load instructions) is susceptible to compiler optimizations (like Dead Code Elimination) which will break the solution's security guarantees.

other. More precisely, the use of one point solution can break the security guarantees of another point solution. Moreover, arguing about security can be difficult when multiple point solutions are combined. For instance, consider a cache side-channel defense that randomly evicts cache lines so as to confuse an adversary monitoring the cache usage [63, 111]. Such a defense cannot be easily and securely composed with a DRAM address trace side-channel defense which expects a predictable stream of memory requests from the CPU [61]. As another example, Figure 1.2 shows how a defense for the instruction count side channel breaks the security guarantee of a defense for the execution time side channel.

**Disabled Optimizations.** Since optimizations can break the security guarantees of point solutions, the use of point solutions can force us to significantly re-engineer compilers and microarchitectures. For instance, consider a solution that adds dummy load instructions to hide variations in the load instruction count [61], as shown in Figure 1.3. Unfortunately, common compiler optimizations such as Dead Code Elimination, Loop Invariant Code Motion, and Instruction Combining interfere with the desired security guarantees so such a point solution is forced to disable many compiler optimizations. The same point solution is also vulnerable to microarchitectural optimizations such as caches, since a *dummy* load instruction could consume a different execution time than a *real* load instruction. Several other microarchitectural optimizations such as prefetchers, branch prediction, and variable-latency instructions also break the security guarantee of this point solution. Consequently, the use of point solutions can require hardware vendors to design new significantly slower hardware to support these side-channel defenses.

Ultimately, point solutions represent a patchwork approach, whose security is difficult to assert in the presence of other point solutions and in the presence of common optimizations. Consequently, point solutions are extremely limited in not just the number of side channels that they can close, but also in the kinds of programs and the kinds of microarchitectures that they can protect. Perhaps unsurprisingly, a number of point solutions have been evaluated using only small cryptographic kernels [56, 63, 100, 114, 121], such as implementations of Advanced Encryption Standard (AES), or on programs using only simple control flow [7, 61, 62, 79], thus ruling out loops and floating-point arithmetic operations.

#### **1.2** Key Contributions of Our Research