#### Energy-Efficient Neural Network Hardware Design and Circuit Techniques to Enhance Hardware Security

# A DISSERTATION SUBMITTED TO THE FACULTY OF THE GRADUATE SCHOOL UNIVERSITY OF MINNESOTA BY

Muqing Liu

#### IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

Prof. Chris H. Kim, Adviser

May 2019

#### Acknowledgements

The body of research detailed in this dissertation would not have been possible without the support of multiple organizations. This research has been financially supported, in part, by the National Science Foundation under award number CNS-1441639 and THE Semiconductor Research Corporation under contract number 2014-TS-2560. Additionally, I need to acknowledge the valuable contribution of the University Programs of Cadence Design Systems, Inc., Mentor Graphics, and Synopsys, Inc. for providing access to design and verification tools utilized in this research.

I would like to express my thanks and appreciation to my committee members for their guidance, instruction, and encouragement. Prof. Chris H. Kim has been a valued advisor and mentor throughout my Ph.D. study. Prof. Kim's guidance helped me in all the time of my research. Prof. Keshab Parhi, Prof. Sachin Sapatnekar, Prof. Maria Gini and Prof. Qi Zhao have graciously agreed to take part in my prelim and final committee, and I appreciate their perspective and guidance.

My colleagues at the University of Minnesota VLSI Lab are a great team to work with on a daily basis. I thank all my fellow lab mates for the stimulating discussions and for all the fun we have had in the last four years. I would like to extend my special thanks to Qianying Tang, Chen Zhou, Po-wei Chiu and Luke Everson for their help and contribution in this research. Their timely help and valuable discussion enabled us to meet critical deadlines and keep the project on time. I thank them for their investment of time and effort.

I am thankful to Luke Everson for introducing the opportunity to me to conduct research at IMEC, Belgium. I am also thankful to Dr. Dwaipayan Biswas at IMEC for the mentoring at IMEC. The valuable support, suggestion and feedbacks he gave me during my stay at IMEC helped me a lot in finishing the LSTM architecture design.

Most importantly, I express my deepest appreciation and thanks to my parents and for their patience, prayers, and support. They are a source of constant encouragement and have provided me with the opportunity to pursue this goal.

#### **Dedication**

I dedicate this work to my family, teachers and my mentor, Prof. Chris H. Kim, who is the person who took me into the academic world in the first place and has guided me through all the way in my Ph. D. study.

#### **Abstract**

Artificial intelligence algorithms and hardware are being developed at a rapid pace for emerging applications such as self-driving cars, speech/image/video recognition, deep learning, etc. Today's AI tasks are performed at remote datacenters, while in the future, more AI workloads are expected to run on edge devices. To fulfill this goal, innovative design techniques are needed to improve energy-efficiency, form factor, and as well as the security of AI chips.

In this dissertation, two topics are focused on to address these challenges: building energy-efficient AI chips based on various neural network architectures, and designing "chip fingerprint" circuits as well as counterfeit chip sensors to improve hardware security.

First of all, in order to deploy AI tasks on edge devices, we come up with energy and area efficient computing platforms based on both multi-layer perceptron (MLP) neural network and long short-term memory (LSTM) neural network. For the MLP neural network, we built a new neural network computation paradigm based on time domain computing. Our first time-based neural network prototype shows orders of magnitude less area and lower power consumption compared to traditional digital or analog domain approaches. A parallel two-layer MLP architecture realized using the proposed core achieves a 91% accuracy in handwritten digit recognition application using MNIST database. For the LSTM neural network, we proposed a binarized LSTM architecture, which greatly simplifies the circuit complexity and reduces the memory footprint, making it suitable to be deployed on edge devices. This proposed network is demonstrated using

an application of heart rate prediction from photoplethysmorgrahpy (PPG) signals, and achieves a good prediction accuracy.

Secondly, to enhance the security of the devices and ensure secure data communication between devices, we need to make sure the authenticity of the chip. Physical Unclonable Function (PUF) is a circuit primitive that can serve as a chip "fingerprint" by generating a unique ID for each chip. The stability of this generated ID is of utmost importance. We proposed a method to select the most stable cells in a large memory array to make sure the output of a memory based PUF is always consistent. Another source of security concerns comes from the counterfeit ICs, and recycled and remarked ICs account for more than 80% of the counterfeit electronics. To effectively detect those counterfeit chips that have been physically compromised, we came up with a passive IC tamper sensor. This proposed sensor is demonstrated to be able to efficiently and reliably detect suspicious activities such as high temperature cycling, ambient humidity rise, and increased dust particles in the chip cavity.

## **Table of Contents**

| List o | of Tables                                                       | ix   |

|--------|-----------------------------------------------------------------|------|

| List o | of Figures                                                      | ix   |

| Chap   | ter 1. Introduction                                             | 1    |

| 1.1    | Time based MLP Neural Networks                                  | 3    |

| 1.2    | Binarized LSTM Architecture                                     | 4    |

| 1.3    | Chip Fingerprint based on Memory Circuits                       | 5    |

| 1.4    | Passive Counterfeit IC Sensor                                   | 6    |

| 1.5    | Summary of Dissertation Contribution                            | 6    |

| Chap   | ter 2. Time-based Integrate-and-Fire Neuromorphic Core Design   | 8    |

| 2.1    | Introduction                                                    | 8    |

| 2.2    | MLP Neural Network Background                                   | 11   |

| 2      | 2.2.1 Multi-Layer Perceptron (MLP) Neural Network               | 11   |

| 2      | 2.2.2 Integrate-and-fire Neuron Model                           | 12   |

| 2.3    | Time-based Integrate-and-Fire DCO Neuromorphic                  | 13   |

| 2      | 2.3.1 Advantages of Time-based Implementation of Neural Network | 13   |

| 2      | 2.3.2 Implementation of Time-based DCO Neuromorphic Core        | 15   |

| 2      | 2.3.3 Characterization of DCO Neuromorphic Core                 | 22   |

| 2.4    | Leak and Local Lateral Inhibition                               | 25   |

| 2.5    | Digit Recognition Application and Measurement Results           | 29   |

| 2.6    | Conclusion.                                                     | 39   |

| Chap   | ter 3. Binarized LSTM Neural Network Architecture Design        | . 41 |

| 3.1    | Introduction                                                    | 41   |

| 3.2   | 2 LSTM and PPG Background                                          | 42         |

|-------|--------------------------------------------------------------------|------------|

| •     | 3.2.1 LSTM Neural Network                                          | 42         |

| •     | 3.2.2 PPG Signal Basics                                            | 44         |

| 3.3   | Proposed LSTM Hardware Architecture                                | 46         |

|       | 3.3.1 System Overview                                              | 46         |

|       | 3.3.2 Implementation Details of LSTM Layer                         | 47         |

| 3.4   | Heart Rate Estimation using the Proposed LSTM Architecture         | 53         |

| 3.5   | 5 Conclusion                                                       | 55         |

| Chap  | pter 4. A Data Remanence based Approach to Generate 100% Stable    | Keys from  |

| an Sl | RAM Physical Unclonable Function                                   | 56         |

| 4.1   | 1 Introduction                                                     | 56         |

| 4.2   | 2 Data Remanence Based Stable Key Selection                        | 59         |

| 4     | 4.2.1 Data Remanence Based Approach                                | 59         |

| 4     | 4.2.2 Characterization of Data Remanence Effect                    | 61         |

| 4.3   | 3 SRAM PUF Measurement Results                                     | 68         |

| 4     | 4.3.1 Uniqueness of Key                                            | 69         |

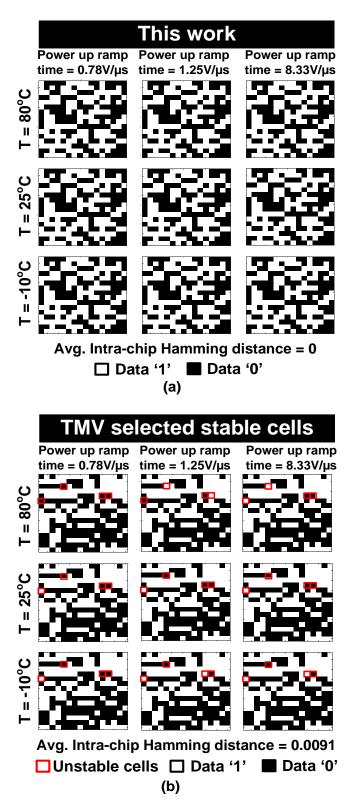

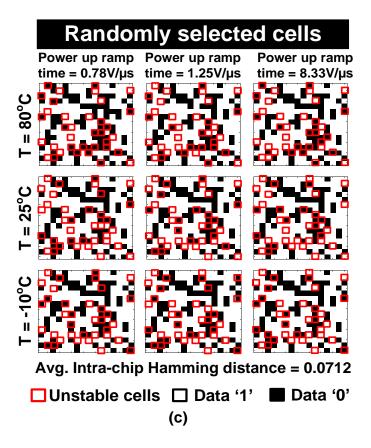

| 4     | 4.3.2 Effect of Power Ramp-up Time and Temperature                 | 70         |

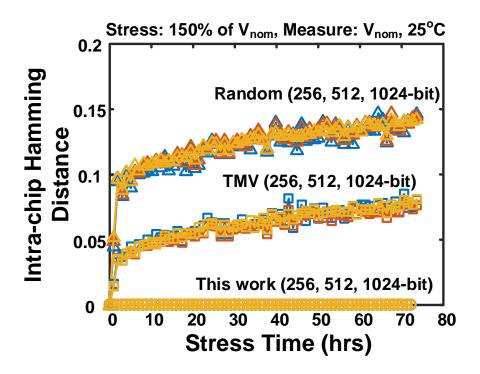

| 4     | 4.3.3 Effect of Device Aging                                       | 73         |

| 4.4   | 4 Conclusion                                                       | 74         |

| Chap  | pter 5. A Passive IC Tamper Sensor Design based on an Exposed Floa | ating Gate |

| Devi  | ce in Standard Logic Processes                                     | 76         |

| 5.1   | 1 Introduction                                                     | 76         |

| 5.2   | 2 5T Eflash Basics                                                 | 77         |

| 5.3   | Sensor Test Structure in 65nm Technology                           | 79         |

| Bibliography                                | 99 |

|---------------------------------------------|----|

| Chapter 6. Summary                          | 96 |

| 5.5 Conclusion                              | 94 |

| 5.4.3 Physical Attack Tests                 |    |

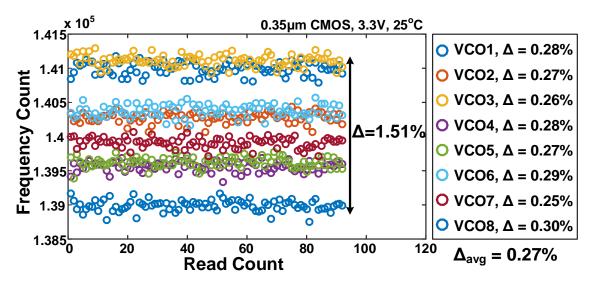

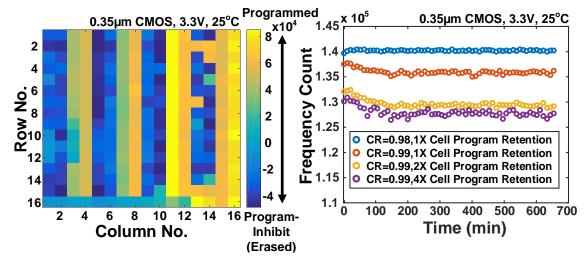

| 5.4.2 Basic Functionality Tests             | 87 |

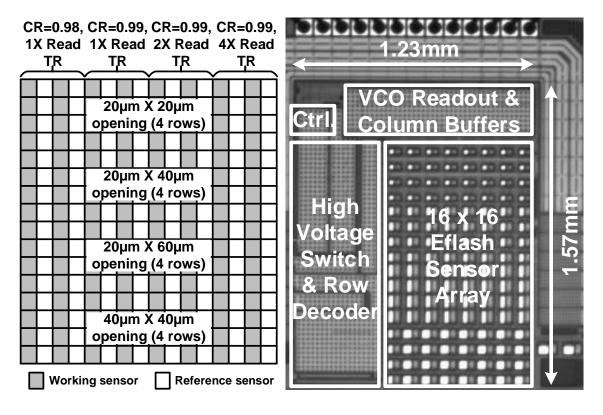

| 5.4.1 Implementation                        | 84 |

| 5.4 16x16 Sensor Array in 0.35μm Technology | 84 |

| 5.3.2 Measurement Results                   | 81 |

| 5.3.1 Basic Concept                         | 79 |

## **List of Tables**

| Table 2.1: Performance Comparison with Prior Arts    37                                  |  |  |  |

|------------------------------------------------------------------------------------------|--|--|--|

| Table 3.1: Comparison of HR Estimation Results    54                                     |  |  |  |

|                                                                                          |  |  |  |

|                                                                                          |  |  |  |

| List of Figures                                                                          |  |  |  |

| Fig. 1.1: Biological neuron model (left) and artificial neuron model (right)             |  |  |  |

| Fig. 2.1: Architecture of multi-layer perceptron (MLP) neural network with one hidden    |  |  |  |

| layer (a) and artificial neuron model (b)                                                |  |  |  |

| Fig. 2.2: Comparison of time-based and digital implementation of neural networks 14      |  |  |  |

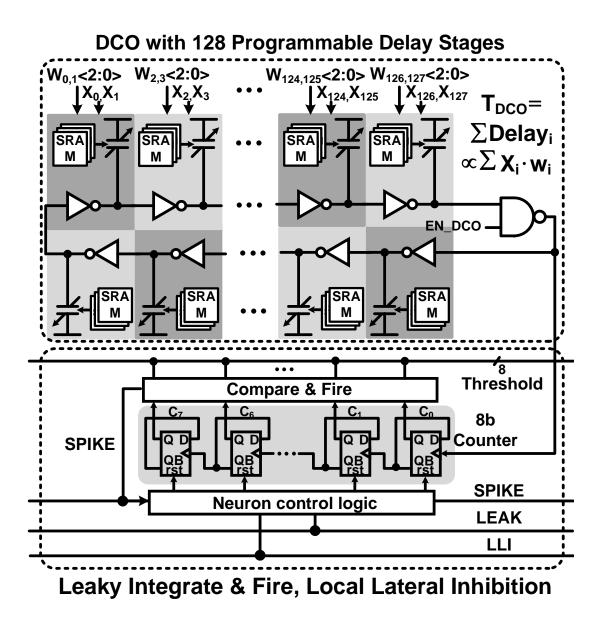

| Fig. 2.3: Circuit diagram of the proposed time-based integrate & fire (I&F) DCO          |  |  |  |

| neuromorphic core                                                                        |  |  |  |

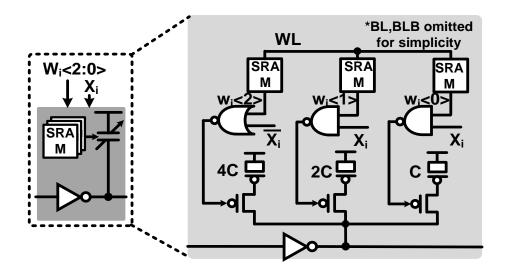

| Fig. 2.4: Detailed implementation of one processing element, which is a programmable     |  |  |  |

| delay stage                                                                              |  |  |  |

| Fig. 2.5: Load capacitor configuration table of all possible states                      |  |  |  |

| Fig. 2.6: Unit cell layout of two processing elements                                    |  |  |  |

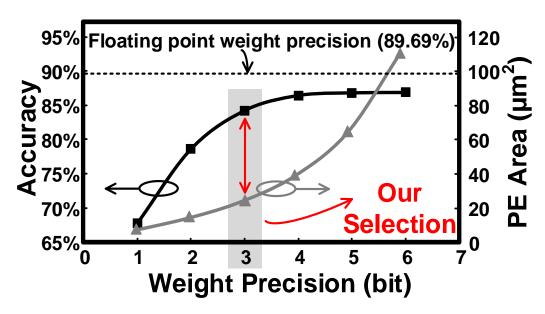

| Fig. 2.7: Neural network accuracy and processing element (PE) area with different weight |  |  |  |

| precision                                                                                |  |  |  |

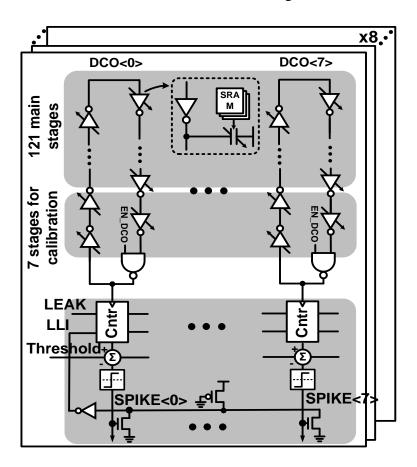

| Fig. 2.8: Architecture of the proposed time-based DCO neuromorphic                       |  |  |  |

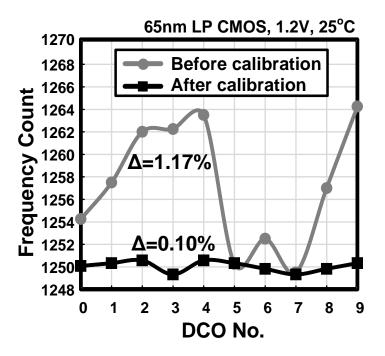

| Fig. 2.9: Measurement results of DCO frequency calibration                               |  |  |  |

| Fig. 2.10: Measurement results of DCO linearity characterization                         |  |  |  |

| Fig. 2.11: Measurement results of injection locking phenomenon in adjacent DCOs 24       |  |  |  |

| Fig. 2.12: Illustration of time-based leaky integrate-and-fire neuron and local lateral      |

|----------------------------------------------------------------------------------------------|

| inhibition operations                                                                        |

| Fig. 2.13: Timing diagrams showing DCO frequency and neuron spike output with (solid         |

| waveform) and without (dashed waveforms) leaky or LLI features. Spiking threshold is 8       |

| in this example                                                                              |

| Fig. 2.14: Effects of leak and LLI features.                                                 |

| Fig. 2.15: Data preprocessing for digit recognition application and summary for the training |

| process                                                                                      |

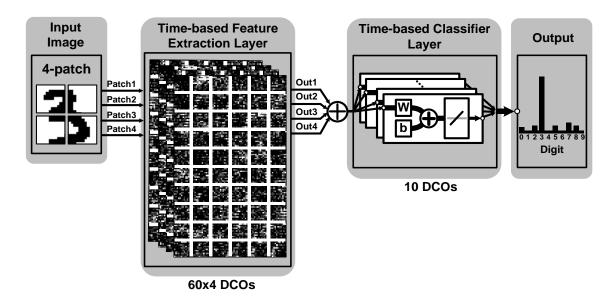

| Fig. 2.16: Single-layer digit recognition application for proof-of-concept                   |

| Fig. 2.17: Multi-layer digit recognition test architecture with 11x11 input images 31        |

| Fig. 2.18: Multi-layer digit recognition test architecture with 4-patched 22x22 input        |

| images. 32                                                                                   |

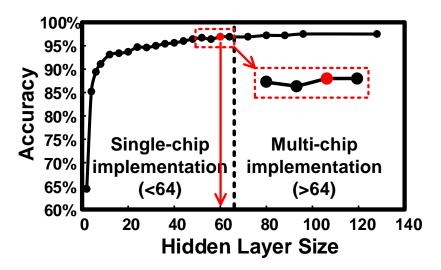

| Fig. 2.19: Hidden layer size selection based on accuracy and circuit implementation          |

| complexity trade-off                                                                         |

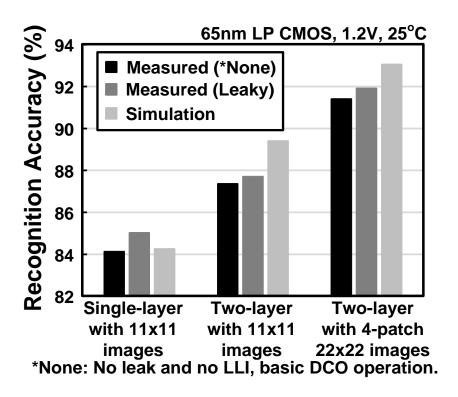

| Fig. 2.20: Measured accuracy results of handwritten digit recognition application 34         |

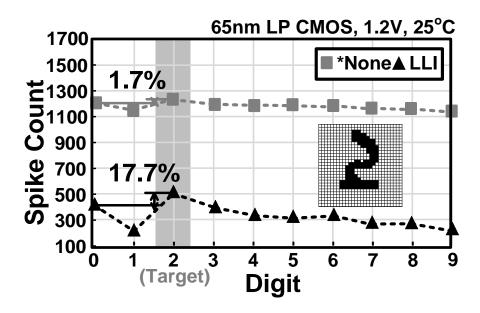

| Fig. 2.21: Measured results of digit recognition application with local lateral inhibition   |

| (LLI) feature enabled                                                                        |

| Fig. 2.22: Measured power consumption and DCO frequency of the test chip under               |

| different supply voltages                                                                    |

| Fig. 2.23: Die photo and performance summary of the test chip                                |

| Fig. 2.24: Implementation of convolutional neural network (CNN) using our proposed           |

| time-based neuromorphic core with some modifications.                                        |

| Fig. 3.1: LSTM unit and equations. 42                                                          |

|------------------------------------------------------------------------------------------------|

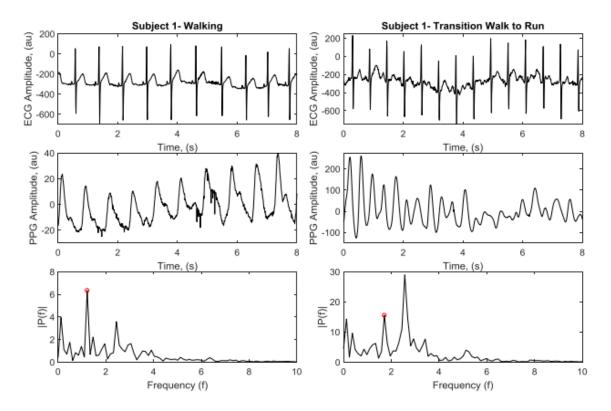

| Fig. 3.2: Raw ECG (top), PPG (middle) signals and spectrums (bottom) while walking             |

| (left) and during transition from walking to running (right) respectively. The highest PPG     |

| spectral peak does not coincide with true HR (encircled) during intense motion 44              |

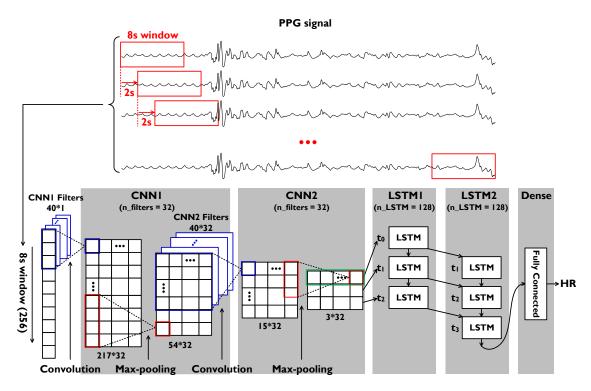

| Fig. 3.3: LSTM based heart rate prediction system [37]                                         |

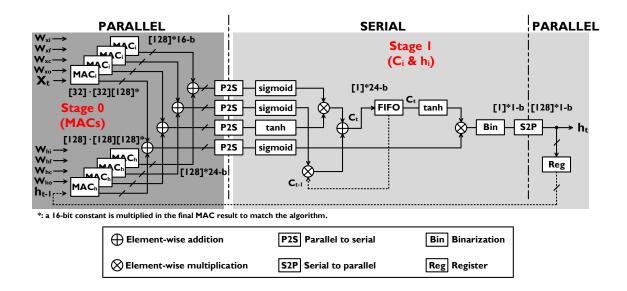

| Fig. 3.4: Proposed binarized first LSTM layer architecture                                     |

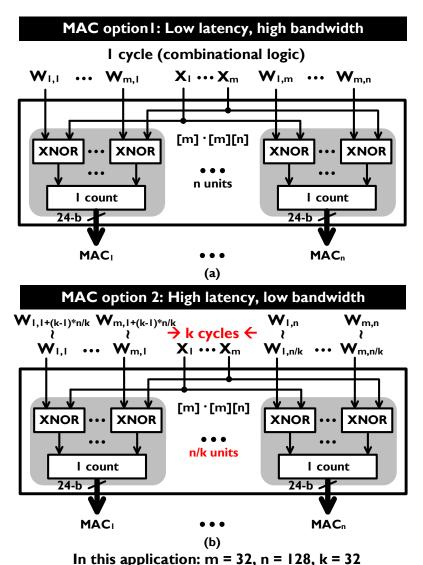

| Fig. 3.5: Detailed MAC implementation, original (a) and optimized (b)                          |

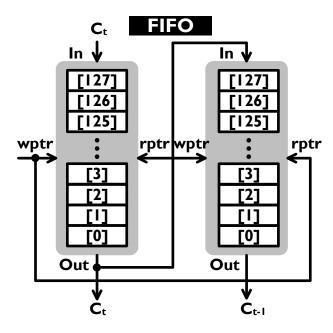

| Fig. 3.6: FIFO implementation for storing the current time step and the previous time step     |

| cell states. 51                                                                                |

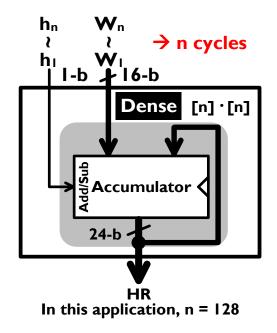

| Fig. 3.7: Dense layer implementation using an accumulator                                      |

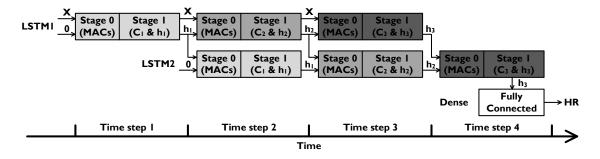

| Fig. 3.8: Timing diagram of the proposed LSTM based heart rate prediction system 52            |

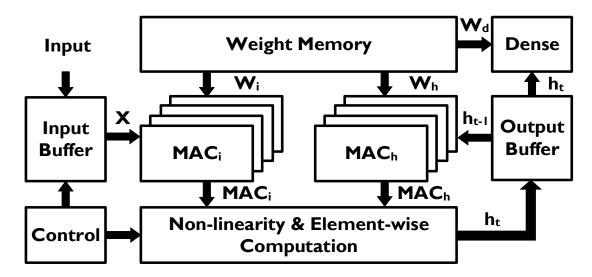

| Fig. 3.9: Block diagram of the proposed LSTM based heart rate prediction system (with          |

| only LSTM layers and the final dense layer)                                                    |

| Fig. 3.10: Customized chest patch supporting two-lead ECG acquisition (left) and               |

| wristband with green LED PPG component. 54                                                     |

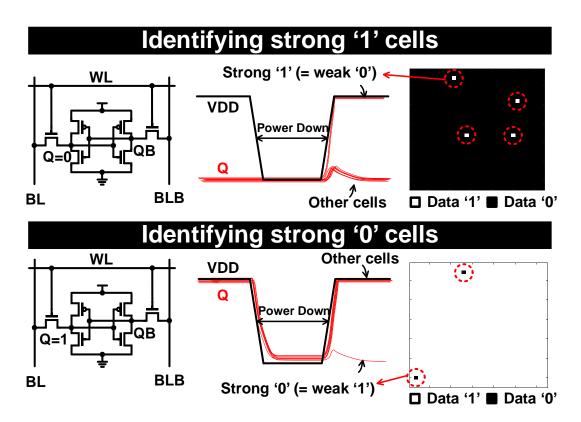

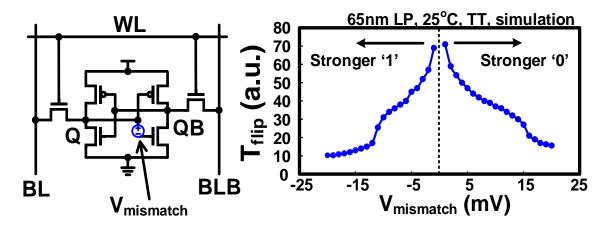

| Fig. 4.1: Proposed data remanence based technique to rapidly select the most stable cells      |

| in a large SRAM array. 59                                                                      |

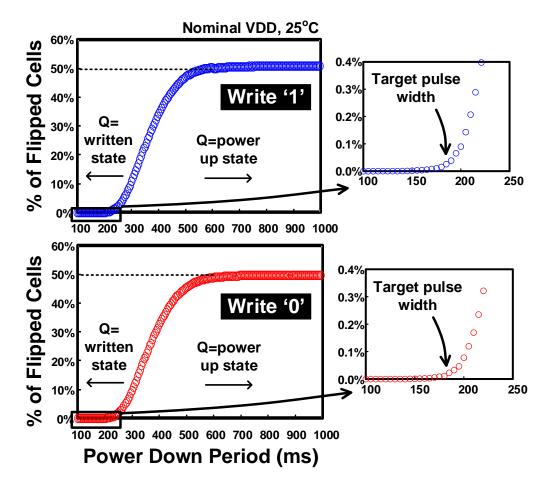

| Fig. 4.2: Required power down period to flip SRAM data with different skew 60                  |

| Fig. 4.3: Percentage of flipped cell versus when writing all '1's (upper) and writing all '0's |

| (lower) to the SRAM cells. 62                                                                  |

| Fig. 4.4: Cell flip maps of randomly selected 1K SRAM cells under different power down         |

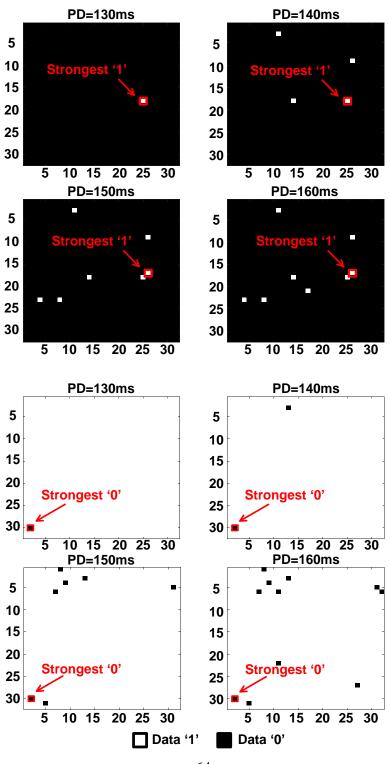

| periods (PD)65                                                                                 |

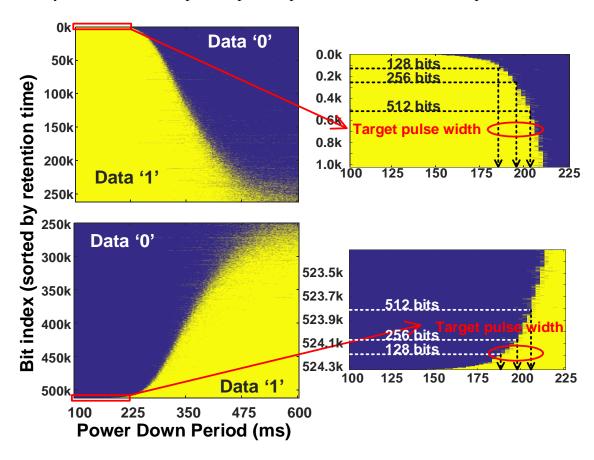

| Fig. 4.5: Measured SRAM data remanence for data 1 (upper) and data 0 (lower). Cells with       |

|------------------------------------------------------------------------------------------------|

| the shortest retention times are highlighted in the zoom-in plots                              |

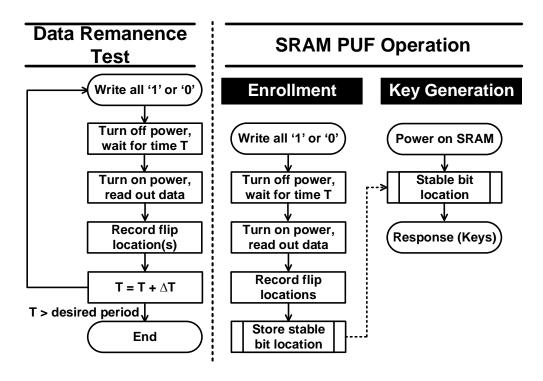

| Fig. 4.6: Flow chart for data remanence test, enrolment test, and key generation test. The     |

| power down time T for enrolment phase can be determined based on a one-time data               |

| remanence test performed at any temperature                                                    |

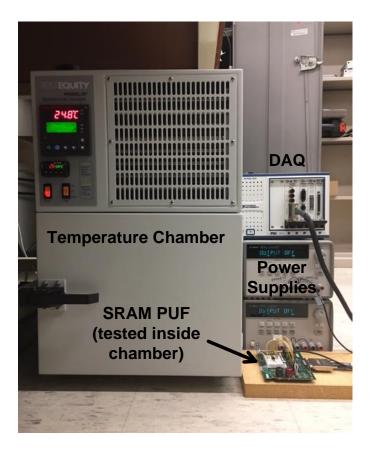

| Fig. 4.7: SRAM PUF measurement set up including a temperature control chamber 68               |

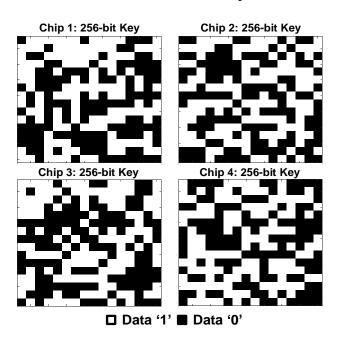

| Fig. 4.8: Keys generated from 4 different SRAM chips. The inter-chip Hamming distance          |

| between the 4 different keys is 0.4935                                                         |

| Fig. 4.9: Measured SER cross-section for inverter, NAND and NOR gates at multiple              |

| supply voltages                                                                                |

| Fig. 4.10: Average intra-chip Hamming distances of different techniques (i.e., proposed,       |

| TMV, and random selection) versus stress time for 256, 512, 1024 selected bits 74              |

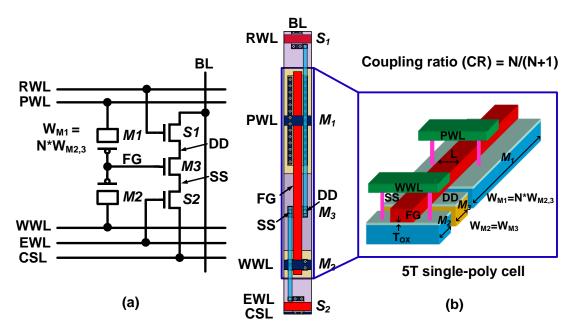

| Fig. 5.1: (Left) 5T eflash cell structure; (middle) layout view; (right)bird's eye view of the |

| cell                                                                                           |

| Fig. 5.2: Three operating modes of the 5T eflash cell                                          |

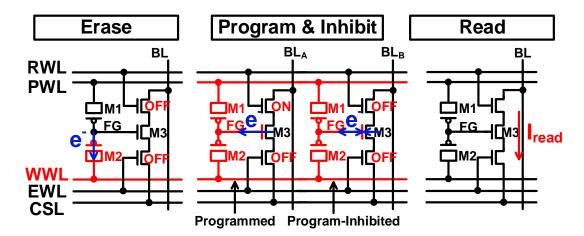

| Fig. 5.3: (Left) Cross section view of eflash with exposed FG; (right) top layout view of      |

| exposed FG and surrounding dummy metals                                                        |

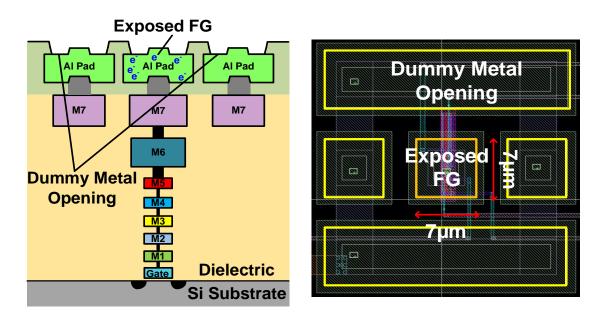

| Fig. 5.4: Temperature (left) and humidity (right) attack test results of 65nm eflash sensor    |

| test structure. 82                                                                             |

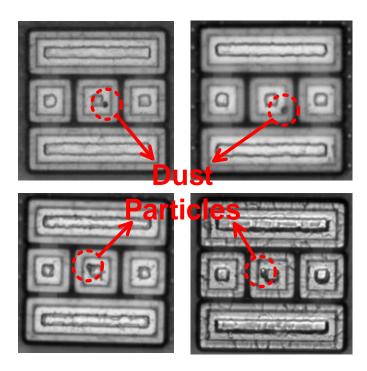

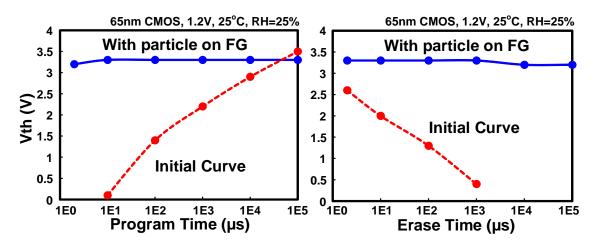

| Fig. 5.5: Microscope images of 4 different chips with particles landed on the FG node of       |

| 65nm eflash sensor test structure.                                                             |

| Fig. 5.6: Program (left) and erase (right) characteristics for eflash sensor with particles  |

|----------------------------------------------------------------------------------------------|

| landed on the FG node. 83                                                                    |

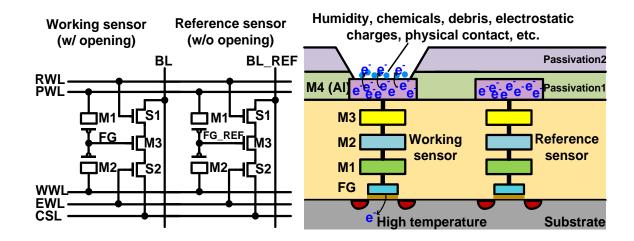

| Fig. 5.7: Differential eflash sensor cell with exposed and buried floating gates implemented |

| in 0.35μm technology                                                                         |

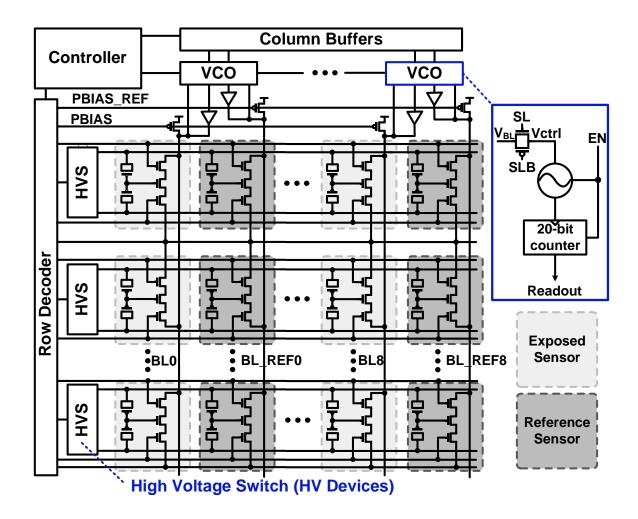

| Fig. 5.8: 16x16 sensor array architecture.                                                   |

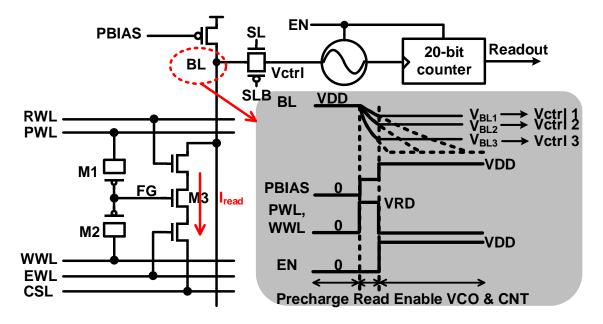

| Fig. 5.9: VCO based sensor readout circuit and timing diagram                                |

| Fig. 5.10: Sensor circuit and opening size configurations (left). Die photo (right) 87       |

| Fig. 5.11: Characterization of VCO frequency variation of the readout circuits               |

| Fig. 5.12: (Left) Erase, program and program-inhibit characteristics and (right) cell        |

| retention results. 88                                                                        |

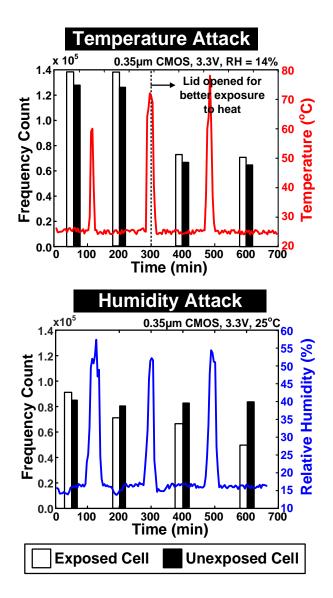

| Fig. 5.13: Temperature (top) and humidity (bottom) attack test results                       |

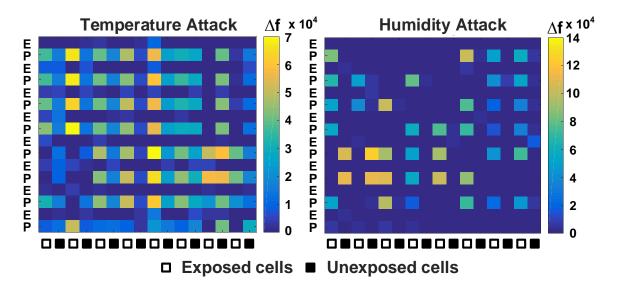

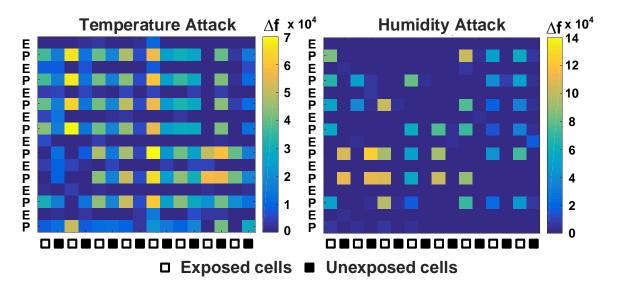

| Fig. 5.14: Frequency change maps of temperature attack (left) and humidity attack (right).   |

| 92                                                                                           |

| Fig. 5.15: Particle/debris test results. Frequency change map (top) and microscope images    |

| of the region that was affected by the particles (bottom)                                    |

# **Chapter 1. Introduction**

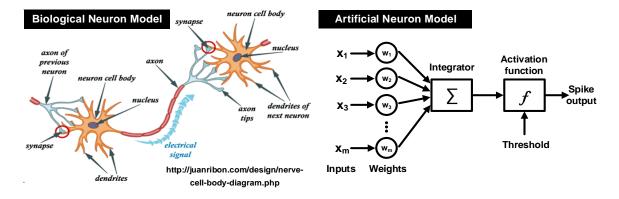

Deep neural networks (DNNs) are now achieving super-human level performance in many real-life applications. For example, human Go masters turned out to be no match for Google's AlphaGo [1], and at the 2016 ImageNet challenge [2], computers could recognize images better than humans, with less than 3.5% [3] error. These breakthroughs are possible because of two primary reasons: (i) greatly improved computing power and (ii) advancements in convolution based DNN algorithms. By performing millions of convolution operations repeatedly, real-life applications such as image classification become possible. Neural networks in general have two operating phases: training (or learning) mode and inference (or prediction) mode. The weights are determined during the training mode, either supervised or unsupervised. The biological and artificial neuron models are shown in Fig. 1.1.

Fig. 1.1: Biological neuron model (left) and artificial neuron model (right).

DNN applications usually involve millions of weights, which may take weeks or

months to obtain even on a super computer. Inference tasks are also compute intensive: for instance, the total number of multiply-and-accumulate operations required for AlexNet [2] is around 832 million with around 60 million weight parameters. Due to their high power consumption and extensive hardware requirements, most inference engines today run on the cloud (i.e. remote datacenter computers). This practice has worked so far; however moving forward, the current cloud computing model is expected to face critical challenges. For example, today's DNN algorithms are designed for cloud computing and therefore are sub-optimal for AI inference tasks performed on ultra-low power mobile devices. Thus, to deploy the AI tasks on mobile edge devices, we need to come up with efficient hardware architectures.

Meanwhile, if edge devices often handle sensitive data (i.e. medical, banking, image, voice) which can raise security concerns. As edge devices penetrate deeper into our daily lives, enhancing the security of these devices has become a critical design consideration. To address security concerns while sharing data between the edge devices and the cloud, we need to make sure that the devices involved in the communication are trustworthy.

A promising approach for ensuring trustworthiness of each device is embedding a "fingerprint" in each chip that is unique and unclonable. Physical unclonable function (PUF) [4] is a circuit that was introduced recently which harnesses inherent manufacturing variations to generate a chip fingerprint. Since manufacturing variations are random, uncontrollable, and unclonable, each device has a unique "fingerprint". One of the most important requirements for PUFs is to generate an output that is stable. A stable PUF circuit ensures that the PUF generates the same key every time, regardless of the temperature,

voltage, number of year in service, etc. Another requirement for PUF is that it should be lightweight, which means it should not take a large area or require too much effort to design. Memory circuit is an attractive option for PUFs as it is readily available in practically all digital systems. The key is generated from the uninitialized power-up state of a memory cell. The power-up state is determined by the unique manufacturing variation.

While on the other hand, ensuring the authenticity of the devices might not be enough sometimes. There is another rising security concern induced by the counterfeit electronics, most of which are recycled and remarked ICs. They are usually recovered from old printed circuits boards (PCBs) and then relabeled and sold as new parts for profits; so they are authentic chips, but they can pose great concerns for customers, since they may function correctly at the beginning, but fails much earlier than expected. Detecting and preventing those counterfeit electronics from entering the market is a critical aspect of ensuring hardware security.

To fulfill the goal of running AI workloads efficiently and securely on edge devices, innovative computing architectures and circuit techniques have been proposed in this dissertation.

#### 1.1 Time based MLP Neural Networks

The greatly improved hardware computing ability enables the deep learning algorithms to achieve great performances in many applications. To further improve the performance and energy efficiency for deep learning applications, a fully scalable light-weight integrate-and-fire neuromorphic core with brain-inspired leak and local lateral inhibition features is proposed in this dissertation. This is a fundamentally different way of

implementing MLP DNNs: time domain computing, which is a much more efficient way of computation than the traditional method. The conventional approaches to implement MLP neural networks are based on bulky digital multipliers and adders to calculate the inner product, which usually has a higher precision but consumes more power and occupies more area. Therefore, the conventional approaches are not suitable for edge devices. In our proposed time based approach, we use a chain of inverters, which are one of the most basic and simplest digital circuits, with programmable delays as processing elements. The inner product function  $y = \sum_i x_i \cdot w_i$  is computed purely in the time domain, where  $x_i$  is the input data,  $w_i$  is the synaptic weight and the individual stage delay is  $x_i \cdot w_i$ . The computation result is reflected as the accumulated delay of the inverter chain, and it can be measured by a simple readout circuit (i.e. frequency counter).

#### 1.2 Binarized LSTM Architecture

Long short-term memory (LSTM) networks have shown to be successful in learning sequences of data. However, due to its high computation complexity and memory requirement, which leads to high power consumption, it is hard to deploy the LSTM networks on embedded devices. And Binarized Neural Networks (BNN) [5-6] become popular recently and have demonstrated to approach state-of-the-art classification accuracy. In this work, a binarized LSTM neural network is proposed and a hardware architecture is designed for accelerating this binarized LSTM network on embedded devices. This proposed network is demonstrated to be area and energy efficient, using an application of heart rate prediction from photoplethysmorgrahy (PPG) signals, and achieves a good heart rate prediction accuracy.

#### 1.3 Chip Fingerprint based on Memory Circuits

PUF is a unique hardware that can generate a "fingerprint" for each chip based on the underlying manufacturing variation. The start-up value of an SRAM cell is unique, random, and unclonable as it is determined by the inherent process mismatch between transistors. These properties make SRAM an attractive PUF circuit for generating unique IDs/keys. The primary challenge for SRAM based key generation, however, is the poor stability when the circuit is subject to random noise, temperature and voltage changes, and device aging. Temporal majority voting (TMV) and bit masking were used in previous works to identify and store the location of unstable or marginally stable SRAM cells. However, TMV requires a long test time and significant hardware resources. In addition, the number of repetitive power-ups required to find the most stable cells is prohibitively high. To overcome the shortcomings of TMV, we propose a novel data remanence based technique to detect SRAM cells with the highest stability for reliable key generation. This approach requires only two remanence tests: writing '1' (or '0') to the entire array and momentarily shutting down the power until a few cells flip. We exploit the fact that the cells that are easily flipped are the most robust cells when written with the opposite data. The proposed method is more effective in finding the most stable cells in a large SRAM array than a TMV scheme with 1,000 power-up tests. Experimental studies show that the 256-bit key generated from a 512 kbit SRAM using the proposed data remanence method is 100% stable under different temperatures, power ramp up times, and device aging.

#### 1.4 Passive Counterfeit IC Sensor

The rising security and reliability concerns induced by the counterfeit electronics necessitate the design to efficiently identify counterfeit electronics from the complex global supply chain nowadays, which is extremely challenging. To help alleviate this challenge, we present an embedded flash (eflash) memory based powerless non-volatile tamper sensor for efficiently detecting counterfeit ICs. By exposing the floating gate (FG) node of a logic-compatible eflash cell to the environment, the proposed sensor can record any subtle physical event that affects the charge stored on the exposed FG. The proposed sensor is demonstrated in both 65nm and 0.35µm standard CMOS technologies, proving that this technique is agnostic to different technology processes. Extensive test results confirm that suspicious activities such as temperature charge injection, humidity rises, and increased dust particle density in the cavity can be recorded powerlessly using the proposed sensor.

## 1.5 Summary of Dissertation Contribution

Several contributions have been made in this dissertation to improve the efficiency of the state-of-the-art neural network hardware architectures and enhance the security for hardware devices.

To summarize the key contributions of this research: 1) a time-based computing architecture has been proposed, which is much more area and energy efficient compared to the traditional digital or analog computing schemes. 2) To deploy the LSTM neural network, which has high computation complexity and memory requirement, on embedded devices, a binarized LSTM architecture is proposed. It greatly simplifies the circuit

complexity and reduces the memory footprint of the LSTM neural network. 3) A data remanence based stable cell selection technique is presented to be able to generate 100% stable responses from a SRAM based PUF circuit. 4) A passive counterfeit electronics detection sensor is demonstrated to be effective in detecting abnormal physical attacks to the chip, thus identifying the counterfeit electronics that have been physically attacked.

The remainder of this dissertation is organized as follows. Chapter 2 presents the design details of the time based MLP neural network in 65nm CMOS technology and the measurement results of the digit recognition application. Chapter 3 demonstrates the basic idea of the proposed binarized LSTM neural network and the design overview of the hardware architecture. The simulation results of the heart rate prediction from PPG signals is also presented. Chapter 4 discusses the proposed data remanence based stable cell selection technique, and the measurement results from commercial SRAM chips. Chapter 5 illustrates the proposed counterfeit IC sensor implemented in both 65nm and 0.35µm technology. The physical attack measurement results are also demonstrated. Finally chapter 6 summarizes this dissertation.

# Chapter 2. Time-based Integrate-and-Fire

# **Neuromorphic Core Design**

#### 2.1 Introduction

Deep learning is a sub-class of machine learning algorithms, which is a braininspired computing algorithm. Deep learning architectures always include multiple layers of non-linear processing units, and the layers used in deep learning mostly refer to the hidden layers of an artificial neural network [7]. Artificial neural network is not a new concept, it has been around for decades [8]. The development of artificial neural network was slow in the past until the computers have gained greater computing power recently. The artificial neural network is based on a simple artificial neuron model, which is a weighted sum of the inputs, followed by an activation function. These artificial neurons are the basic processing units of the neural network and a huge amount of neurons are working in parallel to handle complex algorithms in real applications. There are two stages in deep learning tasks, training (or learning) and inference (or prediction), and the weights is determined by the training process. In this work, we focus on the inference phase. Deep learning applications usually involves millions of weights, which costs a lot of time and energy to access from memory, and large amount of parallel matrix operations, which is also a demanding task for processors. Nowadays, as the processing power of the computers are developing at an extremely fast pace, the implementation of such large scale network becomes possible. The challenge is how to perform the task efficiently so that it can be applied in mobile applications and in real-time embedded systems.

There are several common hardware implementations of artificial neural networks, including using CPU, GPU and custom ASIC. Since CPUs are optimized for latency, they are more suitable for sequential operations, so it's not the best choice to use CPUs in massively parallel neural network applications. GPUs are optimized for memory bandwidth and the thread parallelism in GPUs can hide memory access latency, so GPUs are better suited for deep learning than CPUs. However, one big drawback of using GPUs to implement neural networks is that it always has a high power consumption, making it not suitable for mobile applications. Many researchers believe that major improvements of energy efficiency and performance should come from the specially designed hardware [9]. In [9], the Tensor Processing Unit (TPU), which is a custom ASIC developed by Google, achieved a peak throughput of 92 TeraOps/second (TOPS), which is on average about 15X-30X faster than its contemporary GPU or CPU.

Many approaches have been presented to implement the neural processing elements (PE) in custom ASIC hardware, aiming at higher power and area efficiency. Early approaches relied on analog circuits to mimic synapse and neuron functions [10]. However, using analog circuits to implement brain-inspired neural networks suffers from noise and process variation issues, so homogeneity and precision cannot be guaranteed for large scale networks. Scaling of CMOS technology also poses a challenge for analog circuits. Digital implementation of neural processing elements has been more popular recently. Compared

to analog implementation, they are more robust against noise and process variation, and can benefit from technology scaling, enabling massively parallel neuromorphic ASIC systems, such as IBM's Turenorth [11]. However for digital implementation of neural networks, it usually requires a large amount of adders and multipliers to implement the MAC operations, which is area and power consuming.

There are three types of popular neural networks: Multi-Layer Perceptron (MLP), Convolutional Neural Network (CNN), and Recurrent Neural Network (RNN). According to [9], they represent 95% of the inference workload in Google's datacenters. While there are many works focusing on accelerating CNNs [12]-[18], they represent 5% of Google's datacenter workload [9]. We have dedicated to improve the efficiency in Multi-Layer Perceptron (MLP) neural network in this work.

In this work, we present an implementation of fully connected MLP neural network based on integrate-and-fire neuron model in time domain, which improves the area and power efficiency compared to digital implementation. Instead of using adders and multipliers to implement the multiply and accumulate operations, we do the calculation in time domain using digital circuits, which is more area and power efficient. And data moving can be more energy consuming than computation, as is reported in [19]-[20], so to reduce the memory access power and latency, each PE in our work has its exclusive weights, which eliminates the energy consumption of moving data from memory. This further improves the energy efficiency.

### 2.2 MLP Neural Network Background

In this section, we first briefly introduce the architecture of MLP neural network, then we discuss the integrate-and-fire neuron model we used in this work.

#### 2.2.1 Multi-Layer Perceptron (MLP) Neural Network

Multi-layer perceptron (MLP) neural network is a popular feedforward neural network with one or more hidden layers between input and output layers [21], which is shown in Fig. 2.1 (a). Each node in this MLP represents an artificial neuron model that uses a nonlinear activation function, shown in Fig. 2.1 (b). A supervised learning technique called backpropagation is used to train a MLP neural network. Two common activation functions for MLP are hyperbolic tangent  $y(u_i) = \tanh(u_i)$  and the logistic function  $y(u_i) =$  $(1 + e^{-u_i})^{-1}$ , where  $y(u_i)$  is the output of the ith node (neuron), and  $u_i$  is the weighted sum of the inputs of the ith node (neuron). They are both sigmoids, so the shape of the two functions are similar, the difference is that the former function is centered around 0, ranging from -1 to 1, while the latter one ranges from 0 to 1. Most of the time, tanh can be more quickly converged than logistic function, and performs better accuracy [22]. And it is a good idea to make the input, output and hidden layers have mean values of 0 and standard deviation of 1, since in general if the average input shifts away from zero, it will bias the weight updates in a particular direction, making the learning slower [23]. However, due to the fact that we need to apply the MLP neural network in hardware and there is no negative inputs in our design, so we used the logistic function with range from 0 to 1 as the activation function in this work

Fig. 2.1: Architecture of multi-layer perceptron (MLP) neural network with one hidden layer (a) and artificial neuron model (b).

#### 2.2.2 Integrate-and-fire Neuron Model

Integrate-and-fire neuron model is one of the earliest models of a neuron, which was first investigated in 1907 by Louis Lapicque [24]. A neuron can be modeled by

$$I(t) = C_m \frac{dV_m(t)}{dt} \tag{2.1}$$

which is just like a capacitor. However, the neuron cell membrane is not a perfect insulator, the charges will leak away through the membrane over time. So to be more accurate, we should add a leaky term in the model [25],

$$I(t) = C\frac{dV_m(t)}{dt} + \frac{V_m(t)}{R}$$

(2.2)

which is equivalent to a capacitor C in parallel with a resistor R. This model is also referred to as leaky integrate-and-fire (LIF) neuron model. In this work, we implemented the integrate-and-fire neuron model with leaky feature as a selective option.

## 2.3 Time-based Integrate-and-Fire DCO Neuromorphic

In this section, we first introduce the advantages of using time-based circuits to implement neural networks over digital implementation. Then we present the detailed implementation and characterization of our proposed time-based neuromorphic core [26].

#### 2.3.1 Advantages of Time-based Implementation of Neural Network

Time-based circuits have several known advantages, since time is also an analog signal, so it has higher area and energy efficiency than digital implementation in low-precision computation applications [27], the time-based circuits is implemented using the same standard digital logic gates as digital circuits, so compared to voltage mode or current mode analog computing, it has excellent compatibility with advanced CMOS technologies and can tolerate low operating voltages. Besides, due to its digital nature, time-based circuits is compatible with EDA tools, thus can allow for large-scale integrated design [28].

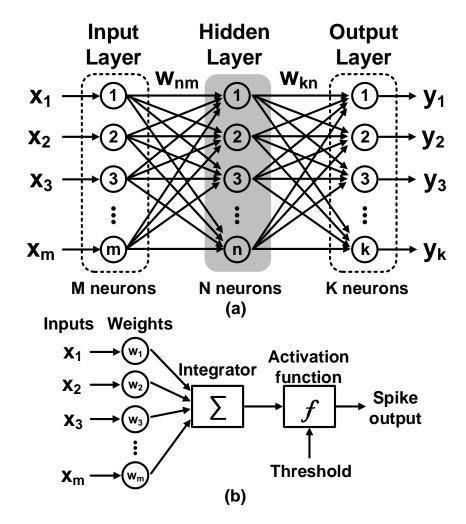

Fig. 2.2: Comparison of time-based and digital implementation of neural networks.

Fig. 2.2 shows the comparison of time-based and digital implementation of neural networks. In this work, we use the programmable delay circuits as the processing elements, calculating the multiplication results, and the integration is implemented by accumulating the delay in time domain. Compared to traditional digital implementation which requires lots of adders and multipliers, time-based implementation is more area and power efficient. We can achieve 16bits/32bits fixed point or even floating point computation using digital implementation, while time-based circuits usually has a lower resolution, which is a main drawback. However, for deep learning applications, the resolution is not so critical. Recently, the binarized neural network (BNN) [5-6] has gained popularity and it has approached state-of-the-art classification accuracy. BNNs are neural networks with binary (1-bit) weights and activations. This proves that neural networks with lower resolution can also work well and it's more favorable for hardware implementation. There have been

several successful hardware implementation of BNNs in time domain which show good energy and hardware efficiency [29-31].

#### 2.3.2 Implementation of Time-based DCO Neuromorphic Core

Fig. 2.3: Circuit diagram of the proposed time-based integrate & fire (I&F) DCO neuromorphic core.

Fig. 2.3 shows the proposed time-based integrate-and-fire neuromorphic core [26]. The main innovation is that it computes  $y = \sum_i x_i \cdot w_i$  purely in time domain, where  $x_i$  is the input data and  $w_i$  is the synaptic weight. The upper part is a digitally controlled oscillator (DCO) with 128 programmable delay stages and one enable stage, which can compute up to 128 multiply and accumulate (MAC) operations at a time, and each programmable delay stage is the processing element (PE). The lower part is the readout circuits, implementing the leaky integrate and fire and local lateral inhibition features. Each PE computes one  $x_i \cdot w_i$ , and the computation result is converted to the delay of that stage. Delay of all stages are accumulated naturally in the DCO loop, which is the integration of the multiplication results. The overall delay in the DCO loop is converted to an oscillation frequency and fed to an 8-bit counter in the readout circuits. The counter increments every DCO cycle, and when the count value reaches a target count, which corresponds to the spiking threshold, a spike is generated and the counter is self-reset. The compare & fire block checks the current counter count and if the count matches the threshold, a pulse is generated as the spike. The spike is fed into the neuron control logic and the reset signal is generated to clear the counter. The output of each DCO unit is the number of spikes generated within a certain sampling period. The measurement precision of the time based DCO neuromorphic core can be easily programmed by changing the spiking threshold. For instance, with a higher spiking threshold, a smaller DCO frequency difference can be detected at the cost of longer delay, thus higher energy consumption.

Fig. 2.4: Detailed implementation of one processing element, which is a programmable delay stage.

| Xi | Wi  | # Cap. | State   | Xi | Wi  | # Cap. | State      |

|----|-----|--------|---------|----|-----|--------|------------|

| 0  | 001 | 4C     | Default | 1  | 001 | 1C     |            |

| 0  | 010 | 4C     |         | 1  | 010 | 2C     | Excitatory |

| 0  | 011 | 4C     |         | 1  | 011 | 3C     |            |

| 0  | 100 | 4C     |         | 1  | 100 | 4C     | Default    |

| 0  | 101 | 4C     |         | 1  | 101 | 5C     |            |

| 0  | 110 | 4C     |         | 1  | 110 | 6C     | Inhibitory |

| 0  | 111 | 4C     |         | 1  | 111 | 7C     |            |

Fig. 2.5: Load capacitor configuration table of all possible states.

Fig. 4 shows the detailed implementation of one processing element (PE), which is a programmable delay stage of the DCO core. Our design has a weight resolution of 3 bits, so each stage accepts 1-bit pixel  $x_i$  and 3-bit weight  $w_i$  as inputs. Each stage of the DCO core is composed of an inverter and binary-weighted MOSFET capacitors controlled by

the input pixel and the 3-bit weight. Input pixels determine whether a stage is activated or not, and weights determine how many capacitors are turned on as load in that stage. Since there are both excitatory and inhibitory synapses, the delay should be able to change in both directions. So weight 100<sub>2</sub> is defined as weight zero, it's also the default weight when the delay stage is disabled. If weights are smaller than 100<sub>2</sub> (i.e. 001~011<sub>2</sub>), fewer load capacitors are turned on, reducing the delay of that stage. These weights represent excitatory synapses. Contrarily, weights larger than 100<sub>2</sub> (i.e. 101~111<sub>2</sub>) represent inhibitory synapse. Fig. 5 shows all the possible load capacitor configurations and the corresponding states. To save the power consumption of data movement during computation, each PE has its exclusive memory for use. In each programmable delay stage, there are three SRAM cells storing the 3-bit weight for each PE. This architecture is called completely parallel or fully spatially unrolled architecture [29-30].

Fig. 2.6: Unit cell layout of two processing elements.

The unit cell layout that is composed of two PEs is shown in Fig. 2.6. The two PEs are made as symmetric as possible to reduce the process variation induced delay mismatch between different stages. Each unit cell has a size of 8.1µm by 5.9µm, so every PE takes an area of approximately 24µm² (in 65nm process), which is very compact compared to the bulky adders and multipliers in digital implementation. So this time-based implementation of neural networks can be more area and power efficient than traditional digital implementation. And because of the fully spatially unrolled architecture, after loading the weights in the SRAM cells initially, the weights don't change during the entire inference application period, so there's no power consumption for moving the data from memory to PEs. This can further increase the energy efficiency of this core.

Fig. 2.7: Neural network accuracy and processing element (PE) area with different weight precision.

The reason why we use the 3-bit weight is based on the accuracy and circuit area and power tradeoff, which is shown in Fig. 2.7. We train a single layer perceptron neural

number weight we got from training, and the black curve shows the accuracy when we round the weight to different number of bit precisions. The grey curve shows the corresponding area estimation under different weight precisions, except for the 3-bit case. The area and power consumption increases exponentially with weight precisions, however the accuracy doesn't increase that much. According to our study, 3-bit weight has the best accuracy and area tradeoff, so we decide to use 3-bit weights in this work.

Fig. 2.8: Architecture of the proposed time-based DCO neuromorphic.

Fig 2.8 shows the overall architecture of the proposed time-based neuromorphic core with 64 DCO circuits array in parallel. The DCO array is divided into 8 groups, each

consisting of 8 DCOs, to realize the local lateral inhibition feature (discussed in next section). Each DCO can be enabled or disabled independently, so any number of DCOs can be activated simultaneously according to different applications, demonstrating the scalability of this proposed neural network. The proposed neuromorphic core compares the raw spike count of each DCO to determine which neuron output is dominant. If we define the multiply and accumulate computation results as the score of each neuron, so the higher the score, the more likely it's the correct prediction. In our proposed neuromorphic core, computation results are represented by the overall delay in the DCO loop, and the DCOs with higher score has smaller delay (higher frequency), thus can generate more spikes. The dominant DCO with the most spikes is the final prediction result. However, due to process variation, different DCOs have different oscillation frequencies for identical inputs. It is critical to have a uniform DCO frequency to start with. Unlike process variation, voltage and temperature variation affect all DCOs in the same direction, so although the absolute spike counts may vary, the dominant DCO will always stay the same under V and T variations. To compensate for process variation, in our design, 7 of the 128 DCO stages are reserved for frequency calibration while the remaining 121 stages are used for the normal neural network function. For frequency calibration, all DCOs are configured to have the same pixel inputs and weights, and the spike counts are measured for a fixed period of time. By tuning the weights of the 7 frequency calibration stages, we can get a uniform baseline DCO frequency. And this is a one-time calibration, since after this calibration, further voltage and temperature variations affect all the DCO frequencies in the same way, the relative order of different DCOs won't change, so no further calibration

is required. Fig. 2.9 shows the measurement results of the frequency calibration of 10 DCOs. After calibration, the frequency variation reduces from 1.17% to 0.10%. Although due to jitters and noises, the DCO frequency will vary from time to time, as long as the frequency variation is smaller than the frequency mismatch between different DCOs, the final prediction result will not be affected. And the frequency mismatches between different DCOs are determined by the weights obtained in the training process, which can be tuned and is measured to be much larger than 0.10%.

Fig. 2.9: Measurement results of DCO frequency calibration.

#### 2.3.3 Characterization of DCO Neuromorphic Core

Before applying this time-based neuromorphic core in real applications, we need to do some further characterization to ensure the accuracy of the computation results. Linearity of the DCO frequency is one important factor that affects the computation accuracy and it

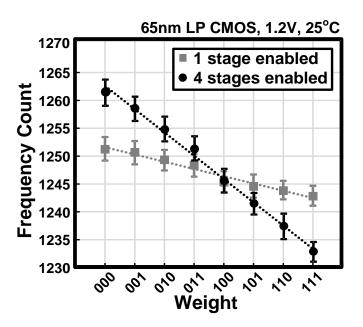

determines whether the hardware results match the software simulation results. Fig. 2.10 shows the measurement results of DCO linearity characterization. It plots the mean and 3 $\sigma$  error bars of the frequency count when different number of stages are activated. The gray curve shows the case when only 1 out of 128 DCO delay stages is enabled, the rest stages are all turned off. In this case, when the weight is swept from 000 to 111, only 1 unit of weight is changed every time, so it corresponds to the minimum tunable frequency this DCO can achieve. The measurement results confirm a good linearity.

Fig. 2.10: Measurement results of DCO linearity characterization.

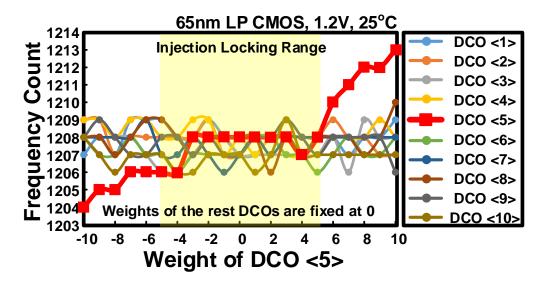

Fig. 2.11: Measurement results of injection locking phenomenon in adjacent DCOs.

Due to the fact that in this work an array of 64 oscillators can oscillate at the same time with similar oscillation frequencies, and they are in a close vicinity to each other, so injection locking might happen. To measure whether there's injection locking in this proposed architecture, we select 10 adjacent DCOs, turn on all the stages and vary the weight of the middle DCO, weights of the rest DCOs are fixed at 0. The measurement results are shown in Fig. 2.11. As the weight of the middle DCO was swept from -10 to 10, we observed that in the range of -5 to 5, when the weight of the middle DCO changed, its oscillation frequency changed little and was similar to its adjacent DCOs, so we believed that when the difference of the computation results between adjacent DCOs were smaller than 5, there was injection locking in this architecture. This injection locking phenomenon is not necessarily a bad thing in our system. Since the measurement results of classification applications show that the output difference between the dominant DCO and the rest DCOs is larger than 5, so the dominant DCO will never be affected by injection locking. And it's

a favorable phenomenon that the rest DCOs are locked at a similar frequency, which makes it easier to select the dominant DCO.

# 2.4 Leak and Local Lateral Inhibition

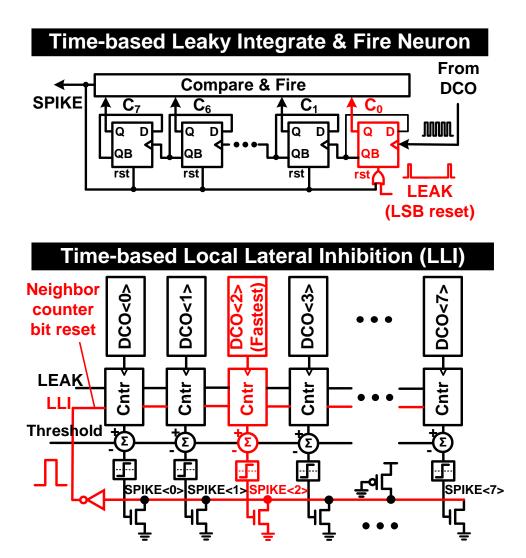

Fig. 2.12: Illustration of time-based leaky integrate-and-fire neuron and local lateral inhibition operations.

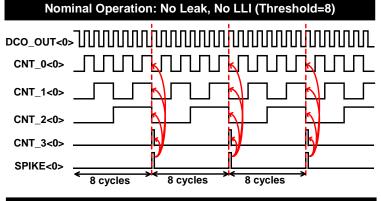

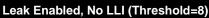

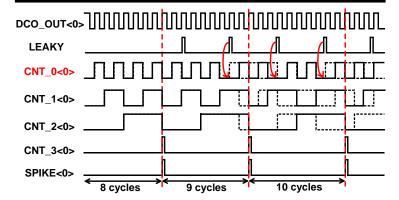

We also implemented brain-inspired leak and local lateral inhibition (LLI) features in this work to improve the performance. These two features can enhance the contrast between different neuron outputs. Fig. 2.12 illustrates the circuit implementation of leaky integrate-and-fire neuron and LLI features. We can decide separately whether to enable the leaky and LLI features or not. When the leaky feature is enabled, the LSB of the 8-bit counter in the readout circuit is not only reset by the generated spikes, but also periodically reset by a low frequency LEAK signal. This has the effect of gradually decrease the stored count value, mimicking a leaky neuron whose charge slowly leaks away through the cell membrane. The timing diagram illustrating the leaky feature is shown in Fig. 2.13 (middle), for comparison, the nominal operation without leaky or LLI features is shown in Fig. 2.13 (top). The threshold is 8 in this example. After enabling the leaky feature, the number of DCO cycles required to generate a spike gradually increases from 8 to 10. Note that the period of the LEAK signal need not be very stable and accurate, but should be several times longer than that of the DCO, otherwise the count value might increase. We also found that the pulse width of this LEAK signal can also affect the extent to which the count value is decreased. So we used an on-chip free-running VCO and pulse generator to tune the frequency and pulse width of this LEAK signal.

#### LLI Enabled, No Leak (Threshold=8, LLI reset CNT\_1 & CNT\_2)

Fig. 2.13: Timing diagrams showing DCO frequency and neuron spike output with (solid waveform) and without (dashed waveforms) leaky or LLI features. Spiking threshold is 8 in this example.

Lateral inhibition is a phenomenon in which the active neuron strives to suppress the activities of its neighbors. In our design, every 8 DCOs are grouped together to realize LLI, so each DCO has 7 neighbors in its group. We can decide the inhibition amount, which is the count decrease in the counter, by setting which bits of the counter are reset. When LLI is enabled, once a DCO in the group generates a spike, there is a pulse generated as LLI signal, which resets the bits we previously defined in the neighboring counters. The fastest DCO in the group resets the other DCOs more often than it is reset by the other DCOs, enhancing the contrast between different DCO outputs. The timing diagram illustrating the LLI feature is shown in Fig. 2.13 (bottom). There are two DCOs in this example and DCO<0> is the dominant one. If there's no LLI, they need 8 cycles to generate a spike. After enabling LLI feature, the faster DCO (DCO<0>) resets the slower DCO (DCO<1> three times, so it takes the slower DCO 17 cycles to generate its first spike. So the output contrast between these two DCOs increases further after enabling the LLI feature.

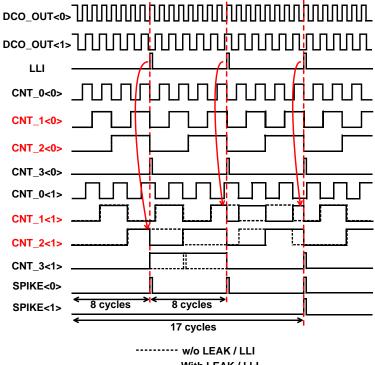

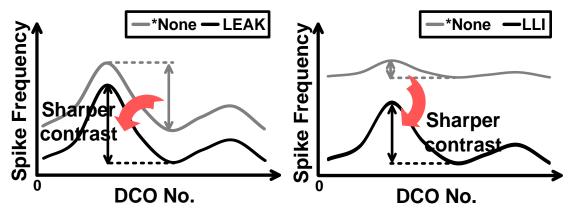

The effects of leak and LLI features are illustrated in Fig. 2.14. The main benefit of the leak operation is that it can increase the relative difference between DCO spike outputs, since the absolute difference between different DCOs stays relatively the same, but the overall level of the DCO frequencies decreases, so the relative difference increases, making the prediction more accurate. And for LLI feature, the faster DCO becomes faster and slower DCO becomes slower. The contrast between different DCO outputs is sharper, so

it ensures that the prediction results are more reliable. But there is usually a greater frequency drop than leaky feature, so it makes the operation slower.

\*None: No leak and no LLI, basic DCO operation.

Fig. 2.14: Effects of leak and LLI features.

# 2.5 Digit Recognition Application and Measurement Results

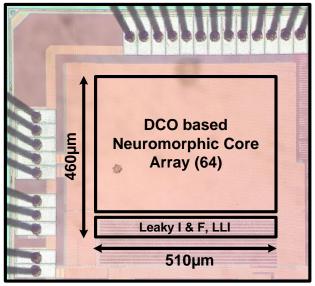

A test chip was fabricated in a 1.2V, 65nm LP CMOS to demonstrate the time-based neuromorphic core. Due to chip size limitations, we opted for a single neuromorphic core implementation with 64 DCO neurons. However, as the chip is fully scalable, we can either tile more DCOs in one neuromorphic core or tile several neuromorphic cores and operate them in parallel to handle complex deep learning algorithms.

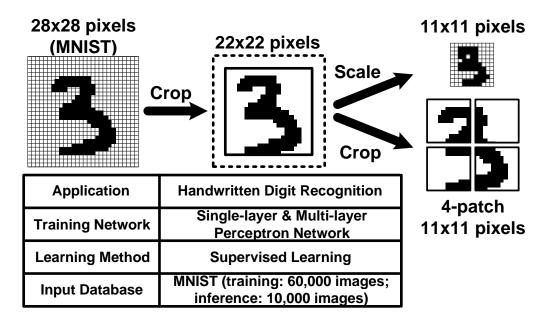

We tested the chip with handwritten digit recognition application to showcase the versatility of the proposed core. Handwritten digit images were obtained from the MNIST database [32]. The original image size from MNIST was 28x28 pixels, while in our test chip, each DCO can accept at most 121 effective input pixels, so we did some preprocessing of the image data, which is shown in Fig. 2. 15. We first removed 3 pixels on each side without affecting the images, as they were almost all blank pixels, containing

little information. Then we had two options, one is to directly scale the image from 22x22 pixels to 11x11 pixels, so that a single DCO circuit can process one complete image. Obviously, this degrades the image and deteriorates the recognition accuracy, so this is just used for proof-of-concept test architectures. In most of the applications, the pixel count is far more than 121, so to demonstrate that our core is able to handle larger images, we also crop the 22x22 images to 4-patch images with 11x11 pixels in each patch. In this case, four DCO circuits can work concurrently to process one image, which improved the throughput and recognition accuracy. The training network we used was the multi-layer perceptron neural network, and all weights were trained off-chip using supervised learning and downloaded to the chip. In the training process, we used all 60,000 images in the MNIST database and used 10,000 images for inference. The summary of the training process is shown in Fig. 2.15.

Fig. 2.15: Data preprocessing for digit recognition application and summary for the training process.

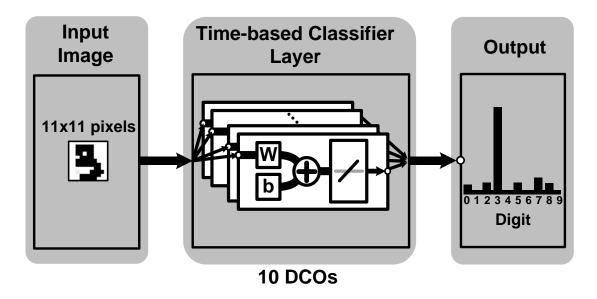

Fig. 2.16: Single-layer digit recognition application for proof-of-concept.

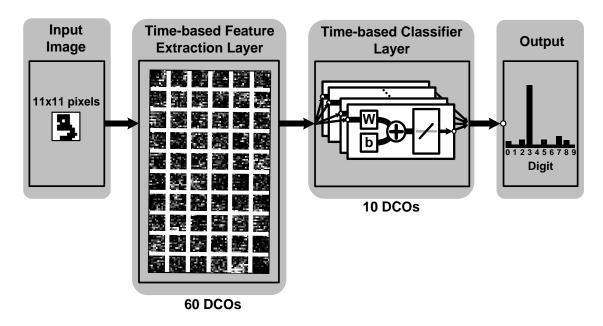

Fig. 2.17: Multi-layer digit recognition test architecture with 11x11 input images.

Fig. 2.18: Multi-layer digit recognition test architecture with 4-patched 22x22 input images.

First of all, for proof-of-concept, we tested the chip using a simple single-layer architecture with no hidden layers. It's a fully connected network with one input layer and one output layer, which is shown in Fig. 2.16. The input images are scaled version with 11x11 pixels. The output layer is the time-based classifier layer. There are 10 DCO neurons in the classifier layer, each neuron is trained to recognize one digit and the spike outputs from the 10 neurons are recorded. The neuron with the most spikes are the recognition output. Next, we ran the chip on a MLP architecture with one hidden layer, which is shown as time-based feature extraction layer in Fig. 2.17. The input images in this case are still 11x11 pixels. The feature extraction layer extracts 60 features from each input image. The output classifier layer is the same as before. Finally, we did our formal test of using 4-patched images with 22x22 pixels in a MLP network with one hidden layer, which is shown in Fig. 2.18. Each patch has 11x11 pixels and 4 DCOs handle the same image in parallel.

60 features are extracted from each patch by the feature extraction layer. Then we did the off-chip data processing to sum and encode the results from the feature extraction layers and feed these results to the output classifier layer to get the final recognition results. The reason why we chose a hidden layer of size 60 is based on the tradeoff between the simulated accuracy result and the circuit implementation complexity, as is shown in Fig. 19. The accuracy generally increases with the size of the hidden layer, but the increasing speed is gradually decreasing because of overfitting. And as our core has 64 DCO circuits, so if the hidden layer size is larger than 64, then it requires a multi-chip implementation, which greatly increase the complexity. In this work, we decide to use a simpler chip implementation and achieve an accuracy as high as possible. As is shown in the zoomedin area in Fig. 2.19, the accuracy of using a hidden layer size of 60 reaches the highest and if we increase the size to 64, the accuracy doesn't improve further due to overfitting, so we decide to use the hidden layer size of 60.

Fig. 2.19: Hidden layer size selection based on accuracy and circuit implementation complexity trade-off.

Fig. 2.20: Measured accuracy results of handwritten digit recognition application.

Fig. 2.21: Measured results of digit recognition application with local lateral inhibition (LLI) feature enabled.

The measured accuracy results from the above three architectures are shown in Fig. 2.20. The two-layer architecture with 4-patch inputs (22x22 pixels) achieves the highest recognition accuracy of 91.4%. With the leak feature enabled, the accuracy increases modestly to 91.9%. The measured accuracy from hardware is comparable to software simulation results, which is due to the DCO circuits have a good linearity. As seen from the measurement results in Fig. 2.20, the recognition accuracy of a single-layer architecture increases from 84.1% to 85.0% after enabling the leak feature, while the accuracy doesn't improve as much in the two-layer architecture. This is because in the two-layer architecture, we have more weights available to improve the contrast between different neuron outputs, which means the output contrast for two layer architecture has already been pretty large. This make the leak feature less effective. Fig. 2.21 shows the measurement results of digit recognition application with LLI enabled. This figure shows the outputs from 10 DCOs in the classifier layer. For an image of digit "2", before enabling the LLI feature, the spike count differences between different DCO neurons are very small, the minimum difference is 1.7%, which is very hard to get the correct recognition result. After enabling the LLI feature, this difference increases to 17.7%. So with a larger difference, we can make the prediction more confidently, and this prediction result is more reliable than without LLI case. The reliability of the prediction results is very important in some applications, for example, in medical field, if the doctors want to diagnose some diseases from some examination results with the help of deep learning algorithms, the reliability of the prediction result is of critical importance to the patients. We always want the doctor to be as confident as possible of the diagnosis result. Fig. 2.22 shows the measured power

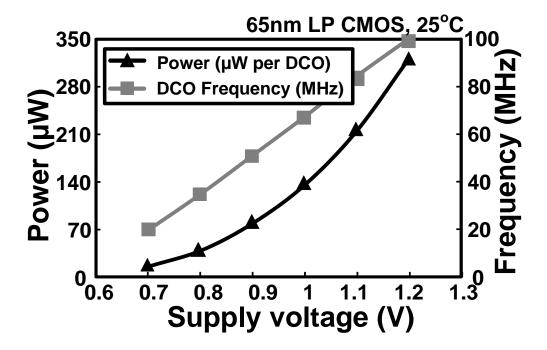

consumption and DCO frequency under different supply voltages. The test chip can work under a wide range of supply from 1.2V to 0.7V. The DCO circuit oscillates at 99MHz consuming 320.4 $\mu$ W under a nominal 1.2V supply voltage. At 0.7V supply, the DCO oscillates at 20MHz with 17.5 $\mu$ W power consumption.

Fig. 2.22: Measured power consumption and DCO frequency of the test chip under different supply voltages.

Table 2.1 shows the performance comparison with recent neuromorphic chip designs [30, 31, 33, 34]. It's worth noting that an apples-to-apples comparison between our time-based scheme and traditional ASIC chips can be tricky. Here, we chose to present metrics (e.g.  $\mu$ W/DCO, spikes/s/W) specific and relevant to our design, and we also provide the comparison of our work with prior arts in different metrics. The proposed DCO neuron can generate  $3.09 \times 10^{11}/16 = 1.93 \times 10^{10}$  spikes per second per watt, for a spiking threshold value N of 16. Compared with the previous time-based neural network [29-30],

our core has a slightly lower power efficiency, but the hardware efficiency is 4X better than the previous work. If we define one multiply and accumulate (MAC) as one operation (OP), our core achieves 37.4 TOPS/W efficiency, which is better than previous works [31, 33]. Note that different works have different weight resolutions, so it might not be the fairest comparison. All the performance numbers listed in the above table for this work is based on the spiking threshold value of 16. The performance can be better if smaller threshold is chosen, but it will slightly reduce the accuracy.

**Table 2.1: Performance Comparison with Prior Arts**

|                           | This work                                                  | JSSC'17 [28]             | VLSI'17 [29]                | ISSCC'16 [31]                              | VLSI'15 [32]                  | Note                                                                                                                                                                     |

|---------------------------|------------------------------------------------------------|--------------------------|-----------------------------|--------------------------------------------|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Application               | Hand writing recognition                                   | Hand writing recognition | Hand writing<br>recognition | Object detection +<br>intention prediction | Object<br>Recognition         | a. N=16 in our measurements.                                                                                                                                             |

| Neural Network<br>Type    | Multi-layer perceptron<br>network                          | Binary neural<br>network | Binary DNN                  | Deep neural<br>network                     | SAILnet                       | b. SOp/s/W: Synaptic operation (SOp). In DCO based time-                                                                                                                 |

| Circuit Type              | Time-based                                                 | Time-based               | Digital                     | Analog + Digital                           | Digital                       | domain neural network, one oscillation of DCO is equivalent                                                                                                              |

| Technology                | 65nm                                                       | 65nm                     | 65nm                        | 65nm                                       | 65nm                          | to 121 SOp.                                                                                                                                                              |

| Area                      | 0.24mm <sup>2</sup> (64 DCOs)                              | 3.61mm² (32K PEs)        | 3.9mm²                      | 16.0mm²                                    | 1.8mm <sup>2</sup>            | c. 1GE: 1.44um²(65nm). PE: processing element.                                                                                                                           |

| Voltage                   | 1.2V                                                       | -                        | 0.55-1.0V                   | 1.2V                                       | 0.45V                         | d. Operation: One operation is                                                                                                                                           |

| Frequency                 | 99MHz (nominal DCO freq.)                                  | -                        | 100-400MHz                  | 250MHz                                     | 40MHz (Inference)             | defined as one multiplication and accumulation (MAC). In                                                                                                                 |

| Power                     | 320.4 μW/DCO                                               | -                        | 0.05-0.6W                   | 330mW                                      | 3.65mW                        | DCO based time-domain neural                                                                                                                                             |

| Power<br>Efficiency       | 309G ÷ N spikes/s/W<br>(N=spiking threshold <sup>a</sup> ) | 48.2TSOp/s/W             | 6.0-2.3TOPS/W <sup>f</sup>  | 862GOPS/W                                  | 5.7pJ/pixel<br>(memory+logic) | network, one oscillation of DCO is equivalent to 121 3-bit MAC.                                                                                                          |

| Hardware<br>Efficiency    | -                                                          | 76.5GE/PE                | •                           | -                                          | •                             | e. Used spiking threshold of 16,                                                                                                                                         |

| Performance<br>Comparison | 37.4TSOp/s/W <sup>b</sup>                                  | 48.2TSOp/s/W             | •                           | -                                          | -                             | and only accounted for the power consumption of core logic circuits, memory power is not included, since weight is not updated during the inference.  f. 1 MULADD = 2OPs |

|                           | 16.6GE/PE°                                                 | 76.5GE/PE                | -                           | -                                          | -                             |                                                                                                                                                                          |

|                           | 37.4TOPS/W <sup>d</sup>                                    | -                        | 6.0-2.3TOPS/W               | 862GOPS/W                                  | •                             |                                                                                                                                                                          |

|                           | 0.43pJ/pixel (logic) <sup>e</sup>                          | -                        | -                           | -                                          | 5.7pJ/pixel<br>(memory+logic) |                                                                                                                                                                          |

Fig. 2.23 shows the die photo and the performance summary of the test chip. The neuromorphic core with 64 DCO circuits takes an area of 0.24mm<sup>2</sup>. There are around 8K synapses and 3.1K bytes of on-chip memory.

| Technology    | 65nm LP CMOS                                                                 |  |  |

|---------------|------------------------------------------------------------------------------|--|--|

| Core Size     | 510µm x 460µm =<br>0.24mm²                                                   |  |  |

| VDD range     | 0.7V~1.2V                                                                    |  |  |

| # of Neurons  | 64 (single core)                                                             |  |  |

| # of Synapses | 8192 (8K)                                                                    |  |  |

| On-chip SRAM  | 3.1K bytes                                                                   |  |  |

| Throughput    | 746Mpixels/s ÷ N (1.2V)<br>148Mpixels/s ÷ N (0.7V)<br>(*N=spiking threshold) |  |  |

| Power         | 320.4μW (per DCO, 1.2V)<br>17.5μW (per DCO, 0.7V)                            |  |  |

\*N = 16 in our measurements

Fig. 2.23: Die photo and performance summary of the test chip.

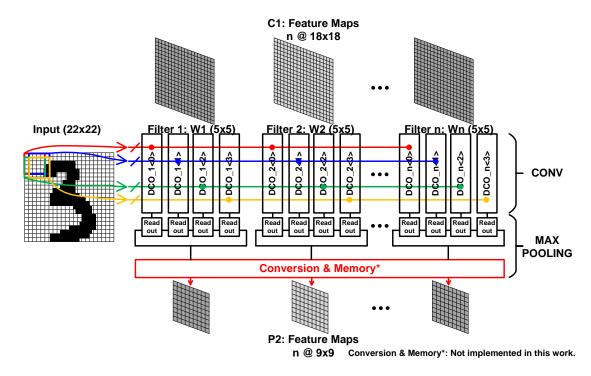

In this work, we have focused on the implementation of MLP using our proposed time-based neuromorphic core, however, the proposed time-based architecture is not limited to MLP only. With some modifications, we can also apply the proposed neuromorphic core in convolutional neural network (CNN), as is shown in Fig. 2.24. We take an input image of 22x22 pixels and filter size of 5x5 as an example. Each DCO can do the computation of convolution between filters and inputs. We can group 4 DCOs together for the max pooling layer to subsampling the feature maps to a smaller size by taking advantage of the LLI feature in this work. Instead of sliding the filter over input images, we fix the filters and shift the input images to feed into different DCOs, which can save the memory access cost. One limitation of the proposed work is that the outputs of the DCOs are spikes, so we need to convert this information to digital domain to feed to the next layer, and we also need some on-chip memory to store the intermediate results for implementing CNN. The main

modification required is to add one conversion and memory block. And this is our possible future works for this time-based neuromorphic core.

Fig. 2.24: Implementation of convolutional neural network (CNN) using our proposed time-based neuromorphic core with some modifications.

#### 2.6 Conclusion

In this work, we present the implementation of neuromorphic function in time domain with programmable delay stages. Brain-inspired leak and local lateral inhibition (LLI) features are also implemented on chip. The processing element of the proposed time-based neuromorphic core is based on inverter which is tiny and compact, and each processing element has its exclusive memory for use, eliminating the power for data movement, making the proposed core highly efficient in area and power. The proposed time-based

neuromorphic core is tested with digit recognition application and achieves a 91.4% recognition accuracy. The energy-efficiency and versatility of the presented time-based DCO neuromorphic core makes it a promising building block for future large scale deep neural network applications.

# Chapter 3. Binarized LSTM Neural

# **Network Architecture Design**

#### 3.1 Introduction

Recurrent neural network (RNN) is very powerful in processing sequential data, and it has been proven to be successful in many applications, such as natural language processing (NLP) [35], machine translation [36], etc. Long short-term memory (LSTM) is a popular type of RNN that is good at dealing with sequential data that has long term dependencies. Photoplethysmorgraphy (PPG) signal is such a type of data, which is a popular and convenient way for heart rate monitoring. However it suffers from motion artifacts (MA) problem, deteriorating the accuracy of heart rate estimation. Recently, LSTM neural networks accompanied with convolution neural networks (CNNs) and fully connected (FC) layers are shown to work well in predicting heart rate from PPG signals [37]. This data-driven and learning-based network obviates the necessity of feature engineering, which requires domain knowledge to select hand-crafted features.

Despite the versatility of the LSTM neural networks, it is hard to implement in hardware due to its high computation complexity and memory requirement. In this work, to deploy the neural network for heart rate prediction on embedded devices, an efficient binarized LSTM hardware architecture that reduces the computation complexity and the

memory footprint is proposed and the performance is evaluated with various PPG datasets. The proposed LSTM architecture is tested using the custom collected PPG signals and the simulation results demonstrates that the proposed binarized LSTM architecture achieves a good heart rate prediction accuracy.

## 3.2 LSTM and PPG Background

#### 3.2.1 LSTM Neural Network

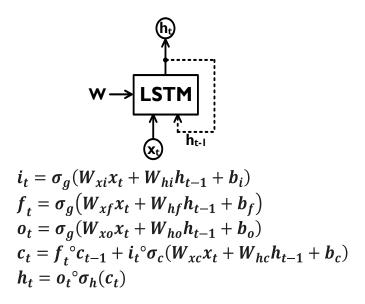

Fig. 3.1: LSTM unit and equations.

The LSTM unit is composed of an input gate, a forget gate, an output gate and a cell. Each gate can be viewed as a feed-forward neural network, implementing the multiply and accumulation (MAC) computation followed by an activation function, as is shown in Fig. 3.1 [38]. The subscript t indexes the time step,  $\sigma_g$  represents the sigmoid function, and  $\sigma_c$ ,  $\sigma_h$  are tanh. The operator  $^{\circ}$  denotes the element-wise product. Each gate computes the

element-wise addition of two weighted sums  $W_x x_t$  and  $W_h h_{t-1}$ , and a bias b. To simplify the neural network, we remove the bias term in this work. Therefore, each gate now computes the element-wise addition of two dot products of inputs  $x_t$  and hidden states  $h_{t-1}$  and their corresponding weights, followed by an activation function. There are two input ports for each gate, one is the actual external input signal of the current time step  $x_t$ ; the other is the output (hidden state) from the previous time step  $h_{t-1}$ , which allows information to persist, and this is the loop shown in the LSTM unit in Fig. 3.1.

In this work, a binarized LSTM neural network is proposed to reduce the memory requirement and simplify the circuit implementation in hardware. During the training, the weights are binarized using loss-aware binarization scheme [39]. Instead of simply finding the closest binary approximation of weights, this loss-aware binarization also considers the loss during binarization. So in this work, the weight in each layer is binarized as