## DESIGN OF LOW COMPLEXITY ACCUMULATOR USING FINFET FOR VARIOUS TECHNOLOGIES

N.Sathya<sup>1</sup>, Dr.M.Anto Bennet <sup>1</sup>M.Mageswari<sup>2\*</sup>, M.Priya<sup>2</sup>, M.Kayalvizhi<sup>2</sup>

<sup>1</sup>Faculty of ECE department, Vel Tech, Chennai-62, India. <sup>2</sup>UG Scholar, ECE department, Vel Tech, Chennai-62, India.

Email: mageswari3mk@gmail.com

Submitted: May 27, 2017 Accepted: June 15, 2017 Published: Sep 1, 2017

Abstract- FINFET terminological in exactitude process reuses a massive part of well accustomed conventional CMOS process. FINFET is a likely-look alternative to conventional MOSFET which has reached its limit and has too much leakage for too little performance gain. FINFET is being suggested as basics for future IC processes because its power or performance benefits, scalability, superior controls over short channel effort etc., In this paper we propose a outlook for scheming accumulator using FINFET for purpose of minimize number of transistor differentiate to CMOS logic. In circuit level, widely used D flip-flop and at constructional level the full adder cells of FINFET (dual gate transistor) 10T can be used. FINFET is the most propitious double gate transistor, forecast as one of the candidate to restore the epic MOSFET. FINFET technology power consumption is compare with CMOS technology to analyze how the area, delay and power can be reduced.

Index terms: FINFET (FIN field effect transistor), CMOS (Complementary Metal oxide semiconductor), accumulator, low power consumption, reduce delay.

N.Sathya, M.Anto Bennet, M.Mageswari, M.Priya and M.Kayalvizhi Design of low complexity accumulator using finfet for various technologies

### I. INTRODUCTION

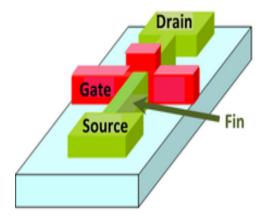

Conventional MOSFETs have an indelible problem for large leakage current for gate to channel increasingly unconvincing transistor characteristics. The integrated circuit technology is flourishing at a serious stride since the origination of first MOS microprocessor in 1970. The prime driving force beyond this development is the technique of scaling. The scaling of MOS transistor has evolve in high density, high performance chips. But this miniaturization is obstructed by much awful case that emerges in MOS device as the device size goes on shrinking. Out of this concern, power dissipation is an extensive complication. CMOS has been used widely in current technologies, but it cause the short channel effect such as DIBL, GIDL, channel length Modulation, mobility degradation etc., In view of the barrier in planar CMOS transistor scaling to preserve tolerable gate to a channel control FINFET based accumulator has been proposed as technology option for restore the existing CMOS technology. The enchantment of FINFET consists in the realization of self-aligned double gate devices with a conventional CMOS process shown in figure-1. This entitle extending the gate scaling following the planar transistor restriction, maintaining a better accomplishment due to low doping concentration in the channel. In this work the area, delay and power consumption of FINFET accumulator are examined. This result of FINFET accumulator is compared against CMOS based accumulator.

Figure.1 FINFET dual gate transistor

In second section discuss about the proposed model of FINFET. The third section describe about explanation of D Flip-flop, full adder and accumulator using FINFET. The fourth section gives the output of accumulator and at last conclusion of the result analyses will be declared.

II. Proposed model

FINFET is a most advanced technology in VLSI (very large scale integration) which replaces bulk CMOS technology. In this proposed model, CMOS accumulator is replaced by a FINFET accumulator to show the reduction in power consumption, area, delay and improvement in the performance of the accumulator. The term accumulator is used in a widely variety of noncomputing application and activities, such as electrical engineering (an energy storage device such as rechargeable battery or ultra-capacitor) hydraulics (mechanical energy storage devices), in stack trading (a contract or agreement) and even in gambling (parlay bet). Accumulator is a register for short term, intermediate storage of arithmetic and logic data in a computer's CPU (central processing unit). The most elementary use for an accumulator is adding a sequence of numbers. The numerical value in the accumulator increase as each number is added, exactly as it happens in simple desktop calculators. Once the sum has been determined, it is written to the main memory or another register.

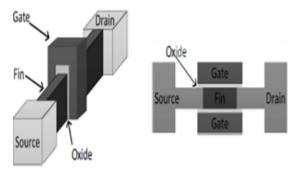

a) Three dimension structure b) Cross section top view

Here in this proposed paper accumulator is designed with FINFET D flip-flop and FINFET full adder and hence the result is showed in MODEM SIM software in percentage compared with CMOS accumulator. Intension of this paper is to reduce the power consumption, delay, numbers of transistor and area.

## **2.1 FINFET Technology**

FINFET is mostly used in a current technology. It is a quasi-planar effect transistor and the working principle is similar to the planar MOSFET. The effective width of the FINFET is 2nHfin.FINFET gate consist of double gate transistor and it optimize the power and performance. Here the double or multiple gates can be used to enhance the electrostatic control. In the conventional planar transistor current flows through the circuits depends only the width of the device (W).Width is the half of the channel length. If the channel scale is down, it necessary to

Design of low complexity accumulator using finfet for various technologies

decrease channel length and transistors which improves the performance of the transistor. In Figure.2 shows that three dimensional structure of FINFET which consists of source, drain, gate and cross section top view shows that dual gate transistor. FINFET has advantage of reduction in leakage power, operating power, leakage current, transistor gate delay, reduced threshold gate level.

#### 2.2 Full adder

Adders have become an important part in this world; there is no design without adder. In VLSI adders used a basics component. Full adder is a combinational circuit that performs the addition operation of inputs bits. Full adder is a core of much digital and analog circuit. It is used as major furbearing circuits for many digital designs. Full adder circuits are analysed for low power consumption, reduced delay and low power products. Design of full adder speed is restricted by size of the transistor, parasitic capacitance and delay in the critical path. The truth table for full adder is given in table1.

| Χ | Y | Z | Sum | Carry |

|---|---|---|-----|-------|

| 0 | 0 | 0 | 0   | 0     |

| 0 | 0 | 1 | 1   | 0     |

| 0 | 1 | 0 | 1   | 0     |

| 0 | 1 | 1 | 0   | 1     |

| 1 | 0 | 0 | 1   | 0     |

| 1 | 0 | 1 | 0   | 1     |

| 1 | 1 | 0 | 0   | 1     |

| 1 | 1 | 1 | 1   | 1     |

Table 1. Truth table of full adder

#### 2.3 Full adder using FINFET

Dual gate FINFET has two electrically independent gates, which gives circuit design more flexibility in design low power and reduced the number of transistor. Field effect transistor full

adder have indicated as alternatives to reduced the short channel effect(SLE) of scaled devices due to their better electrostatic control of

channel charges. In this paper propose a low power and area efficient full adder. FINFET full adder design confirms that there is reduction of 25 to 30 percent in the value of power dissipation when compared to CMOS full adder technique.

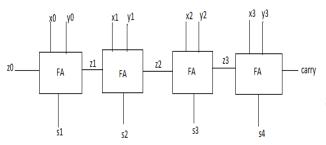

Figure.3 4-bit full adder

In the figure.3 four bit full adder is used for 4 bit addition purpose which includes 4 bit inputs (x0, y0), (x1, y1), (x2, y2), (x3, y3) and four sum outputs s1,s2,s3,s4. A carry input z0 is given to the first full adder FA1; the inputs such as z1, z2, z3 are given to the forthcoming full adder FA2, FA3, FA4 respectively. The full adder block FA1 is schematically represented by using FINFET logic. [8]

Figure.4 1-bit FINFET full adder

In static CMOS Full adder with pull up and pull down networks used 28 transistors but FINFET full adder required only 10 transistors. In this proposed paper FINFET full adder is designed in that accumulator to reduced power consumption, area and delay.

## 2.4 D flip- flop

D flip-flop is considered to be the most essential memory cell in the vast majority of digital circuit, which brings it extensive utilization especially under low power consumption. In recent research focus, numerous different types of D flip-flop have been invented and investigated and the continuous research trend has turned to high speed low power consumption performance. To implement high performance VLSI, obviously D flip-flop is chosen for extremely significant part in design flow. There two aspects for choosing D flip-flop, one is direct effect on clock frequency of digital circuit system and another which tends to consume 30% to 50% of power dissipation. Table 2 shows that D flip-flop stores a bit of data. i.e. input data applied at input D, its change the

Design of low complexity accumulator using finfet for various technologies

output state according to the inputs and remain in the same state until the inputs changes. It is also used to introduce the delay in the circuit, and it is used as a buffer to store the intermediate data.

Table 2.Truth table of D-Flip-flop

| Q | D | outp |

|---|---|------|

|   |   | ut   |

| 0 | 0 | 0    |

| 0 | 1 | 1    |

| 1 | 0 | 0    |

| 1 | 1 | 1    |

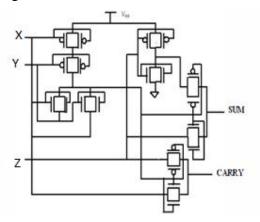

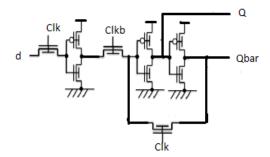

#### 2.5 D flip-flop using FINFET

FINFET has two electrical gates for the more flexibility design to reduce the low power consumption. Here D flip-flop is specifying used in the accumulator for reducing the numbers of transistor. It is delay flip flop used to reduced delay, power and area. In figure.5 shows that FINFET D flip-flop used a clock, reset, and a FINFET transistor is designed in the accumulator to show the reduced in the design when compared to the CMOS transistor. Here accumulator is effective by using the D flip-flop instead of another flip-flop. Hence the performance can be improved. [6]

Figure.5 FINFET D FLIPFLOP

### 2.6 Accumulator

Accumulator is a 8-bit register used as a temporary storage device and to perform a arithmetic operation such as Addition, Subtraction, multiplication, division logic operation like

AND,OR,XOR etc., It is a part of ALU that stores a result in memory. The most elementary use for an accumulator is adding a sequence of numbers.

The term accumulator is used in a widely variety of non-computing application and activities, such as electrical engineering (an energy storage device such as rechargeable battery or ultracapacitor) hydraulics (mechanical energy storage devices), in stack trading (a contract or agreement) and even in gambling (parlay bet). Accumulator dramatically improved the performances in the system like this providing a scratchpad area where the result of one operation can be fed in the next one for little or no performance partly. Accumulator size which is depends on the processor type; it can store the final value of the process already perform the task. FINFET accumulator used 5% of transistor when compared with CMOS technology and also the delay and area are minimized.

## III. Analytical result

CMOS accumulator has 6% of power consumption, 5% of area and numbers of transistor used is 13% shown in figure-6 and table-3 these output waveform is shown in XILINX.

| /finalresu/clk11    | 0    |             | ากกกากกก | הההההה | I | נסטטקסטטקסטסט      |

|---------------------|------|-------------|----------|--------|---|--------------------|

| /finalresu/cin11    | 0    |             |          |        |   |                    |

| /finalresu/rst11    | 0    |             |          |        |   |                    |

| /finalresu/d11      | 1010 | 1010        |          |        |   |                    |

| /finalresu/a11      | 0011 | 0011        |          |        |   | (1011              |

| /finalresu/b11      | 1001 | UUUU (10    | 01       |        |   | <u>(1</u>          |

| /finalresu/sum11    | 1010 | <u>))10</u> | 10       |        |   | <u>)0101 )1 )1</u> |

| /finalresu/coutts11 | 0001 | (wwht )oo   | 01       |        |   | <u>)1011 (1</u>    |

| /finalresu/qsum1    | 10X0 | 0000        |          |        | Ņ |                    |

| /finalresu/tmp      | 1000 | 0000        |          |        | M |                    |

|                     |      |             |          |        |   |                    |

Figure.6 CMOS accumulator output waveform

Model Sim realization of accumulator using CMOS logic

| Table 3. | CMOS | accumul | lator p | performation | nce |

|----------|------|---------|---------|--------------|-----|

|          |      |         |         |              |     |

| Macr<br>o<br>cells<br>Used | P<br>terms<br>used | Register<br>s Used | Pins<br>Used | Functio<br>n block<br>inputs<br>used |

|----------------------------|--------------------|--------------------|--------------|--------------------------------------|

| 4/72                       | 8/360              | 3/72               | 9/72         | 9/216                                |

Design of low complexity accumulator using finfet for various technologies

| (6%) | (3%) | (5%) | 13% | (5%) |

|------|------|------|-----|------|

|      |      |      |     |      |

|      |      |      |     |      |

In FINFET accumulator designed by 12% of power consumption, 1% of area and 5% of transistor is used and the output is shown in figure6 and the table4 model sim.

| /finfetaccumul_1/clk1  | 0 |                  | лл             |          | лл     |          |         |

|------------------------|---|------------------|----------------|----------|--------|----------|---------|

| /finfetaccumul_1/cin1  | 1 |                  |                |          |        |          |         |

| /finfetaccumul_1/d1    | 0 |                  |                |          |        |          |         |

| /finfetaccumul_1/a1    | 1 |                  |                |          |        |          |         |

| /finfetaccumul_1/b1    | 0 |                  |                |          |        |          |         |

| /finfetaccumul_1/clkb1 | 1 |                  | WW             | Innn     | uuu    | uuu      |         |

| /finfetaccumul_1/su    | 0 |                  |                |          |        |          |         |

| /finfetaccumul_1/co    | 1 |                  |                |          |        |          |         |

| /finfetaccumul_1/qs    | L | ┥╷┍╢┍┥           | rlrl           | .իլ.հլ.հ | hl.hl. | ու.հլ.հ. | .hl.hl. |

| /finfetaccumul_1/dra1  | L |                  |                |          | FL.FL  | FLFLF.   | .Γι.Γι. |

| /finfetaccumul_1/clk   | 1 |                  |                |          |        |          |         |

| /finfetaccumul_1/q1    | L | <u> 11 FL F.</u> | <u>. [] []</u> |          |        |          |         |

Figure.7 FINFET accumulator output waveform

The above figure represents the output of full adder designed using FINFET accumulator. The major disadvantage in towards circuit is delay. The main motive of every designer is to reduce the delay and power. This is achieved in our design of accumulator using FINFET. In existing model the design of accumulator using CMOS logic yields more delay and increases power consumption due to the usage of increased number of transistors. When the transistor count reduces the power consumption also gradually increases because the leakage power of any circuit designed using CMOS logic uses increased transistor count. This major drawback observed in the CMOS logic design is overcome by our proposed model. The proposed model includes accumulator design using FINFET, the major advantage of using FINFET is reduced transistor and registers, reduced power consumption and delay. Thus our proposed model acts as a good solution to solve all these problems. Hence this proposed model can be easily applied in real time such as smart phones.

Table 4. FINFET accumulator performance

| Macr  | Р     | Registe | Pins | Functio |

|-------|-------|---------|------|---------|

| 0     | terms | rs Used | Used | n block |

| cells | used  |         |      | inputs  |

| Used |       |      |      | used  |

|------|-------|------|------|-------|

| 1/72 | 1/360 | 0/72 | 3/72 | 1/216 |

| (2%) | (1%)  | (0%) | 5%   | (1%)  |

## IV. Comparison of CMOS and FINFET accumulator

When CMOS is compared with FINFET technology it proved that the area, power consumption and delay have been reduced. In FINFET consumed 4% of power, 7% of the transistor and 4% of area less than the CMOS accumulator. Hence FINFET is most advanced technique and it is used in the current technology.

#### REFERENCES

[1] Aizat Azmi, Ahmad Amsyar Azman, Sallehuddin Ibrahim, and Mohd Amri Md Yunus, "Techniques In Advancing The Capabilities Of Various Nitrate Detection Methods: A Review", International Journal on Smart Sensing and Intelligent Systems., VOL. 10, NO. 2, June 2017, pp. 223-261.

[2] Tsugunosuke Sakai, Haruya Tamaki, Yosuke Ota, Ryohei Egusa, Shigenori Inagaki, Fusako Kusunoki, Masanori Sugimoto, Hiroshi Mizoguchi, "Eda-Based Estimation Of Visual Attention By Observation Of Eye Blink Frequency", International Journal on Smart Sensing and Intelligent Systems., VOL. 10, NO. 2, June 2017, pp. 296-307.

[3] Ismail Ben Abdallah, Yassine Bouteraa, and Chokri Rekik, "Design And Development Of 3d Printed Myoelctric Robotic Exoskeleton For Hand Rehabilitation", International Journal on Smart Sensing and Intelligent Systems., VOL. 10, NO. 2, June 2017, pp. 341-366.

[4] S. H. Teay, C. Batunlu and A. Albarbar, "Smart Sensing System For Enhanceing The Reliability Of Power Electronic Devices Used In Wind Turbines", International Journal on Smart Sensing and Intelligent Systems., VOL. 10, NO. 2, June 2017, pp. 407- 424

[5] SCihan Gercek, Djilali Kourtiche, Mustapha Nadi, Isabelle Magne, Pierre Schmitt, Martine Souques and Patrice Roth, "An In Vitro Cost-Effective Test Bench For Active Cardiac Implants, Reproducing Human Exposure To Electric Fields 50/60 Hz", International Journal on Smart Sensing and Intelligent Systems., VOL. 10, NO. 1, March 2017, pp. 1-17

Design of low complexity accumulator using finfet for various technologies

[6] P. Visconti, P. Primiceri, R. de Fazio and A. Lay Ekuakille, "A Solar-Powered White Led-Based Uv-Vis Spectrophotometric System Managed By Pc For Air Pollution Detection In Faraway And Unfriendly Locations", International Journal on Smart Sensing and Intelligent Systems., VOL. 10, NO. 1, March 2017, pp. 18- 49

[7] Samarendra Nath Sur, Rabindranath Bera and Bansibadan Maji, "Feedback Equalizer For Vehicular Channel", International Journal on Smart Sensing and Intelligent Systems., VOL. 10, NO. 1, March 2017, pp. 50- 68

[8] Yen-Hong A. Chen, Kai-Jan Lin and Yu-Chu M. Li, "Assessment To Effectiveness Of The New Early Streamer Emission Lightning Protection System", International Journal on Smart Sensing and Intelligent Systems., VOL. 10, NO. 1, March 2017, pp. 108- 123

[9] Iman Heidarpour Shahrezaei, Morteza Kazerooni and Mohsen Fallah, "A Total Quality Assessment Solution For Synthetic Aperture Radar Nlfm Waveform Generation And Evaluation In A Complex Random Media", International Journal on Smart Sensing and Intelligent Systems., VOL. 10, NO. 1, March 2017, pp. 174- 198

[10] P. Visconti ,R.Ferri, M.Pucciarelli and E.Venere, "Development And Characterization Of A Solar-Based Energy Harvesting And Power Management System For A Wsn Node Applied To Optimized Goods Transport And Storage", International Journal on Smart Sensing and Intelligent Systems., VOL. 9, NO. 4, December 2016, pp. 1637- 1667

[11] YoumeiSong, Jianbo Li, Chenglong Li, Fushu Wang, "Social Popularity Based Routing In Delay Tolerant Networks", International Journal on Smart Sensing and Intelligent Systems., VOL. 9, NO. 4, December 2016, pp. 1687-1709

[12] Seifeddine Ben Warrad and OlfaBoubaker, "Full Order Unknown Inputs Observer For Multiple Time-Delay Systems", International Journal on Smart Sensing and Intelligent Systems., VOL. 9, NO. 4, December 2016, pp. 1750-1775

[13] Rajesh, M., and J. M. Gnanasekar. "Path observation-based physical routing protocol for wireless ad hoc networks." International Journal of Wireless and Mobile Computing 11.3 (2016): 244-257.

[14]. Rajesh, M., and J. M. Gnanasekar. "Congestion control in heterogeneous wireless ad hoc network using FRCC." Australian Journal of Basic and Applied Sciences 9.7 (2015): 698-702.

[15]. Rajesh, M., and J. M. Gnanasekar. "GCCover Heterogeneous Wireless Ad hoc Networks." Journal of Chemical and Pharmaceutical Sciences (2015): 195-200.

[16]. Rajesh, M., and J. M. Gnanasekar. "CONGESTION CONTROL USING AODV PROTOCOL SCHEME FOR WIRELESS AD-HOC NETWORK." Advances in Computer Science and Engineering 16.1/2 (2016): 19.

[17]. Rajesh, M., and J. M. Gnanasekar. "An optimized congestion control and error management system for OCCEM." International Journal of Advanced Research in IT and Engineering 4.4 (2015): 1-10.

[18]. Rajesh, M., and J. M. Gnanasekar. "Constructing Well-Organized Wireless Sensor Networks with Low-Level Identification." World Engineering & Applied Sciences Journal 7.1 (2016).

[19] L. Jamal, M. Shamsujjoha, and H. M. Hasan Babu, "Design of optimal reversible carry lookahead adder with optimal garbage and quantum cost," International Journal of Engineering and Technology, vol. 2, pp. 44–50, 2012.

[20] S. N. Mahammad and K. Veezhinathan, "Constructing online testable circuits using reversible logic," IEEE Transactions on Instrumentation and Measurement, vol. 59, pp. 101–109, 2010.

[21] W. N. N. Hung, X. Song, G. Yang, J. Yang, and M. A. Perkowski, "Optimal synthesis of multiple output boolean functions using a set of quantum gates by symbolic reachability analysis," IEEE Trans. on CAD of Integrated Circuits and Systems, vol. 25, no. 9, pp. 1652–1663, 2006.

[22] F. Sharmin, M. M. A. Polash, M. Shamsujjoha, L. Jamal, and H. M. Hasan Babu, "Design of a compact reversible random access memory," in 4th IEEE International Conference on Computer Science and Information Technology, vol. 10, june 2011, pp. 103–107.

[23] Dr. AntoBennet, M, Sankar Babu G, Suresh R, Mohammed Sulaiman S, Sheriff M, Janakiraman G, Natarajan S, "Design & Testing of Tcam Faults Using  $T_H$  Algorithm", Middle-East Journal of Scientific Research 23(08): 1921-1929, August 2015.

[24] Dr. AntoBennet, M "Power Optimization Techniques for sequential elements using pulse triggered flipflops", International Journal of Computer & Modern Technology, Issue 01, Volume01, pp 29-40, June 2015.