#### University of New Mexico UNM Digital Repository

Physics & Astronomy ETDs

**Electronic Theses and Dissertations**

Spring 4-9-2019

## Improving the Readout of Semiconducting Qubits

Matthew Jon Curry University of New Mexico

Follow this and additional works at: https://digitalrepository.unm.edu/phyc\_etds Part of the <u>Condensed Matter Physics Commons</u>, and the <u>Quantum Physics Commons</u>

#### **Recommended** Citation

Curry, Matthew Jon. "Improving the Readout of Semiconducting Qubits." (2019). https://digitalrepository.unm.edu/phyc\_etds/211

This Dissertation is brought to you for free and open access by the Electronic Theses and Dissertations at UNM Digital Repository. It has been accepted for inclusion in Physics & Astronomy ETDs by an authorized administrator of UNM Digital Repository. For more information, please contact amywinter@unm.edu.

Matthew Jon Curry

Candidate

Physics and Astronomy

Department

This dissertation is approved, and it is acceptable in quality and form for publication:

Approved by the Dissertation Committee:

Ivan H. Deutsch

Chair person

Stephen M. Carr

Malcolm S. Carroll

Jason R. Petta

## Improving the Readout of Semiconducting Qubits

by

### Matthew Jon Curry

B.S., Physics, California Polytechnic State University, 2011M.S., Physics, University of New Mexico, 2013

### DISSERTATION

Submitted in Partial Fulfillment of the Requirements for the Degree of

> Doctor of Philosophy Physics

The University of New Mexico

Albuquerque, New Mexico

May, 2019

©2019, Matthew Jon Curry

# Dedication

To my family and friends.

## Acknowledgments

This dissertation is a map I wish I had at the beginning of graduate school. Everything here would not have been possible without guidance from my advisers as well as support from my friends and family. I would now like to take the time to thank everyone.

I owe a great deal to my two research advisers at Sandia National Laboratories: Steve Carr, and Malcolm Carroll. I first began research with Steve at Sandia in the summer of 2012. Steve showed me the basics of experimental research in a nicely detailed manner. I learned how to use a lock-in amplifier and electrically characterize devices at cryogenic temperatures. Steve's careful nature with handling devices and instruments is a skill that I practice to this day. I am grateful for Steve's patience with me as I grew to be the experimentalist I am now. Further along in graduate school, I adiabatically began working with Malcolm as my primary research adviser. Malcolm had a fundamentally different way of advising which I grew to appreciate. As we moved from device to device and anticrossing to anticrossing, I learned a great deal about quantum dots and singlet-triplet qubits. I watched new types of readout and qubits develop during our long group meetings. The scientific method style of presentation is something I always try to do moving forward. Planning measurements out well in advance is a skill that I appreciated learning and continue working on. Again, I couldn't be more thankful for both my advisers' patience and guidance.

At Sandia, there are many other people I would like to thank. Mike Lilly helped me get started in a lab at CINT and attended the early HBT meetings. I am very grateful for all the assistance with dilution refrigerators Mike as provided over the vears. Troy England arrived later in the HBT project and his expertise in HBTs was invaluable for the entirety of the project. I could not be more fortunate that such an expert joined Sandia during my graduate studies. Martin Rudolph was also incredibly helpful with the HBT project and publications. I will miss working with him moving forward. Ryan Jock is a great colleague I always look forward to chatting with. It will be nice working together in the future. My previous manager, Clark Highstrete, was an interesting person to talk to. He flew the F-16 in the US Air Force and graduated from the same physics Ph.D. program at UNM, which was rather encouraging. Similarly, my current manager, Steve Rinaldi, was in the US Air Force and has a Ph.D. I've been hired as a member of the staff at Sandia through Steve, so I am very thankful, to say the least. I would not have been able to make it through the long days of research without my fellow graduate students at Sandia: Patrick Harvey-Collard, Chloe Bureau-Oxton, and Amir Shirkhorshidian. Patrick provided incredible amounts of advice and knowledge, and Chloe left hidden bags of M&Ms that I'm still finding to this day. I look forward to working with Dwight Luhman as the new principal investigator for many years to come. In no particular order, I would also like to thank: Tzu-Ming Lu, Meenakshi Singh, Ezra Bussmann, Wayne Witzel, Toby Jacobson, Dan Ward, Shashank Misra, Andrew Baczewski, Andrew Landahl, Kenny Rudinger, Andy Mounce, Lisa Tracy, Rick Muller, Tom Harris, Ed Bielejec,

Vanita Srinivasa, Erik Nielsen, Peter Sharma, Mike Wanke, Jonathan Rivera, Rohith Vudatha, Nick Brechtel, Albert Grine, Victor Chavez, and Chuck Fuller.

At UNM, I had many great professors and fellow graduate students who I would like to thank. Ivan Deutsch was my research advisor throughout my time at UNM. Ivan was extremely helpful with any questions I had about graduate school and the classes I took with him. Long ago, Ivan encouraged me to accept the offer from the UNM physics Ph.D. program, which has opened many doors for me now. When I was deciding what research to begin with, Ivan recommended chatting to Steve Carr which eventually lead to my career at Sandia. I've greatly enjoyed Ivan being on my dissertation committee and all the advice he has given helping me graduate. Carl Caves is a great character that UNM will surely miss as he retires. Carl was also a large part of why I eventually attended the UNM physics Ph.D. program. I enjoyed Carl's quantum mechanics and quantum information classes as well as his dry sense of humor. Dave Dunlap, Kevin Cahill, and Vasudev Kenkre were also professors I enjoyed taking courses from. I have many friends to thank and not nearly enough time! Andy Ferdinand came from Cal Poly with me and was my first roommate in graduate school. I went on many outdoor adventures that I otherwise may not have gone on with Andy, and it made the early years much nicer. And is a great friend and someone I enjoy sharing liter glasses of beer with! Adrian Chapman was an amazing running and gaming buddy for almost all of graduate school. I could not have wished for a better friend. I miss all the good times and hopefully we'll end up working closer together someday! I would like to thank Evelyn Dohme for doing an excellent grammar run-through of this dissertation! Rest in peace, Kornelius Jakobsen, you are not forgotten. In no particular order, I would also like to thank: Josh Combes, Chris Ferrie, Jason Petta, James Hendrie, Jonathan Bainbridge, Karishma Bansal, Mitchell Brickson, Austin Daniel, Kathy DeBlasio, Chris DiLullo, Akram Amin, Matt DiMario, Rachel James, Aidan Grummer, Luke Horstman, Rachel, Horstman, Ning Hsu, Forrest Hubert, Matt Koppa, Megan, Lewis, Neil McFadden, Chelsea McFadden, Kevin Meaney, Anupam Mitra, Ben Morrison, Gopi Muraleedharan, Manuel Arias, Jaksa Osinski, Nate Ristoff, Rockie Curdes, Maziar Ziabari, Keith Sanders, Ezad Shojaee, Sam Slezak, Changhao Yi, Zhixian Yu, Ninnat Dangniam, Jonathan Gross, Anastasia Ierides, Linh Le, Xiaodong Qi, Ciaran Ryan-Anderson, Jacob Miller, Peter Relich, Mark Gorski, Tzu Cheng Wu, Charlie Baldwin, Matt Chase, Bob Keating, Brad Knockel, Ken Obenberger, Satomi Sugaya, Matthias Lang, Akash Rakholia, Ben Baragiola, Chris Cesare, Zhang Jiang, Leigh Norris, Rob Cook, Ben Johnson, Bibek Pokharel, Caleb Grimes, Eric Bahr, Kari Jacobs, Phil Casady, Dillon Thomas, Gena Robertson, Iman Chudnoff, Justin Peinado, Rachel Hellmer, Michael Treiman, Peter Sinclair, Vikas Buchemmavari, Dante Archuleta, and Joe Landers. I probably forgot a few people, so I apologize ahead of time.

At Cal Poly, there were several professors responsible for encouraging me to attend graduate school. Brian Granger gave me my first research opportunity ever with Google Summer of Code 2010. This experience and the research afterward were seminal in my understanding of object-oriented programming and quantum mechanics. I've since used Python and Lyx throughout graduate school, and I've benefited tremendously as a result. I've even written this dissertation using Lyx! I'm very thankful to have worked with Brian so early in my studies and experienced the basics of quantum computing. Kat Gillen provided the first experimental research experience for me in her laser lab. Although I did not end up working with lasers, I still gained an appreciation for the research. Ron Zammit was an excellent electronics teacher and an entertaining friend outside of class. Through Ron's classes, I became motivated to learn about old electronics such as vacuum tubes and analog computers. He even let us keep some old tubes, which I still have today! Dane Iracleous is my comedic partner. Our thoughts resonate on a level I've never since experienced. I don't know how many times I've thought back on some of the silly things we thought up during college and immediately started uncontrollably cracking up. If nothing else works out for me, let's be a comedy duo! Galen Cauble was a great friend throughout my undergraduate experience. I miss all the wonderful adventures we had around San Luis Obispo. I enjoyed working with Addison Cugini on the Python projects, and I'm thankful for his patience with me as I learned how to program. Langston Johnson was an excellent roommate to have during my last year at Cal Poly. Langston is one of the kindest people I know. In no particular order, I would also like to thank: Austin Mello, Tom Gutierrez, Jeremy Kruger, Ben Knudson, Michelle Carey, Matt Sawyer, Leila Jewell, Dani May, Casey Allard, Nate Padilla, Rebecca Rosen, Keith Gresiak, Rebecca Peters, Anna Kopcrak, Bethany Biscaglio, Jonathan Ward, Mitch Sanders, Grant Olson, and Mark Fagundes.

Back home in Santa Cruz, California, there are several friends and teachers I must acknowledge. Dean Mimmack properly introduced me to physics via the "shut up and calculate" school of thought. I had the honor of attending a class from a high school teacher who had taught physics for around 40 years! We programmed BASIC on Apple II computers and made our own double-slit experiments by depositing soot on a glass slide and using a razor blade to scrape two lines close together. By the end of the two years with Dean, we made it to Feynman diagrams! I've never heard of any other high school students in all my career making it as far as we did. There is a nontrivial amount of physics background I received through Dean, and I'm extremely grateful for it. Robyn Miranda was an excellent English teacher, and I learned how to write well from her. Kevin Chapman has been a great friend for many years. We were always on a similar level when it came to running cross country and gaming. We have had so many great discussions over the years, and it's always effortless to resume where we left off. Georgi Dinolov is another great friend who I enjoyed my high school times with. I definitely do not have enough time to cover all the ridiculous adventures I've been on with Georgi, but I look forward to meeting up in the future. Casidhe Lee was my most hard-working friend in high school. I'm still impressed to this day with the progress he's made in his career. I'm sorry about all the horrible pranks we did to you, Casidhe. Try to forget them as you get older! Erin Warren is a fantastic friend and amusing character who always inadvertently encouraged me to be as honest as possible. Erik Lowe has always been a great friend to share an

interesting new pint with. In no particular order, I would also like to thank: Ari Warren, Janine Honey, Neil Warren, Emi Lowe, Kirby Nichol, Alex Hicken, Ethan McSpadden, Elizabeth Talley, Ethan Edwards, Jack Erickson, Kyle Erickson, Bill Erickson, Lazaro Sandoval, Tyler Burroughs, Mark McConnell, Zack Leland, and Joey Braverman.

My family deserves my deepest gratitude for the incredible amount of support they've given me in my life. I wish my paternal grandparents, John and Anita, could have been here to witness me finish graduate school. Anita always said, "I've got my nickel on you!" Uncle John and aunt Daisy are always fun to see when I'm in Oregon. My grandparents, Steve and Barbara, have been amazingly encouraging. Barbara pushed for me to always do better academically, and Steve's "famous scientist guy" mantra is forever burned into my head. My maternal grandmother, Cathy, is a huge source of love and advice that I've always appreciated. I'm certain many of my genetic traits were inherited from her. My brother, Andy, continues to impress me with his progress in life. I'm now looking up to him flying the MV-22B Osprey for the USMC. I know great things lie ahead for him. I always look forward to catching up with Matt Talley every time I visit home. My mother, Heidi, is an infinite source of patience and love which continues to amaze me to this day. I cannot express in words how grateful I am that she's my mother. My father, Tom, has been the most fundamental driving force for me to make it through graduate school. I remember in elementary school that I wished to earn a Ph.D. This is a result of my father's constant insistence that I push as far as possible through school.

Lastly, I would like to thank Jaimie Stephens for all the support, discussions, and love during my time in graduate school.

## Improving the Readout of Semiconducting Qubits

by

Matthew Jon Curry

B.S., Physics, California Polytechnic State University, 2011M.S., Physics, University of New Mexico, 2013

Ph.D., Physics, University of New Mexico, 2019

#### Abstract

Semiconducting qubits are a promising platform for quantum computers. In particular, silicon spin qubits have made a number of advancements recently including long coherence times [1, 2], high-fidelity single-qubit gates [2, 3], two-qubit gates [4], and high-fidelity readout [5]. However, all operations likely require improvement in fidelity and speed, if possible, to realize a quantum computer.

Readout fidelity and speed, in general, are limited by circuit challenges centered on extracting low signal from a device in a dilution refrigerator connected to room temperature amplifiers by long coaxial cables with relatively high capacitance. Readout fidelity specifically is limited by the time it takes to reliably distinguish qubit states relative to the characteristic decay time of the excited state,  $T_1$ . This dissertation explores the use of heterojunction bipolar transistor (HBT) circuits to amplify the readout signal of silicon spin qubits at cryogenic temperatures. The cryogenic amplification approach has numerous advantages including low implementation overhead, low power relative to the available cooling power, and high signal gain at the mixing chamber stage leading to around a factor of ten speedup in readout time for a similar signal-to-noise ratio. The faster readout time generally increases fidelity, since it is much faster than the  $T_1$  time.

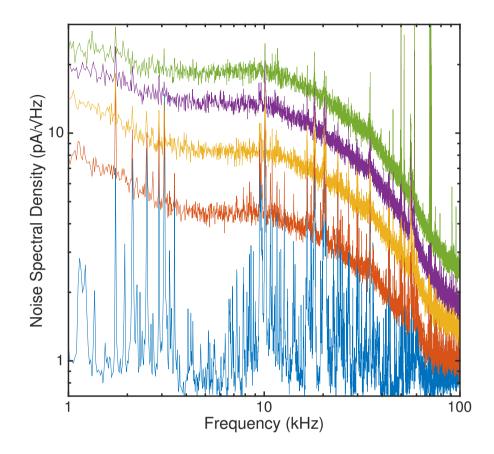

Two HBT amplification circuits have been designed and characterized. One design is a low-power, base-current biased configuration with non-linear gain (CB-HBT), and the second is a linear-gain, AC-coupled configuration (AC-HBT). They can operate at powers of 1 and 10  $\mu$ W, respectfully, and not significantly heat electrons. The noise spectral density referred to the input for both circuits is around 15 to 30 fA/ $\sqrt{\text{Hz}}$ , which is low compared to previous cases such as the dual-stage, ACcoupled HEMT circuit at  $\sim 70$  fA/ $\sqrt{\text{Hz}}$  [6]. Both circuits achieve charge sensitivity between 300 and 400  $\mu e/\sqrt{Hz}$ , which approaches the best alternatives (e.g., RF-SET at ~ 140  $\mu e/\sqrt{Hz}$ ) but with much less implementation overhead. For the singleshot latched charge readout performed, both circuits achieve high-fidelity readout in times < 10  $\mu$ s with bit error rates < 10<sup>-3</sup>, which is a great improvement over previous work at > 70  $\mu$ s [5]. The readout speed-up in principle also reduces the production of errors due to excited state relaxation by a factor of  $\sim 10$ . All of these results are possible with relatively simple, low-power transistor circuits which can be mounted close to the qubit device at the mixing chamber stage of the dilution refrigerator.

| Li            | List of Figures |                              |     |  |  |

|---------------|-----------------|------------------------------|-----|--|--|

| $\mathbf{Li}$ | st of           | Tables                       | xix |  |  |

| $\mathbf{G}$  | lossa           | ry                           | xx  |  |  |

| 1             | Intr            | roduction                    | 1   |  |  |

|               | 1.1             | Motivation                   | 1   |  |  |

|               | 1.2             | Improving Qubit Readout      | 8   |  |  |

|               | 1.3             | Outline                      | 10  |  |  |

| <b>2</b>      | Bac             | kground                      | 12  |  |  |

|               | 2.1             | Semiconducting Devices       | 12  |  |  |

|               | 2.2             | Quantum Dots and Donor Atoms | 18  |  |  |

|               | 2.3             | Singlet-Triplet Qubit        | 34  |  |  |

|               | 2.4             | Cryogenic Amplification      | 40  |  |  |

| 3 | Exp  | Experimental Methods                            |    |  |  |

|---|------|-------------------------------------------------|----|--|--|

|   | 3.1  | Introduction                                    | 46 |  |  |

|   | 3.2  | Tunnel Rate Spectroscopy                        | 47 |  |  |

|   | 3.3  | Electron Temperature                            | 51 |  |  |

|   | 3.4  | Magnetospectroscopy                             | 55 |  |  |

|   | 3.5  | Tunnel Coupling Estimate                        | 59 |  |  |

|   | 3.6  | Latched Charge Readout                          | 63 |  |  |

|   |      |                                                 |    |  |  |

| 4 | Sing | gle-Electron Si-MOS Devices                     | 67 |  |  |

|   | 4.1  | Preface                                         | 67 |  |  |

|   | 4.2  | Introduction                                    | 67 |  |  |

|   | 4.3  | Split Enhancement Gate Tunnel Barrier           | 69 |  |  |

|   | 4.4  | Single-Electron Regime and Tuning Orthogonality | 73 |  |  |

|   | 4.5  | Sample Fabrication                              | 78 |  |  |

|   | 4.6  | Devices and Experimental Parameters             | 80 |  |  |

|   | 4.7  | Tuning Orthogonality                            | 86 |  |  |

|   | 4.8  | Valley Splitting Tuning                         | 88 |  |  |

|   | 4.9  | Conclusion                                      | 91 |  |  |

| 5 | Cha  | aracterization of the CB-HBT at 4 K             | 92 |  |  |

| 5 |      |                                                 |    |  |  |

|   | 5.1  | Preface                                         | 92 |  |  |

|   | 5.2  | Introduction                             |

|---|------|------------------------------------------|

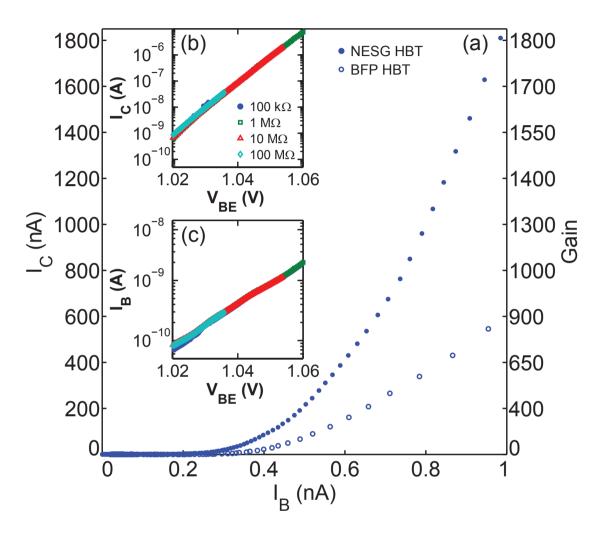

|   | 5.3  | HBT Characterization                     |

|   | 5.4  | Frequency Response                       |

|   | 5.5  | Time Domain Measurements                 |

|   | 5.6  | Conclusion                               |

| 6 | HB   | Γ Circuit Comparison 106                 |

|   | 6.1  | Introduction                             |

|   | 6.2  | AC-HBT Description                       |

|   | 6.3  | CB-HBT Description                       |

|   | 6.4  | Amplifier Performance Comparison         |

|   | 6.5  | Single-Shot Results Comparison           |

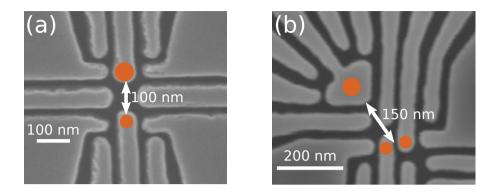

|   | 6.6  | SET Geometries And Details               |

|   | 6.7  | Current-Biasing Effect of CB-HBT Circuit |

|   | 6.8  | Electron Temperature Measurement         |

|   | 6.9  | HBT Characterization                     |

|   | 6.10 | CB-HBT Small Signal Gain                 |

|   | 6.11 | Noise Models                             |

|   | 6.12 | AC-HBT Bias Tee Parameters               |

|   | 6.13 | CB-HBT Circuit Effective Gain Method     |

|   | 6.14 | Conclusion                               |

| 7            | Conclusion |                    |     |

|--------------|------------|--------------------|-----|

|              | 7.1        | Summary of Results | 135 |

|              | 7.2        | Outlook            | 137 |

| $\mathbf{A}$ | HB'        | T Background       | 139 |

| Re           | efere      | nces               | 145 |

# List of Figures

| 1.1  | UNM Punch Card                                    | 2  |

|------|---------------------------------------------------|----|

| 1.2  | Prevailing Quantum Computing Architectures (2018) | 5  |

| 2.1  | MOSFET Schematic and Band Diagrams                | 14 |

| 2.2  | Si-MOS Nanostructure SEM Image                    | 16 |

| 2.3  | Si-MOS 3D Model Complete Device                   | 17 |

| 2.4  | Si-MOS 3D Model Sliced Device                     | 20 |

| 2.5  | MOS Quantum Dot and Donor Atom System             | 21 |

| 2.6  | Si-MOS QD and Donor Potentials                    | 22 |

| 2.7  | Occupancy Probability                             | 24 |

| 2.8  | Coulomb Blockade                                  | 25 |

| 2.9  | Coulomb Diamonds                                  | 27 |

| 2.10 | Charge Sensor Top View                            | 29 |

| 2.11 | Charge Sensing Schematic                          | 30 |

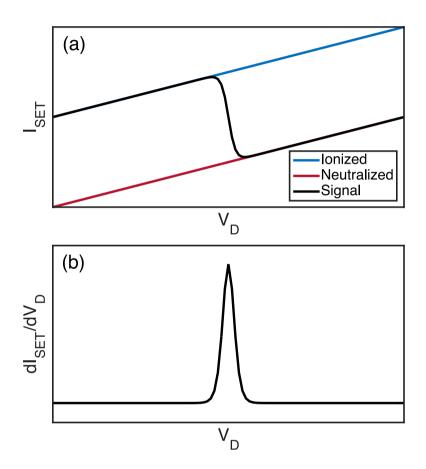

| 2.12 | Charge Sensing Signal                             | 31 |

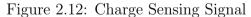

| 2.13 | Stability Diagrams                                      | 34 |

|------|---------------------------------------------------------|----|

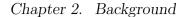

| 2.14 | Singlet-Triplet Qubit Energy Diagram                    | 36 |

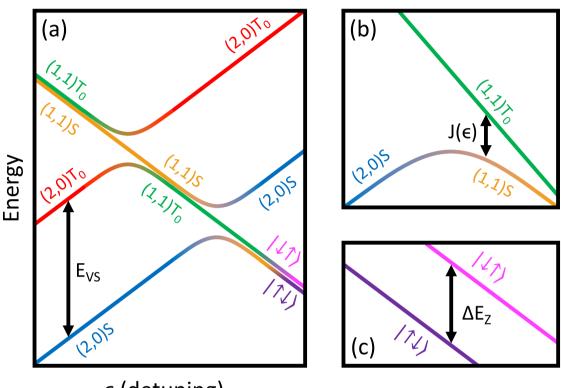

| 2.15 | Singlet-Triplet Qubit Operation and Readout             | 37 |

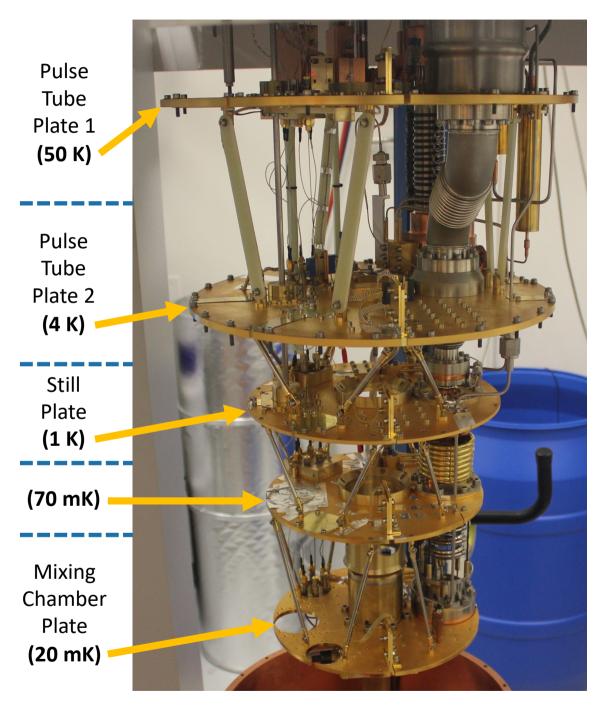

| 2.16 | Inside of Dilution Refrigerator                         | 42 |

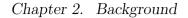

| 2.17 | Cryogenic Amplification                                 | 44 |

| 2.18 | Noise Dependence on Gain                                | 45 |

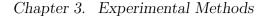

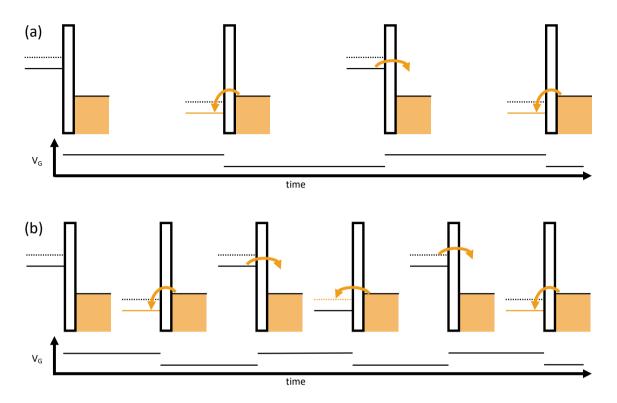

| 3.1  | Tunnel Rate Spectroscopy Example                        | 48 |

| 3.2  | Tunnel Rate Spectroscopy: Higher Frequency              | 49 |

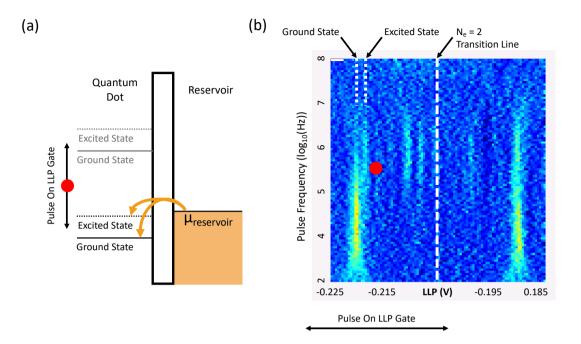

| 3.3  | Electrostatic Gate Bias Tee Schematic                   | 52 |

| 3.4  | Electron Temperature Extraction                         | 54 |

| 3.5  | Magnetospectroscopy Model                               | 56 |

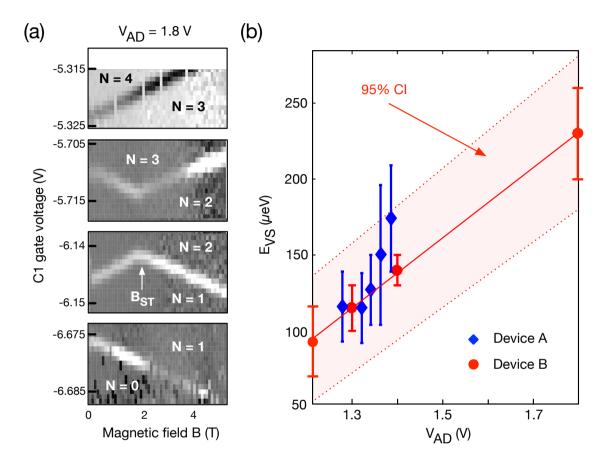

| 3.6  | Magnetospectroscopy Data                                | 57 |

| 3.7  | Tunnel Coupling Measurement Diagram                     | 60 |

| 3.8  | Tunnel Coupling Measurement Data                        | 61 |

| 3.9  | Latched Charge Readout                                  | 64 |

| 3.10 | Latched Charge Readout Single-Shot                      | 65 |

| 4.1  | Single-Lead Device Schematic and Model                  | 70 |

| 4.2  | Single-Lead Device Stability Diagram and Tunnel Rates   | 72 |

| 4.3  | Double-Lead Device Schematic and Occupancy Measurements | 76 |

### List of Figures

| 4.4  | Single-Lead Device Single-Electron Stability Diagrams               |

|------|---------------------------------------------------------------------|

| 4.5  | Double-Lead Device Magnetospectroscopy and Valley Splitting 90      |

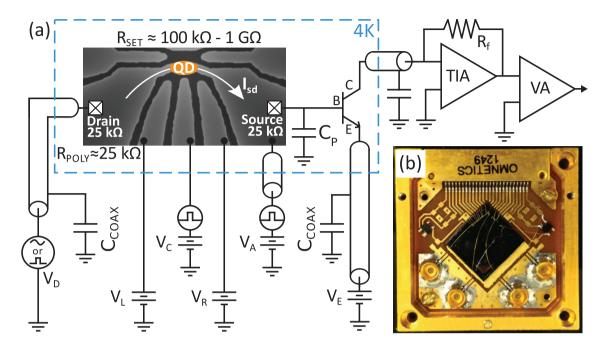

| 5.1  | HBT-SET Circuit                                                     |

| 5.2  | HBT Biasing Calibration Curves at 4 K                               |

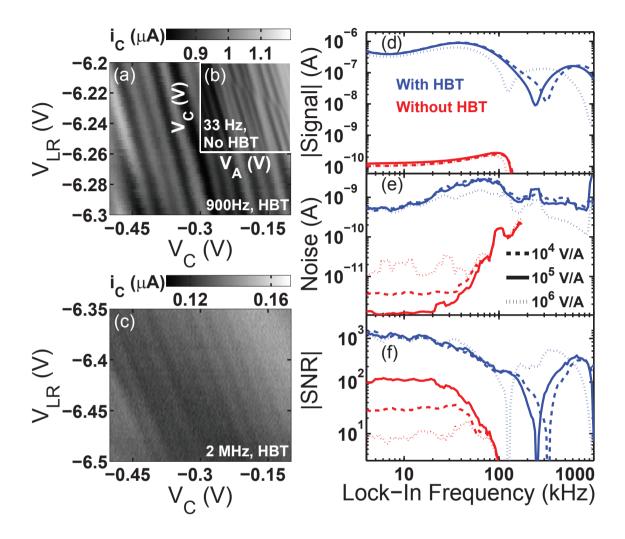

| 5.3  | HBT-SET Stability Plots and Frequency Domain Data 99                |

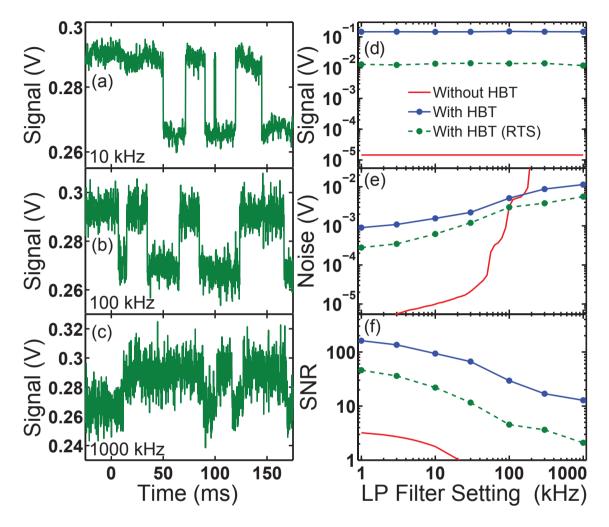

| 5.4  | HBT-SET RTS Readout Traces with Signal, Noise, and SNR $\ .$ 102    |

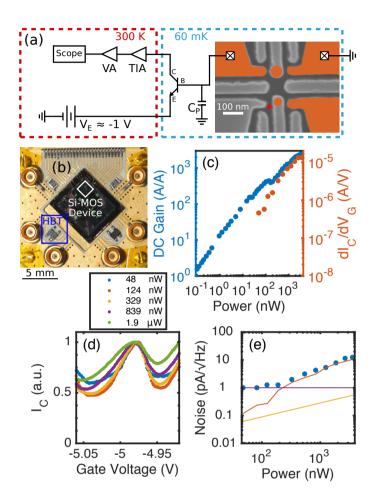

| 6.1  | AC-HBT Schematic and Measurements                                   |

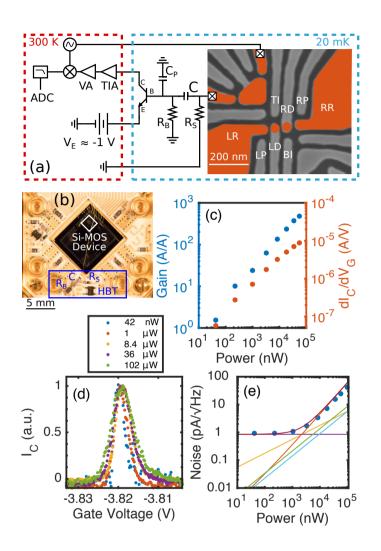

| 6.2  | CB-HBT Schematic and Measurements                                   |

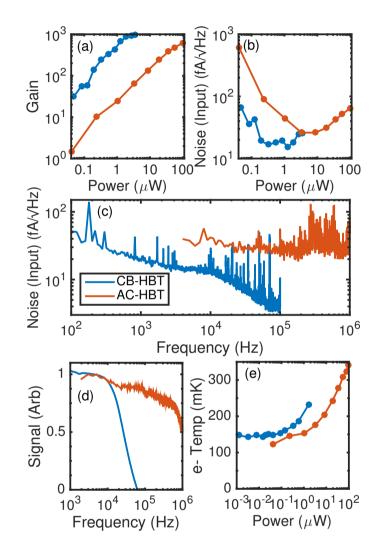

| 6.3  | HBT Amplifier Performance Comparison                                |

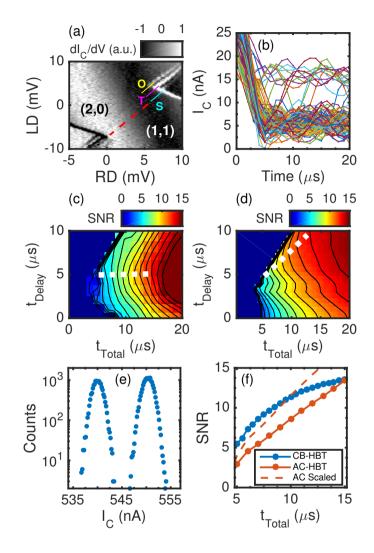

| 6.4  | Single-Shot Results Comparison                                      |

| 6.5  | SET Geometry Comparison                                             |

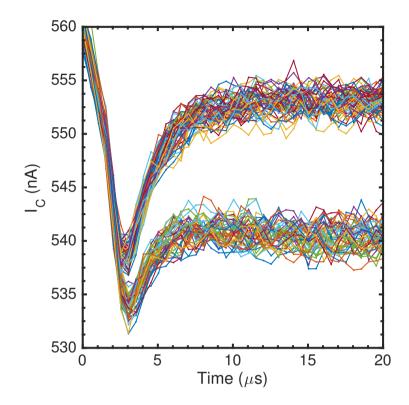

| 6.6  | CB-HBT Single-Shot Readout Traces                                   |

| 6.7  | Current-Biasing Effect Model                                        |

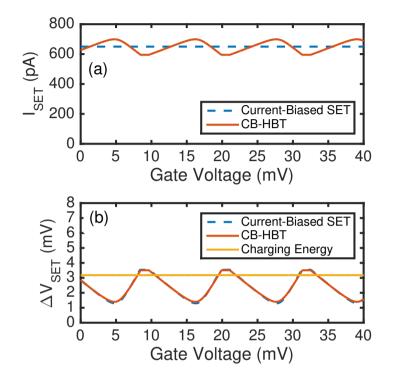

| 6.8  | Current Biasing Effect Signal and Sensitivity Comparison 123        |

| 6.9  | Electron Temperature Comparison                                     |

| 6.10 | HBT DC Characterization                                             |

| 6.11 | Transconductance of HBT With and Without SET Connected $\ldots$ 128 |

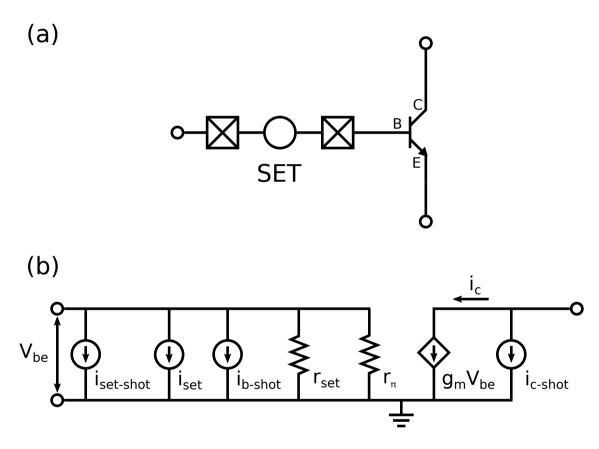

| 6.12 | CB-HBT Circuit Model                                                |

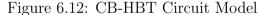

| 6.13 | AC-HBT Circuit Model                                                |

### List of Figures

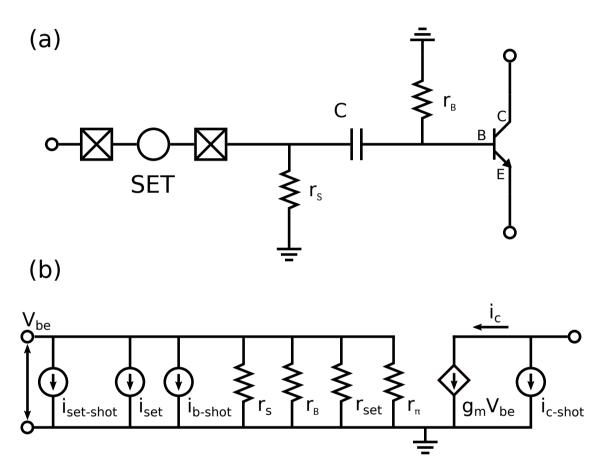

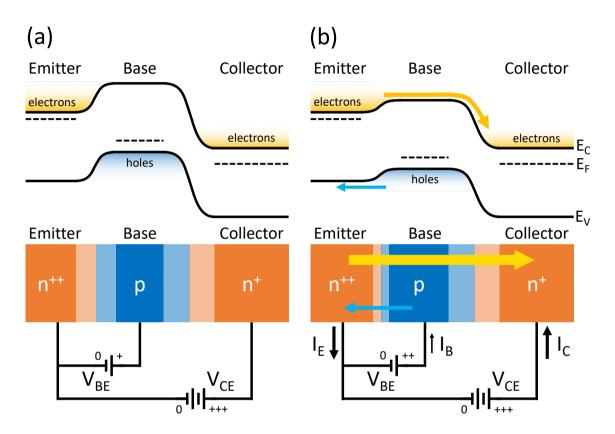

| A.1 | BJT Operation             | 140 |

|-----|---------------------------|-----|

| A.2 | BJT and HBT Band Diagrams | 141 |

| A.3 | Decapped HBT              | 144 |

## List of Tables

| 1.1 | Qubit Coherence Times (2018)               | 6  |

|-----|--------------------------------------------|----|

| 1.2 | Qubit Readout Error Rates (2018)           | 9  |

| 2.1 | Single-Shot Readout Techniques (2018)      | 41 |

| 4.1 | Measured Device Characteristics            | 81 |

| 4.2 | Single-Lead Device Experimental Parameters | 82 |

| 4.3 | Double-Lead Device Experimental Parameters | 83 |

| <sup>28</sup> Si | Silicon Isotope (Mass Number $= 28$ )                |

|------------------|------------------------------------------------------|

| <sup>29</sup> Si | Silicon Isotope (Mass Number $= 29$ )                |

| 2DEG             | Two-Dimensional Electron Gas                         |

| <sup>31</sup> P  | Phosphorus Isotope (Mass Number $= 31$ )             |

| AC               | Alternating Current                                  |

| AC-HBT           | AC-Coupled Heterojunction Bipolar Transistor Circuit |

| Al               | Aluminum                                             |

| AlGaAs           | Aluminum Gallium Arsenide                            |

| As               | Arsenic                                              |

| BASIC            | Beginner's All-Purpose Symbolic Instruction Code     |

| BER              | Bit Error Rate                                       |

| Bit              | Binary Digit                                         |

| BJT              | Bipolar Junction Transistor                          |

| BW               | Bandwidth                                            |

| CB-HBT          | Current-Biased Heterojunction Bipolar Transistor Circuit |

|-----------------|----------------------------------------------------------|

| CdS             | Cadmium Sulfide                                          |

| $\mathrm{CF}_4$ | Tetrafluoromethane                                       |

| CINT            | Center For Integrated Nanotechnologies                   |

| CMOS            | Complementary Metal-Oxide-Semiconductor                  |

| CMP             | Chemical Mechanical Polishing                            |

| CVD             | Chemical Vapor Deposition                                |

| DC              | Direct Current                                           |

| DCE             | Dichloroethene                                           |

| DR              | Dilution Refrigerator                                    |

| e               | Electron Charge $(1.602 \cdot 10^{-19} \text{ C})$       |

| EBL             | Electron-Beam Lithography                                |

| ENIAC           | Electronic Numerical Integrator and Computer             |

| FET             | Field-Effect Transistor                                  |

| GaAs            | Gallium Arsenide                                         |

| h               | Planck Constant $(4.14 \cdot 10^{-9} \ \mu eV \cdot s)$  |

| HBr             | Hydrogen Bromide                                         |

| HBT             | Heterojunction Bipolar Transistor                        |

| HBT-SET         | Antiquated Name For CB-HBT                               |

| HEMT    | High-Electron-Mobility Transistor                     |

|---------|-------------------------------------------------------|

| IBM     | International Business Machines                       |

| IC      | Integrated Circuit                                    |

| JPA     | Josephson Parametric Amplifier                        |

| $k_B$   | Boltzmann Constant (86.17 $\mu {\rm eV/K})$           |

| LC      | Inductor Capacitor                                    |

| LHe     | Liquid Helium                                         |

| MC      | Mixing Chamber                                        |

| $m_e$   | Electron Rest Mass $(9.11 \cdot 10^{-31} \text{ kg})$ |

| MITS    | Micro Instrumentation and Telemetry Systems           |

| MOS     | Metal-Oxide-Semiconductor                             |

| MOSFET  | Metal-Oxide-Semiconductor Field-Effect Transistor     |

| $N_2$   | Nitrogen Gas                                          |

| NV      | Nitrogen-Vacancy                                      |

| $O_2$   | Oxygen Gas                                            |

| OFIG    | Only Found In Glossary                                |

| PCB     | Printed Circuit Board                                 |

| Poly-Si | Polycrystalline silicon                               |

| PTR     | Pulse Tube Refrigerator                               |

| QD                                     | Quantum Dot                                                                                   |

|----------------------------------------|-----------------------------------------------------------------------------------------------|

| QPC                                    | Quantum Point Contact                                                                         |

| Qubit                                  | Quantum Bit                                                                                   |

| RF                                     | Radio Frequency                                                                               |

| RMS                                    | Root Mean Square                                                                              |

| RT                                     | Room Temperature                                                                              |

| RTS                                    | Random Telegraph Signal                                                                       |

| SEM                                    | Scanning Electron Microscope                                                                  |

| SET                                    | Single-Electron Transistor                                                                    |

| Si                                     | Silicon                                                                                       |

| Si-MOS                                 | Silicon Metal-Oxide-Semiconductor                                                             |

| $\mathrm{Si}_3\mathrm{N}_4$            | Silicon Nitride                                                                               |

| -014                                   | Shicon Withde                                                                                 |

| SiGe                                   | Silicon Germanium                                                                             |

|                                        |                                                                                               |

| SiGe                                   | Silicon Germanium                                                                             |

| SiGe<br>SiO <sub>2</sub>               | Silicon Germanium<br>Silicon Dioxide                                                          |

| SiGe<br>SiO <sub>2</sub><br>SNL        | Silicon Germanium<br>Silicon Dioxide<br>Sandia National Laboratories                          |

| SiGe<br>SiO <sub>2</sub><br>SNL<br>SNR | Silicon Germanium<br>Silicon Dioxide<br>Sandia National Laboratories<br>Signal-To-Noise Ratio |

| $T_2$    | Dephasing Time Measured Using Spin Echo             |

|----------|-----------------------------------------------------|

| $T_2^*$  | Dephasing Time Measured Using Ramsey Interferometry |

| TEM      | Transmission Electron Microscopy                    |

| TEOS     | Tetraethoxysilane                                   |

| Ti       | Titanium                                            |

| TIA      | Transimpedance Amplifier                            |

| TiN      | Titanium Nitride                                    |

| TLA      | Three-Letter Acronym                                |

| Transmon | Transmission Line Shunted Plasma Oscillation Qubit  |

| UNM      | University of New Mexico                            |

| W        | Tungsten                                            |

## Chapter 1

## Introduction

### 1.1 Motivation

Humans have been generating, processing, and storing information for thousands of years. The rate at which this occurs is increasing exponentially over time with different eras marked by major technological advances. Beginning with the Sumerian abacus around 2500 BC, humans began encoding and processing numbers as large as 10 billion on a device which used sliding beads. In the 1620s, the slide rule was invented, which allowed calculations to be performed much faster than on an abacus. Shortly after the invention of the slide rule, mechanical calculators were created by several individuals including the mathematician, Gottfried Leibniz. Mechanical calculators were eventually made portable and were not directly replaced until the 20<sup>th</sup> century. In 1804, Joseph-Marie Jacquard invented a loom which used punch cards to store the pattern intended to be woven. This invention laid the foundation for computers storing and processing information via punch cards, which were used well into the 20<sup>th</sup> century. An example of an IBM punch card used at the University of New Mexico in the 1970s can be seen in Figure 1.1. The first programmable com-

Figure 1.1: UNM Punch Card

Punch card from The University of New Mexico Computing Center circa 1970. This storage medium is capable of encoding up to 960 bits per punch card. The pictured punch card represents one line of code instructing the computer to "GO TO 102" and execute the code found at line 102, which is the 102<sup>nd</sup> punch card in the program. The code is printed at the top left region of the punch card, albeit slightly faded.

puter was proposed in 1837 by Charles Babbage. This computer was known as the "analytical engine" and was designed to be completely mechanical and hand cranked, however, it was never constructed. The first analog computers were developed and used in the late 19<sup>th</sup> century to solve specific problems by using a continuously changing physical property. For example, a type of mechanical analog computer known as a "differential analyzer" could use integration to solve differential equations via rotating disks.

The development of the first digital, electronic computers occurred around the time of World War II, with the general idea formulated by Alan Turing in 1937 [7]. These early digital computers were first created using electromechanical relays. Eventually, the electromechanical relay computers were replaced by vacuum tube computers, which were purely electronic in operation. An example of an early vacuum tube tube computer is the Electronic Numerical Integrator and Computer (ENIAC), which

was built in 1945 at the University of Pennsylvania and contained over 20,000 vacuum tubes and around 5,000,000 connections soldered by hand. The ENIAC used punch cards to store information and it was originally designed to compute artillery firing tables, but it actually first computed the feasibility of thermonuclear weapons.

The development of the transistor in 1947 resulted in a highly disruptive advancement for computers. Instead of macroscopic, power-inefficient, and relatively unreliable glass tubes, there were now solid, microscopic, power-efficient, reliable components. Previously taking up the area of a large room, computers could now fit in a much smaller area the size of an office. Eventually, the integrated circuit (IC) was developed in the late 1950s and many transistors could now be fabricated on the same piece of semiconducting material. Using the integrated circuit concept, Intel created the first microprocessor, the Intel 4004, in 1971. The microprocessor contained most of the hardware necessary to build a computer in a component smaller than a single vacuum tube. Computers became far more affordable for individuals to purchase leading to the first commercially successful personal computer, the MITS Altair 8800, being created in Albuquerque, New Mexico in 1975. The success of the Altair 8800 attracted Bill Gates and Paul Allen to found Microsoft in Albuquerque and develop a BASIC programming language interpreter for the Altair 8800. Over the next few decades, computers became smaller, more powerful, and more affordable. Recently developed system on chip (SoC) integrated circuits contain all components required for a computer and enable highly-portable, power-efficient computers such as smartphones. Through more precise fabrication, the number of transistors on an integrated circuit has been roughly doubling every two years [8], however, the transistors will eventually reach hard, physical limits when shrunk to near the atomic scale. Increasing the performance of computers by shrinking the transistors will eventually no longer be viable. Fortunately, another paradigm for computing exists.

The technological advancements covered so far have focused on a form of computation now known as "classical computing." For classical computers, the basic unit of information is a bit, which can encode one of two values (e.g., 1 or 0, true or false, on or off, punched or unpunched). This dissertation focuses on a new form of computation: quantum computation. Quantum computation differs from classical computation by taking advantage of the effects of quantum mechanics such as entanglement and superposition. Instead of bits, quantum computers use quantum bits or "qubits," which are quantum-mechanical two-level systems (e.g., an electron spin state in a magnetic field). Qubits can encode two values similarly to a bit, however, they can also be in a coherent superposition of both values (e.g.,  $\frac{1}{\sqrt{2}}[|0\rangle + |1\rangle]$ ). The idea for quantum computing began in the early 1980s from physicists such as Paul Benioff and Richard Feynman [9-11]. One of the early motivations for quantum computing was the apparent difficulty in simulating quantum systems efficiently with classical computers, therefore direct control of a quantum system would be advantageous for simulation. In 1994, Peter Shor proved that a quantum computer could factorize integers in polynomial time, where the number of steps required to factorize an integer, N, grows at a rate roughly proportional to  $\log(N)$  [12]. This result was highly disruptive to the field of cryptography, where many techniques for protecting sensitive information rely on the notion that classical computers are only known to be able to factor integers in exponential time, where the number of steps for factorization grows at a rate roughly proportional to  $e^N$ . If N is large enough (e.g.,  $N = 2^{4096}$ ), then the number of steps required  $(e^{2^{4096}})$  will be on an enormous scale where the factorization effectively becomes impossible. Another advantage of quantum computers is secure communication using quantum entanglement, which is of particular importance for preventing interception of sensitive information [13]. Efficient simulation of chemical reactions is an application of quantum computing which may lead to major chemical breakthroughs. For example, around 2% of the world's energy is used on the Haber-Bosch process, the current method for producing

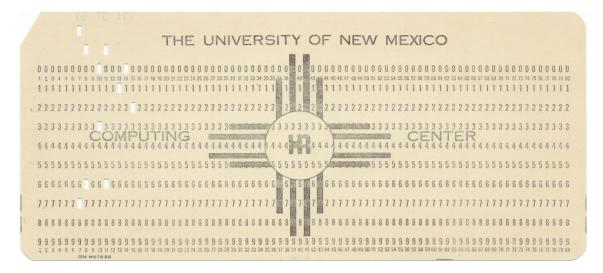

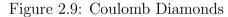

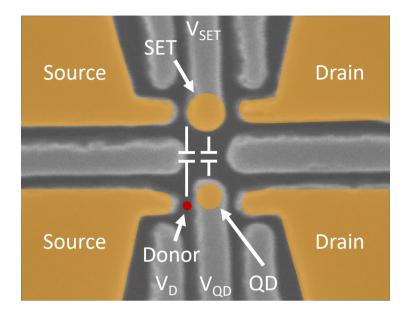

Figure 1.2: Prevailing Quantum Computing Architectures (2018) Example images of the currently prevailing quantum computing architectures as of 2018. (a) Optical image of two superconducting transmon qubits (image credit [15]). The "+" pattern is the relatively large shunting capacitor used to suppress charge noise. (b) SEM image of part of the second-generation Sandia high optical access trap for trapped-ion qubits (image credit [16]). The ions are typically trapped several micrometers apart in these systems. (c) SEM image of Sandia Si-MOS quantum-dot and donor atom qubit device. This dissertation will focus on this type of device.

nitrogen fertilizer. This process requires relatively high temperatures and pressures ( $\sim 20$  MPa and  $\sim 500$  °C), whereas plants extract fertilizer out of atmospheric pressure air at room temperature. The mechanism plants use to do this is not currently understood, however, quantum simulation of the chemicals involved could reveal the underlying mechanism and enable enormous amounts of energy saving [14].

As of 2018, fruitful quantum computers remain a challenge to realize. Just as classical computers had many different early forms (e.g., vacuum tubes and electromechanical switches), quantum computers have several prevailing physical architectures. These qubit architectures include: semiconducting, superconducting, trapped ion, and nitrogen-vacancy (NV) centers. Semiconducting qubits generally use quantum dots or donor atoms to encode qubits on the spin states of the occupy-ing electrons [4, 17–22]. Superconducting qubits are typically made out of aluminum with one or two Josephson junctions connected in parallel to a large shunting capacitor ("+" pattern in Figure 1.2(a)) [15, 23–25]. This type of qubit is known as

| Architecture    | $T_1$              | $T_2$           |

|-----------------|--------------------|-----------------|

| Semiconducting  | > 10,000  s [1]    | > 10,000  s [1] |

| Trapped Ion     | > 4000  s [35]     | > 50  s [35]    |

| NV Center       | 15 s [ <b>34</b> ] | > 1 s [32]      |

| Superconducting | 0.0001 s [25]      | 0.0001 s [25]   |

Table 1.1: Qubit Coherence Times (2018)

Longest observed qubit coherence times for currently prevailing quantum computing architectures as of 2018. The effective  $T_1$  time for trapped ion qubits is limited by the trap lifetime (the intrinsic  $T_1$  time for the trapped ion hyperfine qubits is actually greater than 1,000,000 years). Most numbers shown are approximate values.

a "transmon," and it is analogous to a resonant LC circuit where the linear inductor is replaced with a Josephson junction to create an anharmonic oscillator. While semiconducting and superconducting qubits generally require cryogenic operation ( $\leq$ 100 mK), the trapped-ion and NV center qubits can be operated at room temperature. Trapped ion qubits are created by using a combination of static and oscillating electric fields to form a rotating saddle potential that a single ion cannot escape from [26]. Figure 1.2(b) shows part of an ion trap made on a surface where the ions are shuttled around with electrodes and interact through collective quantized motion [16, 27–30]. NV center qubits are made out of point defects in a diamond lattice, where a neighboring nitrogen atom and a lattice vacancy form a multi-electron system that is controlled optically [31–34].

All quantum computer architectures must satisfy general criteria in order to be a viable candidate for quantum computing. The criteria were originally outlined by David DiVincenzo in 2000 [36] and consist of five main categories:

1. Initialization: Reliable initialization of the qubits to the ground state in a quantum computer is critical to achieve. Each of the current, prevailing quantum computer architectures has a different way to initialize the qubit into the ground state,  $|0\rangle$ . For example, trapped ion quantum computers use a laser

that is focused on the ion at an energy which couples the excited state,  $|1\rangle$ , to higher energy excited states which then decay to the ground state or back to the excited state. When the higher energy states decay, visible light is emitted. The laser only couples the excited state to higher energy excited states, so when the ion is in the ground state, it remains in the ground state and no more light is emitted [30]. For superconducting qubits such as the transmon, the excited state decay is relatively fast (~ 100  $\mu$ s). The protocol is to simply wait for a period of time which is long relative to the decay time and verify that the qubit is in the ground state before performing computations. For semiconducting qubits, the rate at which electrons tunnel back and forth from an electron reservoir to a quantum dot is important for reliable initialization and is covered in Section 3.2.

- 2. *Control*: The ability to perform rotations of the qubit state about the Bloch sphere and conditional rotations which depend on the state of a second qubit is critical for achieving a universal digital quantum computer. The control of the type of semiconducting qubit covered in this dissertation is outlined in Section 2.3.

- 3. Coherence: The lifetime of the excited state, T<sub>1</sub>, and the dephasing time, T<sub>2</sub>, are two timescales that must be long relative to the amount of time the qubit state rotations require. Table 1.1 shows the difference in the longest absolute coherence times for each prevailing quantum computer architecture. Semiconducting qubits can in principle take advantage of the nuclear spins of ionized donor atoms in <sup>28</sup>Si to achieve long absolute coherence times.

- 4. Readout: Different quantum computing architectures use different methods to measure the state of the qubit. For example, in trapped ion quantum computers, the ion will have laser light directed at it such that the excited state will fluoresce and the ground state will not [30]. Superconducting transmon qubits

use a capacitively coupled microwave resonator which changes the phase of the readout signal depending on the state of the qubit [23]. For semiconducting qubits, the readout is usually performed using a charge sensor, and the readout is covered in Sections 2.3 and 3.6. Table 1.2 shows the lowest readout error rates achieved for each of the prevailing quantum computing architectures.

5. Scalability: Since fruitful quantum computers will require many qubits, systemwide operation must remain possible as the number of qubits is increased. In general, the control and readout apparatuses must be able to address multiple qubits, otherwise, the number of apparatuses will increase directly with the number of qubits. The qubits must also be able to remain coupled together quantum mechanically to some degree as qubit number increases. The physical size of the qubits is another factor that is a concern for scalability. For example, Figure 1.2 shows three different quantum computing architecture candidates with dramatically different length scales. The superconducting qubits are relatively large at the hundreds of micrometer scale. The trapped ion and NV center qubits are spaced several micrometers apart on average, and the control electrodes for trapped ions are at the tens of micrometer scale. Semiconducting qubits are relatively small and can be spaced tens of nanometers apart.

### **1.2 Improving Qubit Readout**

This dissertation is about improving the readout fidelity of semiconducting qubits. The readout fidelity typically depends on the time it takes to measure the qubit's quantum state. Once the quantum state is projected on to the basis intended for measurement, the probability that the excited state will decay to the ground state is,

$$P_{\text{decay}} = e^{(-t_{\text{meas}}/T_1)},\tag{1.1}$$

| Architecture    | Readout Error Rate       | Measurement Time     |

|-----------------|--------------------------|----------------------|

| Semiconducting  | $1.4 \cdot 10^{-3}$ [5]  | $70 \ \mu s \ [5]$   |

| Trapped Ion     | $1 \cdot 10^{-3} [38]$   | 400 µs [ <b>3</b> 8] |

| NV Center       | $4.5 \cdot 10^{-2} [34]$ | 200 ms [ <b>34</b> ] |

| Superconducting | $8 \cdot 10^{-3}$ [24]   | 90 ns [24]           |

Table 1.2: Qubit Readout Error Rates (2018)

Lowest readout error rates for currently prevailing quantum computing architectures as of 2018. Measurement times to achieve the error rates are listed in addition. Most numbers shown are approximate values.

where  $T_1$  is the characteristic decay time of the excited state, and  $t_{\text{meas}}$  is the time starting at the beginning of the readout process. This probability is proportional to the fidelity of the readout, therefore, the readout error rate is given by,

$$\Gamma_{\rm error} = 1 - e^{(-t_{\rm meas}/T_1)} \approx \frac{t_{\rm meas}}{T_1},\tag{1.2}$$

where decreases in  $t_{\text{meas}}$  will directly decrease the readout error rate relative to T<sub>1</sub>. Using a readout technique known as "latched readout" and the right balance of tunnel rates (Sections 2.3 and 3.6), the T<sub>1</sub> time during readout can effectively become ~ 10 ms [5]. An important threshold to reach for fault-tolerant quantum computation is error rates less than  $1 \cdot 10^{-3}$  [37]. In order for the readout error rate to be reduced to  $< 1 \cdot 10^{-3}$ , the measurement time must take no longer than ~ 10  $\mu$ s. In previous work, the readout time was limited to > 70  $\mu$ s (see "Semiconducting" section of Table 1.2). Therefore, it is necessary to improve the readout time (i.e., same SNR for faster integration time) to reach fault tolerant operation.

Typical approaches for improving readout include using amplification to increase the signal-to-noise ratio (SNR) and therefore decrease the integration time it takes to achieve a certain SNR. Since semiconducting qubits are operated at cryogenic temperatures in dilution refrigerators, there are nontrivial constraints placed on the amplification possibilities. Common amplifiers such as a transimpedance amplifier (TIA) do not necessarily work at cryogenic temperatures and will dissipate more

energy than the dilution refrigerator can remove while maintaining low temperatures. Certain transistors have been shown to operate at the cryogenic temperatures required for qubit operation (Section 2.4 and Chapter 5). One such transistor is known as a "heterojunction bipolar transistor" (HBT) and can provide signal gain as high as ~ 1,000 at powers as low as ~ 1  $\mu$ w, which allows the dilution refrigerator to maintain cryogenic temperatures.

Two HBT amplification circuits have been designed and used to decrease the measurement time for semiconducting qubit readout. These circuits and the results are covered in Chapter 6. The key result is that for both amplification circuits, the measurement time has been reduced to less than 10  $\mu$ s.

### 1.3 Outline

This dissertation is organized into five main chapters. In Chapter 2, background material is covered for the specific semiconducting qubits used in this work. The chapter begins with a discussion on semiconducting devices in general, starting with the MOSFET device. Then quantum dots are defined and their formation is covered. Measurements specific to quantum dots are shown with example data. Next, the specific semiconducting qubit used in this work, the "singlet-triplet qubit," is described along with its operation and measurement. Finally, a review of the current semiconducting readout techniques is done with the focus on cryogenic amplification and its benefits. Chapter 3 covers the experimental methods used to tune and operate the singlet-triplet qubits. This includes tuning the tunnel rate for reliable qubit initialization, minimizing electron temperature, verifying the energy scales via magnetospectroscopy, tuning the tunnel coupling, and performing readout to characterize cryogenic amplification benefits. Chapter 4 focuses on the Si-MOS devices fabricated at Sandia National Laboratories for improving the single-electron regime

achievability and tunability. Simulations of the devices were a contribution of this dissertation work to the resulting paper described in Chapter 4. The simulations helped verify the tuning orthogonality between the quantum dot occupancy and the tunnel rate. Chapter 5 shows the initial results from characterizing the CB-HBT connected to a charge sensor at 4 K. The amplifier was characterized by increasing the frequency of the input signals as well as monitoring random telegraph signal as the bandwidth of the room temperature amplifier was increased. Finally, in Chapter 6, the two HBT amplification circuits are characterized by performing single-shot latched charge readout. The chapter starts by describing the differences between the two circuits, with the AC-HBT being designed and measured by coworkers at SNL. Then, a comparison of noise, bandwidth, power, and electron temperature is done to highlight the performance differences between the two circuits. Finally, a double quantum dot is tuned to few electrons and single-shot latched charge readout results from the CB-HBT are compared to the AC-HBT case. Both circuits are able to perform high-fidelity readout with measurement times less than 10  $\mu$ s, however, the CB-HBT operates at lower power.

# Chapter 2

# Background

## 2.1 Semiconducting Devices

Semiconducting devices are ubiquitous in the developed world. Whether used as a simple switch, amplifier, or even in a microprocessor, semiconducting transistors form much of the foundation of the information age. A transistor can be described simply as a device which has one input terminal to control the conductance between two other input/output terminals completely electronically. Originally, vacuum tube technology was used to amplify "feeble" electric signals beginning with Lee De Forest's 1907 triode tube invention, but there were several limitations including size, cost, and lifetime. Vacuum tube amplifiers were eventually replaced by semiconducting transistors in the middle of the 20<sup>th</sup>century. The semiconducting transistor was first patented by Julius Lilienfeld in 1925 and then later fully theorized and developed by William Shockley, Walter Brattain, and John Bardeen at Bell Labs in 1947 [39]. Since its creation, the semiconductor industry has expanded exponentially, with sales totaling \$412,000,000,000 in 2017 [40].

The first transistor invented at Bell Labs was essentially a bipolar-junction tran-

sistor (BJT) (see Appendix A). Since the first transistor, many other transistor architectures have been created including: heterojunction-bipolar transistors (HBTs), insulated-gate-bipolar transistors (IGBTs), avalanche transistors, Schottky transistors, field-effect transistors (FETs), metal-oxide-semiconductor field-effect transistors (MOSFETs), junction gate field-effect transistors (JFETs), metal-semiconductor field-effect transistors (MESFETs), fin field-effect transistors (FinFETs), organic field-effect transistors (OFETs), floating-gate transistors, deoxyribonucleic acid fieldeffect transistors (DNAFETs), carbon nanotube field-effect transistors (CNFETs), high-electron-mobility transistors (HEMTs), and numerous others. In this section, the focus is on how metal-oxide-semiconductor field-effect transistors (MOSFETs) operate and are fabricated.

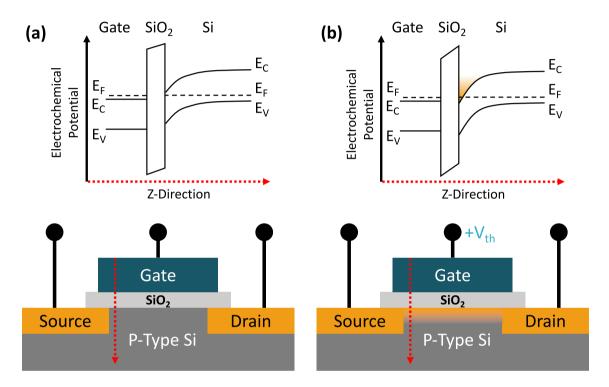

MOSFET devices are typically made up of three material layers and have three input/output terminals. Figure 2.1(a) shows a schematic cross-section of a conventional MOSFET, where the gate is an electrically conductive input which generates an electric field below it in the p-type silicon substrate. By adjusting the voltage on the gate, the electric field will change the energy of the conduction band and valence band edges in the silicon substrate. In an enhancement mode device, a positive voltage on the gate will decrease the energy of the conduction band edge until it is at or below the Fermi level (average energy to add an electron to the silicon substrate). In Figure 2.1(b), when the Fermi level of the electrons is above the conduction band edge in the region below the gate, the silicon substrate becomes conducting. Therefore, current will flow if a voltage bias is placed across the source and drain ohmic contacts. When the gate voltage is sufficiently high and the MOSFET is in saturation mode, the amount of current for a given gate voltage is,

$$I_{\rm SD}(V_G) \approx \frac{\mu_n C_{\rm oxide}}{2} \frac{W_{\rm G}}{L_{\rm G}} \left( V_{\rm G} - V_{\rm th} \right)^2, \qquad (2.1)$$

where  $I_{SD}$  is the source-drain current,  $\mu_n$  is the charge-carrier mobility,  $C_{oxide}$  is the gate oxide capacitance per area,  $W_G$  is the width of the gate,  $L_G$  is the length of the

Figure 2.1: MOSFET Schematic and Band Diagrams

(a) Metal-oxide-semiconductor field-effect-transistor (MOSFET) basic schematic and band diagram pertaining to zero voltage bias on the gate. The band diagram direction corresponds to the red dashed line going from the top of the gate into the p-type silicon substrate. Electrons with energy in the conduction band are represented by orange coloration. Connections to the MOSFET are shown as black lines with black circles on the ends (connection leads). (b) MOSFET basic schematic and band diagram pertaining to large enough voltage bias on the gate to enhance a conducting channel between the source and drain.

gate,  $V_G$  is the gate voltage, and  $V_{th}$  is the threshold voltage.

MOSFETs are fabricated using several different methods. One method is to start with bulk silicon and grow a silicon dioxide  $(SiO_2)$  layer on top (around 5–100 nm thick) by subjecting the silicon to high temperatures. Next, heavily-doped, n-type polycrystalline silicon (polysilicon) is deposited on top of the silicon dioxide and etched into the shape of the gate. Regions of the oxide on either side of the gate are etched away and the silicon substrate underneath is doped with donors to create n-type regions (the source and drain regions). Finally, metal is deposited on to the surface and etched away such that only the source and drain regions have metal channels leading to them to form ohmic contacts.

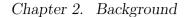

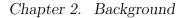

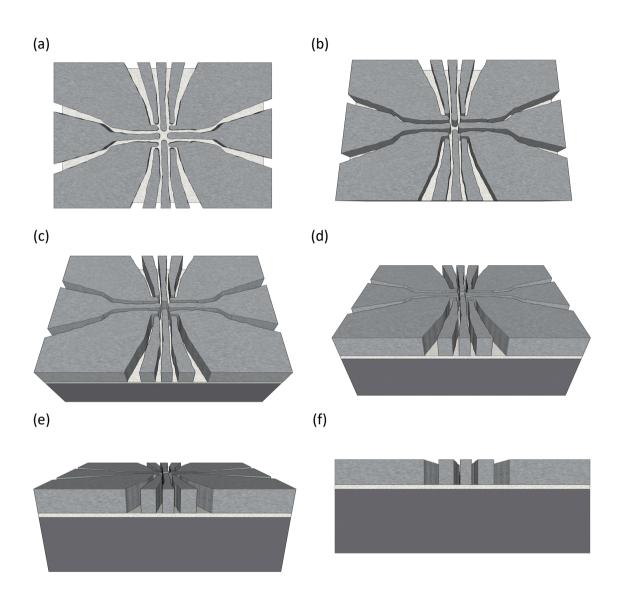

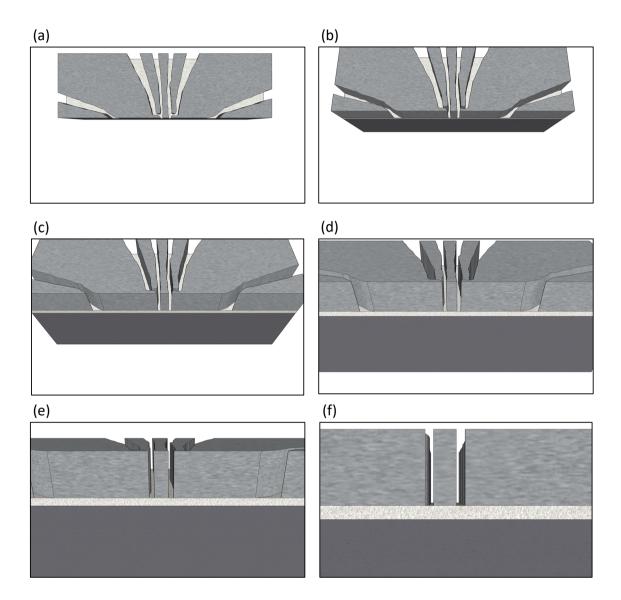

The MOSFET architecture is what forms the basis for the silicon spin qubit platform covered in this dissertation. While this section has focused on the "classical" transistor mode of MOSFETs, most of the dissertation focuses on the MOSFET architecture being used in a far different capacity. Instead of using a relatively large gate to form a well-understood conductive channel, the gate is effectively shrunk down to a size where quantum mechanical tunneling governs the transport of electrons. The gate is also used to form and control quantum dots and qubits, which is covered in Section 2.2. The device used to generate most of the results in this dissertation has many separate polysilicon gates patterned out laterally on top of the oxide layer and is imaged in Figure 2.2. Figure 2.3 shows a three-dimensional model of the region of interest of the silicon MOS (Si-MOS) device used. The images are of the device being gradually rotated from a top view (Figure 2.3(a)) to a side view (Figure 2.3(f)). The narrower gates are generally used to form and control where the quantum dot will be located. The larger gates are used to form electron reservoirs (essentially sources and drains) that provide electrons for the quantum dot.

Si-MOS lateral quantum dot devices are fabricated at Sandia National Laborato-

Figure 2.2: Si-MOS Nanostructure SEM Image

Scanning electron microscope (SEM) image of the Si-MOS nanostructure (top view). Lighter grey regions are the polysilicon gates which lie on top of the silicon dioxide and silicon substrate below. Feature sizes are as small as 50 nm by using electron beam lithography to pattern the polysilicon gates.

ries using a silicon foundry. A p-type silicon substrate with a <sup>28</sup>Si enriched epitaxy layer (500 ppm <sup>29</sup>Si) is used because it has far fewer <sup>29</sup>Si nuclear spin moments coupling to spin qubits, which results in longer spin coherence times [41]. A 35 nm thermal silicon oxide (SiO<sub>2</sub>) is then grown on the substrate at 900 °C. Next, an amorphous silicon layer is formed on top of the oxide and n-type doped with arsenic. The amorphous layer is then crystallized into degenerately doped polysilicon (poly-Si). The poly-Si is patterned using electron beam lithography (EBL) and ZEP resist with feature sizes down to 50 nm. After the resist is stripped away, the remaining poly-Si forms the nanostructure shown in Figure 2.2 (light gray regions).

Figure 2.3: Si-MOS 3D Model Complete Device

Three-dimensional model images of Si-MOS qubit device. All electrostatic gates are drawn to scale. (a) Top view. (b)–(e) Several orientations are shown between top and side view of the device. (f) Side view. The polysilicon and oxide layer thicknesses are drawn to scale, however, only a fraction of the <sup>28</sup>Si epitaxial layer is shown (dark gray bottom layer). The oxide layer is 35 nm thick (light-colored middle layer) and the polysilicon layer is 200 nm thick (top layer). For full fabrication details, see Section 4.5.

## 2.2 Quantum Dots and Donor Atoms

A quantum dot is a nanoscale potential which tightly confines charge into discrete bound states much like the classic "particle in a box" problem found in elementary quantum mechanics classes [42]. A notable early demonstration of a quantum dot was performed by Louis Brus in 1983 via colloidal suspension of semiconducting cadmium sulfide (CdS) crystallites [43, 44]. Using transmission electron microscopy, the CdS crystallites were measured to be 30–50 Å in diameter, and through resonance Raman spectroscopy, they were found to have atom-like electronic bound states. A later experiment using molecular beam epitaxy (MBE) growth found similar behavior with gallium-arsenide (GaAs) aluminum-gallium-arsenide (AlGaAs) quantum well crystalline structures grown on a GaAs substrate [45]. Marc Kastner measured the first gate-voltage-dependent conductance oscillations through a small MOSFET transistor, which was dubbed the "single-electron transistor" (SET), a relatively large quantum dot that will be covered later in this section [46, 47]. Unlike the MBE grown quantum dots, the SET is partially electrostatically formed, meaning that part of the confining potential is defined by electric fields originating from a conducting gate. Similar designs using lateral gate geometry were later shown to form quantum dots with as few as one or two electrons [48, 49]. This dissertation will focus on the electrically measured, electrostatically defined quantum dots in Si-MOS [50-52].

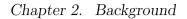

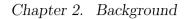

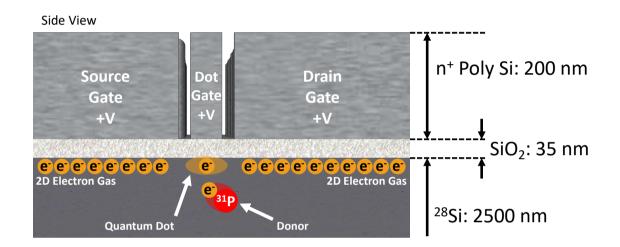

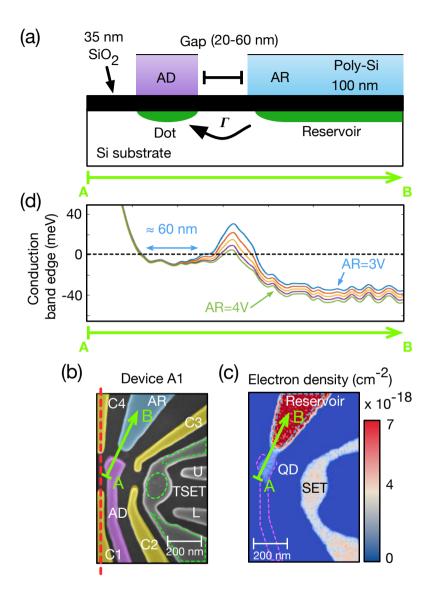

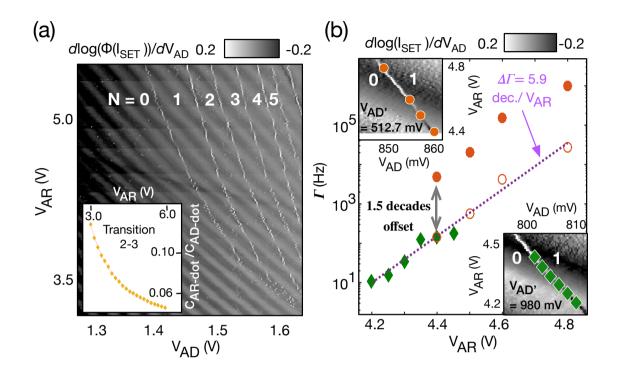

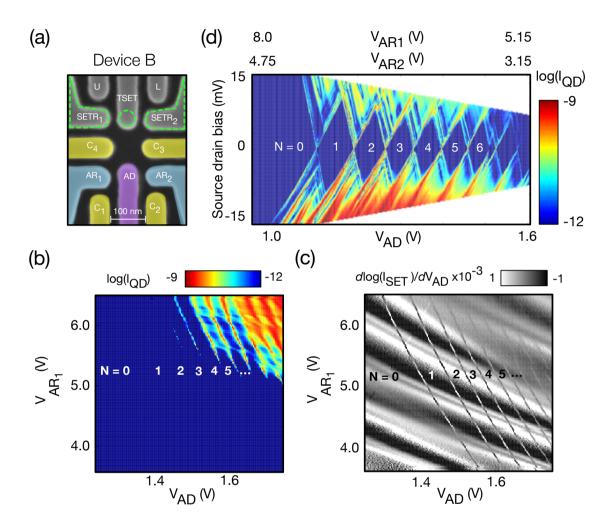

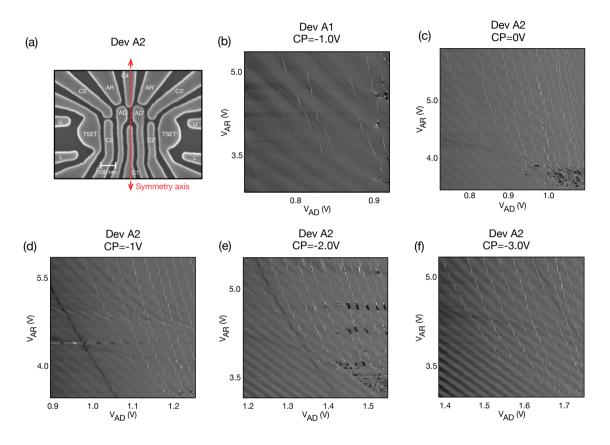

Quantum dots in Si-MOS are created by confining electrons electrostatically in a manner similar to how the conducting channel is formed in a MOSFET. Figure 2.4 shows a model of the Si-MOS device used in this dissertation which has been cut across the gate where the quantum dot is intended to be formed underneath. After rotating the device from a top view (Figure 2.4(a)) to a side view (Figure 2.4(f)), the region where the quantum dot is formed is visible underneath the narrower polysilicon gate in the center. Figure 2.5 shows a schematic representation of the Si-MOS quantum dot and donor atom system. Since this is an enhancement

mode device, a positive voltage is placed across gates where electrons are intended to be accumulated against the Si-SiO<sub>2</sub> interface. Underneath the larger "Source/Drain Gates," two-dimensional electron gases (2DEGs) are formed which act as electron reservoirs. The electrons in the reservoirs are schematically shown relatively large and countable, but the actual number of electrons in the reservoirs is much larger with surface density around  $10^{12}$  electrons/cm<sup>2</sup>. Below the "Dot Gate," as few as one electron is confined vertically against the Si-SiO<sub>2</sub> interface and laterally by electrostatically defined tunnel barriers. Phosphorous donor atoms with mass number 31 are implanted next to the quantum dot via stochastic ion implantation. The <sup>31</sup>P donors are directed into the substrate with 45 keV of energy. A single <sup>31</sup>P donor is intended to be tunnel coupled to the quantum dot to form a singlet-triplet qubit, which is covered in Section 2.3.

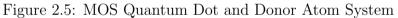

Figure 2.6 shows the electrochemical potential of the conduction band edge for both the quantum dot and donor atom along relevant directions. The quantum dot possesses an anisotropic potential due to two different confinement modes. In the vertical direction, the quantum dot is confined against the  $Si-SiO_2$  interface in a triangle potential. The vertical wall of the triangle potential is due to the large band gap of the insulating  $SiO_2$  (8.9 eV). The slanted wall of the triangle potential is due to the dependence of the conduction band edge on the electric field originating from the conducting gate above. This electric field linearly changes the edge of the conduction band relative to the Fermi level as a function of distance. Confinement in the vertical direction is exactly the same as how a conducting channel is formed in a MOSFET (Section 2.1). Confinement in the lateral direction is the main difference in this type of device. In the lateral direction, tunnel barriers are formed when there is an insufficient electric field to bend the conduction band edge below the Fermi level. This is accomplished by having gaps on the sides of the "Dot Gate" which are visible in Figure 2.5 as well as using other nearby poly-Si gates with negative voltage bias placed on them (Figure 2.2 narrow poly-Si gates on either side of "Dot Gate"). In the

Figure 2.4: Si-MOS 3D Model Sliced Device

Three-dimensional model images of sliced Si-MOS device. The cut has been made through a region of interest where the quantum dot is intended to be formed. (a) Top view. (b)–(e) Multiple orientations of the cut device between top and side view. (f) Side view. The polysilicon and oxide layers are drawn to scale, however not all of the  $^{28}$ Si epilayer is shown.

Schematic drawing of a Si-MOS quantum dot and donor atom system. The upper, conductive polysilicon gates generate electric fields which bend the conduction band in the silicon substrate below the Fermi level of the electrons. Larger-area gates such as the "Source Gate" and "Drain Gate" form two-dimensional electron gases (2DEGs) below which act as reservoirs of electrons for the quantum dot. Electrons in the reservoirs are drawn relatively large (the actual surface density of the electrons is around  $10^{12}$  electrons/cm<sup>2</sup>). Below the smaller "Dot Gate," the quantum dot is formed by the triangular confining potential against the silicon dioxide and the quadratic potential along the lateral direction. <sup>31</sup>P donors are implanted stochastically between the polysilicon gates near the quantum dot.

Chapter 2. Background

#### Figure 2.6: Si-MOS QD and Donor Potentials

Electrochemical potential of the conduction band edge for the Si-MOS quantum dot and donor drawn schematically for different directions in the silicon substrate. The uppermost schematic shows the Si-MOS device with color-coded directions for the potential plots below. Orange represents electrons and electron energy levels. In the quantum dot and donor, filled energy levels are drawn as solid, orange lines, and unoccupied energy levels are drawn as dashed, orange lines. The Fermi level is the average value of the electrochemical potential to add an additional electron to the silicon substrate. In the reservoir regions (left and right of the quantum dot), the energy levels are much closer together than in the quantum dot or donor region. The energy levels of the reservoir near the Fermi level are distributed according to a Fermi-Dirac distribution which depends on temperature.

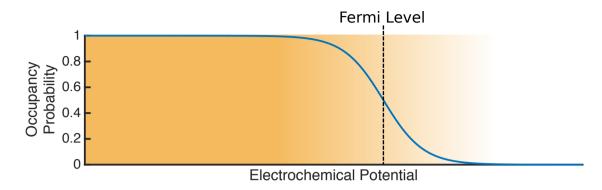

reservoir regions, the energy levels are much closer together than in the quantum dot or donor region, therefore they are drawn as an orange continuum. The energy levels of the reservoir near the Fermi level become faded due to the occupancy probability following a Fermi-Dirac distribution which depends on temperature,

$$n(E) = \frac{1}{e^{(E-E_F)/k_BT} + 1},$$

(2.2)

where n is the occupancy probability, E is the electrochemical potential,  $E_F$  is the Fermi level,  $k_B$  is the Boltzmann constant (86.17  $\mu eV/K$ ), and T is the temperature. Figure 2.7 shows a plot of Equation 2.2.

Electrons in a quantum dot have energy from two different phenomena:

- 1. *Electrostatics*, where the energy stored by adding charge to a capacitor is,  $\frac{Q^2}{2C}$ , where Q is the total charge and C is the capacitance.

- 2. Quantum mechanics, where the energy levels are dictated by the behavior of the confinement potential. For example, consider an electron in a confinement potential that has vertical walls separated by distance, w, with zero potential inside the walls and infinite potential outside the walls. This is the classic "particle in a box" problem from elementary quantum mechanics classes where the energy levels are given by,  $E_n = \frac{n^2 h^2}{2m_e w^2}$ , where n is the level number, his the Planck constant  $(4.136 \cdot 10^{-15} \text{ eV} \cdot \text{s})$ , and  $m_e$  is the electron rest mass  $(9.11 \cdot 10^{-31} \text{ kg})$ .

Estimating the energy of electrons in the quantum dot will involve both electrostatics and quantum mechanics. The source and drain reservoirs and electrostatic gate all have a capacitance to the quantum dot  $(C_S, C_D, C_G)$  and have voltages applied  $(V_S, V_D, V_G)$ . The energy of a quantum dot with N electrons is estimated by,

$$U(N) = \frac{(-eN + C_S V_S + C_D V_D + C_G V_G)^2}{2(C_S + C_D + C_G)} + \sum_{n=1}^N E_n,$$

(2.3)

The probability that the energy state at a given electrochemical potential will be occupied. This is a plot of Equation 2.2 with the average value of the electrochemical potential to add an electron to the reservoir labeled (which is  $E_F$ , the Fermi level). The orange color overlaid represents effectively a continuum of occupied states with white meaning unoccupied. The color changes from orange to white as the occupancy decreases following the Fermi-Dirac distribution. The width of the Fermi-Dirac function depends on temperature, where greater width means higher temperature.

where U is the energy, e is the electron charge  $(1.602 \cdot 10^{-19} \text{ C})$ , and  $E_n$  is an electron energy level given by quantum mechanics. Since the energy depends quadratically on the gate voltage,  $V_G$ , it is more convenient to work with an energy scale which depends linearly on the gate voltage. The electrochemical potential is such an energy scale, and it is defined as,

$$\mu(N) \equiv U(N) - U(N-1) = \frac{Ne^2}{C} - \frac{e^2}{2C} - \frac{e}{C}(C_S V_S + C_D V_D + C_G V_G) + E_N, \quad (2.4)$$

where  $\mu$  is the electrochemical potential, C is the total capacitance to the quantum dot  $(C_S + C_D + C_G)$ , and  $E_N$  the quantum mechanical energy level of the  $N^{\text{th}}$  electron. The electrochemical potential forms a "ladder" of energy levels as each electron is added to the quantum dot. The energy difference between two electrochemical potential levels is,

$$E_{\text{add}}(N) = \mu(N+1) - \mu(N) = \frac{e^2}{C} + E_{N+1} - E_N \equiv E_C + \Delta E, \qquad (2.5)$$

where  $E_{\text{add}}$  is known as the addition energy,  $E_C$  is defined as the charging energy

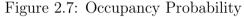

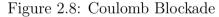

Electrochemical energy of source, drain, and quantum dot showing the phenomenon known as "Coulomb blockade." On the right, there is an available electrochemical potential energy level of the quantum dot between the source and drain bias window, therefore current flows. On the left, there is no available energy level between the bias window and no current flows (Coulomb blockade). As gate voltage is changed, resonances in current show up each time the occupancy of the quantum dot is changed. The width of the resonances depends on temperature.

$(E_C = \frac{e^2}{C})$ , and  $\Delta E$  is the difference between two quantum mechanical energy levels of an electron. As expected, the addition energy consists of an electrostatic component  $(E_C)$  and a quantum mechanical component  $(\Delta E)$ . For a quantum dot with many electrons, it is typically true that  $E_C > \Delta E$ .

When a voltage bias is placed across the source and drain reservoirs, the electrochemical potential difference between the two reservoirs is given by,  $-e(V_S - V_D) \equiv$  $-eV_{SD} = (\mu_S - \mu_D)$ . Current will flow into the source and out of the drain only when

electrons can tunnel into and out of the quantum dot. Electrons will tunnel from the source to the quantum dot and then to the drain only when there is an available electrochemical energy level of the quantum dot in between the source and drain electrochemical potentials. If  $|-eV_{SD}| < E_{add}$ , the current through the quantum dot will resonantly change from zero to a peak value as the gate voltage is changed. The phenomenon where electron tunneling is prevented is known as "Coulomb blockade" and is portrayed in Figure 2.8. The upper left plot of Figure 2.8 shows a blockaded, zero-current condition, where there is no quantum dot electrochemical energy level between the source and drain bias window. The upper right plot of Figure 2.8 demonstrates the case where current does flow at the peak of a resonance. As quantum dot gate voltage is decreased (right to left on the plot), electrons are emptied out of the quantum dot with the resonances marking each time the electron occupancy changes by one. The opposite is true if the quantum dot gate voltage is increased. The source-drain current for a given resonance centered around the peak at a gate voltage,  $V_{center}$ , is given by,

$$I_{SD}(V_G) = \frac{e^2}{4k_BT} \frac{\Gamma_S \Gamma_D}{\Gamma_S + \Gamma_D} \cosh\left(\frac{\alpha_G (V_G - V_{\text{center}})}{2k_BT}\right)^{-2},$$

(2.6)

where  $\Gamma_S$  is the tunnel rate from the source reservoir to the quantum dot,  $\Gamma_D$  is the tunnel rate from the quantum dot to the drain reservoir,  $k_B$  is the Boltzmann constant (86.17  $\mu eV/K$ ), T is the temperature, and  $\alpha_G$  is known as the lever arm of the dot gate. The tunnel rate terms and electron charge may be treated as a free parameter for the purposes of fitting the equation to data. The lever arm is a quantity which relates a change in gate voltage to a change in the electrochemical potential of the quantum dot,

$$\Delta \mu_{QD} = \alpha_G \Delta V_G, \tag{2.7}$$

which can be extracted in several ways outlined in Chapter 3 and from a measurement described next.

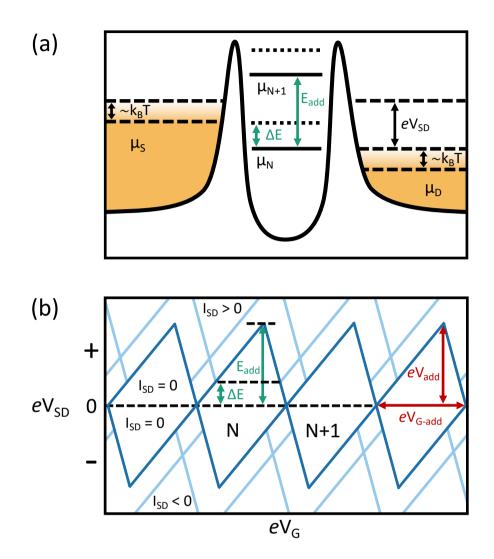

(a) Electrochemical potential of source and drain reservoirs and the quantum dot. Excited state energy levels in the quantum dot are represented as black dashed lines. The Fermi-Dirac width for the source and drain reservoirs is shown between two dashed lines. The bias between the source and drain is depicted above the electrochemical potential of the drain. (b) Coulomb diamond measurement diagram where the derivative of the source-drain current with respect to the source-drain bias is plotted. The dark blue lines represent changes from zero current to some current. In the "diamond" regions, there is no current flowing. Only the first excited states are shown for simplicity, which are depicted as light blue lines. The addition energy and  $\Delta E$  are both shown in green. The voltages used to extract the quantum dot gate lever arm are shown in red.

When the source-drain bias is changed against the dot gate voltage and the source-drain current is plotted, a diamond pattern appears. This pattern and measurement are known as "Coulomb diamonds." Figure 2.9(b) shows this effect when the derivative of the source-drain current with respect to source-drain bias is plotted. Dark blue lines represent changes from zero source-drain current to some current. When  $|eV_{SD}| < \Delta E$ , tunneling of electrons only occurs through the ground state energy as  $V_G$  is changed and Coulomb blockade is observed, which is shown in the lower plot in Figure 2.8. When  $|eV_{SD}| > \Delta E$ , excited state energies will now enter the source-drain bias window in addition to ground state energies as  $V_G$  is changed. These excited state energies show up as changes in the current, which are depicted as light blue lines. More excited state energies are shown for simplicity. Figure 4.3(d) shows actual data for a Coulomb diamond measurement.

The lever arm may be extracted from a Coulomb diamond measurement by using the following relationship,

$$eV_{\rm add} = E_{\rm add} = \alpha_G(eV_{G-\rm add}), \tag{2.8}$$

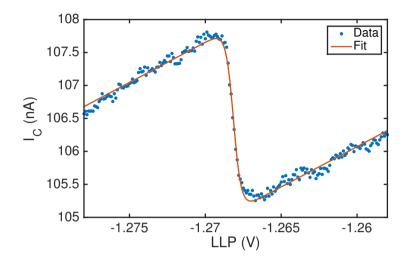

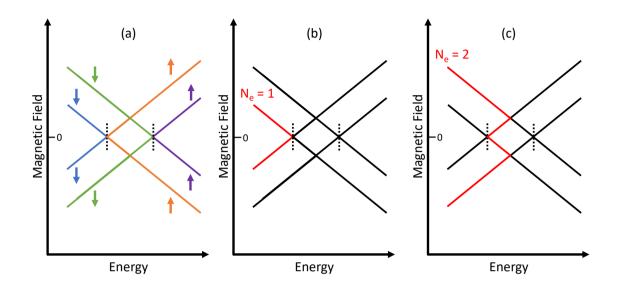

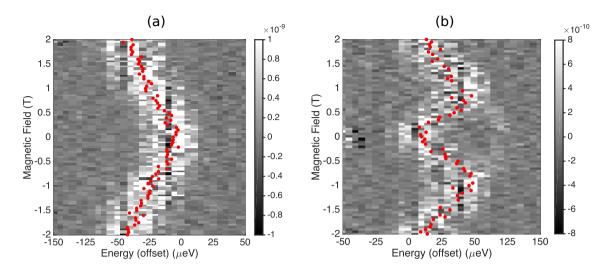

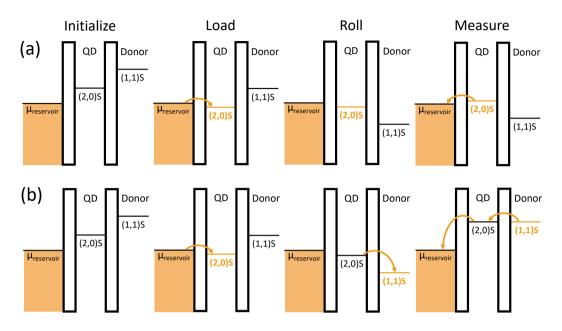

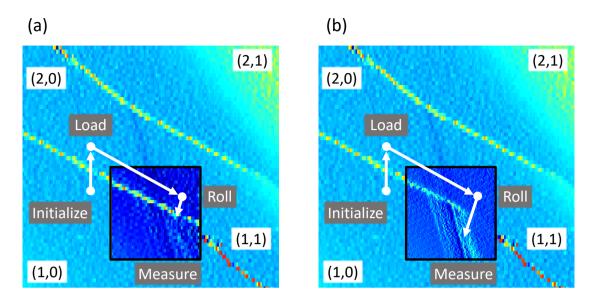

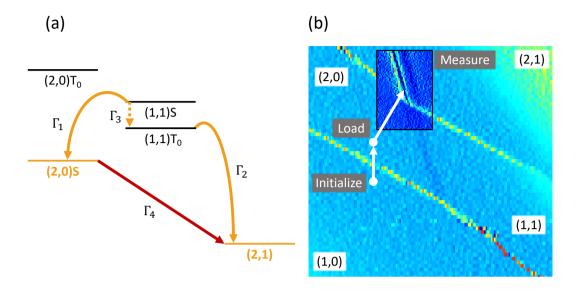

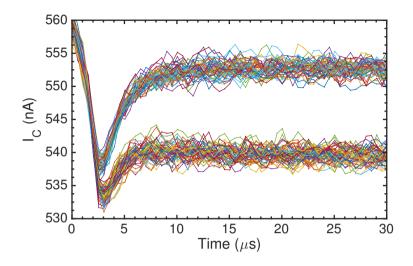

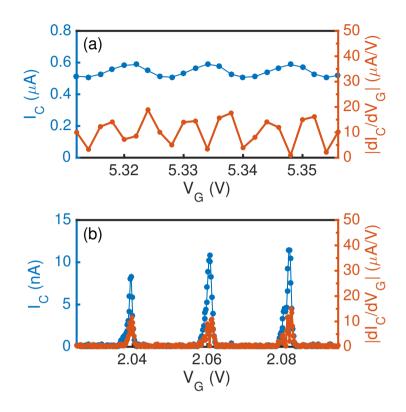

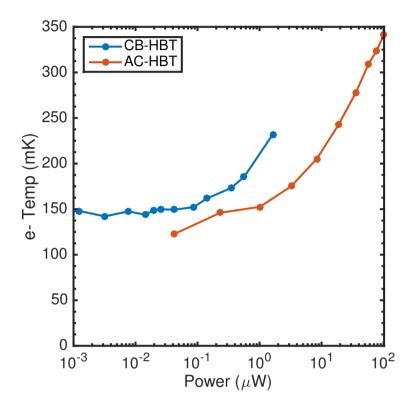

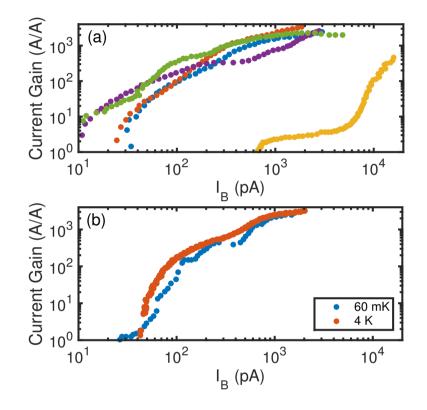

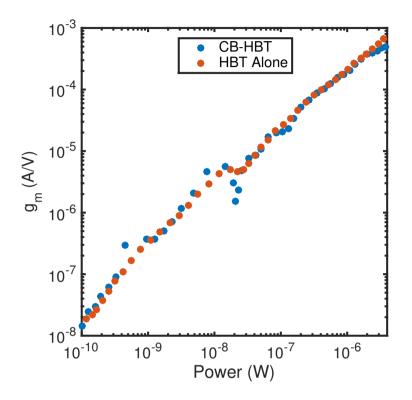

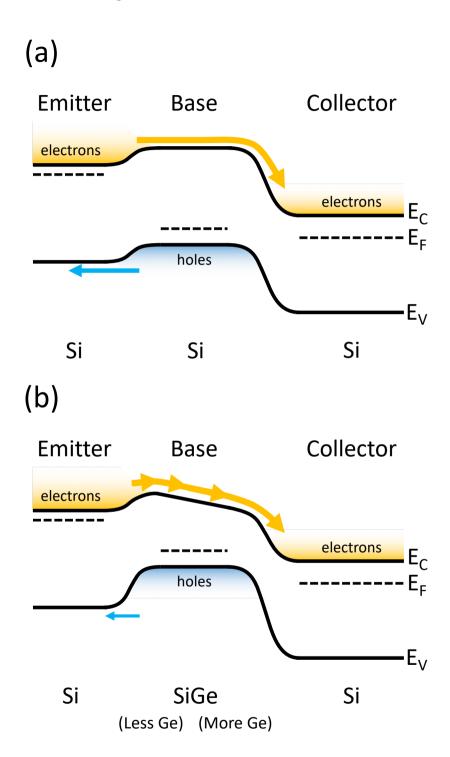

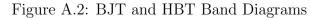

where  $V_{add}$  is the source-drain bias at the "top" of a diamond, and  $V_{G-add}$  is the gate voltage bias difference across a diamond at zero source-drain bias. Both of these quantities are shown in red on Figure 2.9(b).