# This electronic thesis or dissertation has been downloaded from Explore Bristol Research, http://research-information.bristol.ac.uk

Author: Middleton, Callum

Title: Optimising heat flow in wide and ultra-wide bandgap devices

#### **General rights**

Access to the thesis is subject to the Creative Commons Attribution - NonCommercial-No Derivatives 4.0 International Public License. A copy of this may be found at https://creativecommons.org/licenses/by-nc-nd/4.0/legalcode This license sets out your rights and the restrictions that apply to your access to the thesis so it is important you read this before proceeding.

**Take down policy** Some pages of this thesis may have been removed for copyright restrictions prior to having it been deposited in Explore Bristol Research. However, if you have discovered material within the thesis that you consider to be unlawful e.g. breaches of copyright (either yours or that of a third party) or any other law, including but not limited to those relating to patent, trademark, confidentiality, data protection, obscenity, defamation, libel, then please contact collections-metadata@bristol.ac.uk and include the following information in your message:

Your contact details

Bibliographic details for the item, including a URL

• An outline nature of the complaint

Your claim will be investigated and, where appropriate, the item in question will be removed from public view as soon as possible.

# Optimising heat flow in high performance wide and ultra-wide bandgap devices

The application of diamond in heat spreading.

By

CALLUM MIDDLETON

School of Physics UNIVERSITY OF BRISTOL

A dissertation submitted to the University of Bristol in accordance with the requirements of the degree of DOCTOR OF PHILOSOPHY in the Faculty of Science.

DATE 7/12/2018

Word count:  $\approx 42000$

ABSTRACT

ide and ultra-wide bandgap materials are able to give the high performance necessary for applications such as LIDAR and wide bandwidth communications. These applications result in high power densities that must be managed, making innovative heat extraction techniques vital. In this work, heat flow and diamond heat spreading solutions are studied in novel device designs fabricated in GaN, AlGaN, and  $\beta$  – Ga<sub>2</sub>O<sub>3</sub> to ensure that these materials can be utilised to their full potential.

GaN-on-diamond material properties are studied through nanoparticle assisted Raman thermography and transient thermoreflectance. Seeding and growth conditions are shown to impact the thermal properties, with an optimal seed size suggested to be  $\approx 50$  nm. The impact of GaN buffer thickness on GaN-on-diamond device operating temperature is assessed using photoluminescence. Excellent electrical performance and thermal resistances as low as  $9 \pm 1$  K/(W/mm) are demonstrated in devices with a buffer thickness of 354 nm.

Superlattice castellated field effect transistors are efficient RF switches, but power density is localised periodically along the gate. The operating temperature of these devices was found through micro-Raman thermography, gate resistance thermometry, and finite element simulations. The 3D gate was found to aid heat flow by providing a high thermal conductivity heat pipe; the devices have a thermal resistance of  $19.1 \pm 0.7$  K/(W/mm) which is similar to that of GaN-on-SiC devices.

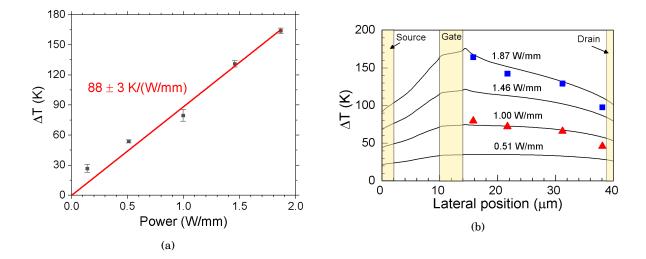

The first thermal study of  $\beta$  – Ga<sub>2</sub>O<sub>3</sub> devices is presented, with a thermal resistance of 88 ± 3 K/(W/mm) found, as well as the first study of it's phonon lifetimes. Devices fabricated in low thermal conductivity materials such as  $\beta$  – Ga<sub>2</sub>O<sub>3</sub> will need innovative thermal management. This is explored using simulations, with a diamond passivation layer recommended.

#### **DEDICATION AND ACKNOWLEDGEMENTS**

would like to begin by thanking my fiancée Sarah for her support, and her patience, through this writing process. I am sure I have not been easy to live with, and Sarah kept me well supplied with tea and snacks. Similarly, I would like to thank all my family and friends who were supportive during the writing process and didn't get offended when I turned down invitations because 'sorry, I'm writing'.

I have found studying for my PhD to be a truly enjoyable experience. Yes, there were frustrating times when things would not go right in the lab, but these were insignificant when compared to the good times. Coming in to the office was never a chore, and that is down to the people I got to work with every day. There are too many to name, but there was never a dull day and I made many friends.

I particularly need to thank those that helped me with my research. Dr Julian Anaya helped me so much in the early days, and following that, Dr James Pomeroy was always on hand to help in the lab and with any questions. I would also like to thank Professor Kuball for giving me the opportunity to study for this PhD and for his guidance. I would like to thank Professor Mark Newton and Professor Julie Macpherson and all at the University of Warwick for hosting the Diamond Science and Technology Centre for Doctoral Training. It was a rewarding experience which gave me a head start in my PhD. I would like to thank Professor Oliver Williams at Cardiff University and Professor Alan Kemp at the University of Strathclyde for being great hosts throughout my mini-projects.

Finally I would like to thank the EPSRC and Element 6 for funding this PhD project. I am grateful for the opportunity, and would like to thank Richard Balmer and Dan Francis for their support.

# **AUTHOR'S DECLARATION**

declare that the work in this dissertation was carried out in accordance with the requirements of the University's Regulations and Code of Practice for Research Degree Programmes and that it has not been submitted for any other academic award. Except where indicated by specific reference in the text, the work is the candidate's own work. Work done in collaboration with, or with the assistance of, others, is indicated as such. Any views expressed in the dissertation are those of the author.

SIGNED: ...... DATE: .....

# TABLE OF CONTENTS

|    |        |              |                                                                                                         | Pa  | age  |

|----|--------|--------------|---------------------------------------------------------------------------------------------------------|-----|------|

| Li | ist of | Tables       | 3                                                                                                       |     | xi   |

| Li | ist of | Figure       | es                                                                                                      |     | xiii |

| 1  | Intr   | oducti       | ion                                                                                                     |     | 1    |

|    | 1.1    | Develo       | opment of high power, high frequency transistors                                                        | ••• | 1    |

|    | 1.2    | Thesis       | s outline                                                                                               |     | 5    |

| 2  | Mat    | erial a      | and Device theory                                                                                       |     | 9    |

|    | 2.1    | Phono        | ons and heat transport                                                                                  | ••• | 9    |

|    |        | 2.1.1        | Phonon theory                                                                                           |     | 9    |

|    |        | 2.1.2        | Heat flow in solids                                                                                     |     | 14   |

|    | 2.2    | GaN a        | and AlGaN high electron mobility transistors                                                            |     | 19   |

|    |        | 2.2.1        | Material properties                                                                                     |     | 19   |

|    |        | 2.2.2        | Material synthesis                                                                                      |     | 22   |

|    |        | 2.2.3        | Wafer epitaxy                                                                                           |     | 23   |

|    |        | 2.2.4        | High electron mobility transistor operation                                                             |     | 26   |

|    | 2.3    | $\beta - Ga$ | $a_2O_3$ FETs $\ldots$ |     | 32   |

|    |        | 2.3.1        | Material properties                                                                                     |     | 32   |

|    |        | 2.3.2        | Material synthesis                                                                                      |     | 36   |

|    |        | 2.3.3        | FET operation                                                                                           |     | 38   |

|    | 2.4    | Diamo        | ond for heat spreading                                                                                  |     | 39   |

|    |        | 2.4.1        | Material properties                                                                                     | ••• | 39   |

|   |     | 2.4.2   | Material synthesis                         | 41  |

|---|-----|---------|--------------------------------------------|-----|

|   |     | 2.4.3   | Diamond integration with electronics       | 46  |

|   | 2.5 | Heat f  | low in device structures                   | 49  |

| 3 | Exp | erimer  | ntal Methods                               | 53  |

|   | 3.1 | Ramai   | n spectroscopy and thermography            | 54  |

|   |     | 3.1.1   | Raman scattering                           | 54  |

|   |     | 3.1.2   | Raman thermography                         | 57  |

|   |     | 3.1.3   | Renishaw Invia spectrometer                | 60  |

|   |     | 3.1.4   | Nanoparticle assisted Raman thermography   | 64  |

|   | 3.2 | Photol  | uminescence                                | 65  |

|   | 3.3 | Transi  | ent thermoreflectance                      | 68  |

|   | 3.4 | Finite  | element analysis                           | 73  |

| 4 | Opt | imisati | on of GaN-on-Diamond Materials and Devices | 79  |

|   | 4.1 | GaN-o   | n-diamond wafer mapping                    | 80  |

|   |     | 4.1.1   | Method                                     | 80  |

|   |     | 4.1.2   | Results                                    | 83  |

|   | 4.2 | Diamo   | nd film thermal conductivity               | 90  |

|   |     | 4.2.1   | Method                                     | 90  |

|   |     | 4.2.2   | Results                                    | 92  |

|   | 4.3 | GaN-o   | n-diamond devices                          | 93  |

|   |     | 4.3.1   | Method                                     | 94  |

|   |     | 4.3.2   | Results                                    | 97  |

|   | 4.4 | Summ    | ary                                        | 101 |

| 5 | The | rmal T  | ransport in Superlattice Castellated FETs  | 103 |

|   | 5.1 | Metho   | d                                          | 106 |

|   | 5.2 | Result  | s                                          | 113 |

|   | 5.3 | Discus  | sion                                       | 117 |

# TABLE OF CONTENTS

|    | 5.4     | Summary                                                                           | .21 |

|----|---------|-----------------------------------------------------------------------------------|-----|

| 6  | Ultr    | a-Wide Bandgap Materials for High Performance Devices 1                           | 23  |

|    | 6.1     | Phonon lifetimes and decay mechanisms in $\beta$ – Ga <sub>2</sub> O <sub>3</sub> | 25  |

|    |         | 6.1.1 Method                                                                      | .26 |

|    |         | 6.1.2 Results and Discussion                                                      | .30 |

|    | 6.2     | Thermal Resistance of $\beta$ – Ga <sub>2</sub> O <sub>3</sub> MOSFETs            | .34 |

|    |         | 6.2.1 Method                                                                      | .35 |

|    |         | 6.2.2 Results and Discussion                                                      | .37 |

|    | 6.3     | Modelling of ultrawide bandgap devices                                            | .38 |

|    |         | 6.3.1 Method                                                                      | .38 |

|    |         | 6.3.2 Results and Discussion                                                      | .41 |

|    | 6.4     | Conclusions                                                                       | .44 |

| 7  | Summary |                                                                                   | .47 |

|    | 7.1     | Future Work                                                                       | 52  |

| A  | Арр     | endix A 1                                                                         | 55  |

|    | A.1     | List of Publications                                                              | 55  |

|    | A.2     | List of Presentations                                                             | .56 |

| в  | Арр     | endix B 1                                                                         | 59  |

|    | B.1     | List of Acronyms and Abbreviations                                                | .59 |

| Bi | bliog   | raphy 1                                                                           | 61  |

# LIST OF TABLES

# TABLE

# Page

| 4.1 | A summary of the transient thermoreflectance wafer mapping performed on GaN-on-  |    |

|-----|----------------------------------------------------------------------------------|----|

|     | diamond wafers.                                                                  | 85 |

| 4.2 | A summary of the growth conditions and thermal conductivity data for the diamond |    |

|     | thin films measured.                                                             | 93 |

| 4.3 | A summary of the derived results from the photoluminescence measurements and the |    |

|     | finite element simulations of the GaN-on-diamond devices.                        | 99 |

# LIST OF FIGURES

# FIGURE

# Page

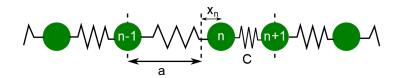

| 2.1  | One-dimensional monatomic lattice used to demonstrate the occurace of phonon                    |    |

|------|-------------------------------------------------------------------------------------------------|----|

|      | normal modes in crystals.                                                                       | 10 |

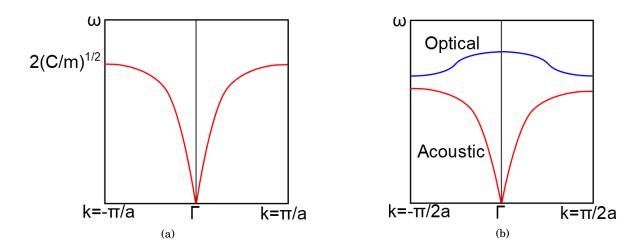

| 2.2  | Sketch of phonon dispersion curves for a one-dimensional monatomic and diatomic                 |    |

|      | lattice.                                                                                        | 13 |

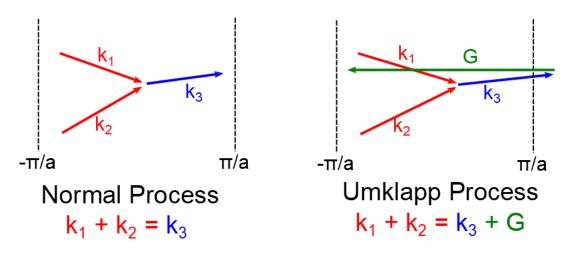

| 2.3  | Sketch of the normal and umklapp phonon scattering processes which occur in a                   |    |

|      | Brillouin zone.                                                                                 | 18 |

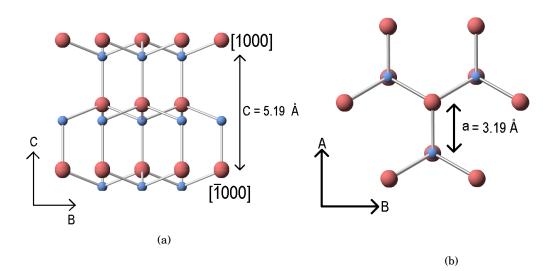

| 2.4  | Crystal structure diagram of wurtzite GaN                                                       | 20 |

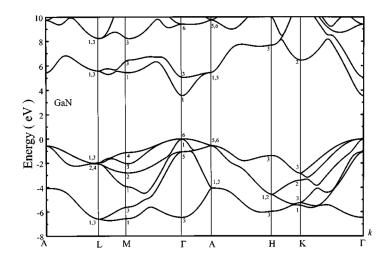

| 2.5  | Electronic band structure of GaN                                                                | 21 |

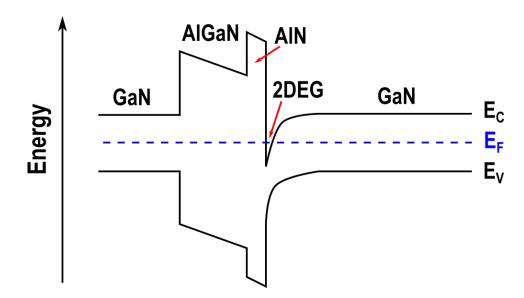

| 2.6  | A sketch of the band structure at a GaN/AlGaN heterojunction.                                   | 28 |

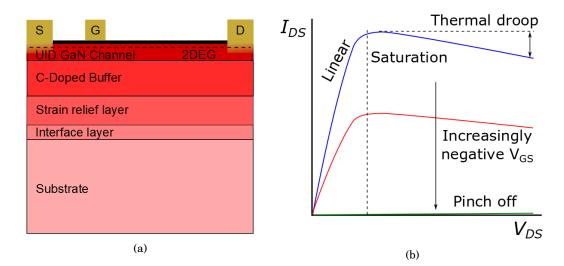

| 2.7  | A schematic example of a typical high electron mobility transistor structure and the            |    |

|      | IV characteristics which may be associated with it                                              | 31 |

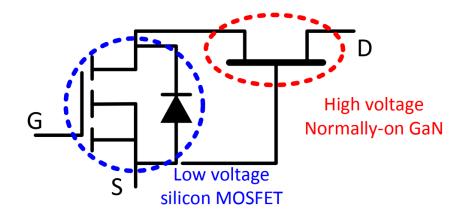

| 2.8  | A circuit diagram of a GaN HEMT and a silicon MOSFET in a cascode arrangement.                  | 33 |

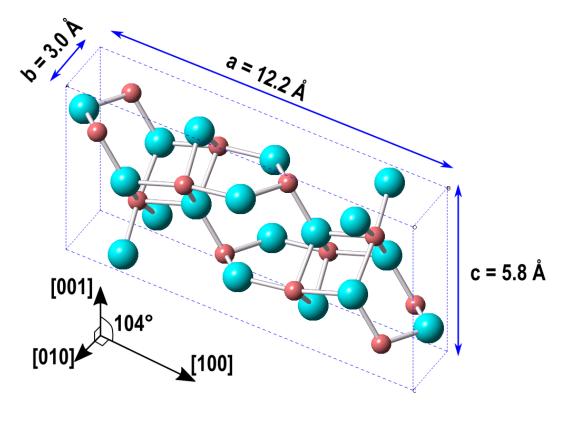

| 2.9  | Crystal structure diagram of the $eta$ polymorph of gallium oxide $\ldots \ldots \ldots \ldots$ | 34 |

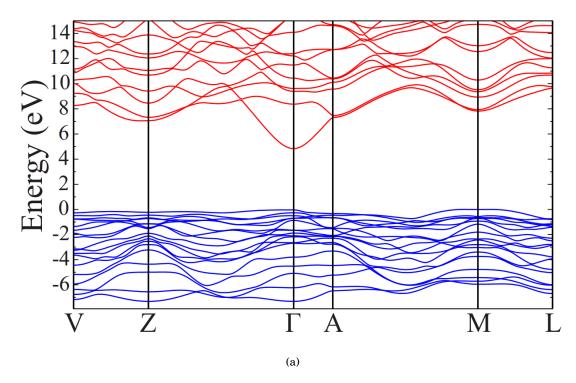

| 2.10 | Electronic band structure of $\beta$ – Ga <sub>2</sub> O <sub>3</sub>                           | 35 |

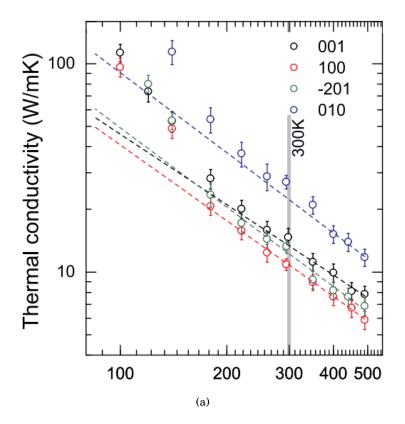

| 2.11 | Temperature dependent thermal conductivity data for $\beta$ – Ga $_2O_3$                        | 36 |

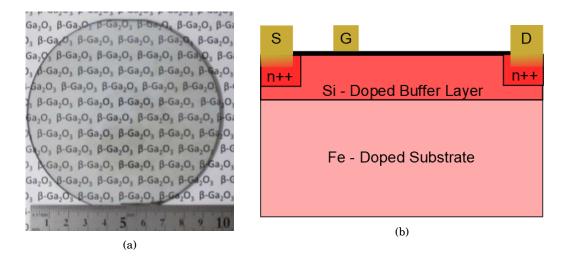

| 2.12 | An image of a 10 mm diameter $\beta-{ m Ga_2O_3}$ wafer and a schematic diagram of a MOSFET     |    |

|      | fabricated in $\beta$ – Ga <sub>2</sub> O <sub>3</sub>                                          | 37 |

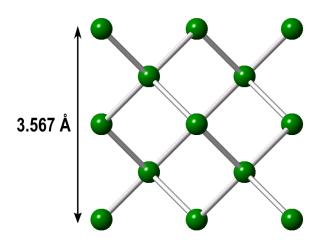

| 2.13 | Crystal structure diagram of diamond.                                                           | 40 |

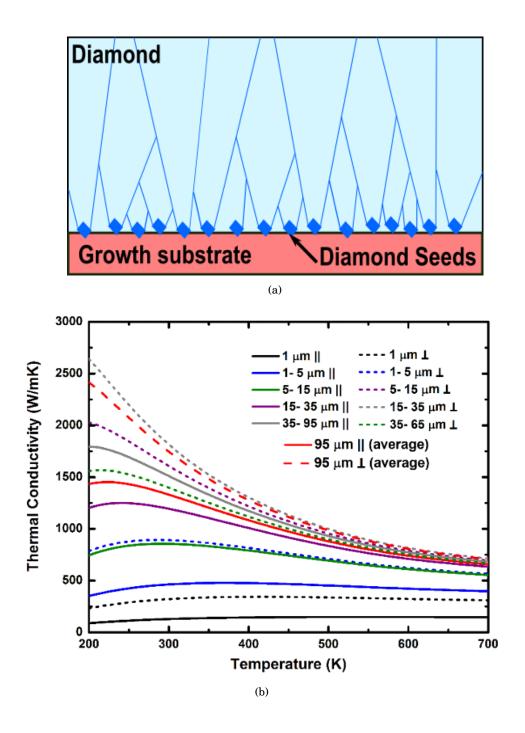

| 2.14 | A sketch showing the van der Drift growth structure in polycrystalline diamond, and             |    |

|      | data showing the thermal conductivity dependence on diamond layer thickness. $\ldots$           | 45 |

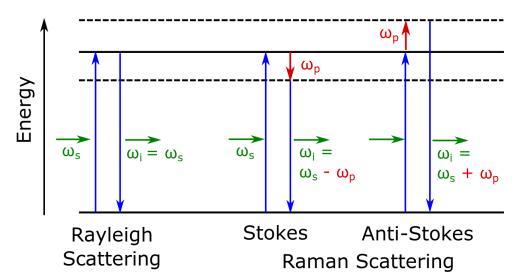

| 3.1  | Sketch of the electron transitions in different forms of photon scattering                      | 55 |

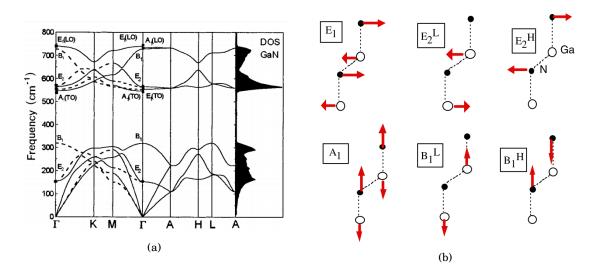

| 3.2  | Phonon dispersion curve of GaN, and a sketch of the normal mode vibrations                   | 58  |

|------|----------------------------------------------------------------------------------------------|-----|

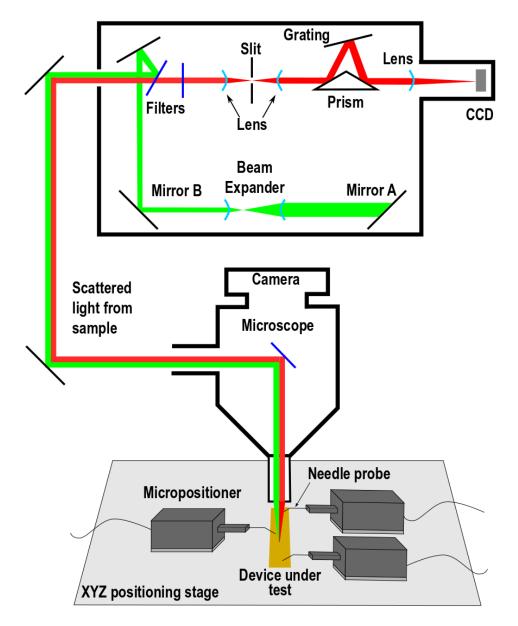

| 3.3  | Sketch of Renishaw Invia spectrometer used for Raman scattering experiments                  | 61  |

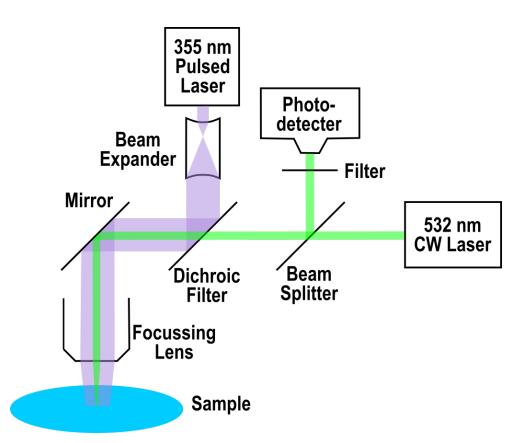

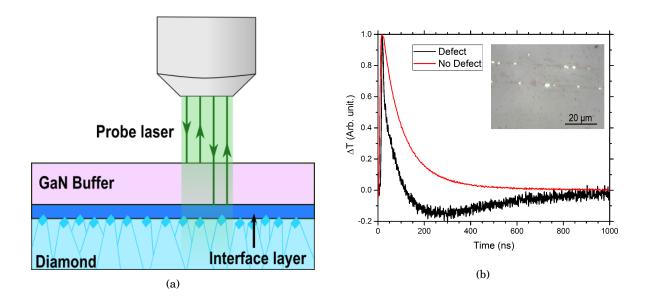

| 3.4  | Sketch of the experimental set up used in transient thermoreflectance measurements.          | 72  |

| 3.5  | An example of the finite element approach to a 1D problem and an example mesh for            |     |

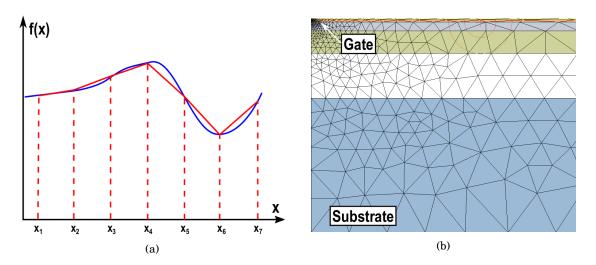

|      | a transistor                                                                                 | 74  |

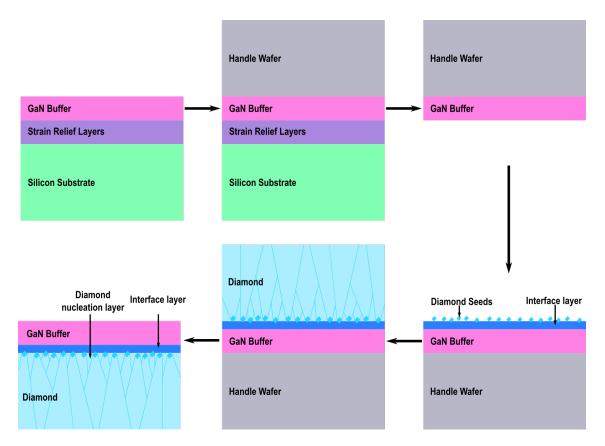

| 4.1  | Element 6 developed process flow for GaN on diamond wafer fabrication                        | 81  |

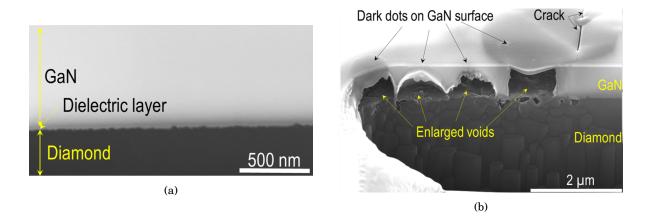

| 4.2  | SEM cross-sections showing voids at a GaN-Diamond interface.                                 | 83  |

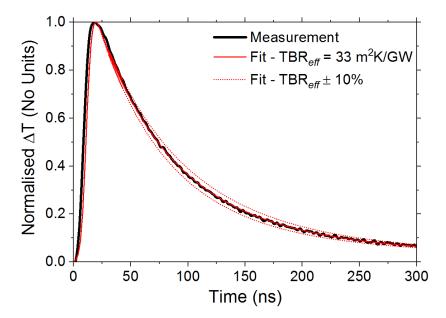

| 4.3  | Data showing the fitting sensitivity in the transient thermoreflectance measurement.         | 84  |

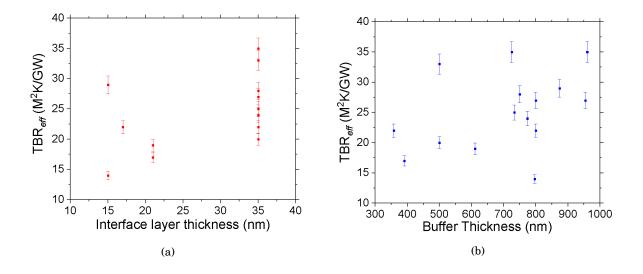

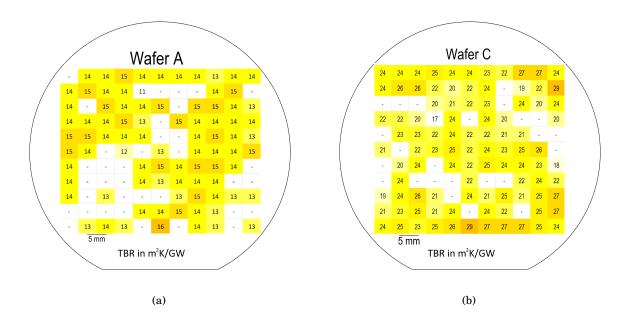

| 4.4  | Graphs showing the measured effective thermal boundary resistance of a number of             |     |

|      | GaN-on-diamond wafers, with the dependence on interface layer thickness and buffer           |     |

|      | thickness shown                                                                              | 85  |

| 4.5  | $Example\ transient\ thermore flectance\ wafer\ maps\ for\ two\ GaN-on-diamond\ wafers. \ .$ | 86  |

| 4.6  | Schematic diagram of how reflections from multiple interfaces can cause incorrect            |     |

|      | measurements, and an example of when this has occured                                        | 87  |

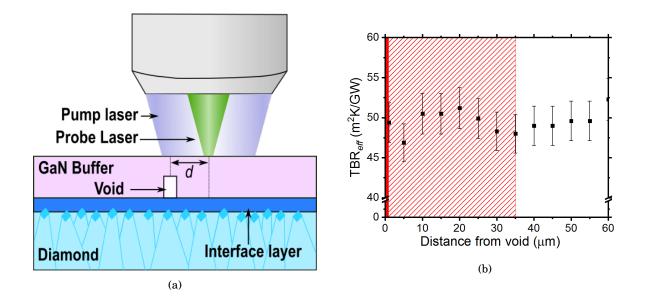

| 4.7  | Schematic diagram of the measurement performed to judge the transient thermore-              |     |

|      | flectance measurement spatial resolution, and the data collected. $\ldots$                   | 88  |

| 4.8  | Simulated results to show the transient thermoreflectance measurement spatial                |     |

|      | resolution                                                                                   | 89  |

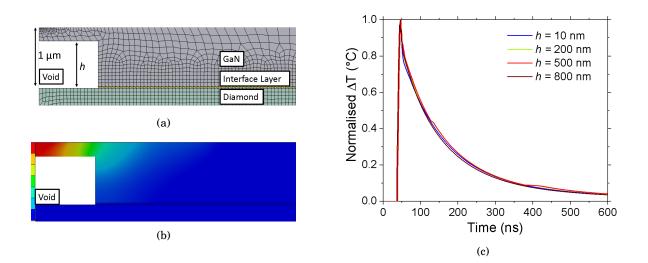

| 4.9  | Sketch of the structures and simulations used to determine the thermal conductivity          |     |

|      | of thin diamond films                                                                        | 91  |

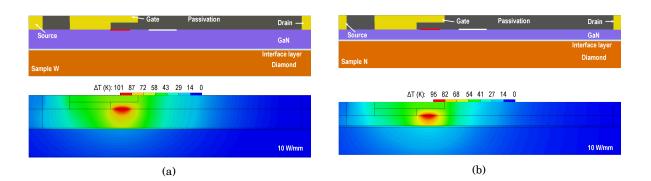

| 4.10 | Simulated structures of the wide and thin buffered GaN-on-diamond devices                    | 95  |

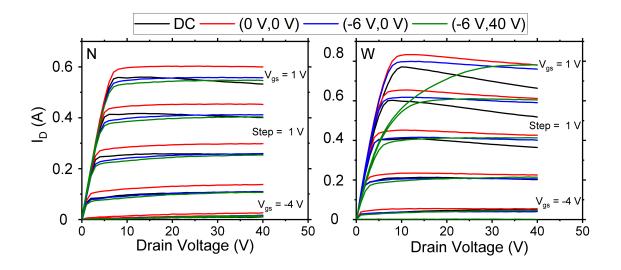

| 4.11 | IV characteristics from both GaN-on-diamond device sets                                      | 97  |

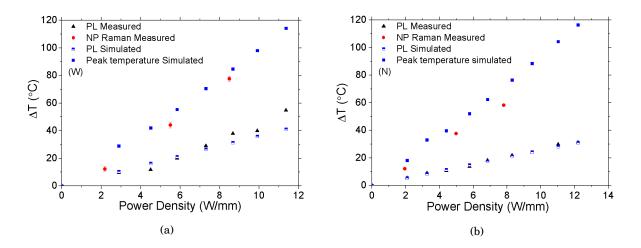

| 4.12 | Data showing the photoluminescence, nanoparticle assisted Raman thermography,                |     |

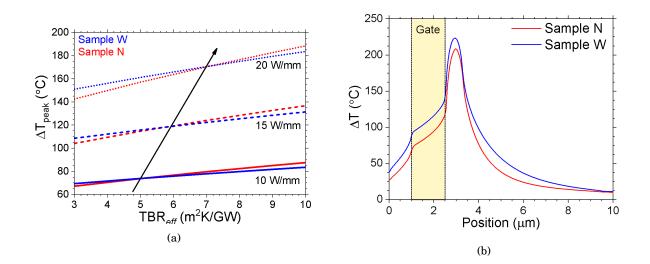

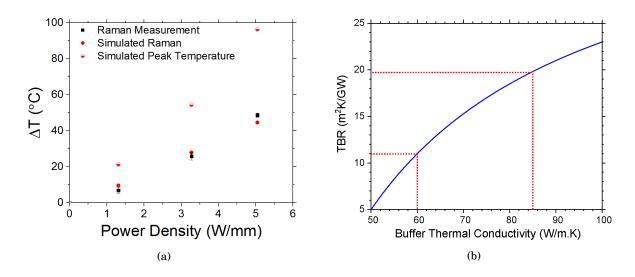

|      | and simulated temperatures in the GaN-on-diamond devices                                     | 98  |

| 4.13 | Simulated temperature profiles showing how the effective thermal boundary resistance         |     |

|      | impacts the optimum buffer thickness, and how the buffer thickness impacts the               |     |

|      | lateral heat spreading.                                                                      | 100 |

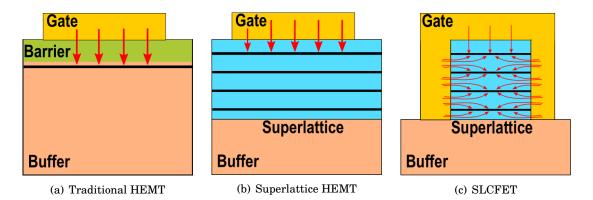

| 5.1  | A comparison of the channel in a HEMT, a superlattice HEMT, and a superlattice             |

|------|--------------------------------------------------------------------------------------------|

|      | castellated FET                                                                            |

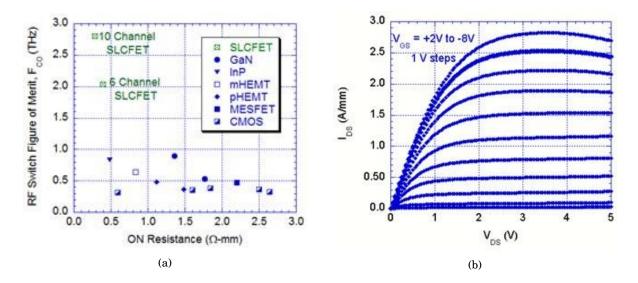

| 5.2  | Cutoff frequency of a superlattice castellated FET compared to the cutoff frequency of     |

|      | other semiconductor switches, and the IV characteristics of superlattice castellated       |

|      | FETs                                                                                       |

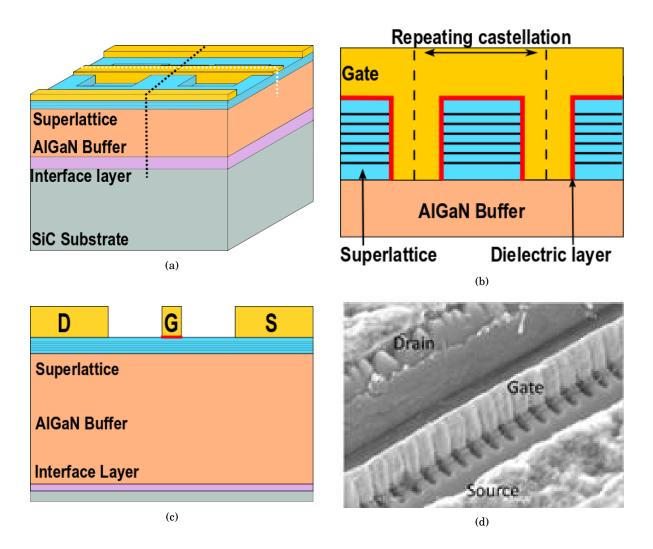

| 5.3  | Schematic diagram of the superlattice castellated FET structure and a SEM microgr-         |

|      | pah of a superlattice castellated FET                                                      |

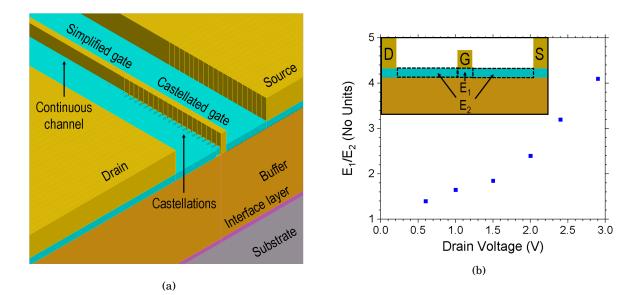

| 5.4  | Diagram showing how the SLCFET is simulated in finite element model, and how the           |

|      | power dissipation is split in the channel between the access region and the gate area. 109 |

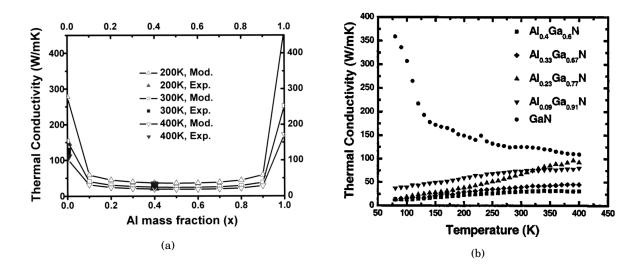

| 5.5  | Data showing the temperature dependent thermal conductivity of AlGaN films with            |

|      | varying aluminium concentration                                                            |

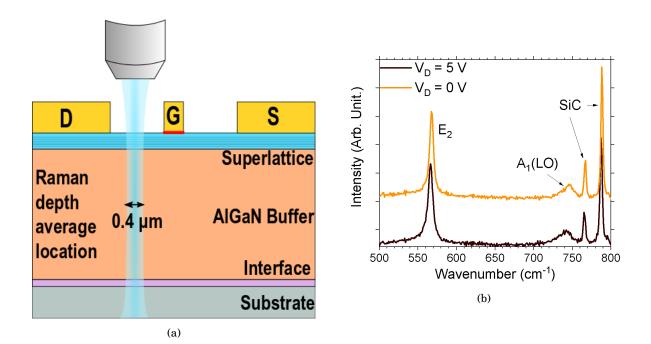

| 5.6  | A sketch showing the location of the micro-Raman thermography measurement, and             |

|      | example spectra taken from a superlattice castellated FET                                  |

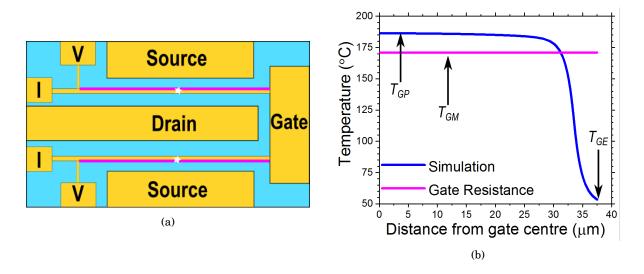

| 5.7  | A sketch of the gate resistance thermometry device structure, and the simulated            |

|      | temperature profile along the gate                                                         |

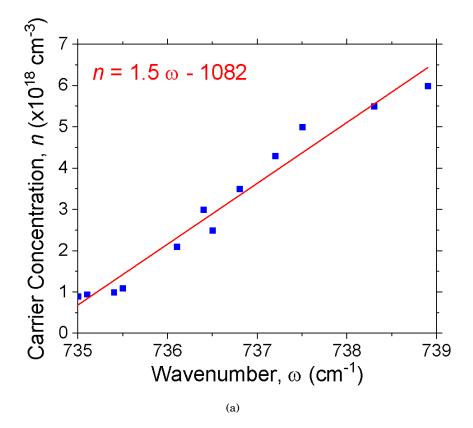

| 5.8  | Data showing the dependence of $A_1(LO)$ peak position on the free carrier concentration   |

|      | in GaN                                                                                     |

| 5.9  | Micro-Raman thermography temperature measurements in superlattice castellated              |

|      | FETs, and the corresponding buffer thermal conductivity and buffer-substrate thermal       |

|      | boundary resistance                                                                        |

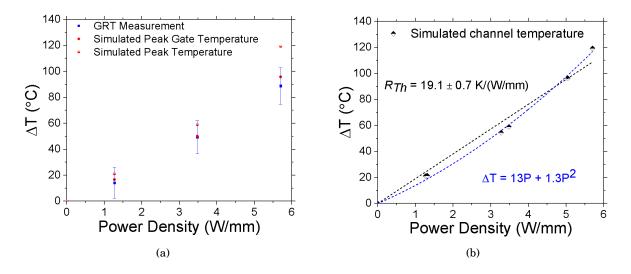

| 5.10 | Gate resistance thermometry measurements and simulated peak temperatures in                |

|      | superlattice castellated FETs                                                              |

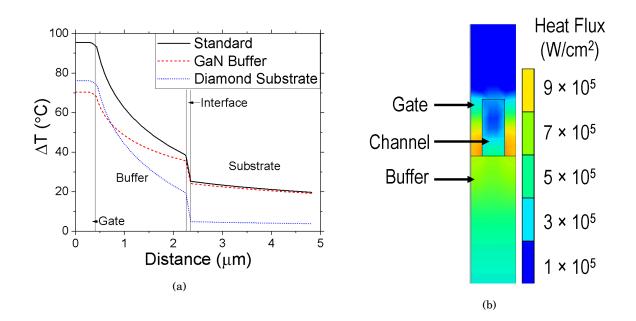

| 5.11 | Simulated temperature profiles through a superlattice castellated FET and the simu-        |

|      | lated heat flux in a castellation within a superlattice castellated FET                    |

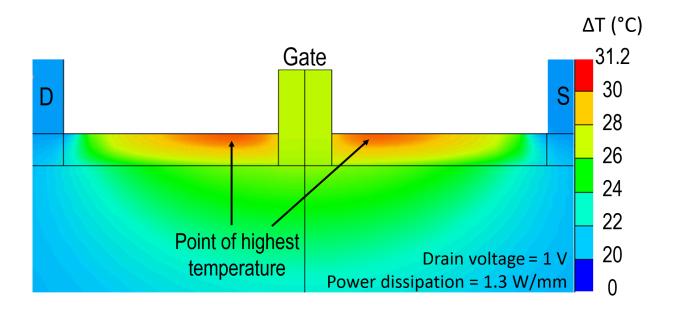

| 5.12 | Simulated temperature profile in a superlattice castellated FET operated in the linear     |

|      | region                                                                                     |

| C 1  | Analyzia of the anostromator induced anostrol buo dening in Demon anostromator             |

| 6.1  | Analysis of the spectrometer induced spectral broadening in Raman spectroscopy             |

|      | measurements                                                                               |

| 6.2  | Phonon dispersion curves for $\beta$ – Ga <sub>2</sub> O <sub>3</sub>                                         | 9 |

|------|---------------------------------------------------------------------------------------------------------------|---|

| 6.3  | An example of the temperature dependence of a Raman mode, and the Raman spectra                               |   |

|      | of $\beta$ – Ga <sub>2</sub> O <sub>3</sub> (100) and ( $\overline{2}$ 01) oriented crystals                  | 0 |

| 6.4  | Measured phonon linewidths from the (100) and ( $\overline{2}01$ ) oriented $\beta-{\rm Ga_2O_3}$ crystals 13 | 1 |

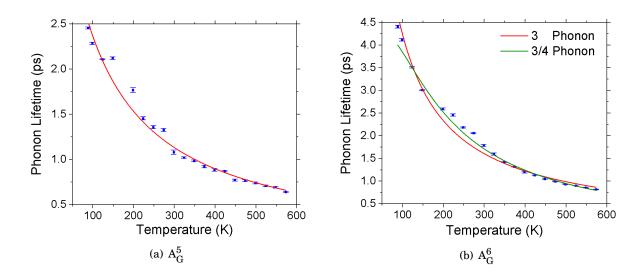

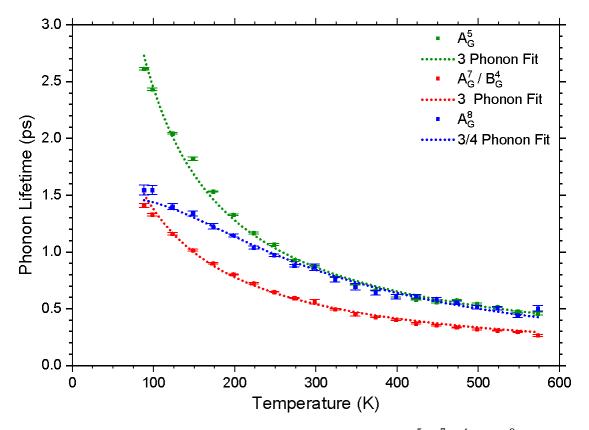

| 6.5  | Temperature dependent phonon lifetimes in the $(\overline{2}01)$ oriented crystal and the associ-             |   |

|      | ated decay fit                                                                                                | 2 |

| 6.6  | Temperature dependent phonon lifetimes in the (100) oriented crystal and the associ-                          |   |

|      | ated decay fit                                                                                                | 3 |

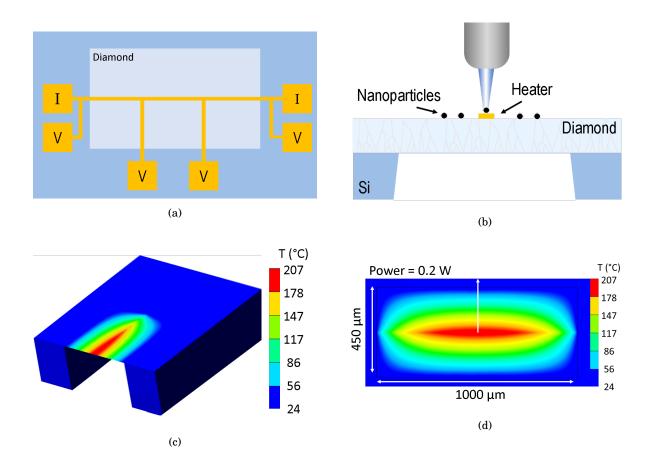

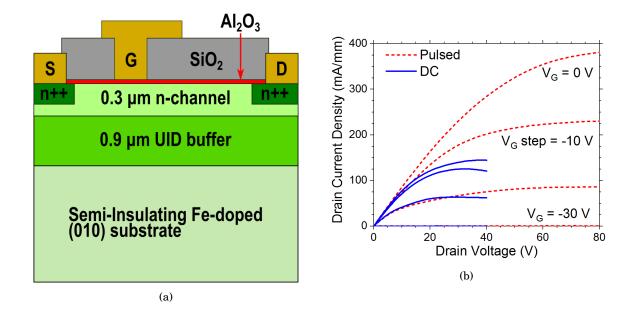

| 6.7  | Schematic diagram of a $\beta$ – Ga <sub>2</sub> O <sub>3</sub> MOSFET                                        | 4 |

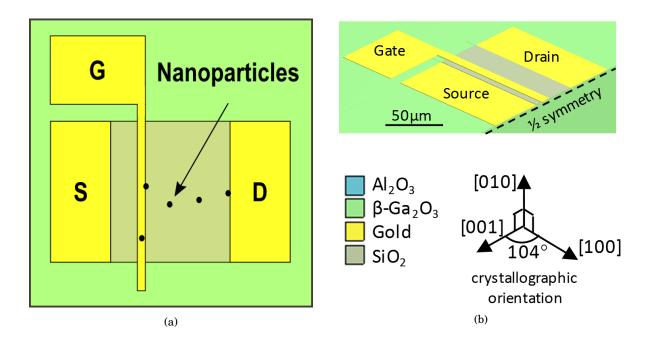

| 6.8  | Sketch of the measured $\beta$ – Ga $_2O_3$ MOSFET, and the nanoparticle assisted Raman                       |   |

|      | thermography measurement locations                                                                            | 6 |

| 6.9  | Measured temperatures used to determine the device thermal resistance and lateral                             |   |

|      | heat spreading                                                                                                | 7 |

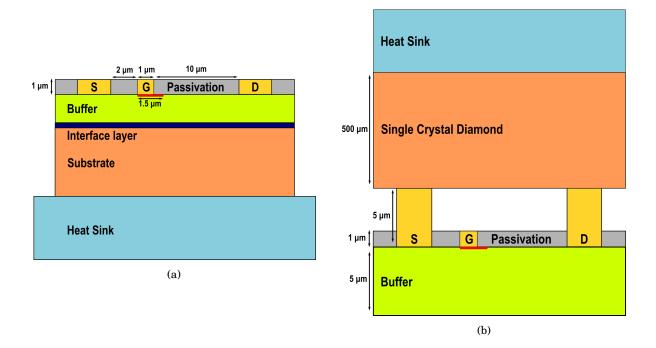

| 6.10 | Finite element modelled device structure in a normal configuration and a flip-chip                            |   |

|      | configuration                                                                                                 | 9 |

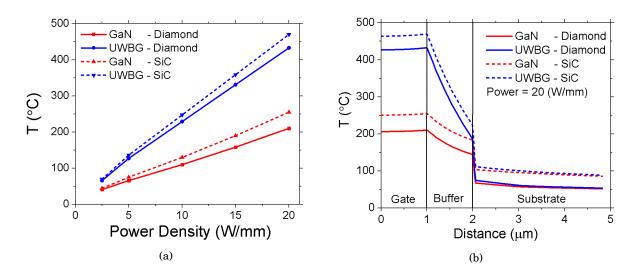

| 6.11 | Simulated temperatures of an ultra-wide bandgap device with a diamond and a SiC                               |   |

|      | substrate                                                                                                     | 2 |

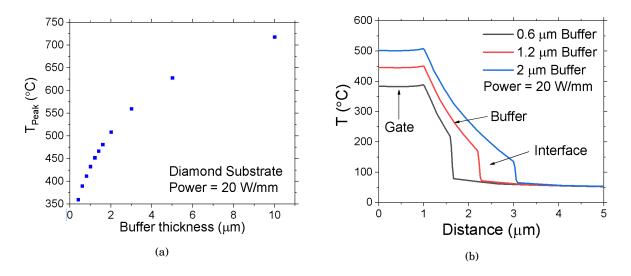

| 6.12 | Simulated temperatures in an ultra-wide bandgap device with varying buffer thickness.14                       | 3 |

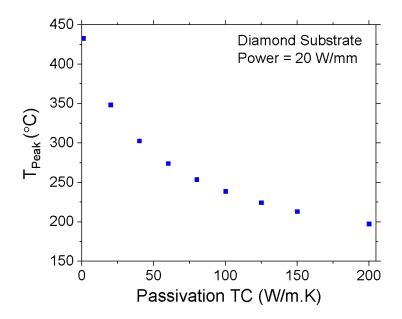

| 6.13 | Simulated temperatures of a device where the passivation has been replaced with                               |   |

|      | diamond of varying quality                                                                                    | 4 |

### INTRODUCTION

# 1.1 Development of high power, high frequency transistors

olid state electronics have been integral to our way of life since the invention of the first point contact transistor at Bell Laboratories in 1947 [1]. That work is most commonly attributed to Shockley, Brattain, and Bardeen, and was followed by a bipolar junction transistor orginally made in germanium due to its lower melting point and higher carrier mobility when compared to silicon, which earned the trio the Nobel prize in physics in 1956 [2]. However germanium's low bandgap (0.67 eV) gave high leakage currents and hence came the first silicon bipolar transistor, developed independently at both Bell Laboratories and Texas Instruments [3]. The theory for Field Effect Transistors (FETs) actually preceded these first transistors, and can be dated back to Lilienfeld in 1928 and then Shockley and Pearson in 1948 [4, 5]. However it was not until 1953 that Dacey and Ross showed the first unipolar FET using germanium. Khang and Atalla then developed the first Metal Oxide Semiconductor Field Effect Transistor (MOSFET) in silicon in 1960, an enabling technology for Complimentary Metal Oxide Semiconductors (CMOS) on which so much of the worlds computing relies today [6].

Although silicon transistors continue to be imperative in our lives, alternative materials with improved fundamental properties have been sought since the early days of the transistor. GaAs technology was used as an alternative for high frequency operation as its electron mobility is almost 6 times higher than that of silicon [7, 8]. MOSFET technology is not compatible with all compound semiconductors as the lack of a native oxide often led to surface traps at the gate, meaning new architectures were required. As a result, the first GaAs MEtal-Semiconductor Field Effect Transistor (MESFET) was fabricated by Mead in 1965, utilising a Schottky gate contact [9]. The desire for higher frequency operation also led to the development of the High Electron Mobility Transistor (HEMT) in GaAs by Mimura *et al* in 1980 [10]. In these devices, the formation of a 2 Dimensional Electron Gas (2DEG) at the interface of a GaAs-AlGaAs heterostructure leads to an enhancement in the electron mobility [11].

Interest in Wide BandGap (WBG) materials developed from the desire for higher power, higher temperature operation. Silicon's 1.1 eV bandgap means that the thermal activation of carriers, which follows an Arrenhius relationship with respect to bandgap, is significantly larger than in materials such as wurtzite gallium nitride (GaN) and 4H silicon carbide (SiC), which have bandgaps of 3.4 eV and 3.2 eV respectively at room temperature [7, 12–14]. The wider bandgap of these materials affords them higher critical fields which allows for higher voltage operation and increased power densities [15]. Of these two WBG materials SiC has the advantage in thermal conductivity with a value of up to 450 W/m.K, compared to 160 W/m.K for GaN [16]. However, issues remain with the cost efficient production of high quality SiC due to basal plane dislocations, although in spite of this 15 kV devices are currently used in power conversion [17]. GaN has an advantage in that heterostructures can be created with AlGaN to allow for the fabrication of HEMTs. This, coupled with its larger bandgap make it ideal for both high power and high frequency applications [18]. In the high power electron device sector, GaN HEMTs will compete with SiC FETs and silicon Insulated Gate Bipolar Transistors (IGBTs) as an enabling technology in fields such as electric vehicle power transformation and high speed charging [19].

An ideal transistor has zero resisitance when it is on, and zero current when it is off. It should also be able to withstand infinite electric fields such that it can block whatever voltage necessary, and to switch between off and on instantaneously. As all materials have a finite breakdown voltage, when exceptionally high voltages must be blocked it is often accomplished in stages, which increases the switching inefficiencies in the circuit. Whilst all wide bandgap materials can operate at higher voltages, GaN offers low ON-resistance and faster switching because of its heterostructures [20]. Ultimately, the maximum operating voltage of GaN power devices is limited by the available GaN buffer thickness, which in turn is limited by the shortage in native substrates. The use of non-native substrates leads to an inherent stress in the GaN layers, meaning there is a critical thickness above which the GaN cracks and delaminates.

In the RF sector GaN technology has been available since 2005, originally on sapphire substrates until SiC substrates were shown to enable devices to operate at significantly higher powers [21, 22]. Whilst GaAs HEMTs perform well at high frequency, the wide bandgap of GaN allows for smaller device footprints and higher operation temperatures [23]. In addition to this, GaN's high mobility allows for higher frequency operation. This makes GaN the material of choice in high power Ku and Ka band applications such as LIDAR, high bandwidth communications, and military uses [18, 24, 25].

However GaN device reliability continues to be a concern. The high drain voltages and small device dimensions result in extremely high electric fields which peak at the gate edge, causing mechanical stress due to GaNs piezoelectricity and activating a range of trap states which degrades device performance [26, 27]. This peak in electric field also causes a local maximum in the power dissipation and temperature. It is important to understand the device channel temperature as device efficiency is impacted by ON resistance and threshold voltage, both of which are temperature dependent. The Mean Time To Failure (MTTF) of a device is also temperature dependent, following the Arrenhius relationship

$$MTTF = A \exp \frac{-E_a}{k_b T},$$

(1.1)

where A is a constant of proportionality,  $E_a$  is the activation energy of the lowest energy failure mechanism which can be thermally induced,  $k_b$  is the Boltzmann constant and T is the channel temperature [28, 29]. Because of this, to ensure the reliability of GaN devices the maximum operating conditions are often de-rated.

The desire for higher and higher power densities, either through increased operating voltage or reduced device footprint, makes near junction thermal management necessary to utilise devices to their full capacity and avoid temperature related accelerated breakdown. Heat extraction from the channel is impeded by low thermal conductivity materials such as the interfaces between epitaxial layers or the epitaxial layers themselves, and their effect can be minimised either by changing the device design or introducing high thermal conductivity elements to aid in heat spreading.

Diamond is often considered as the ideal candidate to assist in effective heat spreading due to is wide bandgap and high thermal conductivity which is the highest known in a bulk material at over 2000 W/m.K [30]. However, the integration of diamond with other WBG semiconductors is non-trivial as there is often a large mismatch in coefficients of thermal expansion, and diamond is also incredibly stiff [31]. In 2010 Francis *et al.* demonstrated the first four inch GaN-on-Diamond wafer with polycrystalline diamond grown onto the GaN as the substrate material [32]. The grain boundaries present in polycrystalline diamond mean it has a somewhat reduced thermal conductivity when compared to single crystal diamond, meaning it is not as efficient at heat spreading. Wafer bonding of single crystal diamond substrates onto GaN has been attempted, although this has not been scaled up to large areas and often results in poor thermal boundary resistances [33–35]. Currently the state-of-the-art GaN-on-polycrystalline diamond devices have a thermal resistance of 10 K/(W/mm), compared to 19 K/(W/mm) for GaN-on-single crystal diamond, and 15 K/(W/mm) for GaN-on-SiC [35, 36].

Whilst the use of diamond is most commonly as a substrate for heat spreading in high power dissipation devices, this is not the only way diamond can be used. Reduced temperatures were demonstrated by Tadjer *et al.* in GaN HEMTs where nanocrystalline diamond films were grown as a passivation layer, before the deposition of the gate [37]. However, they found that the ON-resistance of these devices increased, which was attributed to the diamond putting the channel under tensile stress and creating a non-uniform 2DEG density [38]. Nanocrystalline diamond which has been heavily boron doped has also been used to create a rectifying gate contact which provides decreased on resistance and off state leakage, but also induces a negative threshold voltage shift and adds little in terms of heat spreading due to its small volume [39].

As GaN has entered a more commercial stage in its life cycle, academic research has adjusted to study "generation after next technology", primarily ultra-wide bandgap materials (UWBG) [40]. The major contenders in this field are diamond, gallium oxide (predominantly in its  $\beta$  polymorph) and AlGaN HEMTs (an Al<sub>1-x</sub>Ga<sub>x</sub>N buffer with AlN heterojunction) [30]. Diamond-based devices have long been proposed as the ultimate in power electronics due to the combination of UWBG and exceptional thermal conductivity, however devices have been held back due to a lack of low level dopants and low mobilities [41, 42]. To get around this, attempts have been made to create diamond HEMTs through surface transfer doping and nanometric delta doping. Power dissipation is not likely to be an issue in such devices [43, 44], but power dissipation is likely to be an issue for both AlGaN and  $\beta$  – Ga<sub>2</sub>O<sub>3</sub> devices as both have low thermal conductivities with respect to other semiconductors. In the case of AlGaN, alloy scattering reduces the phonon mean free path and hence the thermal conductivity, with values of approximately 20 W/m.K for alloying concentrations greater than 10% [45].  $\beta$  – Ga<sub>2</sub>O<sub>3</sub> has an anisotropic thermal conductivity which is 27 W/m.K along the [010] direction and 10 W/m.K otherwise [46].

The main theme of this work is understanding and thereby improving the thermal performance of novel FETs by measuring and simulating their temperature profiles. The goal is to aid device development such that they can be utilised efficiently and reliably in an industrial environment. The GaN-on-diamond interface is a key component of wafer epitaxies; if this thermal bottleneck were removed devices would be able to be operated at significantly higher power densities, making them more economically viable. This work improves the understanding of what causes the interface effective thermal boundary resistance, how it can be improved, and how it must be considered in device design. For new materials or devices which are aiming to enter the market it is important that their thermal performance is studied such that reliability concerns can be addressed. Two device structures which have not been thermally characterised are investigated, the superlattice castellated FET and the  $\beta$  – Ga<sub>2</sub>O<sub>3</sub> MOSFET. Both device sets have thermal challenges which must be addressed. The particular problems are identified, and recommendations made for the next generation of device sets.

# **1.2 Thesis outline**

To understand the heat flow in novel FET designs, micro-Raman thermography, nanoparticle assisted Raman thermography, and photoluminescence will be used to probe active device tem-

#### CHAPTER 1. INTRODUCTION

peratures. These measurements will then be combined with finite element simulations of device structures to provide an insight into how the devices behave thermally and to understand their peak temperatures. Finite element simulations will also be used to explore how diamond can be used most effectively with the latest UWBG materials. An understanding of key material parameters in WBG and UWBG systems will also be established by the use of Raman thermometry and transient thermoreflectance.

Chapter 2 will focus on the theoretical background of this work. Phonons and their origins are discussed. The inherent properties, growth, and applications of GaN, AlGaN,  $\beta$  – Ga<sub>2</sub>O<sub>3</sub>, and diamond, the key materials in this work, will be discussed. Each material has its own advantages and challenges that make it suitable for certain applications, and interesting for research and these will be highlighted. A discussion of heat transport will then follow, with reference to the specific nature of heat flow in device structures.

Chapter 3 will explore the experimental techniques utilised in this work, discussing both their theory and laboratory implementations. The two major experimental techniques utilised are Raman scattering, which is used for both spectroscopy and thermography, and photoluminescence, which is also used for thermography. Transient thermoreflectance, which is used for material characterisation, is also explained. Finally the underlying principles behind finite element analysis are discussed. This is used as a tool to further the understanding gained from experimental results, and must be optimised to make the process accurate and efficient.

Following this will be the research segment of this work. Chapter 4 studies how GaN-ondiamond material and devices can be optimised. Transient thermoreflectance is used to measure the effective thermal boundary resistance of GaN-on-diamond systems. Nanoparticle assisted Raman thermography will be employed to measure the temperature profile of suspended thin diamond films which allows for the thermal conductivity of the film to be determined through comparison with finite element simulations. Following this, the thermal resistance of two GaNon-Diamond wafers which have different buffer thickness is determined. Photoluminescence is performed to determine the temperature in the device active area, before finite element analysis is used to determine the device peak temperature. The results show that using ultra-thin buffer layers of as low as 350 nm is not detrimental to device performance. As effective thermal boundary resistances are optimised, thinner buffers have the ability to offer improved thermal and electrical characteristics.

Chapter 5 discusses thermal transport in SuperLattice Castellated FETs (SLCFETs), of which there are no thermal examinations in the literature. The small feature sizes and localised power dissipation in SLCFETs makes heat extraction more complex. Raman thermography is used to measure their buffer temperatures, whilst gate resistance measurements are used to measure gate temperatures. These measurements are used as an input to a finite element simulation of the structures, highlighting how the three dimensional gate structure aids thermal transport by providing a high thermal conductivity heat pipe through to the device buffer.

Finally, Chapter 6 studies the UWBG materials AlGaN and  $\beta$  – Ga<sub>2</sub>O<sub>3</sub>. The lifetimes of certain optical phonons in  $\beta$  – Ga<sub>2</sub>O<sub>3</sub> are determined using Raman spectroscopy. The likely decay mechanisms of these phonon's modes is found by studying the temperature dependence of the lifetime. Nanoparticle assisted Raman thermography is used to show the high thermal resistance of  $\beta$  – Ga<sub>2</sub>O<sub>3</sub> devices. Finite element simulations will then be used to investigate how diamond can be used to address the challenge of efficient heat extraction in these low thermal conductivity materials.

# **MATERIAL AND DEVICE THEORY**

For the analysis of heat transport in high performance electronic devices it is necessary to understand the nature of heat flow, how this is impacted by the materials and device structures used, and how the heat is generated. A discussion of heat flow in metals, semiconductors and amorphous materials is provided, as well as a more in depth discussion on the properties of phonons; the primary heat carrier in semiconductors. For each of the semiconductors studied in this work, the microscopic and macroscopic properties are explored. A discussion of the relevant growth processes and device designs follows this, considering the industrially relevant aspects which impact their use. Finally, these are amalgamated for a discussion on how the device structures generate heat and how this is spread throughout a wafer containing both high and low thermal conductivity elements.

# 2.1 Phonons and heat transport

### 2.1.1 Phonon theory

Phonons are quasiparticles used to describe quantised lattice vibrations. They are a useful tool for understanding heat flow in solids, as heat itself is energy stored in crystals, often through vibrations. Consider an infinite, one-dimensional, monatomic lattice as demonstrated in Figure

FIGURE 2.1. A sketch of a monatomic 1D lattice with the atoms shown in green and the bonds represented by springs with spring constant C. The atomic spacing is a, and the atom n is displaced by an amount  $x_n$

2.1 where each atom is a point mass, the bonds are represented by springs of constant C, and the atoms only interact with their nearest neighbour. If the  $n^{th}$  atom is at position  $x_n$  Newton's second law of motion states that the force of displacement F on this atom is

$$F = m \frac{d^2 x_n}{dt^2},\tag{2.1}$$

where m is the atom's mass. For the central mass of a linear 3 mass system connected by springs, Hooke's law states that the force on this atom will be

$$F = C(x_{n-1} - x_n) - C(x_n - x_{n+1}) = C(x_{n+1} + x_{n-1} - 2x_n)$$

(2.2)

where the subscripts n - 1 and n + 1 refer to the preceding and proceeding atoms in the chain respectively. By equating Equations 2.1 and 2.2 there results a second order differential equation in  $x_n$

$$m\frac{d^2x_n}{dt^2} = C(x_{n+1} + x_{n-1} - 2x_n).$$

(2.3)

By substituting in a trial wave solution of

$$x = Ae^{i(kna-\omega t)} \tag{2.4}$$

where A is the wave amplitude, a is the inter-atomic spacing,  $\omega$  is the frequency of the wave, and k is the wavevector, the differential equation takes the form

$$-\omega^2 m e^{i(kna-\omega t)} = C(e^{i(k(n+1)a-\omega t)} + e^{i(k(n-1)a-\omega t)} - 2e^{i(kna-\omega t)}).$$

(2.5)

By cancelling the common terms in the exponentials this reduces to

$$-\omega^2 m = C(e^{ika} + e^{-ika} - 2).$$

(2.6)

Using Euler's formula to simplify the right hand side and rearranging for the frequency gives

$$-\omega^2 = \frac{C}{m}(2\cos(ka) - 2) = \frac{-2C}{m}(\sin^2(\frac{ka}{2})),$$

(2.7)

where the final step employs the cosine double angle formula. Hence solving for frequency gives the dispersion relation

$$\omega = \sqrt{\frac{2C}{m}} |\sin\frac{ka}{2}| \tag{2.8}$$

confirming the wave like nature of lattice vibrations in crystals, and it is these waves that are named phonons [47].

The Brillouin zone is a tool commonly used in crystallography and the definition of phonons. It is the reciprocal space equivalent of the Wigner-Sietz unit cell in that it defines the smallest repeating unit in the reciprocal lattice. As it is in reciprical space, the size of the Brillouin zone is given in terms of wavevector  $k = \frac{2\pi}{\lambda}$  where  $\lambda$  is the wavelength. The  $\Gamma$  point is always considered the centre of the unit cell where k = 0, and other high symmetry reciprocal lattice directions are denoted by letters. The wavevector-frequency dispersion curves in the Brillouin zone are shown in Figure 2.2 (a). In the one-dimensional, monatomic case considered here the Brillouin zone has width  $k = \frac{\pi}{a}$ . From Equation 2.8 the phonon frequency is zero at the  $\Gamma$  point, at its maximum at the Brillouin zone edge, and is repeating in  $2\pi$ . Phonons of this nature are named acoustic phonons [48].

When a diatomic lattice is considered, the differential equation shown in Equation 2.3 becomes a paired system of two differential equations of the same form. The solution to these equations in matrix form is

$$\begin{bmatrix} 2C - m_1 \omega^2 & -2C \cos ka \\ -2C \cos ka & 2C - m_2 \omega^2 \end{bmatrix} \begin{bmatrix} A_1 \\ A_2 \end{bmatrix} = 0$$

(2.9)

where the subscripts distinguish between the properties of the different atoms of the lattice. There are non-zero solutions to this equation system when the determinate of the matrix on the left hand side is zero, i.e when

$$(2C - m_1 \omega^2)(2C - m_2 \omega^2) - (-2C \cos ka)^2 = 0.$$

(2.10)

This can be rearranged to

$$\frac{m_1 m_2}{2C} \omega^4 - (m_1 + m_2) \omega^2 + 2C(1 - \cos^2 ka) = 0$$

(2.11)

which is a quadratic equation in  $\omega^2$  and hence can be solved by the quadratic equation giving solutions of

$$\omega^{2} = C(m_{1}^{-1} + m_{2}^{-1}) \pm C \sqrt{(m_{1}^{-1} + m_{2}^{-1})^{2} - \frac{4sin^{2}ka}{m_{1}m_{2}}}.$$

(2.12)

This adds an extra branch of solutions to the earlier discussed acoustic phonons as shown in Figure 2.2 (b). At the  $\Gamma$  point the second term under the square root is zero, resulting in

$$\omega_{\Gamma} = \sqrt{C(m_1^{-1} + m_2^{-1}) \pm C(m_1^{-1} + m_2^{-1})}$$

(2.13)

which gives zero when the minus sign is taken but is non-zero when the positive sign is taken. These phonons which have non zero energy at the  $\Gamma$  point are named optical phonons. They can have energy at the Brillouin zone centre as they represent a symmetric oscillation of the two atoms about their lattice point, meaning there is no long range translation. It is these optical phonons that are of interest later in this work as Raman scattering, one of the primary techniques used, probes zone centre phonons. Optical phonons also have higher energy than acoustic phonons as they have higher frequencies, meaning they are the primary heat carrier at room temperature. As is implied by Equation 2.12, the phonon dispersion is still symmetrical about the  $\Gamma$  point although the Brillouin zone now has width of  $k = \frac{\pi}{a}$ , as the two atom system means the unit cell of the 1D lattice now has length 2a. As the complexity of the lattice is increased to more realistic systems, the solutions become more varied, but they are still separated into acoustic and optical phonons. The modes can also be longitudinal, oscillating in the direction of the bond, or transverse, oscillating normal to the direction of the bond and these will have different energies [49].

Another property of phonons which is important for thermal transport is that they have zero spin. This makes them Bosons and as such they obey Bose-Einstein statistics, meaning the population n of an energy level E is given by

$$n(E,T) = \frac{1}{\exp(E/k_b T) + 1}$$

(2.14)

where  $k_b$  is the Boltzmann constant and T is the temperature. As will be discussed in Section 2.1.2, heat transport in a material is dependent on the phonon population as phonons are the dominant heat carrier in many dielectric systems. As Bosons do not obey the Pauli exclusion

FIGURE 2.2. (a) The wavevector-frequency dispersion curve of a monatomic onedimensional lattice in the Brillouin zone. (b) The dispersion curve of a diatomic one-dimensional lattice. There are now two phonon branches known as the acoustic phonons (red) which are linear close to the Brillouin zone centre, and the optical phonons (blue) which are non-zero at the zone centre.

principle they form a Bose-Einstein condensate as T tends to 0 K and hence n tends to zero. This means all phonons will accumulate in their ground state, meaning there will be no thermal carriers. As the temperature increases, the number of carriers increases following Equation 2.14. In the case where the thermal energy  $k_b T \gg E$  the Bose-Einstein statistics approach the Rayleigh-Jeans law which states that

$$n = \frac{k_b T}{E} \tag{2.15}$$

suggesting that the phonon population, and hence the thermal carriers, will increase linearly with temperature.

This is of importance when considering the heat capacity of a dielectric material. Debye theory states that the specific heat capacity tends to a constant value of  $3k_b$  at high temperatures. This value is found from the Dulong-Petit law and is derived from the equipartition theorem which states that the vibrations in all three axis directions will have thermal energy  $k_bT$ . This law holds at temperatures above the Debye temperature, which is defined as

$$T_D = \frac{hv}{2k_b}^3 \sqrt{\frac{6N}{\pi V}}$$

(2.16)

where h is Planck's constant, v is the sound velocity, N is the number of atoms, and V is is the

volume. The Debye temperature physically represents the temperature needed to excite the highest energy vibrational mode. Above this temperature, all the modes are activated and hence the specific heat capacity ceases to increase. However below this value, the specific heat capacity is temperature dependent following approximately a  $T^3$  relationship as the occupation of the modes in three dimensions increases.

### 2.1.2 Heat flow in solids

Phonons also play a crucial role in the thermal conductivity of semiconductors. The thermal conductivity of a material in one dimension x is defined as the  $\kappa$  which relates the heat flux in one dimension  $j_x$  to the temperature gradient in that direction via Fourier's law [50]

$$j_x = -\kappa_x \frac{dT}{dx}.$$

(2.17)

The thermal conductivity can be found by assuming that the quasiparticles carrying the heat in a solid, such as phonons in semiconductors and electrons in metals, act as an ideal gas [49]. These quasiparticles have a flux of  $nv_x$  where n is the number of particles per unit volume and  $v_x$  is their mean velocity. Now consider the situation where these particles are in an area of relative high temperature and are moving to an area of relative low temperature. Once they reach the low temperature area, each of these particles will possess energy equivalent to  $c \times \Delta T$  where c is the heat capacity of a single quasiparticle and  $\Delta T$  represents the difference in temperature between the hot and cold areas. For a particle that travels a distance  $d_x$ , this change in temperature will be the rate of change of temperature with respect to distance, multiplied by that distance, i.e

$$\Delta T = \frac{dT}{dx} \times d_x. \tag{2.18}$$

The flux of heat is the carrier flux multiplied by the carrier energy. Assuming the particles travel a distance  $l_x$  before they are scattered, the heat flux becomes

$$j_x = -nv_x c\Delta T = -nv_x cl_x \frac{dT}{dx},$$

(2.19)

and by comparison with Equation 2.17 it can be seen that

$$\kappa = n v_x c l_x. \tag{2.20}$$

The heat capacity of the quasiparticle gas per unit volume *C* is given by  $n \times c$  which gives

$$\kappa = \frac{1}{3}Cvl, \qquad (2.21)$$

when generalised to three dimensions [48]. Therefore changes in any of these parameters will result in changes in the thermal conductivity. The temperature dependence of a material's thermal conductivity can be explained through the temperature dependence of C, the heat capacity, and l, which is commonly referred to as the mean free path of the quasiparticle. This will now be discussed in more detail for metals, semiconductors, and amorphous materials.

#### Heat transport in metals

Metals are used as contacts and heat sinks in semiconductor devices and as such play a role in heat spreading in high power density electronics. In the case of ideal metals, thermal transport is dominated by free electrons. To understand the thermal properties of metals it is important to understand the energy population statistics of the electrons which are carrying the heat. As electrons are Fermions, they obey Fermi-Dirac statistics which state that the probability of an energy level E being occupied is given by

$$f(E) = \left(\exp\left(\frac{E - E_f}{k_b T}\right) + 1\right)^{-1}$$

(2.22)

where  $E_f$  is the Fermi energy [47]. By definition, the Fermi energy is the energy level which has a 0.5 probability of occupation, as can be seen by setting  $E = E_f$ . In the case where  $E \gg E_f$ the probability of occupation is effectively 0, meaning there are no electrons of sufficient energy to occupy these states. In the case of  $E \ll E_f$  the probability of occupation is 1. An electron in one of these energy levels cannot be thermally excited, as all energy levels within  $k_bT$  of its original energy level are also occupied and as electrons must obey the Pauli exclusion principle the electrons cannot be excited to an already occupied level. Therefore, only electrons which occupy an energy level within  $\approx k_bT$  of the Fermi energy can be excited and the mean energy of thermally active electrons can be approximated as the Fermi energy. As both the Fermi energy  $E_f$ , and the electron effective mass  $m_e$  can be approximated as temperature independent due to the kinetic energy relationship

$$E_f = \frac{1}{2}m_e v_e^2.$$

(2.23)

However, the remaining thermal conductivity parameters from Equation 2.21 are not temperature independent, meaning the thermal conductivity is not constant at all temperatures.

As temperature increases, so does the thermal energy and hence the number of thermally active electrons increases. As stated in Equation 2.20, the specific heat capacity of the electron gas increases as the electron density in that gas increases since there are now more particles which can store energy. This results in an increase in the heat capacity of the metal with the relationship [48]

$$C \propto T.$$

(2.24)

This linear increase competes with the temperature dependence of the electron mean free path, which has two major contributing factors; electron-phonon scattering and defect scattering. At temperatures significantly lower than the Debye temperature of the material the optical phonon population is low meaning the electron scattering is dominated by lattice defects and the mean free path is approximately constant as the number of lattice defects is temperature independent [51]. Electron self scattering interactions are weak at all temperatures and therefore have minimal impact on the thermal conductivity. However as temperature increases and the population of the optical phonon modes increases, the electron-phonon interactions become significant. This causes a decrease in the mean free path with a  $T^{-2}$  dependence at low temperature which then saturates at  $T^{-1}$  once all phonon modes are activated. This  $T^{-1}$  dependence counteracts the heat capacity increase due to the activation of new carriers, resulting in an approximately constant thermal conductivity in metals at room temperature and above. In alloys, the secondary atoms are effectively defects, and as such they limit the electron mean free path resulting in a lower thermal conductivity [51].

#### Heat flow in semiconductors

In materials where there are few free electrons such as the wide and ultra-wide bandgap semiconductors which make up the majority of the devices studied in this work, the main method of heat transfer is through phonons. The thermal conductivity can still be approximated by Equation 2.21 [47]. The heat capacity obeys Debye theory, which results in the thermal conductivity increasing rapidly at low temperatures as the phonon modes are activated, and the mean free path is limited by scattering from static defects or the boundaries of the material. As the temperature approaches the Debye temperature and the heat capacity is approximately constant, the phonon mean free path becomes limited by the interactions of the phonons with themselves. Phonon interactions in crystals must obey conservation of momentum, meaning their wavevectors during interactions are constrained. If two phonons of wavevectors  $\vec{K_1}$  and  $\vec{K_2}$  interact with each other, the wavevector of the resulting phonon  $\vec{K_3}$  is given by the relationship

$$\vec{K}_1 + \vec{K}_2 = \vec{K}_3 + \vec{G} \tag{2.25}$$

where  $ec{G}$  is a reciprocal lattice vector. The simplest type of scattering is called the normal process, shown in Figure 2.3, where  $\vec{K}_3$  exists in the Brillouin zone and  $\vec{G}$  is zero. This type of scattering does not inhibit heat transport as it is simply a linear combination of the momentums of the two orginal phonons [51]. However if  $ec{K}_3$  exists outside of the Brillouin zone it can be the case that  $ec{G}$ does not equal 0 and the wavevector of the resulting phonon is mapped back into the Brillouin zone. This scattering does inhibit the heat flow as the wavevector, and hence the momentum, of the resulting phonon is less than that of the two original phonons, and the non-zero  $ec{G}$  represents a contribution from the phonons to the momentum of the whole lattice. This is called umklapp scattering, with a visual representation shown in Figure 2.3, and it results in a thermal resistance [52]. Only phonons of high enough energy can scatter oustide of the Brillouin zone in this way, which is why there is limited umklapp scattering at low temperatures. As temperature rises the higher energy modes become occupied as described in Equation 2.14 and the phonon mean free path and hence the thermal conductivity sees an exponential decay. As the temperature approaches the Debye temperature all phonon modes are active and the umklapp scattering results in a  $T^{-1}$  decay [48]. It is this umklapp process which dominates at room temperature and above, and hence most material thermal conductivities in this work have a temperature dependence of close to  $T^{-1}$ , although the exponent is often larger than -1 as thermal expansion of the lattice also causes a decrease in the phonon velocity and four phonon process can contribute to a reduced mean free path [51].

FIGURE 2.3. A visual representation of the normal phonon scattering process and the umklapp scattering process. The Brillouin zone is marked by the dashed lines. In the normal process there is no resistance to heat flow. In the umklapp process the phonons scatter outside of the Brillouin zone and interact with a lattice vector G, which inhibits heat flow.

In this work diamond is studied as a passive heat spreader due to its exceptionally high thermal conductivity. More detail will be given on the properties of diamond in Section 2.4, but this high thermal conductivity is due to high phonon velocities  $v_p$  and long phonon mean free paths  $l_p$ , although the heat capacity of diamond is similar to many other semiconductors. The exceptionally high phonon velocities can be sustained as diamond's stiff bonds and low density which, when considering the Hooke's law approximation of bonding, gives a large 'spring constant' and restoring force [53]. These properties result in a phonon velocity which has been measured as high as 17500 ms<sup>-1</sup>, which is 2× higher than in Si and 1.5× higher than in silicon carbide [54]. The long phonon mean free path is due to a low probability of umklapp scattering relative to other semiconductors. One model for the umklapp scattering frequency  $\tau^{-1}$  is

$$\tau^{-1} = B\omega^2 T e^{-T_D/3T},\tag{2.26}$$

where  $\omega$  is the phonon frequency,  $T_D$  is the Debye temperature, and T is the temperature. The value B determines the likelihood of umklapp scattering, and can be approximated by

$$B = \frac{\hbar \gamma^2}{M v_p^2 T_D} \tag{2.27}$$

where M is the average atomic mass and  $\gamma$  is the Grüneisen parameter [55]. In addition to the large sound velocities possible in diamond, the Debye temperature is also relatively large. The

average Grüneisen parameter describes how the phonon properties vary with volume and for diamond is of a similar magnitude as for other semiconductors, making the overall umklapp scattering probability low [54].

#### Heat flow in amorphous solids

In a device stack, amorphous materials such as silicon nitride are often used in passivation layers or gate dielectrics where they are adjacent to the heat source, and in interfacial layers to non-native substrates as their amorphous nature means they are insulating, preventing leakage currents, and they can conform to their surrounding structures [56]. In both cases, although the amorphous layer is very thin (nanometre scale), it can still pose a problem for heat flow as they have thermal conductivities of approximately 1 W/m.K. This low thermal conductivity is caused by the lack of long range order inherent in amorphous materials. The quasi-random arrangement of atoms means that phonons cannot be sustained over long periods, and electrons are still bound to their ion cores. This results in a lack of available heat carrying quasi-particles and instead the majority of heat diffuses through the material, which is a slower process [57].

# 2.2 GaN and AlGaN high electron mobility transistors.

### 2.2.1 Material properties

Gallium nitride (GaN) is a III-V compound semiconductor which is studied in this work as the buffer and channel material for HEMTs. It has a metastable zinc blende allotrope, but more commonly exists in a hexagonal wurtzite structure, shown in Figure 2.4, which is used for devices and hence will be the focus of the following discussion [58]. The wurtzite unit cell contains a pair of gallium atoms and a pair of nitrogen atoms with a bond length of 1.95 Å, a *c* parameter of 5.19 Å and an *a* parameter of 3.19 Å [59]. One of the key reasons that GaN is considered an exciting option for high performance electronics is that it has a wide bandgap of 3.4 eV, which is over 3 times that of silicon (1.1 eV) and two and a half times that of gallium arsenide (1.4 eV). A key property of the III-nitride semiconductors is that they can be alloyed together to give a continuous range of possible bandgaps ranging from the 0.7 eV of InN to the 6.2 eV of AlN

FIGURE 2.4. Wurtzite structure of GaN with gallium atoms in red and nitrogen in blue.(a) shows the structure from the m-plane and (b) shows the structure from the c-plane.

[60]. This tunability has already made GaN a key opto-electronic material in LEDs, but it is also important in transistors as it allows for the formation of heterostructures [61]. GaN has a refractive index which varies from 2.25 in the far infra-red to 2.615 at its bandgap edge, which can make light extraction difficult [62].

The GaN band structure is shown in Figure 2.5. The curvature of the conduction and valence bands can be used to predict the mobility of the electrons and holes respectively, as carrier effective mass is proportional to the second derivative of the dispersion relation. Based on this it would be predicted that electrons are more mobile than holes, and that proves to be the case with reported electron mobilities in undoped GaN of  $1150 \text{ cm}^2 \text{V}^{-1} \text{s}^{-1}$  and hole mobilities of  $170 \text{ cm}^2 \text{V}^{-1} \text{s}^{-1}$  literature [63, 64]. These values are lower or comparable to narrow bandgap semiconductors such as silicon, germanium and gallium arsenide, but are higher than GaN's main wide bandgap competitor SiC, which has an electron mobility of 700 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> [15]. Furthermore the AlGaN/GaN heterostructure, a key factor in high electron mobility transistors, gives an enhancement to these mobilities, and this will be discussed in more detail in Section 2.2.4.

The mechanical properties of semiconductors impacts the fabrication of hetero-epitaxial

FIGURE 2.5. The electronic band structure of wurtzite GaN along high symmetry directions. There is a direct bandgap along the  $\Gamma$  direction of 3.4 eV. Image adapted from Yeo *et al.* [65]. Reprinted with permission from AIP Publishing.

wafers, where strain is often incorporated during the growth processes. GaN has a fracture toughness of 0.8 MPa.m<sup>1/2</sup> and a direction averaged Young's modulus of 287 GPa. The elastic constants of GaN suggest it is less stiff than AlN and BN, but is otherwise more stiff than most other compound semiconductors [66]. A more stiff material can be difficult to integrate with other semiconductors as it can result in greater amounts of strain at interfaces when they expand and contract at different rates. This is most commonly seen in wafer fabrication when the materials are integrated at high temperatures and have different coefficients of thermal expansions. GaN has a room temperature coefficient of thermal expansion of  $3.95 \times 10^{-6}$  K<sup>-1</sup> in the a-plane and  $3.53 \times 10^{-6}$  K<sup>-1</sup> in the c-plane, which is comparable with most compound semiconductors [15, 67].

The thermal conductivity of GaN was found to be heavily dependent on the dislocation density present in the material. Zou *et al.* found that below densities of  $\approx 10^{11}$  cm<sup>-3</sup> the room temperature thermal conductivity was constant at approximately 160 W/m.K, but at higher dislocations it dropped off rapidly with values of 30 W/m.K at dislocation densities of  $\approx 10^{13}$  cm<sup>-3</sup> [68]. Computational methods have found ideal thermal conductivities of 180 W/m.K and phonon mean free paths of approximately 50 nm [69, 70]. Materials with higher thermal conductivities are desirable since the heat which is generated during device operation can be extracted more efficiently from hot spots and this will result in lower device temperatures. The GaN thermal

conductivity values are comparable to silicon, but lower than silicon carbide, meaning thermal management must be considered more carefully in GaN devices. The heat capacity of GaN is 0.44 Jmol<sup>-1</sup>K<sup>-1</sup>, and its Debye temperature is 912 K [70].

#### 2.2.2 Material synthesis

As it stands, bulk growth of GaN is expensive and difficult when compared to silicon which limits its scalability in terms of industrial production. Whereas other semiconductors such as silicon can be synthesised through cost effective melt-growth techniques, the high binding energy of the Ga-N bond means GaN is susceptible to decomposition rather than melting except at high pressures [71, 72]. Melt growth techniques can provide low cost material because the growth rate is high and large area synthesis is possible, and the material is typically of high quality as the defects do not crystallise. Whilst melt growth techniques are desirable, alternative methods must be sought for GaN synthesis. The synthesis of GaN can be split into two main branches, the growth of bulk GaN which can be used for substrates and the growth of GaN films which can be used as active layers in devices.

There are four main techniques for growing bulk GaN, and as these cannot be from the melt they focus on the crystallisation of GaN on seeds from a solution or a gas phase. Ammonothermal growth is very commonly used. In this process a GaN containing starting mixture is heated in super-critical ammonia until it dissolves. It then moves via convection to a hotter part of the growth chamber and crystallises on the GaN seeds located there [73]. For ammonia to become supercritical it requires pressures of approximately 250 MPa and temperatures of approximately 500°C, which is the lowest growth temperature of all the bulk growth techniques discussed here. An alternative which uses higher pressures of approximately 2 GPa and temperatures of approximately 1400°C is High Nitrogen Pressure Solution (HNPS) growth, where the nitrogen is instead dissolved in a gallium solution containing GaN seeds. The seeds are placed in a cooler part of the chamber, so when the nitrogen in the solution reaches them via convection, it is in a supersaturated state which drives crystallisation on the seeds [74]. The third solution growth technique is the sodium flux technique, which uses the lowest pressures at between 5 and 10 MPa and temperatures of approximately 750°C. In this technique GaN synthesises on a seed from a starting solution consisting of gallium and sodium nitride. The mixture is heated in an isolated environment containing the GaN seed until a melt is created. The GaN then crystallises on the seed as the temperature is reduced [75]. Of these growth techniques ammonothermal growth appears to be the most industrially scalable, although the sodium flux technique has been used to produce free standing 6-inch high quality GaN crystals [76]. Denis *et al.* report that HNPS and sodium flux can give lower dislocation densities than ammonthermal growth, but that all techniques can incorporate significant oxygen concentrations if care is not taken, which can reduce wafer resistivity [72].

A common alternative to these solution crystallisation techniques is the gas phase crystallisation technique Hydride Vapour Phase Epitaxy (HVPE). HVPE growth takes place in a chamber filled with an inert gas, where the precursor materials flows in a gaseous form. The first step is to flow chlorine gas over a solid gallium source such that they react and form gallium chloride gas. Separately, ammonia is introduced into the system, and mixes with the gallium chloride in a high temperature zone of the chamber. This gas mixture then flows to the seed crystal which is in a cooler part of the chamber to encourage GaN nucleation [77]. The advantages of HVPE, that high quality material can be grown very quickly at growth rates up to 1870  $\mu$ m h<sup>-1</sup>, have led to HVPE becoming the most common technique for the growth of commercial GaN substrates [78, 79]. However a major issue with HVPE technology is the seed crystal on which the GaN grows epitaxially. If the seed is not GaN, the growth can still occur hetero-epitaxially but there will be an inherent wafer bow caused by the difference in coefficient of thermal expansion of GaN and the host substrate of choice, which makes device processing difficult [77, 80]. Alternatively, a GaN crystal can be used as the seed. It is common to use a GaN substrate grown via the ammonothermal process as this will be unstressed, but the growth area is limited by the seed size. Ammonothermal crystals can also have high dislocation densities which will then propogate through the HVPE grown material [20, 79].

## 2.2.3 Wafer epitaxy

An alternative to bulk GaN growth is to grow the GaN device layers hetero-epitaxially on substrates such as silicon, silicon carbide, or diamond. Because of the high material quality and high level of control necessary for the GaN device layers, gas phase crystallisation techniques are preferred to the solution crystallisation techniques discussed in Section 2.2.2. Whilst HVPE has many advantages for bulk GaN growth, the highly reactive chloride bond means it lacks the control necessary for device layers where layer thickness can be of the order of nanometres and the dopant profile must be carefully controlled [81]. Therefore the two most common techniques for growth of GaN device epitaxies are Metal Organic Vapour Phase Epitaxy (MOVPE) and Molecular Beam Epitaxy (MBE). In MOVPE metal organic compounds containing gallium and nitrogen flow across the substrate in a hydrogen carrier gas and nucleate [82]. The growth takes place in a low pressure chamber ( $\approx$  100 Torr), and with the precursor gases mixed with a hydrogen carrier gas. This has the benefit of producing high quality, atomically flat material which grows quickly and is easy to dope [83]. MBE differs in that the growth takes place at ultra-high vacuum ( $\approx 1 \times 10^{-9}$  Torr) and there is no carrier gas. Pure elemental sources are disassociated in their own feed chambers with controllable shutters, and when the shutter is open the elemental radicals diffuse to the substrate and nucleate. The ultra-high vacuum is necessary to give the feed elements a long mean free path and ensures the purity of the grown material. The shutter system means dopants can be easily controlled and sharp interfaces can be formed [84]. MBE also has the advantage that there is minimal waste material. Originally, MOVPE produced higher quality material, but this is no longer the case and the main disadvantage to MBE comes from the requirement for ultra-high vacuum which can cause production issues in commercial environments [83]. Current research into MBE growth centres on the nitrogen source used. Ammonia is commonly used but this causes impurity corporation, whilst nitrogen plasma sources are difficult to control.

The substrate used for GaN wafers has implicatons for the rest of the device epitaxy, meaning the device application should be considered when choosing the design. For instance if cost is the driving factor, silicon is the cheapest available substrate and provides an option for integration into the already existing CMOS infrastructure, although GaN growth uses [111] substrates and CMOS uses [100] substrates [20]. Silicon carbide and diamond are more suitable for high performance electronics as both have high thermal conductivities making them suitable for applications which require high power densities and enhanced reliability such as LIDAR for autonomous vehicles and high bandwidth satellite communications [21, 32]. Vertical devices are sometimes preferred for high voltage applications in which case GaN substrates are preferable as they have less stress meaning thicker device layers can be grown. Vertical structures are typically used for power devices as it is desireable for electric fields to be as large as possible. Interfaces are often points of breakdown as they contain defect states, as is the substrate if it has a smaller bandgap than GaN. As a result, GaN-on-GaN devices will typically have higher operating voltages than GaN on non-native substrates. Homoepitaxial material can also have fewer threading dislocations which are electrically active and provide direct leakage paths through the device [63, 85].

As the devices studied for this work are designed for high power density RF applications, the focus will be on diamond and silicon carbide substrates. GaN can be grown directly onto silicon carbide with the help of an AlN interface layer, however the most common approach for GaN-on-diamond devices is to grow GaN on silicon, attach a handle wafer to the GaN surface, remove the silicon, grow the diamond on the GaN, and then remove the handle wafer [86]. This process is discussed in more detail later in Section 4.3, however it is clear that for both GaN-on-diamond and GaN-on-SiC, good quality GaN growth on silicon and silicon carbide is imperative. In both cases there is a nucleation layer such as a 100 nm AlN film at the interface between the GaN and the substrate to prevent silicon diffusion and to isolate the devices from the substrate [87].

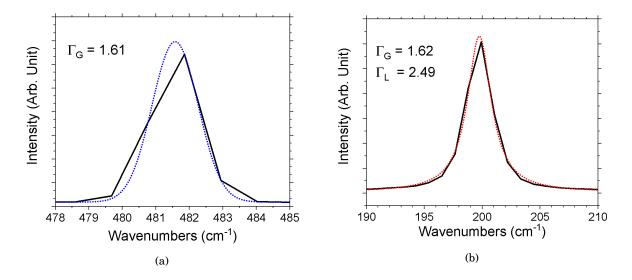

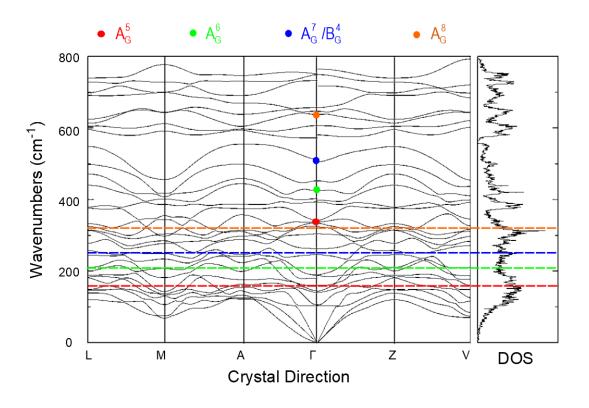

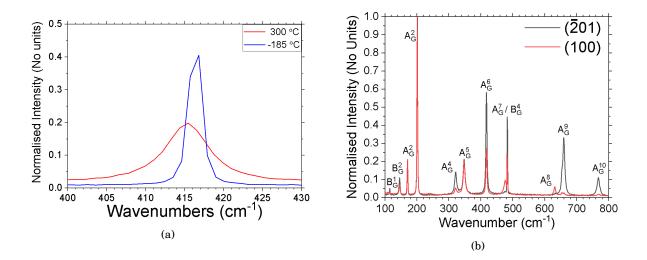

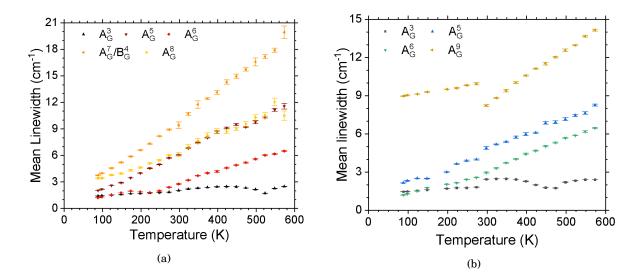

Due to the mismatch in the lattice parameter and the coefficient of thermal expansion between the GaN and the substrate there will be an inherent stress in hetero-epitaxial GaN layers once the wafer is cooled back to ambient conditions. This must be managed as stress can limit the buffer thickness, the maximum operating voltage, and the 2DEG properties since it can alter the piezoelectric polarisation at the AlGaN/GaN heterojunction [20, 88]. To counter this, strain relief layers are often incorporated in the device structure. These can be either a graded AlGaN layer, where the Al concentration decreases gradually from the interface layer to the GaN buffer, or an AlGaN superlattice where the Al concentration reduces with each layer as you move away from the interface [89, 90]. As well as managing stress, such layers also reduce the dislocation density at the heterojunction since the reducing Al content changes the stress environment in the material which causes the dislocations to divert away from the growth axis and eliminate each other.