# Design Techniques for High-Speed ADCs in Nanoscale CMOS Technologies

Ph.D. Thesis by Alper Akdikmen

Advisor: Prof. Edoardo Bonizzoni Co-Advisor: Ing. Matteo Signini PhD Coordinator: Prof. Guido Torelli

University of Pavia Ph. D. School in Microelectronics XXXI Cycle

To my mother & my father

### Acknowledgements

First of all, I would like to thank my advisor Prof. Edoardo Bonizzoni for all the guidance he has provided and for all the support and the opportunities he has given me during my Ph.D. studies and before. I am very grateful to him.

I am grateful to Prof. Franco Maloberti for his technical guidance and for giving me the opportunity to write my Master's Thesis under his supervision. That opportunity eventually opened the way for this Ph.D. position. I am very glad that I have known him and I have been able to work with him.

I would like to thank my co-advisor from industry, Matteo Signini, and to all the others from the ADG-ADD Castelletto R&D Group at STMictoelectronics; Claudio Bona, Simone Bianchi, Antonella Canobbio, Mario Nicotera and Gianluigi Boarin for all their help and guidance during the project that I have done with them. It would not be possible to finalize it in a really short time if there was not their huge effort.

I had the pleasure to work with the then PhD fellow Dante Muratore and it resulted in a valuable publication. I would like to thank him for being such a good colleague.

I would like to thank all the good friends from the IMS Lab at University of Pavia, whom I have known through the years. To name some of them, Arun, Nicola, Yilkal, Waqar, Elisabetta, Flavio and also Prof. Alessandro Cabrini. It was always a pleasure to have them nearby for a little chit-chat and a cup of coffee. I also would like to thank Prof. Malcovati for always being available for helping.

I would like to thank Farshad and İbrahim for their very precious friendship. They were fellows from the Istanbul Technical University, then they have become fellows in PhD. I am very glad that I had the occasion to get to know them better during these last few years in Pavia.

I would like to thank my family, especially to my father İzzet, my mother Kadriye and my sister Merve, also my friends from Turkey whom I consider as a part of my family; for their endless love and support during long years of study away from them and making me feel their warmth each and every time.

Last but not least, I feel very fortunate to have you, Valentina, beside me during all these years. It would not be the same without you. Thank you.

## Contents

| 1 | Intr | oduction                                                         | 1  |

|---|------|------------------------------------------------------------------|----|

|   | 1.1  |                                                                  | 1  |

|   | 1.2  | 6                                                                | 3  |

|   | Refe | erences                                                          | 4  |

| 2 | An 8 | 8-bit 700 MS/s Sub-ranging Flash-SAR ADC in 65nm CMOS            | 5  |

|   | 2.1  | Introduction                                                     | 5  |

|   | 2.2  | 1                                                                | 6  |

|   | 2.3  |                                                                  | 8  |

|   |      | 5                                                                | 8  |

|   |      |                                                                  | 9  |

|   |      | 1                                                                | 0  |

|   |      |                                                                  | 1  |

|   | 2.4  | Preamp with threshold generation for the multi-bit per cycle SAR |    |

|   |      |                                                                  | 2  |

|   | 2.5  |                                                                  | 7  |

|   |      |                                                                  | 7  |

|   |      |                                                                  | 8  |

|   |      | 1                                                                | 8  |

|   |      | I I I I I I I I I I I I I I I I I I I                            | 9  |

|   |      |                                                                  | 4  |

|   |      | 1 1                                                              | 6  |

|   |      | 8 8                                                              | 8  |

|   |      | 2.5.3 Measurement Results 3                                      | 1  |

|   | 2.6  |                                                                  | 6  |

|   | Refe | erences                                                          | 8  |

| 3 | A Ti | iming Skew Calibration Method for Time-Interleaved FATI ADCs 4   | .3 |

|   | 3.1  | Introduction 4                                                   | .3 |

|   | 3.2  | Timing Skew Calibration in Time-Interleaved ADCs 4               | 4  |

|   | 3.3  | Timing Skew Calibration Techniques for FATI ADCs 4               | 6  |

|      | 3.4   | 3.4.1 Two channel time-interleaved FATI ADC                     | 47<br>47 |

|------|-------|-----------------------------------------------------------------|----------|

|      |       |                                                                 | 49       |

|      | 3.5   |                                                                 | 50       |

|      | 3.6   |                                                                 | 50       |

|      | 3.7   |                                                                 | 53       |

|      | 3.8   |                                                                 | 54       |

|      | 3.9   |                                                                 | 56       |

|      | Refe  | rences                                                          | 57       |

| 4    | 40 N  | 1Hz BW, 70 dB SNDR CT $\Sigma \Delta$ M ADC in 28nm FD-SOI CMOS | 59       |

|      | 4.1   |                                                                 | 59       |

|      | 4.2   |                                                                 | 62       |

|      |       | •                                                               | 62       |

|      |       |                                                                 | 63       |

|      |       | 1                                                               | 65       |

|      |       | •                                                               | 65       |

|      |       | 1                                                               | 66       |

|      |       |                                                                 | 67       |

|      |       |                                                                 | 67       |

|      | 4.3   |                                                                 | 68       |

|      |       |                                                                 | 68       |

|      |       |                                                                 | 71       |

|      |       | 8                                                               | 75       |

|      |       |                                                                 | 78       |

|      |       |                                                                 | 82       |

|      |       |                                                                 | 88       |

|      | 4.4   |                                                                 | 91       |

|      |       |                                                                 | 94       |

| _    | G     |                                                                 | ~-       |

| 5    |       |                                                                 | 97       |

|      | 5.1   |                                                                 | 97       |

|      | 5.2   |                                                                 | 98       |

|      |       |                                                                 | 98       |

|      |       | 8                                                               | 99       |

|      | _     |                                                                 | 99       |

|      | Refe  | rences 10                                                       | 00       |

| List | of Pu | ublications                                                     | 01       |

х

## List of Figures

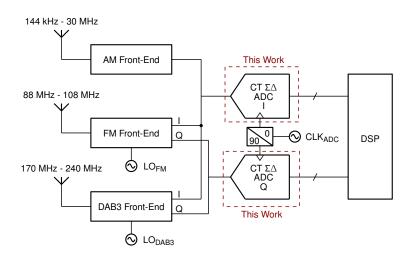

| 1.1  | A software-defined radio receiver                                     | 2  |

|------|-----------------------------------------------------------------------|----|

| 2.1  | Block diagram and timing diagram of a conventional SAR ADC            | 6  |

| 2.2  | Multi-bit/cycle SAR ADC with multiple CDACs [22]                      | 9  |

| 2.3  | Multi-bit/cycle SAR ADC with resistive DAC [15].                      | 10 |

| 2.4  | Multiple threshold generating preamplifier concept.                   | 11 |

| 2.5  | 2-bit/cycle implementation of the preamplifier.                       | 13 |

| 2.6  | 3-bit/cycle implementation of the preamplifier.                       | 13 |

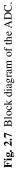

| 2.7  | Block diagram of the ADC.                                             | 16 |

| 2.8  | Successive-approximation path of the ADC (Taken from [32])            | 18 |

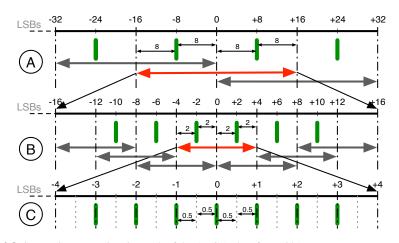

| 2.9  | Dynamic voltage sense amplifier latch (Strong-ARM latch) [35]         | 19 |

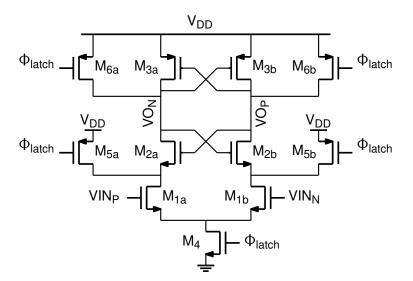

| 2.10 | Improved Strong-ARM latch [38].                                       | 21 |

| 2.11 | Empirical $t_{cmp,std}$ and $t_{cmp,imp}$ as a function of $I_{SS}$   | 23 |

| 2.12 | Transient output comparison of the standard and the improved          |    |

|      | sense amplifier latch                                                 | 23 |

| 2.13 | Kickback noise improvement over the conventional Strong-ARM           |    |

|      | latch as a function of the resistive divider unit resistance when the |    |

|      | improved Strong-ARM latch is used                                     | 24 |

|      | Kickback mismatch issue in flash ADC                                  | 25 |

| 2.15 | Kickback mismatch compensation in flash ADC with CMOS ref.            |    |

|      | sampling switch (a) and NMOS ref. sampling switch (b)                 | 26 |

|      | Post-layout systematic DNL of the flash ADC.                          | 27 |

| 2.17 | Schematic of the multiple-threshold generating preamplifier with      |    |

|      | dummy input differential pair.                                        | 28 |

| 2.18 | Schematic and timing diagram of the timing logic based on a clock     |    |

|      | divider                                                               | 29 |

|      | Switch driving registers. (a) MSBs section. (b) ISBs section          | 30 |

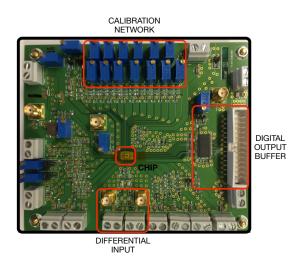

|      | Die photo of the fabricated chip.                                     | 31 |

|      | Evaluation board.                                                     | 32 |

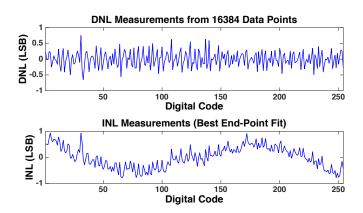

| 2.22 | Measured DNL and INL.                                                 | 32 |

| 2 22 | Manager dispersion of f 500 MS/s for f 22 MU                                                                   |          |

|------|----------------------------------------------------------------------------------------------------------------|----------|

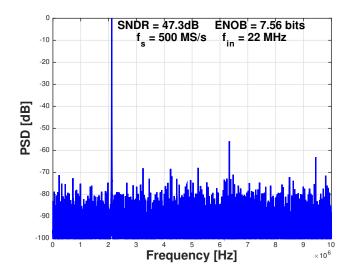

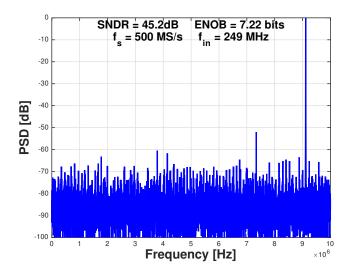

| 2.23 | Measured output spectrum at $f_s = 500$ MS/s for $f_{in} = 22$ MHz<br>(Output decimated by 25x, 16384 pt. FFT) | 33       |

| 2.24 | Measured output spectrum at $f_s = 500$ MS/s for $f_{in} = 249$ MHz                                            | 55       |

|      | (Output decimated by 25x, 16384 pt. FFT).                                                                      | 33       |

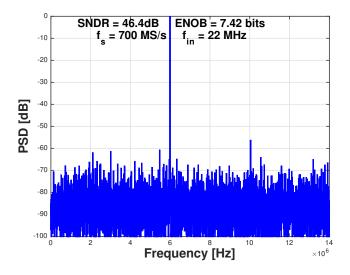

| 2.25 | Measured output spectrum at $f_s = 700$ MS/s for $f_{in} = 22$ MHz                                             |          |

|      | (Output decimated by 25x, 16384 pt. FFT).                                                                      | 34       |

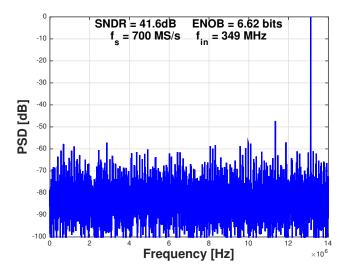

| 2.26 | Measured output spectrum at $f_s = 700$ MS/s for $f_{in} = 349$ MHz                                            |          |

|      | (Output decimated by 25x, 16384 pt. FFT)                                                                       | 34       |

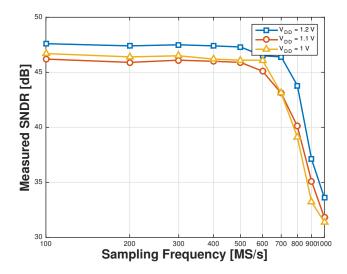

| 2.27 | Measured SNDR as a function of the sampling frequency for                                                      |          |

|      | different supply voltages.                                                                                     | 35       |

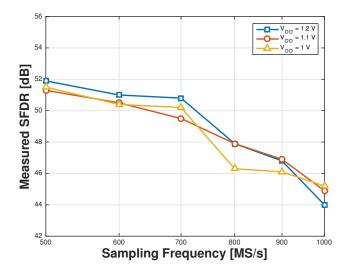

| 2.28 | Measured SFDR as a function of the sampling frequency for                                                      | 25       |

| 2 20 | different supply voltages.                                                                                     | 35       |

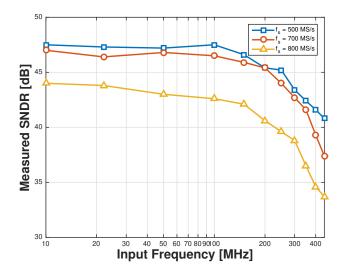

| 2.29 | Measured SNDR as a function of the input frequency for different                                               | 26       |

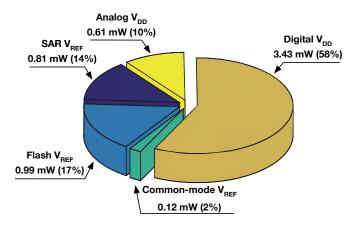

| 2 30 | sampling frequencies<br>Power breakdown of the ADC                                                             | 36<br>36 |

| 2.50 | rower breakdown of the ADC.                                                                                    | 50       |

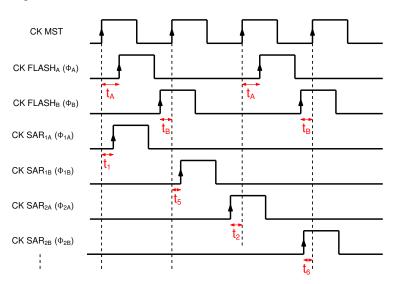

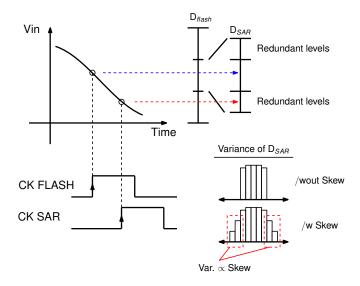

| 3.1  | Block diagram of a two channel time-interleaved FATI ADC                                                       | 44       |

| 3.2  | Clock phases of a two channel time-interleaved FATI ADC                                                        |          |

|      | depicted in Fig. 3.1                                                                                           | 45       |

| 3.3  | The calibration technique proposed in [16]                                                                     | 47       |

| 3.4  | Tabular representation of the calibration phases of the proposed                                               |          |

|      | method.                                                                                                        | 48       |

| 3.5  | Proposed timing skew calibration technique (inputs and outputs of                                              | 40       |

| 20   | flash ADCs and SAR ADCs are omitted for the sake of simplicity)                                                | 49       |

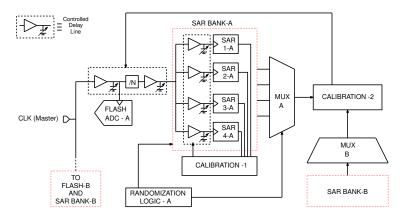

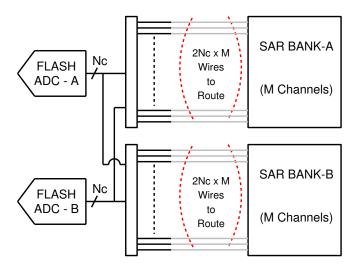

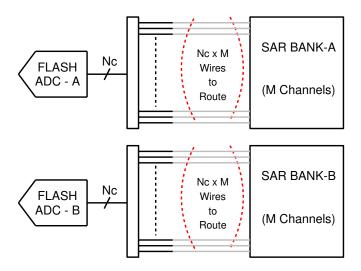

| 3.6  | Congestion due to channel randomization in time-interleaved FATI<br>ADC.                                       | 51       |

| 3.7  | Bank channel randomization in time-interleaved FATI ADC.                                                       | 51       |

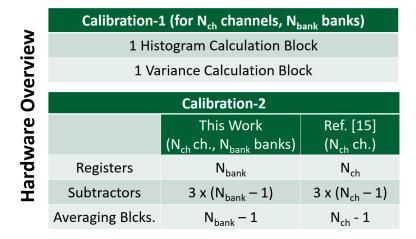

| 3.8  | The hardware overview of the proposed technique.                                                               | 52       |

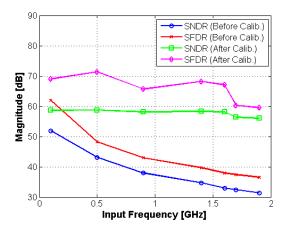

| 3.9  | Simulated SNDR and SFDR as a function of the input signal                                                      | 52       |

| 0.15 | frequency.                                                                                                     | 54       |

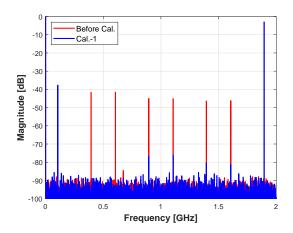

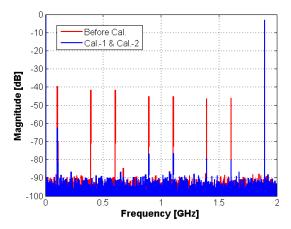

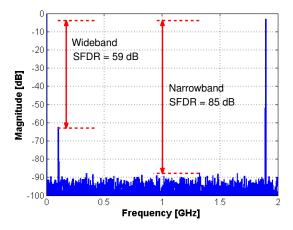

| 3.10 |                                                                                                                |          |

|      | point FFT, $f_{in} = 1.9$ GHz, $A_{in} = -3$ dB <sub>FS</sub> , Correction step = 100 fs)                      | 55       |

| 3.11 | Simulated output spectra before and after calibration (16384 point                                             |          |

|      | FFT, $f_{in} = 1.9$ GHz, $A_{in} = -3$ dB <sub>FS</sub> , Correction step = 100 fs)                            | 55       |

| 3.12 | Simulated output spectrum after calibration and channel                                                        |          |

|      | randomization (16384 point FFT, $f_{in} = 1.9$ GHz, $A_{in} = -3$ dB <sub>FS</sub> ,                           |          |

|      | Correction step = 100 fs)                                                                                      | 56       |

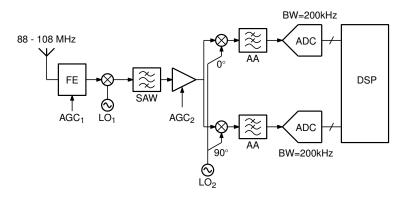

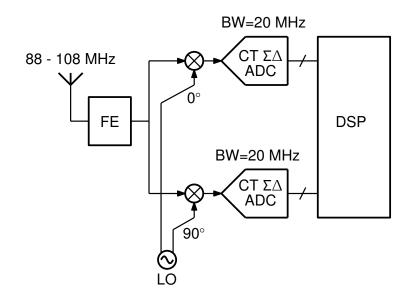

| 4.1  | A Superheterodyne radio receiver for FM band reception                                                         | 59       |

| 4.2  | Wideband IF ADC concept.                                                                                       | 60       |

| 4.3  | A multi-standard tuner for car radio.                                                                          | 61       |

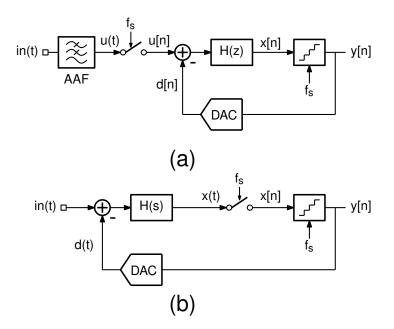

| 4.4  | A DT $\Sigma \Delta M$ (a) and a CT $\Sigma \Delta M$ (b)                                                      | 62       |

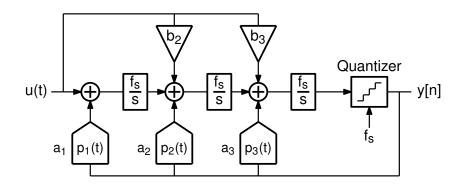

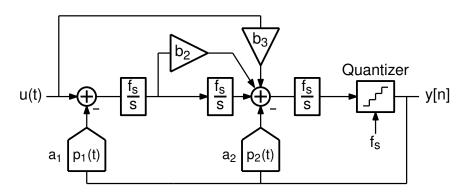

| 4.5  | A CIFB loop-filter structure.                                                                                  | 63       |

| 4.6  | A CIFF loop-filter structure.                                                                                  | 64       |

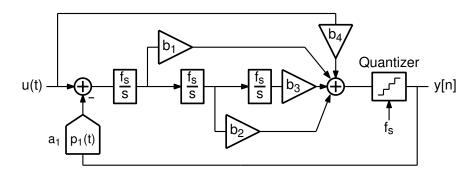

| 4.7  | A CIFF-B loop-filter structure.                                                                                | 65       |

xii

#### List of Figures

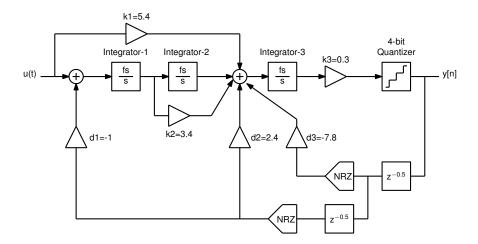

| 4.8  | Block diagram of the modulator employed in this work                           | 68 |

|------|--------------------------------------------------------------------------------|----|

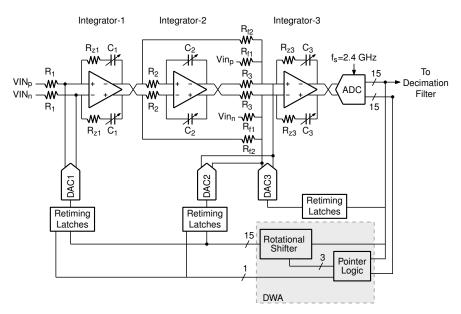

| 4.9  | Schematic of the ADC                                                           | 69 |

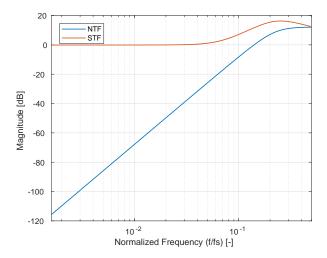

| 4.10 | NTF and STF of the CT modulator used in this work                              | 70 |

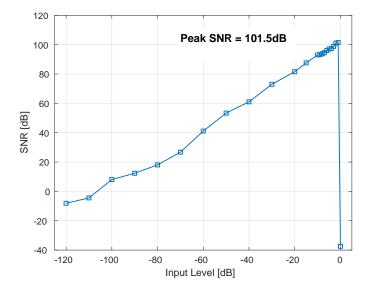

| 4.11 | SQNR as a function input amplitude                                             | 70 |

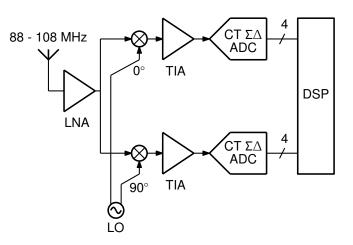

| 4.12 | Block diagram of the FM chain.                                                 | 71 |

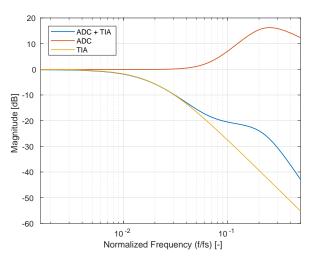

| 4.13 | Simulated STFs for ADC, TIA and TIA and ADC cascade                            | 71 |

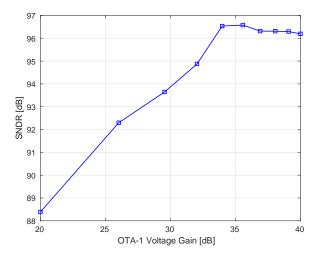

| 4.14 | SNDR as a function of DC voltage gain of the OTA-1.                            | 72 |

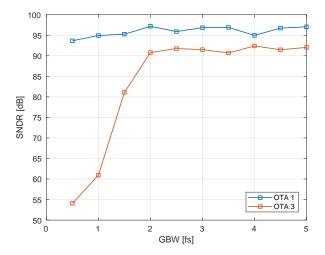

| 4.15 | SNDR as a function of GBW for the OTA-1 and OTA-3                              | 73 |

| 4.16 | SNDR & SFDR as a function of OTA-1 third-order nonlinearity $\beta$            | 74 |

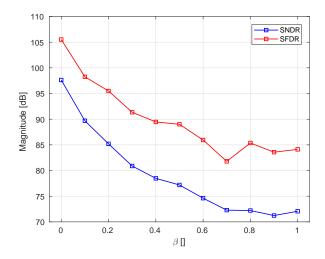

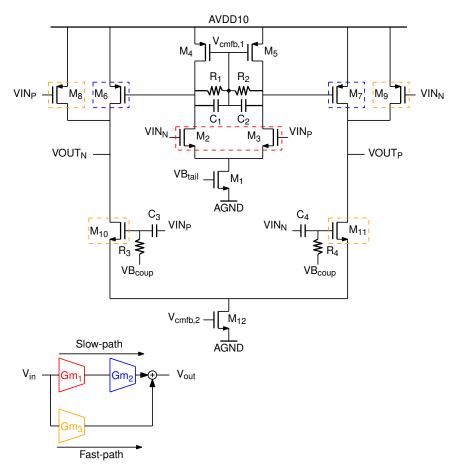

| 4.17 | Two-stage feed-forward compensated OTA.                                        | 75 |

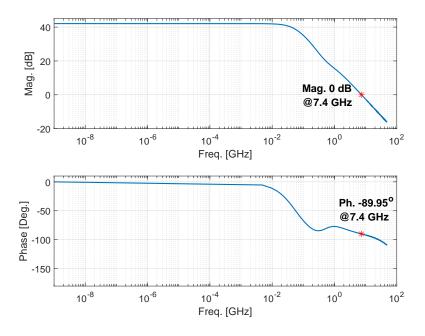

| 4.18 | Bode plot of the post-layout OTA (for $C_{load} = 1 \ pF$ )                    | 76 |

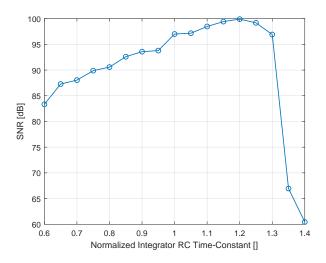

| 4.19 | SNR as a function of integrator RC time-constant.                              | 76 |

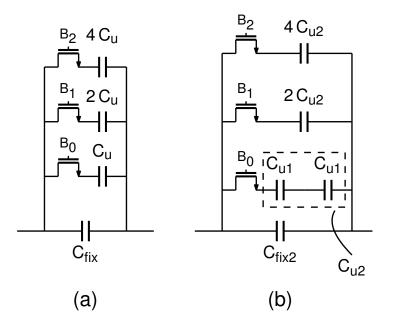

| 4.20 | Capacitor tuning bank of the Integrator 1 (a), Integrator 2 and 3 (b).         | 77 |

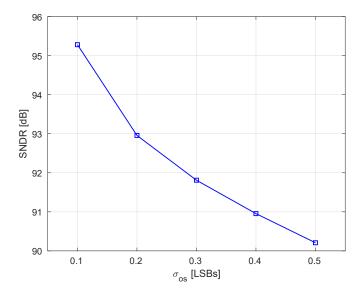

| 4.21 | SNDR as a function of the comparator offset standard deviation $\sigma_{os}$ . | 77 |

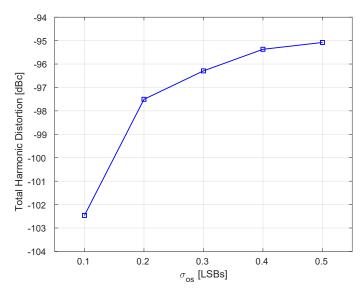

| 4.22 | THD as a function of the comparator offset standard deviation $\sigma_{os}$    | 78 |

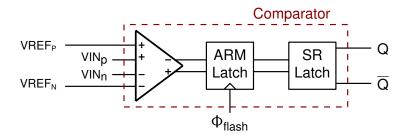

| 4.23 | Three-stage comparator used in flash-ADC quantizer.                            | 79 |

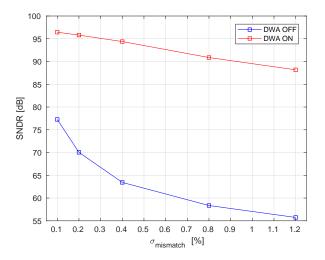

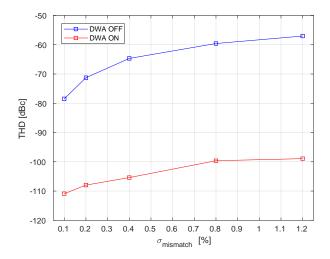

| 4.24 | SNDR of the ADC as a function of $\sigma_{mismatch, DAC1}$                     | 79 |

| 4.25 | THD of the ADC as a function of $\sigma_{mismatch,DAC1}$                       | 80 |

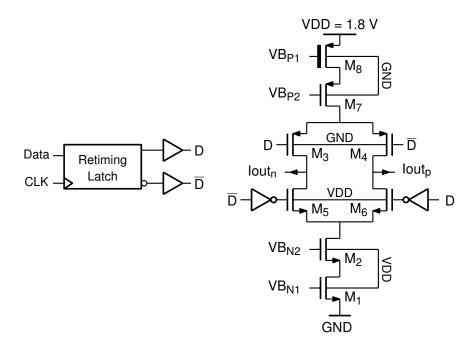

| 4.26 | Current-steering DAC Cells.                                                    | 80 |

|      | Schematic of the Complementary DAC Cell.                                       | 81 |

| 4.28 | Driver Latch of the DAC3.                                                      | 82 |

| 4.29 | DAC retiming latch with embedded 2-to-1 multiplexer                            | 83 |

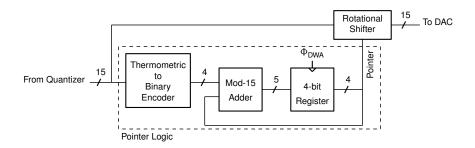

| 4.30 | Block diagram of a conventional DWA implementation.                            | 83 |

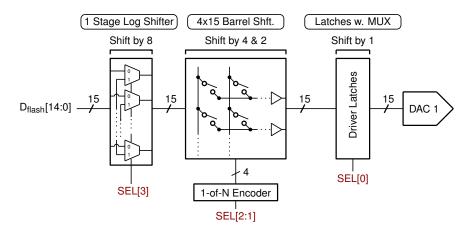

| 4.31 | Block diagram of the proposed rotational shifter.                              | 84 |

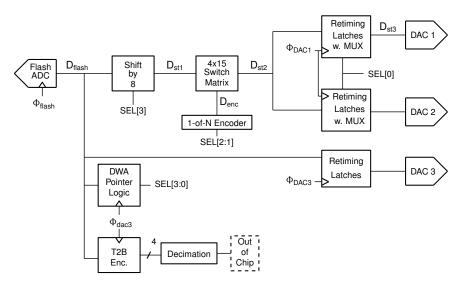

| 4.32 | Block diagram of the ADC feedback network                                      | 85 |

| 4.33 | Timing diagram of the ADC feedback network                                     | 86 |

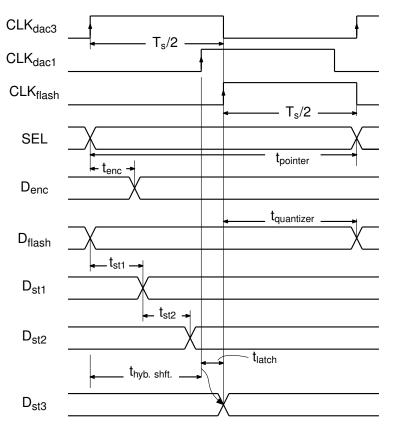

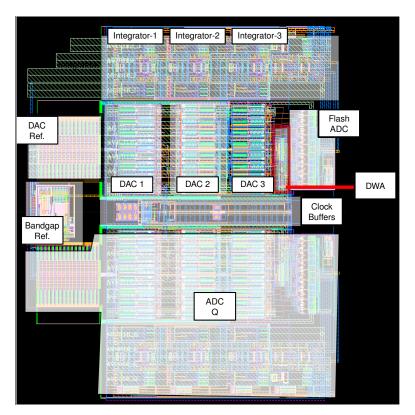

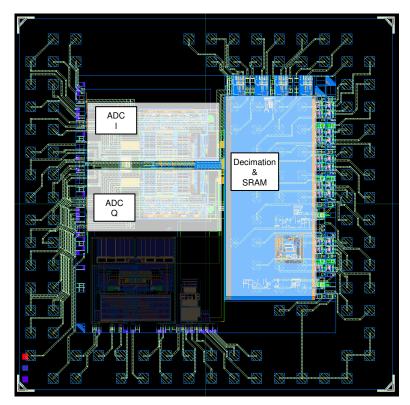

| 4.34 | Layout of the ADCs I & Q                                                       | 88 |

| 4.35 | Layout of the fabricated chip                                                  | 89 |

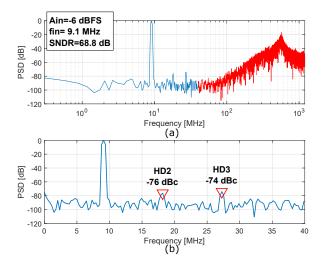

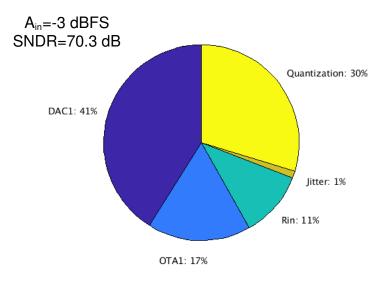

|      | Output Spectrum of the ADC (a), in-band detail of the spectrum (b)             | 90 |

|      | Post-layout thermal noise distribution of the ADC                              | 90 |

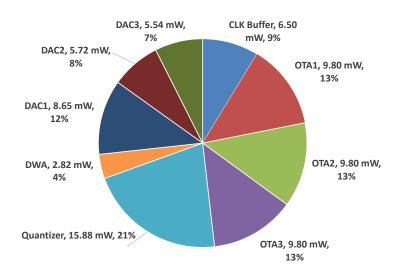

| 4.38 | Power breakdown of the ADC.                                                    | 91 |

#### xiii

## List of Tables

| Preamplifier output combinations of the SAR-1 stage | 27                                        |

|-----------------------------------------------------|-------------------------------------------|

| Preamplifier output combinations of the SAR-2 stage | 28                                        |

| Performance summary and comparison table.           | 37                                        |

|                                                     |                                           |

| Post-layout delay values for the ADC feedback       | 87                                        |

| Performance summary and comparison table of the ADC | 92                                        |

|                                                     | Performance summary and comparison table. |

## Chapter 1 Introduction

Last few decades have seen a digital revolution in the electronics thanks to the rapidly advancing semiconductor technology. As predicted by G. Moore in his famous article [1], the level of integration has dramatically increased at a large pace. With this aggressive semiconductor technology scaling, the size and the cost of integrated functionality have been reduced significantly, especially for digital computing. However, the nature is analog and to utilize the tremendous digital computational power offered by the modern semiconductor technology, there should be a "bridge" or a "doorway" [2]. Thus, analog-to-digital converters (ADCs) represent one of the crucial circuit blocks of the modern technology and play a key role in bridging the analog to the digital for a wide range of applications with frequencies from DC to the few tens of GHz.

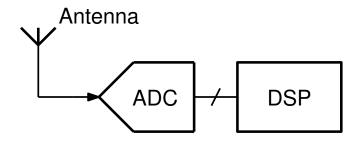

Broadband communication systems have been transformed significantly by the available digital signal processing (DSP) capabilities and introduction of the digital modulation schemes. The rate of the received and transmitted data has substantially increased in the recent years for both for wireless and wireline communication. For modern transceivers, the trend is shifting the analog functionality such as filtering, frequency translation and gain into the digital domain to increase the system flexibility and the precision, to reduce the overall size and the cost by eliminating several off-chip components. The amount of the transferred analog functionality depends on the position of the ADC on the receiver chain. The ultimate goal is realizing software-defined systems [2,3], where the ADC is connected directly to the antenna or to the transducer and executing all the required operations into the digital domain. Such a software-defined receiver is depicted in Fig. 1.1.

#### 1.1 Motivation

The trend of transferring analog functionality into the digital domain is getting combined with the ever increasing data rates in modern broadband communication systems. The ADCs used in those systems should have higher bandwidth and higher

Fig. 1.1 A software-defined radio receiver.

dynamic range. Adding up to the digital functionality significantly increases the area occupied by the digital section in modern communication system-on-chips (SoCs). Therefore, the priority is given to reducing the area and the power consumption of the digital part when a technology node is chosen [4]. The scaled CMOS technologies are preferred in SoCs for higher power efficiency, smaller area and higher speed for the digital section [4]. However, these technologies create several problems to the analog circuit design such as reduced supply voltage and output impedance of the transistors [5].

Considering the above discussed arguments, the motivation of this thesis is developing circuit techniques to improve power efficiency, bandwidth and dynamic-range for high-speed ADCs implemented in scaled CMOS technologies, as they are getting more and more demanded by the modern communication systems. In this thesis three regions of the modern communication system application space are covered:

- Medium resolution and high-speed single-channel successive-approximationregister (SAR) ADCs, since they are dominating the very high-speed medium resolution time-interleaved ADCs [6]. The area and power efficiency of the SAR ADCs make them appealing as a channel in the massively interleaved ADCs used in wireline and optical communication receivers [3].

- 2. High-resolution SAR ADC based time-interleaved ADCs with sampling frequency higher than 1 GHz as they are good candidates for replacing the power hungry pipeline ADCs in power efficient direct radio frequency (RF) sampling applications [8]. These ADCs are commonly used in cellular communication receivers for the standards such as the 4G Long Term Evolution (LTE) and the upcoming 5G in which the whole RF band is converted and no down-conversion is used.

- 3. High-resolution and wide bandwidth continuous-time (CT) sigma-delta modulator ( $\Sigma\Delta M$ ) ADCs as they are appealing solutions for the wideband wireless radio receiver applications. The implicit anti-aliasing filter and signal filtering capabilities of the power-efficient CT  $\Sigma\Delta M$  ADCs have made these ADCs widespread in the cellular handset applications [9] as well as the car radio receivers [4, 10]. In these applications the common characteristic is converting the whole band and performing the channel filtering in the digital domain. This

#### 1.2 Thesis Organization

allows to removing the external filtering components and reducing the system size [3]. Moreover, there are efforts to replace pipeline ADCs with few hundred MHz bandwidth used in base transceiver stations (BTS) [13].

#### **1.2 Thesis Organization**

The thesis is organized as follows:

Chapter 2 starts with a brief introduction to the application space of high-speed single-channel SAR ADCs. The conventional SAR ADC and its limitations on the speed are discussed and existing solutions found in the open literature are presented. Multi-bit per cycle (multi-bit/cycle) technique can significantly boost the conversion speed of the conventional SAR ADC. However, the reference generation is the issue in this technique. A novel preamplifier structure for multi-bit/cycle SAR ADCs is presented. The preamplifier combines the reference generation and the voltage gain. The advantages and limitations of the proposed preamplifier are discussed in detail. The preamplifier concept is applied to an 8-bit 700 MS/s subranging multi-bit/cycle flash-SAR ADC in 65nm CMOS technology. The design details and the measurement results of the fabricated chip are presented and the conclusions on the chapter are drawn.

Chapter 3 presents a background timing skew calibration technique for flashassisted time-interleaved (FATI) SAR ADCs with multiple flash ADCs. Examples from the prior art in timing skew calibration techniques and the specific timing skew calibration methods dedicated to the FATI SAR ADCs are given. The proposed twostep timing skew calibration method is discussed in detail along with the considerations on the implementation, the hardware requirements and the limitations. The benefits of the proposed method on the channel randomization are also presented. Following the behavioral simulation results the conclusions on the chapter are drawn

Chapter 4 presents a CT  $\Sigma\Delta M$  ADC for multi-standard car radio applications. The Section 4.1 briefly introduces the car radio trends and the advantages of the multi-standard radio receiver architectures. The following section discusses the advantages of the CT  $\Sigma\Delta M$  over the discrete-time (DT)  $\Sigma\Delta M$  and the system level considerations for CT  $\Sigma\Delta M$  ADCs. The second half of Chapter 4 presents a 40 MHz BW, 70 dB SNDR CT  $\Sigma\Delta M$  ADC implemented in 28nm fully-depleted silicon-on-insulator (FD-SOI) CMOS. The design choices and circuit blocks are presented in detail. A novel hybrid data rotational shifter structure is presented and the advantages of the structure are discussed. At the end of the chapter the layout of the ADC and the chip as well as the post-layout simulations are presented and finally the conclusions of the chapter are drawn in the Section 4.4.

Chapter 5 draws the conclusions of the thesis and discusses the future work.

#### References

- G. Moore, "Cramming more components onto integrated circuits," *Electronics*, vol. 38, no. 8, pp. 114-117, 1965.

- 2. D. H. Robertson, "Problems and Solutions: How Applications Drive Data Converters (and How Changing Data Converter Technology Influences System Architecture)," in *IEEE Solid-State Circuits Magazine*, vol. 7, no. 3, pp. 47-57, Summer 2015.

- J. Mitola, "The software radio architecture," in *IEEE Communications Magazine*, vol. 33, no. 5, pp. 26-38, May 1995.

- 4. K. Bult, "Embedded analog-to-digital converters," 2009 Proceedings of ESSCIRC, Athens, 2009, pp. 52-64.

- B. Murmann, "A/D converter trends: Power dissipation, scaling and digitally assisted architectures," 2008 IEEE Custom Integrated Circuits Conference, San Jose, CA, 2008, pp. 105-112.

- B. Murmann, "ADC Performance Survey 1997-2018," [Online]. Available: http://web.stanford.edu/ murmann/adcsurvey.html.

- S. Palermo, S. Hoyos, S. Cai, S. Kiran and Y. Zhu, "Analog-to-Digital Converter-Based Serial Links: An Overview," in IEEE Solid-State Circuits Magazine, vol. 10, no. 3, pp. 35-47, Summer 2018.

- Texas Instruments, "Dual-Channel, 14-Bit, 3-GSPS RF-Sampling Analog-to-Digital Converter (ADC)," ADC32RF45 datasheet.

- M. Andersson, M. Anderson, L. Sundstrm, S. Mattisson and P. Andreani, "A Filtering ΣΔ ADC for LTE and Beyond," in *IEEE Journal of Solid-State Circuits*, vol. 49, no. 7, pp. 1535-1547, July 2014.

- J. van Sinderen et al., "A wideband single-PLL RF receiver for simultaneous multi-band and multi-channel digital car Radio reception," 2016 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), San Francisco, CA, 2016, pp. 330-333.

- P. G. R. Silva, L. J. Breems, K. A. A. Makinwa, R. Roovers and J. H. Huijsing, "An IF-to-Baseband ΣΔ Modulator for AM/FM/IBOC Radio Receivers With a 118 dB Dynamic Range," in *IEEE Journal of Solid-State Circuits*, vol. 42, no. 5, pp. 1076-1089, May 2007.

- L. J. Breems, R. Rutten, R. H. M. van Veldhoven and G. van der Weide, "A 56 mW Continuous-Time Quadrature Cascaded ΣΔ Modulator With 77 dB DR in a Near Zero-IF 20 MHz Band," in *IEEE Journal of Solid-State Circuits*, vol. 42, no. 12, pp. 2696-2705, Dec. 2007.

- 13. Y. Dong et al., "A 72 dB-DR 465 MHz-BW Continuous-Time 1-2 MASH ADC in 28 nm CMOS," in *IEEE Journal of Solid-State Circuits*, vol. 51, no. 12, pp. 2917-2927, Dec. 2016.

### Chapter 2 An 8-bit 700 MS/s Sub-ranging Flash-SAR ADC in 65nm CMOS

#### 2.1 Introduction

Medium resolution (6 - 8 bits), high-speed (500 MS/s - 1000 MS/s) single-channel ADCs are used in applications such as digital oscilloscopes [1] and satellite receivers [2]. However, the main driving application for these ADCs are the multi-GHz time-interleaved structures. The data rates of wireline communication standards are pushed to increase dramatically by the huge amount of data transfer in data-centers. The recent ethernet standards such as 56 Gb/s and 100 Gb/s use spectrally efficient modulation schemes such as PAM-4 due to the large losses of the conventional electrical channels. However, the drawbacks of the PAM-4 like intersymbol interference (ISI) sensitivity increase the equalizer complexity dramatically to be robustly implemented in analog domain [3]. Therefore, ADC based seriallinks are used to transfer these complex operations to the digital domain to benefit from the flexibility of the DSP. The ADCs to be used in PAM-4 systems generally have 7-8 bit resolution and up to 28 GHz sampling rate for the 56 Gb/s standard [4]. This asks for large number of interleaved channels. However, for high sampling frequencies and large number of channels, the power consumption and complexity of the clock distribution becomes a concern [5]. Reducing the number of timeinterleaved channels to achieve a given aggregate sampling frequency is possible by increasing the sampling speed of the channel ADCs. Therefore, it is important to find techniques to improve the speed of the single channel ADCs while maintaining the power efficiency.

SAR ADCs are commonly used in these highly interleaved ADCs for PAM-4, given their simple implementation, excellent power efficiency and its compatibility with the advanced nano-scale CMOS technologies which favor digital processing over the analog processing. However, SAR ADCs are inferior to the flash ADCs and binary/multi-bit search ADCs in terms of speed and techniques to improve the speed of the SAR ADCs are popular research topics. This chapter is structured as follows: in the Section 2.2 the speed issues of the conventional SAR ADCs are explained and in the Section 2.3 the techniques in literature to improve the speed

of the single-channel SAR ADCs are summarized. The Section 2.4 introduces a novel reference generation technique for the multi-bit/cycle SAR ADCs and the Section 2.5 presents an 8-bit 700 MS/s sub-ranging flash-SAR ADC fabricated in 65nm CMOS technology which uses the introduced preamplifier among other speed improving techniques. Finally the Section 2.6 draws the conclusions of the Chapter 2.

#### 2.2 Conventional SAR ADC and Its Limitations on Speed

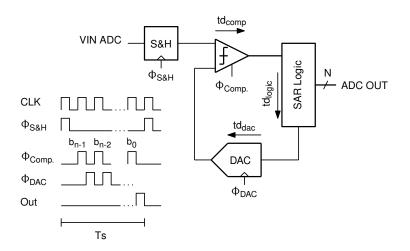

Fig. 2.1 Block diagram and timing diagram of a conventional SAR ADC.

The conventional SAR ADC which is depicted in Fig. 2.1 uses the binary-search algorithm for the analog-to-digital conversion and requires N clock cycles to resolve N-bits. The circuit is composed of a sample-and-hold (S&H) block, a comparator (which is basically a 1-bit ADC), a digital-to-analog converter (DAC) and a register logic. The DAC of the SAR ADC can be capacitive [6], resistive [15] or current-mode [8]. The SAR ADCs with capacitive DACs which are called charge-redistribution SAR ADCs [6] are commonly preferred over the other types due to their important features. The input signal can be sampled onto the capacitive DAC and the DAC has zero static power consumption.

The timing-diagram of the SAR ADC is depicted in Fig. 2.1. At the beginning of the conversion the input is sampled and it is held throughout the conversion. After the sampling of the input, the first comparison is done to determine the most significant bit (MSB). The MSB is held in the register, and according to the MSB value, the DAC gives the next reference value to generate the residue. This process goes on until the least significant bit (LSB) is determined.

#### 2.2 Conventional SAR ADC and Its Limitations on Speed

The SAR ADC has several very attractive aspects which made it one of the dominant ADC architectures in the open literature [9]. First, the SAR ADC doesn't employ operational amplifiers. The difficulty in obtaining the high gain in scaled CMOS technology nodes has become an issue. This, along with the increasing interest in power efficiency shifted the focus to the ADC architectures without the operational amplifiers. Second, the SAR ADCs potentially achieve high-resolutions. Third, SAR ADCs are able to achieve zero-static power consumption. The last but not least, the comparator offset is not problematic since it manifests itself as an offset of the ADC transfer function which can be corrected easily. These aspects yield the SAR ADCs digital friendly and their implementation in scaled CMOS technologies very convenient [10], [11].

One of the main drawbacks of the conventional SAR ADC is the sequential resolving of the bits. The conversion time of a SAR ADC, therefore, linearly increases with the resolution of the ADC. For the N-bit, single-bit per cycle conventional SAR ADC depicted in the Fig. 2.1, the sampling period  $T_s$  is expressed as:

$$T_s = (N+2) t_{SAR}$$

(2.1)

where  $t_{SAR}$  denotes the loop delay which is the time required for resolving the single bit. The loop delay has basically three components and it is given as:

$$t_{SAR} = t_{comp} + t_{DAC} + t_{logic} \tag{2.2}$$

where  $t_{comp}$ ,  $t_{DAC}$  and  $t_{logic}$  are the comparator delay, the DAC settling time and the SAR logic delay, respectively.

The DAC delay  $t_{DAC}$  stems from the settling requirements. The DAC should settle to half LSB to maintain the accuracy of the conversion. For the capacitive DAC, the time required for half-LSB settling is given by:

$$t_{DAC} = \tau_{DAC} N \ln(2) \tag{2.3}$$

where  $\tau_{DAC} = C_{DAC} R_{sw}$  is the time-constant of the DAC.  $C_{DAC}$  is the total array capacitance and  $R_{sw}$  is the on resistance of the DAC driving switches. The straightforward way to improve the DAC settling time is reducing the total array capacitance or the on-resistance of the switches. The on resistance of the switch can be reduced by increasing its aspect ratio, using CMOS implementation or using bootstrapping techniques [12]. Bootstrapped switches are not area efficient for this purpose, considering the large switch count. Latter two are generally used in the SAR ADCs in literature, however increasing the aspect ratio too much has diminishing returns since the switches load the preceding logic. On the other hand, the size of  $C_{DAC}$  depends on the DAC structure used (e.g. binary [6], C-2C [13,14], split DAC [15,16]), and it can be reduced by using one of the techniques such as C-2C or split-DAC. Whatever the capacitive DAC structure, the minimum unit capacitance  $C_u$  of the array for a given resolution is limited by the kT/C noise and the linearity. Generally, for medium resolutions the kT/C noise is not the limiting factor and as soon as the matching requirements are satisfied, very small capacitors can be used. These capacitors generally are not offered in the design-kit libraries, therefore very small custom capacitors can be used to improve the settling time and power efficiency [17, 18].

The above discussed fundamental limitations of the SAR ADC on speed has recently led to some architectural innovations such as asynchronous clocking [19–21], multi-bit/cycle [15, 22–25], redundancy and loop-unrolled SAR ADC architecture [26–28]. These architectural innovations aim to improve the SAR ADC speed by attacking a component or the combination of the components of the total cycle delay given in Equation 2.2. The following subsections explain the advantages and drawbacks of the mentioned speed improvement techniques in detail.

#### 2.3 Techniques to Improve the Speed of a Single-Channel SAR ADC

#### 2.3.1 Asynchronous Clocking

The conventional synchronous SAR ADCs use an external clock with the frequency of  $N F_s$  (where  $F_s = 1/T_s$ ) to generate the phases of conversion as depicted in Fig. 2.1, where N is the resolution of the ADC. This introduces two important disadvantages. First, the power consumed on the clock distribution becomes an issue, especially for the higher sampling rates. Second is the inefficient use of the allocated time for comparators. If the time required for a comparator to make a decision is denoted as  $T_{cmp}$ , it can be expressed for a latch with a preamplifier stage as [19]:

$$T_{cmp} = \frac{\tau}{A_o - 1} \cdot ln \frac{V_{FS}}{V_{res}}$$

(2.4)

where  $\tau$  is the time constant of the latch,  $A_o$  is the small-signal gain of the preamplifier,  $V_{FS}$  is the full scale voltage of the ADC, and  $V_{res}$  is the residue signal at the input of the comparator. During the successive-approximation algorithm  $V_{res}$ changes from cycle to cycle. In synchronous SAR ADCs, the time allocated for the comparator is equal for each cycle and it should be chosen according to the worst case, for which the  $V_{res}$  is equal to half-LSB. Therefore, even if all the other decisions would take less time compared to the worst case, the comparator uses equal time at each cycle.

The asynchronous SAR ADC introduced in [19] circumvents the issues discussed above. The SAR performs the bit-cycling in a domino-like fashion in which a logic block generates a ready signal as soon as the comparator makes the decision and the next cycle begins. In this way, the time lost in easy decisions can be saved and large gains in the sampling rate are achieved. The external clock is only used for the sampling phase. Therefore the external clock has a frequency equal to the sampling frequency and the high-frequency clock issue is resolved. The drawback of the asynchronous SAR ADC is the metastability of the comparator. Since the bitcycling depends on the completion of the preceding cycle, when the metastability occurs, the conversion may take very long time or even get stuck. This causes the reduction of SNR in asynchronous SAR ADCs. An additional logic circuit is added in [20] to deal with the issue.

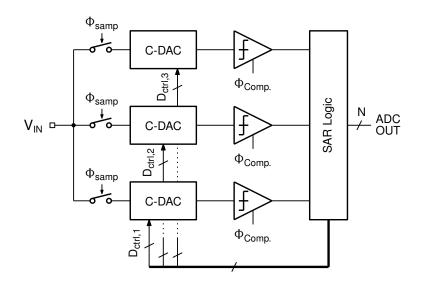

Fig. 2.2 Multi-bit/cycle SAR ADC with multiple CDACs [22].

#### 2.3.2 Multi-bit per cycle SAR ADCs

Multi-bit per cycle (multi-bit/cycle) SAR ADC techniques focus on reducing the overall cycle number. For instance, resolving 2-bits per cycle would halve *N* in Equation 2.1 and theoretically double the SAR ADC speed. The approach was first introduced in [22], which uses a flash-ADC like structure to resolve 2-bits per cycle. Fig. 2.2 depicts the block diagram of the approach. The architecture employs three capacitive DACs to generate the three levels required in each cycle and three comparators for the decision. The input is sampled onto each of the three DACs. Introducing multiple DACs and comparators causes some issues for this architecture. The offset of the comparators entails non-linearity at the output, which is not the case for the conventional SAR ADC. By employing multiple DACs, the input capacitor and the area of the ADC increases considerably.

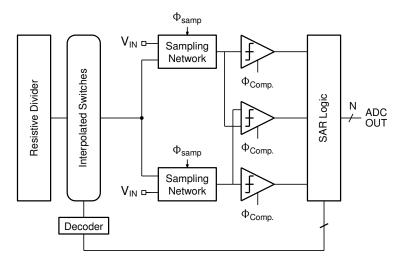

Fig. 2.3 depicts the approach presented in [15] where the three capacitive DACs (CDACs) have been replaced by a resistive DAC. This removes the necessity for multiple DACs. The sampling circuits and the reference switches are interpolated to reduce the number of components. Nevertheless, the disadvantage of this tech-

Fig. 2.3 Multi-bit/cycle SAR ADC with resistive DAC [15].

nique is the increased complexity and area overhead caused by the large number of switches and the static power consumption of the resistive divider.

The recent research focus for the multi-bit/cycle SAR ADCs is on reducing the CDAC number and the size. In [24] a 2-bits/cycle SAR ADC is presented where the CDACs are interpolated to remove one capacitive DAC. The size of the DAC is further reduced by employing a bridge capacitor and custom unit capacitors. In [23], the size of the CDAC is greatly reduced by using the subranging and hybrid resistive - capacitive DAC. In the work presented in [25] to reduce the input capacitance posed by the ADC and to reduce the number of CDACs, two separate CDACs are used for signal and reference.

#### 2.3.3 Loop-unrolled SAR ADCs

The comparator in a conventional SAR ADC must wait for the DAC to settle to start the conversion. Therefore,  $t_{comp}$  and  $t_{DAC}$  cannot occur simultaneously. However,  $t_{logic}$  can be overlapped with  $t_{comp}$  or  $t_{DAC}$ , if not completely eliminated. The work presented in [26] is based on this idea and the architecture is called loop-unrolled SAR ADC. The proposed ADC employs N comparators for an N-bit ADC. After the decision of a bit, the comparator of that cycle passes its output to the ready signal generation logic and the capacitive DAC simultaneously. Thereby the DAC settling occurs while the signal to start the next bit cycle passes to the next comparator and  $t_{logic}$  is eliminated from the critical delay. An issue with the technique is the offset mismatch of the multiple comparators, as seen in multi-bit/cycle architectures. The calibration or redundancy can be used to mitigate the effects of this mismatch [27,28].

#### 2.3.4 Redundancy

The penalty of the DAC settling on the speed of the SAR ADC can be mitigated by using the redundancy. Redundancy allows tolerating and absorbing the errors during the conversion. The redundancy can be introduced by additional decision levels [29], additional conversion steps [30] or by using a radix smaller than 2 [31]. The common idea is to have overlapping trajectories to recover the errors at the steps up to a certain limit determined by the level of the redundancy used. By reducing the time required by the DAC settling, the speed of the SAR ADC can be improved substantially. The drawback of the technique is the increased number of successiveapproximation steps. However, as stated in [21], "the time saved by relaxing the DAC settling is generally much longer than the extra cycles needed to resolve all bits".

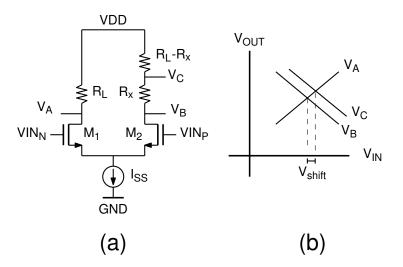

Fig. 2.4 Multiple threshold generating preamplifier concept.

#### 2.4 Preamp with threshold generation for the multi-bit per cycle SAR ADCs

The benefits of the multi-bit per cycle SAR ADC structures are diminished by the necessity of the multiple DACs in case of capacitive approach and the complexity of the switch network in case of resistive approach. Even if the interpolation of the DACs and switches reduces the complexity, it remains as a problem for multibit/cycle SAR ADCs. Therefore, an efficient technique is required for the reference generation.

The work presented in this thesis and reported in [32] introduces a novel way to implement the multi-bit per cycle operation in SAR ADCs. The schematic of the concept is depicted in Fig. 2.4. The method is based on a resistively loaded differential pair in Fig. 2.4(a). The load resistor  $R_L$  is divided in two parts,  $R_x$  and  $(R_L - R_x)$ . By tapping the common node of these two resistors which is denoted as  $V_C$ , a shifted version of the input output characteristic of  $V_B$  is obtained. As depicted in Fig. 2.4(b), the intersection of the two voltages  $V_A$  and  $V_C$  is  $V_{shift}$  volts higher than the intersection of  $V_A$  and  $V_B$  on the  $V_{IN}$  axis. Therefore, two comparators using these two node pairs as the input will have switching thresholds  $V_{shift}$  volts apart from each other.

The value of the  $V_{shift}$  is given by:

$$V_{shift} = \frac{1}{4} \frac{R_x}{R_L} \frac{I_{SS}}{g_m} = \frac{1}{2} \frac{R_x}{R_L} \frac{1}{g_m/I_d}$$

(2.5)

where the  $g_m/I_d$  is the transconductance efficiency of the input transistors. The values of the tail current  $I_{SS}$ , the input transconductance  $g_m$  and the load resistor  $R_L$  are determined by the speed and resolution requirements of the ADC. Therefore, the  $R_x$  remains as the variable to obtain the required shift values. By increasing the  $R_x$ , larger threshold values can be implemented.

There are two key advantages of the proposed amplifier for threshold generation. First, the CDAC is not used for threshold generation but for residue generation. Therefore, it is not required to have multiple CDACs as in conventional multi-bit/cycle implementations. There should be only one CDAC, independently of the number of bits resolved per cycle. Second, although the preamplifier has static power consumption, it is not wasted as in the multi-bit/cycle approaches which employ resistive reference generation. In the proposed approach, the current consumed to implement the voltage gain is reused to generate the thresholds. Preamplifiers are employed to improve the speed and input referred offset of the comparators, therefore, the advantages of using a preamplifier are twofold.

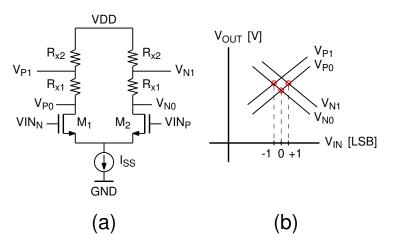

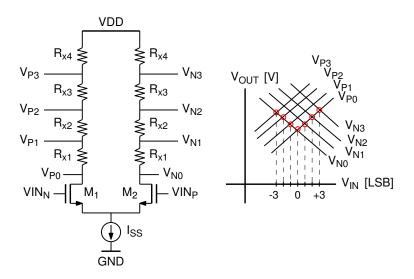

The approach shown in Fig. 2.4 for generating a single positive threshold value can be generalized to obtain the reference voltages required for multi-bit/cycle SAR ADCs. The examples for 2-bit/cycle and 3-bit/cycle cases are shown in Fig. 2.5 and Fig. 2.6, respectively. The required reference values can be obtained by taking the combination of various tap voltages. For instance, for the 2-bit/cycle amplifier

2.4 Preamp with threshold generation for the multi-bit per cycle SAR ADCs

Fig. 2.5 2-bit/cycle implementation of the preamplifier.

Fig. 2.6 3-bit/cycle implementation of the preamplifier.

depicted in Fig. 2.5, the 0 LSB threshold value can be obtained with the  $V_{P0}$  -  $V_{N0}$  combination or the  $V_{P1}$  -  $V_{N1}$  combination.

As shown in Equation 2.5, the threshold value depends on  $R_x$ . However, there are limits on the value of  $R_x$ . It is obvious from the Fig. 2.4 that  $R_x$  can not be larger than  $R_L$ . This puts a limit on the maximum differential threshold voltage which can be implemented with the approach. Defining the  $V_{shift} = k V_{lsb}$ , the maximum value of k can be expressed as:

2 An 8-bit 700 MS/s Sub-ranging Flash-SAR ADC in 65nm CMOS

$$k_{max} = \frac{I_{SS}/2}{g_m V_{lsb}} = \frac{1}{g_m/I_d V_{lsb}}$$

(2.6)

At  $k_{max}$ ,  $R_x$  is equal to  $R_L$  therefore the  $k < k_{max}$  condition should be satisfied. Since  $g_m$ ,  $I_{SS}$  and  $V_{lsb}$  are determined by the ADC specifications,  $k_{max}$  is a limiting factor for the preamplifier for large input ranges. For instance, the ranges of the steps for a conventional 8-bit 2-bit/cycle SAR ADC are:

- Step 1: 0-256 LSB

- Step 2: 0-64 LSB

- Step 3: 0-16 LSB

- Step 4: 0-4 LSB

If the ADC full-scale voltage is 1 V and the  $g_m/I_d$  ratio of the input transistors are 10, then the  $k_{max}$  results in 25.6, which means that theoretically the preamp can not be used in the first two steps of the conversion. The input range can be increased through the transconductance efficiency of the input transistors with the power penalty. However, even if the  $g_m/I_d$  is taken 2.5, the range increases 4 times and it can not cover the full-scale. Moreover, lowering the transconductance efficiency of the input transistors is problematic in low supply voltages of the nanoscale technologies and an transconductance efficiency less than 10 is not convenient due to the headroom considerations. This issue calls for subranging [33], as the ADC presented in this work employs.

The second issue is related to the voltage gain of the preamplifier. In Fig. 2.4, the single-ended voltage gain from  $VIN_P$  to the tap  $V_C$  is denoted as  $A_{v,C}$  and can be expressed as:

$$A_{\nu,C} = \frac{V_C}{VIN_P} = g_m (R_L - R_x) = gm R_L (1 - \frac{R_x}{R_L})$$

(2.7)

It is clear from the equation that the voltage gain is maximum and equal to  $A_v = g_m R_L$  at  $V_B$  where  $R_x = 0$  and linearly decreases with increasing  $R_x$ . The gain loss can be compensated by increasing the  $R_L$ , but this would reduce the bandwidth of the amplifier for a given gain-bandwidth product. Therefore, to maintain the power efficiency of the technique and the accuracy of the SAR step, the number of taps should be limited to a certain value. This value, denoted as  $k_{max,gain}$ , can be calculated with a relationship between the allowed gain reduction and the implemented number of taps.

$$\frac{A_{\nu,C}}{A_{\nu,B}} = (1 - (g_m/I_d k_{max,gain} V_{lsb})$$

(2.8)

where  $A_{v,B}$  is defined in the same manner as  $A_{v,C}$  in Equation 2.7. Then the  $k_{max,gain}$  is given as:

$$k_{max,gain} = \frac{1 - A_{\nu}/A_{\nu,max}}{(g_m/I_d) \, V_{lsb}}$$

(2.9)

where  $A_v$  is the lowest allowed single-ended gain and  $A_{v,max}$  denotes the singleended gain at nodes  $V_B$  and  $V_A$ . The choice of  $A_v$  is arbitrary and depends on the input referred offset of the latches connected to the preamplifier and the accuracy requirements of the step.

The current consumption of the preamplifier can be calculated with the following Equation 2.10

$$I_{SS} = 2 \, \frac{g_m}{g_m/I_d} \tag{2.10}$$

where the  $g_m$  denotes the transconductance and the  $g_m/I_d$  denotes the transconductance efficiency of the input transistors. The transconductance efficiency is mostly determined by the headroom since it is given by  $g_m/I_d = 2/V_{ov}$ . The transconductance of the transistors can be calculated using:

$$g_m = C_{load} \; GBW \tag{2.11}$$

where  $C_{load}$  is the load of the preamplifier and GBW is its gain-bandwidth product. The GBW of the preamplifier can be expressed as:

$$GBW = \frac{A_{\nu}}{\tau} \tag{2.12}$$

The gain of the preamplifier depends on the latch offset and the LSB size of the SAR step.  $\tau$  is the time-constant of the dominant pole and depends on the allowed settling time of the preamplifier and the LSB size of the SAR step.  $\tau$  can be expressed as:

$$\tau = \frac{t_{sett}}{(N_{adc} + 1 - m) \ln(2)} \tag{2.13}$$

where  $N_{adc}$  is the resolution of the ADC and *m* is the multiplying factor for the LSB of the SAR step where  $V_{lsb,step} = 2^m V_{lsb,adc}$ .

Using the equations from (2.10) to (2.13), the tail current of the preamplifier for a SAR step can be calculated using:

$$I_{SS} = \frac{4 \left( N_{adc} + 1 - m \right) \ln(2) C_{load} V_{offset, latch}}{g_m / I_d t_{sett} V_{lsb}}$$

(2.14)

The Equation 2.14 can be used to optimize the current of the preamplifier for different SAR steps which have different load, latch offset and LSB size.

#### 2.5 An 8-bit 700 MS/s Sub-ranging Flash-SAR ADC in 65nm CMOS

#### 2.5.1 Overview of the ADC

The techniques discussed in Section 2.3 can be combined to improve the power consumption and speed further. The ADC presented in this section combines multibit/cycle SAR with loop-unrolling and redundancy to achieve 8-bit resolution at 700 MS/s in a 65nm CMOS technology [32].

The multiple-threshold generating preamplifier presented in Section 2.4 offers important advantages to the multi-bit/cycle SAR ADC operation such as requiring only one capacitive DAC and combining the reference generation and the preamplifier functions. However, as discussed in the same section, the output range of the preamplifier calls for the subranging to reduce the dynamic range of the step. Since the work is aiming 700 MS/s, the number of steps should be low. Therefore, flash ADC is chosen for the first stage of the ADC as it requires only one step for the conversion.

The bit distribution among the flash ADC and SAR steps has impact on many aspects of the ADC, such as the time allowed for the comparator decision and the DAC settling, and the capacitive DAC size. The full-scale of the first SAR step can be used to determine the distribution. The achievable gain for a gain stage is limited in scaled technologies. Therefore, keeping the gain loss low is taken as a criteria on choosing the dynamic-range of the first SAR step. Considering a single-ended gain reduction of -3 dB,  $k_{max,gain}$  is found to be equal to 15.8 using the Equation 2.9. Therefore, the full-scale of the first SAR step can be 32 LSB, where LSB is for 8-bits. This automatically sets the minimum resolution of the flash ADC of the first step as 4-bits. As discussed in [34], distributing the flash and SAR resolutions equally achieves good power efficiency. 1-bit redundancy is added to the flash ADC and the first SAR step considering the advantages discussed in Section 2.3.4.

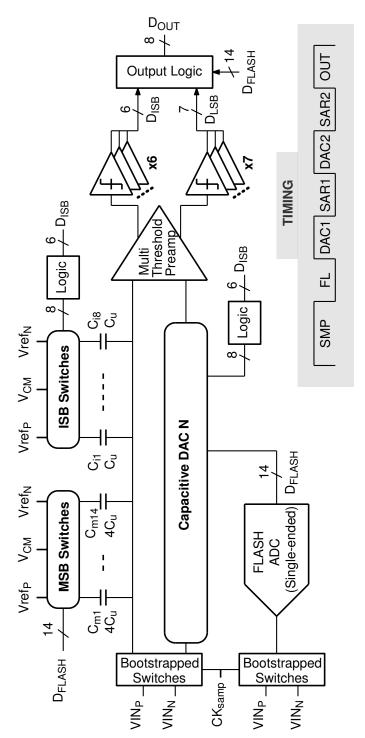

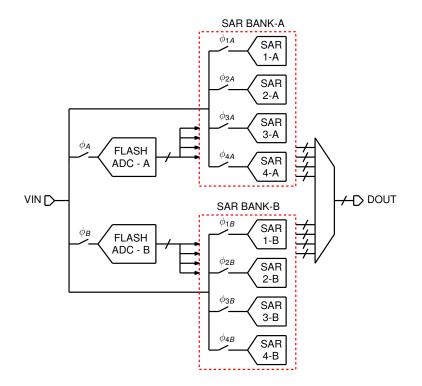

The block diagram of the ADC is shown in Fig. 2.7 together with the timing diagram. In the first step a 4-bit flash ADC with 1-bit redundancy resolves first 3-bits. The output of the flash ADC directly controls the thermometric MSB section of the capacitive DAC to generate the residue. The residue is applied to the multiple threshold generating preamplifier which is connected to the first SAR step (SAR-1) resistive loads and the ISB (Intermediate Significant Bit) bank of latches. The 6 ISB latches resolves 3-bits with 1-bit redundancy for the SAR-1. The ISB latches then directly drive the capacitive DAC. The loop-unrolled operation eliminates the logic delay for this SAR step. Following the second DAC step, the residue is again applied to the multi-bit/cycle preamp but this time it is connected to the second SAR step (SAR-2) resistive load and the LSB latch bank. The SAR-2 stage resolves 3 LSB and passes the output to the logic. The output logic combines the bits and finalizes the conversion.

Fig. 2.8 shows the placement of the reference levels for the conversion steps where A represents the coarse step (Flash ADC), B the intermediate step (SAR-1) and C the fine step (SAR-2).

Fig. 2.8 Successive-approximation path of the ADC (Taken from [32]).

The presented work uses techniques to act on all the principal delay components of the SAR operation. A smaller capacitive DAC is used to reduce the DAC settling time, the loop-unrolling reduces greatly the logic delay, the multi-bit/cycle architecture reduces the cycle number, an improved sense amplifier latch reduces the comparator delay and the multiple threshold generating preamplifier enables the multi-bit operation without any additional capacitive or resistive DACs. The following subsections give details on the blocks and then present the measurement results of the fabricated ADC.

#### 2.5.2 Circuit Blocks

#### 2.5.2.1 Capacitive DAC

The multi-bit/cycle operation realized with the proposed preamp requires only one CDAC and it is used only for the input sampling and the residue generation. A conventional binary weighted CDAC for an 8-bit SAR ADC would have total number of unit capacitors equal to  $2^8 C_u = 256 C_u$ . In this work, 3 LSBs are resolved in the SAR-2 stage and it does not drive the DAC since the outputs are directly passed to the logic. Therefore, the size of the CDAC can be reduced to 5 bits and the  $C_u$  can be sized according to the LSB of the SAR-1 step. Since the LSB of the flash step is 4 times the LSB of the SAR-1 step, the unit capacitor for the flash section becomes  $4C_u$ . Total capacitance becomes  $14 \times 4C_u + 8 \times C_u = 64C_u$ . The total DAC

capacitance of the ADC is 75% less than what required by the conventional binary weighted CDAC. The reduction is even more if the multiple CDACs required for the conventional multi-bit/cycle SAR ADC are considered.

The unit capacitor size to satisfy the kT/C noise requirements for an 8-bit ADC is equal to 8.8 aF for a full-scale range of 1.2 V. The 65nm CMOS technology used in this work offers MOM capacitors with minimum size of 9 fF. Therefore, for more reliable operation and less layout effort, the minimum size MOM capacitor of 9 fF from the design-kit is used as the unit capacitor. This unit capacitor size also satisfies the kT/C noise and matching requirements for the given resolution. The total array capacitance becomes equal to 576 fF.

#### 2.5.2.2 Improved Sense Amplifier Latch

The comparator architectures employed in recent high-speed ADC architectures in literature are dominantly based on the dynamic voltage sense amplifier latch (Strong-ARM latch) which is depicted in Fig. 2.9 [35]. The structure is basically comprised of cross-coupled inverters, an input differential pair and enable and reset switches. Being fully dynamic, it has virtually zero static power consumption and fast-response. The latch uses only one clock phase for enable and reset.

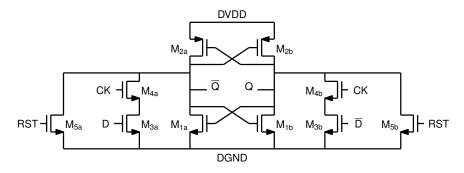

Fig. 2.9 Dynamic voltage sense amplifier latch (Strong-ARM latch) [35].

The regeneration speed of the latch can be analyzed by dividing the regeneration phase into two sub-phases [36]. In the first phase, when the enable signal goes high, the total capacitance on the output nodes starts to discharge with different rates, depending on the polarity and magnitude of the differential input voltage  $\Delta V_{in}$ . This

phase continues until one of the PMOS transistors of the cross coupled inverters turns on. Assuming  $VIN_P > VIN_N$ , the delay associated to this phase can be expressed as:

$$t_o = \frac{C_L V_{thp}}{I_P} \tag{2.15}$$

where  $I_P$  is the drain current of  $M_{1a}$ ,  $C_L$  the total load capacitance at the output node and  $V_{thp}$  the threshold voltage of the PMOS devices in the regenerative loop.

In the second phase, the positive feedback gets activated and a strong regeneration occurs. This phase continues until the voltage difference of the output nodes reaches  $V_{DD}/2$  and a logical decision is taken. The delay in this phase is can be calculated as:

$$t_{latch} = \frac{C_L}{g_{m,eff}} ln \left( 2 \frac{\Delta V_{out}}{V_o} \right)$$

(2.16)

where  $g_{m,eff}$  is the effective transconductance of the latch and  $V_o$  denotes the voltage difference of the output nodes at the beginning of the second sub-phase (at  $t_o$ ).  $V_o$  is defined for the conventional voltage sense amplifier latch as:

$$V_o = V_{thp} \sqrt{\frac{8\beta_n}{I_o}} \varDelta V_{in} \tag{2.17}$$

where  $\beta_n = \frac{W}{L} \mu_n C_{ox}$  is defined for the input transistors  $M_{1a}$  and  $M_{1b}$ .

The total comparison time  $t_{cmp,std}$  of the standard Strong-ARM latch can be then expressed as

$$t_{cmp,std} = \frac{C_L V_{thp}}{I_P} + \tau_{latch} ln \left( \frac{1}{V_{thp}} \frac{\Delta V_{out}}{\Delta V_{in}} \sqrt{\frac{I_0}{2\beta_n}} \right)$$

(2.18)

where  $\tau_{latch} = \frac{C_L}{g_{m,eff}}$  is the time constant of the latch.  $\Delta V_{out} = \frac{V_{DD}}{2}$  is the output swing for which the decision is made and  $\Delta V_{in}$  is the comparator differential input.

For an input signal  $\Delta V_{in}$  small, the latch input is close to the common mode voltage, so  $I_0 = 2I_P$  can be calculated as shown in [37]

$$I_0 = \frac{\beta_n}{9} \left[ \sqrt{3(V_{DD} - V_{thn})^2 - 2V_{cm}^2} - V_{cm} \right]^2.$$

(2.19)

where  $\beta_n$  is the transconductance parameter of NMOS,  $V_{thn}$  the threshold voltage and  $V_{cm}$  is the input common-mode voltage.

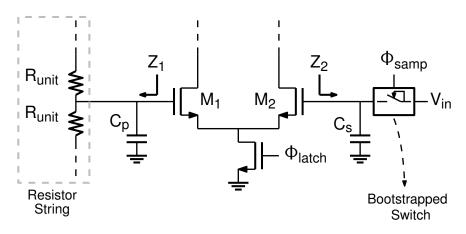

In this work, an improved Strong-ARM latch [38] depicted in Fig. 2.10 is used. A DC current source is inserted in parallel with the enable switch transistor  $M_4$  while the reset transistors on the drain nodes of the input differential pair transistors are removed. These modifications have improving effects on the speed and kickback noise of standard structure as explained shortly.

Fig. 2.10 Improved Strong-ARM latch [38].

The regeneration speed analysis of the structure can be done in a similar way to the conventional Strong-ARM latch, namely by dividing the regeneration phase into two sub-phases,  $t'_o$  and  $t'_{latch}$ .

For the improved Strong-ARM latch, the  $t'_{0}$  is given by

$$t'_{o} = \frac{C_{L}[V_{out,p}(initial) - (V_{DD} - V_{thp})]}{I_{P,on}}.$$

(2.20)

where  $I_{P,on}$  is the drain current of  $M_{1a}$  during the latch phase and given by

$$I_{P,on} = \frac{I_{SS} + I_o}{2} + \Delta I_{IN}$$

(2.21)

where  $I_{SS}$  is the DC tail current of the input differential pair,  $I_o$  is the drain current of the tail switch  $M_4$ , and  $\Delta I_{IN}$  is the differential current based on the input voltage.

For the improved structure, in the reset phase, the DC current source  $I_{SS}$ , the input differential pair transistors  $M_{1a}$ ,  $M_{1b}$  and transistors  $M_{2a}$ ,  $M_{2b}$ ,  $M_{6a}$ ,  $M_{6b}$  form a differential gain stage. Therefore,  $V_{out,p}(initial)$  is determined by a common-mode voltage drop and the differential voltage output of the gain stage are given by:

$$V_{out,p}(initial) = V_{DD} - \frac{I_{SS} r_{ds,6a}}{2} - g_{m1b} r_{ds,6a} \Delta V_{in}$$

(2.22)

It can be noticed from (2.15) that  $t_o$  can be decreased by reducing the time required to reach  $V_{DD} - V_{thp}$ . Equation 2.20 demonstrates that the nominator decreases and at the same time the denominator increases compared to (2.15). Therefore,  $t'_o$  is expected to be lower than  $t_o$  of the standard Strong-ARM latch. In the second phase, the positive feedback gets activated and strong regeneration occurs. The proposed structure has a modified  $V_o$  due to the DC current. It is denoted as  $V'_o$  and it is expressed as:

$$V'_{o} = \frac{2 V_{out,p}(initial) \sqrt{2\beta_n (I_{SS} + I_o)} \Delta V_{IN}}{I_{SS} + I_o} + 2 \left| \Delta V_{out,p}(off) \right|$$

(2.23)

where  $|\Delta V_{out,p}(off)|$  is the differential unbalance from the gain stage in the reset phase. Hence, the regeneration delay for the proposed structure is given by:

$$t'_{latch} = \frac{C_L}{g_{m,eff}} ln \left(\frac{\frac{V_{DD}}{2} - V_{thp}}{V'_o}\right).$$

(2.24)

and the total comparison time of the improved Strong-ARM latch is expressed as:

$$t_{cmp,imp} = \frac{C_L[V_{out,p}(initial) - (V_{DD} - V_{thp})]}{I_{P,on}} + \frac{C_L}{gm_{,eff}} ln \left(\frac{\frac{V_{DD}}{2} - V_{thp}}{V'_o}\right).$$

(2.25)

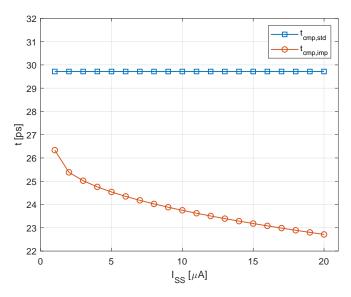

Equations 2.16 and 2.24 show that decreasing  $t_{latch}$  is possible by increasing  $V_o$ . Note that, for the proposed sense amplifier latch,  $V'_o$  is increased by means of the reset gain stage. However, the logarithmic dependence of  $t'_{latch}$  to  $V'_o$  reduces the speed improvement for this phase. Fig. 2.11 shows empirical plots of  $t_{cmp,std}$  and  $t_{cmp,imp}$  as a function of  $I_{SS}$  using Equations 2.18 and 2.25 for generic 65nm CMOS process. A  $t_{cmp}$  improvement from 13% to 24% for  $I_{SS}$  ranging from 1  $\mu$ A to 20  $\mu$ A is obtained.

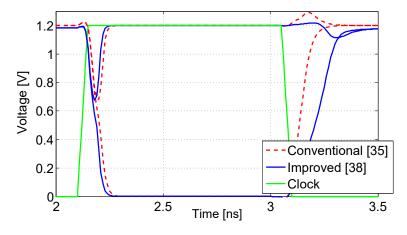

Transistor level simulations are performed to demonstrate the improvements of the latch. Both latches are sized to have offset standard deviation of  $\sigma_{os} = 14.5$  mV.  $I_{SS} = 10 \ \mu\text{A}$  is used as for this current the power consumption of both latches gets equal.  $\Delta V_{in} = 4$  mV and  $V_{CM,in} = 0.6$  V is used in regeneration speed simulations.

Transient waveforms of the compared structures are given in Fig. 2.12. If the comparison is considered completed when the differential output voltage reaches  $V_{DD}/2$ ,  $t_{cmp}$  is found to be 37.1 ps while  $t_{cmp,imp}$  is only 30 ps. The performance of the proposed latch can be further improved by using a proper load inverter switching threshold as proposed in [38].

Dynamic latches generate more kickback noise compared to their static and class-AB counterparts [39]. This is mainly due to two mechanisms: the rail-to-rail swing at the drain terminal of the differential pair coupling to the input through  $C_{gd}$ , and the charge injection of the input transistors due to the dynamic change of region of operation (off-saturation-triode). The comparator used in this work reduces the effect of both mechanisms. The former is tackled by removing the reset transistors on the drain nodes of the differential pair, which reduces the voltage swings on these nodes. Whereas the latter is tackled by the DC current source, as it keeps the input transistors on in the reset phase. This decreases the charge fluctuation due to the change of operation mode.

22

**Fig. 2.11** Empirical  $t_{cmp,std}$  and  $t_{cmp,imp}$  as a function of  $I_{SS}$ .

Fig. 2.12 Transient output comparison of the standard and the improved sense amplifier latch.

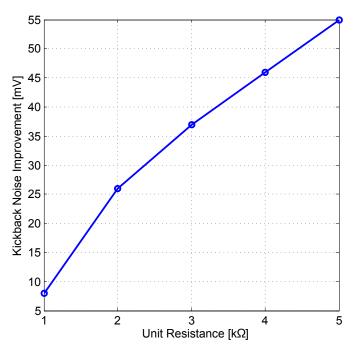

In order to mimic the resistive string used in this design, kickback noise simulations have been done for a 3-bit flash ADC structure using a resistive Kelvin divider with  $R_U = 2 \text{ k}\Omega$ . The worst case scenario is at the middle point of the divider, where the equivalent output resistance is  $R_{out} = 2^{N-1}R_U$ . Both the standard and the proposed comparators were tested and the difference in the kickback noise is plotted in Fig. 2.13 as a function of the unit resistance. The proposed solution is noticeably more robust against kickback perturbations.

Fig. 2.13 Kickback noise improvement over the conventional Strong-ARM latch as a function of the resistive divider unit resistance when the improved Strong-ARM latch is used.

From Fig. 2.12, it can be noticed that removing the reset transistors from the drain node of the differential pair slows down the reset phase of the latch. This is not necessarily a problem if the comparator is not used at a 50% duty cycle as it is the case of the proposed design. Similarly in architectures where the comparators have small duty cycle such as asynchronous SAR, loop-unrolled SAR or comparator-based asynchronous binary search (CABS) [40] ADCs, improved Strong-ARM latch may prove useful.

#### 2.5.2.3 Flash ADC with Reference Voltage Sampling

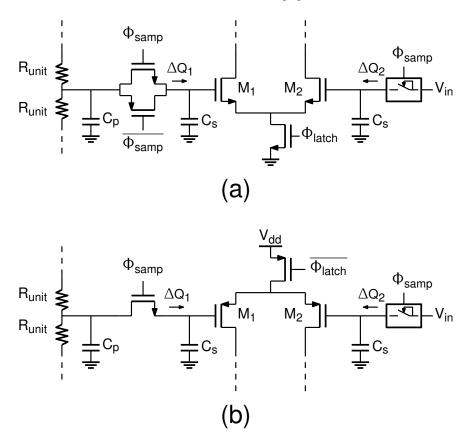

The first 4-bits (with 1-bit redundancy) of the ADC is resolved by a single-ended flash ADC which is composed of a resistive divider and 14 improved Strong-ARM latches. As explained in the Section 2.5.2.2, the improved Strong-ARM latch has less kickback noise compared to the conventional one. Although the magnitude of the kickback noise is reduced, the mismatch between the kickback noise on the resistive divider and the sampling capacitance remains as an issue. This issue is due to the mismatch of the impedance seen by the gates of the input transistors. In Fig. 2.14, the the gate of transistor  $M_1$  sees the parasitic capacitance of the reference node  $C_p$  and the equivalent resistance of the divider at the reference node. Whereas

Fig. 2.14 Kickback mismatch issue in flash ADC.

the gate of the transistor  $M_2$  sees the sampling capacitor  $C_s$ . The kickback mismatch introduces a systematic differential nonlinearity (DNL) and it becomes problematic for small differential input voltages to the comparator. To mitigate the effects of the kickback noise mismatch on the flash ADC comparators, the reference voltages are sampled onto a capacitor whose value is equal to the sampling capacitors'. The reference sampling switches are either NMOS or CMOS (for the motivations explained shortly) switches rather than bootstrapped NMOS due to the area considerations. Since for differential input the voltages at  $V_{d,N}$  and  $V_{d,P}$  (see Fig. 2.10) and the channel charge on the input transistors  $M_{1a}$  and  $M_{1b}$  (see Fig. 2.10) are close in value, the residual mismatch due to these two components would be small.

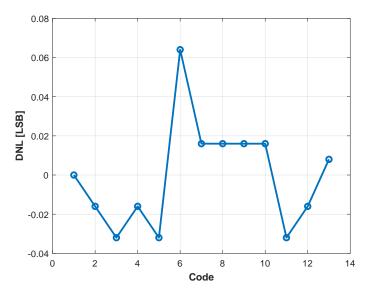

However, the channel charge on the reference sampling switches depends on the reference voltage to which they are connected. Since the reference voltages cover the ADC full-scale, a large variation of the channel charge is expected. On the other hand, the input sampling switches are bootstrapped, and their channel charge stays constant for a first- order approximation. Therefore, the dominant component of the residual kickback noise mismatch is the charge injection mismatch of the sampling switches. To circumvent this issue, the reference sampling switch channel widths are fine-tuned in post-layout. On higher reference voltages, reference sampling switches become slower in settling. Therefore, PMOS switches are used for the three switches from the top. However, this changes the polarity of charge injection and reduces the effectiveness of the technique for these reference levels. In order to solve the issue, CMOS switches are used for these reference sampling switches as depicted in Fig. 2.15(a). Here, PMOS switches are used for main sampling function whereas NMOS switches keeps the polarity of the charge injection same as the switches below. NMOS reference sampling switches are used for the rest of the reference voltages and it is depicted in Fig. 2.15(b). Post-layout systematic DNL plot for the flash ADC is shown in Fig. 2.16 and the maximum DNL is 0.06 LSB, where LSB stands for the overall ADC LSB.

Fig. 2.15 Kickback mismatch compensation in flash ADC with CMOS ref. sampling switch (a) and NMOS ref. sampling switch (b).

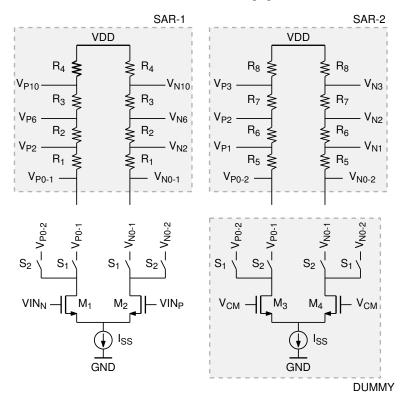

#### 2.5.2.4 Preamp with Multiple-Threshold Generation

The preamp with the multiple-threshold generation is employed in the SAR-1 and SAR-2 stages. SAR-1 and SAR-2 stages are both 3-bit/cycle and SAR-1 step has 1-bit redundancy to relax the DAC settling and comparator offset requirements. As shown in Fig. 2.8, the SAR-1 and SAR-2 stages have different threshold levels and different accuracy requirements. This calls for separate preamps for each SAR cycle, as done in conventional single-bit/cycle loop-unrolled architectures where each step has its own comparator. However, in this case the offset mismatch of the preamplifiers would be an issue. Hence, this work uses a single differential pair with two pairs of resistive load strings, one for each SAR cycle. The preamplifier switches from one to the other depending on the SAR cycle in progress. Switching between the load strings causes large settling times of the output nodes which is a penalty for the achievable speed of the ADC. Therefore, as a speed-power consumption

Fig. 2.16 Post-layout systematic DNL of the flash ADC.

trade-off, a dummy differential pair is added to avoid the output nodes to clip to the supply. The schematic of the preamplifier is shown in Fig. 2.17. The preamplifier is calibrated using the tail current  $I_{SS}$  for the more accurate SAR-2 cycle.

The preamplifier is connected to two banks of latches, one for SAR-1 step and one for SAR-2. The improved sense amplifier latch from Section 2.5.2.2 is employed in both banks. The connection schemes of the latches for SAR-1 and SAR-2 steps are given in Table 2.1 and in Table 2.2 respectively. SAR-2 step latches are designed with a additional parallel input differential pair to be foreground calibrated by external voltages.

| SAR-1 Step Threshold |                     |            |

|----------------------|---------------------|------------|

| -10 LSB              | $V_{P0-1} V_{P0-1}$ | $V_{N10}$  |

| -6 LSB               | $V_{P0-1}$          | $V_{N6}$   |

| -2 LSB               | $V_{P0-1}$          | $V_{N2}$   |

| +2 LSB               | $V_{P2}$            | $V_{N0-1}$ |

| +6 LSB               | $V_{P6}$            | $V_{N0-1}$ |

| +10 LSB              | $V_{P10}$           | $V_{N0-1}$ |

Table 2.1 Preamplifier output combinations of the SAR-1 stage.

Fig. 2.17 Schematic of the multiple-threshold generating preamplifier with dummy input differential pair.

| SAR-2 Step Threshold | <b>VIN</b> <sub>P</sub> | <b>VIN</b> <sub>N</sub> |

|----------------------|-------------------------|-------------------------|

| -3 LSB               | $V_{P0-2}$              | $V_{N3}$                |

| -2 LSB               | $V_{P0-2}$              | $V_{N2}$                |

| -1 LSB               | $V_{P0-2}$              | $V_{N1}$                |

| 0 LSB                | $V_{P0-2}$              | $V_{N0-2}$              |

| +1 LSB               | $V_{P1}$                | $V_{N0-2}$              |

| +2 LSB               | $V_{P2}$                | $V_{N0-2}$              |

| +3 LSB               | $V_{P3}$                | $V_{N0-2}$              |

Table 2.2 Preamplifier output combinations of the SAR-2 stage.

# 2.5.2.5 Switch Driving Logic

Generation and distribution of the digital control signals in high-speed ADCs can contribute more than 50% of the total power consumption and introduce a significant delay in the critical paths. In fact, in modern technologies, the regenerative time of a dynamic latch is comparable to the delay introduced by a few logic gates.

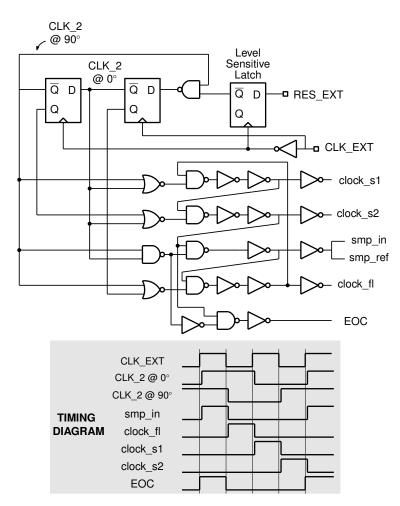

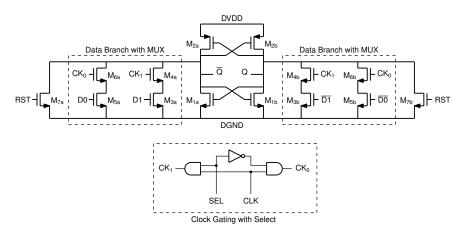

This design uses a shift-register-free logic block based on a clock divider in order to reduce the complexity of the timing control generation, as Fig. 2.18 shows. An external clock, CLK\_EXT, at twice the sampling frequency is divided into two clock signals running at the sampling frequency and shifted by 90°. A combinational logic circuit provides all the phases required for the converter to work properly, while internal feedbacks ensure non-overlapping conditions in the generation of the signals. An external signal, RES\_EXT, can reset the timing logic.

Fig. 2.18 Schematic and timing diagram of the timing logic based on a clock divider.

Apart from the sampling signals, *smp\_in* and *smp\_ref*, which sample both the input and the reference for the flash ADC, three clock signals are required for start each step of the converter. These are *clock\_fl*, *clock\_s1* and *clock\_s2*. Finally, an end

of conversion signal (*EOC*) concludes the conversion cycle. The timing diagram of the clock phases is given in Fig. 2.18.

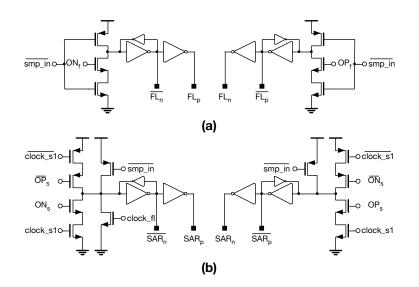

Fig. 2.19 Switch driving registers. (a) MSBs section. (b) ISBs section.

Another critical block in SAR ADCs is the switch driving registers. These registers collect the output of the comparators and feed them back to the capacitive DAC in order to arrange the next approximation in the searching algorithm. The delay introduced by this block is added to the critical feedback path in the SAR operation and can drastically limit the speed operation of the converter [41].

The proposed solution in Fig. 2.19 introduces only a 3-gate delay from when the output of the comparator is ready to when the actual switch at the bottom plate of the DAC is driven. In the MSBs section in Fig. 2.19(a), the clock signal  $\overline{smp\_in}$  first sets the outputs such that the switches at the bottom plates of the DAC are all open. In fact,  $FL_p$  and  $FL_n$  drive the PMOS switches tight to the positive reference, while  $\overline{FL_p}$  and  $\overline{FL_n}$  drive the NMOS switches tight to the negative reference. After the sampling, the logic is ready to sample the output of the flash comparators  $OP_f$  and  $ON_f$ . Based on the latch decision, either one side or the other is reset choosing which side of the DAC is set to '1' and which is set to '0'. There are 14 such structures connected between each comparator of the flash ADC and each capacitor of the MSBs section in the capacitive DAC.

In a similar way, the ISBs section is controlled by the circuit in Fig. 2.19(b).  $\overline{smp\_in}$  reset to an open condition the switch drivers. Next, the signal *clock\_fl* sets the positive DAC section to '1' and the negative one to '0' for the 'test' step of the SAR algorithm. Finally, the output of the SAR comparators OP<sub>s</sub> and ON<sub>s</sub> are read. The nomenclature used is the same as the one used for the flash section. There