# DYNAMIC SILICON FIREWALL

A Thesis Submitted to the College of Graduate Studies and Research in Partial Fulfillment of the Requirements for the degree of Master of Science in the Department of Electrical Engineering University of Saskatchewan Saskatoon

By

Darrell Laturnas

©Darrell Laturnas, September 2006. All rights reserved.

## PERMISSION TO USE

In presenting this thesis in partial fulfilment of the requirements for a Postgraduate degree from the University of Saskatchewan, I agree that the Libraries of this University may make it freely available for inspection. I further agree that permission for copying of this thesis in any manner, in whole or in part, for scholarly purposes may be granted by the professor or professors who supervised my thesis work or, in their absence, by the Head of the Department or the Dean of the College in which my thesis work was done. It is understood that any copying or publication or use of this thesis or parts thereof for financial gain shall not be allowed without my written permission. It is also understood that due recognition shall be given to me and to the University of Saskatchewan in any scholarly use which may be made of any material in my thesis.

Requests for permission to copy or to make other use of material in this thesis in whole or part should be addressed to:

Head of the Department of Electrical Engineering 57 Campus Drive University of Saskatchewan Saskatoon, Saskatchewan Canada S7N 5C9

## Abstract

Computers are networked together in order to share the information they store and process. The internet connects many of these networks together, offering a multitude of options for communication, productivity and entertainment. It also offers the opportunity for unscrupulous individuals to contact these networked computers and attempt to appropriate or destroy the data on them, the computing resources they provide, and the identity or reputation of the computer user. Measures to secure networks need to be implemented by network administrators and users to protect their computing assets.

Firewalls filter information as it flows through a network. This filter can be implemented in hardware or software and can be used to protect computers from unwanted access. While software firewalls are considered easier to set up and use, hardware firewalls are often considered faster and more secure. Absent from the marketplace is an embedded hardware solution applicable to desktop systems.

Traditional software firewalls use the processor of the computer to filter packets; this is disadvantageous because the computer can become unusable during a network attack when the processor is swamped by the firewall process. Traditional hardware firewalls are usually implemented in a single location, between a private network and the internet. Depending on the size of the private network, a hardware firewall may be responsible for filtering the network traffic of hundreds of clients. This not only makes the required hardware firewall quite expensive, but dedicates those financial resources to a single point that may fail.

The dynamic silicon firewall project implements a hardware firewall using a softcore processor with a custom peripheral designed using a hardware description language. Embedding this hardware firewall on each network interface card in a network would offer many benefits. It would avoid the aforementioned denial of service problem that software firewalls are susceptible to since the custom peripheral handles the filtering of packets. It could also reduce the complexity required to secure a large private network, and eliminate the problem of a single point of failure. Also, the dynamic silicon firewall requires little to no administration since the filtering rules change with the users network activity. The design of the dynamic silicon firewall incorporates the best features from traditional hardware and software firewalls, while minimizing or avoiding the negative aspects of each.

## ACKNOWLEDGEMENTS

I would like to acknowledge Dr. Ron Bolton for his guidance and encouragement throughout my post-graduate program. His professionalism, humor, and patience were greatly appreciated.

I also need to thank the management and staff of Telecommunications Research Laboratories (TRLabs) for providing financial assistance and the use of their facilities throughout my research. The knowledge I gained and the equipment I used throughout my time with TRLabs were indispensable.

Finally, I would like to express gratitude to my family for believing in me throughout my education. I have never felt that anything was too hard to learn and never doubted my ability to succeed, due largely in part to their faith in me. This thesis is dedicated to the greatest teachers I have known: Alan Melenchuk in primary school, Donald Nakonechny in secondary school, Jerry Huff, Safa Kasap and Ron Bolton in university. To teach will always remain a noble pursuit, as it improves not only the individual, but future generations of mankind.

# CONTENTS

| Pe | ermission to Use                                                                                                                                                                                                                                                                                                                                                                  |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Al | i                                                                                                                                                                                                                                                                                                                                                                                 |

| A  | cknowledgements iv                                                                                                                                                                                                                                                                                                                                                                |

| Co | ontents                                                                                                                                                                                                                                                                                                                                                                           |

| Li | st of Figures vii                                                                                                                                                                                                                                                                                                                                                                 |

| Li | st of Abbreviations ix                                                                                                                                                                                                                                                                                                                                                            |

| 1  | Introduction       1         1.1       Motivation       1         1.2       Research Objective and Thesis Outline       1                                                                                                                                                                                                                                                         |

| 2  | Computer Networking42.1Network Models42.1.1Application Layer52.1.2Transport Layer62.1.3Network Layer62.1.4Data Link Layer72.1.5Physical Layer112.2Network Security112.2.1Common Network Attacks122.2.2Security Strategies142.3Packet Filtering15                                                                                                                                  |

| 3  | Embedded Systems       18         3.1       Embedded System Overview       18         3.1.1       Embedded System Components       18         3.2       System on a Programmable Chip       18         3.2.1       SOPC Design       20         3.2.2       Altera <sup>®</sup> SOPC Design Software       20         3.3       Dynamic Silicon Firewall Embedded System       21 |

| 4  | Silicon Firewall Hardware Components       23         4.1 Ethernet Device       23         4.1.1 Configuration       23                                                                                                                                                                                                                                                           |

|              |              | 4.1.2 Transmission                      | 24        |  |  |

|--------------|--------------|-----------------------------------------|-----------|--|--|

|              |              | 4.1.3 Reception                         | 24        |  |  |

|              | 4.2          | Content-Addressable Memory              | 25        |  |  |

|              |              | 4.2.1 CAM Writes                        | 25        |  |  |

|              |              | 4.2.2 CAM Reads                         | 26        |  |  |

|              | 4.3          |                                         | 28        |  |  |

|              |              | 4.3.1 $Nios^{(\mathbb{R})}$ Peripherals | 28        |  |  |

|              | 4.4          |                                         | 30        |  |  |

|              |              | 4.4.1 State Machine Entry               | 30        |  |  |

|              |              | 4.4.2 Transmit Interrupt State          | 34        |  |  |

|              |              | 4.4.3 Receive Interrupt State           | 36        |  |  |

|              |              | 4.4.4 Common States                     | 38        |  |  |

|              | ~            |                                         |           |  |  |

| <b>5</b>     |              |                                         | 44        |  |  |

|              | 5.1          |                                         | 44        |  |  |

|              |              |                                         | 44        |  |  |

|              | 5.2          |                                         | 48        |  |  |

|              |              | 5.2.1 Silicon Firewall Routines         | 49        |  |  |

| 6            | Tog          | ing and Results                         | 51        |  |  |

| U            | 6.1          | 8                                       | <b>51</b> |  |  |

|              | 6.2          |                                         | 51 $52$   |  |  |

|              | 6.2          |                                         | 52        |  |  |

|              | 0.5          |                                         | 99        |  |  |

| 7            | Sun          | mary, Conclusion and Future Work        | 60        |  |  |

|              | 7.1          |                                         | 60        |  |  |

|              | 7.2          |                                         | 61        |  |  |

|              | 7.3          |                                         | 63        |  |  |

|              |              |                                         |           |  |  |

| $\mathbf{A}$ | ppen         | lices                                   | 67        |  |  |

| A            | Ver          | log Code                                | 68        |  |  |

|              |              |                                         |           |  |  |

| Β            | B C Code 103 |                                         |           |  |  |

# LIST OF FIGURES

| 2.1  | Example TCP/IP Modeled Network                                                                                                                 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.2  | TCP Segment Structure                                                                                                                          |

| 2.3  | IP Datagram Structure                                                                                                                          |

| 2.4  | Ethernet Packet Structure                                                                                                                      |

| 3.1  | Altera <sup>®</sup> Stratix <sup>®</sup> PCI Development Kit $\ldots \ldots \ldots \ldots \ldots 22$                                           |

| 4.1  | CAM made from dual-port RAM: write functionality                                                                                               |

| 4.2  | CAM made from dual-port RAM: read functionality                                                                                                |

| 4.3  | State Diagram for Silicon Firewall                                                                                                             |

| 4.4  | Detailed State Diagram for Silicon Firewall                                                                                                    |

| 4.5  | Read Interrupt Type State Diagram                                                                                                              |

| 4.6  | Transmit Interrupt State Diagram                                                                                                               |

| 4.7  | Receive Interrupt State Diagram                                                                                                                |

| 4.8  | Release Packet State Diagram                                                                                                                   |

| 4.9  | Data Pre-fetch State Diagram                                                                                                                   |

| 4.10 | Read Ethertype State Diagram                                                                                                                   |

| 4.11 |                                                                                                                                                |

| 5.1  | Plugs Adapter Description                                                                                                                      |

| 5.2  | Plugs Example Routine                                                                                                                          |

| 6.1  | Host Communication Succeeding                                                                                                                  |

| 6.2  | Host Web Browser Received Message                                                                                                              |

| 6.3  | Host Communication Failing                                                                                                                     |

| 6.4  |                                                                                                                                                |

| -    | $\mathbf{HOSt}$ web Drowser rimed Out $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                           |

| 6.5  | Host Web Browser Timed Out $\dots \dots \dots$ |

## LIST OF ABBREVIATIONS

- ARDY Asynchronous Ready

- ARP Address Resolution Protocol

- ASIC Application-Specific Integrated Circuit

- CAM Content-Addressable Memory

- CPU Central Processing Unit

- CRC Cyclic Redundancy Check

- EPH Ethernet Protocol Handler

- FPGA Field-Programmable Gate Array

- FTP File Transfer Protocol

- HDL Hardware Description Language

- HTTP HyperText Transport Protocol

- IP Internet Protocol

- LAN Local Area Network

- MAC Media Access Control

- OS Operating System

- OSI Open Systems Interconnection

- PCI Peripheral Component Interconnect

- PDA Personal Digital Assistant

- PIO Parallel Input/Output

- PLD Programmable Logic Device

- PPP Point-to-Point Protocol

- RAM Random Access Memory

- SOPC System On a Programmable Chip

- TCP Transmission Control Protocol

- UDP User Datagram Protocol

# Chapter 1 Introduction

This chapter begins by outlining the computer security problems motivating this research. The research goals are then presented, followed by an outline of the entire thesis.

## 1.1 Motivation

This research is motivated by many factors in the realm of home computer security. It is becoming quite common in developed nations for people to have high-bandwidth internet connections in their homes, often connected to powerful personal computers. This combination of computing power and communication capability has become an inviting target for malicious hackers and programmers. By corrupting or gaining access to a computer, a malicious programmer may destroy or steal the information stored on that computer. Furthermore, they may appropriate the computer and network resources and use them for their own purposes, denying access to the legitimate user. Some malicious programmers then use these co-opted computers to spread worms, viruses and other forms of malicious software, often called malware. Email spam is sent out from these computers as well, in an effort to make money through fraudulent means and continue the spread of malware.

Gaining access to one computer system using another computer on a remote network is not trivial. To formulate a plan of attack requires knowledge of the victim computer, which operating system (OS) it is running, the services that the victim is providing to the network, and/or the software installed on that computer. Also, the underlying technology being used to provide network access to the victim

computer provides information on how to find and communicate with the victim. The operating system, software, and network services being used on a computer are choices left to the computer user. These choices are often made without security in mind. Users may choose to use an operating system because it comes pre-installed when they purchase a computer, or because it is the only one compatible with their favorite software. Similarly, the networking technology being used is a choice the user must make, though this choice is often determined by the choice of network service provider, since the home network technology must be compatible with the service provider's network technology. This most often results in choices which are not consciously made by the user, leading to the majority of home computer users running a Windows<sup>(R)</sup> operating system on their computer, with Ethernet networking technology connecting their computer to a home network or the internet. The popularity of Windows<sup>(R)</sup> operating systems and the Ethernet networking protocol has resulted in these technologies being the primary targets of malicious programmers. By designing malware for a Windows<sup> $\mathbb{R}$ </sup> operating system, the programmer knows that a large number of computers will be vulnerable to it, simply due to the popularity of the OS. Similarly, software for monitoring Ethernet networks has been developed which allows malicious hackers to get information from network traffic regarding which computers are on the network and which services they are using or providing.

The responsibility to maintain secure computers and networks for the average home user falls to three entities. First,  $Microsoft^{(\mathbb{R})}$ , the maker of  $Windows^{(\mathbb{R})}$ operating systems, releases security patches to help secure the operating system. Second, the user's internet service provider must monitor their networks to mitigate the spread of malicious software and to look for unusual network traffic that may be an indicator of a network attack. Finally, a large portion of computer security is left to the home user. Many commercial software products for home users have been developed to address the threats presented by the various malicious programs, such as viruses. In addition to software, there have been consumer hardware security products developed for computer users at home. The problem which has arisen is that many of these consumer products require knowledge, about the underlying technology being used, to be used effectively. This is knowledge which the average home user does not possess. The malicious programmers developing security attack strategies do have this knowledge, and they are using it.

## **1.2** Research Objective and Thesis Outline

This research explores how an embedded firewall, designed using a hardware description language, may improve upon the positive features and mitigate the negative aspects of traditional firewall implementations. The main focus is on the method of implementing a simple yet useful firewall for network users who are naive to the underlying technology and communication protocols involved in computer networking. This project will build upon and seek to improve upon the limited research done in the area of embedded hardware firewalls [1, 2].

The fundamentals of network functionality and security are presented in chapter 2. In chapter 3, the components and tools used in the design of embedded systems are discussed. The hardware design of the dynamic silicon firewall is presented in chapter 4, while the software components of the design are discussed in chapter 5. In chapter 6, the testing process and results of the conducted tests are explained. In chapter 7, the conclusions drawn from this project are presented and the direction for future work is suggested.

# Chapter 2 Computer Networking

This chapter focusses on the functionality and security vulnerabilities of computer networks. In order to better understand the way computer networks are attacked and the ways in which data is vulnerable, the fundamentals of computer networking are presented. Approaches to keep computer networks secure are also discussed, with an emphasis on network packet filters.

## 2.1 Network Models

Computers are networked together so that information can be shared. Networks, such as the internet, are very complex and made up of multiple communication protocols. Often, engineers and computer scientists organize the protocols into layers for easier understanding. Two main models of these layers exist [3], the most widely used are the Open Systems Interconnection (OSI) and the Transmission Control Protocol / Internet Protocol (TCP/IP) models. The TCP/IP model focusses on the hardware involved in computer networking, while the OSI model extends the TCP/IP model to include the software involved in computer networking. For the purposes of discussion, the TCP/IP model is more than adequate.

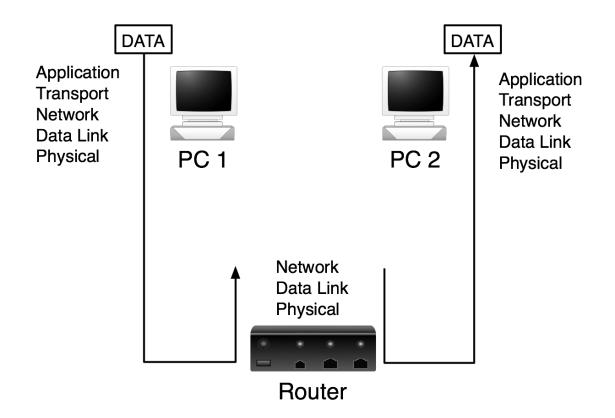

The TCP/IP model consists of five layers: Application, Transport, Network, Data Link and Physical. The application layer concerns the network software the end user is using. In the TCP/IP model, examples of the application layer would include web browsers and instant messaging software. The transport layer involves the protocols that applications use to communicate with each other. The transport layer is also the layer where any desired communication reliability is implemented, since the network, data link, and physical layers provide no guarantees for successful transmission. Furthermore, flow control is implemented at the transport layer. Examples of transport layer protocols are the Transmission Control Protocol (TCP) and the User Datagram Protocol (UDP). The network layer is responsible for routing information from one computer to another. It is also responsible for connecting multiple networks together. This is accomplished in the internet with the aptly-named Internet Protocol (IP). The data link layer is where data is encoded into bits for transmission onto the network medium. The most popular data link layer protocol used in home networking is the Ethernet protocol. Another example of a data link layer protocol is the Point-to-Point Protocol (PPP). The lowest layer in the TCP/IP network model is the physical layer. The physical layer is the actual medium used for communication. Examples of networking media are twisted-pair copper wires, coaxial cable, and optical fiber. Figure 2.1 illustrates a network using the TCP/IP network model. Data being sent from the PC on the left of the diagram travels down through the layers of the network model and onto the network. As the data is routed to its destination it may encounter a number of routers, requiring inspection of the data contained at the network layer. When the message reaches its final destination, the PC must go back up through the various layers in the network model to get to the application data.

#### 2.1.1 Application Layer

Many protocols operate at the application layer since applications often provide a variety of services. For example, a web browser application could implement not only the HyperText Transport Protocol (HTTP), used to access web sites, but also the File Transfer Protocol (FTP) if a user directs the web browser to an FTP server. Application layer protocols implement the functionality needed for a specific application to function, but they abstract the underlying network and rely only on the transport layer for transmission of data across the network.

Figure 2.1: Example TCP/IP Modeled Network

### 2.1.2 Transport Layer

The transport layer takes data from the application layer and passes it to the network layer. The main protocols that operate at the transport layer are the Transmission Control Protocol [4] (TCP) and the User Datagram Protocol [5] (UDP). The message passed from the application layer has data prepended to it, this data forms a header used to implement the transport layer protocols. Essential to all transport layer protocols are the source and destination port numbers. Port numbers represent a service running on a host, and they provide a way to differentiate data from multiple applications running on a single host.

UDP is a simple transport layer protocol. It is made up of only four pieces of data, each consisting of two bytes, that are prepended to the application layer message. This UDP header consists of the source and destination ports, as well as the length and checksum fields. The length field contains the size of the UDP segment, in bytes. The checksum field allows the destination host to check if any errors were introduced during transmission. This does not ensure successful transmission, but it does allow corrupted data to be discarded. As mentioned, the port numbers allow the application layer data to be delivered to the proper application running on the destination host.

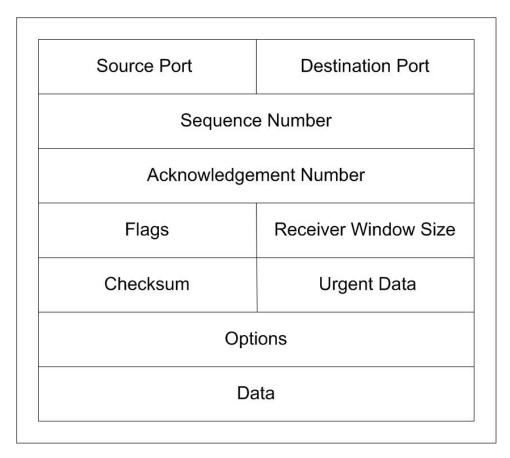

TCP is a more complex transport layer protocol, providing reliability and congestion control to the network. The TCP segment structure is shown in figure 2.2. The source and destination ports remain, as in UDP, but many other header fields are also required. The sequence and acknowledgement numbers are used to ensure reliable delivery of data. When a large piece of data is being transferred across a network, it is broken into pieces. The total data bytes being transferred are counted and each group of bytes in each TCP segment are given sequence numbers so that the data can be reconstructed after being delivered out of order. The acknowledgement number of an outgoing packet is the sequence number for the next byte expected from an incoming packet. Sending an acknowledgement number means that all data prior to the specified byte has been received successfully. The other feature that TCP provides to the network is congestion control. This is a service that benefits the network as a whole. When a network is very busy and saturated with packets, data can be lost due to packet buffer overflows. TCP provides mechanisms for recognizing network congestion, and reducing packet flow until the congestion is reduced.

#### 2.1.3 Network Layer

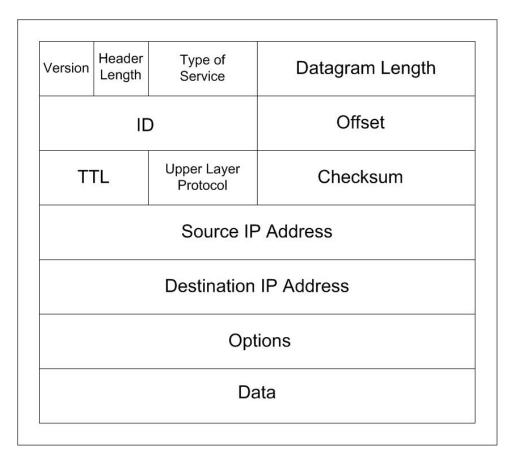

The network layer takes a UDP or TCP segment from the transport layer and sends it to the data link layer for transmission. As with the transport layer, network layer protocols are implemented by adding data to the transport layer segment, forming what is called a network layer datagram. Internet Protocol datagram is an appropriate term when the network layer protocol being used is IP. The Internet Protocol [6] operates at the network layer and is responsible for the routing of datagrams from one computer to another across a network.

Figure 2.3 illustrates the IP datagram format. At the heart of the Internet

Figure 2.2: TCP Segment Structure

Protocol is the Internet Protocol address, or IP address. The IP address is made up of four bytes that define a specific computer on a network. These four bytes can be divided into the network and host portions of the IP address. The network portion is used to identify a group of hosts that all belong to the same network, while the host portion of the IP address specifies an individual host on a network. The network and host portions of the IP address are essential in routing, as packets must first reach the proper destination network before they can reach the proper destination host.

The Address Resolution Protocol [7] (ARP) also operates at the network layer and is responsible for connecting hardware media access control addresses and IP addresses. Media access control addresses will be discussed further in the data link layer section. ARP is an essential service provided by the network layer as it connects the network IP address with the addresses used at the data link layer.

Figure 2.3: IP Datagram Structure

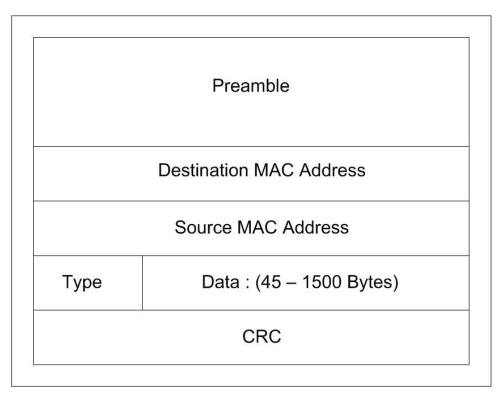

### 2.1.4 Data Link Layer

The Ethernet Protocol [8] operates at the data link layer and defines what signals to send on the physical layer to allow two computers to communicate. Since its invention in the 1970s, it has become the dominant networking protocol for local area networks. An Ethernet network can run over twisted-pair copper wire, coaxial cable, or optical fiber. It can also run at a variety of speeds: 10Mbps, 100Mbps or 1Gbps. Independent of transmission medium and speed, all Ethernet flavors share a few characteristics.

All Ethernet variants are unreliable connectionless services. Ethernet is connectionless in that an adapter does not directly contact the adapter with which it wants to communicate. An Ethernet adapter encapsulates information into a frame of data, often called a packet, and transmits that onto the transmission medium. All adapters connected to the medium then receive that frame of information. Ethernet is considered unreliable because there is no acknowledgement from the intended recipient of the information as to whether the frame was received without error. This raises the question of how the intended recipient knows whether a frame is meant for it, and how it knows the frame is error-free.

Ethernet relies on hardware addresses that are unique to each hardware adapter. These addresses are often called Media Access Control (MAC) addresses, and they consist of a unique six-byte identifier. The MAC address of the intended recipient of an Ethernet frame is included in the frame itself (as is the MAC address of the transmitting adapter), so adapters can check each packet of information to see if it is for them. Once an adapter has determined that it is the intended recipient of a packet, it must check if any errors were introduced during transmission. This is done with a Cyclic Redundancy Check (CRC). Before sending a frame out onto the transmission medium, an adapter appends four bytes to the end of the frame which are obtained from a mapping of the other bits in the frame. This allows receiving adapters to check for errors by performing the same mapping of the data and comparing the results. If the CRC code calculated by the transmitting adapter and sent with the frame does not match the CRC code calculated at the receiving adapter, then it can be concluded that an error occurred during transmission.

Now that the functionality of the Ethernet protocol has been discussed, the Ethernet packet structure can be examined. Figure 2.4 illustrates the fields of an Ethernet packet. The preamble consists of 8 bytes where the first seven bytes consist of the repeated binary pattern 10101010. The eighth byte is 10101011. Alternating bit values allow a receiving adapter to synchronize to the clock of the transmitting adapter, allowing bit positions to be determined. The final byte ends with two high bits. These bits let the adapter know that the preamble is over. The destination and source MAC addresses, along with the CRC field allow adapters to recognize packets that are destined for them and to ensure they have been received without error. Encapsulated between the MAC addresses and the CRC are the type field is a two-byte value that defines the network layer protocol being used, while the data

Figure 2.4: Ethernet Packet Structure

field contains the information being sent by the network layer.

### 2.1.5 Physical Layer

As previously mentioned, the physical layer is the lowest layer in the TCP/IP network model. It represents the physical medium used in communication. This could be optical fiber, coaxial cable, or twisted-pair copper wire. Twisted-pair copper wire is widely used in Ethernet networks [3].

## 2.2 Network Security

There are many reasons for people to connect computers together into a network. Some examples of internet applications include: banking, where someone may pay bills or set up investments; entertainment, where people may enjoy multiplayer online games or streaming media; and sharing information, by sending email or surfing the world-wide web. To accomplish these tasks, personal information often needs to be shared and transmitted over a network. Since personal information can be used for financial gain, some people try to gather this information and either sell it or use it to make money. The internet, by connecting different networks together, can provide a means for unscrupulous people to search for and steal valuable personal information. Network security measures must be taken to protect this data, ensuring only authorized individuals can access it.

#### 2.2.1 Common Network Attacks

Computers execute instructions. These instructions can be pre-defined and organized into computer programs, or software, that tells the computer what to do in certain circumstances. Unfortunately, the people writing computer software can not consider all possible circumstances under which a computer may be executing instructions. These overlooked conditions can leave vulnerabilities which someone may use to gain unauthorized access to a computer [9]. Software containing overlooked or unintentional errors can lead to someone gaining remote access to a computer over the internet, especially if the erroneous software is a networked application. Before software can be exploited, a remote attacker must first find a target for his attack and then gain information about the system which the software is running on.

Many attempts at computer intrusion begin with port scanning [10]. Port scanning is the process of sending out packets to either a specific IP address or an IP address range and attempting to connect to specific UDP or TCP ports. Since most networked programs accept connections only on specific port numbers, any attempts to connect that succeed identify both that a host is connected to the network and that it is running a specific application. Even connection attempts that fail can identify a host as being connected to the network if the host explicitly denies the connection. Once an attacker knows a host IP address and some services that are running on that host, they may begin trying to gain access to the system with usernames and passwords, or by using any known vulnerabilities in the code of the running network application.

Another way to gain information from a network is by network sniffing [9]. In

Ethernet networks, recall that packets are sent to all hosts on the local network and each Ethernet adapter is trusted to only look at packets destined for themselves. Unfortunately, it is easy to get an adapter to look at all packets being sent to it, whether the packets are destined for that adapter or not. This can allow people to not only gain network information such as IP addresses, but even usernames and passwords used to access network services. For example, when someone signs into an email server, the packets that leave their computer with the private username and password in them are first sent to all hosts on the user's local network. Anyone sniffing packets on that local network could then recover the private username and password. For this reason, some email servers encrypt all data including usernames and passwords.

Some network attacks are designed to gain information by attempting to trick a network host into communicating with a different host than was intended. This type of attack can be implemented in a number of ways, but they all rely on manipulating the networking protocols. Spoofing network packets is the act of sending packets out from a host, but changing the IP and/or MAC address to make it appear that the packets were sent from a host other than the actual sender [9]. This type of attack usually needs to be used in conjunction with an attack against a specific service or networked application at one of the higher layers in the network stack. An example of this type of attack is ARP cache poisoning.

As mentioned earlier, ARP is used to associate IP and MAC addresses. When an Ethernet adapter wants to transmit packets to a specific host, it needs to know the MAC address of the destination host. The source host sends out an ARP request, which is a request for the MAC address associated with the destination IP address. The ARP reply contains the association of a MAC address with an IP address. Once the source host has the destination IP and MAC addresses, it can send packets out onto the network to the destination host. However, when ARP was created, it was assumed that ARP replies would only come as responses to ARP requests. Unfortunately, a spoofed ARP reply packet will be accepted by hosts as a response to a request. A packet could be sent out from a host that associates its own MAC

address with the IP address of a different host. In this case, all traffic destined for the second host would be delivered to the first host.

Not all network attacks seek to steal data or services. Some are designed to deny use of network resources to legitimate users. These types of attack are aptly named denial of service attacks [9]. There are two main types of denial of service attacks, those that seek to flood services and those that seek to crash services. Flooding a service refers to sending so much traffic to a specific host on a specific port that the host is unable to answer service requests. If enough traffic is sent to a victim host, it will be overloaded and unable to respond to even authorized service requests. Crashing a service refers to using vulnerabilities in the way the service software was written to halt execution of the software. For networking services, this is usually accomplished by sending packets that are malformed or have invalid data in them to the victim host [9]. If the service software doesn't know how to deal with the malformed packets, it may cause the program to halt execution, which also stops the service from being available.

#### 2.2.2 Security Strategies

There are many strategies that have been developed to try to prevent the above attacks from succeeding [11]. The simplest, and least effective, is often called "security through obscurity" and doesn't implement any security measures at all. Security through obscurity relies on believing that a host would not be attacked because no one knows about it or because it is assumed no information of interest is on the host. Since it is incredibly easy to gain information about hosts on a network, obscurity doesn't last long if someone is probing a network for weak points. The idea that a host is of little interest no longer holds true either, as many attackers will gain access to unprotected systems and use them to attack more interesting and valuable hosts.

A better, and more widely adopted, security strategy is host security [11]. Host security means that each individual host on a network has security measures in place to protect them from attacks. This could include additional hardware or software added to the host machine that prevents or counters the attacker's methods. Host security can work well on individual systems, however it can become quite complex when trying to secure a large network with many connected hosts. Each host requires individual attention because different hosts will have different software and services running on them. As discussed, different pieces of software will have different inherent vulnerabilities in them. Even if all machines on the network were configured identically, it could still be very difficult and time-consuming to implement host security if the number of hosts is large.

A more efficient and effective method is to secure the underlying network [11], instead of securing individual hosts on the network. This network security strategy is composed of using: authentication to limit who is allowed to use network resources, encryption to prevent unauthorized individuals from gaining information by sniffing network packets, and filters that look at network traffic and remove packets that are malformed or come from untrusted hosts or networks. Filtering network packets as they travel through the network is considered key to securing the network infrastructure. Network packet filters are relatively easy to set up and maintain, they scale to support large networks, and they remain transparent to network users [12]. The term "firewall" is a common name for a network packet filter being used to restrict communication between two or more networks.

### 2.2.3 Packet Filtering

Packet filtering is the process of filtering network traffic based on various rules. By default, the packet filter can either allow or deny all traffic, meaning the rules specify conditions under which specific packets are allowed onto the network or are dropped, respectively. The most secure method is to deny all packets that try to come onto the network and only allow specific packets to pass when they match certain filter rules. The filter compares the data in individual packets with a set of rules that defines what to do when there is a match between a rule and a packet. The data used to define filtering rules is primarily based on the information used to implement the various network protocols, such as TCP port numbers, IP addresses or MAC addresses. The consequences of a rule match are often to drop the matching packet, though it will

depend on the default filter conditions. For example, a filter could allow all traffic by default and have rules looking for packets containing matching source MAC or IP addresses with specific transport layer port numbers. By dropping packets that match this rule, a network could prevent specific service requests coming from a specific host. Packet filtering requires a tradeoff between the number of memory accesses needed to implement the filter and the maximum achievable network transfer speed [13]. There is some overhead as the filter rules need to be compared to the network traffic and each memory access takes time to complete. This overhead needs to be minimized in order to achieve a desired network transmission rate and keep the network filter transparent to the end users. Several algorithms exist to minimize this overhead for software-based packet filters, but great speed gains can be made by selecting fast memory, or by using memory that has been adapted for pattern matching, to reduce filtering time.

## 2.3 Content-Addressable Memory

Content-addressable memory (CAM) is similar to random access memory (RAM) except logic comparison circuitry is associated with each bit of storage. This logic comparison circuitry serves to compare all data storage locations in memory at the same time when a search is being conducted. Random access memory associates a piece of data with an address. When an address is provided to RAM, the data at that location is returned. To search for a specific piece of data in RAM requires one to check the data at each address sequentially. This means that the time it takes to search through RAM is dependent upon the number of addressable locations. Content-addressable memory, on the other hand, accepts a piece of data as input and returns the address where that data is located in memory. It searches all data locations at the same time and can identify the location of the data in one clock cycle. This makes CAM an excellent tool for pattern matching applications such as the comparison between internet packet data and pre-defined packet filter rules [14]. Content-addressable memory has become popular with hardware firewall manufacturers because it offers massive parallelism.

# Chapter 3 Embedded Systems

This chapter focusses on the components and design of embedded systems. After discussing the general components that make up an embedded system and the tools used to create them, the specific tools and components used in designing the dynamic silicon firewall embedded system will be presented.

## 3.1 Embedded System Overview

An embedded system is a computer system that has been designed to perform specific tasks, in contrast to a personal computer which is designed to perform general tasks. Also, this specific computer system has been incorporated into a larger system or product [15]. Many consumer electronics products are embedded systems, such as digital music players, personal digital assistants, or cellular phones. Since embedded systems perform specific tasks, the required hardware is customized to the specific application. By selecting only the hardware needed to perform the required task, embedded systems efficiently use hardware and are therefore economical. Any software that may be running in an embedded system is called firmware [16]. Firmware would also be customized to the specific task being performed, and to the limited hardware chosen for the system. The hardware and software in combination are often referred to as an embedded device.

### 3.1.1 Embedded System Components

The hardware components that make up an embedded system are chosen depending on the purpose of the embedded device, but they are drawn from the same types of hardware that general computers use [15, 17]. Embedded systems may have a variety of hardware devices, including: processors, volatile and non-volatile storage, displays, and other input/output peripherals.

The hardware controlling the entire system may consist of a simple logic circuit, or it may be more complex, such as a microcontroller or microprocessor. If a microprocessor is required, then it will likely be executing some sort of firmware. Volatile or non-volatile memory may be used to store data in the system. This may be flash-memory for storage of firmware or other non-volatile information, or simple random access memory used for temporary storage. If user input is required, simple buttons may suffice, however, some embedded systems use more traditional input devices such as a keyboard and mouse. In short, embedded computer systems can draw on hardware available for general computing systems, but are tailored for the specific task they need to accomplish.

For embedded devices that contain a microprocessor and software, the software needs to be compiled to run on the specific hardware in the system. This may be done using cross compilers [16], where the firmware is compiled on a general purpose computer, then transferred into the embedded system. Some embedded devices run an embedded operating system that bridges the gap between hardware and software. These embedded operating systems are also called real-time operating systems [15, 16], as they can change program execution in real-time, depending on external inputs. For embedded systems without an operating system, the firmware needs to include the routines used to access each peripheral being used in the system.

## 3.2 System on a Programmable Chip

The components used in an embedded system draw from the same types of hardware as a general computing system, but they are chosen so that the system is efficient and economical to produce. While many embedded systems will use individual, discretely packaged components that are combined together on a printed circuit board, there is another alternative. Many embedded systems are defined in software and implemented on a programmable logic device (PLD), such as a field-programmable gate array (FPGA). This type of embedded system is called a system on a programmable chip (SOPC) [15].

### 3.2.1 SOPC Design

Systems on a programmable chip contain components that are defined using a hardware description language (HDL) such as VHDL [18] or Verilog [19]. Defining a system using an HDL offers many benefits. First, components can be designed once and re-used in different systems. Second, components can be purchased as intellectual property and used in system design. Third, the entire system can be extensively tested through simulations before a hardware version is put to market. Finally, the entire system can be tested in hardware on an FPGA and then transferred into an application-specific integrated circuit (ASIC) if desired. Also, since the system is defined with software modules which are then translated into logic on a PLD, any custom logic that is needed in addition to standard components can be easily added in a custom software module.

# 3.2.2 Altera<sup>®</sup> SOPC Design Software

The Altera<sup>®</sup> corporation specializes in SOPC solutions, including PLDs, associated software tools and intellectual property software blocks. The primary software package from Altera<sup>®</sup> is the Quartus<sup>®</sup> II design software [20]. It contains tools for all aspects of the design cycle. Designs can be created in block diagram form, with blocks representing the individual HDL modules. The design as a whole is then synthesized as each HDL module is compiled. The compiled project is then fitted to the individual PLD and the result can then be used to program the logic device being used. Tools for design analysis and verification are also included in Quartus<sup>®</sup> II. Timing requirements and logic functionality can be analyzed through software simulations or they can be investigated on a PLD as the design operates.

For embedded systems,  $Quartus^{\textcircled{R}}$  II also comes with a tool called SOPC Builder

[20]. SOPC Builder integrates the various components required for an embedded system. Altera<sup>®</sup> provides many HDL modules, as commercially available intellectual property, that work with SOPC Builder. This includes memories, communication interfaces, and even a configurable soft-core processor. SOPC Builder integrates the processor, busses and peripherals into a memory-mapped system. Firmware can then be written for the processor to access and manipulate the peripherals as needed. Various software libraries and application examples are also provided by Altera<sup>®</sup> for firmware development.

## 3.3 Dynamic Silicon Firewall Embedded System

The dynamic silicon firewall is an embedded system on a programmable chip. The decision to implement the design on a PLD allowed the use of pre-written intellectual property components, the ability to test the system using simulation, and the capability to easily transition the design to an ASIC, if desired. The network filter was to be designed in hardware as a module of custom logic, which lends itself well to PLDs and the use of an HDL. As an HDL module, the filter was relatively easy to test and modify as needed throughout the design cycle.

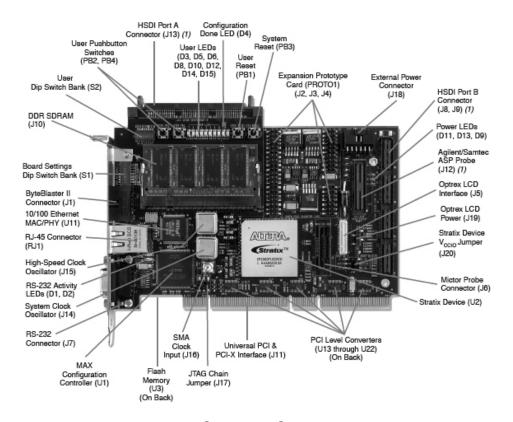

#### 3.3.1 Dynamic Silicon Firewall Testbed

The dynamic silicon firewall was developed and tested on an FPGA development kit from Altera<sup>®</sup> [21]. This kit includes a number of features and peripherals that work in conjunction with SOPC Builder and Quartus<sup>®</sup> II. The FPGA on the board is the Stratix<sup>®</sup> EP1S25F1020C5 device, a general purpose FPGA featuring 25,660 logic elements, 1,994,576 bits of RAM, 10 digital signal processing blocks and 6 phase locked loops. The board comes with 33MHz and 100MHz oscillators, though other clock speeds can be synthesized using HDL modules. The onboard memory includes 256MB of dual data rate RAM and 8MB of flash memory. The hardware board comes in the form of a Peripheral Component Interconnect (PCI) board supporting both the 32 and 64 bit PCI bus configurations. There are expansion ports on the

Figure 3.1:  $Altera^{(R)}$  Stratix<sup>(R)</sup> PCI Development Kit

board that support daughter-cards which can be custom made, or purchased from  $Altera^{(\mathbb{R})}$ . Various communication interfaces are also included, such as serial, parallel and Ethernet ports. The hardware board is shown in figure 3.1.

In addition to the hardware, various software components are also used in the testbed. The firmware being used to test the system is based on an example web server program from Altera<sup>®</sup>. The web server accepts HTTP requests and serves simple web pages. The dynamic silicon firewall was tested by monitoring which specific hosts were allowed or denied access to the web server. The web server relies on another firmware component from Altera<sup>®</sup>. The Plugs Ethernet Library [22] is a set of routines, provided by Altera<sup>®</sup>, used to configure Ethernet devices, and to transmit and receive data packets. Plugs provides the use of the raw Ethernet protocol at the link layer, ARP and IP at the network layer and both TCP and UDP at the transport layer. For the example web server application, Ethernet, ARP, IP and TCP are used from the Plugs library.

## CHAPTER 4

## SILICON FIREWALL HARDWARE COMPONENTS

In this chapter, the hardware design of the dynamic silicon firewall is presented. The core hardware components of the design: the Ethernet chip, the CAM, the soft-core processor, and the firewall HDL module are discussed in detail.

## 4.1 Ethernet Device

The Ethernet chip being used in this design is the LAN91C111 from Standard Microsystems corporation. It is a mixed-signal analog/digital device that implements the Ethernet protocol at transmission rates of 10 or 100 Mbps in either half or full duplex mode. It has 8kB of buffer memory, which is used for both transmission and reception. The registers used to configure and utilize the MAC implementation on the chip are mapped into four banks, each bank holding eight of the 16-bit registers.

### 4.1.1 Configuration

The LAN91C111 is configured by accessing various registers in the device. In this application, auto-negotiation is enabled so that the Ethernet device can achieve the highest performance when it is connected to various networks with differing speeds. Auto-negotiation on the LAN91C111 can result in 10 or 100 Mbps speeds, in either full or half duplex mode. Three interrupt sources are also enabled during configuration. Reception and transmission completions are denoted by an interrupt, as are Ethernet protocol handler (EPH) errors. EPH errors can occur if the physical medium is disconnected or if a fatal transmission error occurs, such as if collisions occur or a transmit buffer under-run occurs.

#### 4.1.2 Transmission

The first step in Ethernet transmission for the LAN91C111 is to allocate a portion of the onboard 8kB buffer memory to hold the packet being transmitted. The packet is then loaded into the allocated memory and assigned a packet number, which is used to enqueue the packet for transmission. Once the packet number has been enqueued, the packet will be keyed onto the transmission medium, assuming that transmissions have been enabled. When the transmission is completed, the first word in the allocated buffer memory is written with a status word. This status word contains important information on the most recently transmitted Ethernet frame, noting if an error occurred or if the transmission succeeded. An interrupt occurs in either case, however the transmission sequence stops in the case of a failure. In addition, the packet number is reported if a failure occurred, whereas the number is moved to a completed transmission queue upon success. When handling the inevitable transmission interrupt, the status word needs to be examined to determine success or failure. If the transmission succeeded, then acknowledging the interrupt is all that is needed to remove the completed packet number from the completed transmission queue, and to continue further transmissions. If the transmission failed, the type of error can be determined from the status register. To retransmit a failed packet, the packet number can be re-enqueued for transmission and it will be sent out again once transmissions have been re-enabled.

#### 4.1.3 Reception

Assuming the LAN91C111 has been enabled to receive packets, the device will first request a portion of buffer memory to hold an incoming packet. When a packet arrives on the interface, it is assigned a packet number and the incoming data is written to the allocated segment of memory. If an overrun of memory occurs, the packet is dropped and the allocated memory is released. When reception has finished, the first word in the allocated buffer memory is written with a status word. This status word contains information on any errors that may have occurred during reception, and denotes if the packet was longer or shorter than a standard Ethernet frame size. A cyclic redundancy check (CRC) is performed on the received frame, and if the result shows that no errors are present in the received data, then the associated packet number is written to a reception queue and an interrupt occurs. If the CRC shows that errors exist in the received data, the packet is dropped, the memory is freed, and no interrupt occurs. When a reception has successfully occurred, the data can be retrieved from the reception area of buffer memory by using the packet numbers in the reception queue. As each packet in the reception queue is processed, commands to remove the packet number from the reception queue and to release the allocated buffer memory must be issued.

## 4.2 Content-Addressable Memory

The content-addressable memory (CAM) used in the dynamic silicon firewall holds 32 32-bit words and was created using dual-port random access memory blocks [23]. Since the system is synthesized on an Altera<sup>®</sup> Stratix<sup>®</sup> FPGA, the Altera<sup>®</sup> alt-syncram megafunction was used for the dual-port memory blocks. The altsyncram megafunction supports single and dual-port configurations for both random-access and read-only memory [24]. Each port of the dual-port RAM is configured independently to provide the separate write and read functionalities of the CAM.

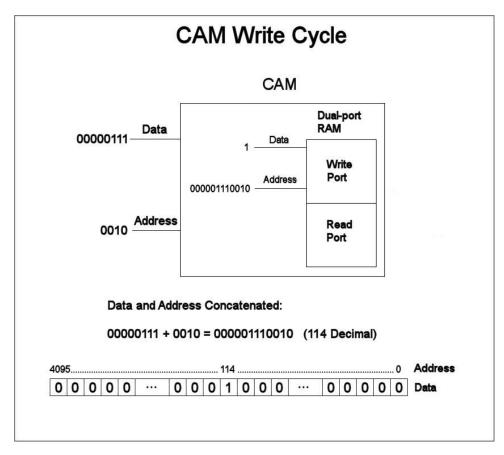

#### 4.2.1 CAM Writes

Write operations are performed by storing a one-hot encoded value. For example, take a 16-byte sized CAM. Each byte would be translated into a 256-bit one-hot word. With 16 of these one-hot encoded bytes, the total storage needed is 4,096 bits. Each write operation toggles one of these bits. The write port of the dual-port RAM has a single bit as the data input and 12 bits for the address input. These 12 bits are used to access the 4,096 individual bits. The 12-bit address going to the RAM is made up of the data and address inputs to the CAM. The CAM data byte and the four bits used to address the 16 CAM locations are concatenated together

Figure 4.1: CAM made from dual-port RAM: write functionality

to provide the 12-bit address going to the RAM, with the CAM data byte in the most significant position. Figure 4.1 illustrates an example write operation for the 16-byte sized CAM. In this example, it is desired that a decimal data value of seven is written to address number two in the CAM. The concatenation shows that the address presented to the RAM is 114, meaning a one is written to the 114th bit of the 4,096-bit storage area. This example will be furthered by looking at the CAM read functionality.

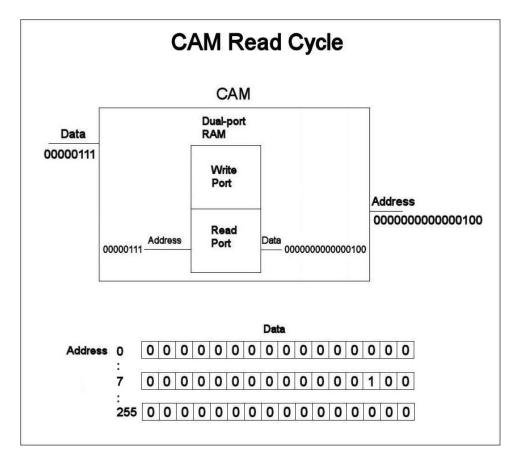

#### 4.2.2 CAM Reads

The port of the dual-port RAM being used for CAM reads, considering our example 16-byte CAM, has a byte-wide address as input and a 16-bit data output. This equates the 4,096 bits of storage into 256 words, each 16 bits in length. The 16 bits of output data represent the 16 storage locations in the CAM. The byte-wide RAM

Figure 4.2: CAM made from dual-port RAM: read functionality

address is connected to the CAM input data byte. When a CAM search is performed, the data byte used as input results in a 16-bit one-hot output, effectively searching all 16 storage locations in the CAM. A value of one at any bit in the output denotes that the input data byte was previously written to one of the 16 storage locations in the CAM. Figure 4.2 shows an example read operation, assuming that a data value of seven was previously written to address number two in the CAM. The input byte has the value of seven, and the 16-bit output has the value one at the third bit location. This represents address number two, counting up from zero. Looking back at the write example, we can see this result comes about because a one was written to the 114th bit of the 4,096-bit storage area. When this storage area is configured as 256 16-bit words, the 114th bit is the third bit of the seventh word, representing a value of seven written to address number two.

# 4.3 Nios<sup>(R)</sup> Soft-core Processor

The Nios<sup>®</sup> central processing unit (CPU) is a soft-core, pipelined, general purpose, reduced instruction set microprocessor provided by  $Altera^{(R)}$  for use in PLDs in either a 16 or 32-bit architecture form [25]. Both variants use a 16-bit instruction set, which reduces instruction-memory bandwidth requirements. Since the Nios<sup>(R)</sup> core is configurable, it is possible to add custom logic directly into the arithmetic logic unit and to add custom instructions to the Nios<sup>(R)</sup> instruction set. The Nios<sup>(R)</sup> CPU has a five-stage pipeline with separate data and instruction busses in accordance with the Harvard computer architecture. Each bus follows the Avalon<sup>(R)</sup> bus specification, which is an  $Altera^{(\widehat{\mathbb{R}})}$  bus specified for use with the Quartus  $^{(\widehat{\mathbb{R}})}$  II and SOPC Builder design tools. The instruction bus master only reads instructions from memory and provides them to the CPU for execution, it never writes any information to memory. It can use an optional cache memory if the instruction memory being used has slow access speeds. The data bus master is a 16-bit wide bus when the 16-bit  $Nios^{\textcircled{R}}$ architecture is used, and is 32 bits wide for the 32-bit architecture. The data master is used for three purposes. It reads data from memory when the CPU is executing a load instruction, it writes data to memory when the CPU is executing a store instruction, and it reads interrupt vectors from the interrupt vector table when an interrupt occurs.

Altera<sup>®</sup> provides a number of soft-core peripherals for use with the Nios<sup>®</sup> CPU. These peripherals exist as HDL modules which integrate with the Altera<sup>®</sup> design tools and allow rapid development of complete systems, since the peripherals operate on the Avalon<sup>®</sup> bus and come with software drivers for use with Nios<sup>®</sup> software programs. Two Nios<sup>®</sup> peripherals are used in the dynamic silicon firewall project.

# 4.3.1 $Nios^{\textcircled{R}}$ Peripherals

The timer peripheral is essential, as it provides the dynamic aspect of the project. A timer is used to determine when the IP addresses, used as filtering rules, should

be purged so that packets received from those addresses are no longer trusted. The  $Nios^{\mathbb{R}}$  timer peripheral is a simple interval timer that is configured and controlled through six 16-bit registers [26]. Two of these registers are used to hold the value of the timer period. Another two of these registers can be used to determine the current value of the timer while it is running. This leaves two registers for status information and timer control. The status register simply denotes whether the timer is currently running or if it has reached the period value stored in the timer period registers. The control register contains four bits of interest. Two bits are used to start or stop the timer. The start and stop bits are event driven, not value driven, meaning the start or stop function occurs when written with a one. Writing a zero to either bit has no effect. The other two bits in the control register are used to enable timer interrupts and to determine how the timer reacts at the end of each period. When the interrupt bit is set to one, the timer will generate an interrupt at the end of every period. Setting this bit to zero ensures no timer interrupts occur. The continuous bit, when set to one, causes the timer to reload and restart at the end of every period. When the continuous bit is zero, the timer reloads, but does not restart at the end of the period. Use of the start bit is then required to restart the timer. For the dynamic silicon firewall project, the timer generates an interrupt every two minutes. It is in the interrupt service routine that the purging of IP addresses occurs. The timer operates in continuous mode, meaning the timer will simply continue to generate interrupts every two minutes for the periodic removal of filtering rules.

The parallel input/output (PIO) peripheral is used to provide a memory-mapped interface between software running on the Nios<sup>®</sup> CPU and user-created logic that is operating external to the system created using SOPC Builder [26]. The PIO port can be configured for input-only, output-only, or bi-directional accesses between the internal Avalon<sup>®</sup> bus and external logic. Data reads or writes occur through register accesses, as does configuration. The PIO can be configured to capture edge transitions and to generate edge or level-triggered interrupts, if desired. For the dynamic silicon firewall project, PIO peripherals are used to connect the custom Verilog packet filter to the  $Nios^{\mathbb{R}}$  CPU.

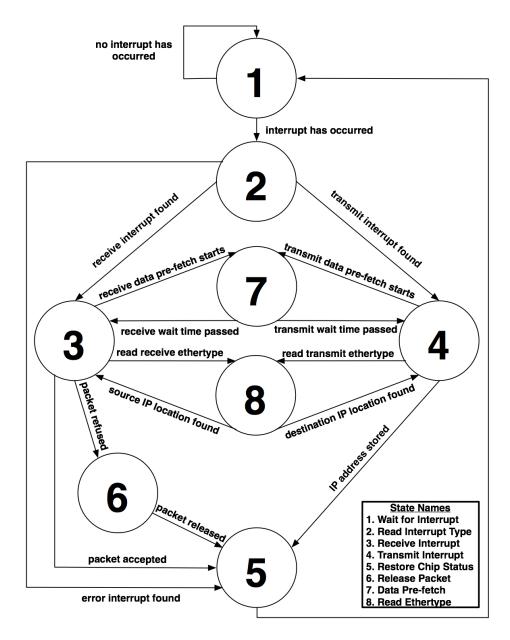

## 4.4 Verilog Silicon Firewall Module

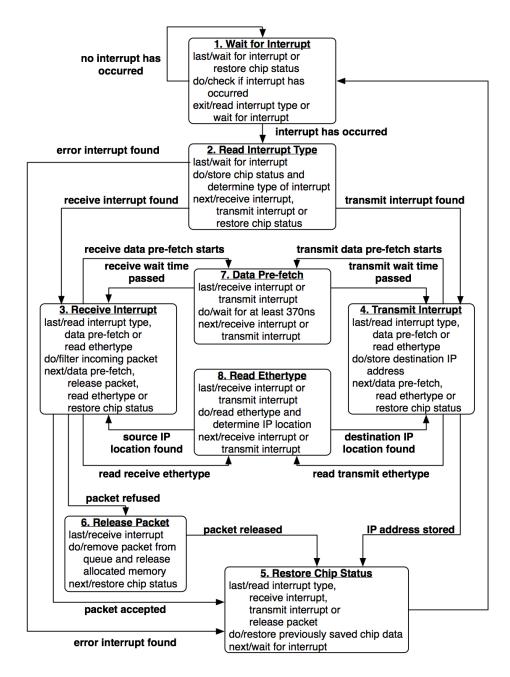

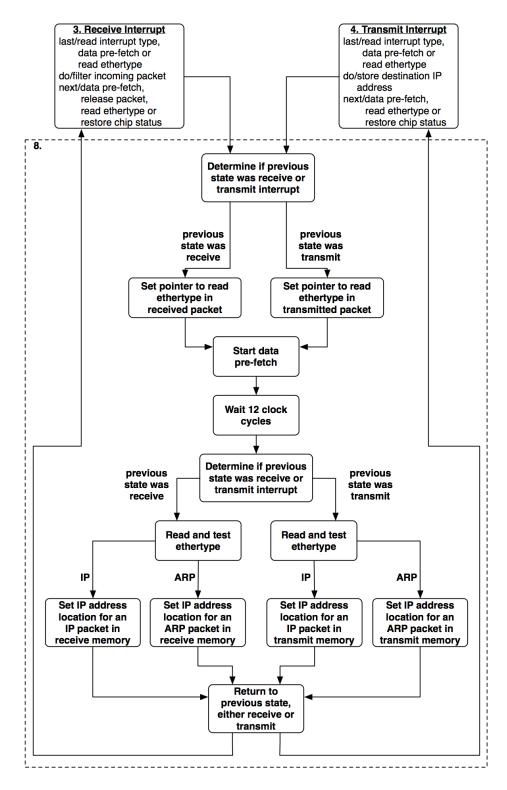

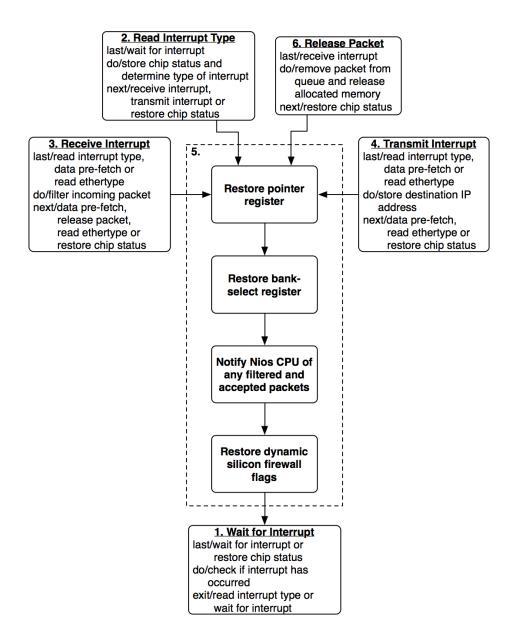

The system component that is performing the filtering operation on Ethernet packets is a finite state machine designed as a custom Verilog module. A state diagram for this finite state machine is shown in figure 4.3. From this diagram, it can be seen that there are eight states in total, with a number of labeled transitions. A more detailed state diagram can be seen in figure 4.4. This diagram includes some state information regarding the last and next states, as well as what functionality is performed in each state.

The finite state machine is implemented using nested case statements. In the outer case statement, each case represents one of the finite states, while the inner case statement has a case select parameter that is incremented on each system clock cycle to step through command execution and to determine the next state. This allows timing requirements to be met for any Ethernet chip instructions, since the system clock speed will always be known and any instructions being executed in the inner case statement can be ordered to execute in any multiple of clock cycles so that the LAN91C111 timing requirements are met.

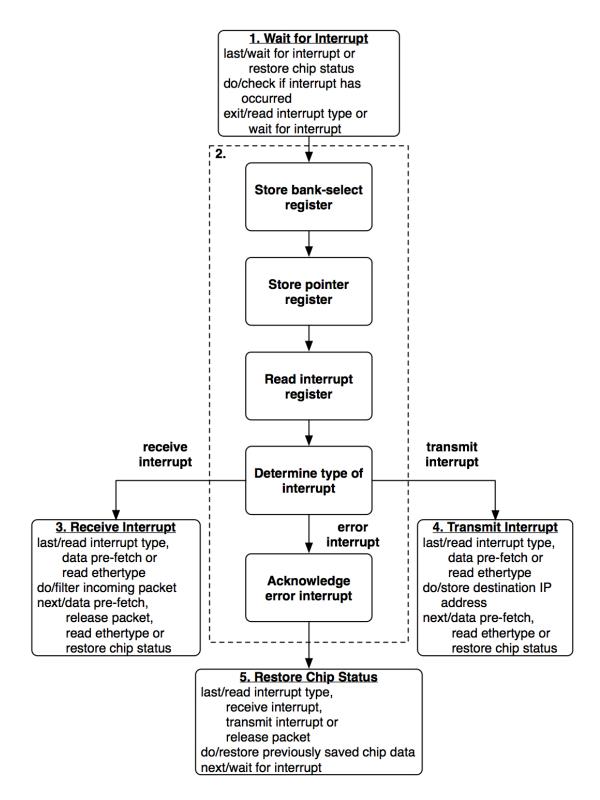

#### 4.4.1 State Machine Entry

The entry point to the state machine occurs when an interrupt is generated by the LAN91C111 Ethernet chip. The first state (Wait for Interrupt) simply waits for a new interrupt to occur, and then transitions to the second state (Read Interrupt Type). A diagram illustrating the flow of the second state is shown in figure 4.5. The second state begins by storing specific LAN91C111 registers, so that the Ethernet chip can be restored to pre-interrupt status after the interrupt has been processed. The next transition is then determined by finding out the cause of the interrupt, which may be due to reception, transmission, or errors. Ethernet is an unreliable transmission protocol, meaning that ensuring successful communication is relegated

Figure 4.3: State Diagram for Silicon Firewall

Figure 4.4: Detailed State Diagram for Silicon Firewall

Figure 4.5: Read Interrupt Type State Diagram

to the higher levels of the network stack, like the transport layer. Therefore, the error condition is the easiest to deal with, as it simply requires an acknowledgement of the interrupt and the restoration of the system to allow future transmissions and receptions. In this case, the second state transitions to the fifth state (Restore Chip Status).

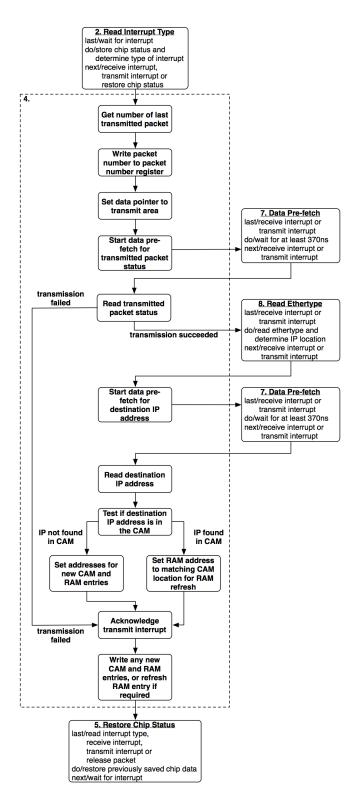

#### 4.4.2 Transmit Interrupt State

In the case of a transmission interrupt, the second state (Read Interrupt Type) transitions to the fourth state (Transmit Interrupt). A diagram of the Transmit Interrupt state is shown in figure 4.6. The purpose of the fourth state is to obtain and store the destination IP address from the last successfully transmitted Ethernet packet. First, the packet number of the last transmitted packet must be read from the transmission-completed queue and written to the packet number register. This makes the data of the last transmitted packet available at the transmit area in memory. After a data pointer is set to the location of the status word of the last transmitted packet, in transmit memory, a data pre-fetch must occur before reading occurs. Due to the way the LAN91C111 chip was used by  $Altera^{(\widehat{R})}$  on their development board, this pre-fetch requires a wait period of at least 370ns. This wait period is done in state seven (Data Pre-fetch), so a state transition to state seven occurs whenever a data pre-fetch is required. After the wait period has passed, a transition from the seventh state back to the previous state occurs. Once the data pre-fetch has occurred, the status word of the last transmitted packet can be read. This status word determines if the last transmission completed successfully. If it did not, and some error occurred, then the transmit interrupt is acknowledged and a transition to state five (Restore Chip Status) occurs. If the transmission succeeded, then the location of the destination IP address to store needs to be determined. The location of the IP address is different depending on if the network layer protocol of the packet in question is IP or ARP. The determination of the Ethertype and the corresponding IP address location is done in state eight (Read Ethertype). A transition to state eight occurs after it has been determined that the transmission succeeded, and a

Figure 4.6: Transmit Interrupt State Diagram

return to state four occurs after the IP address location has been determined. The data pointer is then pointed to the IP address location and another pre-fetch occurs. After this pre-fetch has finished, the destination IP can be read. This IP address is then tested to see if it is already in the CAM, in which case the previous entry simply needs to be refreshed. If the IP address is not in the CAM, then it is stored as one of the 32 CAM words, and the entry is marked as fresh. Entries are marked fresh or stale to provide the dynamic aspect of the project. A 32-bit RAM is used for this, where the 32 bits represent the 32 CAM addresses. When an entry in the CAM is written, the corresponding address in the RAM has its data value set to one. A value of one represents a fresh entry, while a zero represents a stale entry. Entries are only marked fresh by the Verilog module, and only marked stale by software running on the  $Nios^{(\mathbb{R})}$  CPU. Stale entries are periodically removed from the CAM by software. After the destination IP has been stored and marked fresh, a transition to state five occurs, where the Ethernet chip is restored to the enable future receptions or transmissions, and where the system is restored to an initial state where it is ready to handle future interrupts.

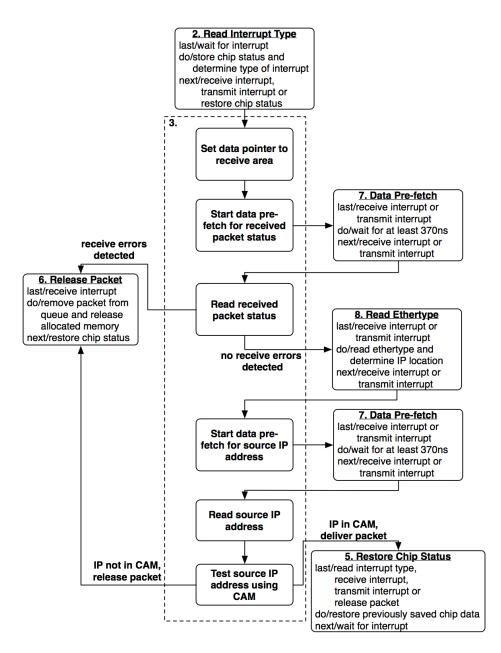

#### 4.4.3 Receive Interrupt State

In the case of a reception interrupt, the second state transitions to the third state (Receive Interrupt). A diagram of the Receive Interrupt state is shown in figure 4.7. The purpose of the third state is to obtain the source IP address from each incoming packet and to compare that address with those stored in the CAM. When matches are found between source IP and CAM entries, the packet is accepted. However, if no matching entry is found, then the packet is dropped from the reception queue. The first step in obtaining the source IP address is to check the status of the last received packet. The packet at the top of the reception queue is available at the receive area in memory. As in the case with transmitted packets, a data pointer is pointed to the location of the status word in the received packet, after which a data pre-fetch must occur. This requires a transition to state seven for a wait period, followed by a transition back to the previous state. Once the pre-fetch has finished,

Figure 4.7: Receive Interrupt State Diagram

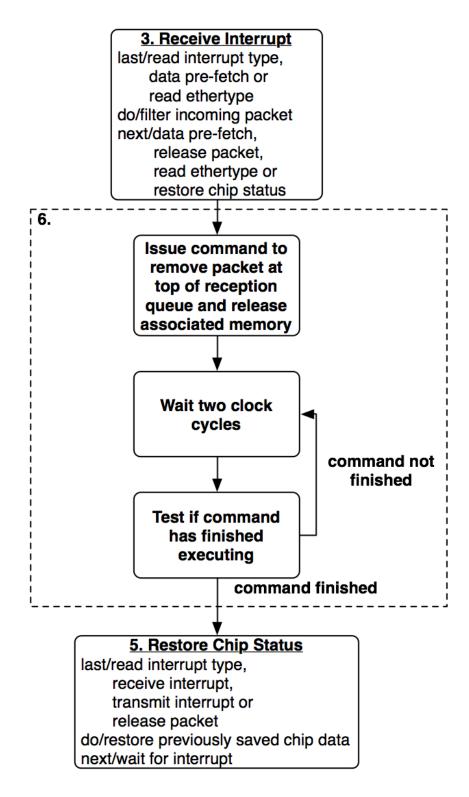

the status word is read and it is determined if any errors occurred during reception. If there were any reception errors, the packet needs to be dropped from the reception queue. This action is performed in state six (Release Packet), requiring a transition from state three to state six. If no errors occurred, then the Ethertype of the packet must be read, in order to determine the source IP address location. This occurs as in the transmit interrupt case. A transition to state eight occurs where the Ethertype is read and the source IP address location is determined. After that, the data pointer is pointed to the IP address location, and a transition to state seven occurs for a data pre-fetch, after which the IP address is read. This source IP address is provided to the CAM, where a search occurs. If the source IP address is found in the CAM, then the packet will not be filtered-out, and a transition to state five will occur, where the Ethernet chip is restored to enable future receptions and transmissions. A flag is stored, denoting whether any higher level entities waiting for incoming packets need to be notified that a successfully received packet is waiting to be read. In the case that the source IP address was not found in the CAM, the packet needs to be dropped from the reception queue. This means a transition will occur from state three to state six (Release Packet). A diagram of the Release Packet state can be seen in figure 4.8. In state six, a command that removes the packet at the top of the reception queue and releases the associated memory is given to the LAN91C111. The Ethernet chip is polled to determine when these actions have finished. Once the remove and release command has finished successfully, a transition to state five occurs, where the Ethernet chip is restored in order to receive and transmit future packets, and the system is restored to an initial state where it is ready to handle future interrupts.

#### 4.4.4 Common States

A few of the system states are common to the way both the receive and transmit interrupts are handled. As mentioned, the Data Pre-fetch state is required in order to provide a delay while information is read from the packet memory in the LAN91C111. This is due to the way the Altera<sup>®</sup> daughtercard, containing the LAN91C111 chip,

Figure 4.8: Release Packet State Diagram

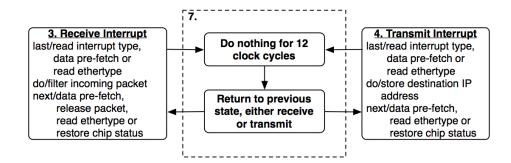

Figure 4.9: Data Pre-fetch State Diagram

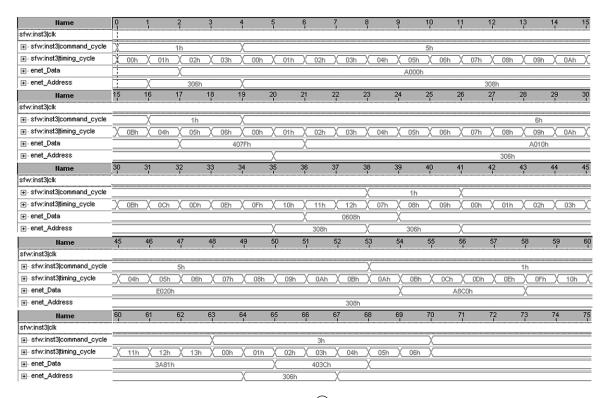

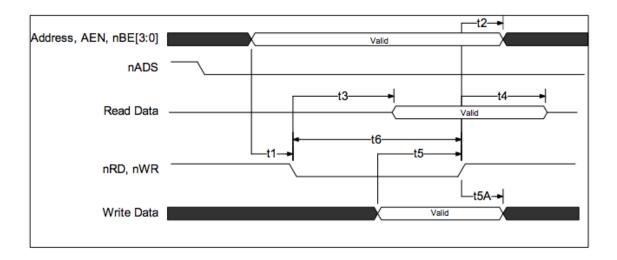

was designed. The Altera<sup>(B)</sup> development board communicates with the Ethernet daughtercard using an asynchronous bus. For asynchronous bus operation, a pin named ARDY (Asynchronous Ready) is provided on the Ethernet chip to denote when valid data has been delivered after a pre-fetch operation. However, there is no connection between the ARDY pin and the daughtercard in the Altera<sup>(B)</sup> implementation. The LAN91C111 datasheet says that a minimum wait time of 370ns should be allowed for the data register to fill, if the ARDY pin is not being used on the chip [27]. This wait period is done in state seven, where 12 clock cycles pass before returning to the previous state. However, 13 clock cycles pass in total, because an additional clock cycle is needed to transition into state seven. Since the system clock has a 30ns period, a total of 390ns pass each time a data pre-fetch occurs. This state is illustrated in figure 4.9.