# A Novel High-Speed Trellis-Coded Modulation Encoder/Decoder ASIC Design

A Thesis Submitted to the College of

Graduate Studies and Research

in Partial Fulfillment of the Requirements

for the Degree of Master of Science

in the Department of Electrical Engineering

University of Saskatchewan

Saskatoon

By

Xiao Hu

© Copyright Xiao Hu, July 2003. All rights reserved.

# **PERMISSION TO USE**

In presenting this thesis in partial fulfillment of the requirements for a Degree of Master of Science from the University of Saskatchewan, the author agrees that the libraries of this University may make it freely available for inspection. The author further agrees that permission for copying of this thesis in any manner, in whole or in part for scholarly purposes may be granted by the professor who supervised this thesis work or, in his absence, by the Head of the Department or the Dean of the College of Graduate Studies and Research at the University of Saskatchewan. Any copying, publication, or use of this thesis, or parts thereof, for financial gain without the author's written permission is strictly prohibited. Proper recognition shall be given to the author and the University of Saskatchewan in any scholarly use which may be made of any material in this thesis.

Requests for permission to copy or to make any other use of material in this thesis in whole or part should be addressed to:

Head of the Department of Electrical Engineering, 57 Campus Drive, University of Saskatchewan, Saskatoon, Saskatchewan, Canada S7N 5A9

# ABSTRACT

Trellis-coded Modulation (TCM) is used in bandlimited communication systems. TCM efficiency improves coding gain by combining modulation and forward error correction coding in one process. In TCM, the bandwidth expansion is not required because it uses the same symbol rate and power spectrum; the differences are the introduction of a redundancy bit and the use of a constellation with double points.

In this thesis, a novel TCM encoder/decoder ASIC chip implementation is presented. This ASIC codec not only increases decoding speed but also reduces hardware complexity. The algorithm and technique are presented for a 16-state convolutional code which is used in standard 256-QAM wireless systems. In the decoder, a Hamming distance is used as a cost function to determine output in the maximum likelihood Viterbi decoder. Using the relationship between the delay states and the path state in the Trellis tree of the code, a pre-calculated Hamming distances are stored in a look-up table. In addition, an output look-up-table is generated to determine the decoder output. This table is established by the two relative delay states in the code. The thesis provides details of the algorithm and the structure of TCM codec chip. Besides using parallel processing, the ASIC implementation also uses pipelining to further increase decoding speed. The codec was implemented in ASIC using standard 0.18µm CMOS technology; the ASIC core occupied a silicon area of 1.1mm<sup>2</sup>. All register transfer level code of the codec was simulated and synthesized. The chip layout was generated and the final chip was fabricated by Taiwan Semiconductor Manufacturing Company through the Canadian Microelectronics Corporation. The functional testing of the fabricated codec was performed partially successful; the timing testing has not been fully accomplished because the chip was not always stable.

# ACKNOWLEDGEMENTS

I am deeply grateful to my supervisor, Dr. Anh Dinh, for his guidance, support, and patience during my graduate program. He has been an invaluable source of knowledge and has certainly helped inspire many of the ideas expressed in this thesis. The other special thanks go to the Canadian Microelectronics Corporation for their software and hardware support. This thesis could not have been accomplished without their support.

Also, I would like to thank the Department of Electrical Engineering and College of Graduate Studies and Research, University of Saskatchewan, for providing a graduate scholarship during this research.

Special appreciation goes to my husband, Tie Peng, for his understanding, endless support and help; and my son, Yuwei Peng, for his smile, listening, smart talk and being a good boy.

# **INDEX OF CONTENTS**

| Permission to use                                     | i    |

|-------------------------------------------------------|------|

| Abstract                                              | ii   |

| Acknowledgements                                      | iv   |

| Index of Contents                                     | v    |

| List of Tables                                        | viii |

| List of Figures                                       | ix   |

| List of Abbreviations                                 | xi   |

| Chapter 1 INTRODUCTION                                | 1    |

| 1.1 Classic Coding                                    | 1    |

| 1.2 Trellis-Coded Modulation                          | 3    |

| 1.3 FPGA Design                                       |      |

| 1.4 ASIC Design                                       | 7    |

| 1.5 Research Objectives, Contribution and Methodology | 8    |

| 1.6 Outline of the Thesis                             |      |

| Chapter 2 TRELLIS-CODED MODULATION BACKGROUND .       | 11   |

| 2.1 Error-Correcting Coding                           | 11   |

| 2.2 Trellis-Coded Modulation                          | 15   |

| 2.2.1 Fundamentals and Concept of TCM                 |      |

| 2.2.2 TCM Encoder                                     | 21   |

| 2.2.3 Set Partitioning                                |      |

|        | 2.2.4   | Mapping and Trellis Diagram                     | 25 |

|--------|---------|-------------------------------------------------|----|

|        | 2.2.5   | TCM Decoder                                     | 29 |

|        | 2.2.6   | Viterbi Algorithm                               | 30 |

| 2.3    | Multi   | - Dimensional Trellis-Coded Modulation          | 33 |

|        | 2.3.1   | Introduction to Multi-Dimensional TCM           | 34 |

|        | 2.3.2   | Four-Dimensional TCM Encoder                    | 35 |

|        | 2.3.3   | TCM 4D 256-QAM Constellation Mapping            | 36 |

| Chapte | er 3 TC | CM CODEC IMPLEMENTATION ALGORITHM               | 39 |

| 3.1    | Encod   | ler Implementation                              | 39 |

|        | 3.1.1   | A 2-Dimensional Encoder Implementation          | 39 |

|        | 3.1.2   | A 4-Dimensional Encoder Implementation          | 42 |

| 3.2    | Decod   | ler Implementation                              | 46 |

|        | 3.2.1   | Structure of the HDLUT and OLUT                 | 47 |

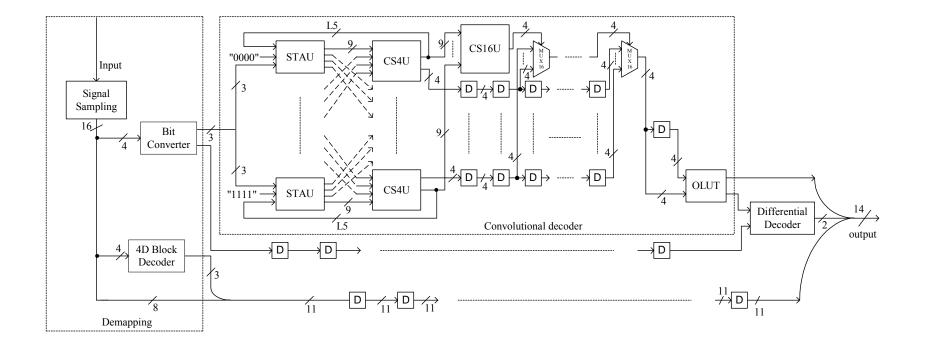

|        | 3.2.2   | A Novel TCM Decoder Architecture Implementation | 52 |

|        | 3.      | 2.2.1 A Decoder for 2-Dimensional TCM Scheme    | 53 |

|        | 3.      | 2.2.2 A Decoder for 4-Dimensional TCM Scheme    | 57 |

| Chapte | er 4 TC | CM CODEC ASIC IMPLEMENTATION                    | 62 |

| 4.1    | ASIC    | Design Introduction                             | 62 |

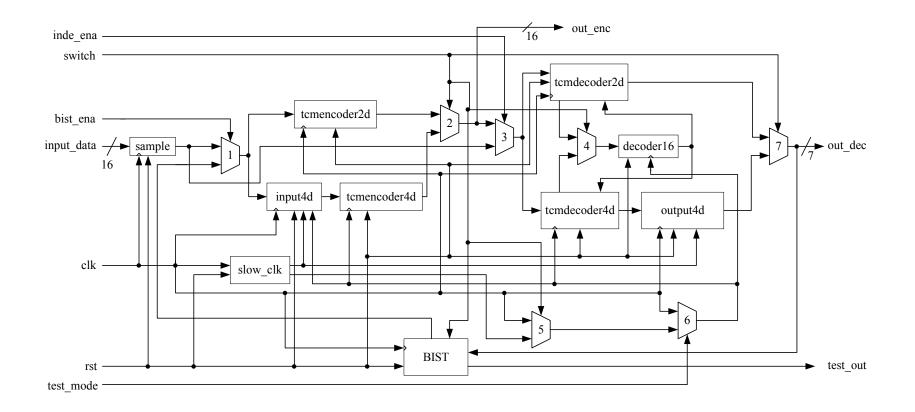

| 4.2    | Тор М   | Nodule Architecture of the TCM Codec ASIC Chip  | 67 |

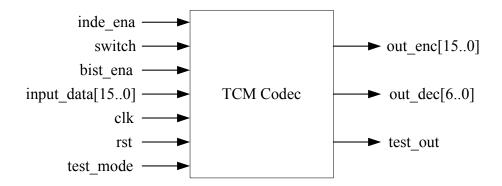

|        | 4.2.1   | I/O Signal Description                          | 69 |

|        | 4.2.2   | Individual Block Description                    | 71 |

|        | 4.      | 2.2.1 The Multiplexers                          | 72 |

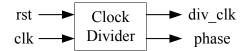

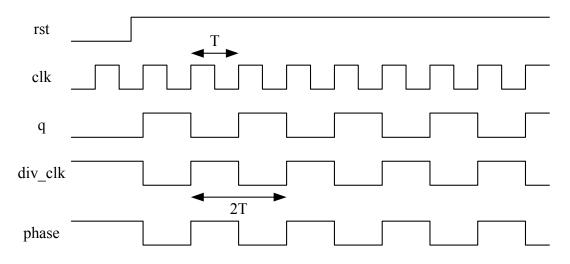

|        | 4.      | 2.2.2 The Clock Divider                         | 73 |

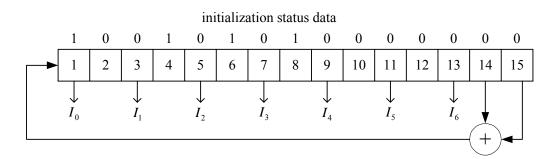

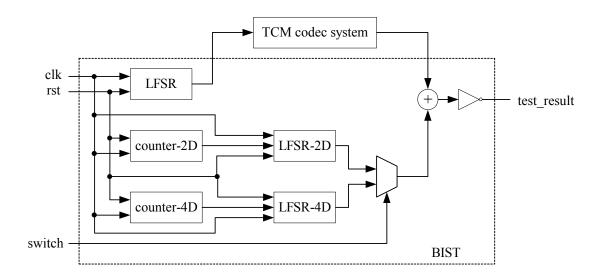

| 4.2.2.3 The Built-In Self Test                |

|-----------------------------------------------|

| 4.3 Register Transfer Level Code in VHDL      |

| 4.4 Pipelining                                |

| 4.5 System Synthesis 79                       |

| Chapter 5 RESULTS 81                          |

| 5.1 MATLAB System Simulation Results 81       |

| 5.2 FPGA Prototype Implementation Results     |

| 5.3 ASIC Implementation Results 85            |

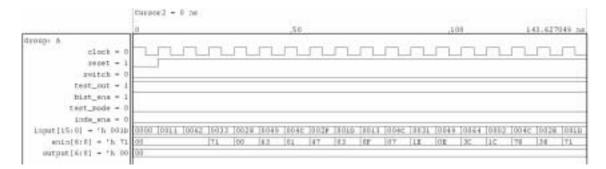

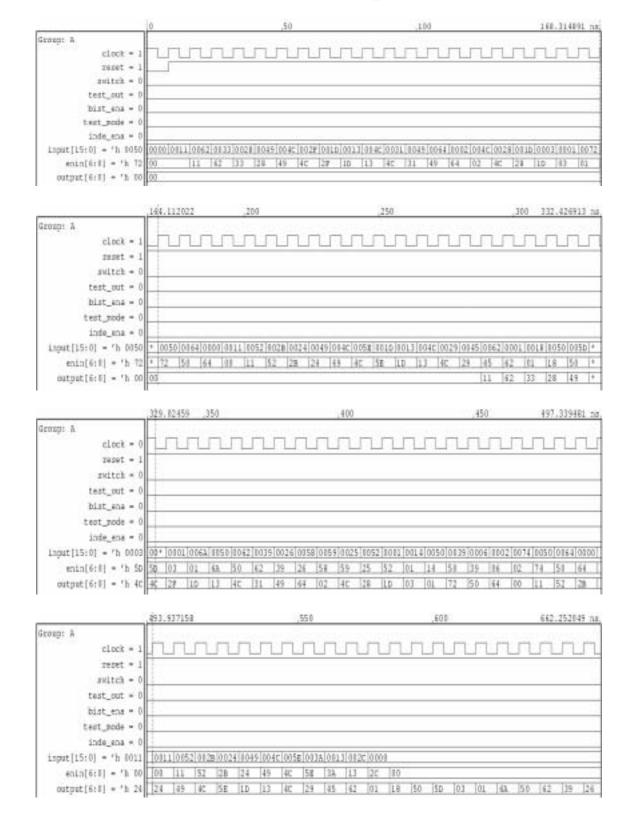

| 5.3.1 Register Transfer Level Code Simulation |

| 5.3.2 Register Transfer Level Code Synthesis  |

| 5.3.3 Layout Generation                       |

| 5.4 The Fabricated TCM Codec                  |

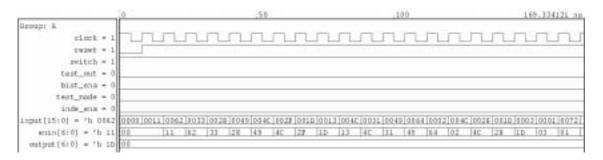

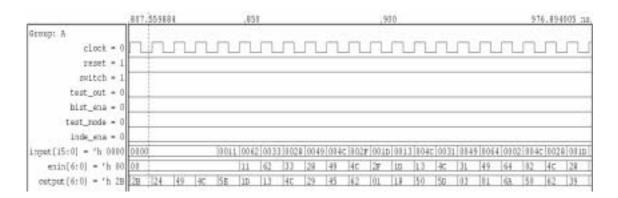

| 5.5 Testing Results                           |

| Chapter 6 CONCLUSION AND FUTURE WORKS 102     |

| 6.1 Research Summary 102                      |

| 6.2 Conclusions 104                           |

| 6.3 Future work 105                           |

| <b>REFERENCES</b>                             |

# LIST OF TABLES

| Table 3.1 4D subsets allocation                                            | 44 |

|----------------------------------------------------------------------------|----|

| <b>Table 3.2</b> Correspondence between $Z_{0k}Z_{1k}$ and four 2D subsets | 45 |

| Table 3.3 4D block encoder                                                 | 46 |

| Table 3.4 A Hamming Distance table                                         | 49 |

| Table 3.5 HDLUT using in the TCM decoder                                   | 50 |

| Table 3.6 An OLUT using in the TCM decoder                                 | 51 |

| Table 3.7 The simplified OLUT using in TCM decoder                         | 52 |

| Table 5.1 FPGA implementation results                                      | 85 |

| Table 5.2 RTL code simulation results                                      | 92 |

| Table 5.3 Physical results of the chip from RTL synthesis                  | 93 |

| Table 5.4 The synthesis results of FPGA and ASIC TCM decoder               | 94 |

# LIST OF FIGURES

| Figure 2.1 Block diagram of a digital-coded system                         | 12     |

|----------------------------------------------------------------------------|--------|

| Figure 2.2 An illustration of a (6, 3) block code                          | 14     |

| Figure 2.3 An illustration of a convolutional code                         | 14     |

| Figure 2.4 The constellation and two-state trellis used in the example TCM | scheme |

|                                                                            | 20     |

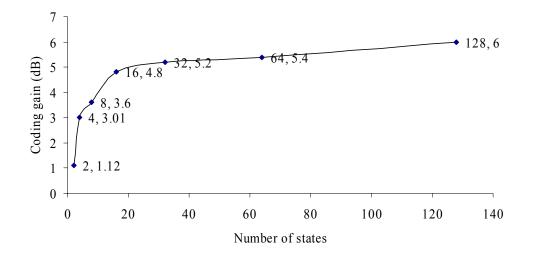

| Figure 2.5 Result of coding gain versus the number of states               | 21     |

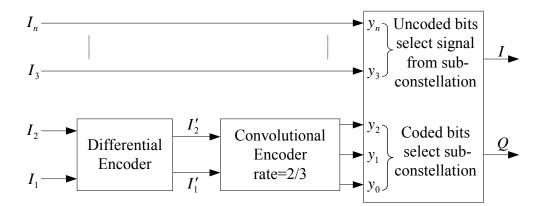

| Figure 2.6 General scheme of a 2D TCM encoder                              | 22     |

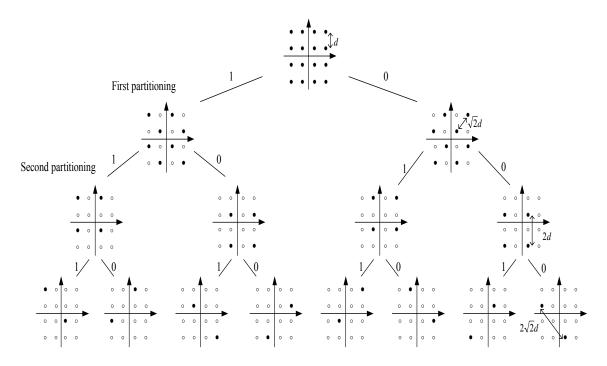

| Figure 2.7 Set partition of a 16-QAM constellation                         | 25     |

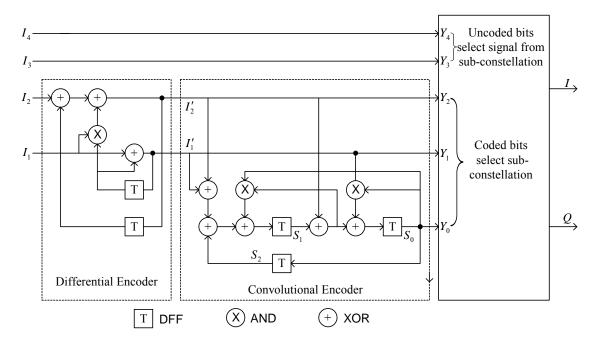

| Figure 2.8 Structure of the TCM encoder used in V.32 modem                 | 26     |

| Figure 2.9 A 32-signal constellation for the V.32 Modem TCM scheme         | 28     |

| Figure 2.10 Trellis diagram of the V.32 modem TCM encoder                  | 29     |

| Figure 2.11 Viterbi algorithm illustration based on two-state trellis      | 33     |

| Figure 2.12 General scheme of a 4D TCM Encoder                             | 35     |

| Figure 2.13 Partitioning of a 4D rectangular lattice                       | 37     |

| Figure 3.1 A 16-state 2-dimensional TCM encoder                            | 40     |

| Figure 3.2 Convolutional coding in TCM encoder                             | 41     |

| Figure 3.3 A 256-signal constellation for the 2D 16-state TCM scheme       | 42     |

| Figure 3.4 A 16-state 4-dimensional TCM encoder                            | 43     |

| Figure 3.5 Trellis diagram of the 16-states TCM encoder                    | 48     |

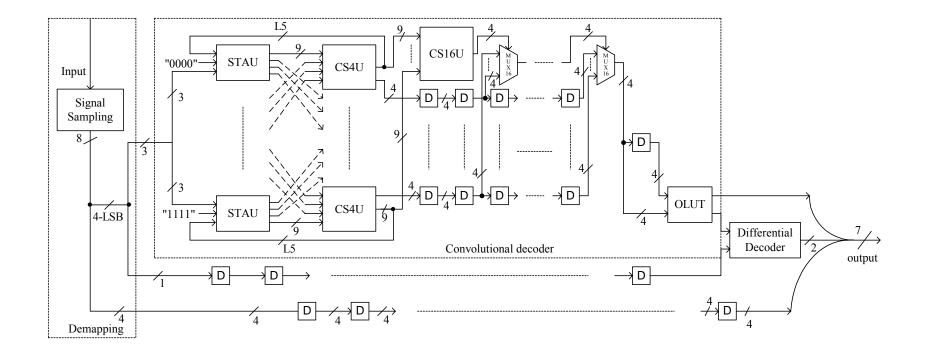

| Figure 3.6 A 2-dimensional 16-state TCM decoder                            | 54     |

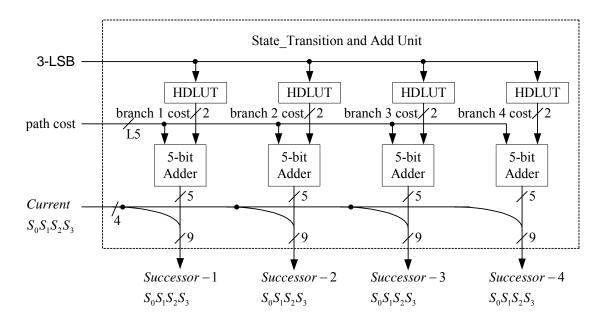

| Figure 3.7 Architecture of the STAU block                           | . 56 |

|---------------------------------------------------------------------|------|

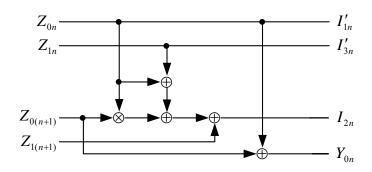

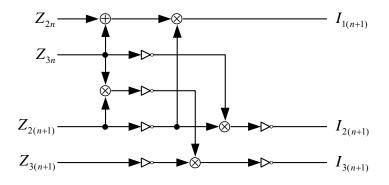

| Figure 3.8 Schematic diagram of the bit converter                   | . 59 |

| Figure 3.9 Schematic diagram of the 4D-block decoder                | . 59 |

| Figure 3.10 A 16-state 4-dimensional TCM decoder                    | . 60 |

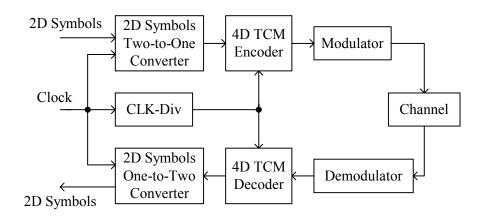

| Figure 3.11 The 4-dimensional TCM coding system                     | . 61 |

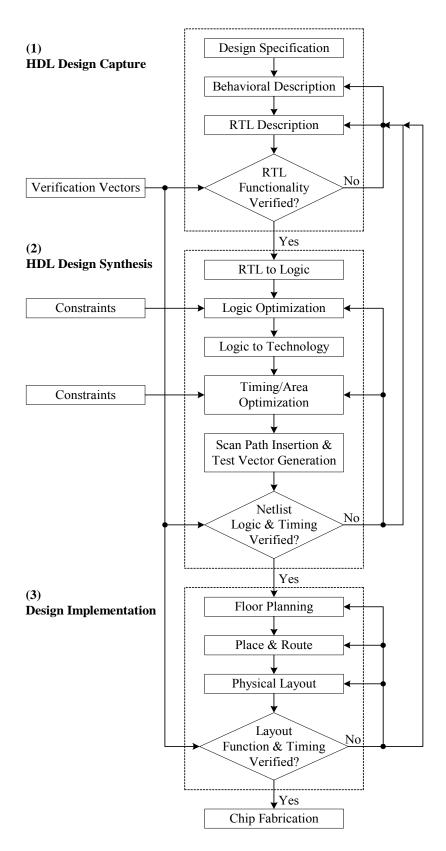

| Figure 4.1 A flow chart of the ASIC design process                  | . 63 |

| Figure 4.2 Overall ASIC chip architecture of the TCM codec          | . 68 |

| Figure 4.3 I/O signal illustration of the TCM codec                 | . 69 |

| Figure 4.4 Clock divider signals illustration                       | . 73 |

| Figure 4.5 The waveform of clock divider                            | . 74 |

| Figure 4.6 The structure of LFSR                                    | . 75 |

| Figure 4.7 The architecture of the BIST block on the TCM codec chip | . 76 |

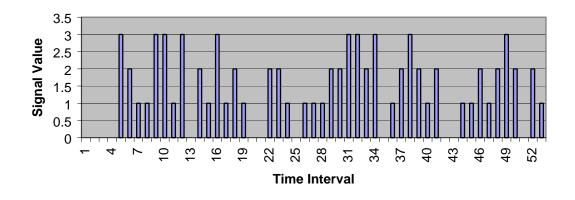

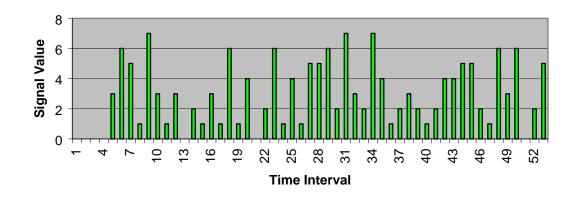

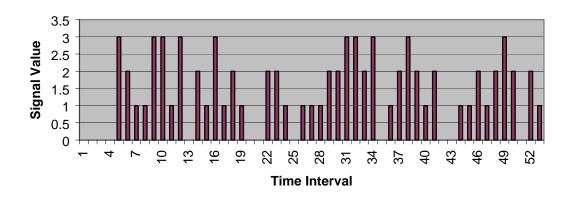

| Figure 5.1 Input sequence of the convolutional encoder              | . 83 |

| Figure 5.2 Codeword sequence of the convolutional coding            | . 83 |

| Figure 5.3 Output sequence of the convolutional decoder             | . 83 |

| Figure 5.4 Final layout of the TCM codec ASIC                       | . 97 |

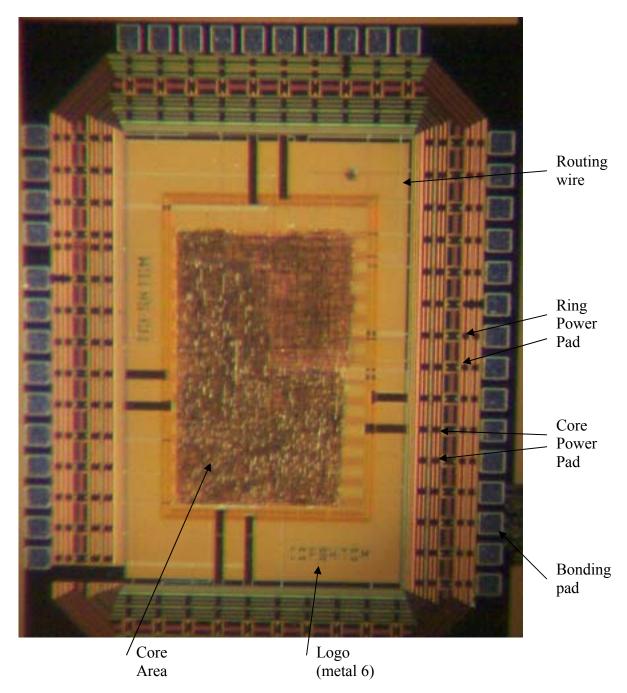

| Figure 5.5 Photograph of the TCM codec chip with bonding pads       | . 98 |

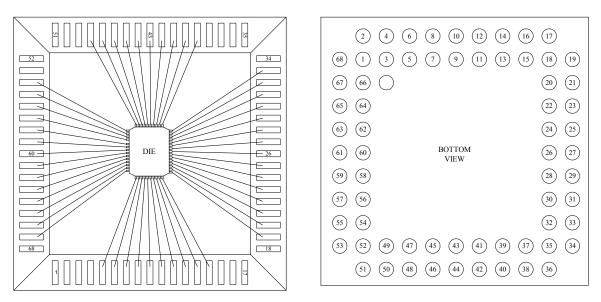

| Figure 5.6 68CPGA pin bonding and pin out diagram                   | . 99 |

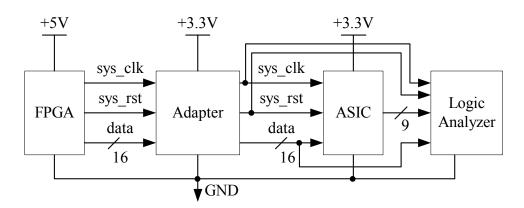

| Figure 5.7 Functional testing set-ups                               | 100  |

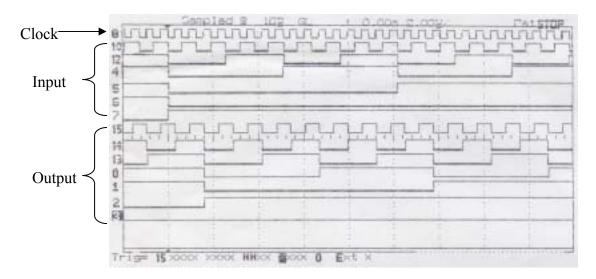

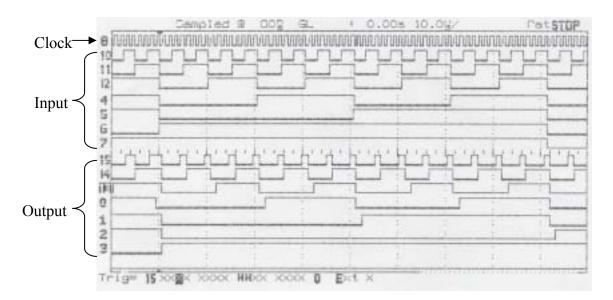

| Figure 5.8 Functional testing for 2D scheme                         | 101  |

| Figure 5.9 Functional testing for 4D scheme                         | 101  |

# LIST OF ABBREVIATIONS

| 2D    | Two-dimensional                            |

|-------|--------------------------------------------|

| 4D    | Four-dimensional                           |

| ARC   | Antenna Rule Check                         |

| ASIC  | Application-Specific Integrated Circuit    |

| AWGN  | Additive White Gaussian Noise              |

| BER   | Bit-Error-Rate                             |

| BIST  | Built-In-Self-Test                         |

| CATV  | Cable Television                           |

| СМС   | Canadian Microelectronics Corporation      |

| CMOS  | Complementary Metal Oxide Silicon          |

| CSU   | Compare-Selection Unit                     |

| DAVIC | Digital Audio Visual Council               |

| dB    | Decibel                                    |

| DBS   | Direct Broadcast Satellite                 |

| DFF   | D-Flip-Flop                                |

| DFII  | Design Framework II (Cadence design tools) |

| DFT   | Design-For-Test                            |

| DRC   | Design Rules Check                         |

| DSP   | Digital Signal Processing                  |

| ECC   | Error-Correcting Coding                    |

| FEC    | Forward Error Correction                       |

|--------|------------------------------------------------|

| FPGA   | Field Programmable Gate Array                  |

| Gbps   | Giga-bit per second                            |

| GDSII  | Graphical Design Stream II                     |

| GHz    | Gigahertz                                      |

| HDL    | Hardware Description Language                  |

| HDLUT  | Hamming Distance Look-Up Table                 |

| HDTV   | High Definition Television                     |

| IC     | Integrated Circuit                             |

| I/O    | Input/Output                                   |

| IP     | Intellectual Property                          |

| LFSR   | Linear Feedback Shift Register                 |

| LSB    | Least Significant Bit                          |

| LUT    | Look-Up Table                                  |

| LVS    | Layout-Versus-Schematic                        |

| MATLAB | Matrix Laboratory (simulation tools)           |

| Mbps   | Mega-bit per second                            |

| MHz    | Megahertz                                      |

| MMDS   | Multi-channel Multipoint Distribution Services |

| MSB    | Most Significant Bit                           |

| MSED   | Minimum Squared Euclidean Distance             |

| MUX    | Multiplexer                                    |

| NC-Sim |                                                |

| OLUT  | Output Look-Up Table                       |

|-------|--------------------------------------------|

| PDP   | Physical Design Planner                    |

| PROM  | Programmable Read Only Memory              |

| PRPG  | Pseudo Random Pattern Generator            |

| PSK   | Phase Shift Keying                         |

| QAM   | Quadrature Amplitude Modulation            |

| QPSK  | Quaternary Phase Shift Keying              |

| RTL   | Register Transfer Level                    |

| SE    | Silicon Ensemble (Cadence layout tools)    |

| SNR   | Signal-to-Noise Ratio                      |

| SOC   | System-On-Chip                             |

| STAU  | State-Transition and Add Unit              |

| TSMC  | Taiwan Semiconductor Manufacturing Company |

| ТСМ   | Trellis-Coded Modulation                   |

| TTL   | Transistor-Transistor Logic                |

| VHDL  | VHSIC Hardware Description Language        |

| VHSIC | Very High Speed Integrated Circuits        |

| VLSI  | Very Large Scale Integration               |

### **CHAPTER 1**

### **INTRODUCTION**

This chapter introduces the history of coding theory and why Trellis-Coded Modulation is chosen to be the research topic and implemented into an Application Specific Integrated Circuit (ASIC). This chapter also presents the main research methodology, research achievement and the thesis outline.

#### 1.1 Classic Coding

In 1948, Claude E. Shannon established the mathematical foundation for information transmission. Shannon demonstrated that the effect of transmitted power, bandwidth, and additive noise can be associated with a channel and incorporated into the channel capacity. In the case of additive white Gaussian noise interference with power spectral density  $N_0$ , an ideal band-limited channel of bandwidth W has a capacity C bits/s given by

$$C = W \log_2\left(1 + \frac{P}{WN_0}\right) \tag{1.1}$$

where P is the average transmitted power.

The significant meaning of the channel capacity is that if the information rate R from the source is less than C, (R<C), then it is theoretically possible to achieve reliable

(i.e., error-free) transmission through the channel by appropriate coding. On the other hand, if R>C, reliable transmission is not possible regardless of the amount of signal processing performed at the transmitter and receiver.

The information theory shows that for optimal communications, system design should have long sequences of signals, with maximum separation among them at the transmitter. At the receiver, the performing decision should be made over such long signal sequence rather than individual bit. If the process is performed properly then the message error probability,  $P_e$ , will decrease exponentially with sequence length n. The condition is that the rate R is less than R<sub>0</sub>, which in turn is less than the channel capacity as stated in the information theory. The message error probability can be expressed as:

$$P_{e} < 2^{-(R_{0}-R)n} \tag{1.2}$$

where  $R_0$  is a quantity that carries dimensions of bits per channel symbol [1]. In order to increase the sequence length n, error-correcting coding (ECC) is introduced. Error-correcting coding method introduces redundant bits into each symbol, which directly increase the codeword length n and decrease error probability.

In conventional ECC coding, the coding process is independent from the modulation process. Coding occurs at the digital symbol 0's and 1's before modulation and generally involves adding redundant bits into an input sequence. The resultant redundancy requires extra transmission bandwidth. At the receiver, the inversion process of coding is the decoding, which occurs after the signal demodulation. Since a digital bit (or symbol) stream that comes into the decoder is either in error or not, corresponding with detection method, decoding divides into hard decoding and soft decoding. The hard decoding operation is based on hard decisions of the digital signal,

which is 0 or 1. The soft decoding is based on soft decision of the analog received samples, which could be any quantized value between the lowest and the highest voltage instead of only 0 and 1. The theoretical loss due to hard versus soft decoding leads to a reduction of 2dB in performance.

Trellis-coded modulation is different from conventional coding; it treats coding and modulation together. The coding process involves handling the mapping a codeword into a modulation scheme.

#### 1.2 Trellis-Coded Modulation

In a power-limited environment, the desired system performance should be achieved with the smallest possible transmitted power. The use of error-correcting codes can increase power efficiency by adding extra bits to the transmitted symbol sequence. This procedure requires the modulator to operate at a higher data rate, which requires a wider bandwidth. In a bandwidth-limited environment, the use of higherorder modulation schemes can increase efficiency in frequency utilization. In this case, a large signal power would be required to maintain the same system bit-error-rate (BER). In order to achieve improved reliability of a digital transmission system without increasing transmitted power or required bandwidth, both coding and modulation are considered in TCM technology; therefore, TCM is a scheme combining error-correcting coding with modulation.

TCM is used for data communication with the purpose of gaining noise immunity over uncoded transmission without changing the data rate. The use of TCM also improves system reliability without increasing transmitting power and required

3

channel bandwidth. Quadrature Amplitude modulation (QAM) and Quaternary Phase Shift Keying (QPSK) are used in TCM to increase data transmission rate. Since channel bandwidth is a function of the signal-to-noise ratio (SNR), larger signal power would be necessary to maintain the same signal separation and the same error probability if more signals are required to be transmitted without enlarging channel bandwidth. It seems that the Trellis code statement violates the basic power, bandwidth and error probability trade-off principle. Actually this is not true; the reason for this will be explained below and as well as in the next chapter.

Trellis coding introduces dependency between every successive transmitting data symbol. The optimum 2-dimensional modulation utilizes the dependency between in-phase and quadrature symbols and the 4-dimensional modulation employs the dependency between symbols of two successive time intervals. Trellis codes and multi-dimensional modulation are designed to maximize the Euclidean distance between possible sequences of transmitted symbols. Euclidean distance is a straight-line distance between two points in signal constellation. In N dimensions, the Euclidean distance between two points p and q is:

$$\sqrt{\sum_{i=1}^{N} (p_i - q_i)^2}$$

(1.3)

where  $p_i$  and  $q_i$  are the coordinate of p and q in the dimension i. The minimum Euclidean distance (i.e., the distance between the closest possible sequences) of transmitted symbols in signal space determines the system performance as:

$$P_e \sim e^{-d_{\min}^2/2\sigma^2} \tag{1.4}$$

where  $P_e$  is message error probability,  $d_{\min}$  is the minimum Euclidean distance between

signal sequences and  $\sigma$  is the noise power. Equation (1.4) indicates that if  $d_{\min}$  increases,  $P_e$  will decrease. This is one of the reasons why TCM technique does not violate the basic trade-off principle between power, bandwidth, and error probability.

Since Ungerboeck invented TCM in 1976 and had his papers published in the 1980's [2-4], numerous researches have been working on TCM applications in voice band modems, satellite communications, numerous areas: wireless communications trials. digital subscriber loop, HDTV (high definition television), broadcast channels, CATV (community antenna television) and DBS (direct broadcast satellite) in the 1980's and 1990's. Many innovations in TCM technology have been introduced, such as multidimensional TCM (1984-1985), rotationally invariant TCM with M-PSK (1988), TCM with built-in time diversity (1988-1990), TCM with Tomlinson Precoder (1990-1991), TCM with unequal error protection (1990), multilevel coding with TCM (1992-1993), and concatenated coding with TCM (1993-present).

Even a number of researches focused on the Viterbi Algorithm to decode convolutional code ([5-10]) and on trellis coding with multi-dimensional modulation ([11-15]), but only a few was developed in the implementation a TCM encoder/decoder on a single chip. This research focuses on the ASIC implementation of TCM encoder/decoder with 2-dimensional and 4-dimensional modulation mapping, and provides an intellectual property (IP) core to incorporate TCM in system-on-chip (SOC). The designed chip was fabricated by Taiwan Semiconductor Manufacturing Company (TSMC) through a grant from Canadian Microelectronics Corporation (CMC). In order to show the advantages of using CMOSP18 technology to implement the ASIC TCM encoder/decoder chip, the ASIC hardware implementation results are compared with the Field Programmable Gate Array (FPGA) implementation from different aspects such as logic gates, chip area and speed. The followings introduce some background of the FPGA and ASIC.

#### 1.3 FPGA Design

An FPGA is a programmable device. Programmable devices are a class of general purpose integrated circuits that can be configured in the field for a wide variety of applications. FPGAs were invented in the mid-1980s as devices that resemble ASICs but could be programmed after the chip was manufactured. A FPGA consists of a matrix of programmable logic cells with a grid of interconnecting lines and switches between them. I/O cells exist around the perimeter providing an interface between the interconnect lines and the chip external pins. Programming an FPGA consists of specifying the logic function of each cell and the switches in the interconnecting lines.

FPGA devices allow rapid design prototyping. They provide some benefits of custom CMOS VLSI design, while avoiding the initial cost, fabrication time delay, and inherent risk of a conventional masked gate array. The devices are customized by loading configuration data into the internal logic gates and memory cells. The FPGA can either actively read its configuration data from external serial or byte-parallel PROM (i.e., master mode), or the configuration data can be written into the FPGA (i.e., slave and peripheral mode). They offer more dense logic and less tedious wiring work than discrete component designs and faster turnaround than sea-of-gates, standard cells, or full-custom design.

FPGA designs can be programmed using one of the various hardware description languages (HDL), such as Very high speed integrated circuit HDL (VHDL) and Verilog HDL, or directly programmed with logic circuit diagrams and graphical schematic component layout.

#### 1.4 ASIC Design

ASIC design is a process of integrating a specific complicated application into a chip. A typical ASIC design process is generalized into three steps: HDL design capture, HDL design synthesis and design implementation. HDL design capture is completed with "pre-synthesis" simulations to verify that the register transfer level (RTL) abstraction fully provides the desired functionality. HDL design synthesis is completed with "post-synthesis" simulations to verify that the gate-level circuit provides the desired functionality and meets appropriate timing requirements. Design implementation is completed with the physical verification to implement the chip layout under the Design Rules Check (DRC) error free and ready for microelectronic circuit fabrication.

ASIC generally runs faster than FPGA because of its specific place and route during the layout process. ASIC costs less than FPGA and DSP implementations under mass production; therefore it is widely used in industries. ASICs are not economical compared to FPGAs if they are used only for research purposes because ASIC implementations require extra time to develop and the chip can not be re-configured if the design requires further modifications; a new development process has to be started.

An ASIC design can be implemented in different ways depending on the

hardware description languages (Verilog or VHDL), synthesis and/or layout tools to be used in the implementation process. Details on ASIC design implementation will be discussed in Chapter 4.

#### 1.5 Research Objectives, Contribution and Methodology

The objective of this research is to design a high speed TCM encoder/decoder and to implement the codec into an ASIC. The results of ASIC implementation are then compared with FPGA implementation in terms of the operating frequency (i.e., system throughput or bit rate) and hardware requirement (i.e., chip cost).

This thesis work focuses on the constructing of a 16-state TCM codec scheme based on DAVIC specification [16], and then implementing it on a single ASIC. The research is accomplished by creating a novel architecture of the TCM decoder and implementing a 16-state TCM codec chip into an ASIC including mapping the signal to both 2-dimensional and 4-dimensional constellations. In the TCM decoder part, the main difference from the traditional technique is the use of look-up tables (LUTs). These tables are used to simplify the cost function calculation in the Viterbi algorithm. The use of these LUTs not only reduces hardware complexity but also increases the decoding speed. Another difference from the traditional decoding technique is the efficient use of the shift registers to perform the tracing back process in the Viterbi algorithm. This technique avoids using a large amount of memory required to store error metrics for all of the paths.

The ASIC consists of two parts: a TCM encoder and a TCM decoder. The TCM encoder starts from sampling digital source data, and ends at the mapping signal

generation. The TCM decoder begins with the sampling of the codeword, and finishes with the restoring of the original digital source data. The VLSI implementation of the TCM decoder includes three parts: the de-mapping process, the convolutional decoding and the differential decoding. The main and complicated part is the convolutional decoding process in which the Viterbi algorithm is used. High-speed operation and low complexity of the codec are achieved by creating of the two LUTs, simplifying the Viterbi algorithm for VLSI implementation, and adopting the parallel algorithm and the pipelining technology.

RTL codes were written in VHDL. Simulation was run on the Cadence NC-Sim simulator to verify the functionality of the ASIC. The RTL codes are then synthesized into a gate-level netlist using Synopsys synthesis tools. The gate-level netlist was turned into layout for fabrication using various Cadence tools: Physical Design Planner (PDP or DP), Silicon Ensemble (SE), and Design Framework II (DFII). The final layout was streamed out to GDSII format file to be ready for fabrication. The ASIC was fabricated by TSMC and tested.

#### **1.6** Outline of the Thesis

The rest of this thesis provides detail descriptions on the background, concept and implementation of the TCM codec. Chapter 2 introduces the background and key point of the TCM and illustrates the related algorithm and technology. Chapter 3 provides details of the TCM codec structures, illustrates methodology and implementation process including the mapping for 2D and 4D constellations; creates the architecture for hardware implementation. Chapter 4 provides further description on the hardware implementation, details of this ASIC design process and the structure of this TCM codec chip. Chapter 5 provides the results of the design TCM codec in three parts: (1) the MATLAB simulation on the TCM encoder/decoder algorithm, (2) the VHDL RTL codes compilation and simulation results on FPGA APEX<sup>®</sup> device, and (3) the ASIC implementation results including the chip layout. Chapter 6 provides conclusion and recommendation for future work.

### **CHAPTER 2**

# **TRELLIS-CODED MODULATION BACKGROUND**

This chapter introduces general error-correcting coding, fundamental and concepts of TCM, general encoder structure, mapping method, algorithm used in the TCM decoding, and the multi-dimensional TCM codec.

#### 2.1 Error-Correcting Coding

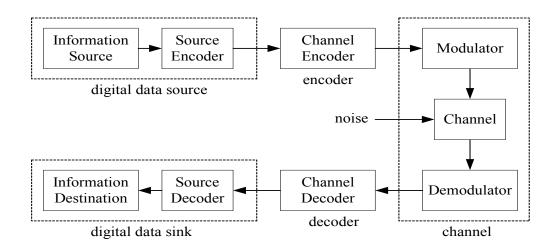

Figure 2.1 shows a typical communication system incorporating with channel coding. In this system, digital data generated by a source encoder are coded through a channel encoder, and the coded information data is used to modulate a carrier for transmission over a communication channel. The channel always introduces attenuation, distortion, interference and noise, which affect the receiver's ability to receive correct information. The demodulator recovers possible values of the transmitted symbols, and the channel decoder recovers the information data before sending to its destination.

Figure 2.1 Block diagram of a digital-coded system

A widely used channel encoding method is error-correcting coding (ECC). In an ECC system, a digital information source sends a data sequence to an encoder; the encoder inserts redundant (or parity) bits, thereby outputting a longer sequence of the code bits. The sequence of the code bits is called a codeword. The codeword is then transmitted to a receiver, which has a suitable decoder to recover the original data sequence.

Error-correcting coding is related to the method of delivering information from a source to a destination with minimum error. The research on ECC began in 1948 with the publication of a landmark paper by Claude E. Shannon [17]. Shannon's work showed that any communication channel could be characterized by a capacity at which information could be reliably transmitted. At any rate of information transmission up to the channel capacity, it should be possible to transfer information at any desired level of error rates. Introducing redundancy into transmissions can provide error control. This means more symbols are included in the message than strictly needed just to convey the information, with the result that only certain patterns at the receiver correspond to valid transmissions. Once an adequate degree of error control has been introduced, the error

rates can be made as low as required by extending the length of the code, thus averaging the effects of noise over a longer period of time [18-19].

The research for error-correcting codes was primarily motivated by the problems arising in communications systems, in particular, systems having limitation in their transmitted powers. Error-correcting codes are an excellent means of reducing transmission power requirements because reliable communications can be achieved with the aid of codes even when the information is weakly received at its destination.

There are two different types of codes used in error-correcting coding: the block codes and the convolutional codes. The primary point of both codes is to add redundant bits to achieve error correction objectives. These redundant bits are added into each symbol of information sequence formulating the codeword. They will be used in the decoder at the receiver to correctly restore the original information sequence under specific decoding algorithms. These redundant bits are also called parity-check bits; the bits provide the code with the capability of combating channel noise.

The encoder for the block codes divides information sequences into information blocks of k-bit, represented by  $d = (d_0, d_1, ..., d_{k-1})$  information sequence. The encoder transforms each k-bit information block *d* independently into a codeword,  $c = (c_0, c_1, ..., c_{n-1})$ . This transformation provides a coding rate R= k/n (R < 1). The code is called a (n, k) block code. Decoding algorithm of the block code is based on the method of constructing the codeword in the encoder.

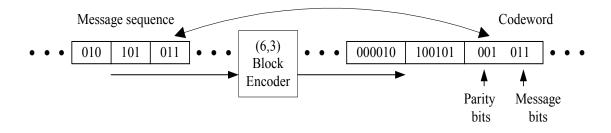

Figure 2.2 shows how a codeword is generated through a (6,3) block encoder. Each 6-bit output codeword is comprised of the original 3-bits message sequence and a 3-bits parity sequence.

Figure 2.2 An illustration of a (6,3) block code

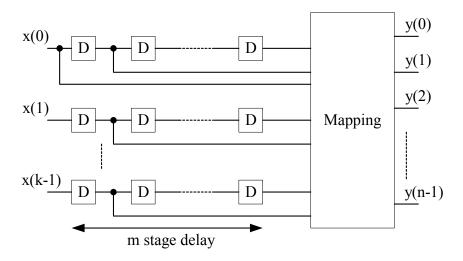

The encoder for convolutional codes generates codeword for transmission utilizing a sequential finite-state machine driven by the information sequence, or an arbitrarily long sequence. The convolutional encoding process installs the properties of memory and redundancy into the codeword stream, as for block codes. Figure 2.3 shows a generic description of a convolutional encoder.

Figure 2.3 An illustration of a convolutional code

The k-bit information sequence as the input of the encoder is coded to the n-bit codeword through the m stage delay (represented by delay cell D). The coding rate is still R = k/n (R < 1). The code is called (n, k, m) convolutional code. Each of k parallel input lines can have different number of stage delay cells, which is smaller than or equal to m ( $m \ge 0$ ).

The most common method used in decoding the convolutional codes is the probabilistic method. The probabilistic decoding method includes sequential decoding (Fano algorithm or stack algorithm) and maximum-likelihood decoding (Viterbi algorithm). The sequential decoding uses a systematic procedure to search for a good estimation of the message sequence; however, such procedure requires a large memory and typically suffers from buffer overflow problems.

Andrew Viterbi developed the Viterbi algorithm in 1967 [20]. Since then, it has become the standard algorithm to decode the convolutional codes. At each time interval, the Viterbi decoding algorithm compares the actual received codeword with the codeword that might have been generated for each possible memory-state transition. The algorithm chooses the most likely sequence within a specific time frame based on the metrics of similarity. The maximum-likelihood decoding requires less memory than the sequential decoding because unlikely sequences are dismissed early, leaving a relatively small number of candidate sequences that need to be stored.

The addition of parity bits in the transmitted sequence eventually increases the transmission bandwidth requirement. In 1976, Ungerboeck invented Trellis-Coded Modulation technique to solve this problem.

#### 2.2 Trellis-Coded Modulation

In communication systems, error-correcting coding (ECC) reduces power utilization (i.e., the ratio of the received energy per bit to the noise spectral density) by adding redundancy to the transmitted signal. The performance improvement of the ECC can be achieved by expanding the bandwidth of the transmitted signal to the code rate in the power-limited region, which requires a high-order modulation scheme. For bandwidth-efficient multilevel amplitude and phase modulation such as PSK or QAM, without expanding the channel bandwidth required by ECC, increasing the number of signal phase or amplitude over the corresponding modulation constellation performs the same data throughput as uncoded modulation. However this increment requires an additional signal power to maintain the same level of system bit-error-rate [21-23]. In communications, Trellis-coded modulation is applied to solve the conflict of utility efficiency between transmission power and channel bandwidth.

The TCM coding process utilizes signal mapping combining error-correcting coding with modulation. The mapping by the set partitioning technique provides a combination of digital signals used in the modulation. This technique increases the minimum Euclidean distance between the pairs of coded signals; hence the loss from the expansion of the signal set is easily overcome and a significant coding gain is achieved with ECC. This is the reason why TCM technique does not violate the basic trade-off principle between power, bandwidth, and error probability. Therefore, in a bandwidth-limited communication system, without bandwidth enlargement, the redundancy bits are introduced into the signal to achieve good performance of coding gain through the TCM codes. This gain can be as high as 5dB.

The widely used ECC code in the TCM encoder is the convolutional code. As mentioned in Section 2.1, the Viterbi decoding algorithm is the standard method to decode convolutional codes, and commonly used in communication systems. In this TCM codec implementation, the TCM decoder design chooses the Viterbi algorithm as its decoding algorithm.

The following subsections describe details of the TCM, such as fundamentals and concepts, standard encoder structures, mapping by set partitioning method and the Viterbi algorithm.

#### 2.2.1 Fundamentals and Concept of TCM

Assume there is a model for the transmission of data with discrete-time, continuous-amplitude over the additive white Gaussian noise (AWGN) channel [24]. In this communication model, messages to be delivered to the user are represented by points, or vectors, in an N-dimensional Euclidean space  $\mathbb{R}^N$ , called a signal space. When a vector  $x = [x_1, x_2, ..., x_i]$  is transmitted, the received signal can be represented by the vector Z as:

$$Z = x + v \tag{2.1}$$

where v is a noise vector  $[v_1, v_2, ..., v_i]$  whose components  $v_1, v_2, ..., v_i$  are independent Gaussian random variables with zero mean and the same variance N<sub>0</sub>/2. N<sub>0</sub> is noise power spectral density. The vector x is chosen from a set, the signal constellation  $\Omega'$ , which consists the number of M' signal vectors. The average square length is referred to as the average signal energy and represented by:

$$E' = \frac{1}{M'} \sum_{x \in \Omega'} \left\| x \right\|^2 \tag{2.2}$$

If a sequence  $\{x_i\}$  of K signals, i = 0, 1, ..., K-1 is transmitted, the receiver observes received sequence  $y_0$ , ...,  $y_{k-1}$  and then decides that  $X_0$ , ...,  $X_{k-1}$  was transmitted if the squared Euclidean distance  $d^2$  is minimized for  $x_i = X_i$  (i = 0, 1, ..., K-1).

$$d^{2} = \sum_{i=0}^{K-1} \left\| y_{i} - x_{i} \right\|^{2}$$

(2.3)

That means if the sequence  $X_0, X_1, ..., X_{k-1}$  is closer to the received sequence than to any other allowable signal vector sequence, then the resulting sequence error probability, as well as the symbol error probability, is upper bounded by

$$P(e) \le \frac{M'-1}{2} \operatorname{erfc}(\frac{d_{\min}}{2\sqrt{N_0}})$$

(2.4)

in which the complementary error function erfc(x) is defined as  $erfc(x) = \frac{2}{\sqrt{\pi}} \int_{x}^{\infty} e^{-t^{2}} dt$ .

The information rate and the normalized squared minimum distance are useful in comparing different constellations. Let *R* represents the information rate, and  $\delta^2$ represents normalized squared minimum distance, these two can be defined as:

$$R = \frac{\log_2 M'}{N} \tag{2.5}$$

and

$$\delta^2 = \frac{d_{\min}^2}{E'} \log_2 M' \tag{2.6}$$

*R* is the ratio between the number of information bits carried by a single signal in the constellation and the number of dimensions *N*, *M'* is the number of signal vectors in constellation  $\Omega'$ , and *E'* is the average signal energy.

If M', N, and E' are given, the problem of designing a good communication system is choosing a set of vector signals such that the minimum distance between any two signals is maximize. The information rate is also referred to as the bandwidth efficiency of that signal set, and the normalized squared minimum distance is its energy efficiency. Equation (2.4) can be rewritten in the form

$$P(e) \le \frac{M'-1}{2} \operatorname{erfc}\left(\frac{\delta}{2} \sqrt{\frac{E_b}{N_0}}\right)$$

(2.7)

where

$$E_b = \frac{E'}{\log_2 M'}$$

represents the average energy per bit.

In TCM system, signals are dependent. To avoid a reduction of the transmission rate, the constellation should be expanded. The minimum free Euclidean distance  $d_{free}$  between two possible sequences in a large constellation is obtained to be greater than the minimum Euclidean distance  $d_{min}$  between two signals in the original constellation. This will be analyzed in Section 2.2.3. Hence using maximum-likelihood sequence detection will yield a distance gain  $d_{free}^2/d_{min}^2$ . On the other hand, expanding constellation induces an increase in the average energy expenditure from E' to E (i.e., energy loss E/E'), where E' and E are the average energy spent to transmit with uncoded and coded transmission, respectively. The asymptotic coding gain  $\gamma$  of a TCM scheme is

$$\gamma = \frac{d_{free}^2 / E}{d_{\min}^2 / E'}$$

(2.8)

The following example shows the advantage of using TCM [24]. Assume the transmission of quaternary source symbols (i.e., 2 bits per symbol) with uncoded transmission a channel alphabet with M'=4 would be adequate, and PSK is used. Then

$$\frac{d_{\min}^2}{E'} = 2$$

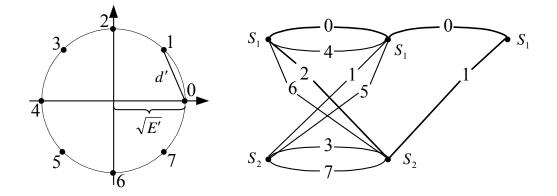

In here, M=2M=8 are used; M is the number of signal vectors in the new TCM constellation. Figure 2.4 shows the TCM scheme based on two quaternary constellations, {0, 2, 4, 6} and {1, 3, 5, 7}. This figure also shows a two-state Trellis construction.

**Figure 2.4** The constellation and two-state trellis used in the example TCM scheme From Figure 2.4, the coding gain of PSK-based TCM can be calculated as:

$$E' = \frac{d'^2}{4\sin^2(\pi/8)}$$

There are distances between signals associated with the parallel transitions, and the distances associated with a pair of paths in the trellis those originate from a common node (i.e., state,  $S_1$  or  $S_2$  in Figure 2.4) and merge into a single node at a later time. The free distance of this TCM scheme is calculated by choosing the smallest distances from them. Then,

$$\frac{d_{free}^2}{E} = \frac{1}{E} [d^2(0,2) + d^2(0,1)] = 2 + 4\sin^2\frac{\pi}{8} = 2.586$$

in which d(i, j) denotes the Euclidean distance between signals i and j, where i,  $j \in (0, 1..., 7)$ . The coding gain of this TCM scheme becomes:

$$\gamma = \frac{d_{free}^2 / E}{d_{\min}^2 / E'} = \frac{2.586}{2} = 1.293 \Longrightarrow 1.12 dB$$

By increasing the number of states (i.e., memory bits) in TCM, the coding gain can be increased. For example, if the four-state or eight-state trellis coding is used in this TCM scheme instead of two-state, the coding gain will be 3.01dB and 3.6dB, respectively [25]. Figure 2.5 shows the coding gain tendency with different numbers of the trellis states. At each point on the graph, the second number shows the coding gain can be achieved when the number of states (the first number) is used.

Figure 2.5 Result of coding gain versus the number of states

Increasing the number of states in TCM is a simple way to improve its performance. However, once the number of states grows high enough, the coding gain increases at much slower rate as illustrated in Figure 2.5. In addition, the error coefficient (i.e., the multiplicity of minimum-Euclidean-distance error events) of the code starts to dominate the code performance [11]. In order to solve this conflict, a multi-dimensional constellations model is introduced to the TCM system, which will be described in Section 2.3.

#### 2.2.2 TCM Encoder

Figure 2.6 shows a general 2-dimensional TCM encoder scheme on one time interval. The input symbol consists of n bits data. While two bits ( $I_1$  and  $I_2$ ) are coded through both differential and convolutional encoder, the other n-2 bits remain uncoded.

Figure 2.6 General scheme of a 2D TCM encoder

The differential encoder provides protection against the  $180^{\circ}$  phase ambiguity introduced by the communication channel. The convolutional encoder introduces forward error correction information for the transmitted data. This convolutional encoder is also called a Trellis encoder. This is a method of achieving coding gain by increasing the density of the constellation while keeping the minimum distance between each constellation points the same. It ensures that the transmitted sequence of points conforms to a valid trellis sequence, which is essential for proper decoding in the receiver. The signal mapping is used to convert the convolutional coded bits to an efficiency combination of Quadrature Amplitude Modulation (QAM) mode. QAM is a method to modulate the digital data in an analog signal in which each combination of phase and amplitude represents one of the  $2^{n}$  n-bit patterns.

As shown in Figure 2.6, without any error correction information, each symbol has n bits, which requires a  $2^{n}$ -point constellation. After the 2/3 convolutional encoder, each symbol has n+1 bits, which requires a  $2^{n+1}$ -point constellation. In general, for the same average power, a modulation scheme using a  $2^{n+1}$ -point constellation has higher BER if compared with the  $2^{n}$ -point constellation scheme. The reason for this is that the

minimum Euclidean distance between any two points on a  $2^{n+1}$ -point constellation is smaller, which decreases the noise margin. However, convolutional encoding introduces constraints in transforming an n-bit input symbol to a (n+1)-bit output symbol. Specifically, it does not allow two consecutive output symbols to be in the eight neighborhood positions of each other. This results in an increment of the minimum Euclidean distance between two consecutive output symbols, which is achieved through mapping by the set partitioning method. This process provides an overall performance gain of 4dB. Set partitioning is an important process after convolutional encode, which will be illustrated in Section 2.2.3.

As differential encoding is used in this TCM scheme; using this coding, errors caused by the phase reversal in the channel are not allowed to propagate. The receiver will reconstruct the information sequence properly except for the errors at the points where phase reversal occurs.

### 2.2.3 Set Partitioning

In TCM, the modulation is an integral part of the encoding process. It is designed in conjunction with the code to increase the minimum Euclidean distance between the pairs of the coded signals. The loss from the expansion of the signal set is easily overcome and a significant coding gain is achieved with relatively simple codes. The key to this integrated modulation and coding approach is to devise an effective method for mapping the coded bits into appropriate signal points so that the minimum Euclidean distance is maximized. In 1982, Ungerboeck developed such method, based on the principle of mapping by set partitioning [2-4].

Based on the set partitioning, the M-ary constellation is successively partitioned into 2, 4, 8, ...,  $2^{(\log_2 M)-1}$  subsets, with size M/2, M/4, M/8, ..., 2 with progressively larger minimum distances. The set partitioning method follows three Ungerboeck rules:

- U1: To parallel transitions are assigned members of the same partition;

- U2: To adjacent transitions are assigned members of the next larger partition;

- U3: To make all the signals are used equally often.

A set partitioning method is illustrated in the Figure 2.7. The figure shows a partitioning of the 16-points QAM constellation.

In Figure 2.7, the  $d_{min}^2$  between points in the subsets is increased by at least a factor of 2 with each partitioning. In the first partitioning, the 16-points constellation is subdivided into two 8-point subsets. The square of the minimum Euclidean distance  $d_{min}^2$  increases to  $2d^2$  from  $d^2$ . In the second partitioning, each of the two 8-point subsets is subdivided into two subsets of 4-point, and the square of the minimum Euclidean distance distance  $d_{min}^2$  is increased to  $4d^2$ . This process continues on the subsets until each subset has only two points, and the square of minimum Euclidean distance  $d_{min}^2$  is now increased to  $8d^2$ .

In QAM constellation, each level of partitioning increases the minimum Euclidean distance by  $\sqrt{2}$ . The level to which the signal is partitioned depends on the characteristics of the code.

Figure 2.7 Set partition of a 16-QAM constellation

In general, the TCM encoding process is performed as illustrated in Figure 2.6. A block of the n information bits is separated into two groups, one will be coded and the other remains uncoded. The group of coded bits will be used to select one of the possible subsets in the partitioned signal set, while the uncoded bits are used to select the points in each subset. Section 2.2.4 will further explain the mapping based on the set partitioning method. Section 2.3.3 will illustrate the mapping for the multi-dimensional constellation set partitioning.

## 2.2.4 Mapping and Trellis Diagram

An 8-state, rate 2/3 convolutional encoder is used as an example to analyze the trellis diagram and mapping method. Figure 2.8 illustrates a convolutional encoder used in the V.32 modem on one time interval [26-27]. Input of this TCM encoder is a 4-bit symbol, and the output is a 5-bit symbol. The output includes a 3-bit codeword and a 2-

bit uncoded word. This encoder works at the full baud rate. The baud rate is a measure of the speed of a serial communication using a modem or null-modem, roughly equivalents to bits per second.

Figure 2.8 Structure of the TCM encoder used in V.32 modem

The encoder operates as follows, the redundant bit  $Y_0$  is functionally obtained from  $I'_1$ ,  $I'_2$  which are differential coded bits obtained from  $I_1$ ,  $I_2$ , and three memory bits,  $S_0$ ,  $S_1$ ,  $S_2$  which interconnected by D-flip-flops (DFF), and a combination of AND and XOR logic gates. The logic functions are expressed by the following rational equations:

$$Y_2 = I'_2 = \frac{I_2 + I_1 I'_1 D}{1 + D}$$

(2.3)

$$Y_1 = I_1' = \frac{I_1}{1+D}$$

(2.4)

$$Y_0 = S_0 \tag{2.5}$$

$$S_2 = S_0 D \tag{2.6}$$

$$S_1 = \frac{S_2 D + I_1' D + I_2' D + S_0 I_2' D}{1 + S_0 D}$$

(2.7)

$$S_0 = \frac{S_1 D + I_2' D}{1 + I_1' D}$$

(2.8)

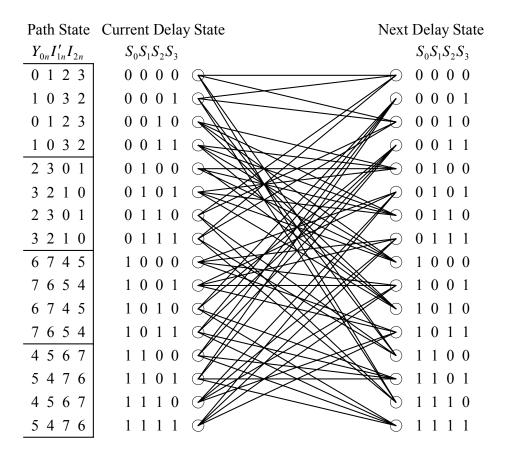

The symbol D represents a delay through a DFF which functions as a memory. There are three memory units  $S_0$ ,  $S_1$ ,  $S_2$  used in this convolutional encoder. The size of the encoder memory is referred to as a constrained length (k) of the code. The constraint length of the V.32 modem encoder shown in Figure 2.8 is 3. As shown in Figure 2.8, this convolutional encoder is eventually a finite-state machine. The number of states in the encoder is  $2^k$  for a given constraint length k. In this encoder, the number of states is  $2^3=8$ , and represented by the three bits  $S_0$ ,  $S_1$ , and  $S_2$ . The states  $S_0$ ,  $S_1$ ,  $S_2$  are also called delay states. The delay states at the last time interval and the output of the encoder at the current time interval  $Y_0$ ,  $Y_1$ ,  $Y_2$  control the conversion between each delay state. The output  $Y_0Y_1Y_2$  is also called the path state of the convolutional encoder.

The constraint condition of the convolutional encoder is that given a particular set of delay states ( $S_0$ ,  $S_1$  and  $S_2$ ) in which not all path states ( $Y_0$ ,  $Y_1$ , and  $Y_2$ ) are possible in that time interval. For example, based on the equations (2.5), (2.6), (2.7), (2.8), if  $S_{0n}S_{1n}S_{2n} = 000$ , the states that can be reached ( $S_{0(n+1)}S_{1(n+1)}S_{2(n+1)}$ ) are 000, 010, 100 and 110. "000" is for  $Y_1Y_2 = 00$ , since  $Y_0 = S_{0n}$ , hence  $Y_0Y_1Y_2 = 000$ , so that the subset of signals denoted "a" in Figure 2.9 is associated. "010" is for  $Y_1Y_2 = 10$ ,  $Y_0Y_1Y_2 = 010$ , corresponding with the subset of signals denoted "c". "100" is for  $Y_1Y_2 = 11$ ,  $Y_0Y_1Y_2 =$ 011, corresponding with the subset of signals denoted "d". "110" is for  $Y_1Y_2 = 01$ ,  $Y_0Y_1Y_2 = 001$ , corresponding with the subset of signals denoted "b. In this discussion, n and n+1 represent two continual time intervals. Figure 2.9 shows each subset formed by signals labeled a, b,... h.

| Imaginary                                                                                                                                                                                                                 |   | $Y_0$ | $Y_1$ | $Y_2$ |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-------|-------|-------|

| •h •g                                                                                                                                                                                                                     | a | 0     | 0     | 0     |

| •c •b •c                                                                                                                                                                                                                  | b | 0     | 0     | 1     |

| $\bullet e \bullet f \bullet e \bullet f$                                                                                                                                                                                 | c | 0     | 1     | 0     |

| $- \overset{\bullet a}{\longrightarrow} \overset{g \bullet d}{\longrightarrow} \overset{h}{\longrightarrow} \overset{a}{\longrightarrow} \overset{g \bullet d}{\longrightarrow} \overset{h}{\longrightarrow} \text{Real}$ | d | 0     | 1     | 1     |

| •b •c •b •c •b                                                                                                                                                                                                            | e | 1     | 0     | 0     |

| •e •f •e •f                                                                                                                                                                                                               | f | 1     | 0     | 1     |

| •d •a •d<br>•h •g                                                                                                                                                                                                         | g | 1     | 1     | 0     |

|                                                                                                                                                                                                                           | h | 1     | 1     | 1     |

Figure 2.9 A 32-signal constellation for the V.32 Modem TCM scheme

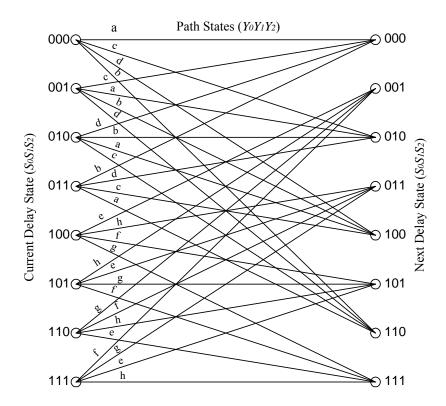

The uncoded bits  $Y_3Y_4$  in Figure 2.8 decide every single point of each subset shown in Figure 2.9. Each set of four points is symmetrically arranged and equally spaced on the constellation as far apart as possible. Eight different  $S_{0n}S_{1n}S_{2n}$  delay states corresponding with  $Y_0Y_1Y_2$  path states is summarized in the trellis diagram shown in Figure 2.10

Each current delay state in Figure 2.10 has four possible new delay state destinations. In each new delay state, there are four possible inputs coming from the last delay states, which are controlled by the path states. Each path state is also a part of the output of the encoder. This path state corresponds to the delay states that traverse from the left to the right side of the trellis diagram. This trellis diagram clearly shows the input bits ( $Y_1$ ,  $Y_2$ ) and output bits ( $Y_0$ ,  $Y_1$ ,  $Y_2$ ) relationship of the system associated with memory bits ( $S_0$ ,  $S_1$ ,  $S_2$ ). The decoder algorithm is created based on the relationship shown in this trellis diagram.

Figure 2.10 Trellis diagram of the V.32 modem TCM encoder

## 2.2.5 TCM Decoder

The TCM encoder is illustrated using a trellis whose branches are associated with transitions between encoder states and codeword transmitted over the channel. The primary task of the TCM decoder is to estimate the path that the codeword sequence traverses through the trellis. In this manner, TCM decoder is a reverse process of TCM encoder. In addition to the convolutional decoding, the de-mapping algorithm is a reverse function of the mapping logic function and the differential decoder performs the reverse function of the differential encoder.

Details of the TCM decoder will be described in Chapter 3. The kernel of the TCM decoder is the convolutional decoder, which completes the path estimation. The decoder algorithm used in this thesis is based on the Viterbi algorithm.

## 2.2.6 Viterbi Algorithm

Andrew Viterbi proposed an algorithm in 1967 to decode convolutional code and this became the Viterbi Algorithm [20]. This algorithm is an application of dynamic programming that finds "shortest paths" (maximum likelihood sequences) widely used in solving minimization problems. A critical feature of this algorithm is the complexity of the decoding process grows linearly with the number of symbols being transmitted, rather than exponentially with the number of the transmitted symbols. The Viterbi algorithm finds the sequence at a minimum Hamming distance (or Euclidean distance) from the received signal with the minimized equivalent accumulated squared error.

The Trellis diagram in Figure 2.10 shows a relationship between the delay states and the path states in each timing interval. The corresponding relations between delay states and path states construct the basic database used in the Viterbi algorithm cost function calculation. Normally, the calculation of cost functions uses two different types of distance: the Hamming distance and the Euclidean distance. In this thesis, the Hamming distance is chosen to be the cost function because the use of this distance is suitable in LUT method to simplify hardware implementation.

The Viterbi algorithm finds the path with the minimum path metric cost by sequentially moving through the trellis for each time interval. In a time interval T, from kT to (k+1)T, the receiver observes the sample received in that interval and computes the metric associated with all the branches. This metric stores the cost value of all branches as shown in the trellis diagram Figure 2.10. For example, if the memory bits (m bits) is used in the convolutional encoder, the N =  $2^{m}$  is the number of the states in

the convolutional encoder. If each delay states have four branches associated with the new delay states, the total 4N branch costs will be calculated; but only N path metrics are retained (i.e., stored in memory). The cost of each branch is defined as the Hamming distance (or Euclidean distance) between the received symbol and the possible true symbol. The minimum branch cost will be the survivor branch for the destination states.

The cost of the path is a sum of the survivor branch cost at the current time interval and the accumulating path cost of the last time interval. Only one path with minimum accumulate cost is kept as a tracing path. Since it is experimentally determined that the optimal length of a convolutional decoder is four or five times the constraint length of the convolutional encoder [26], after 4m or 5m time interval for (n, k, m) convolutional code, the path with minimum accumulate cost of the N paths will be the survivor path. Using the survivor path, the decoder will trace back to recreate the original signal data.

Decoding begins with comparing received channel symbol pairs then building the accumulated error metric for each states branch and path. Based on these metrics, Viterbi decoder will recover the original symbol (i.e., the input of the convolutional encoder). The Viterbi decoding process is accomplished as follows:

- 1. Selecting the Delay State having the smallest accumulated error metric and saving the number of that delay state.

- 2. Iteratively performing the following trace back steps until the beginning of the trellis is reached:

- Working backward through the state history table, for the selected state;

- Selecting a former state which is listed in the state history table as being the predecessor to that state;

- Saving the state number of each selected state.

- 3. Working forward through the list of selected states saved in the previous steps. Look up what input bits correspond to the transition from each predecessor state to its successor state. That is, those bits that must have been encoded by the convolutional encoder.

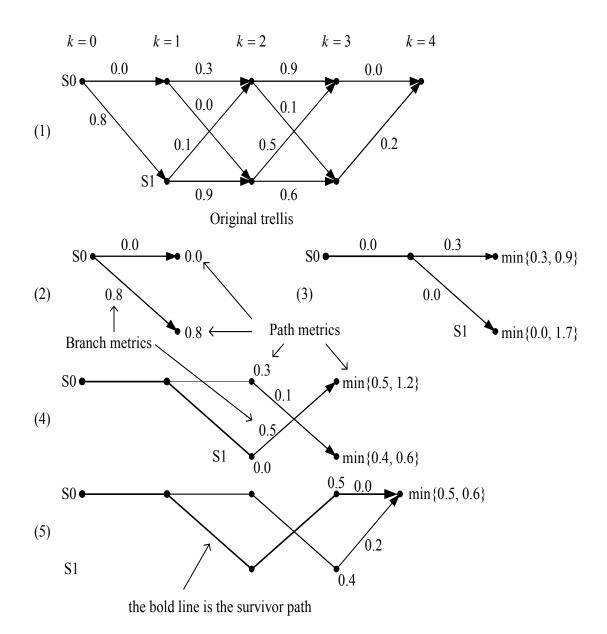

Figure 2.11 shows a simple example illustrating the Viterbi algorithm. The branch metrics, the survivor paths at each node, and the partial path metric of each surviving path are illustrated in this figure. The two-state (S0, S1) trellis with the branch metrics of the transitions is marked and the Viterbi algorithm is illustrated. The Viterbi algorithm finds iteratively the path with the minimum path metric of 0.5.

In Figure 2.11, pattern (1) shows the branch metric values from S0 to S1, or from S1 to S0 at every time interval k=0 to k=4. Pattern (2) assumes starting state is S0 at time interval k=0, the forward states will be S0 and S1. The cost for S0-S0 branch is 0.0, for S0-S1 is 0.8. Because 0.0<0.8, the survival branch is S0-S0, and the accumulate cost is 0.0 at k=1. Pattern (3) shows starting state is S0 at k=1 and the forward states will be S0 and S1. The cost for S0-S1 is 0.0. At k=2, accumulate cost for S0 is 0.3 (i.e., 0.0 plus 0.3), for S1 is 0.0 (i.e., 0.0 plus 0.0). Because 0.0<0.3, the survival branch is S0-S1. Same process works on patterns (4) and (5). Finally, at k=4, the minimum accumulate cost is 0.5 for branch S0-S0. After tracing back, the survival path is S0-S1-S0-S0; this path is shown in the bold line in Figure 2.11.

Figure 2.11 Viterbi algorithm illustration based on two-state trellis

### 2.3 Multi-Dimensional Trellis-Coded Modulation

The performance of TCM can be improved by increasing the number of shift register (i.e., memory bits) used in the convolutional code. This is equivalent to the increment of the number of states in the trellis coding. This has been described in Section 2.2.1. As mentioned earlier, the coding gain saturates at the high number of states, the multi-dimensional TCM concept is introduced in 1980's to overcome this deficiency [11-15].

### 2.3.1 Introduction to Multi-Dimensional TCM

In a 2-Dimensional TCM encoder, if the performance of the trellis code needs to be increased, more states may be used. This implies that the number of convolutional coding memory bits (i.e., constrained length) also increases. However the returns of this manner diminishes as the coding gain increases at much slower rate as shown in Figure 2.5.

An inherent cost of the coded schemes is that the size of the 2D constellation is doubled over uncoded schemes. This is due to the fact that a redundant bit is added every signaling interval. Without the cost, the coding gain of those coded schemes would be 3 dB to 6dB through 4-states to 128-states. Using a multi-dimensional constellation with a trellis code of rate n/n+1 can reduce that cost because fewer redundant bits are added compared to the 2D constellation. In the 4D TCM encoder structure, the redundant bits generated through convolutional encoder are added alternatively in each signaling interval. Compared to 2D constellation, that cost is reduced to 1.5dB in the 4D constellation.

In the following sections, the 4D constellation TCM encoder will be described and the difference between 2D and 4D constellations can be viewed. Because the differential encoder and convolutional encoder are still being used in the coding

34

process, the decoder algorithm is the same in both cases. The main differences between 2D and 4D are the mapping method and the clock rate in the convolutional coding.

### 2.3.2 Four-Dimensional TCM Encoder

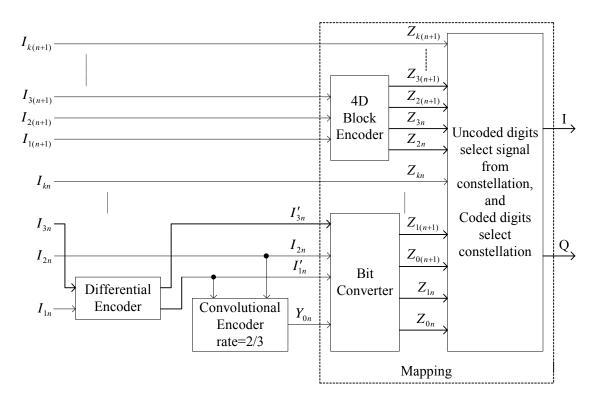

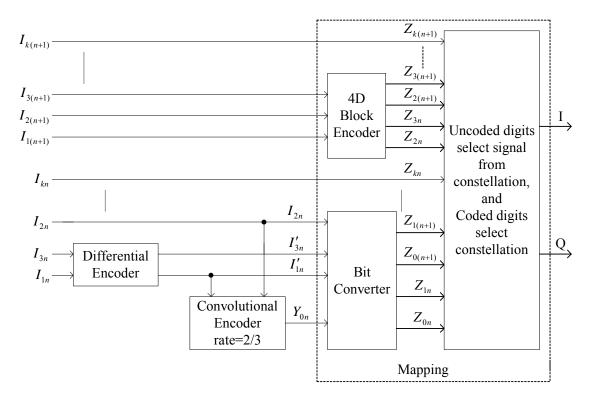

Figure 2.12 shows a general 4D TCM encoder scheme. The differential encoder provides protection against 180<sup>0</sup> phase ambiguity in the channel as described earlier. The convolutional encoder provides Forward Error Correction information for the transmitted data.

Figure 2.12 General scheme of a 4D TCM encoder

The 4D block encoder generates two pairs of selection bits, which are used to select the inner group or outer group of the two-selected 2D subset of the 4D constellation points. The bit converter generates another two pairs of the selection bits,

which is used to select pair subsets in the 4D constellation. Chapter 3 will provide detail of these selection pairs.

As shown in the Figure 2.12, the trellis coding part has a same structure as in Figure 2.6. The difference is on the input signals sequence, which is continual input into differential encoder in Figure 2.6, but is alternatively input into differential encoder in Figure 2.12. The input signals are k-bit symbol sequence, and n and n+1 represent two continual time intervals.

In this thesis, k is selected to be 7 based on the DAVIC specification of the TCM used in the MMDS system [16]. After TCM coding, the signal is mapped into a 256-QAM constellation. How the 4D 256-QAM constellation mapping is performed is described in the next section.

### 2.3.3 TCM 4D 256-QAM Constellation Mapping

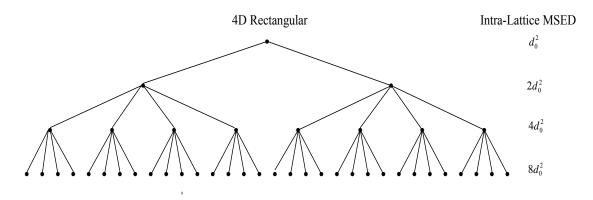

TCM schemes using 4D constellations have been reported in the literatures [11-15]. The 4D constellation is partitioned into thirty-two 4D subsets with eight times larger than the intra-subset minimum squared Euclidean distance (MSED) shown in Figure 2.13. One partitioning method of the 4D constellation is based on the partitioning of each constituent 2D constellation into four 2D subsets; concatenating a pair of 2D subsets forms each 4D subset [12]. The other partitioning method accomplishes algebraically without referring to the partitioning of the constituent 2D constellations [15].

Using the partition of 4D rectangular lattice as an example, Figure 2.13 illustrates a geometrical approach to partitioning multi-dimensional lattices into

sublattices with enlarged intrasublattice MSED. The partitioning of lattice is based on the partitioning of its constituent 2D rectangular lattices. Furthermore, the partitioning of a multi-dimensional lattice is done in an iterative manner. That is, the partitioning of a 2N-dimensional lattice is based on the partitioning of the constituent N-dimensional lattices, which is in turn based on the partitioning of the constituent N/2-dimensional lattice [11]. As shown in Figure 2.13, each time the intrasublattice MSED is doubled; the number of 4D sublattices increases fourfold.

Figure 2.13 Partitioning of a 4D rectangular lattice

To transmit k information bits per signaling interval using a rate of n/n+1 trellis code with a 4D rectangular constellation, the 4D constellation of  $2^{2k+1}$  points is constructed as follows. The first step is to obtain a constituent 4D rectangular constellation. The 2D constellation is divided into two groups, the inner group and the outer group [11]. The number of points in the inner group is  $2^k$ , the same as that in the corresponding uncoded scheme. The number of points in the outer group is 1/2 of that of the inner group. The inner and outer groups must satisfy the following two requirements:

- 1) Each subset has the same number of points (inner and outer).

- 2) Each group is invariant under  $90^{\circ}$ ,  $180^{\circ}$ , and  $270^{\circ}$  rotations.

The first requirement is necessary to convert the 4D constellation mapping into a pair of 2D constellation mappings. The second requirement preserves the symmetries of the lattice in the constellation.

As shown in Figure 2.12, on the 4D constellation mapping, a bit converter converts the four bits  $Y_{0n}$ ,  $I'_{1n}$ ,  $I_{2n}$ ,  $I'_{3n}$  into two pairs of selection bits,  $Z_{0n}$ ,  $Z_{1n}$ ,  $Z_{0n+1}$ ,  $Z_{1n+1}$ , which are used to select the pair of 2D subsets corresponding to the 4D type. The 4D block encoder takes three of the remaining eleven uncoded information bits,  $I_{1n+1}$ ,  $I_{2n+1}$ , and  $I_{3n+1}$ , and generates two pairs of selection bits,  $Z_{2n}$ ,  $Z_{3n}$ ,  $Z_{2n+1}$ ,  $Z_{3n+1}$ , which are used to select the inner group or outer group of each selected 2D subset. The detail of this corresponding relationship will be illustrated in Chapter 3.

# **CHAPTER 3**

# TCM CODEC IMPLEMENTATION ALGORITHM

This chapter focuses on the implementation algorithm and architecture of the TCM encoder and decoder. Illustrations of the encoder and the decoder will separate into two parts based on the mapping process (i.e., mapping for 2-dimensional and 4-dimensional).

## **3.1 Encoder Implementation**

The algorithm and hardware implementations in this thesis focus on the 16-state codec recommended in DAVIC 1.2 specifications [16]. The coded bits are ready for the 256-point constellation QAM modulation. There are two implementations on mapping: one is mapping for the 2-dimensional (2D) constellation, and the other is mapping for the 4-dimensional (4D) constellation. The following sections illustrate details of both processes.

### **3.1.1** A 2-Dimensional Encoder Implementation

A 16-state 2D TCM scheme is constructed with reference to both DAVIC [16] and V.32 TCM scheme [26]. The input signal symbol sequences are continually coming into the 2D TCM encoder at every time interval (i.e., 2D TCM encoder works at the full

baud rate). A combination of logic gates and D-Flip-Flops (DFF) as memory devices is used to implement the differential encoder and to generate the convolutional encoder states. Figure 3.1 shows a schematic diagram of the 2D TCM encoder.

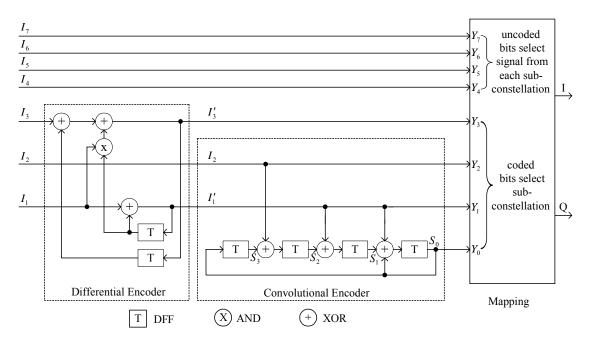

Figure 3.1 A 16-state 2-dimensional TCM encoder

The differential encoder functions as the following Boolean expression:

$$I'_{1}(n) = I_{1}(n) \oplus I'_{1}(n-1)$$

(3.1)

$$I'_{3}(n) = [I_{1}(n) \otimes I'_{1}(n-1)] \oplus I'_{3}(n-1) \oplus I_{3}(n)$$

(3.2)

where n and n-1 represent the two continual time interval.

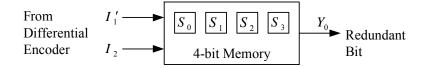

After differential encoding, a rate of 2/3 convolutional encoder generates an extra redundant parity bit  $Y_0$  using two bits  $I'_1$  and  $I_2$ . The parity bit  $Y_0$  carries only forward error-correction information. Figure 3.2 shows the relationship between  $I'_1$ ,  $I_2$  and  $Y_0$ . Outputs of the memory elements  $S_0$ ,  $S_1$ ,  $S_2$  and  $S_3$  are called delay states and values of the 3 bits  $Y_0$ ,  $I'_1$  and  $I_2$  are called path states.

Figure 3.2 Convolutional coding in TCM encoder

The logic function of all symbol bits and memory bits for the TCM scheme shown in Figure 3.1 are obtained from the following equations:

$$Y_i = I_i, \qquad i = m \in \{2, 4, 5, 6, 7\}$$

(3.3)

$$Y_3 = I'_3$$

(3.4)

$$Y_1 = I_1' \tag{3.5}$$

$$Y_0 = S_0 \tag{3.6}$$

$$S_0 = (S_1 \oplus I_1' \oplus S_0)D \tag{3.7}$$

$$S_1 = (S_2 \oplus I_1')D \tag{3.8}$$

$$S_2 = (S_3 \oplus I_2)D \tag{3.9}$$

$$S_3 = S_0 D$$

(3.10)

where D represents the time delay of memory element (i.e., a DFF). In Figure 3.1, four coded bits ( $Y_0$ ,  $Y_1$ ,  $Y_2$ ,  $Y_3$ ) combined with the other uncoded bits ( $Y_4$ ,  $Y_5$ ,  $Y_6$ , and  $Y_7$ ) are mapped into a 256-point constellation. The inphase signal (I) and quadrature signal (Q) are modulated and transmitted over communication channels. The 256-point constellation has 16 subsets (i.e.,  $2^4$  from 4 coded bits). Each subset uniquely identifies a set of 16 points (i.e.,  $2^4$  from 4 uncoded bits) out of 256 constellation points. This TCM scheme signal space mapping is defined in such a way that each set of 16 points is symmetrically arranged and equally spaced on the constellation as shown in Figure 3.3. Furthermore, each set of 16 points is as far apart as possible.

The figure illustrates sixteen subsets of a 256-point constellation formed by signals labeled a, b, c, d, e, f, g, h, i, j, k, l, m, n and o, p. The four coded bits ( $Y_0$ ,  $Y_1$ ,  $Y_2$  and  $Y_3$ ) select specific subset out of subsets a, b, c, d, e, f, g, h, i, j, k, l, m, n and o, p. The uncoded bits ( $Y_4$ ,  $Y_5$ ,  $Y_6$ , and  $Y_7$ ) select a particular signal out of the signals of each subset. Figure 3.3 is based on the mapping by set partitioning methods described in Chapter 2, Section 2.2.3.