# Study of Radiation Effects on 28nm UTBB FDSOI Technology

A Thesis Submitted

to the College of Graduate and Postdoctoral Studies

In Partial Fulfillment of the Requirements

For the Degree of Doctor of Philosophy

In the Department of Electrical and Computer Engineering

University of Saskatchewan

Saskatoon

By

**RUI LIU**

## **PERMISSION TO USE**

In presenting this thesis in partial fulfilment of the requirements for a Postgraduate degree from the University of Saskatchewan, I agree that the Libraries of this University may make it freely available for inspection. I further agree that permission for copying of this thesis in any manner, in whole or in part, for scholarly purposes may be granted by the professor or professors who supervised my thesis work or, in their absence, by the Head of the Department or the Dean of the College in which my thesis work was done. It is understood that any copying or publication or use of this thesis or parts thereof for financial gain shall not be allowed without my written permission. It is also understood that due recognition shall be given to me and to the University of Saskatchewan in any scholarly use which may be made of any material in my thesis.

Requests for permission to copy or to make other use of material in this thesis in whole or part should be addressed to:

Head of the Department of Electrical and Computer Engineering

University of Saskatchewan

57 Campus Drive

Saskatoon, Saskatchewan S7N 5A9

Canada

OR

Dean

College of Graduate and Postdoctoral Studies

University of Saskatchewan

116 Thorvaldson Building, 110 Science Place

Saskatoon, Saskatchewan S7N 5C9

Canada

## **ABSTRACT**

With the evolution of modern Complementary Metal-Oxide-Semiconductor (CMOS) technology, transistor feature size has been scaled down to nanometers. The scaling has resulted in tremendous advantages to the integrated circuits (ICs), such as higher speed, smaller circuit size, and lower operating voltage. However, it also creates some reliability concerns. In particular, small device dimensions and low operating voltages have caused nanoscale ICs to become highly sensitive to operational disturbances, such as signal coupling, supply and substrate noise, and single event effects (SEEs) caused by ionizing particles, like cosmic neutrons and alpha particles. SEEs found in ICs can introduce transient pulses in circuit nodes or data upsets in storage cells. In welldesigned ICs, SEEs appear to be the most troublesome in a space environment or at high altitudes in terrestrial environment. Techniques from the manufacturing process level up to the system design level have been developed to mitigate radiation effects. Among them, silicon-on-insulator (SOI) technologies have proven to be an effective approach to reduce single-event effects in ICs. So far, 28nm ultra-thin body and buried oxide (UTBB) Fully Depleted SOI (FDSOI) by STMicroelectronics is one of the most advanced SOI technologies in commercial applications. Its resilience to radiation effects has not been fully explored and it is of prevalent interest in the radiation effects community. Therefore, two test chips, namely ST1 and AR0, were designed and tested to study SEEs in logic circuits fabricated with this technology.

The ST1 test chip was designed to evaluate SET pulse widths in logic gates. Three kinds of the on-chip pulse-width measurement detectors, namely the Vernier detector, the Pulse Capture detector and the Pulse Filter detector, were implemented in the ST1 chip. Moreover, a Circuit for Radiation Effects Self-Test (CREST) chain with combinational logic was designed to study both SET and SEU effects. The ST1 chip was tested using a heavy ion irradiation beam source in Radiation Effects Facility (RADEF), Finland. The experiment results showed that the cross-section of the 28nm UTBB-FDSOI technology is two orders lower than its bulk competitors. Laser tests were also applied to this chip to research the pulse distortion effects and the relationship between SET, SEU and the clock frequency. Total Ionizing Dose experiments were carried out at the University of Saskatchewan and European Space Agency with Co-60 gammacell radiation sources.

The test results showed the devices implemented in the 28nm UTBB-FDSOI technology can maintain its functionality up to 1 Mrad(Si).

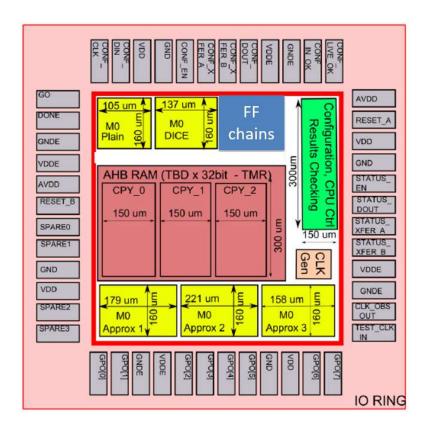

In the AR0 chip, we designed five ARM Cortex-M0 cores with different logic protection levels to investigate the performance of approximate logic protecting methods. There are three custom-designed SRAM blocks in the test chip, which can also be used to measure the SEU rate. From the simulation result, we concluded that the approximate logic methodology can protect the digital logic efficiently.

This research comprehensively evaluates the radiation effects in the 28nm UTBB-FDSOI technology, which provides the baseline for later radiation-hardened system designs in this technology.

## **ACKNOWLEDGEMENTS**

My Ph.D. research is finished under the help from all the professors, research staffs and specialists. Without the guidance, assistance and suggestions from you, it would be impossible for me to complete the project and publish papers in journals and conferences.

Firstly, I hope to show my deep appreciation to my supervisor, Dr. Li Chen. In the past five years, Dr. Chen put great effort on my research and projects. He provided me lots of chances in the cooperation with industrial companies and research institutes. He also gave me many opportunities for chip design in advanced technologies and test campaigns. All these practices are really valuable and beneficial for my work and research in the future.

I also hope to say thank you to Adrian Evans from IRoC technology. In the collaboration projects with IRoC, Adrian taught me so much from IC design to software development. Without his help and guidance, it would be difficult to design the chips successfully. Adrian showed me the chip design and verification methodologies in the industrial area, which is helpful in my job hunting.

Thanks should be given to the other collaborators from CISCO, IRoC and ESTEC as well. Shi-Jie Wen, Véronique Ferlet-Cavrois, Maximilien Glorieux, and Joao Cunha gave me many valuable comments in my projects and publications. It is my honor to work with the great researchers and engineers in the radiation electronic area.

Finally, I would give my deepest appreciations and apologize to my family. In the past five years, my parents gave me their unconditional love and support. Without their understand and support, I could not get all the achievements and finish my Ph.D. study.

# **TABLE OF CONTENTS**

| PERMISSION TO USE                                             | i    |

|---------------------------------------------------------------|------|

| ABSTRACT                                                      | ii   |

| ACKNOWLEDGEMENTS                                              | iv   |

| TABLE OF CONTENTS                                             | v    |

| LIST OF FIGURES                                               | viii |

| LIST OF TABLES                                                | xii  |

| LIST OF ABBREVIATIONS                                         | xiv  |

| Chapter 1: INTRODUCTION                                       | 1    |

| 1.1 Introduction                                              | 1    |

| 1.2 Motivation                                                | 7    |

| 1.3 Thesis Organization                                       | 9    |

| Chapter 2: BACKGROUND INFORMATION                             | 11   |

| 2.1 Single Event Effects                                      | 11   |

| 2.1.1 Charge Deposition and Collection                        | 11   |

| 2.1.2 Single Event Upset                                      | 13   |

| 2.1.3 Single Event Transient                                  | 14   |

| 2.1.4 Single Event Multiple Transient and Multiple Bits Upset | 15   |

| 2.1.5 Single Event Latchup                                    | 15   |

| 2.2 SEE Test Methodologies                                    | 16   |

| 2.2.1 Particle Tests                                          | 16   |

| 2.2.2 Pulsed Laser Test                                       | 17   |

| 2.3 Total Ionizing Dose                                       | 18   |

| 2.4 UTBB-FDSOI Technology                                     | 19   |

| Chapter 3: SET Pulse Measurement Chip (ST1)                   |      |

| 3.1 Top-Level Specification                                   |      |

| 3.2    | Configuration Interface                                     | 25 |

|--------|-------------------------------------------------------------|----|

| 3.3    | On-Chip Clock Generation                                    | 28 |

| 3.3.1  | . Clock Generation logic                                    | 28 |

| 3.3.2  | Clock Observation Circuitry                                 | 31 |

| 3.4    | Error Reporting Interface                                   | 31 |

| 3.5    | Self-Test Experiment                                        | 36 |

| 3.6    | SET Test Circuits                                           | 36 |

| 3.6.1  | . Components                                                | 36 |

| 3.6.2  | Vernier SET Detector                                        | 37 |

| 3.6.3  | Classic Pulse Capture Detector                              | 40 |

| 3.6.4  | Pulse Filter Detector                                       | 42 |

| 3.6.5  | CREST Circuit                                               | 44 |

| 3.7    | Gate Chains for SET Measurement                             | 47 |

| 3.7.1  | Normal SET Capture Gate Chains                              | 47 |

| 3.7.2  |                                                             |    |

| 3.7.3  | Low-voltage SET Capture Chain                               | 50 |

| Chapte | r 4: ST1 CHIP SIMULATION AND IRRADIATION TEST RESULTS       | 55 |

| 4.1    | Detector Response with Different Pulse Inputs               | 55 |

| 4.2    | Detector Response at Different PVT Conditions               |    |

| 4.3    | Simulated Pulse Narrowing and Broadening Effects            |    |

| 4.4    | Testing System introduction                                 |    |

| 4.5    | Heavy-Ion Test Result and Analysis                          | 62 |

| 4.6    | Pulsed-Laser Experimental Results at U of S                 | 69 |

| 4.7    | TID Experiment at U of S and Result Discussions             |    |

| 4.7.1  | TID Test Result in Heavy-ion test                           | 71 |

| 4.7.2  | TID Test Result from Co-60 Irradiation                      | 72 |

| 4.7.3  | Analysis of Static and Dynamic Result Discrepancy           | 74 |

| 4.7.4  | Analysis of Heavy-ion and Co-60 TID Test Result Differences |    |

| 4.8    | TID Experiment at ESTEC                                     |    |

| 4.8.1  | Test Setup                                                  | 77 |

| 4.8.2  | Procedure                                                   | 80 |

| 4.8.3  | Test Result                                                 | 80 |

| 4.8.4  | FSTEC TID Test Conclusion                                   | 84 |

| 4.9 Laser Test at NRL                                     | 84  |

|-----------------------------------------------------------|-----|

| 4.9.1 Laser Test on OR2 chain                             | 85  |

| 4.9.2 Laser Test on CREST circuits                        | 87  |

| Chapter 5: ARM SET Test Chip (AR0)                        | 89  |

| 5.1 Top-Level Specification                               | 89  |

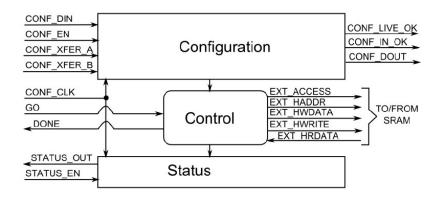

| 5.2 Configuration, Clock Generation, and Status Interface | 90  |

| 5.2.1 Configuration Interface                             | 90  |

| 5.2.2 Clock Generation Logic                              | 91  |

| 5.2.3 Status Interface                                    | 91  |

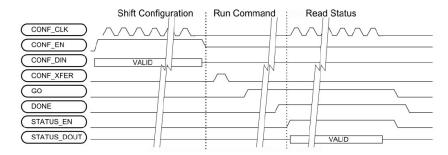

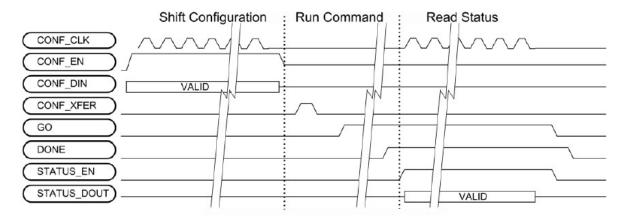

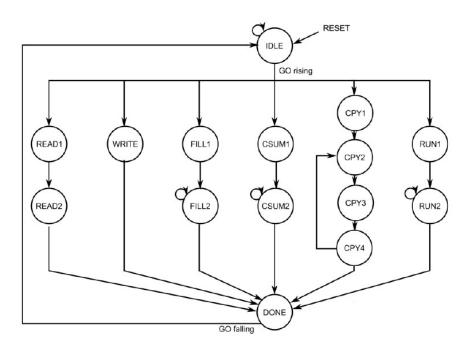

| 5.3 Command Protocol                                      | 92  |

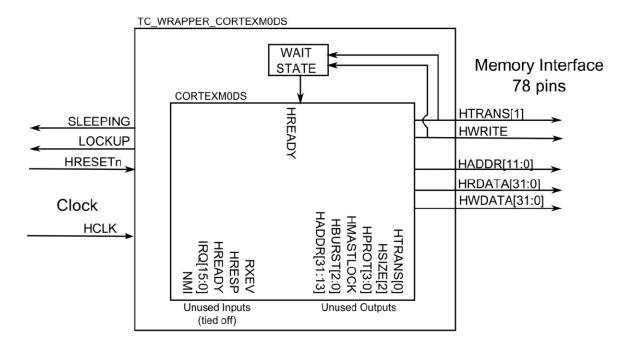

| 5.4 ARM M0 Utilization                                    | 93  |

| 5.5 Memory Interface                                      | 95  |

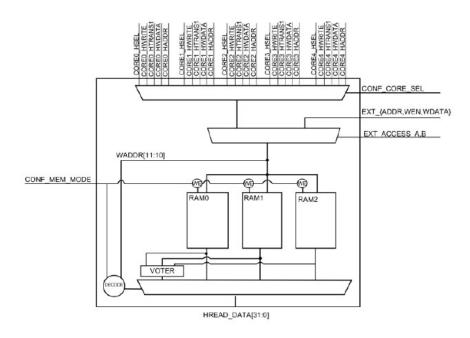

| 5.5.1 TMR Memory Wrapper                                  | 96  |

| 5.5.2 External Memory Controller                          | 97  |

| 5.6 Critical Top-Level Timing                             | 100 |

| 5.7 Approximate Logic ARM Core Simulation result          | 102 |

| Chapter 6: Summary and Future work                        | 104 |

| 6.1 Summary                                               | 104 |

| 6.2 Future Work                                           | 106 |

| REFERENCES                                                | 107 |

# **LIST OF FIGURES**

| Figure 1.1 The Flux of GCR Particles [9]                                                            | 3   |

|-----------------------------------------------------------------------------------------------------|-----|

| Figure 1.2 LET Spectra at Geosynchronous [6]                                                        | 4   |

| Figure 1.3 Air shower [6]                                                                           | 6   |

| Figure 1.4 Error Rate as a Function of Frequency for Combinational and Sequential Logic Elements as |     |

| well as their Sum [27]                                                                              | 7   |

| Figure 2.1 Charge Track in MOS Device                                                               | 11  |

| Figure 2.2 Charge Deposition and Collection Flow                                                    | 12  |

| Figure 2.3 Current Spark                                                                            | 12  |

| Figure 2.4 Back-to-back Invertor Sensitive Points                                                   | 13  |

| Figure 2.5 Transient Pulses with Different LET Ion Strike in a SRAM Cell [7]                        | 14  |

| Figure 2.6 Clock Frequency Influence on SET Soft Error Rate                                         | 15  |

| Figure 2.7 Parasitic Structure in a CMOS Device                                                     | 16  |

| Figure 2.8 Photon Effects                                                                           | 18  |

| Figure 2.9 Charge Injection Process in SiO <sub>2</sub>                                             | 19  |

| Figure 2.10 FDSOI Cross Section                                                                     | 20  |

| Figure 2.11 FDSOI Back-gate Control                                                                 | 21  |

| Figure 3.1 SET Test-Chip Top-Level Logical View                                                     | 23  |

| Figure 3.2 ST1 Test Chip Floor Plan                                                                 | 25  |

| Figure 3.3 High-level View of Configuration Interface                                               | 26  |

| Figure 3.4 TMR Input Configuration Shift Register                                                   | 27  |

| Figure 3.5 TMR Input Configuration Shift Register                                                   | 27  |

| Figure 3.6 High-level View of Clock Generator                                                       | 28  |

| Figure 3.7 Pulse Filter for Clock Generator                                                         | 29  |

| Figure 3.8 Programmable Ring Oscillator                                                             | 30  |

| Figure 3.9 Clock Observation Muxing                                                                 | 31  |

| Figure 3.10 Timing Diagram for Error Reporting Event                                                | 32  |

| Figure 3.11 Circuit Diagram of Control Logic for Error Reporting                                    | 34  |

| Figure 3.12 Circuit Diagram of Data Muxing Logic for Error Reporting                                | 35  |

| Figure 3.13 Circuit Diagram of Data Muxing Logic for Error Reporting                                | 36  |

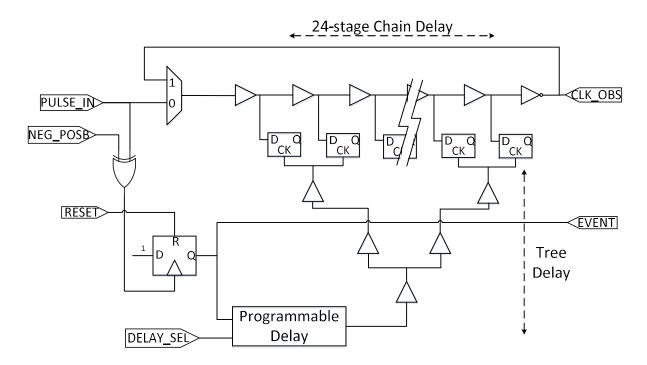

| Figure 3.14 Vernier Detector                                                                        | .37 |

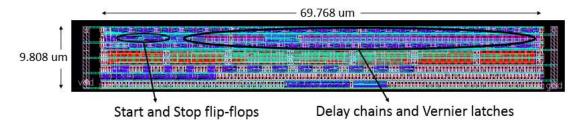

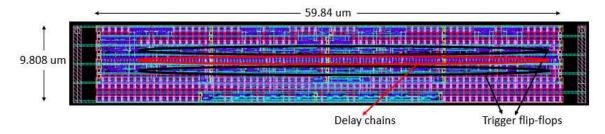

| Figure 3.15 Layout of Vernier Detector                                     | 40 |

|----------------------------------------------------------------------------|----|

| Figure 3.16 Pulse Capture Detector                                         | 40 |

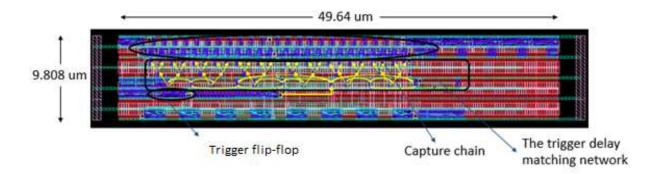

| Figure 3.17 Layout of Pulse Capture Detector                               | 41 |

| Figure 3.18 Pulse Filter Detector                                          | 43 |

| Figure 3.19 Layout of Pulse Filter Detector                                | 43 |

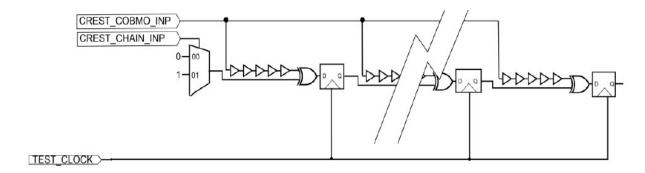

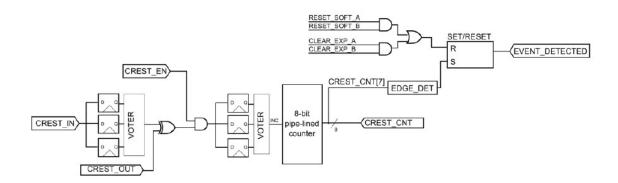

| Figure 3.20 Basic Structure of CREST Circuit                               | 45 |

| Figure 3.21 High-level View of CREST Experiment                            | 45 |

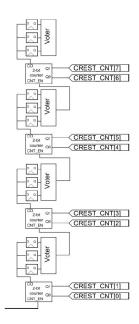

| Figure 3.22 2-Bit Counter                                                  | 46 |

| Figure 3.23 8-Bit Pipelined Counter                                        | 47 |

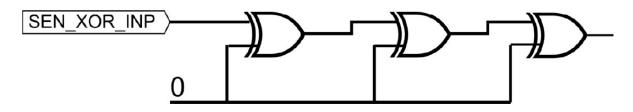

| Figure 3.24 Topology of XOR Gate Chain                                     | 48 |

| Figure 3.25 Topology of MUX Chain                                          | 48 |

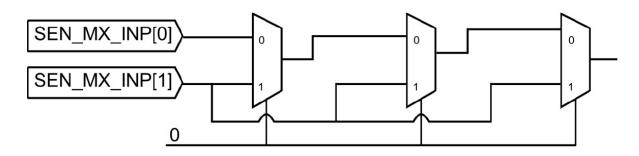

| Figure 3.26 SEMT Capture Chains                                            | 49 |

| Figure 3.27 Layout of SEMT Capture Chains                                  | 49 |

| Figure 3.28 Sensor Chain with Level Shifter                                | 50 |

| Figure 3.29 Final Chip Layout and Block Level Division                     | 50 |

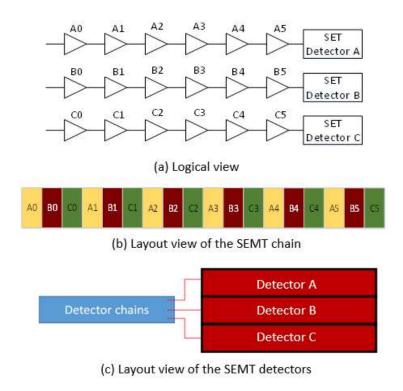

| Figure 3.30 Chip picture                                                   | 51 |

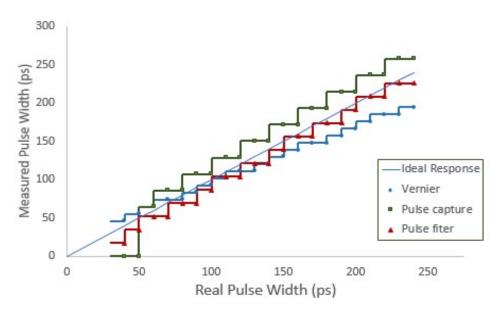

| Figure 4.1 Simulated Sensitivity of SET Detectors                          | 56 |

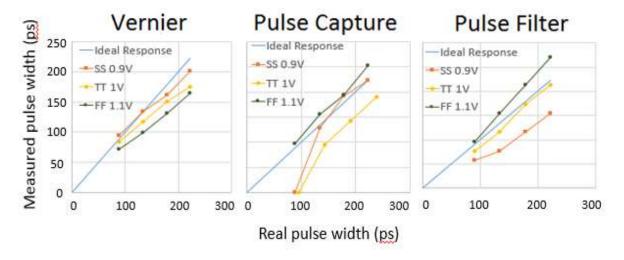

| Figure 4.2 SET Detector Response at three PVT Conditions                   | 57 |

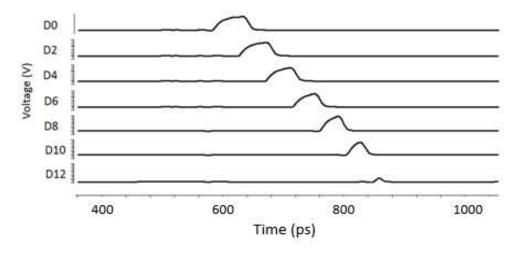

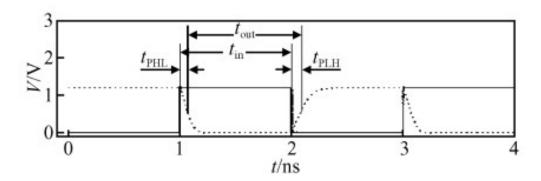

| Figure 4.3 Narrowing of a Positive Transient                               | 59 |

| Figure 4.4 Broadening of a Negative Transient                              | 59 |

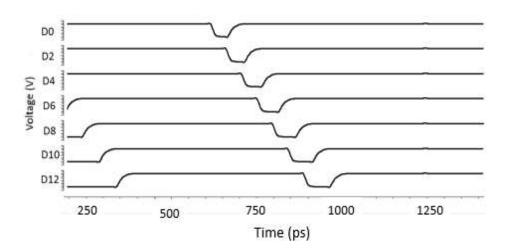

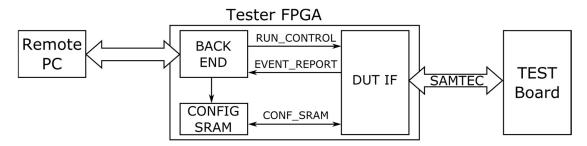

| Figure 4.5 Hierarchical view of the testing system                         | 60 |

| Figure 4.6 Testing System Structure                                        | 62 |

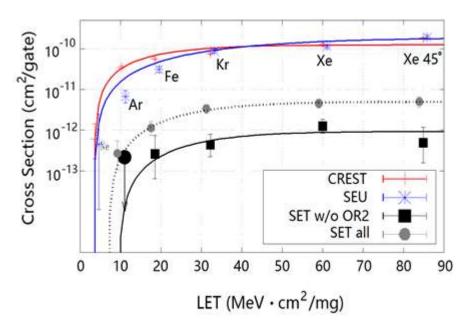

| Figure 4.7 CREST, SEU, SET Cross Section versus LET, VDD=1V                | 63 |

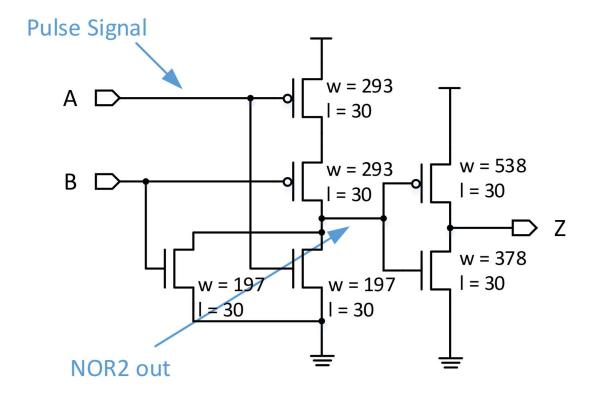

| Figure 4.8 OR2X8 Schematic                                                 | 64 |

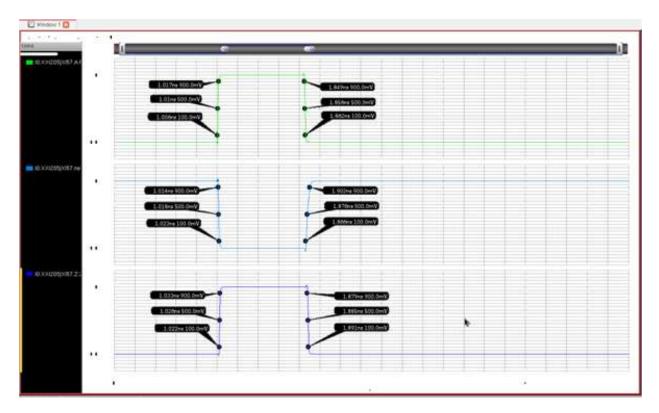

| Figure 4.9 OR2X8 Post-Layout Simulation result                             | 65 |

| Figure 4.10 Example of pulse broadening                                    | 66 |

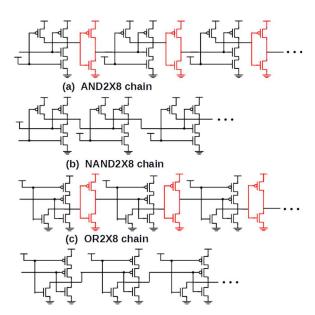

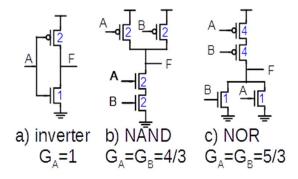

| Figure 4.11 NOR2X8, OR2X8, NAND2X8 and AND2X8 Chain Schematic              | 67 |

| Figure 4.12 Logic Effort of the Invertor, Two-input NAND and NOR Gates     | 68 |

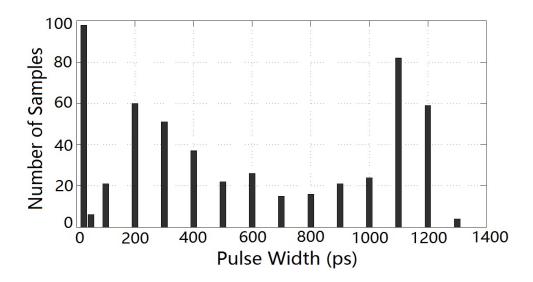

| Figure 4.13 SET Pulse Width Distribution –OR2X8, VDD=1V                    | 69 |

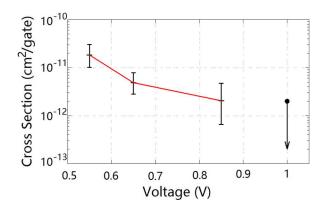

| Figure 4.14 BUFX4 SET Cross-Section Showing Voltage Sensitivity            | 69 |

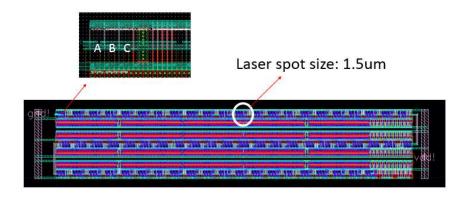

| Figure 4.15 Two-photon Pulsed-Laser Facility at University of Saskatchewan | 70 |

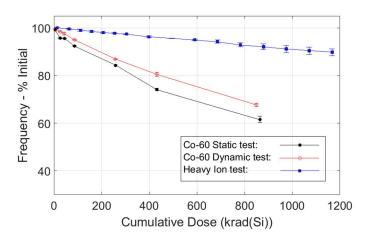

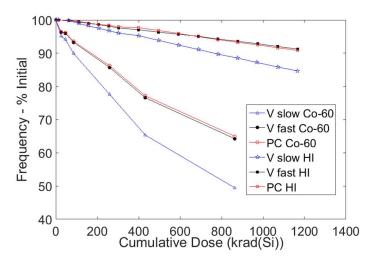

| Figure 4.16 Impact of TID on Main RO Frequency                             | 72 |

| Figure 4.17 RO Frequency versus TID in Vernier(V) Slow, Vernier(V) Fast and Pulse Cap | oture (PC) |

|---------------------------------------------------------------------------------------|------------|

| Detectors for HI and Co-60 Experiments                                                | 72         |

| Figure 4.18 Gammacell 220 Co-60 Irradiator in University of Saskatchewan              | 73         |

| Figure 4. 19 Mechanism of RICN                                                        | 75         |

| Figure 4.20 Charge Yield vs Electric Field [53]                                       | 76         |

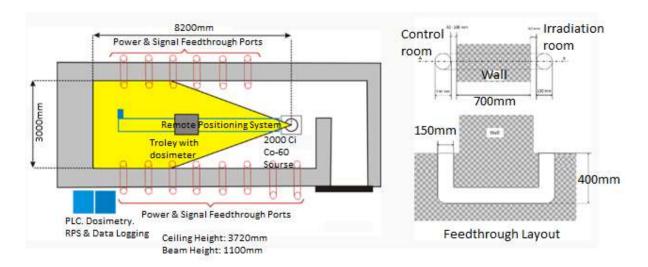

| Figure 4.21 Radiation Facility Layout                                                 | 77         |

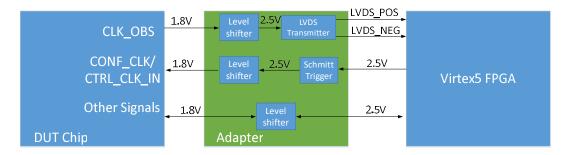

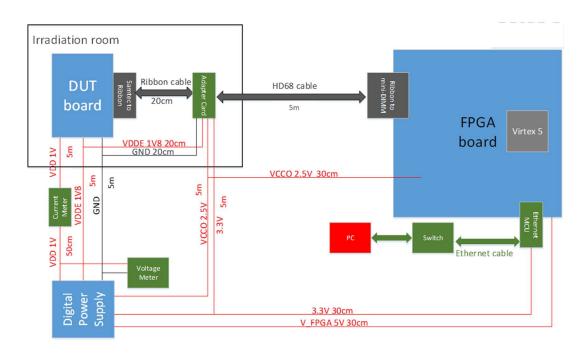

| Figure 4.22 ESTEC TID Test Scheme                                                     | 78         |

| Figure 4.23 ESTEC TID Test Setup                                                      | 79         |

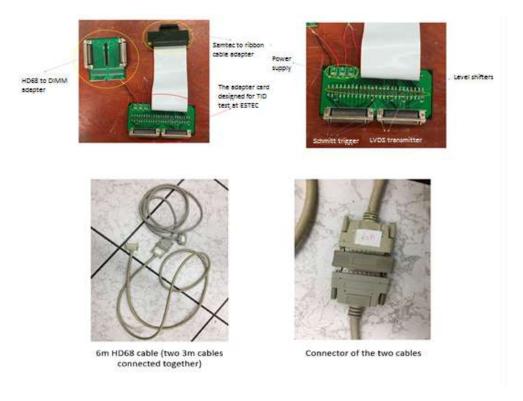

| Figure 4.24 Adapter Cards and HD68 Ribbon Cable                                       | 79         |

| Figure 4.25 Adapter Cards and HD68 Ribbon Cable                                       | 80         |

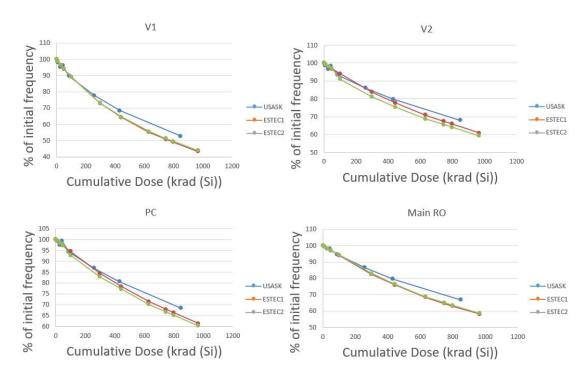

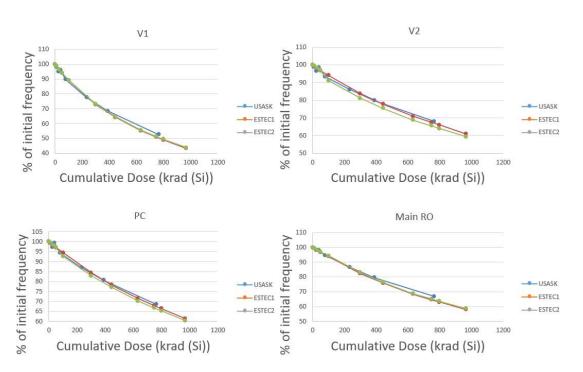

| Figure 4.26 TID test results comparison                                               | 82         |

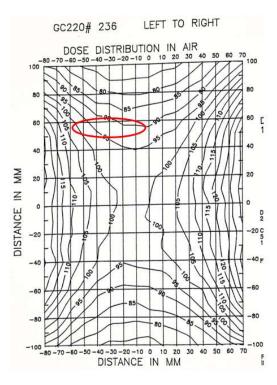

| Figure 4.27 TID Facility Calibration Chart at the U of S                              | 83         |

| Figure 4.28 Calibrated TID Test Results Comparison                                    | 83         |

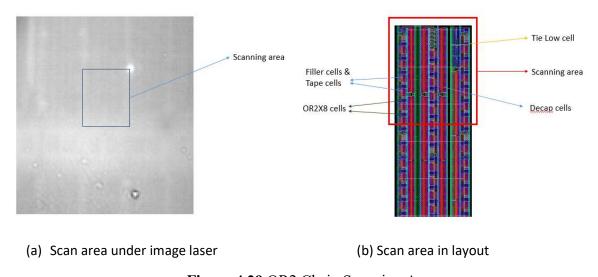

| Figure 4.29 OR2 Chain Scanning Area                                                   | 85         |

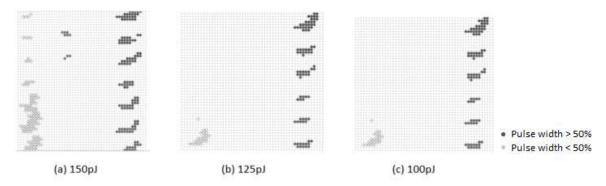

| Figure 4.30 OR2 Chain with Vernier Detector Laser Scanning Results                    | 85         |

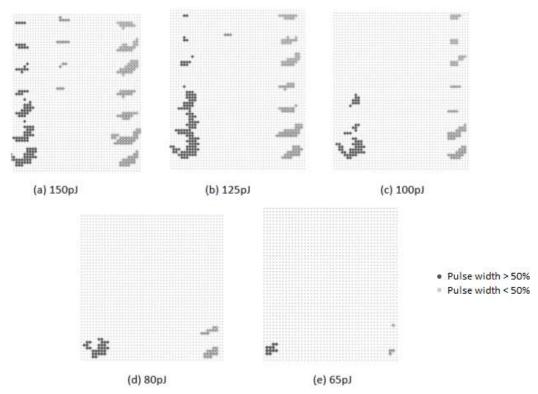

| Figure 4.31 OR2 Chain with Pulse Capture Detector Laser Scanning Results              | 86         |

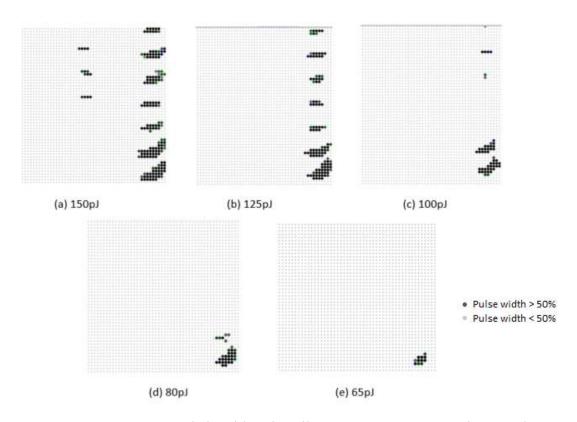

| Figure 4.32 OR2 Chain with Pulse Filter Detector Laser Scanning Results               | 86         |

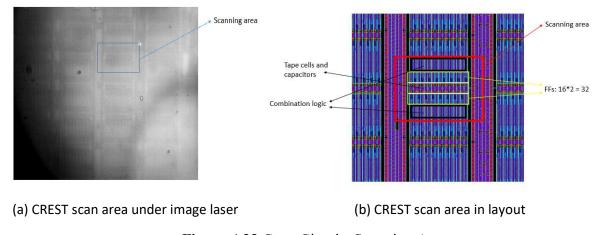

| Figure 4.33 Crest Circuits Scanning Area                                              | 87         |

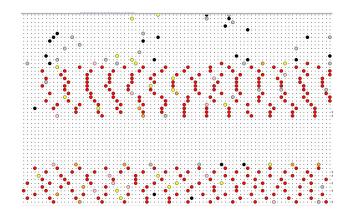

| Figure 4.34 CREST Circuits Scanning Result at 580MHz                                  | 88         |

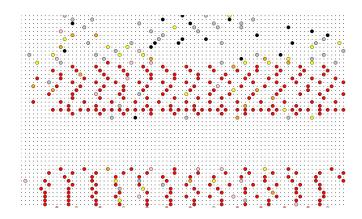

| Figure 4.35 CREST Circuits Scanning Result at 750MHz                                  | 88         |

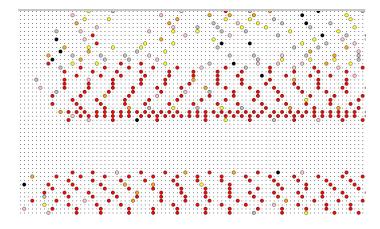

| Figure 4.36 CREST Circuits Scanning Result at 1GHz                                    | 88         |

| Figure 5.1 AR0 test-chip floor plan                                                   | 90         |

| Figure 5.2 High-level Control Structure                                               | 92         |

| Figure 5.3 Typical Command Execution Sequence                                         | 93         |

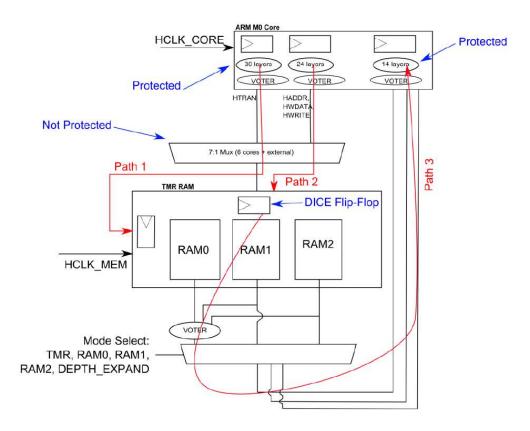

| Figure 5.4 Wrapper Around ARM M0 Core                                                 | 94         |

| Figure 5.5 Wrapper around ARM M0 Core                                                 | 96         |

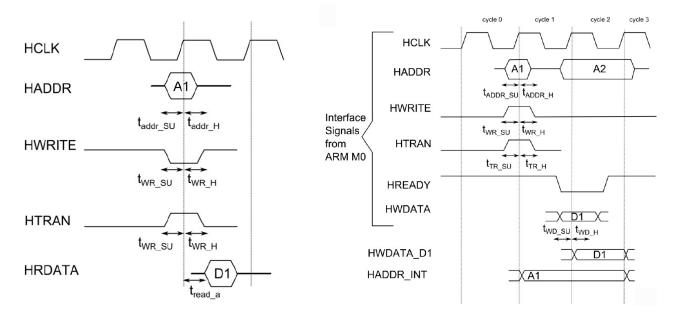

| Figure 5.6 SRAM Write Cycle Timing with One Wait State                                | 96         |

| Figure 5.7 TMR Memory Wrapper                                                         | 97         |

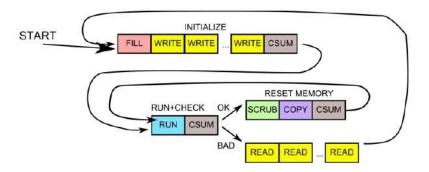

| Figure 5.8 Memory Controller State Machine                                            | 98         |

| Figure 5.9 Timing Diagram for Configuration Operation                                 | 98         |

| Figure 5.10 Typical Operation Sequence under Radiation Testing                        | 90         |

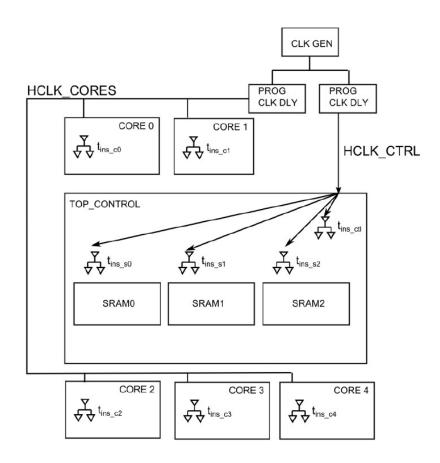

| Figure 5.11 Memory Interface and Critical Timing                 | 101 |

|------------------------------------------------------------------|-----|

| Figure 5.12 Top-level Clock Distribution with Programmable Delay | 102 |

## LIST OF TABLES

| Table 1.1 Spacecraft for Which SEEs Have Had an Impact [3] | 2   |

|------------------------------------------------------------|-----|

|                                                            |     |

| Table 3.1 ST1 Test Chip Pinout                             | 24  |

| Table 3.2 Available On-Chip Clock Frequencies              | 30  |

| Table 3.3 Types of Experiments                             | 37  |

| Table 3.4 SET Test Chip List of SET Experiments            | 38  |

| Table 3.5 Vernier Detector Port List                       | 39  |

| Table 3.6 Pulse Capture Detector Port List                 | 42  |

| Table 3.7 Pulse Filter Detector Port List                  | 44  |

| Table 3.8 Gate Delays for 8-Bit Counter                    | 46  |

| Table 3.9 Signal List of the ST1 Chips                     | 51  |

|                                                            |     |

| Table 4.1 Stage Delay at Different PVT Conditions          | 57  |

| Table 4.2 Stage Delay at Different PVT Conditions          | 58  |

| Table 4.3 FPGA Testing System Signal List                  | 61  |

| Table 4.4 Simulation Conclusion                            | 65  |

| Table 4.5 Laser Test Result on OR2X8 Chain                 | 70  |

| Table 4.6 Embedded Ring Oscillators                        | 71  |

| Table 4. 7 Frequencies VS. Total Absorbed Dose             | 74  |

| Table 4.8 TID Experiment Test Points                       | 81  |

|                                                            |     |

| Table 5.1 ARM Cortex M0 Design Information                 | 89  |

| Table 5.2 Processor Core Variants                          | 89  |

| Table 5.3 Available On-Chip Clock Frequencies              | 91  |

| Table 5.4 List of Configuration Fields                     | 92  |

| Table 5.5 On-Chip Commands                                 | 93  |

| Table 5.6 ARM M0 Port Connections                          | 95  |

| Table 5.7 Memory Write Path Critical Timing (Path 1)       | 100 |

| Table 5.8 Memory Write Path (Path 2)                       | 100 |

| Table 5.9 Memory F   | Read Access Path                                          | 101                     |

|----------------------|-----------------------------------------------------------|-------------------------|

| Table 5.10 Error Mit | itigation Rate vs. Overhead (The second column is summari | zed from an unpublished |

| paper)               |                                                           | 103                     |

## LIST OF ABBREVIATIONS

ARM Advanced RISC Machine

CMOS Complementary Metal-Oxide Semiconductor

CTS Clock Tree Synthesis

DICE Dual Interlocked Storage Cell

DUT Device Under Test

ESA European Space Agency

FDSOI Fully Depleted Silicon On Insulator

FPGA Field Programmable Gate Array

GCR Galactic Cosmic Rays

HI Heavy Ion

IC Integrated Circuit

LET Linear Energy Transfer

LVDS Low-Voltage Differential Signaling

MSB Most Significant Bit

NRL Naval Research Laboratory

PC Personal Computer

PLL Phase-locked loops

PVT Process, Voltage and Temperature

RAM Random Access Memory

RO Ring Oscillator

SEE Single Event Effect

SET Single Event Transient

SEU Single Event Upset

SPICE Simulation Program with Integrated Circuit Emphasis

TID Total Ionizing Dose

TMR Triple Modular Redundancy

TPA Two Photon Absorption

UTBB Ultra-Thin Body and Buried oxide

UVM Universal Verification Methodology

## **Chapter 1: INTRODUCTION**

#### 1.1 Introduction

A single particle with high energy may cause unexpected effects in integrated circuits (ICs), which is known as Single Event Effects (SEEs). An SEE may result in disastrous consequences in an electronic system.

In 1975, Binder and his colleagues reported that the unexpected triggering of digital circuits had caused anomalies in communication satellite operation [1]. Some JK flip-flops were triggered unexpectedly, which caused the malfunctioning of the satellite. In 1980, two spacecraft, Pioneer 10 and Pioneer 11, were launched to explore Jupiter and Saturn. These two spacecraft were observed abnormal behavior in the acceleration stages. Their velocity decreased more than expected, which appeared to cause a constant acceleration towards sun for both of them [2]. In 1991, malfunctions occurred on a Japanese communications satellite, Superbird-A [3]. Following a wrong operation, the satellite fuel tank leaked and finally caused the satellite total loss, which induced a 1.5-million-dollar loss. In 2003, it was reported that Cisco 12000 line cards reset without expectation [4]. The system engineers found out that the line cards need 2-3 minutes to be recovered because of the digital logic error or ECC memory parity error.

. . . . . .

Engineers and researchers investigated the accidents or malfunctions mentioned above. The results indicated that SEEs were the root cause of these events. When exposed to radiation environments, semiconductor material may be ionized by energetic particles, and electron-hole pairs are created along the particle path in the semiconductor. If a semiconductor device absorbs these generated carriers, it will lead to current/voltage transients of the affected nodes. This is called a Single Event Transient (SET). If the transient is propagated into a sequential circuit unit such as a flip-flop or a memory cell, then a Single Event Upset (SEU) occurs. These kinds of effects can introduce errors into an electronic system, and cause significant costs to a company, or even an entire society.

Since the 1970s, it is reported that SEEs have impacted numerous spacecraft (Table 1.1). In recent years, with the growth of IC complexity, SEEs have become a serious problem not only for the electronics in radiation environments, but also for many ground-level applications as demonstrated by the aforementioned Cisco line card failures and other reported malfunctions.

**Table 1.1** Spacecraft for Which SEEs Have Had an Impact [3]

| For the Period                      | 1970-1982 |              |                       |

|-------------------------------------|-----------|--------------|-----------------------|

| DE-1                                | Galileo   | INSAT-1      | Intelsat - IV         |

| Landsat-D                           | LES 8     | LES 9        | Pioneer Venus         |

| SMM                                 | Tiros-N   | Voyager      |                       |

| For the Period                      | 1982_1990 |              |                       |

| AMTE/CCE                            | DSCS      | ERBS         | Galileo Lander        |

| GEOS-6                              | GEOS-7    | Geosat       | GPS 9521              |

| GPS 9783                            | GPS 9794  | HUT          | IUS                   |

| MOS-1                               | OPEN      | Shuttle      | SPOT-1                |

| TDRS-1                              | TDRS-4    | UOSAT-2      |                       |

|                                     |           |              |                       |

| For the Period                      | 1990–1997 |              |                       |

| COBEERS-1                           | ETS-V     | <b>ADEOS</b> |                       |

| (SEL)                               | (SEL)     |              |                       |

| EUVE                                | HST       | HST-STIS     | Kitsat-1              |

| NATO-3A                             | PoSAT-1   | S80/T        | SOHO                  |

| Spot-2                              | SPOT-3    | STS-61       | Superbird             |

| TDRS-5                              | TDRS-6    | TDRS-7       | Topex/Poseidon        |

| UoSAT-2                             | UoSAT-3   | UoSAT-5      | WIND                  |

| Yahkoh-BCS                          |           |              |                       |

| Amateur Radio Satellite Experiments |           |              |                       |

| AO-16                               | LO-19     | I0-26        | Spartan/OAST/SPRE     |

| 110 10                              | LO 17     | 10 20        | Sparani Orio 1/01 ICD |

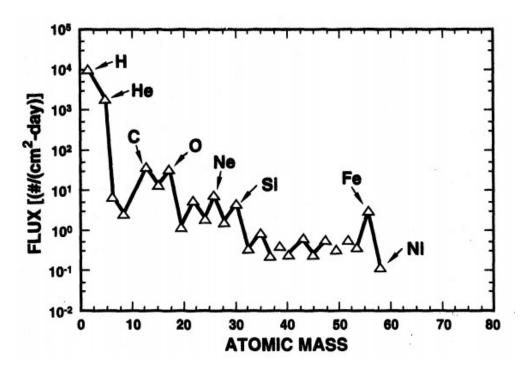

One of the major sources of high-energy particles that cause SEEs is cosmic rays that are mainly from the Sun and sources outside of the solar system (galactic cosmic rays, GCR). The major radiation particles in GCR are protons (85%), neutrons, alpha particles and heavy ions. As can be seen in Figure 1.1, the flux of H (proton) particles is more than two orders higher than the flux of heavy ions.

Figure 1.1 The Flux of GCR Particles [9]

Solar cosmic rays greatly depend on solar activity. A solar flare involves a very broad spectrum of emissions with typically a 1\*10<sup>20</sup> energy release [6, 7]. When a solar flare occurs, an excessive amount of protons, alpha particles and heavy ions are emitted by the Sun, and can last for several days to a week [6, 7]. These particles can arrive at Earth within tens of minutes. Normally, the particles emitted in a solar flare are mostly proton and alpha particles. Heavy ions contribute only a small portion, which is less significant compared to GCR. In a large solar flare, the proportion of heavy ions can reach up to 50% of the space background, and the number of alpha and proton particles can increase to thousands of times over the cosmic background [5] [6]. Figure 1.2 shows the Linear Energy Transfer (LET) spectrum variation in solar activities.

Figure 1.3 LET Spectra at Geosynchronous [6]

When semiconductor materials interact with the particles in cosmic rays, extra charges are generated and they can create SEEs.

Although comprising only a small portion of cosmic rays, heavy ions, such as Ne, Ar, Fe, Kr, can cause significant SEEs in electronics because they can deposit more energy in a material than lighter particles. When a single heavy ion passes through a semiconductor material, ions are deposited along its track. Most of the heavy ions in space are energetic enough to travel through a semiconductor device, leaving huge amount of ions on its track, which can potentially cause SEEs.

Protons are another source of SEEs. As shown in Figure 1.1, protons comprise the main portion of space rays (85% in GCR and more than 90% in solar rays). A proton is a subatomic particle with one positive electric charge. Although a proton is ionized, only a small amount of charge is

deposited into silicon materials along its track. In other words, its passage is not easy to produce SEEs. However, a small portion  $(1/10^5)$  of protons will have nuclear reactions with the atoms inside the silicon material, generating various secondary ion particels. These secondary particles can be energetic enough to produce SEEs. Because of the large number of protons in cosmic rays, they can trigger even more SEEs than heavy ions in space electronics.

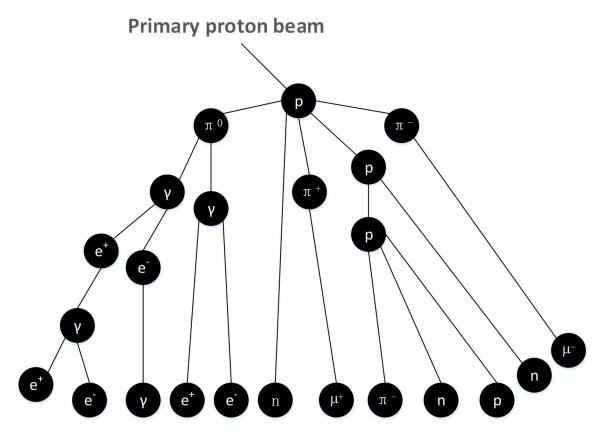

Neutrons were discovered in the 1930s. They are subatomic particles with no electric charge. Consequently, they do not react with semiconductor materials to generate electron-hole pairs directly. Nuclear reaction is their only way to generate SEEs. When a neutron collides into a nucleus in the material, secondary charged particles may be generated, and then cause SEEs. When cosmic rays enter the atmosphere, the primary particles react on average 12 times with molecules in the air before reaching ground level, a phenomenon called an air shower [8]. As shown in Figure 1.3, neutrons along with muons and pions are generated in an air shower. Recent work has revealed that the generated neutrons and the thermal (low energy) neutrons can be the main sources of SEEs at ground level [10-15]. This imposes significant challenges to ground-level commercial electronic systems for reliable operations, especially for small feature-size silicon technologies.

Figure 1.5 Air shower [8]

## **Primary proton beam**

An alpha particle is equal to a helium nucleus with no electron. With two protons in its atomic nucleus, an alpha particle has two positive electric charges. Consequently, alpha particles can also generate extra charges when interacting with semiconductor materials. Alpha particles comprise 14% of cosmic rays, which can cause errors in space-borne circuits [7]. On the ground level, neutron nuclear reactions in silicon can also generate alpha particles as a by-product. Moreover, some IC packaging materials can also emit alpha particles, which may result in SEEs in digital systems.

#### 1.2 Motivation

To reduce SEEs and increase system reliability, researchers have proposed numerous methods, circuit structures and technologies in the past thirty years. Recent research has proved that Fully Depleted Silicon On Insulator (FDSOI) technologies are more reliable than their bulk competitors in harsh radiation environments, since their charge collection volume is extremely small [16-24]. It is reported that the soft error rate of the SRAM chip based on ST 28nm UTBB-FDSOI is two orders lower than a similar 28nm bulk technology [25, 26]. Moreover, FDSOI technologies are virtually immune to a Single Event Latchup (SEL), which could be destructive event, causing a direct current path between power and ground in an IC. Because of these merits, FDSOI is a good option for applications in high-radiation environments, such as space applications.

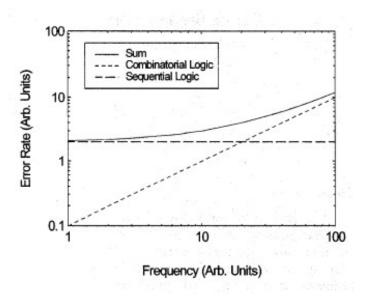

FDSOI technologies are attractive due to their high-speed and low-power features, and their applications are well suited to high-clock frequency systems. However, when clock frequency increases, transient errors from combinational logic circuits may become dominant. In [27], it was predicted that the soft error rate (SER) caused by SETs from combinational logic circuits would increase linearly with the clock frequency, while the SER induced by SEUs from sequential logic circuits generally remains the same. As a result, at a certain frequency point, SETs would outstrip

**Figure 1.7** Error Rate as a Function of Frequency for Combinational and Sequential Logic Elements as well as their Sum [27]

SEUs and become the major source of soft errors. Therefor, for high-speed applications, more attention should be paid to the investigation of SET characterization and mitigation methods.

For FDSOI technologies, Total Ionizing Dose (TID) effects also need to be investigated. Because of the additional oxide layer between the body and substrate, FDSOI is expected to be more sensitive to TID. In a space environment, TID effects are another major source that cause device failure. Since the TID effects impact on the transistor electrical characteristics, the transistor threshold voltage will be influenced as well. As a result, the TID effects will influence the operating clock frequency of the devices. Moreover, the cumulative yield charge in the insulator lays will increase the leakage current and power consumption of the devices.

Currently, some research works focusing on nano-scale FDSOI technologies have been performed to evaluate the radiation effects on them. The studies of TID effects on single transistors have been performed to measure their leakage currents and threshold voltages [28]. The SEU effects on flip-flops and latches were also evaluated with various irradiation sources [29-32]. Based on the SEU evaluation results, some hardened flip-flop designs based on different techniques have been proposed [33, 34]. Back-gate voltage effect research was also performed [35]. However, all of the works mentioned above did not focus on the high-speed applications of the 28nm FDSOI technologies. Due to the increase of clock frequency, SETs could become the dominant soft error source, it is important to evaluate the SET effects for high-speed applications. Moreover, how the TID influences the circuit speed is also crucial. In this dissertation, the research is mainly focused on the SET and circuit-level TID investigations. The research objectives of the thesis are defined as follows:

- 1. Investigate and evaluate different types of on-chip SET pulse measurement circuits;

- 2. Measure the SET pulse width in various standard cell logic gates with 28nm FDSOI technology;

- 3. Evaluate the approximate logic soft error mitigation method using an ARM Cortex-M0 processor fabricated with ST 28nm UTBB-FDSOI technology;

- 4. Study the TID tolerance of ST 28nm UTBB-FDSOI technology.

To carry out the radiation effects investigation mentioned above, two test chips were designed and implemented, using ST 28nm UTBB-FDSOI technology. The first chip (ST1) focuses on the SET measurement. There are 96 combinational logic chains for the SET capture and three kinds of pulse-width measurement circuits in the chip. There is also one CREST chain with parallel

combinational logic between each stage, in order to research the relationship between the SER and the clock frequency. The second chip (AR0) is designed mainly for the SET mitigation research. There are five ARM Cortex-M0 processors implemented in the chip. All of these five cores have identical functionality; however, they have different SET-tolerant levels. By comparing the SER in the irradiation experiments, we can evaluate the performance of mitigation methods.

### 1.3 Thesis Organization

This thesis is organized as follows:

Chapter 1 briefly introduces radiation environments. Some of the incidents potentially caused by SEEs are listed to emphasize the influence of radiation in different electronic systems. The space radiation beam sources, solar rays and GCR, and the composition are described briefly. Then, there is a demonstration of the motivation for the project, emphasizing the significance of SET investigation in modern technologies.

Chapter 2 illustrates the basic SEE mechanisms. Three types of single event effects, Single Event Upset, Single Event Transient and Single Event Latchup are introduced in this chapter. The chapter also gives an overview of ST UTBB-FDSOI technology, showing the reason for a low Soft Error Rate. The photon effects in the semiconductor materials are also demonstrated to show that pulsed laser is a useful method for SEE research.

Chapter 3 presents the SET pulse measurement chip that was designed at the University of Saskatchewan. The top-level specification, infrastructure circuits, SET detectors, test chains and circuit layout are described, showing that this chip can be used to investigate various single event effects.

Chapter 4 first compares the SPICE simulation results of the different SET detector responses with different pulse inputs. Then, the PVT corner simulation results are used to illustrate the significance of the calibration ring-oscillators (ROs). The chapter also discusses how the pulse broadening and narrowing effects inside the delay chains of the detectors can be a risk in measurement accuracy. Chapter 4 also provides radiation test results on the ST1 chip. In the heavy-ion test, OR2X8 chains were observed to be more sensitive than other circuits. A laser test was performed to investigate the reason. Then the chapter discusses the influence of transistor

mismatch on pulse distortion effects, using the SPICE simulation result. The TID test results (both at the University of Saskatchewan and at the European Space Agency) are also introduced in this section. Finally, the laser test results at the Naval Research Lab are attached to prove the pulse broadening effect in the OR2X8 chains. The SET soft error rate vs. clock frequency is also investigated.

Chapter 5 investigates the second chip, AR0, designed in this project. The AR0 chip includes five ARM cores with different level of circuit protection. The details of the chip are discussed, including the peripheral circuits, the control logic, the support instruction, the operating frequencies, the logic protection method and the test schemes. The fault injection simulation result is also shown to prove the performance of the approximate logic protection method.

The whole work has been summarized in chapter 6, which also outlines the future research work in this project.

## **Chapter 2: BACKGROUND INFORMATION**

## 2.1 Single Event Effects

### 2.1.1 Charge Deposition and Collection

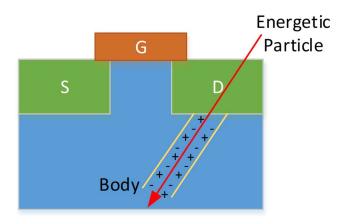

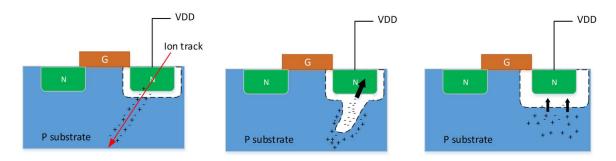

As introduced in the first chapter, various kinds of energetic particles can cause SEEs. However, the basic mechanism in SEEs generation is quite similar, among which charge deposition and charge collection play key roles [35-40]. When an energetic particle travels through a semiconductor material, extra electron and hole pairs are generated along the particle track (Figure 2.1). There are two ways an energetic particle generates charges in semiconductor materials, namely direct ionization and indirect ionization [41-43].

Figure 2.1 Charge Track in MOS Device [3]

If the incidence particle, such as a heavy ion has a charge, when passing through the material, it can generate extra charge pairs while losing its energy. Before it loses all its energy and stops, it will release the charge pairs within a range of area along its track. Heavy ions deposit their energy in the material and generate SEEs mainly in this way.

Light particles normally cannot generate enough charge to produce SEEs directly. However, they can still induce SEEs in devices through indirect ionization [44, 45]. When an energetic particle such as a proton or neutron, travels through semiconductor material, it may have either an elastic

or inelastic collision with a semiconductor nucleus. The nuclear reactions may generate secondary charged particles, which can generate charge along their tracks.

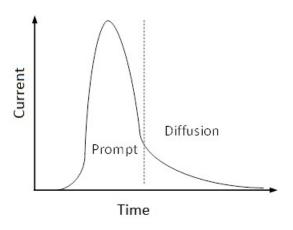

If the generated electron-hole pairs concentrate near a node, which has high electric field, the extra charges will drift towards the electric field and get absorbed efficiently. With the separation of the electrons and holes, a current turbulence can be observed at the node. There are two phases in the generated current spike: a sharp leading edge which can last in the scale of tens of picoseconds, and a tailing edge that can last hundreds of nanoseconds or even longer [3]. The first part, the leading edge, occurs because of the charge that is collected at the original depletion area and the funnel region. The delayed part is due to the charge collection from the diffusion area in the silicon body. Figure 2.2 shows the charge deposition and collection flow when a particle strikes at the inversed PN junction. Figure 2.3 shows the current spike waveform.

Figure 2.2 Charge Deposition and Collection Flow [41]

Figure 2.3 Current Pulse in an Inversed PN junction [41]

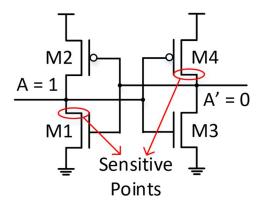

## 2.1.2 Single Event Upset

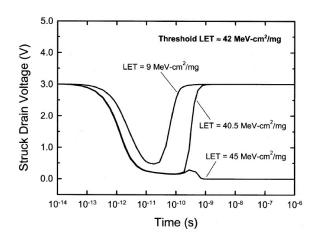

The current spike at an inversed PN junction may cause voltage fluctuation at the electrode. If the energy of the striking particle is large enough, the voltage at the node may be flipped in a short time, which means a voltage pulse is generated.

When the radiation-induced pulse occurs in a digital storage cell, such as a flip-flop or an SRAM cell, the stored value can be flipped by the particle hit, which is called Single Event Upset (SEU). Figure 2.4 shows two back-to-back invertors, which are the basic element of the storage structure in SRAMs and latches. As discussed above, the inversed PN junctions can effectively collect the extra charge when hit by a particle. As a result, the drain nodes of transistors M1 and M4 are the sensitive nodes, which are susceptible to SEEs. If an ion strikes at either of these nodes, a transient voltage pulse can be generated due to the current spike. With the increase of the ion LET, the voltage pulse is larger. If the pulse is wide enough, it will flip the signal level in the invertor loop, and cause an upset in the storage cell (shown in Figure 2.5).

Figure 2.4 Back-to-back Invertor Sensitive Points [3]

Figure 2.5 Transient Pulses with Different LET Ion Strike in a SRAM Cell [3]

#### 2.1.3 Single Event Transient

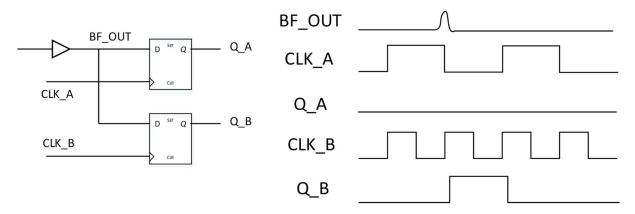

Different from an SEU, which happens in a sequential cell, a Single Event Transient (SET) is the single event effect related to the combinational circuits in a digital system. Since the combinational logic itself cannot store a value, if a transient is not captured by a flip-flop or latch in later stage, it will not influence the system functionality. Consequently, the soft error rate caused by SETs is a function of the clock speed and other factors. Figure 2.6 shows a simple example of how the clock frequency influences the SET soft error rate. When an ion strikes the buffer in Figure 2.6, it generates a transient pulse at the output, BF\_OUT. Then the pulse propagates to two flip-flops which belong to different clock domains. Since the frequency of CLK\_B is twice the frequency of CLK\_A, flip-flop B has more possibility to capture the transient pulse. If an SET pulse is caught by a flip-flop, the wrong output may impact on the functionality of the circuit or even the whole digital system. Moreover, if an SET happens in the system clock tree, it will generate an extra clock edge, which will scramble the sequential logic and cause a system failure.

Figure 2.6 Clock Frequency Influence on SET Soft Error Rate

#### 2.1.4 Single Event Multiple Transient and Multiple Bits Upset

Recently, with the evolution of technologies, ICs have been reported as more susceptible to radiation particles. The explanation for this phenomenon is multiple cells (combinational or sequential) are influenced due to multiple node charge collection. Because of the downscale of modern technologies, the electron-hole pairs generated by an incident particle are collected by the striking node as well as the adjacent nodes. This effect is known as multiple node charge collection or charge sharing. If the ion is energetic enough to generate charges which can flip the striking node and the nearby nodes, multiple transients may happen in the circuits, an occurrence which is call Single Event Multiple Transient (SEMT). When the transients cause more than one bit upset in a memory or storage array circuits, multiple bits upset (MBU) happens [46]. Observing SEMTs was also an initial purpose in an earlier project (chapter 3).

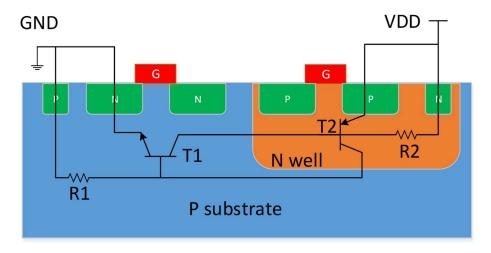

## 2.1.5 Single Event Latchup

In 1979, another single event effect called Single Event Latchup was reported in [47]. In modern CMOS technologies, PMOS devices are fabricated in the n-well and share the same substrate with the NMOS transistors. As shown in Figure 2.7, there are two parasitic transistors in a CMOS device. The n-type active area, the p-substrate and the n-well construct a parasitic NPN transistor (T1), and the p active area, the n-well and the p-substrate form a lateral PNP transistor (T2). The p-substrate and the n-well also have their equivalent resistors in this structure (R1 and R2 in Figure

2.7). When a current spark occurs in the p-sub, the NPN transistor will open, and the current in the n-well transistor (R2) will be enlarged, which can increase the IR drop in the n-well. When the voltage drop in R2 is high enough to turn on the T1 NPN transistor, there is a direct path from power to ground, which can cause the latchup effect in the device.

Figure 2.7 Parasitic Structure in a CMOS Device [48]

Different from the SEEs discussed above, the SEL may result in a hard error since there is a short path between VDD and GND. The large current may damage the device if no proper protection is in place.

## 2.2 SEE Test Methodologies

Since SEEs can impact system reliability, various kinds of irradiation tests have been introduced to investigate the SEE influence on ICs. The ideal test method is to launch the digital systems into space to perform the testing, but it is very costly and time consuming. Thus, ground-level accelerated irradiation experiments are usually adopted.

#### 2.2.1 Particle Tests

To imitate the irradiative environments, such as in space or in a nuclear power plant, particle accelerators are used for particle tests. There are many particle accelerator facilities around the world which can be used for SEE experiments. The 88-Inch Cyclotron facility in the Lawrence

Berkeley National Lab (LBNL) can provide both heavy-ion and light-ion particle beams. It can provide four standard ion cocktails with 4.5, 10, 16 and 30 MeV/nucleon. The Radiation Effects Facility (RADEF) is located at the University of Jyväskylä, Finland (JYFL). RADEF provides proton and heavy-ion beam lines in the same cave and the electron beam from a linear accelerator. TRIUMF is an accelerator-based research center in Canada for energetic particle and nuclear science study [49]. The 500 MeV cyclotron facility can provide four proton beam lines with an energy range from 20 to 500 MeV [50, 51]. Thermal (low-energy) and high-energy neutron tests can also be performed at TRIUMF.

#### 2.2.2 Pulsed Laser Test

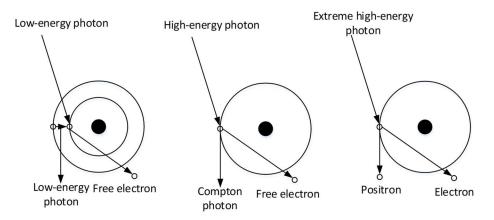

A laser can also be used for SEE investigation because of the charge generation by the photon effects. There are three kinds of the photon effects: the photoelectric effect, the Compton effect and pair production [52].

The photoelectric effect is related to low-energy photons. When a low-energy photon interacts with an atom in semiconductor materials, it will free an inner electron from the atom by losing all its energy. It produces an ionized atom and a free electron. When the electron in an outer shell falls into the inner orbit, a low-energy photon is generated.

When a high-energy photon strikes semiconductor materials, it frees charges through the Compton effect, which is also known as the Compton scattering. When a photon has a collision with the target atom, the photon transfers part of its energy to free an electron from the atom and also generates a low-energy photon.

A pair production is generated by an extremely high-energy photon. The photon hits a target atom, generating an electron-positron pair. A positron is similar to an electron but it has an opposite polarity of charge.

Figure 2.8 Photon Effects [7]

Because of the cost and the ease of access, the pulsed laser test is widely used in single event effects research [53-60]. Compared to the ion or proton test, the pulsed laser test is much simpler. A laser pulse with around 1 um diameter is focused or scanned on a device, and the laser energy is increased to test the relationship between the soft error rate and the pulse energy.

There are two main types of pulsed lasers: Single Photon Absorption Laser (SPA) and Two Photon Absorption Laser (TPA). The wavelength of SPA is relatively short, which makes it difficult to penetrate the silicon and reach the active area. Therefore, TPA is preferable in modern laser test methodology.

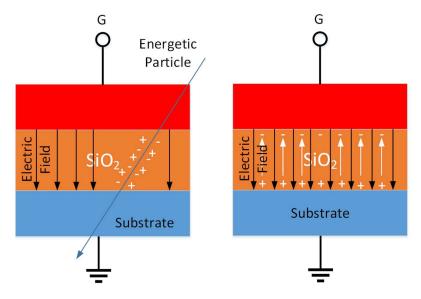

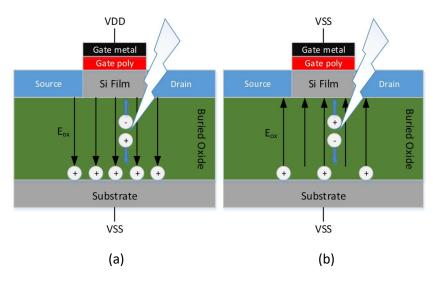

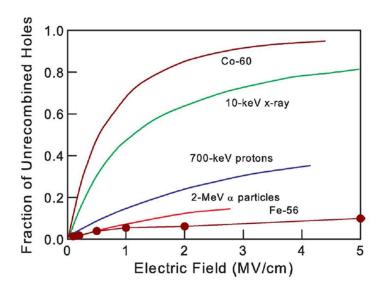

## 2.3 Total Ionizing Dose

The total ionizing dose effect [61-68] is the degradation that is caused by large number of highenergy particles over a long period expose. In the irradiative environment, the TID effect can potentially cause a device hard failure. When exposing a device to a radiation beam, the energetic particles can generate charged pairs in the SiO<sub>2</sub> layer when depositing enough energy to free electrons from semiconductor nucleus. If the generated electron-hole pairs get trapped at the Si-SiO<sub>2</sub> interface, they will form an electric field inside the SiO<sub>2</sub> layer, which can gradually degrade the electric character of the device. Figure 2.9 shows this process. When a high-energy particle travels through the SiO<sub>2</sub> layer, it will generate charged pairs along its track. The charge density depends on the irradiation type. After the initial recombination, the un-recombined charges are pulsed to the material interface by the electric field. These charges may be trapped at the Si-SiO2 interfaces and form a reversed electric field. With the accumulation of the trapped charges, the generated electric field can finally degrade the electric characteristics of the device.

Figure 2.9 Charge Injection Process in SiO<sub>2</sub>

The accumulative charges can result in a decrease of the NMOS threshold voltage and an increase of the PMOS threshold voltage, which means the transistor becomes slower and the gate delay gets higher. In addition, the transistor leakage current can be enlarged when it is in the off state. In the extreme case, the PMOS can be off permanently in the nominal operation voltage, which will result in the malfunction of the circuits.

In modern technologies, the gate oxide layer is down to nanometer scale, which can effectively relieve the TID effects [33]. However, in SOI technologies, except for the gate oxide and the Shallow trench isolation (STI), there is an additional isolation layer (Buried Oxide) between the substrate and body, which makes the TID analysis of SOI devices much more complex.

## 2.4 UTBB-FDSOI Technology

In the 1960s, Silicon-On-Insulator technologies were developed for military and space [16], [35]. Compared to bulk technologies, SOI technologies have an additional dielectric isolation between the substrate and the silicon body, which can prevent latchup by totally separating the transistors. Initially, SOI technologies were less attractive because of the introduction of a series of parasitic

structures. Since the 1990s, because of the significant improvement in SOI wafer quality, they have become widely used, especially in hard irradiation environment applications.

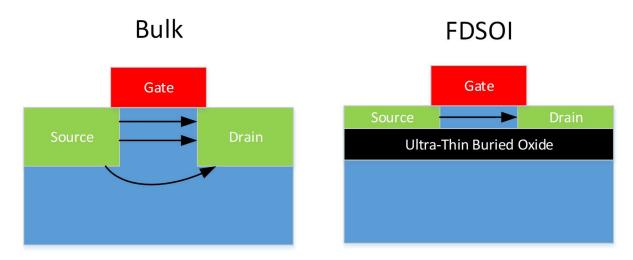

The Fully Depleted Silicon-On-Insulator (FDSOI) is an innovative technology based on the planner process. There are mainly two innovative technics in state-of-the-art FDSOI technologies. The first innovation is a very thin insulator layer, which is also known as buried oxide, positioned between the base silicon and the active area. Secondly, the transistor channel is implemented by a super-thin silicon film. Ultra-Thin Body and Buried Oxide (UTBB) Fully Depleted SOI (FDSOI) technologies are known as a combination of these two innovations together.

Compared to its bulk competitor, FDSOI technologies have much better transistor electrostatic

Figure 2.10 FDSOI Cross Section [16]

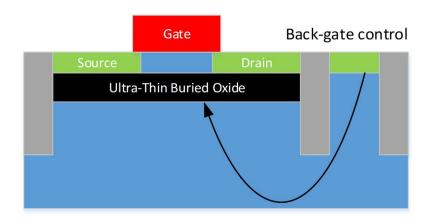

characteristics. Because the buried oxide lowers the parasitic between the source and the drain, the transistor switching speed increases and the leakage current decreases dramatically. Also thanks to the ultra-thin insulator layer, back-gate biasing voltage can transmit more efficiently than in bulk technologies, which makes it possible to control the transistor by polarizing the substrate. In other words, the transistor performance can be controlled dynamically through adjusting the back-gate voltage.

Figure 2.11 FDSOI Back-gate Control [82]

# **Chapter 3: SET Pulse Measurement Chip (ST1)**

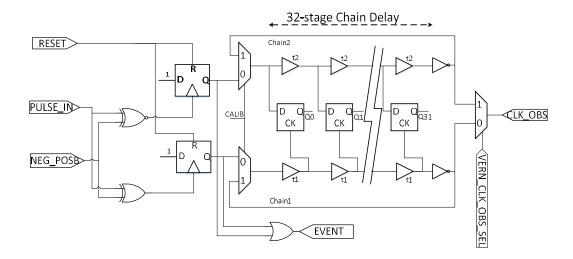

The first test chip was designed to study Single Event Transient (SET) pulse characterization. When researching the SEUs, we focus mostly on the cross-section, in other words, error rate vs. irradiation beam fluence. However, in the SET research, besides the error rate, the pulse width distribution is also an area of interest.

Generally, there are two methods for doing the pulse measurement: on-chip and off-chip. Considering the SET pulse width is at the magnitude of picosecond, a precise off-chip measurement is hard to implement. As a result, the on-chip measure circuits were implemented in the ST1 chip.

Three kinds of the SET pulse detectors were implemented: a Pulse Capture detector, a Vernier detector and a Pulse Filter detector. To study SET event rate vs. clock frequency, a high-speed CREST chain with 4096 stages was also implemented in the ST1 chip. In this chip, there are also four types of Ring Oscillators (ROs) which can be used to study TID effects. The ST1 test chip focuses on SET characterization research. The research result can be used to estimate the influence of SETs in actual complex digital circuits. Moreover, the appropriate mitigation method can use the ST1 chip radiation test result as a reference.

# 3.1 Top-Level Specification

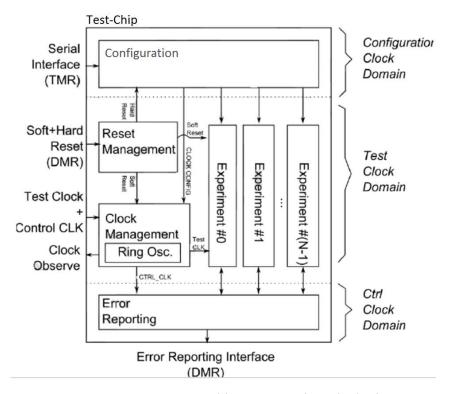

A top-level diagram of the test chip is shown in Fig. 3.1. The main part of the test chip consists of 96 experiment circuits for measuring transients. In addition to the experiments, there is a common infrastructure which is used for configuration, for reset and clock management, and for error reporting.

There are three main clock regions in the chip. The configuration logic consists of shift registers that are clocked through the external serial input interface and designed to operate at low speed (nominally 10MHz). The logic for the experiments is driven by the test clock which is created by

the clock generation module. Finally, there is a control clock (nominally 10MHz) which is used to control the logic for error reporting (Table 3.1).

Figure 3.1 SET Test-Chip Top-Level Logical View

Table 3.1 ST1 Test Chip Pinout

| Pin Name              | Direction  | Туре                | Description                            |

|-----------------------|------------|---------------------|----------------------------------------|

|                       | Configur   | ation Interface (8  | Signals)                               |

| CONF_CLK              | IN – CLK   | 1.8V CMOS           | Configuration CLK                      |

| CONF_DIN              | IN         | 1.8V CMOS           | Configuration Data                     |

| CONF_EN               | IN         | 1.8V CMOS           | Configuration Enable                   |

| CONF_XFER_A           | IN         | 1.8V CMOS           | DMR – Transfer Enable (shift ->        |

| CONF_XFER_B           | IN         | 1.8V CMOS           | in)                                    |

| CONF_DOUT             | OUT        | 1.8V CMOS           | Configuration Data Output (debug)      |

| CONF_IN_OK            | OUT        | 1.8V CMOS           | Configuration In Parity Check          |

| CONF_LIVE_OK          | OUT        | 1.8V CMOS           | Configuration Live Parity Check        |

|                       | Clock      | and Reset (5 Sign   | als)                                   |

| TEST_CLK_IN           | IN – CLK   | 1.8V CMOS           | CREST Test CLK                         |

| CTRL_CLK_IN           | IN – CLK   | 1.8V CMOS           | Control Circuitry CLK                  |

| CLK_OBS_OUT           | OUT        | 1.8V CMOS           | Clock Observation Signal               |

| RESET_A               | IN         | 1.8V CMOS           | DMR – Global Reset                     |

| RESET_B               | IN         | 1.8V CMOS           | DIVIN – Global Neset                   |

|                       | Error Repo | rting Interface (17 | 7 Signals)                             |

| ERR_VLD_A             | OUT        | 1.8V CMOS           | DMR – Error Valid Indication           |

| ERR_VLD_B             | OUT        | 1.8V CMOS           | Divin Error valid maleación            |

| SEL_NUM_DAT           | IN         | 1.8V CMOS           | Choose NUM or DAT Output               |

| ERR_ACK               | IN         | 1.8V CMOS           | Error report acknowledge               |

| ERR_NUM_DAT [7]       | OUT        | 1.8V CMOS           |                                        |

| ERR_NUM_DAT [6]       | OUT        | 1.8V CMOS           |                                        |

| ERR_NUM_DAT [5]       | OUT        | 1.8V CMOS           | Either the Current Event               |

| ERR_NUM_DAT [4]       | OUT        | 1.8V CMOS           | Reporting Test Number or the           |

| ERR_NUM_DAT [3]       | OUT        | 1.8V CMOS           | Reported Data for a selected           |

| ERR_NUM_DAT [2]       | OUT        | 1.8V CMOS           | sensor                                 |

| ERR_NUM_DAT [1]       | OUT        | 1.8V CMOS           |                                        |

| ERR_NUM_DAT [0]       | OUT        | 1.8V CMOS           |                                        |

| ERR_DAT_SEL [2]       | IN         | 1.8V CMOS           | Signals to Select Error Data (if it    |

| ERR_DAT_SEL [1]       | IN         | 1.8V CMOS           | is more than 8 bits)                   |

| ERR_DAT_SEL [0]       | IN         | 1.8V CMOS           |                                        |

| ERR_CLR_A             | IN         | 1.8V CMOS           | DMR – Clears the Current Error         |

| ERR_CLR_B             | IN         | 1.8V CMOS           |                                        |

|                       | Ana        | alog Power (2 Pin   | T                                      |

| VDD <sub>analog</sub> | IN         | 0.6V - 1V           | Power for Variable Voltage SET Sensors |

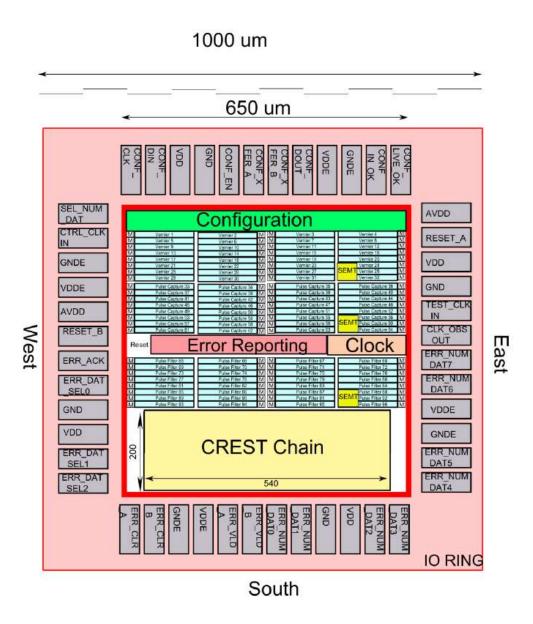

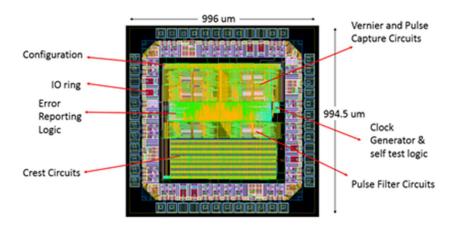

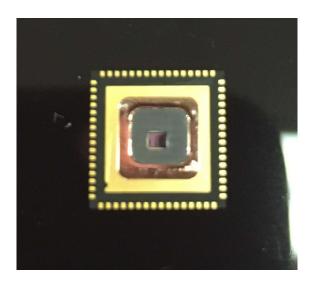

An approximate floorplan of the SET test chip is shown in Figure 3.2.

Figure 3.2 ST1 Test Chip Floor Plan

# 3.2 Configuration Interface

Many aspects of the test chip require configuration. For example, the clocking modes are configurable and some of the sensors have modes which can be enabled. The configuration is input to the chip using a serial shift interface. All the input signals on this interface are TMR and the

interface is designed so that the device can be reconfigured during radiation. However, normally the radiation would be stopped during reconfiguration.

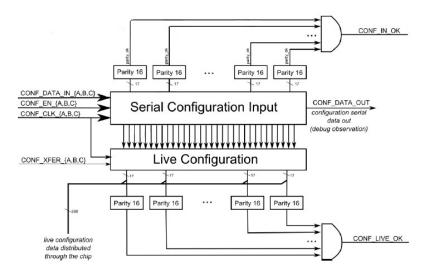

The configuration interface is clocked using an independent TMR serial clock (CONF\_CLK\_{A, B, C}) and can thus function in the absence of other clocks. In total, there are 192 bits of configuration data. Internally every 16 bits of configuration data is protected with an odd parity bit (16D+1P). The parity of the configuration data is continuously checked (18 groups of 16+1 bits). The outputs of the 12-parity checkers are ANDed together, and this is made available on a primary output, providing an indication that the configuration data is stored correctly. A high-level view of the configuration interface is shown in Figure 3.3.

Figure 3.3 High-level View of Configuration Interface

In order to enable live reconfiguration, two copies of the configuration data are stored. One copy is shifted in serially (Serial Configuration Input) and the other, the live configuration, is distributed in the chip. The live configuration can be updated when CONF\_XFER\_{A, B, C} are asserted on a rising edge of the configuration clocks. In this way, the full configuration data can be updated automatically. The live configuration is unaffected during the time the new configuration is being shifted in.

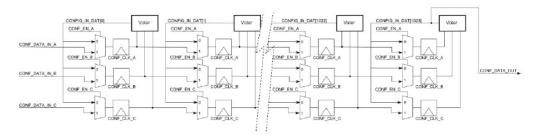

The detailed structure of the serial input configuration interface is shown in Figure 3.4. The clock and the data input are independent for each of the TMR chains (A, B, C). When CONF\_EN\_{A, B, C} is asserted (1), the input data (CONF\_DATA\_IN\_{A, B, C}) is shifted into the chains on

the rising edge of the configuration clock (CONF\_CLK\_{A, B, C}). When CONF\_EN\_{A, B, C} is de-asserted (0), then the contents of each stage is recirculated through a TMR voter.

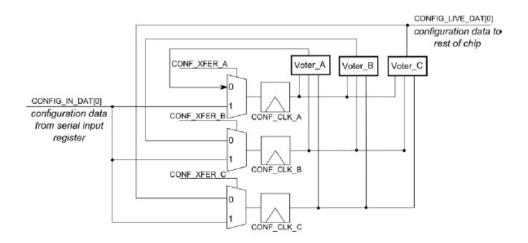

Figure 3.4 TMR Input Configuration Shift Register

The live copy of the configuration data is loaded in parallel from the input shift register. This transfer occurs on a rising clock edge (CONF\_CLK\_{A, B, C}) when CONF\_XFER\_{A, B, C} are asserted. When CONF\_XFER\_{A, B, C} are not asserted, the configuration is recirculated. Separate voters are used for recirculating the configuration for each copy (A, B, C). In this way, an error in the voter does not cause the configuration to be permanently corrupted. One of the voter outputs (C – chosen arbitrarily) drives the actual configuration data to the rest of the chip. The live configuration storage chain is illustrated in Figure 3.5.

Figure 3.5 TMR Input Configuration Shift Register

# 3.3 On-Chip Clock Generation

# 3.3.1 Clock Generation logic

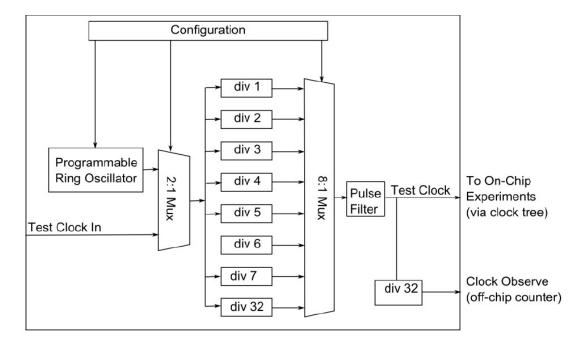

Many of the experiments on the chip require a test clock and, in most cases, it is necessary to vary the frequency of the test clock. A Phase-Lock Loop (PLL) is not available for this design, and there are limits on the bandwidth through the pads. For this reason, there is the option to generate an on-chip clock using a programmable Ring Oscillator (RO). An overview of the clock generation circuitry is shown in Figure 3.6.

Two techniques are used to reduce the sensitivity of the clock generation circuitry to radiation effects. The first is the use of the largest possible invertors in the Ring Oscillator (RO). Using larger cells in the RO has two main advantages. First, larger cells are less sensitive to transients. Second, larger cells have a higher inertial delay and will filter transients. This filtering effect greatly reduces the probability that the ring oscillator will start to oscillate at a harmonic frequency due to a transient.

Figure 3.6 High-level View of Clock Generator

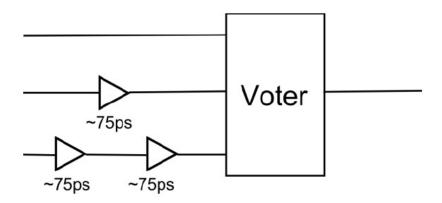

The second SEE mitigation technique is the Pulse Filter placed at the output of the clock generation circuitry. This filter must block both positive and negative transients and this is achieved with the circuit shown in Figure 3.7.

Figure 3.7 Pulse Filter for Clock Generator

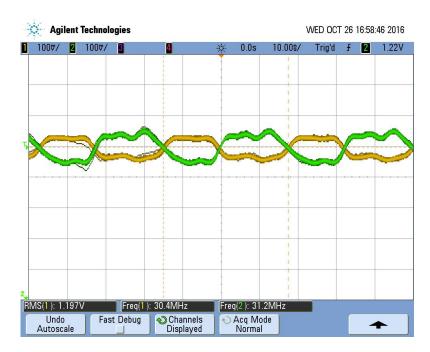

The clock for the experiments either comes from the external test clock (Test Clock In) or is generated from the programmable RO, and this is controlled by the configuration bit EXT\_CLK\_SEL. In either case, it can be selectively divided by either 1, 2, 3, 4, 5, 6, 7, or 32. The selection of divisors is chosen to give the broadest range for the resulting frequencies, and this is controlled by the configuration bits DIV\_SEL[2:0]. The division-by-32 option is provided as a contingency in case it is necessary to run the circuits at very low frequencies. For the CREST experiments, when the chain is clocked with the division-by-32 clock, the frequency will be so low that effectively only the SEU component will be measured. In all cases, a divided version of the selected test clock is made available on a dedicated output pin (clock observation). During operation, this is sent to a counter in the off-chip FPGA tester and is used to measure the frequency of the test chip.

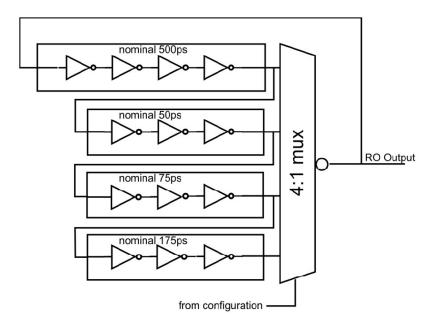

Figure 3.8 Programmable Ring Oscillator

The design of the programmable RO is shown Figure 3.8. There is an initial chain with a nominal delay of 500ps (2GHz frequency). Then, through a 4:1 mux, additional delay can be added in increments of 50ps, 75ps and 175ps, and this selection is made by the control bits RO\_SEL. Taken together, the programmable RO and the programmable divider make it possible to generate a wide range of frequencies for the on-chip test clock, as shown in Table 3.2.

Table 3.2 Available On-Chip Clock Frequencies

| RO    | RO    | DIV 1 | DIV 2 | DIV 3 | DIV 4 | DIV 5 | DIV 6 | DIV 7 | DIV 32 |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|--------|

| Delay | Freq  | (MHz)  |

| (ps)  | (MHz) | , ,   | , ,   | , ,   | , ,   | , ,   | , ,   | , ,   | , ,    |

| 500   | 2000  | 2000  | 1000  | 667   | 500   | 400   | 333   | 286   | 63     |

| 550   | 1818  | 1818  | 909   | 606   | 454   | 364   | 303   | 260   | 57     |

| 625   | 1600  | 1600  | 800   | 533   | 400   | 320   | 267   | 229   | 50     |

| 800   | 1250  | 1250  | 625   | 417   | 313   | 250   | 208   | 179   | 39     |

# 3.3.2 Clock Observation Circuitry

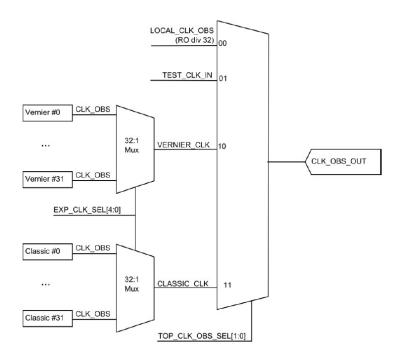

Figure 3.9 Clock Observation Muxing

For debugging and calibration purposes, the on-chip clocks can be observed on the output pin CLK\_OBS\_OUT. The clock that is output on this pin can come from one of four sources, selected by TOP\_CLK\_OBS\_SEL configuration bits:

- 1. the clock from the local ring-oscillator (divided by 32);

- 2. the externally provided clock (TEST CLK IN);

- 3. the clock from one of the selected Vernier detectors (selected by EXP CLK SEL[4:0]);

- 4. the clock from one of the selected classic detectors (selected by EXP CLK SEL[4:0]).

The clock observation muxing hierarchy is shown in Figure 3.9.

# 3.4 Error Reporting Interface

When an error is detected in the test chip, it is reported to the tester through the error reporting interface. The chip is designed such that all the experiments are active in parallel. When any one

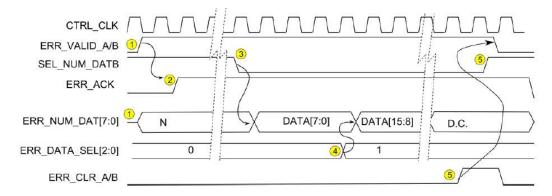

of them detects an error, the error number (N) is reported on the error reporting interface. Figure 3.10 shows the timing diagram for an error reporting event from the test chip to the tester.

Figure 3.10 Timing Diagram for Error Reporting Event

Most of the control signals are duplicated (DMR) to enable the detection of erroneous transactions. In the figure, the replicated signals (A/B) are only shown once. When an error occurs, the first step (1) is that the test chip signals the error to the tester by asserting ERR\_VALID\_A/B and by indicating the error number on the ERR\_NUM\_DAT[7:0] bus.

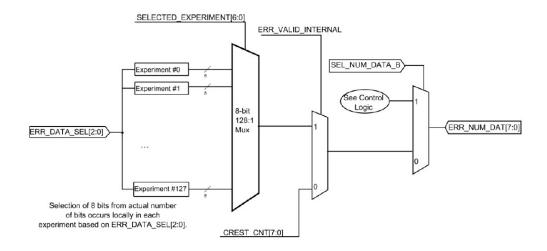

Note that the ERR\_NUM\_DAT[7:0] bus is multiplexed to perform two functions. If SEL\_NUMDATB is 1, then the current error number is output on the bus. If SEL\_NUM\_DATB is 0, then the bus (ERR\_NUM\_DAT[7:0]) outputs eight bits of data from the currently selected experiment. By default (e.g., in the absence of an error), the tester drives the SEL\_NUM\_DATB to 1 so that the error number is output.

After the tester observes an error (based on ERR\_VALID\_A/B), it acknowledges the error (2) by asserting ERR\_ACK. This has the effect of locking the error number (N), so that it will no longer change. At this point, the tester records the error number and is now ready to access the data associated with that error.

To do this, the tester de-asserts SEL\_NUM\_DATB in order to start reading the data from the experiment. Each experiment can output up to 40 bits of data. The data is multiplexed, 8 bits at a time, onto the ERR\_NUM\_DAT[7:0] bus. The selection of which 8 of the 40 bits is output comes from ERR\_DATA\_SEL[2:0]. After the tester has read the first byte of data, it can select the subsequent bytes, by updating ERR\_DATA\_SEL[2:0], as shown in step (4).

Finally, in step (5), when the last piece of data has been read, the tester clears the error by asserting ERR\_ACK\_A/B. This causes ERR\_VALID\_A/B to be de-asserted (assuming no other errors are present). The tester should also clear SEL\_NUM\_DATB, so that when the next error occurs, the error number can be recorded. At this point, the test chip is ready to process the next error.

It is, of course, possible that a second experiment may record an error before the previous error has been processed. In this case, the second error is recorded by the tester after the first error has been fully logged. In this situation, after ERR\_CLR\_A/B is pulsed, instead of ERR\_VALID\_A/B being cleared, it would stay asserted. In this case, a new error number then would appear on ERR\_NUM\_DAT[7:0], and it would be processed in the same way.

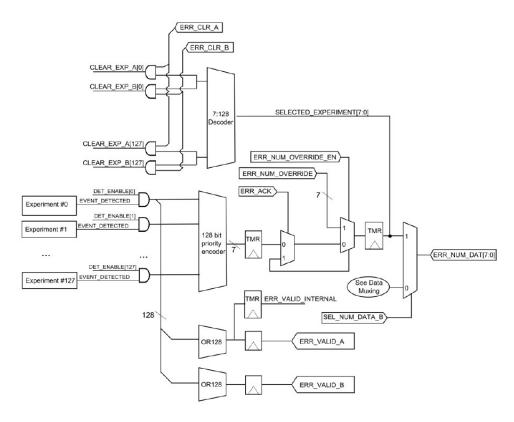

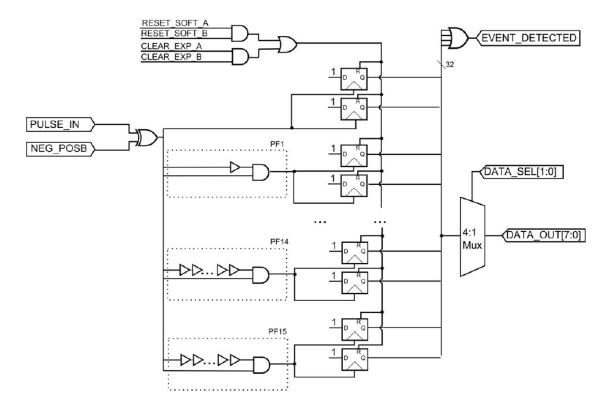

The circuit diagram of the main portion of the error reporting logic is shown in Figure 3.11. On the left of this figure, we can see that each experiment outputs a signal, "EVENT\_DETECTED", indicating whether it has detected an error. These are bit-wise ANDed with the enable bits which come from the configuration array (DET\_ENABLE[127:0]). A 128-bit priority encoder selects which experiment will report its error. The resulting 7-bit value is captured in a register (protected with TMR). If the primary input SEL\_NUM\_DATAB is asserted, this flows to the output pins as ERR\_NUM\_DAT[7:0].

Figure 3.11 Circuit Diagram of Control Logic for Error Reporting

The primary input pin, ERR\_ACK, is used to lock the SELECTED\_EXPERIMENT. When ERR\_ACK is low, the newly selected error number is loaded into SELECTED\_EXPERIMENT, and when it is high, the selected experiment is locked. The only state elements in the error reporting logic are the output of the priority encoder and the selected experiment. Both of these 7-bit registers will be implemented using TMR. The error reporting interface operates at a low frequency so SETs in the combinatorial logic have a very low chance of being captured and will almost certainly be filtered through the IO pads. The flops for the ERR\_VALID\_A/B signals are DMR. The external test logic (FPGA) will only react if both ERR\_VALID\_A and ERR\_VALID\_B are asserted.

There is a small risk that a transient could cause a glitch on the CLEAR\_EXP signals. If this occurs when the selected experiment has not currently detected an error, it is benign, as no error information is stored. In the unlikely event that an SET did occur and cleared an experiment that has currently logged an error, then the data read from that experiment would be invalid. Potentially, this could be detected by the external FPGA if the ERR\_VALID\_A/B outputs de-asserted before

the FPGA actively cleared the results, and in this case, the FPGA could ignore the partial data that had been read.

As an emergency backup feature, the SELECTED\_EXPERIMENT can be manually loaded using the configuration interface. If the configuration bit, ERR\_NUM\_OVERRIDE\_EN, is set to 1, then the SELECTED\_EXPERIMENT is loaded directly from the configuration bits ERR\_NUM\_OVERRIDE[6:0]. In this way, it possible for the external FPGA to directly poll the experiments rather than reacting to the reported errors.

Once an experiment has reported that it has an error (ERR\_VALID\_INTERNAL=1) and it has been selected, the associated data from that experiment must be read. This is performed by first having the external FPGA set SEL\_NUM\_DATA\_B to 0, which selects the data-path portion, shown in Figure 3.12. Internally, each experiment can have up to 40 bits of data to report. However, each experiment has a 5:1 mux1 controlled by the primary inputs ERR\_DATA\_SEL[2:0], which selects only 8-bits of data. The 8-bits of output data from each experiment feed to a central 128:1 mux (8-bits wide). This mux is controlled based on the SELECTED\_EXPERIMENT. The selected 8-bits of data flow out to the output pins. In this way, under the control of the FPGA, the full 40-bits of data in each experiment can be read, one byte at a time, as illustrated in Figure 3.10.

Figure 3.12 Circuit Diagram of Data Muxing Logic for Error Reporting

Note that the CREST experiment is slightly different. In the absence of an error being reported by any of the experiments (ERR VALID INTERNAL=0), the default data driven to the 8-bit output

bus is the contents of the CREST error counter (CREST\_CNT[7:0]). In this way, it is possible for the external FPGA to monitor "continuously" the count from the CREST experiment.

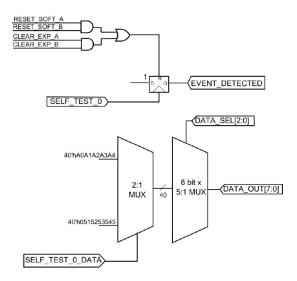

## 3.5 Self-Test Experiment

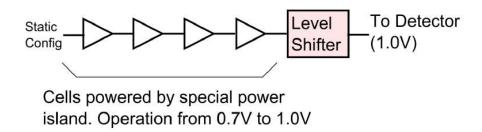

It is essential that the chip can be functionally tested prior to any radiation testing. For this reason, two identical test experiments have been included. These test experiments can be triggered under the control of the FPGA, by programming SELF\_TEST\_[0|127] to 1. When they are triggered, these experiments cause the chip to report an error as if a radiation event had occurred. The FPGA can then follow the regular sequence to read out 40 bits of data, one byte at a time and then clear the experiment. The structure of the self-test experiments is very simple and is shown in Figure 3.13. Note that through configuration (SELF\_TEST\_[0|127]\_DATA), one of two different data patterns can be selected.