# ALGORITHMS AND ARCHITECTURES FOR DECIMAL TRANSCENDENTAL FUNCTION COMPUTATION

A Thesis Submitted to the

College of Graduate Studies and Research

in Partial Fulfillment of the Requirements

for the degree of Doctor of Philosophy

in the Department of Electrical and Computer Engineering

University of Saskatchewan

Saskatoon, Saskatchewan, Canada

By

Dongdong Chen

©Dongdong Chen, January, 2011. All rights reserved.

# PERMISSION TO USE

In presenting this thesis in partial fulfilment of the requirements for a Postgraduate degree from the University of Saskatchewan, I agree that the Libraries of this University may make it freely available for inspection. I further agree that permission for copying of this thesis in any manner, in whole or in part, for scholarly purposes may be granted by the professor or professors who supervised my thesis work or, in their absence, by the Head of the Department or the Dean of the College in which my thesis work was done. It is understood that any copying or publication or use of this thesis or parts thereof for financial gain shall not be allowed without my written permission. It is also understood that due recognition shall be given to me and to the University of Saskatchewan in any scholarly use which may be made of any material in my thesis.

Requests for permission to copy or to make other use of material in this thesis in whole or part should be addressed to:

Head of the Department of Electrical and Computer Engineering

57 Campus Drive

University of Saskatchewan

Saskatoon, Saskatchewan

Canada

S7N 5A9

# Abstract

Nowadays, there are many commercial demands for decimal floating-point (DFP) arithmetic operations such as financial analysis, tax calculation, currency conversion, Internet based applications, and e-commerce. This trend gives rise to further development on DFP arithmetic units which can perform accurate computations with exact decimal operands. Due to the significance of DFP arithmetic, the IEEE 754-2008 standard for floating-point arithmetic includes it in its specifications. The basic decimal arithmetic unit, such as decimal adder, subtracter, multiplier, divider or square-root unit, as a main part of a decimal microprocessor, is attracting more and more researchers' attentions. Recently, the decimal-encoded formats and DFP arithmetic units have been implemented in IBM's system z900, POWER6, and z10 microprocessors.

Increasing chip densities and transistor count provide more room for designers to add more essential functions on application domains into upcoming microprocessors. Decimal transcendental functions, such as DFP logarithm, antilogarithm, exponential, reciprocal and trigonometric, etc, as useful arithmetic operations in many areas of science and engineering, has been specified as the recommended arithmetic in the IEEE 754-2008 standard. Thus, virtually all the computing systems that are compliant with the IEEE 754-2008 standard could include a DFP mathematical library providing transcendental function computation. Based on the development of basic decimal arithmetic units, more complex DFP transcendental arithmetic will be the next building blocks in microprocessors.

In this dissertation, we researched and developed several new decimal algorithms and architectures for the DFP transcendental function computation. These designs are composed of several different methods: 1) the decimal transcendental function computation based on the table-based first-order polynomial approximation method; 2) DFP logarithmic and antilogarithmic converters based on the decimal digit-recurrence algorithm with selection by rounding; 3) a decimal reciprocal unit using the efficient table look-up based on Newton-Raphson iterations; and 4) a first radix-100 division unit based on the non-restoring algorithm with pre-scaling method. Most decimal algorithms and architectures for the DFP transcendental function computation developed in this dissertation have been the first at-

tempt to analyze and implement the DFP transcendental arithmetic in order to achieve faithful results of DFP operands, specified in IEEE 754-2008.

To help researchers evaluate the hardware performance of DFP transcendental arithmetic units, the proposed architectures based on the different methods are modeled, verified and synthesized using FPGAs or with CMOS standard cells libraries in ASIC. Some of implementation results are compared with those of the binary radix-16 logarithmic and exponential converters; recent developed high performance decimal CORDIC based architecture; and Intel's DFP transcendental function computation software library. The comparison results show that the proposed architectures have significant speed-up in contrast to the above designs in terms of the latency. The algorithms and architectures developed in this dissertation provide a useful starting point for future hardware-oriented DFP transcendental function computation researches.

# ACKNOWLEDGEMENTS

It is a pleasure to express my sincere appreciation to the people who have assisted me throughout the years of research that have led to this Ph.D dissertation at University of Saskatchewan.

First and foremost, I sincerely thank my supervisor, Dr. Seok-Bum Ko, who has supported me throughout this dissertation with his expertise, understanding, and patience whilst allowing me the room to work in my own way. Without his constant guidance, advice and encouragement, this dissertation would not have been possible.

Second, I would like to thank the members of my dissertation committee, Dr. Daniel Teng, Dr. Khan Wahid and Dr. Derek Eager, for the invaluable suggestions for my Ph.D dissertation. Also, I would like to thank Dr. Tor Aamodt from the University of British Columbia for taking time out from his busy schedule to serve as my external examiner.

Third, I thank all people in the Department of Electrical and Computer Engineering for providing such a great academic environment, in which I can carry out this dissertation. In particular, I would like to thank the faculties and staff of VLSI research group; and thank all workmates for collaborations on several research projects.

Fourth, I would appreciate the anonymous reviewers from *IEEE Symposium on Computer Arithmetic* and *IEEE Transactions on Computer* for their invaluable comments. I am very grateful to the Dr. Ivan Godard for his insightful advice and brilliant idea for several future research projects. I would like to mention Dr. Liang-Kai Wang, Dr. Mark A. Erle and Dr. Álvaro Vázquez for their impressive Ph.D works in the area of the DFP computer arithmetic, which continually inspire me on doing my Ph.D research.

Fifth, I would to deliver my thanks to my friends in 2C60 for their friendship and help; special thanks to my beloved family for their love and support. They always encouraged me and asked me to be patience and work harder, and that is the thing I really kept in mind.

Finally, I am grateful to the College of Graduate Studies and the Department of Electrical and Computer Engineering for providing financial assistance through scholarships that were invaluable to me.

Dedicate to my beloved family

# Contents

| Pe             | rmission to Use                                                                                                                                                                                                                                                                                                                                                                                                                     | 1                                                            |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| $\mathbf{A}$ l | ostract                                                                                                                                                                                                                                                                                                                                                                                                                             | ii                                                           |

| A              | knowledgements                                                                                                                                                                                                                                                                                                                                                                                                                      | iv                                                           |

| Co             | ontents                                                                                                                                                                                                                                                                                                                                                                                                                             | vi                                                           |

| $\mathbf{Li}$  | st of Tables                                                                                                                                                                                                                                                                                                                                                                                                                        | X                                                            |

| $\mathbf{Li}$  | st of Figures                                                                                                                                                                                                                                                                                                                                                                                                                       | xi                                                           |

| $\mathbf{Li}$  | st of Abbreviations                                                                                                                                                                                                                                                                                                                                                                                                                 | xii                                                          |

| I              | Preface                                                                                                                                                                                                                                                                                                                                                                                                                             | 1                                                            |

| 1<br>II        | Introduction  1.1 Why Decimal Arithmetic                                                                                                                                                                                                                                                                                                                                                                                            | . 4                                                          |

| 2              | Decimal Transcendental Arithmetic  2.1 DFP Formats in IEEE 754-2008 Standard 2.1.1 DFP Formats and Encodings 2.1.2 DFP Arithmetic Operations 2.1.3 DFP Rounding Modes 2.1.4 Exception Handling 2.2 Decimal Transcendental Unit Design 2.2.1 Some Details of DFP Transcendental Operations 2.2.2 Classification of Hardware Approaches in BFP 2.2.3 Considerations of Hardware Implementation 2.2.4 Related Basic Decimal Arithmetic | . 14<br>. 17<br>. 19<br>. 20<br>. 20<br>. 21<br>. 23<br>. 26 |

| II             | I Table-based First-Order Polynomial Approximation                                                                                                                                                                                                                                                                                                                                                                                  | 29                                                           |

| 3              | A Dynamic Non-Uniform Segmentation Method                                                                                                                                                                                                                                                                                                                                                                                           | 30                                                           |

|   | 3.1 | Introduction                                               | <br>. 30 |

|---|-----|------------------------------------------------------------|----------|

|   | 3.2 | Minimax Polynomial Approximation                           | <br>. 32 |

|   |     | 3.2.1 Notations                                            | <br>. 32 |

|   |     | 3.2.2 Minimax Error Analysis in One Segment                | <br>. 33 |

|   | 3.3 | A Non-Uniform Segmentation Method                          | <br>. 35 |

|   |     | 3.3.1 Determination of Initial UFB by MiniBit Approach     |          |

|   |     | 3.3.2 Evaluation of Bit-Width of Segment Boundary          |          |

|   |     | 3.3.3 Partition of Non-Uniform Segments by BSPS            |          |

|   | 3.4 | · · · · · · · · · · · · · · · · · · ·                      |          |

|   |     | 3.4.1 Segment Index Encoder                                | <br>. 41 |

|   |     | 3.4.2 Estimation of Memory Sizes                           |          |

|   | 3.5 | · · · · · · · · · · · · · · · · · · ·                      |          |

|   |     | 3.5.1 Comparison Results                                   |          |

|   |     | 3.5.2 Evaluation Results for More Functions                |          |

|   |     | 3.5.3 Memory Sizes for Two Methods                         |          |

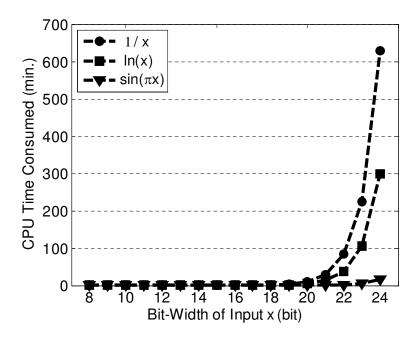

|   |     | 3.5.4 CPU Time Consumed                                    |          |

|   | 3.6 |                                                            |          |

|   | 0.0 |                                                            |          |

| 4 | Dec | cimal Logarithmic and Antilogarithmic Converters           | 50       |

|   | 4.1 | Introduction                                               | <br>. 50 |

|   | 4.2 | 0                                                          |          |

|   |     | 4.2.1 Binary-based Decimal Logarithm Conversion (Alg. 1) . | <br>. 51 |

|   |     | 4.2.2 Decimal Logarithm Conversion (Alg. 2)                |          |

|   |     | 4.2.3 Decimal Antilogarithm Conversion (Alg. 3)            | <br>. 53 |

|   | 4.3 | Piecewise Linear Approximation Method                      | <br>. 54 |

|   |     | 4.3.1 Notations                                            | <br>. 54 |

|   |     | 4.3.2 Decimal Minimax Error Analysis in One Segment        | <br>. 54 |

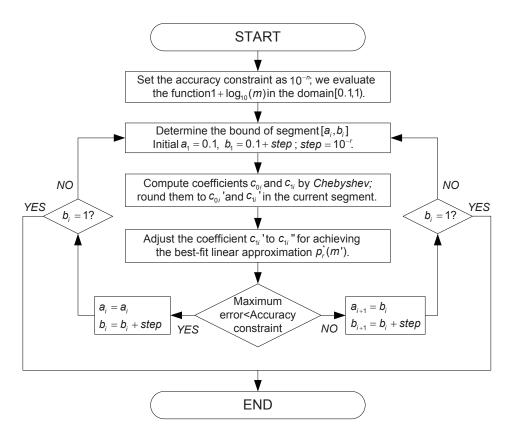

|   |     | 4.3.3 Decimal Dynamic Non-Uniform Segmentation Method      | <br>. 55 |

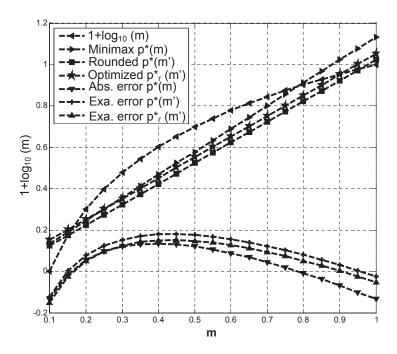

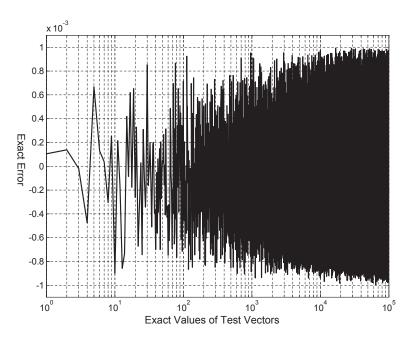

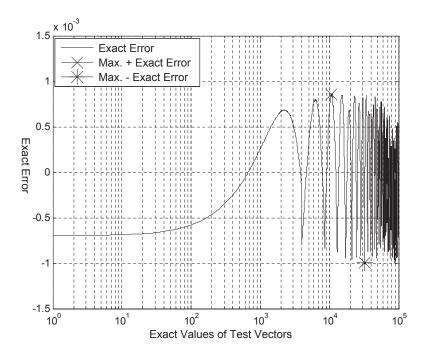

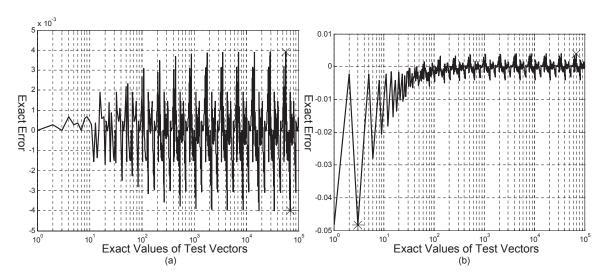

|   |     | 4.3.4 Approximation Results for Decimal Logarithm          | <br>. 57 |

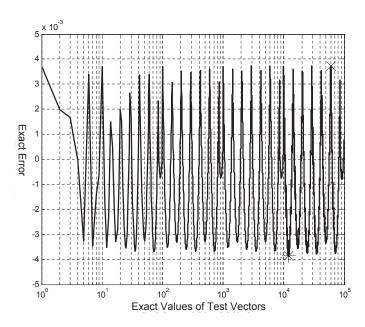

|   |     | 4.3.5 Approximation Results for Decimal Antilogarithm      |          |

|   | 4.4 | Error Analysis of Two Algorithms                           | <br>. 60 |

|   | 4.5 | Hardware Architecture                                      | <br>. 63 |

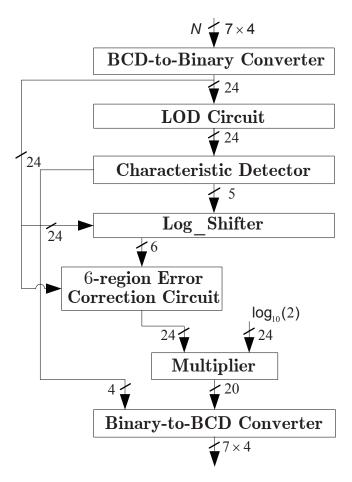

|   |     | 4.5.1 Binary-based Decimal Logarithmic Converter (Alg. 1). | <br>. 63 |

|   |     | 4.5.2 Decimal Logarithmic Converter (Alg. 2)               | <br>. 64 |

|   |     | 4.5.3 Decimal Antilogarithmic Converter (Alg. 3)           | <br>. 65 |

|   |     | 4.5.4 Decimal Segment Index Encoder                        |          |

|   |     | 4.5.5 Coefficients Look-up Table                           | <br>. 67 |

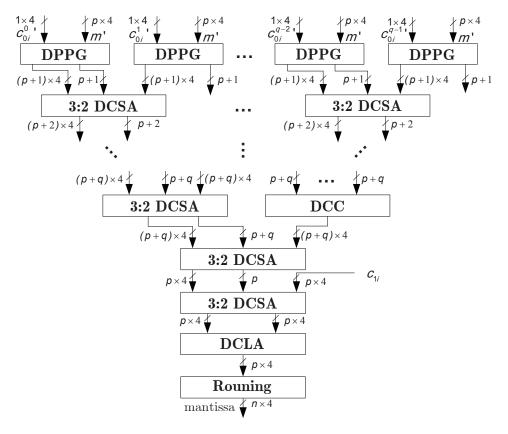

|   |     | 4.5.6 Decimal Linear Approximation Unit                    | <br>. 68 |

|   |     | 4.5.7 Design Example                                       |          |

|   | 4.6 |                                                            |          |

|   |     | 4.6.1 Implementation Results and Analysis                  |          |

|   |     | 4.6.2 Tradeoff Analysis of Hardware Implementation         |          |

|   |     | 4.6.3 Scale up to a Higher Required Accuracy               |          |

|   |     | 4.6.4 Hardware Performance Comparison in Two Algorithms    |          |

|   | 4.7 |                                                            | . 75     |

| I            | / ] | Digit-Recurrence with Selection by Rounding        | 76         |

|--------------|-----|----------------------------------------------------|------------|

| 5            | Dec | cimal Floating-Point Logarithmic Converter         | 77         |

|              | 5.1 | Introduction                                       | 77         |

|              | 5.2 | DFP Logarithm Operation                            | 79         |

|              |     | 5.2.1 Exception Handling                           | 79         |

|              |     | 5.2.2 Range Reduction                              | 79         |

|              | 5.3 | Digit-Recurrence Algorithm for Logarithm           | 80         |

|              |     | 5.3.1 Overview                                     | 80         |

|              |     | 5.3.2 Selection by Rounding                        | 82         |

|              |     | 5.3.3 Index of Initial Iteration                   | 84         |

|              |     | 5.3.4 Approximation of Logarithm                   | 85         |

|              |     | 5.3.5 Error Analysis and Evaluation                | 86         |

|              |     | 5.3.6 Guard Digit of Scaled Residual               | 89         |

|              | 5.4 | Architecture of DFP Logarithmic Converter          | 90         |

|              | 0.1 | 5.4.1 Datapath                                     | 92         |

|              |     | 5.4.2 Hardware Implementation                      | 97         |

|              | 5.5 | Implementation and Comparisons                     | 108        |

|              |     |                                                    |            |

|              | 5.6 | Summary                                            | 112        |

| 6            | Dec | eimal Floating-Point Antilogarithmic Converter     | 113        |

|              | 6.1 | Introduction                                       | 113        |

|              | 6.2 | DFP Antilogarithm Operation                        | 114        |

|              |     | 6.2.1 Exception Handling                           | 114        |

|              |     | 6.2.2 Range Reduction                              | 115        |

|              | 6.3 | Digit-Recurrence Algorithm for Antilogarithm       | 116        |

|              |     | 6.3.1 Overview of Algorithm                        | 116        |

|              |     | 6.3.2 Selection by Rounding                        | 117        |

|              |     | 6.3.3 Approximation of Logarithm                   | 119        |

|              |     | 6.3.4 Error Analysis and Evaluation                | 120        |

|              |     | 6.3.5 Guard Digit of Scaled Residual               | 124        |

|              | 6.4 | Architecture of DFP Antilogarithmic Converter      | 125        |

|              | 0   | 6.4.1 Datapath                                     | 127        |

|              |     | 6.4.2 Hardware Implementation                      | 130        |

|              | 6.5 | Implementation and Comparisons                     | 138        |

|              | 6.6 | Summary                                            | 141        |

|              | 0.0 | Summary                                            | 141        |

| $\mathbf{V}$ | D   | Decimal Reciprocal and Radix-100 Division Units    | 143        |

| 7            | Dos | sign and Implementation of Decimal Reciprocal Unit | 144        |

| 1            | 7.1 | Introduction                                       | 144        |

|              | •   |                                                    |            |

|              | 7.2 | Initial Reciprocal Approximation                   | 146        |

|              |     | 7.2.1 Algorithm                                    | 146<br>147 |

|              |     | LZZ AT CHICIETT POOK-ID TRDIE CCERTION             | 14/        |

|              | 7.3   | Newton-Raphson Iteration                                | 148 |

|--------------|-------|---------------------------------------------------------|-----|

|              | 7.4   | Hardware Implementation                                 | 150 |

|              | 7.5   | Implementation Results                                  |     |

|              | 7.6   | Summary                                                 |     |

| 8            | Des   | sign and Implementation of A Radix-100 Decimal Division | 154 |

|              | 8.1   | Introduction                                            | 154 |

|              | 8.2   | Algorithm                                               | 155 |

|              |       | 8.2.1 Radix-100 Non-Restoring Decimal Division          | 155 |

|              |       | 8.2.2 Pre-scaling method                                | 156 |

|              |       | 8.2.3 Analysis of Look-up Table Size                    | 157 |

|              | 8.3   | Architecture                                            | 158 |

|              | 8.4   | Analysis of Implementation Results                      | 161 |

|              | 8.5   | Summary                                                 | 162 |

| $\mathbf{V}$ | Ι (   | Conclusion                                              | 164 |

| 9            | Sun   | nmary and Future Research                               | 165 |

|              | 9.1   | Summary                                                 | 165 |

|              | 9.2   | Future Research                                         | 167 |

|              |       | 9.2.1 Decimal Logarithmic Arithmetic Unit               | 167 |

|              |       | 9.2.2 A Combined DFP Division/Square Root Unit          | 169 |

|              |       | 9.2.3 DFP Transcendentals via BID Encoding              |     |

| R            | efere | nces                                                    | 172 |

# LIST OF TABLES

| 2.1<br>2.2<br>2.3<br>2.4                      | Parameters in DFP interchange formats                                                                                                                                                                                                                                                                          | 16<br>21<br>22                     |

|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

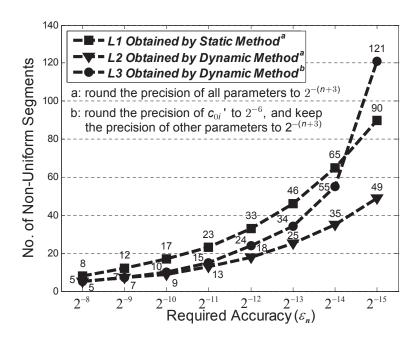

| 3.1                                           | Number of non-uniform segments obtained by <i>Static Method</i> and <i>Dynamic Method</i>                                                                                                                                                                                                                      | 48                                 |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6        | Parameters of decimal logarithm linear approximation (Alg. 2).  Comparsion of two decimal logarithm algorithms.  Details of combinational delay.  Tradeoff analysis of hardware implementation.  Implementation results in different accuracy constraints.  Hardware performance comparison in two algorithms. | 58<br>62<br>70<br>72<br>73<br>74   |

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7 | Details of critical path of Decimal64 logarithmic converter                                                                                                                                                                                                                                                    | 84<br>85<br>89<br>98<br>109<br>109 |

| 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6        | Error analysis of DFP antilogarithm for DFP interchange formats                                                                                                                                                                                                                                                | 119<br>124<br>130<br>139<br>139    |

| 7.1<br>7.2                                    | 1                                                                                                                                                                                                                                                                                                              | 148<br>153                         |

| 8.1<br>8.2<br>8.3                             | Details of critical path on FPGA                                                                                                                                                                                                                                                                               | 157<br>162<br>163                  |

| 9.1                                           | Operations by decimal logarithmic arithmetic unit                                                                                                                                                                                                                                                              | 169                                |

# LIST OF FIGURES

| 2.1                                                                 | DFP interchange format with DPD encoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 14                                                       |

|---------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

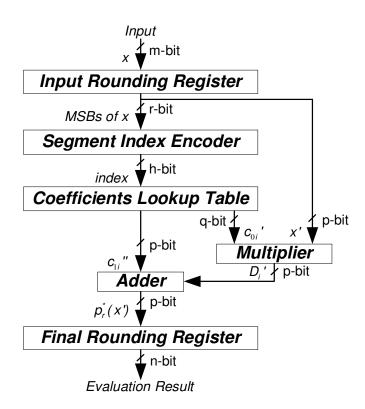

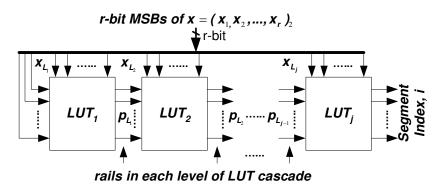

| 3.1<br>3.2<br>3.3<br>3.4                                            | FPGA implementation for function evaluations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 41<br>42<br>43<br>46                                     |

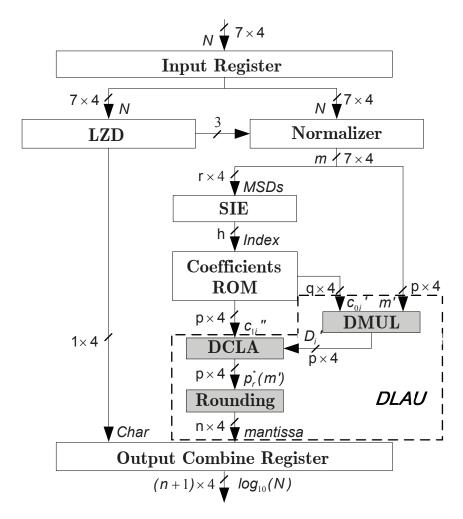

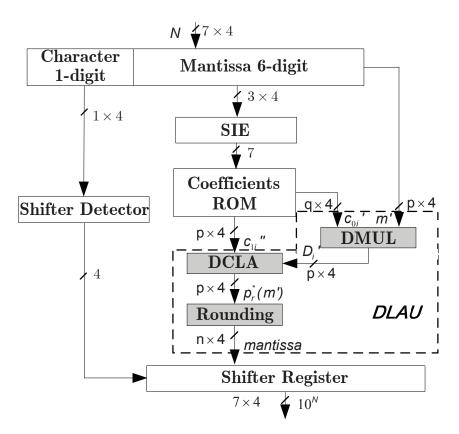

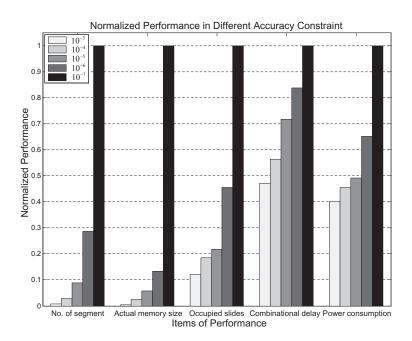

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9<br>4.10 | Optimization of linear approximation in one segment of decimal logarithm.  Proposed dynamic non-uniform segmentation method                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 55<br>56<br>59<br>59<br>61<br>63<br>65<br>66<br>68<br>73 |

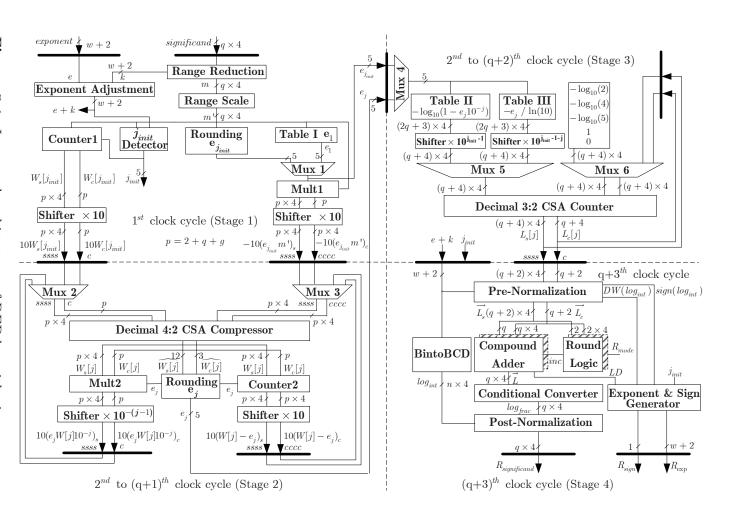

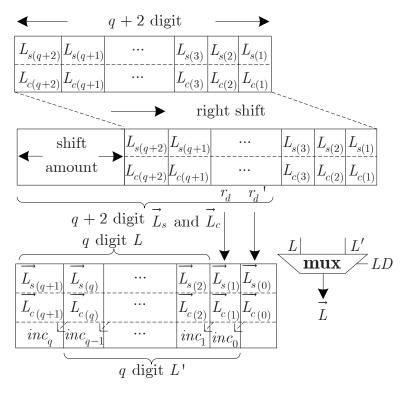

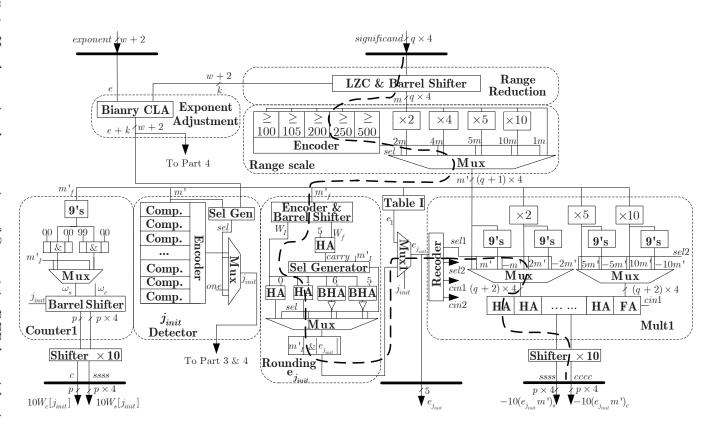

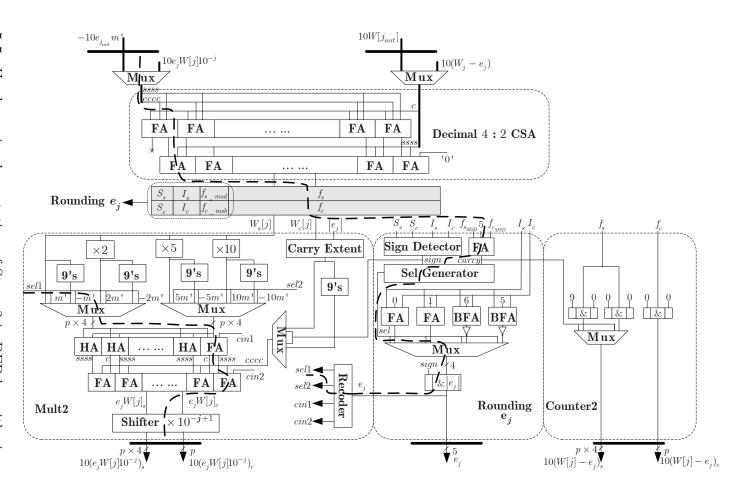

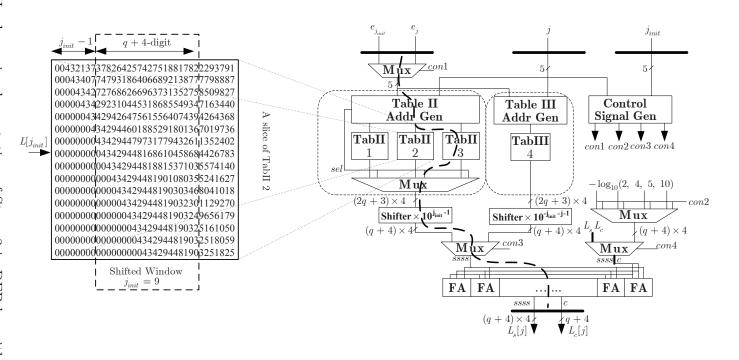

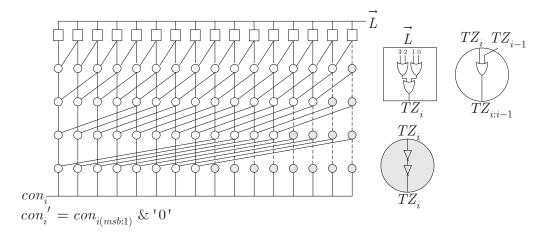

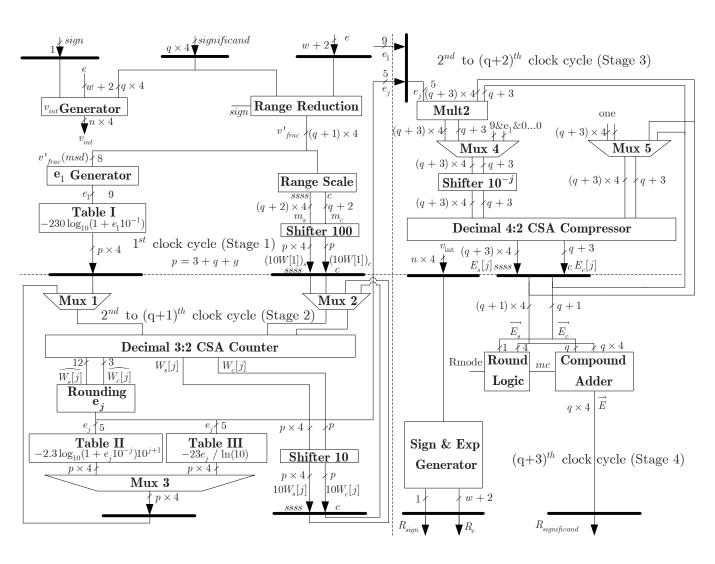

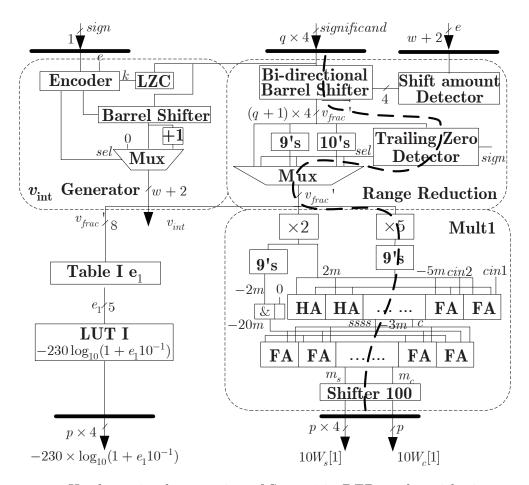

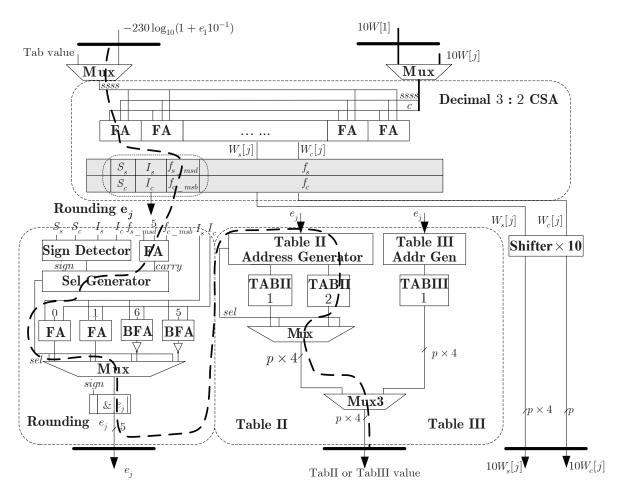

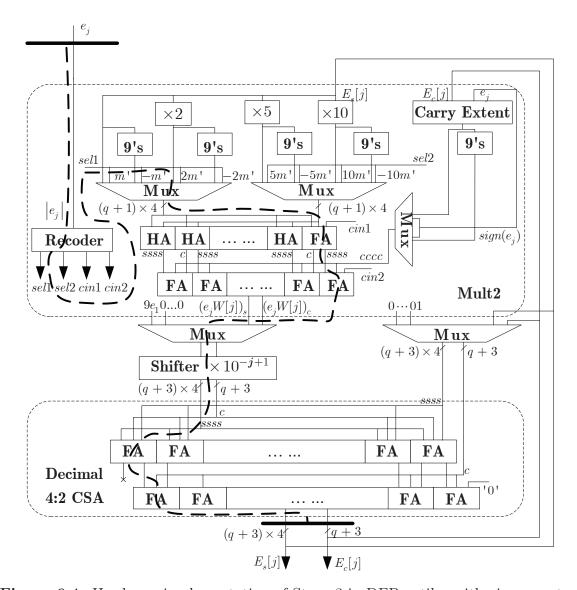

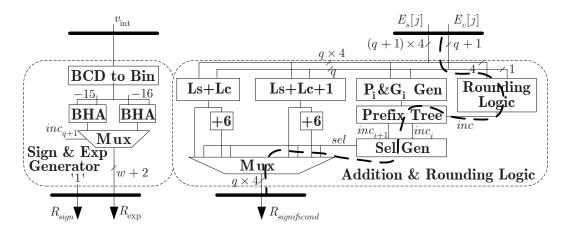

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8                | $\begin{array}{c} \text{Improved architecture of DFP logarithmic converter.} & \\ \text{Decimal carry-save representation of } W[j]. & \\ \text{Data-path of the computation of } L \text{ and } L'. & \\ \text{Hardware implementation of Stage 1 in DFP logarithmic converter.} & \\ \text{Hardware implementation of Stage 2 in DFP logarithmic converter.} & \\ \text{Hardware implementation of Stage 3 in DFP logarithmic converter.} & \\ \text{Hardware implementation of Stage 4 in DFP logarithmic converter.} & \\ \text{Portion of a trailing zeros detector for Decimal 64.} & \\ \end{array}$ | 91<br>92<br>96<br>99<br>102<br>104<br>106                |

| 6.1<br>6.2<br>6.3<br>6.4<br>6.5                                     | Improved architecture of DFP antilogarithmic converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 126<br>132<br>134<br>136<br>137                          |

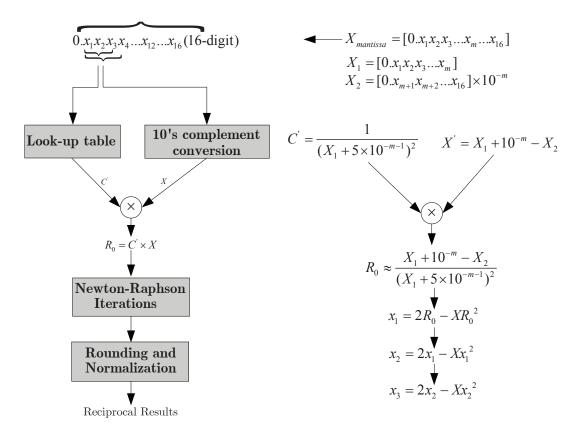

| 7.1<br>7.2                                                          | Data-path of the reciprocal computation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 149<br>151                                               |

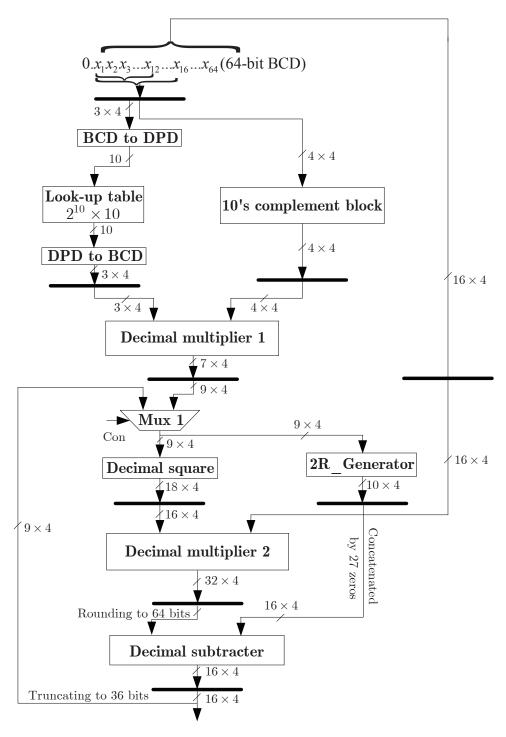

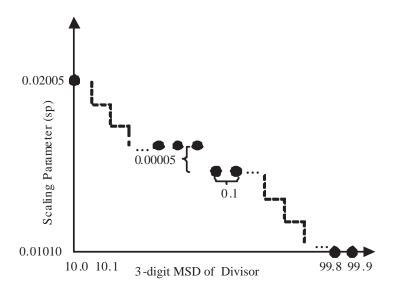

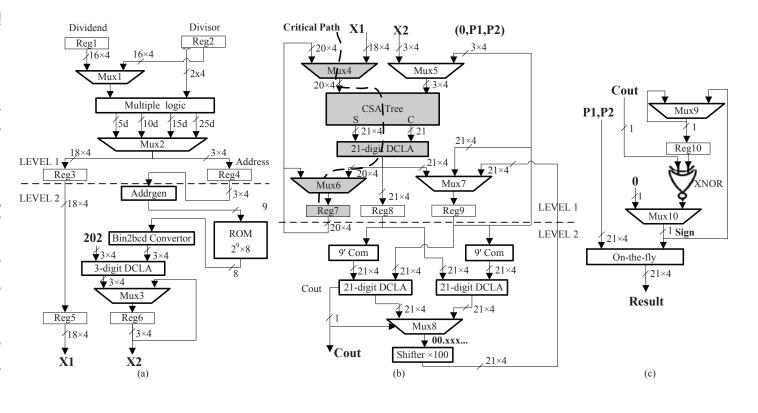

| 8.1<br>8.2                                                          | Scaling parameters in the look-up table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 159<br>160                                               |

| 9.1                                                                 | Decimal logarithmic arithmetic unit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 168                                                      |

# LIST OF ABBREVIATIONS

ALU Arithmetic Logic Unit ASIC Application Specific Circuit Binary Coded Decimal BCD **BFP** Binary Floating-Point BID Binary Integer Decimal **BSPS** Binary Search Partition Scheme BXP Binary Fixed-Point CSCarry-Save Number System DCC Decimal Carry Counter **DCFA** Decimal Carry-free Adder DCLA Decimal Carry-look-ahead Adder DCSA Decimal Carry-save Adder DFP Decimal Floating-Point DLAU Decimal Linear Approximation Unit DLAU Decimal Logarithmic Arithmetic Unit DMUL Decimal Multiply Logic DPD Denselv Packed Decimal Decimal Partial Product Generation **DPPG** DSP Digital Signal Processing DXP Decimal Fixed-Point FLP Floating-Point Number System **FPGA** Field-Programmable Gate Array ΙP Intellectual Property LNS Logarithmic Number System LOD Leading One Detector LSB Least Significand Bit LSD Least Significand Digit LUTs Look-up Tables LZD Leading Zero Detector **MSB** Most Significand Bit MSD Most Significand Digit MTBDD Multi-terminal Binary Decision Diagram MiniBit Static Bit-width Optimization Approach NaN Not-a-Number ROM Read Only Memory SDSigned-Digit Number System SIE Segment Index Encoder Single Instruction Multiple Data SIMD UFB Uniform Fractional Bit-width

Unit in the Last Place

ulp

Part I

Preface

# CHAPTER 1

# Introduction

This chapter discusses the importance of Decimal Floating-Point (DFP) arithmetic and the necessity that existing computer processors support DFP arithmetic. Based on the existing basic decimal arithmetic units, more complex DFP transcendental arithmetic could be built in computer processors to meet the strict requirements on computational speed and accuracy for tomorrow. This motivates the need to create DFP transcendental arithmetic in hardware, which is the focus of this dissertation. Section 1.1 presents an overview of the necessity of decimal arithmetic. Section 1.2 discusses the motivation of this research work. Section 1.3 describes the road-map of this research dissertation. Section 1.4 summarizes research contributions.

# 1.1 Why Decimal Arithmetic

We will start this chapter with a story shown in a design article in EETimes [1]:

"If you ask engineers how numbers are represented, stored, and manipulated in computers and calculators, most will reply: "as signed or unsigned binary integers or as binary fixed-point (BXP) or floating-point (BFP) values." (...) And even if one should happen to enquire about Binary Coded Decimal (BCD) representations, the response is almost invariably: "Oh, that went out of style 25 to 30 years ago; no one uses it now." Is that true?"

Decimal number is a whole lot simpler for people to understand and use than binary number, because it is basically based upon the decimal arithmetic that we have learned in school. In the early computers, the decimal arithmetic units were implemented in microprocessors, however, they have not been popular due to its lower computation speed and larger hardware cost compared with binary arithmetic. The reasons are evident, first, binary arithmetic is more suitable for scientific computations than decimal, due to its mathematical properties and performance advantage; second, the substrate of digital systems is based on two-state transistors so that binary number can be stored more efficiently and processed faster than decimal number in hardware. We realize the advantages of the binary computation, however, we intend to show in this section that the decimal computation still has its significance on many financial, commercial and Internet business applications, such as banking, accounting, tax calculation, currency conversion, insurance, marketing, retail sales, e-commerce and e-banking [2]. The following is more comprehensive reasons for the need of decimal arithmetic.

First of all, numbers in commercial databases are primarily decimal. Dr. M. F. Cowlishaw in his paper [2] cites a survey of commercial databases reported by Tsang [3]. The databases in this survey cover a wide range of applications, including airline systems, banking, financial analysis, insurance, inventory control, management reporting, marketing services, order entry and processing, pharmaceutical, and retail sales. In those databases, over 456,420 columns contained numeric data and of which 55% are decimal, and the further 43.7% are integer types which could have been stored as decimal numbers. Dr. M. F. Cowlishaw concludes that the extensive use of decimal numbers in these commercial databases suggests that it is worthwhile to study how the decimal data are used and how decimal arithmetic should be defined.

Second, most decimal fractional numbers can not be exactly represented or exactly rounded by BFP numbers. In [4], Dr. M. F. Cowlishaw presents several examples to show computation problems. The first example shows that the decimal number 0.1 requires an infinitely recurring binary number (0.00011001...), which can only be approximated to a decimal number (0.09765...) instead of the exact value of 0.1. It is evident that a conversion error between the decimal and binary format can not be avoided, so using BFP to compute decimal is not possible to guarantee the same results as those from decimal arithmetic. Another potential problem may be produced later on when rounding the BFP result after the decimal computation by binary. For example, consider a calculation, 0.70×1.05, using the most widely used double-precision BFP format, the exact result is little less than

0.734999999999999. This result, rounded to a decimal number with two decimal fraction digits, is 0.73, which is 0.01 less than manual computation result (0.735), rounded to the same fraction digits, 0.74. Although the error in a single operation shown in above examples is very small, these tiny errors may accumulate and lead to a large error after several operations. Dr. M. F. Cowlishaw presents a study [4] which shows that a large telephone billing system can accumulate errors of up to 5 million dollars per year, if using BFP arithmetic (the telco benchmark [5]).

Third, decimal arithmetic could be a significant part of commercial workloads with the increasing use of DFP format. In [2], Dr. M. F. Cowlishaw presents a case study about a new benchmark, designed to model an extreme case such as a telephone company's daily billing application. This case study indicates that the decimal processing overhead in the benchmark could reach over 90% and very time consuming. Therefore, he predicts that this kind of applications would clearly benefit from the hardware component of DFP arithmetic units built in microprocessors. Such a hardware could be two to three orders of magnitude faster than software.

# 1.2 Motivation

In today's world, few microprocessors have instructions or dedicated hardware components for DFP arithmetic. In a microprocessor without DFP support, decimal numbers are usually processed with two methods. One method is to convert the decimal numbers to binary numbers before computation in binary hardware arithmetic units, and then the binary format results are converted back to decimal format. The other method is to store the data in decimal format and process data using decimal software arithmetic library, such as the Java BigDecimal class [6] and the C/C++ decNumber library [7]. The first method is error-prone because BFP format can not exactly represent decimal fractions, while the software based method is typically 100 to 1000 times slower than binary arithmetic implemented in hardware [2]. These problems give rise to the need to develop hardware DFP arithmetic components in microprocessors for accurate and fast calculation fully in decimal. Due to the significance of DFP arithmetic, it is included in the specifications of the IEEE 754-2008

standard [8], which defines three decimal data formats that can be used for decimal integer, decimal fixed-point (DXP), and DFP computer arithmetic. For the same reason, the DFP arithmetic units have been implemented in IBM's microprocessors POWER6 [9], system z9 [10] and z10 [11] microprocessors.

Most microprocessors in computer systems usually include the basic arithmetic units, such as adder, subtracter, multiplier, divider and square-root unit  $(+, -, \times, \div \text{ and } \sqrt{})$ . These basic decimal arithmetic units, as the main components of a decimal microprocessor, have been designed and implemented to be compliant with the DFP arithmetics defined in IEEE 754-2008 standard by recent works. Examples include the decimal adders in [12, 13, 14, 15, 16, 17, 18, 19], the decimal multipliers [20, 21, 22, 23, 24], the decimal dividers in [25, 26, 27, 28, 29] and the decimal square-root unit in [30]. A complete survey of hardware designs for the basic decimal arithmetic is summarized in [31].

The transcendental functions, such as logarithm, antilogarithm, exponential, and trigonometric, defined in the Dr. J-M Muller's book [32], are useful arithmetic concepts in many areas of science and engineering. Some applications, such as computer 3D graphics, scientific computing, artificial neural networks, logarithmic number system (LNS), digital signal processing (DSP) [33, 34, 35, 36, 37] are implemented in hardware by using binary transcendental arithmetics to replace the basic computer arithmetic units. For instance, the multiplication and division can be simplified to the level of addition and subtraction by using logarithmic units [33]. The decimal transcendental function computation is also very useful for some specific applications, such as some computations used in financial applications in banks [38] (eg. the compound interest computation), the scientistic decimal calculator [39], and some pocket computers [40]. Furthermore, with the continuous reduction of the size of the transistor and the scale of the integration, the decimal transcendental arithmetic units are more likely to be cheap enough to be implemented in microprocessors, and its performance could be close to the performance of the binary units. And then, maybe the decimal transcendental arithmetic units will finally replace or co-exist with binary units in all applications because of the human preference for the decimal representation.

The decimal transcendental functions, as recommended decimal arithmetic operations, have been specified in the IEEE 754-2008 standard [8]. Therefore, virtually all the computing

systems that are compliant with the IEEE 754-2008 standard should provide a software or hardware solution for the decimal transcendental function computation. Recently, *Intel Cooperation* provides the first software solution to compute DFP and DXP transcendental functions using an existing and well-established BFP transcendental function mathematical library [41]. However, with the strict requirement on computational speed and accuracy in the future, the hardware components may be included in the high-end microprocessor to support the decimal transcendental computation.

The previous hardware implementations of the decimal transcendental function computation are reported in several patents [42, 43, 44, 45, 46] in which the decimal transcendental function computation is based on a binary arithmetic, rather than decimal. Therefore, they are not compliant with the DFP formats specified in the IEEE 754-2008 standard. In [40], a radix-10 BKM algorithm is presented for an efficient computation of DXP exponential and logarithm results. Unfortunately, this radix-10 BKM algorithm is not built according to the IEEE 754-2008 DFP standard. Recently, based on the recent development of basic decimal arithmetic units, more complex decimal transcendental arithmetic would be the next useful hardware components built for the future microprocessors. Therefore, the decimal transcendental arithmetic, as one of the hottest topic in decimal computer arithmetic, is attracting more and more researchers' attentions.

Some new algorithms and architectures, that are based on the IEEE 754-2008 standard, are developed for the computation of the DXP or DFP transcendental functions. In [47, 48, 49, 50, 51], the CORDIC-based architectures for a high performance decimal computation are described. The CORDIC-based methods have the potential to be modified for the computation of more transcendental functions in further development. However, since the CORDIC-based method needs to apply decimal multiplication and division operations, it has a large latency and hardware complexity. All of these considerations motivate us to design and implement the more efficient architectures for DFP or DXP units to satisfy the increasing potential demands of high-performance decimal transcendental computations.

#### 1.3 Research Overview

A set of new algorithms and architectures for the DFP and DXP transcendental function computation based on different approaches are investigated in this dissertation. We mainly focus on the following DFP or DXP transcendental operations in this dissertation: the DFP and DXP based-10 logarithms (log10) and the antilogarithms (exp10), where v presents the DFP or DXP operands. The proposed algorithms and architectures of the based-10 logarithms and antilogarithms can be easily modified to compute the DXP natural logarithms (log) and the exponential (exp) operations. Moreover, the DXP reciprocal (rootb(v,-1)) and division ( $div(v_1, v_2)$ ), which are considered as the most complex basic decimal arithmetic operation, are also investigated in this dissertation. This dissertation is structured in six parts with nine chapters shown as follows:

#### -Part I: **Preface** includes:

Chapter 1: *Introduction* presents the background, motivation, overview and contributions of this dissertation.

#### -Part II: Research Background includes:

Chapter 2: *DFP Transcendental Arithmetic* gives the overview about the DFP standard specified in IEEE 754-2008 and the common issues of DFP transcendental arithmetic design.

From this point, this dissertation is an original research, starting with:

#### -Part III: Table-based First-Order Polynomial Approximation includes:

Chapter 3: A Novel Dynamic Non-Uniform Segmentation presents a novel dynamic non-uniform segmentation method for the first-order polynomial elementary function approximation.

Chapter 4: Efficient Decimal Logarithmic and Antilogarithmic Converters present the new algorithms and architectures of DXP logarithmic and antilogarithmic converters based on the decimal first-order approximation polynomial method.

In Chapter 3, a novel dynamic non-uniform segmentation method is presented in detail, which can approximate the transcendental function by an optimized linear approximation with few non-uniform segments. Compared with previous non-uniform static method, the proposed method can significantly reduce the memory size occupied in hardware. Moreover, the proposed dynamic method can approximate the function to satisfy accuracy by the linear approximation in which the input, coefficients, and intermediate values are rounded to least bit-width, and this can not be achieved by the previous static non-uniform segmentation method.

In Chapter 4, we analyze the tradeoff of the hardware performance, and scale up the proposed architecture to achieve a higher precision of accuracy (obtain faithful results up to the precision of  $10^{-7}$ ). Moreover, a binary-based decimal linear approximation algorithm and its architecture are simulated as a benchmark to evaluate the performance of the proposed design. As far as we know, this work is the first attempt to study the decimal logarithmic and antilogarithmic converters based on the decimal piecewise first-order polynomial approximation method.

#### -Part IV: Digit-Recurrence with Selection by Rounding includes:

Chapter 5: Improved Design of Decimal Floating-Point Logarithmic Converter presents the algorithm and architecture of the DFP logarithmic converter, based on digit-recurrence algorithm with selection by rounding.

Chapter 6: Improved Design of Decimal Floating-Point Antilogarithmic Converter presents the algorithm and architecture of DFP antilogarithmic converter, based on digit-recurrence algorithm with selection by rounding.

In Chapter 5 and Chapter 6, the proposed algorithms and architectures can compute faithful DFP logarithm and antilogarithm results for any one of the three DFP formats, which are specified in the IEEE 754-2008 standard. These two designs make the first attempt to comprehensively analyze and implement the DFP logarithmic and antilogarithmic converters based on digit-recurrence algorithm with selection by rounding. The rough delay estimation results of the proposed architectures indicate that the latencies are close to or shorter than that of the binary radix-16 logarithmic and exponential converters, and that they have a

significant decrease in terms of the latency in contrast with our original published designs, the recent decimal CORDIC design, and the software implementation.

#### -Part V: Function Iteration Method includes:

Chapter 7: A Decimal Reciprocal Unit Using Efficient Table Look-up presents the efficient design and implementation of a 16-digit DXP decimal reciprocal unit based on Newton-Raphson iteration method.

Chapter 8: Design and Implementation of A Radix-100 Decimal Division presents a new algorithm and architecture of the 16-digit DXP radix-100 decimal divider based on the decimal non-restoring algorithm with pre-scaling method.

In Chapter 7, we analyze the computation error for the look-up tables with different sizes, in order to find the smallest size of look-up table for the efficient hardware implementation. The proposed design can utilize a half size of the look-up table as that used in the previous design to compute a faithful reciprocal result.

In Chapter 8, we design and implement a new radix-100 divider, which can can reduce the clock cycle to 1/4 of the previous radix-10 design, while maintaining accuracy of the result. As far as we know, this is the first work to research the algorithm and architecture of the radix-100 division. In addition, we would appreciate Mr. Yu Zhang's help for this work.

-Part VI: Conclusion includes:

Chapter 9: Summary and Future Research includes a summary of research, and thoughts on related future research.

# 1.4 Research Contributions

In this dissertation, we have researched and developed several new decimal algorithms and architectures for the DFP transcendental function computation. Some of them are the first published designs which can achieve faithful logarithm or antilogarithm results of DFP or DXP operands, specified in the IEEE 754-2008 standard. The algorithms and hardware designs presented in this dissertation provide a basis for the future hardware-oriented DFP or DXP transcendental function computation research. To help researchers evaluate the

performance of the proposed DFP transcendental arithmetic, we analyze the hardware implementation results of these arithmetic units, and compare the hardware performances of the proposed architectures with the binary based architectures, the recent decimal CORDIC designs, and the Intel's DFP software library. Our research on DFP transcendental arithmetic serves as a useful starting point for researchers who are interested in this area. In the future, as the performance gap between BFP and DFP arithmetic becomes smaller, DFP arithmetic units may replace or co-exist with BFP arithmetic units in the microprocessor. This dissertation may also be useful in guiding the design of future hardware and instruction set extensions for the computation of the decimal transcendental function in the microprocessor.

#### List of Publications:

We show next a list of the publications, arranged according to their correspondence to the different chapters of this dissertation.

Chapter 4: Efficient Decimal Logarithmic and Antilogarithmic Converters

- D. Chen and S. Ko, et al "A novel decimal-to-decimal logarithmic converter," *Proc. IEEE Symp. on Circuit and System (ISCAS'08)*, Seattle, Washington, pp. 688-691, May 2008.

- **D. Chen** and S. Ko, et al "A decimal-to-decimal antilogarithmic converter", *Proc. IEEE Canadian Electrical and Computer Engineering (CCECE'08)*, Niagara Falls, Ontario, Canada, pp. 1223-1226, May 2008.

Chapter 5: Improved Design of Decimal Floating-Point Logarithmic Converter

- D. Chen, Y. Zhang and S. Ko, et al "A 32-bit decimal floating-point logarithmic converter," Proc. 19th IEEE Symp. on Computer Arithmetic (ARITH'19), Portland, Oregon, pp. 195-203, June 2009.

- **D. Chen** and S. Ko, et al "Improved decimal floating-point logarithmic converter based on selection by rounding", accepted for publication, *IEEE Trans. on Computers*, to appear, 2011.

Chapter 6: Improved Design of Decimal Floating-Point Antilogarithmic Converter

• D. Chen and S. Ko, et al "A new decimal antilogarithmic converter," *Proc. IEEE Symp. on Circuit and System (ISCAS'09)*, Taipei, Taiwan, pp. 688-691, May 2009.

#### Chapter 7: A Decimal Reciprocal Unit Using Efficient Table Look-up

• D. Chen and S. Ko, "Design and implementation of decimal reciprocal unit", *Proc. IEEE Canadian Electrical and Computer Engineering (CCECE'07)*, Vancouver, British Columbia, Canada, pp. 1094-1097, Apr. 2007.

#### Chapter 8: Design and Implementation of A Radix-100 Decimal Division

• Y. Zhang, **D. Chen** and S. Ko, et al "Design and implementation of a radix-100 decimal division", *International Workshop on Multimedia Signal Processing and Transmission*, Seoul, Korea, pp. 123-126, Sep. 2009.

The following papers are also published, but not considered to be the part of this dissertation.

- D. Chen, B. Zhou, Z. Guo and P. Nilsson, "Design and implementation of reciprocal unit", 48th Midwest Symp. on Circuits and Systems (MWSCAS'05), Cincinnati, Ohio, pp. 1318-1321, Aug. 2005.

- A. Malik, **D. Chen** and S. Ko, et al "A study on the design trade-off analysis of floating-point adders in FPGAs," *Canadian J. Electrical and Computer Engineering*, Vol. 33, No. 3/4, pp. 169-175, Summer/Fall 2008.

- K. Muma, **D. Chen** and S. Ko, et al "Combining ESOP minimization with BDD-based decomposition for improved FPGA synthesis," *Canadian J. Electrical and Computer Engineering*, Vol. 33, No. 3/4, pp 177-182, Summer/Fall 2008.

- Y. Zhang, **D. Chen** and S. Ko, et al "A high performance pseudo-multi-core ECC processor over GF(2<sup>163</sup>)", *Proc. IEEE Symp. on Circuit and System (ISCAS'10)*, pp 701-704, May 2010.

- Y. Zhang, **D. Chen** and S. Ko, et al "A high performance ECC hardware implementation with instruction-level parallelism over GF(2<sup>163</sup>)", *Elsevier J. Microprocessors and Microsystems*, vol. 34, pp. 228-236, Apr. 2010.

# Part II Research Background

# Chapter 2

# Decimal Transcendental Arithmetic

This chapter provides background information and discusses related fundamental concepts about the DFP and DXP transcendental function computation described in this dissertation. Section 2.1 gives an overview of DFP standard specified in IEEE 754-2008, which includes DFP formats and encoding, DFP arithmetic operations, DFP rounding modes, DFP special values and exception handling. Section 2.2 presents the common issues of the decimal transcendental arithmetic design, which include 1) the computation of DFP transcendental operations; 2) different types of hardware methods and their main features; and 3) the considerations of hardware implementation of DFP transcendental arithmetic.

# 2.1 DFP Formats in IEEE 754-2008 Standard

The IEEE 754 standard for floating-point arithmetic is the most widely-used standard for floating-point computation, and is implemented for many microprocessor designs and software mathematical libraries. The current version, IEEE 754-2008 [8], is the revision to the original IEEE 754-1985 [52] standard for BFP arithmetic and IEEE 854-1987 [53] for radix-independent floating-point arithmetic. One of the most important revisions to IEEE 754-1985 is the introduction of DFP formats and operations, which includes:

- **DFP formats**: which consist of finite numbers (including signed zeros and subnormal numbers), infinities, and special not-a-number (NaN).

- **DFP arithmetic operations**: which include basic DFP arithmetic operations, two decimal-specific operations, different types of conversions and some recommended DFP operations (transcendental operation).

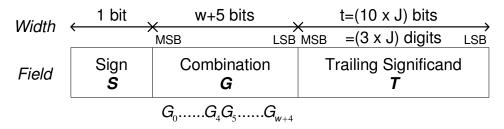

Figure 2.1: DFP interchange format with DPD encoding.

- **DFP rounding modes**: which include five rounding modes (roundTiesToEven (RNE), roundTiesToAway (RNA), roundTiesToPositive (RPI), roundTiesToNegative (RMI) and roundTowardZero (RNZ)) to guarantee the exactly or faithful rounded results for the inexact computation and conversion.

- **DFP exceptions handling**: which include the invalid operation, division by zero, overflow, underflow and inexact.

#### 2.1.1 DFP Formats and Encodings

The encodings for DFP operands allow for a range of positive and negative values together with values of  $\pm 0$ ,  $\pm \infty$ , and not-a-number (NaN). Three interchange DFP formats are specified in the IEEE 754-2008 standard, which includes a storage format (Decimal32) and two basic computational formats (Decimal64 and Decimal128) as follows:

- Storage format is an interchange format not required by DFP arithmetic. The standard defines one decimal storage floating-point format encoded in 32-bit (Decimal 32).

- Basic format is an interchange format available for DFP arithmetic. The standard defines two basic decimal computational floating-point format encoded in 64-bit (Decimal 64) and 128-bit (Decimal 128) respectively.

Figure 2.1 shows the basic DFP interchange format specified in the IEEE 754-2008 standard, which includes:

- 1-bit Sign Field: 1-bit field S, which indicates the sign of the number in the same way as BFP numbers.

- w+5-bit Combination Field: w+5-bit field G, and can be considered as two subfields: first, the five most significant bits (MSBs) of the Combination Field,  $G_0...G_4$ , is defined

Table 2.1: Decoding of the combination field.

| $G_0G_1G_2G_3G_4$ | Type      | Exponent MSBs (2-bit) | Coefficient MSD (4-bit) |

|-------------------|-----------|-----------------------|-------------------------|

| a b c d e         | $d_0 < 8$ | a b                   | 0 c d e                 |

| 11cde             | $d_0 > 7$ | c d                   | 100e                    |

| 11111             | Infinity  |                       |                         |

| 11110             | NaN       |                       |                         |

as one subfield, which 1) encodes two MSBs of the nonnegative biased exponent and the most significant digit (MSD) of the decimal significand,  $d_0$ , 2) indicates the Not-a-Number (NaN) and infinite number  $(\pm \infty)$ ; second, the remaining w-bit of Combination Field,  $G_5...G_{w+4}$ , is defined as a suffix to the two MSBs derived from  $G_0...G_4$ , which consists of w+2-bit nonnegative biased exponent. The whole encoded exponent is an unsigned binary integer with the largest unsigned value. The value of the exponent is calculated by subtracting an Exponent Bias from the value of the encoded exponent, in order to represent both negative and positive exponents. Table 2.1 shows the detail of the encoding for the 5-bit MSBs of the Combination Field,  $G_0...G_4$ , where a, b, c, d, e are used to represent the value (0 or 1) of  $G_0...G_4$ .

Packed Decimal (DPD) encoding [54] or Binary Integer Decimal (BID) encoding [55] in IEEE 754-2008. In this dissertation, the DPD encoding is chosen to represent Trailing Significand Field, as a suffix to the MSD derived from Combination Field to construct q-digit decimal significand,  $(q = 3 \times J + 1)$ . Trailing Significand Field  $(J \times 10\text{-bit})$  is a multiple of 10-bit, and the most significant group is on the left. Every 10-bit group represents three decimal digits, using DPD encoding and can be decoded to a 12-bit binary-coded decimal (BCD) representation. The DPD encoding has the advantage of straightforward decimal rounding and shifting, so it is usually used in the hardware implementations of decimal arithmetic units. The BID encoding has the advantage of using the current high-speed binary integer arithmetic logic unit (ALU) in the microprocessor, so it is usually used in the software implementations [55] for decimal computations. For more fundamental concepts of the BID encoding, refer

**Table 2.2:** Parameters in DFP interchange formats.

| Format Name                                           | Decimal32 | Decimal64 | Decimal128 |

|-------------------------------------------------------|-----------|-----------|------------|

| Storage Width (bit)                                   | 32        | 64        | 128        |

| Trailing significand field $(J \times 10\text{-bit})$ | 20        | 50        | 110        |

| Combination Field $(w+5-bit)$                         | 11        | 13        | 17         |

| Decimal Significand (q-digit)                         | 7         | 16        | 34         |

| Exponent bias                                         | 101       | 398       | 6176       |

| emax                                                  | +96       | +384      | +6144      |

| emin                                                  | -95       | -383      | -6143      |

to [8]. Table 2.2 provides important parameters used in the standard for different DFP interchange formats. In this dissertation, the DFP format in the DPD encoding is selected for all research works so that the decimal significand of a DFP operand can be decoded to binary-coded decimal (BCD) representation in hardware.

In the IEEE 754-2008 standard, the value of the decimal significand is a non-normalized unsigned decimal fraction in the form of  $d_0.d_1d_2...d_{q-1}$ ,  $0 \le d_i < 10$ . In decimal computer arithmetic, the decimal significand is usually represented as an integer. The value of a DFP number is represented as follows:

$$v = (-1)^S \times 10^e \times significand \tag{2.1}$$

In (2.1), S is the sign of the DFP number; the value of the real exponent e is in the range of  $(emin-q+1) \le e \le (emax-q+1)$ ; and the decimal significand, significand, is represented as a non-normalized decimal integer. Since the decimal significand is non-normalized, DFP number may have multiple representations, which is called DFP number's **cohort**. For example [8], if significand is a multiple of 100 and e is less than its maximum allowed value, then (S, e, significand) and (S, e+2, significand/100) are two representations for the same DFP number which are members of the same **cohort**.

Based on an example shown in [56], we illustrate how the decimal number  $v = -8.35 = -835 \times 10^{-2}$  is encoded in the Decimal64 format using the DPD encoding.

- 1. The decimal significand can be represented using BCD encoding, significand = 00000000  $00000835_{radix-10}$  except the most significand digit (MSD), the remaining fifteen decimal digits are represented using the 50 bits DPD encoding (T = 000...001000111101).

- 2. The w+5-bit combination field G=0100010001100 where the two MSBs and eight least significand bits (LSBs) of G are from the biased exponent e, and the middle three bits of G are from the MSD of the significand.

- 3. The sign bit S=1 represents the negative DPF number, thus, the representation of DFP number  $v=-835\times10^{-2}$  in the DPD format is:  $10100010001100000...001000111101_{radix-2}$ .

The interpretation of the combination of the various fields in a DFP **special value** is as follows:

- Not-a-Number (NaN): If  $G_0$  through  $G_4$  are 11111 (refer to Table 2.1), then v is NaN regardless of S. Furthermore, if  $G_5$  is 1, then v is a signaling NaN (sNaN); otherwise, v is a quiet NaN (qNaN). The remaining bits of G are ignored, and T constitutes the NaN's payload, which can be used to distinguish various NaNs.

- Infinite number: If  $G_0$  through  $G_4$  are 11110, then v represents  $+\infty$  or  $-\infty$ , according to the sign bit. The values of the remaining bits in G, and T, are ignored.

- Overflow: If DFP numbers with absolute values are larger than the largest DFP number  $(|v_{\text{max}}| = (10^q 1) \times 10^{emax-q+1})$  then overflow occurs.

- Underflow and Subnormal: If DFP number is less than the smallest DFP number  $(|v_{\min}| = 10^{emin-q+1})$  then underflow occurs. If the absolute value of DFP number is less than  $10^{emin}$  and larger than  $10^{emin-q+1}$ , it produces subnormal.

- Normal number: The remaining exponent values and significands represent normal numbers.

# 2.1.2 DFP Arithmetic Operations

The hardware implementations of DFP arithmetic units, which are compliant with the IEEE 754-2008 standard, must provide support for at least one basic computational format (Decimal64 and/or Decimal128). For each of specified DFP operation, first, DFP operands with the external format (DPD or BID) are converted to the internal format (BCD or binary),

accompanied with sign bit, unsigned binary exponent and exception flag; second, the DFP operation is computed to produce an intermediate result correct to infinite precision without rounding; third, the intermediate result is rounded to a target finite digit-width of decimal significand; fourth, if necessary, the rounded results are packaged back to the destination's DFP format. The decimal arithmetic operations specified in IEEE 754-2008 are mainly classified as follows:

- Basic DFP arithmetic operations: include DFP addition, subtraction, multiplication, division, square-root and fused multiply addition, which are usually implemented in most today's microprocessors. The standard recommends to provide exactly rounded DFP computation results for these basic DFP arithmetic operations.

- Two decimal-specific DFP operations: SameQuantum $(v_1,v_2)$  compares the exponents of  $v_1$  and  $v_2$  and the output true if they are the same and false if they are different. Quantize $(v_1,v_2)$  generates a DFP number that has the same value as  $v_1$  and the same exponent as  $v_2$ , unless rounding or an exception occurs.

- DFP comparison operations: Comparison $(v_1,v_2)$  compares the numerical values of  $v_1$  and  $v_2$ . The comparison operations do not differentiate the redundant representations of the same number.

- **DFP conversion operations:** Conversion(v) supports the conversions among the decimal integer, BFP and DFP formats. The conversions between DFP and BFP must be exactly rounded.

- Recommended DFP operations: decimal transcendental arithmetic operations are defined as recommended operations, such as logarithms, exponentials, trigonometric functions as so on. The standard recommends to provide exactly rounded DFP computation results for these transcendental functions.

Since a DFP number might have multiple representations (DFP number's cohort), the value of a DFP result is not only determined by the operation and the DFP operands' values, but also depends on the selection of the proper representation of DFP numbers. Because of this characteristic, the standard defines the preferred representation exponent, which refers to a required exponent (quantum). The selection of a particular representation for a DFP

result is dependent on whether the representation of operation result is exact or inexact:

- Exact DFP operation result: If the DFP arithmetic operation result is exact, the cohort member is selected based on the preferred exponent (quantum) for a DFP result of that operation. The preferred exponents have been specified in the standard for different operations. For DFP addition, if the result is exact, the preferred exponent is the minimum quantum of the operands for a DFP addition, that is  $e_R = \min(e_{v_1}, e_{v_2})$ .

- Inexact DFP operation result: If the DFP arithmetic operation (except for quantize operation) result is inexact, the cohort member of the least possible exponent is used to get the maximum number of significant digits. For DFP addition, if the result is inexact, the preferred exponent may be decreased to keep the MSD of decimal significand not zero.

#### 2.1.3 DFP Rounding Modes

Rounding is often done on purpose to obtain a finite number that can exactly represent the closest value to the exact infinite result. In general, since the result of floating-point operation is not a finite number, the inexact result must be converted to a close representable floating-point number in a given finite precision format, which is referred as rounding. The IEEE 754-2008 standard specifies five types of active rounding modes for the DFP arithmetic:

- roundTiesToEven: rounds the result to the nearest representable DFP number. The number with an even least significant digit (LSD) should be selected, if a tie occurs.

- roundTiesToAway: rounds the result to the nearest representable DFP number.

The number with a larger magnitude should be selected, if a tie occurs.

- roundTiesToPositive: rounds the result toward positive infinity. The closest DFP number, which is greater than the exact result, should be selected.

- roundTiesToNegative: rounds the result toward negative infinity. The closest DFP number, which is lower than the exact result, should be selected.

- roundTowardZero: truncates the result. The closest DFP number, which is lower in magnitude than the exact result, should be selected.

#### 2.1.4 Exception Handling

The exceptions happen when the result of an operation is not the expected floating-point number. In this case, the default non-stop exception handling delivers a default result, and raises the corresponding status flag for exceptions. The IEEE 754-2008 standard specifics five kinds of exceptions, shown as follows:

- Invalid operation: is signaled when there is no usefully definable DFP result. The invalid operation usually happens if the operand is invalid, such as the NaN or infinite operand, or if the operation is invalid, such as quare-root of negative operands. In this case, the default result is a qNaN.

- Division by zero: is signaled only if an operation with finite operands produces an exact infinite result. For example, the dividend is a finite non-zero operand and the divisor is zero. The default result may be plus or minus infinity.

- Overflow: is signaled if the magnitude of a result exceeds the largest finite representable number in the format of the operation. The default result may be plus or minus infinity, or plus or minus the largest representable number in the format, depending on the rounding mode.

- Underflow: is signaled if the magnitude of a result exceeds the smallest finite representable number in the format of the operation. This is detected before rounding examining the precision digits and the exponent range. The default result may be zero, a subnormal number or a smallest finite number representable in the format.

- Inexact: is signaled if the rounded result of an operation differs from the infinite precision result. The default result is the rounded or the overflowed result.

# 2.2 Decimal Transcendental Unit Design

In this section, some considerations about the design and implementation of DFP and DXP transcendental arithmetic units are presented. First, the description of DFP transcendental operations covered in this dissertation is described in terms of the exception handling, the range reduction, and the rounding. Second, different types of BFP hardware-oriented

**Table 2.3:** DFP arithmetic functions included in this dissertation.

| Operations      | Domain               | Exceptions                                      |

|-----------------|----------------------|-------------------------------------------------|

| log10           | $[0,+\infty]$        | invalid operation, divideByZero, inexact        |

| exp10           | $[-\infty, +\infty]$ | invalid operation, overflow, underflow, inexact |

| rootn(v,-1)     | $[-\infty, +\infty]$ | invalid operation, divideByZero                 |

| $div(v_1, v_2)$ |                      | overflow, underflow, inexact                    |

methods and their main features are presented based on the summary in [32, 57].

#### 2.2.1 Some Details of DFP Transcendental Operations

In this dissertation, the decimal arithmetic functions include the DFP and DXP based-10 logarithm (log10) and the antilogarithm (exp10), the DXP reciprocal (rootb(v,-1)) and the DXP division ( $div(v_1, v_2)$ ) as shown in Table 2.3, where v presents the DFP or DXP operands. More decimal transcendental functions (not covered in this dissertation) are specified in the IEEE 754-2008 standard as the recommended DFP operations [8].

#### **Exception Handling**

All the exceptions for the each specific transcendental function are shown in Table 2.3. Details about the exception handling of the based-10 logarithm and antilogarithm operations, can be referred to Section 5.2.1 and Section 6.2.1. However, since the DFP computation for reciprocal and division operations is not covered in this dissertation, more details about the exception handling of these two operations can be referred to the description in [8, 28].

#### Range Reduction

To compute a DFP transcendental function, f(v), over a range  $v \in [a, b]$  with a given target precision requirement, the range reduction leads to compute the transcendental function in a smaller interval, [a', b'], which can simplify the function approximation, reduce the size of tables, and achieve the faster speed for the hardware implementation [32]. Table 2.4 presents the reduced intervals we will use throughout this dissertation for approximating

**Table 2.4:** Reduced intervals for considered transcendental functions.

| Functions                     | Domain               | Reduced Interval |

|-------------------------------|----------------------|------------------|

| $\log_{10}(v)$                | $[0,+\infty]$        | [0.1, 1)         |

| $10^{v}$                      | $[-\infty, +\infty]$ | (-1,1)           |

| $v^{-1} \text{ and } v_1/v_2$ | $[-\infty, +\infty]$ | [0.1, 1)         |

considered DFP transcendental functions. For the DFP based-10 logarithm operation, the non-normalized decimal significand of DFP operand, which is in the range of  $[0, +\infty]$ , should be adjusted into the range of [0.1, 1) before it is computed. For the DFP antilogarithm operation, the non-uniform decimal significand of DFP operand, which is in the range of  $[-\infty, +\infty]$ , should be adjusted into the range of (-1, 1) before it is computed. For DFP reciprocal and division operations, the non-uniform decimal significand of DFP operand, which is in the range of  $[-\infty, +\infty]$ , should be adjusted into the range of [0.1, 1) before it is computed [28]. More details about the range reduction of DFP based-10 logarithm and antilogarithm operations are presented in Section 5.2.2 and Section 6.2.2.

#### Rounding

The arithmetic operation in systems must behave as if the results are first computed exactly with infinite precision, and then rounded. In terms of exact rounding, the operation result provided by an algorithm computing a certain operation is always the floating-point number which is closest to the exact result. Another frequently used notion is faithful rounding, which happens when the intermediate result is in the interval between the two closest floating-point numbers surround the exact result. The unit in the last place ulp, denotes the absolute value of the difference between the two numbers in a given finite numerical representation which are closest to a given number [58]. It is used as a measurement of precision in numeric calculations. If the floating-point arithmetic computation error from the exact result is less than  $0.5 \ ulp$ , it means that the exactly rounded result in the round-to-nearest rounding mode is always provided. On the other hand, the faithful rounding means that the computation error from the exact result is less than one unit in the last place  $(1 \ ulp)$  [57].

For DFP basic arithmetic operations, such as addition, multiplication, division and square