## CORE Provided by University of Saskatchewan's Research Archiv

# HYBRID SWITCHING: CONVERGING PACKET AND TDM FLOWS IN A SINGLE PLATFORM

A Thesis Submitted to the College of

Graduate Studies and Research

In Partial Fulfillment of the Requirements

For the Degree of Master of Science

In the Department of Electrical and Computer Engineering

University of Saskatchewan

Saskatoon

By

**Roshan Parajuli**

© Copyright Roshan Parajuli, February, 2009. All rights reserved.

### **PERMISSION TO USE**

In presenting this thesis in partial fulfilment of the requirements for a Postgraduate degree from the University of Saskatchewan, I agree that the Libraries of this University may make it freely available for inspection. I further agree that permission for copying of this thesis in any manner, in whole or in part, for scholarly purposes may be granted by the professor or professors who supervised my thesis work or, in their absence, by the Head of the Department or the Dean of the College in which my thesis work was done. It is understood that any copying or publication or use of this thesis or parts thereof for financial gain shall not be allowed without my written permission. It is also understood that due recognition shall be given to me and to the University of Saskatchewan in any scholarly use which may be made of any material in my thesis.

Requests for permission to copy or to make other use of material in this thesis in whole or part should be addressed to:

Department of the Department of Electrical and Computer Engineering 57 Campus Drive Saskatoon, SK, S7N 5A9, Canada Phone: (306) 966-5380 Fax: (306) 966-5407

## ABSTRACT

Optical fibers have brought fast and reliable data transmission to today's network. The immense fiber build-out over the last few years has generated a wide array of new access technologies, transport and network protocols, and next-generation services in the Local Area Network (LAN), Metropolitan Area Network (MAN), and Wide Area Network (WAN). All these different technologies, protocols, and services were introduced to address particular telecommunication needs. To remain competitive in the market, the service providers must offer most of these services, while maintaining their own profitability. However, offering a large variety of equipment, protocols, and services posses a big challenge for service carriers because it requires a huge investment in different technology platforms, lots of training of staff, and the management of all these networks.

In today's network, service providers use SONET (Synchronous Optical NETwork) as a basic TDM (Time Division Multiplexing) transport network. SONET was primarily designed to carry voice traffic from telephone networks. However, with the explosion of traffic in the Internet, the same SONET based TDM network is optimized to support increasing demand for packet based Internet network services (data, voice, video, teleconference etc.) at access networks and LANs. Therefore the service providers need to support their Internet Protocol (IP) infrastructure as well as in the legacy telephony infrastructure. Supporting both TDM and packet services in the present condition needs multilayer operations which is complex, expensive, and difficult to manage. A hybrid switch is a novel architecture that combines packets (IP) and TDM switching in a unified access platform and provides seamless integration of access networks and LANs with MAN/WAN networks. The ability to fully integrate these two capabilities in a single chassis will allow service providers to deploy a more cost effective and flexible architecture that can support a variety of different services.

This thesis develops a hybrid switch which is capable of offering bundled services for TDM switching and packet routing. This is done by dividing the switch's bandwidth into VT1.5 (Virtual Tributary -1.5) channels and providing SONET based signaling for routing the data and controlling the switch's resources. The switch is a TDM based architecture which allows each switch's port to be independently configured for any mixture of packet and TDM traffic, including 100% packet and 100% TDM. This switch allows service providers to simplify their edge networks by consolidating the number of separate boxes needed to provide fast and reliable access. This switch also reduces the number of network management systems needed, and decreases the resources needed to install, provision and maintain the network because of its ability to "collapse" two network layers into one platform.

The scope of this thesis includes system architecture, logic implementation, and verification testing, and performance evaluation of the hybrid switch. The architecture consists of ingress/egress ports, an arbiter and a crossbar. Data from ingress ports is carried to the egress ports via VT1.5 channels which are switched at the cross point of the crossbar. The crossbar setup and channel assignments at ingress port are done by the arbiter. The design was tested by simulation and the hardware cost was estimated. The performance results showed that the switch is non-blocking, provide differentiated service, and has an overall effective throughput of 80%. This result is a significant step towards the goal of building a switch that can support multiprotocol and provide different network capabilities into one platform. The long-term goal of this project is to develop a prototype of the hybrid switch with broadband capability.

### ACKNOWLEDGEMENTS

I would like to express my gratitude to my supervisor Dr. Carl McCrosky for his support, guidance, and encouragement throughout the course of this research work. I greatly appreciate his timely thesis revision and critical feedback. I would also like to thank Telecommunication Research Laboratories (TRLabs) for providing financial support and other resources for this research. Jack Hanson, Vera ljubovic, Andrew Kostiuk, and the rest of the students and staffs at TRLabs, Saskatoon, are all thanked for their time and help. I am also thankful to Dr. Eric Salt, Dr. Ron Bolton, Dr. Li Chen, Dr. David Dodds, and Dr. Daniel Teng who helped me at some point of time during this research. I also express sincere thanks to the committee members, Dr. Li Chen, and Dr. Wahid Khan for their valuable comments and suggestion in the preparation of this thesis. I would also like to thank Dr. Simone Ludwig for acting as my external examiner.

I am grateful to my friends in Saskatoon, as well as at the University of Saskatchewan for their constant support and encouragement. I would like to give special thanks to Prem Sharma, Nirmala Sharma, Sumit Paudyal, Dipendra Rai, Umesh Gyawali, Jeeva Paudyal, Aseem Sharma, and Edwin Gono Santosa for their help in many ways. I have a very special feeling for my lovely wife, Shrijana Dhakal, who in many ways helped me during my Master's program. Her consistent support, encouragement, and understanding are highly appreciated.

I wish to dedicate my work to my loving parents, Balika Parajuli and Gyan Prasad Parajuli. Without their encouragement and support I would not have come this far.

## **TABLE OF CONTENTS**

| PERMISSION TO USE                                        | i  |

|----------------------------------------------------------|----|

| ABSTRACT                                                 | ii |

| ACKNOWLEDGEMENTS                                         | iv |

| TABLE OF CONTENTS                                        | v  |

| LIST OF FIGURES                                          |    |

| LIST OF TABLES                                           |    |

| LIST OF ABBREVIATIONS                                    |    |

|                                                          |    |

| 1) Introduction                                          | 1  |

| 1.1 Motivation for Research                              |    |

| 1.2 Background of Hybrid switching                       |    |

| 1.3 Objectives                                           |    |

| 1.4 Thesis organization                                  |    |

|                                                          |    |

| 2) Hybrid Switching Architecture Overview                |    |

| 2.1 Hybrid Switching Concept                             |    |

| 2.2 System Overview                                      |    |

| 2.3 Data Path                                            |    |

| 2.3.1 Class of Service (CoS)                             |    |

| 2.4 Arbiter                                              |    |

| 2.5 Control Paths                                        |    |

| 2.5.1 Control Path for Carrying Flow Requests            |    |

| 2.5.2 Control Paths for Carrying Time Slot Assignments   | 17 |

| 3) SONET Signaling, Data Paths and Control Paths         | 18 |

| 3.1 SONET Signaling                                      |    |

| 3.1.1 The SONET Frame                                    |    |

| 3.1.2 SONET Bandwidth                                    |    |

| 3.1.3 The STS-N Frame                                    |    |

| 3.1.4 SONET Virtual Tributaries (VTs)                    | 21 |

| 3.2 Packet Queuing Issues and Virtual Output Queue (VOQ) | 21 |

| 3.3 Data Path Architecture                               |    |

| 3.3.1 Ingress Ports                                      | 23 |

| 3.3.2 Ingress Packet Queues                              | 23 |

| 3.3.3 TDM Filler                                         |    |

| 3.3.4 Switch Core                                        |    |

| 3.3.5 TDM Extractor                                      |    |

| 3.3.6 Packet Assembler                                   | 27 |

| 3.3.7 Egress Packet FIFO                       |    |

|------------------------------------------------|----|

| 3.4 Control Paths                              |    |

| 3.4.1 Flow Requests                            |    |

| 3.4.2 Ingress Time Slot Assignment             |    |

| 3.4.3 Egress Time Slot Assignment              | 29 |

| 3.4.4 Switch Time Slot Assignment              |    |

| 3.4.5 Packet Channel Assignment                | 30 |

| 3.4.6 SONET Channel Assignment                 | 30 |

| 4) Arbiter Bandwidth Allocation                |    |

| 4.1 Introduction                               |    |

| 4.2 Arbitration Goal                           |    |

| 4.2.1 Priority                                 |    |

| 4.2.2 Fairness                                 |    |

| 4.2.3 Efficient Bandwidth Utilization          |    |

| 4.3 Arbiter Block                              |    |

| 4.3.1 Request Matrix                           |    |

| 4.3.2 Fair Proportional Algorithm (FPA)        |    |

| 4.3.3 Time Slot Algorithm (TSA)                |    |

| 4.3.3.1 Goal                                   |    |

| 4.3.3.2 Ingress/Egress Open                    |    |

| 4.3.3.3 Open Time Slot                         |    |

| 4.3.3.4 Masking Slot                           |    |

| 4.4 Arbiter Design Alternatives                | 46 |

| 4.4.1 Software Approach                        | 46 |

| 4.4.1.1 NIOS II Processor                      | 47 |

| 4.4.1.2 Hardware and Software Partitioning     | 47 |

| 4.4.1.3 Software Design Process                | 48 |

| 4.4.1.4 Software Arbitration Process           | 49 |

| 4.4.1.5 Advantages of Software Based Approach  | 50 |

| 4.4.1.6 Implementation Results                 | 51 |

| 4.4.1.7 Limitations of Software Based Approach | 52 |

| 4.4.2 Hardware Approach                        |    |

| 4.4.2.1 Hardware Architecture                  | 52 |

| 4.4.2.2 Advantages of Hardware Approach        |    |

| 4.5 Arbiter Implementation Summary             | 54 |

| 5) Design Verification and Testing             | 56 |

| 5. 1 Introduction                              |    |

| 5.2 Simulation and Verification Process        | 56 |

| 5.3 Verification and Testing                   |    |

| 5.4 Summary of the Verification                | 60 |

| 6) Performance Results and Discussions         |    |

| 6.1 Introduction                               |    |

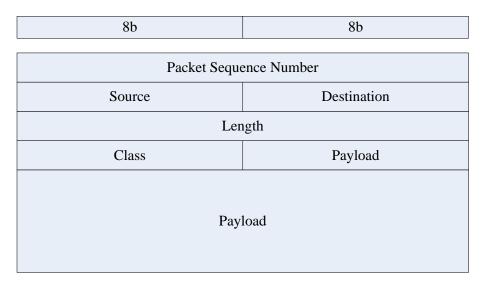

|            | 6.2 Simplified IP Packet Structure                                                     | 61       |

|------------|----------------------------------------------------------------------------------------|----------|

|            | 6.3 Load Model                                                                         | 61       |

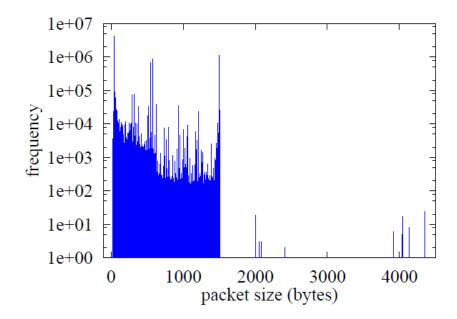

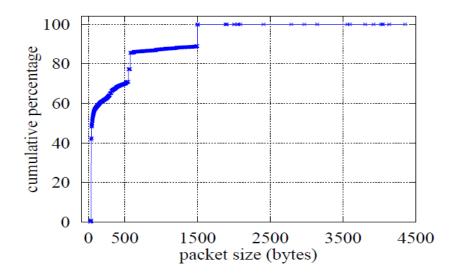

|            | 6.3.1 Distribution of IP Packets by Size                                               | 63       |

|            | 6.3.2 Distribution of IP Packets by Class of Service (CoS)                             | 64       |

|            | 6.3.3 Distribution of IP Packets by Offered Load                                       | 65       |

|            | 6.3.4 Distribution of IP Packets by Hotspot Port                                       | 65       |

|            | 6.4 Performance Matrices                                                               | 66       |

|            | 6.4.1 Throughput                                                                       | 66       |

|            | 6.4.2 Queue Depth Vs Arbitration Cycles                                                | 67       |

|            | 6.4.3 Non-blocking and Uniform Loads                                                   | 67       |

|            | 6.5 Simulations and Performance Results                                                |          |

|            | 6.5.1 Objectives                                                                       | 68       |

|            | 6.5.2 The Simulations                                                                  | 68       |

|            | 6.5.3 Determining the Operating Load                                                   | 69       |

|            | 6.5.4 Results and Discussions                                                          |          |

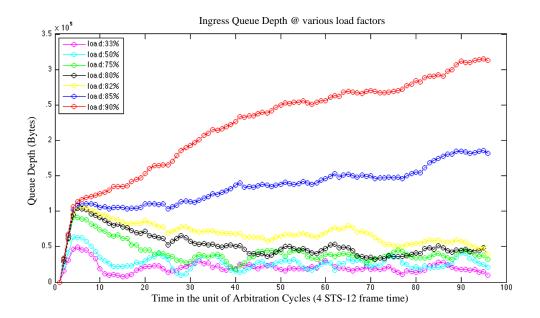

|            | 6.5.4.1 Variation of Queue Depth with Offered Load for Uniform                         |          |

|            | Traffic                                                                                | 70       |

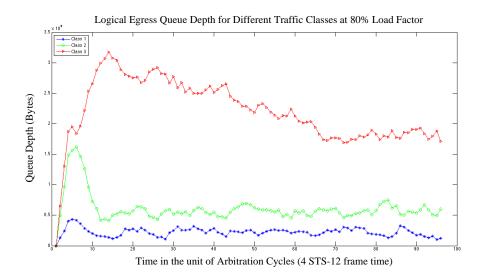

|            | 6.5.4.2 Variation of Queue Depth with Packet Classes for                               |          |

|            | Uniform Traffic                                                                        |          |

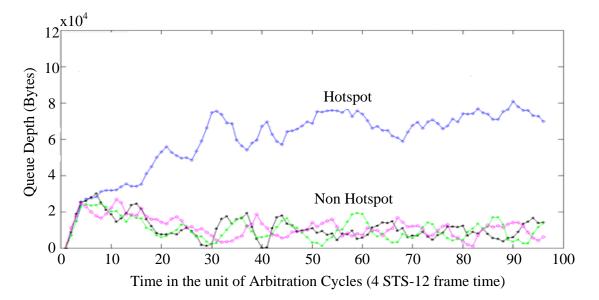

|            | 6.5.4.3 Variation of Queue Depth with Hotspot Port                                     |          |

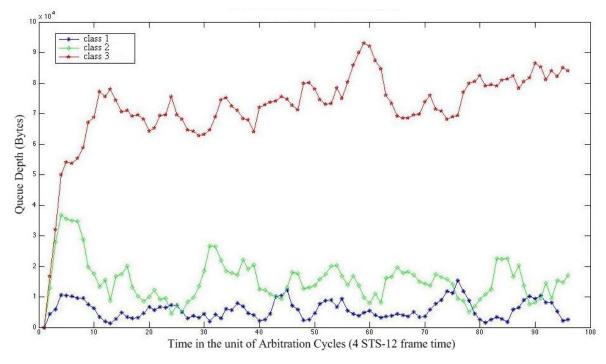

|            | 6.5.4.4 Variation of Queue Depth with Hotspot Classes                                  | 73       |

|            | 6.5.5 Summary of the Results                                                           | 74       |

| 7)         | <b>FPGA mapping: Logic Utilization, Delay and Power Estimation</b><br>7.1 Introduction |          |

|            | 7.2 Field Programmable Gate Arrays (FPGAs)                                             | 76       |

|            | 7.2.1 Logic Utilization                                                                | 77       |

|            | 7.2.2 Propagation Delay                                                                | 77       |

|            | 7.2.3 Power Consumption                                                                |          |

|            | 7.3 FPGA Cost Estimation Methodology                                                   |          |

|            | 7.4 Synthesis Result and Analysis                                                      |          |

|            | 7.5 Summary of FPGA Mapping                                                            | 82       |

|            |                                                                                        |          |

| 8)         | Conclusions and Future work                                                            |          |

|            | 8.1 Conclusions                                                                        |          |

|            | 8.2 Thesis Contributions                                                               |          |

|            | 8.3 Future Work                                                                        |          |

|            | 8.3.1 Prototype Fabrication in FPGA                                                    |          |

|            | 8.3.2 Simulation for TDM and Packet Traffic                                            |          |

|            | 8.3.3 Switch with Speedup                                                              | 86       |

|            | 8.3.4 Broadband Switching by Scaling Up Granularity                                    | c        |

|            | to STS-1                                                                               |          |

|            | 8.3.5 Search for an Improved Arbitration Scheme                                        | 87       |

| <b>0</b> ) | References                                                                             | <u> </u> |

| 71         |                                                                                        | . 00     |

## **LIST OF FIGURES**

| Figure 1.1 Traditional LAN and MAN Network                         | 5  |

|--------------------------------------------------------------------|----|

| Figure 1.2 Hybrid Switching LAN and MAN Network                    | 6  |

| Figure 2.1 Hybrid Switching Model                                  |    |

| Figure 2.2 Hybrid Switching Block                                  | 10 |

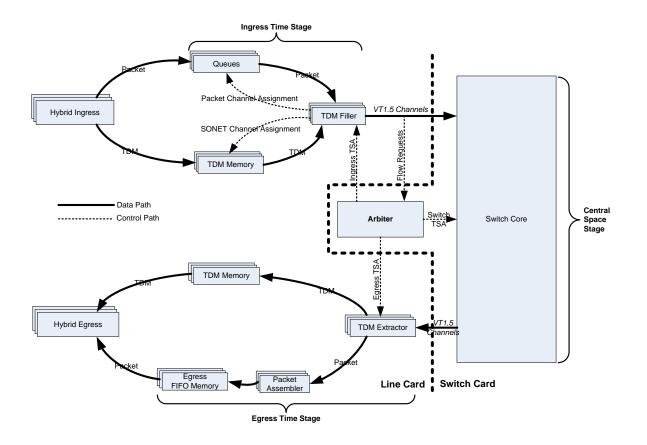

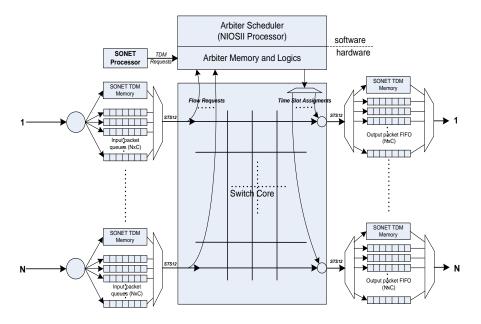

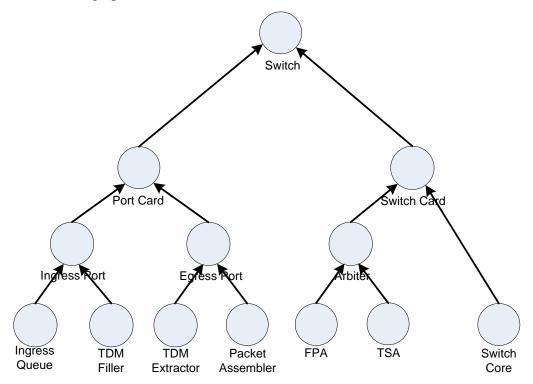

| Figure 2.3 Block diagram of Hybrid Switch Architecture             | 11 |

| Figure 2.4 Arbiter Block Diagram                                   | 15 |

| Figure 3.1 SONET Frame                                             | 19 |

| Figure 3.2 Formation of STS-3 frame by byte interleaving           | 20 |

| Figure 3.3 Virtual Output Queues for N destinations and C classes  | 24 |

| Figure 3.4 TDM Filler Block                                        | 24 |

| Figure 3.5 Switch Core Block                                       | 25 |

| Figure 3.6 TDM Extractor Block                                     | 26 |

| Figure 3.7 Packet Assemblers and FIFO Memory Blocks                | 27 |

| Figure 4.1 Arbiter Functional Block Diagram                        |    |

| Figure 4.2 Arbiter Flow Chart                                      |    |

| Figure 4.3 Switch Flow Matrix Defining Time Slot Assignment Goal   | 40 |

| Figure 4.4 Time Slot Assignment Logic Block                        | 41 |

| Figure 4.5 Ingress/Egress Open Vector                              |    |

| Figure 4.6 Formation of OTS Vector                                 |    |

| Figure 4.7 Masking Slot Finding Process                            |    |

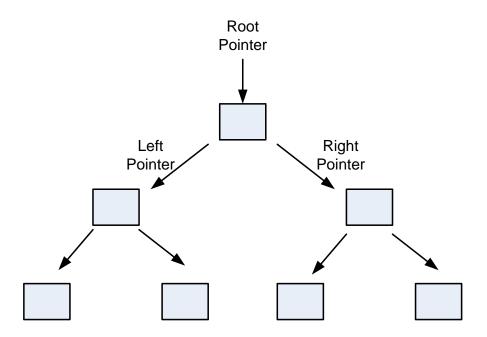

| Figure 4.8 Binary Tree                                             | 44 |

| Figure 4.9 Binary Add Algorithm Block                              | 45 |

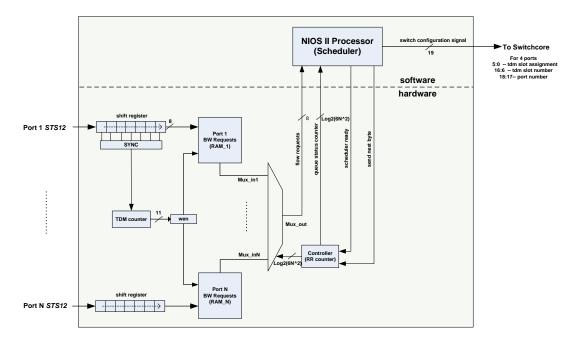

| Figure 4.10 Arbiter Module with Software and Hardware Partitioning |    |

| Figure 4.11 Detailed Arbiter Hardware/Software Partitioning        |    |

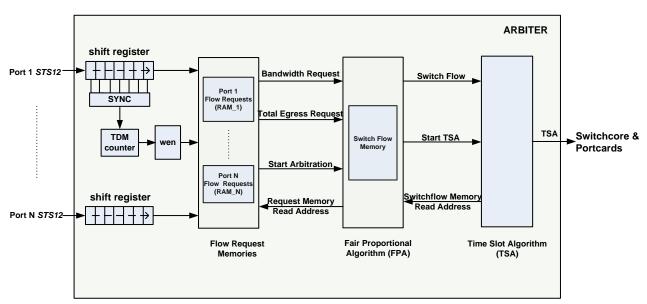

| Figure 4.12 Arbiter Hardware Block                                 |    |

| Figure 5.1 Simulation Process for Design Verification              | 57 |

| Figure 6.1 Structure of IP Packet Generated by Load Model                            | 62 |

|--------------------------------------------------------------------------------------|----|

| Figure 6.2 Internet Packet Distributions: Relative Frequency of Various Sizes        | 64 |

| Figure 6.3 Internet Packet Distribution: Accumulated Distribution                    | 64 |

| Figure 6.4 Ingress Queue Length for Various Load Factors                             | 70 |

| Figure 6.5 Egress Queue Length for Various Load Classes of Traffic at Operating Load | 71 |

| Figure 6.6 Egress Queue Length for Various Load Classes of Traffic at Operating Load | 73 |

| Figure 6.7 Egress Queue Length for Various Classes of Hotspot Traffic                | 74 |

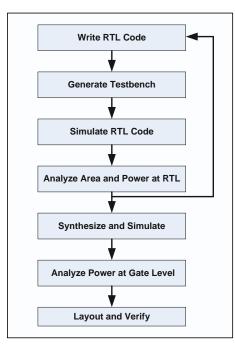

| Figure 7.1 RTL Area and Power Analysis in IC Design Flow                             | 79 |

## LIST OF TABLES

| Table 3.1 SONET Virtual Tributaries                             | 21 |

|-----------------------------------------------------------------|----|

| Table 4.1 Request Matrix for Class 1 Traffic                    | 37 |

| Table 4.2 Converting Request Matrix to Column Grant Matrix      | 39 |

| Table 4.3 Converting Column Grant Matrix to Switch Flow Matrix  | 39 |

| Table 4.4 Arbiter Timing Result for Software Implementation     | 51 |

| Table 7.1 FPGA Resource Utilization Table for 4x4 Hybrid Switch | 80 |

| Table 7.2 Scale-up Cost for Hybrid Switch                       | 81 |

|                                                                 |    |

## **LIST OF ABBREVIATIONS**

| ADM    | Add-Drop Multiplexer                    |

|--------|-----------------------------------------|

| ASIC   | Application Specific Integrated Circuit |

| ATM    | Asynchronous Transfer Mode              |

| CoS    | Class of Service                        |

| CIR    | Committed Information Rate              |

| CLB    | Configurable Logic Block                |

| DWDM   | Dense Wave Division Multiplexing        |

| DUT    | Device Under Test                       |

| EIR    | Extended Information Rate               |

| FPA    | Fair Proportional Algorithm             |

| FPGA   | Field Programmable Gate Arrays          |

| FIFO   | First In First Out                      |

| FR     | Frame Relay                             |

| HDL    | Hardware Descriptive Language           |

| HoL    | Head of Line                            |

| IB-VOQ | Ingress Buffered Virtual Output Queue   |

| IC     | Integrated Circuit                      |

| IP     | Internet Protocol                       |

| LAN    | Local Area Network                      |

| LE     | Logic Elements                          |

| LUT    | LookUp Table                            |

| MSS    | Maximum Segment Size                    |

| MTU    | Maximum Transmission Unit               |

| MAN    | Metropolitan Area Network               |

| MPLS   | Multiprotocol Label Switching           |

|        |                                         |

| OTS   | Open Time Slot                    |  |  |

|-------|-----------------------------------|--|--|

| OQ    | Output Queue                      |  |  |

| РОН   | Path OverHead                     |  |  |

| POTS  | Plain Old Telephone Service       |  |  |

| PSTN  | Public Switched Telephone Network |  |  |

| QoS   | Quality of Service                |  |  |

| RAM   | Random Access Memory              |  |  |

| RTL   | Register Transfer Level           |  |  |

| SLA   | Service Level Agreement           |  |  |

| SONET | Synchronous Optical NETwork       |  |  |

| SPE   | Synchronous Payload Envelope      |  |  |

| STS   | Synchronous Transfer Signal       |  |  |

| TDM   | Time Division Multiplication      |  |  |

| ТОН   | Time OverHead                     |  |  |

| TSA   | Time Slot Algorithm               |  |  |

| ТСР   | Transport Control Protocol        |  |  |

| VOQ   | Virtual Output Queue              |  |  |

| VT    | Virtual Tributary                 |  |  |

| WAN   | Wide Area Network                 |  |  |

## Chapter 1 Introduction

Communications of voice, video and data has experienced several technological revolutions in last two or three decades. One of the greatest inventions of recent years is the Internet. The Internet has had phenomenal success, growing from a small research network to a global network that we use on a daily basis. The Internet is a packet based network. When a host wants to communicate with other hosts, it uses the Internet Protocol (IP) to place information in packets, which are then sent to the nearest router. The router stores, and then forwards these packets to the next hop. Through hop-by-hop routing, packets find their way to the desired destination. This is called packet switching. With this communication technique, link bandwidth is shared among many information flows, and these flows are statistically multiplexed on the link.

To keep up with the explosive demand for bandwidth as well as to adhere to Service Level Agreements (SLAs) for a growing number of mature business applications on the Internet, network switches must be both faster and smarter. These switches must not only simply terminate high-speed optical connections but also must switch a large number of connections from Dense Wavelength Division Multiplexing (DWDM) transport systems [1]. They must provide guarantees on parameters such as bandwidth, latency, loss rate, and jitter, which are not supported by current best-effort switch architectures. Finally, they must provide a path to migrate to Multiprotocol Label Switching (MPLS) based networks without abandoning existing investments in the legacy networks such as Synchronous Optical NETwork (SONET) and Frame Relay (FR).

Time division multiplexing (TDM) is a multiplexing technique that divides a circuit into multiple channels based on time. The technique is associated with telephone company voice services. TDM was designed to deliver a steady stream of digitized voice. The data rate for each channel is exactly what is needed to carry a digitized voice which is 64 Kbps. While companies have long used TDM circuits for both voice and data, TDM circuits are not ideal for data because data tends to be bursty. The repeating time slots do a good job at delivering the streaming bits of digitized voice, but data bursts fill up the slots unevenly. When there is no data to send, bandwidth goes unused. When data bursts, there is usually not enough bandwidth.

In order to support traditional TDM based telephone network and packet based internet network, the service provider must have a multi-layer architecture; one layer supporting the packet based internet traffic while the other layer supporting the TDM based voice traffic. To compete on market, the service providers must provision all these services by squeezing as much expense as possible out of serving provisioning and support. However, supporting both types of services in today's multilayer architecture is expensive, inefficient, complex, and difficult to manage and troubleshoot.

This thesis describes a hybrid switch architecture designed to address these problems and provide enhanced flexibility at significantly reduced cost. We propose a switching method suitable for mapping packet based traffic into TDM time slots and to consequently allow simultaneous switching of packets and TDM traffic on the same switching platform. In this architecture TDM or packet data is mapped to TDM channels, enabling TDM switches to be used in the switch fabric of a router. This switching architecture provides lower cost TDM and packet switching and protects the investment already made in the legacy technology (principally SONET) while enabling new investments in both TDM switching and packet switching. In addition, the proposed hybrid packet/TDM architecture is straightforward and offers high speed data transfer. Because of its multiservice capability of handling both packets and TDM traffic, scalability, and support for quality of service, the switch architecture is directly applicable to at least the following areas:

- ✤ simplified networks,

- unified packet and TDM based circuit switching platforms,

- ✤ cost-effective delivery of multiple services on one platform,

- ✤ capacity to increase bandwidth and add new services,

- optimized used of physical space,

- ✤ high end enterprise applications, and

- ✤ easy installation and operation.

#### **1.1 Motivation for Research**

Over the last decade, through the combination of telecommunication market deregulation, economic globalization, and the Internet revolution, we have witnessed the emergence of a range of novel communication services for both residential and enterprise customers. IP-based applications and the deployment of IP technology not only increased the demand for new communication services but also established the quest for greater transmission speeds [2]. Yesterday's focus was purely on the transmission of telephone voices by circuit provisioning with SONET and DWDM. The data world was based on TDM circuits designed for voice transmission. However, with the introduction of many protocols, access services, and internet applications at the access edge, the trend in data services, stretching out of the local area into the metro and regional transmission domain is changing the requirements for switching and routing. Transmission networks and systems are therefore also evolving to include mapping of multiple services and signal types into SONET. However, the service providers face the challenge of connecting multiple data traffic and voice traffic into their high-speed backbone because supporting wide range of access interfaces is complex and expensive.

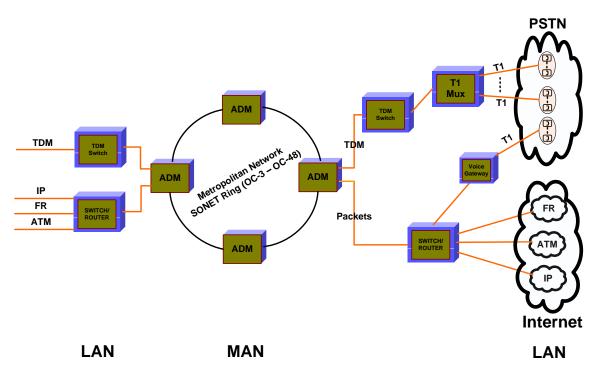

Many challenges are associated with provisioning voice and data services using today's legacy architecture, as shown in Figure 1.1. Voice-data overlay networks results in duplication of equipments, demands more operational space, and yields high costs. Also running separate operations for each service is complex, and difficult to manage and troubleshoot. Tomorrow's transmission networks must therefore efficiently manage both types of services-provisioned circuits for voice traffic and switched multipoint data services simultaneously in one platform. Investment is reduced by having only one converged network managing both traffic types, ultimately leading to lower operational expenditures.

The hybrid switch addresses the requirements of a single common minimum-cost platform from an inter-community prospective. The switch is capable of handling both TDM flows and packet flows on any of its ports, and on sub-channels of its various ports. Each switch port uses SONET STS-12 signaling with a bandwidth of 622.08Mb/s. Each VT1.5 component of an STS-12 is treated as a conventional SONET (TDM) flow, or as stream of IP packets. The switch then switches TDM flows as logical circuits with low latency and negligible switching jitter, and switches packet flows with fair virtual output queuing techniques. The advantage of this architecture is that it allows the normal use of two different switching technologies and 'boxes' to be collapsed into one 'box', thereby offering substantial savings and flexibility to the user in Local Area Network (LAN) and Metropolitan Area Network (MAN) environments. It also follows a new and unique design for multiservice provisioning by integrating the right amount of packets and TDM functionality and provides a dedicated fabric for each technology, thereby guaranteeing optimum performance of this truly converged platform.

#### **1.2 Background of Hybrid Switching**

Figure 1.1 shows a typical carrier application under today's network conditions. From the figure it is obvious that different types of switching equipments are being used. Traditional TDM traffic for Plain Old Telephone Service (POTS) for Public Switched Transport Networks (PSTN) and dial-up Internet traffic are mostly carried over TDM based T1 lines. These T1 circuits are terminated in a T1 multiplexer. Packet based IP, Asynchronous Transfer Mode (ATM), and FR traffic are terminated in different terminal devices. Both TDM and packet traffic are mapped into the SONET signal and carried over the service provider's SONET network. Add-Drop Multiplexer (ADM) provides access to the SONET network.

The requirements for different types of equipments and protocols lead to substantial network complexity. Rack space is needed for the various types of equipment. Each set of equipment usually comes with its own management system. This requires expertise in multiple technologies with equipment from multiple vendors to manage each transport –

network type. In addition to the expense of supporting this infrastructure, the provisioning of services requires co-ordination of the configuration of all the network elements that are involved.

Figure 1.1 Traditional LAN and MAN Network

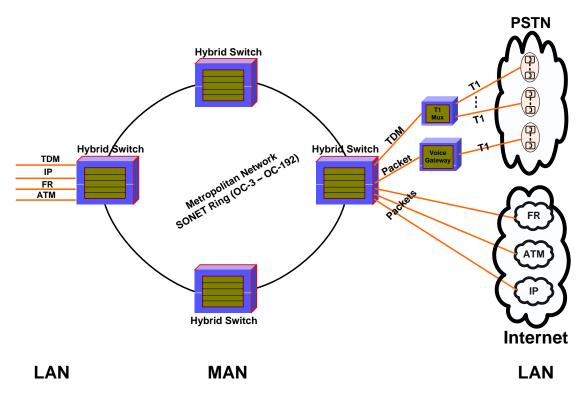

The hybrid switching concept combines the functions of a multiplexer with multiple service access devices and adds the capability to support multiple protocols in one platform. This new approach uses a rack-mounted chassis in which a wide variety of interface and function cards can be inserted to tailor the platform to specific roles. This new paradigm for building the network infrastructure converge the functions of time division backbone switches and packet switches into a single backbone making the infrastructure much simpler, cheaper, and easy to manage.

Figure 1.2 shows the hybrid switch application in a carrier network. The optical (or electrical) interface function to the hybrid switch has been combined with different access interfaces. All of this has been integrated into one platform and positioned strategically at the boundary between the MAN and the LAN. This new architecture removes barriers to

operational efficiency and flexible provisioning for voice and data by creating a unified network that can be operated and managed easily.

Figure 1.2 Hybrid Switching LAN and MAN Network

#### **1.3 Objectives**

The research objective is to design and evaluate the performance of a hybrid switching architecture for LAN and MAN networks. The key is to design a switch that is capable of accepting both TDM flows and packet flows on any of its ports, and forwarding it to its destination. Design, performance characterization, and simulation of the switch will be done in order to study the cost and benefits of having such a switching architecture on the current internet backbone network. More specifically, the research work is done in order to:

(1) study the feasibility of supporting both TDM based traffic and packet based traffic on a single switching platform,

(2) develop new algorithms for arbitration and study the performance of switches using that arbitration scheme, and

(3) study the design alternatives, and examine the cost and performance issues; and find what heuristics are most useful in developing efficient hybrid switching.

Our challenges in order to meet the above objectives are:

✤ Design of a switching platform which integrates the functionality of a TDM based switch and a packet based switch, with the challenge of not having excessive implementation costs.

Design of the data path that can carry both TDM and packet traffic.

✤ Design of the TDM based switch backbone with a suitable fast arbiter. The three stage time-space-time (TST) switch should have an arbitration cycle less than four SONET cycles.

#### **1.4 Thesis Organization**

This thesis is organized in the following way. Chapter 2 gives a brief introduction to the hybrid switch. It gives an overview of the data paths, control paths, and the arbiter unit, and defines the interconnection networks. It also introduces the TST (Time-Space-Time) switching nature of the hybrid switch. Different classes of service supported by the switch and their priority for providing the Quality of Service (QoS) for the subscribers are also explained. Chapter 3 reports the architectural design of the data paths and the control signals. It also gives a brief introduction to SONET and describes how SONET signaling is used on the communication link between port card and the line card. This chapter also introduces packet queuing issues and the use of Ingress Buffered Virtual Output Queue (IB-VOQ) memories in our hybrid switch. Chapter 4 is about the arbiter. It explains arbitration process for packet and TDM traffic. The bandwidth arbitration algorithm and the time slot assignment processes are also described. Finally the chapter describes the arbitration design alternatives and explains a software approach and a hardware approach and their advantages and disadvantages. Chapter 5 explains how the design was verified and tested to make sure it functions correctly. Chapter 6 describes our simulation experiments and results. It describes the load model used for simulating the design, and analyses of the obtained results. Chapter 7 explains the FPGA implementation of the switch with cost and area analysis. Chapter 8 concludes the thesis and discusses future work.

### Chapter 2

### Hybrid Switching Architecture Overview

This chapter provides an architectural overview of our hybrid switch. Section 2.1 describes the overall switching concept. A hardware system overview is introduced in Section 2.2. An introduction to the data path is given in Section 2.3. Arbiter and control signals of the switch are introduced in Section 2.4 and Section 2.5 respectively.

#### 2.1 Hybrid Switching Concept

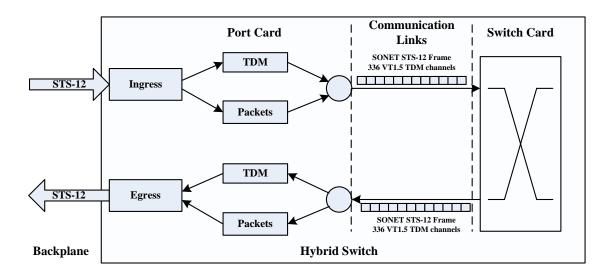

The hybrid switch switches both TDM and packet traffic carried by SONET STS-12 (Synchronous Transport Module level - 12) links on a single switching platform. Figure 2.1 shows the hybrid switching model.

Figure 2.1 Hybrid Switching Model

Traffic carried by each SONET STS-12 link is differentiated into packet and TDM traffic at the ingress port. These packets are switched at level 3 (IP packets) or level 2 (ATM or Frame Relay). The remaining SONET TDM voice components are switched at

their native TDM level. The switch's ingress and egress communication links are divided into 336 Virtual Tributary 1.5 (VT1.5) channels. The number of VT1.5s in one STS-12 frame is 336. Each channel can carry either packet or TDM traffic from ingress port to egress port. The traffic carried by the ingress VT1.5 channels is switched at the switch card. The VT1.5 channel allocation and crossbar set-up logic is provided by arbiter logic in the switch card. The traffic coming out of the switch card is extracted and differentiated into TDM and packet traffic at the egress side. Egress traffic is read, assembled, and stored at the egress port and sent as an STS-12 signal across the backplane.

VT1.5 channels are used to carry long packets by byte interleaving. Each channel can carry packet bytes from any queue. Each queue (flow) can be carried by one or more VT1.5 channels. The channel allocations may change at any STS-12 frame boundary. It is the job of the arbiter to announce such changes to the TDM filler, crossbar and TDM extractor so that the packets are switched and reassembled properly.

#### 2.2 System Overview

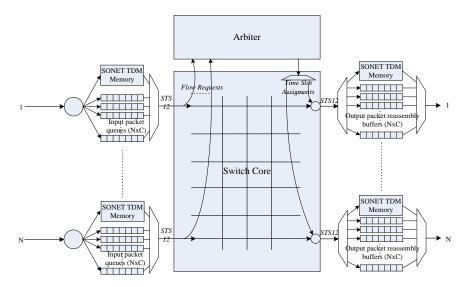

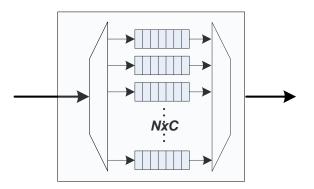

Figure 2.2 shows a block diagram of an *NxN* hybrid switch which supports *C* priority classes. The switch contains *NxC* packet queues at each input, *NxC* output buffers at each output, a crossbar fabric and an arbiter.

Figure 2.2 Hybrid Switching Block

The *NxC* input queues at each input port are used as IB-VOQ in order to respect priorities and eliminate head-of-line (HOL) blocking. N ingress ports by N egress ports are cross connected by the NxN crossbar which provides ingress lines for each input and egress lines for each output. This hybrid switch allows each port to be independently configured for any mixture of packet and TDM traffic, including 100% packet and 100% TDM.

Figure 2.3 shows the hybrid architecture in more detail. The communication paths from ingress ports, through the crossbar and to the egress ports carry the SONET STS-12 protocol which contains 336 VT1.5 channels. The switch connects inputs to outputs through these channels, each of which have an aggregate bandwidth of 1.544 Mbps. These VT1.5's can be used to carry standard virtual tributaries (SONET TDM) or byte streams which are used to carry the switch's packet traffic. Aggregations of VT1.5's can be used to carry STS-N's as broadband TDM.

Figure 2.3 Block Diagram of Hybrid Switch Architecture

As shown in Figure 2.3, the hybrid switch architecture consists of three switching stages; two time switching stages on the line card and a space switching stage on the switch card. Traffic at the hybrid ingress ports is mapped to VT1.5 time slots within an aggregate SONET STS-12 by the TDM filler module, which is a time switch. The crossbar (switch core) acts as a space switch which connects STS-12 TDM signals from one input port to another output port. The crossbar makes separate connections for each VT1.5. The TDM extractor (the final time stage) reads the traffic carried by egress VT1.5 channels and uses it as a source to extract and reassemble packets and to extract SONET TDM traffic.

At each ingress port, there may be conflicting demands for resources such as buffer space and time through the crossbar. A control scheme for resource allocation is provided by the arbiter module. Its main objective is to resolve the conflicts and provide efficient and fair scheduling of these resources. The arbitration enforces three specific goals:

- (1) respect for priorities,

- (2) fairness among the ports, and

- (3) maximum bandwidth utilization and maximal throughput.

By enforcing the above goals, arbiter maximizes bandwidth utilization and meets the QoS requirements as closely as possible.

#### 2.3 Data Path

The solid lines in Figure 2.3 represent the data path. Each packet arriving at an ingress port is classified and placed in the appropriate ingress buffered queue based on its class and its destination. Each packet with distinct class and destination represents a separate flow. There are *NxC* distinct flows at each ingress port. The TDM (SONET) traffic is simply put in a SONET memory and each VT1.5 column of the SONET traffic represents one separate flow.

In each arbitration cycle each packet flow is assigned some set of VT1.5's to carry

packets from ingress to egress port. The collection of VT1.5's in aggregate form a byte stream into which the packets are fed in priority order. In each arbitration period a new set of VT1.5s may be allocated to any flow. The switch must be capable of hitlessly changing from one set of VT1.5's to the next set, without disrupting the traffic flow. For each output port, there is a choice of which of several input ports it will connect to. For each output grant, the crossbar arbitration logic selects one of the inputs and blocks the others. The TDM extractor on the output side selects the channel, reads the byte stream, and sends the data into the appropriate packet assembler. Once a full packet is assembled, it is sent to a FIFO buffer which is then read by the egress port. The packet assembler begins assembling the next packet with the next arriving byte.

For switching SONET TDM traffic, the switch carries out an N port SONET STS-12 time-space-time (TST) switch with switching occurring at every VT1.5 frame. The switch fabric exchanges the aligned STS-12 data streams at VT1.5 granularity through TST stages. Both ingress and egress time switch (TDM filler and TDM extractor) perform time slot interchange on the data stream while the space switch stage switches data from one SONET pipe to another. Each time slot is switched independently in the space switch stage. Switch control memories (TDM filler, TDM extractor and switch set up) are organized into pages of control words, which determine what permutations are implemented for each of the 336 VT1.5 positions per SONET STS-12 frame (in time) at each of the N ports (in space) for the switching stages. The switched TDM traffic is extracted and stored in TDM memory at the egress side and then transmitted through the egress port.

No frequency speed up is assumed for this switch architecture. As we shall see in the chapters on performance results and conclusions, some speed up is required in practice.

#### 2.3.1 Class of Service (CoS)

CoS is a way of managing traffic in a network by grouping similar types of traffic together and treating each type as a class with its own level of service priority. It enables more predictable traffic delivery of priority data across IP-enabled networks. Our hybrid

switch supports three classes of services: first (high priority), second (medium priority) and third (low priority).

The high-priority class supports strictly bounded delay and jitter applications such as VoIP and real-time video applications with non-preemptive bandwidth guarantees. The medium-priority class supports applications that are less sensitive to delay and jitter such as non-real-time video and VPN services. User-provisioned committed information rate (CIR) and extended information rate (EIR) guarantees are supported for different service requirements. The low-priority class of service supports best-effort applications that do not need bandwidth guarantees such as consumer Internet access via the IP protocol suite. With three unique classes of service, service providers can offer differentiated services with different price points to satisfy different customer requirements.

#### 2.4 Arbiter

An *NxN* hybrid switch contains *NxNxC* queues at the ingresses which store different packet traffic flows based on sources, destination, and CoS assignment. Due to the presence of IB-VOQs at each ingress port (Figure 2.2), packets which are destined to different output ports may be transmitted through the switch in any order; regardless of their arrival time at the ingress port. It is the job of the arbiter to decide when the packet from each queue should be sent to the egress port.

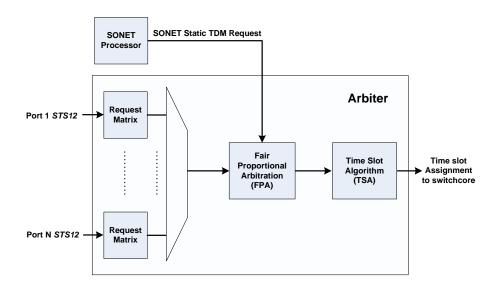

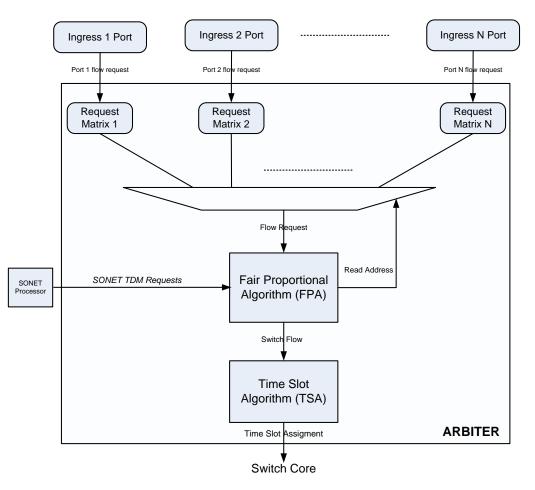

Figure 2.4 shows the block diagram of the arbiter. The arbiter examines TDM requests for SONET traffic and flow requests for packet traffic and makes scheduling decisions for every VT1.5 channel, including which input buffers to read, which output buffers to write, and the configuration settings for the crossbar. The SONET control unit (microprocessor) embedded in the hybrid switch (not shown) carries TDM requests to the arbiter while SONET STS-12 Transport Overhead (TOH) and Path Overhead (POH) carry packet flow requests to the arbiter. TDM traffic has priority over all packet traffic and is served first. The remaining VT1.5 channels are allocated by the arbiter to packet traffic.

Channel allocation for SONET TDM traffic is static. All the channels are "open" for TDM requests and they get channels for all of their requests. However, the channel distribution for packet traffic is dynamic in nature and needs a rapid and flexible arbitration scheme in order to respond to the bursty, self addressing nature of packet traffic. In order to perform packet arbitration, the arbiter accepts bandwidth requests for the *NxNxC* input flows from the N ingress ports. These bandwidth requests are stored in a request matrix. The bandwidth requests combine information about current queue size (depth) and current traffic flow at ingress port (recent flow). The Fair Proportional Algorithm (FPA) scheme in the arbiter uses this information to allocate bandwidth to each ingress-to-egress flow. The Time Slot Algorithm (TSA) gives time slot assignments which map bandwidth allocations from the FPA to specific TDM channels. The time slot assignments computed by the TSA are passed to the switch core to configure the crossbar. The time slot assignments are also sent to port cards by embedding them in the SONET STS-12 signal's overheads. Port cards use this information to fill the ingress TDM channels with packets and to extract packets out of STS-12 frame on the egress side.

Figure 2.4 Arbiter Block Diagram

Unlike other packet switches which need only one grant per ingress port for full utilization of the channel bandwidth, our hybrid switch must have multiple grants per ingress port, one for each active ingress-to-egress VT1.5 flow. The total grant per port is the number of VT1.5 channels allocated per ingress by the switch's arbiter. Since there are 336 VT1.5 channels per ingress/egress link, we need to have 336 VT1.5 channel allocations per STS-12 frame to fully utilize the switch's bandwidth. Similarly, each output port contends for multiple input ports and there must be 336 VT1.5 channel allocations per STS-12 frame to fully utilize total switch's bandwidth. The arbitration task is thus symmetrical with respect to inputs and outputs. Furthermore, since the arbitration result for each port is dependent on the arbitration for other ports, the arbitration task cannot be performed by separate independent arbiters at the input ports or output ports. In order to maximize performance, the arbitration should result in switch configurations that allow for the maximum number of packets traffic to be transmitted simultaneously. The arbitration process itself must be fast relative to the rate at which packets are received and relative to the latency of packet transmission through the switch.

#### **2.5 Control Paths**

The dashed lines in Figure 2.1 represent the control paths. Control paths are used to carry the flow requests from port cards to the arbiter, and time slot assignment information from the arbiter to the port cards and from the arbiter to the crossbar. The control signals (paths) in our hybrid switch have the following main functions:

- (1) Control the flow of packets from ingress queues to egress port.

- (2) Configure switch crossbar to connect appropriate ingress port to egress port for each of 336xN VT1.5 time slots.

- (3) Control egress port to select appropriate TDM channel in STS12 stream for packet and TDM recovery.

#### 2.5.1 Control Path for Carrying Flow Requests

Flow requests from ingress queues are carried to the arbiter in SONET STS-12 signal's overheads. The entire SONET frame is passed to the arbiter module which parses the frame, extracts the flow requests and saves them as a request matrix. The request matrix

is used to find the TDM channel arbitration for each flow at ingress port. The arbitration process is described in Section 2.3.

#### **2.5.2** Control Paths for Carrying Time Slot Assignments

Time slot assignments are passed from the arbiter module to port cards by embedding them in SONET STS-12's TOH and POH bytes being sent to the egress port. The time slot assignments are extracted at egress port card and used for controlling the TDM fillers and the TDM extractors as shown in Figure 2.2. The same time slot assignment at switch card is used by the crossbar (space switch) to cross-connect ingress and egress ports at VT1.5 granularity.

## **Chapter 3**

### **SONET Signaling, Data Path and Control Paths**

This chapter extends Chapter 2 by providing more detail about the data paths and the control signals. It begins with a brief introduction to SONET, and the formation of STSx signal and VTs which are the basis for carrying data and control information across the switching platform. Section 3.1 describes the SONET frame and signaling. Section 3.2 describes the packet queuing issues. Section 3.3 gives an introduction to the hybrid switch at the architectural level and describes the data path block diagram. Section 3.4 describes the control paths and explains how the control signals are used to control data flow.

#### **3.1 SONET Signaling**

SONET is the basis for the transport of packet and TDM traffic in our hybrid switch. Ingress traffic and switch control information is carried via STS-12 signaling. Each SONET STS-12 frame is divided into multiple VT1.5 virtual tributaries (VTs) which provide the data path channels for ingress-to-egress traffic flow. The SONET overheads carry the control information for data flow and switch setup. The following subsections describe the SONET frame and VT sub-structure.

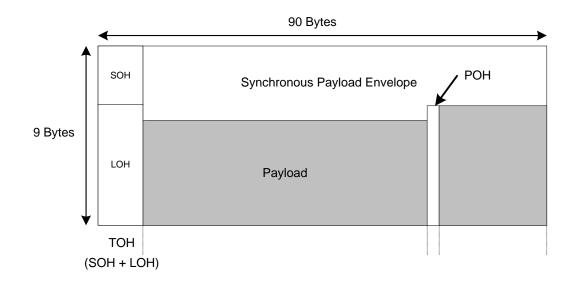

#### **3.1.1 The SONET Frame**

Figure 3.1 shows the fundamental SONET frame. This frame is known as a Synchronous Transport Signal, Level One (STS-1). It is 9 bytes tall and 90 bytes wide for a total of 810 bytes of transported data including both user payload and overhead. The first three columns of the frame are the Section and Line Overhead (SOH and LOH), known collectively as the Transport Overhead. The bulk of the frame itself, to the left, is the

synchronous payload envelope (SPE), which is the container area for the user data that is being transported. The data, previously identified as the payload, begins somewhere in the payload envelope. The actual starting point will vary. The Path Overhead (POH) begins when the payload begins; because it is unique to the payload itself, it travels closely with the payload. The first byte of the payload is the first byte of the Path Overhead.

Figure 3.1 SONET Frame

#### **3.1.2 SONET Bandwidth**

The SONET frame consists of 810 bytes, and like the T-1 frame, it is transmitted once every 125µs (8000 frames per second). This works out to an overall bit rate of 810 bytes/frame x 8 bits/byte x 8000 frames/second= 51.84 Mbps, the fundamental transmission rate of the SONET STS-1 frame which is slightly more than a 44.736 Mbps DS-3, a respectable carrier level by anyone's standard. The basic structure of the STS-1 frame is repeated for the higher rates. Three STS-1 frames are multiplexed to create the STS-3 which has a bandwidth of 155.52 Mbps, these in turn are multiplexed to create the STS-12, and so on. If the payload requires less than 51.84 Mbps, the Synchronous Payload Envelope (SPE) is subdivided into smaller components, known as *virtual tributaries*, for the purpose of transporting and switching payloads smaller than the STS-1 rate [3].

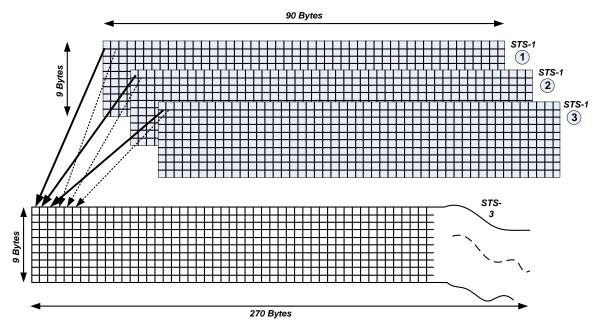

#### 3.1.3 The STS-N Frame

In situations where multiple STS-1s are required to transport more payload information, SONET enables the creation of what is called STS-N frames, where N represents the number of STS-1 frames that are multiplexed together to create the frame. If three STS-1s are combined, the result is an STS-3. In this case, the three STS-1s are brought into the multiplexer and byte interleaved to create an STS-3, as shown in Figure 3.2. In other words, the multiplexer selects the first byte of frame one, followed by the first byte of frame two, followed by the first byte of frame three. Then it selects the second byte of frame one, followed by the second byte of frame two, followed by the second byte of frame three, and so on, until it has built an interleaved frame that is now three times the size of an STS-1: 9x270 bytes instead of 9x90 and is still generated 8000 times per second. The technique described above is called a single stage multiplexing process because the incoming payload components are combined in a single step. A two-stage technique is also commonly used. For example, an STS-12 can be created in two ways. Twelve STS-1s can be combined in a single stage process to create the byte interleaved STS-12; alternatively, four groups of three STS-1s can be combined to form four STS-3s, which can then be further combined in a second stage to create a single STS-12 [4].

Figure 3.2 Formation of STS-3 frame by byte interleaving

#### **3.1.4 SONET Virtual Tributaries**

When a SONET frame is modified for the transport of sub-rate payloads, it is said to carry virtual tributaries (VTs) in which the payload envelope is chopped into smaller pieces that can then be individually used for the transport of multiple lower-bandwidth signals.

To create a VT, the SPE is subdivided. An STS-1 comprises 90 columns of bytes, four of which are reserved for overhead functions (Section, Line, and Path). This leaves 86 for actual user payload. To create virtual tributaries, the payload capacity of the SPE is divided into seven, 12-column pieces called "VT groups". This leaves two unassigned columns which are called "fixed stuff". Each of the VT groups can be further subdivided into one of four different VTs to carry a variety of payload types, as shown in Table 3.1 [4].

| VT Туре | Columns/VT | Bytes/VT | VTs/Group | VTs/SPE | VT Bandwidth (Mbps) |

|---------|------------|----------|-----------|---------|---------------------|

| VT1.5   | 3          | 27       | 4         | 28      | 1.728               |

| VT2     | 4          | 36       | 3         | 21      | 2.304               |

| VT3     | 6          | 54       | 2         | 14      | 3.456               |

| VT6     | 12         | 108      | 1         | 7       | 6.912               |

Table 3.1 SONET Virtual Tributaries

#### **3.2 Packet Queuing Issues and Virtual Output Queue**

The two main tasks involved in switching are: scheduling and data forwarding. Scheduling involves deciding for each input port which output port the packet should be sent to and arbitrating when more than one input port requests for the same output port while data forwarding involves sending the packet data from input ports to output ports according to the scheduling decision. Data is generally stored in a queue before sending it to output ports.

In general, packet switches can be divided into two categories: output queued (OQ) switches and input queued (IQ) switches, based on where delayed packets are queued. A typical OQ switch has a first-in-first-out (FIFO) queue at each output port to buffer the packets destined to that output port. OQ switches are shown to be able to achieve unity throughput and can easily meet different QoS requirements, such as delay and bandwidth, by applying various scheduling algorithms [5]. However, since there is no buffer at the input side, if the packets arriving at different input ports are destined to the same output port, all the packets must be transmitted simultaneously. Therefore, in order for OQ switches to work at full throughput, the switching speed of the internal fabric and the receiving speed of the output port must be N times faster than the sending speed of the input port in an N x N switch. This speedup requirement makes OQ switches difficult to scale. In particular, when the switch has a large number of input ports or the speed of a single input port increases to Gb/s, it is impractical to achieve the N speedup [6]. On the other hand, for IQ switches, the switching fabric and the output port only need to run at the same speed as that of the input port and, therefore, IQ switches have been the main research focus of high speed single stage switches. The single input queued switch, has a FIFO queue at each input port to store the incoming packets waiting for transmission. Since only the packet at the HOL of each input queue can participate in the scheduling, the packets behind the HOL packet suffer from so called "head of line" blocking, which means that, even though their destination output ports may be free, they cannot be scheduled to transfer because the HOL packet is blocked [7].

An efficient yet simple buffering strategy to avoid HOL blocking is to adopt a multiple input queued switch structure, which was introduced in [8]. A typical multiple input queued switch has a separate FIFO queue corresponding to each output port. It is the IB-VOQ structure since each queue stores those packets which have arrived at a given input port and are destined to the same output port. HOL blocking is eliminated because a packet cannot be held up by a packet ahead of it that goes to a different output. It is known that the VOQ switch structure can achieve 100 percent throughput for all independent arrival processes by using the maximum weight matching algorithm [9] or by using other maximum matching algorithms with speedup [10], [11], [12], [13].

#### **3.3 Data Path Architecture**

The hybrid switch is configured as a circuit switching platform which can switch both packets and TDM traffic. As described in Chapter 2, the switching process starts at the ingress port where traffic is differentiated into packet traffic and TDM traffic. Packet traffic is switched by request-grant process which is described in more detail in Chapter 4. SONET TDM traffic is switched by static channel allocation process which is also described in the next chapter. The switched TDM traffic and packet byte streams are extracted, assembled and transmitted through egress port. The following sub-sections describe the data path blocks of the hybrid switch.

#### **3.3.1 Ingress Ports**

Our experimental hybrid switch architecture is optimized for 32 ports. Each port supports 622 Mbps link bandwidth which is organized as 336 VT1.5 channels for carrying data from ingress to egress. Therefore, the aggregate duplex bandwidth of the switch is 19.9 Gbps (19.9 Gbps ingress, 19.9 Gbps egress). The communication backplane is SONET structured network. The packet traffic coming to the ingress port is differentiated according to class and sent to their appropriate queues (VOQs) and the TDM traffic is sent to a SONET memory.

#### **3.3.2 Ingress Packet Queues**

Figure 3.3 shows the ingress packet queues. There are *NxC* separate queues at each input port. Packets coming to the ingress port are stored in queues before they are transmitted to the egress port. Packets in the ingress queue are sent to the egress port through the crossbar in a controlled fashion by the arbiter. Scheduling of the crossbar and the arbitration of packet flows in queue are based on the queue depth and current traffic flow in the queue, as described in detail in Chapter 4.

Figure 3.3 Virtual Output Queues for N destinations and C classes

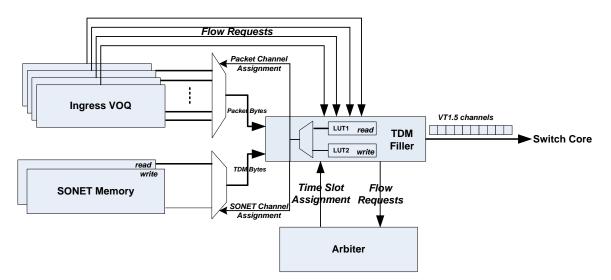

# 3.3.3 TDM Filler

Figure 3.4 shows the block diagram of the TDM filler. The ingress (and egress) communication link is divided into 336 (28x12) VT1.5 TDM channels. Each channel can carry 9 bytes/column x 3 columns = 27 bytes. The TDM filler receives traffic from the ingress queues (VOQs and SONET memory) and fills ingress VT1.5 channels to carry data to the switch core. The channel assignment for each queue can change on any STS-12 frame boundary and it's the job of the arbiter to make these changes to the TDM filler/extractor at a time. For the same priority traffic if more and more traffic are coming to the ingress port, the arbiter allocates more and more bandwidth to that flow.

Figure 3.4 TDM Filler Block

There are *N* TDM Fillers, one per ingress port. The channel mapping decision for each TDM filler is based on the switch's arbitration process. The arbitration process generates time slot assignments that define which flow should use which channel at a time. The slot assignment is stored in a look-up table (LUT). There are two LUTs per TDM Filler block; one is used for writing TDM filling instruction for the next arbitration cycle and the other LUT is used for current VT1.5 channel filling instructions. In the next arbitration cycle, LUT roles are swapped.

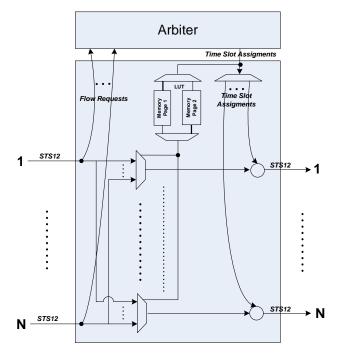

#### 3.3.4 Switch Core

Figure 3.5 shows the diagram of the switch core. The switch core located at the switch card connects all switch input ports to the output ports. It is the switch pipeline root, because it is the source of configurations that trigger the transmission of packets/TDM cells throughout the crossbar. The switch core is made up of a scheduler and a crossbar. The scheduler implements algorithms that provide efficient use of the crossbar bandwidth and the crossbar connects each ingress port to the egress port as directed. The crossbars and the arbiter connect to each port via high-speed serial links.

Figure 3.5 Switch Core Block

The digital crossbar in the switch core makes connections between the ingress ports and the egress ports. The arbiter configures the crossbar with time slot assignments generated by TSA module. The time slot assignments generated by TSA are stored in a LUT to be used in the next arbitration cycle. There are two LUTs; one for reading crossbar configuration and another for writing new configuration from arbiter. In every arbitration cycle the LUT's roles are swapped.

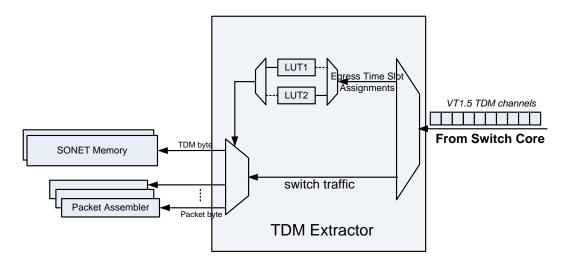

# **3.3.5 TDM Extractor**

The TDM Extractor, as show in Figure 3.6, is used to extract packet and TDM traffic from STS-12 stream coming out of the switch core. The channel extraction information, which is stored in LUTs, is provided by the arbiter. The payload in the SONET STS-12 frame needs to be extracted and assembled at the egress port. Like in the TDM Filler and the Switch Core, there are also two LUTs in each TDM Extractor block (LUT1 and LUT2 in Figure 3.6); one for reading and one for writing. In each arbitration cycle, their roles are swapped.

Figure 3.6 TDM Extractor Block

In order to extract the data from SONET signal, the extractor must be synchronized with the SONET frame. For synchronization, the TDM extractor monitors the incoming SONET signal and looks for the frame boundary signals (A1, A2). Once the boundary is found, it differentiates SONET data into control data (ingress and egress time slot assignments which are appended to SONET header) and payload data (actual traffic). The payload data is extracted from the VT1.5 channels and forwarded to corresponding traffic handler where as the control data is used to fill-up TDM filler/extractor LUTs as shown in Figure 3.6.

### 3.3.6 Packet Assembler

Before IP packets are sent to the output buffers, the packet's byte chunks which are carried by the SONET frame in the form of TDM cells (in SONET STS-12 payload) need to be assembled to re-form the original packets. Packet assembler modules are used for this purpose.

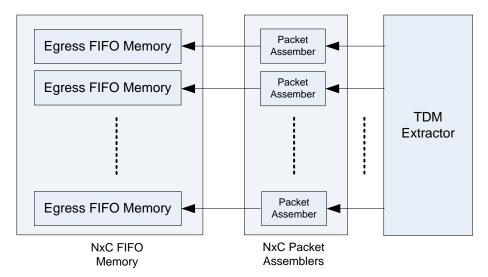

Packets from ingress VOQs are filled in VT1.5 channels by TDM filler and since one VT1.5 channel can accommodate only 9x3 = 27 bytes, the egress port may have to wait for other channels in order to get all the bytes of a packet. During the waiting period, the transmitted bytes are stored in a memory inside the packet assembler. Once all the bytes of a packet arrive at the assembler, it is sent to an output FIFO memory as a single packet and then stored in a FIFO memory as shown in Figure 3.7.

Figure 3.7 Packet Assemblers and FIFO Memory Blocks

# **3.3.7 Egress Packet FIFO**

The assembled packet from the packet assembler is stored in egress FIFO memory (Figure 3.7). There are NxC FIFO memories, one for each source and class combination. The egress port transmits these packets to the backplane links.

# **3.4 Control paths**

Our hybrid switch is equipped with data path and control signaling paths for cooperating with arbiter and other data path modules for high throughput packet routing. There are several control paths in the switch that carries control information. Following are the main control signals the control path carries:

- (1) Flow Request from queues to the arbiter

- (2) Ingress Time Slot Assignment from arbiter to port card.

- (3) Egress Time Slot Assignment from arbiter to port card.

- (4) Switch Time Slot Assignment from arbiter to crossbar.

- (5) Packet Channel Assignment from TDM filler block to queue block.

- (6) SONET Channel Assignment from TDM filler block to SONET memory.

# **3.4.1 Flow Request**

In hybrid switch the arbiter allocates channel(s) for a particular flow at ingress port based on the channel requests for that particular flow. The Flow request is the number of VT1.5 channels requested by a queue at ingress port. It is calculated based on the current queue depth and recent traffic flow at the ingress port. The following equation is used to calculate the flow request:

$$BR = Q/N + F \tag{3.1}$$

Where,

BR = Flow Requested.

F = Recent Traffic Flow.

Q = Current Queue Depth.

N = Number of arbitration cycles to bring Q to zero.

The requested bandwidth information is carried to arbiter in SONET headers which are used by arbiter for crossbar scheduling and packet arbitration purposes.

# **3.4.2 Ingress Time Slot Assignment**

The ingress time slot assignment signal carries the ingress link channel allocations information from the arbiter which tells the TDM filler how the ingress VT1.5 channels should be filled by ingress traffic. There are 336 VT1.5 channels in each ingress communication link and each of these channels may be carrying either packet traffic or TDM traffic or simply not carrying any traffic at all. Ingress TSA signal tells the TDM filler whether or not the channels are to be filled with packet traffic from ingress VOQ or from the SONET memory. The channel allocation is computed by the arbiter and the allocation result is carried to the port card by embedding it into SONET STS-12 (aggregation of 336 VT1.5 channels) signal's path and transport overheads.

#### **3.4.3 Egress Time Slot Assignment**

The egress time slot assignment signal from the arbiter module carries the information about how the communication channel's bandwidth is distributed among all the ports. This information is used to extract the TDM and packet traffic from the link and send them to their corresponding traffic handler. The egress time slot assignment is computed by TSA block in the arbiter and the signal is carried to the port card by embedding it into SONET STS-12 signal's path and transport overheads.

#### **3.4.4 Switch Time Slot Assignment**

The crossbar in the switch core is used to connect multiple inputs to multiple outputs at a time. A standard problem in crossbar switches is that of setting the cross-points when the particular ingress should be connected to specific output. In our hybrid switch the cross-points are closed and opened according to the time slot assignments provided by the arbiter. When the crossbar is enabled, the input is connected to the output and the traffic carried by VT1.5 channels in ingress communication link is switched to VT1.5 channels in egress communication link.

### 3.4.5 Packet Channel Assignment

The TDM filler divides ingress time slot assignments into two parts, one to allocate VT1.5 channels for packet traffic, and another to allocate channels for TDM traffic. Packet channel assignment is a control signal from the TDM filler to the ingress queue module that carries the information which queue should use which VT1.5 TDM channel to send packets to the egress port. This signal controls the flow of packets from ingress queue to the egress ports.

# 3.4.6 SONET Channel Assignment

This is a signal from TDM filler to the SONET memory that map is used to map the SONET TDM traffic directly into ingress VT1.5 TDM channels. This is also computed by the arbiter module.

# Chapter 4 Arbiter Bandwidth Allocation

The arbiter controls and allocates access to the data path by controlling and allocating the shared resources. In our hybrid switch the shared resources are the ingress TDM channels, the egress TDM channels, and the crossbar paths. This chapter describes the resources, arbitration algorithms, design alternatives, implementation issues, and the timing results of the arbiter.

# **4.1 Introduction**

The arbiter provides a mechanism to control and regulate the flow of traffic from the ingress ports to the egress ports. It manages the ingress traffic by distributing the available bandwidth resources fairly among ports and satisfying customer's QoS requirements. This is accomplished by differentiating traffic in priority order. In order to perform the arbitration, the arbiter resolves bandwidth requests from the ingress ports according to some specifications. These specifications are defined in Section 4.3. The arbiter's goal is to find an optimal set of switch settings through solving these requests.

# 4.2 Arbitration Goal

The goal of arbitration is to allocate bandwidth to all ports fairly, efficiently, and in a reasonable time. In order to achieve this goal, the arbiter allocates the switch's bandwidth to the *NxNxC* flows according the following principles:

(1) priority of the packet flows,

- (2) fairness between ingress ports and between egress ports, and

- (3) efficient bandwidth utilization.

#### 4.2.1 Priority

Our hybrid switch respects the customer's QoS requirement by allocating available bandwidth according to traffic types. Three classes of service are supported by the switch and each class represents traffic with different QoS requirements. Flow (bandwidth) requests from the ingress ports are served in strict order of priority classes. The higher priority traffic is allocated as much bandwidth as possible first and the residual bandwidth is passed on to the next lower priority traffic.

# 4.2.2 Fairness

The arbiter maintains fairness among all the ingress and all the egress ports by assigning bandwidth in proportion to their bandwidth requests, i.e., the channel requesting more bandwidth gets the higher bandwidth while the channel requesting less bandwidth gets the lower bandwidth. This fairness is accomplished by applying proportional bandwidth allocation scheme which is discussed in the next section.

# **4.2.3 Efficient Bandwidth Utilization**

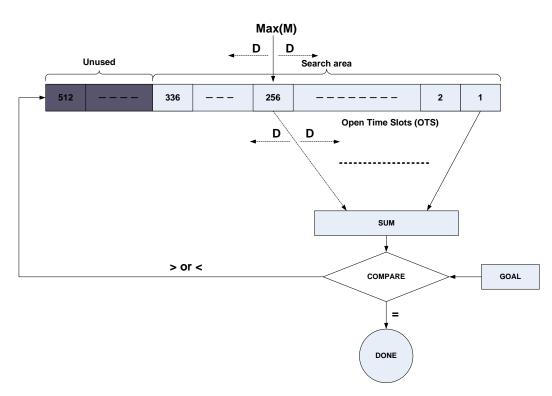

Our switch is bandwidth limited. A central issue in our hybrid switch is how to allocate this limited bandwidth to ingress flows efficiently while maintaining the fairness. The switch utilizes bandwidth efficiently by regulating the traffic on "per flow" basis. Our communication link is divided into multiple VT1.5 channels. The channel allocation is done by finding all the available channels first, and then assigning these channels to the flows. This scheme is efficient because bandwidth allocation for any flow may be realized along any available free channels and as long as there is any open (unassigned) channel. This process is called TSA which is discussed in the next section. The process of finding open channels and assigning them to different traffics in priority order forms a network policy that alleviates the application's performance and optimizes the bandwidth utilization.

# **4.3 Arbiter Block**

Figure 4.1 shows the block diagram of the arbiter module.

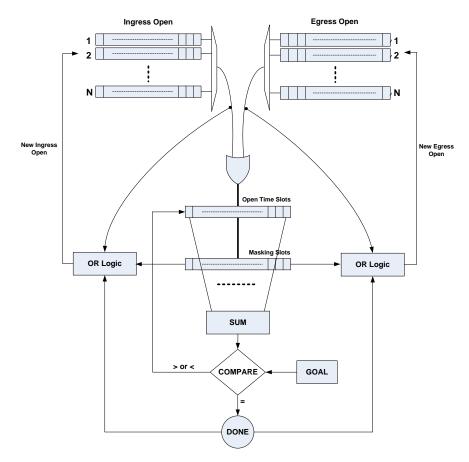

Figure 4.1: Arbiter Functional Block Diagram

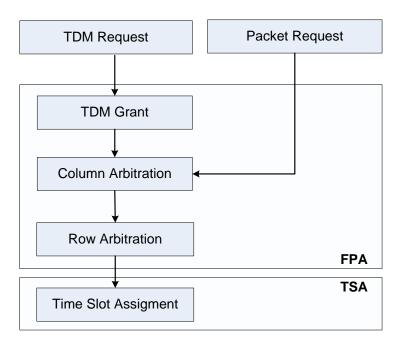

The inputs to the arbiter are *flow requests* from port cards and *TDM requests* from SONET processor. The output from the arbiter is a set of time slot assignments which are passed to the switch core's LUT and to the port cards by appending them to SONET STS-12 frames. The entire arbitration process is completed in the following five steps:

- (1) read TDM flow requests,

- (2) allocate VT1.5 channels for TDM flow requests,

- (3) read packet flow requests,

- (4) allocate VT1.5 channels for packet flow requests, and

(5) update crossbar setting for next arbitration cycle and send time slot assignments in (2) and (4) to port cards.

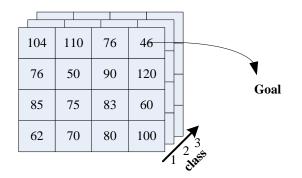

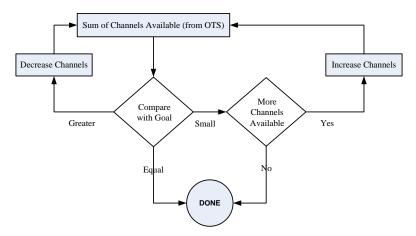

These steps are described in reference to the flow chart in Figure 4.2. SONET TDM traffic has priority over packet traffic and thus bandwidth is allocated to TDM traffic first. The remaining bandwidth is allocated to packet traffic using a FPA scheme. In FPA, the flow request matrix is viewed separately as a set of column requests and a set of row requests. The arbitration is carried out in two separate steps: arbitration by column in step 1 and arbitration by row in step 2. In the first step, our arbitration algorithm checks the flow requests of each element of the matrix along columns and assigns bandwidth proportional to the request. This represents assigning bandwidth along the egress port so the bandwidth is fairly distributed along the egress port without violating the bandwidth threshold (336 VT1.5 channels). Similarly, in the second step bandwidth over-allocation on the ingress ports.

Figure 4.2 Arbiter Flow Chart

The bandwidth assigned to each flow using FPA must be assigned VT1.5 TDM channels such that there is no any ingress-to-egress violation; i.e. no more than one ingress flow should send traffic in one particular VT1.5 TDM channel and no more than one egress

channel should get data from one particular VT1.5 channel. The process of "conflict free" slot assignment is done by time slot algorithm which is described in Section 4.3.3. After the time slot assignment by TSA, the arbiter's decisions are then sent to the port cards and the switch core LUTs for crossbar configuration.

In our hybrid switch, the arbiter tries to find an "optimal" switch setting. However, the optimal result described here is not a "perfect" solution. The arbiter described here decomposes the arbitration process into two steps: arbitration among conflicting column requests (egress) followed by arbitration among conflicting row requests (ingress) that have won in the first step. In each step, the highest priority requests are served first in order to meet the QoS requirements. This solution is not optimal in the sense of finding perfect matches in switch settings because the arbitration in the second step may further reduce the optimal switch setting we found in the first step leaving switch capacity unused. In order to achieve the optimal result, arbitration would have to be an iterative process between step 1 and step 2 with alternating increasing and decreasing of individual request number until the optimal settings are found. This iterative process is heuristic in nature and may take a long time to converge. Instead, the arbiter described here is motivated by the need to find useful switch settings very quickly. In the other words, in this application there is an important trade-off between optimality and speed. A slow, optimal solution would be much less useful than a fast good but not-so optimal solution. This is discussed in more detail in the later parts of this chapter.

#### **4.3.1 Request Matrix**

Bandwidth (flow) requests from each traffic flow at the ingress ports are carried to the arbiter by appending the requests to SONET STS-12 overheads. The arbiter unit extracts these requests and saves them in bandwidth request memories in the form of a matrix. These requests are used to calculate the bandwidth different distribution to different ingress flows during the next arbitration cycle.

The bandwidth request for each ingress flow is calculated by using the following equation:

$$BR = Q/4 + F \tag{4.1}$$

Where,

- BR = Bandwidth Requested (no. of VT1.5 channels)

- Q = Queue Depth (no. of VT1.5 channels)

F = Recent Flow, i.e. total traffic in last arbitration period (no. of VT1.5 channels)