# CIRCUIT SIMULATION USING DISTRIBUTED WAVEFORM RELAXATION TECHNIQUES

#### A Thesis

Submitted to the College of Graduate Studies and Research in Partial Fulfillment of the Requirements

for the Degree of Doctor of Philosophy in the

Department of Electrical Engineering University of Saskatchewan

by

Anant D. Jalnapurkar

Saskatoon, Saskatchewan, Canada Spring 1998

© Copyright Anant D. Jalnapurkar, 1998. All rights reserved.

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre référence

Our file Notre référence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-27414-4

#### PERMISSION TO USE

The author has agreed that the Library, University of Saskatchewan, may make this thesis freely available for inspection. Moreover, the author has agreed that permission for extensive copying of this thesis for scholarly purposes may be granted by the Professor who supervised the thesis work recorded herein or, in his absence, by the Head of the Department or the Dean of the College in which the thesis work was done. It is understood that due recognition will be given to the author of this thesis and to the University of Saskatchewan in any use of the material in this thesis. Copying or publication or any other use of this thesis for financial gain without approval by the University of Saskatchewan and the author's written permission is prohibited.

Requests for permission to copy or to make any other use of the material in this thesis in whole or in part should be addressed to:

Head of the Department of Electrical Engineering University of Saskatchewan Saskatoon, Canada S7N 0W0

#### ACKNOWLEDGEMENTS

The author would like to express his gratitude and appreciation to his supervisors Prof. H. C. Wood and Prof. Carl D. McCrosky for their guidance during the course of this work. Their help in the preparation of the thesis is thankfully acknowledged.

The author would like to thank members of the research committee, Prof. A. E. Krause, Prof P. Pramanick, Prof. Ram Manohar, Prof. Ron Bolton and Prof. T. S. Sidhu for their valuable comments and suggestions

Help and guidance provided by Dr. Res Saleh and his student Mr. Y. Wen during author's visit to the University Illinois at Urbana-Champagne is thankfully acknowledged.

The author would like thank Dr. Rama Munikoti, Director, Software Engineering and Analysis Laboratory, Nortel, for his encouragement and support. The author would like to thank his friends, Mr. Pramod Dhakal, and Dr. Atul Jain for their help during the course of this research and in the preparation of the thesis.

The author is grateful to his uncle, Mr. Madhav Jalnapurkar, aunt Mrs. Sheela Jalnapurkar for their constant encouragement and support.

Financial support provided by the University of Saskatchewan in the form of graduate scholarship and, Natural Sciences and Engineering Research Council of Canada, in the form of research assistantship is thankfully acknowledged.

Finally, the author would like to thank his wife Mrs. Archana Jalnapurkar for her patience and support.

#### **ABSTRACT**

Simulation plays an important role in the design of integrated circuits. Due to high costs and large delays involved in their fabrication, simulation is commonly used to verify functionality and to predict performance before fabrication. Depending upon the level of abstraction used, simulators may be classified as behavioral simulators, register transfer level simulators, gate level logic simulators, switch level simulators and electrical circuit simulators. Gate and switch level simulators provide approximate timing information, however, none of these simulators provide detailed timing Electrical circuit simulation is the only tool that provides information. accurate timing information and performance details. This, however. requires more than three orders of magnitude more computing time compared to gate or switch level simulators The importance and the high computing cost of circuit simulation provides motivation for the development of fast and accurate electrical circuit simulators. These can be achieved by using improved algorithms and high performance computer architectures to run the simulation engines.

This thesis describes analysis, implementation and performance evaluation of a distributed memory parallel waveform relaxation technique for the simulation of MOS VLSI circuits. The waveform relaxation technique exhibits inherent parallelism due to the partitioning of a circuit into a number of sub-circuits. These sub-circuits can be concurrently simulated on parallel processors. In addition, the full window waveform relaxation technique permits exchange of large and infrequent messages among sub-circuits. This feature is useful for parallel implementation on low cost distributed memory machines.

Different forms of parallelism in the direct method and the waveform relaxation technique are studied. An analysis of single queue and distributed queue approaches to implement parallel waveform relaxation on distributed memory machines is performed and their performance implications are studied. The distributed queue approach selected for exploiting the coarse grain parallelism across sub-circuits is described. A distributed queue implementation involves static partitioning and placement of sub-circuits on processors. An algorithm based on the critical path method and an algorithm based on bin packing heuristics are used to partition Gauss-Seidel and Gauss-Jacobi task graphs respectively. Parallel waveform relaxation programs based on Gauss-Seidel and Gauss-Jacobi techniques are implemented using a network of eight Transputers. Static and dynamic load balancing strategies are studied. A dynamic load balancing algorithm is

developed and implemented. Results of parallel implementation are analyzed to identify sources of bottlenecks.

This thesis has demonstrated the applicability of a low cost distributed memory multi-computer system for simulation of MOS VLSI circuits. Speed-up measurements prove that a five times improvement in the speed of calculations can be achieved using a full window parallel Gauss-Jacobi waveform relaxation algorithm. Analysis of overheads shows that load imbalance is the major source of overhead and that the fraction of the computation which must be performed sequentially is very low. Communication overhead depends on the nature of the parallel architecture and the design of communication mechanisms. The run-time environment (parallel processing framework) developed in this research exploits features of the Transputer architecture to reduce the effect of the communication overhead by effectively overlapping computation with communications, and running communications processes at a higher priority.

This research will contribute to the development of low cost, high performance workstations for computer-aided design and analysis of VLSI circuits.

# **Table of Contents**

| PER    | MISSION TO USE                              | i  |

|--------|---------------------------------------------|----|

| ACK    | ii                                          |    |

| ABS    | iii                                         |    |

| TAB    | LE OF CONTENTS                              | v  |

| LIST   | viii                                        |    |

| LIST   | OF TABLES                                   | ix |

| 1. INT | RODUCTION                                   | 1  |

| 1.1.   | Circuit Simulation                          | 4  |

| 1.2.   | Parallel Processing                         | 6  |

| 1.3.   | Motivation and Research Objectives          | 8  |

| 1.4.   | Thesis Outline                              | 10 |

| 2. CIR | CUIT SIMULATION TECHNIQUES                  | 12 |

| 2.1.   | Formulation of the Equations                | 13 |

|        | 2.1.1. Branch Relations                     | 16 |

| 2.2.   | Direct Method                               | 19 |

|        | 2.2.1. Time Step Control                    | 23 |

| 2.3.   | Relaxation Methods                          | 26 |

|        | 2.3.1. Linear Relaxation                    | 27 |

|        | 2.3.2. Nonliniar Relaxation Methods         | 32 |

| 2.4.   | Iterated Timing Analysis                    | 35 |

| 2.5.   | Waveform Relaxation                         | 37 |

|        | 2.5.1. Windowing Mechanism                  | 42 |

|        | 2.5.2. Circuit Partitioning                 | 44 |

| 2.6    | Summary                                     | 47 |

|        | ALLEL RELAXATION METHODS                    | 49 |

| 3.1.   | Parallel Processing Techniques              | 49 |

|        | 3.1.1. Shared Memory Systems                | 50 |

|        | 3.1.2. Distributed Memory Systems           | 52 |

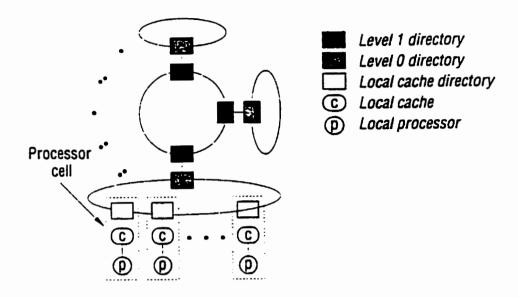

|        | 3.1.3. KSR Architecture                     | 54 |

| 3.2.   | Efficiency and Speed-up in Parallel Systems | 56 |

| 3.3.   | Parallel Direct Methods                     | 58 |

| 3.4.   | Common Parallelism in Relaxation Methods    | 61 |

| 3.5.   | Parallel Waveform Relaxation                | 67 |

| 3.6.   | Parallel Iterated Timing Analysis           | 70 |

| 3.7.                                       | Static Partitioning Techniques                            | 71  |

|--------------------------------------------|-----------------------------------------------------------|-----|

| 3.8.                                       | Placement Techniques                                      | 79  |

| 3.9.                                       | Summary                                                   | 82  |

| 4. PAR                                     | RALLEL WAVEFORM RELAXATION IMPLEMENTATION                 | 84  |

| 4.1.                                       | Implementation Strategies                                 | 85  |

|                                            | 4.1.1. Parallel Model Evaluation                          | 86  |

|                                            | 4.1.2. Single Queue Approach                              | 86  |

|                                            | 4.1.3. Distributed Queue Approach                         | 87  |

|                                            | 4.1.4. Multicomputer Interconnection Network              | 88  |

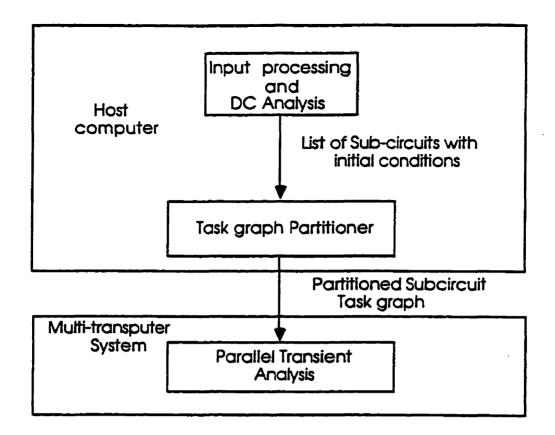

| 4.2.                                       | Program Structure Chart                                   | 89  |

| 4.3.                                       | Partitioning Algorithms                                   | 92  |

|                                            | 4.3.1. Partitioning Algorithm for Gauss Seidel Task Graph | 92  |

|                                            | 4.3.2. Partitioning Algorithm for Gauss Jacobi Task Graph | 94  |

| 4.4.                                       | Placement Algorithm                                       | 95  |

| 4.5.                                       | Parallel Transient Analysis                               | 95  |

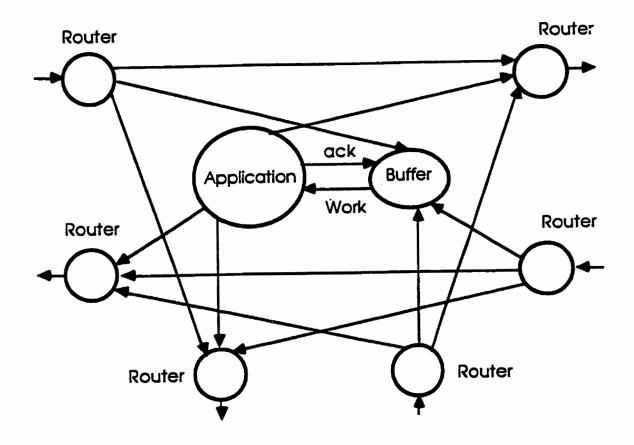

|                                            | 4.5.1. Process Framework                                  | 96  |

|                                            | 4.5.2. Instrumentation for Performance Measurements       | 98  |

| 4.6.                                       | Summary                                                   | 99  |

| 5. DYN                                     | NAMIC LOAD BALANCING                                      | 101 |

| 5.1.                                       | Limitations of Static Partitioning                        | 102 |

| 5.2.                                       | Dynamic Load Balancing Methods                            | 103 |

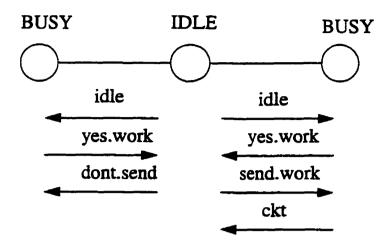

| 5.3.                                       | Dynamic Load Balancing Algorithm                          | 105 |

| <b>5.4</b> .                               | Implementation of Dynamic Load Balancing                  | 106 |

| 5.5.                                       | Summary                                                   | 111 |

| 6. RES                                     | SULTS                                                     | 112 |

| 6.1.                                       | Gauss Seidel Method                                       | 113 |

| 6.2.                                       | Gauss Jacobi Method                                       | 117 |

| 6.3.                                       | Analysis of Performance Limiting Factors                  | 118 |

|                                            | 6.3.1. Communication Overhead                             | 118 |

|                                            | 6.3.2. Sequential Computation                             | 122 |

|                                            | 6.3.3. Load Imbalance Overhead                            | 122 |

| 6.4.                                       | Dynamic Load Balancing                                    | 124 |

| 6.5.                                       | Summary                                                   | 125 |

| 7. SUMMARY, CONCLUSION AND FUTURE WORK 126 |                                                           |     |

| 7.1.                                       | Summary                                                   | 126 |

| 7.2.                                       | Conclusions                                               | 130 |

| 7.3. Future Work           | 131 |

|----------------------------|-----|

| REFERENCES                 | 133 |

| A. DEVICE MODEL EVALUATION | 141 |

| A.1. Linear Devices        | 141 |

| A.2. Nonlinear Devices     | 143 |

| B. NUMERICAL ANALYSIS      |     |

| C. TRANSPUTER AND OCCAM    | 149 |

# **List of Figures**

| Figure 2.1 | A MOS nand gate.                                   | 16  |

|------------|----------------------------------------------------|-----|

| Figure 2.2 | A MOS transistor in free space.                    | 18  |

| Figure 2.3 | A MOS transistor model.                            | 19  |

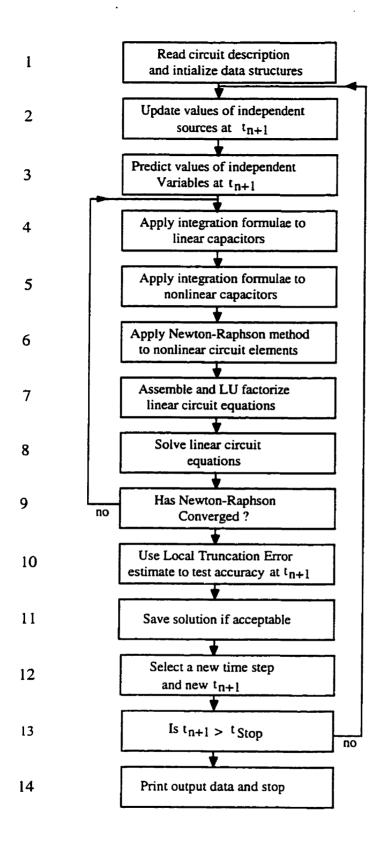

| Figure 2.4 | Flowchart of simulation process                    | 22  |

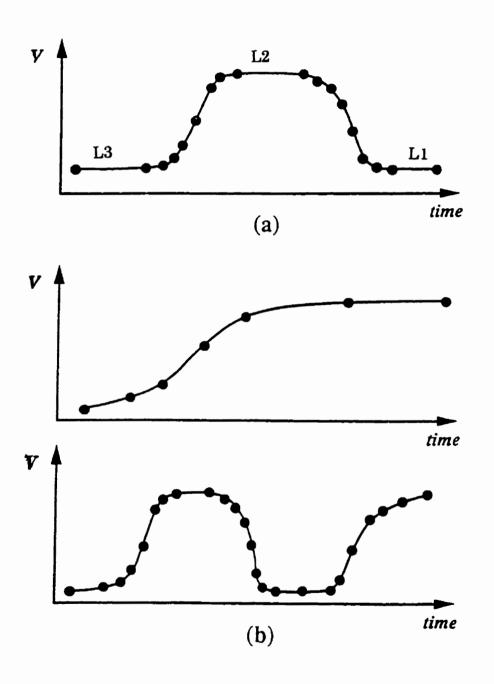

| Figure 2.5 | Waveform properties [a] Latency [b] Multi-rate     | 28  |

|            | behavior.                                          |     |

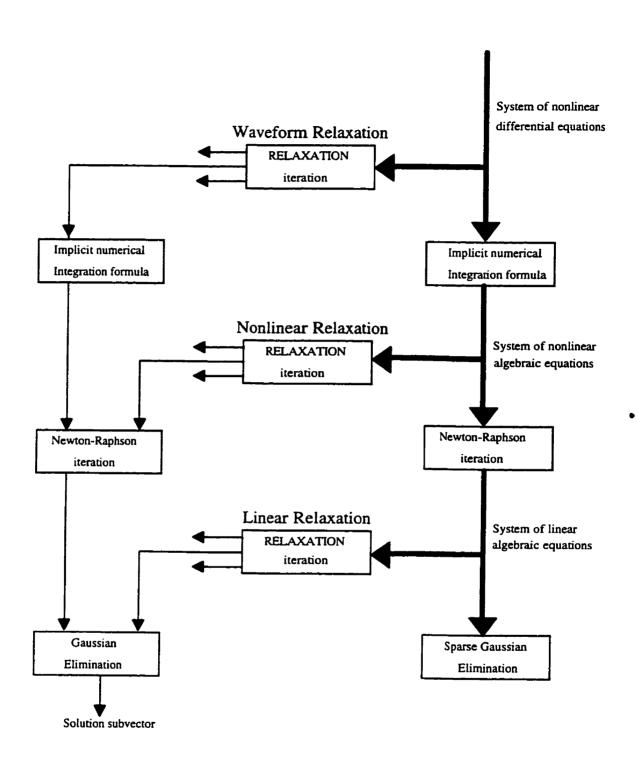

| Figure 2.6 | Relaxation-based techniques.                       | 29  |

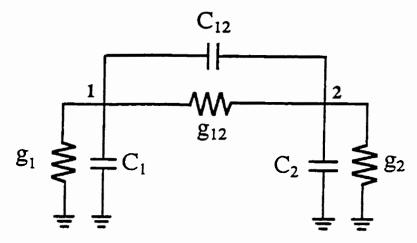

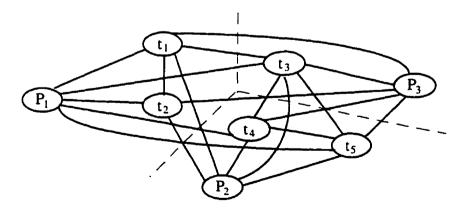

| Figure 2.7 | A linear circuit considered for partitioning.      | 46  |

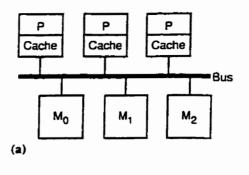

| Figure 3.1 | Shared memory interconnection networks.            | 51  |

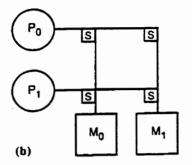

| Figure 3.2 | Multi-computer interconnection network topologies. | 53  |

| Figure 3.3 | KSR-1 architecture with a slotted ring for         | 56  |

|            | communication.                                     |     |

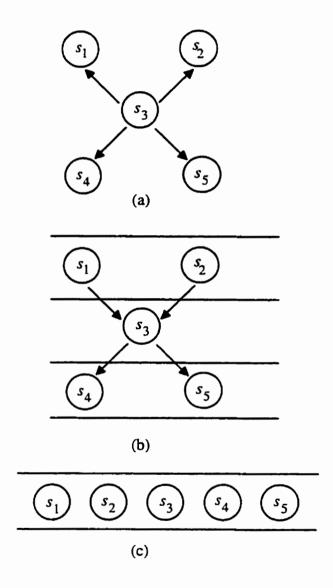

| Figure 3.4 | Examples of Gauss-Seidel and Gauss-Jacobi partial  | 64  |

|            | ordering for one iteration.                        |     |

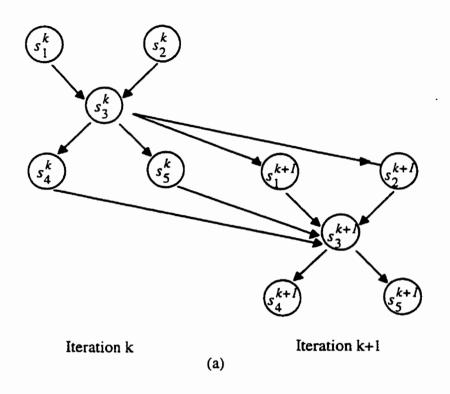

| Figure 3.5 | Unrolled (a) Gauss-Seidel (b) Gauss-Jacobi         | 66  |

|            | iterations.                                        |     |

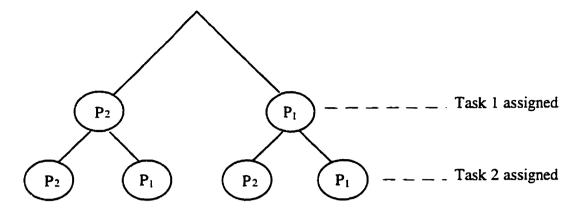

| Figure 3.6 | A <i>n</i> -processor network.                     | 75  |

| Figure 3.7 | A two-level search tree with two processors.       | 77  |

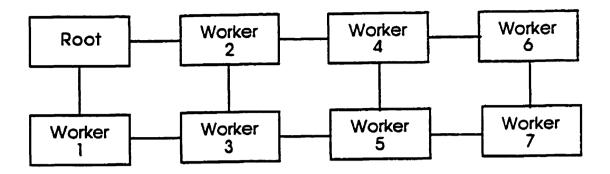

| Figure 4.1 | Network topology.                                  | 89  |

| Figure 4.2 | Program structure chart.                           | 91  |

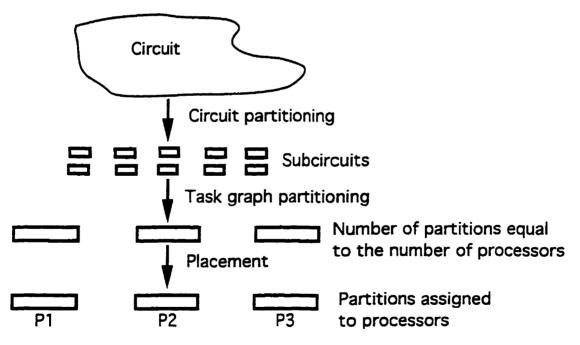

| Figure 4.3 | Circuit partitioning, task graph partitioning and  | 91  |

|            | placement.                                         |     |

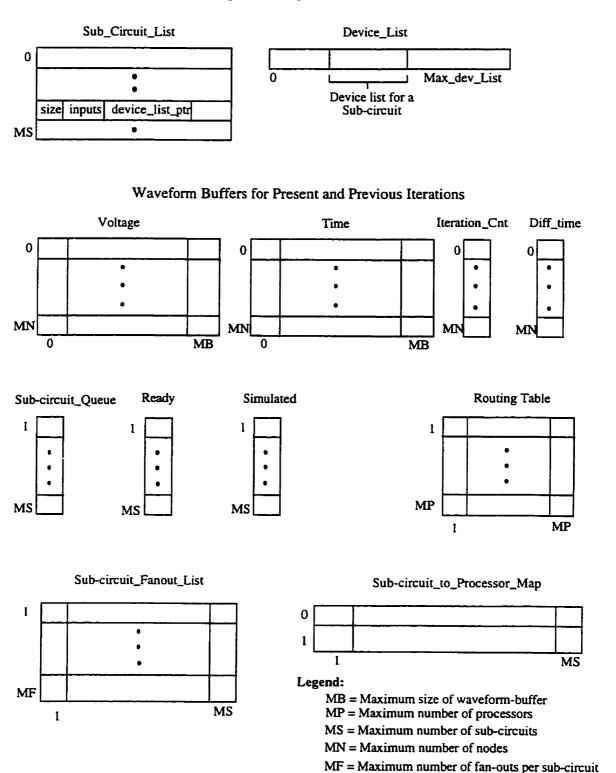

| Figure 4.4 | Data structures.                                   | 97  |

| Figure 4.5 | Process framework.                                 | 99  |

| Figure 5.1 | A dynamic load balancing algorithm.                | 107 |

| Figure 5.2 | The sim.remote() (Simulate Remote) procedure.      | 109 |

| Figure 5.3 | The sim.rdy.ckts() (Simulate Ready Circuits)       | 110 |

|            | procedure.                                         |     |

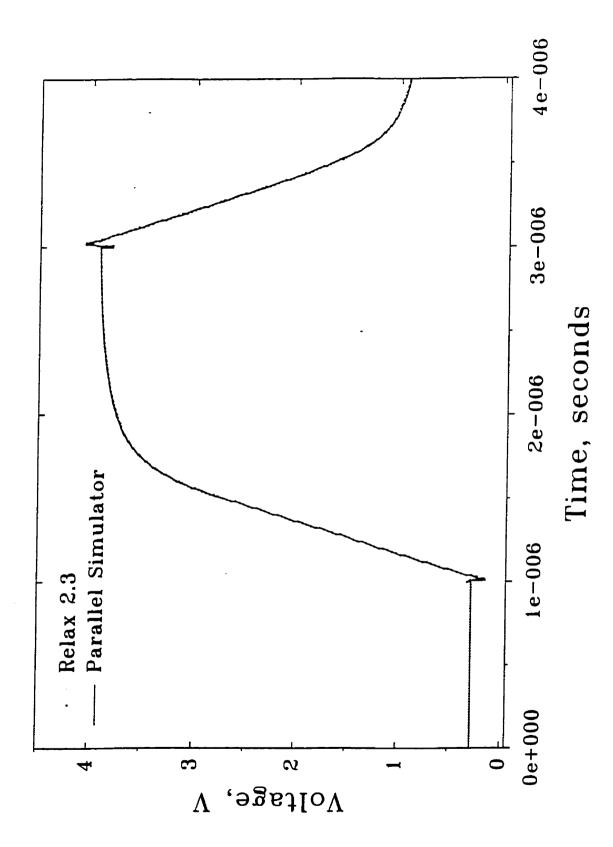

| Figure 6.1 | Node voltage waveforms for OPAMP.                  | 114 |

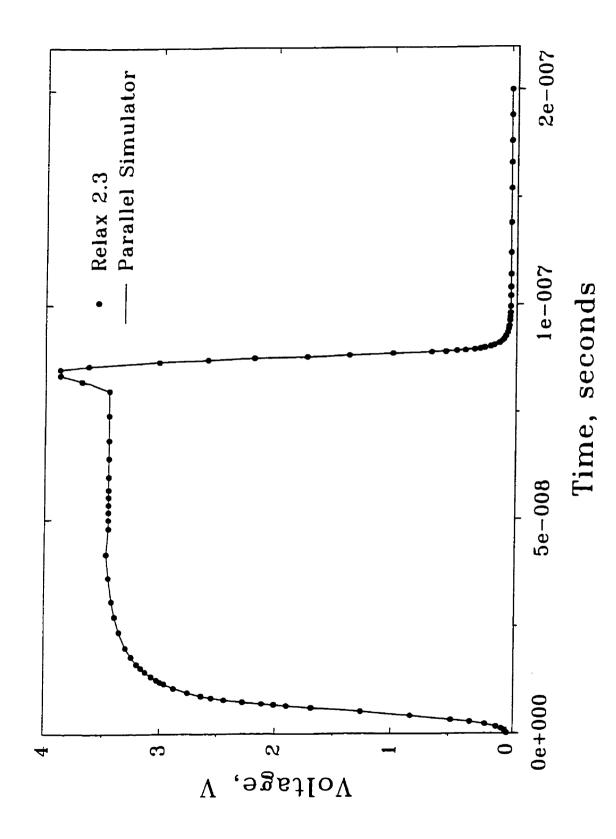

| Figure 6.2 | Node voltage waveforms for DECPLA                  | 115 |

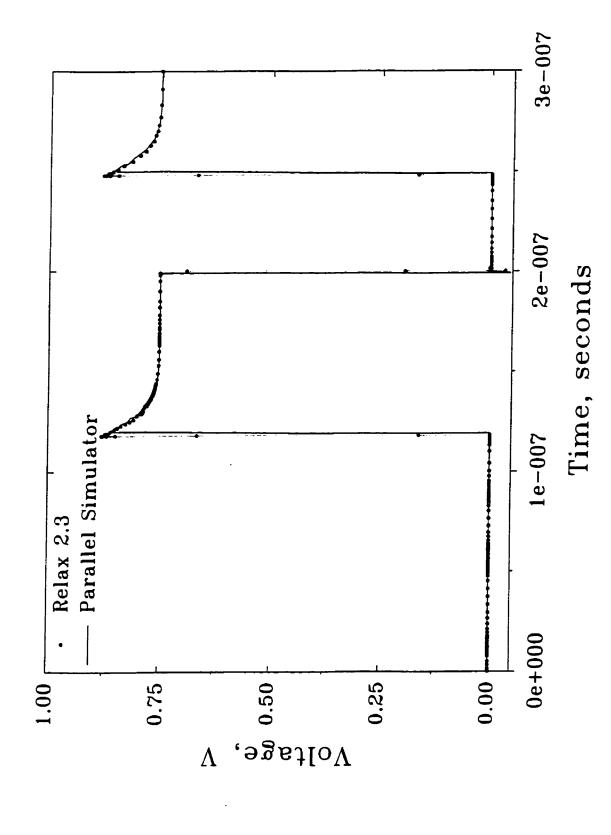

| Figure 6.3 | Node voltage waveforms for CRAMB.                  | 116 |

# **List of Tables**

| Table 6.1 | Benchmark Circuits.              | 113 |

|-----------|----------------------------------|-----|

| Table 6.2 | Speed-up for GS Algorithm.       | 117 |

| Table 6.3 | Speed-up for GJ Algorithm.       | 118 |

| Table 6.4 | Variation of Communication Cost. | 121 |

| Table 6.5 | Aggregrate Processors Idle Time. | 123 |

#### 1. INTRODUCTION

Advancement in integrated circuit technology has been very rapid since its inception in the early 1960s. Integrated circuit technology has pervasively influenced developments in many areas of science and technology. Several application domains such as data processing, consumer electronics, telecommunications, industrial electronics and automotive electronics have witnessed a phenomenal growth, especially in the last decade. This can largely be attributed to the developments in integrated circuit technology.

The economic impact of this technology in the world market has been remarkable. According to 1992 figures, electronics goods had a total market of over \$1000 billion, which constituted approximately 10% of the worldwide gross product. Projections for year 2000 indicate that electronics will have a market of over \$3000 billion [1][2]. A large sector of this market is driven by advancements in integrated circuit technology and its ever increasing applications.

The complexity of integrated circuits has grown tremendously. In the late 1960s, it was projected that the transistor density of chips would quadruple every three or four years. The actual growth in the complexity of the integrated circuits has exceeded these expectations.

An integration density of up to one million transistors per chip has become the reality and industry is now focusing on the integration of a billion transistors in a single chip. The major contributing factors in the growth of the integration density have been high-resolution lithography, improved reliability in processing silicon wafers, better understanding of system level design issues, and the availability of better computer aided design tools for circuit layout, simulation, verification and testing. Simulation plays an important role in the design of integrated circuits. Due to high costs and large delays involved in their fabrication, simulation is commonly used to verify functionality and to predict performance before fabrication. Fast and accurate simulation programs have been used to reduce the time to market the products. They provide a competitive advantage in today's rapidly changing marketplace.

Simulation programs have replaced traditional breadboard based prototyping techniques which are commonly used to validate circuits consisting of discrete components. Development of a breadboard based prototype of a modestly sized integrated circuit can be expensive and time consuming. In addition, it may provide grossly inaccurate results due to differences in the behavior of devices and values of parasitic components. Simulation programs also permit evaluation of architectural and design alternatives, during different phases of a development cycle, at a substantially lower cost than build and test methods. Early feedback on the validity of architecture and design can provide large economic gains.

A simulation program represents a circuit to be simulated in the form of an abstract model. The model accepts the primitive elements, and the rules of interconnection and operation as inputs. The output of the simulator describes the predicted behavior and performance characteristics of the circuit.

Different levels of abstraction of the circuit model are used at different stages of the design process. Depending upon the level of abstraction used, simulators may be classified as behavioral (also called algorithmic or functional) simulators, register transfer level simulators, gate level logic simulators, switch level simulators and electrical circuit simulators [2].

Behavioral simulators are used during the initial phase of design to verify important design concepts and algorithms. Behavioral simulators describe digital systems using functional blocks. Examples of applications appropriate for behavioral simulation include validation of the operation of a direct memory access (DMA) controller, or checking a new network protocol for a local area network (LAN).

Register transfer level (RTL) simulators describe integrated circuits using combinational components such as multiplexers, arithmetic units, and sequential components such as counters and registers. RTL simulators have been commonly used for data path design.

Gate level logic simulators use macro-models of logic gates that simulate digital circuits. Gate level simulators provide approximate timing information including the detection of hazards, glitches, and race conditions.

Switch-level simulators are used for logic simulation of MOS digital circuits. These simulators simulate the circuit at the transistor level. The transistors are modeled as gate controlled switches.

Electrical or circuit level simulators describe integrated circuits using devices such as transistors, resistors, capacitors and diodes. A system of equations is formulated using circuit topology, device models, input signals and initial conditions and solved using numerical methods. Circuit simulators provide detailed information about the circuit behavior and performance.

The nature of information provided by a simulator and its execution time depend on the level of abstraction. In general, as the level of abstraction goes down, the amount of computation increases. Behavioral and RTL simulators verify important design ideas and compare architectural alternatives without providing timing information. Gate and switch level simulators provide approximate timing information, however, none of these simulators provide the detailed timing information. Electrical circuit simulation is the only tool that provides accurate timing information and performance details. Typical timing accuracy is 1 nano-second and voltage tolerance is 0.001 Volts relative. This, however, requires more than three orders of magnitude more computing time compared to gate or switch level simulators [3].

The importance and the high computing cost of circuit simulation provides motivation for the development of fast and accurate electrical circuit simulators. These can be achieved by using improved algorithms and high performance computer architectures to run the simulation engines.

#### 1.1 Circuit Simulation

Electrical circuit simulation programs such as SPICE [4], ASTP [5] and SLATE [6] are commonly used by IC designers. SPICE is the most popular circuit simulation program. Many different versions of SPICE such as SPICE2, and SPICE3 [7] and commercial implementations such as HSPICE, PSPICE, and IGSPICE are in use [8]. These simulators are robust and permit analysis of a wide variety of circuits. However, they are not cost-effective for the analysis of circuits with more than few hundred transistors.

Commonly used circuit simulators such as SPICE and HSPICE provide models for several nonlinear, active circuit devices such as field-effect transistors (FETs), bipolar-junction transistors (BJTs), and diodes. They offer a wide variety of analyses including dc analysis, time domain transient analysis, ac analysis, noise analysis, and distortion analysis. Among these, time domain transient analysis is the most expensive in terms of computer time. The present work focuses on techniques to improve the speed of time-domain transient analysis while maintaining acceptable waveform accuracy.

The transient analysis process can be divided into two stages: equation formulation and equation solution. Given the circuit external excitations and topological description, the equations are derived by means of Kirchoff's current law (KCL), Kirchoff's voltage law (KVL) and branch relations (BR). Branch relations are mathematical descriptions of the electrical behavior of circuit elements, for example the diode current-voltage relation. Applying KCL, KVL and BR to a circuit yields a set of nonlinear algebraic-differential equations (NL-ADEs). The unknowns are usually node voltages and branch currents. Two approaches are used to solve NL-ADEs. The first approach consists of transforming the NL-ADEs into nonlinear algebraic equations. Subsequently, a set of linear algebraic equations is derived. These equations are then solved using a conventional direct method, generally LU decomposition.

The second approach, developed more recently, employs iterative or relaxation, methods at different levels of the simulation process. Depending upon the stage of application of iterative techniques, relaxation techniques can be classified as linear relaxation, non-linear relaxation and waveform

relaxation [3]. Linear relaxation techniques are used to replace Gaussian elimination. Non-linear relaxation techniques such as non-linear Gauss-Seidel and Gauss-Jacobi techniques can be used to solve the system of non-linear algebraic equations. Waveform relaxation techniques use iterative techniques at the differential equation level. Simulators based on these algorithms provide waveforms as accurate as those of a standard circuit simulator, with up to two orders of magnitude speed improvement for large circuits [9,10,11]. These simulators have been used for simulation of both digital and analog MOS ICs. Relaxation methods lend themselves well to parallel processing and have been the subject of extensive research within the last few years [10, 11, 12, 13].

Conventional circuit simulators such as SPICE and ASTAP were designed for the analysis of circuits containing up to a few hundred transistors [14]. Many designers have used these programs for simulating circuits containing thousands of transistors even though the computation requirement is several CPU hours. Saleh and Newton [8] have reported that at some companies the SPICE program is executed over 50,000 times a month. It is observed that 80% are small jobs which consume 20% of the CPU time, while 20% of the jobs consume 80% of the CPU time.

The main reasons for high computing costs are briefly explained below. The time domain transient analysis involves formulation and iterative solution of nonlinear ordinary differential equations. The equation formulation is an O(M) process where M is the total number of devices in the circuit. If M is large and device model equations are complex then the formulation process requires a large number of floating point operations. The order of complexity of each solution iteration varies from  $O(N^{1.1})$  to  $O(N^3)$ , where N is the total number of equations in the system, depending on the sparseness of the system [3]. Several such iterations are required to obtain the solution of the system at each time point. Therefore, time-domain transient analysis is very expensive in terms of computer time. The importance and the CPU intensive nature of transient analysis is the motivation for the development of high performance simulators.

Two approaches have been used to improve the simulator performance. The first approach involves the development of new algorithms, such as

waveform relaxation and iterated timing analysis. These algorithms have proven effective for the analysis of MOS digital circuits. The second approach involves partitioning the circuit simulation problem into subproblems such that a number of them can be evaluated concurrently using parallel processing techniques. More recently this approach has attracted a lot of attention. This research focuses on the application of parallel processing techniques to enhance performance of waveform relaxation techniques.

### 1.2 Parallel Processing

}'

Parallel processing is a form of information processing that exploits concurrent manipulation of data elements to reduce total elapsed time to completion. Pipelining and task parallelism are two methods used to achieve Pipelining increases concurrency by dividing a concurrency [15]. computation into a number of steps. Each computation step is assigned to a pipeline stage. Buffers exist between pipeline stages and the pipeline control mechanism ensures that all the pipeline stages are evenly loaded. Parallelism is the use of multiple resources (processing elements). Parallel processor designs can be divided into three classes according to the number and complexity of the processing elements used: fine-grain, medium-grain and large-grain [16]. In fine-grain parallel processing systems, each processing element (PE) is typically capable of executing a few simple instructions, whereas each PE of a medium-grain system is able to process a procedure-sized group of instructions, and a PE of a large grain system may have the capacity of an entire modern day computer. Several medium-grain systems have been built in the last decade; their popularity can be partly attributed to the availability of off-the-shelf medium-grained components (microprocessors and memory units).

According to the number of instruction and data streams used, parallel systems can be classified as single instruction, multiple data systems (SIMD) and multiple instruction, multiple data systems (MIMD) [17]. SIMD operation involves multiple processors simultaneously executing the same instruction on different data. A wide variety of array processors fall in this category. MIMD operation involves multiple processors autonomously

executing diverse instructions on diverse data. Depending upon the inter processor communication technique used, MIMD systems can be further classified as shared memory and message passing [18]. Each of these has its advantages and disadvantages. The primary advantage of shared memory systems is the ability of parallel processes to share a single address space; a significant disadvantage is the bottleneck created by this shared resource. In addition, other important problems such as data access synchronization and cache coherence must be solved. In message passing architectures, PEs share data by passing messages. These architectures have been principally constructed in an effort to provide a parallel architecture that will scale (accommodate a significant increase in number of processors) well and will satisfy the performance requirements of large scientific applications characterized by local data references [16][19]. This architectural approach requires that a parallel program be divided into disjoint processes such that there is minimal communication between them. An important disadvantage of the message passing approach is the message latency as the data is queued and forwarded by intermediate PEs. It is important to note that neither of the two approaches described above is a clear cut winner. Substantial research is in progress to find a match between applications and suitable architectures.

As mentioned above, medium grain systems can be built using commercially available processors and memory chips. These are usually less expensive in comparison with fine grain and large grain systems. Hardware complexity and cost of medium grain message passing systems is usually lower than that of shared memory systems. Several medium grain systems are readily available in the market. Therefore, a medium-grained message passing architecture based on the Inmos microprocessor T800 [20] is used for the project.

## 1.3 Motivation and Research Objectives

A number of approaches have been used to improve the performance of conventional DIRECT circuit simulators [3]. Look-up table techniques have been used to reduce the time required to evaluate complex device model equations [21, 22]. Techniques based on special purpose micro-code have

been investigated for reducing the time required to solve the sparse linear systems arising from the linearization of circuit equations [23]. Node tearing techniques have been used to exploit circuit regularity by bypassing the solution of sub-circuits whose state is not changing [24] and to exploit the vector processing capabilities of high performance computers such as the CRAY-1 [25]. In all the above cases, the overall speed improvement of the simulation has been at most an order of magnitude, for practical circuits [3].

Several commercial implementations of both shared memory and distributed memory parallel processing systems have become available in recent years. Multi-processor/multi-computer systems are attractive due to their low cost. These systems have been used to implement parallel direct method simulators. Parallel direct methods can exploit parallelism in formulation and solution of systems of equations. Newton and Sangiovanni-Vincentelli [3] have reported that for large circuits the majority of the time is spent in solution of linear systems of equations. The linear equation solution time grows faster than linearly with the circuit size. The LU factorization, forward elimination, and backward substitution used for the solution offers a limited • amount of parallelism. In addition, the sparse and asymmetric nature of the system matrix makes parallel implementation difficult.

Relaxation techniques such as non-linear relaxation and waveform relaxation partition the system of equations into a number of sub-systems. Iterative techniques are used across sub-systems. This avoids parallel solution of large and sparse systems of linear equations. It is usually possible (depending on the algorithm used and the nature of the circuit) to solve sub-systems in parallel. Some parallel architectures also allow exploitation of fine grain parallelism within an iteration of a single sub-system. Thus parallelism available at various levels of the simulation process can be exploited. In addition, relaxation based simulators allow the use of waveform properties such as latency and multi-rate behavior to reduce the simulation time. Therefore parallel relaxation based simulators have become a focus of research. Two relaxation based techniques, parallel Iterated Timing Analysis and parallel waveform relaxation have been reported in the literature [11][10]. Waveform relaxation is a robust technique. It inherently exploits multi-rate properties. It is also possible to

reported in the literature [11][10]. Waveform relaxation is a robust technique. It inherently exploits multi-rate properties. It is also possible to organize parallel implementation in such a way that sub-systems exchange large relatively infrequent messages. This property is useful for parallel implementation on distributed memory machines.

Most of the relaxation based parallel simulator implementations described in the literature [10,11,12,13], with the exception of CONSISE (a simulator developed at CALTECH by Sven Mattison [12]), use shared memory multiprocessors. CONSISE does not perform block partitioning. Block partitioning and its impact on parallel implementation will be discussed later in the thesis. The message passing programming model is substantially different from a shared-memory programming model. Therefore detailed investigation of problems involved in implementing a circuit simulator on the more economical message passing systems is necessary.

While a few implementations have been described in the literature, there has been little done by way of performance analysis and evaluation of distributed memory parallel waveform relaxation. This is an area that deserves much more attention to identify bottlenecks of particular implementations or architectures.

The principal objective of this work is to study issues involved in the application of distributed memory parallel processing for the simulation of MOS digital VLSI circuits using waveform relaxation techniques. In particular, this thesis will determine how much the speed of calculation in circuit simulation can be increased with a low cost distributed memory parallel processing system. Also, a method will be sought to efficiently implement circuit simulation on the distributed memory machine.

The study involves analysis of different forms of parallelism in the direct method and the waveform relaxation technique. An analysis of various implementation strategies and their performance implications will be performed. A strategy appropriate for implementation on medium grained distributed memory machines will be selected. Two forms of the waveform relaxation algorithm will be implemented using a multi-transputer system to compare their performance characteristics. Load imbalance is a major

algorithm will be developed and implemented. Results of parallel implementation will be analyzed to identify sources of bottlenecks and possible remedies will be suggested.

#### 1.4 Thesis Outline

This thesis describes important aspects of the distributed memory parallel waveform relaxation technique for the simulation of MOS VLSI circuits. The understanding of the research work requires background information in waveform relaxation techniques and parallel processing.

Chapter 2 reviews prior research on the waveform relaxation techniques. The chapter presents speed and robustness enhancement techniques, such as circuit partitioning and window selection. The waveform relaxation technique partitions a circuit into a number of sub-circuits. The direct method is used for simulation of sub-circuits, therefore, the direct method is also described. The topics presented in this chapter are mainly based on [3][14][8][26].

The objective of Chapter 3 is to describe issues and options involved in the parallel implementation of relaxation based circuit simulators. The information presented in this section can be divided into two logical parts. The first part consists of generic background on parallel processing issues. Important classes of parallel architectures are described and the effects of different forms of overheads on performance of parallel applications are analyzed. The second part is devoted to the analysis of issues involved in the parallel implementation of circuit simulation programs. Coarse and fine grain parallelism in the direct and relaxation methods are analyzed. The discussion in Section 3.3 and Section 3.4 is based on the work of Saleh et al. [27]. The discussion concentrates mainly on issues involved in parallel implementation of waveform relaxation programs on shared memory multi-Issues specific to distributed memory machines such as processors. partitioning and allocation are described in Sections 3.7 and 3.8.

Chapter 4 presents an implementation of a parallel waveform relaxation program. Two implementation strategies, a single queue and a distributed queue approach are compared. The parallel processing framework, and the

placement and partitioning algorithms used for the implementation are described.

An imbalanced workload in a parallel processing system results in low overall efficiency and speed-up. Load offered by a circuit simulator when simulating a large digital circuit changes with simulation time due to latency and multi-rate behavior. Therefore, load imbalance is an important source of overhead. Chapter 5 presents dynamic load balancing techniques used to reduce the load imbalance overhead. A implementation using a multi-transputer system is also presented.

Results of implementations described in Chapters 4 and 5 are given in Chapter 6. The effects of performance limiting factors are also analyzed. Finally Chapter 7 concludes the thesis, and gives suggestions for further research.

## 2. CIRCUIT SIMULATION TECHNIQUES

The last two decades have seen a substantial growth in the size and complexity of integrated circuits. Conventional prototyping techniques used to verify electronic circuit design and predict performance, such as breadboard implementation, are inadequate for large integrated circuits for several reasons. For example, modeling of parasitic components is difficult because the physical contexts of the prototype and the resultant system are so different. In addition, time and cost of prototype development is usually Important goals of integrated circuit development very high. minimize development time and to reduce risk. These goals fostered the development of computer programs to simulate integrated circuits. Early attempts in this direction led to the development of a simulation program CANCER [28]. SPICE, a successful circuit simulation program, evolved from CANCER. Later versions of SPICE, SPICE2 [4], and SPICE3 [7] added functionality and improved robustness. These programs use conventional Newton-Raphson based methods.

A wide variety of algorithms to improve the performance of simulators without sacrificing accuracy have been described in the literature. Of these approaches, the relaxation based approaches, such as, waveform relaxation [9][10], iterated timing analysis [11] and waveform-relaxation-Newton [11] are ideally suited for simulating MOS digital circuits. This is due to the unidirectional nature of MOS devices. That is, due to the insulated gate terminal, the current through the gate is independent of the voltages at the other device terminals, if the effects of small gate-to-drain and gate-to-source capacitances are ignored [14]. The unidirectionality property helps relaxation decomposition, as will become clear later. This chapter describes basic mathematical techniques used for development of a circuit simulation program to perform time-domain transient analysis. Techniques used to formulate a system of non-linear ordinary differential equations are

described. Both direct and relaxation based techniques are discussed. Topics presented in this chapter are mainly based on [3][14][8][26][29][30].

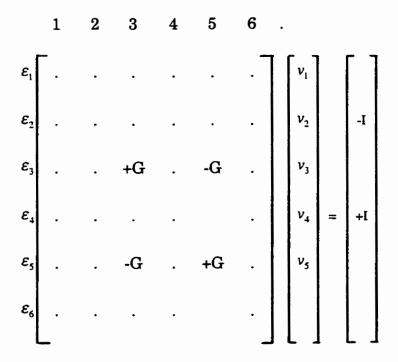

## 2.1 Formulation Of The Equations

The first task performed by a circuit simulator is to read the circuit description and formulate a set of algebraic differential equations based on Kirchoff's Current (KCL) and Voltage law (KVL), and Branch relations. There are several different ways of formulating a system of equations. The most popular of these are Nodal Analysis, Modified Nodal Analysis and Sparse Tableau Analysis. Nodal analysis is the oldest and the most frequently used method [29]. Node voltages are unknown variables in this formulation. The main reason for popularity of nodal analysis is its simplicity. However it is difficult to simulate circuits with floating voltage 's sources and current controlled devices. Direct evaluation of branch currents is also difficult. Modified Nodal Analysis (MNA), implemented by Ho et al. [31], overcomes these difficulties. MNA can treat node voltages, voltage source currents, output currents and controlling source currents as unknown variables. The SPICE2 program uses MNA.

Sparse Tableau Analysis is the most general method. In this method, the set of unknown variables includes all branch voltages, branch currents and node voltages. This method formulates more equations per circuit than the previous two techniques, however the system of equations is usually very sparse and therefore the number of floating point operations necessary to solve these equations can be less than the number required to solve smaller, more dense systems such as those derived from nodal analysis [29].

MOS digital circuits seldom use floating voltage sources and current controlled devices. Therefore NA is an adequate formulation for their analysis. NA has been used in this thesis. The following assumptions are made while formulating the system of equations.

1. All resistive elements, including active devices, are characterized by constitutive equations where voltages are controlling variables and currents are controlled variables.

- 2. All energy storing elements are two-terminal, possibly nonlinear, voltage-controlled capacitors.

- 3. All independent voltage sources have one terminal connected to ground or can be transformed into independent current sources with the use of the Norton transformation.

Another important assumption required by relaxation-based simulators is that a two-terminal capacitor be connected from each node of the circuit to ground. This assumption is satisfied by circuits where lumped parasitic capacitances are present between circuit interconnect and ground or on the terminals of active circuit elements. This assumption helps in ensuring that the capacitance matrix has all non-zero diagonal elements. This point is further elaborated in Section 2.3.

The process of formulating a system of equations with node voltages as unknown variables consists of three steps. The first step is to use KCL to formulate a system of equations in terms of branch currents and node charges. The form of KCL which states that the algebraic sum of currents incident at a node must be equal to the rate of change of the algebraic sum of charges at the node, is assumed in the discussion. Then the branch currents and node charges are expressed in terms of branch voltages using branch relations. Finally, branch voltages are expressed in terms of node voltages using KVL.

The application of nodal analysis to a (N+1) node circuit yields N linear independent equations in N unknowns. Node (N+1) is treated as a reference or ground node and the corresponding equation is discarded. Thus, for each node in the circuit the following equation can be written:

$$\frac{d}{dt} \sum_{\text{capactive element at } j} q_{\text{element}} + \sum_{\text{other elements at } j} i_{\text{element}} = 0. \tag{2.0}$$

The resulting system of N equations can be written in the form:

$$\dot{\mathbf{q}}(v(t), u(t)) = -\mathbf{f}(v(t), u(t)) \tag{2.1}$$

where  $q(v(t), u(t)) \in \mathbf{R}^n$  is the vector of the sum of charges due to the capacitors connected to nodes,  $\dot{\mathbf{q}}(v(t), u(t)) \in \mathbf{R}^n$  is the vector of time derivatives of  $q(v(t), u(t)) \in \mathbf{R}^n$ ,  $v(t) \in \mathbf{R}^n$  is the vector of node voltages at time t,  $u(t) \in \mathbf{R}^n$  is the input voltage vector at time t and  $f, f: \mathbf{R}^n \times \mathbf{R}^n \to \mathbf{R}^n$  is a vector function. It can be expressed as:

$$f(v(t),u(t)) = [f_1(v(t),u(t)),f_2(v(t),u(t)),\cdots,f_N(v(t),u(t))]^T$$

An *i*th element of f,  $f_i(v(t),u(t))$ , represents the sum of currents charging the capacitors connected to node i. Equation 2.1 is known as the charge formulation of the circuit equations because charge is treated as a state variable. It is also possible to treat voltage as the state variable. The resulting system of N equations can be written in the following form:

$$C(v(t),u(t))\dot{v}(t) = -f(v(t),u(t)); t \in [0,T];$$

$$v(0) = V.$$

(2.2)

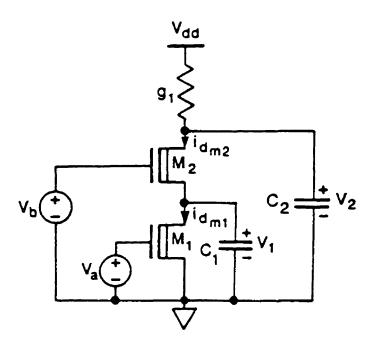

where  $C(\bullet): \mathbb{R}^n \to \mathbb{R}^{n \times n}$  represents the nodal capacitance matrix. The two formulations are equivalent for circuits with linear capacitors. However charge formulation must be used in circuits with nonlinear capacitors in order to keep the total charge in the system constant during the simulation process. Both formulations are used in this thesis. The equation formulation process can be explained with help of the following example [14]. Consider the nodal equation formulation for the MOS nand circuit of Figure 2.1:

The nodal equation for the first node is:

$$i_{d_{m1}}(v_1, V_a, 0) - i_{d_{m2}}(v_2, V_b, v_1) + \frac{d}{dt}[q_{d_{m1}}(v_1, V_a, 0) + q_{s_{m2}}(v_2, V_b, v_1) + C_1v_1] = 0,$$

(2.3)

and for the second node,

$$i_{d_{m_2}}(v_2, V_b, v_1) + g_1 * (v_2 - V_{dd}) + \frac{d}{dt}[q_{d_{m_2}}(v_2, V_b, v_1) + C_2 v_2] = 0,$$

(2.4)

where  $i_{d_{m1}}$  and  $i_{d_{m2}}$  are the currents from drains to sources of transistors M1 and M2 respectively, and  $q_{d_{m1}}$ ,  $q_{d_{m2}}$ ,  $q_{s_{m2}}$  are the charges accumulated at the drain of transistor M1 and the drain and source of transistor M2, respectively. Although KVL equations have not been formulated explicitly, they have been used for expressing branch voltages in terms of node voltages. Current and charge terms in these equations can be expressed in terms of node voltages using branch relations. Branch relations are discussed in the following subsection.

Figure 2.1: A MOS nand gate [14].

#### 2.1.1 Branch Relations

Branch relations are mathematical descriptions of the electrical behavior of circuit elements. The branch relations can be divided into three different categories: resistive, capactive and inductive. Resistive and capactive branch relations are described because these are necessary for analysis of MOS digital circuits. Resistive branch relations relate voltages to currents and capacitive equations relate voltages to charges.

The branch relations for an n-terminal device can be represented by a set of (n-1) algebraic equations involving (n-1) terminal voltages and currents or

charges. One terminal is used as a reference and voltages of the other terminals are determined with respect to this reference terminal. The relation between diode current and anode-to-cathode voltage is an example of resistive branch relation. The current through the diode,  $i_a$ , can be computed from the following approximate equation:

$$i_a = I_s(e^{\frac{v_{ac}}{V_t}} - 1)$$

(2.5)

where  $v_{ac}$  is the anode-to-cathode voltage across the diode,  $I_s$  is the saturation current and  $V_s$  is the thermal voltage.

If the device currents can be uniquely determined from the equations, given the device voltages, then the device equations are said to be voltage-controlled. Often, given a set of device equations, it is possible to perform a transformation so that the device currents are explicit functions of device voltages. For example, Equation 2.5 is voltage-controlled because in it the current,  $i_a$ , is an explicit function of the device voltage,  $v_{ac}$ .

The commonly used approximate equations for a MOS transistor are another example of voltage-controlled device equations. The approximate device equations can be expressed as:

$$i_{d} = \frac{kW}{2L} \left[ 2(v_{gs} - v_{T})v_{ds} - v_{ds}^{2} \right] \quad \text{for } v_{ds} \le v_{gs} - v_{T}; \tag{2.6}$$

$$\begin{split} i_d &= \frac{kW}{2L} (v_{gs} - v_T)^2 \qquad \text{for } v_{ds} \geq v_{gs} - v_T; \quad \text{and} \\ i_g &= 0; \end{split} \tag{2.7}$$

where  $i_d$  is the drain current, k is a parameter depending on the carrier mobility and thickness of the oxide, W and L are the width and the length of the channel of the transistor,  $v_{gs}$  is the gate-to-source voltage,  $v_{ds}$  is the drain-to-source voltage,  $v_{\tau}$  is the threshold voltage, and  $i_g$  is the gate current. The branch current equations for the MOS transistor are specified by two different algebraic functions, where the function is determined by the voltages at the terminals. Most of the devices in use today can be expressed by voltage controlled equations and therefore satisfy the first assumption mentioned above.

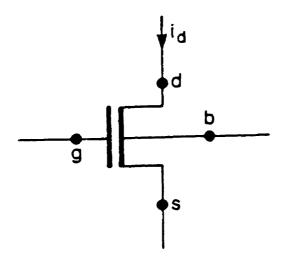

Figure 2.2: A MOS transistor in free space.

Branch equations for an n-terminal capacitive device are a set of (n-1) algebraic equations involving terminal voltages and terminal charges. For most commonly modeled devices, there exists a set of equations for the terminal charges that are voltage-controlled. For example, consider the junction capacitance for the diode for the case where the voltage across the diode  $v_{ac} \leq 0.0$ . Then, the anode charge,  $q_a$ , can be computed to the first order with the equation:

$$q_a = C_0 \left(\frac{1 - v_{ac}}{\phi}\right)^{1 - m} \tag{2.8}$$

where  $C_0$  is the zero-bias junction capacitance and  $\phi$  is the junction potential. Similarly, charge equations for capacitors of a MOS transistor (see Figure 2.2) in the saturation region are given by:

$$q_{g} = \frac{2}{3} WLC_{\alpha x} (v_{gs} - v_{T}) + C_{p} (v_{gs} - v_{ds}); \text{ and}$$

$$q_{d} = 0;$$

(2.9)

where  $q_g$  and  $q_d$  are respectively the charge stored at the gate and the charge stored at the drain of the device,  $C_{\alpha}$  is the oxide capacitance, and  $C_p$  is small parasitic capacitance.

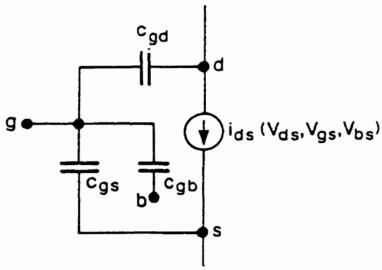

Given a physical device, its electrical behavior is best described by a combination of resistive and capacitive branch equations. Certain devices may require inductive branch equations as well. Inductive effects are usually considered for analysis of high frequency circuits. Analysis of MOS digital circuits seldom involves inductive branch equations. Therefore, these equations have been omitted from the discussion. Often the branch equations are symbolically represented by ideal elements such as two-terminal linear and nonlinear resistors, two terminal capacitors and controlled sources. For example, the MOS transistor model is represented by Figure 2.3.

Figure 2.3: A MOS transistor model.

#### 2.2 Direct Method

This section describes the procedure to obtain transient response of a given circuit using the direct method. As mentioned in the previous section, transient analysis involves formulation and solution of a system of nonlinear algebraic differential equations. Important mathematical steps involved in the simulation process are described below.

The first step is to formulate a system of equations similar in form to Equation (2.1) or Equation (2.2). The time derivative terms in the system of equations are then discretized using stiffly stable integration formulas, such as Backward Euler (BE), the Trapezoidal Rule (TR), or Gear's Variable-

Order Method (GE) [26][29]. An integration method divides the continuous simulation interval [0, T], into a set of M discrete time points defined by

$$t_0 = 0,$$

$t_{n+1} = t_n + h_n,$   $t_M = T.$

The system of equations is solved at each time point  $t_{n+1}$ . The quantity  $h_n$  is known as the time step at time point  $t_n$ . The commonly used stiffly stable integration formulas are given below:

**Backward Euler:**

$$\dot{v}_{n+1} = \frac{v_{n+1} - v_n}{h_n}$$

Trapezoidal Rule:

$$\dot{v}_{n+1} = \frac{2}{h_n} (v_{n+1} - v_n) - \dot{v}_n$$

Gear's Variable Order Method:

$$\dot{v}_{n+1} = \frac{1}{h_n} \sum_{i=0}^{k} \alpha_i v_{n+1-i}$$

where  $v_n$  is the value of the unknown variable v at time  $t_n$ ,  $h_n$  is the nth integration time step, and  $\alpha$  and k are constants that depend on the order of the Gear's method. The application of integration formulas results in a set of nonlinear algebraic equations of the form:

$$g(v) = 0, (2.10)$$

where  $v \in \mathbb{R}^N$  is the vector of unknown voltages at  $t_{n+1}$ . These equations are then solved using a Newton-Raphson algorithm. A general form of the Newton-Raphson iteration equation to solve F(v) = 0, where  $v \in \mathbb{R}^N$  and  $F: \mathbb{R}^N \to \mathbb{R}^N$  is:

$$J_F(v^k)(v^{k+1}-v^k) = -F(v^k), \tag{2.12}$$

where  $J_F(v)$  is the Jacobian of F(v) and  $v^{k+1}$ ,  $v^k$  are k+1th and kth iterates respectively. Thus, the Newton-Raphson algorithm yields a set of linear equations of the form:

Av = b, (2.5)

where  $A \in \mathbb{R}^{N \times N}$  is a matrix related to the Jacobian of g and  $b \in \mathbb{R}^N$ . Typically less than 2 percent of the entries of A are non-zero for N > 500. The matrix is sparse because each node in the circuit is connected to only a few other nodes. These equations are then solved by using direct methods, such as sparse LU decomposition or Gaussian elimination. The Newton-Raphson process is iterated until convergence or until an upper bound on the number of iterations is reached. Typical bounds on convergence are 50 micro-volts absolute and 0.001 relative. A new time step is then selected. This procedure is continued until the simulation is complete.

Figure 2.4 shows a flowchart of the simulation process. The simulator operation begins by reading the circuit description. Values of the independent sources are computed at the present time point and values of the unknown variable are predicted using their values at previous time points. Each device is represented using resistors, capacitors and current sources. Integration formulas are applied to linear and nonlinear capacitors, nonlinear devices are linearised using the Newton-Raphson method and a system of linear equations is formulated. The process of applying integration formulas to capacitors and linearising nonlinear devices (steps 4, 5 and 6) is known as device model evaluation which is described in Appendix A. The system of equations is solved using sparse matrix techniques. convergence of the NR iteration, local truncation error estimates are used to test the accuracy of the solution and to select a new time step. Time step control techniques are discussed in the following subsection. Steps (2) to (13) are repeated until the simulation is complete.

The direct method discussed above has proved to be reliable and accurate for simulation of a wide variety of circuits. However it has several limitations. Referring again to Figure 2.4, the majority of time spent in steps (2) to (13) can be lumped in two categories: the time required to form entries of A and b in Equation 2.5, the FORM phase (steps (5) and (6)), and the time required to solve the system of sparse linear equations, the SOLVE phase, (steps (7) and (8)). Several researchers have observed that for small circuits

Figure 2.4: Flowchart of the simulation process [32].

(N < 20), the majority of the time is spent in performing the FORM, however, when the size of the circuit grows, an increasing percentage of the time is spent in the SOLVE phase [3]. The time spent in the SOLVE phase has been measured to grow as  $O(N^{\beta})$  where  $1.1 < \beta < 1.5$  [3]. On the other hand, the time required for FORM grows linearly with the number of circuit elements. Thus the SOLVE phase becomes a major bottleneck while simulating large circuits using the conventional approach. In addition, it is difficult to exploit waveform properties described later such as latency and multi-rate behavior. The relaxation-based techniques described in the next section attempt to solve these problems.

#### 2.2.1 Time Step Control

The time required for simulating a circuit is proportional to the number of time steps necessary. Therefore, an objective of any circuit simulation algorithm is to reduce the number of time steps without sacrificing accuracy. Several schemes to select time steps for solving systems of NL-ADEs have been described in the literature. Commonly used time step control schemes for circuit simulation are: global fixed time step, iteration count, and Local Truncation Error (LTE) based time step control [4, 18, 26].

The fixed time step scheme selects the time step depending upon the fastest changing variable of a circuit. This scheme is very inefficient because several unnecessary time points are computed for time intervals when signals are changing slowly. The iteration count scheme uses some heuristic for selecting an initial time step. If the number of iterations required for convergence is larger than some  $N_{high}$ , the step size is reduced by some factor. If the number of iterations is less than  $N_{low}$ , the step size is increased by some factor. Otherwise the step size remains the same. This scheme is efficient; however there is no explicit accuracy control. It is commonly used in conjunction with the LTE-based scheme described below.

The LTE-based schemes observe the state of the circuit and the time step is adaptively changed accordingly. The Local Truncation Error (LTE) is the error made in one time step. If  $x_{n+1}$  is the numerical solution of a system of differential equations of the form

$$\dot{x}(t) = f(x(t), u(t)), \quad x(0) = X, \quad t \in [0, T], \tag{2.13}$$

at time point  $t_{n+1}$  and  $x(t_{n+1})$  is the corresponding exact solution. Also if all previous solutions  $(x_n, x_{n-1}, \cdots)$  are exact. Then the local truncation error for a general multistep integration method is defined as:

$$LTE_{n+1} = x(t_{n+1}) - x_{n+1}. (2.14)$$

The local truncation error depends on the integration method and the time step. For example, the LTE for the trapezoidal method [26] can be shown to be

$$LTE_{n+1} = -\frac{h_n^3}{12} \frac{d^3 x}{dt^3}(\xi) \qquad t_n \le \xi \le t_{n+1}. \tag{2.15}$$

The general form of the local truncation error [29] for most multistep integration methods of order k is given by

$$LTE_{n+1} = \tilde{C}_k h^{k+1} x^{(k+1)}(\xi) \qquad t_n \le \xi \le t_{n+1}. \tag{2.16}$$

where  $\tilde{C}_k$  is a constant which depends on the integration method. The LTE-based time step control scheme estimates the LTE at each time step. The solution is accepted if the estimated LTE is less than the user-specified tolerance. The user-specified tolerance is usually expressed in terms of an absolute error parameter  $\varepsilon_a$  and a relative error parameter  $\varepsilon_a$  as

$$E_{UserLTE} = \varepsilon_a + \varepsilon_r \times \max |x_{n+1}, x_n|$$

(2.17)

The value of the derivate term  $x^{(k+1)}(\xi)$  in the Equation 2.16 above is unknown. It can be approximated using divided difference as

$$x^{(k+1)}(\xi) \approx (k+1)! DD_{k+1}(t_{n+1}), \tag{2.18}$$

where  $DD_{k+1}(t_{n+1})$  is the k+1st order divided difference. The LTE estimate is then

$$E_{k} = C_{k} h^{k+1} D D_{k+1} (t_{n+1})$$

(2.19)

If predictor-corrector technique and BDF integration methods are used for the solution of differential equations then LTE can be easily estimated using the difference between the computed solution  $x_{n+1}$  and the predicted value  $x^{P}(t_{n+1})$ . The estimated LTE for a kth order BDF is given by [11]:

$$E_{k} = \left[\frac{h_{k}}{t_{n+1} - t_{n-k}}\right] (x_{n+1} - x^{P}(t_{n+1}))$$

(2.20)

where the predicted solution  $x^{P}(t_{n+1})$  can be computed using an explicit integration method. The predictor can be expressed as

$$x_{n+1}^0 = \sum_{i=1}^{k+1} \gamma_i x_{n+1-i}$$

(2.21)

where the superscript 0 indicates the 0th iteration and the  $\gamma_i$  values are selected such that the predictor  $x_{n+1}^0$  is correct if the solution is a kth order polynomial. Usually a kth-order predictor is used with a kth order integration method. The computed solution  $x_{n+1}$  is accepted if

$$|E_K| < E_{UserLTE}$$

.

Saleh [11] has proposed a convenient method of implementing this check which is described below. A ratio r of allowable LTE and the actual LTE is computed.

$$r = \left| \frac{E_{UserLTE}}{E_k} \right| = \frac{\left| C_k h_{\max}^{k+1} \ddot{x}(\xi) \right|}{\left| C_k h_n^{k+1} \ddot{x}(\xi) \right|}$$

(2.22)

Therefore

$$r = \left[\frac{h_{\text{max}}}{h_n}\right]^{k+1} \tag{2.23}$$

and

$$r_{LTE} = \left[\frac{h_{\text{max}}}{h_n}\right] = (r)^{(\frac{1}{k+1})}$$

(2.24)

If

$$r_{ITF} > 1.0$$

,

then the solution is accepted. The ratio can be also used to compute the next time step. The next recommended step is given by

$$h_{n+1} = r_{LTE} h_n \tag{2.25}$$

In addition to limits imposed by the local truncation error, a few practical considerations are also used for selecting the next time step. For example, time step is selected in such a way that steps fall on input break points and window boundaries. Bryton et al. [33] have observed that in several practical cases, rapid changes in step sizes introduce instability problems. Therefore it is necessary to limit changes in step size. The Relax2.3 and iSPLICE3 [14, 8] programs use four parameters,  $s_l$ ,  $s_u$ ,  $\alpha$ , and  $\beta$  to control changes in step size. The step can be reduced at most by a factor  $s_l$  and increased by a factor  $s_u$ . The factor  $\alpha$  permits the same step size to be used a number of times and  $\beta$  is a growth factor. The strategy used for limiting changes in step size is described below. If  $r_{LTE} < 1.0$  then the step size is reduced by a factor  $MAX(s_l, r_{LTE})$ . If  $1.0 < r_{LTE} < \alpha$ , the same step size is maintained. Similarly if  $r_{LTE} \ge \alpha$  then the step size is increased by  $MIN(s_u, \beta r_{LTE})$ . Typical values of the parameters are  $s_l = 0.25$ ,  $s_u = 2.0$ ,  $\alpha = 1.2$  and  $\beta = 0.9$ .

### 2.3 Relaxation Methods

Relaxation methods are numerical techniques used for the solution of a system of linear, nonlinear and differential equations. The basic structure of a relaxation-based simulator is similar to the standard circuit simulator. A set of NL-ADEs, in the form of Equation 2.2 or Equation 2.3, are formulated using KCL, KVL and branch relations and relaxation-based techniques are used to solve them. The relaxation techniques have two advantages: they do not require direct solution of a large system of linear equations, resulting in a considerable reduction in the SOLVE bottleneck, and they permit the simulator to exploit latency and multi-rate behavior efficiently [11]. Latency and multi-rate behavior are discussed below.

As discussed in Section 2.2, most direct method circuit simulators use a common time step for the complete circuit. This results in computation to solve for each variable at every time point. The time step at a time point is computed by calculating a minimum of recommended time steps for all variables. Therefore the fastest changing variable in the system determines the time step. As a result, several extra points are calculated for slowly changing variables than necessary to represent the variable accurately. This effect is particularly significant for variables that are not changing

appreciably over some interval of time. Waveform latency refers to the situation where a variable is not changing appreciably over some interval of time and its solution can be obtained from the explicit equation:

$$x_{n+1} = x_n .$$

That is, the value  $x_{n+1}$  is not computed using a numerical integration formula but instead is updated using the value at the previous time point. Latency is a well-known property of large digital circuits. Figure 2.5a shows a node voltage waveform with three latent regions, L1, L2 and L3, where node voltages are updated using their previous values. Multirate behavior refers to signal values changing at different rates, relative to one another, over the same interval of time. MOS digital circuits show multirate behavior because of different transistor sizes and capacitance values. Figure 2.5b shows voltage waveforms of two nodes of a sub-circuit which are changing at different rates where large time steps are used to obtain the slowly changing, first, waveform and smaller time steps are taken to obtain the rapidly changing, second, waveform. This is an example of the multirate behavior. An effective exploitation of latency and multirate behavior can result in significant reduction in simulation time.

As shown in Figure 2.6, relaxation based techniques can be used at various stages of the solution process. Depending upon the stage at which the relaxation process is applied, the techniques are classified as *Linear*, *Nonlinear* or *Waveform*. The most commonly used numerical analysis techniques for the purpose are Gauss-Seidel and Gauss-Jacobi.

#### 2.3.1 Linear Relaxation

Linear relaxation techniques use iterative methods for the solution of system of linear equations. Referring to the flow chart of a direct method simulator shown in Figure 2.4, either Gauss-Seidel or Gauss-Jacobi methods can be used instead of LU decomposition or Gaussian elimation in steps (7) and (8). GS and GJ algorithms used for the solution of equation Ax = b, are given below. The constant  $\varepsilon$  indicates the error tolerance and k is the iteration count.

Figure 2.5: Waveform properties [a] Latency [b] Multi-rate behavior [8].

Figure 2.6: Relaxation-based techniques [9].

### Gauss-Jacobi Algorithm to Solve Ax = b

$$k \leftarrow 0$$

estimate  $x^0$ ;

$$\mathbf{repeat} \{$$

$$k \leftarrow k+1;$$

$$forall (i \in \{1, \dots, n\})$$

$$x_i^k = \frac{1}{a_{ii}} \left[ b_i - \sum_{j=1}^{i-1} a_{ij} x_j^{k-1} - \sum_{j=i+1}^{n} a_{ij} x_j^{k-1} \right]$$

$$\mathbf{until} (|x_i^k - x_i^{k-1}| \le \varepsilon, (i = 1, \dots, n));$$

### Gauss-Seidel Algorithm to solve Ax = b

$$k \leftarrow 0$$

estimate  $x^0$ ;

$$\mathbf{repeat} \{$$

$$k \leftarrow k+1;$$

$$foreach (i \in \{1, \dots, n\})$$

$$x_i^k = \frac{1}{a_{ii}} \left[ b_i - \sum_{j=1}^{i-1} a_{ij} x_j^k - \sum_{j=i+1}^n a_{ij} x_j^{k-1} \right]$$

$$\mathbf{until} (|x_i^k - x_i^{k-1}| \le \varepsilon, (i = 1, \dots, n));$$

It is important to note that in the GJ method, each iteration  $x_i^k$  is calculated by using values from the previous iteration,  $x_j^{k-1}$ . Therefore equations can be solved in any order or can be scheduled in parallel on multiple processors. In the GS method, the most recent (i.e. latest k) iteration values are used for calculating the current iteration. Therefore the order of processing equations is important. This is indicated by the use of the *foreach* construct.

In order to study convergence properties of the GS and GJ methods, A in the equation Ax = b can be expressed as A = L+D+U, where  $L \in \mathbb{R}^n$  is strictly

lower triangular,  $D \in \mathbb{R}^n$  is diagonal and  $U \in \mathbb{R}^n$  is strictly upper triangular. The application of GJ and GS methods results in the following equations:

Gauss-Jacobi:

$$x^{k+1} = -D^{-1}(L+U)x^k - D^{-1}b = M_{C}x^k + D^{-1}b.$$

(2.26)

Gauss-Seidel:

$$x^{k+1} = -(L+D)^{-1}Ux^{k} + (L+D)^{-1}b = M_{GS}x^{k} + (L+D)^{-1}b$$

(2.27)

A necessary and sufficient condition for iterations defined by Equations 2.26 and 2.27 to converge to the solution of equation Ax = b, independent of any starting vector  $x^0$ , is that the eigenvalues of  $M_{GS}$  and  $M_{GJ}$  be inside the unit circle in the complex plane [34]. If these conditions are satisfied then GS and GJ methods converge at least linearly. That is, the error at each iteration decreases according

$$\left\|x^{k+1} - \hat{x}\right\| \leq \varepsilon \left\|x^k - \hat{x}\right\| \tag{2.28}$$

where  $\hat{x}$  is the solution of the equation Ax = b.

The two relaxation based methods can be compared with the standard approach. The direct methods are certainly more reliable, however, their computational cost is  $N^{11-15}$ , compared with O(N) for the relaxation based methods [3]. Thus relaxation methods are advantageous from a computational point of view, if the number of iterations required to converge is of the order of  $N^{01}$ .

It is also possible to compare the Gauss-Seidel approach with the Gauss-Jacobi approach. Gauss-Seidel can be shown to converge faster than Gauss-Jacobi in most cases. For example, if A is lower triangular, Gauss-Seidel can converge to the solution of the system of equations in one iteration while Gauss-Jacobi converges in N iterations. However, in the Gauss-Jacobi approach, computations for all the equations can proceed in parallel,

therefore this technique is appropriate for parallel systems having a large number of processors.

### 2.3.2 Nonlinear Relaxation Methods

As mentioned in the earlier section, the first step in solving a system of differential equations obtained from the circuit description is to convert it to a system of nonlinear algebraic equations using integration formulas (refer Equation 2.4). The system of nonlinear equations thus formed can be solved using relaxation techniques without linearising them. This technique is known as nonlinear relaxation.

Consider a system of nonlinear equations F(x)=0,  $F:R^n\to R^n$  with components  $(f_1,f_2,\cdots,f_n)$  and  $f_i:R^n\to R$ . Gauss-Seidel and Gauss-Jacobi algorithms for solution of F(x)=0 are given below. The index k is the iteration count and  $\varepsilon_1,\varepsilon_2$  are error tolerances

### Nonlinear Gauss-Seidel Algorithm:

```

k \leftarrow 0; assume x^0 repeat( k \leftarrow k+1; for each ( i \in \{1, \cdots, n\} ) solve \ f_i(x_1^k, \cdots, x_{i-1}^k, x_i^k, x_{i+1}^{k-1}, \cdots, x_n^{k-1}) = 0 \ \ for \ x_i^k; } until(|x_i^k - x_i^{k-1}| \le \varepsilon_1, |f_i(x^{k,i})| \le \varepsilon_2, \quad i = 1, \cdots, n)

```

The foreach construct specifies that the computations for each value of i must proceed sequentially and in the specified order. As mentioned earlier, convergence of this method depends on the order of processing equations. The order can be determined statically or dynamically.

### Nonlinear Gauss-Jacobi Algorithm:

```

\begin{array}{l} k \leftarrow 0; \\ assume \, x^0 \\ \textbf{repeat} \, \{ \\ k \leftarrow k+1; \\ forall \, (\, i \in \{\, 1, \cdots, n \,\}\,) \\ solve \, f_i \, (\, x_1^{k-1}, \cdots, x_{i-1}^{k-1}, x_i^k, x_{i+1}^{k-1}, \cdots, x_n^{k-1}\,) = 0 \  \, for \, x_i^k; \\ \textbf{| until } \, (\, |x_i^k - x_i^{k-1}| \leq \varepsilon_1, |f_i \, (x_i^{k,i})| \leq \varepsilon_2, \quad i = 1, \cdots, n \,) \end{array}

```

The *forall* construct specifies that the computations for all values of i can proceed concurrently, i.e. in parallel and in any order.

The conditions under which these methods converge are similar to the linear case. Let F(x) denote the Jacobian of F at x and let  $\hat{x}$  be the solution vector, i.e.  $F(\hat{x}) = 0$ . Assume that F is continuously differentiable in the open neighborhood  $S_0$  of  $\hat{x}$ . The Jacobian F(x) can be expressed as  $L(\hat{x}) + D(\hat{x}) + U(\hat{x})$  where  $L(\hat{x})$ ,  $D(\hat{x})$ , and  $U(\hat{x})$  are lower triangular, diagonal and upper triangular parts respectively. Let  $M_{GJ}(\hat{x})$  and  $M_{GS}(\hat{x})$  be defined as:

$$M_{GJ}(\hat{x}) = -D(\hat{x})^{-1} (L(\hat{x}) + U(\hat{x})), \qquad (2.29)$$

$$M_{GS}(\hat{x}) = -(D(\hat{x}) + L(\hat{x}))^{-1}U(\hat{x}). \tag{2.30}$$

If  $D(\hat{x})$  is non-singular and the spectral radii  $\rho(M_{GS}(\hat{x})) < 1$ ,  $\rho(M_{GI}(\hat{x})) < 1$ , then there exists an open ball  $S \subset S_0$  such that nonlinear Gauss-Jacobi and Gauss-Seidel methods converge to the solution  $\hat{x}$  for any starting vector  $x^0 \in S$  [35]. It is important to note that unlike linear relaxation, convergence is guaranteed only if the initial guess (starting vector) is sufficiently close to a solution.

The nonlinear Gauss-Seidel and Gauss-Jacobi algorithms presented above assume that the equations can be solved exactly. However, since these are nonlinear equations, iterative methods must be used for obtaining their solution. Each equation, in one unknown, is usually solved using a single variable Newton-Raphson method. The resulting composite methods are known as Gauss-Seidel-Newton and Gauss-Jacobi-Newton. Ideally the inner Newton-Raphson loop should be iterated to convergence. However, it is found that a single iteration of the loop is usually adequate [35].

Nonlinear iteration methods can be compared with the direct Newton-Raphson method. It is observed that the convergence rate of direct Newton-Raphson methods is quadratic while it is only linear for relaxation based methods. However, each iteration of the direct Newton-Raphson method requires solution of a set of simultaneous equations while the relaxation method involves a set of decoupled equations. Thus, relaxation methods have better inherent parallelism. In addition, relaxation methods are ideally suited to exploit the latency of the circuit under analysis.

A comparison can be made of the use of relaxation methods at the linear and nonlinear equation level. The linear relaxation methods have an outer Newton-Raphson loop and an inner relaxation loop embedded in it, while nonlinear relaxation methods have an outer relaxation loop and an inner Newton-Raphson loop, operating independently on each equation, embedded in it. The use of relaxation at the linear equation level involves computation of the Jacobian of F, which is quite expensive. Nonlinear relaxation coupled with an inner Newton-Raphson only needs the partial derivative of  $f_i$ , with respect to  $x_i$ , resulting in a considerable saving of computer time per iteration.

The application of iterative methods at the linear and nonlinear equation level has been presented. It is also possible to use these techniques at the differential equation level. This method is known as Waveform Relaxation and is discussed in Section 2.5. The following section describes a circuit simulation approach based on nonlinear relaxation, known as Iterated Timing Analysis (ITA).

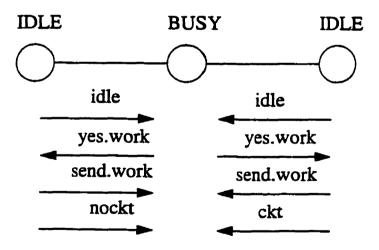

## 2.4 Iterated Timing Analysis