# Instrumentation of CdZnTe detectors for measuring prompt gamma-rays emitted during particle therapy

Dissertationsschrift

zur Erlangung des akademischen Grades Doktor der Medizintechnologie Doctor rerum medicinalium (Dr. rer. medic.) vorgelegt der Medizinischen Fakultät Carl Gustav Carus der Technischen Universität Dresden

von

Dipl.-Ing. Philipp Födisch

aus Wolfen

Dresden 2016

- 1. Gutachter: Prof. Dr. rer. nat. habil. Wolfgang Enghardt

- 2. Gutachter: Prof. Dr.-Ing. habil. Uwe Hampel

Tag der mündlichen Prüfung: 12. Mai 2017

gez.: PD Dr. rer. nat. habil. Steffen Löck Vorsitzender der Promotionskommission

## Contents

| 1. | Intro | Introduction 1                                                                                                                           |   |  |  |  |  |  |

|----|-------|------------------------------------------------------------------------------------------------------------------------------------------|---|--|--|--|--|--|

|    | 1.1.  | Aim of this work                                                                                                                         | 3 |  |  |  |  |  |

| 2. | Ana   | log front-end electronics                                                                                                                | 5 |  |  |  |  |  |

|    | 2.1.  | State-of-the-art                                                                                                                         | 5 |  |  |  |  |  |

|    | 2.2.  | Basic design considerations                                                                                                              | 6 |  |  |  |  |  |

|    |       | 2.2.1. CZT detector assembly                                                                                                             | 6 |  |  |  |  |  |

|    |       | 2.2.2. Electrical characteristics of a CZT pixel detector                                                                                | 7 |  |  |  |  |  |

|    |       | 2.2.3. High voltage biasing and grounding                                                                                                | 9 |  |  |  |  |  |

|    |       | 2.2.4. Signal formation in CZT detectors                                                                                                 | 0 |  |  |  |  |  |

|    |       | 2.2.5. Readout concepts                                                                                                                  | 2 |  |  |  |  |  |

|    |       | 2.2.6. Operational amplifier                                                                                                             | 6 |  |  |  |  |  |

|    | 2.3.  | Circuit design of a charge-sensitive amplifier                                                                                           | 8 |  |  |  |  |  |

|    |       | 2.3.1. Circuit analysis                                                                                                                  | 9 |  |  |  |  |  |

|    |       | 2.3.2. Charge-to-voltage transfer function                                                                                               | 2 |  |  |  |  |  |

|    |       | 2.3.3. Input coupling of the CSA                                                                                                         | 5 |  |  |  |  |  |

|    |       | 2.3.4. Noise                                                                                                                             | 6 |  |  |  |  |  |

|    | 2.4.  | Implementation and Test                                                                                                                  | 8 |  |  |  |  |  |

|    |       | Results                                                                                                                                  | 0 |  |  |  |  |  |

|    |       | 2.5.1. Test pulse input                                                                                                                  | 1 |  |  |  |  |  |

|    |       | 2.5.2. Pixel detector                                                                                                                    | 2 |  |  |  |  |  |

|    | 2.6.  | Conclusion                                                                                                                               |   |  |  |  |  |  |

| 3. | Diai  | tal signal processing 3                                                                                                                  | 7 |  |  |  |  |  |

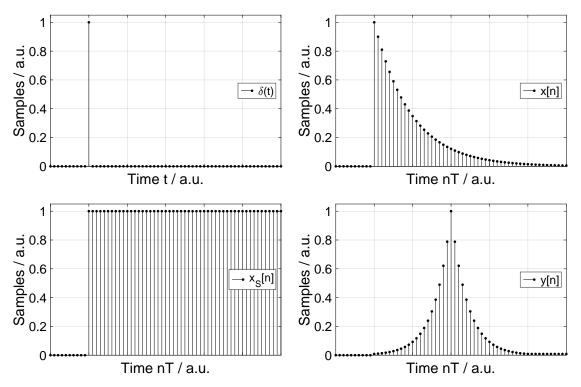

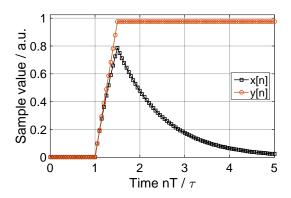

| -  | -     | Unfolding-synthesis technique                                                                                                            |   |  |  |  |  |  |

|    |       | Digital deconvolution                                                                                                                    | 9 |  |  |  |  |  |

|    |       | 3.2.1. Prior work                                                                                                                        | 9 |  |  |  |  |  |

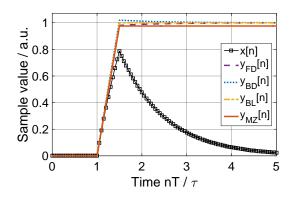

|    |       | 3.2.2. Discrete-time inverse amplifier transfer function                                                                                 |   |  |  |  |  |  |

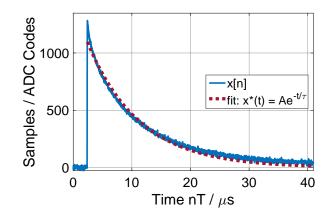

|    |       | 3.2.3. Application to measured signals                                                                                                   |   |  |  |  |  |  |

|    |       | 3.2.4. Implementation of a higher order IIR filter                                                                                       |   |  |  |  |  |  |

|    |       | 3.2.5. Conclusion                                                                                                                        | - |  |  |  |  |  |

|    | 33    | Digital pulse synthesis                                                                                                                  |   |  |  |  |  |  |

|    | 0.0.  | 3.3.1. Prior work                                                                                                                        |   |  |  |  |  |  |

|    |       |                                                                                                                                          |   |  |  |  |  |  |

|    |       |                                                                                                                                          |   |  |  |  |  |  |

|    |       | 3.3.1. Prior work       5         3.3.2. FIR filter structures for FPGAs       5         3.3.3. Optimized fixed-point arithmetic       5 | 1 |  |  |  |  |  |

|                                               |                               | 3.3.4.           | Conclusion                                    | 60  |  |  |  |  |

|-----------------------------------------------|-------------------------------|------------------|-----------------------------------------------|-----|--|--|--|--|

| 4.                                            | Data interface 61             |                  |                                               |     |  |  |  |  |

|                                               | 4.1.                          | State-o          | of-the-art                                    | 61  |  |  |  |  |

| 4.2. Embedded Gigabit Ethernet protocol stack |                               |                  |                                               | 62  |  |  |  |  |

|                                               | 4.3. Implementation           |                  |                                               |     |  |  |  |  |

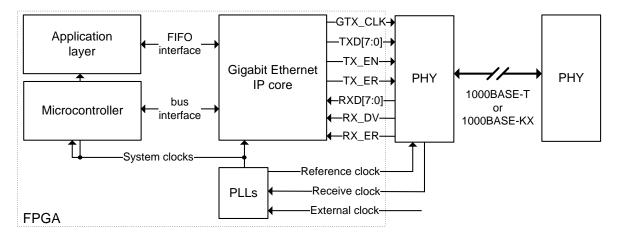

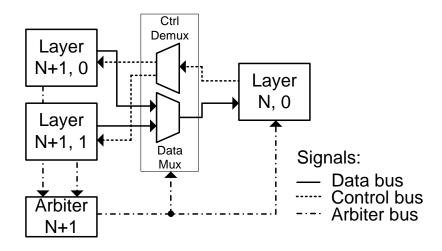

|                                               |                               | 4.3.1.           | System overview                               | 65  |  |  |  |  |

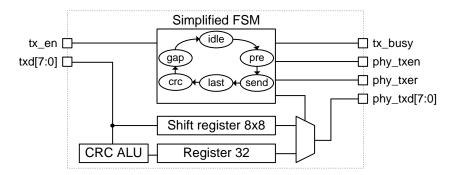

|                                               |                               | 4.3.2.           | Media Access Control                          | 65  |  |  |  |  |

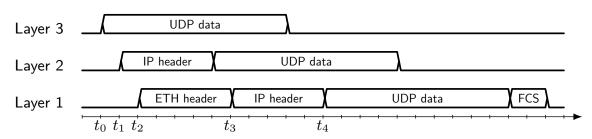

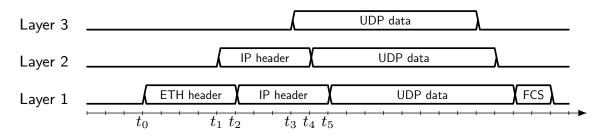

|                                               |                               | 4.3.3.           | Embedded protocol stack                       | 66  |  |  |  |  |

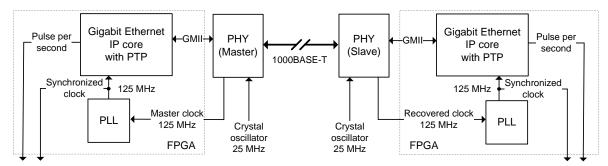

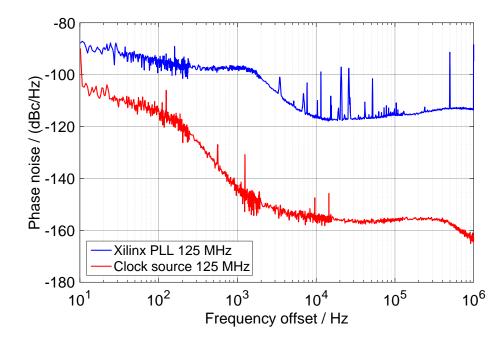

|                                               |                               | 4.3.4.           | Clock synchronization                         | 68  |  |  |  |  |

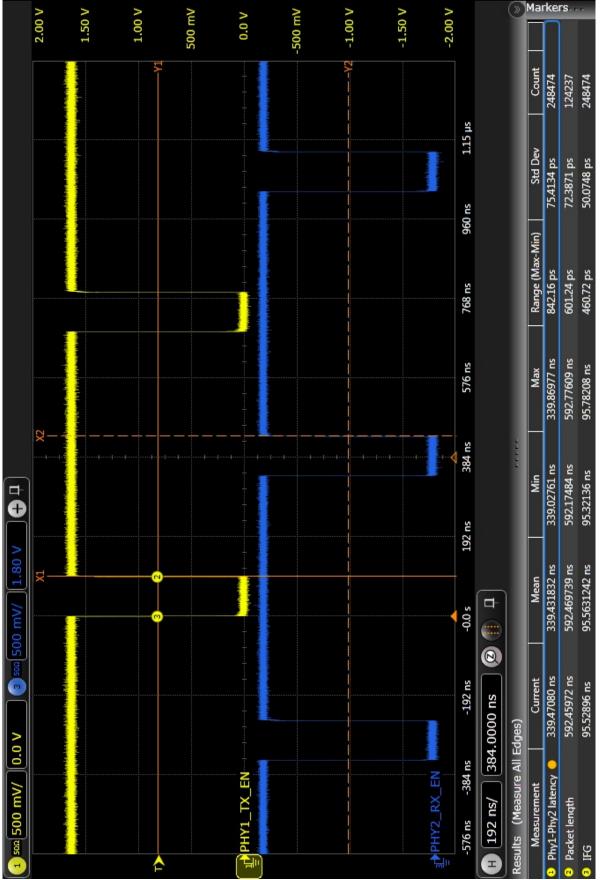

|                                               | 4.4.                          | Measu            | rements and results                           | 69  |  |  |  |  |

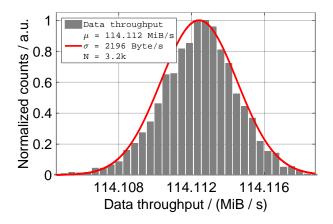

|                                               |                               | 4.4.1.           | Throughput performance                        | 70  |  |  |  |  |

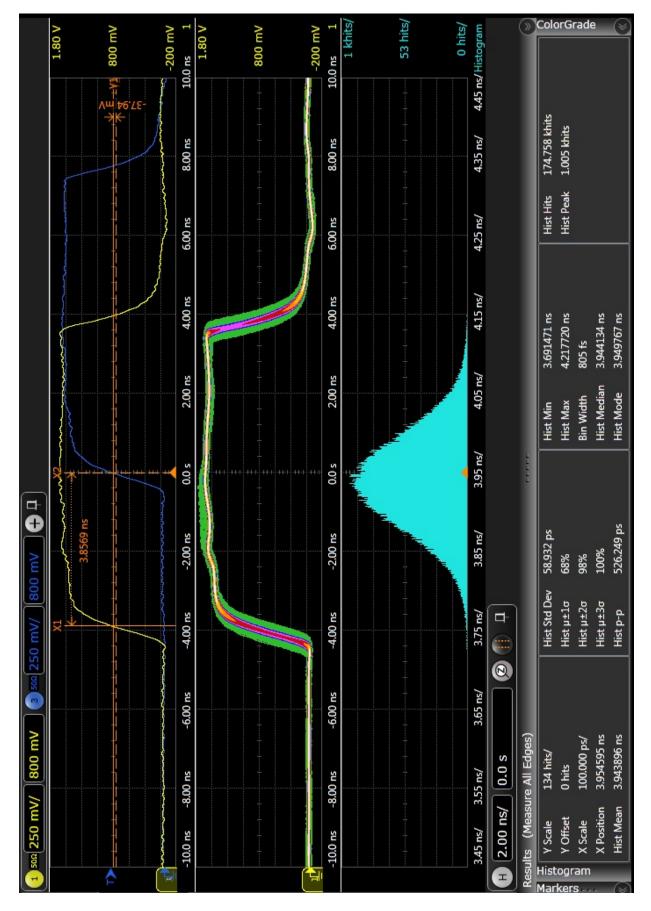

|                                               |                               | 4.4.2.           | Synchronization                               | 72  |  |  |  |  |

|                                               |                               | 4.4.3.           | Resource utilization                          | 74  |  |  |  |  |

|                                               | 4.5.                          | Conclu           | sion                                          | 75  |  |  |  |  |

| 5.                                            | 5. Experimental results       |                  |                                               |     |  |  |  |  |

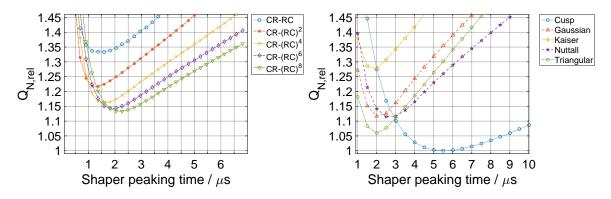

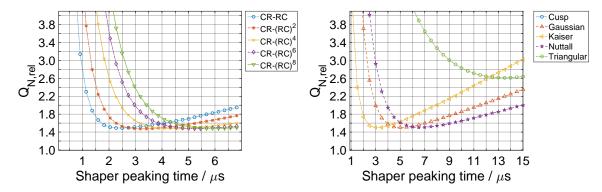

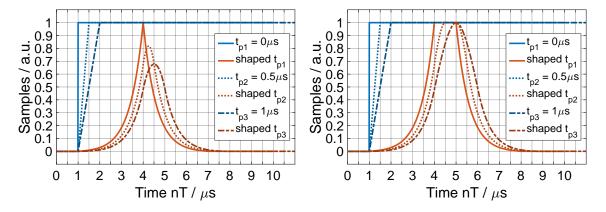

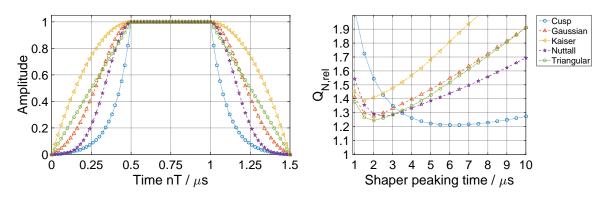

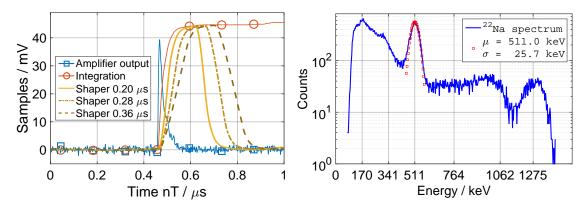

|                                               | 5.1.                          | Digital          | pulse shapers                                 | 77  |  |  |  |  |

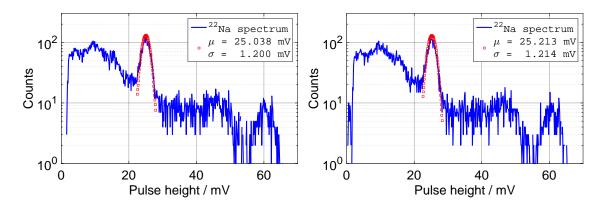

|                                               |                               | 5.1.1.           | Spectroscopy application                      | 78  |  |  |  |  |

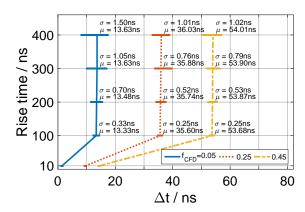

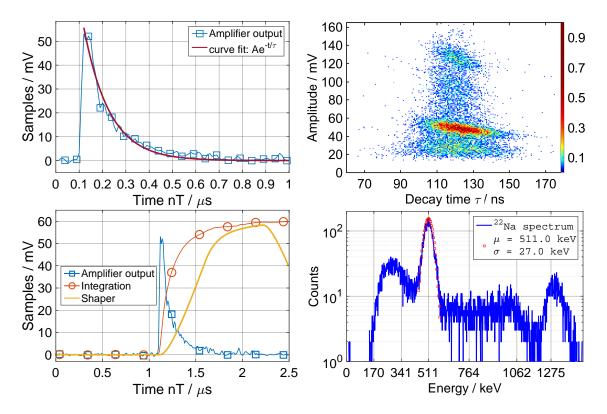

|                                               |                               | 5.1.2.           | Timing applications                           | 82  |  |  |  |  |

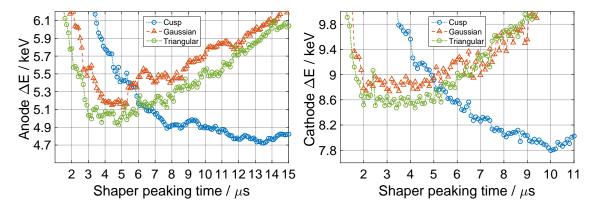

|                                               | 5.2.                          | $\gamma$ -ray s  | pectroscopy                                   | 85  |  |  |  |  |

|                                               |                               | 5.2.1.           | Energy resolution of scintillation detectors  | 85  |  |  |  |  |

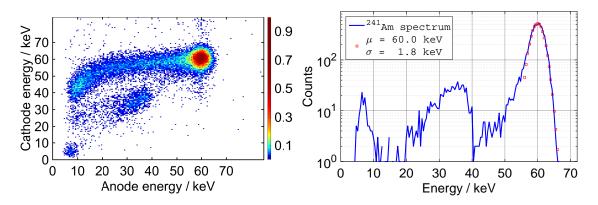

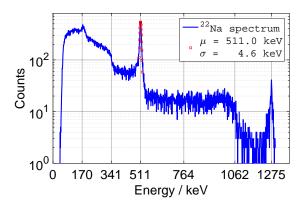

|                                               |                               | 5.2.2.           | Energy resolution of a CZT pixel detector     | 90  |  |  |  |  |

|                                               | 5.3.                          | $\gamma$ -ray ti | ming                                          | 93  |  |  |  |  |

|                                               |                               | 5.3.1.           | Timing performance of scintillation detectors | 93  |  |  |  |  |

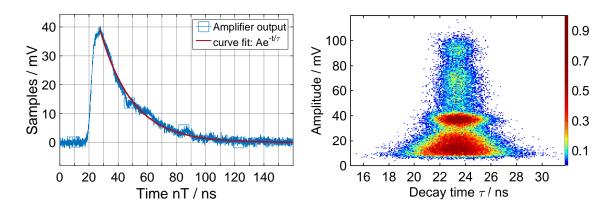

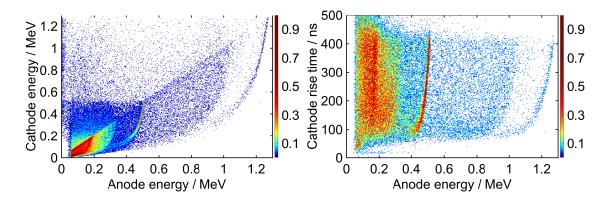

|                                               |                               | 5.3.2.           | Timing performance of CZT pixel detectors     | 95  |  |  |  |  |

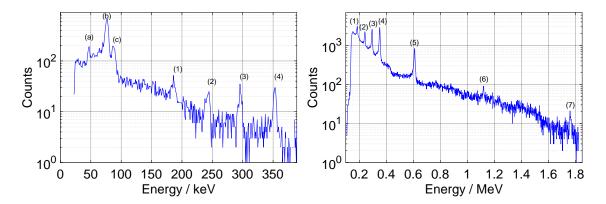

|                                               | 5.4.                          | Measu            | rements with a particle beam                  | 99  |  |  |  |  |

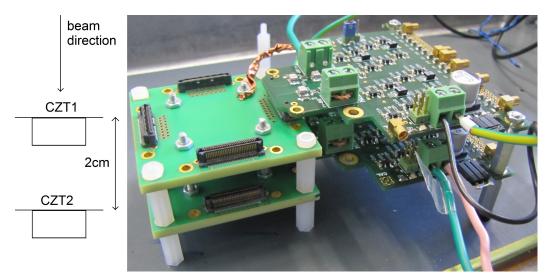

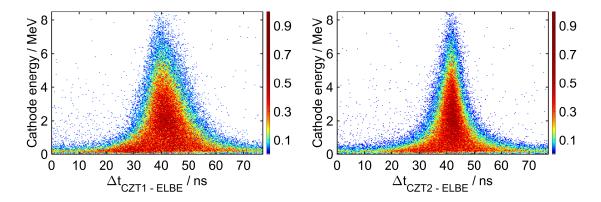

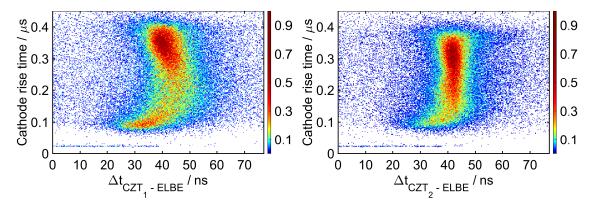

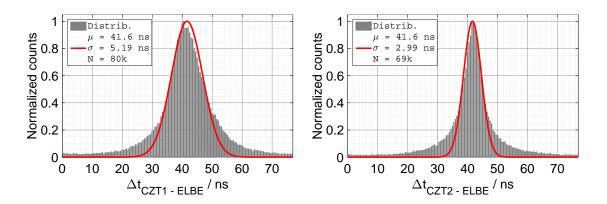

|                                               |                               | 5.4.1.           | Bremsstrahlung Facility at ELBE               | 99  |  |  |  |  |

| 6.                                            | Disc                          | ussion           |                                               | 103 |  |  |  |  |

| 7.                                            | Sum                           | mary             |                                               | 105 |  |  |  |  |

| 8                                             | 7.15                          | ammen            | fassung                                       | 107 |  |  |  |  |

|                                               |                               |                  |                                               |     |  |  |  |  |

| Ap                                            | Appendices 10                 |                  |                                               |     |  |  |  |  |

| Α.                                            | A. Waveform diagrams 109      |                  |                                               |     |  |  |  |  |

| В.                                            | B. Rear Transition Module 115 |                  |                                               |     |  |  |  |  |

# List of acronyms and abbreviations

| 3D   | Three-dimensional                                                                     |

|------|---------------------------------------------------------------------------------------|

| ADC  | Analog-to-digital converter                                                           |

| ALM  | Adaptive Logic Module                                                                 |

| ALU  | Arithmetic logic unit                                                                 |

| AMC  | Advanced mezzanine card                                                               |

| ARP  | Address Resolution Protocol                                                           |

| ASIC | Application-specific integrated circuit                                               |

| BGO  | $Bi_4Ge_3O_{12}$ , bismuth germanate                                                  |

| CAR  | Cathode-over-anode ratio                                                              |

| CFD  | Constant fraction discriminator                                                       |

| COTS | Commercial off-the-shelf                                                              |

| CSA  | Charge-sensitive amplifier                                                            |

| CZT  | CdZnTe, Cadmium zinc telluride                                                        |

| DAQ  | Data acquisition                                                                      |

| DESY | Deutsches Elektronen-Synchrotron                                                      |

| DOI  | Depth of interaction                                                                  |

| DSP  | Digital signal processor, Digital signal processing                                   |

| ELBE | Elektronen Linearbeschleuniger für Strahlen hoher Brillianz und niedriger<br>Emittanz |

| ENC  | Equivalent noise charge                                                               |

| FCS  | Frame check sequence                                                                  |

| FIFO | First-In-First-Out                                                                    |

| FIR  | Finite impulse response                                                               |

| FMC  | FPGA Mezzanine Card                                                                   |

| FPGA | Field-programmable gate array                                                         |

| FR-4 | Flame Retardant 4                                                                     |

| FSM  | Finite state machine                                                                  |

| FWHM | Full width at half maximum                                                            |

| GAGG | $Gd_3Al_2Ga_3O_{12}$ :Ce, cerium-doped gadolinium aluminum gallium garnet             |

| GBP      | Gain-bandwidth product                          |

|----------|-------------------------------------------------|

| GMII     | Gigabit Media Independent Interface             |

| GSPS     | Gigasamples per second                          |

| HZDR     | Helmholtz-Zentrum Dresden-Rossendorf            |

| ICMP     | Internet Control Message Protocol               |

| IC       | Integrated circuit                              |

| IFG      | Interframe gap                                  |

| IIR      | Infinite impulse response                       |

| IP       | Intellectual property                           |

| IP       | Internet Protocol                               |

| LTI      | Linear time-invariant                           |

| LUT      | Look-up table                                   |

| MAC      | Media Access Control                            |

| MCH      | MicroTCA Carrier Hub                            |

| MDIO     | Management Data Input/Output                    |

| MicroTCA | Micro Telecommunications Computing Architecture |

| MSPS     | Megasamples per second                          |

| MWD      | Moving Window Deconvolution                     |

| Nal      | Sodium iodide                                   |

| OSI      | Open Systems Interconnections                   |

| PCB      | Printed circuit board                           |

| PC       | Personal computer                               |

| PGI      | Prompt gamma imaging                            |

| PGT      | Prompt gamma timing                             |

| PHY      | Physical layer transceiver                      |

| PLL      | Phase-locked loop                               |

| PPS      | Pulse per second                                |

| PTP      | Precision Time Protocol                         |

| RGMII    | Reduced Gigabit Media Independent Interface     |

| RMS      | Root-mean-square                                |

| RTL      | Register-transfer level                         |

| RTM      | Rear Transition Module                          |

| RTT      | Round-trip time                                 |

| SFD      | Start frame delimiter                           |

| SGMII    | Serial Gigabit Media Independent Interface      |

|          |                                                 |

- SNR ..... signal-to-noise ratio

- SoC ..... System on a chip

- TCA ..... Telecommunications Computing Architecture

- TIA ..... Transimpedance amplifier

- UDP ..... User Datagram Protocol

- VHDL ..... Very High Speed Integrated Circuit Hardware Description Language

- VMEbus ...... Versa Module Europa bus

### 1. Introduction

Cancer is a deadly disease for humans. In Germany, the total number of cancer diseases increased from 338,300 in the year 1997 to 477,950 in 2012 (Batzler et al., 1999; Kaatsch et al., 2015). The quoted study claims that at the same time the associated cancer deaths remain constant slightly above 210,000 people. Regardless of how the statistics are interpreted, the decreasing cancer mortality rate is based on advances in medical science.

The successes in treating cancer are driven by a continuous improvement of medical technology. Nowadays, surgery is assisted by computers, chemotherapy benefits from computed tomography imaging, and radiation therapy involves cutting-edge technologies for particle accelerators and detector systems. An effective cure is achieved by combining the available techniques. With respect to the mentioned methodologies, radiotherapy is one of the main cancer treatments (Krause and Supiot, 2015). Therefore, a beam of high energy is generated by a particle accelerator, and is used to destroy the cancer cells in the patient's body. This can generally be a photon beam (X-rays), which is currently the standard type of radiation used for treatment, or even a particle beam (proton or ion beam). Particle beams have the same biological effect on tumor cells as photon beams, but they are aligned to stop at a determined position in the tumor, and healthy tissue behind the target is less irradiated. Thus the largest dose is deposited in the tumor, while healthy tissue is spared.

For now, there are 60 proton therapy facilities in operation around the world, where 6 are located in Germany (PTCOG, 2016). With regard to facilities under construction or in a planning stage, the total number will increase rapidly in the next years. In proton therapy, a major task is the development of a treatment plan delivering most of the dose to the tumor cells by adjusting beam parameters. An a posteriori verification of the applied dose is still challenging, as the protons are stopped inside the tissue, and transport no direct information about that location out of the patient. Consequently, information caused by interactions of protons with the target must be considered for a measurement to make progress in range verification. Monitoring the proton beam finally enables the exploitation of whole precision for proton therapy.

A promising approach for an indirect measurement of the finite range of a proton beam is based on the detection of emitted  $\gamma$ -rays. These  $\gamma$ -rays are promptly emitted as a result of nuclear reactions of protons with tissue. Thus the emission of prompt  $\gamma$ -rays correlates with the range of the proton beam and therefore with the deposited dose in the tumor (Fiedler et al., 2011). The emission spectrum is dominated by interactions of <sup>12</sup>C and <sup>16</sup>O, which is observable at 4.4 MeV and 6.1 MeV (Rohling, 2015). In order to locate the range or at

least a range shift, several methods have been proposed and are currently evaluated for clinical use. Throughout that task, a pinhole camera (Kim et al., 2009), or a knife-edge slit camera (Smeets, 2012; Richter et al., 2016) for prompt gamma imaging (PGI) have been investigated. For systems with passive collimation, "the difficulty is obviously to find a tradeoff between good spatial resolution and high detection efficiency" (Smeets, 2012). Moreover, it has been demonstrated that a time-of-flight measurement is feasible for detecting range shifts (Golnik, 2016). The prompt gamma timing (PGT) method requires "a stabilized photon detection (in terms of energy and timing) at high throughput rates" (Golnik, 2016). A further technique was proposed, which correlates the measured prompt  $\gamma$ -ray spectrum to nuclear reaction cross sections (Verburg and Seco, 2014). The data acquisition (DAQ) required a digitizer running at about 1 GSPS synchronous to the particle accelerator. At last, the most complex system for PGI is a Compton camera (Richard et al., 2009; Peterson et al., 2010; Roellinghoff et al., 2011; Kormoll et al., 2011b; Hueso-González et al., 2014; McCleskey et al., 2015; Polf et al., 2015; Taya et al., 2016). "A slight scepticism has settled down in the scientific community concerning Compton cameras for PGI. Due to the technical complexity and high radiation background, only few experimental results hint at their applicability in a clinical environment." (Hueso-González, 2016).

All quoted studies about methodology lead to the conclusion that range verification in proton therapy requires new developments in electronics. In general, a successful translation into practical clinical use-cases is possible, if nuclear instruments rise to the challenges of:

- Energy range: Prompt γ-rays are emitted at energies up to ≈ 7 MeV (Schumann et al., 2015). In case of PGI with a Compton camera, scattered events with energies below 100 keV must be also detectable by the electronics for improved event statistics (Rohling, 2015). Thus the measurement dynamic range must be extraordinarily high.

- γ-ray flux: Depending on the material and the volume of the detector, the estimated detector load is in the few-Mcps range (Pausch et al., 2016). For CdZnTe (CZT) detectors, which have been proposed for use in a Compton camera (Kormoll, 2013), the load is rather reduced. As clinical benchmarks are still ongoing work, instruments must be designed for highest possible performance in terms of dead time and achievable event throughput.

- Energy resolution: For all methods, discrimination of prompt γ-rays according to empirically defined ranges is convenient. Moreover, in case of a Compton camera, the precision of reconstructed scattering angles depends on energy resolution (Rohling, 2015). The energy resolution of the readout electronics must exceed the intrinsic resolution of the detector material. Hence, the electronic noise and processing system should not limit the overall spectroscopy performance.

- Time resolution: Regardless of the method, a timing of incident γ-rays relative to the accelerator frequency or another detector in coincidence enables filtering of usable events. In case of a time-of-flight measurement, requirements for timing are intensified to the range of picoseconds (Golnik, 2016). A precise timing demands a low-jitter clock

distribution and high bandwidth for fast signal rise times.

Spatial resolution: For PGI, i.e. pinhole-camera, knife-edge slit camera, or Compton camera, a high segmentation of the detector enhances the precision of obtained images. But an increased spatial resolution demands an increased number of readout channels for the DAQ system, which concurrently multiplies complexity and amount of data (Kormoll, 2013).

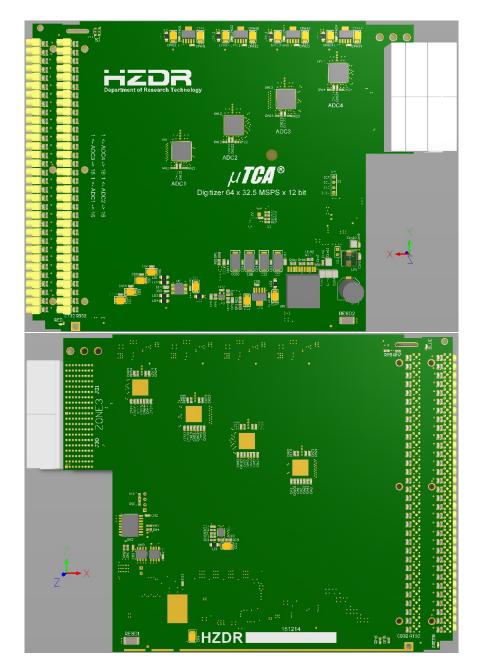

A detector system serving all the emphasized features is necessary for an implementation of a Compton camera, but is not available. In general, before designing electronic systems, a decision between proprietary or standardized components has to be made. Proprietary systems tend to be compact and optimally adapted to a single task. On top of that design approach are application-specific integrated circuits (ASICs). For use in experimental systems, they are expensive, less versatile, and hard to access. On the contrary, standardized components benefit from their versatility due to their modular architecture at the cost of additional overhead. For nuclear physics, the Versa Module Europa bus (VMEbus) standard is widely used for instrumentation of control and experimental systems. Recent experimental results for range verification were based on electronics built with VMEbus systems (Kormoll, 2013; Hueso-González, 2016; Golnik, 2016). Moreover, an emerging trend for MicroTCA systems in the physics community is noticeable. In conjunction with field-programmable gate arrays (FPGAs), that platform seems to fit the generalized requirements of a prototype detector system for range verification, i.e. high data throughput, high signal bandwidth, and high input channel count with precise clock synchronization and distribution.

#### 1.1. Aim of this work

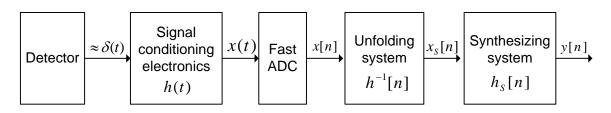

Starting from the development of a prototype system of a Compton camera for range verification in proton therapy (Kormoll, 2013), the integration of an ASIC-based system (Födisch et al., 2013) to that camera failed due to the limited energy range, time resolution, and throughput of the customized readout electronics. The only available ASIC for the readout of a CZT pixel detector could not withstand the requirements of a clinical scenario. With this experience and knowledge about present limitations, the development and investigation of a new prototype with commercial off-the-shelf (COTS) components was reinitialized. Electronics were replaced by highly integrated components, and analog signal processing was discarded for the purposes of digital pulse shape analysis and processing. Despite digitization, new developments in analog front-end electronics were necessary to acquire signals from a CZT pixel detector (Födisch et al., 2016a). Moreover, new algorithms for improving digital pulse processing with an FPGA have been developed (Födisch et al., 2016c) and efficiently implemented (Födisch et al., 2016d). To cope with the challenges of high data throughput and synchronization in distributed systems, an Ethernet-based interface optimized for timing applications was implemented (Födisch et al., 2016b). Finally, CZT pixel detectors were characterized for their potential use in a Compton camera application.

### 2. Analog front-end electronics

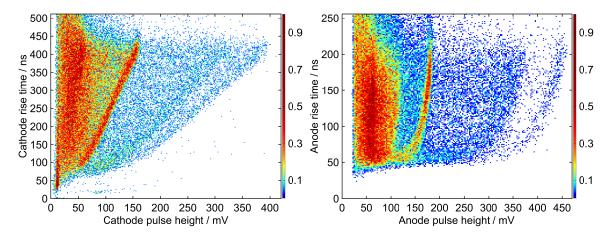

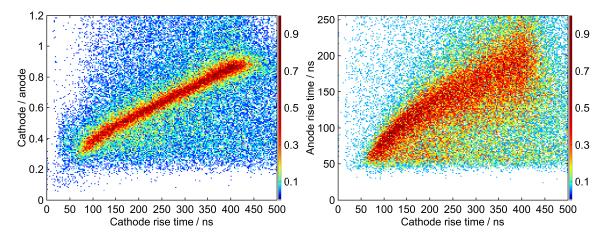

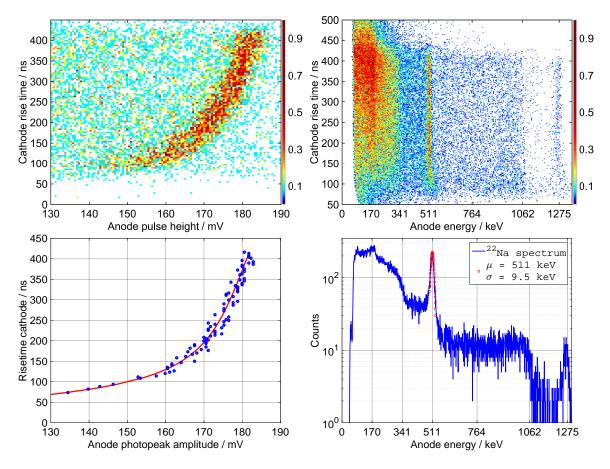

Cadmium zinc telluride (CdZnTe, CZT) radiation detectors are suitable for a variety of applications, due to their high spatial and energy resolution at room temperature. However, state-of-the-art detector systems require high-performance readout electronics. Though an ASIC is an adequate solution for the readout, requirements of high dynamic range and high throughput are not available in any commercial circuit. Consequently, this chapter describes the development of analog front-end electronics with operational amplifiers for an 8×8 pixe-lated CZT detector. For this purpose, we modeled an electrical equivalent circuit of the CZT detector with the associated charge-sensitive amplifier (CSA). Based on a detailed network analysis, the circuit design is completed by numerical values for various features such as ballistic deficit, charge-to-voltage gain, rise time, and noise level. A verification of the performance is carried out by synthetic detector signals and a pixel detector. The experimental results with the pixel detector assembly and a <sup>22</sup>Na radioactive source emphasize the depth dependence of the measured energy. After fitting the weighting potential, a correction of the energy based on the derived depth of interaction (DOI) was feasible, thus improving the energy resolution.

#### 2.1. State-of-the-art

CdZnTe is a room-temperature semiconductor material for radiation detectors (Del Sordo et al., 2009). It is available in compact detector units with highly segmented pixel layouts and is ideally suited for high energy resolution  $\gamma$ -ray spectroscopy (Verger et al., 2005) and 3D imaging (Wahl et al., 2015). As has been previously reported, CZT detectors have been used in Compton camera systems (Kormoll et al., 2011a; Hueso-González et al., 2014; Lee et al., 2016). With regard to recent investigations, they have the potential to build an imaging system for proton therapy (McCleskey et al., 2015; Polf et al., 2015; Taya et al., 2016; Golnik et al., 2016). State-of-the-art readout systems for highly segmented CZT detectors are conventionally built with an ASIC (He et al., 1999; Gan et al., 2016). Available ASICs are optimized for  $\gamma$ -ray spectroscopy. Low energy range, usually up to 2 MeV (McCleskey et al., 2015; Gan et al., 2016; Födisch et al., 2013), limited count rate capability, and poor availability and product life cycle are unsolved challenges of an ASIC-based readout system for an imaging system in proton therapy. In this environment, high energies up to 7 MeV and count rates up to 1 Mcps have to be handled (Schumann et al., 2015; Hueso-González et al., 2015; Pausch et al., 2016). Instead of using an ASIC for the readout electronics, COTS operational amplifiers have been used for the front-end electronics (Ramachers and Stewart, 2007). Along with space-saving multi-channel analog-to-digital converters (ADCs) and an FPGA, all tasks related to the signal acquisition and processing can be done with a COTS system. A programmable digital system benefits from its versatility, which is needed for the evaluation of a detector system for new applications like proton therapy. Even for application in a fixed installation, a system made of COTS components provides the advantages of proven reliability and life-cycle support.

In general, front-end electronics are the key element of overall performance of a detector system. Our goal is to maximize the dynamic range of the front-end electronics since the CZT is exposed to high-energy  $\gamma$ -rays, but also has to detect low-energy scatter events used for Compton imaging. As this is the main objective, which cannot be solved with a state-of-the-art ASIC, the timing information of an interaction must be preserved by the readout system. Most ASICs merely include simple analog signal processing (e.g. leading-edge trigger for timing and peak-hold circuit for energy information) making pulse shape analysis or advanced timing algorithms difficult or even impossible. As the design of front-end electronics is a tradeoff between signal bandwidth, noise, complexity, size, and costs, the best solution must be driven by the application. For the prototype of a Compton camera, we investigate a space-saving and simple circuit design with minimal components. The system must include at least 65 analog readout channels, which are set up with COTS voltage feedback operational amplifiers.

#### 2.2. Basic design considerations

#### 2.2.1. CZT detector assembly

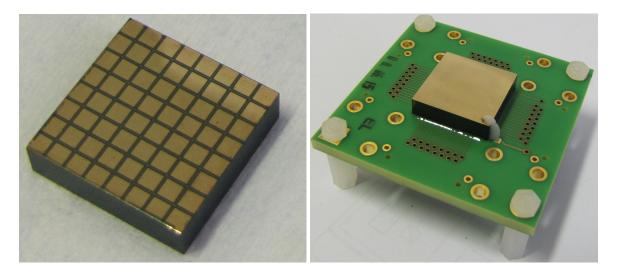

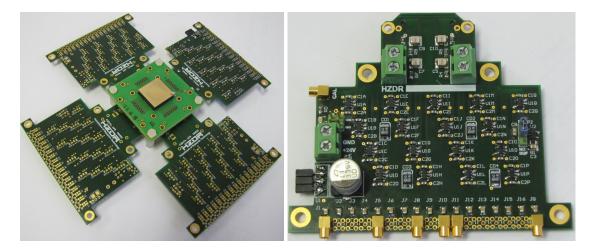

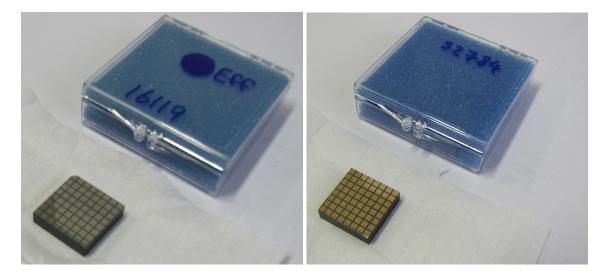

For a medical imaging application, we use a CZT detector as the scattering layer in a Compton camera. A reasonable choice for this task is a pixelated CZT radiation detector from Redlen Technologies (Redlen Technologies, 2011). The detector size is  $19.42 \times 19.42 \text{ mm}^2$ with a thickness of 5 mm. Towards the continuous planar electrode on the back side, there are 64 pixel electrodes aligned in an 8×8 array on the front side. The size of a pixel pad is 2.2×2.2 mm<sup>2</sup> for all pixels except the corner pixels with 1.98×1.98 mm<sup>2</sup>. In addition, a steering grid surrounds all pixels. The inter-pixel space is 0.26 mm. The bulk device and an assembled detector are shown in fig. 2.1. The detector is mounted on a printed circuit board (PCB) with the continuous planar electrode on top. A bond wire is attached to a copper pad on the carrier PCB. Furthermore, a conductive adhesive on each pixel pad ensures the electrical connection to the pixel array on the PCB. An underfill between the pixel array and the PCB supports the adhesive connection and improves mechanical stability. We also decided to use a 3.2 mm-thick FR-4 material for the PCB to enhance the robustness of the assembly. The electrodes of the detector are accessible via rugged high-speed connectors on the bottom side. To shield the detector against visible light, a 3D-printed cap is attached above the detector on the top of the carrier board. Our front-end electronics are designed to work with this type of detector assembly, and the readout boards are plugged into the side

Figure 2.1.: A 5 mm thick pixelated CZT detector from Redlen Technologies (Redlen Technologies, 2011) with 8×8 electrodes (each 2.2 mm×2.2 mm) on the front side (left) and a continuous planar electrode (19.42 mm×19.42 mm) on the back side (right). The detector is mounted on a 3.2 mm-thick carrier board with rugged connectors on the bottom side.

faces of the detector carrier board (see fig. 2.22). Therefore a stacked system with arbitrary depth, as required for the evaluation of a suitable Compton camera setup, can be easily constructed. Further investigations on ruggedization of CZT detectors and detector assemblies have been presented in (Lu et al., 2015).

#### 2.2.2. Electrical characteristics of a CZT pixel detector

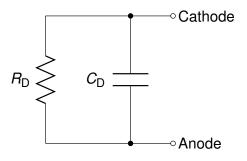

From the electrical point of view, a CZT detector can be modeled with the equivalent circuit shown in fig. 2.2. With an external operating voltage at the electrodes of the detector, the terminals are referred to as cathode and anode in accordance with the applied polarity. Usually, the continuous electrode is biased with a negative potential and the pixel electrodes are at ground potential. For an ideal detector material, this would force the negative charge carriers (electrons) to move towards the anode and the positive charge carriers (holes) to move towards the cathode. As a consequence of charge trapping due to structural defects, impurities, and irregularities of the material (Awadalla, 2015), the mobility and lifetime of the holes in CZT are very poor compared to the electrons (Spieler, 2005). Only the moving electrons induce a signal on the electrodes, while the portion of the signal due to the holes can be neglected. Thus, if the generated electrons move to the position-sensitive side of the detector, the overall detection performance is improved. As the readout electronics are directly connected to the electrodes, the electrical characteristics of the detector influence the dynamic behavior of the entire circuit. Finally, the network model for the readout electronics must include the electrical equivalent circuit of the detector. In general, a very simple equivalent circuit is adequate to model the properties of the detector. As summarized in fig. 2.2, it is a passive two-terminal component with a permittivity and a specific conductance. A capacitor represents the permittivity of the material and the electrical conductivity is modeled by a resistor. For the evaluated pixelated CZT detector, the capacitance can be roughly approximated by the model of the parallel-plate capacitor with an electrode area A separated by the distance d. Therefore the capacitance C is calculated by

$$C = \varepsilon_0 \varepsilon_r \frac{A}{d} , \qquad (2.1)$$

where  $\varepsilon_0$  is the vacuum permittivity and  $\varepsilon_r$  is the relative permittivity of CZT. For the detector in this study, the values are  $A = 377 \text{ mm}^2$ , d = 5 mm. In practical terms, the bias voltage does not influence the relative permittivity in the applicable voltage range up to -600 V. The capacitance of the detector is therefore largely independent of the bias voltage (Garson et al., 2007). The value of  $\varepsilon_r$  depends on the manufacturing process, but ranges from 10 to 11 (De Antonis et al., 1996; Spieler, 2005). Thus, the entire bulk capacitance is in the range from 6.6 pF to 7.4 pF. The capacitance of a single pixel can also be calculated by eq. 2.1, where the size of the pixel determines the value of *A* (Rossi et al., 2006). With the same assumption for  $\varepsilon_r$ , the pixel capacitance is in the range from 69 fF to 95 fF, including the smaller corner pixels. Besides the estimation of capacitance, the bulk resistivity of the detector is needed to model the electrical characteristics. We measured the leakage current of the assembled CZT detector from fig. 2.1 with a precision high-voltage source with current monitor (Iseg SHQ series) (iseg, 2014). This device reports a current of 10 nA $\pm$ 1 nA with a detector bias voltage of -500 V. For a homogenous material, the resistance is defined as:

$$R = \rho \frac{d}{A} \tag{2.2}$$

where  $\rho$  is the resistivity of the material. Our measurement corresponds to a resistor of 50 G $\Omega$  for the two-terminal equivalent circuit or a resistivity of 4.10<sup>11</sup>  $\Omega$ cm. This is in accordance with the values from the datasheet ( $\rho > 10^{11} \Omega$ cm) from Redlen (Redlen Technologies, 2011).

Figure 2.2.: An electrical equivalent circuit of a CZT detector. The bulk resistivity is modeled with the resistor  $R_D$ , which is typically of several tens of G $\Omega$ . The capacitor  $C_D$  represents the parallel-plate geometry of the electrodes. Its value can be estimated with eq. 2.1.

Finally, the electrical characteristics of a CZT crystal mainly depend on the manufacturing process. If they cannot be experimentally verified, the values for the components of the elec-

trical equivalent circuit can be estimated with the geometry of the detector and the constants from the literature by eqs. 2.1 and 2.2. The equivalent circuit shown in fig. 2.2 is the simplest electrical representation of the detector unit. It does not model a frequency dependency with a complex permittivity. Additionally, stray capacitances introduced by traces and the carrier board itself, cross-coupling between pixels, and any inductivities of the connectors are ignored. However, a well-designed PCB layout can minimize these effects.

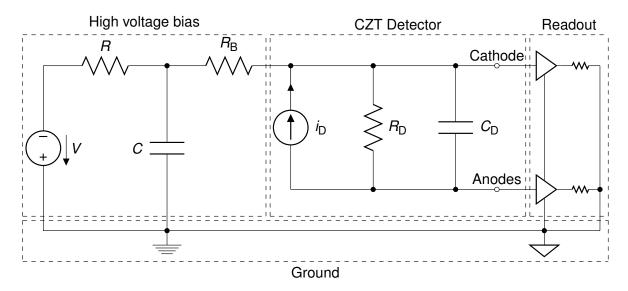

#### 2.2.3. High voltage biasing and grounding

A fundamental operating condition for a CZT detector is the presence of an electric field between the electrodes. Thus, the charge carriers generated by incident radiation move towards the electrodes, and an electric current is measurable. Typical electric field strengths for CZT detectors are in the range of 1 kV/cm (Redlen Technologies, 2011). As the continuous electrode of the detector is biased with a negative voltage, the ground potential is connected to the pixelated electrodes on the opposite side. In general, the high voltage with low ripple is generated by an external power supply connected to the detector via a cable or PCB traces. To reduce any pickup noise related to electromagnetic interference, we put a high-voltage filter close to the detector electrode. This is in the simplest case a passive first-order low-pass filter (*RC* network shown in fig. 2.3). The value of the resistor *R*<sub>B</sub> should

Figure 2.3.: Basic connection scheme of the CZT detector. A high voltage supply with an RC low-pass filter and a resistor  $R_B$  are used to generate the bias voltage for the cathode. The readout electronics are directly connected to the cathode and anodes of the detector. The anodes are biased by ground signal of the readout electronics, and consequently both ground potentials must be tied together.

be chosen to minimize the voltage drop across the high-voltage filter and maximize the voltage across the detector. The value of the filter capacitor C should be as high as possible to achieve the best noise filtering. According to eqs. 2.1 and 2.2, the capacitance is inversely proportional to the resistance. Therefore, the capacitor C must be chosen, such that the insulation resistance of the dielectric material is much higher than the resistance of the detector. Commercial capacitors of class 1 have an insulation resistance of more than 100 G $\Omega$ with a maximum capacitance of 10 nF. Thus, a passive first-order low-pass filter with a cutoff frequency below 1 Hz is possible (e.g.  $R = 47 \text{ M}\Omega$ , C = 10 nF). As a noise-filtered voltage is the output of the RC circuit, it cannot be directly connected to the electrode in order to bias the detector. One reason for this is that the filter capacitor C would be in parallel with the capacitance  $C_D$  of the detector. A bias resistor  $R_B$  of 47 M $\Omega$  separates the filter network from the detector. Another point that has to be taken into account is the path of current flow generated by the detector. The current should not flow into the high-voltage source. This can be ensured by choosing a high resistance for biasing the detector, so that the time constant  $R_{\rm B}C$  is much larger than the time constant of the readout electronics (Grupen and Shwartz, 2011). The active components of the readout electronics have their own power supply, which is separated from the high-voltage supply. Further, the anodes are biased with the ground potential of the readout electronics (signal ground in fig. 2.3). Both grounds have to be at the same potential and must be tied together. The electric field between the cathode and the anodes is therefore referenced to a known potential.

#### 2.2.4. Signal formation in CZT detectors

As implied, incident radiation hitting the detector generates free charge carriers. These electrons and holes move towards the electrodes because of the applied electric field. However, the generated charge is proportional to the incident  $\gamma$ -ray energy and the signal of the detector is an electric current. The induced current through an electrode is defined as

$$i = q \overrightarrow{v} \overrightarrow{E}_0 (\overrightarrow{x}), \qquad (2.3)$$

where *q* is the moving charge,  $\vec{v}$  is the instantaneous velocity of the charge *q* and  $\vec{E_0}(\vec{x})$  is the weighting field associated with the electrode at the position  $\vec{x}$  of the charge (He, 2001). The weighting potential  $\varphi_0(\vec{x})$  is defined as

$$\vec{E}_{0}(\vec{x}) = -\nabla \vec{\varphi}_{0}(\vec{x}), \qquad (2.4)$$

by setting one electrode to unit potential and all others to zero. For a parallel-plate geometry of a detector, where the widths in *x* and *y* dimensions of the electrodes are much larger than the thickness *z*, the electric field inside the detector is distributed homogeneously with a constant field strength. Therefore, the weighting field  $\vec{E_0}$  ( $\vec{x}$ ) is equal to the electric field, and, solving eq. 2.4 in the *z*-dimension, the normalized weighting potential  $\varphi_{0_c}(z)$  of the cathode is a linear function (He, 2001):

$$\varphi_{0_{\mathsf{C}}}(z) = z, 0 \le z \le 1.$$

(2.5)

The solution for the Poisson equation in two dimensions was given by (Rossi et al., 2006; Wermes, 2006). These authors presented an equation for the calculation of the weighting

potential for a detector with a segmented electrode layout. By setting one dimension of the pixel area to zero and normalizing the thickness *z* of the detector to 1, the weighting potential  $\varphi_{0_A}$  of a single pixel with the normalized width *a* can be calculated as

$$\varphi_{0_{\mathsf{A}}}(x,z) = \frac{1}{\pi} \arctan\left(\frac{\sin(\pi z)\sinh(\pi \frac{a}{2})}{\cosh(\pi x) - \cos(\pi z)\cosh(\pi \frac{a}{2})}\right), \tag{2.6}$$

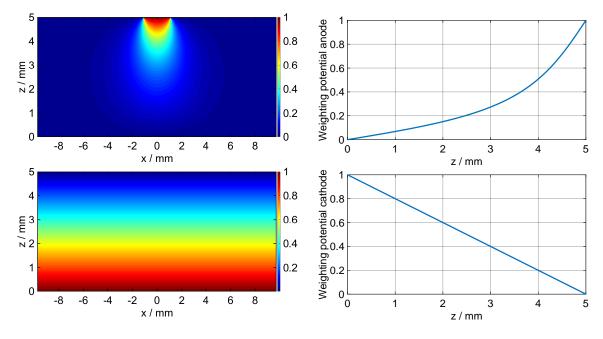

where x and z are the coordinates and  $0 \le z \le 1$ . The weighting potentials are shown in fig. 2.4. The weighting field  $E_0(z)$  under the collecting electrode (x = 0, y = 0) can be

Figure 2.4.: The weighting potentials of the cathode (bottom) and pixel anode (top) of the 5 mm-thick detector. The cathode is located at position z = 0 mm. The right plots show the weighting potential under the collecting electrode (x = y = 0 mm).

calculated by solving eq. 2.4 with eq. 2.6. This results in the following equation:

$$E_0(z) = \frac{\sinh(\pi \frac{a}{2})}{\cos(\pi z) - \cosh(\pi \frac{a}{2})}.$$

(2.7)

As we can estimate the weighting field of the detector with eq. 2.7, the next step is to calculate the expected electric current to simulate the transient behavior of the detector signals. With the assumption that the electric field E is constant and homogenous across the detector because all anodes are at the same potential, the electric field is calculated by

$$E = \frac{V}{d}, \qquad (2.8)$$

where V is the applied bias voltage and d is the thickness of the detector. Then, the velocity v of a moving charge q in the detector is calculated by

$$u = \mu_{e}E$$

, (2.9)

where  $\mu_e$  is the mobility of the charge carriers (electrons). A typical value of  $\mu_e$  for a CZT is about 1000 cm<sup>2</sup>/(Vs) (He et al., 1998; Cho et al., 2011). With the ionization energy  $\tilde{E}_i = 4.64 \text{ eV}$  for CZT (Spieler, 2005) and the energy  $\tilde{E}_{\gamma}$  of incident radiation, the generated moving charge *q* is defined as

$$q = e \frac{\tilde{E}_{\gamma}}{\tilde{E}_{i}}$$

(2.10)

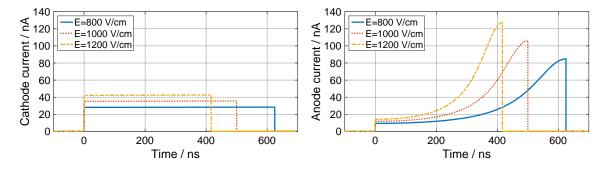

where *e* is the elementary charge. By inserting eqs. 2.7, 2.8, 2.9, 2.10 into eq. 2.3, the detector current can be numerically estimated. An example of incident radiation of  $\tilde{E}_{\gamma}$  = 511 keV is shown in fig. 2.5.

Figure 2.5.: Induced current *i* on the detector electrodes for incident  $\gamma$ -rays with an energy of 511 keV. The left plot shows the current induced on the cathode and the right plot shows the current induced on an anode pixel. The signals are calculated with eq. 2.3. An increased electric field strength *E* causes a higher current *i* with shorter drift times  $t_D$ . The generated charge remains constant.

Fig. 2.5 shows the currents flowing through the electrodes for an interaction at the cathode side of the detector. If the DOI is closer to the anode side, the total charge collection is incomplete, as the fraction of charge from the holes cannot be measured. This circumstance introduces a depth dependence and requires a correction for spectroscopic applications.

#### 2.2.5. Readout concepts

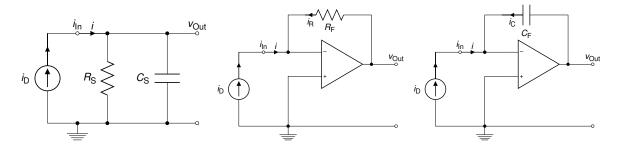

The results from fig. 2.5 give an estimate of the required sensitivity for the readout electronics. The signals are in the range of several nA (e.g. 8 nA for 100 keV at the cathode with an electric field of 1200 V/cm). In addition, the drift time  $t_D$  can be as short as 40 ns if the interaction takes place in the last 10% of the detector volume at the anode side. As the detector signals are electric currents, the simplest method for acquiring the signals is to use a shunt resistor and a measurement of voltage drop across this resistor. Finally, the measured transient voltage signal could be fed to an arbitrary signal processing system. In fact, a single resistor would be the simplest, smallest, and cheapest solution for the front-end electronics. With a resistor in the range of some M $\Omega$ , i.e. is small enough to force the detector current to flow into it, a voltage drop in the range of some mV is generated. This is sufficient for most signal processing systems. However, this concept suffers from a lack of signal bandwidth. As the left circuit in fig. 2.6 shows, the induced current will flow through  $R_S$ , but the  $R_S C_S$  time constant of the two-terminal circuit determines the bandwidth and therefore the rise time of the circuit. Moreover, the detector adds its own capacitance to the shunting elements. The -3 dB bandwidth of the output signal is given by

$$f_{-3\,dB} = \frac{1}{2\pi R_{\rm S}(C_{\rm D} + C_{\rm S})}\,,\tag{2.11}$$

where  $C_D$  is the capacitance of the detector and  $C_S$  is the shunting capacitance of the readout electronics. Even with an undersized value of 1 pF for  $C_D + C_S$  and a shunt resistor of 1 M $\Omega$ , the resulting bandwidth is only 159 kHz. However, the rise time  $t_r$  of the output pulse is proportional to the cutoff frequency  $f_c$  of a low-pass filter. For a first-order low-pass filter, the rise time from 10% to 90% of the step response is calculated by

$$t_{\rm r} = \frac{\ln(0.9) - \ln(0.1)}{2\pi f_{\rm c}} \,, \tag{2.12}$$

where  $f_c$  is the -3 dB cutoff frequency. In other words, the rise time for the given example is about 2.2  $\mu$ s. Most of the current pulses would no longer be detectable.

To increase the bandwidth for such a current-to-voltage converter, a transimpedance amplifier (TIA) is an appropriate solution (fig. 2.6, middle circuit). This configuration forces the generated current to flow into the negative terminal (virtual ground) of the amplifier. That means  $C_{\rm D}$  and  $C_{\rm S}$  are still present, but do not have the same impact on the time constant as the shunting readout circuit. Instead, the rise time and current-to-voltage gain of an ideal TIA are determined by the feedback network. Similarly to the example with the shunting resistor, the TIA is assumed to have a current-to-voltage gain of  $1 M\Omega$ , but the bandwidth is now limited by the parasitic capacitance of the feedback resistor  $R_{\rm F}$ . The resulting bandwidth of the TIA is about 1.6 MHz with a rise time of 220 ns, if the parasitic capacitance of the resistor is around 100 fF. This is sufficient to detect events near the cathode with drift times longer than the rise time of the TIA, but most of the events will suffer from a significant pulse amplitude loss. To further increase the bandwidth of a TIA, several methods can be applied (Brisebois, 2015), but, nevertheless, the achievable gain-bandwidth product is too low with regard to the rise times of anode signals and an adequate signal-to-noise ratio (SNR). Preserving the pulse shape by means of a current-to-voltage converter is guite challenging; however, the detector generates a charge, which can be measured with a modification of the feedback network. A single capacitor  $C_{\rm F}$  in the feedback loop of the amplifier results in a current-integrating circuit (fig. 2.6, right). Finally, the current ic through the capacitor is

$$i_{\rm D} = -i_{\rm C} = C_F \frac{dv_{\rm Out}}{dt} \,. \tag{2.13}$$

Therefore, the voltage  $v_{Out}$  at the output becomes

$$v_{\text{Out}} = \frac{-1}{C_{\text{F}}} \int i_d dt = \frac{-q}{C_{\text{F}}} + v_0.$$

(2.14)

This results in an output voltage whose amplitude is proportional to the moving charge q generated by the detector. This circuit is referred to as the charge-sensitive amplifier (CSA).

Both the TIA and the CSA are basic negative-voltage-feedback operational amplifier circuits.

Figure 2.6.: Three different readout circuits for the conversion and amplification of the detector current  $i_D$  to a voltage  $v_{Out}$ . The left circuit converts the current to a voltage by means of a shunt resistor. The transimpedance amplifier (middle) is also used as a current-to-voltage converter, whereas the CSA (right) is used for a charge-to-voltage conversion.

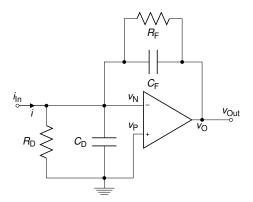

As the gain of the TIA is designed with a resistor in its feedback path, the gain of the CSA is determined by its feedback capacitance. Nevertheless, a resistor has a parasitic capacitance and a capacitance also has a parasitic resistance. Thus, both circuits are adequately modeled by an operational amplifier with an *RC* feedback network. Equally importantly, an operational amplifier also introduces a shunting resistor and capacitor. These are in parallel with the impedance of the detector and abstracted by the resistor *R*<sub>D</sub> and capacitor *C*<sub>D</sub> in fig. 2.7. On the whole, the model of a CSA is a mixture of the three circuits shown in fig. 2.6.

Figure 2.7.: A real configuration of a readout circuit as CSA. The shunting impedance cannot be eliminated, but the effects are reduced by the operational amplifier. The resistor  $R_F$  from the feedback path also has the parasitic capacitance  $C_F$ . This circuit will be used for further analysis.

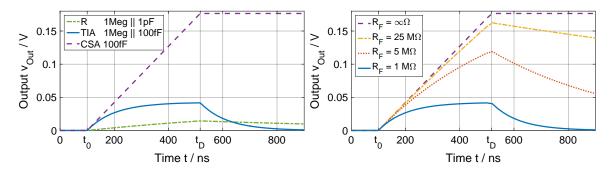

For illustration, the simulated signal waveforms of the three readout circuits with typical values are shown in fig. 2.8. With this example, it is clearly visible that the CSA achieves the highest amplitude. As the output voltage of the CSA begins to increase at time  $t = t_0$  and reaches its peak amplitude  $v_{\text{peak}}$  at time  $t_D$  when the current flow stops, the resulting output voltage for an input current pulse with rectangle shape and constant amplitude  $i_D$  is

$$v_{\text{peak}}\left(R_{\text{F}}\right) = i_{\text{D}}R_{\text{F}}\left(1 - e^{\frac{-t_{\text{D}}}{R_{\text{F}}C_{\text{F}}}}\right).$$

(2.15)

Figure 2.8.: Output signals from the three different readout circuits (left). The resistor-based current-to-voltage conversion has poor gain and bandwidth. These are improved by the transimpedance amplifier (TIA). The largest gain is achieved with the CSA. With a constant parasitic capacitance  $C_F = 100$  fF and an increased feedback resistor  $R_F$ , the TIA becomes a CSA (right).

Therefore, the maximum output voltage  $v_{max}$  for the same input signal is calculated by replacing  $R_F$  with a resistor  $R = \infty$ . Thus, we can define  $v_{peak}$  over  $v_{max}$  as the peak ratio P of the CSA with the time constant  $\tau = R_F C_F$  as

$$\frac{v_{\text{peak}}(R_{\text{F}})}{v_{\text{max}}(R)} = \frac{i_{\text{D}}R_{\text{F}}\left(1 - e^{\frac{-t_{\text{D}}}{R_{\text{F}}C_{\text{F}}}}\right)}{i_{\text{D}}R\left(1 - e^{\frac{-t_{\text{D}}}{RC_{\text{F}}}}\right)}$$

(2.16)

$$P = \lim_{R \to \infty} \frac{v_{\text{peak}}(R_{\text{F}})}{v_{\text{max}}(R)} = \frac{\tau}{t_{\text{D}}} \left(1 - e^{\frac{-t_{\text{D}}}{\tau}}\right).$$

(2.17)

Eq. 2.17 describes the attenuation of the peak amplitude. Referring to (Knoll, 2010), the degree of which the infinite time constant amplitude has been decreased is called the ballistic deficit B. With eq. 2.17, a numerical expression of B can be defined as follows:

$$B = 1 - P$$

. (2.18)

The calculations are based on the assumption that the input current pulse has a rectangular shape and a constant value during the drift time  $t_D$ , as it is seen by the cathode. If we consider a pixelated detector, where the size of the pixel is small compared to the continuous electrode and detector thickness, the current pulse as shown in fig. 2.5 only rises when the moving charge reaches the pixel electrode. However, the drift time  $t_D$  is the same as for the cathode current, but most of the charge is deposited at the end of the pulse. Thus, the anode current can be simply imagined as a rectangular pulse with a shorter drift time and higher current than the cathode signal. Consequently, the ratio of  $\tau/t_D$  is larger than the ratio of the continuous electrode, if the same CSA is used. Thus the ballistic deficit has a greater impact on the cathode signal than on anode signals. The influence of  $t_D$  and  $\tau$  is illustrated in fig. 2.9 Eq. 2.18 is essential to select an optimized feedback time constant dependent on the characteristics of the detector. Usually, the charge-to-voltage gain is a requirement imposed by the lowest measurement range of the application and is set by a carefully selected feedback capacitance (see eq. 2.14). One parameter which can be

#### 2. Analog front-end electronics

Figure 2.9.: The peak ratio *P* of the output signal from the CSA is decreased by a smaller time constant  $\tau = R_F C_F$  (left). Moreover, the ballistic deficit *B* according to eq. 2.18 depends on the time constant  $\tau$  and the drift time  $t_D$  of the moving charge (right).

optimized is the value of the feedback resistor. Of course, the best choice is a value close to infinity, since it matches the ideal CSA. However, this is practically not useful, as every current pulse from the detector forces the amplifier to integrate the charge onto its steady state voltage level. After a while, the amplifier overflows, when the output voltage reaches the level of the supply voltage (or even far below this level). Then, it cannot process another event until the feedback capacitor has discharged. A conventional method for the discharge of the capacitor uses a switch, which is added to the feedback network. This requires an additional reset logic and active control, as featured by an ASIC. A more prevalent practice is to reset the amplifier by making an appropriate choice of the feedback resistor  $R_F$ . The feedback resistor discharges the capacitor  $C_F$  with the characteristic time constant  $\tau$ . An optimally adjusted value of the resistor is a tradeoff between the ballistic deficit, count rate, and frequency response of the amplifier.

#### 2.2.6. Operational amplifier

For the design and investigation of a CSA with an operational amplifier, we will analyze the circuits in time and frequency domains. Our notation for a complex number in the frequency domain is

$$s = \sigma + j\omega$$

, (2.19)

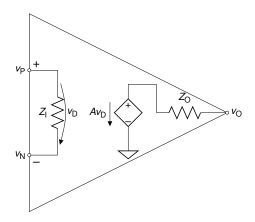

where j is the imaginary unit,  $\sigma$  is the real part, and  $\omega$  is the imaginary part in the range of real positive values. For many circuit designs, it is useful and sufficient to analyze a network containing an operational amplifier with ideal constraints, which means the device has an infinitely high input impedance, infinite open-loop voltage gain, etc. For a realistic and detailed analysis, an operational amplifier can be modeled as shown in fig. 2.10. In contrast to the ideal operational amplifier, the input impedance  $Z_1$  is not infinite. The basic function of an operational amplifier is the amplification of the voltage drop across its positive and negative input terminals. The output voltage is therefore given by

$$v_{\rm O} = (v_{\rm P} - v_{\rm N})A$$

, (2.20)

Figure 2.10.: A model of a realistic operational amplifier (Horowitz and Hill, 2015). The voltage difference  $v_D$  between the two terminals is amplified by the bandwidthlimited factor *A*. The input impedance  $Z_I$  should be as high as possible, whereas the output impedance  $Z_O$  should be close to zero.

where  $v_{P}$  is the potential at the positive terminal and  $v_{N}$  at the negative terminal. For an ideal operational amplifier, the transfer function A(s) has no frequency dependencies, so that the corresponding frequency response

$$H_{\rm A}(f) = A(0) = A_{\rm OL}$$

(2.21)

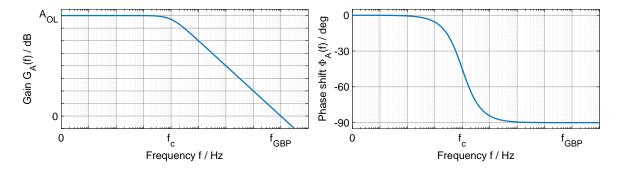

is constant.  $A_{OL}$  is the zero-frequency open-loop gain. For a realistic operational amplifier, the frequency response of the open-loop gain has the shape of a low-pass filter. Consequently, we model the transfer function A(s) of the operational amplifier as a first-order low-pass filter in the frequency domain using

$$A(s) = \frac{A_{\rm OL}}{1+s\tau} \tag{2.22}$$

with the finite open-loop voltage gain AOL and the -3 dB cutoff frequency

$$f_c = \frac{1}{2\pi\tau} \,. \tag{2.23}$$

A characteristic parameter which simplifies the frequency response of an operational amplifier is the gain-bandwidth product (GBP). At frequencies larger than  $f_c$ , the GBP is constant for the first-order low-pass filter frequency response. At the frequency  $f_{GBP}$ , the open-loop gain equals the unity gain. With the maximum open-loop voltage gain  $A_{OL}$ , the functional relationship is given by

$$f_c A_{\rm OL} = f_{\rm GBP} \,. \tag{2.24}$$

With the given parameters  $A_{OL}$  and  $f_{GBP}$  of an operational amplifier, we can set

$$\tau = \frac{A_{\rm OL}}{2\pi f_{\rm GBP}} \tag{2.25}$$

and by setting  $s = j\omega$  with  $\omega = 2\pi f$ , the transfer function of the open-loop gain for periodic sinusoidal signals is

$$A(j2\pi f) = \frac{A_{OL}}{1 + j\frac{f}{f_{GRP}}A_{OL}}.$$

(2.26)

The frequency-dependent gain  $G_A(f)$  and phase shift  $\Phi_A(f)$  are derived from eq. 2.26.

$$G_{A}(f) = |A(j2\pi f)| = \frac{A_{OL}}{\sqrt{1 + \left(\frac{f}{f_{GBP}}A_{OL}\right)^{2}}}$$

(2.27)

$$\Phi_{A}(f) = \angle A(j2\pi f) = -\tan^{-1}\left(\frac{f}{f_{GBP}}A_{OL}\right)$$

(2.28)

Figure 2.11.: The gain  $G_A(f)$  and the phase shift  $\Phi_A(f)$  of the frequency response of an operational amplifier with zero-frequency gain  $A_{OL}$ . The frequency response is modeled as a first-order low-pass filter with the cutoff frequency  $f_c = f_{GBP}/A_{OL}$ . The attenuation of  $A_{OL}$  is -20 dB/decade above  $f_c$ .

#### 2.3. Circuit design of a charge-sensitive amplifier

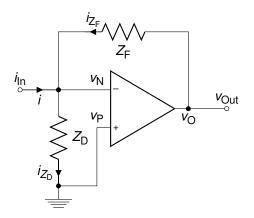

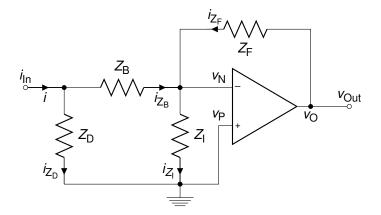

As briefly described in sec. 2.2.5, an operational amplifier integrates a charge, as there is a capacitor  $C_F$  in the feedback and the time constant of the  $R_F C_F$  network is large compared to the drift time of the moving charge at its input. In general, a two-terminal equivalent circuit adequately represents the feedback circuit. Thus, the  $R_F C_F$  network is summarized with the impedance  $Z_F$ . In accordance with fig. 2.2, the impedance of the detector is modeled with the two-terminal impedance  $Z_D$ . Both impedances are connected to the inverting terminal of the operational amplifier. In addition, there are parasitic shunt impedances between the negative and the positive input terminal of the operational amplifier. As they are in parallel with the impedance of the detector, all additional shunt impedances are absorbed by the model of  $Z_D$ . For a simplified circuit analysis, the positive terminal of the operational amplifier is grounded. If the operational amplifier requires a single supply operation, the positive terminal is biased towards the desired potential for the virtual ground. For a circuit analysis, this is negligible. Therefore, the initial circuit for the analysis is shown in fig. 2.12.

Figure 2.12.: An operational amplifier with a current input and a voltage feedback connected to the negative input terminal. With  $Z_F = C_F ||R_F$ , this configuration is used for the charge-to-voltage amplification.  $Z_D$  represents all impedances connected between the input  $i_{In}$  and ground (e.g. capacitance of the detector and parasitic capacitance of the negative input terminal).

#### 2.3.1. Circuit analysis

Kirchhoff's current law is used for the fundamental circuit analysis. For the node at the negative terminal of the operational amplifier, the sum of all currents must be zero.

$$0 = i - i_{Z_{\rm D}} + i_{Z_{\rm F}} \tag{2.29}$$

Further, the currents can be expressed in terms of the feedback impedance  $Z_F$  and shunt impedance  $Z_D$ .

$$i_{Z_{\rm F}} = \frac{(v_{\rm O} - v_{\rm N})}{Z_{\rm F}}$$

(2.30)

$$i_{Z_{\rm D}} = \frac{v_{\rm N}}{Z_{\rm D}} \tag{2.31}$$

According to eq. 2.20, and setting  $v_{\rm P}=0$ , the voltage  $v_{\rm N}$  in eqs. 2.30 and 2.31 can be substituted with

$$v_{\rm N} = \frac{-v_{\rm O}}{A} \,. \tag{2.32}$$

The solution of eq. 2.29 with eqs. 2.30-2.32 results in the current-to-voltage transfer function

$$\frac{-v_{\rm O}}{i} = \frac{AZ_{\rm D}Z_{\rm F}}{Z_{\rm D}(A+1) + Z_{\rm F}},$$

(2.33)

where *A* is the transfer function of the operational amplifier according to eq. 2.22. Another useful method for the circuit analysis is the principle of superposition. Because the system can be described with linear equations, a superposition of all current and voltage sources is possible. That means that first, if the current source for *i* is turned off (replaced with an open circuit), the voltage source for  $v_0$  is acting alone and the resulting voltage at the negative

input terminal of the operational amplifier is

$$v_{\rm N}|_{i=0} = v_{\rm O} \frac{Z_{\rm D}}{Z_{\rm D} + Z_{\rm F}}$$

(2.34)

Second, if the voltage source  $v_0$  is turned off (replaced with a short), the current source is acting alone and the voltage at the negative input terminal of the operational amplifier is

$$v_{\rm N}|_{v_{\rm O}=0} = i \frac{Z_{\rm D} Z_{\rm F}}{Z_{\rm D} + Z_{\rm F}}$$

(2.35)

Finally, the superposition for the voltage node  $v_N$  is the sum of eqs. 2.34 and 2.35

$$v_{\rm N} = v_{\rm N}|_{i=0} + v_{\rm N}|_{v_{\rm O}=0}$$

(2.36)

By inserting eqs. 2.32, 2.34 and 2.35 into eq. 2.36, the output voltage  $v_0$  can be rewritten as

$$v_{\rm O} = -A\left(v_{\rm O}\frac{Z_{\rm D}}{Z_{\rm D}+Z_{\rm F}} + i\frac{Z_{\rm D}Z_{\rm F}}{Z_{\rm D}+Z_{\rm F}}\right).$$

(2.37)

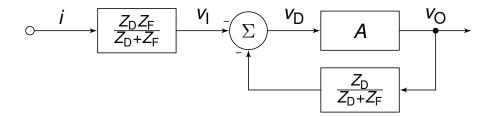

The derived eq. 2.37 is the same as eq. 2.33, but shows the terms for the basic block structure shown in fig. 2.13 in an intuitive and easily readable form.

Figure 2.13.: Block diagram of the closed-loop transfer function with input current *i* and output voltage  $v_0$ . This structure shows the voltage feedback network and loop gain, which are essential for a stability analysis. The voltage difference  $v_D$  at the negative input terminal of the amplifier is the sum of the feedback voltage and an input current-dependent voltage  $v_1$ .

The basic block structure is used to identify the voltage feedback and the stability of the loop. It is obvious that the feedback network  $\beta$  is

$$\beta = \frac{Z_D}{Z_D + Z_F} \tag{2.38}$$

and the closed-loop voltage gain G is only (Horowitz and Hill, 2015)

$$G = \frac{A}{1 + A\beta} = -\frac{v_0}{v_1} \,. \tag{2.39}$$

The closed-loop gain *G* becomes  $1/\beta$  if the loop gain  $A\beta$  is much greater than one. On the contrary, the closed-loop gain becomes infinite if the loop gain  $A\beta = -1$ . At this frequency, the system tends to be unstable, and oscillates. As *A* and  $\beta$  are defined to have positive real values, the case where the loop gain becomes -1 only occurs if the loop gain is 1 and a phase

shift of 180° is introduced by the frequency response of  $A\beta$ . A phase shift of a sinusoidal signal with 180° is equal to a multiplication with -1. To make the feedback circuit stable, the phase shift therefore has to be less than 180° at the frequency  $f_i$ , where the loop gain is 1. A sufficient phase margin at the frequency  $f_i$  is required to ensure a stable operation over the entire temperature range, and also to cover tolerances of the used integrated circuits. The

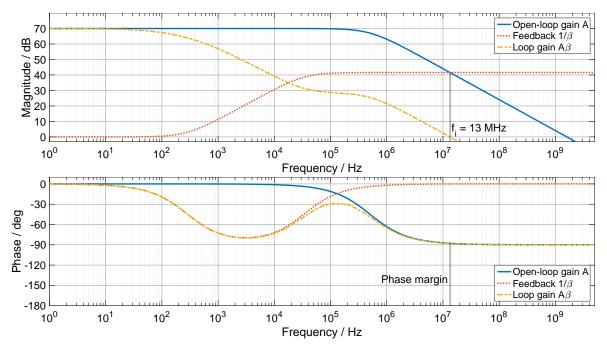

Figure 2.14.: The Bode plot of the closed-loop transfer function. The loop gain is 1 at the frequency  $f_i$  with a phase margin of roughly 90°. This is sufficient for a stable operation. See text for numerical values of the example.

example in fig. 2.14 is calculated with the parameters from table 2.1 for the OPA657. The feedback impedance was chosen to be 100 fF in parallel with  $25 M\Omega$ . Further, the detector capacitance of 6.7 pF in parallel with a  $50 G\Omega$  resistor and the parasitic input capacitance of 5.2 pF are the shunting impedance  $Z_D$ . The stability is investigated at the frequency, where the loop gain is 1. Mathematically, this intersection can be calculated by solving

$$|A(j2\pi f)\beta(j2\pi f)| = 1.$$

(2.40)

From the Bode plot shown in fig. 2.14, this point can be found at

$$\log_{10}(|A|) - \log_{10}(|\frac{1}{\beta}|) = 0.$$

(2.41)

In this plot, the reciprocal of the feedback network  $\beta$  intersects the open-loop gain at approximately 13 MHz. At this frequency, the phase shift of the loop gain is 88°, resulting in a phase margin  $\phi$  of 92°, which is sufficient for a stable operation. The phase margin  $\phi$  is calculated by

$$\phi = 180^{\circ} - (\angle A(2\pi f_i) + \angle \beta(2\pi f_i)) .$$

(2.42)

Besides the stability of the circuit, the effective input impedance also depends on the open-

loop voltage gain of the amplifier, and is changed by the feedback network (Horowitz and Hill, 2015). The effective input impedance of the CSA should be very low, to make sure that all current flows into the amplification circuit. Regarding fig. 2.12, the effective input impedance from the CSA is defined by the ratio of the voltage at the input terminal  $i_{ln}$  and the input current *i*. The voltage at the input terminal is  $v_N$ , so the effective input impedance  $Z_i^*$  is

$$Z_{\mathsf{I}}^* = \frac{v_{\mathsf{N}}}{i} \,. \tag{2.43}$$

Solving eq. 2.29 for  $v_N$  with eqs. 2.30-2.32,  $Z_I^*$  can be expressed as

$$Z_{\rm I}^* = \frac{Z_{\rm D} Z_{\rm F}}{Z_{\rm D} (A+1) + Z_{\rm F}} \,. \tag{2.44}$$

As *A* becomes infinitely large, as we assume for an ideal operational amplifier, the effective input impedance is zero. This satisfies the principle of the virtual ground. If we assume an ideal detector without a parasitic impedance from the CSA,  $Z_D$  is infinite. For this case, the effective input impedance

$$\lim_{Z_{\mathsf{D}}\to\infty} Z_{\mathsf{I}}^* = \frac{Z_{\mathsf{F}}}{A+1}$$

(2.45)

is determined by the open-loop gain and the feedback network  $Z_F$ . To make sure that all current flows into the CSA and is integrated on the feedback capacitor, the impedance from eq. 2.45 must be small compared to the shunting impedance  $Z_D$ . Consequently, an operational amplifier with a large open-loop gain is required.

#### 2.3.2. Charge-to-voltage transfer function

The CSA is designed to measure a charge with a voltage output signal, where the peak amplitude is proportional to the charge seen at the input. The relation of the output voltage  $v_0$  to the input charge Q is the charge-to-voltage transfer function

$$\frac{v_{\rm O}}{Q} = H_{\rm Q} \,. \tag{2.46}$$

As the charge is defined to be

$$\frac{dQ}{dt} = i, \qquad (2.47)$$

where *i* is the electrical current, the corresponding Laplace transformation of eq. 2.47 is

$$\mathcal{L}\left\{Q'(t)\right\} = sQ(s) = i(s).$$

(2.48)

If we replace *i* in the current-to-voltage transfer function from eq. 2.33 by eq. 2.48 and set the feedback network  $Z_{\rm F} = \frac{1}{sC_{\rm F}}$  and parasitic impedance  $Z_{\rm D} = \frac{1}{sC_{\rm D}}$  to single capacitors, then the charge-to-voltage transfer function is given by

$$H_Q = \frac{-A}{C_D + C_F(A+1)}.$$

(2.49)

The simplification of the impedances to single capacitors is valid, as we want to investigate the frequency response of the charge-to-voltage conversion. If the feedback time constant is chosen appropriately according to eq. 2.18, there is no significant peak amplitude loss in the voltage signal. The peak amplitude of the voltage signal is therefore independent of the feedback resistor  $R_F$ . The impedance  $Z_D$  can also be simplified for this analysis, as the equivalent input resistance of the amplifier and detector is much larger than the effective input impedance according to eq. 2.44. For an ideal operational amplifier with infinite openloop gain A,  $H_Q$  from eq. 2.49 becomes  $-1/C_F$  over the entire frequency domain. Since the open-loop voltage gain of an operational amplifier is not independent of frequency, a more realistic charge-to-voltage transfer function is obtained by replacing *A* from eq. 2.49 by eq. 2.22

$$H_Q(s) = \frac{-A_{\rm OL}}{C_{\rm D} + C_{\rm F}(A_{\rm OL} + 1) + s\tau(C_{\rm D} + C_{\rm F})} \,.$$

(2.50)

The charge-to-voltage gain is then given by

$$|H_Q(j2\pi f)| = G_Q(f) = \frac{A_{OL}}{\sqrt{(C_D + C_F(A_{OL} + 1))^2 + \left(\frac{f}{f_{GBP}}A_{OL}(C_D + C_F)\right)^2}}.$$

(2.51)

The steady state of the system is derived by calculating the zero-frequency gain:

$$G_{\rm QS} = \lim_{f \to 0} G_{\rm Q}(f) = \frac{A_{\rm OL}}{C_{\rm D} + C_{\rm F}(A_{\rm OL} + 1)}.$$

(2.52)

Eq. 2.52 shows that a finite open-loop gain  $A_{OL}$  attenuates the measured peak voltage. The measured fraction of charge as a ratio of  $G_{QS}$  over the ideal charge-to-voltage gain  $1/C_{F}$  is given by

$$G_{\rm QS} C_{\rm F} = \frac{A_{\rm OL}}{\frac{C_{\rm D}}{C_{\rm F}} + A_{\rm OL} + 1}$$

(2.53)

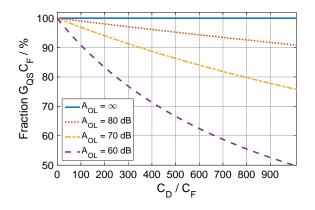

It is obvious that the measured peak amplitude is decreased by an increased detector capacitance  $C_D$  or a reduced open-loop voltage gain  $A_{OL}$ . Thus, the operational amplifier should provide a high and stable open-loop voltage gain for an improved system performance as illustrated in fig 2.15.

An equally important parameter of the CSA is the rise time of the output voltage as a reaction of a charge step at its input. As shown by eq. 2.12, the rise time is proportional to the cutoff frequency of the system. Therefore, to determine the rise time, we have to calculate its cutoff frequency, which is derived by using eq. 2.51

$$\frac{|H_Q(j2\pi f_c)|}{|H_Q(0)|} = \frac{1}{\sqrt{2}}$$

(2.54)

$$f_{\rm c} = f_{\rm GBP} \frac{\frac{C_{\rm D}}{C_{\rm F}} + (A_{\rm OL} + 1)}{A_{\rm OL}(\frac{C_{\rm D}}{C_{\rm F}} + 1)}.$$

(2.55)

Eq. 2.55 shows, that the upper bandwidth limit is lowered with an increased fraction of the shunting capacitance  $C_D$  over  $C_F$ . The bandwidth is extended with a lower value of  $A_{OL}$ , but

Figure 2.15.: The measured fraction of charge dependent on the ratio of input capacitance  $C_{\rm D}$  over feedback capacitance  $C_{\rm F}$ . The fraction is increased with an increased zero-frequency open-loop voltage gain  $A_{\rm OL}$  of the operational amplifier.

this will reduce the measured fraction of charge, as shown in fig. 2.15. This also means that the SNR is decreased and therefore the resolution of the charge measurement is also decreased.  $A_{OL}$  should therefore be as large as possible. For this assumption, the bandwidth of the CSA is

$$\lim_{A_{\rm OL}\to\infty} f_{\rm c} = \frac{f_{\rm GBP}}{\frac{C_{\rm D}}{C_{\rm c}} + 1} \,. \tag{2.56}$$

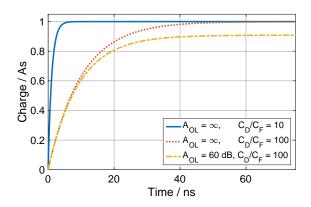

Eq. 2.56 shows that the cutoff frequency and therefore the rise time of the CSA are directly proportional to the gain-bandwidth product of the amplifier. The response of the transfer function from eq. 2.49 to a unit step is shown in fig. 2.16.

Figure 2.16.: The output signal of the CSA with a unity step at its input. The rise time is increased with an increasing ratio of  $C_D/C_F$ . The gain-bandwidth product of the operational amplifier was assumed to be  $f_{GBP} = 1$  GHz. In this example, the rise times are 17 ns (solid line), 32 ns (dashed line) and 35 ns (dotted line). The decreased rise time related to a smaller open-loop gain  $A_{OL}$  is caused by the attenuation of the peak amplitude.

#### 2.3.3. Input coupling of the CSA

As shown in fig. 2.3, at least one of the electrodes is biased at a negative high voltage. Thus, the amplifier at the cathode must be protected against the bias voltage, since it is not common for integrated circuits to operate at high input voltages in the range of several hundreds of volts. A capacitor in series to the amplifier input blocks the bias voltage of the detector, but allows the detector current to flow. This electrical circuit is shown in fig. 2.17, where the coupling capacitor  $C_B$  is represented by the impedance  $Z_B$ . In this configuration, the parasitic impedance  $Z_I$  of the operational amplifier and the detector impedance  $Z_D$  are separated by the impedance  $Z_B$ . As the influence of the coupling capacitor is not apparent at

Figure 2.17.: A functionally equivalent configuration to fig. 2.12 for the charge-to-voltage amplification. The input impedance at the terminal  $i_{ln}$  is a Pi network instead of the single impedance  $Z_D$ .  $Z_B$  is a high-voltage coupling capacitor to protect the low-voltage input terminals of the operational amplifier.

first glance throughout the equation for the current-to-voltage transfer function, a calculation with an infinite loop gain turns out the simplified equation

$$\frac{-v_{\rm O}}{i} = \frac{Z_{\rm D} Z_{\rm F}}{Z_{\rm B} + Z_{\rm D}} \,. \tag{2.57}$$

To eliminate the influence of the impedance  $Z_B$ , it must be much smaller than  $Z_D$ . In the case that all impedances are represented by a single capacitor, the steady-state charge-to-voltage gain is ultimately given by

$$\frac{v_{\rm O}}{Q} = \frac{1}{C_{\rm F} \left(1 + \frac{C_{\rm D}}{C_{\rm B}}\right)}.$$

(2.58)

Eq. 2.58 shows that the coupling capacitor must be much larger than the detector capacitance to avoid a peak amplitude loss, thus improving the SNR.

#### 2.3.4. Noise

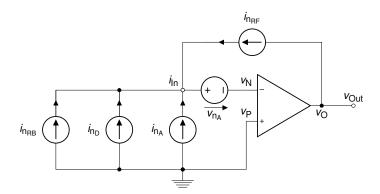

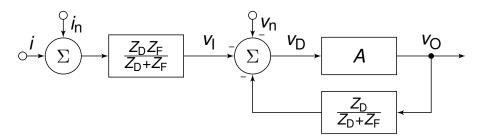

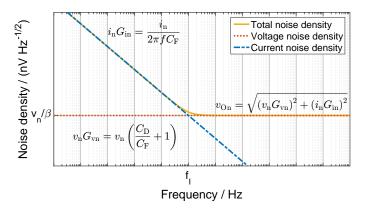

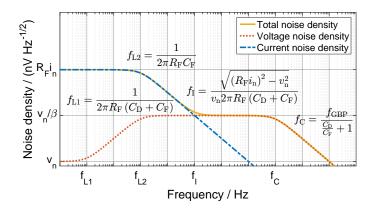

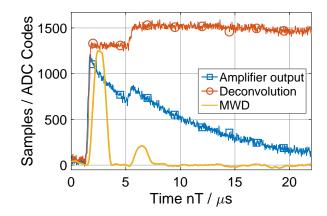

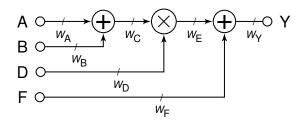

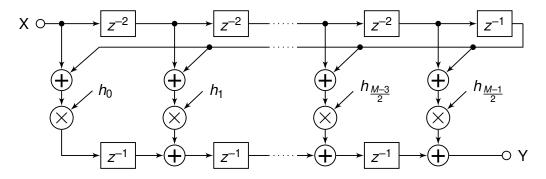

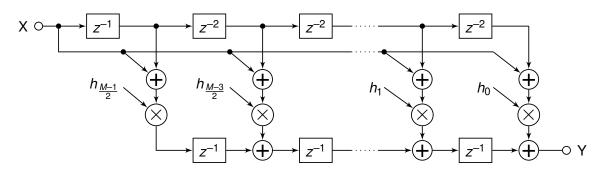

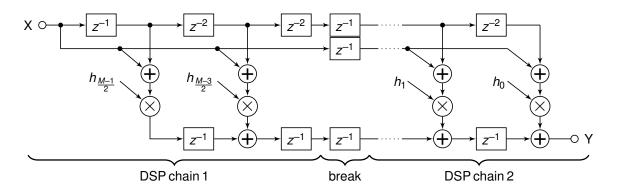

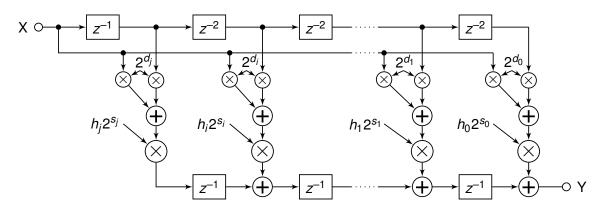

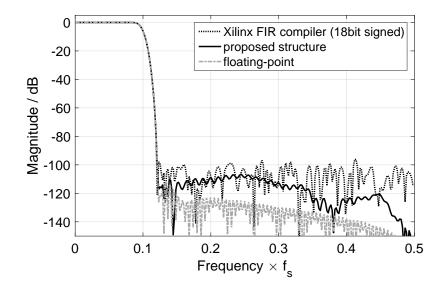

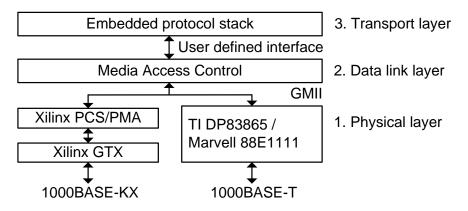

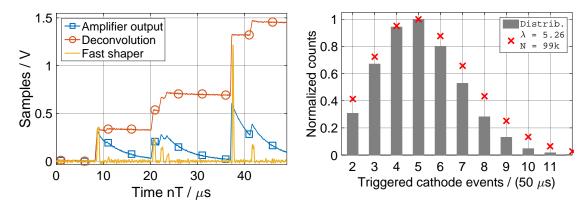

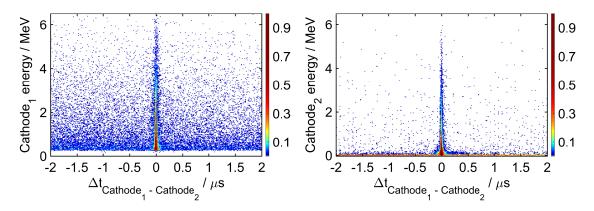

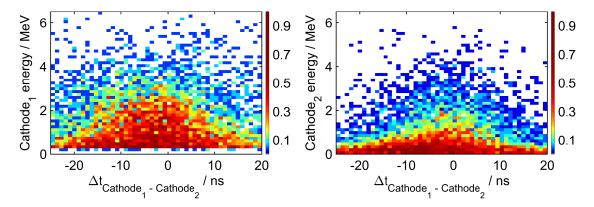

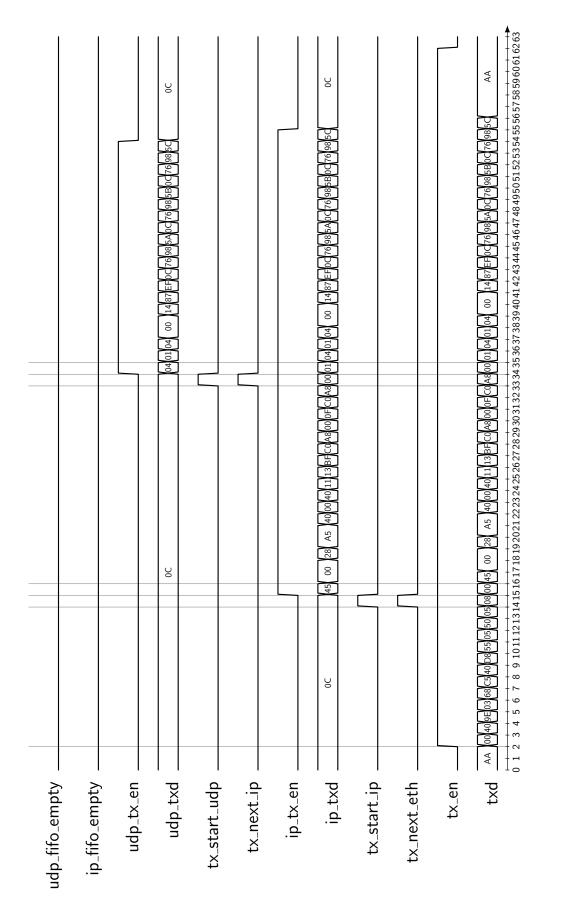

As has been pointed out, the noise caused by the electronics and the corresponding SNR characterize the quality of the CSA with respect to the achievable energy resolution. The precision of the charge measurement and the achievable timing are directly related to the SNR. Regarding both values, the front-end electronics should not limit the intrinsic resolution of the detector. Thus, to reduce the electronics noise, the noise sources of the detector system must be identified in the first step. The main source for the electronics noise is the operational amplifier. But the passive components of an electronic circuit also generate noise. The resulting noise at the output is the sum of all noise sources at the input, amplified by the noise gain. The essential noise sources of the electronics circuit are shown in fig. 2.18. The noise contribution of the operational amplifier is simplified to a model, where its noise is