# Improved Fault Tolerant SRAM Cell Design & Layout in 130nm Technology

A Thesis Presented to the

College of Graduate Studies and Research

In Fulfillment of the Requirement

For the Degree of Master of Science

In the Department of

Electrical and Computer Engineering

University of Saskatchewan

Saskatoon, Saskatchewan

Canada

By

# Govindakrishnan Radhakrishnan

© Copyright Govindakrishnan Radhakrishnan, August 2014. All rights reserved.

**PERMISSION TO USE**

In presenting this thesis in partial fulfilment of the requirements for a Postgraduate degree from

the University of Saskatchewan, I agree that the libraries of this University may make it freely

available for inspection. I further agree that permission for copying of this thesis in any manner,

in whole or in part, for scholarly purposes may be granted by the professor or professors who

supervised my thesis work or, in their absence, by the Head of the Department or the Dean of the

college in which my thesis work was done. It is understood that any copying or publication or use

of this thesis or parts thereof for financial gain shall not be allowed without my written permission.

It is also understood that due recognition shall be given to me and to the University of

Saskatchewan in any scholarly use which may be made of any material in my thesis.

Requests for permission to copy or to make other use of material in this thesis in whole or part

should be addressed to:

Head of the Department of Electrical and Computer Engineering

57 Campus Drive

University of Saskatchewan

Saskatoon, Saskatchewan, Canada

S7N 5A9

i

### **ACKNOWLEDGEMENT**

I would like to express my gratitude to my supervisor, Dr. Li Chen, for his support and guidance during the course of my thesis work. I really appreciate the extraordinary effort he has done to come up with the infrastructure and testing facilities needed for the completion of my thesis. I am grateful to Dr. Ron Bolton for teaching me VLSI design, which has inspired me to pursue a career in this exciting field. I would also like to thank my teachers Dr. Anh Dinh, Dr. Rajesh Karki and Dr. Seok Bum Ko, who has taught me several courses during my studies here at University of Saskatchewan.

I also wish to thank my fellow members in the VLSI Lab for their support. It was a great learning experience working with them during my graduate studies. Lastly, I would like to thank my uncle and aunt for their support and hospitality during my studies here. Without their support, I wouldn't have been able to complete my thesis work.

## **ABSTRACT**

Technology scaling of CMOS devices has made the integrated circuits vulnerable to single event radiation effects. Scaling of CMOS Static RAM (SRAM) has led to denser packing architectures by reducing the size and spacing of diffusion nodes. However, this trend has led to the increase in charge collection and sharing effects between devices during an ion strike, making the circuit even more vulnerable to a specific single event effect called the single event multiple-node upset (SEMU). In nanometer technologies, SEMU can easily disrupt the data stored in the memory and can be more hazardous than a single event single-node upset.

During the last decade, most of the research efforts were mainly focused on improving the single event single-node upset tolerance of SRAM cells by using novel circuit techniques, but recent studies relating to angular radiation sensitivity has revealed the importance of SEMU and Multi Bit Upset (MBU) tolerance for SRAM cells. The research focuses on improving SEMU tolerance of CMOS SRAM cells by using novel circuit and layout level techniques. A novel SRAM cell circuit & layout technique is proposed to improve the SEMU tolerance of 6T SRAM cells with decreasing feature size, making it an ideal candidate for future technologies. The layout is based on strategically positioning diffusion nodes in such a way as to provide charge cancellation among nodes during SEMU radiation strikes, instead of charge build-up. The new design & layout technique can improve the SEMU tolerance levels by up to 20 times without sacrificing on area overhead and hence is suitable for high density SRAM designs in commercial applications. Finally, laser testing of SRAM based configuration memory of a Xilinx Virtex-5 FPGA is performed to analyze the behavior of SRAM based systems towards radiation strikes.

# TABLE OF CONTENTS

| PERI | MISSION TO USE                                                          | i   |

|------|-------------------------------------------------------------------------|-----|

| ACK  | NOWLEDGEMENT                                                            | ii  |

| ABS' | TRACT                                                                   | iii |

| TAB  | LE OF CONTENTS                                                          | iv  |

| LIST | OF FIGURES.                                                             | vii |

| LIST | OF TABLES.                                                              | xi  |

| ABB  | REVIATIONS                                                              | xii |

| СНА  | PTER 1 INTRODUCTION                                                     | 1   |

| 1.1  | Background                                                              | 1   |

| 1.2  | Motivation                                                              | 2   |

| 1.3  | Research Focus & Objectives.                                            | 5   |

| 1.4  | Thesis Overview.                                                        | 7   |

| СНА  | PTER 2 OVERVIEW                                                         | 8   |

| 2.1  | Radiation Problems in Terrestrial Environment.                          | 8   |

| 2.2  | Effects of Scaling on SRAM Radiation Tolerance                          | 10  |

| 2.3  | Physics of Single Event Upsets in SRAM cells.                           | 14  |

| 2.4  | Laser fault Injection techniques for SEU Tolerance Evaluation           | 17  |

| 2.5  | Existing 6T cell layout design                                          | 18  |

| 2.6  | Current Layout techniques for SEMU / MBU mitigation & their Limitations | 19  |

|      | 2.6.1 Placing Bit-lines between Sensitive nodes                         | 20  |

|      | 2.6.2 Well / Substrate Tapping Scheme                                   | 20  |

|     | 2.6.3   | Placing Guard Bands                                  |

|-----|---------|------------------------------------------------------|

|     | 2.6.4   | Guard Diodes                                         |

|     | 2.6.5   | LEAP (Layout Error Aware Positioning of Transistors) |

| СНА | PTER 3  | PROPOSED LAYOUT TECHNIQUE AND SRAM DESIGN            |

| 3.1 | Propos  | sed 12T SRAM Design                                  |

| 3.2 | Propos  | sed Layout28                                         |

| 3.3 | Mitiga  | ation Mechanism for SEMU Events                      |

| 3.4 | Schem   | natic Design and Simulations                         |

|     | 3.4.1   | Cadence Simulation & Virtuoso: Brief Description30   |

|     | 3.4.2   | SRAM Design30                                        |

|     | 3.4.3   | Critical Charge Analysis31                           |

|     | 3.4.4   | SNM Analysis                                         |

|     | 3.4.5   | Drawbacks                                            |

| СНА | PTER 4  | TESTING METHODOLOGY                                  |

| 4.1 | Accur   | o <sup>TM</sup> Software Description                 |

| 4.2 | LET T   | Threshold Calculation                                |

| 4.3 | Post P  | Processing                                           |

| СНА | PTER 5  | SINGLE EVENT SIMULATION RESULTS                      |

| 5.1 | 6T SR   | AM Cell Simulation Results                           |

| 5.2 | 12T S   | RAM Cell Simulation Results                          |

| 5.3 | Error ( | Cross section Analysis and Comparison                |

| 5.4 | Summ    | nary                                                 |

| CHA | PTER 6  | LASER TESTING OF XILINX VIRTEX-5 FPGA                |

| 6.1 | Object  | tives                                                |

| 6.2 | Test S  | etup63                                               |

| 6.3 | Testin  | g Methodology65                                      |

| 6.4 | Config  | guration Memory test66                               |

| 6.5 | Cross   | Section Analysis 73                                  |

| 6.6  | Test Results of Other Functional Blocks in the FPGA |                                   | 76 |

|------|-----------------------------------------------------|-----------------------------------|----|

|      | 6.6.1                                               | Configurable Logic Blocks (CLB's) | 76 |

|      | 6.6.2                                               | DSP48E Blocks.                    | 80 |

|      | 6.6.3                                               | Block RAM (BRAM)                  | 83 |

|      | 6.6.4                                               | Summary                           | 86 |

| CHAI | PTER 7                                              | CONCLUSION.                       | 87 |

| 7.1  | Future                                              | work                              | 89 |

| REFE | RENCE                                               | SS                                | 90 |

# **LIST OF FIGURES**

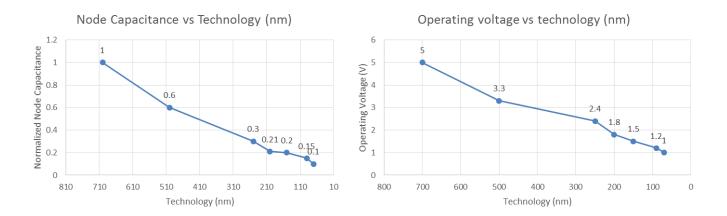

| Figure 2.1: Decrease in normalized capacitance and operating voltage with technolog    | gy scaling    |

|----------------------------------------------------------------------------------------|---------------|

| [2]                                                                                    | 11            |

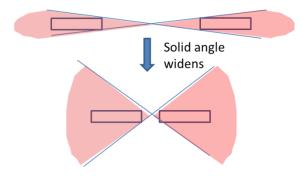

| Figure 2.2: Widening of solid angle when nodes get closer during technology scaling    | 12            |

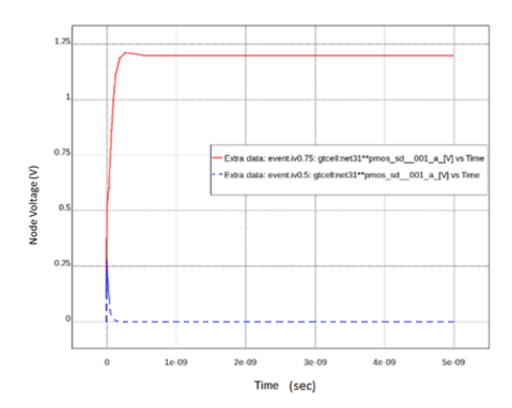

| Figure 2.3a: Node voltage at PMOS Drain for SEMU strike for LET = 0.7 (red) and l      | LET = 0.5     |

| (blue)                                                                                 | 13            |

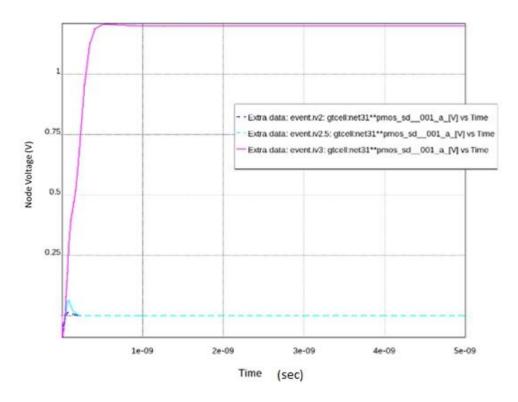

| Figure 2.3b: Node voltage for a Normal NMOS strike for LET = 3 (pink) and LET =        | 2.5           |

| (blue)                                                                                 | 14            |

| Figure 2.4: Funneling of depletion region to gather minority carriers. (Right) Current | at the Drain  |

| during a single event strike [1].                                                      | 15            |

| Figure 2.5: a) Radiation strike on a 6T SRAM cell Drain node(red) b) Equivalent inv    | erter circuit |

| with PMOS transistor replace by an equivalent resistance.                              | 16            |

| Figure 2.6: a) Traditional 6T SRAM cell b) Thin cell layout of 6T cell                 | 18            |

| Figure 2.7: PMOS and NMOS devices separated by guard bands [16]                        | 21            |

| Figure 2.8: Charge cancellation in an inverter based on LEAP technique [4]             | 23            |

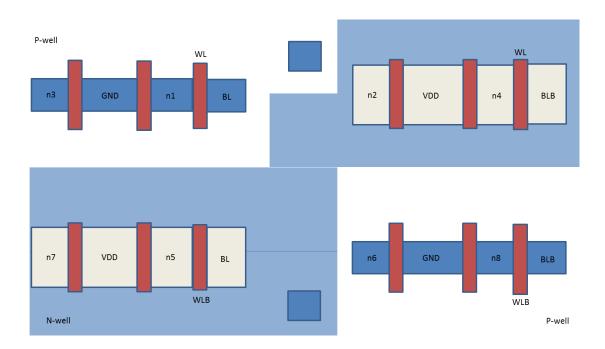

| Figure 3.1: The schematic diagram of the proposed 12T cell                             | 26            |

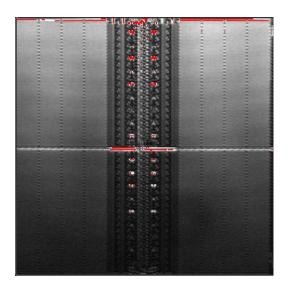

| Figure 3.2: Layout of the proposed 12T SRAM cell.                                      | 28            |

| Figure 3.3: Illustration of 3 major radiation strike directions                        | 28            |

| Figure 3.4: The current pulse waveform used for upset                                  | 31            |

| Figure 3.5: Block diagram for test setup for SNM noise margin analysis                 | 34            |

| Figure 3.6: Schematic setup for SNM noise margin analysis based on method proposed by          |

|------------------------------------------------------------------------------------------------|

| Severick[13]                                                                                   |

| Figure 3.7a: 6T cell hold noise margin                                                         |

| Figure 3.7b: 6T cell read noise margin                                                         |

| Figure 3.7c: 6T cell write noise margin.                                                       |

| Figure 3.8a: 12T cell hold noise margin                                                        |

| Figure 3.8b: 12T cell read noise margin                                                        |

| Figure 3.8c: 12T cell read noise margin                                                        |

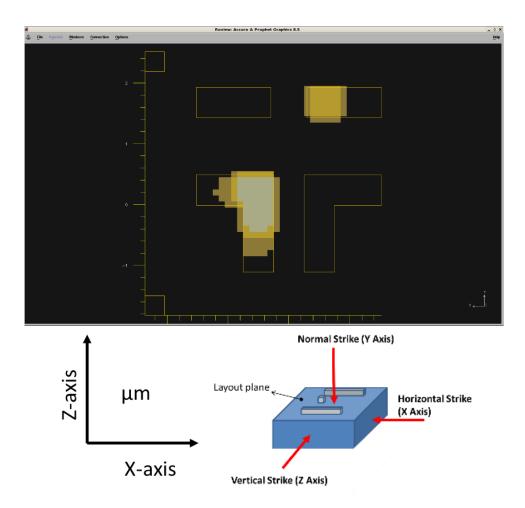

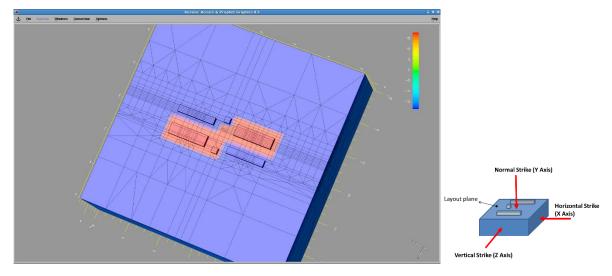

| Figure 4.1: 3D mesh model of the 6T Cell used for radiation simulation in Accuro43             |

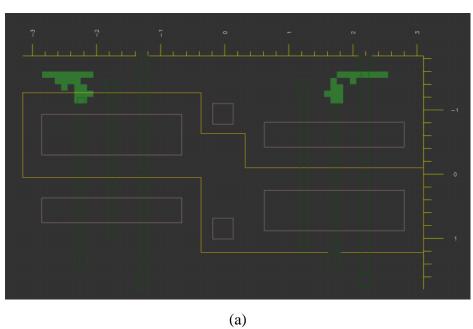

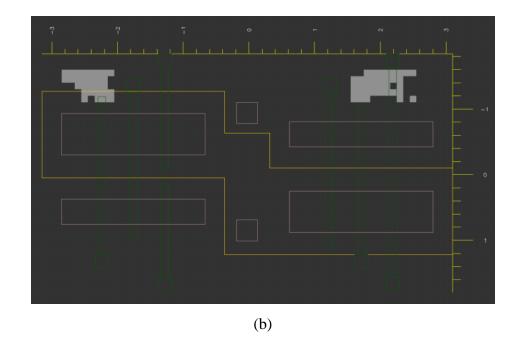

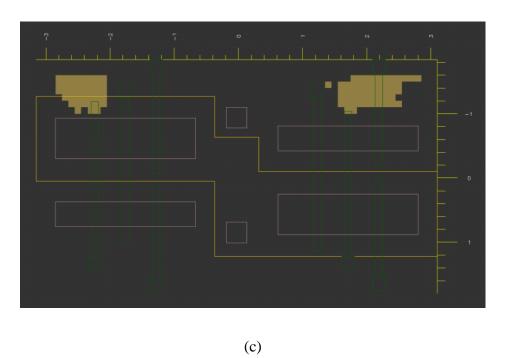

| Figure 5.1: Layout of the 6T SRAM cell                                                         |

| Figure 5.2: 3D mesh model of 6T SRAM cell                                                      |

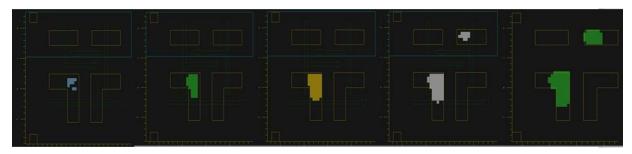

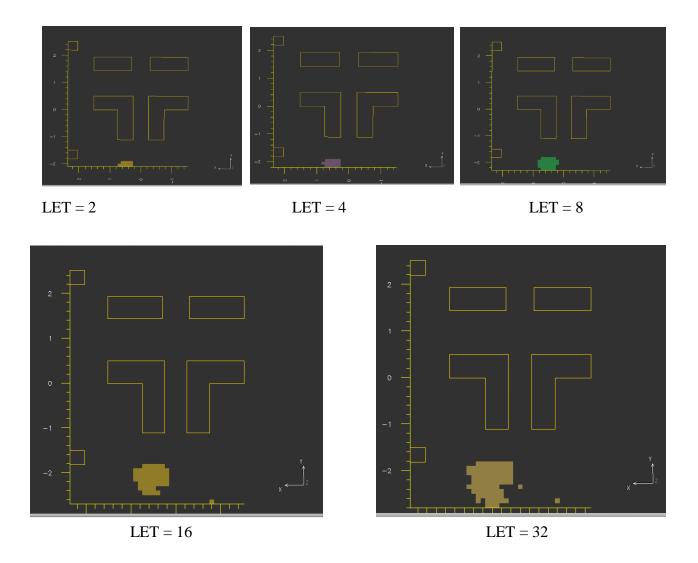

| Figure 5.3: Normal strike cross section map of 6T cell for LET= 4 (grey), LET = 5 (yellow) and |

| LET = 10 (light yellow)                                                                        |

| Figure 5.4: LET profile, from left a) LET = 3, b) LET = 3.6, c) LET = 4, d) LET = 5, e) LET =  |

| 1048                                                                                           |

| Figure 5.5: Shows the sensitivity map for horizontal strike on 6T SRAM cell for LET = 24, LET  |

| = 32, LET = 64                                                                                 |

| Figure 5.6: (Top) Vertical sensitivity map for LET=2 (yellow), LET = 4 (grey), LET = 16        |

| (green); (Bottom) shows the vertical sensitivity map for LET = 2, 4, 8, 16, 3250               |

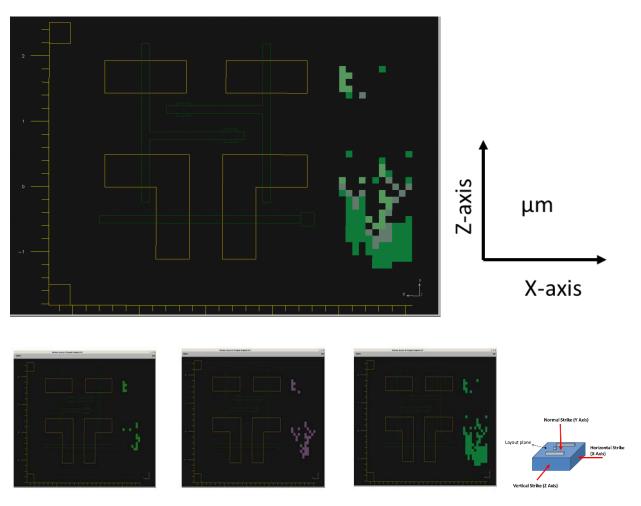

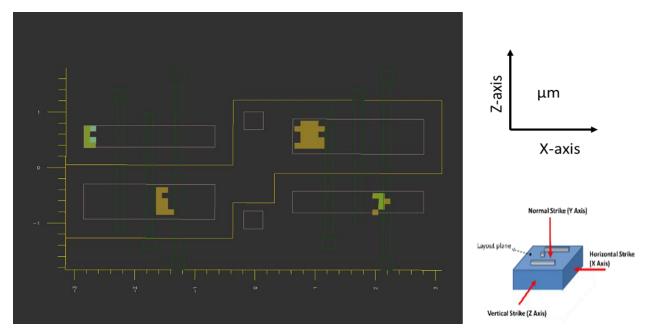

| Figure 5.7: Layout footprint of the 12T SRAM cell design.                                      |

| Figure 5.8: 3D mesh model of the 12T SRAM cell                                                                      | 52 |

|---------------------------------------------------------------------------------------------------------------------|----|

| Figure 5.9: Sensitivity map of 12T SRAM cell for normal strike                                                      | 53 |

| Figure 5.10: Sensitivity map for normal strike, from left a) LET = 3, b) LET = 4, c) LET = 5:                       | 53 |

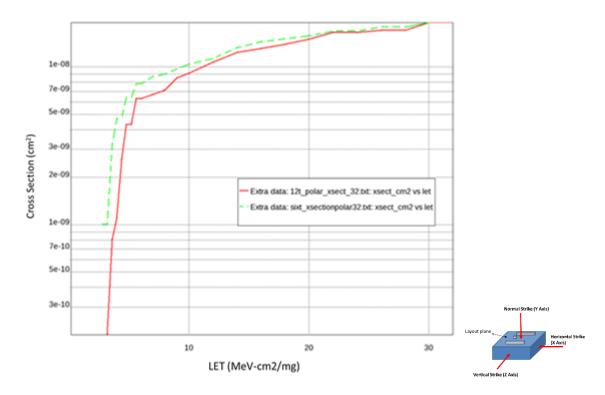

| Figure 5.11: Cross section map of 6T Vs 12T cell for normal strikes                                                 | 54 |

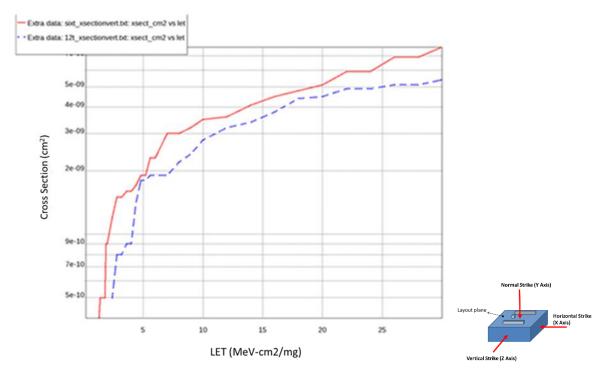

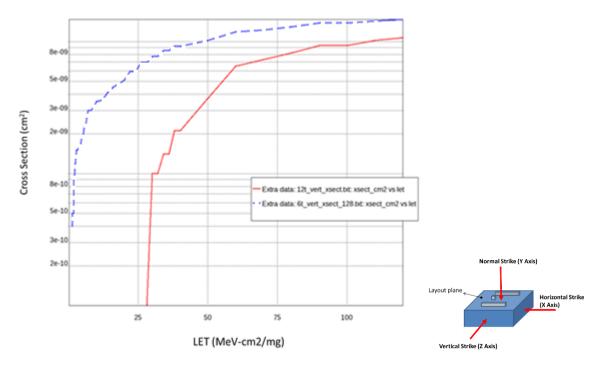

| Figure 5.12: Initial vertical strike cross section map for 6T (red) and 12T cell (blue) without PMOS/NMOS matching. | 55 |

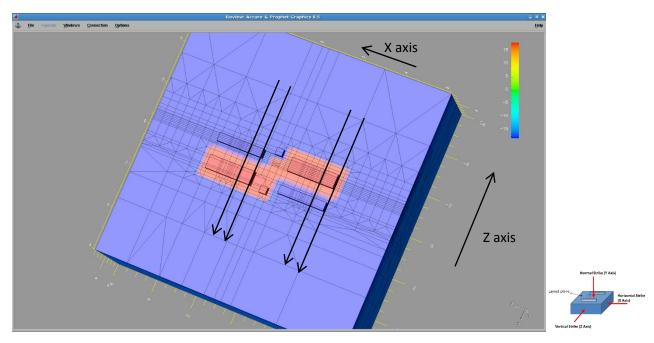

| Figure 5.13: 3D mesh model of the 12T SRAM cell, the 2 regions scanned are within black arrows.                     | 56 |

| Figure 5.14: Vertical cross section plot for 6T (dashed blue) and 12T (red) after PMOS / NMOS matching              |    |

| Figure 5:15: Shows the sensitivity map of 12T cell for a) LET = 48 b) LET=64 c) LET=965                             | 59 |

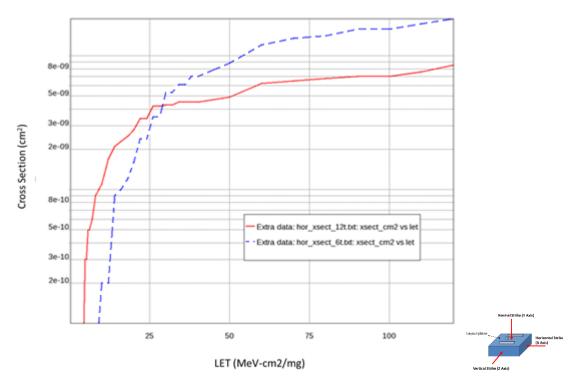

| Figure 5.16: Horizontal cross section plot for 6T cell (blue) and 12T cell (Red)                                    | 60 |

| Figure 6.1a: Virtex 5 LX50T board used for laser testing                                                            | 64 |

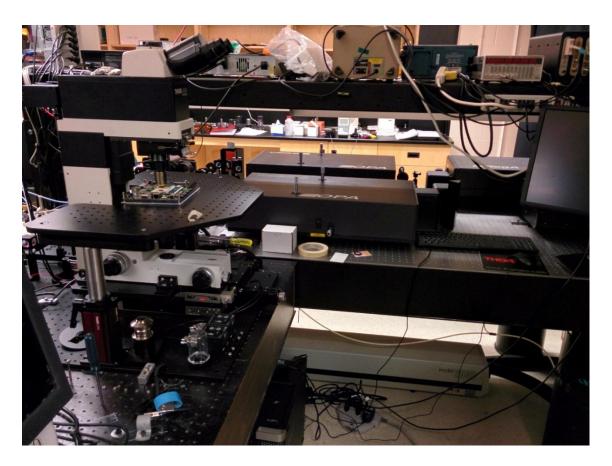

| Figure 6.1b: TPA laser testing facility at SSSC, University of Saskatchewan                                         | 65 |

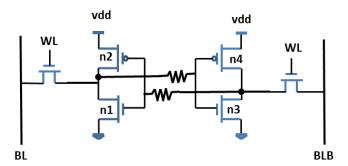

| Figure 6.2: Resistive feedback based SRAM cell used in FPGA's                                                       | 67 |

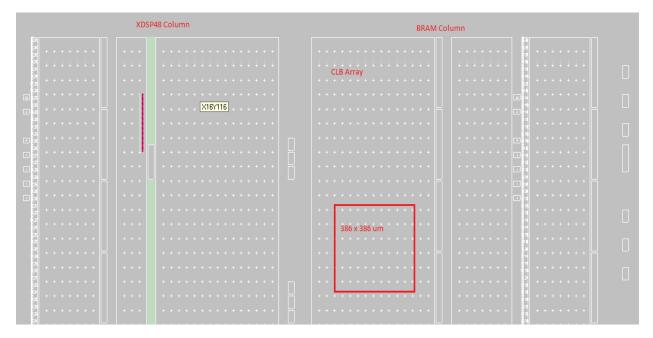

| Figure 6.3: The 386 x 386 μm scan area chosen for configuration memory testing in Virtex-5                          | 68 |

| Figure 6.4: Configuration memory micrograph for laser scan area (384 x 384µm)                                       | 69 |

| Figure 6.5: Configuration memory micrograph for laser scan area (96 x 96 μm)                                        | 70 |

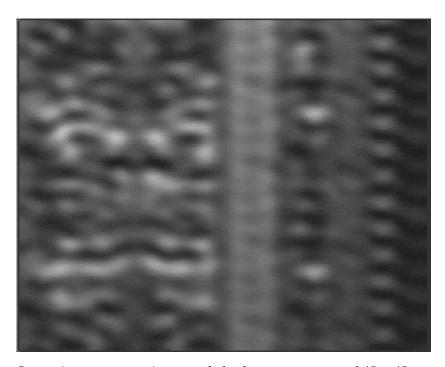

| Figure 6.6: Configuration memory micrograph for laser scan area (48 x 48 µm)                                        | 72 |

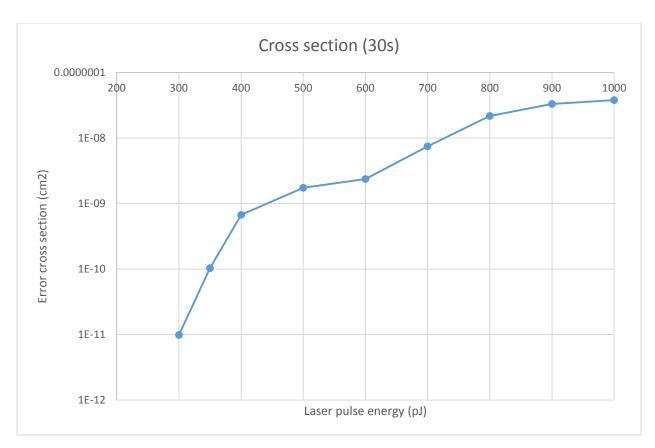

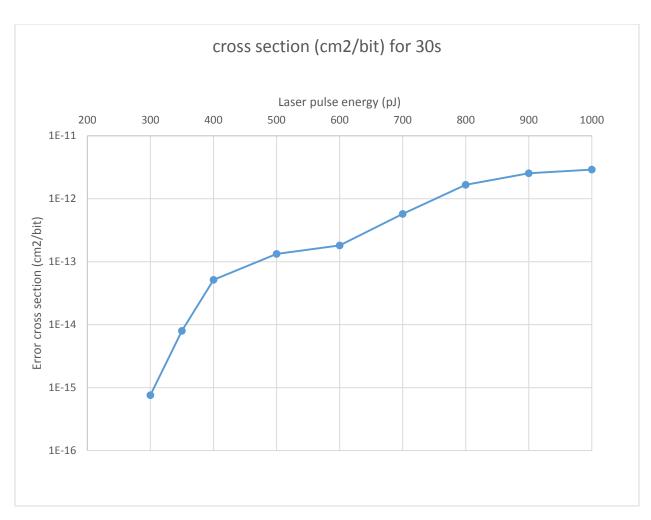

| Figure 6.7: Error cross section (cm2) vs laser pulse energy of configuration memory                                 | 74 |

| Figure 6.8: Error cross section per bit (cm2/bit) vs laser pulse energy of configuration memory         |

|---------------------------------------------------------------------------------------------------------|

| 7                                                                                                       |

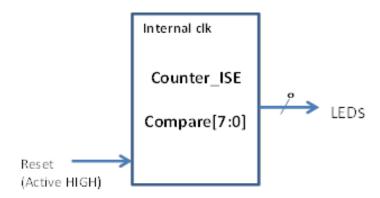

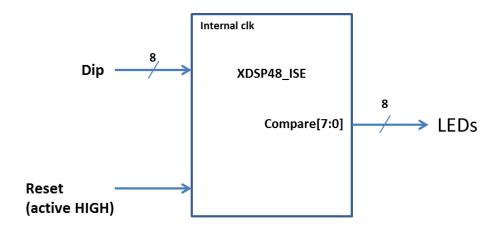

| Figure 6.8: Functional block diagram of the counter code                                                |

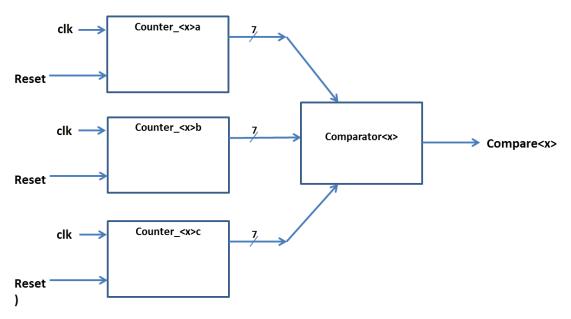

| Figure 6.9: Functional diagram of counters within a section and the comparator                          |

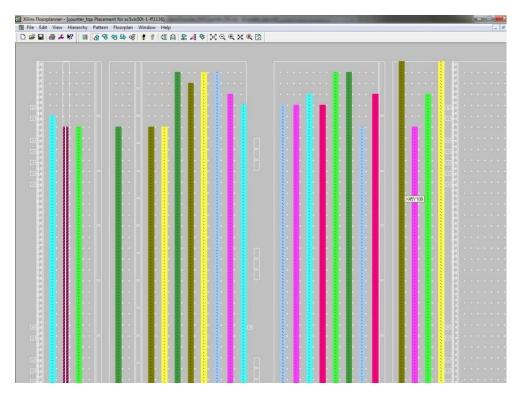

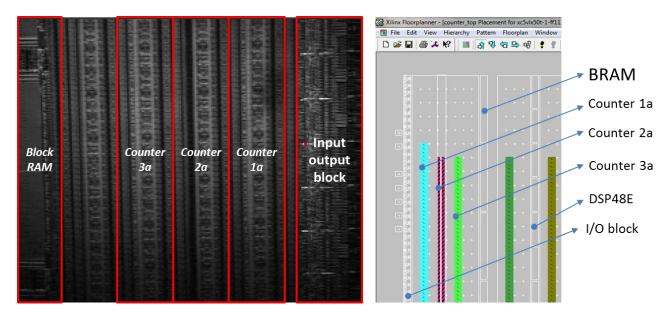

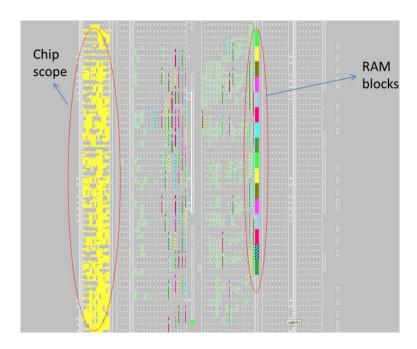

| Figure 6.10: Xilinx floor planner layout of 456 bit counter modules arranged in a column78              |

| Figure 6.11: Laser micrograph showing counter 1a, 2a & 3a located in between the I/O logic and          |

| BRAM (768 x 768 µm) (right) shows the corresponding blocks in the Xilinx floor planner78                |

| Figure 6.12: Functional block diagram of DSP48E Macro80                                                 |

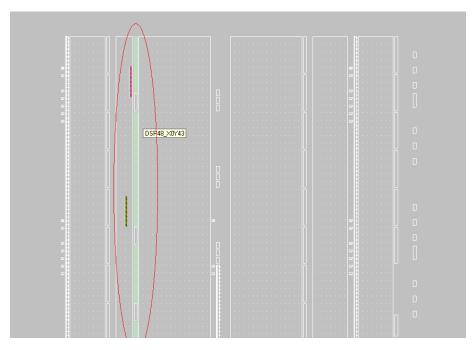

| Figure 6.13: DSP48 VHDL code floor plan showing the DSP column (colored blocks) in the                  |

| Virtex-5 FPGA81                                                                                         |

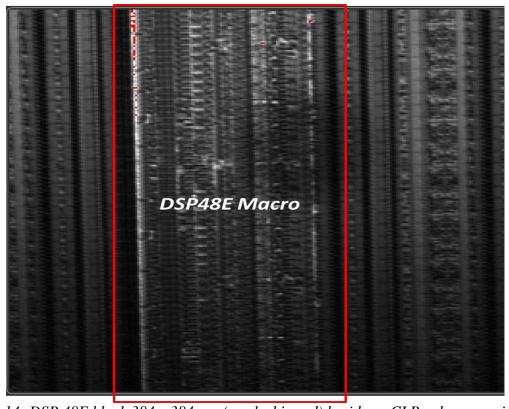

| Figure 6.14: DSP 48E block 384 x 384 μm (marked in red) besides a CLB column on right81                 |

| Figure 6.15. Laser micrograph of DSP48 (96 x 96 $\mu$ m) (left) and 48 x 48 $\mu$ m (right) scan area82 |

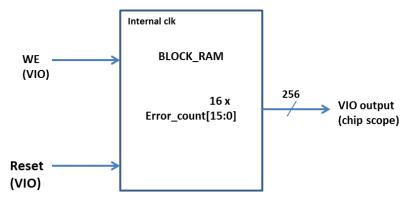

| Figure 6.16: Functional block diagram of Block RAM                                                      |

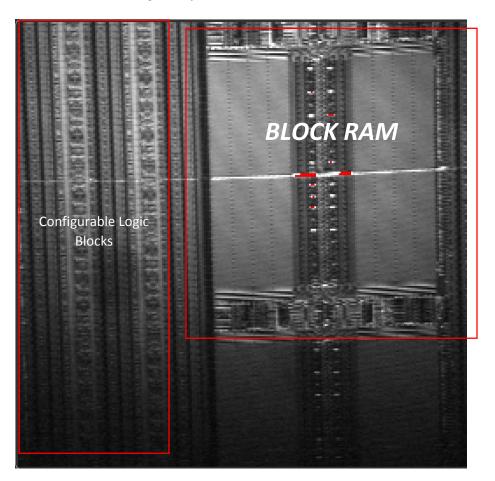

| Figure 6.17: Laser micrograph of BRAM (768 x 768 µm)84                                                  |

| Figure 6.18: Floor plan of BRAM test code in Virtex-5 FPGA                                              |

| Figure 6.19: Laser testing on 384 x 384 µm BRAM cell85                                                  |

# **LIST OF TABLES**

| Table 2.1: LET threshold energy needed to induce a single event upset on an SRAM cell for |              |

|-------------------------------------------------------------------------------------------|--------------|

| various strike scenarios                                                                  | 13           |

| Table 3.1: Critical charge comparison of 6T and 12T cell.                                 | 33           |

| Table 3.2: SNM characteristics of 6T and the proposed 12T cell                            | 39           |

| Table 5.1: LET threshold for radiation strikes at different locations for various PMC     | OS / NMOS    |

| ratio                                                                                     | 57           |

| Table 6.1: Number of configuration bit errors vs laser pulse energy (pJ)                  | 68           |

| Table 6.2: Configuration bit errors with laser exposure time for different laser pulse    | energies at  |

| 384 x 384um scan area.                                                                    | 69           |

| Table 6.3: Configuration bit errors with laser exposure time for different laser pulse    | energies at  |

| 96 x 96 μm scan area                                                                      | 71           |

| Table 6.4: Configuration bit errors with laser exposure time for different laser pulse    | energies at  |

| 48 x 48 μm scan area                                                                      | 72           |

| Table 6.5: Counter error output for different laser pulse energies                        | 79           |

| Table 6.6: DSP48E upset vs laser exposure time for different scan area sizes and las      | ser energy82 |

| Table 6.7: BRAM Bit errors vs energy of the pulse                                         | 85           |

| Table 6.8: Threshold upset energy for various functional blocks of the FPGA               | 86           |

# **ABBREVIATION**

ASIC - Application Specific Integrated Circuit

BRAM - Block RAM

CLB - Configurable Logic Block

CMOS - Complementary Metal Oxide Semiconductor

DICE - Dual Interlocked Storage Cell

DRAM - Dynamic Random Access Memory

DRC - Design Rule Check

DSP - Digital Signal Processing

**DUT** - Device under Test

FPGA - Field Programmable Gate Array

FF - Flip Flop

GDSII - Graphic Database System 2 format

GUI - Graphical User Interface

H\_SNM - Hold Noise Margin

IC - Integrated Circuit

IR - Infra Red

ITRS - International Technology Roadmap for Semiconductors

JTAG - Joint Test Access Group

LEAP - Layout Error Aware Position of transistors

LED - Light Emitting Diode

LET - Linear Energy Transfer

LSB - Least Significant Bit

LVS - Layout versus Schematic

MBU - Multi Bit Upset

MeV - Mega Electron Volt

MSB - Most Significant Bit

NMOS - N type Metal Oxide Semiconductor

**OPA - Optical Parametric Amplifiers**

OTP - One Time Programmable

PBE - Parasitic Bipolar Amplification Effect

PMOS - P type Metal Oxide Semiconductor

RCI - Robust Chip Inc

RHBD - Radiation Hardening By Design

RTL - Register Transfer Level

R\_SNM- Read Noise Margin

SBU - Single Bit Upset

SEU - Single Event Upset

**SET- Single Event Transient**

SEE - Single Event Effect

SEFI - Single Event Functional Interrupt

SEMU - Single Event Multiple-node Upset

SOC - System on Chip

SOI - Silicon on Insulator

SPA - Single Photon Absorption

SPICE - Simulation Program with Integrated Circuit Emphasis

SNM - Signal to Noise Margin

SRAM - Static Random Access Memory

STI - Shallow Trench Isolation

TCAD - Technology Computer Aided Design

TPA - Two Photon Absorption

VHDL - Very High Speed Hardware Description Language

VIO - Virtual Input Output

VLSI - Very Large Scale Integration

W\_SNM - Write Noise Margin

# CHAPTER 1

### **INTRODUCTION**

### 1.1 Background

Today's commercial and wireless industries are demanding high performance, ultra-low power Application-Specific Integrated Circuits (ASIC) and System on Chips (SOCs) for implementing their future products. They are driving the integrated circuit (IC) industry to fabricate ICs with denser architectures capable of better performance. IC reliability capable for long-term operations is an important factor that decides the quality of the commercial products, and radiation tolerance plays a big role in it. Before the 1970's, the effects of radiation events on ICs were considered only in mission critical applications for space and military projects, where the reliability of the system was more important than area minimization and speed requirements, that are demanded by commercial applications. During the 1980's, several reports were published showing evidence of radiation strike effects on commercial VLSI circuits in terrestrial environment. The single event effects (SEE) on VLSI circuits in terrestrial environment were initially published by woods et al. in 1979 [35]. In his investigations, the effects of alpha particles in DRAM cells were considered, where the single event phenomenon was treated as a physical problem that corrupted the memory cell, rather than a statistical problem like noise. Hence the suggestion was to incorporate memory design related changes to deal with the problem rather than implementing noise reduction techniques [35]. Currently, the reliability issues due to radiation effects are considered to be larger than all of the other semiconductor reliability problems such as hot-carrier injection and electromigration [36].

Radiation effects on semiconductors are generally classified into two categories, hard errors and soft errors. Hard errors occur when high energy irradiation particles strike the material to change the chemical lattice configuration of the semiconductor material. This creates a permanent fault in the VLSI circuit which cannot be repaired. Hard errors occur commonly on VLSI chips used in space applications where radiation environments are harsh. Soft errors, on the other hand, are temporary errors which don't change the chemical configuration of the semiconductor material. Typical soft error effects involve ion particle - semiconductor interactions that result in charge deposition in the semiconductor material. Ideally, soft error upsets can be restored by resetting the power. The resetting process leads to draining away of the ion-deposited charge during the disconnection of power. The thesis focuses on soft errors and its mitigation.

Radiation events on digital systems can affect both combinatorial and sequential systems. However, the effect on sequential systems such as memories and flip flops are considered to be more severe since these errors are stored in the memory and hence persist for a longer period of time. Single event transients (SET) generated in the combinational circuits are considered hazardous only if they propagate into the storage circuits, resulting in the storage and propagation of error data.

#### 1.2 Motivation

Static Random Access Memories (SRAM) occupy a large portion of the total chip area in the modern processors and SOCs. According to the ITRS road map, it is predicted that the SRAMs

will occupy up to 80 % of the total area in SOC chips by 2014 [26]. However, SRAMs are often the most sensitive blocks to radiation strikes, where the ions can easily deposit charge on the storage node of these memory cells, corrupting the data stored in them. The errors then will be stored in the memory, unless they are identified and rewritten with the correct data. Hence upsets in memories are considered more critical than the ephemeral single event transients occurring in combinational circuits.

SRAM blocks are commonly used as cache memories in processors because of their high-speed performance compared to Dynamic Random Access Memories (DRAM). SRAMs have a direct impact on the processor performance and therefore its radiation tolerance should be considered with paramount importance. Other common applications of SRAMs are in the Field Programmable Gate Arrays (FPGA). The SRAM based FPGA's have significant performance improvement and re-configurability options compared to the one time programmable (OTP) FPGA's which are based on anti-fuse technology. However, from the reliability perspective, single event upset on SRAMs and their impact on the FPGA operations have to be considered.

The criticality of an SRAM upset is decided based on its effect on the FPGA functionality. A SRAM upset can result in various impacts on the FPGA performance, from negligible output variations, to critical disruption of FPGA functionality. Single Event Functional Interrupt (SEFI) in SRAM-based FPGA is a good example of the detrimental effects of the SRAM single event upset (SEU). SRAM configuration memories are the fundamental blocks that store the configuration and interconnection data of all the functional units within the FPGA. An SEFI configuration bit error has the potential to alter the functionality of the FPGA by corrupting the data stored in the memory, which can lead to the complete disruption of the functional block

associated with that configuration bit. Several studies have been conducted, to observe this phenomenon, by upsetting the FPGA with protons and heavy ion particles [30].

Soft errors on SRAM cells are generally classified into two types. There are single-bit upsets (SBU) and multi-bit upsets (MBU) depending on the number of bits upset due to the single-ion strike. The soft errors are also classified based on the number of nodes the single-ion hits to create an upset in an SRAM cell. There can be a single-ion single-node upset or a single-ion multi-node upset depending on the number of nodes hit in a single cell. Single-ion multi-node upset occurs when ions strike in grazing angles with respect to the IC's plane and is also called as single-event multi-node upset (SEMU).

The multi-bit upset rate in SRAM cells is increasing significantly compared to the single-bit upset rate [6]. Multi-bit upsets in memories depend on several factors such as the energy of the strike, circuit design, layout orientation and density of the cell. They also depend on the direction of the strike, where the number of bits affected by a single ion strike increase with the energy of the ion [29]. The percentage of multi-bit upsets to single-bit upsets was observed to be 1% for 65nm 6T SRAM in SOI technology [27] and 20% for 6T SRAM in 65nm bulk technology [28]. The MBU to SBU ratio has further increased during scaling from 65nm to 45nm [6]. In this study, it was shown that the double bit upsets, which increased during scaling, had a strong dependence on the layout of the cells.

There are 3 main approaches for mitigating soft errors in digital systems. They are

- a) System level approach,

- b) Circuit or layout level approach and,

- c) Device or manufacturing process level approach.

System level approach involves the introduction of error correction coding, bit interleaving [38-40] and triple module redundancy techniques into the SRAM array design. System level approaches can provide efficient mitigation on soft errors with minimum design changes, however the advantage comes at a price of large area overhead. Device and semiconductor level approaches involve mitigation by varying the structures and properties of the semiconductor devices. The cost could be huge since it involves changing the fabrication process. Circuit/ layout level approach uses circuit or layout techniques to mitigate single event effects, which is also called Radiation-Hardening-By-Design (RHBD). This technique involves introducing circuit/layout modifications such as redundancy to improve the SEU tolerance. RHBD techniques have been successful implemented in ASICs to mitigate soft errors [28]. Since RHBD approach does not involve in any process modifications, it has shown huge potential for mitigation of single and multi-bit upsets in SRAM designs without greatly sacrificing on performance or area [12, 28, 43].

#### 1.3 Research Focus & Objectives

The focus of the thesis is to explore the single event characteristics of conventional SRAM cell structures and understand the mechanisms involved in the single event upset. Currently, high-density memory architectures implemented in bulk CMOS technologies have resulted in an increase of MBU upsets [28]. The single-node upset issues have been alleviated to a certain extent by fabricating circuits in SOI process technologies; however, SRAMs fabricated with SOI technologies also exhibit an increase in multi-bit upset rates, with scaling, for grazing angle ion strikes. The primary question to ask here is: how to come up with a RHBD design/layout technique that can reduce the MBU upsets in conventional SRAM designs without severe performance or area penalty.

The central aim of the thesis is to answer this question by introducing a circuit / layout structure that can improve the multi-bit upset tolerance, specifically single-event multiple-node upset tolerance in conventional 6 Transistor (6T) SRAM cells. In order to evaluate the radiation tolerance, the proposed 12T SRAM cell is compared with conventional 6T cell design under several SEMU upset scenarios. A quantitative evaluation of the proposed 12T cell is performed to demonstrate the effectiveness of the achieved multi-bit upset mitigation.

SEU characteristics of SRAMs can be studied by evaluating SRAM based FPGAs, which can give insight into the SEU mechanisms involved during an upset. The radiation tolerance of the FPGA strongly depends on the SRAM blocks used to store the configuration data of the FPGA. Virtex-5 FPGA is an SRAM based FPGA which is used in a wide variety of commercial applications. The FPGA consist of SRAM based configuration memory blocks, which are spread all over the chip area, along with other dedicated functional blocks such as DSP48E, BRAMs etc. Therefore, it is an excellent platform that can help to understand the single event effect (SEE) characteristics of SRAM cells.

The main research objectives of the thesis are

- 1. Propose a new layout technique that provides better SEMU mitigation

- 2. Propose a new SRAM design that can utilize this layout technique

- 3. Understand and evaluate the SEU error cross section of SRAM based configuration memories in Virtex-5 FPGA by using a TPA laser.

### 1.4 Thesis Overview

The rest of the thesis is organized as follows. In Chapter 2, a background about SEE is provided along with the effects of SEE and SEMU and the techniques used to mitigate them in current CMOS SRAM technologies. The novel layout technique and the 12T SRAM cell are proposed, with the principle of operations explained in Chapter 3. Several SEMU radiation strike scenarios are discussed in details to explain the mechanisms involved in SEMU reduction during grazing angle strikes. Chapter 3 also consists of preliminary schematic level simulation results such as critical charge analysis and signal to noise analysis for evaluation of single event upset characteristics of the proposed cell and 6T cell. Chapter 4 discusses the 3D mixed mode simulation methodology and post processing techniques done using Accuro tools. Chapter 5 discusses the 3D mixed mode simulation results of 6T and the proposed 12T cell using Accuro [12]. The sensitivity map and error cross section curves are plotted to quantitatively compare the effects of radiation strikes in 3 major strike directions (X, Y and Z). Chapter 6 introduces laser testing methodology used for SEE evaluation of Virtex-5 FPGA, followed by the laser testing results of configuration memories in Xilinx Virtex-5 FPGA. Other functional blocks such as CLB blocks, DSP slices and BRAM's in the FPGA are also tested for SEE upsets. Chapter 7 gives the conclusion of the thesis and the future research work that can be done for improvement.

# Chapter 2

### **OVERVIEW**

### 2.1 Radiation Problems in Terrestrial Environment

During the past decades, radiation hardening research was mainly focused on space applications, where various techniques based on redundancy were implemented to mitigate single event effects in electronics [31]. But recently, commercial ICs in the terrestrial environment are also getting affected by radiation events due to low-energy neutrons from space and secondary alpha particle emissions [1]. Nuclear interaction of cosmic rays on boron phosphate silicate glass (BPSG) present in the packaging material demonstrates this effect of secondary emissions on commercial IC reliability. The low-energy neutrons present in the cosmic rays can hit the boron atom to produce secondary alpha particle emission that leads to the upset of SRAM cells [14].

There are 3 major types of radiation sources in the earth's terrestrial environment that can cause single event upsets in SRAM cells. They are a) alpha particles, b) high energy cosmic rays, c) low energy cosmic rays. Alpha particles consist of a helium ion with 2 neutrons and two protons. It is very difficult for an alpha particle to directly strike the silicon from outside the chip because of their rapid loss in energy while propagating through the material [1]. Radiation strike energy is measured in terms of energy lost per unit length in the material called Linear Energy Transfer (LET, MeV-cm²/mg). A typical 10 MeV-cm²/mg alpha particle can propagate only 100 µm in

the silicon material before its energy is lost [1]. Therefore, external alpha radiations don't pose a serious threat to ICs. However the secondary alpha emissions from impurities present in packaging material and device material within the chip, pose a serious threat due to its proximity towards the diffusion regions of the SRAM circuit. The most common source of alpha particles is from <sup>238</sup>U, <sup>235</sup>U, <sup>232</sup>Th impurities present inside the chip. In order to mitigate the secondary generation of alpha particle radiations within the chip, manufacturers are using techniques that remove the impurities during the fabrication process. Additionally, design techniques are also incorporated to spatially separate the potential alpha radiation sources from the sensitive nodes of the circuits.

High energy cosmic rays are the second source of irradiation particles in terrestrial environment. These radiation particles react with the earth's atmosphere to create secondary and tertiary radiations. The secondary radiation particles created include muons, protons and neutrons, from which neutrons are the particles with the highest flux and LET energy. Neutrons have more potential to cause MBU and SEMU radiation upset compared to alpha radiation strikes due to its ability to propagate greater distances without energy loss. They are also capable of depositing higher charge per unit length compared to alpha particles [14]. Unlike alpha particle mitigation approaches, neutron radiation effects cannot be mitigated by removing impurities in packaging materials because of its direct charge deposition nature in the silicon [37]. Hence new RHBD based SRAM cells has to be proposed to address this issue.

Finally the 3<sup>rd</sup> significant source of radiation is the low energy cosmic rays consisting of neutrons (< 1 MeV-cm<sup>2</sup>/mg). BPSG material used in packaging of ICs reacts with the cosmic rays to introduce potential single event particles [1]. The nuclear reaction process involves the generation of secondary particles such as alpha and Li recoil that deposit charge on the semiconductor devices creating upsets. This problem is mitigated to a certain extent by using packaging dielectric

materials without BPSG in it. Introduction of the new packaging material has significantly improved the single event reliability of the ICs fabricated by current advanced manufacturing processes.

### 2.2 Effects of Scaling on SRAM Radiation Tolerance

The old era CMOS technologies used for commercial IC fabrications were inherently robust to radiations events because of their larger diffusion node sizes. The dimensions of the diffusion nodes were relatively large so that radiation strikes couldn't accumulate enough charge to upset the cells. But with dimension scaling, the charge used by the circuit to hold its data has shrunk to an extent that even a low energy ion strike can induce sufficient charge in the circuit to corrupt the data stored in the SRAM cell. Moore's law trend in VLSI scaling is the main factors for this degradation in radiation tolerance. According to Moore's law, the number of transistors doubles every 18 months. This trend has led to a rapid reduction in circuit dimensions, but at the same time has led to a drastic reduction in single event tolerance of the SRAM cell. The implications of this trend are as follows:

- a) The circuit node size is reducing rapidly with each technology generation, leading to a reduction in the diffusion node capacitance of the transistor,

- b) The operating voltage of the transistor is decreased to reduce power consumption and maintain constant electric field scaling.

The effect of decrease in node capacitance and operating voltage with scaling has been well documented in the publication by Lloyd et al. [2]. The Figure 2.1 shows the decrease in capacitance and voltage of circuit nodes with technology scaling. The SRAM cell's ability to hold its data, while getting affected by radiation, is evaluated by measuring the critical charge of the affected

node. Critical charge is the minimum amount of charge injected at a circuit node before it triggers an upset [5]. This critical parameter of the node directly depends on the node capacitance and the operating voltage of the SRAM cell. Hence, the reduction in capacitance and operating voltage will reduce the critical charge and thereby decrease the single event tolerance of the CMOS SRAM circuit.

Figure 2.1: Decrease in normalized capacitance and operating voltage with technology scaling [2]

Secondly, scaling has resulted in the fabrication of high density VLSI architectures that has led to the decrease of spatial separation between nodes. This is an advantage for commercial ICs because it can hold more transistors in the same area, but from the radiation tolerance perspective, it has led to several reliability issues. When nodal spacing decreases, the ions have a wider solid angle window for potential single event multiple upset (SEMU) [2]. SEMU is an upset that occurs due to a single ion striking multiple-nodes in the SRAM cell. The effect is more common for ion particle strikes occurring at grazing angles with respect to the layout plane. SEMU phenomenon in SRAMs was demonstrated in a study by Hiedel et al. [6], where the cross sections of the 6T SRAM cell were compared for 2 different data storage patterns such as blanket and checkerboard patterns. In the blanket pattern, the location of the sensitive nodes were so close that a wide solid angle window between the NMOS nodes of the SRAM cell allowed for ions to strike multiple

sensitive nodes of the cell at grazing angles. The effect was significantly low in checker board pattern due to larger spatial separation of sensitive nodes. As the sensitive nodes get closer, the solid angle window for a potential SEMU gets widen. This rapidly increased the probability of an SEMU upset on the SRAM cells. The solid angle widening effect is demonstrated in the Figure 2.2.

Figure 2.2: Widening of solid angle when nodes get closer during technology scaling

SEMU strikes can upset a cell with less ion energy compared with a single-node strike. This phenomenon can be simulated using a 3D mixed mode simulation that couples the effects of the schematic and the layout of the VLSI circuits. Synopsis TCAD is the most commonly-used tool for mixed mode simulations, however, the computing time is extremely large in order to simulate circuit-level designs. Therefore the application of TCAD tools is often limited to transistor level simulations. Accuro tool by Robust Chip Incorporated [RCI] [12] is capable of simulating circuit level designs using less computational resources. The tool is also suitable for cross section evaluation and LET threshold prediction [4]. All the mixed mode simulation in this project was carried out with Accuro.

A 3D Accuro simulation of a standard 6T cell is performed to compare the effects of normal strike and an SEMU strike. Table 2.1 illustrates the LET threshold energies for different strike situations.

Table 2.1: LET threshold energy needed to induce a single event upset on an SRAM cell for various strike scenarios

| Strike Characteristics                    | LET                     |

|-------------------------------------------|-------------------------|

|                                           | Threshold               |

|                                           | MeV-cm <sup>2</sup> /mg |

| Strike on OFF NMOS Drain node             | 2.75                    |

|                                           |                         |

| Strike on OFF PMOS Drain node             | 4.75                    |

|                                           |                         |

| SEMU strike hitting both OFF NMOS and OFF | 0.6875                  |

| PMOS nodes                                |                         |

Figure 2.3a: Node voltage at PMOS Drain for SEMU strike for LET = 0.7 (red) and LET = 0.5 (dashed blue)

Figure 2.3b: Node voltage for a Normal NMOS strike for LET = 3 (pink) and LET = 2.5 (dashed blue).

From Table 2.1, Figure 2.3a and 2.3b, it is noted that the SEMU strike needs only ¼th the energy of a normal NMOS strike and 1/7<sup>th</sup> the energy of a PMOS strike to corrupt the data stored in the cell. Therefore SEMU's should be considered more problematic than a single event single-node upset. This single event vulnerability towards SEMU strikes will significantly deteriorate the overall radiation tolerance of the circuit. Therefore, novel circuit and layout techniques need to be introduced to improve SEMU radiation tolerance of SRAM cells.

### 2.3 Physics of Single Event Upsets in SRAM Cells

Charge deposition in semiconductor devices can occur due to direct ionization or ionization by secondary particles. During ionization, the ion passes though the semiconductor particle releasing electrons and holes, decreasing its energy during its travel path. The amount of energy lost per unit length is measured in terms of LET. This energy is normalized with respect to the density of the

material and so the LET energy measured can be considered independent of the semiconductor material. For silicon, LET of 97 MeV-cm<sup>2</sup>/mg corresponds to 1pC / μm [2].

Charge collection mechanism in semiconductors can be explained with an example of a radiation strike on the Drain of the OFF transistor. The reverse biased P/N junction formed by the Drain and substrate of the transistors is the location where the circuit is most sensitive to radiation. Under reverse-bias condition, the depletion region gets wider due to a higher electric field across the Drain-substrate junction, enabling the junction to collect more minority charge carriers from the surrounding areas.

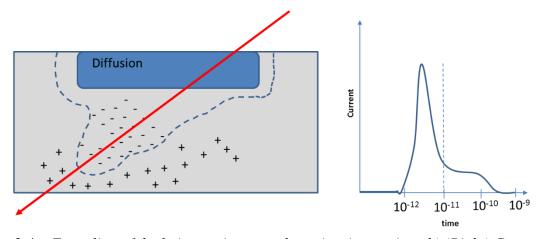

Figure 2.4a: Funneling of depletion region to gather minority carriers. b) (Right) Current at the Drain during a single event strike [1].

During a single event strike at the Drain node, the ion leaves a trail of electrons and holes along its strike path, forcing the depletion region to extend itself along the ion strike path in the shape of a funnel as shown in figure 2.4a (left). The funnel, then collects all of the deposited minority carriers in the substrate through drift mechanism, which results in the sharp increase of charge accumulation in the junction. After all the minority carriers are absorbed, the majority carriers diffuse into the depletion junction. This is a slow diffusion process resulting in the decrease in

charge at the junction as shown in waveform in Figure 2.4 (right). This is the basic physics of single event upsetting in semiconductor circuits. These concepts can be used to explain the single event upset process of 6T SRAM cells.

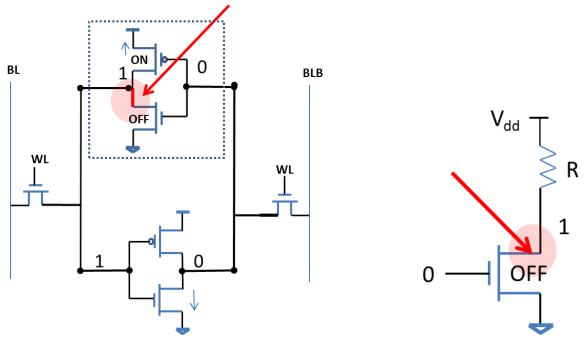

Figure 2.5: a) Radiation strike on a 6T SRAM cell Drain node(red) b) Equivalent inverter circuit with PMOS transistor replace by an equivalent resistance.

Consider the inverter part of a 6T SRAM cell as shown in Figure 2.5a, one of the transistors (NMOS) will be OFF and the complementary transistor (PMOS) will be ON. When the ion strikes the OFF transistor Drain node (NMOS), charge builds up at the depletion junction of the Drain region. This will force the ON complementary transistor (PMOS) to function as a restoring transistor by supplying a transient current to compensate for the charge build up at the Drain junction. The transient current flow results in a voltage drop across the restoring transistor because of its fixed trans-conductance across the source Drain path. The equivalent circuit of the inverter with the PMOS replaced by a fixed trans-conductance is as shown in Figure 2.5b. This voltage drop at the output of the inverter is the source for the single event upset. If the pulse width is long enough, the SET pulse generated propagates to the input of the other inverter and changes its

output. If the SRAM cell is not able to recover itself from this single event upset before the SRAM feedback time, the data gets latched and the SRAM cell gets corrupted.

### 2.4 Laser Fault Injection Techniques for SEU Tolerance Evaluation

Several methods are available to experimentally evaluate single event tolerance of SRAM cells. The common techniques involves accelerated heavy ions and protons/nuetrons testing using particle irradiation facilities. However, the access to test facilities needed for the SEU tolerance evaluations are expensive and difficult to obtain. Pulsed lasers offer an easy and convenient solution for evaluating SEEs in SRAM cells.

Based on the carrier excitation technique in the semiconductor material, pulsed lasers can be classified into single photon absorption and two photon absorption lasers. The classification is based on the number of photons used by the atoms in the material to reach its excited state. Single photon absorption (SPA) technique uses a single photon to create an electron-hole pair, but it has a major drawback. The laser must have a wavelength above the band gap energy of the semiconductor material (less than 1100nm). This results in a short penetration depth for SPA lasers because of the exponential loss of laser power while propagating through the silicon material. Therefore SPA lasers cannot be used to deposit charge deep in the substrate for single event studies. Two photon absorption (TPA) lasers eliminate this problem by using larger wavelength, at sub band gap energies deep into the material. The technique is based on simultaneous absorption of two photons to generate a single electron-hole pair in the incident region. TPA generates photons at high peak power within a duration of femtoseconds. The individual photons do not incur losses during its propagation through the material because its energy is in the sub band gap region. The collision of these photons results in the electron-hole pair generation at the location where the two

photons are focused. This enables the TPA laser to upset localized regions within the semiconductor material. This can be considered as a huge advantage because it allows to introduce charge through the back side of the IC (silicon side), thereby eliminating metal obstruction problems faced during IC front side testing.

### 2.5 Existing 6T cell layout designs

Layout for 6T SRAM cells has to be suitable for high density fabrication. The traditional 6T SRAM cells is as shown in Figure 2.6a. The layout is commonly used in fabrication of 6T SRAM designs in 130 and 90 nm technology. The layout design is mirrored and overlapped to create the larger 6T memory array. The main disadvantage of the traditional SRAM layout is that its lithographic unfriendly nature for SRAM fabrication below 90nm [24]. The bends in the diffusion and polysilicon limits the layout fabrication of this design below 90nm.

The thin cell was introduced to combat these disadvantages. As shown in Figure 2.6b, the layout limits the use of polysilicon only in the horizontal direction and the diffusion in the vertical direction without any bends. The layout also removes diffusion bends, which makes them more layout friendly for advanced fabrication technologies below 90nm.

Figure 2.6 a) Traditional 6T SRAM cell b) Thin cell layout of 6T cell

### 2.6 Current Layout Techniques for SEMU / MBU Mitigation & their Limitation

SEMU events may be triggered by 2 mechanisms. The direct mechanism is a single ion directly hitting multiple sensitive nodes of the SRAM cell. This kind of SEMU upsets depends highly on the angle of the strike and the proximity of the strike to the sensitive node. An indirect mechanism of an SEMU upset involves an ion hitting a sensitive node and depositing enough charge on the substrate so that the sensitive node nearby shares this deposited charge from the strike node or the substrate. Studies regarding the effects of directional radiation strike on charge sharing demonstrate this mechanism for different CMOS technologies [18-20].

Several circuit / layout level techniques have been proposed to mitigate SEMU and MBU effects, such as increasing the separation of critical nodes to 5um [11], introducing redundancy in nodes [12], increasing the number of well contacts to avoids well collapse source injection[15]. This will be further explained in the next section. But all these spatial separation and redundancy techniques are susceptible to failures with device scaling. As per the investigation conducted by Bhuva et.al [16], the Dual Interlocked Storage cell (DICE) flip flop loses its radiation tolerance capabilities drastically with scaling. The DICE design shows 100 times better single event tolerance compared to regular D Flip flops in 65nm. However at 40 nm, this improvement has been reduced to 5X [16]. All the redundancy techniques depend on keeping the affected nodes as far away as possible from the sensitive node, but with device scaling these nodes get closer and charge sharing effect would trigger multi bit upsets [9]. Currently, the following circuit / layout level techniques are used to reduce SEMU effects

### 2.6.1 Placing Bit-lines between Sensitive Nodes

Bit-lines are used to store and retrieve data from the memory cells. The diffusion nodes of the bit-lines can be strategically placed between sensitive nodes to isolate them, thereby reducing the spreading and collection of charge across nodes. Daniele et al. [10] carried out an investigation on multi bit upset patterns formed in a 150nm SRAM array. It has been seen that the upset pattern signatures on the SRAM chip are more horizontal in nature than vertical (5:1 distribution). The reason provided for this distribution was that the charge collection and sharing between nodes in the horizontal direction was much easier because of the minimum distance between sensitive nodes. However, it was difficult to collect charge and share them vertically across nodes because of the presence of bit-line contacts in between them. Hence the placement of bit-lines between sensitive nodes may aid in reducing the charge sharing effect across sensitive nodes thereby reducing SEMU upsets.

### 2.6.2 Well / Substrate Tapping Scheme

Well and substrate taps play an important role in multi-bit-upsetting mechanism. For CMOS technologies, an ion strike can deposit charge in the well or substrate to locally collapse the body potential of the transistor [9]. This results in the upsetting of the Drain nodes of the transistors sharing the same substrate. Taps helps maintain the well / substrate potential by giving a good ohmic contact to the power supply and ground. Closer well and substrate tap contacts can help in maintaining the substrate potential by draining away the deposited charge in the well and substrate.

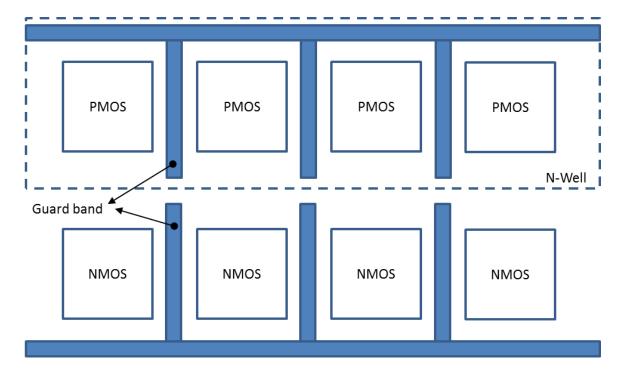

### 2.6.3 Placing Guard Bands

Placing guard bands between nodes reduce charge collection for low LET strikes, resulting in lowering of multi-bit charge accumulation [16]. Guard bands use the same diffusion material as

their well / substrate taps. Black et al. has investigated the effects of placing guard between PMOS devices and NMOS devices as shown in Figure 2.7 [16].

Figure 2.7: PMOS and NMOS devices separated by guard bands [16]

For direct Drain node hits, addition of guard band between PMOS transistors has reduced the charge collected to ½ the value compared to the designs without guard band [16]. For non-direct hits, guard bands offer even better isolation between Drain nodes by preventing spreading of charge through the N-well. However, this technique doesn't offer significant isolation for NMOS devices. This is due to the difference in charge collection mechanism of PMOS and NMOS transistors. Charge collection in PMOS transistors occurs mainly due to parasitic bipolar amplification effect (PBE). In this mechanism, the ion strike deposits charge in the well to drop the local well potential, resulting in switching ON of a parasitic transistor that injects current into the PMOS node [9]. Guard contacts prevent the parasitic transistors of PMOS from turning ON by maintaining the N-well potential. However, charge collection in NMOS transistors is due to charge

diffusion through the substrate and guard bands do not have significant effect on it. Another main drawback of this technique is the area penalty associated with the addition of guard bands between transistor nodes. Also, guard bands do not offer significant reduction of multiple-node charge collection at higher LETs.

### 2.6.4 Guard Diodes

Guard diodes provide isolation by reducing charge sharing in a way similar to guard bands, but the mechanism involved is different. Guard diodes have the same diffusion material type as the transistors they are guarding. They provide additional reverse biased junctions between nodes, which siphons away the deposited charge so that the amount of charge spread to the adjacent node will be reduced [18]. Guard diodes provide effective reduction in multi node charge sharing for NMOS devices but, the technique also suffers the same area overhead draw back faced by guard bands.

### 2.6.5 <u>LEAP (Layout Error Aware Positioning of Transistors)</u>

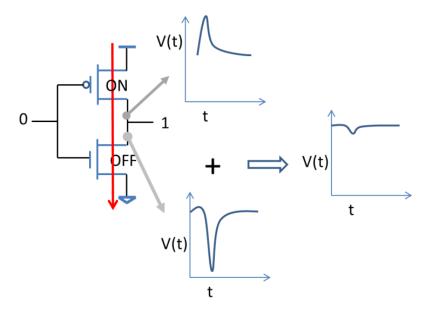

LEAP is by far the most effective technique used for SEMU mitigation. LEAP was proposed by Lee et al. in 2010[4]. The effectiveness of the technique was demonstrated using LEAP based DICE cells which showed an improvement of up to 5X times compared to the regular DICE cells. The basic principle of the LEAP is to carefully position the NMOS and PMOS transistors in a way as to cancel out the effects of the charge deposition during multi-node strikes. Considering an example of an inverter circuit, during single event strikes at the Drain node of the NMOS transistor, a current is injected into the node, which creates a voltage drop across the PMOS transisitor, resulting in a negative voltage transient. Similarly, a current is generated out of the PMOS transistor Drain during an ion strike, which creates a voltage drop across NMOS transistor,

resulting in a positive transients in Drain node [2]. The OFF transistors Drain nodes are more sensitive to radiation strikes compared to the ON transistor, and hence they create larger transient spikes during upsets.

For an inverter circuit as shown in Figure 2.8, the PMOS and NMOS transistors Drain nodes are electrically connected together. A simultaneous strike on both these nodes will result in generation of a voltage transient of opposing nature. The right sizing of NMOS and PMOS transistor can optimally cancel out the transients generated. The same concept can be extended to a latch design which consists of 2 inverters connected back to back. In the latch layout, the inverters are arranged along a line so that a grazing angle strike hitting all four transistor nodes of the latch will result in cancellation of the charge developed.

Figure 2.8: Charge cancellation in an inverter based on LEAP technique [4]

For optimum charge cancellation, NMOS and PMOS width should be sized to a particular ratio to achieve optimal effect. This ratio depends on the mobility of the charge carriers in PMOS and

NMOS transistors, which in turn are dependant on the CMOS manufacturing technology and semiconductor doping used.

Despite these advantages, LEAP technique has not been implemented for SRAM designs yet. 6T SRAM cells show high vulnerability to radiation strikes in grazing angles and LEAP technique would be an excellent tool to improve its SEMU Tolerance. The conventional 6T SRAM design is not suitable for implementation with LEAP because of its un-symmetrical layout across the horizontal axis of the layout plane. Hence a new layout of the 6T SRAM cell has to be proposed that can utilize the advantages of the LEAP technique. Additionally, the access transistors has to be considered while applying LEAP technique to SRAM design, since OFF access transistors can inject single event transients into the circuit during SEMU events.

Another factor to consider is the effect of the LEAP technique for CMOS technologies below 180nm. As the technology scales down, the PMOS to NMOS ratio needs to be changed due to the variation in mobility parameters of transistors. The PMOS / NMOS sizing ratio for the 130nm technology has to be investigated to completely utilize the potential of the LEAP technique in advanced CMOS technologies.

The main objective of the thesis is to introduce a novel layout technique that reduces the effects of SEMU in conventional 6T SRAM cells. The layout technique developed in 130nm technology, utilizes the advantages of the LEAP, strategic bit-line placement and guard contact placements to improve SEMU tolerance without introducing additional area penalty to the design. The effectiveness of the layout technique is demonstrated by proposing the 12T SRAM cell and comparing it with its 6T cell counterpart having the same diffusion and total layout area.

## CHAPTER 3

## PROPOSED LAYOUT TECHNIQUE AND SRAM DESIGN

Radiation tolerance of a 6T SRAM cell for a particular fabrication process depends on both the size of the diffusion area and charge collection efficiency. Generally as the width of the NMOS and PMOS transistors increases, the node capacitance of the transistor also increases, improving the single event transient (SET) tolerances. An alternative approach is to introduce redundancy of storage nodes with isolation in between them. Paralleling 6T cells is an effective technique for mitigating SEMU. The technique provides redundancy, introducing spatially separated transistors driving the same electrical node. Hence during an ion strike, only one of the transistor would likely get upset while the other remains safe, which will improve the single-node upset tolerance of the SRAM cell [1]. Additionally, the Drain nodes of the NMOS and PMOS transistors of the redundant chain can then be arranged on the layout in a particular way so that the charge accumulation at multiple-nodes created during an ion strike can partially or fully cancel out, provided the affected NMOS and PMOS Drain nodes are electrically connected to the same node. Finally, bit-lines can be effectively used for isolation of identical transistor nodes. The layout technique works on reducing the SEMU tolerance of designs that are symmetrical across horizontal and vertical axis of the layout plane. The proposed 12T cell was developed from conventional 6T cell based on this objective in mind. The technique greatly improves the SEMU tolerance of the 6T SRAM cell designs.

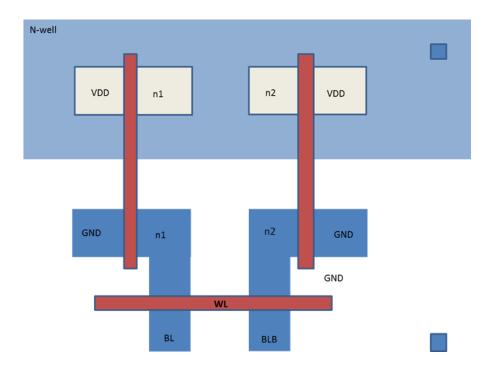

### 3.1 Proposed 12T SRAM Design

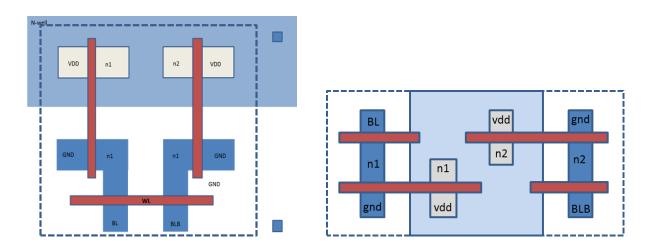

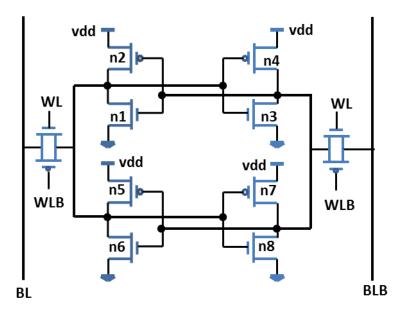

The 12T cell was derived from the standard 6T cell by splitting each transistor into 2 and spatially separating them in an interleaved fashion. During the layout translation, the total diffusion area and overall layout area of 12T cell is maintained the same as 6T cell for the purpose of fair comparison. The area overhead introduced by the transistor duplication process is overcome in the layout by sharing the diffusion nodes of identical transistors. The NMOS access transistors of the 6T cell are split into 2 complementary transistors which helps cancel out the transients generated during SEMU at the source. The NMOS and PMOS nodes in the layout are aligned in a particular order so that SEMU strike from vertical and horizontal directions along the layout plane, will lead to charge cancellation at the interconnected node. This greatly improves the SEMU tolerance of the 12T SRAM cell. The proposed 12 T cell is shown in Figure 3.1.

Figure 3.1: The schematic diagram of the proposed 12T cell

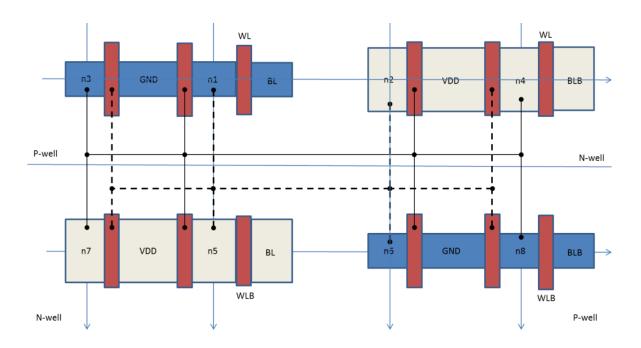

Additional layout technique was employed in such a way that bit-line (BL/BLB), power (vdd) and ground (gnd) diffusion nodes are placed in between the storage nodes. Figure 2.2 shows the layout of the 12T SRAM cell design. Here, the bit-line diffusion nodes can act as guard diodes [18] that

isolates the sensitive nodes from each other by minimizing the charge sharing effect between nodes having the same type of diffusion. Additionally, the interleaving method allows the transistors to be placed closer together.

The main layout based features of the proposed 12T cell is as follows.

- a) The diffusion nodes of the same type are spatially separated. This improves the single-node upset tolerance by offering a dual redundancy way of protection, where if an ion passes through one node, it only deposits charge on that node, the other node is kept isolated from the affected area.

- b) The NMOS and PMOS transistors are arranged such that SEMU strikes along the horizontal and vertical directions lead to charge cancellation at the nodes where they are electrically connected.

- c) Placement of bit-line contacts between diffusion nodes tends to act as an isolation band between adjacent nodes.

The charge accumulation and compensation of Drain nodes depend on the NMOS and PMOS Drain width and angle of incidence of the ion beam. Proper sizing of drain width is needed for equal amount of charge collection and cancellation at NMOS and PMOS Drain nodes.

## 3.2 Proposed Layout

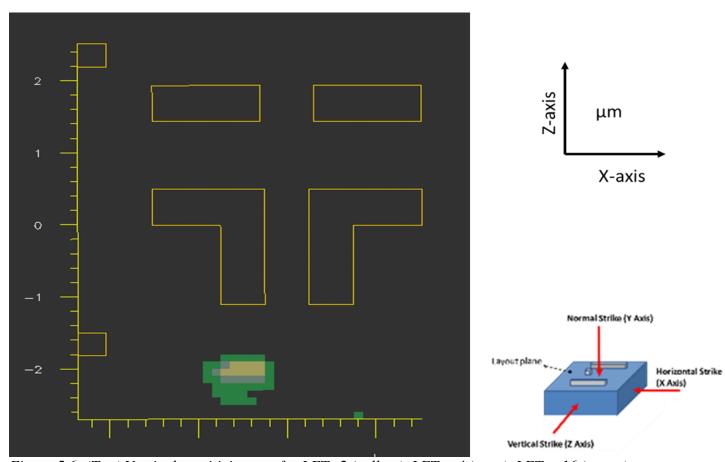

Figure 3.2 Layout of the proposed 12T SRAM cell

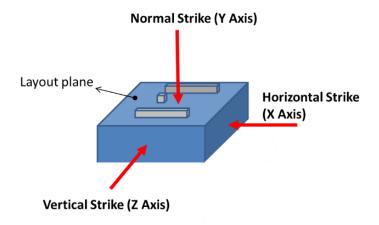

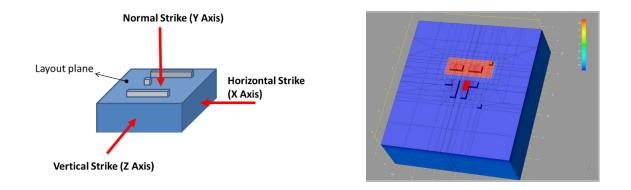

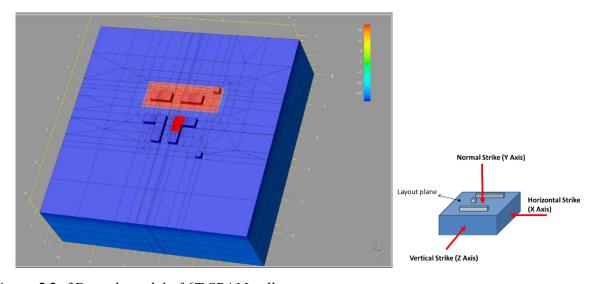

In order to explain the effectiveness of the layout in SEMU reduction, 2 major strike scenarios are illustrated as follows. SEMU strikes are considered in both vertical and horizontal direction along the layout plane. The conventions used for directional radiation strikes are as shown in Figure 3.3.

Figure 3.3: Illustration of 3 major radiation strike directions

#### 3.3 Mitigation Mechanism for SEMU Events

- a) Horizontal strike (0 deg elevation, 0 deg azimuth): Consider that the 12T SRAM cell is in state 0. This makes the nodes (n1, n2, n5, n6) connected to zero and the nodes (n3, n4, n7, n8) connected to 1. Under this condition, the sensitive nodes are the drain nodes of the OFF transistors which are n2, n6, n3, n7. During horizontal ion strikes along the layout plane, Nodes (n3, n1, n2, n4) or (n7, n6, n5, n8) are mostly affected. Considering top part of the layout in Figure 2.2, nodes n3 and n1 of NMOS, develops a negative voltage transient, which is compensated by the positive voltage built up at n4 and n2 of the PMOS transistors. In addition, striking n3 and n1 NMOS transistors (where n3 is high and n1 is low) will result in a generation of negative voltage transient at both Drain nodes. However, the generation of negative voltage at the non-sensitive Drain node (n1) will provide more negative bias voltage to the gate of the OFF sensitive NMOS transistor (n3 transistor), thereby preventing the sensitive transistor from flipping ON. Another way to induce an SEMU upset in the cell is to simultaneously hit nodes (n3, n2) or (n1, n4), but due to the geometry of the layout, n3 and n2 nodes can't be upset selectively without upsetting n2 and n4. This simultaneous hit of all 4 nodes also result in charge cancellation.

- b) Vertical Strike (0 deg elevation, 90 deg azimuth): During vertical strikes, the following pairs of nodes are affected (n3, n7), (n6, n1), (n2, n5), (n4, n8). These are the Drain nodes of PMOS and NMOS transistors in the inverters. When an ion strikes these nodes, the PMOS transistor creates a positive voltage transient and the NMOS transistor creates a negative voltage transient. The charge developed is cancelled out because they are electrically connected to the same node.

## 3.4 Schematic Design and Simulations

## 3.4.1 Cadence Simulation & Virtuoso: Brief Description

Cadence simulations were performed in 130nm IBM technology. 2 different schematic simulations are performed, as a preliminary step, in evaluation of radiation tolerance. They are a) critical charge analysis b) signal to noise margins (SNM) analysis. Cadence composer and analog design environment are used for schematic design and testing of the schematic circuit designs. After the functional testing of the SRAM cell, the layouts are done using Virtuoso. Design rule check (DRC) and layout versus schematic (LVS) checks are done to make sure that the schematic and layout are equivalent and they obey all the layout design rules.

## 3.4.2 **SRAM Design**

### 6T cell Transistor sizing

PMOS pull up transistor W/L = 630nm / 130nm

Access transistor W/L = 630nm / 130nm

NMOS pull down transistor W/L = 630 nm / 130 nm

#### 12 Cell Transistor sizing

PMOS pull up transistor W/L = 630 nm / 130 nm

NMOS pull down transistor W/L = 390nm / 130nm

Access transistor PMOS (W/L) = 630nm / 130nm

Access transistor NMOS (W/L) = 390nm /130nm

PMOS to NMOS ratio is chosen to be 1.6 for optimum charge cancellation during SEMU strikes.

This ratio depends on the fabrication technology used and it can be found through a 3D mixed

mode simulation of the 12T cell layout. The ratio (1.6) was obtained from Accuro simulations

done on 12T SRAM cell mesh model (Detailed explanations later). For 12T cell design, the width of the NMOS transistors are found first. The width of NMOS transistor is chosen as half the 6T cell NMOS transistor width. SEMU radiation strikes are then performed for different PMOS widths and the radiation characteristics are studied to find the optimum PMOS width.

## 3.4.3 Critical Charge Analysis

Critical charge is defined as the minimum amount of charge collected at a sensitive node that can cause the SRAM cell to upset. Critical charge at a node gives us an approximate idea about the radiation tolerance of the SRAM Cell. Upset occurs when the SRAM cells upset recovery time exceeds its feedback time [2]. The significant amount of charge deposited that results in the SRAM upset can be given as

Qsig =

$$\int_0^T Id(t).dt.....[2]$$

Where Id = drain current

T = Tf, feedback time if cell upsets

Tr recovery time if the cell doesn't upset

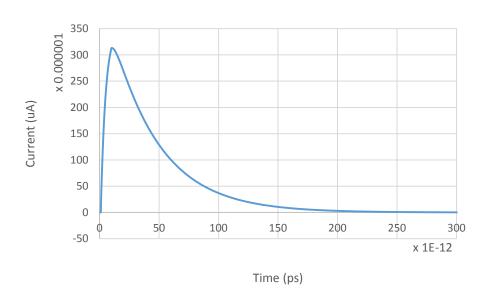

Figure 3.4: The current pulse waveform used for upset

Critical charge of a circuit is evaluated by injecting a current pulse into the sensitive node of the

SRAM cell design. In the simulations, a current source with the double exponential characteristics,

as shown in figure 3.4, is used to simulate a 1 to 0 and a 0 to 1 upset. The critical charge at the

sensitive node is evaluated for both 6T and 12T SRAM cell

Pulse Characteristics

Rise time: 10ps

Fall time: 200ps

Pulse shape: double exponential

First, the sensitive node is identified and a current pulse is injected into this node. The magnitude

of the pulse is initially set to a low value (10 uA) so that it would not upset the cell. The current

magnitude is then gradually increased until the cell flips. The threshold current when the cell flips

is identified and the current pulse is integrated to get the critical charge associated with the node.

For 1 to 0 upset, the current source is connected between ground and the sensitive Drain node as

shown in Figure 4.2. For 0 to 1 upset, the current source is connected between power supply (Vdd)

and the sensitive Drain node [8]. After getting the upset transient waveforms for the cell flip, the

current pulse is integrated from 0 to T, where T is the time at which the cell output flips (50ps).

The time instant when the voltage at the sensitive node cross 50% of the power supply voltage is

considered as the cell flip event. This is done to measure the actual charge that resulted in the

single event upset rather than integrating the total charge collected at the node.

However, the schematic simulations is only a preliminary analysis, which gives an approximation

of the SEU characteristics of the SRAM cell for an ion strikes directly on a single-node. The actual

semiconductor effects of an ion strike, like charge sharing and well collapse, play a significant role

32

in the cell upsetting process. In order to understand these single event effects, A TCAD or Accuro simulation has to be performed.

6t cell Critical charge analysis: Test results

Critical charge (1-> 0) analyses: 6.89fC (225.7uA, 0 to 50ps. The SRAM is in hold condition)

Critical charge (0->1) analysis: 12.7fC (420.3uA, 0 to 50ps. The SRAM is in hold condition)

Proposed 12 T cell Critical Charge analysis: Test results

Critical charge (1-> 0) analyses: 12.3fC (406.7uA, 0 to 50ps. The SRAM is in hold condition)

Critical charge (0 -> 1) analysis: 17fC (563uA, 0 to 50ps. The SRAM is in hold condition)

Summary of critical charge analysis of SRAM cells

*Table 3.1: Critical charge comparison of 6T and 12T cell.*

| Parameter         | 6T cell | Proposed 12T cell |  |  |

|-------------------|---------|-------------------|--|--|

| Single-node upset |         |                   |  |  |

| 1-> 0 upset       | 6.89 fC | 12.3 fC           |  |  |

| 0 ->1 upset       | 12.7 fC | 17 fC             |  |  |

From the schematic simulations we can observe that the 12T cell structure has got 5fC more critical node charge compared to 6t cell for both 0->1 and 1->0 upsets, even though the cell areas are the same (area calculations explained in chapter 6). This improvement in critical charge can increase the single-node radiation tolerance of 12T cell design compared to its 6T cell counterpart.

### 3.4.4 SNM Analysis

SEU sensitivity depends on the size and stability of the SRAM cell. The SRAM cell stability is decided based on signal to noise margins (SNM) of the SRAM cell. Better SNM margins for the cell will improve the stability of the cell during data storing and write/read operations, which will automatically improve the radiation tolerance of the cell.

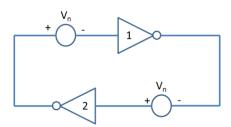

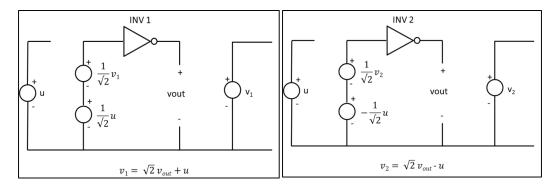

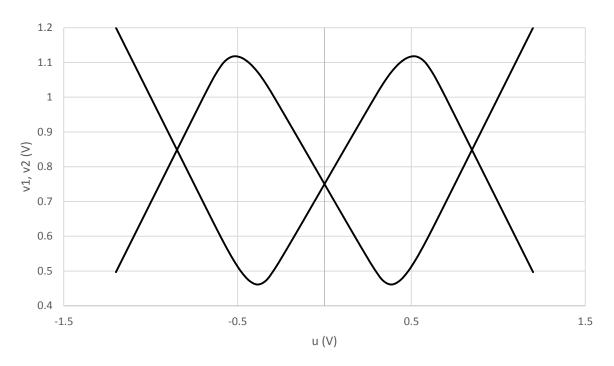

Figure 3.5: Block diagram for test setup for SNM noise margin analysis

As shown in Figure 3.5, an SRAM cell consist of inverter cells connected back to back in a loop to form a latch. For SNM analysis, an additional static noise source is inserted between the inverters. The static noise voltage of the noise source is then varied until the SRAM functionality is disrupted. The maximum noise voltage the cell can withstand without data corruption corresponds to its SNM margin. For SRAM cells, the SNM margin is evaluated for 3 different states of SRAM operation. They are

- a) Hold state: The SRAM cell is in hold mode when data is not read / written into it. In this mode, the access transistors are switched OFF. The bit-lines are disconnected from the SRAM cell using the access transistor.

- b) Read state: In this mode of operation, both bit-lines (BL and BLB) are pre charged to vdd (1.2V). The access transistors are then turned ON so that the SRAM cell is connected to the bit-lines for read operation.

c) Write state: In this mode, both the bit-lines are pre charged to either [1,0] or [0,1], depending on the data to be written into the SRAM cell. After pre-charging, the access transistors are turned ON to connect the bit-lines to the SRAM cell nodes.

The SNM simulation is done based on the evaluation technique proposed by Severick et.al [13] and Calhoun [21]. Based on this analytical method, additional circuit elements are added to the simulation setup to perform a coordinate transformation of the SNM plot by 45 degrees. This allows us to plot and visualize the SNM curve directly, and measure the actual SNM margin from the graph by looking at the maximum voltage difference of the eye diagram along the vertical axis. The circuit setup proposed by Severick et al. is as shown in Figure 3.6. Here the inverters INV1 and INV2 are connected to additional circuits as per the coordinate transformed equation (shown below the diagram of Figure 3.6). The voltage input u is swept from 0 to supply voltage (vdd) and the output voltages v1 and v2 obtained directly corresponds to the SNM eye diagram.

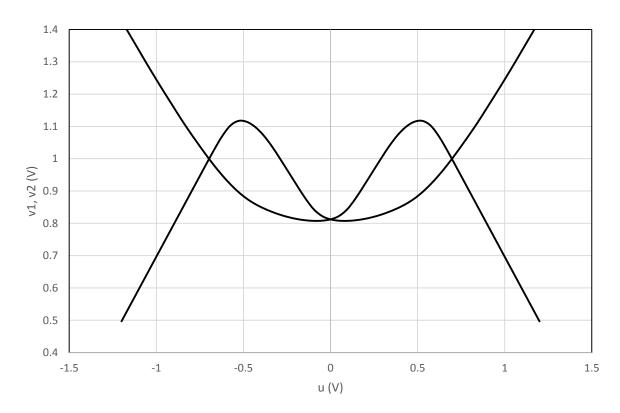

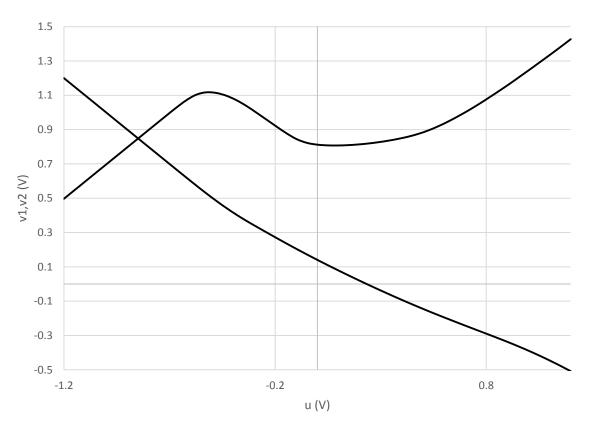

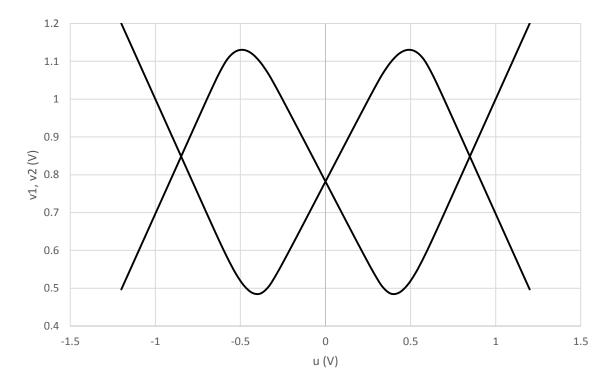

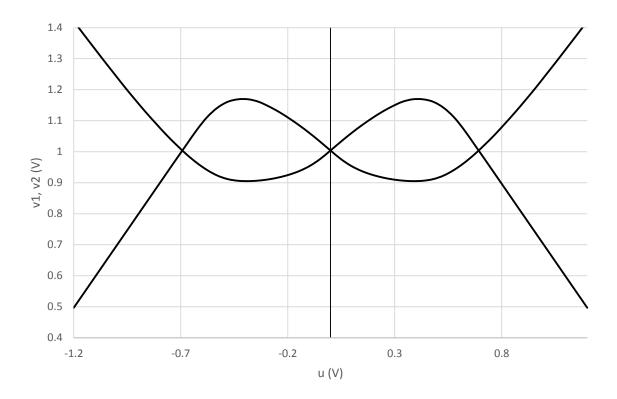

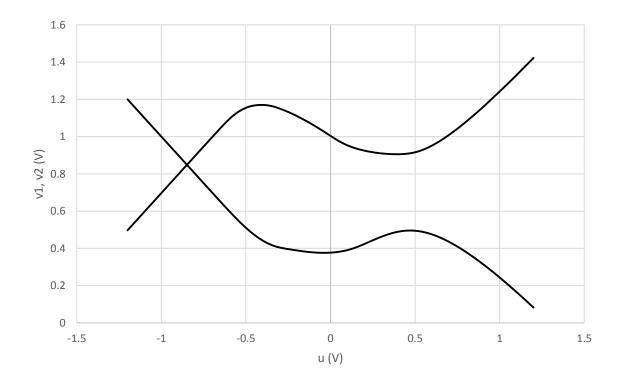

Figure 3.6: Schematic setup for SNM noise margin analysis based on method proposed by Severick [13] The cadence SNM eye diagram for the 6T and proposed 12T cell are as shown in Figure 3.7 and 3.8 respectively. The SNM margin voltages are obtained from the diagram by measuring the maximum voltage difference within the eye. This maximum voltage is then scaled by  $\sqrt{2}$  due to coordinate transformation requirement. The SNM margins for extracted from the Figures 3.7 and 3.8 are listed in Table 3.2.

Figure 3.7a: 6T cell hold noise margin

Figure 3.7b: 6T cell read noise margin

Figure 3.7c: 6T cell write noise margin

Figure 3.8a: 12T cell hold noise margin

Figure 3.8b: 12T cell read noise margin

Figure 3.8c: 12T cell read noise margin

## **Summary**

Table 3.2: SNM characteristics of 6T and the proposed 12T cell

| Cell              | H_SNM  | R_SNM  | W_SNM  |

|-------------------|--------|--------|--------|

| 6t_cell           | 440 mV | 168 mV | 425 mV |

| Proposed 12t cell | 445 mV | 188 mV | 340 mV |

The SNM noise margin analysis shows that the 12T cell shows an improvement in hold and read noise margins but at the expense of write noise margin degradation. Additionally, the SNM analysis proves the functionality of both SRAM cells.

#### 3.4.5 <u>Drawbacks</u>

The main drawback of the proposed design is the increase in power consumption due to introduction of redundant transistors. The conventional 6T cell design consumes a power of 310 pW due to leakage, whereas the 12T cell design consumes a power of 590 pW. Thus the proposed design increases the static power dissipation of the SRAM design by 2X, which is the tradeoff made for the radiation tolerance improvement. The presence of PMOS and NMOS access transistors per bit-line also increases the leakage current via the bit lines, compared to the 6T cell designs that use a single NMOS access transistor per bit-line.

Additionally, the PMOS / NMOS ratio constraint requirement and introduction of transmission gates for access transistors has resulted in the reduction of the write noise margin of the SRAM cell at the expense of improvement in SEMU tolerance.

## Chapter 4

## 4. TESTING METHODOLOGY

## 4.1 Accuro<sup>TM</sup> Software Description

Accuro stands for accurate and efficient semiconductor process, device and circuit simulation. It's a highly efficient tool for simulating several single event experiments simultaneously. The tool is suitable for cross section analysis and LET threshold prediction. The GDSII layout and net-list files obtained from Calibre DRC verification tool are the two important input files used for 3D mixed mode single event simulation in Accuro. Apart from that, Accuro also needs supporting library files such as HSPICE models and layout and schematic annotation files.