# DIGITAL IMPLEMENTATION OF AN UPSTREAM DOCSIS QAM MODULATOR AND CHANNEL EMULATOR

A Thesis Submitted to the College of Graduate Studies and Research in Partial Fulfillment of the Requirements for the Degree of Master of Science in the Department of Electrical and Computer Engineering University of Saskatchewan

> by Andy D. Fontaine

Saskatoon, Saskatchewan, Canada September 2014

© Copyright Andy D. Fontaine, October, 2014. All rights reserved.

### Permission to Use

In presenting this thesis in partial fulfillment of the requirements for a Postgraduate degree from the University of Saskatchewan, it is agreed that the Libraries of this University may make it freely available for inspection. Permission for copying of this thesis in any manner, in whole or in part, for scholarly purposes may be granted by the professors who supervised this thesis work or, in their absence, by the Head of the Department of Electrical and Computer Engineering or the Dean of the College of Graduate Studies and Research at the University of Saskatchewan. Any copying, publication, or use of this thesis, or parts thereof, for financial gain without the written permission of the author is strictly prohibited. Proper recognition shall be given to the author and to the University of Saskatchewan in any scholarly use which may be made of any material in this thesis.

Request for permission to copy or to make any other use of material in this thesis in whole or in part should be addressed to:

Head of the Department of Electrical and Computer Engineering 57 Campus Drive University of Saskatchewan Saskatoon, Saskatchewan, Canada S7N 5A9

## Acknowledgments

I would like to thank my supervisors, Dr. Eric Salt and Dr. Ha Nguyen for their patience and encouragement throughout the duration of the program. Their courses were well structured and provided me with practical tools which helped to cement my knowledge during the project development phase. Further, Dr. Salt's guidance during the writing process was very helpful and something for which I am enormously grateful.

A very special thanks goes to David Dodds and Brian Daku for steering me towards the Industry Oriented Master's (IOM) when I first inquired about the graduate programs being offered by the department. The financial assistance which Mr. Dodds was able to provide was of tremendous benefit, and I am extremely fortunate and appreciative.

I would also like to thank my fellow IOM cohorts Mushtafizur Choudhury and Rory Gowen. Their ideas and suggestions have proved very useful and helped to guide the development of this project. In addition, Mr. Gowen created some valuable software that allowed me to convert RAM output data for circuit performance analysis in MATLAB. His contribution was instrumental to the performance evaluation of the channel emulator.

Finally, I must thank my parents, Dennis and Bette, whose enduring love, patience, and support have made this journey possible. Their faith in my abilities kept me on track whenever I was doubting myself. Thank you so much — I could not have done this without you.

### Abstract

The concept of cable television, originally called community antenna television (CATV), began in the 1940's. The information and services provided by cable operators have changed drastically since the early days. Cable service providers are no longer simply providing their customers with broadcast television but are providing a multi-purpose, two-way link to the digital world. Custom programming, telephone service, radio, and high-speed internet access are just a few of the services offered by cable service providers in the 21st century.

At the dawn of the internet the dominant mode of access was through telephone lines. Despite advances in dial-up modem technology, the telephone system was unable to keep pace with the demand for data throughput. In the late 1990's an industry consortium known as Cable Television Laboratories, Inc. developed a standard protocol for providing high-speed internet access through the existing CATV infrastructure. This protocol is known as Data Over Cable Service Interface Specification (DOCSIS) and it helped to usher in the era of the information superhighway.

CATV systems use different parts of the radio frequency (RF) spectrum for communication to and from the user. The downstream portion (data destined for the user) consumes the bulk of the spectrum and is located at relatively high frequencies. The upstream portion (data destined to the network from the user) of the spectrum is smaller and located at the low end of the spectrum. This lower frequency region of the RF spectrum is particularly prone to impairments such as micro-reflections, which can be viewed as a type of multipath interference. Upstream data transfer in the presence of these impairments is therefore problematic and requires complex signal correction algorithms to be employed in the receiver.

The quality of a receiver is largely determined by how well it mitigates the signal impairments introduced by the channel. For this reason, engineers developing a receiver require a piece of equipment that can emulate the channel impairments in any permutation in order to test their receiver. The conventional test methodology uses a hardware RF channel emulator connected between the transmitter and the receiver under test. This method not only requires an expensive RF channel emulator, but a functioning analog front-end as well. Of these two problems, the expense of the hardware emulator is likely less important than the delay in development caused by waiting for a functional analog front-end. Receiver design is an iterative, time consuming process that requires the receiver's digital signal processing (DSP) algorithms be tested as early as possible to reduce the time-to-market.

This thesis presents a digital implementation of a DOCSIS-compliant channel emulator whereby cable micro-reflections and thermal noise at the analog front-end of the receiver are modelled digitally at baseband. The channel emulator and the modulator are integrated into a single hardware structure to produce a compact circuit that, during receiver testing, resides inside the same field programmable gate array (FPGA) as the receiver. This approach removes the dependence on the analog front-end allowing it to be developed concurrently with the receiver's DSP circuits, thus reducing the time-to-market.

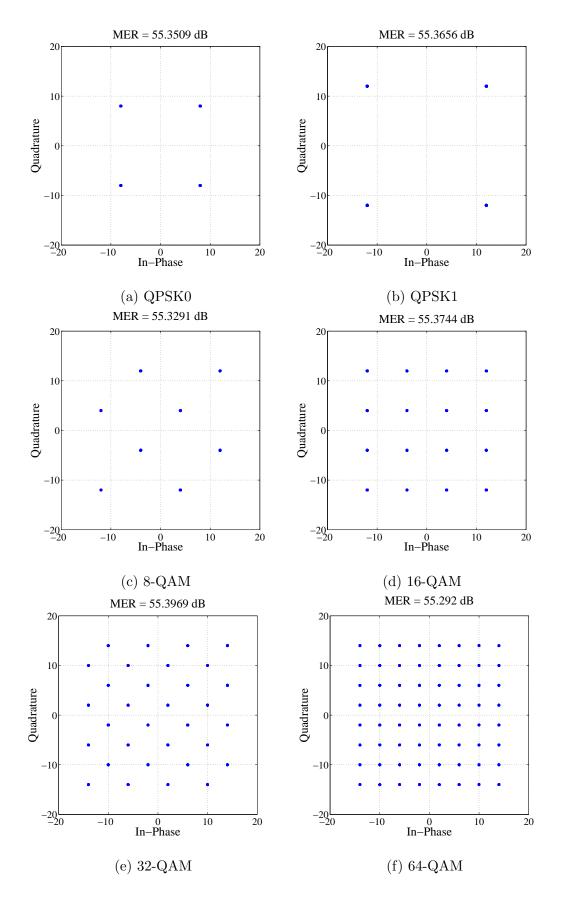

The approach taken in this thesis produces a fully programmable channel emulator that can be loaded onto FPGAs as needed by engineers working independently on different receiver designs. The channel emulator uses 3 independent data streams to produce a 3-channel signal, whereby a main channel with micro-reflections is flanked on either side by adjacent channels. Thermal noise normally generated by the receiver's analog front-end is emulated and injected into the signal. The resulting structure utilizes 43 dedicated multipliers and 401.125 KB of RAM, and achieves a modulation error ratio (MER) of 55.29 dB.

## Table of Contents

| Permission to Use |                 |                                                  |      |  |

|-------------------|-----------------|--------------------------------------------------|------|--|

| A                 | Acknowledgments |                                                  |      |  |

| $\mathbf{A}$      | Abstract        |                                                  |      |  |

| Τa                | able o          | of Contents                                      | v    |  |

| $\mathbf{Li}$     | st of           | Tables                                           | ix   |  |

| $\mathbf{Li}$     | st of           | Figures                                          | х    |  |

| $\mathbf{Li}$     | st of           | Abbreviations                                    | xiii |  |

| 1                 | Intr            | roduction                                        | 1    |  |

|                   | 1.1             | Hardware Emulation Versus Software Simulation    | 9    |  |

|                   |                 | 1.1.1 Integrating the Emulator and the Modulator | 10   |  |

|                   | 1.2             | Problem Statement                                | 11   |  |

|                   | 1.3             | Thesis Outline                                   | 12   |  |

| <b>2</b>          | Cha             | annel Modelling                                  | 14   |  |

|                   | 2.1             | Methodology                                      | 14   |  |

|                   | 2.2             | Time Delay                                       | 15   |  |

|                   | 2.3             | Multipath                                        | 16   |  |

|                   | 2.4             | Thermal Noise                                    | 17   |  |

|                   | 2.5             | Carrier Frequency Offset                         | 18   |  |

|                   | 2.6             | Incorporating Adjacent Channels                  | 19   |  |

| 3 | $\mathbf{Syst}$ | stem Architecture |                                                     |    |  |  |

|---|-----------------|-------------------|-----------------------------------------------------|----|--|--|

|   | 3.1             | Top L             | evel Emulator Architecture                          | 23 |  |  |

|   |                 | 3.1.1             | Operational Overview                                | 23 |  |  |

|   | 3.2             | Key C             | Circuits                                            | 28 |  |  |

|   |                 | 3.2.1             | Loading and Editing Channel Profiles                | 28 |  |  |

|   |                 | 3.2.2             | Main Channel Transmit Data Circuit                  | 31 |  |  |

|   |                 | 3.2.3             | Multiplexed Polyphase Pulse Shaping Filter          | 32 |  |  |

|   |                 | 3.2.4             | Upsampling                                          | 40 |  |  |

|   |                 | 3.2.5             | Multiplexed Pipelined Fractional Delay Filter       | 46 |  |  |

|   |                 | 3.2.6             | Adjacent Channels                                   | 48 |  |  |

|   |                 | 3.2.7             | Complex AWGN Generator                              | 50 |  |  |

| 4 | The             | e DOC             | SIS Specification and Channel Emulator Performance  | 53 |  |  |

|   | 4.1             | Mode              | of Operation                                        | 53 |  |  |

|   |                 | 4.1.1             | Modulation Rate                                     | 55 |  |  |

|   | 4.2             | Modul             | lation Modes                                        | 55 |  |  |

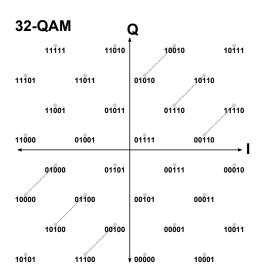

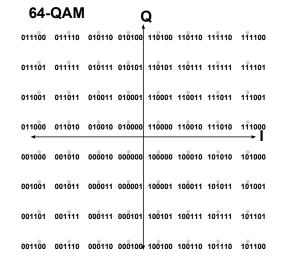

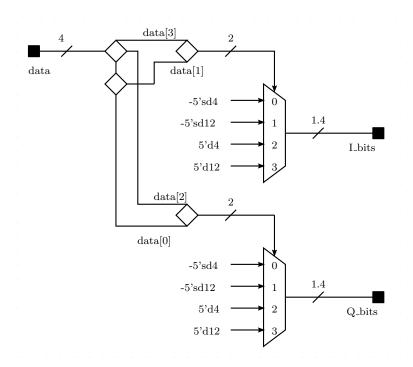

|   |                 | 4.2.1             | Modulation Constellations                           | 56 |  |  |

|   |                 | 4.2.2             | Symbol Mapping                                      | 58 |  |  |

|   | 4.3             | Deterr            | mining Upstream RF Channel Emulator Characteristics | 58 |  |  |

|   |                 | 4.3.1             | Carrier to Interference Plus Ingress Ratio          | 58 |  |  |

|   |                 | 4.3.2             | Determining Carrier Frequency Agility and Quality   | 60 |  |  |

|   |                 | 4.3.3             | Micro-Reflections                                   | 60 |  |  |

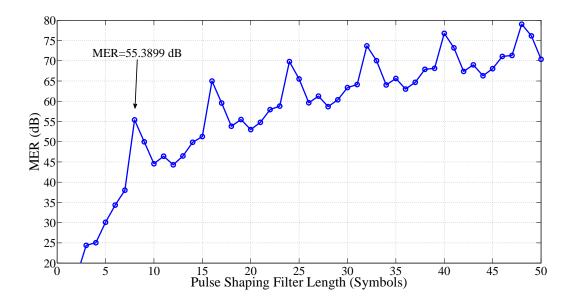

|   |     | 4.3.4 Deter   | mining MER Perfomance of Emulator      | 61 |

|---|-----|---------------|----------------------------------------|----|

|   | 4.4 | Determining   | Pulse Shaping Filter Length            | 63 |

|   |     | 4.4.1 Pulse   | Shaping Filter Length and MER          | 63 |

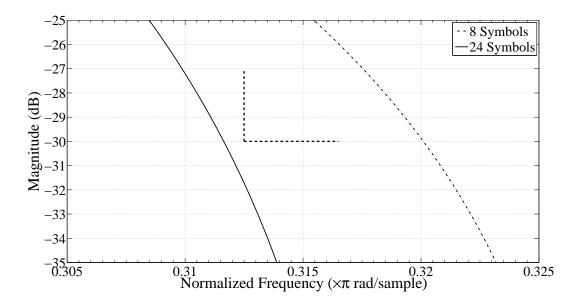

|   |     | 4.4.2 Spect   | ral Mask                               | 64 |

|   |     | 4.4.3 Pulse   | Shaping of Adjacent Channels           | 66 |

| 5 | Pra | ctical Hardv  | vare Limitations                       | 68 |

|   | 5.1 | Implementat   | ion Issues                             | 68 |

|   | 5.2 | Test Assemb   | ly and Hardware Performance Results    | 70 |

| 6 | Con | clusion and   | Future Work                            | 76 |

|   | 6.1 | Summary .     |                                        | 76 |

|   | 6.2 | Contribution  | s and Results                          | 76 |

|   | 6.3 | Resources an  | d Performance                          | 77 |

|   | 6.4 | Future Work   |                                        | 78 |

| A | Aux | ciliary Circu | it Schematics                          | 79 |

|   | A.1 | Generating a  | and Mapping Symbol Data                | 79 |

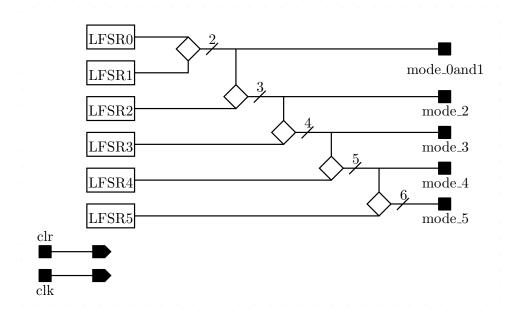

|   |     | A.1.1 Linea   | r Feedback Shift Register              | 79 |

|   |     | A.1.2 Symb    | ol Generator                           | 80 |

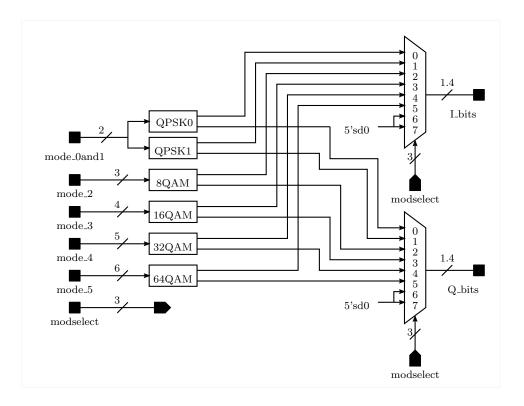

|   |     | A.1.3 Symb    | ol Mapper                              | 81 |

|   | A.2 | Multiplexed   | Sample Interleaving                    | 82 |

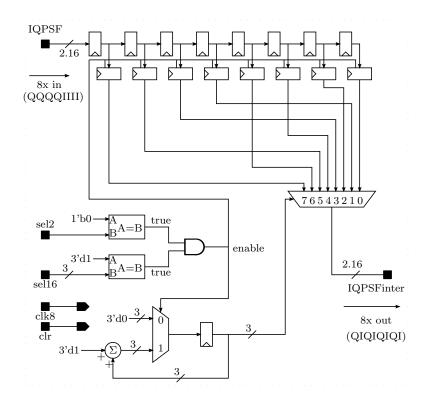

|   |     | A.2.1 Interl  | eaving the Pulse Shaping Filter Output | 83 |

|   |     | A.2.2 Interl  | eaving the Upsampling Filter Output    | 84 |

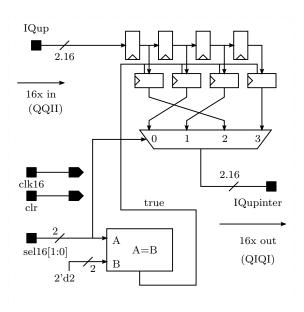

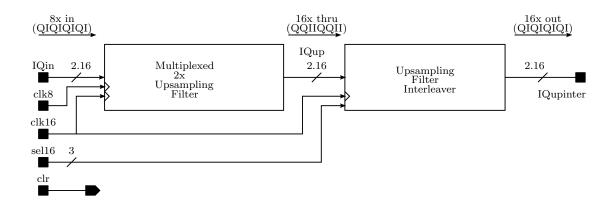

| A.3 Upsampling Filter Assembly                  | 85  |

|-------------------------------------------------|-----|

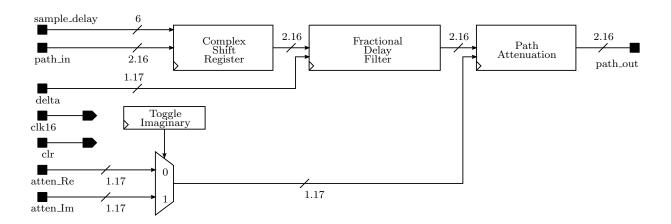

| A.4 Echo Path Assembly                          | 85  |

| A.4.1 Integer Delay                             | 87  |

| A.4.2 Path Attenuation                          | 88  |

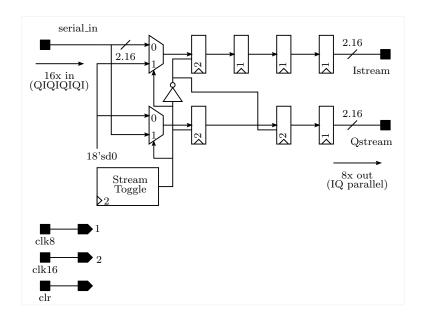

| A.5 Demultiplexing Data into Parallel Streams   | 88  |

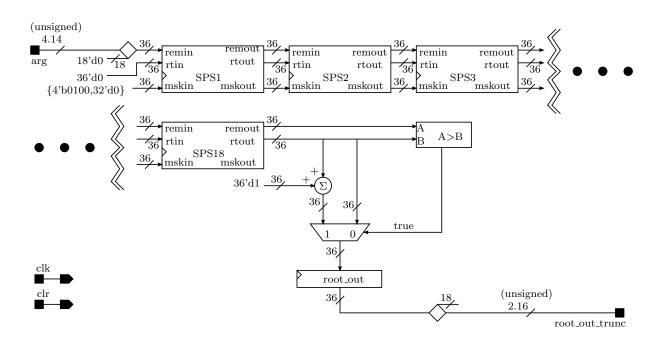

| A.6 Pipelined Successive Approximation Circuits | 89  |

| A.6.1 Square Root                               | 90  |

| A.6.2 Natural Logarithm                         | 91  |

| A.6.3 CORDIC                                    | 96  |

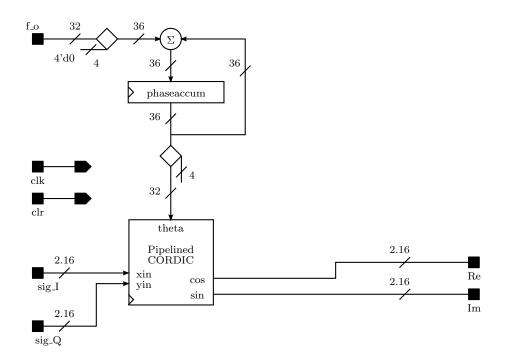

| A.7 CORDIC-based Complex Multiply               | 99  |

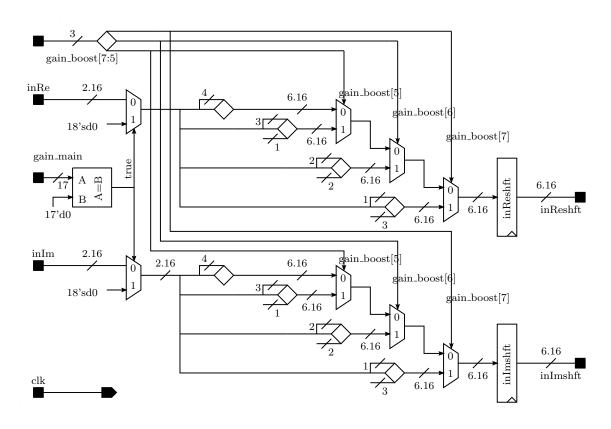

| A.8 Gain Boosting in Main Channel               | 99  |

| A.9 Auxiliary Circuits for Adjacent Channels    | .00 |

| A.9.1 Pulse Shaping in Adjacent Channels        | .01 |

| A.9.2 Demultiplexing Data into Parallel Streams | .01 |

| References 1                                    | .04 |

## List of Tables

| 3.1 | Clocks Used in Top Level of Channel Emulator    | 22 |

|-----|-------------------------------------------------|----|

| 4.1 | DOCSIS Upstream Channel Micro-Reflections       | 61 |

| 4.2 | DOCSIS Upstream RF Channel Spectral Mask Limits | 65 |

## List of Figures

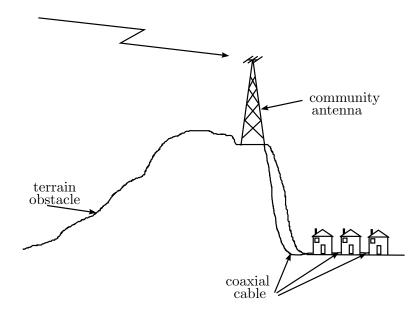

| 1.1  | Example of Community Antenna Television                                     | 2  |

|------|-----------------------------------------------------------------------------|----|

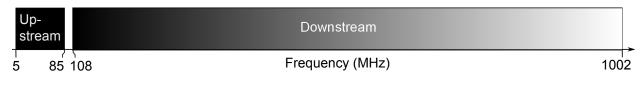

| 1.2  | DOCSIS 3.0 Extended RF Spectrum                                             | 4  |

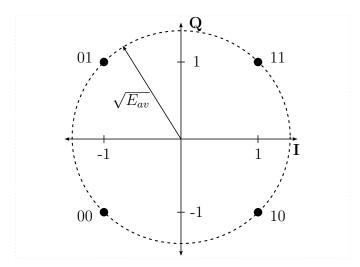

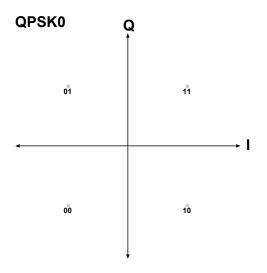

| 1.3  | Example of QPSK Symbol Constellation                                        | 6  |

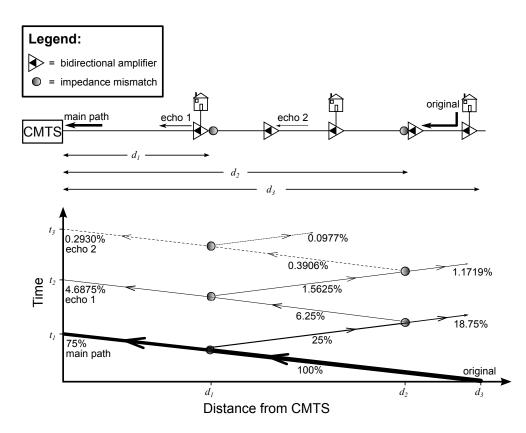

| 1.4  | Upstream Cable Plant Echoes                                                 | 8  |

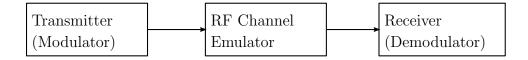

| 1.5  | Channel Emulation With External RF Emulator                                 | 10 |

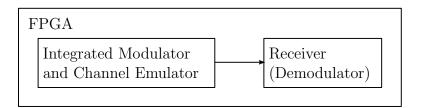

| 1.6  | Channel Emulation Using Integrated Structure                                | 11 |

| 2.1  | Equivalent Structures                                                       | 18 |

| 3.1  | Conventions for Hardware Schematic Diagrams                                 | 21 |

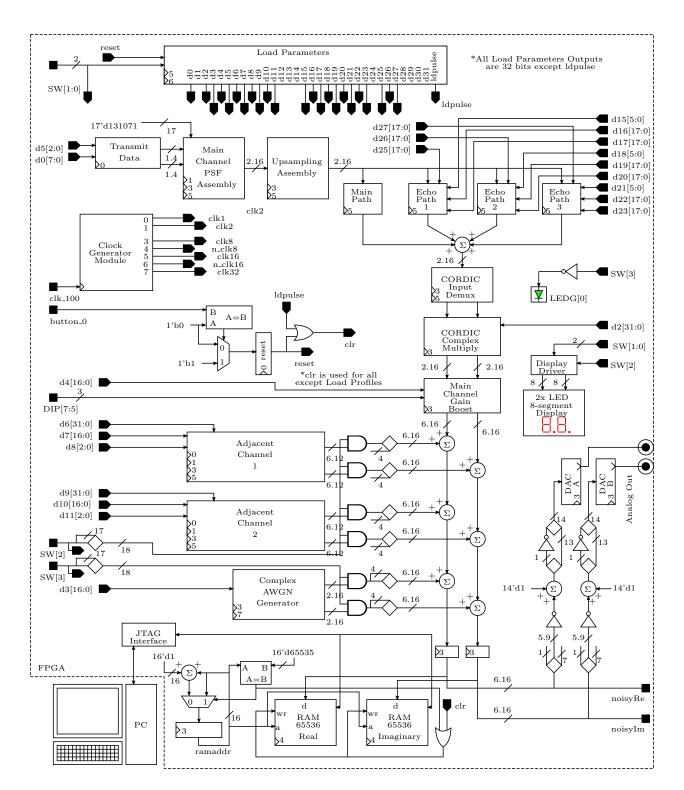

| 3.2  | Schematic for Top Level of Channel Emulator                                 | 24 |

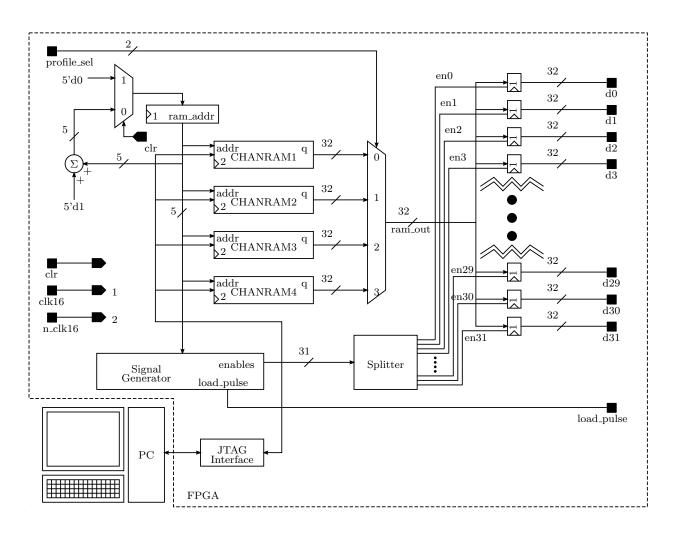

| 3.3  | Schematic for Load Parameters Circuit                                       | 29 |

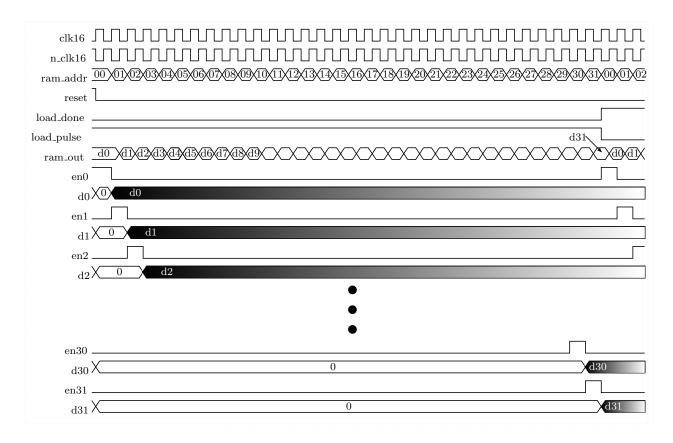

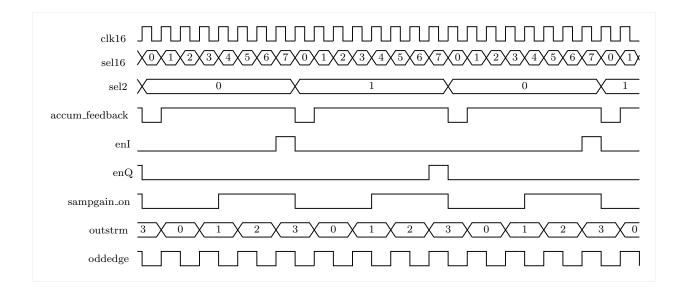

| 3.4  | Timing Diagram for Load Profiles Signal Generator                           | 30 |

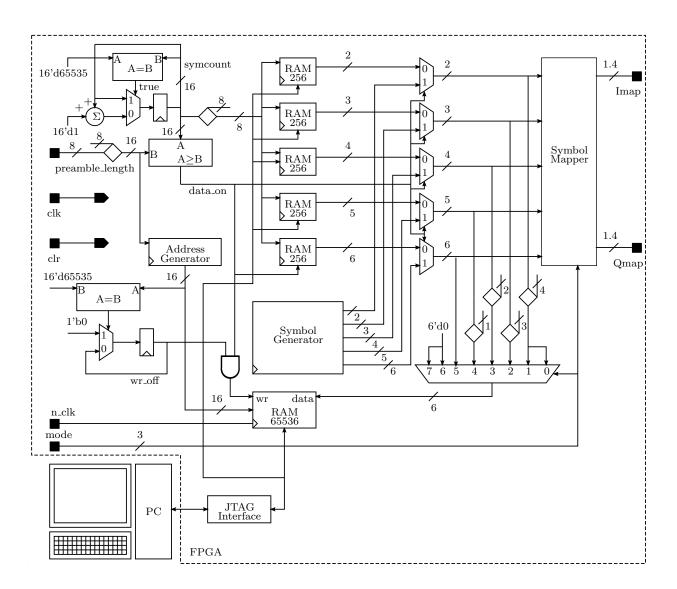

| 3.5  | Schematic for Main Channel Transmit Data Circuit                            | 33 |

| 3.6  | Schematic for 8 Symbol SRRC Pulse Shaping Filter                            | 36 |

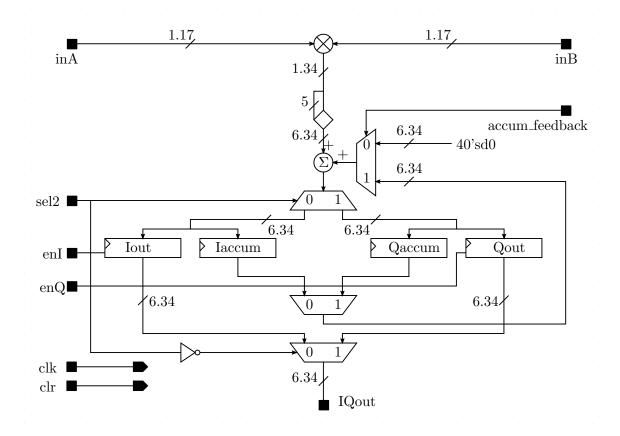

| 3.7  | Schematic for Dual Stream Multiply and Accumulate (DSMAC) $\ . \ . \ . \ .$ | 38 |

| 3.8  | Timing Diagram for Dual Stream Multiply and Accumulate                      | 39 |

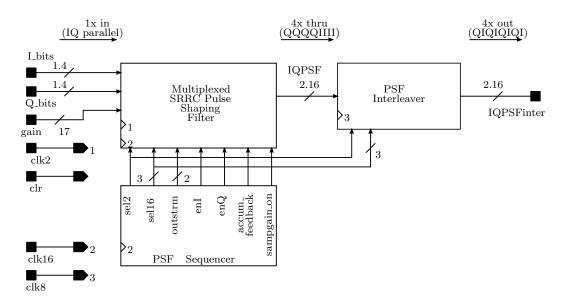

| 3.9  | Main Channel Pulse Shaping Filter Assembly                                  | 40 |

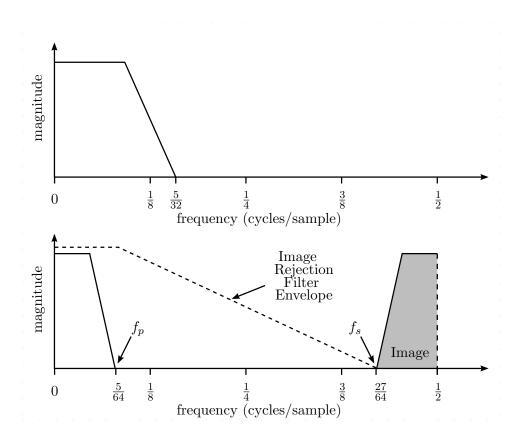

| 3.10 | Determining the Stop Band Edge of Upsample by 2 Filter                      | 42 |

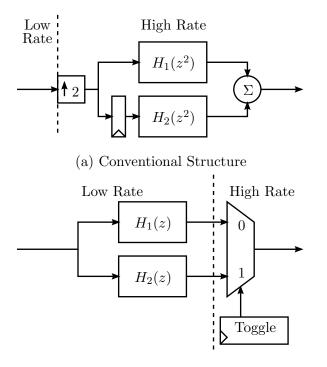

| 3.11 | Equivalent Two-Path Filter Structures                                       | 44 |

| 3.12 | Schematic for Multiplexed 2-Path Nearly Linear Phase Upsampling Filter      | 45 |

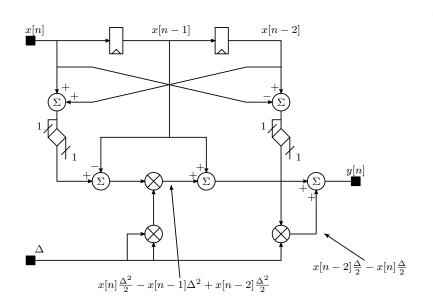

| 3.13 | A 3-Tap Variable Fractional Delay Filter                          | 47 |

|------|-------------------------------------------------------------------|----|

| 3.14 | Pipelined Multiplexed 3-Tap Variable Fractional Delay Filter      | 48 |

| 3.15 | Schematic for Adjacent Channel Assembly                           | 50 |

| 3.16 | Schematic for Single Component (I or Q) of Complex AWGN Generator | 52 |

| 4.1  | A Typical FDMA Spectrum                                           | 54 |

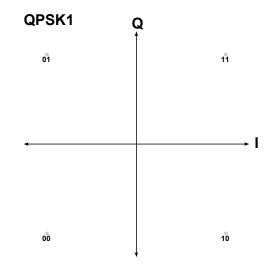

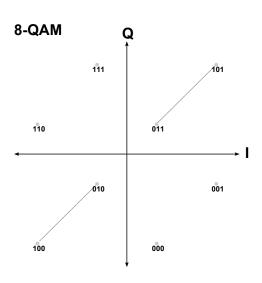

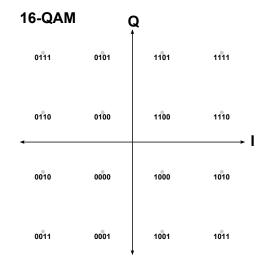

| 4.2  | DOCSIS Upstream Modulation Modes                                  | 57 |

| 4.3  | DOCSIS Upstream Symbol Maps                                       | 59 |

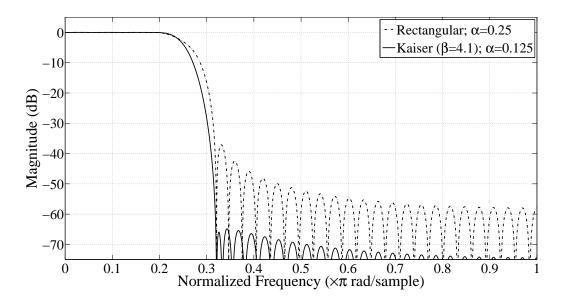

| 4.4  | Effect of Pulse Shaping Filter Length on MER                      | 64 |

| 4.5  | Effect of Pulse Shaping Filter Length on Bandwidth                | 66 |

| 4.6  | Modifying Adjacent Channel Pulse Shaping Filters                  | 67 |

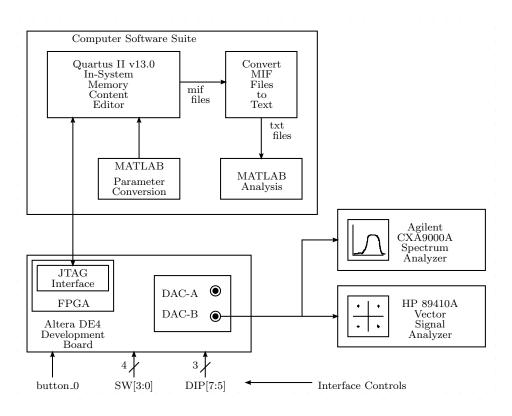

| 5.1  | Schematic for Channel Emulator Test Assembly                      | 71 |

| 5.2  | Functional Verification of Fractional Delay Filter                | 72 |

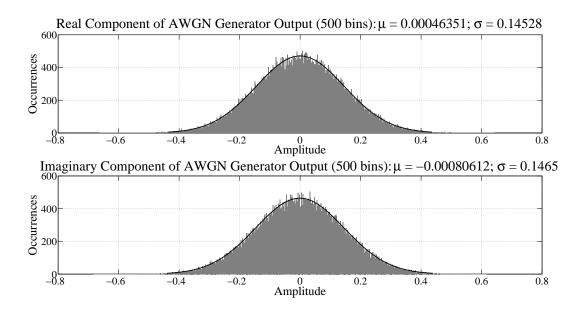

| 5.3  | Histogram of Hardware AWGN Generator Output                       | 73 |

| 5.4  | Unimpaired Channel Output Results                                 | 75 |

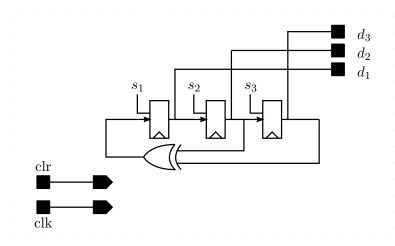

| A.1  | Schematic for 3-bit Linear Feedback Shift Register (LFSR)         | 80 |

| A.2  | Schematic for Symbol Generator                                    | 81 |

| A.3  | Schematic for Symbol Mapper                                       | 82 |

| A.4  | Schematic for 16-QAM Modulation Map                               | 83 |

| A.5  | Schematic for Pulse Shaping Filter Output Interleaver             | 84 |

| A.6  | Schematic for Upsampling Filter Output Interleaver                | 85 |

| A.7  | Schematic for | Upsampling Assembly                                    |      | •   | 86  |

|------|---------------|--------------------------------------------------------|------|-----|-----|

| A.8  | Schematic for | Echo Path with Complex Attenuation                     |      |     | 86  |

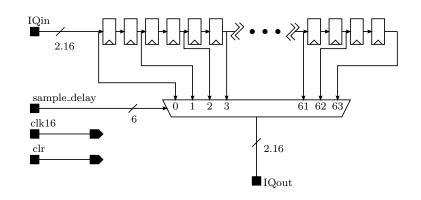

| A.9  | Schematic for | Multiplexed Complex Shift Register                     |      |     | 87  |

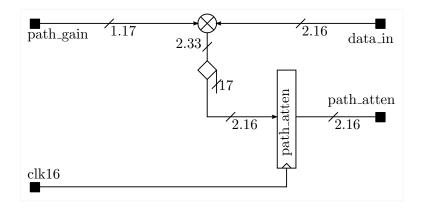

| A.10 | Schematic for | Path Attenuator                                        |      |     | 88  |

| A.11 | Schematic for | CORDIC Input Demux (Main Channel)                      |      |     | 89  |

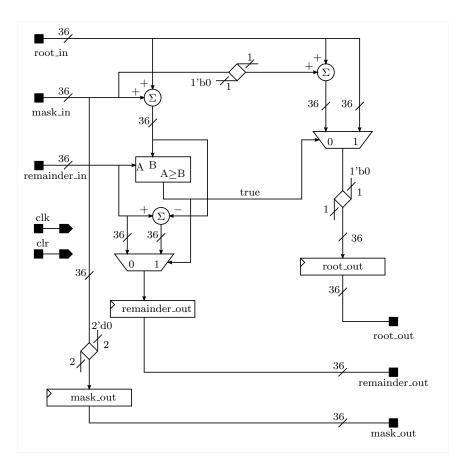

| A.12 | Schematic for | 18-Stage Pipelined Square Root                         |      |     | 91  |

| A.13 | Schematic for | Single Stage of Pipelined Square Root (SPS)            |      |     | 92  |

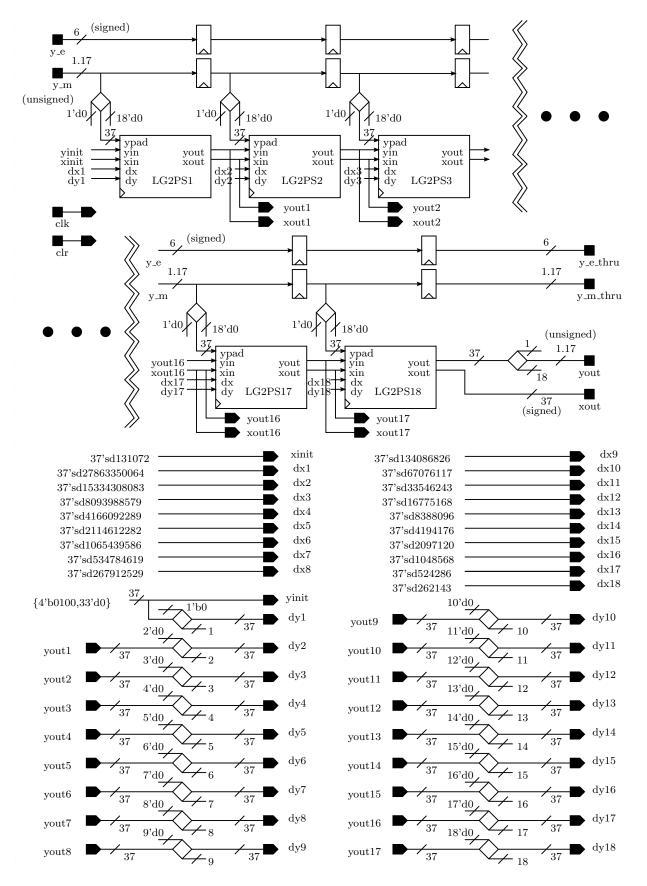

| A.14 | Schematic for | 18-Stage Pipelined Natural Logarithm                   |      |     | 93  |

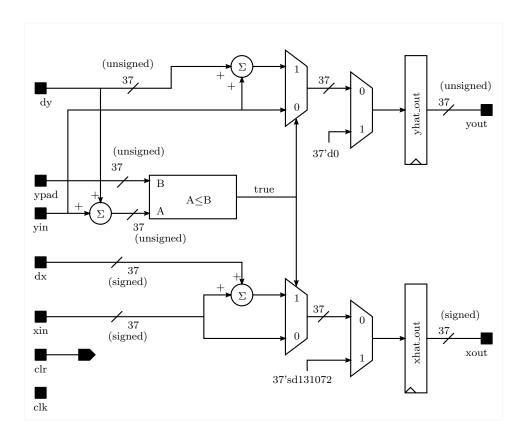

| A.15 | Schematic for | Single Stage of Pipelined Base-2 Logarithm $(LG2PS)$ . |      |     | 94  |

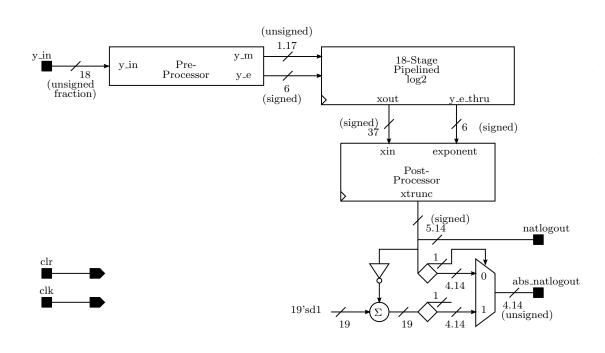

| A.16 | Schematic for | Natural Logarithm Assembly                             |      |     | 95  |

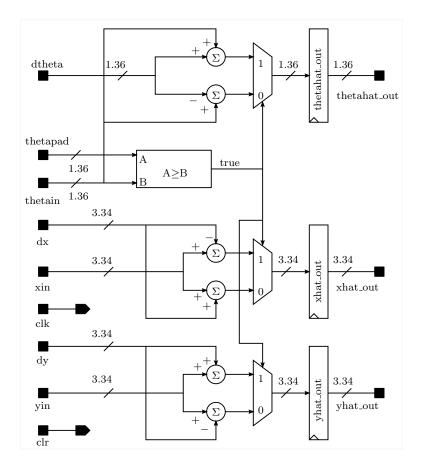

| A.17 | Schematic for | 18-Stage Pipelined CORDIC                              |      |     | 96  |

| A.18 | Schematic for | Single Stage of Pipelined CORDIC (CPS)                 |      |     | 97  |

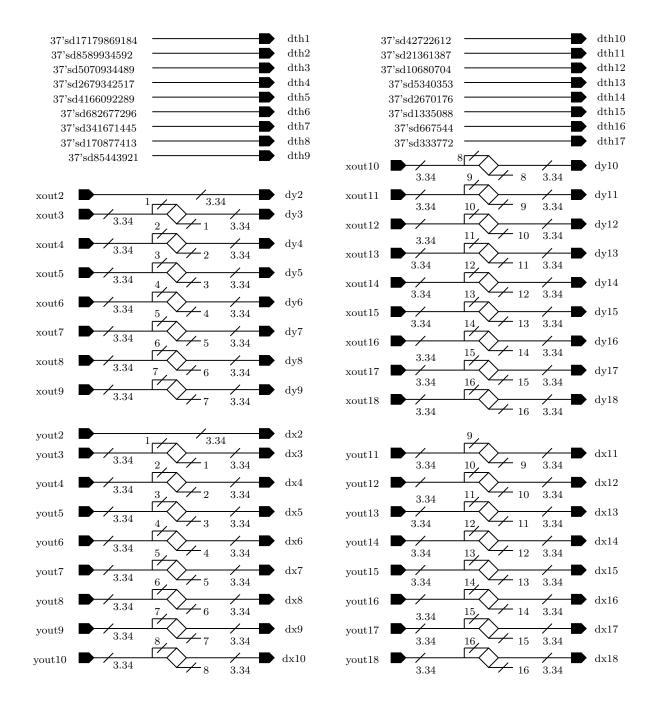

| A.19 | Schematic for | Constants and Arithmetic Shifts in 18-Stage Pipelined  | CORE | DIC | 98  |

| A.20 | Schematic for | CORDIC-based Complex Multiply                          |      |     | 99  |

| A.21 | Schematic for | Main Channel Gain Boost                                |      |     | 100 |

| A.22 | Schematic for | 16 Symbol SRRC Pulse Shaping Filter                    |      |     | 102 |

| A.23 | Schematic for | CORDIC Input Demux (Adjacent Channel)                  |      |     | 103 |

## List of Abbreviations

ACI Adjacent Channel Interference

${\bf APF}\,$  All Pass Filter

AWGN Additive White Gaussian Noise

**BASK** Binary Amplitude Shift Keying

**BPSK** Binary Phase Shift Keying

**CATV** Community Antenna TeleVision

${\bf CM}\,$  Cable Modem

**CMTS** Cable Modem Termination System

**COI** Channel of Interest (also referred to as the main channel)

**CORDIC** COordinate Rotation DIgital Computer

DAC Digital to Analog Converter

$\mathbf{dB}$  DeciBels

**dBc** DeciBels with respect to Carrier

**DDS** Direct Digital Synthesis

**DEMUX** Demultiplexer

${\bf DFT}$ Discrete Fourier Transform

**DOCSIS** Data Over Cable Service Interface Specification

FDMA Frequency Division Multiple Access

${\bf FIFO}\,$  First-In First-Out

**FIR** Finite Impulse Response

- FPGA Field Programmable Gate Array

- I In-phase (Component of Quadrature Modulated Signal)

- **IIR** Infinite Impulse Response

- **IP** Intellectual Property

- **ISI** InterSymbol Interference

- JTAG Joint Test Action Group

- **LED** Light Emitting Diode

- LFSR Linear Feedback Shift Register

- LPF Low-Pass Filter

- LSB Least Significant Bit

- LUT Look Up Table

- MAC Media Access Control or Multiply and ACcumulate obvious from context

#### MATLAB MATrix LABoratory

- MER Modulation Error Ratio

- ${\bf MIF}\,$  Memory Initialization File

- ${\bf MSB}\,$  Most Significant Bit

- ${\bf MSE}\,$  Mean Squared Error

- $\mathbf{MUX}$  Multiplexer

- NCO Numerically Controlled Oscillator

- **Q** Quadrature (Component of Quadrature Modulated Signal)

${\bf QAM}\,$  Quadrature Amplitude Modulation

**QPSK** Quadrature Phase Shift Keying

**RAM** Random Access Memory

${\bf ROM}\,$  Read Only Memory

${\bf RF}\,$  Radio Frequency

S-CDMA Synchronous Code Division Multiple Access

${\bf SNR}\,$  Signal to Noise Ratio

**SRRC** Square Root Raised Cosine

**TDMA** Time Division Multiple Access

$\mathbf{VSA}$  Vector Signal Analyzer

$\mathbf{XOR}\;\;\mathrm{eXclusive}\;\mathrm{OR}\;$

## 1. Introduction

Today's cable television industry is an outgrowth of the work of a few enterprising inventors in the late 1940's. Although there is some disagreement as to who built the very first cable television system, L. E. Parsons of Astoria, Oregon and John Walson, Sr. of Mahanoy City, Pennsylvania are credited with independently constructing the first cable television networks [1], [2]. Located on opposite ends of the United States, these men pioneered a new way of delivering broadcast television to a much wider audience. Areas that are remote or located in mountainous terrain do not have a line of sight to the transmitter and signal reception is severely degraded. By building a large antenna in a location with a line of sight to the transmitter, the received radio frequency (RF) signal could be amplified and passed through coaxial cables into the televisions of those in the community. Originally known as community antenna television (CATV), these networks have evolved substantially over the course of the last few decades.

Cable television was initially developed to produce TV reception for viewers in areas with poor reception, as depicted in Figure 1.1. These viewers were required to pay a connection fee to be granted access to the cable. As its popularity grew, entrepreneurs saw opportunities to invest in a burgeoning industry. It was found that viewers were willing to pay a subscription fee for the reception of television broadcasts, and the notion of pay TV was born. Several companies such as Zenith Radio Corporation, the International Telemeter Corporation, and Skiatron were active throughout the 1950's and 60's developing strategies to provide metered 'pay-as-you-see' content to cable TV subscribers [3]. Although the services developed by these companies were experimental and did not see widespread use, they helped to identify not only the types of services customers expected, but how these services could be effectively

Figure 1.1: Example of Community Antenna Television

provided.

With the advent of satellite technology, the cable television industry underwent another drastic change in the 1970's. Satellites could deliver programming to cable systems, allowing more channels than was possible from transmitters on the ground [4]. With its high channel content, this type of cable television allowed the notion of pay TV to gain traction with an ever larger market. Cable television was no longer simply a way for remote viewers to tune into regular broadcast content. It had become a means to deliver a premium television service to viewers anywhere. For viewers who were already able to receive over-the-air broadcast signals, cable TV had evolved into a high quality service worth paying for.

Aside from satellite advances, companies such as Vicom and CAS Manufacturing were developing methods to provide a true two-way cable service [5]. By the 1980's, the original one-way service provided by cable companies was being replaced by a two-way system that allowed cable service providers to provide pay-per-view content to their customers. Orders could be placed through a set-top box in the subscriber's home, sending commands through the coaxial cable network to the head-end. Such systems paved the way for the modern two-way digital cable communications networks currently in use. At the time, however, the internet was still in its infancy, and dial-up modems were the dominant data transfer technology. The birth of the worldwide web at the turn of the 1990's once again changed the game [6], as it became another profitable telecommunication service with a high demand. The complexity of web pages and the amount of data they contained quickly grew, and despite advances in dial-up modem technology, telephone-based internet became inadequate for many subscribers.

Fortunately, a solution to the rapidly expanding demands for bandwidth was already in place. By the middle of the 1990's, cable networks were well established in many areas [7], [8], and technological advances in signal processing allowed the same two-way functionality enjoyed by telephone networks [9]. These cable networks were able to provide a wide range of services through a single coaxial connection. Further, the higher bandwidths available on CATV networks allow data transmission at much higher rates than was previously possible with dial-up modems, making them the preferred technology for the emerging information age.

Although cable networks were in widespread use and were a capable medium for data transfer, there was no standardized method of transferring data over the CATV infrastructure. Cable service providers were generally forced to purchase entire networks or systems from a single manufacturer. Among other standards developed in the late 1990's [10], an open-source specification was developed by an industry consortium known as Cable Television Laboratories, Inc. (CableLabs), with the intent of standardizing high-speed data over cable service. This standard, the Data Over Cable Service Interface Specification (DOCSIS), provides a complete framework for the types of systems to be used from head-end to customer as well as specific tolerances for conditions on the network. It allows interoperability between components manufactured by different companies while maintaining a high quality of service under ever-changing conditions.

Current CATV networks use duplexers and bidirectional amplifiers to allow two-way communication on the cable. The RF spectrum is partitioned into two bands: downstream (from head-end to user) and upstream (from user to head-end). The wide array of services consumes the available downstream bandwidth, so in order to maximize the data throughput to the customer, the spectrum is divided according to demand. A relatively small portion

Figure 1.2: DOCSIS 3.0 Extended RF Spectrum

of bandwidth at the low end of the spectrum is allotted to the upstream direction, and the remainder is allotted to the downstream direction. In the DOCSIS 3.0 physical layer specification the upstream spectrum is either 5–30 MHz, 5–42 MHz, or the 5–85 MHz extended spectrum. The lower edge of the downstream spectrum is either 54 or 108 MHz. The upper edge is implementation dependent and can be anywhere from 300–1002 MHz [11]. This is shown in Figure 1.2 for the extended upstream spectrum.

It is clear that downstream data transfer is much easier than in the upstream direction. The first reason is obvious — there is more bandwidth available for simultaneous transmission of many more channels. The second reason is that the lower end of the RF spectrum is an especially noisy region [12]. Historically, this was not a major issue since upstream data traffic for pay-per-view used robust, low-rate, low-order modulation schemes [13]. However, the upstream data traffic in two-way internet communications require high modulation orders to achieve a high data throughput, causing difficulties with efficient data transfer.

Although CATV networks use shielded coaxial cables and are not as prone to interference as wireless networks, they are still subject to imperfections that can pose significant receiver design challenges. For example, spurious emissions from adjacent channels can spill over into the channel of interest (COI) and negatively impact signal quality. The signal located in the COI can also be subjected to echoes which cause the signal to interfere with itself. This phenomenon, known as multipath, is a formidable opponent for a receiver. A discussion of the causes and effects of multipath will be deferred until later.

Thermal noise generated at the analog front-end of a receiver is an impairment that cannot be avoided and care must be taken to ensure signals are transmitted with sufficient power. However, boosting the signal power with impunity is costly both in terms of hardware and power consumption. A balance between signal power and noise must be achieved, and the aim is to set the transmit power just high enough to dominate over the noise.

Ingress is also a factor in CATV networks, particularly in the upstream direction. Ingress refers to signals emitted from transmitters that are not a part of the CATV network. The upstream path of a CATV network consists of a large sum of modem signals combined into a common cable trunk. Any shielding flaw in the cable connecting each modem to the trunk can cause the cable to act as an antenna and capture a portion of the ingress signal. With potentially thousands of modems interconnected over a wide geographical area, significant ingress regions can form in the upstream spectrum. Recurring narrowband ingress can be easily avoided, but sporadic ingress is much more difficult to avoid.

Before discussing the performance measures used for CATV channels, the meaning of data symbols and average symbol energy must be clarified. Consider first a serial bit sequence. Every bit in the sequence is in one of two possible states: 1 or 0. The bits in this binary sequence can be encoded in the amplitude of a real signal. For example, the values +1 and -1 could be used for 1 and 0 respectively. This type of modulation is commonly referred to as binary phase shift keying (BPSK). The binary data has been encoded into symbols — unique signal locations allocated to each combination of bits in the data. Multiple data bits can be encoded by creating more discrete amplitudes for mapping. For example, 2-bit symbols could be mapped to the amplitudes -3/4, -1/4, +1/4, and +3/4 — a type of modulation known as binary amplitude shift keying (BASK).

Complex values are frequently used to map symbols in a plane rather than on a line, which is known as quadrature amplitude modulation (QAM). The real component is referred to as the in-phase (I) component and the imaginary component is referred to as the quadrature (Q) component. The set of possible mapping locations is often referred to as a constellation. The average symbol energy,  $E_{av}$ , is given by

$$E_{av} = \frac{\sum_{k=1}^{K} I_k^2 + Q_k^2}{K},$$

(1.1)

where K is the number of symbol locations in the constellation, and  $I_k$  and  $Q_k$  are the in-phase and quadrature components of the k-th symbol in the constellation. For example,

Figure 1.3: Example of QPSK Symbol Constellation

a 4-QAM constellation (also known as quadrature phase shift keying (QPSK)) has 4 unique symbol locations as depicted in Figure 1.3. If these are located at  $s_1 = (1, 1)$ ,  $s_2 = (-1, 1)$ ,  $s_3 = (-1, -1)$ , and  $s_4 = (1, -1)$ , then  $E_{av} = 2$ . In this special case, all symbols have the same energy.

Transmitter quality sets the base level quality of the signal that reaches the receiver. In the DOCSIS 3.0 standard, for example, QAM is used to transmit data as a series of symbols which are shaped with a pulse shaping filter. The filtering transforms the wideband energy pulses into a bandlimited signal for transmission. If a perfect, infinitely long pulse shaping filter were used, which is not implementable, it would not contribute to the intersymbol interference (ISI) in the received signal. However, since the pulse shaping filter used by the transmitter must have a finite length, some amount of ISI will be introduced by the transmitter. The collective impact of ISI and thermal noise is quantified by a measure referred to as the modulation error ratio (MER). This is the ratio of average signal energy to the mean squared error (MSE) in the decision variable. It is expressed in decibels (dB) as follows [11]:

$$MER_{dB} = 10\log_{10} \left( \frac{E_{av}}{\frac{1}{N} \sum_{j=1}^{N} |e_j|^2} \right),$$

(1.2)

where N is the number of samples being averaged,  $E_{av}$  represents the average symbol energy,

and  $e_j$  represents the error samples.  $E_{av}$  is dependent on both the modulation order and the symbol constellation.

In ideal operation, the topology of the cable network has no effect on the signal quality. Signal loss is corrected by filters and amplifiers along the cable distribution plant. However, the quality and age of the components that make up the network can significantly affect the signal. Deficiencies in the coaxial cable network such as wire faults, improperly terminated cables, or corroded connections cause impedance mismatches along the propagation path [14]. Part of the RF energy is reflected and re-reflected at these mismatched points, causing echoes in the signal. This effect, commonly known as multipath, is central to this thesis.

Consider an upstream transmission from a cable modem (CM) to the head-end cable modem termination system (CMTS). As the transmission travels through the cable, it is passed through a series of amplifiers and subscriber taps along the way [15]. If the connector to one of the amplifiers or taps is mismatched, it will reflect some energy back in the direction of the CM. This reflection will be re-reflected if it meets another impedance mismatch elsewhere. In such a case, it travels toward the CMTS and arrives later in the form of an echo. Echoes can themselves be reflected, and it is possible to have several re-reflected echoes. This scenario is illustrated in Figure 1.4 for the case of two echoes. The reflection amplitude at each mismatch is 25% of the incident amplitude.

The original signal meets the mismatch at  $d_1$  and 75% is passed directly to the CMTS, arriving at time  $t_1$ . This is the main path which has no reflections and has travelled distance  $d_3$ . The remaining 25% reaches the mismatch at  $d_2$ , where 25% is re-reflected back towards the CMTS. Upon reaching the mismatch at  $d_1$  for a second time, 75% of the re-reflection is passed to the CMTS after travelling a distance of  $d_3 + 2(d_2 - d_1)$ . It arrives at the CMTS at time  $t_2$ . The remaining re-reflection that reaches the mismatch is echoed in the same fashion to arrive at the CMTS at time  $t_3$ . Echo 2 has travelled a distance of  $d_3 + 4(d_2 - d_1)$ . It is clear from Figure 1.4 why cable plant echoes can be referred to as multipath. The signal arriving at the CMTS is the sum of the main signal and the echoes. Each component travels a different distance and therefore takes a different path to arrive at the CMTS.

Figure 1.4: Upstream Cable Plant Echoes

Channel impairments such as cable plant echoes can be mitigated by the receiver through the use of an equalizer. Yet in order to do so the receiver must have some specific information about the impairments present on the channel. Before sending any data, the transmitter sends a pre-determined sequence of symbols often referred to as a preamble. This preamble sequence becomes distorted as it propagates through the channel and arrives at the receiver. However, the receiver knows what the correct sequence of symbols should be and can therefore compare the distorted sequence to the correct sequence to extract information about the channel. This information is then used to generate a set of complex correction coefficients (i.e. impulse response) to be used in the equalizer.

The ratio between an echo amplitude and the main path amplitude can be specified in decibels with respect to the carrier (dBc). These units are more meaningful than percentages, as echo strengths in DOCSIS are specified in dBc. The unit conversion is given by

Echo Strength in dBc =

$$20\log_{10}\left(\frac{A_{echo}}{A_{signal}}\right)$$

, (1.3)

where  $A_{signal}$  represents the amplitude of the original signal, and  $A_{echo}$  represents the amplitude of the echo. If the signal amplitude percentages shown in Figure 1.4 are used with  $A_{signal} = 75\%$  and  $A_{echo} = 4.6875\%$ , then 1.3 yields -24.08 dBc. Even low-level echoes can significantly increase ISI, and the digital equalization algorithms employed by CM receivers to mitigate the echoes tend to be costly. In order to test such receiver algorithms, the signal must either be sent over a physical multipath channel or something that emulates one. Not only is an emulation more economical than building a physical CATV network, but its parameters can be controlled precisely. Additionally, testing a different set of parameters does not require the construction of a different network topology.

#### 1.1 Hardware Emulation Versus Software Simulation

Channel emulation can be performed by either hardware or software methods, or by using a combination of the two. A purely software driven approach would be the use of a simulation environment such as ModelSim to generate a testbench for the receiver. This approach allows testing of the receiver implementation without hardware synthesis. The simulation of the channel impairments could be performed inside the testbench and used as receiver input. However, depending on the size and complexity of both the FPGA and the design, this type of gate level simulation is extremely slow. Part of the reason for this is that the FPGA hardware is highly parallel, yet general purpose computer processors are very serialized in design. Every bit transition must be calculated along with estimated propagation delay. At best, each transition could consume a single computer processor cycle — in reality it is likely to be more. Even a relatively short 1 second simulation could take many hours or even days to finish, after which another simulation would be needed for a different set of channel parameters. Clearly this type of offline processing is very time consuming.

An alternative to a purely software based approach would be to combine the software and hardware approaches. A set of data can be generated and altered with a channel model constructed inside a program such as MathWorks Matrix Laboratory (MATLAB).

Figure 1.5: Channel Emulation With External RF Emulator

The output data can then be loaded into the device block memory for use as an input to the receiver that has been synthesized in hardware. Unfortunately, the amount of test data required quickly consumes the device memory and only very short simulations (less than 1 second) can be achieved. In order to effectively test a physical receiver, a real-time RF channel emulator is needed to emulate a CATV channel as it can operate continuously.

One common approach to receiver testing is to use an external RF channel emulator. This method has been discussed in [16] and [17]. It requires the use of a full transmitter which includes an analog back-end, and an analog front-end for the receiver. Furthermore, many of the commercial RF channel emulators that are available use state of the art components making them an inherently expensive piece of equipment. Although this approach (shown in Figure 1.5) provides a real-time emulation and is effective for the final stages of testing, it does not allow a fully digital receiver test.

#### 1.1.1 Integrating the Emulator and the Modulator

Modern digital systems such as modems are often developed and implemented on field programmable gate arrays (FPGA). Combining flexibility and parallel processing with high clock rates, these devices are programmable microchips with a variable architecture. Using a hardware description language such as Verilog allows an entirely different system to be loaded into the device without the need to change the physical hardware. In essence, these devices provide system designers with the means to tailor the on-chip hardware to suit the needs of the application. This flexibility is invaluable during the early stages of hardware development as it allows test hardware to be included on the same device as the circuit being tested.

It is possible to rearrange the signal path in such a way that an RF channel emulation can be performed inside the modulator of the transmitter. By moving the physical location

Figure 1.6: Channel Emulation Using Integrated Structure

of the emulator so that impairments are applied to the signal before upconversion to RF, a complex baseband equivalent channel is realized. This method is much less demanding in terms of hardware resources than the approach shown in Figure 1.5. Not only can this integrated modulator/emulator structure be included on the same FPGA as the receiver, it can be used in the absence of a receiver analog front-end to provide a fully digital realtime channel emulation at baseband. Although such an emulator must be designed and developed in addition to the receiver being tested, the associated cost savings often outweigh this inconvenience. This approach is illustrated in Figure 1.6.

#### **1.2** Problem Statement

The central concern of this thesis is the implementation of an economical hardware circuit for DOCSIS receiver testing that is capable of replacing the need for a commercial RF emulator. Fully digital testing of different equalization, frequency, and timing recovery circuit implementations is the primary motive for creating the channel emulator. Frequency recovery and equalization are implemented with digital signal processing (DSP) algorithms that are most easily tested with a direct digital signal.

A stringent theoretical treatment of each building block in the emulator design is not the goal of this thesis, as the works of others are cited throughout. The aim is instead to accurately mimic a practical RF multipath channel in a digital emulator implemented on an FPGA. The focus is optimizing the hardware economy of the emulator. With this consideration, appropriate measures are taken to reduce the number of multipliers required by the components inside the emulator by taking advantage of the large number of registers available in the device. For example, successive approximation algorithms are used in the place of hardware multipliers wherever suitable. Such an approach inevitably increases the register count and debug time of the system, but this is generally outweighed by the multiplier savings that are realized. Furthermore, development of a digital in-circuit emulator is a one-time cost in terms of development time and procurement. The emulators can be instantiated concurrently in multiple FPGAs at no additional per-unit cost.

This thesis proposes an alternative method for hardware receiver testing that is much less costly than conventional emulation. It proposes using the approach outlined in [18] to integrate the QAM modulator and channel emulator into a single structure, thus forming a complex baseband equivalent of the RF channel. Channel modelling is applied at complex baseband, thus eliminating the need for RF upconversion. The reduced baseband sampling rates allow a high level of multiplier time-sharing. The proposed architecture is also easily modified to suit the needs of different channel conditions (i.e. more signal paths, variation of parameters with time, different modulation schemes, etc.). Such an integrated modulator/emulator is an economical structure that is small enough (in terms of device resources) to reside in the same FPGA as the receiver under test, making it a cost-effective alternative to a commercial RF channel emulator.

#### **1.3** Thesis Outline

Beginning with Chapter 2, the fundamentals of modelling a general communications channel are addressed. The notion of a complex baseband equivalent channel is developed as it is a means of obtaining an economical channel emulation. Deficiencies commonly encountered in CATV channels are then investigated one at a time and incorporated into the model.

In Chapter 3, the proposed hardware structure is presented in detail. This begins with an explanation of the conventions used in the schematic diagrams followed by a list of the various clock frequencies used in the system. Next, the overall system architecture is examined with a functional description of the system followed by a block diagram of the architecture. Key circuits that are central to the operation and efficiency of the system are presented by first discussing the motivation for their inclusion. Detailed schematics and functional descriptions

of these key circuits are then provided.

Chapter 4 is a vital part of this thesis, as the DOCSIS specification is used to determine the parameters and performance capabilities of the emulator. The relevant protocols and processing techniques used in DOCSIS-compliant systems are examined as are their effects on the MER of the received signal. Special emphasis is placed on the channel echoes and their effect on the signal quality. The MER to be achieved by the emulator is determined by establishing a noise budget for the system. Finally, the MER goal and DOCSIS spectral mask limits are used to determine the appropriate pulse shaping filter configurations to be used in the emulator.

Practical implementation considerations and emulator performance are presented in Chapter 5. Specifically, the compromises that were made in the design process are discussed, followed by an examination of the equipment and methods used for testing and verification of the system. The performance of a few critical circuits is scrutinized, followed by an examination of the best-case MER performance achieved by the implementation.

Finally, Chapter 6 sums up the document, recaps the results, and ends with some remarks regarding the flexibility of the proposed channel emulator structure to future enhancements. It is demonstrated that a complex baseband channel emulation can be feasibly implemented in the same hardware fabric as the receiver under test, expediting the testing of the receiver DSP circuitry.

## 2. Channel Modelling

A typical CATV network consists of many miles of coaxial cable, bidirectional amplifiers, subscriber taps, and CMTS equipment located at the head-end. A fully functioning CATV network cannot be used for testing as doing so would disrupt normal service. Alternatively, building a duplicate network solely for testing is too expensive and too difficult to reconfigure for a different set of channel conditions. For these reasons the CATV network, or channels therein, are either emulated in hardware or simulated in software according to a mathematical model of the channel.

A test platform that accurately models the channel is crucial for debugging and testing a communication system. The shortcomings of a system may not surface until a realistic channel is encountered. For instance, the adaptive equalization and automatic gain control circuits of a receiver cannot be adequately tested without using the kind of channel that would be typically encountered. The development of a realistic CATV channel model is the focus of this chapter.

#### 2.1 Methodology

Before discussing RF channel emulation, it is important to understand that the informationbearing component of the RF signal can be expressed as a complex baseband signal. Besides mathematical convenience, this complex baseband equivalent is used in hardware. Rather than performing a DSP function at passband (i.e. at RF), the function can be implemented on the complex baseband equivalent signal. Performing the signal processing at baseband is much more efficient as it can be done at a lower sampling rate.

As addressed in [19], a passband signal can be represented by a complex low-pass band-

limited signal,  $\mathbf{s}(t)$ , that modulates a complex sinusoidal carrier  $e^{j\omega_o t}$  with center frequency  $\omega_o$ . The complex baseband equivalent is related to the RF signal by the following relation,

$$\mathbf{p}(t) = \Re \left\{ \mathbf{s}(t)e^{j\omega_o t} \right\},\tag{2.1}$$

where the symbol  $\Re$  denotes the real part of the complex argument. As the desired RF signal  $\mathbf{p}(t)$  is real, a well known property of complex numbers can be used to recast 2.1 in a different form. Given a complex number,  $\mathbf{a}$ ,

$$\Re \left\{ \mathbf{a} \right\} = \frac{1}{2} \left( \mathbf{a} + \mathbf{a}^* \right), \qquad (2.2)$$

where  $\mathbf{a}^*$  denotes the complex conjugate of  $\mathbf{a}$ . Applying this to 2.1 gives

$$\mathbf{p}(t) = \frac{1}{2}\mathbf{s}(t)e^{j\omega_o t} + \frac{1}{2}\mathbf{s}^*(t)e^{-j\omega_o t}.$$

(2.3)

This equation represents a real RF signal as the sum of 2 complex conjugate signals. This representation is a useful starting point for developing the channel model since it is this signal that becomes distorted during transmission.

#### 2.2 Time Delay

Echoes due to multipath can be modelled using time delays, the implementation of which will be discussed in Chapter 3. Given a function of time, say  $\mathbf{p}(t)$ , a constant time delay of  $\tau$  can be applied to the signal, which is represented by  $\mathbf{p}(t - \tau)$ . Time delay affects both the baseband (envelope) and passband (carrier) signal components of a complex baseband equivalent. A delayed RF signal can be expressed as

$$\mathbf{p}(t-\tau) = \frac{1}{2}\mathbf{s}(t-\tau)e^{-j\phi}e^{j\omega_o t} + \frac{1}{2}\mathbf{s}^*(t-\tau)e^{j\phi}e^{-j\omega_o t},$$

(2.4)

where  $\phi = \omega_o \tau$  is the constant carrier phase shift due to the time delay. Since the phase shift factors are also complex conjugates, 2.3 holds and the delayed RF signal is also real. It is clear that the phase shifts can be decoupled from the carrier signal and included with the complex low-pass component of the signal.

As demonstrated in the next section, this representation allows multiple complex baseband paths to modulate a common RF carrier signal for a baseband channel emulation.

#### 2.3 Multipath

The development of a multipath channel model is an extension of the concept of time delay presented in the previous section. In this thesis, multipath is viewed as a composite signal consisting of the sum of a main path and several echoes where the delay times and power in the echoes are with respect to the main path. Without loss of generality, the main path is assumed to have unity gain and no delay.

To better understand the scenario of interest suppose the main path,  $\mathbf{p}(t)$ , is combined with 3 echoes to form a multipath RF signal. The time delayed signals are attenuated and added to the main signal to form  $\mathbf{r}(t)$ , which has

$$\mathbf{r}(t) = \mathbf{p}(t) + A_1 \mathbf{p}(t - \tau_1) + A_2 \mathbf{p}(t - \tau_2) + A_3 \mathbf{p}(t - \tau_3).$$

(2.5)

The echoes have gains  $A_n$  and delays  $\tau_n$ . The effect of the time delay on each path is decoupled from the complex sinusoid allowing a sum of baseband paths to modulate a single complex carrier. For an RF signal exposed to M + 1 paths, multipath is expressed as

$$\mathbf{r}(t) = \mathbf{p}(t) + \sum_{n=1}^{M} A_n \mathbf{p}(t - \tau_n).$$

(2.6)

At this point an important distinction must be made. The term multipath is often associated with wireless transmissions, where the multiple paths are physically separate [20]. Frequently such wireless multipath signals contain many signal paths with only a very small variation in the gain and delay — there is no dominant main path. This is in contrast to the upstream portion of a CATV network, where the multiple paths exist on the same physical medium and have a dominant main path component. The multipath phenomenon is referred to as micro-reflections by the DOCSIS physical layer specification [11]. Going forward, any reference to multipath is intended to mean micro-reflections on a CATV network.

#### 2.4 Thermal Noise

Thermal noise, which is an impairment common to all communication systems, is additive zero-mean noise. The spectrum of such noise is essentially flat, meaning the power in an interval depends only on the length of the interval and not the frequency at which it is located [21]. Noise with a flat spectrum is referred to as white noise, in reference to white light containing all frequencies in the visible spectrum. Thermal noise has an amplitude distribution that is Gaussian. Since it is also additive it is commonly referred to as additive white Gaussian noise (AWGN).

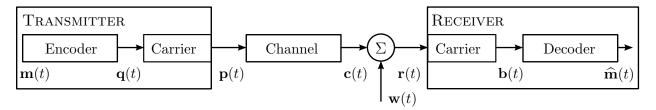

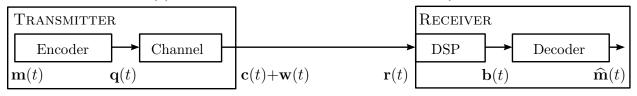

A block diagram of a general passband communication system is shown in Figure 2.1a. The AWGN is added to the signal at the channel output. The transmitter and receiver blocks are depicted with carrier blocks that represent the up/down conversion to/from RF. Here  $\mathbf{m}(t)$  is the message data,  $\mathbf{c}(t)$  is the channel output,  $\mathbf{w}(t)$  represents the AWGN signal, and  $\mathbf{r}(t)$  is the signal that is received. The additional signals are as follows:  $\mathbf{q}(t)$  is the encoded signal,  $\mathbf{p}(t)$  is the RF signal,  $\mathbf{b}(t)$  is the baseband signal, and  $\hat{\mathbf{m}}(t)$  is the decoded message signal, which is a corrupted and distorted version of what was sent by the transmitter.

From Figure 2.1a, a digital representation of thermal noise  $\mathbf{w}(t)$  must be injected. Frequency conversion to digital RF requires a higher sampling rate than than the baseband signal. Thermal noise along with the other channel impairments can be emulated at complex baseband. This is advantageous as it requires less hardware primarily due to the lower sampling rate. This is shown in Figure 2.1b where the channel is shown inside the transmitter at baseband. Note that  $\mathbf{p}(t)$  is no longer in the figure as all paths have been accounted for by the baseband equivalent channel and are implicitly included in  $\mathbf{c}(t)$ . The model of Figure 2.1b has no RF upconversion or downconversion so the input to the DSP portion of the receiver is a complex baseband signal.

(a) A Generalized Passband Communication System

(b) A Complex Baseband Equivalent System

Figure 2.1: Equivalent Structures

#### 2.5 Carrier Frequency Offset

Communication systems are designed in a way that requires the receiver to synchronize to the carrier. As the transmitter and receiver are physically separate devices, they use independent crystal clock oscillators so the receiver cannot be synchronized to a carrier generated in the transmitter. The frequency offset caused by independent reference crystals must be found and corrected by the DSP portion of the receiver.

Frequency offset is caused by components located inside the transmitter and receiver circuits rather than by the channel itself. While offset is normally encountered, the situation is different if the transmitter and receiver are implemented on a single FPGA and are referenced to the same crystal oscillator. In this case the complex baseband equivalent channel must include a special circuit to simulate the frequency offset. When expressed in terms of  $\mathbf{c}(t)$  and  $\mathbf{w}(t)$  this has

$$\mathbf{r}(t) = \mathbf{c}(t)e^{j\Delta\omega_o t} + \mathbf{w}(t), \qquad (2.7)$$

where  $\Delta \omega_o$  is the intentional frequency offset. A complex multiplication is applied to the channel normally located at baseband (i.e. when  $\Delta \omega_o = 0$ ) in order to induce the desired frequency offset.

#### 2.6 Incorporating Adjacent Channels

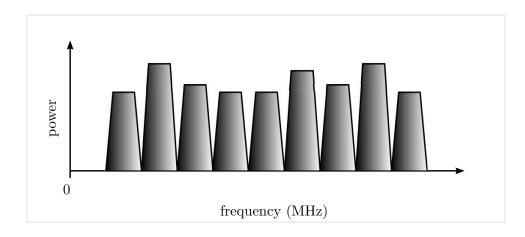

The upstream spectrum of a CATV network has a limited bandwidth and contains many tightly packed channels with power gains that can vary significantly. The combination of signals with large power gains in close proximity creates interference referred to as adjacent channel interference (ACI), which hinders the receiver.

Receiver performance can be more thoroughly tested if multiple channels are included in the model since a well designed receiver filter should remove them. Only the channels closest to the channel of interest (COI) have a significant effect, so only these adjacent channels are included in the model. Suppose the received signal is a complex baseband signal containing the COI, noise, and adjacent channels on either side of the COI. This is expressed as

$$\mathbf{r}(t) = \mathbf{c}(t)e^{j\Delta\omega_o t} + \mathbf{c}_1(t)e^{j\omega_1 t} + \mathbf{c}_2(t)e^{j\omega_2 t} + \mathbf{w}(t), \qquad (2.8)$$

where the complex baseband components of the adjacent channels and the COI are  $\mathbf{c}_1$ ,  $\mathbf{c}_2$ , and  $\mathbf{c}$ , respectively. These have been frequency shifted to center frequencies  $\omega_1 < \Delta \omega_o < \omega_2$ and in general,  $|\Delta \omega_o| \ll |\omega_n|$ . This creates a stack of 3 channels at complex baseband.

Although some of the methodologies of this chapter can be used to develop a general channel model for any application, the particular model presented here only applies to a wired CATV channel. This model cannot be used for a wireless communication channel as different physical phenomena and processes are encountered. For example, wireless channels are subject to specific types of signal drops, referred to as fading, which are not accounted for by the model developed in this chapter.

Having laid the foundation for the channel model which will be used going forward, a more detailed view of the channel emulator implementation can be provided. The next chapter explores the architecture used to implement the channel model presented in this chapter. The DOCSIS 3.0 physical layer specification will be examined later in Chapter 4, as the upstream channel conditions defined by this document are used to define the operational parameters of the channel emulator.

### 3. System Architecture

This chapter begins with a description of the schematic conventions to be used in this thesis. An overview of the emulator operation is provided next as a basis for an examination of key circuits within the emulator. The key circuits are either central to the overall operation of the channel emulator or have been structured with hardware cost in mind. Although many other important circuits are required to enable correct operation of the emulator, discussion of these circuits is deferred to Appendix A.

Before discussing the hardware specifics it is necessary to establish the notational and labelling conventions that are used in schematic diagrams:

- Signals marked clr go to the 'clear' input of all registers and are not shown explicitly connected.

- Clock connections to circuits and registers are omitted where such connections are obvious from the context. Circuits with multiple clock inputs are indicated with numbers beside the clock caret to match the corresponding clock signal.

- Data inputs to registers are shown with arrow tips.

Wherever possible, commonly used schematic and digital logic gate symbols are used in the diagrams. A diagram of the symbolic conventions used in the schematics is shown in Figure 3.1. As depicted, all sequential modules have one or more clock carets to indicate clock ports. Combinational modules have no such carets.

As is shown in Figure 3.1, different signal formats are used in the schematics. Some are shown with a single number while others have two numbers separated by a period.

Figure 3.1: Conventions for Hardware Schematic Diagrams

The meanings of these signal formats are discussed here. First consider the single number format. Unless otherwise indicated in the schematics, a single number signal format is to be interpreted as an unsigned integer. For example, the signal format 4 refers to a signal that can have integer values from 0 to 15.

The interpretation is a little more complicated for the two number signal formats. Unless otherwise indicated in the schematics, these signals are to be interpreted as signed mixed format signals. That is to say, they are two's complement numbers with an integer component and a fractional component. The integer component of the signal is located to the left of the period and includes the sign bit. The fractional component is located to the right of the period. For example, consider a 2.6 signal format. This being a signed number, the most significant bit (MSB), which is the leftmost bit, has a value of -2. The next bit to the right has a value of +1. These are both of the integer bits in the signal. To the right of the period are the fractional bits. These have values  $+2^{-1}$ ,  $+2^{-2}$ ,  $+2^{-3}$ ,  $+2^{-4}$ ,  $+2^{-5}$ , and  $+2^{-6}$  respectively. Thus this signal format can accommodate values from -2 to  $2 - 2^{-6}$ .

Truncation and rounding operations are denoted by diamond and circle symbols, respectively. Consider the truncation shown in Figure 3.1. The input signal format is 4.12, while there are two output formats: 4.8 and 4. Here the 4 least significant bits (LSB), which are fractional bits, are trimmed from the signal, leaving 8 fractional bits remaining in the trimmed signal. The rounding shown here also has 4 fractional bits removed. Rounding of fixed point binary numbers is identical to rounding of decimal numbers. If the MSB of the bits being removed is a 1, then a 1 is added to the LSB of the remaining bits. Otherwise the remaining bits are unaltered. For example, suppose the 8-bit binary number 10010111 is rounded to 6-bits, with the 2 LSBs being removed. Since the MSB of 11 is 1, then 100101 + 000001 = 100110 gives the result after rounding.

Clock name conventions are based on multiples of the symbol rate. For example, clocks clk1, clk2, clk8, and clk16 operate operate at 1, 2, 8, and 16 samples/symbol, respectively. Clocks n\_clk8 and n\_clk16 are inverted with respect to their counterparts. A list of the clocks used by the top level of the emulator, their phases, and associated connection codes is given in Table 3.1.

| Clock Name | Frequency (MHz) | Phase (rad) | Connection Code |

|------------|-----------------|-------------|-----------------|

| clk1       | 5               | 0           | 0               |

| clk2       | 10              | 0           | 1               |

| clk8       | 40              | 0           | 3               |

| n_clk8     | 40              | $\pi$       | 4               |

| clk16      | 80              | 0           | 5               |

| n_clk16    | 80              | $\pi$       | 6               |

| clk32      | 160             | 0           | 7               |

Table 3.1: Clocks Used in Top Level of Channel Emulator

The on-board 100 MHz clock provides a reference for the phase-locked loop (PLL) circuit which generates the system clock signals for the emulator. This circuit instantiates the Altera IP generated by the ALTPLL megafunction.

# **3.1** Top Level Emulator Architecture

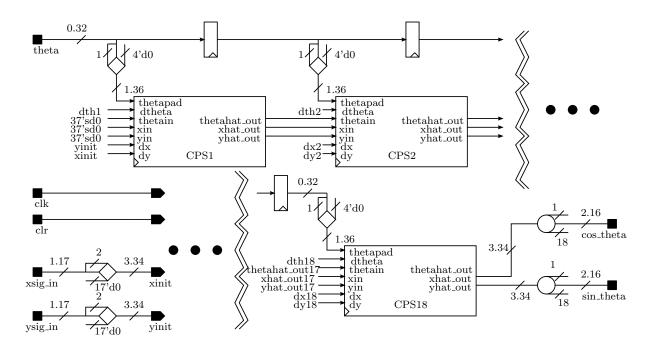

The top level of the hardware structure is presented first since it provides a good overall picture of the emulator operation. As is shown in Figure 3.2, the emulator architecture and operation are quite complex and require substantial explanation. The function of each major component shown in the figure is briefly described in the next subsection, and Figure 3.2 is referenced frequently.

# 3.1.1 Operational Overview

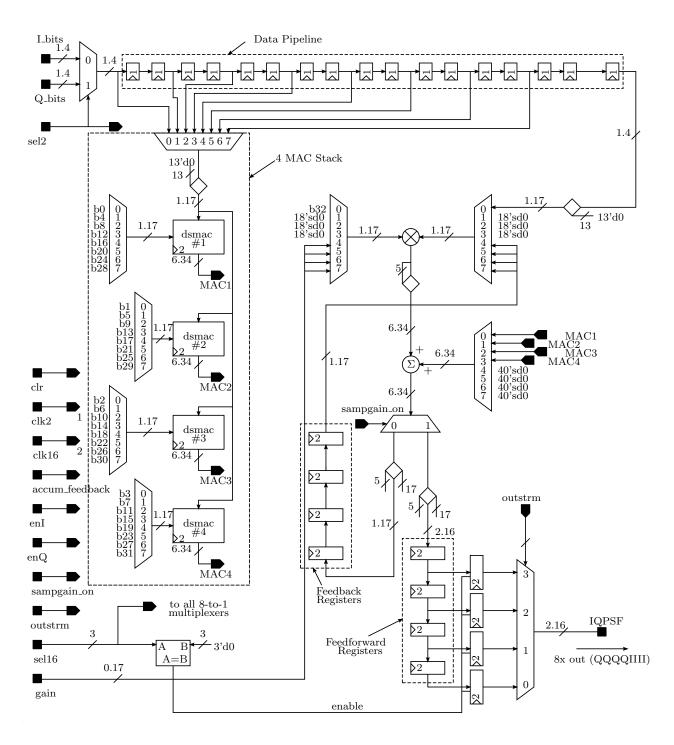

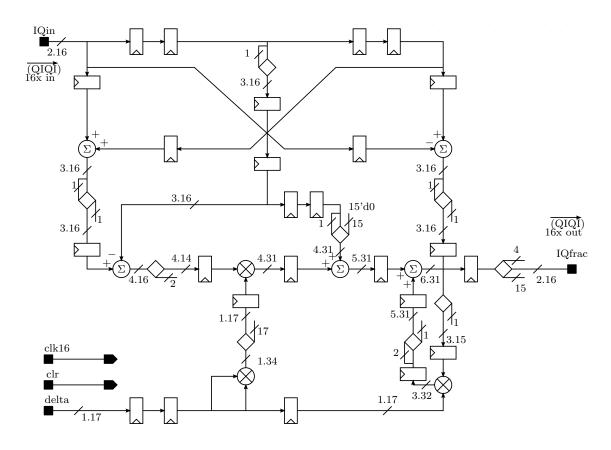

#### Loading the Parameters

Upon power-up/reset, which is initiated by pressing button\_0, one of 4 user-programmable channel profiles is loaded from memory. There are 31 memory slots for channel parameters and loading these takes 2 symbol periods. The rest of the circuit does not begin operation until these 2 symbol periods have elapsed. Registers in the load parameters circuit (located at the top of Figure 3.2) hold the values cycled in from memory and provide them as inputs to other circuits. Any time the user changes parameters in the selected memory or selects a different channel profile with switches SW[1:0], the registers are updated within two symbol periods.

#### Main Channel Transmit Data

Once channel parameters are loaded from memory, the main channel transmit data circuit (located in the upper left corner of Figure 3.2) takes over and begins reciting the preamble symbol data for the chosen main channel modulation mode. This preamble can be up to 256 symbols long and is user-programmable. A unique preamble can be programmed for each modulation scheme, with the same preamble being used for both the low-power and high-power QPSK modes. Upon completion of the preamble, the pseudorandom data generator begins generating raw (unmodulated) symbol data with an approximately uniform distribution. At the same time, a 6-bits/word by 65536 word RAM is enabled to store the generated data for off-line MER analysis.

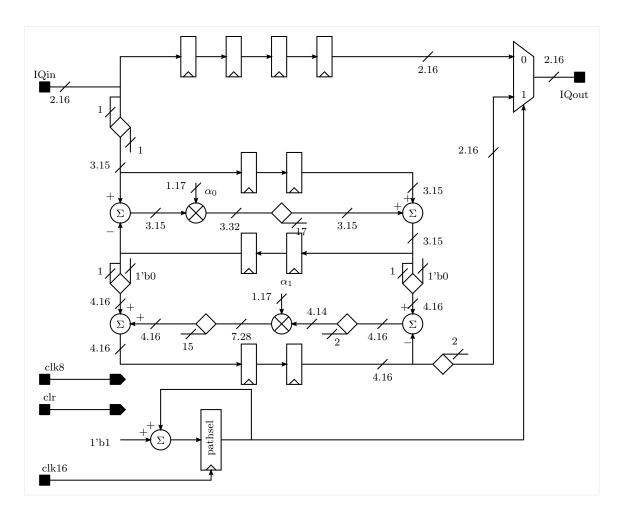

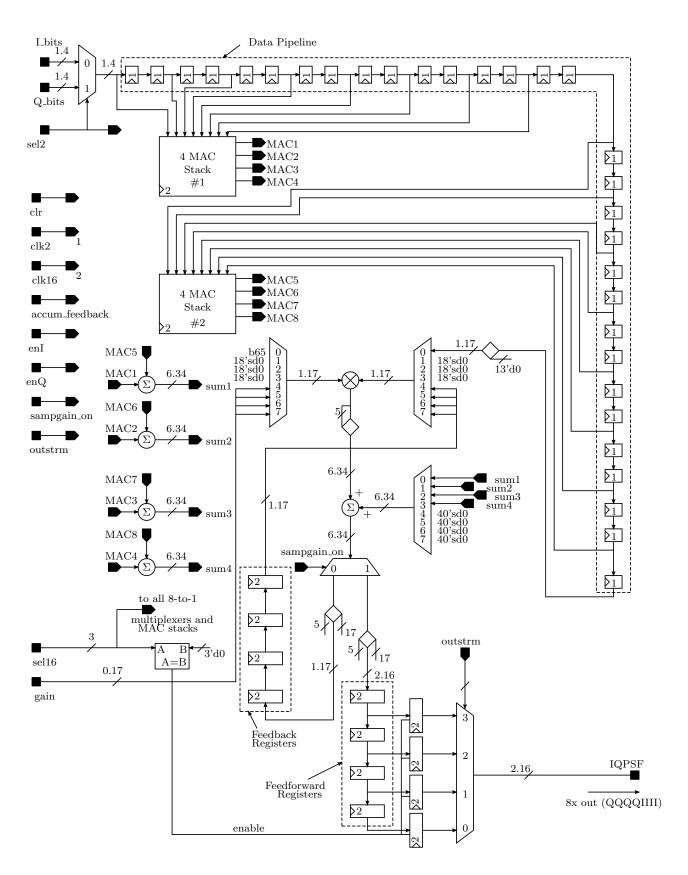

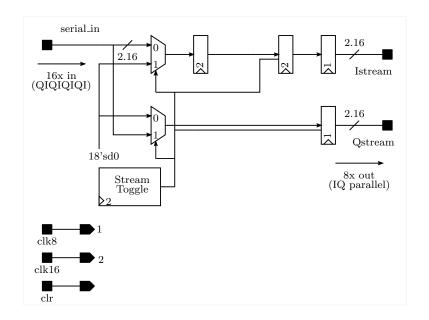

Figure 3.2: Schematic for Top Level of Channel Emulator

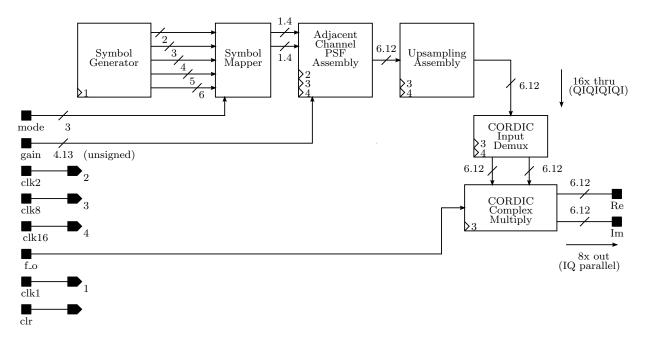

The preamble and generated data are mapped to constellation points by the symbol mapper. The symbol mapper encodes the raw symbol data into two streams (I and Q) of numbers in signed format with 1 integer bit and 4 fractional bits, which is referred to as 1.4 signed format. It is this complex stream that is used to modulate the I and Q carriers. Independent data must also be generated and mapped for each of the adjacent channels, but is much simpler than in the main channel since there is no need for a preamble. Furthermore, as these channels are not demodulated there is no need to store the generated data for analysis so no RAM module is included. This means the transmit data circuits for adjacent channels simply consist of a symbol data generator and a symbol mapping circuit.

#### Pulse Shaping the Symbol Stream

The mapped symbols proceed to the pulse shaping filter (to the right of the transmit data circuit) where the I and Q components are multiplexed into a single serial stream. This single structure performs the required spectral shaping on two independent streams of data, thus eliminating the need for duplicate parallel filter structures.

### Upsampling by 2

The channel emulator must accommodate adjacent channels. This is done by generating 3 I-Q pairs of baseband signals at 4 samples/symbol and then upsampling each of these to 8 samples/symbol (i.e. 40 MHz clock) before frequency shifting. Doing so doubles the bandwidth available to the 3-channel stack. The output of upsampled I-Q pairs are interleaved (multiplexed) to make a single stream operating at a clock rate of 80 MHz. The upsampling assembly is located in the center of Figure 3.2, directly beneath the load parameters circuit.

## Echo Paths

The upsampled output is then split into 4 paths: a main path and 3 echoes, located at the upper right corner of Figure 3.2. Each echo path delays and attenuates its signal. The main path simply applies a delay to compensate for the latency introduced by the echo paths — it applies no attenuation or variable delay. The echo paths are then summed to form a multipath signal. The structures in the echo paths are also multiplexed to reduce hardware requirements.

## **CORDIC** Input Demultiplexer

The CORDIC complex multiplier located beneath the echo path adder requires that the quadrature signal components be parallel rather than multiplexed. The CORDIC input demultiplexer takes the multiplexed I and Q samples as an input at a rate of 16 samples/symbol (80 MHz). The output is the parallel I and Q streams with a sample rate of 8 samples/symbol (40 MHz), making this module a serial to parallel converter.

#### **CORDIC** Complex Multiplication

Once demultiplexed, complex multiplication is performed on the baseband signal. Complex multiplication is commonly implemented using a ROM-based quadrature numerically controlled oscillator (NCO) and a pair of signed multipliers. An alternative approach is to implement a pipelined successive approximation circuit such as a CORDIC to realize the quadrature NCO. The CORDIC pipeline is initialized with the I and Q components of the signal being frequency shifted, thus eliminating the need for the hardware multipliers. Complex multiplication is performed on the adjacent channels as well as the main channel.

#### Main Channel Gain Boost

Located beneath the complex multiply circuit in Figure 3.2, the main channel gain boost is provided as a means of quickly increasing main channel gain without the need to edit the RAM. The default gain for the main channel is 0 dB. The DIP switches DIP[7:5] are provided for the user to implement main channel gains of +6, +12, or +18 dB if desired.

# **Channel Stacking**

After the 3 signals have been frequency shifted to the appropriate center frequencies, they are summed to form a single 3-channel FDMA signal at complex baseband, as depicted by the vertical stack of quadrature adders on the right side of Figure 3.2. Adjacent channels are toggled on or off by the user with SW[2].

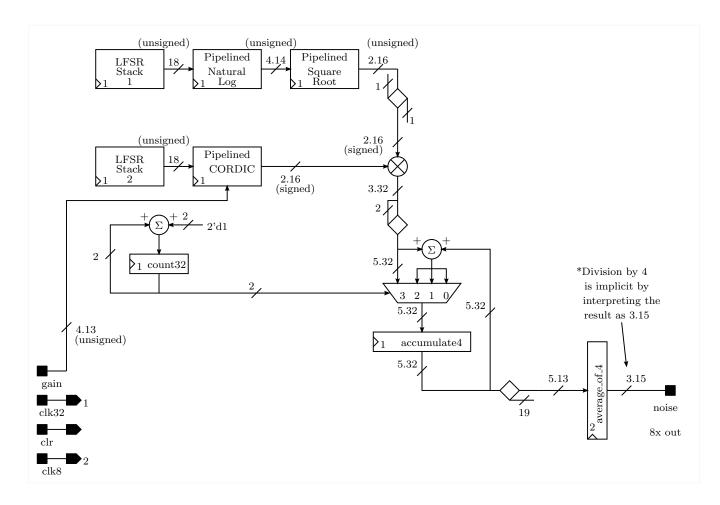

#### **Complex AWGN Generator**

The baseband channel stack is then added to complex AWGN from the thermal noise generator, forming the noise-laden 3-channel FDMA stack. This noisy signal constitutes the output of the channel emulator — the desired test signal. The generated noise floor spans the full 3-channel spectrum, with the specified SNR referenced from the main channel (i.e. the COI). Using main channel gain boost will therefore increase the SNR by 6, 12, and 18 dB respectively. The noise is toggled on or off by the user with SW[3].

## **Output Signal RAM**

Upon completion of power-up/reset and load parameters, the complex output RAMs (located at the bottom of Figure 3.2) are enabled and the first portion of the signal (i.e. the preamble and some data) is captured. The cumulative effects of all user settings (profile parameters, gain boost, and toggle switches) are accounted for in the captured signal. This RAM is provided for channel emulator performance measurements and is not necessary for a receiver testing scenario.

The noisy complex output signal is captured for 65536 samples at 8 samples/symbol. This allows analysis of a packet consisting of approximately 8000 symbols. Increasing the output storage capacity by using 8 pairs of page indexed RAM blocks would allow analysis of close to 65536 symbols, which is the number of symbols captured by the main channel transmit data circuit for MER analysis. The signal RAM word size is 22-bits for each of the real and imaginary components. Once the RAM is full, writing to RAM is disabled so that the preamble portion does not get overwritten, as it is useful in testing and verification. The captured data is saved to memory initialization files (MIF) on a PC and converted off-line<sup>1</sup> for analysis in MATLAB.

<sup>&</sup>lt;sup>1</sup>Executable file mif\_convert.exe written by Rory Gowen, University of Saskatchewan, 2013.

#### LED Indicators

A few of the different functions of the channel emulator are indicated with LEDs to make the emulator interface more user friendly. The most important of these indicators is the dual 8-segment LED display located on the upper left corner of the DE4 development board. This display shows which of the 4 channel profiles is selected by displaying P1, P2, P3, or P4. The decimal points are only lit when the adjacent channels are toggled on with SW[2]. For example, if channel profile 2 is selected (i.e. SW[1:0]==2'b01 and adjacent channels are on (SW[2]==1'b1), then P.2. will be displayed.

There are 8 green LEDs located to the right of the dual 8-segment LED display. The right-most of these, labelled LEDG[0], will be lit only when the AWGN is toggled on with SW[3].

# 3.2 Key Circuits

# 3.2.1 Loading and Editing Channel Profiles

#### **Background and Motivation**

As with any user controlled equipment, the interface between the user and the hardware is very important. The DE4 development board contains a very powerful FPGA but, unfortunately, has relatively few switches and displays connected to the FPGA. This means the channel parameters cannot be entered through these switches. This necessitates the use of a JTAG interface<sup>2</sup> to edit the channel parameters.

Switches SW[1:0] on the DE4 board are used to select one of 4 preset channel profiles from internal memory. The parameters in memory are edited through the JTAG interface which can be accessed through the Quartus II software. The interface is set up this way to allow the user to quickly select one of the 4 profiles preprogrammed into the memory.

<sup>&</sup>lt;sup>2</sup>Joint Test Action Group (JTAG) interface is a circuit embedded in the FPGA which provides access to the contents of RAM modules instantiated in the FPGA. The RAM contents can be written/read to a PC through this interface.

Figure 3.3: Schematic for Load Parameters Circuit

A circuit was designed that fetches channel parameters from memory and presents them to the various emulator circuits. The circuit is, in essence, a serial to parallel converter since it takes consecutive values made only briefly available by the RAM and turns them into parallel outputs that are held in a set of parameter registers. While transferring memory contents to the parameter registers after a power-up/reset, a pulse is generated to reset the channel emulator. This ensures all circuits have received the parameters needed for correct operation. The load parameters circuit is shown in Figure 3.3.

At the heart of the load parameters circuit are 4 RAM blocks. These RAM are 32bits/word by 32 words (1 kilobit) each as all parameters used in the circuit are at most 32-bits long. The RAM address cycles all 4 RAM blocks simultaneously, which feed a data

Figure 3.4: Timing Diagram for Load Profiles Signal Generator

selector controlled by the user through switches SW[1:0]. Only the RAM selected by the user updates the parameter registers, which hold the parameters until the next update (enable).

#### **Generating Load Signals**

Correct load signal timing is critical for the load profiles circuit. Output registers are enabled one-by-one as the RAM cycles through its contents. A timing diagram for the required load signals is provided in Figure 3.4.

The RAM data and address registers are written on the positive edges of clk16 and the transfer to RAM is done with the negative edge of clk16. This is done so that there is only a single clock edge of delay between the address and the parameter register output.

Once the load parameters circuit detects that the final RAM address has been reached (i.e. ram\_addr==5'd31), it sets the load pulse low and leaves it there until another power-up/reset command is encountered. This means that either the individual RAM parameters

or the entire channel profile can be changed by the user while the emulator is in operation.

#### **Editing Channel Profiles**

When the FPGA is configured with the channel emulator, memory on the FPGA can be written and read through the JTAG interface using the In-System Memory Content Editor while the circuit is operational. This allows the channel profiles to be altered without reconfiguring the device. Unfortunately, the memory content editor needs a very specific data format making it difficult to use.

The memory content editor uses hexadecimal format, but parameters are more meaningful to a user when specified in signed decimal format. For this reason, a MATLAB script was developed to convert signed decimal channel parameters into hexadecimal values to be used in the memory content editor and memory initialization files (MIF). This script, entitled convert4rom.m<sup>3</sup>, converts user-defined channel parameters into equivalent 32-bit hexadecimal representations. Input values with units of Hz, ns, or dB, for example, are used to generate a list of unitless hex parameters to be entered into the memory by the user.

# 3.2.2 Main Channel Transmit Data Circuit

#### **Background and Motivation**

The transmit data circuit for the main channel is the starting point for the signal generated by the channel emulator. Its purpose is to recite the preamble symbol sequence, generate the pseudorandom symbol data, and map these symbols to locations in the complex plane.

#### **Operational Overview**

After the channel parameter registers have been loaded from memory, the main channel transmit data circuit begins operation. This circuit, shown in Figure 3.5, is always in one of two modes. In mode 1, which is the preamble mode, the circuit sequentially transfers the symbols held in the preamble memory to the symbol mapper. Once the circuit has

<sup>&</sup>lt;sup>3</sup>Script file written by Andy Fontaine, University of Saskatchewan, 2013.

transferred the entire preamble it enters mode 2, which is the data mode. In this mode, the circuit generates pseudorandom symbol data to represent a data packet. The circuit stays in data mode until the next power-up/reset.