# DESIGN AND IMPLEMENTATION OF A MODULAR CONTROLLER FOR ROBOTIC MACHINES

A Thesis Submitted to the College of

Graduate Studies and Research

In Partial Fulfillment of the Requirements

For the Degree of Doctor of Philosophy

In the Department of Mechanical Engineering

University of Saskatchewan

Saskatoon

By

#### **RODNEY ATTA-KONADU**

Keywords: architecture, communication, distributed control, embedded, Java, modular, real-time network, reconfigurable, robots, Zeroconf

© Copyright Rodney Atta-Konadu, September, 2006. All rights reserved.

#### **PERMISSION TO USE**

In presenting this thesis in partial fulfilment of the requirements for a Postgraduate degree from the University of Saskatchewan, I agree that the Libraries of this University may make it freely available for inspection. I further agree that permission for copying of this thesis in any manner, in whole or in part, for scholarly purposes may be granted by the professor or professors who supervised my thesis work or, in their absence, by the Head of the Department or the Dean of the College in which my thesis work was done. It is understood that any copying or publication or use of this thesis or parts thereof for financial gain shall not be allowed without my written permission. It is also understood that due recognition shall be given to me and to the University of Saskatchewan in any scholarly use which may be made of any material in my thesis.

Requests for permission to copy or to make other use of material in this thesis in whole or part should be addressed to:

Head of the Department of Mechanical Engineering

University of Saskatchewan

Saskatoon, Saskatchewan (S7N 5A2)

#### **ABSTRACT**

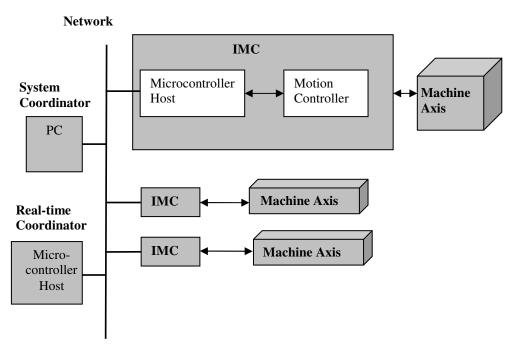

This research focused on the design and implementation of an Intelligent Modular Controller (IMC) architecture designed to be reconfigurable over a robust network. The design incorporates novel communication, hardware, and software architectures. This was motivated by current industrial needs for distributed control systems due to growing demand for less complexity, more processing power, flexibility, and greater fault tolerance. To this end, three main contributions were made.

Most distributed control architectures depend on multi-tier heterogeneous communication networks requiring linking devices and/or complex middleware. In this study, first, a communication architecture was proposed and implemented with a homogenous network employing the ubiquitous Ethernet for both real-time and non realtime communication. This was achieved by a producer-consumer coordination model for real-time data communication over a segmented network, and a client-server model for point-to-point transactions. The protocols deployed use a Time-Triggered (TT) approach to schedule real-time tasks on the network. Unlike other TT approaches, the scheduling mechanism does not need to be configured explicitly when controller nodes are added or removed. An implicit clock synchronization technique was also developed to complement the architecture. Second, a reconfigurable mechanism based on an auto-configuration protocol was developed. Modules on the network use this protocol to automatically detect themselves, establish communication, and negotiate for a desired configuration. Third, the research demonstrated hardware/software co-design as a contribution to the growing discipline of mechatronics. The IMC consists of a motion controller board designed and prototyped in-house, and a Java microcontroller. An IMC is mapped to each machine/robot axis, and an additional IMC can be configured to serve as a real-time coordinator. The entire architecture was implemented in Java, thus reinforcing uniformity, simplicity, modularity, and openness. Evaluation results showed the potential of the flexible controller to meet medium to high performance machining requirements.

#### **ACKNOWLEDGMENTS**

I will like to thank my supervisor Professor Chris Zhang for the generous support and guidance he committed to me. My co-supervisor Dr. Sherman Lang of NRC-IMIT provided key directions, motivations, and support toward this research. I appreciate the guidance and encouragement I received from my committee members Professors Schoenau, Hertz, Gander, and Dr. Peter Orban of NRC-IMIT.

I certainly acknowledge NSERC and the Department of Mechanical Engineering for supporting my PhD work. Most of my research time was spent at the NRC-IMIT where I received part-funding for this project. I thank Mr. Georges Salloum the Director General and Dr. Gian Vascotto (Director) for endorsing this collaborative project. Memories of the congenial IMTI microcosm will linger with me for years to come. I acknowledge the input of Dr. Orban whose pragmatism and prodding had tremendous impact on this work. I note the support of Marcel Verner on many technical issues. Dr. Zhuming Bi gave me great companionship and *bent* the rules a few times to let me in during silent hours. I am very thankful for the companionship and support of IMTI staff such as Susan Salo, Brian Wong, Stan Kowala, Dave Kingston, Steve Kruithof, Lori Cox, Dr. Helen Xie, Millan Yeung, Dr. Lihui Wang, Dr. Weiming, and Mike Meinert. Trent Steensma (UWO Electronics Department) gave me much advice in PCB production. I also benefited greatly from forum discussions with the Java and Systronix communities.

I am exceedingly thankful for the invaluable impact of precious friends, particularly; Nii and Celestina Allotey, Erasmus and Catherine Amoateng, Charles and Agnes Annan, Frank and Cynthia Arku, Ernest and Monica Ansah-Sam, Eddie and Francisca Bansah, Milan Bhasin, Basia Bodzanowski, Brian and Darleen Carter, Joyce Grant, Mobi Emodi, Ron Hampson, Franklin and Bridgette Krampa, Michael and Irene Nketia, Jay and Tammy Nyyssonen, Kwaku and Regina Odei, Felix Oppong, Esther Oppong, Dr. Osei, George and Gertrude Quainoo, Professor Tachie who introduced me to my supervisor, Dr. Jean Yuchuan, my pastors Greg Olson and Howard Katz, and my stepmum Esther. I am thankful to all my family for coping with my protracted *abeyance*, and my dear wife Edwoba for her relentless prayers and support. The Lord Jesus Christ has always been and will always be my life and my resurrection.

### **DEDICATED TO**

My dear wife Edwoba My adorable son Elijah My precious parents Dr. Atta-Konadu and Beatrice Adjei My uncle Jackson (rtd. aircraft engineer) who has inspired me from my pre-school days

# TABLE OF CONTENTS

| PERMISSI                                                                                                                                                                   | ON TO USE                                                                                                                                                                                          | I           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| ABSTRAC                                                                                                                                                                    | Т                                                                                                                                                                                                  | II          |

| ACKNOW                                                                                                                                                                     | LEDGMENTS                                                                                                                                                                                          | III         |

| DEDICAT                                                                                                                                                                    | ED TO                                                                                                                                                                                              | IV          |

| TABLE OF                                                                                                                                                                   | F CONTENTS                                                                                                                                                                                         | V           |

| LIST OF T                                                                                                                                                                  | ABLES                                                                                                                                                                                              | XI          |

| LIST OF F                                                                                                                                                                  | IGURES                                                                                                                                                                                             | XII         |

| LIST OF A                                                                                                                                                                  | BBREVIATIONS                                                                                                                                                                                       | XV          |

| 1. INTROD                                                                                                                                                                  | DUCTION                                                                                                                                                                                            | 1           |

| 1.2 Mo<br>1.3 Gos<br>1.4 Org                                                                                                                                               | erview                                                                                                                                                                                             | 1<br>3<br>4 |

|                                                                                                                                                                            | bot Control Architecture, Introduction                                                                                                                                                             |             |

| 2.2.1<br>2.2.2<br>2.2.3<br>2.2.4<br>2.2.5<br>2.2.6<br>2.2.7<br>2.2.8<br>2.2.9<br>2.2.10<br>2.3 Sof<br>2.3.1<br>2.3.2<br>2.3.3<br>2.3.4<br>2.3.5<br>2.3.6<br>2.3.7<br>2.3.8 | Dealing with Complexity 6  Execution 7 Openness 8 Performance 8 Scalability 9 Simplicity 9 Modifiability 9 Portability 9 Reliability 9 Distributed Real-Time Systems 10 ftware Architecture Styles |             |

| 2.3.10 Mobile Code 14                                                         |            |

|-------------------------------------------------------------------------------|------------|

| 2.3.11 Data Abstraction and Object-Oriented Organization 15                   |            |

| 2.3.12 Event-Based, Implicit Invocation 16                                    |            |

| 2.3.13 Repositories 16                                                        |            |

| 2.3.14 Heterogeneous Architectures 17                                         |            |

| 2.3.15 Rules-of-Thumb for Selecting Styles 17                                 |            |

| 2.4 Taxonomy for Controller Architectures                                     | 18         |

| 2.5 Controller Hardware Architecture Review                                   |            |

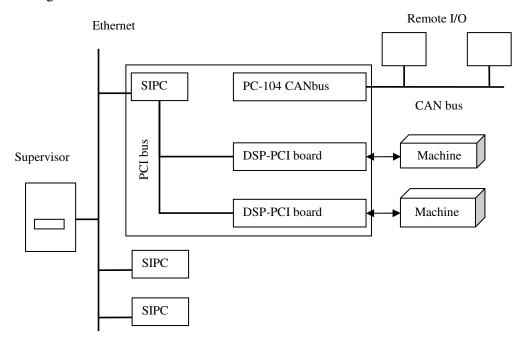

| 2.5.1 WinRec 19                                                               |            |

| 2.5.2 MUPAAC Architecture 20                                                  |            |

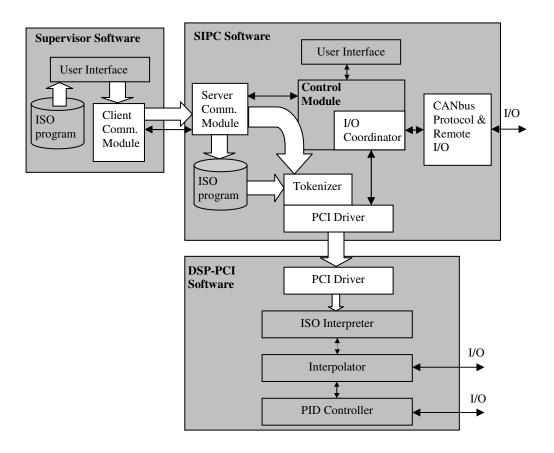

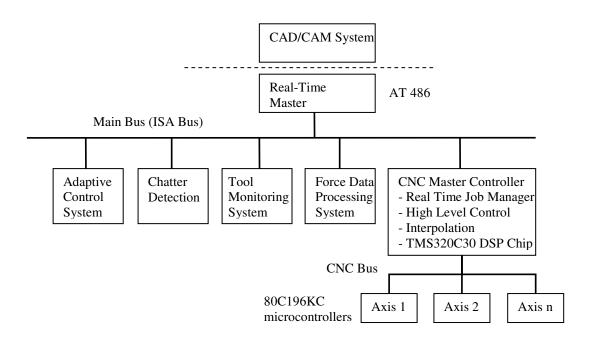

| 2.5.3 Modular CNC System Architecture 22                                      |            |

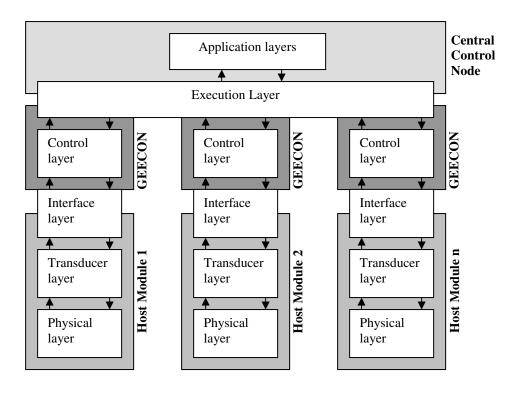

| 2.5.4 GEECON Architecture 24                                                  |            |

| 2.6 Controller Software Architecture Review                                   | 26         |

| 2.6.1 OMAC Architecture API 27                                                |            |

| 2.6.2 UBC Open Architecture Control System 29                                 |            |

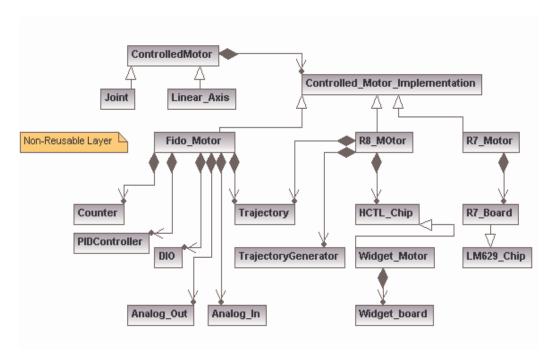

| 2.6.3 NRC Tripod 32                                                           |            |

| 2.6.4 CLARAty Architecture 34                                                 |            |

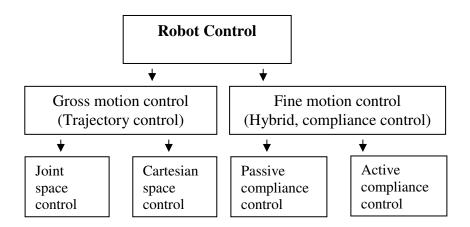

| 2.7 Control Architectures                                                     | 36         |

| 2.7.1 Classic Control 36                                                      |            |

| 2.7.2 Reconfigurable Control Architectures 39                                 |            |

| 2.8 Concluding Remarks                                                        | 42         |

| 3. SYSTEM ARCHITECTURE                                                        |            |

|                                                                               |            |

| 3.1 Architecture Design Philosophy                                            |            |

| 3.2 Intelligent Modular Controller (IMC)                                      | 48         |

| 3.2.1 Interfaces 49                                                           |            |

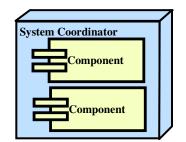

| 3.3 The System Coordinator(s)                                                 |            |

| 3.4 Conclusion                                                                |            |

| 4. EMBEDDED COMPUTING PLATFORM                                                | 51         |

| 4.1 Introduction                                                              | <b>5</b> 1 |

| <ul><li>4.1 Introduction</li></ul>                                            |            |

| 4.2 Java for Real-time System Design                                          |            |

|                                                                               | 55         |

| 4.3.1 The Java Micro Edition (J2ME) 55 4.4 Microcontroller Hardware Selection | 56         |

| 4.4.1 The aJile Processor 57                                                  | 50         |

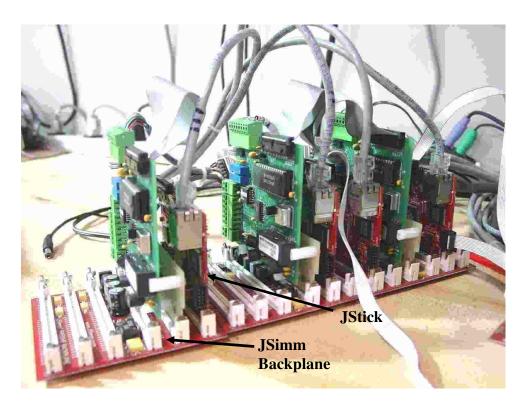

| 4.4.2 The JStick Platform 59                                                  |            |

| 4.4.2 The Joues Flatform 39  4.5 Motion Controller Hardware                   | 60         |

| 4.5.1 Motion Controller Design Options 62                                     | 00         |

| 4.5.2 Motion Controller Board Design Criteria 63                              |            |

| 4.5.3 Motion Controller Chip Selection 64                                     |            |

| 4.6 Conclusion                                                                | 61         |

| 5. MOTION CONTROLLER BOARD DESIGN                                             |            |

| J. MOTION CONTROLLER BOARD DESIGN                                             | 03         |

| 5.1 Introduction                                                              | 65         |

| 5.2 JStick's Peripheral Interface Signals                                     |            |

| 5.2.1 The Phase Locked Loon (PLL) 66                                          |            |

| 5.2.2    | The External Bus Interface 67           |                   |        |

|----------|-----------------------------------------|-------------------|--------|

| 5.2.3    | HSIO Bus Address Space and Tir          | nings 67          |        |

| 5.2.4    | JSimm Interface and Signals 68          | _                 |        |

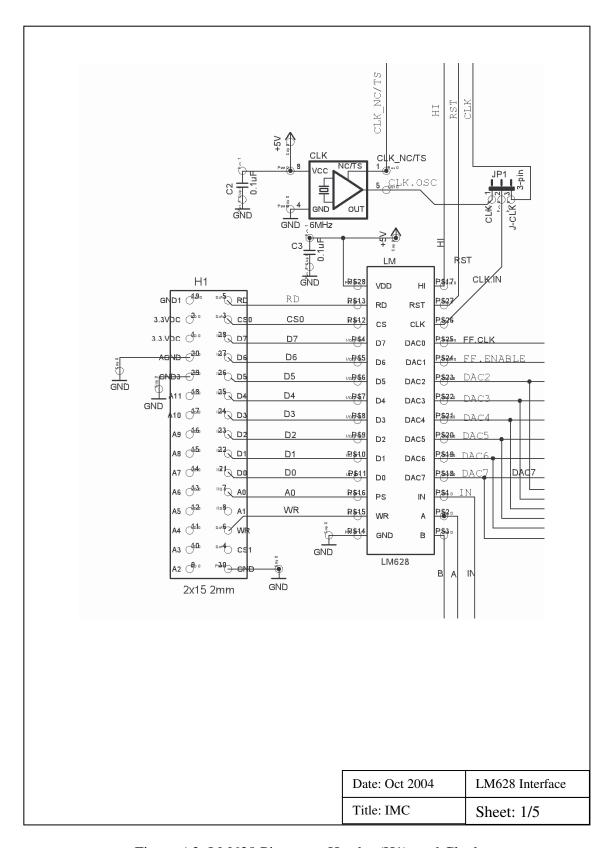

| 5.3 Th   | e Interface Design                      |                   | 68     |

| 5.3.1    | Clocking 74                             |                   |        |

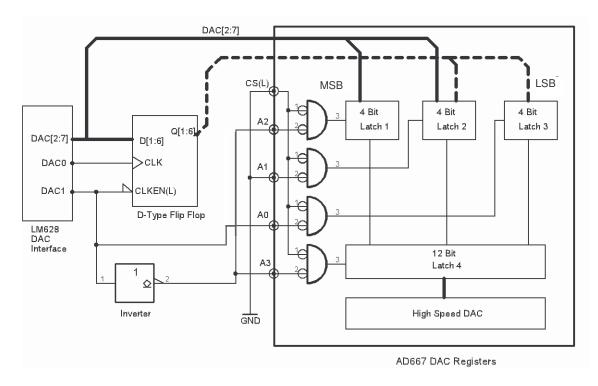

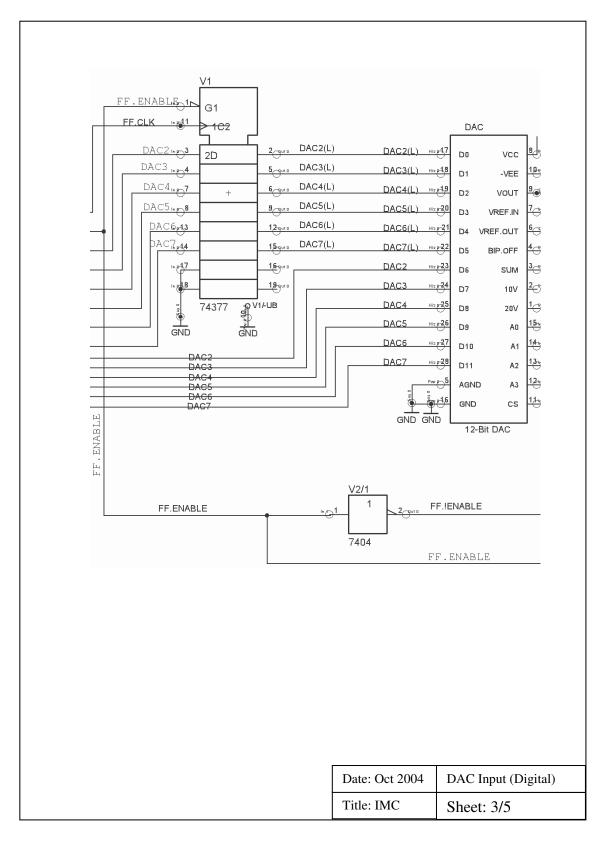

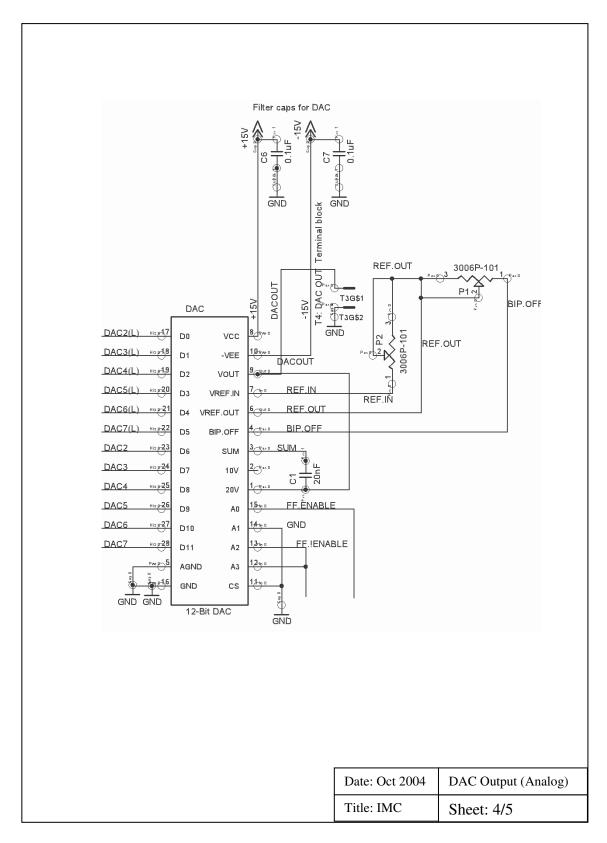

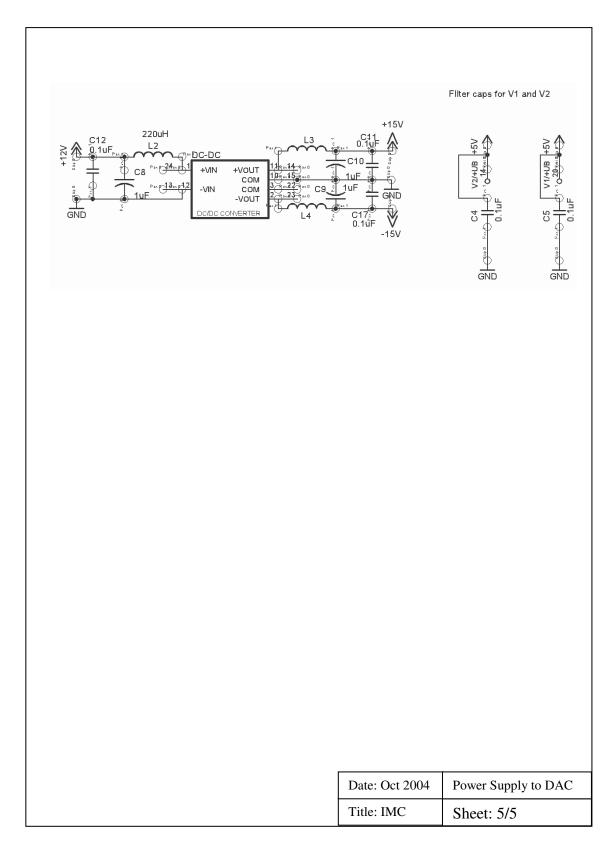

| 5.4 LM   | 1628 DAC Output                         |                   | 75     |

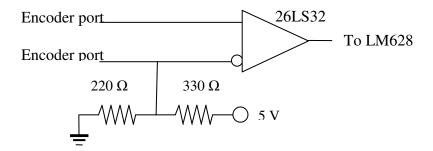

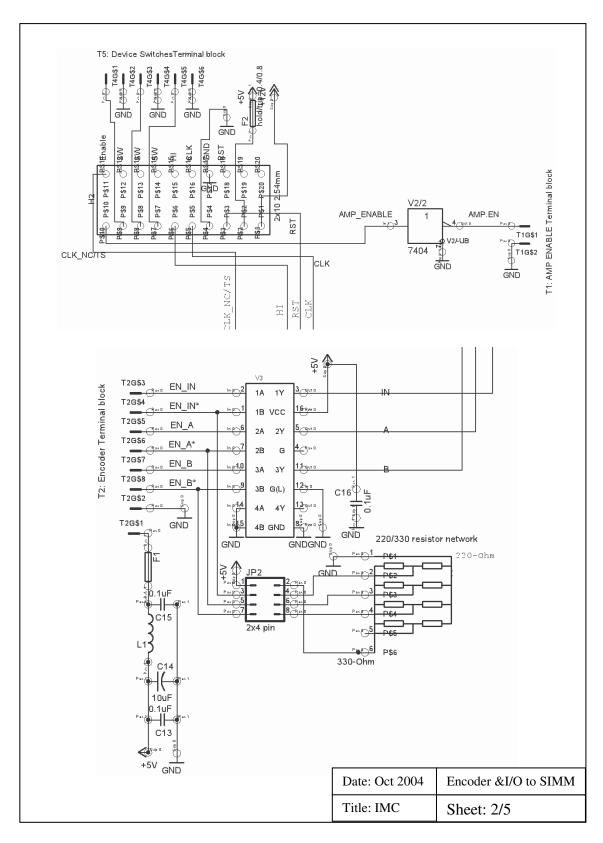

|          | Encoder Interface 78                    |                   |        |

| 5.4.2    | Power Supply and Noise Emissio          | n 78              |        |

|          | Board Schematics 79                     |                   |        |

| 5.4.4    | The LM628 Hardware Driver 79            |                   |        |

| 5.4.5    | Initializing 82                         |                   |        |

| 5.4.6    | Interrupt Service Routines and dig      | gital I/O operati | ons 82 |

|          | nclusion                                |                   |        |

|          | C COMMUNICATION ARCHIT                  |                   |        |

|          |                                         |                   |        |

| 6.1 Int  | roduction                               |                   |        |

| 6.2 Re   | quirements for Real-Time Commu          | nication          | 85     |

| 6.2.1    |                                         |                   |        |

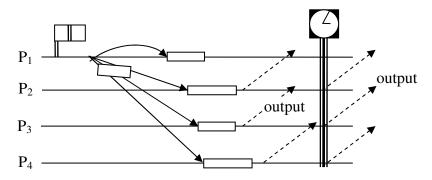

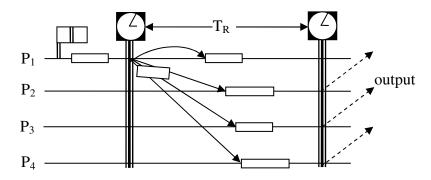

| 6.2.2    | Co-operation Models 88                  |                   |        |

|          | Composability 89                        |                   |        |

| 6.3 Re   | al Time Network Applications            |                   | 90     |

|          | Physical Layer 91                       |                   |        |

|          | Data Link Layer 92                      |                   |        |

|          | Network Layer95                         |                   |        |

|          | Transport Layer Protocols 95            |                   |        |

| 6.3.5    | Application Layer 95                    |                   |        |

|          | tomatic Configuration                   |                   | 96     |

|          | The Zeroconf Protocol 97                |                   |        |

|          | e IMC Communication Architectu          | ·e                | 98     |

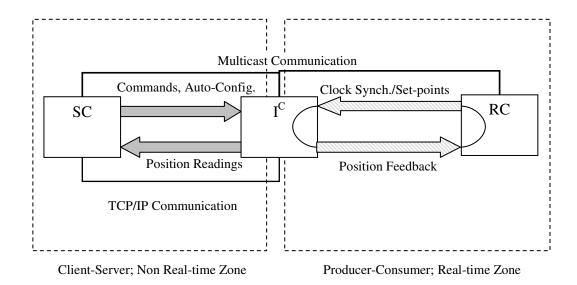

| 6.5.1    | Communication and Computing I           |                   |        |

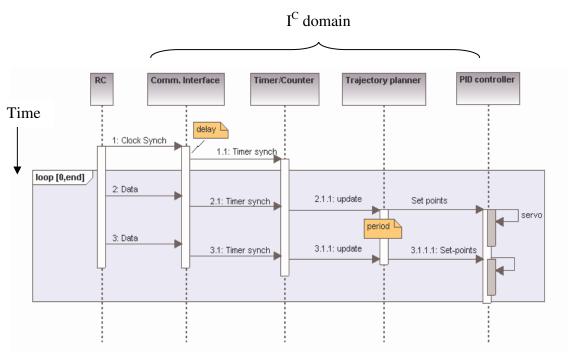

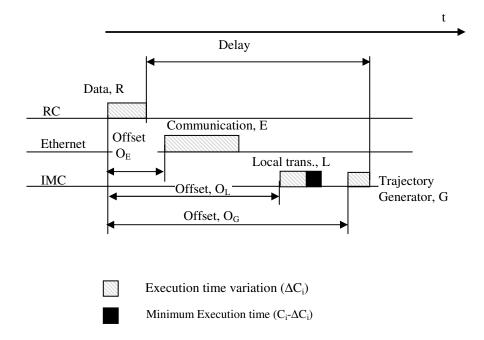

|          | Communication Flow and Control          |                   |        |

| 6.5.3    | Triggering and Scheduling 103           |                   |        |

| 6.5.4    | Automatic Configuration 10'             |                   |        |

|          | nclusion                                |                   | 108    |

|          | SYNCHRONIZATION                         |                   |        |

| 7. CLOCK |                                         | •••••             | 110    |

| 7.1 Int  | roduction                               |                   | 110    |

|          | ne                                      |                   |        |

| 7.2.1    | Properties of Physical Clocks 11        |                   |        |

| 7.2.2    | Global Clocks 112                       |                   |        |

| 7.2.3    | Failure Mode 113                        |                   |        |

|          | e Synchronization Problem               |                   | 113    |

| 7.3.1    | Internal Synchronization 114            |                   | 110    |

| 7.3.2    | External Synchronization 11:            |                   |        |

|          | e IMC Clock Synchronization Arc         |                   | 117    |

| 7.4.1    | Assumptions and Properties 11           |                   | 117    |

| 7.4.2    | Analysis 119                            |                   |        |

| , , 1,2  | 111111111111111111111111111111111111111 |                   |        |

| 7.5    | Conclusion                                                          | . 120      |

|--------|---------------------------------------------------------------------|------------|

| 8. TRA | JECTORY PLANNING                                                    | 121        |

| 0.4    |                                                                     |            |

| 8.1    | Introduction                                                        |            |

|        | Planer Motion Trajectory Planning                                   | . 121      |

|        | 2.1 Interpolation by Search Technique 122                           |            |

|        | 2.2 Linear Interpolation by Digital Differential Analyzer (DDA) 123 |            |

|        | 2.3 Circular Interpolation 125                                      |            |

| 8.3    | Robot Motion Planning                                               |            |

| 8.4    | Other Interpolation Methods                                         |            |

| 8.5    | r · · · · · · · · · · · · · · · · · · ·                             |            |

| 8.6    | Conclusion                                                          |            |

| 9. THE | IMC SOFTWARE ARCHITECTURE                                           | 136        |

| 9.1    | Software Development Phases                                         | . 136      |

|        | .1 Analysis 136                                                     |            |

|        | .2 The Design Phase 137                                             |            |

|        | .3 Implementation 137                                               |            |

| 9.2    | <u> </u>                                                            | . 137      |

| 9.2    | =                                                                   |            |

|        | 2.2 Design 139                                                      |            |

| 9.3    | C                                                                   | . 139      |

| 9.3    | 3.1 Database Abstractions 140                                       |            |

| 9.3    | 3.2 Coordination Abstractions 144                                   |            |

| 9.3    | 3.3 Driver Abstractions 151                                         |            |

| 9.3    | 3.4 Network Abstractions 152                                        |            |

| 9.3    | 3.5 User Interface and Plug-And-Play Abstractions 153               |            |

| 9.4    | e ,                                                                 | . 160      |

| 9.4    |                                                                     |            |

| 9.4    | <u>.</u>                                                            |            |

| 9.4    | 1.3 The Database Abstraction 170                                    |            |

| 9.4    | 1.4 The Interpolator Component 172                                  |            |

| 9.4    | Network Abstractions 175                                            |            |

| 9.5    | The IMC Real-Time Coordinator                                       | . 175      |

| 9.5    | 5.1 Real-Time Services 176                                          |            |

| 9.6    | Conclusion                                                          | . 178      |

| 10. SY | STEM EVALUATION                                                     |            |

| 10.1   |                                                                     | 170        |

| 10.1   | Introduction                                                        |            |

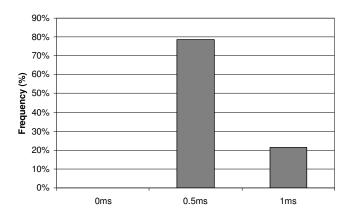

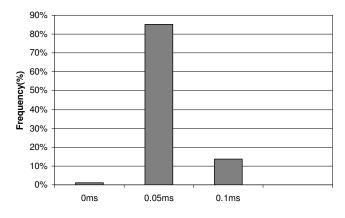

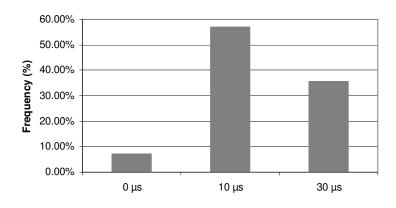

| 10.2   | Sampling Time and Communication Latency                             |            |

| 10.3   | Block Processing Time and Real-Timeliness                           |            |

| 10.4   | Synchronicity                                                       |            |

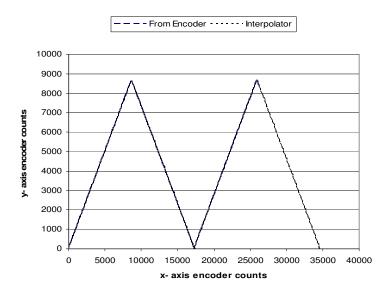

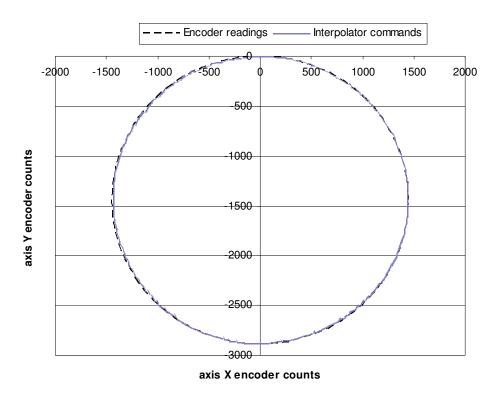

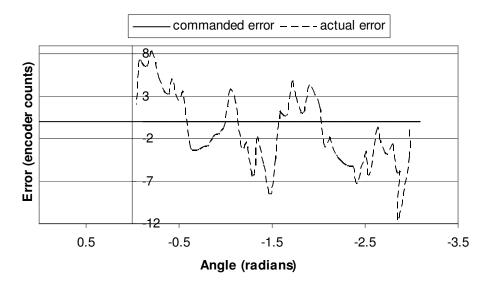

| 10.5   | Positioning Accuracy                                                |            |

| 10.6   | Architectural Flexibility                                           |            |

| 10.7   | Conclusion  NCLUSION AND DISCUSSIONS                                | 186<br>187 |

| 11 (T) | INCLUSION AND DISCUSSIONS                                           | IX/        |

| 11.1 Overview                        |                             |

|--------------------------------------|-----------------------------|

| 11.2 Summary of Results              |                             |

| 11.2.1 Control Architecture Revie    | ew Summary 188              |

| 11.2.2 Recapitulation of the IMC     |                             |

| 11.2.3 Prototype Development Su      | ımmary 189                  |

| 11.2.4 Summary of the IMC Com        | munication Architecture 189 |

| 11.2.5 Summary of Computationa       | al and Software Models 190  |

| 11.2.6 Summary of the Controller     | Performance 191             |

| 11.3 Research Achievements           | 191                         |

| 11.4 Discussions and Future Research | Direction                   |

| REFERENCES                           | 194                         |

|                                      |                             |

| APPENDIX A. THE IMC HARDWARI         | E201                        |

|                                      |                             |

|                                      | matics201                   |

|                                      | 207                         |

|                                      |                             |

| APPENDIX B: IMC SOFTWARE INTE        | ERFACE211                   |

| D1 DAC database                      | 210                         |

|                                      | 212                         |

| Class Data 212                       |                             |

| Class PushPullData 214               |                             |

| Class FIFO 216                       |                             |

| Class FileServer_ConfigFiles 216     |                             |

| Class FileService 218                |                             |

|                                      | 219                         |

|                                      | 220                         |

| Class StateCoordinator 220           |                             |

| Class Counter 222                    |                             |

| Class Device 222                     |                             |

| Class EncoderReader 223              |                             |

| Class Interpolation_Server 223       |                             |

| Class Interpolation_Server_Starter   | 224                         |

| Class MainClass 225                  |                             |

| Class Monitor 225                    |                             |

| Class MultiCasted_States 226         |                             |

| Class StateBuffer 226                |                             |

| B3 com.IMC.servlets                  | 228                         |

| Class PositionDump 228               |                             |

| Class ConfigureDevice 228            |                             |

| Class ControllerInfo 230             |                             |

| Class EditJmDNS 231                  |                             |

| Class JmDNS_Coordinator 232          |                             |

| B4 com.IMC.drivers                   |                             |

| Class Reference_Switch_Driver        | 233                         |

| Class GPIOPinA3 234                  |                             |

| Class HSIO_Driver 234                |                             |

|            | Class JStickTimer_tc2 236   |        |                  |

|------------|-----------------------------|--------|------------------|

|            | Class LimitSwitch_Left      | 237    |                  |

|            | Class LimitSwitch_Right     | 237    |                  |

|            | Class LM628 238             |        |                  |

|            | Class Board Clock 244       |        |                  |

|            | Class LM628_Interrupt       | 244    |                  |

|            | Class MotorAmp 244          |        |                  |

| В5         | *                           |        | 245              |

|            | Class TCPServer 245         |        |                  |

|            | Class DatagramServer 245    |        |                  |

|            | Class MulticastServer 245   |        |                  |

| API        |                             | R SOFT | WARE INTERFACE24 |

|            |                             |        |                  |

| <b>C</b> 1 | com.coordinator.database    |        | 248              |

|            | Class Traj_Configuration_Da | ta     | 248              |

|            | Class Data 249              |        |                  |

|            | Class DataTranspose 252     |        |                  |

|            | Class FileDataToArrayConve  | erter  | 253              |

|            | Class GCodeParser 253       |        |                  |

|            | Class GCodeSender 254       |        |                  |

|            | Class JmDNS_DATA 254        |        |                  |

| C2         | com.coordinator.coordina    | tion   | 254              |

|            | Class ControllerIO 254      |        |                  |

|            | Class Trajectory_Server     | 256    |                  |

|            | Class JmDNS_Coordinator     | 257    |                  |

|            | Class JmDNS_Event_Server    | 258    |                  |

|            | Class Monitor 258           |        |                  |

|            | Class SynchFlag 259         |        |                  |

| C3         |                             | tion   | 260              |

|            | Class Transmission_Flag     | 260    |                  |

|            | Class Interpolator 260      |        |                  |

|            | Class Transmission 261      |        |                  |

|            | Class Transmission_ACK      | 261    |                  |

| <b>C</b> 4 |                             |        | 262              |

|            | Class TrajTable 262         |        |                  |

|            | Class MainApplication       | 262    |                  |

|            | Class MainGUIFrame 262      |        |                  |

|            | Class PIDTable 265          |        |                  |

|            | Class TrajDataApplication   | 266    |                  |

|            | Class TrajDataFrame 266     |        |                  |

| C5         | · ·                         |        | 268              |

|            | Class UDP_Client 268        |        |                  |

|            | Class DatagramSender269     |        |                  |

|            | Class McastDirect 271       |        |                  |

|            | Class McastFlag 271         |        |                  |

|            | Class MulticastSender 271   |        |                  |

|            | Class TCP_Client 271        |        |                  |

# LIST OF TABLES

| Table 4.1: Java Hardware Comparison                        | 53  |

|------------------------------------------------------------|-----|

| Table 5.1: Chip Configuration Register                     | 67  |

| Table 5.2: LM628 Signal Levels                             | 68  |

| Table 5.3: LM628 Timing Requirements                       | 71  |

| Table 5.4: Timer Settings                                  | 75  |

| Table 6.1: Typical JmDNS Services on the IMC Architecture  | 108 |

| Table 9.1: Software Packages                               | 139 |

| Table 9.2: The IMC Database Components                     | 140 |

| Table 9.3: Coordination Components                         | 144 |

| Table 9.4: Driver Component                                | 151 |

| Table 9.5: Network Component                               | 152 |

| Table 9.6: Servlets Component                              | 155 |

| Table 9.7: System Coordinator Software Packages            | 161 |

| Table 9.8: GUI Component                                   | 161 |

| Table 9.9: System-Coordinator Coordination Components      | 166 |

| Table 9.10: System Coordinator Database Sub-Components     | 170 |

| Table 9.11: System Coordinator Interpolator Sub-Components | 173 |

| Table 9.12: Network Package                                | 175 |

| Table 9.13: Real-Time Coordinator Software Packages        | 175 |

| Table 9.14: Real-Time Service Components                   | 176 |

| Table 9.15: Real-time Coordinator Command Structure        | 176 |

| Table 11.1: Summary of Research Objectives                 | 188 |

| Table 11.2: Performance Evaluation Results                 | 192 |

| Table A1: Bill of Materials (2004)                         | 207 |

| Table A2: IMC Microcontroller, Cables & Router (2003)      | 209 |

| Table A3: Comparison of Motion Control Chips               | 210 |

| Table B1: IMC Software                                     | 211 |

| Table C1: System Coordinator Software                      | 247 |

# LIST OF FIGURES

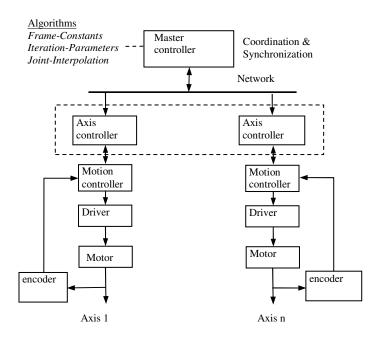

| Figure 2.1: MUPAAC Architecture                                                | .0 |

|--------------------------------------------------------------------------------|----|

| Figure 2.2: MUPAAC Software Architecture                                       | 21 |

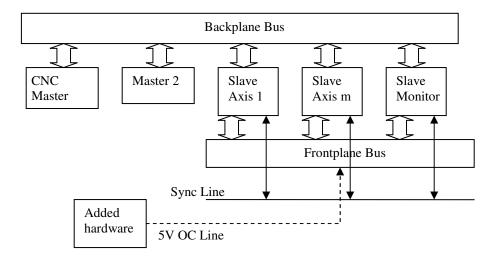

| Figure 2.3: Modular CNC System Architecture                                    | 23 |

| Figure 2.4: GEECON Architecture Implementation                                 | 25 |

| Figure 2.5: GEECON Architecture                                                | 6  |

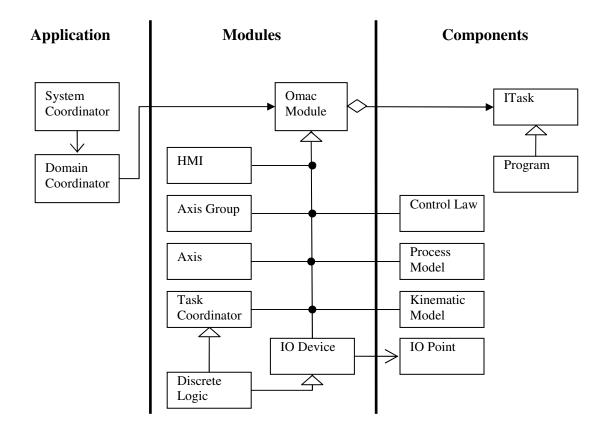

| Figure 2.6: OMAC Architecture                                                  | 28 |

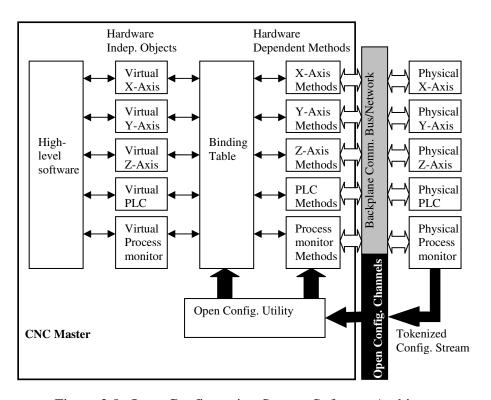

| Figure 2.7: The UBC Open Controller Reference Architecture                     | 0  |

| Figure 2.8: Open Configuration System Software Architecture                    | 1  |

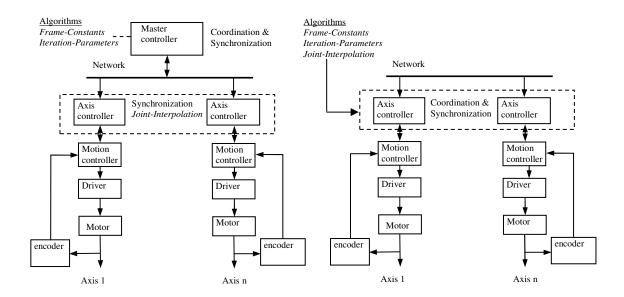

| Figure 2.9: Three-Tier Computing Hierarchy for the NRC-IMTI Tripod             | 3  |

| Figure 2.10: Tripod Computing Architecture Variations                          | 4  |

| Figure 2.11: CLARAty Implementation on Various Rover Platforms                 | 6  |

| Figure 2.12: Classification of robot control problems                          | 7  |

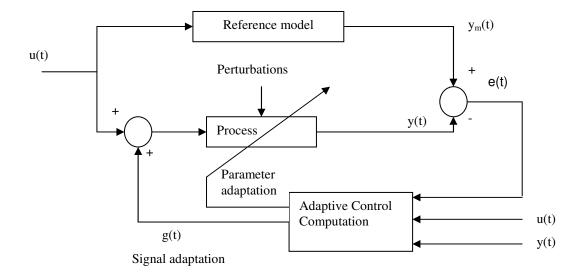

| Figure 2.13: Model Reference Adaptive Control (MRAC)                           | 9  |

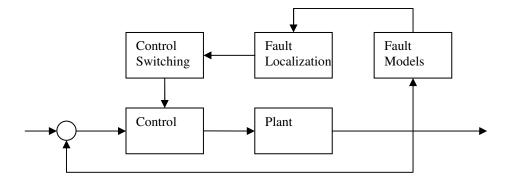

| Figure 2.14: Control Configuration – General Strategy                          | -0 |

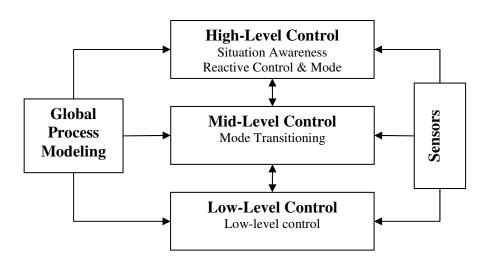

| Figure 2.15: Hierarchical Control Reconfiguration Structure                    | -1 |

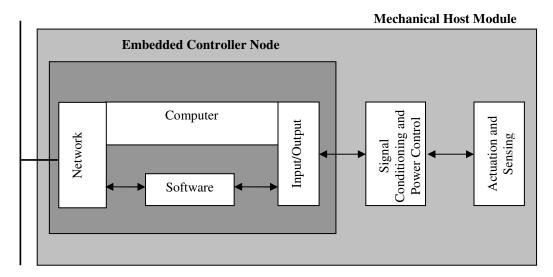

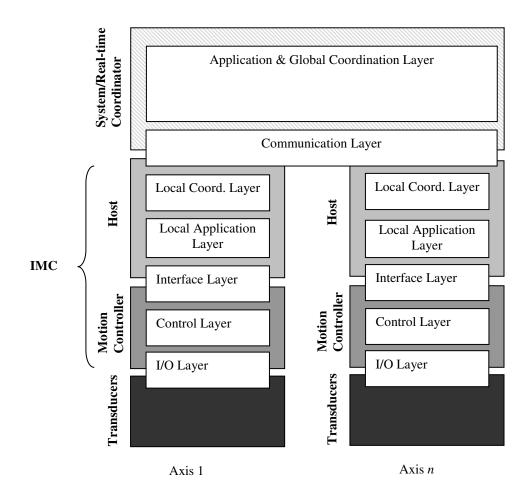

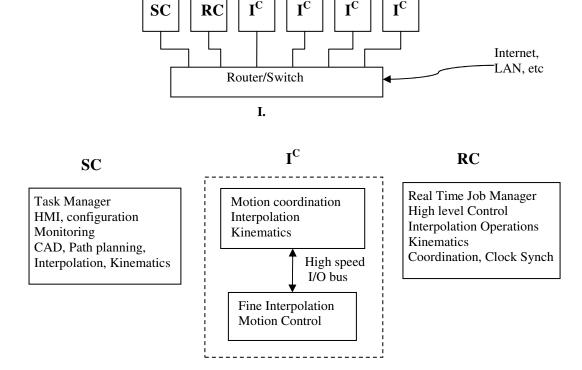

| Figure 3.1: The IMC Hardware Architecture                                      | .5 |

| Figure 3.2: The IMC Reference Architecture                                     | -6 |

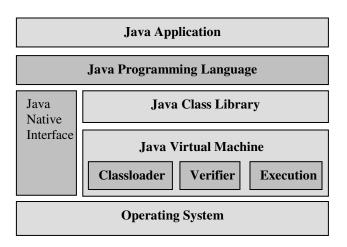

| Figure 4.1: The Java System Architecture                                       | 2  |

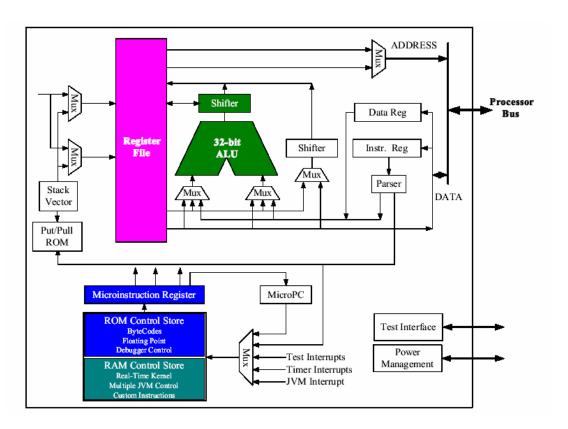

| Figure 4.2: The aJile JEM2 Processor (aJ-100, 2001)                            | 8  |

| Figure 4.3: aJ-100 Architecture (aJ-100, 2001)                                 | 9  |

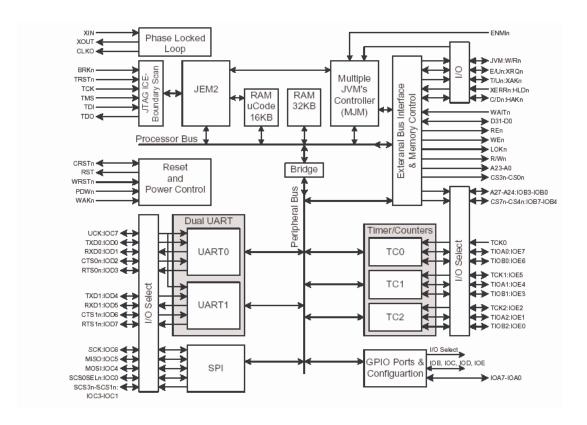

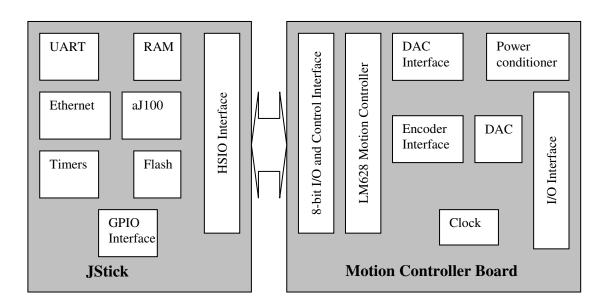

| Figure 5.1: Peripheral Motion Controller Board Architecture                    | 5  |

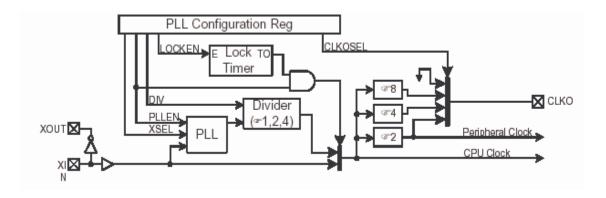

| Figure 5.2: aJile PLL Circuit Diagram (aJ-100, 2001)                           | 6  |

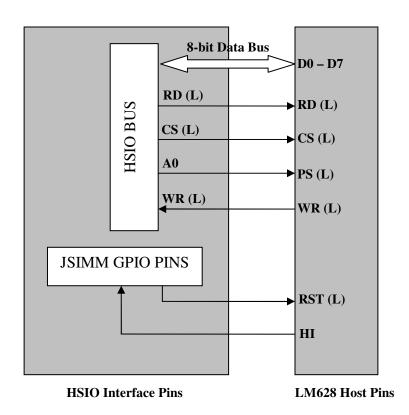

| Figure 5.3: JStick LM628 Interface                                             | 9  |

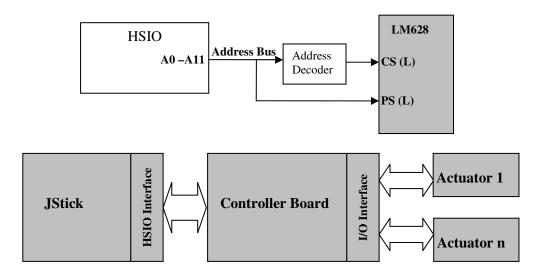

| Figure 5.4: Interface Architecture for Multiple LM628                          | 0' |

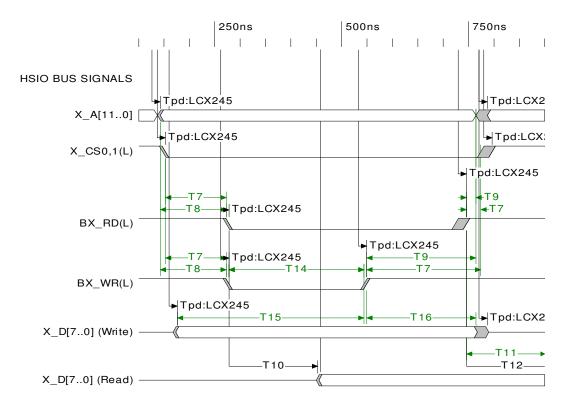

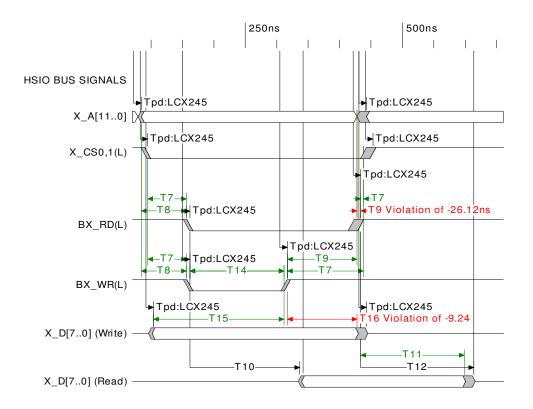

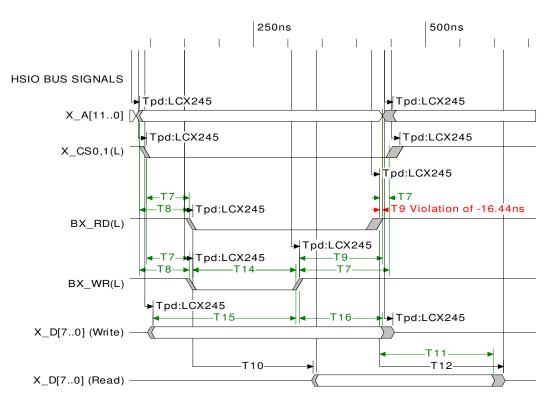

| Figure 5.5: HSIO Timing Diagram with Bus Speed of 7.37 MHz                     | 2  |

| Figure 5.6: HSIO Timing Diagram with Bus Speed of 12.9 MHz Showing Violations7 | 73 |

| Figure 5.7: Final HSIO Timing Diagram with Bus Speed of 12.9 MHz               | 4  |

| Figure 5.8: DAC – LM628 Interface Architecture                                 | 7  |

| Figure 5.9: Receiver Line Filter for Single-Ended Totem Pole Encoder           | 8  |

| Figure 5.10: Pseudo-code for High Speed I/O (HSIO)                             | 0  |

| Figure 6.1: Timing in an Event Triggered System                        | 87  |

|------------------------------------------------------------------------|-----|

| Figure 6.2: Timing in a Time-Triggered System                          | 88  |

| Figure 6.3: The OSI Protocol Stack                                     | 91  |

| Figure 6.4: Communication and Computing Elements:                      | 100 |

| Figure 6.5: Communication Flow                                         | 101 |

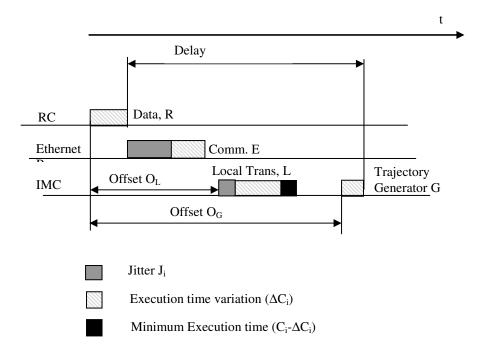

| Figure 6.6: Produce-Consumer Co-operation between the RC and IMC Nodes | 103 |

| Figure 6.7: TT communication with TT processors                        | 105 |

| Figure 6.8: ET Communication with TT Processor                         | 106 |

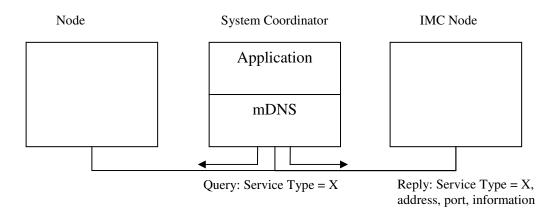

| Figure 6.9: Multicast DNS Query                                        | 107 |

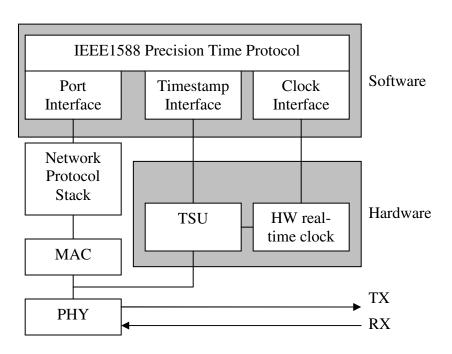

| Figure 7.1: IEEE1588 Precision Time Protocol Architecture              | 116 |

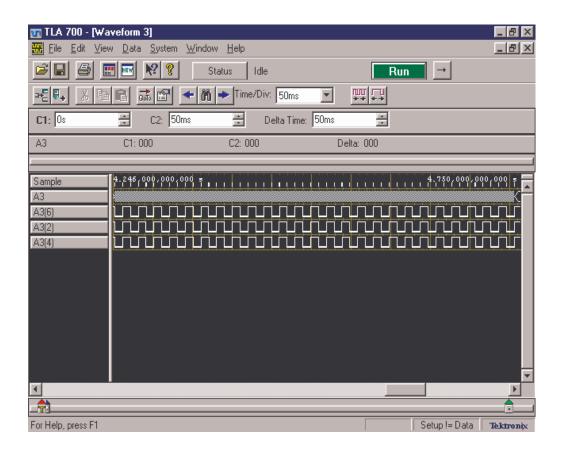

| Figure 7.2: Clock Synchronization Capture on a Logic Analyzer          | 120 |

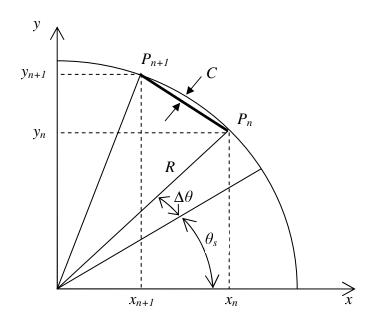

| Figure 8.1: Circular Interpolation                                     | 126 |

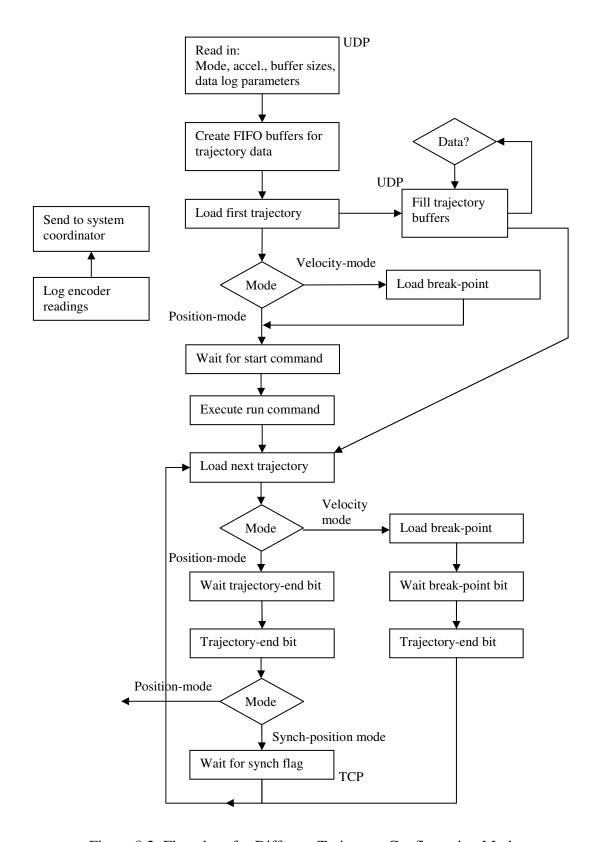

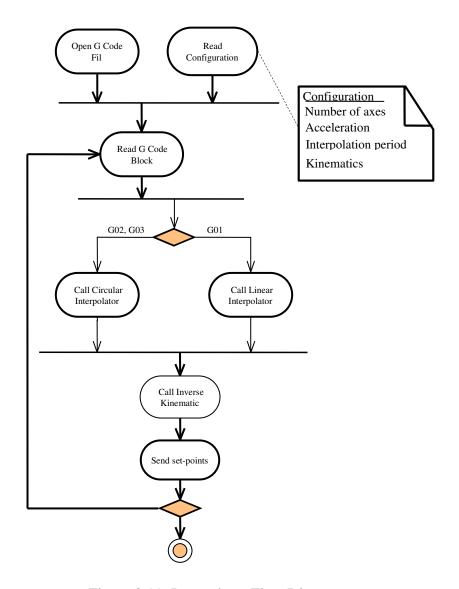

| Figure 8.2: Flowchart for Different Trajectory Configuration Modes     | 131 |

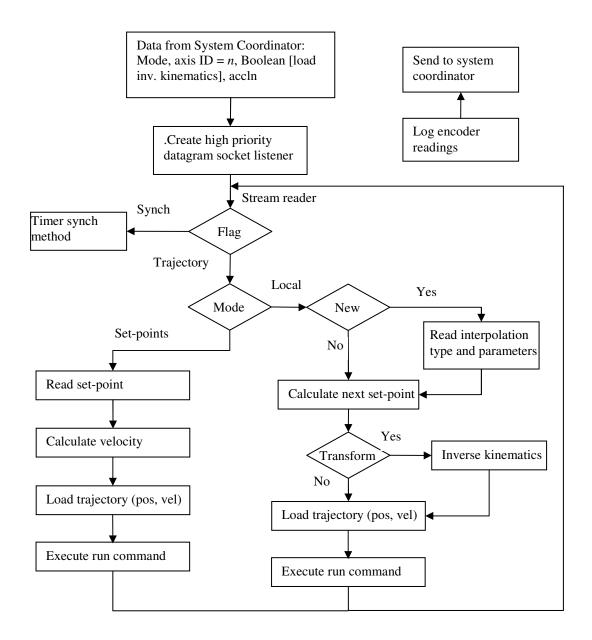

| Figure 8.3: Flowchart for Coordinated-Motion                           | 134 |

| Figure 9.1: The IMC Architecture Software Components                   | 138 |

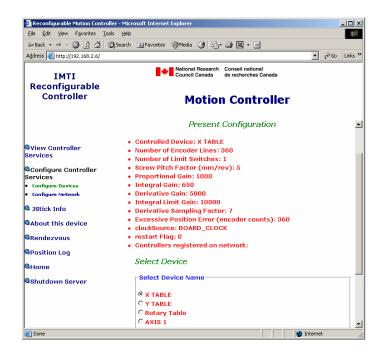

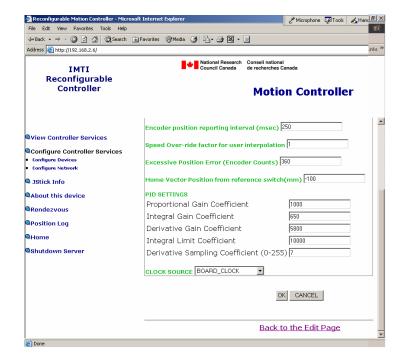

| Figure 9.2: IMC Configuration Servlet II                               | 158 |

| Figure 9.3: IMC Configuration Servlet II                               | 158 |

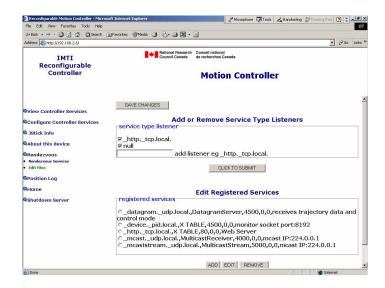

| Figure 9.4: JmDNS Service/Discovery Browser                            | 159 |

| Figure 9.5: JmDNS Service/Discovery Editor Webpage                     | 160 |

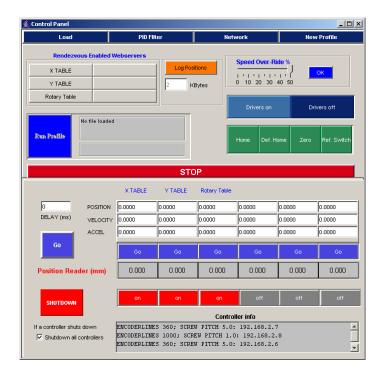

| Figure 9.6: Main GUI Browser                                           | 163 |

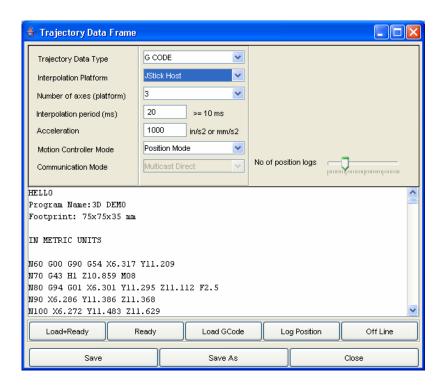

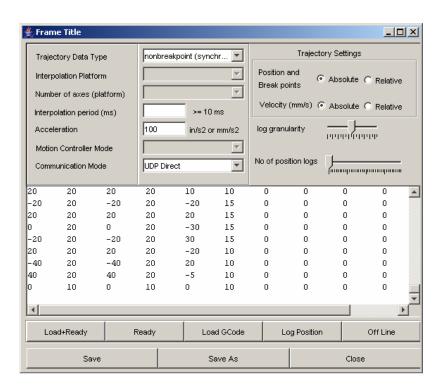

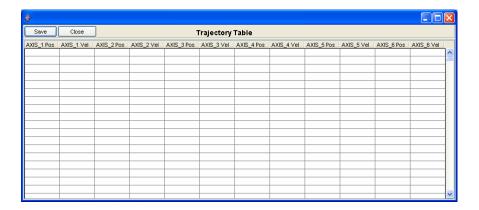

| Figure 9.7: Trajectory Editor I                                        | 164 |

| Figure 9.8: Trajectory Data and Configuration Browsers                 | 164 |

| Figure 9.9: Trajectory Editor Frames                                   | 165 |

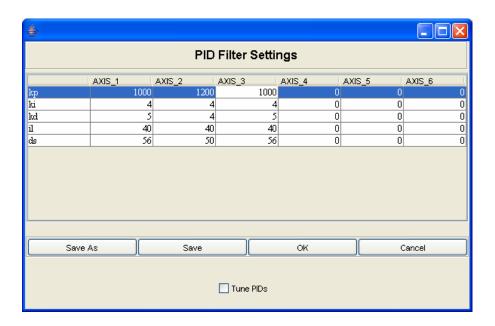

| Figure 9.10: PID Filter Parameter Editor                               | 165 |

| Figure 9.11: Interpolator Flow Diagram                                 | 174 |

| Figure 10.1: Timing Variations–Uncompensated Delays                    | 181 |

| Figure 10.2: Timing Variations– Compensated Delays                     | 181 |

| Figure 10.3: Timing Variation– Synchronization by Interrupts           | 182 |

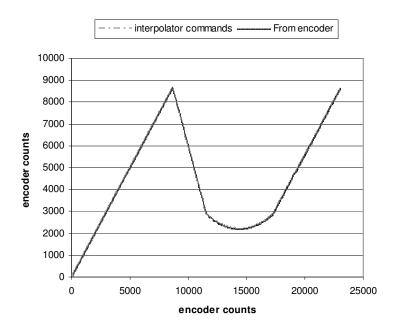

| Figure 10.4: Linear Trajectory                                         | 182 |

| Figure 10.5: Circular Trajectory – 5-mm radius                         | 183 |

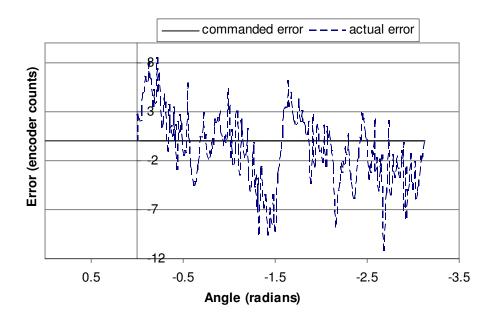

| Figure 10.6: Radial Error – 1-mm radius                                | 183 |

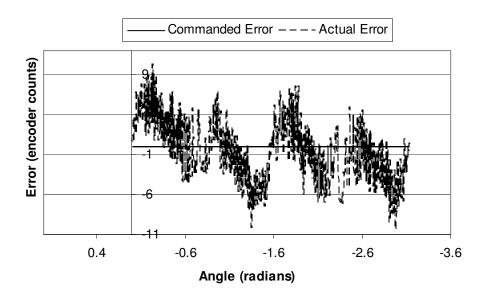

| Figure 10.7: Radial Error – 5-mm radius                       | . 184 |

|---------------------------------------------------------------|-------|

| Figure 10.8: Radial Error – 25-mm radius                      | . 184 |

| Figure 10.9: Combined Linear and Circular Paths               | . 185 |

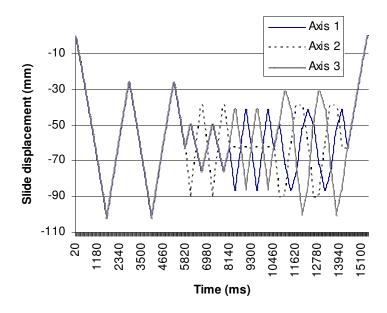

| Figure 10.10: Tripod Slider Displacements                     | . 186 |

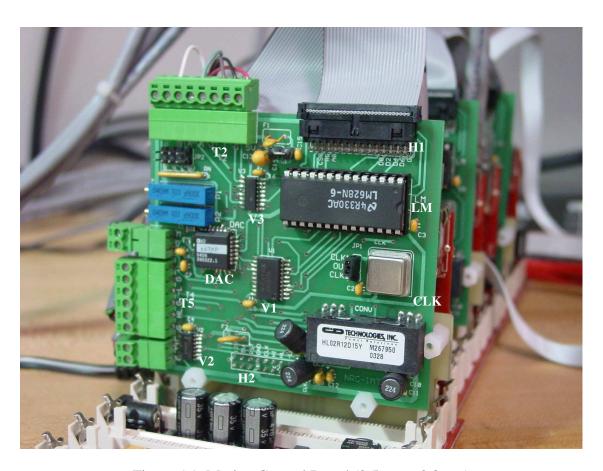

| Figure A1: Motion Control Board (3.5mm x 3.2mm)               | . 201 |

| Figure A2: LM628 Pin-out to Header (H1), and Clock            | . 202 |

| Figure A3: Encoder Interface and I/O to JStick SIMM Interface | . 203 |

| Figure A4: AD667 DAC Interface with Logic Devices             | . 204 |

| Figure A5: AD667 DAC Output Circuit                           | . 205 |

| Figure A6: Filters and Power Supply                           | . 206 |

| Figure A7: IMC Ensemble                                       | . 207 |

#### LIST OF ABBREVIATIONS

offset, j offset of microtick i between clocks j and k with the same

granularity

$\delta$  Network latency

$\delta_{max}$  Maximum network latency

$\delta_{min}$  Minimum network latency (delay)

Δu Displacement step

$\Delta x$  Incremental displacement in axis x

A, B, I Encoder output signals

aJile Manufacturer of aJ100 and aJ80 microprocessors that

directly execute Java bytecodes in hardware

Architecture The structure of specific components (such as hardware

software components) and the way they interact

ASIC Application Specific Integrated Circuit

BLU Basic Length Unit of a Machine indicates its precision

C Chord error (circular interpolation)

Client-Server Cooperation model based on Client node(s) that request

the service(s) of server(s)

CLKO Clock output

$C_{max}$  Maximum chord error

CMOS Complementary Metal-Oxide Semiconductor; a major

class of integrated circuits.

CNI Communication Network Interface

COTS Commercial-Off-the-Shelf

CSMA Carrier Sensing Multiple Access

CSn Chip Select n; n = integer

CTC Continuous Path Control

DAC Digital to Analog Converter

D-Type Flip-Flop A pulsed digital circuit capable of serving as a one-bit

memory. D (data) – type is one of the four basic types

EBI aJ100 External Bus Interface

ET Event-Triggered

Fieldbus Control network based on a serial bus

*fr*<sup>z</sup> Reference clock frequency

g Granularity: duration between two consecutive microticks

of a clock

$g^k$  Granularity of a clock k

GPIO General purpose I/O

hex Hexadecimal I/O Input/Output

IMC Intelligent Modular Controller

J or  $\varepsilon$  Latency jitter; Difference between minimum and

maximum latencies

Java bytecode Machine-independent code generated by the Java compiler

and executed by a Java interpreter.

JDK Java Development Kit

JNI Java Native Interface

JStick aJile-based microcontroller by Systronix

JVM Java Virtual Machine

k Time interval (in the context of trajectory planning)

LSB Least Significant Bit

microtick Periodic event generated by a clock oscillating mechanism

$microtick_i^k$  microtick i of clock k is identified

MSB Most Significant Bit

Number of interpolation steps (in the context of trajectory

planning)

$N_1$  Number of interpolation steps in acceleration region

$N_2$  Number of interpolation steps in constant velocity region

$N_3$  Number of interpolation steps in deceleration region

n-DOF n Degrees of Freedom

Node An element on a network consisting of at least a host

computer and a local communication network interface

NRC-IMTI National Research Council Integrated Manufacturing and

**Technology Institute**

OS Operating System

PID Proportional-Integral-Derivative filter for a controller

PKM Parallel Kinematic Mechanism

PLL Phase-Locked-Loop: a closed loop frequency control

system based on the phase sensitive detection of phase

difference between the input and output of the controlled

oscillator

PnP Plug-and-Play

prescalar A continuous count-down timer that divides aJile's

internal peripheral clock (or an external clock) by

*PrescalerReloadRegisterValue – 1*

PrescalerReloadRegisterValue value of the prescaler register

PS Port Select for LM628

$P_s(x_s, y_s)$  and  $P_e(x_e, y_e)$  Starting and end points of a line

PTP Point-to-Point motion

Publish-Subscribe Cooperation model based on publishers and subscribers of

information

R(t) Reliability

RC IMC real-time coordinator

RD Read control strobe

ReloadRegisterValue Reload register value (aJile)

RST Reset pin

SC IMC system coordinator

T Interpolation period (in the context of trajectory planning)

$T_c$  clock periods

TDMA Time Division Multiple Access

$T_i$  Interpolation time interval (in the context of trajectory

planning)

TT Time-Triggered

TTL Transistor-Transistor Logic: A class of digital circuits built

from bipolar junction transistors (BJT), and resistors.

$T_w$  Timing duration in CLKO periods

VME bus A 32-bit bus developed by Motorola

WR Write control strobe

z Reference clock

z(e) Absolute timestamp of event e

λ Failures/hour

$\rho$  Clock Drift

Π Clock precision

#### 1. INTRODUCTION

#### 1.1 Overview

This thesis presents the design of a modular reconfigurable controller for machine tools. This is not a new concept, as the literature in the subsequent chapters reveals; however the design breaks new ground by incorporating embedded technology using commercial-off-the-shelf (COTS) components, flexible architectural design patterns based on object-oriented technology, plug-and-play, and web-design into a distributed control system. All these properties are harnessed by well-conceived and novel hardware, software, and communication architecture designs. The treatise takes a tour through the different design stages from concepts to production, and also gives a rich background of the related state-of-the-art. Experimental results and future research directions wrap up the main thesis body. The rest of this chapter gives the motivation for the research, goals and contributions, and the organizational structure of the thesis.

#### 1.2 Motivation

The Mechatronic approach in modern design of control systems inevitably involves embedded technology. This approach is gaining a lot of attention due to the growing demand for distributed real-time systems. Indeed, the gradual paradigm shift from centralized systems is justified in many ways. The most compelling reasons are the needs for less complexity, more processing power, flexibility, and greater fault-tolerance. A typical distributed control system (DCS) consists of several processing nodes connected by a communication network. The network presents a duo of both convenience of connectivity, and inconvenience of dealing with real-time situations. For this reason, some control designers treat the DCS arena with caution, quite reluctant to breakaway from tried-and-tested microprocessor communication systems such as backplanes. However, designs based on such systems have limited flexibility in terms of scalability, unlike serial communication systems where a few serial lines could connect many elements. Currently, there are several such systems, collectively called fieldbuses, which are employed in many

industries to operate peripheral devices such as sensors and actuators. Fieldbus systems have roots in automotive systems where data rates are only a few kilobytes per second. Apparently, their bandwidths have not changed substantially since their debut some twenty years ago. Moreover the current market is now inundated with fieldbus products, and this poses a challenge to standardization and interoperability. Industries need interoperable devices and techniques to reduce integration costs of factory information systems (Dugenske et al., 2000). In the midst of evolving communication standards, Ethernet has stood out as the most consistent and robust, though its presence in low-level control is almost non-existent due to its non real-time properties. Against this backdrop, this research investigates the constraints and opportunities for using Ethernet and proposes and implements a design scheme to realize real-time control to meet stringent time demands. The communication architecture uses a producer-consumer coordination model for real-time data communication over a segmented network, and a client-server approach for point-to-point transactions. Moreover, the proposed scheme employs a time-triggered (TT) approach to schedule tasks for the network. Unlike other TT approaches – normally branded as inflexible, the proposed scheme does not need to be configured explicitly. Furthermore, an auto-configuration protocol that enables devices on the network to be cognizant of the operational environment has been successfully integrated in the architecture. This scheme allows devices on the network to automatically detect configuration changes, and react according to local event-service routines.

Another important aspect of the architecture is the use of an object-oriented architectural style. This style of programming leverages reuse, fast development, and high quality software semantics. Presently, C++ and Ada are the most commonly used object-oriented tools in embedded system designs. Both are robust real-time programming tools, but while C++ is prone to poor readability and maintainability, Ada is large and complex. Breaking from the norm, we use Java as the sole programming tool. Java adds flexibility by being platform-independent with rich support for networking. However, not many real-time applications have been written in this language due to its inherent tardiness. For this reason, we resorted to Java-based processors with native Java machines. This led us to design customized motion controller boards based on COTS components. Test results

demonstrate the capabilities of the design. In the section below, the main objectives and goals of this research are presented.

#### 1.3 Goals and Contributions

The proposed research aims to advance reconfigurable controller architecture to a new limit by addressing the above issues. The research is a collaborative effort between the Mechanical Engineering Department of the University of Saskatchewan and the Integrated Manufacturing and Technology Institutes of the National Research Council (IMIT-NRC). The following list summarizes the research objectives for the proposed design:

#### **Primary Objectives:**

- 1. A generic framework for a modular reconfigurable control architecture. The framework addresses software and hardware requirements, and also the communication structure.

- 2. A small and simple design that fits into embedded low-cost platforms.

- 3. A working prototype, not just concepts and simulations of the architecture.

#### **Secondary Objectives:**

Literature review on the current work being done in the field of design and to identify those areas that require additional investigations.

- 1. A critical review of the state-of-the-art in control architecture, distributed communication paradigms, and reconfigurable networked systems.

- 2. A synchronization algorithm and protocols to enable Ethernet to be used for real-time control.

- 3. An operational software architecture based on modularity and reusability.

- 4. Demonstration of the strengths of the proposed design.

#### **Contributions:**

The main contributions of the thesis are as follows:

1. Embedded technology is a cost-effective approach to motion control design. C++ and Ada have dominance in this field, but Java has certain unique and superior strengths albeit some weakness in real-time design. In Chapters 4 and 5, a Java-based design is presented that utilizes COTS components. The concepts are simple (simplicity is the governing principle), and can easily be replicated. To the best of our knowledge, no

- literature has revealed a hard real-time motion controller design thoroughly based on embedded Java technology.

- 2. Ethernet is the de facto network standard, but is seldom considered for time critical events due to its inherent 'sluggishness'. Therefore many distributed systems rely on fieldbuses or microprocessor communication hardware (e.g. VME). However, the real-time communications market is unregulated, and is therefore cluttered with many different systems, which normally require special middleware and hardware systems to make them interoperable. Moreover, not many of them have the robustness and flexibility of Ethernet. In view of this, an Ethernet-based real-time communication architecture with implicit clock synchronization has been implemented and demonstrated as part of the overall architecture. The technology also enables the controller sub-component design to incorporate embedded web-servers for remote monitoring and system configuration.

- 3. Zeroconf protocol was developed by Apple to enable networked devices to automatically reconfigure (plug and play) without the need for high level intervention. A subset of the Zeroconf protocol, JmDNS, is written in standard Java (J2SE). With regard to this protocol, two ideas are realized in this research: First, the protocol has been re-engineered and ported to a subset of J2SE called the Java micro-edition (J2ME) commonly used in embedded Java systems such as personal device assistants (PDA). Secondly, the protocol has been successfully demonstrated as an automatic configuration tool for controllers and other shop floor devices.

#### 1.4 Organization of Thesis

The structure of the thesis is outlined in this section. In Chapter 2, a detailed review of control architectures is discussed and critiqued. Typical requirements for control and software architecture are presented to enable a comprehensive review. A snapshot of the proposed architecture codenamed the IMC (Intelligent Modular Axis Controller) architecture is presented in Chapter 3. The design is based on a layered reference model, and modularity, simplicity and flexibility are the governing principles. A detailed review of the constraints and opportunities for Java technology in real-time design is presented in Chapter 4. Inferences drawn from this enabled us to select and to understand the implications of using JStick, which is a Java-based COTS microcontroller. An overview

of the relevant characteristics of the microcontroller is outlined. The premise for the selection of a motion controller chip (LM628) is also included in this chapter. In Chapter 5, the hardware architecture is described in detail. The architecture consists of control modules (IMC) dedicated to each machine axis, and a host computer (system coordinator). Each IMC is made up of a JStick as the host microcontroller and a motion controller board purposefully designed for this research. Details of the board design are provided: This includes the procedure for integrating it with the JStick such as timing analysis. Chapter 6 details communication architecture concepts and principles. Following this, the system communication architecture is described. A Time-Triggered approach enhanced with a producer-consumer co-operation model, is employed to realize real-time communication on a switched-Ethernet network. Analysis of the computation and communication model is also presented. Clock synchronization in distributed systems is discussed in Chapter 7; an external clock synchronization model developed for the IMC architecture is described. Chapter 8 gives an overview of trajectory generation schemes and the methodologies adopted for this project. The software architecture framework is vividly described in Chapter 9. Experiments to verify the architecture are provided in Chapter 10, and finally conclusions and future research directions are outlined in Chapter 11. Schematic diagrams of the motion controller board, BOM (Bill of Materials) including prices, and the software interfaces are appended.

#### 2. ARCHITECTURE DESIGN CONCEPTS AND REVIEW

#### 2.1 Robot Control Architecture, Introduction

Robot control architectures embody several different notions and implications, particularly architectural styles and structures. Architectural structure shows how a system is decomposed into subsystems, and how subsystems interact. The computation and communication underpinnings of a given system invariably reflect a style. For example, one system might use a publish-subscribe message passing style of communication, while another may use a more synchronous client-server approach (Coste-Maniere and Simmons, 2000). Most often the holistic architecture is realized only at the working stage. This is unfortunate, since a well-conceived architecture can have many advantages in the specification, execution, and validation of robot systems. This chapter serves as a roadmap to developing a robot control architecture framework. Generally, a framework refers to the structure external to an architecture which organizes information about the architecture and its application (Kramer and Senehi, 1993).

#### 2.2 Architectural Properties

The architectural style employed has a direct impact on the performance of the overall system. For example, the *pipe-and-filter* software style supports components' reusability and configurability of the application by applying generality to its component interfaces. However, components are constrained to a single interface type. Some salient properties of architectures are discussed in the following sections.

#### 2.2.1 Dealing with Complexity

A daunting challenge is the need to manage the complexity of interactions between the system and its environment, and interactions between individual units of a system (Coste-Maniere and Simmons, 2000). One way to achieve simplicity is through modularity within a given structure. The global system complexity can be decomposed into smaller components with well-defined abstraction levels and interfaces between them.

Another means of curtailing complexity is to provide expressive languages and tools, e.g., ALPHA, and high-level languages such as TCA and TDL (Coste-Maniere and Simmons, 2000). Architecture description languages (ADL) are particularly useful for architecture-based development and formal modeling notations and analysis (Medvidovic and Taylor, 2000). The software architecture must provide a basis for complexity management by providing abstract models of the system under development, which is necessary in comprehension, cross-domain communication, verification, validation and maintenance (Chen, 2001). Coupling and cohesion issues must also be addressed by the architecture. Coupling refers to the way modules are connected, while cohesion indicates the degree of relatedness of sub-modules, or components within a module. An ideal system provides low coupling and high cohesion without violating performance parameters (Chen, 2001).

#### 2.2.2 Execution

The architecture should also define the run-time execution of the software. This includes real-time responses, appropriate goal-directed behavior and reliable reactivity to environmental changes. The issue on real-time provokes this famous definition:

A real-time computer system is a computer system in which the correctness of the system behavior depends not only on the logical results of the computations, but also on the physical instant at which these results are produced (Kopetz, 1997).

There are two variants of real-time systems: In a hard real-time system, timing violations are to be avoided at *all* times. In contrast, a soft real-time system can tolerate some degree of timing violations. Typical tasks for a real-time system include data collection, digital control and man-machine interactions. The architecture has to describe, quantify or specify the *temporal requirements* of the system. These include timing of events (e.g., deadlines), arrival patterns of events (e.g., sporadic or periodic), and the triggering policies required. Goal-directed behavior refers to the mechanism within the architecture to manage tasks and behaviors such as task decomposition and behavior arbitration, and for managing the interactions between tasks and behaviors such as resources management, multitasking and temporal sequencing. Task management facilitates concurrent execution in a single process or by a collection of distributed processes. For reliable reactive behaviors, the architecture can provide software support for monitoring the environment and invoking exception handlers, if necessary. The extent

of reactivity depends on the real-time capabilities of the system. The management of exceptional conditions also includes support for cleanly terminating tasks, and if necessary recovery strategies.

#### 2.2.3 Openness

Openness is a buzzword in the control systems community. Open architecture control systems offer services according to standard resources, and/or standard rules that describe the syntax and semantics of those services (Tanenbaum and van Steen, 2003; Hong, et al, 2001). This approach forces all manufacturing vendors to conform to an agreed standard, thereby promoting integration and interoperability. It is becoming more acceptable for open-architecture control system to possess the common capabilities and functionalities offered by standard platforms: these include standard computing architecture, standard processors, standard operating systems, and standard and widely used programming languages. Moreover, openness promotes application of user-specified functions (Mehrabi et al., 2000; Chesney, 1998).

#### 2.2.4 Performance

The performance of an architecture implementation is bound by first the application requirements, then by the chosen interaction style, followed by the realized architecture, and lastly by the implementation of individual component. As an example, if the application requires that data be located on system X and processed on system Y, then the software cannot avoid moving that data from X to Y. Also, an architecture cannot be any more efficient than its interaction style allows; e.g., the cost of multiple interactions to transport data from X to Y cannot be less than that of a single interaction from X to Y. Lastly, regardless of the quality of an architecture, interactions cannot take place faster than the capacity individual components can endure. The quality of a distributed control architecture hinges on its network performance, which is measured by data throughput, overhead, bandwidth and usable bandwidth (Fielding, 1999). From the end-user perspective, network performance metrics are latencies, jitter and ultimately the ability of the controller to track a prescribed motion path accurately and efficiently within the dynamic constraints of the system.

#### 2.2.5 Scalability

Scalability is the ability of the architecture to support many components, or interactions among components within an active configuration. Scalability can be enhanced by simplifying components and decentralizing interactions between elements. Another complement approach is the proper control of monitoring or user interactions and configurations. The architecture style influences scalability by determining the location of application states, the extent of distribution, and the coupling between components (Fielding, 1999). Scalability is also affected by the frequency of interactions and timeliness requirements of data transfer.

#### 2.2.6 Simplicity

Allocation of functionality to the individual components to reduce complexity enables easier understanding and implementation of components and the overall architecture.

#### 2.2.7 Modifiability

Modifiability is the ease with which a change can be made to the architecture implementation. Modifiability is also a measure of evolvability, customizability, reconfigurability, and reusability (Fielding, 1999). Customizability refers to modifying a component at run-time, specifically so that the component can then perform an unusual service. A component is customizable if it can be extended by one client of that component's services without adversely affecting other clients of that component.

#### 2.2.8 Portability

Portable software can run in different environments. Architecture styles that support portability include those that move code along with the data to be processed, such as the virtual machine and mobile agent styles, and those that constrain the data elements to a set of standardized formats.

#### 2.2.9 Reliability

Reliability refers to the robustness of an architecture to failure at the system level in the presence of partial failures within components, connectors, or data. By definition (Kopetz, 1997), if a system has a constant failure rate of  $\lambda$  failures/hour, then the reliability R at time t is given by

$$R(t) = e^{\left(-\lambda(t-t_0)\right)};$$

where t- $t_0$  is given in hours. The inverse of the failure rate is referred to as the *Mean-Time-To-Failure (MTTF)*.

#### 2.2.10 Distributed Real-Time Systems

There are several definitions of distributed systems found in the literature. According to a general definition given by Tanenbaum and van Steen (2003), "A distributed system is a collection of independent computers that appears to its users as a single coherent system". Their definition has two implications: Firstly, the machine hardware is autonomous. Secondly, regarding software, the users think they are dealing with a single system. In terms of distributed system hardware, they divide all computers into two groups: those with shared memory (multiprocessors) and those without shared memory, i.e. multi-computers. Interconnection networks may be a bus such as a network or backplane, or switched as in the case of the public telephone system. Essentially, it is the software that largely determines the nature of a distributed system. The definition given by Kopetz (1997) is more specific: "If a real-time system is distributed, it consists of a set of (computer) nodes interconnected by a real-time communication network".

A distributed system leverages designing systems into fault-containment regions for easy diagnosing and smothering of faults, i.e., in a well-designed system, faults are dealt with locally and thus do not pervade the system. Moreover, scalability and modifiability is not as restrictive as in the case of a centralized system. However, the communication system can be a bottleneck if not properly designed.

#### 2.3 Software Architecture Styles

Modern day robot control architectures encase intensive software engineering. This necessitates choosing software architecture styles. For example, one has to select a suitable style (or a combination) for network-based applications, which will induce laid out objectives. Researchers are still refining the definition of software architecture. Two views are as follows:

A software architecture is an abstraction of the run-time behavior of a software system during some phase of its operation. A system may consist of many levels of abstraction and many phases of operation, each with its own software architecture. A software architecture consists of components, connectors, data, a configuration, and a set of architectural properties (Fielding, 1999).

The architecture of a software system defines that system in terms of components and of interactions among those components. In addition to specifying the structure and topology of the system, the architecture shows the intended correspondence between the system requirements and elements of the constructed system. It can additionally address system-level properties such as capacity, throughput, consistency, and component compatibility (Shaw, 1995).

Two common words that show up in various definitions are 'components' and 'connectors'. Components are described by Garlan and Shaw (1993) as *computational* components and by Fielding (1999) as abstract units of software that provide a transformation of data via their interface. In Birla et al., (2001) it is described as a reusable piece of software that serves as a building block within an application. This approach has the potential to enhance productivity by reducing architectural complexity (Chadha and Welsh, 2000). It is generally accepted that a connector is an abstract mechanism that mediates communication, coordination or cooperation among components (Fielding, 1999; Shaw, 1995).

In this section we examine some widely used styles. Our purpose is to capture the variety of choices available and the implications thereof.

#### 2.3.1 Pipe-and-Filter System (Data-Flow Model)

A pipe-and-filter (PF) system has two types of units: filters (component) and pipes (connector). Filters are responsible for incrementally transforming continuous streams of input data to streams of output data while pipes handle transportation of data streams between the filters, i.e., connections between producer and consumer components are data streams (Garlan and Shaw, 1993). Filters are usually implemented as software processes and pipes as system services. Filters are independent entities and hence are not allowed to share state with other filters. Invariably, a filter has no knowledge about its upstream and downstream filters. Filters are initiated when data is available and run to completion at the end of input data. In other words, computations are triggered by the availability of input data. Several variations of PF exist including those found in the UNIX family, LabVIEW and some database systems (Lee, 2002). The PF styles are suitable for applications where

the problem can be decomposed into a series of independent computations. This kind of configuration implies low coupling and high cohesion, which are necessary for simplicity, modifiability, reusability, and portability. However, it can be difficult to create interactive applications with this style. Secondly, there can be some performance-related problems due to the overheads of parsing and unparsing operations resulting from a fine-grained data stream (Chen, 2001).

#### 2.3.2 Layered Style

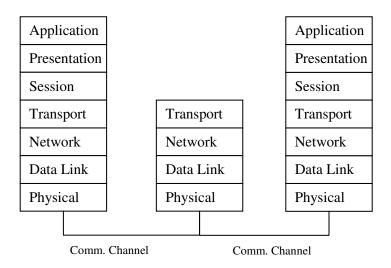

A layered system is organized hierarchically, with each layer providing services to the layer above it and using services of the layer below it (Garlan and Shaw, 1993). A function in one layer can only interact with other functions in the same layer or adjacent layers through a protocol (connector). This decoupling enhances evolvability and reusability since each layer represents a group of modules or functions for one class of services. The most widely used application of this kind of architectural style are layered protocols such as the TCP/IP and OSI protocol stacks (Zimmerman, 1980), Windows NT and hardware interface libraries. Layered styles are suitable for systems that can be decomposed into application-specific and implementation-specific functions. The major disadvantage of layered systems is that they add overhead and latency to the processing of data and hence could degrade user-perceived performance (Fielding, 1999).

#### 2.3.3 Time Triggered

In some systems timed events are driven by clocks, which are signals with events that are repeated indefinitely with a fixed period. A number of software frameworks and hardware architectures support this regular style of computation. The time-triggered architecture (TTA) is a hardware architecture that employs this regularity by statically scheduling computations and communications among distributed components.

#### 2.3.4 Synchronous/Reactive

In the synchronous/reactive (SR) style, connections between components represent data values that are aligned with global clock ticks, as with time-triggered approaches. However, unlike the time-triggered approach, there is no assumption that signals have a value at each time tick. This model is ideal for concurrent models with irregular events such as concurrent and complex control logic. Also because of tight synchronization,

safety-critical real-time applications are a good match but this makes distributed systems difficult to model.

#### 2.3.5 Process Networks

In this technique, components are processes or threads that communicate by asynchronous buffered message passing. The sender of the message does not need to wait for the receiver to be ready to receive the message. Process networks (PN) are excellent for signal processing. They are loosely coupled, and therefore relatively easy to parallelize or distribute. They can be implemented efficiently in both software and hardware. The main weakness of PN models is that they are awkward for specifying complicated control logic (Lee, 2002).

#### 2.3.6 Publish and Subscribe

In publish-and-subscribe models, connections between components are through named event streams. A consumer component registers an interest in the stream. When a producer produces an event to the stream, the consumer is prompted that a new event is available. It then queries a server for the event's value.

#### 2.3.7 Client-Server (CS)

The client-server style is the most frequently used architectural style for network-based applications (Fielding, 1999). A server component offering a set of services listens for requests: a client component in need of that service sends a request to the server via a connector. The server may either reject or serve the request and send a response back to the client. A client can be regarded as a triggering process while a server is a reactive process. Requests from clients trigger reactions from servers (Andrews, 1991). Separation of functionality is the main principle behind the client-server constraints. A proper separation of functionality simplifies the server component in order to improve scalability. This simplification usually involves moving all of the user interface functionality into the client component. The separation also allows the two types of components to be modified independently, provided that the interface does not change. There are several flavors of client-server systems, depending on the number of servers and clients in the overall system.

#### 2.3.8 Process Control

Also called the control-loop style (Shaw, 1995), this style is based on the notion of closed loop control. Data flow topology is cyclic between control functions. The style has two types of units: controlled process including process modeling as well as process variables and sensors, and controller including control algorithms and set points. The interactions of these units involved intense data interactions, where the controller receives values of measured process variables at predefined time points and produces control signals to manipulate the controlled process.

#### **2.3.9** Finite State Machines

It is often useful to combine models, especially concurrent ones, hierarchically with finite-state machines (FSM) to get modal models. FSM execution is strictly sequential. A component is called a *state* or *mode*, and exactly one state is active at a time. Connections between states denote transitions or transfer of control between states and execution is an ordered sequence of state transitions. FSM models are excellent for describing control logic and are easily mapped to either hardware or software implementations (Fielding, 1999). However, the number of states can get very large even in simple system. Hence, FMS is often combined with other styles.

#### 2.3.10 Mobile Code

Mobile code styles use mobility to dynamically change the distance between the processing and source of data or destination of results (Fielding, 1999; Fuggetta et al., 1998). A site abstraction is introduced at the architectural level, as part of the active configuration, thereby taking into account the location of the different components. The concept of location makes it possible to model the cost of an interaction between components at the design level. An interaction between components in the same location is considered to have negligible cost compared to an interaction through a communication network. By changing its location, a component may improve the proximity and quality of its interaction, reducing interaction costs and thereby improving efficiency and performance. In all mobile code styles, a data element is dynamically transformed into a component. The virtual machine or interpreter is the main mobile code style (Garlan and Shaw, 1993). The virtual machine style provides code execution in a secured and reliable

way, preferably within a controlled environment. The benefits of VM are the separation between instruction and implementation on a particular platform (portability) and ease of extensibility. One of the most popular implementation is the Java Virtual Machine (JVM), which enables Java to be platform-independent. In the mobile agent style, an entire computational component is migrated to a remote site along with its state, the code it needs, and possibly some data required to perform the task. The main advantage of the mobile agent style is that there is greater flexibility in the selection of when to move the code. An application can be in the midst of processing information at one location when it decides to transfer to another location – presumably in order to narrow the distance between it and the next set of data it wishes to process (Fielding, 1999).

#### 2.3.11 Data Abstraction and Object-Oriented Organization