# FIELD-PROGRAMMABLE GATE-ARRAY (FPGA) IMPLEMENTATION OF LOW-DENSITY PARITY-CHECK (LDPC) DECODER IN DIGITAL VIDEO BROADCASTING — SECOND GENERATION SATELLITE (DVB-S2)

A Thesis Submitted to the

College of Graduate Studies and Research

in Partial Fulfillment of the Requirements

for the degree of Master of Science

in the Department of Electrical and Computer Engineering

University of Saskatchewan

Saskatoon, Saskatchewan, Canada

By Kung Chi Cinnati Loi

© Kung Chi Cinnati Loi, August 2010. All rights reserved.

### PERMISSION TO USE

In presenting this thesis in partial fulfilment of the requirements for a Postgraduate degree from the University of Saskatchewan, I agree that the Libraries of this University may make it freely available for inspection. I further agree that permission for copying of this thesis in any manner, in whole or in part, for scholarly purposes may be granted by the professor or professors who supervised my thesis work or, in their absence, by the Head of the Department or the Dean of the College in which my thesis work was done. It is understood that any copying or publication or use of this thesis or parts thereof for financial gain shall not be allowed without my written permission. It is also understood that due recognition shall be given to me and to the University of Saskatchewan in any scholarly use which may be made of any material in my thesis.

Requests for permission to copy or to make other use of material in this thesis in whole or part should be addressed to:

Department of Electrical and Computer Engineering

University of Saskatchewan

57 Campus Drive

Saskatoon, Saskatchewan

Canada, S7N 5A9

## Abstract

In recent years, LDPC codes are gaining a lot of attention among researchers. Its near-Shannon performance combined with its highly parallel architecture and lesser complexity compared to Turbo-codes has made LDPC codes one of the most popular forward error correction (FEC) codes in most of the recently ratified wireless communication standards. This thesis focuses on one of these standards, namely the DVB-S2 standard that was ratified in 2005.

In this thesis, the design and architecture of a FPGA implementation of an LDPC decoder for the DVB-S2 standard are presented. The decoder architecture is an improvement over others that are published in the current literature. Novel algorithms are devised to use a memory mapping scheme that allows for 360 functional units (FUs) used in decoding to be implemented using the Sum-Product Algorithm (SPA). The functional units (FU) are optimized for reduced hardware resource utilization on a FPGA with a large number of configurable logic blocks (CLBs) and memory blocks. A novel design of a parity-check module (PCM) is presented that verifies the parity-check equations of the LDPC codes. Furthermore, a special characteristic of five of the codes defined in the DVB-S2 standard and their influence on the decoder design is discussed.

Three versions of the LDPC decoder are implemented, namely the 360-FU decoder, the 180-FU decoder and the hybrid 360/180-FU decoder. The decoders are synthesized for two FPGAs. A Xilinx Virtex-II Pro family FPGA is used for comparison purposes and a Xilinx Virtex-6 family FPGA is used to demonstrate the portability of the design. The synthesis results show that the hardware resource utilization and minimum throughput of the decoders presented are competitive with a DVB-S2 LDPC decoder found in the current literature that also uses FPGA technology.

## ACKNOWLEDGEMENTS

The project is supported by the Natural Sciences and Engineering Research Council of Canada and SED Systems Inc., a division of Calian Ltd., Saskatoon, SK, Canada. I would like to thank my supervisor, Dr. Seok-Bum Ko, for his support in this project. In the beginning of my M.Sc. program, he gave me a lot of freedom in the topic selection, and supported and guided me in every decision that I made along the way. Even when he was away he constantly touched base with me to make sure everything is going well. Without Dr. Ko's support, this project would not have been possible. I would also like to thank my supervisor at SED Systems, Mr. Dave Armstrong, and all other SED Systems employees for their help while I researched at SED Systems. Special thanks for Prof. Dave Dodds and Mr. Dennis Akins for setting up the project with SED Systems. Thanks to all the professors at the University of Saskatchewan who have supported me and their instruction, help and inspiration during my studies. Also, thanks to Dr. J. C. Lo for his input on the PCM design. Finally, a big thanks to my parents, friends and family for their moral support throughout the years.

# Contents

| Pe            | ermissio                                           | on to Use                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1                                                                                      |

|---------------|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| $\mathbf{A}$  | bstract                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ii                                                                                     |

| A             | cknowle                                            | edgements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | iii                                                                                    |

| Co            | ontents                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | iv                                                                                     |

| Li            | st of Ta                                           | ables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | vi                                                                                     |

| $\mathbf{Li}$ | st of Fig                                          | gures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | vii                                                                                    |

| $_{ m Li}$    | st of Al                                           | obreviations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | viii                                                                                   |

| 1             | 1.2 M<br>1.3 De                                    | terature Review of DVB-S2 LDPC Decoders                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1<br>2<br>7<br>9<br>10                                                                 |

| 2             | 2.1 An<br>2.2 Re                                   | round Information rchitecture of Target FPGA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 11<br>11<br>15<br>24                                                                   |

| 3             | 3.1 An 3.2 An 3.3 3.3 3.3 An 3.3 3.3 3.4 An 3.5 An | rechitecture of the Decoder rechitecture of the RAM and the ROM  2.1 Memory Mapping Scheme  2.2 Generation of ROM Coefficient  2.3 Function and Architecture of the Shuffle Network  2.4 Special Case of Code Rates in Short Frames rechitecture of the Functional Units  3.1 Implementation of the $\psi$ Function  3.2 Usage and Design of the SUM FIFO  3.3 LLR Value Update  3.4 The Initialization Step rechitecture of the Parity Check Module rechitecture of the LLR and Decoded Message Buffers rechitecture of the 180-FU and Hybrid 360/180-FU Decoders | 33<br>33<br>38<br>39<br>47<br>48<br>51<br>53<br>56<br>61<br>63<br>64<br>65<br>72<br>74 |

| 1             | Rosult                                             | s and Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 70                                                                                     |

|                                                                      | 4.1 Synthesis Results                            | 81 |  |

|----------------------------------------------------------------------|--------------------------------------------------|----|--|

|                                                                      | 4.3 Simulation Results                           | 85 |  |

| 5                                                                    | Conclusion                                       | 87 |  |

| References                                                           |                                                  |    |  |

| A The Encoding and Decoding of a Simple Linear Systematic Block Code |                                                  |    |  |

| $\mathbf{B}$                                                         | Values from Annex B and C of the DVB-S2 Standard | 99 |  |

# LIST OF TABLES

| 2.1                                                                                                         | The values of $p$ values in DVB-S2 LDPC codes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 26                                                                                     |

|-------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7                                                               | Description of the Inputs and Outputs of the Decoder RAM size of all the block length and code rates in DVB-S2 row, shift and ishift coefficients in the ROM of the example Row Weight of submatrix $\bf A$ of Problematic Code Rates $\psi$ Function Quantization Scheme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 34<br>41<br>50<br>52<br>59<br>60<br>61                                                 |

| 4.1<br>4.2                                                                                                  | Synthesis results and comparison                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 79<br>84                                                                               |

| A.1<br>A.2                                                                                                  | Example of a (7,4) Linear Systematic Block Code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 95<br>97                                                                               |

| B.1<br>B.2<br>B.3<br>B.4<br>B.5<br>B.6<br>B.7<br>B.8<br>B.9<br>B.10<br>B.11<br>B.12<br>B.13<br>B.14<br>B.15 | N=64800, Code Rate = $1/4$ $N=64800$ , Code Rate = $1/3$ $N=64800$ , Code Rate = $2/5$ $N=64800$ , Code Rate = $1/2$ $N=64800$ , Code Rate = $3/5$ $N=64800$ , Code Rate = $2/3$ $N=64800$ , Code Rate = $2/3$ $N=64800$ , Code Rate = $3/4$ $N=64800$ , Code Rate = $4/5$ $N=64800$ , Code Rate = $4/5$ $N=64800$ , Code Rate = $8/9$ $N=64800$ , Code Rate = $8/9$ $N=64800$ , Code Rate = $9/10$ $N=16200$ , Code Rate = $1/5$ $N=16200$ , Code Rate = $1/3$ $N=16200$ , C | 99<br>100<br>100<br>101<br>102<br>103<br>104<br>105<br>106<br>107<br>108<br>108<br>109 |

| B.17<br>B.18<br>B.19<br>B.20                                                                                | N=16200, Code Rate = $2/3$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 109<br>110<br>110<br>110<br>111<br>111                                                 |

| ⊥⁄.∠⊥                                                                                                       | $T_1 = 10200$ , code $T_{0000} = 0/0$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | TIT                                                                                    |

# LIST OF FIGURES

| 1.1  | Graph of the $\psi$ function                                  |

|------|---------------------------------------------------------------|

| 2.1  | Example of a Tanner graph                                     |

| 2.2  | Initialization step of SPA                                    |

| 2.3  | Check node update step of SPA                                 |

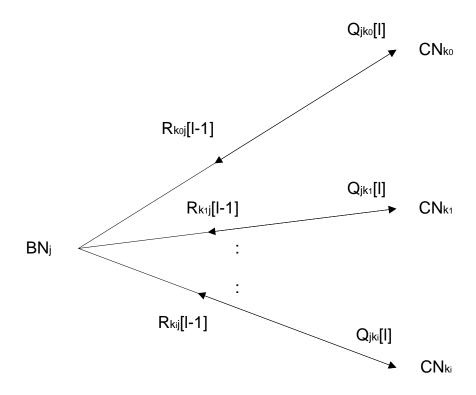

| 2.4  | Bit node update step of SPA                                   |

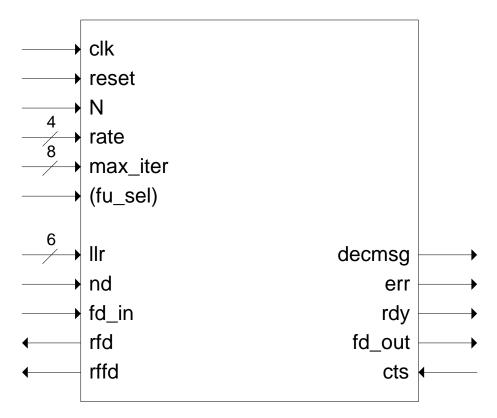

| 3.1  | Inputs and Outputs of the LDPC decoder                        |

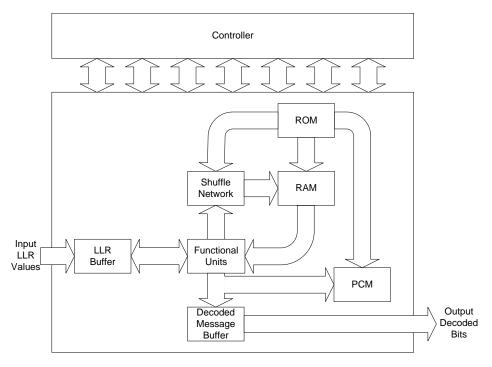

| 3.2  | Top level block diagram of LDPC decoder                       |

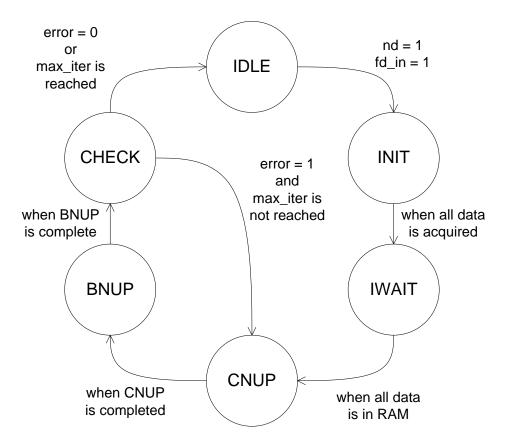

| 3.3  | Controller FSM state diagram                                  |

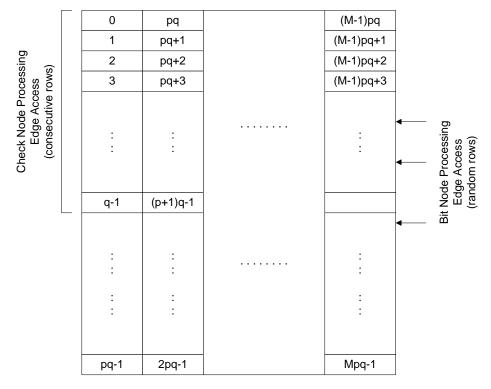

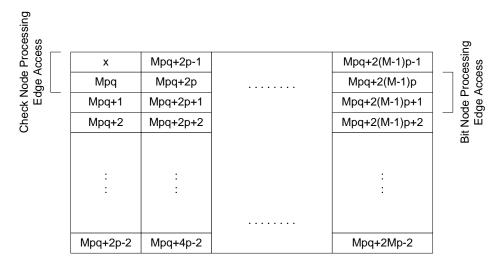

| 3.4  | Edge placement and access of the Top RAM                      |

| 3.5  | Edge placement and access of the Bottom RAM                   |

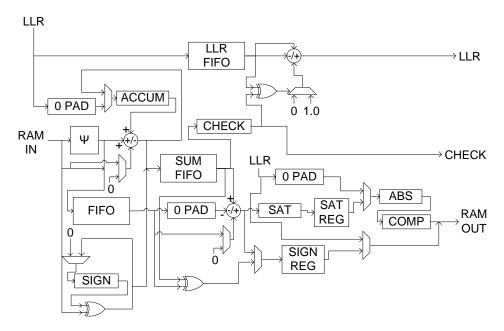

| 3.6  | Block diagram of functional unit                              |

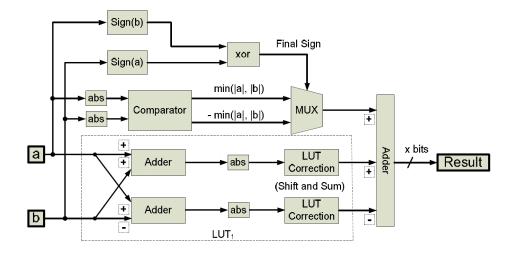

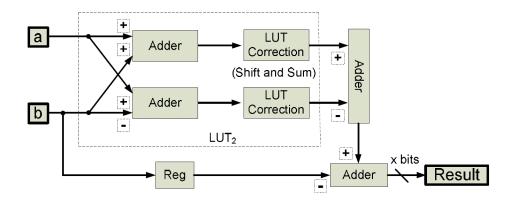

| 3.7  | Block Diagram of the boxplus unit                             |

| 3.8  | Block Diagram of the boxminus unit                            |

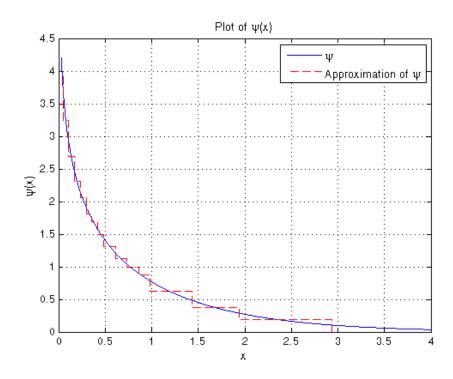

| 3.9  | Graph of the $\psi$ function and its approximation            |

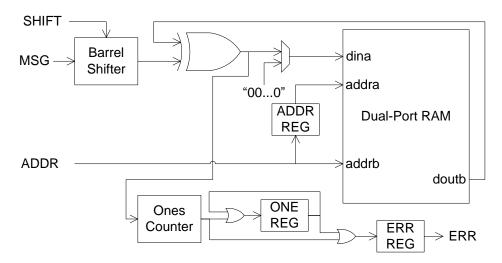

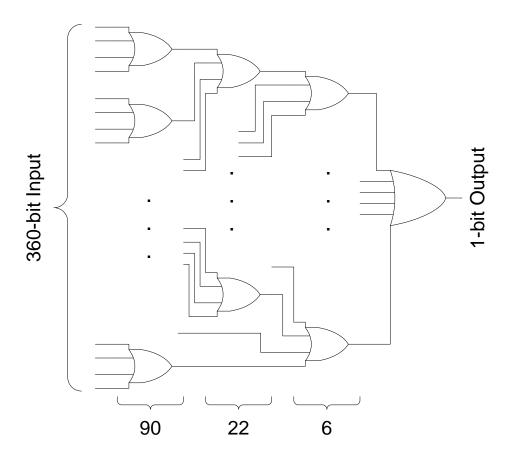

| 3.10 | Block diagram of parity check module                          |

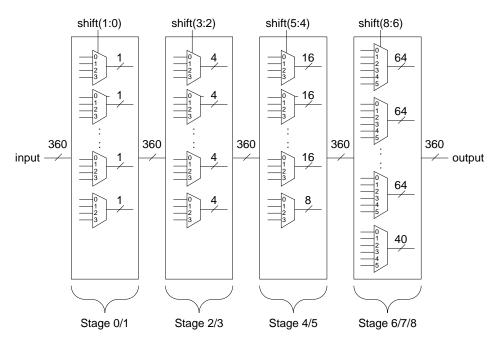

| 3.11 | Block diagram of the barrel shifter                           |

| 3.12 | Block diagram of ones counter                                 |

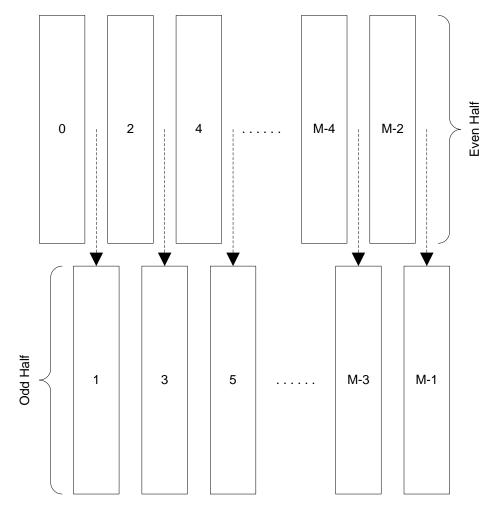

| 3.13 | Diagram of splitting the RAM for 180 FU implementation        |

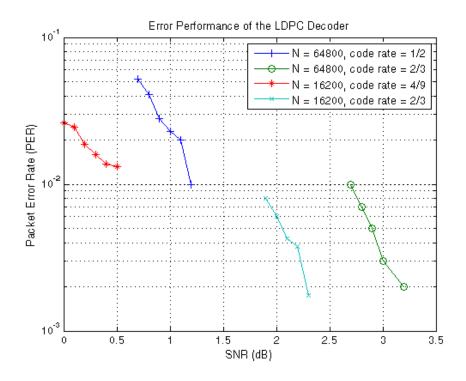

| 4.1  | PER vs. SNR of the LDPC decoder                               |

| A.1  |                                                               |

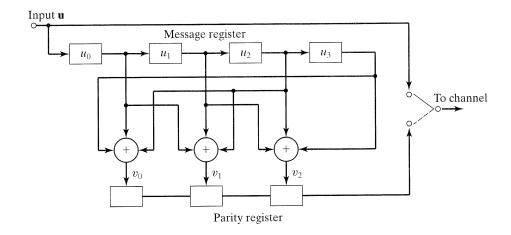

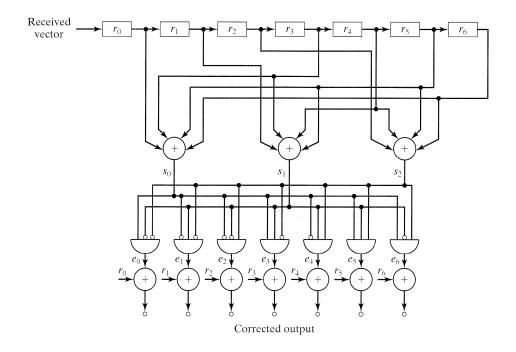

| A.2  | An example decoder for the (7,4) linear systematic block code |

## LIST OF ABBREVIATIONS

APSK - Amplitude and Phase-Shift Keying

ASIC - Application-Specific Integrated Circuit

AWGN - Additive White Gaussian Noise

BCH - Bose, Chaudhuri and Hocquenghem codes

**BPSK** - Binary Phase-Shift Keying

BS - Barrel Shifter

BSC - Binary Symmetric Channel

**BRAM -** Block Random-Access Memory

**CLB** - Configurable Logic Block

dB - decibel

DVB-C2 - Digital Video Broadcasting - Second Generation Cable

DVB-T2 - Digital Video Broadcasting - Second Generation Terrestrial

DVB-S2 - Digital Video Broadcasting - Second Generation Satellite

FEC - Forward Error Correction

FIFO - First-In First-Out

FPGA - Field-Programmable Gate-Array

FF - Flip-Flop

$\mathbf{FU}$  - Functional Unit

GPU - Graphics Processing Unit

$\mathbf{HDL}$  - Hardware Description Language

IC - Integrated Circuit

**IP** - Intellectual Property

IRA - Irregular Repeat-Accumulate

**Kb** - Kilobit

LDPC - Low-Density Parity-Check

LLR - Log-Likelihood Ratio

LOF - List of Figures

**LOT** - List of Tables

**LUT** - Look-Up Table

**LRP** - Least Reliable Position

LSB - Least Significant Bit

Mb - Megabit

MBWA - Mobile Broadband Wireless Access

MRIP - Most Reliable Independent Position

MRP - Most Reliable Position

MLD - Maximum Likelihood Decoding

MSB - Most Significant Bit

**OC** - Ones Counter

PCM - Parity Check Module

PER - Packet Error Rate

**PSD** - Power Spectral Density

**PSK** - Phase-Shift Keying

PWL - Piece-Wise Linear

**QPSK -** Quadrature Phase-Shift Keying

RAM - Random-Access Memory

RMSE - Root Mean Square Error

**ROM -** Read-Only Memory

**SNR** - Signal-to-Noise Ratio

VHDL - VHSIC Hardware Description Language

VHSIC - Very-High-Speed Integrated Circuit

WLAN - Wireless Local Area Network

**WPAN -** Wireless Personal Area Network

**XOR -** Exclusive-OR

#### Chapter 1

#### Introduction

In digital data transmission or storage systems, messages transmitted or stored often go through a channel or storage medium that introduces noise that may corrupt the original message. Forward error correction (FEC) codes were introduced in order to solve this problem. In the case of a data transmission communication system, an encoder is introduced at the transmitter to encode the message bits by adding redundancy to the message. This redundancy is transmitted to the receiver along with the message. At the receiver, the received message is decoded in hopes of correcting the errors that may have been introduced during the transmission through the channel and retrieving the original message. According to Shannon's theorem [1], no matter how noisy the communication channel is, there exists an error correction code that can make the probability of error arbitrarily small provided that the transmission rate is less than the Shannon limit. Over the years, researchers have been developing different kinds of codes to increase the transmission rate, in hopes to reach the channel capacity as described by Shannon. In recent years, one of the most successful types of codes in doing so has been LDPC codes.

LDPC codes were originally introduced by Gallanger [2] in the 1960s. However, due to the lack of an efficient decoding algorithm and subpar hardware capabilities, the codes were not widely used at the time and slowly faded away. In the 1990s, LDPC codes were rediscovered and were shown to have performance close to the Shannon limit [3]. In addition, the encoding and decoding process is much less complex in LDPC codes compared to Turbo codes [4], another code that has shown to perform close to the Shannon limit. Furthermore, LDPC codes have highly parallel code structures which are extremely suitable for FPGA implementation. Due to its advantages, it was adopted by many standards to be used for FEC such as Digital Video Broadcasting – Second Generation Satellite (DVB-S2),

Digital Video Broadcasting – Second Generation Cable (DVB-C2), and Digital Video Broadcasting – Second Generation Terrestrial (DVB-T2) [5], wireless local area network (WLAN) air interface (802.11), wireless personal area networks (WPAN) (802.15), broadband wireless metropolitan area network (802.16), and mobile broadband wireless access (MBWA) networks (802.20), among others.

Field-programmable gate-array (FPGA) is an integrated circuit (IC) consisting of logic circuit elements that can be configured by the user after the IC is fabricated, as opposed to application-specific integrated circuits (ASICs), where the users' logic circuits are configured prior to fabrication. FPGAs are usually programmed using hardware description languages (HDL), such as VHDL or Verilog. The advantages of the FPGAs compared to ASIC is in its flexibility to be re-programmed without the need to re-fabricate the IC, which allows for faster turn-around time for hardware designers. For example, design faults can be fixed by simply fixing the programming code, re-synthesizing the design, generating all the programming files and re-programing the FPGA, as opposed to submitting the updated design for fabrication. Furthermore, an existing FPGA design can be implemented for a different target FPGA by simply re-synthesizing the existing design for the new target FPGA, which makes FPGAs very portable. For these reasons among others, FPGA designs have gained much attention in recent years.

This thesis presents a FPGA implementation of a LDPC decoder in the DVB-S2 standard. The architecture of the LDPC decoder in this thesis is a combination and improvement of some of the designs published in the current literature. These designs are reviewed in the next section.

#### 1.1 Literature Review of DVB-S2 LDPC Decoders

Since the adoption of LDPC codes into the DVB-S2 standard in 2005 [6], researchers have been working on designing efficient implementations of an LDPC decoder that is compliant with the standard.

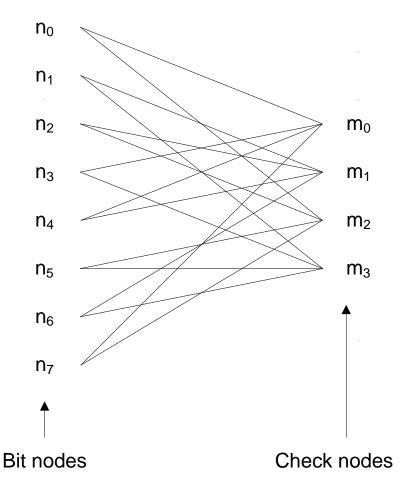

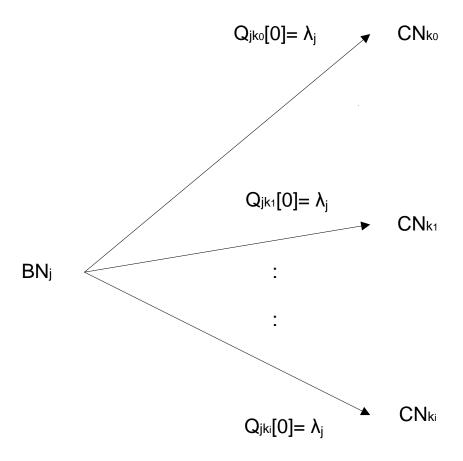

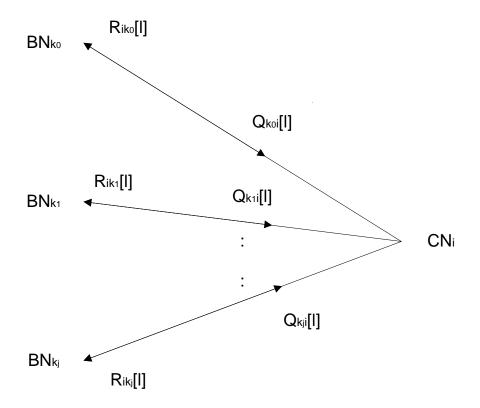

The algorithm used for decoding LDPC codes is a message passing algorithm, where messages, which are real numbers, are passed between two sets of nodes, called bit nodes and check nodes, through a code rate-specific interconnection network. These messages are updated at the nodes by performing a mathematical calculation. A more detailed description of the decoding algorithm is presented in Section 2.3.

One of the challenges in implementing the LDPC decoder for the DVB-S2 standard is its large block length, or frame size. In the DVB-S2 standard, the block length, N, of the LDPC codes is either 64800 bits, called normal frames, or 16200 bits, called short frames. For high throughput, which means a high number of message bits are decoded per unit of time, the LDPC decoders can be designed with a fully parallel architecture, such as the one by Blanksby and Howland [7]. In the fully parallel architecture of the LDPC decoder, N bit node functional units (FUs) are connected to N-K check node FUs, where K is the number of bits in the transmitted message, through a network of interconnections. A more detailed discussion on FUs is presented in Section 3.3. However, even with a 1024-bit block length, such as the decoder by Blanksby and Howland [7], the routing of the interconnections between the FUs is already cumbersome, not to mention the even larger block lengths in the DVB-S2 standard. Furthermore, N bit node FUs and N-K check node FUs need to be implemented. Thus, a fully parallel architecture of the time is not practical to be used by the LDPC decoders for the DVB-S2 standard. On the other hand, in a fully serial architecture, where only one FU is implemented to perform all N+N-K calculations, a very large memory must be used to store all temporary values updated at the nodes and the throughput of the decoder becomes extremely low. Therefore, a partially parallel architecture is best suited for the implementation of the LDPC decoders for the DVB-S2 standard. In 2006, Eroz et al. [8] present a memory architecture that allows for the usage of 360 FUs in the decoder design. In the paper, the authors explain how the interconnection between the bit and check nodes is mapped to memory and how the memory is accessed for processing.

The first known hardware decoder design compliant with the DVB-S2 standard is published in 2005 by Kienle et al. [9]. In their decoder design, 360 FUs are implemented, but it decodes only the normal frame code rates and not the short frame code rates. Furthermore, the authors have optimized the message passing algorithm, such that instead of updating all the messages in the bit node before passing all the messages to the check nodes for processing, and vice versa, some bit nodes are processed as soon as some of the check nodes

messages are updated and vice versa, which reduces processing time. In addition, the design is implemented using ASIC technology.

Subsequently, many other ASIC decoder designs have been published based on the decoder by Kienle et al. [9]. In 2005, Urard et al. [10] present a decoder that uses 360 FUs and supports both normal frames and short frames, yet does not support all the short frame code rates in the DVB-S2 standard. In 2006, Dielissen et al. [11] propose a decoder that uses fewer FUs by further subdividing the calculations at the nodes. The authors also use a modified algorithm, in which the node update calculations are simplified, called the minsum algorithm. However, their decoder also only handles normal frame code rates. Segard et al. [12] use a different decoding scheduling, called horizontal shuffle scheduling, where multiple bit and check nodes are updated in one step. In 2007, Masera et al. [13] present a decoder that supports the DVB-S2, 802.11n and 802.16 standards, but only 32 FUs are used, so the throughput of the decoder when used for the DVB-S2 standard is very low. Brack et al. [14] present a decoder that uses 90 FUs and only decodes normal frame code rates. In 2009, Zhang et al. [15] and Ying et al. [16] also use modified versions of the min-sum algorithm.

In addition to ASIC designs, some hardware designs have been implemented on FPGAs. In 2005, Yadav and Parhi [17] have proposed LDPC codes different from the ones that are used in the standard [6]. However, they were not able to implement all the code rates into one decoder due to memory limitations at the time and the paper only discusses normal frame code rates. In 2007, Gomes et al. [18] have presented a decoder that uses 180, 90 or 45 FUs. The paper presents a method that can reduce the number of FUs to factors of 360 without the need to increase the amount of memory utilization. The architecture of the decoder is the most similar to the one presented in Chapter 3, so its synthesis results and throughput are used for comparison in Chapter 4. In 2008, Beuschel and Pfleiderer [19] designed a LDPC decoder that supports any LDPC code up to the block length of 65536 bits. However, it only uses 16 FUs, which deteriorates the throughput to only about 75 Mbps.

In the implementation of the FUs, one of the main concerns is the approximation of the

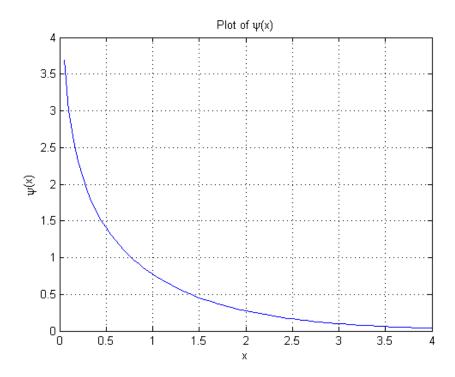

**Figure 1.1:** Graph of the  $\psi$  function.

$\psi$  function defined as follows:

$$\psi(x) = -\ln\left(\tanh\left|\frac{x}{2}\right|\right) = \ln\left(\frac{(1+e^{-|x|})}{(1-e^{-|x|})}\right)$$

(1.1)

and the graph of the equation is shown in Figure 1.1. One of the approximation approaches is to use a look-up table (LUT) where an input value is mapped into an output value. However, using a uniform step size for the input values generates wasted storage in the LUT because at high input values the slope of the  $\psi$  function graph is close to zero. In 2001, Zhang et al. [20] propose the use of a variable precision quantization scheme for the inputs and outputs of the  $\psi$  function. In this scheme, if the value is less than 1, then its most significant bit (MSB) is 0, and the rest of the bits are fractional; if the value is greater than or equal to 1, then the MSB is 1, the decimal point is between the 3rd and 4th MSB, and the integer part is interpreted as (n is the number of bits):

$$v_{n-1} \cdot \overline{v}_{n-2} \cdot \overline{v}_{n-3} \cdot 2^2 + v_{n-2} \cdot 2 + v_{n-3}$$

(1.2)

The authors show that the use of 6 magnitude bits for the messages between the bit node and the check nodes provides reasonable trade-off between hardware complexity and

performance. Furthermore, the proposed variable precision quantization scheme improves error performance by about 0.1 dB compared to a uniform quantization scheme.

In 2006, Oh and Parhi [21] propose a different variable quantization scheme for the  $\psi$  function using LUTs. Their quantization scheme is based on the uniform (q:f) quantization scheme, where q is the total number of bits, including the sign bit, and f is the number of bits in the fractional part of the value. For input values, x, below decimal number 1.0, the (q:f) uniform quantization scheme is used for their outputs values. If the input values are 1.0 or above, then its output values use a quantization scheme given as follows:

$$(q, f)$$

for  $0 < x < 2^{(q-f-3)}$

$(q-1, f-1)$  for  $2^{(q-f-3)} \le x < 2^{(q-f-2)}$

$(q-2, f-2)$  for  $2^{(q-f-2)} \le x < 2^{(q-f-1)}$  (1.3)

The proposed quantization scheme reduces the LUT size by 50% compared to the uniform (q:f) quantization scheme. Furthermore, the authors propose further reduction of the LUT size to 75% by using the following quantization scheme instead of (1.3):

$$(q-1, f-1)$$

for  $0 < x < 2^{(q-f-3)}$

$(q-2, f-2)$  for  $2^{(q-f-3)} \le x < 2^{(q-f-2)}$

$(q-3, f-3)$  for  $2^{(q-f-2)} \le x < 2^{(q-f-1)}$  (1.4)

Using (1.4) to approximate the  $\psi$  function reduces the LUT size to only have  $2^{(q-3)}$  entries, which means the input of the LUT is q-3 bits. Thus, Oh and Parhi propose a compression function that reduces the messages sent between the bit nodes and the check nodes to only have q-3 bits. Furthermore, the authors show that the performance loss of using the LUT reduction schemes presented is less than 0.05 dB.

Aside from using LUTs to approximate the  $\psi$  function, Masera et al. [22] have proposed two other approximation techniques: a) piece-wise linear (PWL) approximation and b) a direct implementation of base 2 formulation (PSI2). The PWL approximation uses linear equations to approximate sections of the  $\psi$  function. The coefficients of the linear equations are selected to easily implemented with shift and add operations. The PSI2 approximation changes the base of the logarithmic and exponential functions in (1.1) to base 2 and uses state-of-the-art binary logarithmic arithmetic units to approximate the  $\psi$  function. Both of

the techniques show to have no more than 0.1 dB performance loss compared to the infinite precision case, but the implementation of these techniques in hardware is more complex than using the LUT approximations. Other approximations can also be found in the literature based on different approximations of the  $\psi$  function, different approximations of the node update equations and different scheduling techniques, i.e. the order that the bit node and check nodes are updated. A comparison and analysis of these algorithms is published by Papaharalabos et al. [23].

#### 1.2 Motivation

In all the LDPC decoder designs discussed in Section 1.1, only the design of the FUs and the memory mapping schemes are shown. These units perform the updates at the bit and check nodes and the message passing between the nodes. However, no publication presents the architecture of a module that is used to verify the parity-check equations to perform hard-decision decoding. More information about parity-check equations is presented in Section 2.2. Furthermore, most of the decoders only support normal frames in the DVB-S2 standard. Some of the ones that support short frames omit some code rates defined in the standard.

Additionally, most of the decoder designs are implemented using ASICs, and only a few use FPGAs. One reason may be that ASIC implementations give the designers the freedom to use as many hardware resources as it is necessary to implement the decoder, as opposed to FPGAs that have a limited number of hardware resources fabricated with the device that is available to the users. However, FPGA designs gives the design increased portability and faster design turn-around time compared to ASIC designs, as discussed earlier in this chapter. Thus, in this thesis, the main design goal of the LDPC decoder is to reduce hardware resource utilization, such that the design can be implemented using FPGAs. One way to reduce hardware utilization is by reducing the number of FUs, such as the decoder by Beuschel and Pfleiderer [19], but using fewer FUs corresponds to lowering throughput. Therefore, the other design goal of the decoder in this thesis is not to reduce throughput drastically in the process of reducing hardware resource utilization.

This research project is done in collaboration with SED Systems<sup>1</sup>, who have expressed a high interest in an FPGA implementation of the DVB-S2 LDPC decoder. SED Systems currently use commercial ASIC decoders in use in their DVB-S2 receivers. However, implementing the LDPC decoder section of the receiver for use on an FPGA can facilitate system debugging and increase the portability of the decoder to other systems. Some existing commercial decoders are sold as system-on-chip ASICs, which include the complete DVB-S2 receiver design [24], or as devices in a chassis [25, 26]. In some situations, the functionalities of these complete receiver solutions are not applicable, which makes these products very difficult, if not impossible, to integrate with other components.

Furthermore, the complete receiver solutions have a limited throughput. In some situations, if a higher throughput is required that is not supported by the complete receiver solutions, the receiver must be re-designed. However, using an FPGA solution, multiple decoders can be instantiated and executed in parallel to increase throughput. In other situations when lower throughput is sufficient, an FPGA implementation can be easily modified to reduce throughput by for example, reducing the number of FUs. Thus, the FPGA implementation provides the flexibility to implement "special" DVB-S2 receivers that the complete receiver solutions cannot accommodate.

There are also software solutions available for LDPC decoders, such as the MATLAB built-in functions dvbs2ldpc [27] and fec.ldpcdec [28], yet the large block lengths of the LDPC codes defined in the DVB-S2 standard makes the throughput of the software solutions very low. Furthermore, the low number of processors in current computer architectures does not allow software implementations to efficiently take advantage of the parallel structure of LDPC codes.

Moreover, currently, the two world leading FPGA suppliers, Xilinx [29] and Altera [30], only distribute FPGA intellectual property (IP) Core for DVB-S2 LDPC encoders and not for decoders. However, some FPGA IP designs can be purchased from smaller independent suppliers, such as Navtel Systems [31], SoftJin [32] and RAD3 Communications [33].

Even though the architecture of the decoders presented in this thesis targets the LDPC decoder in the DVB-S2 standard, the soon-to-be ratified DVB-C2 and DVB-T2 standards

<sup>&</sup>lt;sup>1</sup>SED Systems, a Division of Calian Ltd., Saskatoon, SK, Canada

also adopt LDPC codes for FEC with almost the same structures as the ones in the DVB-S2 standard. Thus, the LDPC decoders described herein may be extended to include DVB-C2 and DVB-T2 standard LDPC codes in the future.

# 1.3 Description of the Problem and Major Contributions

Based on the discussion in Section 1.2, the problem with the existing DVB-S2 LDPC decoders is that the published designs are incomplete, as no module is presented to verify the parity-check equations and many of the designs only handle normal frames, and not short frames. The existing designs are also less flexible for the end users as they are implemented using ASIC technology. However, implementing the design using FPGAs requires optimizations for the decoder architecture to reduce hardware resource utilization as hardware resources are limited in FPGAs. Furthermore, there are FPGA decoder designs that reduce hardware resources by reducing the number of FUs used, but also reduce the throughput, which is not desired. The objective of this thesis is to improve the DVB-S2 LDPC decoder designs by combining the decoder architectures published in the current literature and is a proposed solution for the aforementioned problems. This is verified by comparisons with other implementations for correctness and performance.

The main issue that originally challenged SED Systems in implementing the DVB-S2 LDPC decoder in FPGA is the memory size. Originally, the idea is to implement two RAMs for message exchange, where one RAM would store the messages temporarily, while the other is used for computing, which might consume too many memory resources on the FPGA. However, using the decoder architecture and memory organization proposed by Eroz et al. [8], the memory required by the decoder to handle all code rates in the DVB-S2 standard is only approximately 2 Mb, which can be easily accommodated by most modern FPGAs. Nevertheless, the authors do not clearly indicate the algorithm that is used to map the interconnection network between the bit and check nodes to the RAM. Thus, a novel algorithm is devised and presented in Section 3.2.1 to perform such mapping.

Another architecture that is improved upon is the FU architecture by Gomes et al. [34]. The components of the FU are modified in order to reduce hardware resource utilization of the FPGA, while maintaining a competitive decoding throughput. The  $\psi$  function and adders are used instead of the boxplus and boxminus units. More details on these improvements are presented in Section 3.3. Furthermore, the decoder by Gomes et al. [18] is used for comparison in Chapter 4 as previously mentioned.

Section 1.2 has indicated that none of the published decoders in the current literature present a module that verifies the parity-check equations. Thus, a novel module is designed, called the parity-check module (PCM), and presented in this thesis to perform the verification of the parity-check equations. Section 3.4 shows that the operation of the PCM is very similar to the operation of the DVB-S2 LDPC encoder. Thus, the architecture of the PCM is based on the DVB-S2 LDPC encoder architecture by Gomes et al. [35].

Furthermore, as mentioned in Section 1.2, the short frame code rates are not implemented in many of the designs in current literature. Among the ones that do, not all short frame code rates are supported or the details of the implementation are not clear. One of the reasons may be that there are some code rates in the short frame, denoted as special short frame code rates in this thesis, have a characteristic that changes the memory organization and memory mapping of the decoder. These code rates are discussed in more detail in Section 3.2.4.

#### 1.4 Organization of Thesis

The subsequent chapters of the thesis are organized as follows: Chapter 2 reviews some background information, including the architecture of the target FPGA, the encoding and decoding of linear block codes, and the encoding and decoding of LDPC codes in the DVB-S2 standard. Chapter 3 presents the architecture and implementation of the designed LDPC decoder, the details of each component of the decoder, and the modifications on the decoder architecture to create two other decoders designs. Chapter 4 presents the synthesis results and minimum throughput of the decoders on the target FPGAs and their comparison with the decoder designed by Gomes et al. [18], and the simulation results of the decoder are also presented. Chapter 5 concludes the thesis and suggests potential future work.

# CHAPTER 2

#### BACKGROUND INFORMATION

# 2.1 Architecture of Target FPGA

The DVB-S2 LDPC decoder design that is shown in Chapter 3 is implemented on two FPGAs: Xilinx Virtex-II Pro XC2VP100 and Xilinx Virtex 6 XC6VLX240T. In this section, a brief overview of the architecture of these two FPGAs is presented, in order to give some insight into some of the design decisions made in Chapter 3 and to help understand the synthesis results in Chapter 4. The information in this section and more information about the architecture of these two FPGAs can be obtained from Xilinx datasheets and user guides [36, 37, 38, 39].

The Xilinx XC2VP100 FPGA is a Virtex-II Pro device. In Virtex-II Pro FPGAs, configurable logic blocks (CLBs) are used to realize combinational and sequential logic designs. CLBs are arranged in arrays in an FPGA. A CLB is made up of four slices organized in two columns, with two slices on each column, with local feedback within the CLB. Each slice consists of two 4-input function generators, two storage elements, wide function multiplexers, carry logic and arithmetic logic gates.

Each of the two 4-input function generators can be used as a 4-input look-up table (LUT), among other functionalities. Each of the two function generators have four independent inputs and can be used to realize any 4-input Boolean function, and the propagation delay is independent of the function implemented. The output of each function generator can drive an output of the slice, the input of the XOR dedicated gate, the input of the carry-logic multiplexer, the D input of the storage element, or the input of a multiplexer. There is also logic within a slice that is capable of combining the 4-input functions generators to provide

functions of five, six, seven or eight inputs, or selected functions of nine inputs.

The storage elements in the slice can be configured as either edge-triggered D-type flipflops or level-sensitive latches. The D input can be driven by either the output of the function generators or directly by the input of the slice. For control, other than the clock input, there are also the clock enable and the set and reset inputs, which can be configured to be synchronous or asynchronous.

The function generators and multiplexers in the Virtex-II Pro FPGAs can be configured to implement multiplexing functionalities and the resources utilized are as follows:

- 2:1 multiplexer in one LUT

- 4:1 multiplexer in one slice

- 8:1 multiplexer in two slices

- 16:1 multiplexer in one CLB (four slices)

- 32:1 multiplexer in two CLBs (eight slices)

There are other functions that the multiplexers can be used for, but the discussion of these functionalities are beyond the scope of this thesis.

The dedicated lookahead carry logic allows for faster arithmetic addition and subtraction calculations. Each CLB has two separate carry chains. The arithmetic logic has an XOR gate that allows for a 2-bit full adder to be implemented within a slice.

For large memory needs, the Virtex-II Pro FPGAs have a large amount of 18 Kb block SelectRAM+ (BRAM) resources. Each BRAM can be configured to be single-port RAM, single-port ROM, dual-port RAM or dual-port ROM, where the ROMs are essentially RAMs without write ports. Each BRAM can also be configured to have one of the following dimensions:

- 16 Kb configurations:

- 16K  $\times$  1 bit

- $-8K \times 2$  bits

- $-4K \times 4$  bits

- 18 Kb configurations:

$-2K \times 9$  bits

$-1K \times 18$  bits

$-512 \times 36$  bits

where the first value is the depth of the memory and the second value is the width of the data.

Multiple BRAMs can be combined to implement memory deeper or wider memories. In the

single-port configuration, each BRAM memory has access to either 18 Kb or 16 Kb memory

locations depending on the configuration, it is synchronous and the input and output data

bus widths are identical.

In the dual-port configuration, each port of a BRAM that accesses a common 18 Kb

memory location, is synchronous and has independent control signals. The data width of

each port can be configured independently. The two ports have separate inputs and outputs

and have independent clock inputs.

For the target Xilinx Virtex-II Pro XC2VP100 FPGA, the total available logic and mem-

ory resources are as follows:

Number of Slices: 44096

Number of 4-Input LUTs: 88192

Number of Slice Flip-Flops: 88192

Total Number of 18 Kb BRAMs: 444

The Xilinx XC6LX240T belongs to the Virtex-6 FPGA family, which is a group Xil-

inx's state-of-the-art FPGA devices. Virtex-6 FPGAs also implement combinational and

sequential logic in CLBs, yet the architecture of the CLB differs from the Virtex-II Pro

FPGAs.

In Virtex-6 devices, each CLB consists of two slices, with no direct connection between

them. The two slices are organized in two columns, with a slice on each column. Each slice

is made up with four function generators, eight storage elements, wide-function multiplexers

and carry logic.

Each of the four function generators is implemented as a LUT. Each LUT can be used

to realize one 6-input Boolean function with six independent inputs or two 5-input Boolean

functions provided that at least one of the inputs is common. Thus, the function generators

13

have either one or two outputs, depending on the function. These outputs can drive the output of the slice, be used for fast lookahead carry logic, feed the D input of the storage elements or go to the multiplexers. Each slice has the ability to combine multiple function generators to implement Boolean functions with seven or eight independent inputs. For functions with more than eight inputs, multiple slices are necessary.

There are eight storage elements in a slice. Four out of the eight storage elements can be configured as edge-sensitive D-type flip-flops or level-sensitive latches, as in the Virtex-II Pro FPGAs. The other four storage elements can only be configured as edge-sensitive D-type flip-flops and they cannot be used if the former four are used as latches. The input to the storage elements can come directly from the input of the slice or from the output of the function generators. Similar to Virtex-II Pro FPGAs, the control inputs of the storage elements are clock, clock enable, and set and reset.

The function generators and multiplexers in a Virtex-6 CLB can be configured to be multiplexers using the following amount of resources:

- 4:1 multiplexer in one LUT

- 8:1 multiplexer in two LUTs

- 16:1 multiplexer in four LUTs

Similar to Virtex-II Pro devices, dedicated carry logic is available in the slices to provide fast lookahead carry logic to perform arithmetic addition and subtraction more efficiently.

Virtex-6 BRAMs differ from Virtex-II Pro BRAMs in that Virtex-6 BRAM stores up to 36 Kb of data. The Virtex-6 BRAM can be used as two independent 18 Kb BRAMs or one 36 Kb BRAM. Each 36 Kb BRAM can be configured to the following dimensions:

- 32 Kb configurations:

- $-64K \times 1$  bit (by cascading two 36 Kb BRAMs)

- $-32K \times 1$  bit

- $-16K \times 2 \text{ bits}$

- $-8K \times 4$  bits

- 36 Kb configurations:

$-4K \times 9$  bits

$-2K \times 18$  bits

$-1K \times 36$  bits

$-512 \times 72$  bits

and each 18 Kb BRAM can be configured to the same dimensions as in Virtex-II Pro. Similar to the Virtex-II Pro BRAMs, they can be implemented as single- or dual-port RAMs or ROMs. The memory is synchronous and in dual-port configuration, the ports have independent read and write data buses and clocks that share a common memory data.

The total available logic and memory resources of the XC6VLX240T FPGA are as follows:

Number of Slices: 37680

Number of 6-Input LUTs: 150720

Number of Slice Flip-Flops: 301440

Total Number of 36 Kb BRAMs: 416 (or 832 18 Kb BRAMs)

Review of Linear Block Codes 2.2

In this section, linear block codes are reviewed. The encoding and hard-decision decoding of linear block codes using generator and parity check matrices are presented. Decoding with soft-decision decoding metrics is also discussed and a general reliability-based soft-decision decoding scheme is presented. The information in this section is based on chapters 3 and 10 from Lin and Costello's book [40]. The block codes discussed in this section are binary block codes and the information source is also binary digits.

Block codes are a type of error control codes where a message block of length K information bits, denoted by  $\mathbf{u}$ , is encoded into codewords of N bits, denoted by  $\mathbf{v}$ . Linear block codes are block codes that the modulo-2 sum of two codewords is also a codeword. In fact, in linear block codes, it is possible to find K linearly independent codewords,  $\mathbf{g}_0, \mathbf{g}_1, \cdots$ ,  $\mathbf{g}_{K-1}$ , such that every codeword  $\mathbf{v}$  is a linear combination of these K codewords. These Klinearly independent codewords can be organized in a  $K \times N$  matrix to form the generator

15

matrix, as follows:

$$\mathbf{G} = \begin{bmatrix} \mathbf{g}_0 \\ \mathbf{g}_1 \\ \vdots \\ \mathbf{g}_{K-1} \end{bmatrix} = \begin{bmatrix} g_{00} & g_{01} & g_{02} & \cdots & g_{0,N-1} \\ g_{10} & g_{11} & g_{12} & \cdots & g_{1,N-1} \\ \vdots & \vdots & \vdots & & \vdots \\ g_{K-1,0} & g_{K-1,1} & g_{K-1,2} & \cdots & g_{K-1,N-1} \end{bmatrix}$$

(2.1)

where  $\mathbf{g}_i = (g_{i0}, g_{i1}, \dots, g_{i,N-1})$  for  $0 \le i \le K$  is one of the codewords. In order to encode the message  $\mathbf{u} = (u_0, u_1, \dots, u_{K-1})$ , the following operation is performed:

$$\mathbf{v} = \mathbf{u} \cdot \mathbf{G}$$

$$= (u_0, u_1, \dots, u_{K-1}) \cdot \begin{bmatrix} \mathbf{g}_0 \\ \mathbf{g}_1 \\ \vdots \\ \mathbf{g}_{K-1} \end{bmatrix}$$

$$= u_0 \mathbf{g}_0 + u_1 \mathbf{g}_1 + \dots + u_{K-1} \mathbf{g}_{K-1}$$

$$(2.2)$$

As shown in equation (2.2), the K linear independent codewords that form the generator matrix can be used to form all the codewords in the code. Thus the generator matrix completely specifies the linear block code and only the K rows of the generator matrix need to be stored in the encoder during implementation instead of all  $2^K$  N-bit codewords.

In order to further simplify encoding, linear systematic block codes can be used. The systematic structure means that the codeword can be subdivided into two parts, the message part and the redundant checking part. The message part has the K information bits of the original message before encoding and the redundant checking part has N-K bits, called parity-check bits, that are linear sums of the information bits. The generator matrix of a linear systematic code has the form:

$$\mathbf{G} = \begin{bmatrix} \mathbf{g}_0 \\ \mathbf{g}_1 \\ \mathbf{g}_2 \\ \vdots \\ \mathbf{g}_{K-1} \end{bmatrix} = \begin{bmatrix} p_{00} & p_{01} & \cdots & p_{0,N-K-1} & 1 & 0 & 0 & \cdots & 0 \\ p_{10} & p_{11} & \cdots & p_{1,N-K-1} & 0 & 1 & 0 & \cdots & 0 \\ p_{20} & p_{21} & \cdots & p_{2,N-K-1} & 0 & 0 & 1 & \cdots & 0 \\ p_{K-1,0} & p_{K-1,1} & \cdots & p_{K-1,N-K-1} & 0 & 0 & 0 & \cdots & 1 \end{bmatrix}$$

(2.3)

where  $p_{ij} = 0$  or 1. Let **P** be the left side of **G** in equation (2.3) and  $\mathbf{I}_k$  be the  $K \times K$  identity matrix on the right, then  $\mathbf{G} = [\mathbf{PI}_k]$ . Encoding message  $\mathbf{u} = (u_0, u_1, \dots, u_{K-1})$  with the generator matrix in equation (2.3) yields:

$$v_{N-K+i} = u_i \tag{2.4}$$

for  $0 \le i < K$ , which is the message part, and

$$v_j = u_0 p_{0j} + u_1 p_{1j} + \dots + u_{K-1} p_{K-1,j}$$

(2.5)

for  $0 \le j < N - K$ , which is the redundant checking part. The equations in (2.5) are called parity-check equations. When encoding linear systematic block codes, the parity-check bits are generated from the parity-check equations and the codeword is formed by concatenating the parity-check bits and the information bits.

For decoding linear block codes, there is another matrix that is associated with linear block codes, called the parity-check matrix, denoted matrix  $\mathbf{H}$ .  $\mathbf{H}$  is a  $(N-K) \times N$  matrix with N-K linearly independent rows that satisfies the equation  $\mathbf{G} \cdot \mathbf{H}^T = \mathbf{0}$ , where  $\mathbf{H}^T$  is the transpose of  $\mathbf{H}$ . Matrix  $\mathbf{H}$  also satisfies the equation  $\mathbf{v} \cdot \mathbf{H}^T = \mathbf{0}$ . If  $\mathbf{G}$  is in the systematic form as shown in equation (2.3), the  $\mathbf{H}$  matrix has the following form:

$$\mathbf{H} = [\mathbf{I}_{N-K}\mathbf{P}^T] = \begin{bmatrix} 1 & 0 & 0 & \cdots & 0 & p_{00} & p_{10} & \cdots & p_{K-1,0} \\ 0 & 1 & 0 & \cdots & 0 & p_{01} & p_{11} & \cdots & p_{K-1,1} \\ 0 & 0 & 1 & \cdots & 0 & p_{02} & p_{12} & \cdots & p_{K-1,2} \\ \vdots & & & & & & \\ 0 & 0 & 0 & \cdots & 1 & p_{0,N-K-1} & p_{1,N-K-1} & \cdots & p_{K-1,N-K-1} \end{bmatrix}$$

(2.6)

The parity-check equations can also be generated from the parity-check matrix, and linear block codes are also completely specified by its parity-check matrix **H**.

Let  $\mathbf{v} = (v_0, v_1, \dots, v_{N-1})$  be the transmitted codeword and  $\mathbf{r} = (r_0, r_1, \dots, r_{N-1})$  be the received vector from the channel. Subsequently, the error vector, denoted  $\mathbf{e}$ , is given by:

$$\mathbf{e} = \mathbf{r} + \mathbf{v}$$

$$= (e_0, e_1, \cdots, e_{N-1})$$

(2.7)

where  $e_j = 1$  if and only if  $r_j \neq v_j$  and  $e_j = 0$  if and only if  $r_j = v_j$ . By rearranging the terms, the following equations are produced:

$$\mathbf{v} = \mathbf{r} + \mathbf{e} \tag{2.8}$$

$$\mathbf{r} = \mathbf{v} + \mathbf{e} \tag{2.9}$$

Since the decoder receives  $\mathbf{r}$  from the channel, the goal of the decoder is to generate  $\mathbf{e}$  in order to recover the original codeword  $\mathbf{v}$ . Subsequently, for linear systematic block codes, the original message can be obtained from the message part of  $\mathbf{v}$ .

When decoding, the decoder receives  $\mathbf{r}$  and produces the syndrome of  $\mathbf{r}$ , denoted by  $\mathbf{s}$ , by performing the following calculation:

$$\mathbf{s} = \mathbf{r} \cdot \mathbf{H}^T \tag{2.10}$$

The syndrome vector has length N - K and since  $\mathbf{v} \cdot \mathbf{H}^T = \mathbf{0}$ ,  $\mathbf{s} = \mathbf{0}$  if and only if  $\mathbf{r}$  is a codeword, otherwise  $\mathbf{s} \neq \mathbf{0}$ . However, if  $\mathbf{e}$  is itself a codeword, then  $\mathbf{r} = \mathbf{v} + \mathbf{e}$  is also a codeword, from the definition of linear block codes. Thus, the syndrome,  $\mathbf{s} = \mathbf{0}$ , but  $\mathbf{r}$  is not the original codeword sent through the channel, in which case, it is said that a decoding error has occurred. Furthermore, according to equation (2.9),  $\mathbf{s}$  can also be written as:

$$\mathbf{s} = \mathbf{e} \cdot \mathbf{H}^T \tag{2.11}$$

Solving the set of linear equations resulting from the expansion of equation (2.11) would yield the error vector  $\mathbf{e}$ . However, the result of the linear equations does not have a unique solution. Thus, in order to minimize decoding error, the most probable solution is selected. In a binary symmetric channel (BSC), where the output of the channel is a binary digit, the most probable solution is the one with the fewest number of non-zero elements. Furthermore, for large values of N and K, solving the set of N-K equations with N unknowns becomes impractical, so more efficient methods are required.

One of these methods is called syndrome decoding. In this decoding method, the first step is to build a standard array. First, 1) place the  $2^K$  codewords on the zeroth row of the standard array with the all-zero codeword,  $\mathbf{v}_0 = (0, 0, \dots, 0)$  as the leftmost element. Then, 2) select  $\mathbf{e}_1$  to be a N-bit vector with the smallest number of non-zero elements and place

it under the all-zero vector,  $\mathbf{v}_0$ . 3) Complete the first row by adding each of the remaining  $2^K - 1$  codewords in the zeroth row to  $\mathbf{e}_1$  and place  $\mathbf{e}_1 + \mathbf{v}_i$  under  $\mathbf{v}_i$ . Afterwards, 4) select  $\mathbf{e}_2$  to be another N-bit vector with the smallest number of non-zero elements that does not already exist in the standard array. 5) Complete the second row using the same method as the first row. 6) Complete the remaining rows in a similar fashion until all N-bit vectors are exhausted. The completed standard array has the following format:

$$\mathbf{v}_{0} = \mathbf{0} \qquad \mathbf{v}_{1} \qquad \cdots \qquad \mathbf{v}_{i} \qquad \cdots \qquad \mathbf{v}_{2^{K}-1}$$

$$\mathbf{e}_{1} \qquad \mathbf{e}_{1} + \mathbf{v}_{1} \qquad \cdots \qquad \mathbf{e}_{1} + \mathbf{v}_{i} \qquad \cdots \qquad \mathbf{e}_{1} + \mathbf{v}_{2^{K}-1}$$

$$\vdots \qquad \qquad \cdots \qquad \qquad \vdots$$

$$\mathbf{e}_{l} \qquad \mathbf{e}_{l} + \mathbf{v}_{1} \qquad \cdots \qquad \mathbf{e}_{l} + \mathbf{v}_{i} \qquad \cdots \qquad \mathbf{e}_{l} + \mathbf{v}_{2^{K}-1}$$

$$\vdots \qquad \qquad \cdots \qquad \qquad \vdots$$

$$\mathbf{e}_{2^{N-K}-1} \qquad \mathbf{e}_{2^{N-K}-1} + \mathbf{v}_{1} \qquad \cdots \qquad \mathbf{e}_{2^{N-K}-1} + \mathbf{v}_{2^{K}-1}$$

Each row in the standard array is called a coset, and the leftmost element,  $\mathbf{e}_l$  is called the coset leader. Decoding can be performed using the standard array as a dictionary because all  $2^N$  possible N-bit vectors are present. In order to use the standard array for decoding, find the received vector,  $\mathbf{r}$ , among the vectors in the standard array, and the decoded codeword is vector,  $\mathbf{v}_i$ , on the same column as  $\mathbf{r}$ . However, the decoded codeword  $\mathbf{v}_i$  may or may not be the original codeword sent through the channel because using this method to decode  $\mathbf{r}$  to  $\mathbf{v}_i$  means that  $\mathbf{r} = \mathbf{e}_l + \mathbf{v}_i$ , where  $\mathbf{e}_l$  is interpreted as the error vector. Thus,  $\mathbf{v}_i$  is the original codeword sent through the channel if and only if the error vector is indeed  $\mathbf{e}_l$ . Therefore, assuming on a BSC, in order to minimize decoding error, the coset leaders,  $\mathbf{e}_l$ , are chosen to have the smallest number of non-zero elements.

One drawback in decoding using the standard array directly is that all  $2^N$  vectors must be stored in the decoder, so for large N it becomes impractical. This drawback can be overcome with some observations about the standard array.

Firstly, the syndrome of every vector in a coset is the same. Consider the vector  $\mathbf{e}_l + \mathbf{v}_i$ ,

then its syndrome is as follows:

$$\mathbf{s} = (\mathbf{e}_l + \mathbf{v}_i) \cdot \mathbf{H}^T$$

$$= \mathbf{e}_l \cdot \mathbf{H}^T + \mathbf{v}_i \cdot \mathbf{H}^T$$

$$= \mathbf{e}_l \cdot \mathbf{H}^T + \mathbf{0}$$

$$= \mathbf{e}_l \cdot \mathbf{H}^T$$

(2.13)

Since  $\mathbf{s}$  is independent of  $\mathbf{v}_i$ , the syndrome of any element of the coset is equal to the syndrome of the coset leader. In addition, the set of all non-zero coset leaders can generate the set of all non-zero syndromes using equation (2.13) and there is a one-to-one correspondence between them. Thus, the decoder only needs to store or to wire a look-up table that converts the syndrome to the coset leader and uses it to correct the received vector from the channel,  $\mathbf{r}$ .

In summary, syndrome decoding is performed using the following three steps:

- 1. Compute the syndrome of  $\mathbf{r}$ ,  $\mathbf{s} = \mathbf{r} \cdot \mathbf{H}^T$ .

- 2. Using the look-up table to convert the syndrome, s, into the error vector,  $e_l$ .

- 3. Decode the received vector,  $\mathbf{r}$ , into the codeword,  $\mathbf{v}^* = \mathbf{r} + \mathbf{e}_l$ .

An example of the encoding and decoding using the syndrome decoding of a N = 7 and K = 4 linear systematic block code is attached in Appendix A.

As mentioned earlier in this section, decoding a received vector into a codeword does not guarantee that the decoded codeword is the original codeword sent through the channel. An important parameter that determines the random-error-detecting and random-error-correcting capabilities of a linear block code is the minimum distance, denoted  $d_{min}$ . The minimum distance can be defined using one of two parameters, the Hamming weight or the Hamming distance. The Hamming weight of a vector  $\mathbf{v} = (v_0, v_1, \dots, v_{N-1})$ , denoted by  $w(\mathbf{v})$ , is defined as the number of non-zero elements in  $\mathbf{v}$ . The Hamming distance between two vectors,  $\mathbf{v} = (v_0, v_1, \dots, v_{N-1})$  and  $\mathbf{w} = (w_0, w_1, \dots, w_{N-1})$ , denoted by  $d(\mathbf{v}, \mathbf{w})$ , is the number of places where  $\mathbf{v}$  and  $\mathbf{w}$  differ by. Subsequently, the minimum distance can be defined as the minimum Hamming distance among all the codewords in the linear block code. The minimum distance can also be defined as the minimum Hamming weight of all

the codewords in the linear block code. Based on the minimum distance,  $d_{min}$ , the random-error-detecting capability of a block code is  $d_{min} - 1$ , which means any error vector with  $d_{min} - 1$  or less non-zero elements is guaranteed to be detected by the decoder. Additionally, the random-error-correcting capability of a block code is given by:

$$t = \left| \frac{d_{min} - 1}{2} \right| \tag{2.14}$$

which means that any error vector with t or less non-zero elements is guaranteed to be corrected by the decoder.

The discussion presented so far only applies to hard-decision decoding, where the received values from the channel are only treated as binary digits, 0 or 1. By doing so, much of the information from the channel is lost, which degrades performance. If the received values are interpreted as more than two levels, then the decoding is called soft-decision decoding. In general, soft-decision decoding has better performance than hard-decision decoding from the usage of the channel information. However, the drawback is the increased complexity in the implementation of the decoder to handle the multi-level values.

In soft-decision decoding, the minimum distance, Hamming weight and Hamming distance metrics are not applicable, so other metrics must be used. The most commonly used metrics are likelihood functions, Euclidean distance, correlation and correlation discrepancy.

Assume that the codeword  $\mathbf{v} = (v_0, v_1, \dots, v_{N-1})$  is transmitted over an additive white Gaussian noise (AWGN) channel with two-sided power spectral density (PSD)  $N_0/2$  using binary phase-shift keying (BPSK) modulation. The codeword is mapped into a bipolar signal sequence  $\mathbf{c} = (c_0, c_1, \dots, c_{N-1})$ , as follows:

$$c_l = 2v_l - 1 = \begin{cases} -1 & \text{for } v_l = 0\\ +1 & \text{for } v_l = 1 \end{cases}$$

(2.15)

where  $l = 0, 1, \dots, N$ . In addition, assume at the output of the channel, the soft-decision vector,  $\mathbf{r} = (r_0, r_1, \dots, r_{N-1})$ , is received. The log-likelihood function of  $\mathbf{r}$  given a codeword  $\mathbf{v}$  is as follows:

$$\log P(\mathbf{r}|\mathbf{v}) = \sum_{i=0}^{N-1} \log P(r_i|v_i)$$

(2.16)

Using the log-likelihood function as decoding metric to perform maximum likelihood decoding (MLD), the received vector  $\mathbf{r}$  is decoded into codeword  $\mathbf{v}$  for which the log-likelihood function in (2.16) is maximized.

The squared Euclidean distance between  $\mathbf{r}$  and  $\mathbf{c}$ , denoted  $d_E^2(\mathbf{r}, \mathbf{c})$  is defined as follows:

$$d_E^2(\mathbf{r}, \mathbf{c}) \triangleq \sum_{i=0}^{N-1} (r_i - c_i)^2$$

(2.17)