# Study of Single-Event Transient Effects on Analog Circuits

A Thesis Submitted

to the College of Graduate Studies and Research

in Partial Fulfillment of the Requirements

for the Degree of Doctor of Philosophy

in the Department of Electrical and Computer Engineering

University of Saskatchewan

by

**Tao Wang**

#### PERMISSION TO USE

In presenting this thesis in partial fulfilment of the requirements for a Postgraduate degree from the University of Saskatchewan, I agree that the Libraries of this University may make it freely available for inspection. I further agree that permission for copying of this thesis in any manner, in whole or in part, for scholarly purposes may be granted by the professor or professors who supervised my thesis work or, in their absence, by the Head of the Department or the Dean of the College in which my thesis work was done. It is understood that any copying or publication or use of this thesis or parts thereof for financial gain shall not be allowed without my written permission. It is also understood that due recognition shall be given to me and to the University of Saskatchewan in any scholarly use which may be made of any material in my thesis.

Requests for permission to copy or to make other use of material in this thesis in whole or part should be addressed to:

Head of the Department of Electrical and Computer Engineering

57 Campus Drive

University of Saskatchewan

Saskatoon, Saskatchewan, Canada

S7N 5A9

#### **ABSTRACT**

Radiation in space is potentially hazardous to microelectronic circuits and systems such as spacecraft electronics. Transient effects on circuits and systems from high energetic particles can interrupt electronics operation or crash the systems. This phenomenon is particularly serious in complementary metal-oxide-semiconductor (CMOS) integrated circuits (ICs) since most of modern ICs are implemented with CMOS technologies. The problem is getting worse with the technology scaling down. Radiation-hardening-by-design (RHBD) is a popular method to build CMOS devices and systems meeting performance criteria in radiation environment.

Single-event transient (SET) effects in digital circuits have been studied extensively in the radiation effect community. In recent years analog RHBD has been received increasing attention since analog circuits start showing the vulnerability to the SETs due to the dramatic process scaling. Analog RHBD is still in the research stage. This study is to further study the effects of SET on analog CMOS circuits and introduces cost-effective RHBD approaches to mitigate these effects.

The analog circuits concerned in this study include operational amplifiers (op amps), comparators, voltage-controlled oscillators (VCOs), and phase-locked loops (PLLs). Op amp is used to study SET effects on signal amplitude while the comparator, the VCO, and the PLL are used to study SET effects on signal state during transition time. In this work, approaches based on multi-level from transistor, circuit, to system are presented to mitigate the SET effects on the aforementioned circuits. Specifically, RHBD approach based on the circuit level, such as the op amp, adapts the auto-zeroing

cancellation technique. The RHBD comparator implemented with dual-well and triple-well is studied and compared at the transistor level. SET effects are mitigated in a LC-tank oscillator by inserting a decoupling resistor. The RHBD PLL is implemented on the system level using triple modular redundancy (TMR) approach. It demonstrates that RHBD at multi-level can be cost-effective to mitigate the SEEs in analog circuits. In addition, SETs detection approaches are provided in this dissertation so that various mitigation approaches can be implemented more effectively. Performances and effectiveness of the proposed RHBD are validated through SPICE simulations on the schematic and pulsed-laser experiments on the fabricated circuits. The proposed and tested RHBD techniques can be applied to other relevant analog circuits in the industry to achieve radiation-tolerance.

#### **ACKNOWLEDGEMENTS**

I would like to express my appreciation and gratitude to all the people who have contributed to this accomplishment. First, I would like to express my appreciation to my academic advisor, Professor Anh Dinh, and Professor Li Chen, for providing me the chance to work in the projects, for letting me freely think on innovative ideas, for offering me the design/simulation and measurement environment with various tools and equipment to confirm my ideas. I also express my gratitude for their kindness, their endless guidance, and support throughout my graduate studies at the University of Saskatchewan. Without their encouragement and support, this work would not have been possible.

I would like to thank all of the members in my advisory committee for their advices, support, and reviewing this dissertation. I also would like to give my thanks to all of the faculty and staffs of the Department of Electrical and Computer Engineering for their great teaching, support, and advices during my study. I would also like to express my appreciation to the SSSC, and in particular, Dr. S. Brunet for setting up the pulsed-laser facility and for her assistance in the laser testing.

I would like to thank Natural Sciences and Engineering Research Council (NSERC) of Canada and Department of Electrical and Computer Engineering for the financial support. I also thank CMC Microsystems for providing EDA tools and chip fabrication services.

Specifically, I would like to express my appreciation to my wife, Li Liu, my parents, Zhuyu Zhao, and Guodong Wang, for their love, support, and encouragement through many years of my graduate studies.

## **Table of Contents**

| PERM    | ISSION TO USE                                                                                        | i    |

|---------|------------------------------------------------------------------------------------------------------|------|

| ABST    | RACT                                                                                                 | ii   |

| ACKN    | OWLEDGEMENTS                                                                                         | iv   |

| Table o | of Contents                                                                                          | vi   |

| List of | Figures                                                                                              | viii |

| List of | Tables                                                                                               | xiii |

| List of | Abbreviations                                                                                        | xiv  |

| 1. Int  | roduction                                                                                            | 1    |

| 1.1     | Motivation                                                                                           | 1    |

| 1.2     | Research Objectives                                                                                  | 6    |

| 1.3     | Thesis Organization                                                                                  | 7    |

|         | liation Effects Overview, Background of the Selected Analog Circuits, an                             |      |

|         | -Laser Testing                                                                                       |      |

| 2.1     | Total Ionization Dose (TID) Effects                                                                  |      |

| 2.2     | Single-Event Effects (SEEs)                                                                          |      |

| 2.3     | General SEU/SET Mitigation Approaches                                                                |      |

| 2.4     | SETs on CMOS Analog Circuits                                                                         |      |

| 2.5     | Pulsed-Laser Testing                                                                                 |      |

|         | gle-Event Transients-Tolerant Operational Amplifiers                                                 |      |

| 3.1     | Introduction to Offset and Auto-Zeroing Cancellation Technique                                       |      |

| 3.2     | SET on the Folded-Cascode Op Amp                                                                     | 42   |

| 3.3     | Folded-Cascode Op Amp RHBD Design with Input Offset Storage                                          | 44   |

| 3.4     | Folded-Cascode Op Amp RHBD Design with Output Offset Storage                                         | 47   |

| 3.5     | Folded-Cascode Op Amp RHBD Design with Auxiliary Offset Storage                                      | 49   |

| 3.6     | Summary                                                                                              | 51   |

|         | gle-Event Transients Effects on Dynamic Comparators in the 90nm CM<br>-Well and Dual-Well Technology |      |

| 4.1     | Dual-Well and Triple-Well Process Technology                                                         | 53   |

| 4.2     | Dynamic Comparator Circuit                                                                           | 54   |

| 43      | Experimental Results                                                                                 | 58   |

| 4.4         | Discussions                                                                        | 60   |

|-------------|------------------------------------------------------------------------------------|------|

| 4.5         | Summary                                                                            | 64   |

| 5. A I      | RHBD LC-Tank Oscillator-Tolerant to Single-Event Transients                        | 66   |

| 5.1         | VCO Introduction                                                                   | 66   |

| 5.2         | SET Effects on the LC-Tank Oscillator                                              | 70   |

| 5.3         | Experimental Results                                                               | 76   |

| 5.4         | Summary                                                                            | 80   |

| 6. A        | Single-Event Transient-Tolerant Monolithic Phase-Locked Loop Design                | n 82 |

| 6.1         | Basic Technology and Operating Principles of Phase-Locked Loops                    | 82   |

| 6.2         | Phase-Locked Loops in Radiation Environments                                       | 88   |

| 6.3         | A Triple Modular Redundancy Scheme in RHBD PLLs Design                             | 91   |

| 6.4         | Summary                                                                            | 100  |

| 7. Sin      | ngle-Event Transients Detection                                                    | 101  |

| 7.1         | Motivation                                                                         | 101  |

| 7.2<br>Tran | Voltage Mode Bulk Built-In Current Sensing Circuit for Single-Eversient Detection  |      |

| 7.3<br>Tran | Current Mode Bulk Built-In Current Sensing Circuit for Single-Eversients Detection |      |

| 7.4         | Summary                                                                            | 112  |

| 8. Su       | mmary, Conclusion and Future Work                                                  | 113  |

| 8.1         | Summary                                                                            | 113  |

| 8.2         | Conclusion                                                                         | 116  |

| 8.3         | Future Work                                                                        | 117  |

| Roforo      | nces                                                                               | 110  |

## **List of Figures**

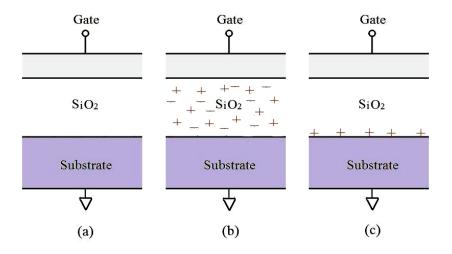

| Figure 2.1 Total dose effects on a MOS transistor.                                                                                                                                           | . 10 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

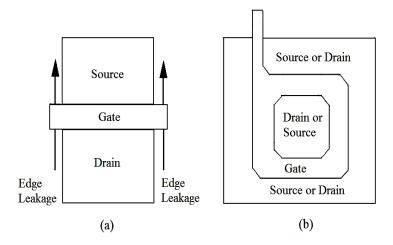

| Figure 2.2 (a) TID-induced edge leakage. (b) Enclosed-gate transistor shape [38]                                                                                                             | . 12 |

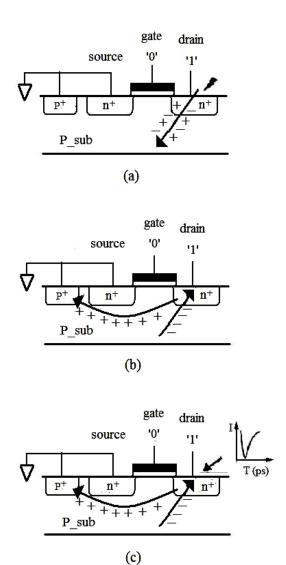

| Figure 2.3 Illustration of charge generation, collection and circuit response for a floating node in an nMOS transistor. (a) Charge generation. (b) Charge collection. (c) Circuit response. | . 14 |

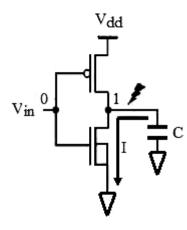

| Figure 2.4 Error under SEEs based on an inverter                                                                                                                                             | . 15 |

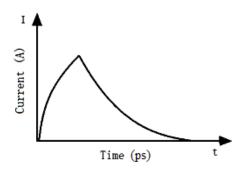

| Figure 2.5 The shape of transient current pulse.                                                                                                                                             | . 15 |

| Figure 2.6 SEU in memory cell due to a heavy ion strike.                                                                                                                                     | . 17 |

| Figure 2.7 SET propagates in a logic circuit                                                                                                                                                 | . 18 |

| Figure 2.8 Timing of a SET pulse meets the setup and hold time of the latch or flip-flop.                                                                                                    | . 19 |

| Figure 2.9 Diagram of the parasitic latch-up structure in a CMOS inverter                                                                                                                    | . 20 |

| Figure 2.10 A CMOS device with guard ring.                                                                                                                                                   | . 21 |

| Figure 2.11 A SEU-hardened approach with RC filter in a SRAM cell                                                                                                                            | . 22 |

| Figure 2.12 (a) Architecture of a pulse width filtering with inserted delay.  (b) Waveforms of pulse width filtering with inserted delay.                                                    | . 23 |

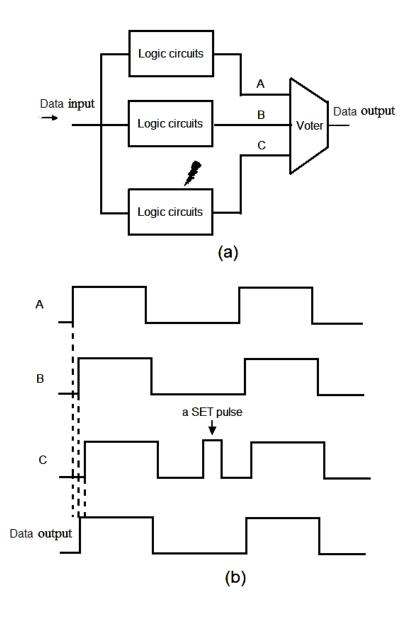

| Figure 2.13 (a) Diagram of the TMR technique. (b) Waveforms of the TMR under a SET pulse propagation.                                                                                        | . 25 |

| Figure 2.14 Schematic of DICE latch circuit [25].                                                                                                                                            | . 26 |

| Figure 2.15 An architecture of signal digitization.                                                                                                                                          | . 27 |

| Figure 2.16 Diagram of a data link.                                                                                                                                                          | . 28 |

| Figure 2.17 (a) RC model of transmission lines. (b) Periodic data response. (c) Random data response.                                                                                        | . 29 |

| Figure 2.18 Phase noise and timing jitter. (a) Ideal case. (b) Practical case                                                                                                                | . 30 |

| Figure 2.19 An nMOS-based current-mirror.                                                                                                                                                    | . 31 |

| Figure 2.20 A differential pair amplifier.                                                                                                                                                                               | 32 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

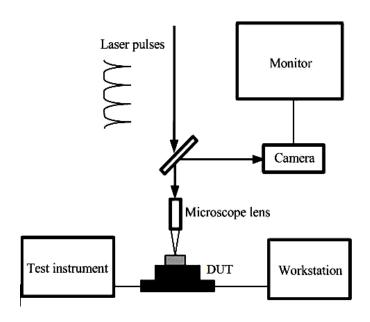

| Figure 2.21 Diagram of pulsed-laser testing setup [55]                                                                                                                                                                   | 37 |

| Figure 2.22 Laser and microscope setup.                                                                                                                                                                                  | 38 |

| Figure 3.1 Differential pair sensing common mode input [50].                                                                                                                                                             | 40 |

| Figure 3.2 Differential pair with offset referred to the input [50].                                                                                                                                                     | 41 |

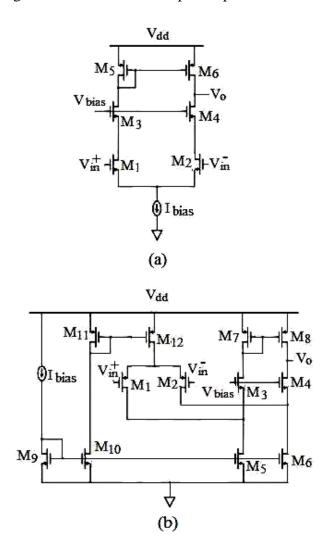

| Figure 3.3 (a) A telescopic cascode op amp. (b) A folded-cascode op amp                                                                                                                                                  | 43 |

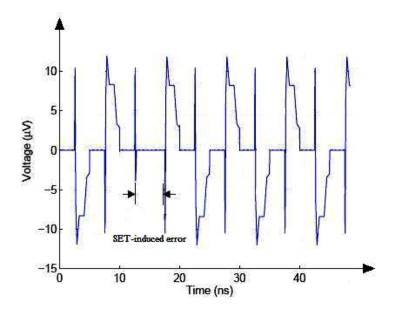

| Figure 3.4 (a) Simulated output voltage of the folded-cascode pre-amplifier without SET interaction. (b) Simulated output voltage of the folded-cascode pre amplifier with SET interaction.                              | 44 |

| Figure 3.5 An input offset storage folded-cascode op amp.                                                                                                                                                                | 45 |

| Figure 3.6 Differential output voltage with input offset storage folded-cascode op amp under a SET interaction.                                                                                                          | 46 |

| Figure 3.7 An output offset storage folded-cascode op amp.                                                                                                                                                               | 48 |

| Figure 3.8 Differential output voltage with output offset storage folded-cascode op amp under a SET interaction.                                                                                                         | 48 |

| Figure 3.9 An auxiliary offset storage folded-cascode op amp.                                                                                                                                                            | 50 |

| Figure 3.10 Differential output voltage with auxiliary offset storage folded-cascode op amp under a SET interaction.                                                                                                     | 50 |

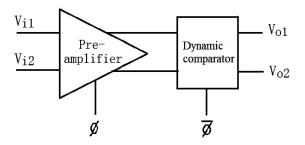

| Figure 4.1 A simple comparator architecture.                                                                                                                                                                             | 52 |

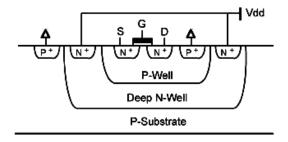

| Figure 4.2 Cross-section view of a nMOS transistor implemented with triple-well CMOS technology.                                                                                                                         |    |

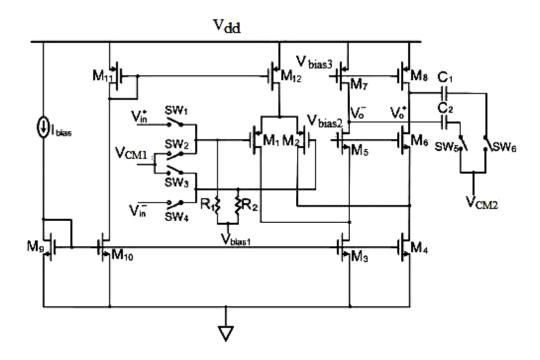

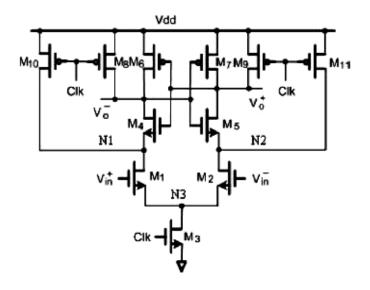

| Figure 4.3 Schematic diagram of a dynamic comparator.                                                                                                                                                                    | 56 |

| Figure 4.4 A basic transistor implemented with closed-geometry.                                                                                                                                                          | 56 |

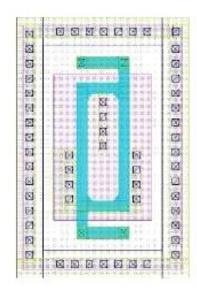

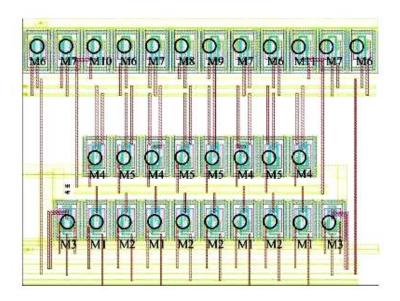

| Figure 4.5 Layout of the dynamic comparator. Transistors in the first row from the top are the pMOS transistors, the second and third rows are nMOS transistors. The circles on the transistors are laser hit locations. | 57 |

| Figure 4.6 Photograph of the comparators. The large bright square blocks around the comparator are the filling tile layers from Poly to Metal 7. There is no filling layer on top of the comparator.                     | 58 |

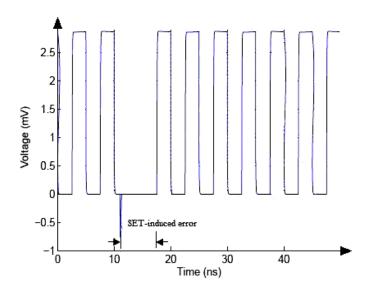

| Figure 4.7 Photograph of the SET pulse at the output of the dual-well comparator                                                                                                                                                          | . 59 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

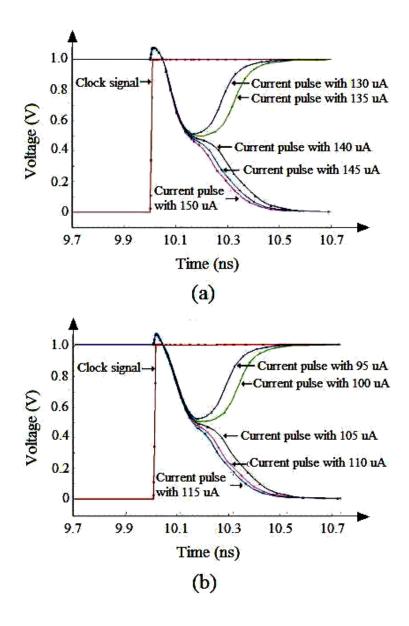

| Figure 4.8 (a) Dual-well comparator output waveforms with SET current pulses from $130\mu A$ to $150\mu A$ . (b) Triple-well comparator output waveforms with SET current pulses from $95\mu A$ to $115\mu A$ .                           | . 62 |

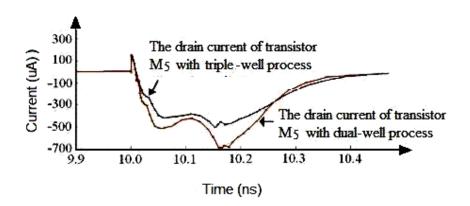

| Figure 4.9 Dual-well and triple-well comparators output voltage waveforms and M5 drain current waveforms with SET current pulses of $200\mu A$ .                                                                                          | . 64 |

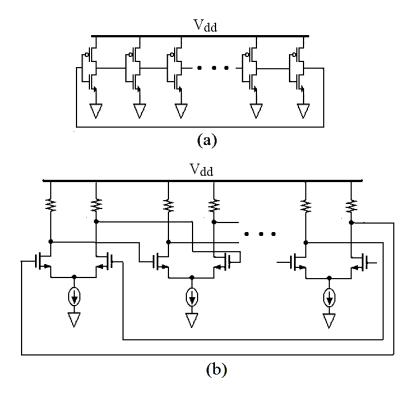

| Figure 5.1 An inverter-based ring oscillator. (b) A differential amplifier-based ring oscillator.                                                                                                                                         | . 67 |

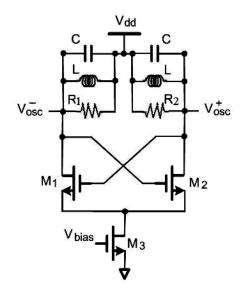

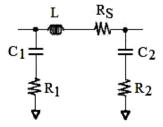

| Figure 5.2 Schematic of a LC-tank VCO                                                                                                                                                                                                     | 68   |

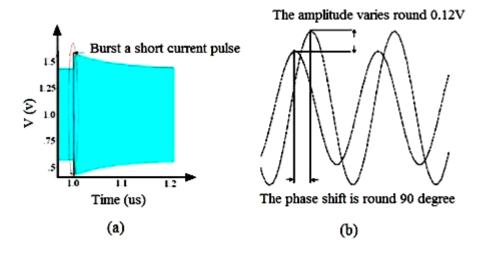

| Figure 5.3 (a) A varactor implementation by nMOS transistor. (b) Capacitance characteristic with voltage variation.                                                                                                                       | . 69 |

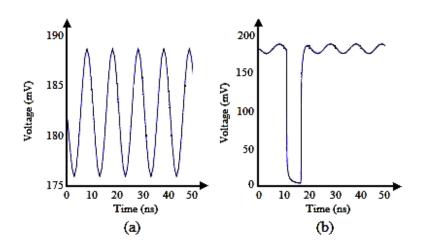

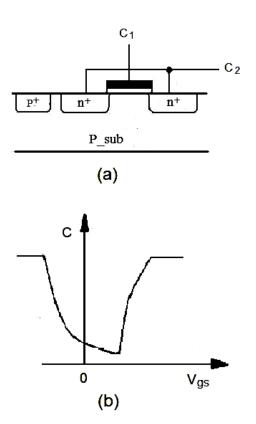

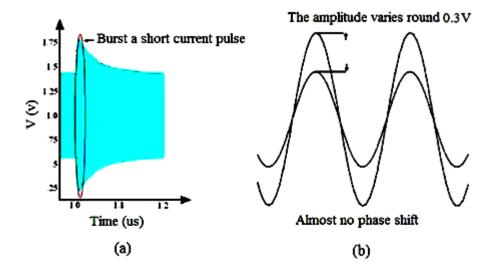

| Figure 5.4 (a) Simulation result for the LC-tank oscillator as a SET is injected at the drain of transistor of $M_3$ when a SET happens at the zero-cross point. (b) Zoomed-in oscillating signal.                                        | . 72 |

| Figure 5.5 (a) Simulation result for the LC-tank oscillator as a SET is injected at the drain of transistor $M_3$ when a SET happens at the peak amplitude point. (b) Zoomed-in oscillating signal                                        | . 72 |

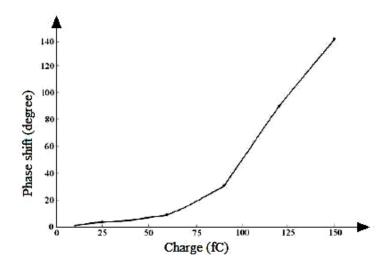

| Figure 5.6 Phase shift associates SET charges injected on the drain of $M_3$ with bias current of $0.45 \mu mA$ .                                                                                                                         |      |

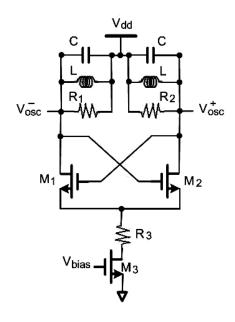

| Figure 5.7 Schematic of the LC-tank VCO with the decoupling resistor R <sub>3</sub>                                                                                                                                                       | . 75 |

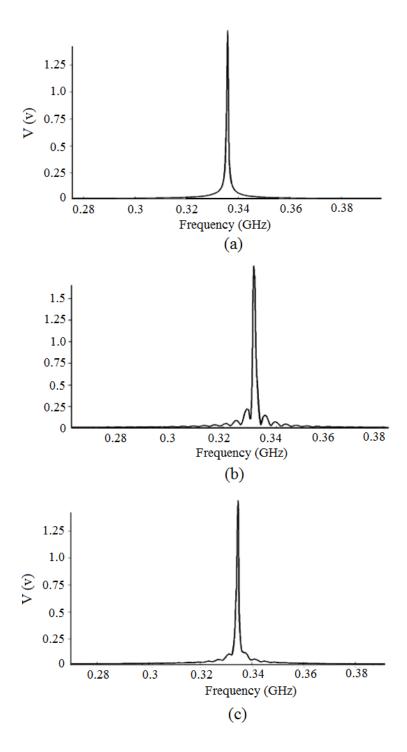

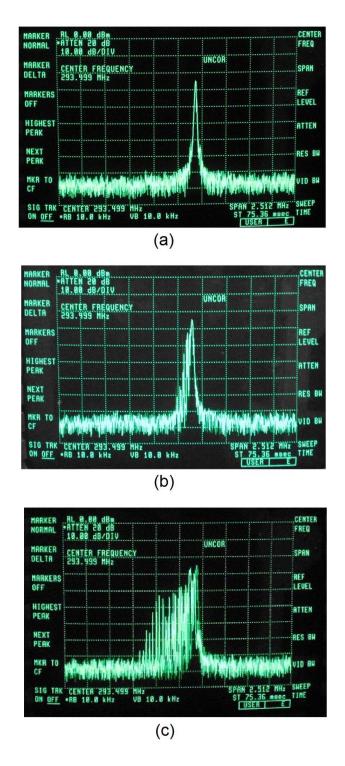

| Figure 5.8 The output signal spectrum.                                                                                                                                                                                                    | .77  |

| Figure 5.9 pi model of a spiral inductor.                                                                                                                                                                                                 | . 78 |

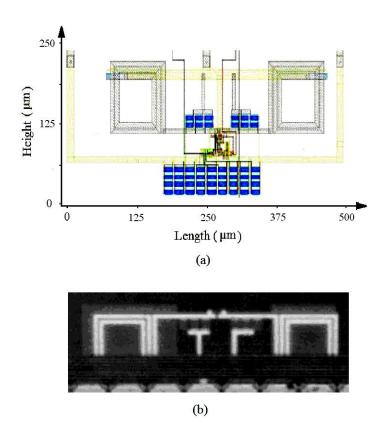

| Figure 5.10 (a) Layout view of the oscillator. (b) Die photograph of the oscillator                                                                                                                                                       | . 79 |

| Figure 5.11 Oscillator output spectrum (a) Before the pulsed-laser beam irradiation. (b) During the pulsed-laser beam irradiation with a decoupling resistor. (c) During the pulsed-laser beam irradiation without a decoupling resistor. | . 81 |

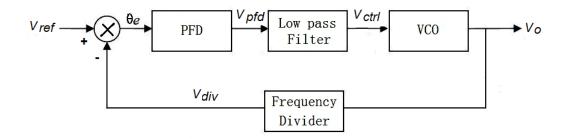

| Figure 6.1 A PLL model.                                                                                                                                                                                                                   | . 83 |

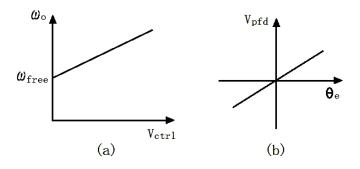

| Figure 6.2 (a) Ideal transfer curve of VCOs. (b) Ideal transfer curve of PFDs [50]                                                                                                                                                        | 84   |

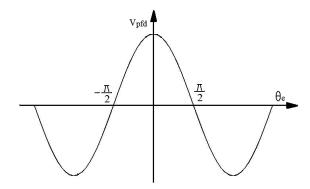

| Figure 6.3 Characteristic of multiplier PFD.                                                                                                                                                                                              | . 85 |

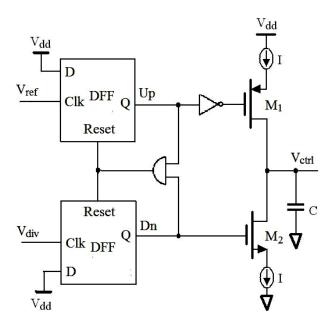

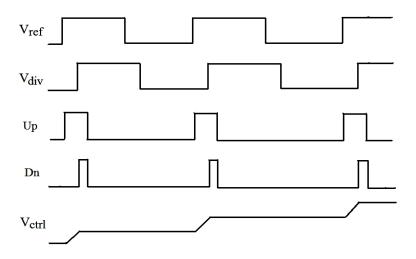

| Figure 6.4 Architecture of the PFD with the CP                                                                                                                                                                                            | 87   |

| Figure 6.5 Input/output signal waveform of the digital PFD with the CP [80] 87                                                                                                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

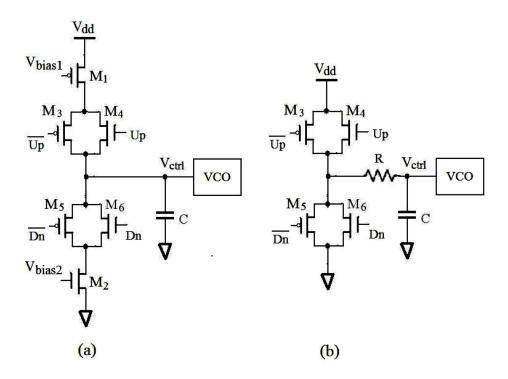

| Figure 6.6 (a) Schematic of the current-based CP. (b) Schematic of the voltage-based CP                                                                                                      |

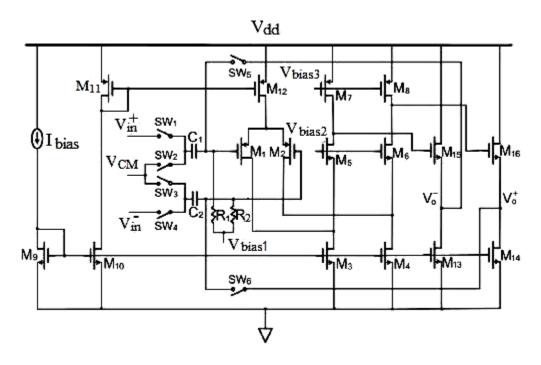

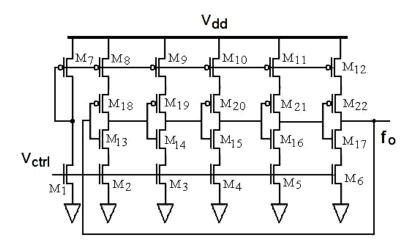

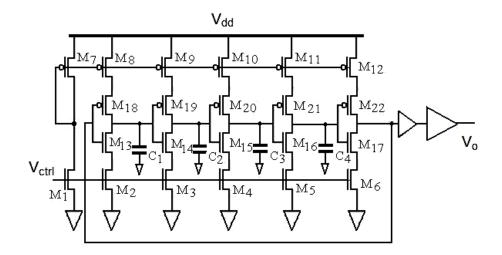

| Figure 6.7 Schematic of the five-stage current-starved ring VCO                                                                                                                              |

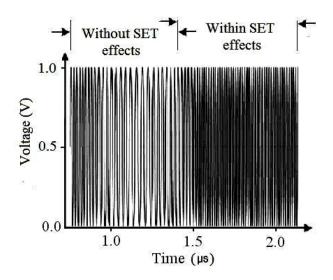

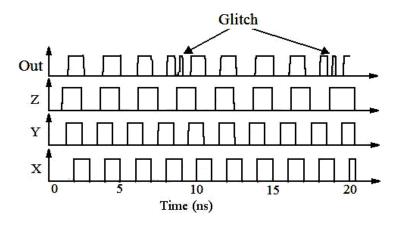

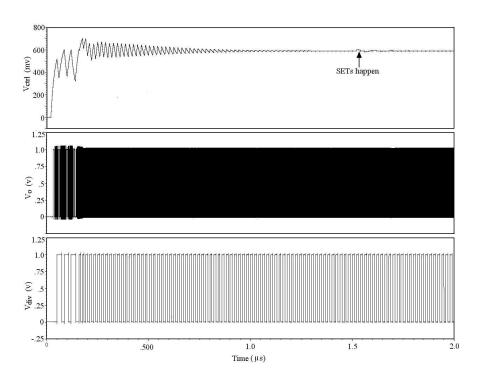

| Figure 6.8 Waveform of the VCO under the SET strike                                                                                                                                          |

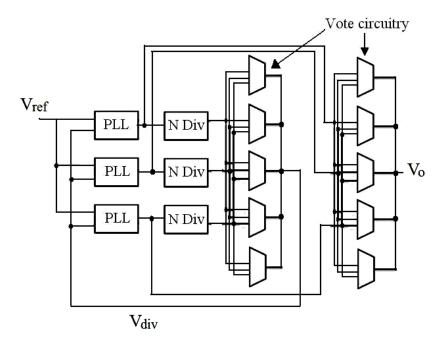

| Figure 6.9 Block diagram of the TMR PLL with voting circuit                                                                                                                                  |

| Figure 6.10 Phase-induced voting error [85].                                                                                                                                                 |

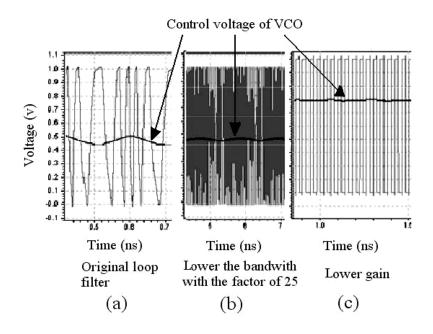

| Figure 6.11 Stability management and comparison [85].                                                                                                                                        |

| Figure 6.12 Schematic diagram of the low-gain current-starved ring VCO                                                                                                                       |

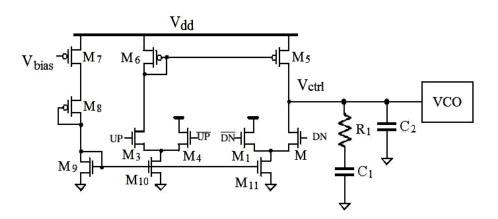

| Figure 6.13 A practical implementation of the current-steering charge pump [90] 96                                                                                                           |

| Figure 6.14 Output waveform of the PLL under SETs event with radiation hardened design                                                                                                       |

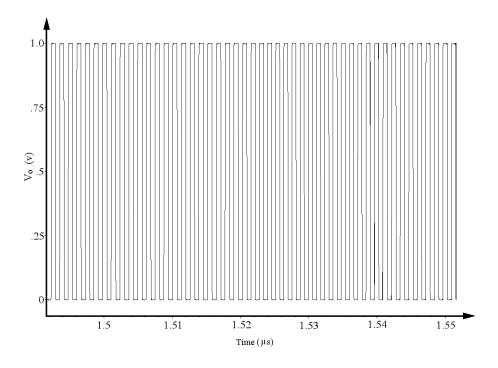

| Figure 6.15 A zoom-in view of the output waveform of a PLL at a SET event                                                                                                                    |

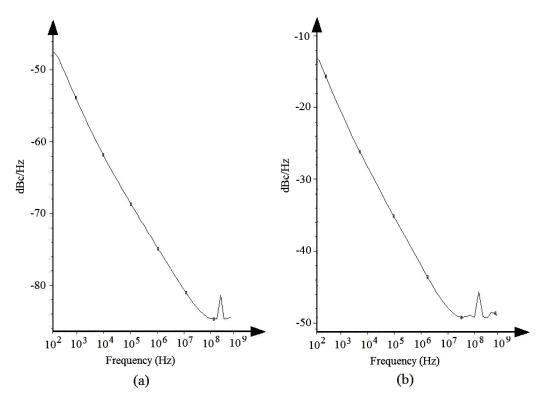

| Figure 6.16 (a) The phase noise of the PLL without RHBD design. (b) The phase noise of the PLL with RHBD design                                                                              |

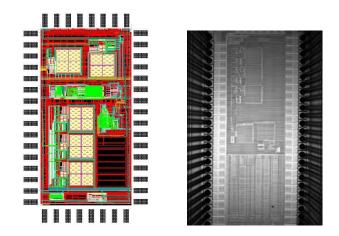

| Figure 6.17 A PLL layout view and photograph of the PLL.                                                                                                                                     |

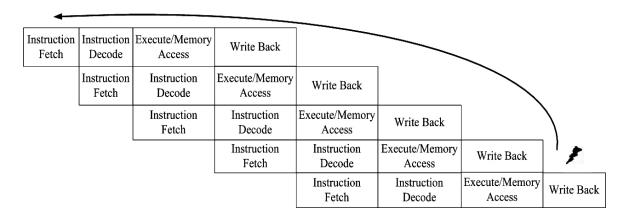

| Figure 7.1 Flow chart of SET-induced errors elimination in the pipeline architecture microprocessor.                                                                                         |

| Figure 7.2 Diagram of the SET-induced errors detection and location in FPGAs 103                                                                                                             |

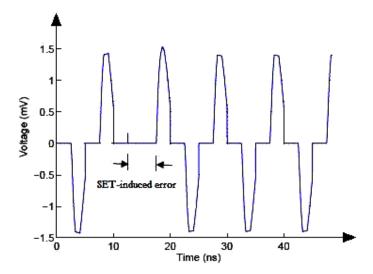

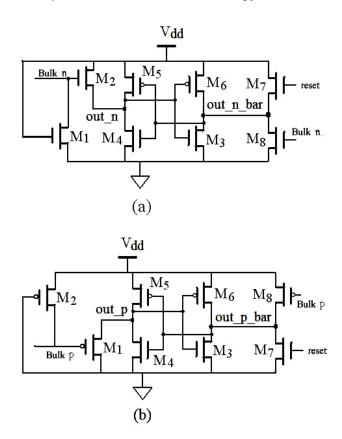

| Figure 7.3 (a) Schematic of the voltage mode n-bulk BICS detection circuit to detect SETs. (b) Schematic of the voltage mode P-bulk BICS detection circuit to detect SETs. 105               |

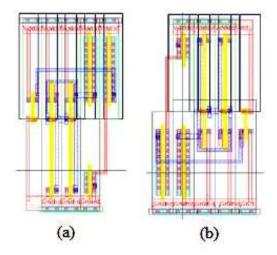

| Figure 7.4 (a) Layout view of the voltage mode n-bulk BICS detection circuit. (b) Layout view of the voltage mode P-bulk BICS detection circuit                                              |

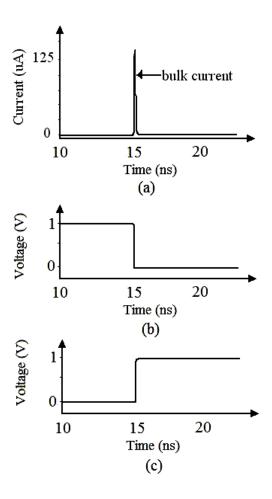

| Figure 7.5 SET detection simulation results with voltage mode. (a) SET-induced current flows in/out through the bulk. (b) Signal of out_p in Fig. 7.3(b). (c) Signal of out_n in Fig. 7.3(a) |

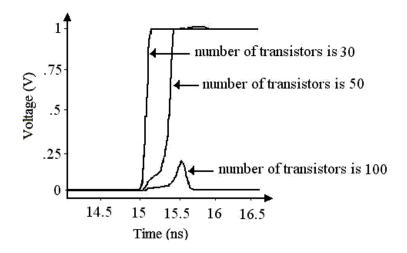

| Figure 7.6 Impact of transistor number on SET detection with voltage mode n-bulk BICS                                                                                                        |

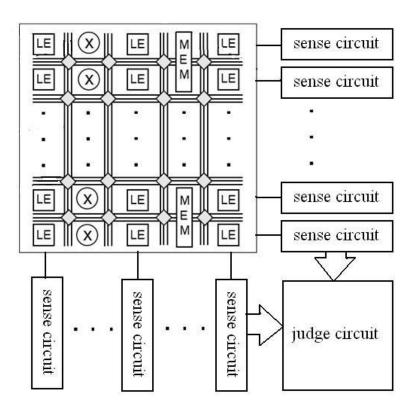

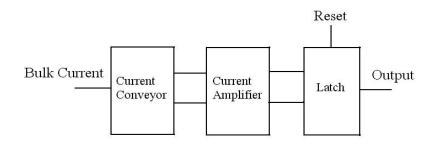

| Figure 7.7 Block diagram of the proposed current mode BICS sensing circuit                                                                                                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

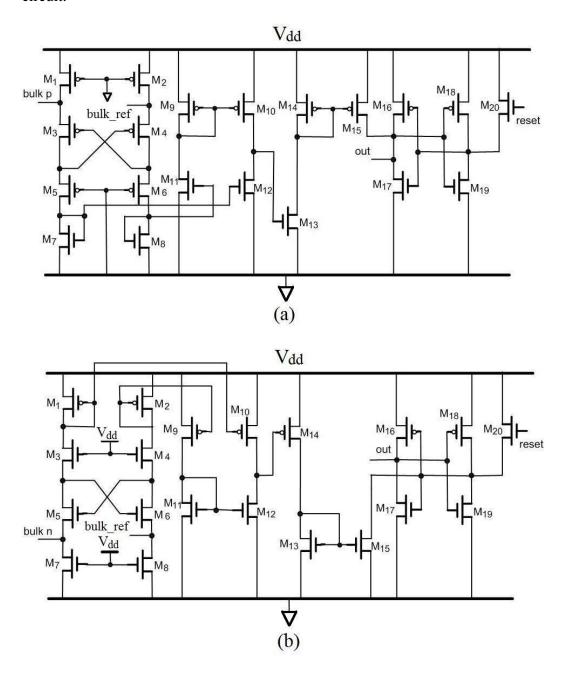

| Figure 7.8 (a) Schematic of the current mode p-bulk BICS detection circuit to detect SETs. (b) Schematic of the current mode n-bulk BICS detection circuit to detect SETs.                    |

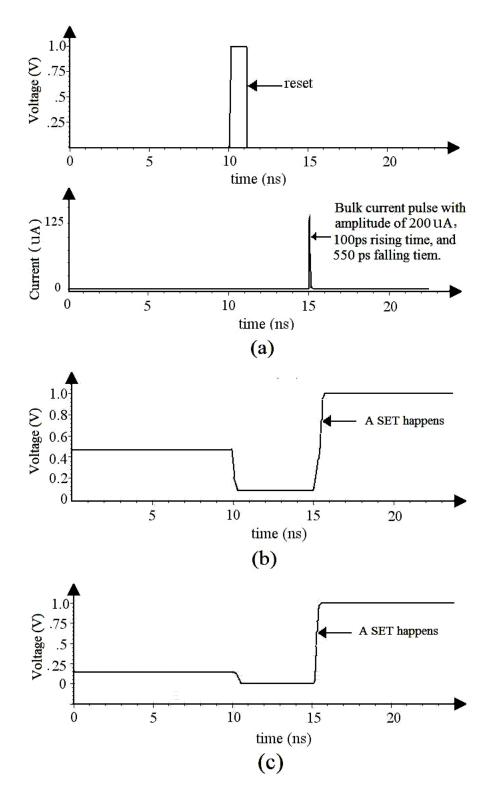

| Figure 7.9 (a) Reset signal and SET-induced current pulse. (b) SET detection simulation result for current mode n-bulk BICS. (c) SET detection simulation result for current mode p-bulk BICS |

| Figure 7.10 Die photograph of the BICS sensing circuit                                                                                                                                        |

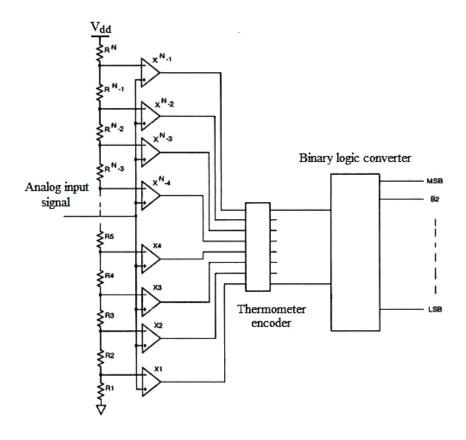

| Figure 8.1 Architecture of a typical flash ADC                                                                                                                                                |

## **List of Tables**

| Table 2-1 Quantification of the current pulse and the voltage pulse. Both of them are tested under an ion interruption with an energy of 80 MeV-cm <sup>2</sup> /mg in the $0.25\mu m$ |      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| CMOS technology.                                                                                                                                                                       | . 15 |

| Table 4-1 Transistor size of the comparators                                                                                                                                           | . 57 |

| Table 4-2 Threshold laser pulse energy of the transistors for the dual-well and triple-well comparators. Lower energy implies higher vulnerability                                     |      |

| Table 4-3 Critical charges for the output node between dual-well and triple-well designs                                                                                               |      |

| Table 5-1 Phase and amplitude shifts when 120fC SET charges injected to the drains of $M_1$ , $M_2$ and $M_3$ at various bias current values.                                          | . 73 |

| Table 5-2 List of resistances of R <sub>3</sub> and corresponding phase and amplitude shifts at the bias current of 0.45mA                                                             |      |

| Table 5-3 Threshold laser energy for the bias current of 0.05mA for the conventional and RHBD designs.                                                                                 | . 80 |

#### **List of Abbreviations**

ADC Analog-To-Digital Converter

AGC Automatic Gain Controller

AOS Auxiliary Offset Storage

BICS Bulk Built-In Current Sensor

CCD Charge-Coupled Device

CDR Clock and Data Recovery

CMC Canadian Microelectronics Corporation

CMOS Complementary Metal-Oxide-Semiconductor

CP Charge Pump

CUT Circuit Under Test

DFF D Flip-Flop

DICE Dual Interlocked Storage Cell

DSP Digital Signal Processing

DUT Device Under Test

EDA Electronic Design Automation

FIT Failures-In-Time

FPGA Field Programmable Gate Array

GCR Galactic Cosmic Rays

IC Integrated Circuit

IP Intellectual Property

IOS Input Offset Storage

ISI Inter Symbol Interference

LET Linear Energy Transfer

LO Local Oscillator

LPF Low Pass Filter

LUT Look-Up Table

MBU Multiple Bit Upset

MIM Metal Insulator Metal

Op Amp Operational Amplifier

OOS Output Offset Storage

PDK Process Design Kit

PFD Phase Frequency Detector

PCB Printed Circuit Board

PLLs Phase-Locked Loops

RADs Radiation Absorbed Dose

RHBD Radiation-Hardening-by-Design

RF Radio Frequency

RO Ring Oscillator

SE Single Event

SEL Single-Event Latch-up

SER Soft Error Rate

SET Single-Event Transient

SEE Single-Event Effects

SEU Single-Event Upset

SNR Signal To Noise Ratio

SPICE Simulation Program With Integrated Circuit Emphasis

SRAM Static Random Access Memory

SSSC Saskatchewan Structural Sciences Centre

TCAD Technology Computer Aided Design

TID Total Ionizing Dose

TMR Triple Modular Redundancy

TSMC Taiwan Semiconductor Manufacturing Company

VCO Voltage-Controlled Oscillator

#### 1. Introduction

#### 1.1 Motivation

In space, one of the important sources of high energy particles are from far away in the galaxy referred as galactic cosmic rays (GCR) [1]. Even the origin of the GCR is still an open question in the field of astrophysics and astronomy, some of the characteristics of GCR were discovered by scientists. GCR travel at nearly the speed of light and strike the earth from all directions [2]. The GCR typically consists of 85% protons, 14% nucleus of helium atom, which is called alpha particles, and 1% electrons and other high energy heavy ions [3]. Most GCR have energies between 100MeV<sup>1</sup> corresponding to a velocity for protons of 43% of the speed of light and 10GeV corresponding to 99.6% of the speed of light [4], where eV (electron volt) is a unit with energy gained when an electron is accelerated through a potential difference of 1 volt. The other source of the cosmic rays can be associated with solar flares, a sudden brightening observed over the sun surface. Sun flares and other energetic solar events emit a large amount of low energy particles into space, and these high energetic particles' energy range is from several hundred MeV to several GeV [4]. When these particles are passing planets in space, they are accelerated by the magnetic fields that are around these celestial objects due to their negative or positive charges. As the results, these particles achieve high energy. An equation for the energy of a particle in the magnetic field is given by [5].

\_

$<sup>^{1}</sup>$  MeV means million electron volt.  $1 \text{MeV} \approx 1.602 \times 10^{-13}$  Joules.

$$E = \frac{(QBR)^2}{2M} \tag{1.1}$$

where E is the energy of a particle in Joules, Q is the charge of a particle in Coulomb, B is the strength of magnetic field in Tesla, M is the mass of a particle in Kilogram, and R is the radius of particle circular path in Meter. As these high energetic particles pass through the atmosphere, they collide with the nucleus of the air atoms leading to secondary particles that shower down to the earth surface through the atmosphere. Secondary cosmic rays include neutrons, gamma rays, electrons, and protons [3] [6] [7]. Both primary cosmic rays and secondary cosmic rays contribute to the space radiation environment.

The space radiation environment is potentially hazardous to microelectronic circuits and systems which are used in the aerospace. Energetic particles such as heavy ions, neutrons, and protons can strike sensitive nodes in the circuits, causing temporary effects which are called single-event effects (SEEs) [8]. Permanent failure may occur when the circuits are under total dose effects from continuous exposure in radiation environments [9]. In the 1970's, the first single event (SE) happened in the semiconductor circuits due to cosmic rays and alpha particles was reported in [1] [10] [11] [12]. Another example of SEEs is the SOHO (Solar and Heliospheric Observatory) satellite has experienced four power supply switch-off events since its launch in December 1995. These four events were believed to originate from space radiation in one or more integrated circuits (ICs) [13]. Recently in November 2000, it was reported that the SUN servers were having problems with bit flips in the static random access memory (SRAM) used for the L2 cache memory which were caused by cosmic rays or alpha particles. Geostationary and GPS-satellites are more prone to radiation and inherit

component failures due to SEEs [14]. Memory failures, charge-coupled device (CCD) damage are also examples of the impact of high energy particles on space circuits and systems [15] [16]. As the dimensions and operating voltages of electronic devices that are used in aerospace are reduced to satisfy requirements of functionality, portability, and lower power; their radiation sensitivity such as SEEs, dramatically increases [17].

Radiation effects on CMOS microelectronic circuits can be divided into two categories: the instantaneous effects of the collision of a single energetic particle on the sensitive locations in the circuits, and the cumulative effects caused primarily by the abundant energetic particles over a long period of time. In general, CMOS scaling has improved the cumulative effects tolerance, however reducing the instantaneous effects has become more challenging.

Some lightweight shielding materials can be used to prevent electronic circuits and systems from accumulated radiation damages to a certain degree, however the shielding cannot stop the high energy particles from reaching the electronics. Therefore, in the radiation effects research and development community, the major goal is to study how the energetic particles interact with electronic circuits and to provide radiation-hardened devices, robust circuits and systems that can function as intended over the mission lifetime in the harsh radiation environment. Radiation-hardening can be implemented at the process level by foundries to meet specified radiation performance criteria. While this approach can provide reliable hardened devices but it requires expensive manufacturing processes. Radiation-hardening can also be achieved by designs at transistor, circuit, or system level to meet specified radiation performance criteria without any modification of the existing process or violation of design and layout rules. This particular approach is called radiation-hardening-by-design (RHBD) [18]. The

RHBD approach satisfies IC development trend and relationship between circuits and systems design, and semiconductor fabrication. IC design companies and design houses tape out their designs and their intellectual property (IP) cores to external foundries for fabrication, whereas the RHBD circuits and systems are fabricated with standard commercial processes.

In the past, researchers have focused on the RHBD designs such as single-event transients (SETs)-tolerant in digital circuits. Authors in [19–23] have introduced SET error analysis in combinational logic and sequential logic circuits. There have been special RHBD digital designs such as the radiation-hardened latch [24], and single-event upset (SEU)-hardened memory [25], etc. Successful SEU-hardened designs have operated reliably in popular digital RHBD circuits such as the dual interlocked storage cells (DICE) in hardened memory cells [25], and the triple modular redundancy (TMR) in hardened latches [24]. Unlike a single feedback topology in traditional latches, the DICE implements a dual feedback topology to store a bit. With this approach, at least two critical nodes must be hit simultaneously under SEEs to lead to a SEU. TMR is a popular radiation-hardening approach applied in digital circuits. The major drawback of this method is the penalty in area and power consumption.

In the past, digital circuits were studied more in hardened design than analog circuits because digital circuits are usually implemented with the minimum transistor size while the transistors in analog circuits are much larger. However, in recent years, with the device scaling down, analog RHBD design has received increased attention. In 2000, Addel, et al. [26] performed SET analysis on the analog circuit of an op amp. A radiation-hardened design was applied in one of the important stages in the op amp, the operational transconductance amplifier (OTA) [27]. A mathematical modeling for

radiation-hardened transistors has been presented in details [28]. Hogue, et al. [29] have intended to put the radiation-hardened transistor as a pcell into the standard library for a CMOS process technology. Generally speaking, RHBD design techniques for analog circuits are highly demanded, and should be studied more in the future.

In general, radiation effects such as SET-induced error responses in analog circuits are categorized into two groups. The first group is the signal amplitude variations. Specifically, SEEs in analog circuits are temporary effects in the time domain. The signal amplitude variation can lead to signal distortion and signal to noise ratio (SNR) degradation. This phenomenon becomes considerably worse in the sample and hold (S/H) circuits in op amps, comparators, and analog-to-digital converters (ADCs). The second group of error responses in analog circuits is the signal transition state effect. For example, the output signal of the dynamic comparator is sensitive to SEEs when the sampling clock is active [30]. Other examples are oscillation circuits such as voltage-controlled oscillators (VCOs) and phase-locked loops (PLLs). Signal frequency and phase variations under radiation effects result in loosing lock in the PLLs [31–33].

This dissertation presents the study of SEEs on analog CMOS circuits and their mitigation approaches. Op amps, dynamic comparators, LC-tank oscillators, and PLLs were selected in this study for investigation. The study is of importance due to the following reasons:

First, the signal amplitude of an op amp, the transition time of a dynamic comparator, and the oscillation frequency and phase of a LC-tank oscillator/PLL are critical parameters and important performance indicators in real world applications. All of them are vulnerable to the radiation effects. Second, all of these circuits are widely used not only in aerospace industry but also in consumer electronic products. Op amps

and dynamic comparators are necessary for the interface between analog and digital circuits. Oscillators and PLLs are two critical sub-blocks in the applications of frequency synthesizers, wireless communications, and high-speed data links. Third, op amps and comparators are the fundamental sub-blocks of ADCs design while PLLs are critical sub-blocks of radio frequency (RF) front-end design and clock and data recovery (CDR) design.

All of these circuits were designed in EDA tool (Cadence) with the advanced CMOS process design kits (PDKs). After successfully investigated by schematic simulation, the typical analog IC design flows such as circuit design, layout, and tape out were carried out for the dynamic comparator, the LC-tank oscillator, and the PLL. Normally, RHBD circuits and non-RHBD circuits were taped out in the same chip in order to compare the SET vulnerability between the two. The experiment test including function test and laser validation was followed on the fabricated chips. Experimental results are used to compare the simulation results and to validate the effectiveness of the RHBD approaches.

## 1.2 Research Objectives

Based on previous discussion, objectives of this thesis work are set as follows:

- SET effects leading to erroneous signal amplitude and phase sudden change during the transition time will be studied based on some typical analog circuits such as op amps, comparators, oscillators, and PLLs.

- 2. Depending on the analysis of SET effects in analog circuits, RHBD approaches will be proposed, designed, and implemented on the

aforementioned circuits based on the multi-level approach, namely transistor, circuit and system levels.

- A transistor level based RHBD design will be studied and implemented in a dynamic comparator. nMOS transistors in the comparator will be implemented using dual-well or triple-well technology.

- Circuit level based RHBD design will be studied and applied in an op amp and a LC-tank oscillator.

- System level based RHBD design will be studied and adopted in a PLL.

Triple modular redundancy strategy is to be used in the RHBD PLL to obtain a stable oscillation signal under SET effects.

- 3. An effective SETs detection circuit will be designed and implemented. If the occurrence of a SET event in an IC can be detected in real time, then various SET mitigation approaches would be used at the system level.

- 4. The performances and effectiveness of SET mitigation approaches are to be investigated and validated by the schematic simulations and pulsed-laser experiments on fabricated circuits.

## 1.3 Thesis Organization

This thesis is organized as follows: Chapter 2 overviews radiation effects and discusses theory and mechanism of the SET effects on MOS transistors. This chapter also illustrates how SETs affect circuits and systems based on transistor and circuit level analysis. The pulsed-laser used to test the effect of heavy ions on the fabricated circuits is described in this chapter. The background of the analog circuits of op amps, comparators,

LC-tank oscillators, and PLLs are also introduced. Chapter 3 describes a RHBD op amp design to mitigate SET effects using three types of auto-zeroing techniques: input offset storage (IOS), output offset storage (OOS), and auxiliary offset storage (AOS). Chapter 4 introduces different implementation techniques to mitigate SET effects on a dynamic comparator. The hardened dynamic comparator design was verified based on the circuit simulations and experimental results. Chapter 5 presents a SET-tolerant LC-tank oscillator. Both of the circuit simulations and experimental results demonstrated the effectiveness of the proposed mitigation approach. Chapter 6 introduces PLL concepts and topologies. This chapter also provides performance analysis and describes the design of a SET-tolerant PLL. Chapter 7 introduces a design for SET detection which has potential applications in the SET-tolerant digital ICs. Chapter 8 concludes the dissertation and describes research direction for future explorations.

## 2. Radiation Effects Overview, Background of the Selected Analog Circuits, and Pulsed-Laser Testing

Radiation has both instantaneous and long-term effects on CMOS microelectronic circuits. The instantaneous effects of the collision of a single energetic particle on the sensitive locations in the circuits are called SEEs. The cumulative effects caused primarily by abundant energetic particles over a long period of time are called total ionization dose (TID) effects [34]. In general, CMOS scaling has improved TID tolerance but SEEs still have strong effects on the circuits. Reducing SEEs in advanced CMOS circuits and systems remains a challenge.

#### 2.1 Total Ionization Dose (TID) Effects

Total ionization dose effects have a capability of damaging electronic circuits by ionizing semiconductor material over a certain period of time in aerospace applications [35]. When energetic particles pass through silicon dioxide (SiO<sub>2</sub>) layer of a CMOS transistor, they deposit enough energy to break certain atomic bonds in the device that results in forming of electron-hole pairs (i.e., causing ionization). The amount of ionization is related to the total dose absorbed in the silicon dioxide layer and is usually given in units of rads (1rad = 100ergs/gm, while 1erg = 100nJ) [15]. In the regime of TID effects on MOS devices, the main concern from this energy deposition is the trapping of either or both the electrons and holes created in silicon dioxide. These electron-hole pairs can gradually degrade the performance or change functionality of MOS devices. Fig. 2.1 illustrates a simple model of TID generation and trapping of charges in the silicon

dioxide of a MOS device with a positive bias applied to the gate. Fig. 2.1(a) shows a MOS device before the ionizing radiation.

Figure 2.1 Total dose effects on a MOS transistor.

Electron-hole pairs are generated when ionizing radiation passes through the device as shown in Fig. 2.1(b). Before transporting through the oxide layer, most of the carriers recombine within the oxide layer. Higher mobility electrons quickly drift out of the oxide through the gate (in time of the order of picoseconds [36]) while the lower mobility holes are trapped in the silicon dioxide. Under the influence of the internal electric field, a small fraction of holes are trapped near the Si/SiO<sub>2</sub> interface as shown in Fig. 2.1(c). As the total dose in the device accumulates over a certain period of time, the amount of trapped positive charges increases. Eventually, these accumulated charges impact the MOS device properties by resulting in a decreased threshold voltage (V<sub>thn</sub>) and an increased leakage current between the source and the drain of nMOS transistors. For pMOS transistors, the accumulated charges increase the threshold voltage (V<sub>thp</sub>). The worst case for nMOS transistors is that positive charges trapping in the gate oxide can cause large leakage current to flow while nMOS transistors are in the off state. For pMOS

transistors, the worst case is that transistors remain off permanently. This effect will not only result in an increase in the static power consumption but also change the logic state, and thus causes permanent failure to CMOS circuits and systems.

To develop a TID-hardened design, state-of-the-art processes with nanometer-thick gate oxide layers have been shown as the effective solution for TID hardening [37]. Due to the scaling rules, the gate oxide thickness must be decreased at each process technology. As a result, the gate oxide thickness of the most advanced process technology is within 1-2nm, which is only a few atoms thick. In this way, the gate oxide traps less positive charges. Therefore, CMOS transistors are naturally becoming more TID tolerant. A published data has been reported at the Boeing Radiation Effects Laboratory with 45nm process shows negligible change in transistor threshold shift and off-state leakage with TID irradiation [34].

The other TID effect occurring in the transistor edge oxide is shown in Fig. 2.2(a). Instead of flowing right below the gate from the drain to the source, the leakage flows along the edge of the active region from the drain to the source of a transistor. These current paths are eliminated by special layout techniques such as enclosed-gate MOSFETs, shown in Fig. 2.2(b) [38]. In this way, current flows from the center to the outside of the device, making it immune to edge leakage current. However, this approach requires a larger area for each transistor, and also introduces a large source/drain capacitance. The most influence for this implementation is the difficulty in building a device model to perform circuit simulations.

In summary, with the scaling-down process, the TID effects becomes insignificant compared to SEEs. This thesis work concentrates on the other effect to CMOS circuits and systems, the SEEs.

Figure 2.2 (a) TID-induced edge leakage. (b) Enclosed-gate transistor shape [38].

### 2.2 Single-Event Effects (SEEs)

SEEs are another type of radiation effects coming from a single energetic particle such as heavy ions penetrating a semiconductor material [39, 40]. Heavy particle impacts are random and can happen at any node in the electronic circuits. The heavy particle strikes the lattice structure of the semiconductor, transfers energy to the lattice, and leaves a number of free electron-hole pairs. These electron-hole pairs will recombine without introducing effects if the heavy ion passes through the bulk. However, the most sensitive part to SEEs in semiconductor device structure is the reverse-biased junctions such as n<sup>+</sup>/p junction of the drain to substrate in nMOS transistor and p<sup>+</sup>/n junction of the drain to substrate in pMOS transistor. One of the reasons for this phenomenon is that the electron-hole pairs will be separated by the electric field before recombination. The electric field comes from the reverse-biased p/n junction voltage potential causing

electrons to be swept to n-diffusion region while holes to be swept to bulk contact regarding nMOS transistors. This drift motion is called charge collection.

The other reason is that the drains of nMOS or pMOS transistors are usually driven by the supply rail through transistors so that the charge collection caused by SEEs cannot be compensated by the supply voltage directly. SEE-induced electron-hole pairs around the reverse-biased junction of the drain nodes of nMOS and pMOS transistors lead to a transient current across device junctions. This may change the voltage level or logic state on the sensitive nodes in analog or digital circuits. SEEs may cause system failures in this situation.

The example shown in Fig. 2.3 illustrates an nMOS transistor under the strike of a particle. Fig. 2.3(a) shows an energetic particle passing through the drain of an nMOS transistor in a few picoseconds while leaving behind a column of ionized material containing a number of electrons and holes. The total numbers of charges are proportional to the linear energy transfer (LET) of the incoming particle as well as the silicon density. LET is the amount of energy deposited per unit of distance as the particle traverses the silicon material. It is usually expressed in MeV-cm<sup>2</sup>/mg. These charges are absorbed by the potential of the drain node and bulk node of the nMOS transistor shown in Fig. 2.3(b) before they are dissipated by recombination. When this happens, a transient current pulse is generated flowing from the drain to the bulk in the nMOS transistor as shown in Fig. 2.3(c). In the circuits, this transient current pulse charges or discharges the potential on some critical nodes, and thus pulling up or pushing down the logic level of these nodes.

An example of an inverter is shown in Fig. 2.4. The initial state in this example of input logic is low and the output logic is high. When an ion strikes the drain of the nMOS

transistor, a large number of electron-hole pairs are produced. Electrons will be collected by the node of the drain of nMOS transistor and voltage in this node will drop. A diagram of Fig. 2.5 shows the shape of the transient current pulse. Table 2-1 lists the quantification of the transient current pulse and induced voltage pulse in the  $0.25\mu m$  CMOS technology [41] [42] [43].

Figure 2.3 Illustration of charge generation, collection and circuit response for a drain node in a nMOS transistor. (a) Charge generation. (b) Charge collection. (c) Circuit response.

Figure 2.4 Transient error under SEE based on an inverter.

Figure 2.5 The shape of transient current pulse.

**Table 2-1** Quantification of the current pulse and the voltage pulse. Both of them are tested under an ion interruption with an energy of 80 MeV-cm<sup>2</sup>/mg in  $0.25\mu m$  CMOS technology.

|               | Peak amplitude | Rise time | Fall time |

|---------------|----------------|-----------|-----------|

| Current pulse | ≈6.5mA         | ≈4ps      | ≈50ps     |

| Voltage pulse | ≈1.2V          | ≈20ps     | ≈0.45ns   |

Unlike the total dose radiation which causes gradual degradation of the device parameters, a single-event interaction is an instantaneous effect in the circuits. As this event typically does not cause permanent damage to the circuits, it is referred as a soft error [34]. Statistics of soft errors in radiation environments are represented by soft error rate (SER), which is defined as the probability of a device having an error or failure which is given in unit of failure in time (FIT) or Failures/10<sup>9</sup> hours [34]. Some types of single-event errors in CMOS circuits include:

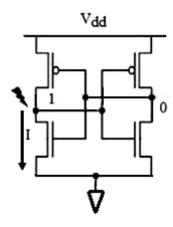

A- Single-event upset (SEU) [8]: When digital circuits such as flip-flops, SRAM-cells, and latches are hit by a high energy particle, an upset of internal logic state can happen. An example of this type of error is a state change of a memory bit as shown in Fig. 2.6. The standard 6T SRAM cell is composed of two pMOS transistors and two nMOS transistors forming a positive feedback loop [44] (switch transistors between the cell and word-line are not shown in the figure). This feedback loop maintains the data state of the cell. When an ion strikes at the output of the left side of the inverter where the logic is high, a large number of electron-hole pairs are produced along the particles trajectory and a large portion of these are separated by the electrical field. In this case, electrons will be collected by the node of the drain of nMOS transistor and the voltage in this node will drop. However, the supply rail tries to hold the high logic of this node through the pMOS transistor. As the node voltage drops, a current flowing from the supply voltage starts to charge this node to compensate for the dropped voltage. If the compensation current through the pMOS transistor is not strong enough to compensate for the current induced by SEEs, the voltage at the drain of nMOS transistor drops. If this voltage drops below the threshold voltage of the inverter on the other side of the cell, the SRAM bit flips with positive feedback loop. In this case, an upset of the state occurs [34].

This situation becomes more serious in the low power SRAM design because noise margin decreases with lower power supply and most of transistors are working in the subthreshold region.

Figure 2.6 SEU in memory cell due to a heavy ion strike.

**B- Multiple bits upset** (**MBU**) [45] [46]: Rather than affecting a single bit in memory, an ion could affect several bits. The distance between circuit elements decreases in the down-scaled CMOS processes. If the ion beam incident angle increases, the particles trajectory across multiple devices. In this way, SEE-induced charges are collected by multiple nodes from different devices. More than one bits in the SRAM cells are upset at the same time. The effect of MBU is typically alleviated by a combination of error-correcting code that works on a word-by-word basis. Also layout rules can be defined to prevent physically-adjacent bits from belonging to the same word of memory.

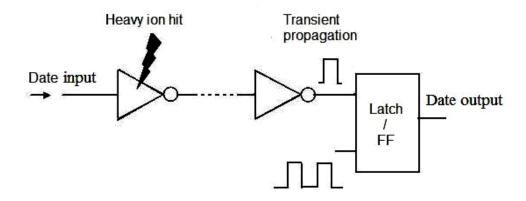

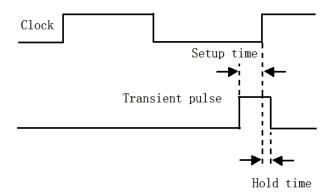

C- Single-event transient (SET) [15]: Once a temporary spike or short signal pulse caused by a heavy ion is generated, it will propagate through logic gates until it reaches a latch or a flip-flop as shown in Fig. 2.7. If the timing of the SET pulse meets the setup and hold times of the latch or flip-flop which is shown in Fig. 2.8, an incorrect

logic will be stored in the latch or flip-flop and thus causes system malfunction. The increasing clock rate leads to increasing SET vulnerability in advanced CMOS technologies, since the clock period has the same order of the width to that of the SETs.

Figure 2.7 SET propagates in a logic circuit.

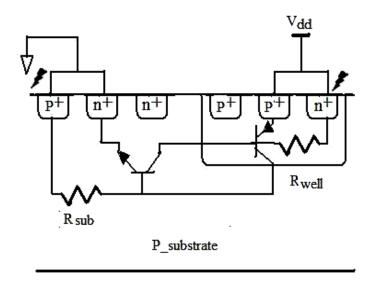

**D-** Single-event latch-up (SEL) [47] [48]: In most of the advanced CMOS processes, nMOS transistors and pMOS transistors share the same p-type substrate while pMOS transistors are fabricated in an n-well. In this way, CMOS inherits parasitic bipolar transistors with positive feedback topology in its well structure that can cause latch-up as shown in Fig. 2.9 [44]. For this CMOS structure, a parasitic npn transistor is formed by the n+ (emitter), p-substrate (base), and n-well (collector). Similarly, a parasitic pnp transistor is formed by the p+ (emitter), n-well (base), and p-substrate (collector). This structure forms a positive feedback loop between the two transistors [49].

Figure 2.8 Timing of a SET pulse meets the setup and hold time of the latch or flip-flop.

If a heavy ion-induced current flows through the equivalent substrate resistance of  $R_{sub}$  to turn on the npn transistor, a current will flow through the equivalent n-well resistor,  $R_{well}$ . The voltage drop across  $R_{well}$  can be high enough to turn on the pnp transistor. As a result, a direct path from power supply to ground causes serious latch-up. This problem cannot be corrected until the power is removed and put back on again.

The SEL can cause permanent damages to the circuits since there is a short path between power supply and ground. SEL protection can be implemented by layout strategy. Depending on the process layout rule of the space between the p+ and n+, the p+ contact can be moved closer to the n+ diffusion region in the p-substrate while the n+ contact can be moved closer to the p+ diffusion region in the n-well. In this way, the resistances of  $R_{sub}$  and  $R_{well}$  can be so small that the voltage drop across it cannot turn on these two parasitic bipolar transistors.

The other SEL protection approach in the layout is to reduce the gain product of the two parasitic bipolar transistors by moving the n-well away from the n+ source/drain. The gain product of the two parasitic bipolar transistors is a prerequisite condition for latch-up. In theory, if the gain product of two parasitic bipolar transistors is less than one,

then latch-up can be avoided. The width of the base of the npn transistor increases in this way and leads to a gain reduction.

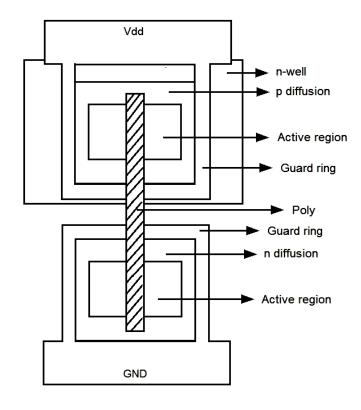

Some of other SEL protection approaches such as high substrate doping and high well doping, putting guard ring round the pMOS and nMOS devices separately as shown in Fig. 2.10 are also introduced [34]. The purpose of these approaches is intended to decrease the resistances of  $R_{\text{sub}}$  and  $R_{\text{well}}$  shown in Fig. 2.9.

Figure 2.9 Diagram of the parasitic latch-up structure in a CMOS inverter.

In contrary to TID, SEEs on ICs become more significant for advanced CMOS technologies, especially SETs and SEUs. Soft error rate (SER) in nanometer circuits and systems increases due to three main reasons. First, the current drivability decreases because of the use of lower power supply voltage and the smaller transistor size. Second, the capacitances including parasitic capacitors and load capacitors at the SEE-sensitive nodes reduce. Third, for high-speed application using the nanometer technology, the circuits and systems are more vulnerable to SETs as the clock rate increases.

Figure 2.10 A CMOS device with guard ring.

## 2.3 General SEU/SET Mitigation Approaches

To develop digital SEE-hardened designs, a transistor with a large width can be implemented to improve the current drivability and increase the capacitance at the sensitive nodes. This hardening approach can be implemented in the latches, flip flops, and SRAM cells. Obviously, there is a tradeoff between SEU hardness and circuit speed and area. Large transistor size is preferred for the SET propagation path since the low pass nature of digital circuit may shorten the pulse at each stage until it disappears [34]. However, this hardening approach is not practical because a SEU can happen at any node while a SET can propagate through any path. In addition, it is impossible to enlarge all of

the transistors to mitigate SEEs. Even a timing-critical path is analyzed satisfactory by electronic design automation (EDA) tools, large transistors can slow down the signal propagation in this path. Low pass filter such as a simple RC circuit as shown in Fig. 2.11 can be inserted into the sensitive nodes to filter out the high frequency SET pulses. However, this approach is still subjected to the tradeoff between SET hardening and circuit speed and area. As a result, special approaches to mitigate both SETs and SEUs are essential in modern CMOS technologies used in the applications for radiation environments.

Figure 2.11 A SEU-hardened approach with RC filters in a SRAM cell.

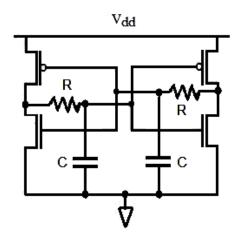

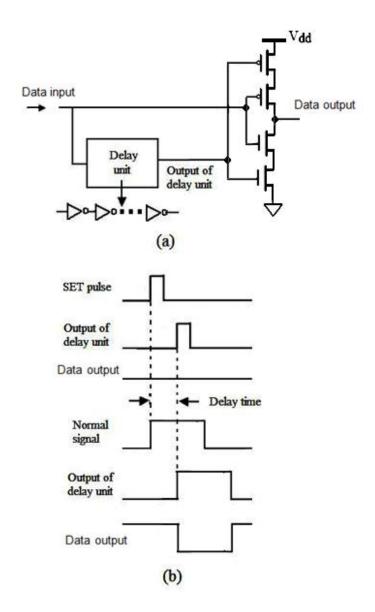

Pulse width filtering with inserted delay [34]: Normally the width of the SET pulse is shorter than the propagation signal width. A delay unit with an inverter chain can be designed to make the delay time longer than the SET pulse width but must be shorter than the signal width. In this case, as shown in Fig. 2.12, the SET pulse can be filtered out while the normal signal is allowed to pass. The disadvantage of this method is that

there is a tradeoff between speed and SET hardening because an additional delay is introduced into the signal path.

Figure 2.12 (a) Architecture of a pulse width filtering with inserted delay. (b) Waveforms of pulse width filtering with inserted delay [34].

Triple modular redundancy: TMR is a popular SET mitigation solution in the digital radiation-hardened design [24]. Fig. 2.13 illustrates the technique. Circuits and

systems are triplicated in parallel following by a voter to produce a single output. If SETs happen in any one of the three circuits or systems while the other two functions correctly, the correct logic value can be produced at the output with majority voting function. Even TMR is the most common SET mitigation method, there are some disadvantages with this solution. First, it is obvious that these three identical parallel blocks should not be placed closely in physical layout in case the charge share happens between any of the two blocks. This constraint requires more effort in the automatic placing and routing. Second, the voter does not protect itself if a SET strikes upon it. The whole system fails if the voter fails. Third, TMR method can work very well in the low frequency circuits and systems. However, glitch-induced error can happen in the high frequency circuits and systems as described in Chapter 6. Fourth, TMR approach has high power/area penalties.

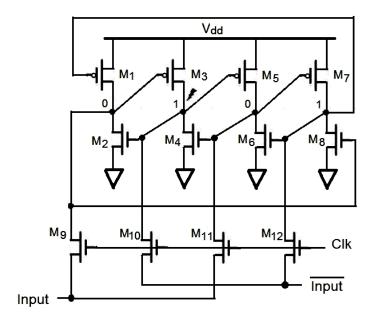

Dual interlocked storage cells: DICE circuit is usually implemented in the latch which is called DICE latch [25]. Instead of a single feedback topology in the traditional latch, DICE implements a dual feedback topology to store a bit to improve SEU immunity. As shown in Fig. 2.14, at the rising edge of the clock, complementary data are stored in the drains of  $M_2$  and  $M_4$ , respectively. Their redundant partners are also stored in the drain of  $M_6$  and  $M_8$ , respectively. If a SEU happens at the drain of  $M_4$  changing the logic of this node from 1 to 0, this abrupt change turns on the  $M_5$  and makes logic competition between  $M_5$  and  $M_6$ . Because both of  $M_5$  and  $M_6$  are turned on, the logic of output depends on the drivability of  $M_5$  and  $M_6$ . The worst situation is that the logic of the drain of  $M_6$  charges from 0 to 1. However, the logic change at the nodes of the drains of  $M_4$  and  $M_6$  will not affect the logic at the drain of  $M_2$  and  $M_8$  since both of these nodes are in the floating state. This mitigation approach introduces the area and speed penalty while improves SEU immunity.

Figure 2.13 (a) Diagram of the TMR technique. (b) Waveforms of the TMR under a SET pulse propagation.

Figure 2.14 Schematic of DICE latch circuit [25].

## 2.4 SETs on CMOS Analog Circuits

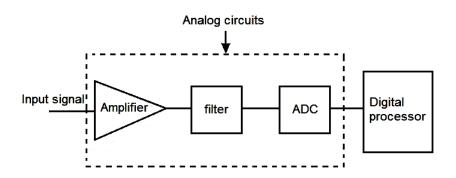

With the development of semiconductor technologies and EDA tools, more circuit and system functions can be efficiently implemented in the silicon in digital domain. In the modern digital ICs design, millions and billions transistors are integrated on the same substrate to execute complicated functions and operations such as memory and data processing. However, analog circuits are still playing an important and indispensable role in today's ICs design. Almost all of interface circuits are composed by analog and mixed signal circuits. The reasons are presented in the following:

First, signals are eventually processed by computational system such as digital signal processing (DSP). However, the amplitudes of most nature signals are too small which can be a few microvolts to be digitized directly. In this way, amplifiers or automatic gain controllers (AGCs) are required to amplify these signals before processed

by the ADCs. Also, in order to get a "cleaned" digitized signal, filters are introduced to get rid of the out-of-band undesired signals. Furthermore, ADCs themselves are also typical analog circuit. Fig. 2.15 shows this front-end block.

Figure 2.15 An architecture of signal digitization.

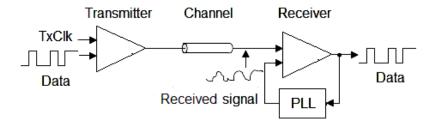

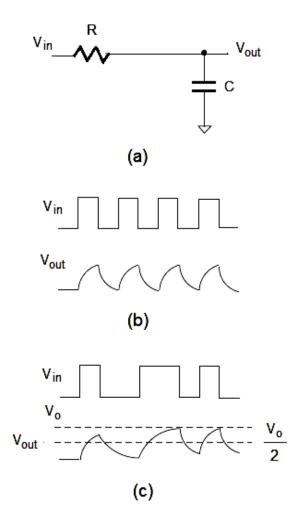

Second, analog circuits are extensively used in the front-end design in high speed data link applications as shown in Fig. 2.16. The channel is typically a cable or a printed circuit board (PCB) trace through which signals propagate from the transmitter to the receiver. The channel is the origin of many voltage noise and timing noise sources which impose a challenging design constraint in high speed circuit design. Voltage noise directly reduces voltage margins. To simplify the analysis, a transmission line can be modeled as a simple RC low-pass filter as shown in Fig. 2.17 (a). For a periodic square wave, a low-pass filter attenuates the high-frequency components, yielding finite rise and fall times, shown in Fig. 2.17 (b). But for a random digital signal, as illustrated in Fig. 2.17 (c), for a single one followed by a zero, the output does not come close to V<sub>0</sub>. In this way, the output voltage level corresponding to ones and zeros varies with time, making it difficult to define a decision threshold. This phenomenon is due to the inter symbol

interference (ISI). The narrower the bandwidth, the larger the value of R and C, the longer the signal tails and the greater the ISI.

Figure 2.16 Diagram of a data link.

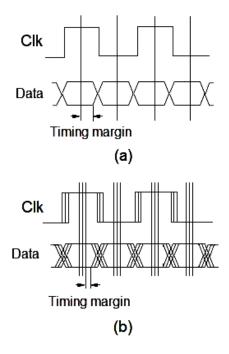

Other voltage noise sources come from the signal reflection, cross-talk, etc. Timing errors shift the transition edges of the received signals relative to the transition edges of the clock and reduce the timing margin. Fig. 2.18 (a) shows an ideal data sampling case in which the sampling point is right in the middle of a bit time. The timing margin is half of the bit time. However, in reality, as shown in Fig. 2.18 (b), the timing margin is reduced because jitter is introduced in the transmitted signal as well as the clock. With these effects, the input signals at the receiver are distorted in such a way that the transmitted data cannot be restored at the receiver side. So how to correct these problems is the heart of analog circuit design in the high speed data link applications. Normally, the analog blocks of the impedance matching, the signal driver, the preemphasizer, the post-equalizer, the PLL, the VCO, the CDR, and the sample and hold circuit are necessary functional blocks in the front-end of high speed data link designs. Quality of these analog circuits directly affects system performance. Analog circuits are

also extensively used in frequency synthesizer, front-end of the RF transceiver, power management, etc.

Figure 2.17 (a) RC model of transmission lines. (b) Periodic data response. (c) Random data response.

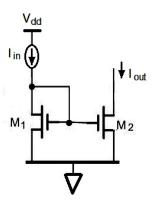

In analog circuits, SET is the most troublesome SEE that needs to be mitigated [34]. Unlike SETs in digital circuits in which SET-induced pulses need to surpass the gate threshold to propagate, a small SET-induced pulse can cause significant circuit degradation in analog circuits. A typical analog circuit is the current-mirror shown in

Fig .2.19. The current-mirror is a simple but very popular circuit to generate a bias current independent of voltage variations in analog circuits. Normally, an accurate bias current is critical for analog circuits because it directly affects many important performances such as voltage gain, bandwidth, voltage swing, and noise. In Fig. 2.19, the output current,  $I_{out}$ , is given by

$$I_{out} = \frac{W_2}{W_1} * I_{in} \tag{2.1}$$

where  $W_1$  and  $W_2$  is width of  $M_1$  and  $M_2$ , respectively,  $I_{in}$  is the current flowing through  $M_1$ .

Figure 2.18 Phase noise and timing jitter. (a) Ideal case. (b) Practical case.

Channel length modulation is neglected in this equation. Normally, the lengths of two transistors are the same so as to minimize errors due to the side-diffusion of the source and drain areas. In the radiation environments, the current through  $M_1$  changes

when a high energy ion strikes the sensitive node of  $M_1$  and results in a change of  $I_{out}$  by the multiplication ratio. Usually, the multiplication ratio is from 3 to 10 in order to decrease the current variation [34]. In this case, the change of  $I_{out}$  degrades circuit performances such as gain, voltage swing, noise, common-mode rejection ratio, etc.

Figure 2.19 An nMOS-based current-mirror.

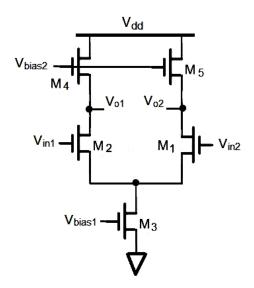

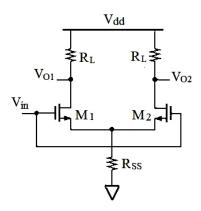

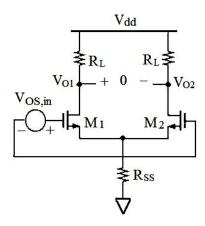

The other example is a differential pair amplifier. Differential architecture is extensively used in analog circuit design for the benefits of noise rejection, high linearity, and high voltage swing. As shown in Fig. 2.20,  $M_{1,2}$  are the two input transistors. With a certain bias gate voltage,  $M_3$  provides bias current determining the static operation point for  $M_{1,2}$ .  $M_{4,5}$  work as an active load to transfer the current to output voltage. In the normal operation, the output voltage is given by

$$V_{o1} - V_{o2} = -g_{m1,2} * (r_{1,2} // r_{4,5}) * (V_{in1} - V_{in2})$$

(2.2)

where  $g_{m1,2}$  are the transconductances of  $M_{1,2}$ ,  $r_{1,2}$  and  $r_{4,5}$  are output resistances of  $M_{1,2}$  and  $M_{4,5}$ , respectively. If a high energy ion strikes the sensitive node, such as the drain of  $M_1$  or  $M_2$ , the output voltage is

$$V_{o1} - V_{o2} = -g_{m1.2} * (r_{1.2} / / r_{4.5}) * (V_{in1} - V_{in2}) \pm \Delta V$$

(2.3)

where  $\Delta V$  is the SET-induced voltage drop at the output. "±" depends on the high energy ion striking at the drain of  $M_1$  or  $M_2$ . If the high energy ion strikes at the drain of  $M_3$ , ideally, due to the characteristic of common-mode rejection of differential pair, the currents flow through the  $M_1$  and  $M_2$  are kept constant. So does the output voltage. However, the output resistance of  $M_3$  cannot be ignored due to the short channel modulation effect. In this way, the SET-induced voltage drop at the drain of  $M_3$  will affect the circuit performance. The gain of amplifier is changed which is given by

$$A_{V} = -\frac{r_{4,5}/2}{\frac{1}{2}g_{m1,2} + r_{3}}$$

(2.4)

Figure 2.20 A differential pair amplifier.

Other effects on the differential pair amplifier include shift of the static operating point, degradation of the output voltage swing, and disturbance of the following stage.

The analog circuits studied in this dissertation are op amps, dynamic comparators, LC-tank oscillators, and PLLs. The motivation of the selection was discussed in Chapter 1. The detailed analyses of circuit operations and SET effects on these circuits are presented in the following chapters. Brief introductions of these circuits are described in the following:

Operational amplifier: The op amp is a versatile functional block used in almost every analog and mixed signal systems. It can be used to construct a simple application such as instrumentation amplifier, voltage regulator or relative large circuits and systems such as active high-order filter, switch capacitor circuits, and band gap reference circuits. Op amp amplifies the differential input signals with the voltage gain up to 10<sup>5</sup> while a general single stage amplifier has only tens of voltage gain. Because this huge voltage gain drives the op amp into a nonlinear region even with a small input signal voltage, op amp is usually employed in a feedback system. In this case, its high voltage gain only decides the precision and linearity of the closed-loop circuit.

**Comparator:** Similar to op amps, comparators take a tiny differential input voltage and generate a logic level output. However, the comparators usually work synchronously with a clock signal. At the rising edge or falling edge of the clock signal, logic signal can be generated at the output. Comparators are generally used in ADC and front-end of the receiver in high-speed data link applications.

Voltage-controlled oscillator: Oscillators are necessary in almost all of analog circuits and systems. For example, signals need to be sampled by the clock to perform analog to digital conversion. Also in data communications, all of the transmitted and received signals are synchronized by the clocks. However, most applications require a tunable oscillation frequency such as in a RF transceiver. Normally, the output frequency

is a function of input control voltage in the VCOs. Using a control voltage, variable output frequency of an oscillator can be generated.

Phase-locked loop: In the VCOs, many factors such as noise, temperature, power supply fluctuation, and ground bouncing can introduce jitter in the oscillation signals, therefore they will cause the shift of the frequency and phase of the oscillation signals. A mechanism must be introduced to generate an accurate output frequency and also correct the frequency shift automatically. PLL is a particular system which can perform this function. With a low frequency reference signal, PLLs can synchronize their output signals with this reference signal in frequency as well as in phase by a negative feedback topology. In this way, the frequency variation cannot be accumulated and a "clean" oscillation signal can be generated.

## 2.5 Pulsed-Laser Testing