# Universität Leipzig Fakultät für Mathematik und Informatik Institut für Informatik

Bereitstellung eines kompletten System-on-Chip aus lizenzfreien AMBA 2.0 Komponenten sowie des LEON3-SPARC-Prozessors im Xilinx-EDK

# Diplomarbeit

Leipzig, Februar 2008 vorgelegt von

Markus Jäger

geb. am: 04.02.1983

Studiengang: Diplom Informatik

Betreuung: Prof. Dr. Udo Kebschull

Universität Heidelberg

Für meine Mutter

# **Danksagung**

Hier möchte ich allen danken, die mir diese Arbeit ermöglicht haben.

Ich danke Prof. Dr. Udo Kebschull für das aufschlussreiche und anregende Arbeitsthema sowie meinem Betreuer Norbert Abel für seine immerwährende Hilfsbereitschaft und seine Unterstützung bei allen denkbaren Problemen.

Großer Dank gilt auch meiner Mutter, die mir mit ihrer Kraft und Ausdauer jeden Tag aufs Neue ein Vorbild ist.

# **Abstract**

Aufgrund der wachsenden Ressourcen heutiger FPGAs, durch neue technologische Entwicklungen, erschließen sich immer neue Einsatzmöglichkeiten.

Beispielsweise wächst der Wunsch, ein vollständiges System in einem einzigen Chip einzubringen. Die sogenannten Systems-on-Chip (kurz SoC) bestehen dabei aus einem Prozessor, einen Bussystem, Schnittstellen zu externen Speichern und anderen Peripheriegeräten.

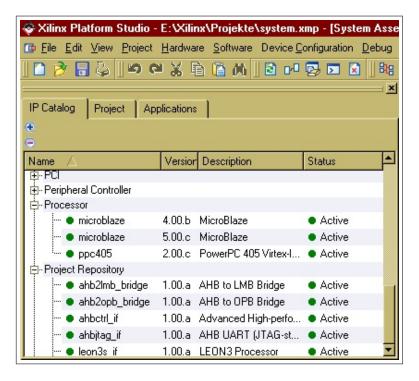

Die Firma Xilinx bietet mit ihrer Software EDK eine IP-Core Bibliothek an, mit der es möglich ist, ein komplettes SoC für einen FPGA zu synthetisieren. Die Xilinx-IP-Core-Bibliothek benutzt dabei den Soft-Prozessor MicroBlaze als  $\mu$ P. Die IP-Core Bibliothek von Xilinx ist nicht Open-Source und zu ihrer Benutzung werden Lizenzgebühren verlangt.

In dieser Arbeit wird eine neue IP-Core Bibliothek bereitgestellt, welche Open-Source ist und damit frei einsehbar und frei verwendbar ist. Die neue IP-Core Bibliothek wird durch diese Arbeit in den Workflow des Xilinx-EDK eingebunden und ist somit komfortabel benutzbar.

Als Grundlage dient die IP-Core Bibliothek der Firma Gaisler Research, auch genannt Gaisler Research Library (kurz GRLIB). Die GRLIB besitzt eine Vielzahl von IP-Cores unter denen, für jeden IP-Core der Xilinx Bibliothek, ein Ersatz gefunden werden konnte. Die GRLIB setzt als  $\mu$ P auf den LEON3-Prozessor. Der LEON3-Prozessor wurde nach den Spezifikationen der SPARC entworfen und ist ein höchst flexibler und konfigurierbarer Soft-Prozessor.

In dieser Arbeit wurde weiterhin das "SnapGear"-Linux evaluiert, welches auf dem LEON3-Prozessor mit Komponenten der GRLIB ausgeführt werden kann.

| AŁ | ostrac                                           | t       |            |                                                                 | 4  |  |

|----|--------------------------------------------------|---------|------------|-----------------------------------------------------------------|----|--|

| 1  | Einl                                             | eitung  |            |                                                                 | 11 |  |

|    | 1.1                                              | Motiva  | ation      |                                                                 | 13 |  |

|    | 1.2                                              | Inhalt  | der Arbeit |                                                                 | 13 |  |

|    |                                                  | 1.2.1   | Gliederu   | ing der schriftlichen Ausarbeitung                              | 14 |  |

|    | 1.3                                              | Lizenz  | rechtliche | Bedingungen und Probleme                                        | 18 |  |

|    |                                                  | 1.3.1   | Xilinx, I  | nc. CORE SITE LICENSE AGREEMENT                                 | 18 |  |

|    |                                                  | 1.3.2   | GNU G      | eneral Public License (GPL)                                     | 20 |  |

|    |                                                  | 1.3.3   | Zusamm     | nenfassung                                                      | 21 |  |

| 2  | Gru                                              | ndlager | 1          |                                                                 | 22 |  |

|    | 2.1                                              | Systen  | n-on-Chip  | (SoC)                                                           | 22 |  |

|    |                                                  | 2.1.1   | Der Mik    | roprozessor ( $\mu$ P)                                          | 23 |  |

|    |                                                  | 2.1.2   | Das Bus    | system                                                          | 24 |  |

|    |                                                  | 2.1.3   | Werkzeu    | ige zur Erstellung von SoCs                                     | 26 |  |

|    | 2.2 Das Werkzeug: Embedded Development Kit (EDK) |         |            |                                                                 |    |  |

|    |                                                  | 2.2.1   | Arbeitsp   | olan der Software EDK                                           | 31 |  |

|    |                                                  |         | 2.2.1.1    | Arbeitsschritt 1 (VHDL-Code der System-Entity generieren)       | 32 |  |

|    |                                                  |         | 2.2.1.2    | Arbeitsschritt 2 (Hardware Synthetisieren)                      | 35 |  |

|    |                                                  |         | 2.2.1.3    | Arbeitsschritt 3 (Software Kompilieren)                         | 36 |  |

|    |                                                  |         | 2.2.1.4    | Arbeitsschritt 4 (Hard- und Software zum Bitstream verbinden) . | 38 |  |

|    |                                                  | 2.2.2   | EDK-Ko     | onstrukte für IP-Cores                                          | 39 |  |

|    |                                                  |         | 2.2.2.1    | Das IP-Core Verzeichnis                                         | 41 |  |

|    |                                                  |         | 2.2.2.2    | Microprocessor Hardware Specification (MHS)                     |    |  |

|    |                                                  |         | 2.2.2.3    | Microprocessor Peripheral Definition (MPD)                      | 44 |  |

|    |                                                  |         | 2.2.2.4    | Peripheral Analyze Order (PAO)                                  | 47 |  |

|    |                                                  |         | 2.2.2.5    | Microprozessor Software Specification (MSS)                     | 48 |  |

|    |                                                  |         | 2.2.2.6    | Das Treiber-Verzeichnis                                         | 50 |  |

|    |                                                  |         | 2.2.2.7    | Microprocessor Driver Definition (MDD)                          | 51 |  |

|    |                                                  |         | 2.2.2.8    | Das BSP-Verzeichnis                                             | 52 |  |

|    |                                                  |         | 2.2.2.9    | Tool Command Language (Tcl)                                     | 52 |  |

| 3 | Star | nd der T | echnik      |                                                             | 55    |

|---|------|----------|-------------|-------------------------------------------------------------|-------|

|   | 3.1  | Die Ga   | aisler Rese | earch IP Library (GRLIB)                                    | . 57  |

|   |      | 3.1.1    | Überblic    | ck                                                          | . 58  |

|   |      | 3.1.2    | Installati  | ion                                                         | . 59  |

|   |      | 3.1.3    | Verzeich    | nnisstruktur                                                | . 59  |

|   |      |          | 3.1.3.1     | "bin"-Verzeichnis                                           | . 60  |

|   |      |          | 3.1.3.2     | "boards"-Verzeichnis                                        | . 60  |

|   |      |          | 3.1.3.3     | "design"-Verzeichnis                                        | . 61  |

|   |      |          | 3.1.3.4     | "doc"-Verzeichnis                                           | . 64  |

|   |      |          | 3.1.3.5     | "lib"-Verzeichnis                                           | . 64  |

|   |      |          | 3.1.3.6     | "software"-Verzeichnis                                      | . 65  |

|   |      | 3.1.4    | Handhab     | oung der GRLIB                                              | . 65  |

|   |      |          | 3.1.4.1     | Der Workflow von Gaisler Research                           | . 65  |

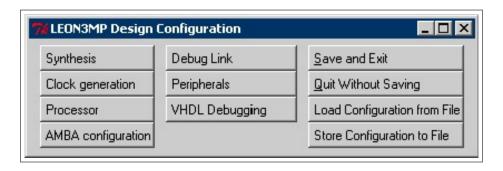

|   |      |          |             | Schritt 1 (Festlegen und Konfigurieren der SoC-Komponenten) | ) 66  |

|   |      |          |             | Schritt 2 (Synthetisieren des erstellten SoC)               | . 69  |

|   |      |          | 3.1.4.2     | Der Workflow mit Xilinx ISE                                 | . 71  |

|   |      | 3.1.5    | Design-l    | Konzepte der GRLIB                                          |       |

|   |      |          | 3.1.5.1     | AMBA Standard                                               | . 75  |

|   |      |          |             | Richtlinien                                                 | . 76  |

|   |      |          |             | Spezifikation                                               | . 76  |

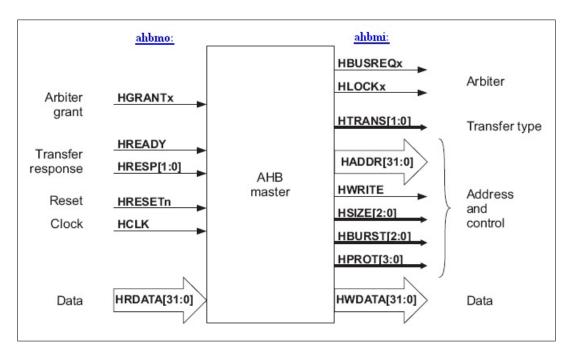

|   |      |          | 3.1.5.2     | AMBA Advanced High-performance Bus (AHB)                    |       |

|   |      |          |             | Das AHB-Master-Interface                                    | . 81  |

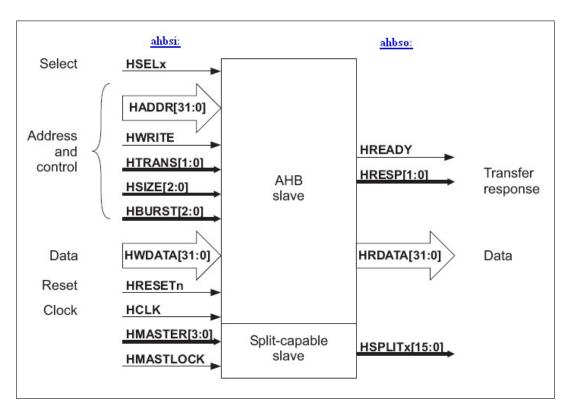

|   |      |          |             | Das AHB-Slave-Interface                                     |       |

|   |      |          |             | Das AHB-Select-Signal ("hsel")                              | . 95  |

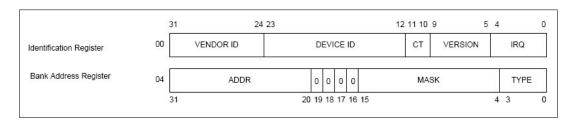

|   |      |          |             | "Plug and Play"                                             | . 96  |

|   |      |          |             | Der Adressierungs-Prozess                                   | . 98  |

|   |      |          |             | Interrupt-Steuerung                                         |       |

|   |      |          | 3.1.5.3     | AMBA Advanced Peripheral Bus (APB)                          | . 100 |

|   |      |          | 3.1.5.4     | Technologie-Unabhängigkeit                                  | . 101 |

|   |      |          |             | Umsetzung                                                   |       |

|   |      | 3.1.6    |             | Werkzeuge für die GRLIB                                     |       |

|   |      | 3.1.7    | LEON3-      | -Prozessor in der GRLIB                                     | . 103 |

| 4 | Der  | Ansatz   |             |                                                             | 106   |

|   | 4.1  | GRLIE    | B-IP-Core   | s in das EDK einbinden                                      | . 106 |

|   | 4.2  | Testen   | des LEOI    | N3-Systems mit nativer Software                             | . 108 |

|   | 4.3  | Bereits  | stellung ei | nes Linux für das LEON3-System                              | . 109 |

|   | 4.4  | Verbin   | den des L   | EON3-Systems mit einem MicroBlaze-System                    | . 110 |

| 5 | Einb | oindung  | der GRL     | .IB in das EDK                                              | 112   |

| 5.1 | Ausga  | ngspunkt und Ansatz                                                      | . 112 |

|-----|--------|--------------------------------------------------------------------------|-------|

|     | 5.1.1  | Erstellung eines IP-Cores mit dem "Create and Import Peripheral Wizard". | . 113 |

| 5.2 | Einbin | dung eines GRLIB-IP-Cores in das EDK                                     | . 114 |

|     | 5.2.1  | Bibliothek-IP-Cores                                                      | . 114 |

|     | 5.2.2  | IP-Core-Verzeichnis                                                      | . 116 |

|     | 5.2.3  | MPD-Anpassungen                                                          | . 117 |

|     |        | 5.2.3.1 OPTION                                                           | . 117 |

|     |        | 5.2.3.2 BUS_INTERFACE                                                    | . 120 |

|     |        | 5.2.3.3 PARAMETER                                                        | . 121 |

|     |        | 5.2.3.4 PORT                                                             | . 122 |

|     | 5.2.4  | PAO-Anpassungen                                                          | . 124 |

|     | 5.2.5  | Tcl-Anpassungen                                                          | . 125 |

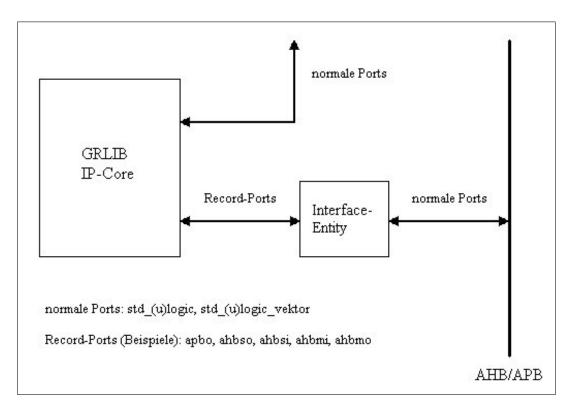

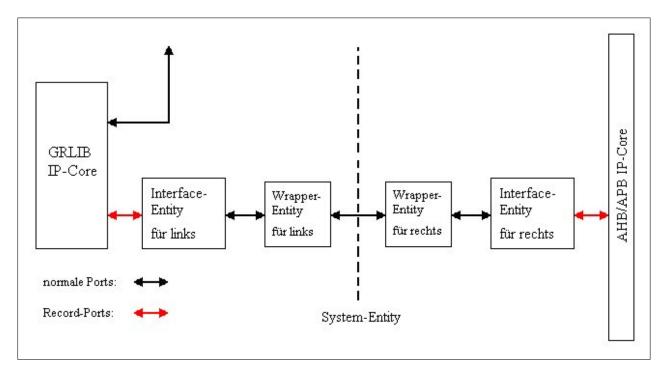

| 5.3 | Proble | me bei der Einbindung und Synthese der GRLIB                             | . 126 |

|     | 5.3.1  | "Interface-Entity-Problem"                                               | . 126 |

|     |        | 5.3.1.1 Lösung des "Interface-Entity-Problems"                           | . 127 |

|     | 5.3.2  | "Bus-Problem"                                                            | . 131 |

|     |        | 5.3.2.1 "Bus-Problem (APB)"                                              | . 132 |

|     |        | 5.3.2.2 ,,Bus-Problem" (,,irqmp_if" und ,,dsu3_if")                      | . 132 |

|     | 5.3.3  | "BMM-Problem"                                                            | . 134 |

|     |        | 5.3.3.1 Lösung des "BMM-Problems"                                        | . 134 |

|     | 5.3.4  | "MHS-Reihenfolge-Problem"                                                | . 135 |

|     |        | 5.3.4.1 Lösung des "MHS-Reihenfolge-Problems"                            | . 136 |

|     |        | 5.3.4.2 Zusammenfassung des "MHS-Reihenfolge-Problems"                   | . 140 |

|     | 5.3.5  | "GRMON-APB-Problem"                                                      | . 140 |

|     |        | 5.3.5.1 Lösung des "GRMON-APB-Problems"                                  | . 142 |

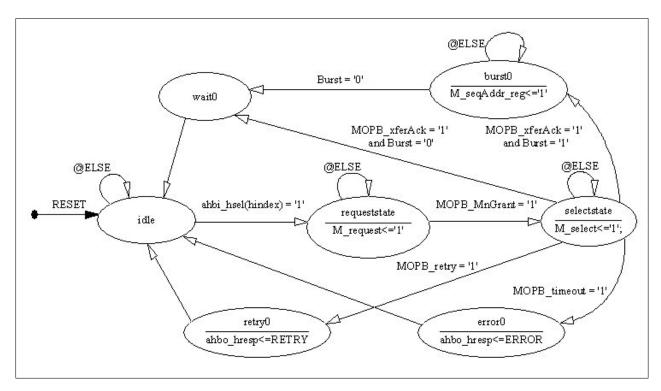

|     | 5.3.6  | "FSM-Problem"                                                            | . 142 |

|     |        | 5.3.6.1 Lösung des "FSM-Problems"                                        | . 143 |

|     | 5.3.7  | "Constraints-Problem"                                                    | . 143 |

|     |        | 5.3.7.1 Lösung des "Constraints-Problem"                                 | . 144 |

|     | 5.3.8  | "GR Ethernet-Problem"                                                    | . 145 |

|     |        | 5.3.8.1 Lösung des "GR Ethernet-Problems"                                | . 145 |

|     | 5.3.9  | "system.make-Problem"                                                    | . 146 |

|     |        | 5.3.9.1 Anpassungen der "systemLEON.make"                                | . 146 |

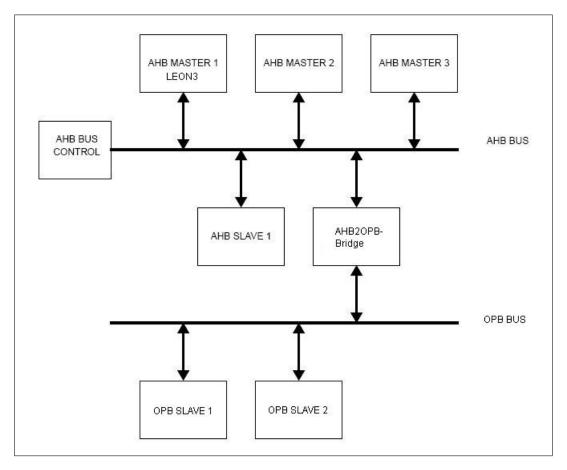

| 5.4 | Verbin | dung von GRLIB-System und MicroBlaze-System                              | . 147 |

|     | 5.4.1  | AHB2LMB-Bridge                                                           | . 148 |

|     | 5.4.2  | AHB2OPB-Bridge                                                           | . 149 |

| 5.5 | Ausge  | wählte IP-Cores der GRLIB im EDK und ihre Besonderheiten                 | . 151 |

|     | 5.5.1  | "clkrstgen_if"-IP-Core                                                   | . 151 |

|     | 5.5.2  | "ahbuart_if" und "apbuart_if"-IP-Core                                    | . 152 |

|   |      | 5.5.3   | "ahbjtag_if"-IP-Core                                               | . 153 |

|---|------|---------|--------------------------------------------------------------------|-------|

|   |      | 5.5.4   | "greth_if"-IP-Core                                                 | . 153 |

|   |      | 5.5.5   | "ddrspa_if"-IP-Core                                                | . 154 |

|   |      | 5.5.6   | "apbvga_if" und "svgactrl_if"-IP-Core                              | . 154 |

|   |      |         | 5.5.6.1 "apbvga_if"-IP-Core                                        | . 154 |

|   |      |         | 5.5.6.2 "svgactrl_if"-IP-Core                                      | . 155 |

|   |      | 5.5.7   | "ahbram_if"-IP-Core                                                | . 155 |

|   |      | 5.5.8   | "apbps2_if"-IP-Core                                                | . 156 |

|   |      | 5.5.9   | "gptimer_if"-IP-Core                                               | . 156 |

|   |      | 5.5.10  | "logan_if"-IP-Core                                                 | . 156 |

| 6 | Nati | ve C-Pr | ogramme für ein LEON3-SoC                                          | 158   |

|   | 6.1  | Registe | erdeklaration der IP-Cores                                         | . 159 |

|   | 6.2  | _       | ration einer Registerstruktur                                      |       |

|   | 6.3  |         | re Register lesen und schreiben                                    |       |

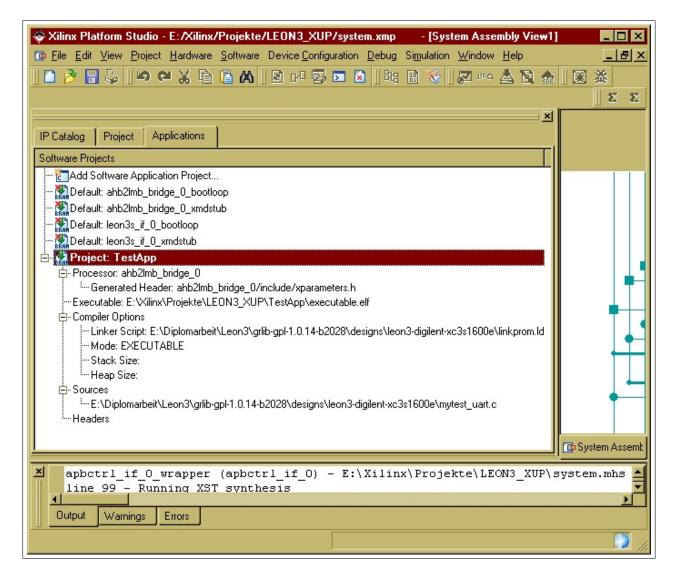

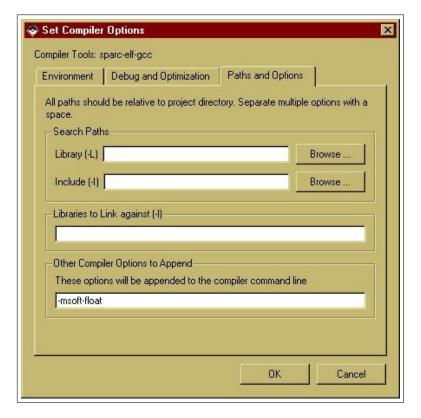

|   | 6.4  |         | C-Programme im EDK                                                 |       |

| _ |      |         |                                                                    | 40=   |

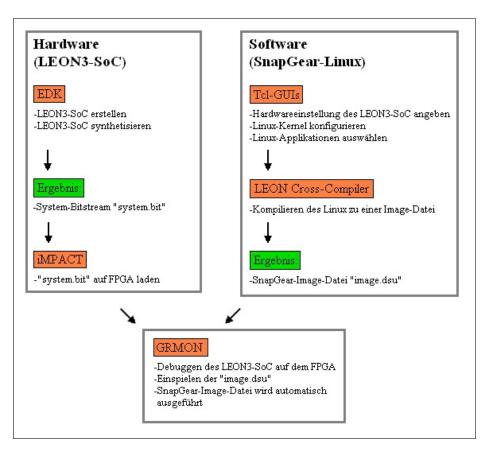

| 7 |      |         | em LEON3-System                                                    | 165   |

|   | 7.1  |         | Cross-Compiler für Linux                                           |       |

|   | 7.2  |         | SnapGear"-Linux                                                    |       |

|   |      | 7.2.1   | Der Erstellungsprozess und dessen Werkzeuge                        |       |

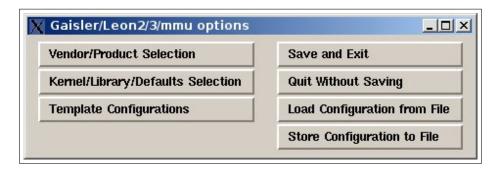

|   |      |         | 7.2.1.1 Schritt 1 (Grundeinstellungen zum SoC)                     |       |

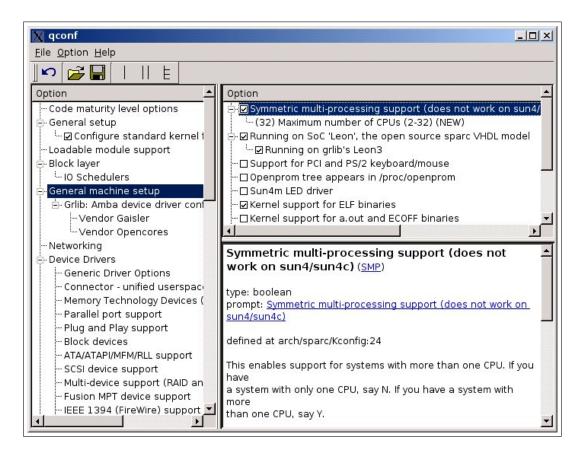

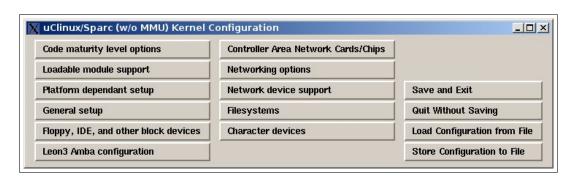

|   |      |         | 7.2.1.2 Schritt 2 (Konfiguration des "SnapGear"-Linux-Kernels)     |       |

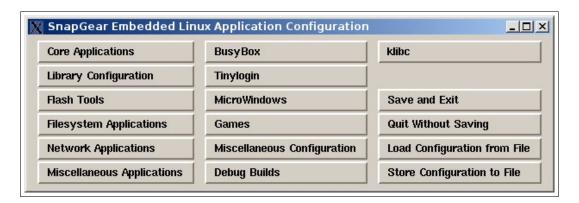

|   |      | 7.0.0   | 7.2.1.3 Schritt 3 (Anwendungen für das "SnapGear"-Linux)           |       |

|   |      | 7.2.2   | Hinzufügen zusätzlicher Treiber                                    | . 1/3 |

| 8 | Erge | ebnisse |                                                                    | 175   |

|   | 8.1  | Erreich | hte Ziele und Grenzen der Arbeit                                   | . 176 |

|   | 8.2  | Die GF  | RLIB-IP-Cores im EDK                                               | . 178 |

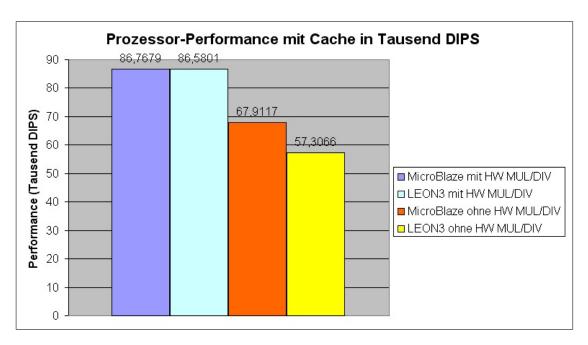

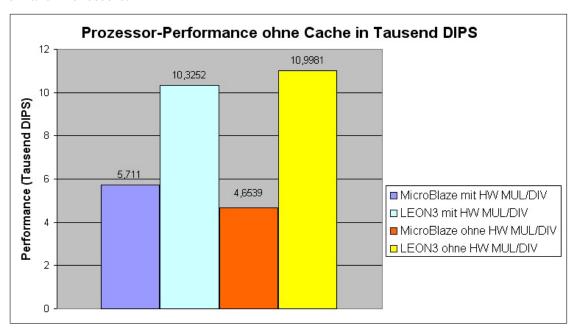

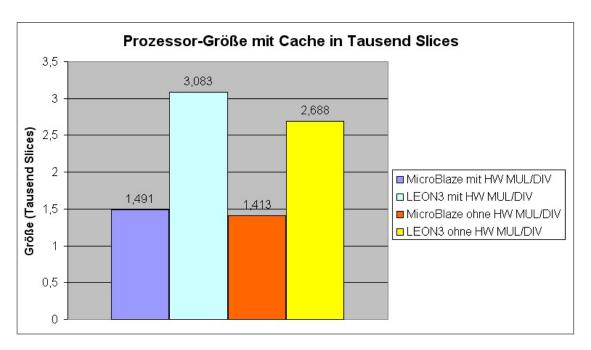

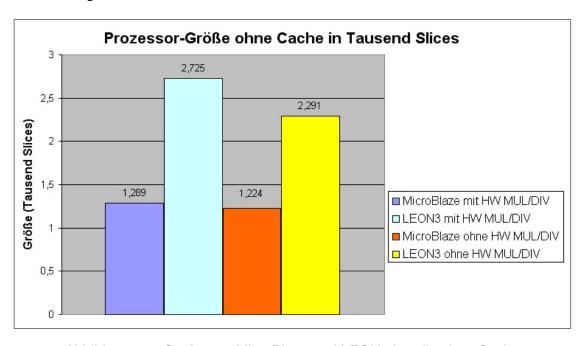

|   | 8.3  | Verglei | cich von MicroBlaze und LEON3                                      | . 179 |

|   |      | 8.3.1   | Testbedingungen allgemein                                          | . 179 |

|   |      | 8.3.2   | Testszenario                                                       | . 181 |

|   |      |         | 8.3.2.1 Systemzusammenstellung                                     | . 181 |

|   |      |         | 8.3.2.2 Systemkonfiguration                                        | . 182 |

|   |      |         | 8.3.2.3 Benchmarks                                                 | . 184 |

|   |      | 8.3.3   | Testergebnisse des Dhrystone 2.1 Benchmark                         | . 184 |

|   |      |         | 8.3.3.1 MicroBlaze 5.00.c Prozessor                                | . 185 |

|   |      |         | 8.3.3.2 LEON3-Prozessor                                            | . 186 |

|   |      | 8.3.4   | Auswertung der Testergebnisse                                      | . 186 |

|   |      |         | 8 3 4 1 Performance und Größen-Ergebnisse von MicroRlaze und I FON | 3186  |

|   |             |         | 8.3.4.2 Großen-Ergebnisse von MicroBlaze-SoC und LEON3-SoC 1 | 90 |

|---|-------------|---------|--------------------------------------------------------------|----|

|   | 8.4         | Maxim   | al-Performance vom MicroBlaze und LEON3                      | 92 |

|   |             | 8.4.1   | Testergebnisse                                               | 93 |

| 9 | Aust        | olick   | 1                                                            | 97 |

| Α | Anha        | ang zur | GRLIB 1                                                      | 99 |

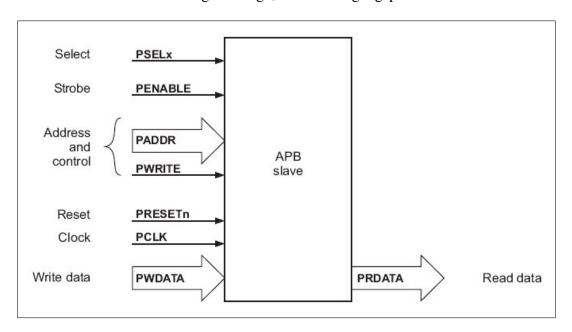

|   | <b>A.</b> 1 | AMBA    | Advanced Peripheral Bus (APB)                                | 99 |

|   |             | A.1.1   | Das APB-Slave-Interface                                      | 02 |

|   |             | A.1.2   | Das APB-Select-Signal ("psel")                               | 80 |

|   |             | A.1.3   | "Plug and Play"                                              | 09 |

|   |             | A.1.4   | Der Adressierungs-Prozess                                    | 10 |

|   |             | A.1.5   | Interrupt-Steuerung                                          | 12 |

|   | A.2         | Weiter  | e Werkzeuge für die GRLIB                                    | 12 |

|   |             | A.2.1   | Compiler                                                     | 13 |

|   |             |         | A.2.1.1 Installation des BCC                                 | 13 |

|   |             |         | A.2.1.2 Handhabung des BCC                                   | 14 |

|   |             |         | A.2.1.3 Erstellen einer "ahbrom"-Entity                      | 15 |

|   |             | A.2.2   | Gaisler Research Debugmonitor (GRMON)                        |    |

|   |             |         | A.2.2.1 Installation                                         | 17 |

|   |             |         | A.2.2.2 Handhabung                                           | 17 |

|   |             | A.2.3   | SPARC-Simulator (TSIM)                                       | 21 |

| В | Der l       | LEON3-  | Prozessor 2                                                  | 22 |

| _ | B.1         |         | ARC-Architektur Version 8                                    |    |

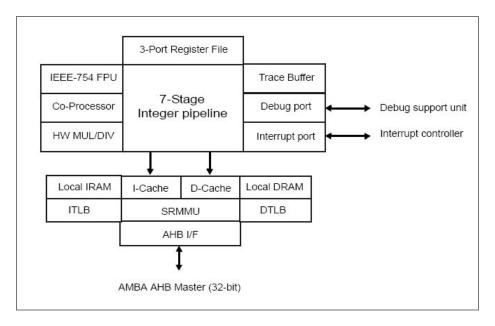

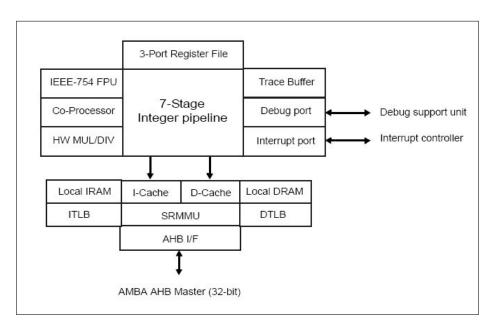

|   | B.2         |         | vählte Eigenschaften des LEON3                               |    |

|   |             | _       | Integer Unit (IU)                                            |    |

|   |             |         | B.2.1.1 Multiplikation und Division                          |    |

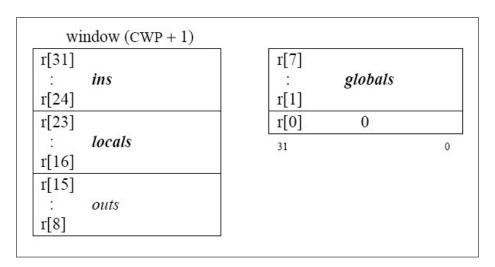

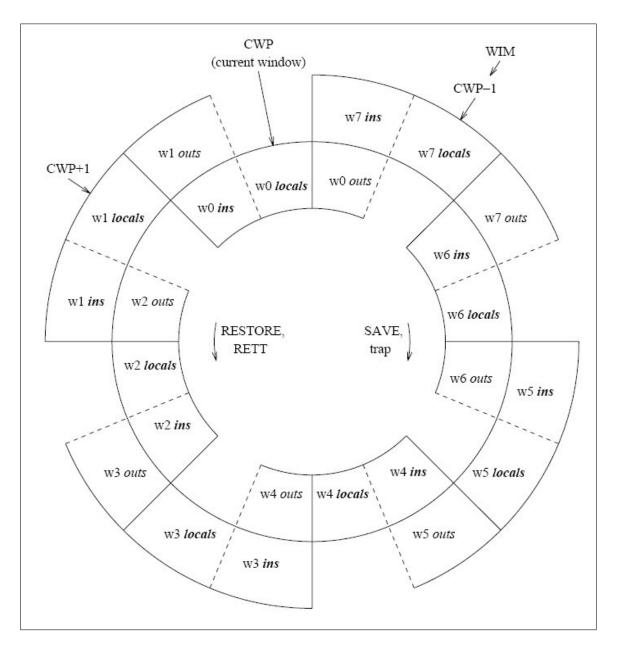

|   |             |         | B.2.1.2 Register                                             |    |

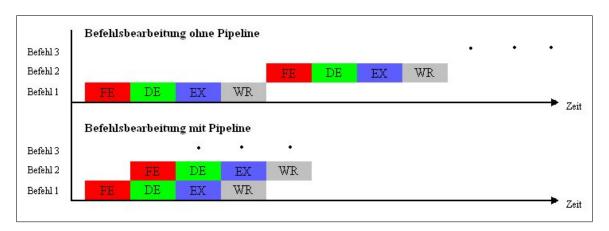

|   |             |         | B.2.1.3 Instruktion Pipeline                                 |    |

|   |             |         | B.2.1.4 Co-Prozessoren                                       |    |

|   |             | B.2.2   | Floating-Point Unit (FPU)                                    |    |

|   |             | B.2.3   | Power-down Modus                                             |    |

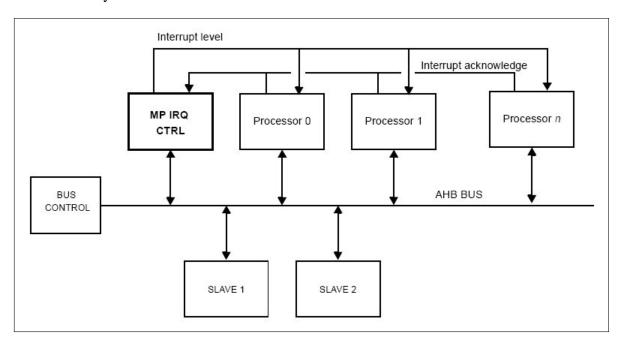

|   |             | B.2.4   | Multi-Prozessor Unterstützung                                |    |

|   |             | B.2.5   | Daten-Cache Snooping                                         |    |

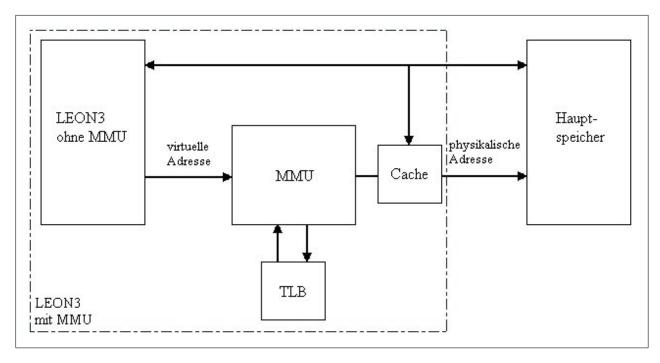

|   |             | B.2.6   | Memory Managment Unit (MMU)                                  |    |

|   |             |         | B.2.6.1 MMU im Gesamtkontext                                 |    |

|   |             |         | B.2.6.2 Konfiguraton                                         |    |

|   |             | B.2.7   | Cache-System                                                 |    |

|   |             |         | B.2.7.1 Konfiguration                                        |    |

|     |             |          | B.2.7.2    | Programm-Cache                                      | . 241 |

|-----|-------------|----------|------------|-----------------------------------------------------|-------|

|     |             |          | B.2.7.3    | Daten-Cache                                         | . 241 |

|     |             |          | B.2.7.4    | Cache-Flush                                         | . 242 |

| _   | _           | . =      |            |                                                     |       |

| С   |             |          |            | system als eingebettetes System                     | 243   |

|     | <b>C</b> .1 |          |            | er GRLIB                                            |       |

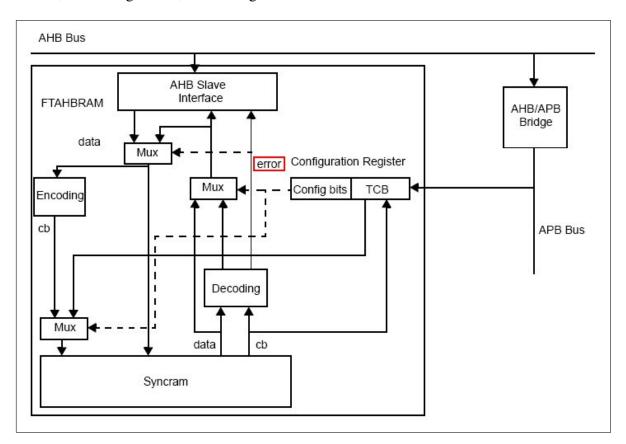

|     |             | C.1.1    | •          | SRAM mit EDAC ("ftahbram")                          |       |

|     |             | C.1.2    | 32/64-Bi   | t PC133 SDRAM Controller mit EDAC ("ftsdctrl")      | . 248 |

|     |             | C.1.3    | Der fehle  | ertolerante LEON3 SPARC V8 Prozessor ("leon3ft")    | . 248 |

|     |             |          | C.1.3.1    | IU-Register Schutz                                  | . 248 |

|     |             |          | C.1.3.2    | FPU-Register Schutz                                 | . 249 |

|     |             |          | C.1.3.3    | Cache-Speicher Schutz                               | . 249 |

|     | C.2         | Möglic   | hkeiten fü | ir Echtzeit-Umsetzungen                             | . 250 |

|     |             | C.2.1    | "eCos" E   | Betriebssystem                                      | . 251 |

|     |             | C.2.2    | "VxWorl    | ks" Betriebssystem                                  | . 251 |

|     |             | C.2.3    | RTAI-Er    | weiterung                                           | . 251 |

|     |             | C.2.4    | Der Mult   | ti-Prozessor-Interrupt-Controller                   | . 252 |

|     |             |          | C.2.4.1    | Interrupt Prioritäten                               | . 253 |

|     |             |          | C.2.4.2    | Interrupt-Broadcasting                              | . 254 |

|     |             |          | L DV       | S                                                   | 055   |

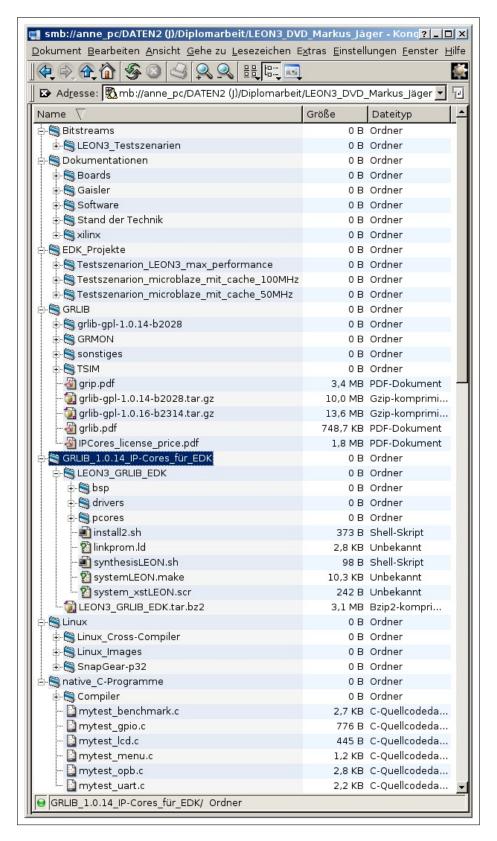

| D   |             |          | •          | D, zu dieser Arbeit                                 | 255   |

|     | D.1         |          |            | rzeichnis                                           |       |

|     | D.2         |          |            | en"-Verzeichnis                                     |       |

|     | D.3         |          | •          | -Verzeichnis                                        |       |

|     | D.4         | **       |            | chnis                                               |       |

|     | D.5         |          |            | _IP-Cores_für_EDK"-Verzeichnis                      |       |

|     |             | D.5.1    | Vorbereit  | tung eines Host-PC zur Benutzung der GRLIB-IP-Cores | . 259 |

|     |             | **       |            | hnis                                                |       |

|     | D.7         | "native  | _C-Progra  | amme"-Verzeichnis                                   | . 261 |

| Lit | eratu       | rverzeio | chnis      |                                                     | 262   |

| Ab  | bildu       | ngsver   | zeichnis   |                                                     | 267   |

| Tal | beller      | nverzeio | hnis       |                                                     | 269   |

| Zu  | Beac        | hten Ve  | erzeichnis | s                                                   | 271   |

| ۸h  | kürzı       | ından    |            |                                                     | 272   |

# **Einleitung**

Der praktische Einsatz von Field Programmable Gate Arrays (kurz FPGAs) hat in den letzten Jahren weiter zugenommen. Der Grund für diese rasante Entwicklung sind die Grundprinzipien der FPGAs.

So ist ein FPGA rekonfigurierbar. Dadurch kann bei entdeckten technischen Fehler die Funktionalität leicht und schnell korrigiert werden ohne einen Chip oder eine Platine aus dem Gerät auszutauschen. Gleichzeitig liegt auf einem FPGA echte Hardware-Parallelität vor.

Allein durch die Automobilindustrie erfährt der "FPGA-Markt" ein stetiges Wachstum. Zusätzlich erreichen die FPGAs, mit ihren steigenden Integrationsdichten und Taktfrequenzen, auch in Bereichen der Forschung immer größere Relevanz.

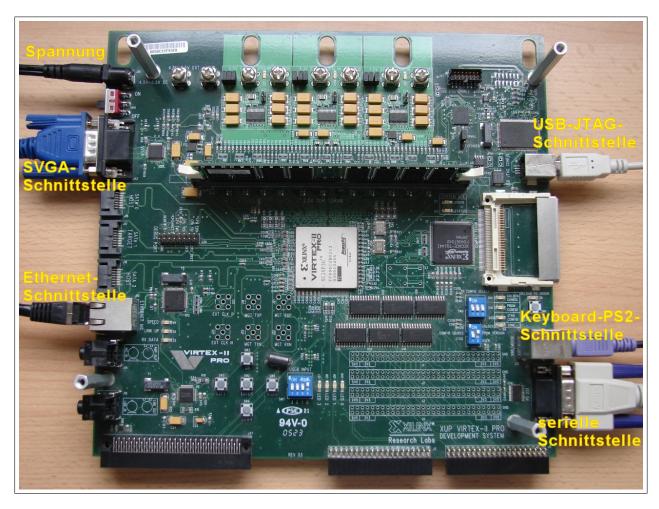

Bei der Betrachtung von FPGAs der Firma Xilinx, lassen sich interessante Trends der Entwicklung feststellen. In den letzten Jahren werden die FPGAs der Familie Virtex-II Pro, welche seit dem Jahr 2002 erhältlich sind, für Forschungszwecke eingesetzt. Die neuen FPGAs der Familie Virtex-5, seit 2006 erhältlich, haben entscheidende Verbesserungen, die ihren Einsatz noch vielseitiger machen.

So gibt es FPGAs der Familie Virtex-5 mit:

- ständig wachsender Kapazität an verwertbarer Logik (Virtex-5 Device: XC5VLX330T mit 51840 Slices)

- einer bis zu 550 MHz bereitgestellten Clock

- auf dem Chip zur Verfügung stehenden Block-RAMs bis zu einer maximalen Gesamtkapazität von 1.3 MB

• zusätzlichen Monitoren, zur Überwachung der Betriebstemperatur und Spannungsversorgung

Vor allem die zusätzlichen Möglichkeiten zur Überwachung des Betriebszustandes und die ständig sinkende Leistungsabnahme, machen den FPGA für eingebettete Systeme zukünftig noch attraktiver.

| FPGA Bezeichnung             | Anzahl |            |          |  |

|------------------------------|--------|------------|----------|--|

| TT GA Bezelchhang            | Slices | Block-RAMs | PowerPCs |  |

| Xilinx Virtex-II Pro Familie |        |            |          |  |

| XC2VP4                       | 3008   | 28         | 1        |  |

| XC2VP7                       | 4928   | 44         | 1        |  |

| XC2VP20                      | 9280   | 88         | 2        |  |

| XC2VP30                      | 13696  | 136        | 2        |  |

| XC2VP40                      | 19392  | 192        | 2        |  |

| XC2VP50                      | 23616  | 232        | 2        |  |

| XC2VP70                      | 33088  | 328        | 2        |  |

| XC2VP100                     | 44096  | 444        | 2        |  |

| Xilinx Virtex-4 Familie      |        |            |          |  |

| XC4VFX12                     | 5472   | 36         | 1        |  |

| XC4VFX20                     | 8544   | 68         | 1        |  |

| XC4VFX40                     | 18624  | 144        | 2        |  |

| XC4VFX60                     | 25280  | 232        | 2        |  |

| XC4VFX100                    | 42176  | 376        | 2        |  |

| XC4VFX140                    | 63168  | 552        | 2        |  |

| Xilinx Virtex-5 Familie      |        |            |          |  |

| XC5VLX30T                    | 4800   | 72         | 0        |  |

| XC5VLX50T                    | 7200   | 120        | 0        |  |

| XC5VLX85T                    | 12960  | 216        | 0        |  |

| XC5VLX110T                   | 17280  | 296        | 0        |  |

| XC5VLX220T                   | 34560  | 424        | 0        |  |

| XC5VLX330T                   | 51840  | 648        | 0        |  |

Tabelle 1.1: Xilinx Virtex Familien und ihre Kenngrößen [Xilfam1], [Xilfam2], [Xilfam3]

Tabelle 1.1 zeigt einen Ausschnitt der verbreitetsten Virtex-Familien. Dabei werden die, für diese

Arbeit relevanten, Kenngrößen (Slices<sup>1</sup>, Block-RAMs, PowerPCs) angezeigt. Es ist zu erkennen, dass nicht alle FPGAs mit einem PowerPC Prozessorkerne ausgeliefert werden. Trotzdem sind viele Benutzer bestrebt einen Prozessor auf einem beliebigen FPGA einzusetzen. Auf einem FPGA ohne PowerPC Prozessorkern ist dies nur durch einen Soft-Prozessor möglich.

Durch die ständig wachsende Anzahl der zur Verfügung stehenden Slices, auf einem FPGA, wird es immer lohnender ein komplettes System auf einem einzelnen FPGA unterzubringen. Dieses Konzept nennt sich System-on-Chip oder System-on-a-Chip (kurz SoC) und umfasst die Einbettung eines Systems mit zugehörigen SoC-Komponenten auf einem konfigurierbaren Chip. Solche SoC-Komponenten sind beispielsweise ein Prozessor, Register, Busse, Schnittstellen zu Speichern und anderen Peripheriekomponenten.

# 1.1 Motivation

Möchte ein Benutzer einen Prozessor auf einem FPGA einsetzen, auf dem kein kompakter Prozessorkern, wie der PowerPC, vorhanden ist, so kann dies nur mit einem Soft-Prozessor geschehen. Die Firma Xilinx bietet eine Bibliothek von Intellectual Properties (deut.: geistige Eigentümer, kurz IPs) an. Diese IPs sind einzelne SoC-Komponenten, mit denen es bereits möglich ist ein komplettes SoC zu erstellen. Diese Komponenten werden auch IP-Cores genannt. Ein besonderer IP-Core ist der MicroBlaze-Prozessor. Dies ist ein Soft-Prozessor, der den fehlenden kompakten PowerPC Prozessorkern ersetzen kann. Die Bezeichnung Soft-Prozessor oder Softcore meint, dass ein IP-Core, mit seinem Verhalten, in einer Hardware Description Language (deut.: Hardwarebeschreibungssprache, kurz HDL) vorliegt und nur durch den Prozess der Synthese, mit einer entsprechenden Software, auf einem konfigurierbaren Chip als Hardware betrieben werden kann. Der Nachteil der Xilinx Bibliothek ist allerdings, dass an die Verwendung deren IP-Cores Lizenzbedingungen geknüpft sind. Diese Lizenzbedingungen machen den Einsatz von Xilinx-IP-Cores, wie dem MicroBlaze-Prozessor, oft unflexibel oder teuer.

Es werden IP-Cores benötigt, welche möglichst flexiblen Lizenzbedingungen unterliegen und in einsehbarem VHDL-Code vorliegen. Mit diesem IP-Cores soll es möglich sein, alle wichtigen IP-Cores der Xilinx Bibliothek zu ersetzen.

# 1.2 Inhalt der Arbeit

Diese Arbeit beschäftigt sich mit der Erstellung eines kompletten SoC. Das Ziel dieser Arbeit ist, alle SoC-Komponenten in vollständigen, ungeschützten VHDL-Code vorliegen zu haben. Alle

<sup>&</sup>lt;sup>1</sup>Laut [Xilfam3] ist zu Beachten, dass ab der Virtex-5 Familie ein Slice aus 4 LUTs und 4 flip-flops besteht. Bis zur Virtex-4 Familie waren es 2 LUTs und 2 flip-flops.

Komponenten, einschließlich des Prozessors, werden unter Beachtung der GNU General Public License (kurz GPL) beliebig veränderbar und frei verwendbar sein. Für ein SoC aus diesen freien Komponenten soll das Betriebssystem Linux nutzbar gemacht werden.

Die Eigenschaft der IP-Cores der GPL zu unterliegen wird in dieser Arbeit mit dem Adjektiv "frei" bezeichnet.

Zur Synthese des VHDL-Codes werden die Werkzeuge Xilinx ISE 8.2i (kurz ISE) und Xilinx-EDK 8.2i (kurz EDK) genutzt. Die Besonderheit des Werkzeugs EDK ist es, mit der Xilinx-IP-Core-Bibliothek ausgestattet zu sein. Die neuen, freien IP-Cores werden einen vollständigen Ersatz der Xilinx-IP-Core-Bibliothek bilden und werden ebenfalls, wie die IP-Cores der Xilinx Bibliothek, in den Workflow des EDK eingebunden.

Als Quelle freier IP-Cores dient die von der Firma Gaisler Research (kurz GR) bereitgestellte Gaisler Research Library (kurz GRLIB). Diese Bibliothek beinhaltet vollständig zugängliche IP-Cores, die der oben genannten GPL unterliegen. Unter anderem befindet sich in der GRLIB eine VHDL-Entity eines Soft-Prozessors namens LEON3.

Als Ergebnis dieser Arbeit steht die Verbindung der freien GRLIB-SoC-Komponenten mit der Benutzerfreundlichkeit des Xilinx Werkzeugs EDK.

## 1.2.1 Gliederung der schriftlichen Ausarbeitung

Die schriftliche Ausarbeitung dieser Arbeit ist in folgende Abschnitte gegliedert.

In **Kapitel 1** der Arbeit werden die Lizenzrechtlichen Bedingungen (Kapitelpunkt 1.3) der Xilinx-IP-Cores und der GRLIB-IP-Cores näher erläutert, welche dann die Motivation dieser Arbeit untermauern werden.

Das **Kapitel 2** bereitet die Grundlagen auf, welche benötigt werden, um dem weiteren fachlichen Inhalt der Arbeit folgen zu können und um dargestellte Probleme sowie gewählte Lösungen nachvollziehbar zu machen.

Es wurden spezielle Schwerpunkte gelegt auf allgemeine Möglichkeiten der Realisierung von Systems-on-Chip (Kapitelpunkt 2.1) auf FPGAs und die dazu verwendbaren Werkzeuge von Xilinx. In Kapitelpunkt 2.2.2 werden alle wichtigen EDK-Konstrukte vorgestellt und erklärt, welche später in Kapitel 5, dem eigentlichen Kern der Arbeit, benutzt wurden, um die Einbindung der GRLIB-SoC-Komponenten in das Werkzeug EDK zu realisieren. Dadurch erhält der Leser einen Einblick in die eigentlichen Möglichkeiten sowie das Potential der Software EDK und es werden später geschilderte Probleme besser verständlich.

**Kapitel 3** vermittelt einen Einblick in den aktuellen Stand der Technik. Es werden vergangene Arbeiten vorgestellt, in denen die GRLIB zum Einsatz gekommen ist. Dieses Kapitel ordnet die Arbeit in ein technisches Umfeld ein. Kapitelpunkt 3.1 beschäftigt sich ausführlich mit der Gaisler

Research IP Library. In den Kapitelpunkten 3.1.2 bis 3.1.6 wird der Zustand beleuchtet in dem die GRLIB offiziell zu erhalten ist. Es wird ein Einblick in die Verzeichnisstruktur und die Bibliotheken gegeben. Zusätzlich wird der Arbeitsablauf, auch genannt "Workflow", der GRLIB vorgestellt, wie er von der Firma GR vorgegeben wird um ein SoC mit dem LEON3-Prozessor zu synthetisieren.

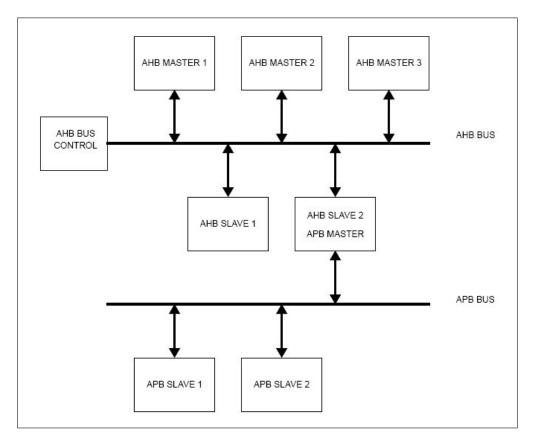

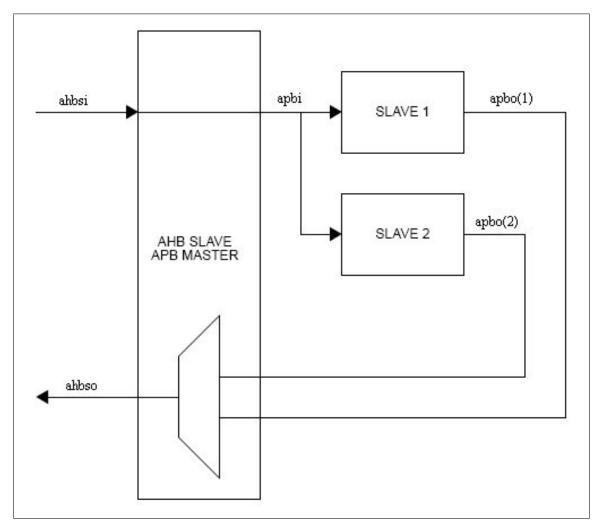

In Kapitelpunkt 3.1.5 werden die Modelle der GRLIB im Detail vorgestellt. Als Kern dieser Vorstellung stehen die Designumsetzungen der in der GRLIB verwendeten Busse. Diese sind der Advanced High-performance Bus (kurz AHB) und der Advanced Peripheral Bus (kurz APB). Der AHB und der APB bilden das Grundgerüst eines jeden LEON-Systems.

Der LEON3-Prozessor spielt hier eine untergeordnete Rolle, da er nur ein Master des AHB ist. Der LEON3-Prozessor ist für die Grundfunktionalität eines GRLIB Systems unwichtig. Er könnte ebenso gut durch eine einfache Steuereinheit ersetzt werden.

Um die neuen Busse in ihrer Umgebung besser zu verstehen werden Analogien, zum bekannten MicroBlaze-System der Firma Xilinx, deutlich gemacht.

In Kapitelpunkt 3.1.5.4 wird erklärt wie Gaisler Research seiner GRLIB eine technologische Unabhängigkeit verliehen hat und es wird erläutert wie diese Unabhängigkeit in EDK fortgesetzt wird. Die GRLIB ist somit für viele FPGAs verschiedenster Firmen, wie Xilinx und Altera, ausgelegt.

In Kapitelpunkt 3.1.6 werden weitere Werkzeuge genannt und erklärt, welche während des intensiven Umgangs mit einem LEON-System benötigt werden.

Dazu gehört der Compiler, zum Kompilieren nativer C-Programme für den LEON3-Prozessor, der Gaisler Research Debugmonitor (kurz GRMON) für das Debugging eines auf dem FPGA-Board befindlichen Systems und das Werkzeug SPARC-Simulator (kurz TSIM) zur Simulation eines kompletten LEON-Systems auf der Konsole. Hier werden zum besseren Verständnis wieder Analogien und Vergleiche zum MicroBlaze-System gezogen.

In **Kapitel 4** wird der Ansatz der Arbeit dargestellt. Es wird kurz auf die Ausgangssituation eingegangen und dann alle Ansätze und Vorgehensweisen, zur Erreichung der Ziele dieser Arbeit, vorgestellt und begründet.

**Kapitel 5** umfasst die eigentlichen Leistungen der Arbeit. Es wird eine Schilderung der Ausgangssituation vorgenommen und die Ideen zur Umsetzung der Ziele besprochen. In Kapitelpunkt 5.2 wird beschrieben wie die Einbindung eines einzelnen allgemeinen IP-Cores, der GRLIB, in das EDK erfolgt ist. Dazu werden die in Kapitel 2 erklärten Grundlagen benötigt, da die dort aufgelisteten Konzepte benutzt wurden, um eine saubere Einbindung eines IP-Cores in das EDK zu bewirken.

In Kapitelpunkt 5.2 werden bei diesem Prozess aufgetretene Probleme und Besonderheiten besprochen und die Entscheidung zur Lösung begründet und diskutiert. Ein großes Problem hinsichtlich Constraints trat hier bei den IP-Cores Gaisler Research DDR RAM und Gaisler Research Ethernet

auf. Dieses Problem wurde mit Hilfe der Tool Command Language (kurz Tcl) und Synthese Parametern für das Tool XST gelöst.

Unter dem Begriff "Constraints" (deut.: Einschränkung) werden hier Bedingungen bezeichnet, welche ein IP-Core bei der Synthese erfüllen muss. Solche Bedingungen sind beispielsweise Forderungen an zeitliches Verhalten der Schaltsignale, auch "Timing" genannt.

Um eine komplette komfortable Einbindung der GRLIB-SoC-Komponenten in das EDK zu erreichen wurden zusätzlich zwei Bridges konstruiert. Diese "AHB zu OPB" und "AHB zu LMB"-Bridges sollen hier in ihrem Design ausführlich vorgestellt werden. Zusätzlich werden Gründe für die Erstellung und sich erschließende Möglichkeiten, durch Erstellung dieser Bridges geliefert. Die genaue Beschreibung dieses Sachverhaltes, sowie Begriffserklärungen, befinden sich im Kapitelpunkt 5.4.

In Kapitelpunkt 5.5 werden ausgewählte IP-Cores der GRLIB besprochen, welche verstanden werden müssen, um ein LEON3-System benutzen zu können. Es sollen hier nicht die genauen Funktionsweisen der IP-Cores erläutert, sondern Bedienungsbesonderheiten erklärt werden, welche sich durch die Einbindung der IP-Cores in das EDK ergeben haben.

Das **Kapitel 6** befasst sich mit der Erstellung nativer C-Programme für ein LEON3-System. Speziell der Aufbau eines C-Programms für den LEON3 unterscheidet sich von den Programmen für einen MicroBlaze-Prozessor. Dies liegt nicht zuletzt daran, dass für den LEON3-Prozessor keine so umfangreiche Softwarebibliothek vorhanden ist, wie für den MicroBlaze-Prozessor.

In diesem Kapitel wird das allgemeine Vorgehen erläutert, wie der LEON3-Prozessor Bus-Transfers einleiten kann.

**Kapitel 7** beschäftigt sich mit einer Linux Distribution namens "SnapGear". Das SnapGear-Linux ist speziell zur Ausführung auf einem SoC der GRLIB gedacht und kann mit dem LEON3-Prozessor betrieben werden.

Das SnapGear-Linux bietet eine umfassende Treiberdatenbank speziell für die SoC-Komponenten der GRLIB. Der Kapitelpunkt 7.2.1 beschreibt die Möglichkeiten zur Konfigurationen eines SnapGear-Linux-Kernels für ein beliebig gegebenes LEON3-System.

In Kapitelpunkt 7.2.2 wird beschrieben, wie es theoretisch möglich ist, eigene SnapGear-Linux Treiber, für beliebige LEON3-Systemkomponenten zu erstellen und in SnapGear-Linux einzubinden. Eine praktische Umsetzung dieses Prozesses wurde allerdings in dieser Arbeit nicht durchgeführt.

In **Kapitel 8** werden alle Ergebnisse der Arbeit zusammengefasst. Es werden alle erreichten Ziele aber auch Grenzen dieser Arbeit aufgezählt.

Da der LEON3 ein umfassender Soft-Prozessor ist, wird er, in Kapitelpunkt 8.3, mit dem MicroBlaze-Prozessor hinsichtlich seiner Größe, Performance und benötigten Ressourcen verglichen. Zusätzlich soll im Kapitelpunkt 8.4 ein Performance-Vergleich eines MicroBlaze-SoC und eines LEON3-SoC mit jeweils maximal möglicher Leistung stattfinden.

Durch **Kapitel 9** sollen Lösungsmöglichkeiten gezeigt und Anregungen gegeben werden, in wie weit sich Verbesserungen zukünftig umsetzen lassen. Von manchen Verbesserungen wurde in dieser Arbeit Abstand genommen, da sie teilweise mit Veränderungen des, von Gaisler Research erstellten, VHDL-Codes verbunden sind. Würden diese Änderungen vorgenommen, so müssten umfassende Tests erfolgen, um die Funktionalität und Fehlerfreiheit zu gewähren.

Des weiteren wird die GRLIB ständig aktualisiert und gefundene Bugs werden von der Firma GR ständig behoben. Deshalb soll hier beschrieben werden wie eine neue Version der GRLIB übernommen werden kann und welche Besonderheiten bei diesem Prozess zu beachten sind.

#### Anhänge

Der **Anhang A** bietet Ergänzungen zum Kapitelpunkt 3.1, welche nicht für den Leitfaden dieser Arbeit wohl aber für den Umgang mit der GRLIB benötigt werden.

Der Anhang B widmet sich ausführlich dem LEON3-Prozessor. Es wird allgemein die SPARC-Architektur erläutert, nach der der LEON3 konstruiert ist. Im Anhang B.2 werden viele Fakten des LEON3 beleuchtet, die ein gutes Verständnis des Prozessors erzeugen. Besprochen werden unter anderem die Integer-Unit, die Floating-Point Unit, das Cache-System und die Memory Managment Unit. Besonderes Augenmerk wird auf die Memory Managment Unit des LEON3 gelegt, da diese nicht im MicroBlaze-Prozessor vorhanden ist.

In **Anhang** C soll der sehr umfangreiche LEON3-Prozessor aus der Sicht der eingebetteten Systeme (engl.: embedded systems) betrachtet werden. Als Besonderheit bietet die Firma Gaisler Research äußerst Fehlertolerante IP-Cores an, welche mit Schutz- und Fehlerkorrekturmechanismen versehen wurden, um Betriebsbedingungen stand zu halten bei denen Eingebettete Systeme vorkommen können.

Dazu gehört auch ein fehlertoleranter LEON3 (kurz LEON3FT). In Kapitelpunkt C.2 wird die Echtzeit-Anforderung auf das LEON3-System betrachtet und für den LEON3 erhältliche Realtimeoperatingsystems (kurz RTOS) vorgestellt. Als sehr wichtige Komponente soll hier der Interrupt-Controller des LEON3-Systems in seiner detailierten Funktionsweise besprochen werden.

**Anhang D** stellt eine Zusammenfassung dar, wie die DVD, zu dieser Diplomarbeit, gehandhabt wird. Die DVD beinhaltet beispielsweise alle in das EDK eingebundenen IP-Cores. Soll ein neues EDK-Projekt mit der GRLIB ausgestattet werden, so können die Daten auf der DVD benutzt werden.

#### Leitfaden der Arbeit

**Kapitel 2** (Grundlagen) und **Kapitelpunkt 3.1** (Die GRLIB) stellen Vorimplementierungen vor, die zu Beginn der Arbeit bereitstanden. Diese Vorimplementierungen werden in **Kapitel 5** (Einbindung der GRLIB in das EDK), dem Implementierungskapitel dieser Arbeit, ausgenutzt, um eine benutzerfreundliche Synthese von SoCs, mit Hilfe der GRLIB-IP-Cores, zu erreichen.

Nachdem die Hardware synthetisiert werden kann, wird in **Kapitel 6** (Native C-Programme für ein LEON3-SoC) erklärt wie erste, einfache Software auf einem LEON3-System ausgeführt werden kann. In **Kapitel 7** (Linux auf dem LEON3-System) wird aufbauend erläutert, wie eine komplexere Software, wie ein Linux-Betriebssystem, auf einem LEON3-System ausgeführt wird.

# 1.3 Lizenzrechtliche Bedingungen und Probleme

Dieser Kapitelpunkt stellt die Lizenzbedingungen der Xilinx-IP-Core-Bibliothek und der GRLIB gegenüber. Daraus ist erkennbar, warum die GRLIB eine Alternative zu den IP-Cores der Firma Xilinx ist.

## 1.3.1 Xilinx, Inc. CORE SITE LICENSE AGREEMENT

Die Firma Xilinx stellt mit ihrer Software EDK ein umfangreiches Werkzeug zur Verfügung, um Eingebettete Systeme und SoC Lösungen zu erstellen.

In der Version 8.2i des EDK liegt beispielsweise der Soft-Prozessor MicroBlaze in der Version 5.00.c vor. Aus rechtlichen Gründen veröffentlicht die Firma Xilinx den MicroBlaze allerdings nur in verschlüsseltem VHDL-Code. Andere IP-Cores der "Communication"-Klasse, wie der OPB Ethernet oder der OPB Uart 16550 IP-Core sind, neben den normalen Lizenzbedingungen, zusätzlich mit einem zeitlichen Verfall der Nutzungsrechte versehen.

Grundsätzlich unterliegen alle IP-Cores, welche sich in der Xilinx Bibliothek des EDK befinden, dem Xilinx, Inc. CORE SITE LICENSE AGREEMENT.

Aus akademischen Gründen soll an dieser Stelle ein Auszug aus diesen Lizenzvereinbarungen erfolgen. Es wird allerdings darauf hingewiesen, dass dieser Auszug kein Ersatz gegenüber dem original Dokument darstellt. Ebenfalls sind Ungenauigkeiten in der Formulierung, welche von der Übersetzung herrühren, nicht ausgeschlossen.

#### Kapitel 1 Einleitung

Die Firma Xilinx definiert den Begriff "Intellectual Property Rights" mit den auszugsweisen Punkten:

- (i) Rechte assoziiert mit der Arbeit der Autoren

- (iv) Patent- und Designrechte des gewerblichen Eigentums

- (v) alle weiteren Rechte am geistigen Eigentum

Dies sind drei Punkte der Begriffsdefinition und deren, im Xilinx Lizenzdokument verwendeten, römische Gliederungspunkte. Es sind noch weitere Punkte genannt, welche hier aber nicht von Belang sein sollen.

Die eigentliche Lizenz umfasst auszugsweise Äußerungen wie:

Nach Zahlung der anwendbaren Gebühren, bewilligt Xilinx dem Lizenznehmer eine nichtexklusive, nicht übertragbare, widerrufbare Lizenz, welche folgende Genehmigung umfasst:

(i) Der Lizenznehmer darf das lizenzierte Material (IP-Cores) an den lizenzierten Örtlichkeiten zur Erstellung, Simulation und Implementierung von Chipdesigns benutzen. Dabei sind nur FPGAs der Firma Xilinx zur Konfiguration gestattet.

Es ist also nicht gestattet FPGAs anderer Firmen als Xilinx mit den erstellten Designs aus Xilinx-IP-Cores zu konfigurieren. Dies ist ein grundlegender Unterschied zu den Rechten der GRLIB, die das Ziel haben eine technologische Unabhängigkeit zu erreichen.

Zusätzlich nennt die Firma Xilinx noch Einschränkungen zur Benutzung:

- Die Benutzung des lizenzierten Materials auf nicht Xilinx FPGAs ist verboten.

- Das Erstellen von Kopien, des lizenzierten Materials, ist nur mit starken Einschränkungen gestattet. Weiterführende Erstellungen von Kopien sind nur mit Genehmigung der Firma Xilinx erlaubt.

- Der Lizenznehmer darf kein lizenziertes Material an Dritte weitergeben ohne Genehmigung der Firma Xilinx. Gestattet ist allerdings das Weitergeben von Bitstreams, zur Konfiguration von Xilinx FPGAs und Speicherung, an Dritte.

- Werden Xilinx-IP-Cores mit anderen Technologien, wie Software, dritter Parteien in Verbindung gebracht, ist der Lizenznehmer verpflichtet, Lizenzen Dritter zu beschaffen.

- Es ist dem Lizenznehmer nicht gestattet, ohne Genehmigung der Firma Xilinx, Resultate eines Benchmarks, des lizenzierten Materials zu veröffentlichen.

Es ist zu erkennen, dass erhebliche Einschränkungen bei der Benutzung der Xilinx-IP-Cores vorliegen. Wobei die obige Auflistung, der Lizenzrechtlichen Bedingungen, nicht vollständig ist. Diesen Bedingungen sind in der Forschung sehr hinderlich, da es dort nötig ist, viele Experimente mit Designs durchzuführen, welche empfindlich an die Grenzen der Lizenzrechte stoßen können.

# 1.3.2 GNU General Public License (GPL)

Eine Alternative stellt hier wiederum die GRLIB dar. Zur verantwortungsvollen Benutzung der GRLIB werden hier einige Auszüge der GNU General Public License (kurz GPL) diskutiert, welcher die GRLIB unterliegt. Es sei wieder gesagt, dass diese Auszüge kein Ersatz des vollständigen GPL Lizenzdokuments sind. Wenn in diesem Kapitelpunkt von Software gesprochen wird, so ist damit auch die GRLIB gemeint, obwohl mit ihr Hardware synthetisiert wird.

Die GNU General Public License hat es sich zum Ziel gemacht die Freiheiten der Benutzer von Produkten, die der GPL unterliegen, zu bewahren und nicht zu beschneiden. Dadurch wird sichergestellt, dass die Software frei ist für alle ihre Nutzer und Folgenutzer.

Wenn in der GPL von freier Software gesprochen wird, wird die Freiheit des Gebrauches gemeint, nicht aber die Kostenfreiheit. Es ist also erlaubt eine Gebühr auf die Benutzung einer Software zu erheben. Dazu muss die besagte Software im Vergleich zur ursprünglichen GPL Software verändert worden sein.

#### Einige Richtlinien der GPL sind auszugsweise:

- Benutzer von GPL Software haben das Recht die Software frei zu verwenden und zu verändern, müssen aber die Veränderungen ebenfalls an die GPL binden.

- Auf die Veränderung der vorhergehenden Version muss hingewiesen werden.

- Dem Lizenznehmer ist es erlaubt die Software beliebig zu kopieren und zu verbreiten. Vorraussetzung für diese Erlaubnis ist ein an die Kopie auffällig angebrachter Urheberrechtsvermerk und ein Verzicht auf Garantie.

Diese drei Punkte der GPL haben auch für die vorliegende Arbeit große Bedeutung. Während der Umsetzung der Arbeit war es nötig Veränderungen an der GRLIB vorzunehmen, um die Einbindung der IP-Cores in das EDK fehlerfrei und benutzerfreundlich zu ermöglichen.

Aufgrund der GPL werden somit alle Veränderungen genau beschrieben und deren Folgen deutlich gemacht. Ebenfalls sind die Veränderungen öffentlich einsehbar.

## 1.3.3 Zusammenfassung

Durch die Ausführungen des Kapitelpunktes 1.3 ist deutlich geworden, dass die GRLIB in Verbindung mit der GPL eine Alternative zu den IP-Cores der Firma Xilinx ist.

Es steht nun der Weg offen die SoC-Komponenten der GRLIB als IP-Cores in das Werkzeug EDK einzubinden und beide Vorteile miteinander zu verbinden.

Die Vorteile der GRLIB sind ihre freien SoC-Komponenten und die Vorteile des Xilinx-EDK sind die benutzerfreundlichen und übersichtlichen Möglichkeiten ein vollständiges SoC zu synthetisieren und die zugehörige Software zu kompilieren.

Das Xilinx-EDK und die GRLIB arbeiten "boardorientiert". Das bedeutete, dass der Benutzer vor der Erstellung eines SoC entscheiden muss, auf welchem FPGA-Board das Design betrieben werden soll. Durch diese Entscheidung werden beispielsweise im EDK die Pinbezeichnungen festgelegt und SoC-Komponenten, die nicht benutzt werden können, ausgeblendet.

Die GRLIB arbeitet nach dem selben Prinzip. Da die GRLIB allerdings viel weniger FPGA-Boards als das EDK unterstützt wird die Erstellung eines SoC bei Benutzung eines nicht bekannten Boards erheblich erschwert. Dies ist ein weiterer Grund die Vorteile der beiden SoC-Lösungen zu verbinden.

# Grundlagen

Wurden früher noch einzelne integrierte Schaltkreise auf einer Platine zu einem vollständigen eingebetteten System verbunden, so wird heute das Design des eingebetteten Systems mit einer HDL beschrieben, dann synthetisiert und auf einen einzelnen konfigurierbaren Chip geladen. Ein solches Werkzeug mit dem es möglich ist, den vollständigen Entwicklungsprozess eines SoC durchzuführen ist beispielsweise die Software Xilinx-EDK.

Die Vorteile von SoCs sind ihr geringer Platzbedarf, in den einzelnen Geräten, und die verhältnismäßig kurze Zeit in der sie entwickelt werden können, um dann vermarktet zu werden, auch genannt "time to market". Die Umsetzung der SoCs in Hardware ist beispielsweise auf CMOS Schaltkreisen oder FPGAs möglich.

Der Zusatz der Rekonfigurierbarkeit von FPGAs hat den Vorteil, dass sich schnelle und einfache Support-Möglichkeiten bieten. Dadurch kann ein Fehler im SoC-Desgin durch eine Rekonfiguration, mit einem im Werk erstellten neuen Bitstream, schnell behoben werden. Auch das aufspielen eines neuen Updates ist meist ohne das Austauchen von Gerätekomponenten möglich.

# 2.1 System-on-Chip (SoC)

Die Besonderheit der SoCs ist, wie der Name sagt, das vollständige Unterbringen eines ganzen Mikro-Controllers auf einem einzigen Chip. Da in dieser Arbeit mit einem FPGA als Chip gearbeitet wurde, werden im Folgenden nur SoCs auf FPGAs betrachtet.

Zu den Komponenten eines SoC gehören alle denkbaren Komponenten, welche in Hardware realisierbar sind. SoCs bestehen aus dem **Mikrop**rozessor (kurz  $\mu$ P, CPU), einem oder mehreren Bussen und Schnittstellen zu Speichern und Eingabe/Ausgabe (kurz E/A) Komponenten. Gegebenenfalls können sich zusätzliche, kleine aber schnelle, Speichermodule direkt auf dem FPGA

befinden. In diesem Fall wäre nicht nur die Schnittstelle zum Speicher, sondern auch der Speicher "on Chip".

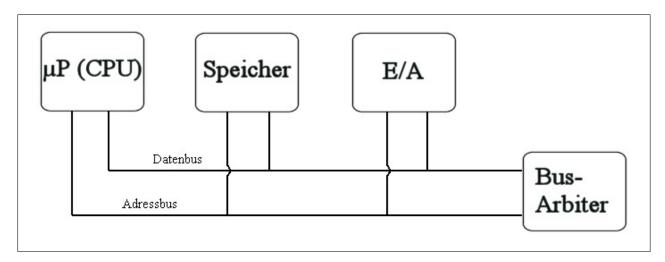

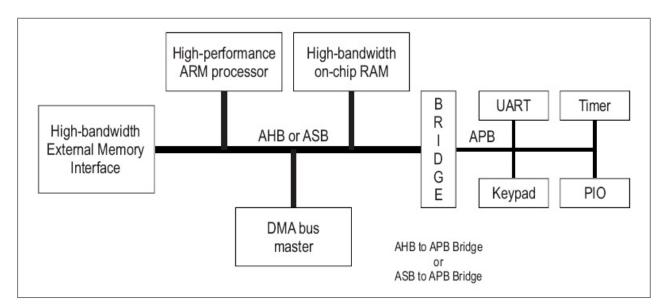

Abbildung 2.1: Blockschaltbild eines SoC

Abbildung 2.1 Zeigt das Blockschaltbild eines typischen SoC, mit allen Standardkomponenten. Die Linien des Daten- und Adressbus bilden den gesamten Bus.

## 2.1.1 Der Mikroprozessor ( $\mu$ P)

Der Mikroprozessor eines SoC ist wie bei einem **P**ersonal Computer (kurz PC) ein wichtiger Bestandteil des Systems. Um Bezug zu den zukünftig in dieser Arbeit auftauchenden Begriffen zu halten, wäre der  $\mu$ P in der GRLIB, der LEON3-Prozessor und in der Xilinx-IP-Core-Bibliothek der MicroBlaze-Prozessor.

Wie jede CPU, eines Personal Computers, ist der  $\mu P$  in der Lage als zentrale Steuereinheit zu arbeiten. Er liest Befehle, auch Operationen genannt, aus dem Programmspeicher in seine Register, decodiert sie und führt die Befehle aus. Anschließend schreibt der  $\mu P$  berechnete Daten in den Systemspeicher oder führt andere Operationen aus.

Eine wichtige Unterscheidung, welche im letzten Satz geprägt wurde, ist die Unterscheidung zwischen Programmspeicher und Systemspeicher.

**Der Programmspeicher** ist im allgemeinem Sinn ein Datenspeicher. Er speichert normale Daten welche vom  $\mu$ P als Programmdaten oder Befehle interpretiert werden. Im physikalischen Sinne sind Datenspeicher integrierte Schaltungen, welche aus sich wiederholenden aneinander geketteten Speicherzellen bestehen.

**Der Systemspeicher** bezeichnet keinen Speicher zum Speichern großer Datenmengen. Zum Systemspeicher gehören auch die Register beliebiger SoC-Komponenten. Diese Register können sich beispielsweise in E/A Komponenten befinden, in Prozessoren oder sogar in Bus-Arbitern. Register werden zur schnellen Kommunikation zwischen den SoC-Komponenten

genutzt. Schreibt der  $\mu$ P ein Datum in das Register einer E/A-Komponente, beispielsweise in die Controllerkomponente für einen Monitor, so weiß die Controllerkomponente, dass sie den Monitor so ansteuern muss, damit er ein Zeichen anzeigt.

Als Systemspeicher wird der gesamte Systemadressraum bezeichnet, über den Zugriff auf alle Register und Datenspeicher erlangt werden kann.

Für den  $\mu$ P ist es somit kein Unterschied, ob er mit einem Datum ein Ergebnis in den Speicher schreiben will oder eine E/A-Komponente steuern möchte.

Für den  $\mu$ P eines SoC gilt, genauso wie für die CPU eines PC, dass er einen komplexen Befehlssatz besitzen kann, ein sogenannter CISC-Prozessor (Complex Instruction Set Computer). Dagegen besitzt ein RISC-Prozessor (Reduced Instruction Set Computer) einen kleinen, einfachen Befehlssatz.

Speicher und E/A-Komponenten sind ebenfalls SoC-Komponenten wie der  $\mu$ P. Sie sind über den Bus mit einander verbunden und können so Daten austauschen.

SoC-Desgins werden wie  $\mu$ C-Systeme gehandelt, können allerdings umfangreichere Ausmaße annehmen, vergleichbar mit einem normalen PC. Diese Flexibilität ist meist nur von Einstellungen abhängig, welche vor der Synthese der SoCs im VHDL-Code festgelegt werden müssen.

Eine Vereinfachung eines SoC kann sogar so weit gehen, dass sich in dem SoC kein konventioneller  $\mu$ P mehr befindet, sondern eine rudimentäre Steuereinheit. Für einfache  $\mu$ C reicht solch eine einfache Steuereinheit manchmal aus. Bei eingebetteten Systemen wird eine derartige Vereinfachung gezielt angestrebt, da eine einfache Steuereinheit erheblich weniger Chipfläche und elektrische Leistung benötigt. Außerdem kann eine kleine Steuereinheit viel schneller getaktet werden.

Aus dem Grund der Vereinfachung des  $\mu P$  zur Steuereinheit ist es gerechtfertigt den  $\mu P$  nicht mehr als zentrale Einheit eines SoC zu bezeichnen. An die Stelle der zentralen Einheit tritt in einem SoC oder  $\mu C$  das Bussystem.

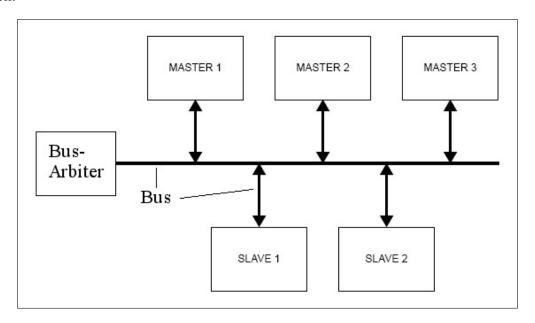

# 2.1.2 Das Bussystem

Ein Bussystem besteht aus dem Bus und dem Bus-Arbiter. In den SoCs dieser Arbeit besteht der Bus aus den Daten- und Adressbus sowie anderen Steuerleitungen. Der Bus wird im wesentlichen durch die Verbindung der SoC-Komponenten bestimmt. Bei der technischen Umsetzung dieser Verbindungen wird von Verdrahtung gesprochen.

Der Bus-Arbiter ist eine kleine Regeleinheit, welche im wesentlichen angibt welche an den Bus angeschlossene SoC-Komponente mit Welcher kommunizieren darf. An das Bussystem eines SoC werden erhebliche Anforderungen gestellt.

Zu diesen Anforderungen gehören:

- Hohe Geschwindigkeit und Datendurchsatzrate von einer zur anderen SoC-Komponente

- Hohe Zuverlässigkeit der Kommunikation und entsprechend schnelle Reaktion beim Auftreten eines Fehlers, während der Kommunikation von SoC-Komponenten

- Zusätzliche Konfigurationsmöglichkeiten zur Festlegung der Daten- und Adressbusbreite sowie Festlegung der "Arbitrierungs-Strategie"<sup>1</sup>

- Hilfreich, bei der Steuerung eines SoC durch den μP, ist auch die Möglichkeit, die Konfigurationsinformationen der SoC-Komponenten über den Bus zugänglich zu machen. Dieser Prozess wird auch Plug and Play genannt.

Die Busse eines GRLIB LEON3-Systems sind der Advanced High-performance Bus (kurz AHB) und der Advanced Peripheral Bus (kurz APB). Während die Busse der Xilinx SoC-Komponenten Bibliothek, für den MicroBlaze-Prozessor, Local Memory Bus (kurz LMB) und On-Chip Peripheral Bus (kurz OPB) genannt werden.

#### **Bus-Kommunikation**

Die Kommunikation der SoC-Komponenten über den Bus erfolgt nach einem ganz bestimmten Muster. Eine SoC-Komponente übergibt zur Kommunikation ein Datum an den Bus mit einer zugehörigen Adresse des Systemspeichers, an den das Datum geschrieben werden soll. Die Adresse kann dabei auch im Adressbereich eines Datenspeichers liegen.

Der Bus-Arbiter übernimmt die Daten- und Adress-Information, speichert sie in einem seiner eigenen Register und leitet eine Regelung auf dem Bus ein. Diese Regelung soll bewirken, dass die ursprünglichen Daten an ihrer Zieladresse ankommen und von einer anderen SoC-Komponente empfangen werden.

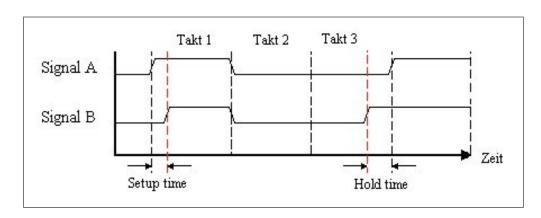

Das vorgeschriebene Muster der Kommunikation von SoC-Komponente zum Bus und umgekehrt wird als Protokoll bezeichnet. Grundlage der meisten Protokolle ist die Vier-Zyklus-Kommunikation (engl.: four-cycle handshake). Die SoC-Komponenten verfügen dabei nicht nur über eine Daten- und Adressleitung sondern zusätzlich über eine "Anfrage" und "Bestätigungs"-Leitung.

<sup>&</sup>lt;sup>1</sup>Unter den Begriff "Arbitrierungs-Strategie" versteht man einen Entscheidungsalgorithmus, der gewährleistet, dass nach einer "fairen" Wahrscheinlichkeitsverteilung alle vorhandenen SoC-Komponenten Zugriff auf den Bus erlangen können.

Die Durchführung zur Kommunikation ist folgendermaßen:

- Schritt 1: SoC-Komponente A aktiviert die "Anfrage"-Leitung, wenn sie Daten an eine Adresse senden will und die Daten zur Sendung am Bus bereit liegen.

- **Schritt 2:** SoC-Komponente B aktiviert die "Bestätigungs"-Leitung, wenn sie bereit ist Daten anzunehmen.

- **Schritt 3:** Ist die Datenübertragung abgeschlossen, d.h. SoC-Komponente B hat die Daten erfolgreich in ein eigenes Register geschrieben, so deaktiviert SoC-Komponente B die "Bestätigungs"-Leitung.

- **Schritt 4:** Erkennt SoC-Komponente A die Deaktivierung der "Bestätigungs"-Leitung so deaktiviert SoC-Komponente A die "Anfrage"-Leitung.

Danach ist der Bus wieder bereit neue Daten zu übertragen.

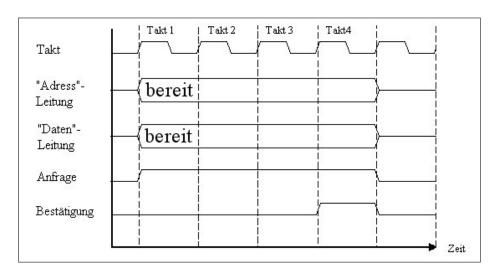

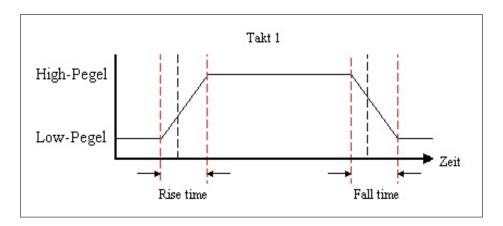

Abbildung 2.2: Timingdiagramm der Vier-Zyklus-Kommunikation

Abbildung 2.2 zeigt eine typische Vier-Zyklus-Kommunikation. Schritt 1 des obigen Kommunikationsmusters geschieht zu Anfang des Takt 1. Schritt 2 zu Beginn des Takt 4. Und die Schritte 3 und 4 geschehen am Ende von Takt 4.

Die gesamte Aufgabe eines Bussystems ist zusammenfassend zu beschreiben als das "Multiplexen" von Leitungen zwischen den SoC-Komponenten. Ist das Multiplexen geschehen, so signalisiert das Bussystem an die SoC-Komponenten die Bereitschaft zur Datenübertragung.

# 2.1.3 Werkzeuge zur Erstellung von SoCs

Wie bereits erwähnt ist es nötig SoC-Komponenten in VHDL zu beschreiben. Eine weitere Möglichkeit wäre es die HDL "Verilog" zu verwenden, was aber in dieser Arbeit nicht durchgeführt

wird, da die GRLIB in VHDL vorliegt.

Das grundlegende Element in VHDL, um Hardware zu beschreiben, ist die Entity (deut.: Entität). Die Entity ist ein VHDL-Konstrukt, das es ermöglicht Verhalten von Hardware modular zu beschreiben, um so eine übersichtliche Zusammensetzung eines SoC zu gewährleisten. Da ein SoC nun aus Entitys zusammen gesetzt wird und ein SoC aus SoC-Komponenten besteht, sind also Entitys mit SoC-Komponenten gleichzusetzen.

Beispielsweise ist der LEON3-Prozessor eine Entity. Dieser Prozessor hat Bestandteile wie die Memory Management Unit (kurz MMU) oder den Cache, welche ebenfalls Entitys sind. Alle Bestandteile eines SoC sind Entitys, neben dem Prozessor auch der Bus-Arbiter, und Schnittstellen zu Speichern. Selbst das SoC an sich, wird letztendlich in einer einzelnen Entity verpackt.

Eine Entity hat grundsätzlich folgenden Aufbau:

```

entity SoC is

port (

sys_clk_pin : in std_logic;

ied1 : out std_logic;

button1 : in etd.

sys_rst_pin : in std_logic;

);

end system;

architecture STRUCTURE of SoC is

signal clk : std logic;

signal rst : std logic;

begin

clk <= sys clk pin;

rst <= sys rst pin;

Prozessor : p1

port map ( CLK => clk, RST => rst, .. );

ea Komponente : eal

port map ( CLK => clk, RST => rst, LED => led1,

Button1 => buton1 );

end architecture STRUCTURE;

```

Abbildung 2.3: Aufbau einer SoC-Entity

Abbildung 2.3 zeigt ein einfaches Beispiel einer SoC-Entity. Der rote Rahmen markiert die Port-Deklarationen der SoC Haupt-Entity. Der grüne Rahmen markiert den Aufbau der SoC-Entity. Blau sind alle Signale markiert. Diese können später den Bus beinhalten. Mit den Deklarationen im schwarzen Rahmen werden zusätzliche SoC-Komponenten (Entitys) in das SoC eingebunden und mit dem Konstrukt "port map" verdrahtet.

#### Kapitel 2 Grundlagen

Der Bus, der die Verdrahtung bezeichnet (optional im blauen Rahmen in Abbildung 2.3), ist keine Entity. Das hat die Ursache, dass Kommunikationsleitungen, welche jeweils ein Bit übertragen, in VHDL mit Signalen erzeugt werden. Diese Signale dienen sozusagen als Informationsquelle und Senke. Sie sind vergleichbar mit Variablen eines Softwareprogramms.

Wird ein Signal an einen Eingangsport einer Entity gelegt und bei einer anderen Entity an den Ausgangsport, so generiert die Synthesesoftware eine Leitung zur Übertragung eines logischen Pegels zwischen den beiden Ports.

Wird eine Sammlung von solchen Signalen betrachtet, von der einige Signale in alle SoC-Komponenten münden und einige Signale von den SoC-Komponenten beschrieben werden können, spricht man von einem Bus.

Die Firma Xilinx bietet zwei Möglichkeiten den VHDL-Code, also alle Entitys, zu synthetisieren und auf einem FPGA konfigurierbar zu machen.

Eine Möglichkeit ist es das Werkzeug Xilinx ISE zu verwenden. In diesem Werkzeug ist es dem Autor des VHDL-Codes überlassen, wie er sein System aufbaut. Der Autor schreibt die Entitys des SoC mit einer einfachen Editoroberfläche und ist selbst für die Verbindung der einzelnen Entitys verantwortlich. Es ist also nötig, dass der Autor seine Entitys auf Register-Transfer-Ebene (kurz RT-Ebene) im Verhalten beschreibt. Während des gesamten Entwicklungsprozesses des SoC durchläuft der Autor alle Ebenen des Hardwareentwurfs.

Die Synthese der SoC Haupt-Entity, welche alle Entitys als Untermodule beinhaltet und auch als System-Entity bezeichnet wird, erfolgt dann mit den von Xilinx vorgegebenen Synthesetools.

Eine andere Möglichkeit, ein SoC zu entwerfen, bietet das Werkzeug Xilinx-EDK. Hier beschreibt der Autor das SoC auf Systemebene. Das bedeutet der Autor übernimmt nur die Aufgabe der strukturellen Verknüpfung der SoC-Komponenten.

Im Hintergrund wird letztendlich nichts anderes vorgenommen als eine SoC Haupt-Entity zu erstellen. Diese Entity wird bei der Benutzung des EDK immer System-Entity genannt. In der erstellten System-Entity werden dann lediglich die direkten Unter-Entitys eingetragen und strukturell durch den Bus verbunden.

Da nun aber keine Verhaltensbeschreibung der Unter-Entitys, durch den Autor, notwendig ist wird eine Bibliothek benötigt aus denen die direkten Unter-Entitys, wie der  $\mu$ P, den Schnittstellen zu Speichern oder E/A-Komponenten, entnommen werden. Diese Bibliothek ist die schon erwähnte Xilinx-IP-Core-Bibliothek.

Prinzipiell sind die Arbeitsweisen von EDK und ISE identisch. Als Endprodukt entsteht eine Entity-Hierarchie aus VHDL-Dateien, welche dann in die Synthese gegeben wird. Die Synthese der nun erstellten System-Entity verläuft kaum unterschiedlich zur Synthese mit dem Werkzeug Xilinx ISE.

Die Benutzung der Xilinx Bibliothek erzeugt also eine erhebliche Zeitersparnis bei der Erstellung von SoC-Lösungen. Die Verhaltensbeschreibungen der einzelnen SoC-Komponenten sind durch die einzelnen IP-Cores vorgegeben.

# 2.2 Das Werkzeug: Embedded Development Kit (EDK)

In diesem Kapitelpunkt werden Betrachtungen durchgeführt welche an einem unverändertem Xilinx Embedded Development Kit (kurz EDK) zu beobachten sind. Es soll also der Zustand des EDK nach einer Installation beschrieben werden, um die Ausgangssituation zu verstehen. Hier werden also noch keine Änderungen durch das Einbinden der GRLIB diskutiert, sondern nur Ansätze gezeigt.

Die Software Xilinx-EDK arbeitet mit einfachen VHDL-Entitys, welche im Hintergrund miteinander verbunden werden. Dieser Vorgang ist allerdings für den Benutzer nicht direkt sichtbar. Die SoC-Entitys der System-Entity, werden zusätzlich in Wrapper (engl.: Verpackung) Entitys eingebettet. Wrapper Entitys sind einhüllende VHDL-Entitys. In ihnen werden die Generic Informationen der IP-Cores fest eingeschrieben, so dass sie zur Synthese bereitstehen.

Zur Erstellung eines SoC werden die nötigen IP-Cores aus dem "IP Catalog" in das Projekt aufgenommen. Dies kann in einem einfachen Fall ein MicroBlaze-Prozessor, ein OPB Bus, der LMB Bus mit Block-RAM (kurz BRAM) und ein GPIO (Schnittstelle zu LEDs und Buttons) sein. Der MicroBlaze-Prozessor würde dann, nach der Synthese, ein einfaches Programm aus dem BRAM über den LMB auslesen. Dieses Programm würde den MicroBlaze-Prozessor beispielsweise anweisen einen Zähler auf den GPIO LEDs, über den OPB Bus, auszugeben.

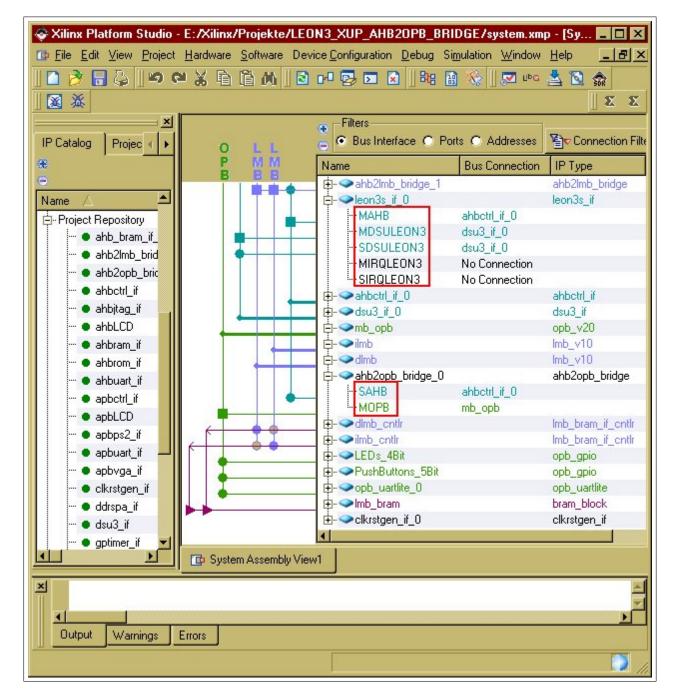

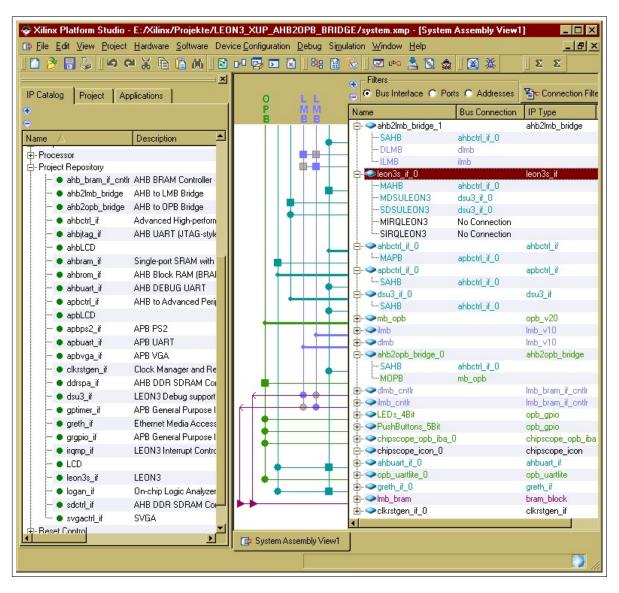

Seit EDK Version 8.2i ist die "Bus Interface"-Ansicht vorteilhaft überarbeitet worden. Dem Benutzer wird nun neben einer Auflistung aller SoC-Komponenten zeitgleich eine Übersicht der entstehenden Busstruktur dargestellt.

Die "Ports"-Ansicht stellt alle nach außen sichtbaren Ports einer Entity, also einer SoC-Komponente, dar. Hier kann der Benutzer Entity-Ports mit physikalischen Pins des FPGAs verbinden. Diese Pins sind dann auf dem FPGA-Board mit den LEDs verbunden oder werden als Steuersignale an einen anderen "Hard-Controller", wie beispielsweise den Ethernet MAC Controller, geleitet. Als "Hard-Controller" wird hier eine Funktionseinheit von Integrierten Schaltkreisen (kurz ICs) bezeichnet. Dieser Hard-Controller übernimmt dann die detaillierte Ansteuerung der Schnittstelle. Dazu kann zum Beispiel eine Digital-Analog-Wandlung nötig sein.

In der "Addresses"-Ansicht hat der EDK Benutzer die Möglichkeit die Systemadressen der einzelnen SoC-Komponenten festzulegen. Schreibt oder liest der  $\mu$ P, während der Programmausführung, an solch eine Adresse, kommuniziert der  $\mu$ P mit der jeweiligen SoC-Komponente.

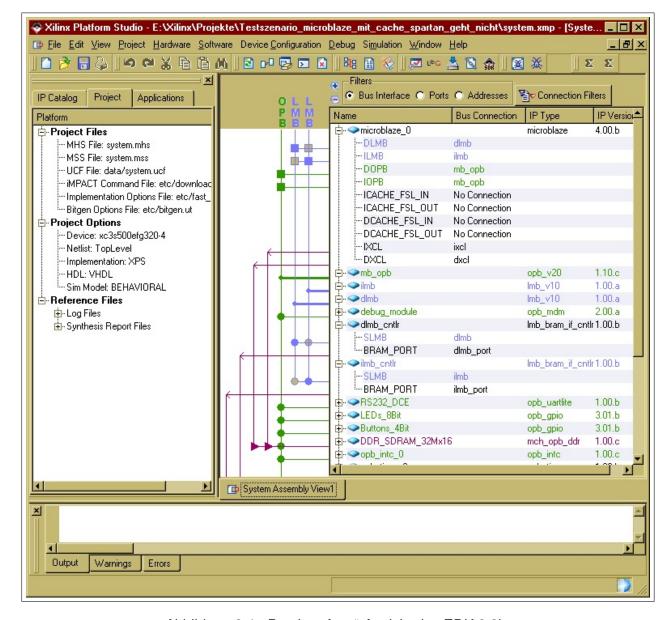

Abbildung 2.4: "Bus Interface"-Ansicht des EDK 8.2i

Abbildung 2.4 zeigt die "Bus Interface"-Ansicht. Rechts ist die Auflistung der SoC IP-Cores zu erkennen und in der Mitte die daraus resultierende Busstruktur.

#### Klassifikation der IP-Cores

In Kapitelpunkt 2.1 wurde in dieser Arbeit eine Klassifikation der SoC-Komponenten eingeführt. Es wurde grob zwischen Prozessoren, Bussen, Speichern und Schnittstellen unterschieden. Dies ist eine Klassifikation nach Arbeitsweisen oder Verhalten von Entitys. Durch einen Blick auf die "Bus Interface"-Ansicht ist es nun an der Zeit eine praktischere Klassifikation einzuführen.

Ab jetzt werden nur Entitys unterschieden, welche Master oder Slave auf einem Bus sind. Vorab sei noch einmal gesagt, dass alle SoC-Komponenten Entitys im Sinne von VHDL sind.

Bekannte Entitys werden nun wie folgt klassifiziert:

- Ein Prozessor ist eine Entity, welche meist Master auf einem Bus ist.

- Speicher und Schnittstellen sind Entitys, die meist Slaves auf einem Bus sind.

- Ein Bus ist eine Entity, die weder Master noch Slave auf einem Bus ist.

Weiter sei gesagt, dass es von nun an nicht mehr wichtig ist die Bezeichnungen Prozessor, Bus usw. zu verwenden. Alle SoC-Komponenten sind Entitys. Wenn allerdings von der Arbeitsweise oder dem Verhalten der Entitys gesprochen wird, ist es wieder hilfreich auf die alten Bezeichnungen zurückzugreifen.

Die oben genannten Ansichten ("Bus Inteface", "Ports", "Addresses"), des EDK, ermöglichen es in kurzer Zeit ein SoC benutzerfreundlich zu erstellen. Die Vorteile dieser Ansichten sollen später auch für die GRLIB zur Verfügung stehen.

Eine Ausnahme bildet die "Addresses"-Ansicht. Aus Gründen, welche in Kapitel 5 erörtert werden, war es nicht möglich diese Ansicht für die GRLIB nutzbar zu machen. Die "Addresses"-Ansicht wird also in Zukunft nur für Xilinx-IP-Cores nützlich sein und für GRLIB-IP-Cores verworfen werden.

# 2.2.1 Arbeitsplan der Software EDK

In diesem Kapitelpunkt soll der Arbeitsplan des EDK genauer erläutert werden. Dies ist zwingend notwendig, um zu verstehen, wo sich alle Ansätze zum Einbinden der GRLIB befinden.

Außerdem sind beim Einbinden der GRLIB Unterschiede im herkömmlichen Workflow entstanden. Mit Unterschieden im Workflow sind Handlungen gemeint, welche ausgeführt werden müssen, um ein GRLIB LEON3-SoC erfolgreich zu synthetisieren. Diese Handlungen sind bei der Arbeit mit den Xilinx-IP-Cores nicht notwendig.

Als Ziel der Hardwaresynthese und Kompilierung der Software steht ein Bitstream, benannt mit "download.bit". Dieser befindet sich im "[EDK\_PROJECT]/implementation"<sup>2</sup> Verzeichnis. Dieser Bitstream beinhaltet die FPGA-Daten zur Realisierung der synthetisierten Hardware und die BRAM-Daten. Die BRAM-Daten werden ebenfalls bei der Bitstream-Konfiguration geschrieben, da sich in ihnen das kompilierte native C-Programm befindet. Der Bitstream "system.bit", im selben Verzeichnis, beinhaltet nur die Konfigurationsdaten für den FPGA ohne BRAM-Daten.

<sup>&</sup>lt;sup>2</sup>Mit dem Ausdruck [EDK\_PROJECT] wird das Verzeichnis bezeichnet in dem sich das gespeicherte EDK-Projekt befindet.

Zur Erstellung des "download.bit" Bitstreams muss der EDK-Arbeitsplan erfolgreich abgearbeitet werden. Der EDK-Arbeitsplan wird in vier Arbeitsschritten ausgeführt.

#### Diese Arbeitsschritte sind:

**Arbeitsschritt 1:** Erstellung einer **B**RAM **M**emory **M**ap (kurz BMM) Datei und Abbilden der ausgewählten SoC IP-Cores auf eine VHDL-Code Hierarchie.

Arbeitsschritt 2: Das Synthetisieren der SoC IP-Cores sowie der System-Entity. Bei diesem Vorgang werden die Hardware Netzlisten (engl.: Netlists) generiert. Dies geschieht durch die Xilinx Synthesetools (Xst, Place, Route, Trace, Bitgen).

Als Ergebnis steht der Bitstream "system.bit".

Arbeitsschritt 3: Das Kompilieren des nativen C-Programms mit einem, für den Prozessor, gelieferten Compiler. Dies geschieht durch die Xilinx Tools (Libgen, Compiler, Linker).

Als Ergebnis steht ein Executable and Linking Format (kurz ELF), die ELF-Datei des nativen C-Programms.

Arbeitsschritt 4: Verbinden der System Netlist mit der ELF-Datei zum vollständigen Bitstream "download.bit". Dies geschieht durch die Xilinx Tools (Bitinit, Data2Mem)

Alle 4 Arbeitsschritte laufen in kleinen unterteilten Schritten ab, welche nach dem Konzept der MAKEFILE in der Datei "system.make" aufgelistet sind. Die Datei "system.make" befindet sich im "[EDK\_PROJECT]"-Verzeichnis. Sie bindet die Datei "system\_incl.make" ein, welche nützliche Informationen über den zu benutzenden Compiler und Benennungen von Verzeichnissen enthält. Damit der EDK-Arbeitsplan für die GRLIB fehlerfrei durchlaufen kann, war ist es nötig Änderungen an der Datei "system.make" vor zu nehmen.

#### 2.2.1.1 Arbeitsschritt 1 (VHDL-Code der System-Entity generieren)

In Arbeitsschritt 1 werden allgemeine Vorbereitungen getroffen, die der Synthese der System-Entity dienen. Die System-Entity wird nach dem Projektnamen benannt. In dieser Arbeit soll sie mit "system.vhd" bezeichnet werden. Alle VHDL-Code Dateien mit den Endungen ".vhd", von denen in Arbeitsschritt 1 gesprochen wird, werden im Verzeichnis "[EDK\_PROJECT]/hdl" gespeichert.

Es werden folgende Operationen ausgeführt:

- 1. Es wird eine BMM-Datei erstellt. Sie bildet die Daten des kompilierten nativen C-Programms auf den Systemspeicher ab.

- 2. Für jede SoC-Komponente wird eine Wrapper-Entity erstellt. Diese Wrapper-Entitys binden als Unter-Entitys die Entitys der SoC-Komponenten ein.

- 3. Es wird eine System-Entity generiert, welche alle Wrapper-Entitys zu einem SoC verbindet.

#### **Operation 1: BMM-Datei**

Die BMM-Datei namens "system.bmm", welche sich im "[EDK\_PROJECT]/implementation"-Verzeichnis befindet wird zu Beginn generiert. Die BMM-Datei enthält eine syntaktische Beschreibung in welcher Weise einzelne BRAMs zu einem zusammenhängenden, logischen Datenraum verbunden werden. Die BMM wird vom EDK benötigt, um ein natives C-Programm in die BRAMs zu laden.

```

ADDRESS_MAP microblaze_O MICROBLAZE 100

ADDRESS_SPACE lmb_bram_combined COMBINED [0x00000000:0x00001fff]]

ADDRESS_RANGE RAMB16

BUS_BLOCK

Imb_bram/lmb_bram/ramb16_s9_s9_0 [31:24];

lmb_bram/lmb_bram/ramb16_s9_s9_1 [23:16];

lmb_bram/lmb_bram/ramb16_s9_s9_2 [15:8];

lmb_bram/lmb_bram/ramb16_s9_s9_3 [7:0];

END_BUS_BLOCK;

END_ADDRESS_RANGE;

END_ADDRESS_SPACE;

END_ADDRESS_MAP;

```

Abbildung 2.5: Inhalt der BMM eines MicroBlaze-Systems

Ein BRAM hat eine Kapazität von 2 KByte. An der Abbildung 2.5 der BMM-Datei ist zu erkennen, dass, für das native C-Programm, ein Speicher von 8 KByte verwendet werden soll. Dies entspricht einem Adressraum von 0x1FFF Bytes. Insgesamt werden also 4 BRAMs benötigt.

Bei der Einbindung der GRLIB musste sichergestellt werden, dass diese BMM-Datei ebenfalls beim Start des Arbeitsschritts 1 erstellt wird. Dies führte zu dem "BMM-Problem", welches näher in Kapitelpunkt 5.3.3 beschrieben wird.

#### Operation 2: Erstellen der Wrapper Entiäten

Die Wrapper-Entitys haben prinzipiell eine Benennung nach dem Muster: "[name]\_wrapper.vhd"<sup>3</sup>. Bei der Konfiguration der SoC-Komponenten mittels der EDK GUI, werden die sogenannten Generics festgelegt. Generics sind für eine Entity festgelegte Konstanten mit denen es möglich ist Einstellungen vorzunehmen. In dieser Arbeit wird die Bezeichnung Generic-Konstanten verwendet. Die mit der EDK-GUI festgelegten Generic-Konstanten werden in die Wrapper-Entitys eingebettet und versorgen so die Haupt-Entity eines IP-Cores mit den korrekten Werten.

```

entity leds_4bit_wrapper is

port (

OPB_ABus : in std_logic_vector(0 to 31);

OPB BE : in std logic vector (0 to 3);

OPB Clk : in std logic;

GPIO d out : out std logic vector (0 to 3);

);

end leds_4bit_wrapper;

architecture STRUCTURE of leds 4bit wrapper is

begin

leds_4bit : opb_gpio

generic map (

C BASEADDR => X"40000000",

C_HIGHADDR => X"4000ffff",

C_OPB_AWIDTH => 32,

C_OPB_DWIDTH => 32,