## UNIVERSITÄT LEIPZIG Fakultät für Mathematik und Informatik Institut für Informatik

Operation Graph Oriented Correlation of ASIC Chip Internal Information for Hardware Debug

**Diploma thesis**

Leipzig, August 2006

vorgelegt von: Große, Michael geb. am: 05.05.1981 Studiengang: Informatik

#### Zusammenfassung

In dieser Diplomarbeit wird ein neuer Ansatz zum Operations-Tracing für die Hardware-Fehlersuche mit Hilfe einer Analyse von verteilten Traces vorgestellt. Dazu zeichnen Traces Operationen zur Laufzeit auf, deren Einträge mit einem Programm korreliert werden, nachdem ein Problem aufgetreten ist. Das Programm basiert auf einer allgemeinen Methode, die Identifier aus den Operationen verwendet. Da die Identifier sich während der Abarbeitung einer Operation ändern und die Traces unterschiedliche Informationen abspeichern, müssen die Einträge transformiert werden, um die Einträge der selben Operation in anderen Traces zu erkennen. Nach der Korrelation der Einträge rekonstrutiert die Methode die Operationspfade mit Hilfe eines Operationsgraphen, der für jeden Operationstypen die Teiloperationen und deren Reihenfolge beschreibt. Durch die Pfade erhält der Entwickler einen besseren Überblick über die Chip- bzw. Systemaktivität und kann dadurch Probleme schneller eingrenzen, um dann mit Hilfe anderer Informationen deren Ursache zu finden. Der TRACE MATCHER implementiert die beschriebene Methode und wird anhand eines Beispiel-Bridge-Chips evaluiert. Dazu wird der Nutzen für die Hardware-Fehlersuche, die Korrektheit der rekonstruierten Pfade, die Performance der Implementierung und der Konfigurationaufwand bewertet. Außerdem beschreiben Leitlinien für das Trace und System Design, wie das Matching mit sorgfältig gewählten Identifiern in den Operationen verbessert werden kann.

# Preface

This thesis presents a novel approach to operation-centric tracing for hardware debug with a retrospective analysis of traces which are distributed across a computer system. Therefore, these traces record entries about the operations at runtime, and a software tool correlates these entries after a problem occurred. This tool is based on a generic method using identifiers saved from operations. Because identifiers are changed along the path of an operation through the system and traces record different information, the entries are transformed to find matching entries in other traces. After the correlation, the method reconstructs the operation paths with help of an operation graph which describes for each type of operation the subtasks and their sequence. With these paths the designer gets a better overview about the chip or system activity, and can isolate the problem cause faster. The TRACE MATCHER implements the described method and it is evaluated with an example bridge chip. Therefore, the benefit for hardware debug, correctness of the reconstructed paths, the performance of the implementation, and the configuration effort are evaluated. At the end guidelines for trace and system design describe how matching can be improved by carefully designed identifiers at operations.

# Contents

| Pr         | Preface     i     |                                     |    |  |  |  |  |

|------------|-------------------|-------------------------------------|----|--|--|--|--|

| 1          | Intro             | oduction                            | 1  |  |  |  |  |

|            | 1.1               | Structure of this work              | 3  |  |  |  |  |

| 2          | Basi              | ics                                 | 4  |  |  |  |  |

|            | 2.1               | Traces                              | 4  |  |  |  |  |

|            | 2.2               | Operation paths                     | 7  |  |  |  |  |

|            | 2.3               | Time and Order of Events            | 9  |  |  |  |  |

|            | 2.4               | Identifiers                         | 11 |  |  |  |  |

|            | 2.5               | Operation Types                     | 13 |  |  |  |  |

| 3          | State             | e of the art                        | 14 |  |  |  |  |

| 4 Approach |                   | proach                              | 17 |  |  |  |  |

|            | 4.1               | Basic ideas                         | 17 |  |  |  |  |

|            | 4.2               | Configuration                       | 19 |  |  |  |  |

|            |                   | 4.2.1 Logical traces                | 19 |  |  |  |  |

|            |                   | 4.2.2 Transformation function       | 20 |  |  |  |  |

|            |                   | 4.2.3 Transformation graph          | 21 |  |  |  |  |

|            |                   | 4.2.4 Operation graph               | 22 |  |  |  |  |

|            | 4.3               | Algorithm                           | 24 |  |  |  |  |

|            |                   | 4.3.1 Local matching                | 24 |  |  |  |  |

|            |                   | 4.3.2 Global matching               | 26 |  |  |  |  |

|            |                   | 4.3.3 Operation path reconstruction | 28 |  |  |  |  |

|            | 4.4               | Complexity analysis                 | 30 |  |  |  |  |

| 5          | Implementation 34 |                                     |    |  |  |  |  |

|            | 5.1               | Debug tool                          | 34 |  |  |  |  |

|            |                   | 5.1.1 Architecture                  | 35 |  |  |  |  |

| B              | Sour              | ce code        |                                  | 73        |

|----------------|-------------------|----------------|----------------------------------|-----------|

| A              | Ack               | nowledg        | gements                          | 72        |

| Bi             | bliogr            | aphy           |                                  | 66        |

|                | 7.4               | Outloo         | k                                | . 65      |

|                | 7.3               | Summa          | ary                              | . 64      |

|                | 7.2               | Guidel         | ines for trace and system design | . 63      |

|                | 7.1               | Proble         | ms                               |           |

| 7 Consequences |                   | ces            | 62                               |           |

|                |                   | 0.4.3          |                                  | . 39      |

|                |                   | 6.4.2<br>6.4.3 | Performance                      |           |

|                |                   | 6.4.1<br>6.4.2 | Correctness                      |           |

|                | 0.4               | Evalua         | tion                             |           |

|                | 6.3<br>6.4        | U              | workflow                         |           |

|                | 6.2<br>6.3        |                | uration workflow                 | _         |

|                | 6.1<br>6.2        | -              | ble chip                         | -         |

| 6              | <b>Rest</b> 6.1   |                | ala akin                         | <b>46</b> |

| _              | _                 |                |                                  |           |

|                |                   | 5.3.3          | Operation path reconstruction    |           |

|                |                   | 5.3.2          | Global matching                  |           |

|                | 2.0               | 5.3.1          | Local matching                   |           |

|                | 5.3               |                | er                               | -         |

|                |                   | 5.2.5          | Logical traces                   |           |

|                |                   | 5.2.4          | Transformation function          |           |

|                |                   | 5.2.2          | Identifier tree                  | -         |

|                |                   | 5.2.2          | OTGraph                          | -         |

|                | 0.2               | 5.2.1          | Naming                           |           |

|                | 5.2 Configuration |                |                                  |           |

|                |                   | 5.1.3          | Decoder                          |           |

|                |                   | 5.1.2          | Trace analyzer                   | . 36      |

## **Chapter 1**

# Introduction

Computer systems are getting more and more complex. In order to deal with their complexity, chips in these systems are built out of modules which are also used among other chips. Additionally an increasing number of functionality is executed in parallel to improve the performance of the systems. On the other side complex tasks like virtualization and recovery become viable and are implemented in the firmware.

Due to this complexity, hardware debugging of developed systems consisting of chips and firmware is more complicated than before. Some time ago, chips were debugged with logical analyzers attached to their pins. Higher clock frequencies and the resulting mechanical problems forced the designers to move the information for debugging onto chips[Tur04]. In high-availability systems this *chip internal information* is automatically captured to dumps in case of an error on customer machines[KBF<sup>+</sup>04]. This is necessary, because errors may not be easy to reproduce and those machines cannot be used for testing. Therefore, chips contain traces, which record the executed steps in small memories, and checkers, which are latches indicating the state of a certain condition, and registers which are code-accessible memories. This internal information can be read out over side-band interfaces[IEE01] or an assistant processor aggregates them to a dump if a checker indicates that a severe problem occurred and the recovery failed. The dumps are send to the designers so that the problem can be analyzed.

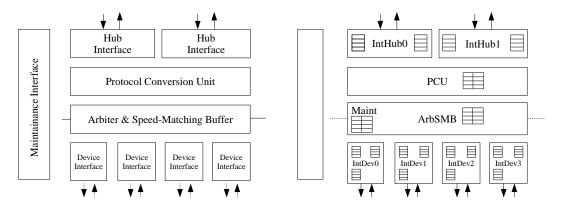

As a result, chips now contain plenty of debug information, but designers need a fast overview when looking at a problem for the first time. Then a certain part of the chip can be debugged further or the problem is redirected to the responsible person. Therefore, in the high-performance I/O chip MBA<sup>1</sup>[PH04] in zSeries<sup>2</sup> systems, operation-centric tracing was introduced[BFG<sup>+</sup>99] to track operations across the chip. This is accomplished at runtime by a central activity monitor using an operation graph, and additionally a tool called OHRMATCH combines information of the remaining parts of the chip after a problem occurred to reconstruct the operation paths. The activity monitor checks

<sup>&</sup>lt;sup>1</sup>MBA is the abbreviation for Memory-Bus-Adapter.

<sup>&</sup>lt;sup>2</sup>Trademark or registered trademark of International Business Machines Corporation.

the paths of operations through the functional units in the chip at runtime for inconsistencies with operation graphs describing for each type of operation the valid subtasks and their sequence. The monitor writes an entry to a central trace either for each inconsistency or for all completed subtasks. In addition OHRMATCH analyzes the trace data in a chip dump in order to reconstruct the operation path from the subtasks in the central trace to the chip interfaces by matching the trace entries of one operation together.

With these information, problems caused by the user, the interaction between the firmware and the hardware, or in the chip logic can be debugged faster. For example, operations might get timeouts while sending them to another chip because the firmware is retiming the link at the wrong point in time. In addition during the power-on of a prototype a user might forget to plug in a cable, so that all operations are dropped at that link. Due to the operation-centric tracing which focuses onto the operations instead of the functional units, the designer notices such problems faster. Hence, using the reconstructed operation paths, a designer can recognize operations where the response is missing and derive the cause of a problem by patterns in operations, or can look then into other chip internal information.

But the information in one chip is not sufficient anymore for debugging. Due to the modularization of chips, the context around functional units and chips becomes more and more important. The implementation of the operation graph as finite-state machine in hardware has significant shortcomings. First, a central trace poses a major problem when many parties try to trace, because the probability of write conflicts increase, so that the written entries can be invalid. The order of the entries might not reflect the order of events in the system if the information has to travel different distances through the system. Additionally, the number of parallel trackable operations is limited by the number of implemented finite-state machines. Because current systems support more outstanding operations, costs in terms of chip area increase significantly for this approach. Consequently, traces are distributed at important places across functional units in chips of a system recoding the passing operations without an activity monitor. Thus, the operation-centric tracing, which reduced the debugging effort, has to be implemented in software by correlating the traces.

OHRMATCH is not sufficient to reconstruct the operation path from the data in the traces distributed across the system, because the tool is highly chip-specific and uses hard coded information about the structure of the chip, the operations, and assumptions about the operations. Therefore, a generic method is required which correlates the trace entries with each other in order to reconstruct the operation paths from chip internal information. Similarly to OHRMATCH, this method must provide a condensed view at executed operations and their paths through several chips in the system. Therefore, the user has to specify the paths for different operation types through the system. The trace entries should be correlated with information from entries like addresses and identifiers created by the system. Additionally the transformation of operations between traces, done by functional units, need to be described. This work should address ambiguities caused by duplicate identifiers as well as the

behaviour of I/O operations like resends caused by high system utilization, and splitting of operations with large data blocks into many smaller ones and their later merging.

The method should be implemented in Java and integrated in a new debugging framework called DE-BUG TOOL which is accessed by an interactive front-end. Hence, the implementation of the method, which is called TRACE MATCHER, needs to be responsive and take at most 10 seconds for a correlation. Additionally the result of a correlation has to be understandable and the implementation must be robust enough to deal with duplicates. The work should contain an evaluation of the effectiveness and the performance of the method and their implementation. Configurations for the TRACE MATCHER have to be described in a way, that designers can write them for chips and easily reuse them for system-wide analysis. The requirements and limitations for the method should be described, and recommendations for trace design should be given.

## **1.1** Structure of this work

This thesis is structured as follows. The first chapter presents basics about traces, operations in the system, time and order of events, identifiers, and operation types which are required to understand the following chapters. In the second chapter the state of the art in event correlation is evaluated with respect to a set of criteria derived from the problem description. After that, first the basic ideas of the new approach are described, and then the algorithm is presented in detail including a complexity analysis. The fourth chapter contains the implementation of the new approach called TRACE MATCHER. In the next chapter the results of the work are presented with the necessary steps to create configurations, run the TRACE MATCHER and to interpret the results. The correctness of the results is analyzed and the performance is evaluated at several test cases. The last chapter highlights problems which arose during the work, presents rules for the trace design to reconstruct the operation paths, as well as limitations of the approach and a conclusion.

## Chapter 2

# **Basics**

In this chapter basics will be introduced, which are necessary to evaluate existing approaches and to understand the further work. First traces are presented in detail, which are the main data source for reconstructing the operation path with the used method. Therefore, different kinds of traces, their features, and information which is usually traced are outlined. After showing this rather local perspective, we will go on to a chip and system-level analysis of operation paths in the machines. In this analysis sample paths of operations through the system and their representation in the traces are outlined, and structural primitives are derived from the trace placement along these paths.

Then different time concepts are described, which are used in the real world and computer systems to keep track of the order of events. After highlighting their limitations, identifiers will be presented, which are the foundation for the generic method. Therefore, their quality is analysed, scopes are introduced, and different primitives for combining those identifiers are described.

Finally, operation types are presented, which are used to refer to different operation paths through the system. Since many different protocols are used in systems, abstract types are introduced to capture types at a system level so that operation paths can be described.

## 2.1 Traces

Traces are used in both software and hardware to debug problems. They provide a detailed record of the steps a system has performed during execution. When an error occurs, traces get stopped so that the they contain the steps executed before the error. In contrast, to other chip internal information, the hardware traces do not provide a snapshot of the chip state but information about a period of time. This information is very valuable for debugging, for example to see operations in the interaction between different chips. Thus, one can find operation patterns to be executed for reproducing the problem. The

traces must be simple enough to not pose a problem itself during debugging. Additionally the traced information should help the designer in different problem scenarios.

Software traces are created by special trace statements which are spread over the entire code between functional code. These statements trace the position in the control flow, for example the executed function or the chosen branch after a condition. Furthermore these traces contain values of variables which might help to track down the problem. All these traced information is usually printed out to the screen or into a file.

Hardware traces are implemented as cyclic memories which wrap when a certain number of entries has been written. At the rising edge of a trigger signal a new entry is written to the trace, where the signal is usually selecting from several input signals with a multiplexer. Since the hardware traces cannot be changed after chip production, these traces provide different modes which record different information. These modes are carefully designed according to the predicted problem scenarios. The format, for example, for debugging the internal logic of functional unit is different from the information needed to track an operation through the system. The memories used for storing a trace, which are also called trace arrays, are expensive in terms of chip area and power consumption because such arrays usually reachs up to 1000 cells or more. As a consequence traces are used sparingly only at important places in the system and are restricted in size. So the depth of a trace – the number of entries – and the width of each trace entry in bits are limited compared to software traces. Additionally, large traces take a longer time to read out. On the other side a large trace can contain the information one might need to debug a complex problem.

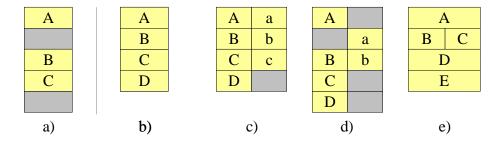

Figure 2.1: One cycle trace and four different event trace formats.

Traces are distinguished in *cycle* and *event* traces shown in the examples a and b in figure 2.1. The first kind triggers in each clock cycle and the second one triggers only if an event occurs, for example a valid signal rises on a bus. Therefore, the cycle trace is restricted to a fixed duration by its depth, for example a 64 entries deep trace will trace 64 ns on a chip running at a clock speed of 1 GHz. Additionally these traces contain equal or unused entries if the state of the traced unit does not change as shown with entry two and five in trace a. In contrary event traces contain a history of events, for example of passing operations, which are also called *operation history register* or short "OHR". The history of the event traces can reach up to the microsecond range depending on the workload.

Both kinds of traces have their advantages. With a cycle trace the designer can be used to make timing and performance measurements, and to track the utilization of different logic parts. On the other side the trace shows only a short picture of the activities in the chip. Event traces on the other side provide a deeper history of the activities in the chip, but cannot show utilization of different logic parts. That is why mixed forms of these traces have been developed which perform a run-length encoding over the entries in cycle traces or add timestamps from a PLL<sup>1</sup> to an event-trace. Additionally different kinds of traces and setups are used throughout the chip to get a complete picture for debugging.

Another important aspect of traces is the timing. Especially in real-time and high-performance systems, traces should not change the timing of the traced logic. This non-intrusive tracing is possible if the data for the entry is stored in staging latches until all information is present and the entry can be written out. In most cases only the order of these entries is relevant so that this little delay is not a problem.

Traces found in I/O chips are usually operation history registers which write an entry when an operation passes. However, those traces can have different formats shown in examples b to e in figure 2.1. Trace b, for example, is a classic event trace whereas the next two traces are split according to the direction in which the operations pass the trace. Operations heading in different directions are named with uppercase and lowercase letters are triggering the trace independently in example c. In example d an entry is written if an operation in one direction is passing the trace. In the last example the trace stores information about two operations in one entry and similarly one operation across could be traced in two entries. Thus, there are quite different trace setups in the system.

| Α |  |

|---|--|

| В |  |

| Α |  |

| В |  |

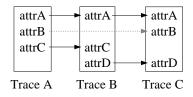

Figure 2.2: Different traced attributes depending on the operation type.

Additionally the logic in a functional unit traces different information depending on the operation type in order to to use the limited memory efficiently as shown in figure 2.2. So beside the type, unique and control information as well as sometimes data from the operation are stored in the trace. Unique information, for example, are identifiers for the sender and recipient of the operation and for this specific operation. In contrary control information are checkers and error bits or a checksum indicating the state of the operation and of their payload. Sometimes the space in the trace is so limited that only a *part of an attribute* is traced. For example the logic might trace only the lower or upper address bits.

<sup>&</sup>lt;sup>1</sup>PLL is the abbreviation for phase-locked loop which can be used to generate a clock signal from a lower-frequency signal like a reference crystal.

### 2.2 Operation paths

After looking at single traces, an understanding of trace effects at the system scope is necessary. Therefore, the relation between executed operations, traces, their entries as well as global effects due to the retrospective analysis need to be investigated.

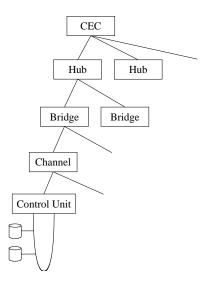

Two example operation types will help to understand the paths of operations through the system. A DMA<sup>2</sup> fetch is an operation which reads data directly from the memory to store them on the devices without utilizing the processor. These DMA fetch requests are issued at the channel and go upbound through the bridge, the hub and the CEC<sup>3</sup> to the memory. If the data is found in the cache, it is sent back the same way downbound as part of a fetch response. In the other case the data is first fetched from the memory and then sent back. In contrary the Sense/Controls are issued by the processor to read or set registers in functional units of the I/O subsystem, for example in the bridge and flow from the CEC downbound through the hub to the bridge. If a response was requested, the response goes upbound to the CEC on the same path.

These two example operations highlight two properties of most operations like out-of-order processing due to caches at the memory and the request and responses structure. Below all properties are described which are relevant for the tracing and the later operation path reconstruction.

1. consist of a request and in most cases a response

The issuer of operations, like a fetches of a memory block, receives a response either with the data or a failure notice. In contrast, unreliable operations like heartbeats, timer pulses and broadcasts require no response.

2. processed in or out of order

The system can process the operations in order or out of order. Unordered processing is used in several applications, for example for control operations passing regular operations, to send two operations over a link. In addition, a newer DMA fetch operation accessing cached data returns earlier than an older fetch accessing uncached data.

3. resend of operations if recipient is busy or as recovery strategy

An operation is resend when the recipient was busy in the first try, for example due to a busy link or a processor with a task running at a higher priority.

4. operations can be split and merged

Protocols are optimized or configured for a special application to reach better latency or throughput. Thus data on the operation might not fit in one operation of another protocol due to the

<sup>&</sup>lt;sup>2</sup>DMA is the abbreviation for Direct Memory Access.

<sup>&</sup>lt;sup>3</sup>CEC is the abbreviation for Central Electronic Complex containing multiple processors, chips for accessing the memory and caching data from the memory.

MTU<sup>4</sup>. In this case the data is split and sent out in several operations each smaller than the MTU. The data is then merged on the remote site when all parts are received and sent further as one operation.

These operation properties are reflected in the traces as well, since the entries are constructed from information of passing operations.

As stated in [BFG<sup>+</sup>99] "operations [...] [are] typically composed of several subtasks which are executed sequentially" at several function units. For debug the tracing captures the execution of these subtask by adding operation history registers in the functional units along the path of the different operation types. Hereby, the functional unit writes an entry to the operation history register during the execution or at the completion of the subtask. So later the trace entries can be used to reconstruct the path of the operation through the system.

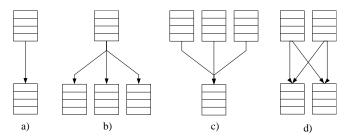

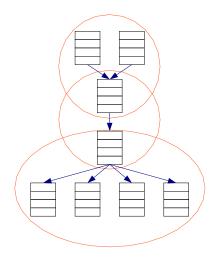

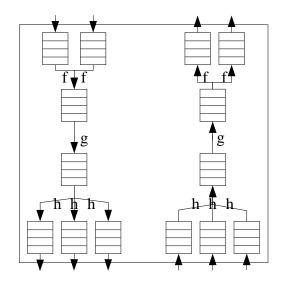

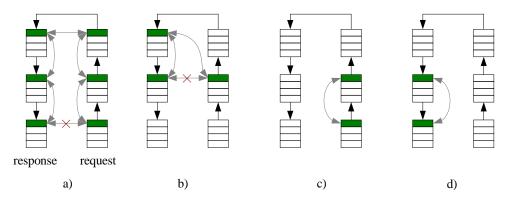

After analyzing the traces and their placement in the functional units across systems, the following primitives shown in figure 2.3 have been discovered. These primitives describe a set of source and target traces where entries in the target traces are only caused by operations which have also passed the source traces.

Figure 2.3: Operation path primitives.

The four primitives are called *direct*, *fan-out*, *fan-in* and *fail-over*. The direct primitive connects two traces with each other where the entries in the target trace are caused only by the operations passing the source trace. In constrast the fan-out primitive represents one source trace with many target traces. This primitive is used, for example, at arbiters or demultiplexers. The fan-in primitive is the counterpart for the fan-out primitive with many source traces and one target trace used for multiplexers. The most complex primitive is called fail-over connecting many sources to many targets and is for example used to represent traces at multiple ports of a chip with more than one driving functional unit. With these primitives at hand, all trace connections found in the system can be described.

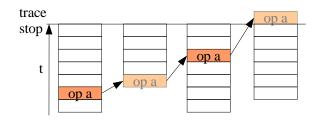

In contrary to runtime analysis of information where all data is current, the traces contain information about a period of time where these periods might not be the same across all traces. Therefore, the traces must be stopped at the same time, so that a consistent picture of the activity in the chip or

<sup>&</sup>lt;sup>4</sup>MTU is the abbreviation for maximum transmission unit describing the maximal size of a packet or an operation sent across a medium.

system emerges during the analysis. These trace stops occur only at nearly the same time because the stop event after a problem must propagate over the chip in a few cycles. Usually this is not a problem because idle cycles occur between the passing operations and the picture exactly at the chip stop is captured by other chip internal information. As a result, the information from each local history shows the events before the error which is later used to reconstruct the running operations. When the traces get stopped, some operations might be on their way between the traces. In contrast,other operations might cause entries after the stop event was sent due to the propagation time of this event.

Figure 2.4: Traces along an operation path.

Because traces are cyclic memories, each trace wraps at some point in time and old entries are overwritten with new ones. Thus, no information about old passed operation can be found in a trace anymore. Figure 2.4 shows traces along the path of an operation where the second trace has wrapped, but all the first and the third trace contain an entry for operation a. These differences between traces are caused either by operation paths split in several directions, for example at the fan-in and fan-out primitives, or by different trace depths. The last trace shown in the figure does not contain an entry about the operation because the trace stopped before the entry was written.

### **2.3** Time and Order of Events

The order of events, describing which event happened before which others, captures the causality between events. This causality between events is widely used in computer science to ensure consistency in replicated databases or liveness and fairness in distributed computations. Because traces distributed across the system contain entries about the passing operations, and each entry can be interpreted as an event, the operation path can be expressed by the order of events. Plenty of research[TvS02] has been conducted about the causal precedence relation which captures causality between events. Different notions of time are used to reconstruct this relation and will be outlined later on.

In daily life people use watches displaying a *global time* to determine which event happens before which others by assigning times to them. As Raynal stated[RS96], the order of events cannot be captured by unprecisely synchronised clocks when the events occur at a high rate. Beside that not all functional units writing to traces have a built-in physical time like a PLL. So global time is not usable to track events in hardware, since the chips easily reach clock frequencies higher than 100 MHz and

entries can potentially be written in every cycle to the trace.

Lamport proposed *logical clocks* in 1978[TvS02], because one typically wants to capture the order of the events in a distributed system and not the precise time of these events. So it does not matter if one system is ahead of other systems, as long as all agree on the same time. In contrast, to physical time, logical clocks are only updated when events happen in a part of a distributed system and these changes are propagated in messages with piggybacked information. Depending on the consistency requirements and the knowledge about other clocks in the system, several approaches with different data structures and synchronization protocols have been developed [RS96]. With *scalar time* developed by Lamport, the logical timestamps of two events cannot be compared with each other to determine which event causes another one. Because scalar time can only determine which events timely preceded an event, this notion of time cannot capture the causality precendence among events and cannot be the basis for an operation path reconstruction. The later developed *vector time* fills this gap by keeping the local and global clock information separate, so that by comparing the timestamps the causality can be obtained.

In order to reconstruct the operation path, the order of events using the logical clocks, vector time must be used and the vector timestamps need to be stored in the traces. The functional units with their traces, equivalent to distributed system without a global memory, communicate only by sending signals as messages to other units. Each functional unit would then update the vector timestamps according to the rules described in Raynals work[RS96]. These approach has two significant shortcomings. First, with each sent message the vector timestamp containing the local view about timestamps of all units in the system needs to be transmitted. For example, assuming a system has ten functional units, ten additional values would need to be transmitted to another unit in order to maintain the vector time. The vector timestamps may be reduced with other more sophisticated approaches, but a significant overhead will remain which results in additional logic so that the method would not be applicable soon. And second, these timestamps need to be stored in traces, increasing their size considerable. Additionally their might occur problems with wrapping timestamps due to the size limitations of the traces.

All those approaches which keep the order of events at a system level with time like physical clocks in form of PLLs or logical clocks are not applicable. At a local level between two functional units, that use the same physical clock the situation might be different because synchronization problems decline, but these cases are only "special" cases and are not the foundation for an operation path reconstruction.

### 2.4 Identifiers

This section will present another potential foundation for operation path reconstruction based on identifiers instead of time. An identifier tries to "establish the identity" based on the "sameness of essential or generic character in different instances"[Mor93, p575]. Therefore, an operation has attributes which establish the identity and are also stored in the traces. Due to the described character, different operations cannot have the same identifier value and so falsely perceived as being identical.

Identifiers can be distinguished in two kinds - artifically-created and user-created identifiers. *Artificial-created* identifiers are created by the system and are designed to be unique, for example sequence numbers in connections, identifiers for connections or tags for outstanding operations. Therefore, these identifiers work for all operation types and at each workload if they are well-designed. Second, *user-created identifiers* are not unique by creation, but have a character of uniqueness due to the distribution of the values. For example, the variance of the values of these identifier is high but some operations might be falsely identified as the same. Addresses in memory accessing operations might contain a high variance if the processes access different parts of their assigned memory areas. But these identifiers have a serious weaknesses. They are not designed to be unique so that they work only in special cases, for example only with certain operation types or at a special workload. As a result, artificial identifiers are the identifiers of choice from now on.

The ideal way to accomplish the goal of unique identifiers for different operations is a *global unique identifiers* also called GUID. GUIDs are identifiers which are unique at all times and at all places in the system. As a result, different operations would be completely distinguishable by their identifier. Because no identifier gets invalid, the identifiers get potential infinite over time. Unfortunately, they are not storable, even not creatable and so not implementable. That is why in real world limited identifiers are used which can be created and stored without problems.

*Limited identifiers* have a limited range and are only unique in a certain part of the system during a certain period in time which will be called scope from now on. For example, tags at outstanding operations are used to refer to these operations on the response side after sending the request. These tags are only valid on the path between sender and recipient until the response is received or a timeout occurs. The *scope* describes time period and places in which the identifiers are unique, similar to the scope of variables in programming languages.

The scope of identifiers can change over time due to changing requirements in the protocols. In the TCP protocol sequence numbers are used for the sent packets which need to be acknowledged. During the time technology improved and long-distance low-speed connections to space and highspeed backbone connections between large cities or continents became possible[JBB93]. Therefore, the sequence numbers attached to the packets wrap on a 1 GBps connection just after 17 seconds while the timeout for the acknowledgments from the communication partner was recommended to be set to two minutes. On the other side the low-speed traffic legitimates the two minute acknowledgment timeout. As a result, the sequence numbers were extended in the protocol so that the sender must not wait until the packets were acknowledged in order to prevent a sequence number wrap.

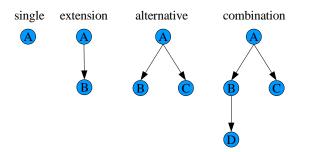

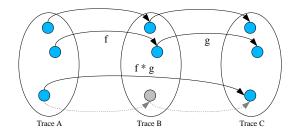

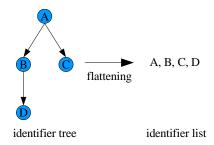

The scopes can also change in one system so that the identifier needs to change as well. These changes at the identifier are reflected in the combination of several identifier attributes in an identifier tree shown in figure 2.5. This identifier tree is a simplified descision tree[RN03], which is used to compare the attributes of two trace entries to determine if they were caused by the same operation. In the simple case, for example, the values of attribute A are compared with each other and in the extended case the values of B are used if the values of attribute A are equal. Likewise attribute C is used in the alternative case during the comparison if the attribute B was not found in both compared entries.

The primitives used to build these trees are *extension* and *alternative* which can be combined as shown in the figure 2.5. For example in the second tree, the attributes B is extended with attribute A in order to distinguish operations at a single port from the ones at other ports in an arbiter. Additionally two different paths of operations might join at a part of the system as shown in the third tree and a condition like A is needed to refer to either the identifier of the first or second type. Furthermore the identifier of an operation might get replaced by another identifier or removed because they are invalid at this place in the system This case is already captured by the primitive extension and alternative. By combining these three primitives, identifiers can be built which have a greater scope. Ideally the combined identifiers are unique across each entry caused by a specific operation in the system.

Figure 2.5: Identifier trees combining identifier attributes to compare entries.

The actual comparison of two trace entries starts at the root attribute in the identifier tree. Two entries are equal with respect to the identifier tree if the currently visited identifier attribute is equal and no attribute descibed in the children below is present in both entries. If the attribute has children in the tree, the first of these attributes is used for the comparison. When an attribute in the tree is not present in both entries or the values are not equal in both entries, the next sibling of the attribute is compared. Thus, several attributes can be used to compare two trace entries with each other.

### 2.5 **Operation Types**

Operation types distinguish different kinds of operations, for example DMA fetch operations from Sense/Controls operations. On their path through the system an operation is transformed between different protocols. Especially mainframes, with legacy devices and new devices, support a wide range of protocols to connect devices to the system where each of these protocols has grown on its own and has a different representation for each operation type. Additionally these operation types can describe different paths of operations based on the part of the system where they are used.

That is why an abstraction layer above the different representations of each operation type and the usage context is required, to be able to track operation paths through the entire system. These abstract operation types subsume the different protocol-specific operation types and are used to describe the different paths of each operation type around the entire system. In contrast, to the protocol-specific types which are usually based on the notion of sender and receiver, these abstract types are unique at a system level. For example, a DMA fetch operation would have entries in the sending trace of the bridge chip and the receiving trace the connected hub chip. Hence, the different types in both traces must be decoded to the same abstract operation type. Additionally the names of these abstract operation types.

The protocol-specific operation types must be mapped to abstract operation types. This mapping is distinguished in different complexities from simple over context-independent to context-dependent. In the *simple* mapping, the abstract type can be calculated by a one-to-one mapping from the protocol-specific type. This can be done with a table assigning to each operation-specific type an abstract type. In the *content-independent* mapping, several attributes in the entry are combined to determine the abstract operation type. For example, beside the type attribute in the entry an additional attribute might indicate if a response was requested. The *context-dependent* mapping is the most expressive one because it uses additional context information beside the several attributes to determine the abstract type. Currently this context includes the name of the chip and the trace, so that operation types in a functional unit used in different chips can be distinguished or the responses going either upbound or downbound can be mapped to different abstract types.

## Chapter 3

# State of the art

In this chapter the state of the art in information correlation will be presented. Correlation refers to the statistical notion where the similarity of two objects is described with a certain probability. In most cases in computer science, the developers want no fuzzy but safe results where two objects are only returned if they are correlated with 100% probability. This type of correlation is called matching. Several ideas or approaches will be analyzed to assess their applicability to the operation path reconstruction based on trace entries. Therefore, event correlation used in network management, string matching as a basic algorithm from introductory computer science courses and the current trace matching tool OHRMATCH are outlined and evaluated.

In order to evaluate the applicability to the reconstruction, criteria are needed to recognize the strengths and weaknesses of the approaches. Based on the problem description and the chapter 2, the following criteria covering non-functional, structural and entry-specific aspects have been chosen for the evaluation. The *generality* demanded by the problem description ensures that the approach is applicable to a broad range of chips and systems. Similarly, the *extensibility* ensures that later changes can incorporated without larger problem. The *understandability* is necessary so that a large range of users with different knowledge can use the method and correctly interpret the results. Additionally the approach must also cover all *structural primitives* like fan-in or fail-over found in the trace structure of I/O subsystems. Because the trace data of customer machines is only accessible after a problem occurred, the approach must deal with incomplete information due to *wrapped traces* in the correlation. The operation properties cause additional criteria like proper handling of *out-of-order* processing and of *one-to-many* relationships between entries. These relationships are necessary to express operation resends as well as the splitting and merging of operations.

In the management of complex networks the event correlation, also called alarm correlation, is used to condense information so that the root cause of a problem can be determined more easily [Tif02][Lew99]. This is particularly important for growing networks with an increasing number of events caused by

| Criteria          | Event correlation | String matching        | OHRMATCH                |

|-------------------|-------------------|------------------------|-------------------------|

| Generality        | ok                | ok                     | fail                    |

|                   |                   |                        | chip specific, only one |

|                   |                   |                        | operation type          |

| Extensibility     | ok                | ok                     | fail                    |

|                   |                   |                        | not modular enough      |

| Understandability | ok                | ok                     | fail                    |

|                   |                   |                        | understanding of        |

|                   |                   |                        | heuristics needed       |

| Structural primi- | ok                | fail                   | ok                      |

| tives             |                   | fail-over not possible |                         |

| Retrospective     | fail              | ok                     | ok                      |

| analysis          | only runtime      |                        |                         |

| Wrapped traces    | fail              | fail                   | ok                      |

|                   |                   | search text not defin- |                         |

|                   |                   | able                   |                         |

| Out-of-order      | ok                | fail                   | ok                      |

|                   |                   | strings are linear     |                         |

| One-to-many/      | ok                | fail                   | fail                    |

| Many-to-one       |                   | only one-to-one map-   |                         |

| relations         |                   | ping supported         |                         |

Table 3.1: Comparison of different approaches

attacks or failed components. An event is hereby a piece of information dealing with a problem for example a fault or an intrusion in the system. These events are created at several components of the systems like routers, switches or computers and are stored in log files or are transmitted to the correlator. The event correlators try to determine the causal relationship between the events to see which event caused another one and to condense simple events to more complex aggregated events. Many different approaches have been developed to correlate events based on dependency graphs between functional parts[Gru], rules and reasoning, models and reasoning, codebooks as well as learning approaches[Tif02]. Contrary to these approaches the generic method must support an easy way to deal with incomplete information due to wrapped traces. These approaches rely either on a global time or analyze data at runtime. But time is not an option for the trace matching and a runtime analysis is not possible at customer machines.

String matching tries to find a search text in a larger piece of text and is used for searching and filtering in computer science[Sed93, pp329]. The strings itself consist of a sequence of characters where the same character can occur multiple times. Traces can be interpreted as strings if the contained entries are interpreted as characters with a special equality relation which needs to be defined on the identifiers used in the trace entries. Hence, matching algorithms get applicable to the problem. Therefore, one of the popular string matching algorithms with linear time complexity in the worst-case like Knutt-Morris-Pratt or Boyer-Moore can be used. String matching supports only one structural primitive -

the direct connection - because normally only two strings are compared with each other. The fanin and fan-out case can be covered by extensions of these algorithms yielding the same worst-case complexity class as standard matching algorithms. In contrast, the fail-over case and out-of-order processing cannot be covered, due to the linearity of strings. In addition the string matching cannot deal with wrapped traces, because the search text cannot be defined easily. So the matching provides just a solution to a part of the problem and not general solution to the operation path reconstruction.

In the introduction the existing tool called OHRMATCH was mentioned. This tool matches the entries of in all traces of one chip and returns as result the corresponding entries in other traces and whether a response was received for the request. The matcher is a script written in ReXX which has grown over time to 22.000 lines of code, however it is chip-specific and is difficult to extend. The tool runs on pre-processed data and can be started in different modes to improve the matching quality. It is usually started at a deep trace which should contain entries about most operations found in other traces. Then the matcher tries to find corresponding entries in all preceding traces by comparing hard-coded identifiers at each entry. Therefore, the order of entries and chip-specific assumptions about the operation order are used to match with relatively high confidence in most cases. As a result, of the assumptions, the corner cases are not covered well. The tool is mainly used by the developer, who knows how to interpret the results of the matcher correctly, and how to tune certain parameters. Because the heuristics and the function must be comprehended first, the understandability is limited.

Hence, no approach fulfills the requirements. Thus, a new generic method must be developed based on some ideas of the approaches in order to satisfy the requirements.

## Chapter 4

# Approach

After explaining the necessary basics, this chapter presents the developed generic method to reconstruct the operation path based on trace entries. At the beginning the basic ideas behind the approach will be highlighted. These major design decisions help to understand the details in the further sections.

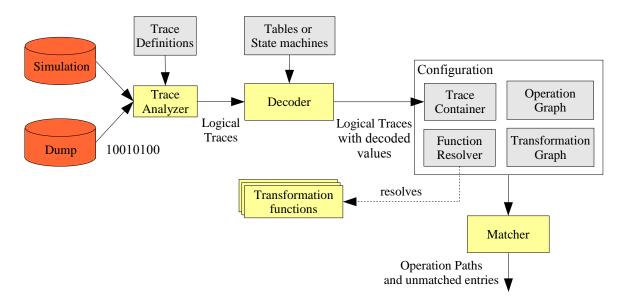

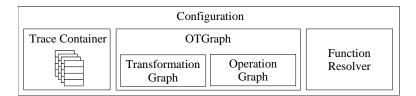

Since the method can be applied to single chips, multiple chips or a entire subsystem, the method need to be configured for the reconstruction. This configuration consists of transformation functions, several logical traces, a transformation graph and an operation graph presented in the next section. After this the matching algorithm will be described in detail. At the end several parameters will be introduced in order to analyse the time complexity of the algorithm for different configurations.

## 4.1 Basic ideas

The reconstruction of operation paths is based on identifiers in those operations which are part of the entries written to the traces. The identifiers are used to find matching entries of the same operation in adjacent traces. Because these identifiers are only valid during a certain period and region in the system, they must be designed to be unique in the adjacent traces and the traces must be stopped at nearly the same time. Additionally each trace must trigger at the same event when a new operation passes the trace.

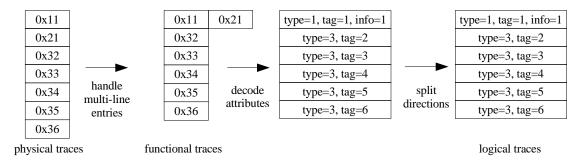

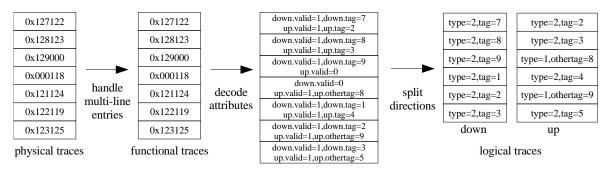

Traces have a totally different format so that *logical traces* were introduced as an abstraction. Due to this abstraction several traces can be created from one trace depending on the trace format, entries about the same operation are combined together and the attributes are extracted from data in the traces.

Because traces can wrap and contain different attributes, transformation functions map the attributes of the entries in the source trace to the one of the target trace. After transforming the identifier attributes, identifier trees are used to compare the transformed source entry to the target entry, because different

adjacent traces can use different attributes for the comparison. Therefore, the trees describe which attributes of the entries can be used to compare the entries with each other.

Traces usually contain 32 up to 256 entries so that a search starting at each entry is infeasible because an operation passes at average 10 traces in a single chip. So the method uses *no backtracking* and is done *stateless*. Therefore, no information gathered by earlier matches can be used for further matching in the operation path and wrong matching descisions cannot be revidated later on. Additionally the algorithm must be split in two steps, the *matching* part and the *operation path reconstruction*. During the matching, entries of the same operation are linked together so that the paths can be reconstructed later on.

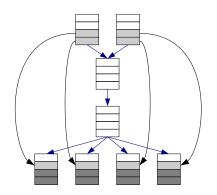

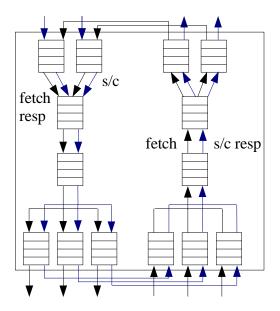

Figure 4.1: Local matching of entries in each locality.

Figure 4.2: Global matching of the unmatched entries across wrapped traces.

Based on the stateless approach, the matching is further split in a *local matching* and a *global matching* step. The local matching shown in figure 4.1, links entries in the localities described by the red circle together. As a result, not wrapped entries are linked together. During the global step in figure 4.2, a search for corresponding entries is done for each remaining grey unmatched entry across already wrapped traces. The number of unmatched entries is usually much smaller than the number of trace

entries, so that the branching factor and the time complexity are smaller for a search across all entries.

After the two matching steps the linked entries are checked against the operation graph, and paths are build based on the graph. The remaining dark grey entries stay unmatched because no other trace contains that old entries or the search depth.

## 4.2 Configuration

The old OHRMATCH use hard-coded information about the system structure and the trace format. In order to create a generic method, a configuration must contain every piece of information used to reconstruct the operation path. Therefore, the developed method requires several input data structures from logical traces over transformation graphs to operation graphs and functions to transform between entry representations in the traces. As a result, the approach is applicable for matching traces in a single chip, a subsystem or the entire system.

#### 4.2.1 Logical traces

Logical traces have been introduced to abstract from the physical traces described in section 2.1. These logical traces decouple the trace matching algorithm from the formats of the physical traces and the structure of the traced data. Additionally the transformation and operation graph are later defined based on the logical traces.

Therefore, the traces contain only entries caused by operations heading in *one direction*. For example, the physical trace d in figure 2.1 is split into two logical traces where one contains entries caused by operations heading to the processor and the other one contains operations in the direction of the devices. So the path of operations heading in certain directions can be later represented by a sequence of logical traces.

Contrary to physical traces found in hardware which contain entries in form of binary data without meaning, logical traces contain entries consisting of *attributes*. These attributes are name-value-pairs where the values can be of any type, but are usually are numbers or strings, for example an address or the name of an operation type.

Traces can start and stop recording passing operations so that an unpredictable period of time can pass between the traced operations. Therefore, the limited identifiers in the physical traces might have the same values because they traced during two different periods where the same identifier can be reused. In contrast, the logical traces contain only the entries since the last trace start event.

#### 4.2.2 Transformation function

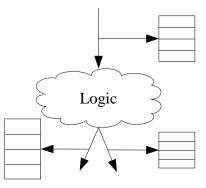

A transformation function transforms entries from a source logical trace in a way that they look like entries from the target logical trace. Additionally it describes which identifier tree - as presented in the identifier section 2.4 - must be used to compare two entries. For the matching the transformation of the attributes in this tree need to be described.

The function must abstract from the *logic between the traces* and also from the information written to the trace as shown in figure 4.3. For example, the logic in a functional unit can transform operations between two protocols which have different attributes and also identifiers. This unit transforms the source and target identifier of an operation according to the its translation table. So the traces on the operation paths before and after this unit contain entries, which have different attributes. The transformation function must transform those identifiers found in the source trace to the ones found in the target trace. This is accomplished by implementing a part of the chip logic which changes the identifiers, and uses other chip internal information like the translation table or registers.

The function represents which *information the logic writes to the trace*. Beside the changes at the operations from the logic, traces might record different information depending on the designers needs. For example, one trace can write the complete identifier in each entry and another trace just writes a pointer to an additional register in the entries. Since the matching relies on the information in the traces, these changes at the identifiers need to be transformed in the transformation function as well.

Figure 4.3: Transformation function abstracting the logic between and the format of the traces.

On the path of an operation through the system some traces have wrapped already. In order to combine the path fragments found before and after these wrapped traces, the transformation functions must be *transitive*. So the functions can be applied one after another, acting virtually as one function between the non-wrapped traces. For example in figure 4.4, two functions f and g can be applied one after another to an entry in trace A so that the transformed entry can be compared to the entries in trace C. The functions need to be transitive with respect to the identifier attributes so that no identifier attribute is lost by applying several functions in sequence.

Depending on the represented logic and the traced information, the functions vary in complexity from

Figure 4.4: Transitive combination of transformation functions.

an identity function, over functions using conditions for the mapping, to functions using chip internal information like registers values. In most cases a identity function is sufficient when the identifier attributes are stored in both traces. Some functions need to transform entries, for example the request type can be mapped to the response type at the border of the considered part of the system. Therefore, conditions are used to deal with the different cases. More complex functions may even use register values or translation tables to transform identifier attributes or to expand some bits of them.

The transformation function between a source and a target trace need to described the *forward* and *backward* transformation of entries. So even not injective functions can used for the entry transformation. Thereby the transformation of entries with the direction of the edge is called forward and the other way around backward.

#### 4.2.3 Transformation graph

The transformation graph describes which traces exist in the system and between which traces the matcher can transform with help of which transformation functions. A transformation graph is a directed graph whose nodes are logical traces which are connected by edges if a transformation function exists between both traces. The edges start at a source trace and end at a target trace, and the transformation functions are attached to them as markings. These graphs are *simple* and *transitive* so that between a pair of logical traces at most one edge can exist, and consecuting transformations must not be expressed with an additional function.

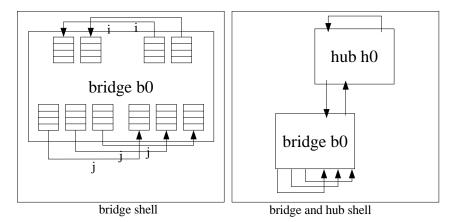

To support the reuse of these graphs, the transformation graph is modular. Therefore, each graph module can be instantiated in each another graph module with a instance name as prefix for the graph module. The instantiations must be cycle free so that a module cannot include another module which includes this module again. Each module has ports which are traces without outgoing edges that are not start or end point of a operation path. Due to these ports already defined transformation graph modules can be combined by connecting outgoing and ingoing ports with each other. So once written modules can be easily combined to get a chip level or system level transformation graph depending on the scope needed for the debug. For example, the graph module bridge describing a bridge chip shown in figure 4.5 is instantiated in the graph module bridge-shell in figure 4.6 with the prefix

Figure 4.5: Transformation graph module for a chip.

b0. All logical traces defined in bridge are accessible with the prefix b0 in bridge-shell. The shells are necessary in order to reuse the definitions. In the second example, two chips are combined for a chip-interaction analysis. Thus, the bridge and the hub module are reused and only a new shell is developed.

Figure 4.6: Different shells for single chip or interaction analysis between chips.

### 4.2.4 Operation graph

The operation graph describes for each operation type the subtasks and their sequence. In the old implementation[BFG<sup>+</sup>99], the subtasks of the operations were described as a sequence of events in a finite-state machine. Those events have been sent out on the completion of a subtask executed in a functional unit. By contrast, the operation graph in the generic method describes the subtasks of the operations as a sequence of logical traces. Since the traces are usually distributed across the functional

units in the chips, the logical traces contain an entry about an operation if the subtask was executed. As simplification it is assumed that the subtask is completed when the entry is written to the trace. So each trace contains only entries caused by one kind of event, when a subtask of a passing operation is executed.

The operation graph is a *typed* directed graph of logical traces where the abstract operation types are used as types. An edge starts at a source trace and ends at a target trace and two logical traces can be connected by edges of different operation types. The graph is *simple* and *modular* as the transformation graph described and in addition these graphs are *acyclic* so that for no type exists a logical trace which has a path to itself. Operation resends as well as operation splits and merges are not expressed in the operation graph, but can be handled by special flags at the transformation functions.

The example operation graph in figure 4.7 shows the operation paths for a DMA fetch operation and Sense/Controls operation described in section 2.2.

Figure 4.7: Operation graph for the operation types fetch and Sense/Controls with their responses.

In chips usually many request types are mapped to few response types. So one type is not sufficient to express the path of an operation with request and response through the system. Therefore, the graph must support *type conversions* which can connect these two different parts of operation path together. So an edge in the operation graph can have two different types - an outgoing type at the source trace and a incoming type at the target trace. The outgoing and incoming types are usually the same and are only different at the border of the considered part of the system.

The start of the operation path for a certain type is determined by the edges in the operation graph. If no incoming edge to a trace is found for an outgoing edge of a certain type, the operation path can start trace at this trace.

## 4.3 Algorithm

The matching algorithm uses the described configuration to match the entries, and returns then the reconstructed operation paths and the unmatched entries.

| Algorithm 1 Matching algorithm                                  |  |  |

|-----------------------------------------------------------------|--|--|

| Require: match configuration                                    |  |  |

| Ensure: match result with operation paths and unmatched entries |  |  |

| match local                                                     |  |  |

| match global                                                    |  |  |

| reconstruct the operation paths                                 |  |  |

The algorithm consists of three steps shown in algorithm 1, two matching steps and a final step where the operation paths are reconstructed from the created links between the entries. The first two steps are called local matching, because only adjacent traces get matched, and global matching where unmatched entries are matched across wrapped traces. In the last step the operation graph and the abstract operation types are used to reconstruct the operation paths from the linked entries. These paths can then be checked for completeness and inconsistencies.

### 4.3.1 Local matching

The local matching links only not wrapped entries from source and target traces in a locality together. A *locality* contains a source trace and all adjacent target traces plus the source traces for these target traces. For example, each presented primitive is a locality if no other trace is connected from the traces in the primitive. As a result, different trace processing orders can not cause side-effects like different links between entries.

Then all transformation functions which connect a source trace with a target trace in the locality are queried from the transformation graph. Afterwards all entries from the target traces are stored in a single list and a second list is populated with entries from the source traces transformed forward with the functions starting at the respective trace.

Later the identifier trees from each used transformation function get merged so that each entry on the source side can be compared to entries on the target side of the locality.

| Algo | orithm 2 Local matching between adjacent traces                                                   |

|------|---------------------------------------------------------------------------------------------------|

| Req  | uire: logical traces, transformation graph, transformation functions, identifier trees            |

| Ensu | ure: unmatched entries                                                                            |

| ,    | while unprocessed source traces left do                                                           |

| 2:   | get locality with source traces and target traces                                                 |

|      | for all source traces do                                                                          |

| 4:   | get the <i>entries</i> in the <i>source trace</i>                                                 |

|      | apply all transformation functions starting at the source trace to the entries                    |

| 6:   | add the transformed source entries to the source entries set                                      |

|      | end for                                                                                           |

| 8:   | for all target traces do                                                                          |

|      | add the entries from this target trace to the target entries set                                  |

| 10:  | end for                                                                                           |

|      | merge all identifier trees used between source traces and target traces to merged identifier tree |

| 12:  | for all source entries do                                                                         |

|      | set <i>duplicates</i> to the empty set                                                            |

| 14:  | while target entries do                                                                           |

|      | if <i>target entry</i> is unlinked <b>then</b>                                                    |

| 16:  | if source entry and target entry are equal with respect to the merged identifier tree and         |

|      | the masks <b>then</b>                                                                             |

|      | add <i>target entry</i> to the <i>duplicates</i> sort                                             |

| 18:  | end if                                                                                            |

|      | end if                                                                                            |

| 20:  | end while                                                                                         |

|      | if duplicates has only one target entry candidate then                                            |

| 22:  | link the source entry to the target entry candidate                                               |

|      | else if duplicates has more than one target entry candidate then                                  |

| 24:  | mark the entries in <i>duplicates</i> as duplicate                                                |

|      | end if                                                                                            |

| 26:  | end for                                                                                           |

| (    | end while                                                                                         |

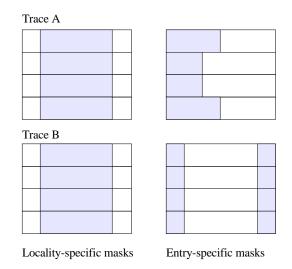

A *mask* describes which bits in an attribute have been written to the traces, for instance an address is usually not written completely to the trace but only the significant bits representing the memory region. Thus, only these bits can be used for the comparison. Masks are either *locality-specific* when the masks for an attribute are equal across all trace entries in the locality, or *entry-specific* if the masks change as shown on the right side in figure 4.8. In case of the locality-specific masks a linear ordering can be defined on the merged identifier tree with the in-order traversal of this tree. So the mask can be applied to all source and target entries before comparing the entries. As a result, the source and target entries can be sorted in an optimised local matching algorithm, and the comparison is then done in linear time afterwards. Depending on the masks either a standard or an optimised local matching algorithm can be used.

On the other side, the chosen standard algorithm makes no assumptions about the masks and uses

Figure 4.8: Locality-specific and entry-specific masks.

a nested loop to compare each source entry with the target entries. So before each comparison the masks of each identifier attribute must be combined and applied to the source and target entry so that only the bits present in both entries are used for the comparison. The inner loop finishes if all target entries have been compared to the source entry or a duplicate target entry was found. If no duplicate was found, both entries get linked together.

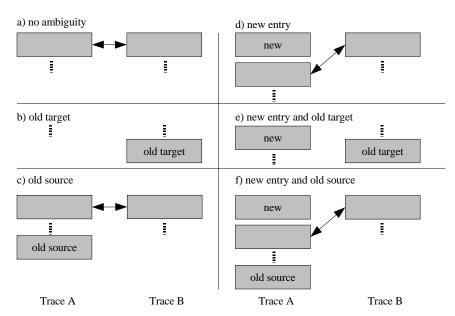

#### 4.3.2 Global matching

After the local matching is finished, several entries are not linked to an entry in the previous or next trace in the operation path. These unlinked entries can be caused by wrapped traces or duplicates. In order to complete these operation paths, the global matching tries to find corresponding entries by searching within the traces reachable from this trace in the transformation graph. Hence, deep traces or traces which contain only a part of the operations act as interpolation points for the matching. The search from the unlinked entry is only done in the directions where the link is missing, for example forward if no next entry is linked from this entry.

As described in the subsection 4.2.2, transformation functions can be applied one after another due to their transitivity property. So a transformed entry which was not found in a target trace, can be transformed again with the another function to the format of the next trace.

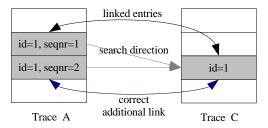

Because the format of the traces and of the contained identifier attributes can change along this search, the identifier attributes need to be merged similarly along this transformation. This merged identifier is then used to compare a transformed entry to an entry of the target trace. Therefore, the transformation function needs to define all identifier attributes even if they are not used for local matching because they are only in one of the connected traces. For example attrB in figure 4.9 can help to improve

the global matching if it is defined in the identifier trees between trace A and B as well as B and C. In addition the transformation functions between the trace A and B as well as B and C must not remove the attribute attrB.

Figure 4.9: Identifier attributes in global matching.

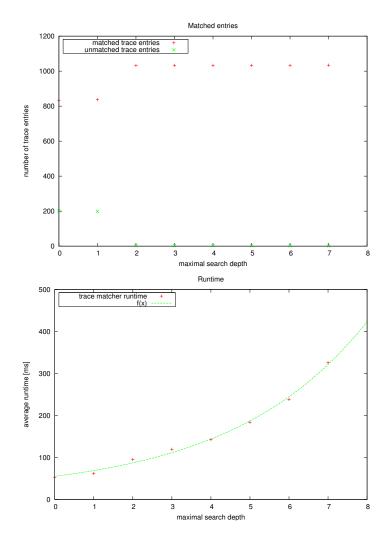

In order to choose the appropriate search algorithm[RN03, pp73], the requirements are used as guideline. All informed or other incomplete algorithms can be ignored because a robust and understandable method is needed for the debug. Since the method needs to be implemented at reasonable cost, space complexity is another important decision factor. Therefore, a depth-limited depth-first search algorithm was chosen to find entries for an operation in traces after a wrapped trace. The algorithm was modified so that it does not return if a match was found but searches further and remembers the best found match.

This algorithm is complete if the search depth is large enough. In addition, it has a space complexity of O(maximalDepth) and a time complexity of O(|N| + |E|) like other complete search algorithms.

| Algorithm 3 Global matching of unmatched entries                                                                |

|-----------------------------------------------------------------------------------------------------------------|

| Require: logical traces, transformation graph, transformation functions, identifier trees                       |

| for all traces do                                                                                               |

| 2: <b>for all</b> unmatched <i>entries</i> in <i>trace</i> <b>do</b>                                            |

| if <i>entry</i> is not linked to a next entry <b>then</b>                                                       |

| 4: search forward in the transformation graph from this <i>trace</i> for a <i>match</i> with the <i>entry</i>   |

| if match was found then                                                                                         |

| 6: link the found <i>unmatched entry</i> to the <i>match</i>                                                    |

| end if                                                                                                          |

| 8: end if                                                                                                       |

| if <i>entry</i> is not linked to a previous entry <b>then</b>                                                   |

| 10: search backward in the transformation graph from this <i>trace</i> for a <i>match</i> with the <i>entry</i> |

| if match was found then                                                                                         |

| 12: link the found <i>match</i> to the <i>unmatched entry</i>                                                   |

| end if                                                                                                          |

| 14: <b>end if</b>                                                                                               |

| end for                                                                                                         |

| 16: end for                                                                                                     |

|                                                                                                                 |