# Investigation on LIGA-MEMS and On-Chip CMOS Capacitors for a VCO Application

A Thesis Submitted to the

College of Graduate Studies and Research

in Partial Fulfillment of the Requirements for the Degree of

Master of Science

in the Department of Electrical and Computer Engineering

University of Saskatchewan

Saskatoon, Saskatchewan

by

Lina Fang

<sup>©</sup> Copyright Lina Fang, June 2007. All rights reserved.

### PERMISSION TO USE

In presenting this thesis in partial fulfillment of the requirements for a Postgraduate degree from the University of Saskatchewan, I agree that the Libraries of this University may make it freely available for inspection. I further agree that permission for copying of this thesis in any manner, in whole or in part, for scholarly purposes may be granted by the professor or professors who supervised my thesis work or, in their absence, by the Head of the Department or the Dean of the College in which my thesis work was done. It is understood that any copying or publication or use of this thesis or parts thereof for financial gain shall not be allowed without my written permission. It is also understood that due recognition shall be given to me and to the University of Saskatchewan in any scholarly use which may be made of any material in my thesis.

Requests for permission to copy or to make other use of material in this thesis in whole or in part should be addressed to:

Head of the Department of Electrical and Computer Engineering University of Saskatchewan Saskatoon, Saskatchewan, Canada S7N 5A9

### ABSTRACT

Modern communication systems require high performance radio frequency (RF) and microwave circuits and devices. This is becoming increasingly challenging to realize in the content of  $\cos t/\sin z$  constraints. Integrated circuits (ICs) satisfy the  $\cos t/\sin z$  requirement, but performance is often sacrificed. For instance, high quality factor (Q factor) passive components are difficult to achieve in standard silicon-based IC processes.

In recent years, microelectromechanical systems (MEMS) devices have been receiving increasing attention as a possible replacement for various on-chip passive elements, offering potential improvement in performance while maintaining high levels of integration. Variable capacitors (varactor) are common elements used in various applications. One of the MEMS variable capacitors that has been recently developed is built using deep X-ray lithography (as part of the LIGA process). This type of capacitor exhibits high quality factor at microwave frequencies.

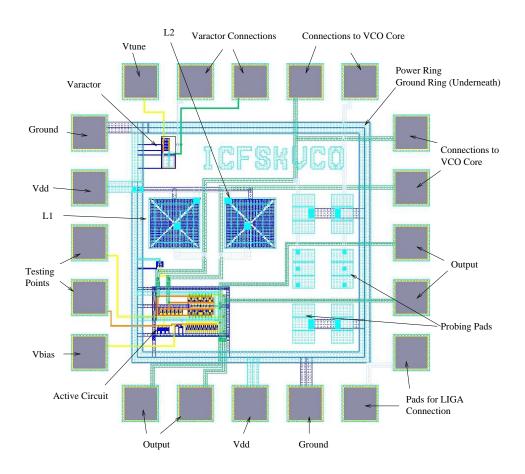

The complementary metal oxide semiconductor (CMOS) technology dominates the silicon IC process. CMOS becomes increasingly popular for RF applications due to its advantages in level of integration, cost and power consumption. This research demonstrates a CMOS voltage-controlled oscillator (VCO) design which is used to investigate methods, advantages and problems in integrating LIGA-MEMS devices to CMOS RF circuits, and to evaluate the performance of the LIGA-MEMS variable capacitor in comparison with the conventional on-chip CMOS varactor. The VCO was designed and fabricated using TSMC 0.18  $\mu$ m CMOS technology. The core of the VCO, including transistors, resistors, and on-chip inductors was designed to connect to either an on-chip CMOS varactor or an off-chip LIGA-MEMS capacitor to oscillate between 2.6 GHz and 2.7 GHz. Oscillator phase noise analysis is used to compare the performance between the two capacitors. The fabricated VCO occupied an area of 1 mm<sup>2</sup>.

This initial attempt at VCO fabrication did not produce a functional VCO, so the performance of the capacitors with the fabricated VCO could not be tested. However, the simulation results show that with this LIGA-MEMS capacitor, a 6.4 dB of phase noise improvement at 300 kHz offset from the carrier is possible in a CMOS-based VCO design.

#### ACKNOWLEDGEMENTS

I would like to thank my supervisors, Dr. David M. Klymyshyn and Dr. Anh Dinh, for their guidance, support and encouragement throughout this project.

I would like to thank Mr. Darcy Haluzan, who designed the LIGA-MEMS tunable capacitors, for providing me the corresponding data and all sorts of help.

I would like to thank CMC Microsystems (Canadian Microelectronics Corporation) for the CMOS integrated circuit fabrication, and the Institute of Microstructure Technology (IMT), Forschungszentrum Karlsruhe in Germany for LIGA related device fabrication.

I would like to thank the management and staff of Telecommunication Research Laboratories (TRLabs) for providing financial assistance and research facilities for the project. In particular, I would like to thank Garth Wells for his contributions to the integration and testing of the device.

# TABLE OF CONTENTS

| $\mathbf{P}$     | ERM               | ISSION TO USE                                   | i   |

|------------------|-------------------|-------------------------------------------------|-----|

| ABSTRACT         |                   |                                                 | ii  |

| $\mathbf{A}^{0}$ | CKN               | OWLEDGEMENTS                                    | iii |

| $\mathbf{T}_{A}$ | TABLE OF CONTENTS |                                                 |     |

| LI               | ST (              | F FIGURES                                       | vii |

| LI               | ST (              | F TABLES                                        | ix  |

| LI               | ST (              | F ABBREVIATIONS                                 | x   |

| 1                | Intr              | oduction                                        | 1   |

|                  | 1.1               | CMOS Radio Frequency Integrated Circuits        | 1   |

|                  | 1.2               | Introduction to MEMS                            | 2   |

|                  | 1.3               | LIGA Process                                    | 3   |

|                  | 1.4               | LIGA-MEMS Variable Capacitor                    | 6   |

|                  | 1.5               | Introduction to VCO                             | 6   |

|                  | 1.6               | Motivation                                      | 8   |

|                  | 1.7               | Objectives                                      | 9   |

|                  | 1.8               | Thesis Organization                             | 9   |

| 2                | $\mathbf{VC}$     | ) Background                                    | 10  |

|                  | 2.1               | Voltage-Controlled Oscillator                   | 10  |

|                  |                   | 2.1.1 Types of Oscillators                      | 10  |

|                  |                   | 2.1.2 Barkhausen Criteria                       | 12  |

|                  |                   | 2.1.3 Negative Resistance Oscillator Principles | 13  |

|                  |                   | 2.1.4 Resonator Principles                      | 15  |

|   | 2.2  | Qualit  | ty Factor $(Q)$                                         | 6  |

|---|------|---------|---------------------------------------------------------|----|

|   | 2.3  | Phase   | Noise                                                   | 7  |

|   |      | 2.3.1   | Definition                                              | 8  |

|   |      | 2.3.2   | Leeson's Phase Noise Model                              | 20 |

|   |      | 2.3.3   | LTV Phase Noise Model                                   | 23 |

|   |      | 2.3.4   | Figure of Merit                                         | 28 |

| 3 | VC   | O Desi  | $_{ m ign}$                                             | 9  |

|   | 3.1  | Design  | n Issues                                                | 29 |

|   |      | 3.1.1   | CMOS Fabrication Technologies                           | 9  |

|   |      | 3.1.2   | Oscillator Design Approaches                            | 0  |

|   |      | 3.1.3   | Oscillator Topologies                                   | 1  |

|   |      | 3.1.4   | Resonator Components                                    | 6  |

|   |      |         | 3.1.4.1 Spiral Inductor                                 | 6  |

|   |      |         | 3.1.4.1.1 CMOS Spiral Inductor Modeling 3               | 6  |

|   |      |         | 3.1.4.1.2 Design Guidelines for CMOS Spiral Inductors 3 | 9  |

|   |      |         | 3.1.4.2 CMOS Variable Capacitors                        | 0  |

|   |      |         | 3.1.4.3 MIM Capacitors                                  | 5  |

|   |      |         | 3.1.4.4 LIGA-MEMS Capacitor                             | 6  |

|   |      |         | 3.1.4.4.1 Capacitor Design and Fabrication 4            | 6  |

|   |      |         | 3.1.4.4.2 Capacitor Specification 4                     | 9  |

|   |      |         | 3.1.4.4.3 Capacitor Integration 5                       | 0  |

|   | 3.2  | System  | natic Design                                            | 2  |

|   |      | 3.2.1   | Design Flow                                             | 2  |

|   |      | 3.2.2   | CMOS Varactor                                           | 3  |

|   |      | 3.2.3   | CMOS Inductors                                          | 4  |

|   |      | 3.2.4   | Bonding Wires                                           | 4  |

|   |      | 3.2.5   | Transistors                                             | 7  |

|   | 3.3  | Analy   | sis                                                     | 9  |

| 4 | Circ | cuit La | ayout 6                                                 | 0  |

|   | 4.1 | Layou   | t Basics                                                  | 60 |

|---|-----|---------|-----------------------------------------------------------|----|

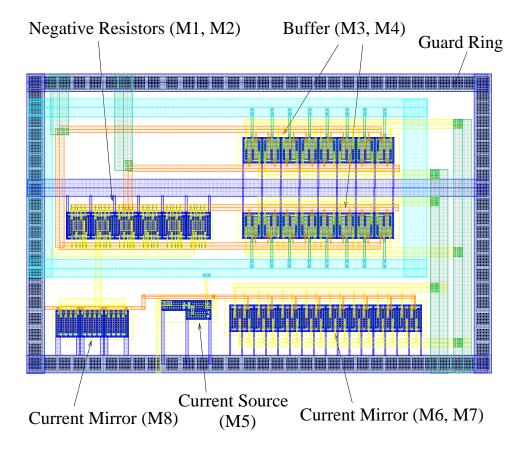

|   | 4.2 | VCO     | Circuit Layout                                            | 61 |

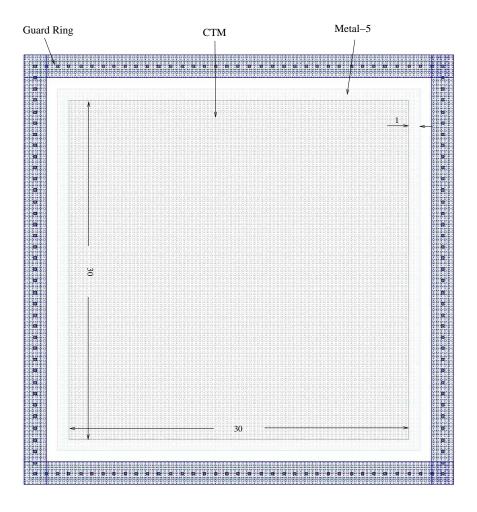

|   |     | 4.2.1   | Inductor Layout                                           | 61 |

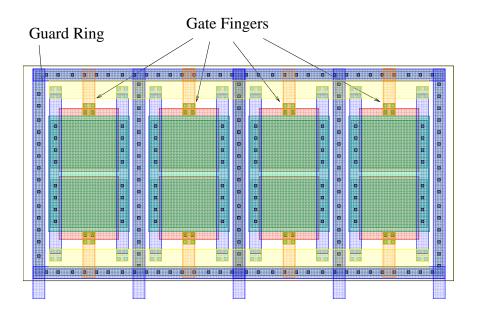

|   |     | 4.2.2   | Transistor Layout                                         | 62 |

|   |     | 4.2.3   | Varactor Layout                                           | 63 |

|   |     | 4.2.4   | VCO Chip Layout                                           | 65 |

| 5 | Res | ults    |                                                           | 68 |

|   | 5.1 | Simula  | ation Results                                             | 68 |

|   |     | 5.1.1   | Simulation Tool                                           | 68 |

|   |     | 5.1.2   | Simulation Results Using CMOS Varactor                    | 69 |

|   |     | 5.1.3   | Simulation Results Using Fabricated LIGA-MEMS Capacitor . | 72 |

|   |     | 5.1.4   | Simulation Results Using Other Possible LIGA-MEMS Designs | 74 |

|   |     | 5.1.5   | Performance Comparison                                    | 75 |

|   | 5.2 | Measu   | arement Results                                           | 77 |

|   |     | 5.2.1   | Measurement                                               | 77 |

|   |     | 5.2.2   | Discussion                                                | 81 |

| 6 | Cor | nclusio | n                                                         | 84 |

|   | 6.1 | Concl   | usion                                                     | 84 |

|   | 6.2 | Recon   | nmendations for Future Work                               | 85 |

|   |     | 6.2.1   | Recommendations on VCO Design                             | 85 |

|   |     | 6.2.2   | Recommendations on LIGA-MEMS Capacitor Design             | 87 |

|   |     | 6.2.3   | Recommendations on Integrations & Fabrications            | 87 |

# LIST OF FIGURES

| 1.1  | Parallel Plate Capacitor Designs                                     | 3  |

|------|----------------------------------------------------------------------|----|

| 1.2  | Lateral Comb Capacitor Design [4]                                    | 4  |

| 1.3  | Shunt Mounted Capacitor Design [5]                                   | 4  |

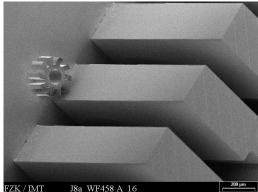

| 1.4  | LIGA Structure Examples                                              | 5  |

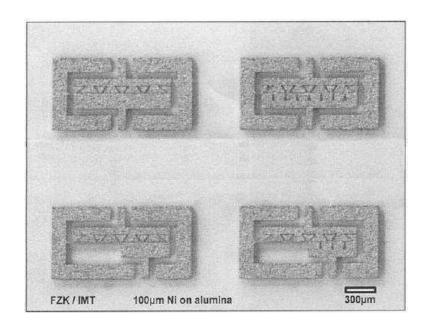

| 1.5  | LIGA MEMS Variable Capacitors [14]                                   | 7  |

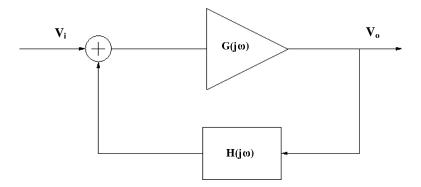

| 2.1  | Block Diagram of Feedback Circuit                                    | 12 |

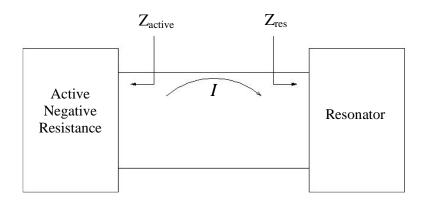

| 2.2  | One-port Negative Resistance Oscillator Model                        | 14 |

| 2.3  | Second Order Parallel Resonator                                      | 17 |

| 2.4  | Effect of Oscillator Phase Noise                                     | 18 |

| 2.5  | Sine Wave with Phase Fluctuation                                     | 19 |

| 2.6  | Single Sideband Phase Noise to Carrier Ratio                         | 20 |

| 2.7  | Phase Noise in Leeson's Model                                        | 23 |

| 2.8  | Impulse Responses of Oscillator                                      | 25 |

| 2.9  | Evolution of Circuit Noise into Phase Noise                          | 27 |

| 3.1  | Two Common Oscillator Configurations: (a) Colpitts and (b) Hartley   | 32 |

| 3.2  | Modeling Colpitts Oscillator: (a) Oscillator Circuit AC Model. (b)   |    |

|      | Modeling Transistor. (c) Modeling Transformer. (d) Simplified Model. | 32 |

| 3.3  | (a) NMOS-Only Cross-Coupled Oscillator (b) Complementary Cross-      |    |

|      | Coupled Oscillator                                                   | 34 |

| 3.4  | Cross-Coupled Negative Resistance                                    | 35 |

| 3.5  | A Typical Spiral Inductor Layout                                     | 37 |

| 3.6  | Lumped-Element Model of an On-Chip Spiral Inductor: (a) Low Fre-     |    |

|      | quency Model and (b) High Frequency Model                            | 38 |

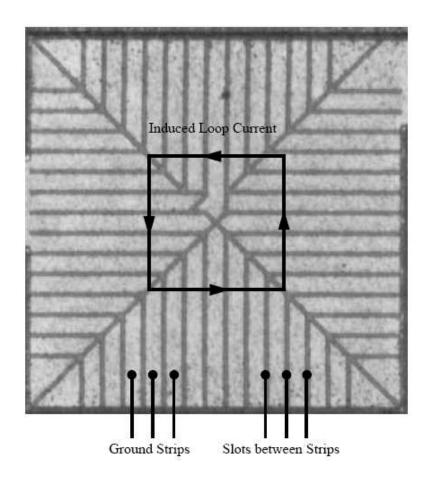

| 3.7  | Patterned Ground Shield [42]                                         | 41 |

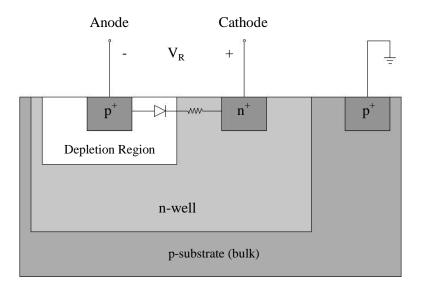

| 3.8  | PN Junction Varactor                                                 | 41 |

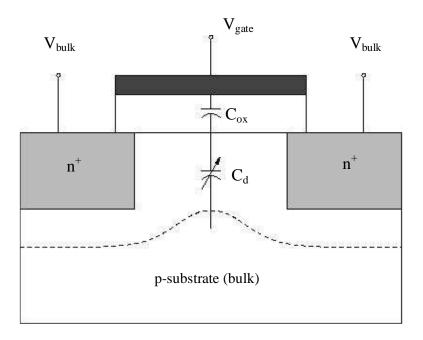

| 3.9  | NMOS varactor                                                        | 42 |

| 3.10 | Capacitance in NMOS varactor                                         | 43 |

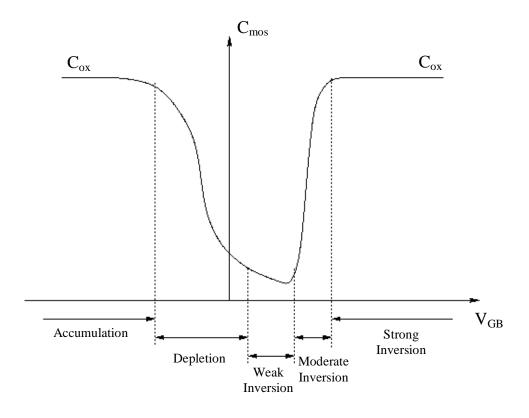

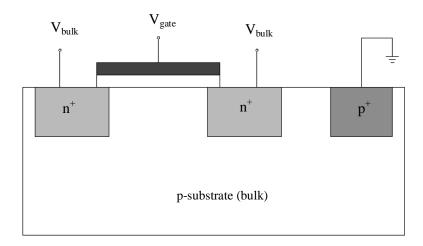

| 3.11 | Inversion Mode MOS Varactor                                           | 44 |

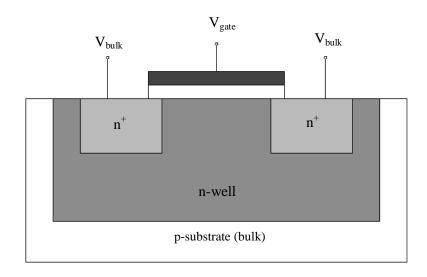

|------|-----------------------------------------------------------------------|----|

| 3.12 | Accumulation Mode MOS Varactor                                        | 45 |

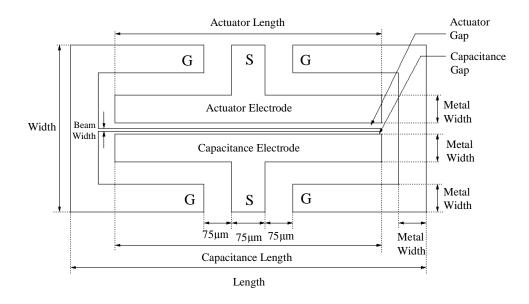

| 3.13 | Three-Plate Cantilever Beam Capacitor                                 | 46 |

| 3.14 | Top View of the Capacitor [14]                                        | 47 |

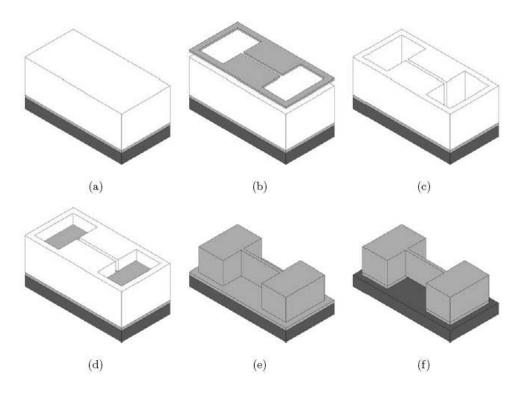

| 3.15 | LIGA-MEMS Capacitor Fabrication Steps [14]                            | 48 |

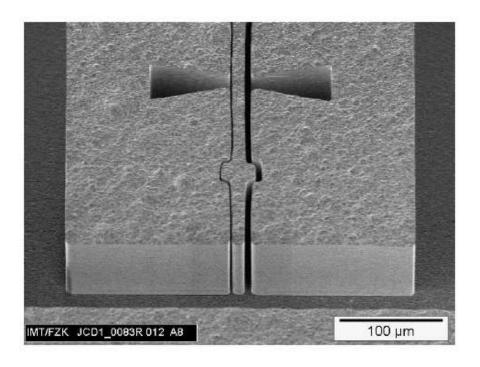

| 3.16 | Micrograph of LIGA-MEMS Capacitor [14]                                | 49 |

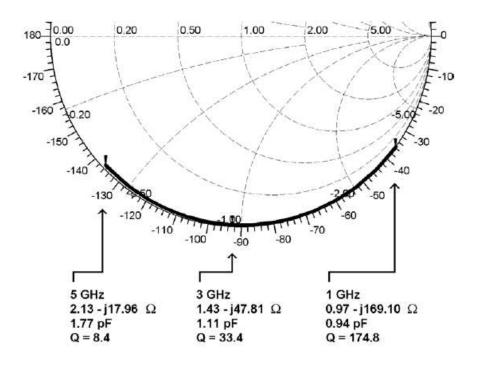

| 3.17 | Measured LIGA Capacitor $S_{11}$ [14]                                 | 50 |

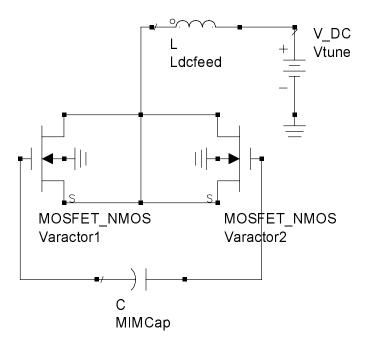

| 3.18 | CMOS Varactor Schematic in ADS                                        | 53 |

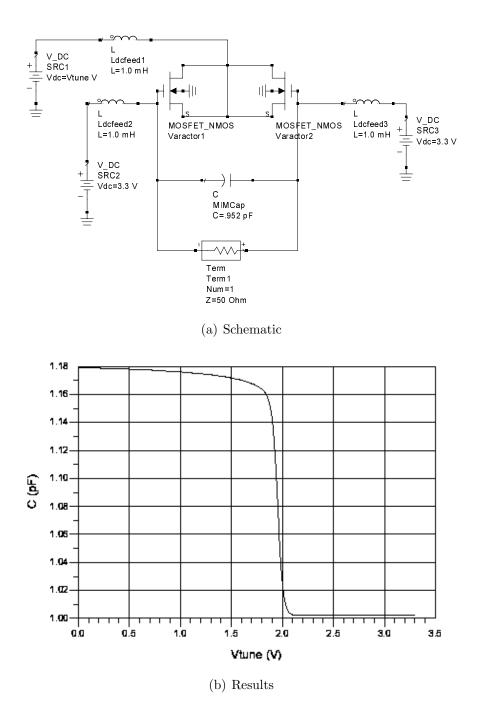

| 3.19 | CMOS Varactor Capacitance Simulation at 2.7 GHz                       | 55 |

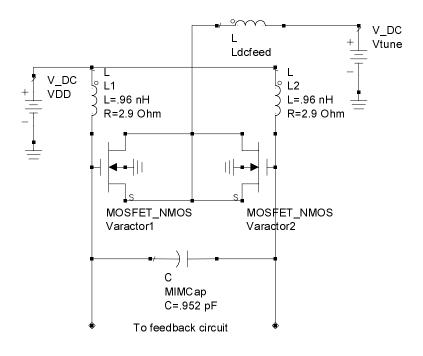

| 3.20 | Resonant Tank Schematic in ADS                                        | 56 |

| 3.21 | A Simple VCO Schematic in ADS                                         | 57 |

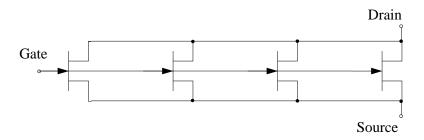

| 3.22 | A Example of Multiple Transistors in Parallel                         | 58 |

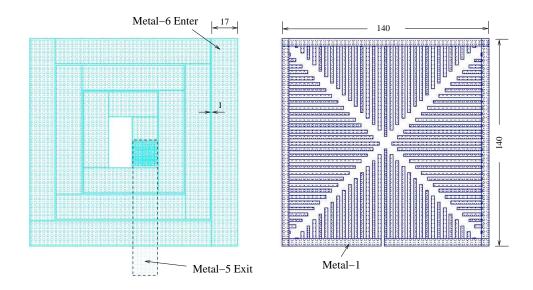

| 4.1  | Cadence Inductor Layout (left) and PGS Layout (right)                 | 62 |

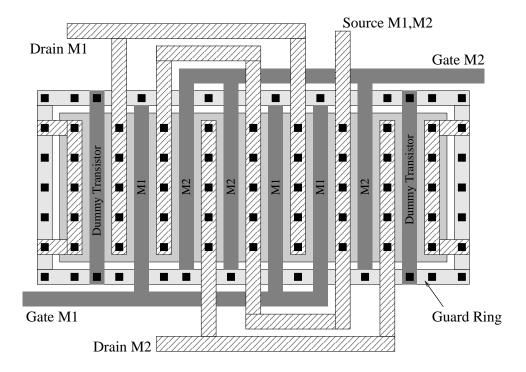

| 4.2  | Common-Centroid Transistor Layout Example for Differential Circuits   | 63 |

| 4.3  | Active Part of the VCO Layout                                         | 64 |

| 4.4  | MIM Capacitor Layout                                                  | 65 |

| 4.5  | NMOS Varactor Pair Layout                                             | 66 |

| 4.6  | VCO Chip Layout                                                       | 67 |

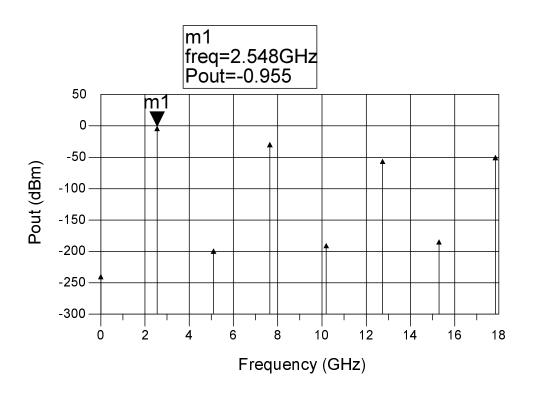

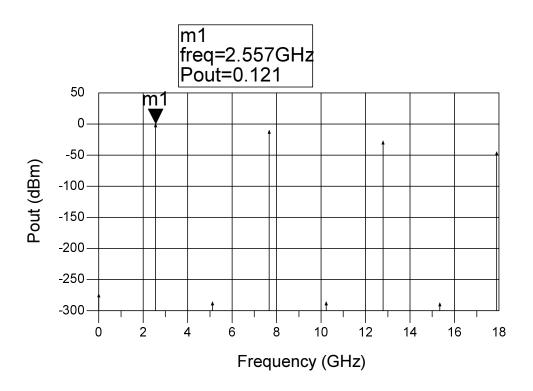

| 5.1  | Output Power of VCO with Varactor                                     | 70 |

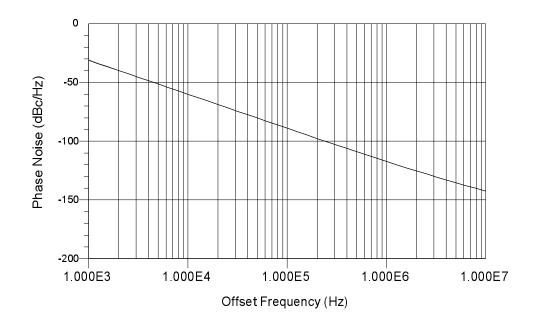

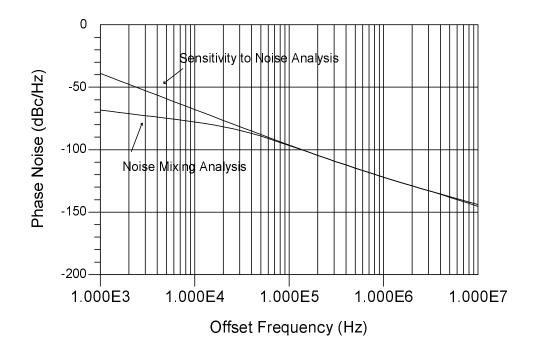

| 5.2  | Phase Noise of VCO with Varactor                                      | 71 |

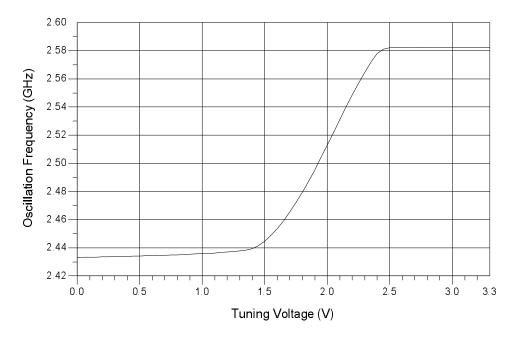

| 5.3  | Frequency Tuning of the VCO with Varactor                             | 71 |

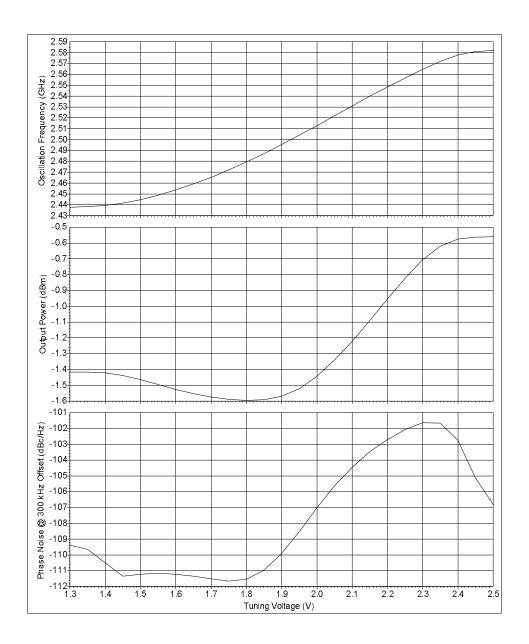

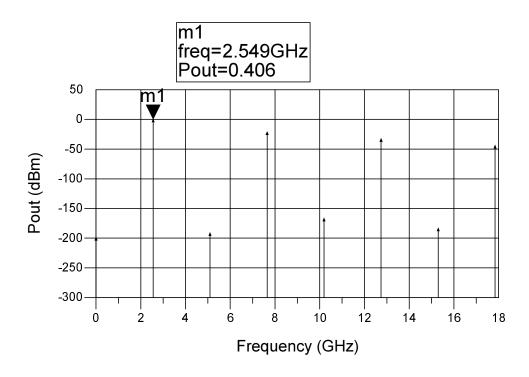

| 5.4  | VCO Tuning                                                            | 72 |

| 5.5  | Output Power of VCO with Fabricated LIGA-MEMS Capacitor $\ . \ . \ .$ | 73 |

| 5.6  | Phase Noise of VCO with Fabricated LIGA-MEMS Capacitor $\ \ .$        | 74 |

| 5.7  | Output Power of VCO with Copper LIGA-MEMS Capacitor                   | 75 |

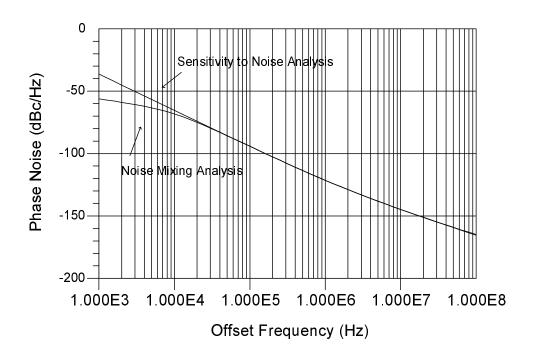

| 5.8  | Phase Noise of VCO with Copper LIGA-MEMS Capacitor                    | 76 |

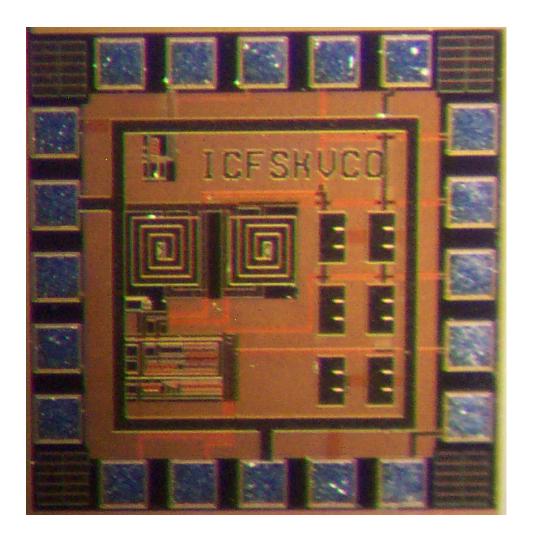

| 5.9  | Fabricated VCO Chip                                                   | 78 |

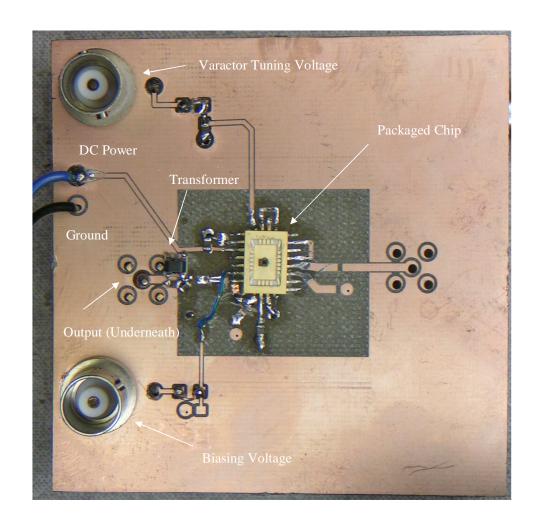

| 5.10 | Packed VCO Chip On the Testing Board                                  | 79 |

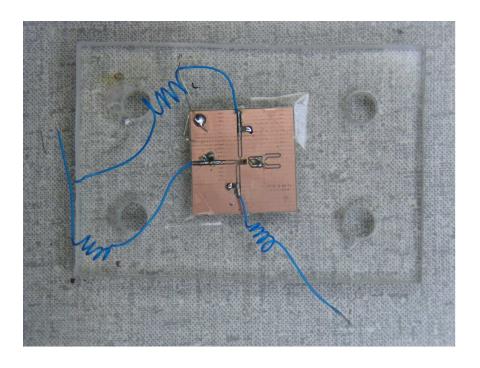

| 5.11 | Loose Die VCO On the Testing Board                                    | 81 |

# LIST OF TABLES

| 3.1 | LIGA-MEMS Capacitor Dimensions [14]        | 47 |

|-----|--------------------------------------------|----|

| 3.2 | Inductance and Resistance of Bonding Wires | 56 |

| 3.3 | Transistors Parameters                     | 58 |

| 4.1 | Spiral Inductor Parameters at 2.7 GHz      | 62 |

| 5.1 | VCO Comparison                             | 76 |

| 5.2 | DC Voltage Levels In the VCO Circuit       | 79 |

## LIST OF ABBREVIATIONS

ADS Advanced Design System

ASITIC Analysis and Simulation of Spiral Inductors and

Transformers for ICs

BJT Bipolar Junction Transistor

CAD Computer Aided Design

CMOS Complementary Metal Oxide Semiconductor

CPW Coplanar Waveguide

CTM Capacitor Top Metal

DXRL Deep X-ray Lithography

EDM Electro Discharge Machining

FET Field Effect Transistor

FOM Figure Of Merit

FZK Forschungszentrum Karlsruhe (Research Centre Karlsruhe)

GaAs Gallium Arsenide

HB Harmonic Balance

HFSS High Frequency Structure Simulator

IC Integrated Circuit

IF Intermediate Frequency

IMT Institute of Microstructure Technology

LC Inductor Capacitor (Passive Network)

LO Local Oscillator

ISF Impulse Sensitivity Function

LIGA German acronym for Lithography, Electroforming, and Moulding

(Lithographie, Galvanoformung, Abformung)

LTI Linear Time-Invariant

LTV Linear Time-Varying

MEMS Microelectromechanical Systems

MIM Metal-Insulator-Metal (Capacitor)

MOS Metal Oxide Semiconductor

MOSFET Metal Oxide Semiconductor Field Effect Transistor

MUMPS Multi-user MEMS Process

NMOS N-type Metal Oxide Semiconductor

PGS Patterned Ground Shield

PLL Phase-Locked-Loop

PMMA Polymethyl Methacrylate

PMOS P-type Metal Oxide Semiconductor

RC Resistor Capacitor (Passive Network)

RF Radio Frequency

RLC Resistor, Inductor and Capacitor (Passive Network)

SEM Scanning Electron Microscope

SOC System-On-Chip

TSMC Taiwan Semiconductor Manufacturing Company

UJT Unijunction Transistor

VCO Voltage-Controlled Oscillator

YIG Yittrium Iron Garnet

#### 1. Introduction

# 1.1 CMOS Radio Frequency Integrated Circuits

The explosive growth in wireless telecommunications has brought the field of radio frequency (RF) circuit design to a renaissance. It is advantageous from cost and size perspectives to integrate RF transceiver front-end components into a single chip with the back-end baseband components. Thus, radio transceiver design is merging with integrated circuit (IC) design, particularly in CMOS (complementary metal oxide semiconductor). CMOS technology has become the most popular technology in digital design. It has three major advantages: high integration level, low cost, and low power consumption. The rapid advancement in CMOS technology and the continuous down-scaling the size of CMOS device has made low cost, small size RF integrated circuits feasible.

However, difficulties exist in synthesizing RF integrated circuits on CMOS. Due to the lossy silicon substrate, performance of CMOS circuits at microwave frequencies (i.e., > 1 GHz) is an issue. High quality (Q) passive components are difficult to achieve in CMOS due to the nature of materials and fabrication process. These factors make CMOS RF integrated circuit design an interesting and challenging area to study.

RF circuits are typically made up of many passive components. Since integrated circuit processes were mainly developed to satisfy the demands of digital circuits, passive components are limited and often unsatisfying to the RF IC designers. For example, CMOS inductors occupy large chip area and have poor Q-factor (typically less than 10) and low self-resonant frequency (a few GHz). CMOS capacitors also exhibit low Q-factor. New techniques, such as metal-insulator-metal (MIM) capacitors

and thick top layer metal inductors, have been introduced to CMOS, which provide relatively higher quality [1]. However, traditional CMOS passive components are still inadequate for high performance applications with increasing operating frequencies, and alternative technologies for realizing high performance passive components are the subject of recent research.

#### 1.2 Introduction to MEMS

In recent years, microelectromechanical systems (MEMS) have been receiving increasing attention. As the name suggested, MEMS are devices in the micrometer scale. They typically range in size from the sub-micron to 100's of microns.

MEMS technology promises high integration abilities between structural mechanical devices and electronics. But by not being strictly tied to CMOS electronics, MEMS offers the potential for improved performance. Also, MEMS processes, which are similar to integrated circuit fabrication and suitable for high volume production, make MEMS devices potentially inexpensive.

There are numerous possible applications for MEMS. MEMS products are found in medical devices, optical devices, sensors, actuators and many different areas. In RF circuits such as voltage-controlled oscillators (VCOs), phase shifters, MEMS devices are used as switches, filters, inductors, and variable capacitors (also known as varactors).

There are a number of MEMS microfabrication technologies. Silicon surface micromachining makes completely assembled mechanical systems. Silicon bulk micromachining uses either etches that stop on the crystallographic planes of a silicon wafer or etches that act isotropically to generate mechanical parts. These techniques combined with wafer bonding and boron diffusion allow complex micro-mechanical devices to be fabricated. Another technique in MEMS fabrication is called LIGA, which will be introduced in the next section.

Most of the existing MEMS capacitors are fabricated using silicon-based thin film processes, such as the multi-user MEMS process (MUMPS). Typically they fall into three categories. The first type is the parallel plate designs in which planar

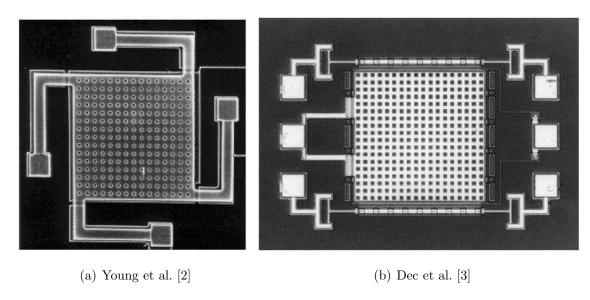

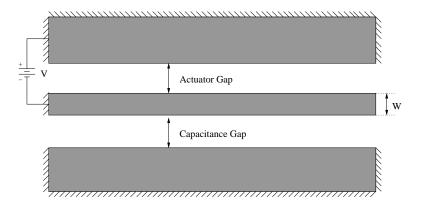

geometries and the plates are parallel to the substrate. The capacitance is varied by changing the gap between the plates. These capacitors typically have capacitance values between 1 - 4 pF, and are targeted for applications in lower end of the microwave frequency range (1 - 3 GHz) [2,3]. Figure 1.1 shows some examples of this type of capacitors.

Figure 1.1: Parallel Plate Capacitor Designs

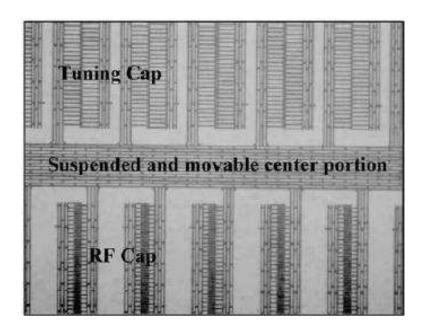

A second type are the lateral comb designs. They have comb-shaped fingers overlapping each other and the capacitance is varied by adjusting the overlap. Figure 1.2 shows an example of these capacitors [4].

A third type is shunt mounted designs. These are a variation of the parallel plate design and intended to operate at higher frequency. A bridge shunt mounted over a coplanar waveguide (CPW) transmission line forms the capacitor instead of two plates. Figure 1.3 shows an example of this type of capacitor, which can operate above 10 GHz [5].

### 1.3 LIGA Process

LIGA is the German acronym for lithografie, galvanoformung, and abformung, which means lithography, electrodeposition, and moulding. The LIGA technology

Figure 1.2: Lateral Comb Capacitor Design [4]

Figure 1.3: Shunt Mounted Capacitor Design [5]

makes miniature parts with spectacular accuracy and structural quality. Electro discharge machining (EDM) extends conventional machine shop technology to make sub-millimeter sized parts [6].

The complete LIGA process involves deep X-ray lithography (DXRL) using syn-

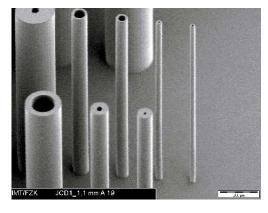

chrotron radiation, electroplating of metals, and replication using moulding techniques. The LIGA process was developed during the 1980's in Germany at the Research Centre Karlsruhe (Forschungszentrum Karlsruhe) as a method to produce tiny and precise separation nozzles for uranium isotopes [7,8]. The unique advantage of the LIGA process, due to the strong penetration ability of high energy X-rays, is that it can produce structures with extremely high vertical aspect ratios (greater than 100). Also, the structures can have greater than 89.9° and optically smooth sidewalls, and can be very tall (hundreds of microns or even millimetres), while the lateral feature sizes can be smaller than one micron. No other fabrication technique so far can provide comparable structure quality. Figure 1.4 shows two examples of structures fabricated using LIGA, which demonstrate the tiny but precise features of LIGA devices [9, 10].

(a) 1100  $\mu$ m Posts in SU-8 with Minimum (b) 1100  $\mu$ m PMMA Frames & 125  $\mu$ m Nickel 7  $\mu$ m internal diameter holes [9] Turbine [10]

Figure 1.4: LIGA Structure Examples

The unique properties of the LIGA process have led to an interest in developing high performance RF/microwave LIGA devices. Researches on microwave LIGA devices include transmission lines, filters, and couplers have been reported [11–13].

# 1.4 LIGA-MEMS Variable Capacitor

As described in Section 1.2, most of the traditional MEMS variable capacitors operate either at the lower end of the microwave frequency range below 3 GHz (planar parallel plate designs and lateral comb structure designs), or in the 10 - 40 GHz range (shunt mounted designs). In the 3 - 10 GHz frequency range, current techniques have difficulty realizing high Q-factor variable capacitors. The LIGA technology could potentially fill the gap.

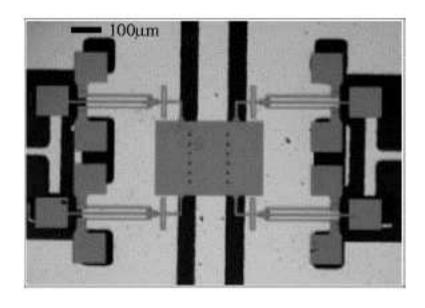

LIGA-MEMS variable capacitors have demonstrated promising performance [14]. The capacitor designs feature parallel plates and the capacitance is varied by changing the gap between the plates. But unlike traditional planar parallel plate capacitors, in the LIGA-MEMS capacitor designs, the parallel plates are perpendicular to the substrate. This vertical structure is suitable to realize with the LIGA technology because of the high aspect ratio possibilities of the vertical plates. The use of thick metal structure reduces the resistance, while use of the vertical dimension results in an electrically compact structure and also separates the fields from the substrate, both of which result in devices with high Q-factors and high self-resonance frequencies. The use of alumina and other low-loss substrates, avoiding the lossy silicon substrates, also leads to improved performance. The LIGA-MEMS variable capacitors exhibit excellent properties for microwave frequency applications.

#### 1.5 Introduction to VCO

Most electronic signal processing systems require frequency or time reference signals. For the lower end of the spectrum, the stable quartz crystals can be used as resonators to build high accuracy fixed frequency reference signals. For higher frequencies, the quality of crystal resonators degrades due to physical limitations and material properties. Many communications applications require programmable carrier frequencies. For these applications, multiple crystal resonators usually would not be used due to the limitations in cost and size. In such cases, RF oscillators, whose frequency can be controlled with a control signal are used.

Figure 1.5: LIGA MEMS Variable Capacitors [14]

Oscillators are one-port devices that consume DC power and generate periodic signals at certain frequencies without any input signal. Often, the oscillation frequency can be controlled by a voltage (or, in some cases, current). This kind of device is called a voltage-controlled oscillator.

The VCO is a very important component in a phase-locked-loop (PLL). PLLs are widely used in analog and digital systems. For example, PLLs are used in clock recovery in communication and digital systems, in frequency synthesizers used in wireless communication systems to select different channels, and in modulation and demodulation of frequency or angle modulated carriers.

Technology evolutions have pushed realization of VCOs into the GHz range. The better propagation characteristics and the larger available bandwidth in the 1 GHz to 2 GHz range have allowed the standardization and exploitation of digital cellular phone systems worldwide. At higher frequencies around 2.5 GHz to 5 GHz, new wireless data applications have spurred a lot of interest and large markets, such as short range automation applications, and cable replacement wireless links. These new applications set a large demand for high performance GHz VCOs. Internet growth and the convergence of data and voice communications, which deploys Gbit/sec data channels and relies on clock recovery architectures, also increases the

demand for GHz VCOs [15].

Recent research on RF VCOs is generally focused on IC technologies [16–20]. The choice of IC technology is mainly driven by the requirements of the majority of the circuits, which are usually digital. Price, package, performance and power are four "P words" that govern high volume markets. For the VCO itself, integration has advantages in terms of cost, package and power consumption. ICs reduce production cost by allowing mass production. Integrating VCOs in ICs allows easy integration between VCOs and other RF components. ICs allow low voltage operation which results an advantage in power consumption. Using ICs for RF typically results in a lower performance, such as noise.

## 1.6 Motivation

The LIGA technology provides a new method of fabricating high quality passive components. The LIGA-MEMS variable capacitors mentioned in the previous section have shown performance advantages over conventional CMOS varactors, and promising potential in RF circuits. However, capitalizing on these advantages in RF circuits and still maintaining high levels of integration likely require effectively integrating such devices with RF ICs.

CMOS has become a mainstream of RF IC design, while the CMOS on chip passive components are not satisfying the increasingly demanding performance requirements of the fast advancing telecommunication systems. There is a good potential for the high quality LIGA-MEMS passive components as a replacement for CMOS passive components in performance-oriented RF circuits.

As for replacing the CMOS passive components with LIGA-MEMS devices, many issues must be considered. How can the LIGA-MEMS devices be integrated into the CMOS chip? How much improvement can the MEMS dvice achieve in the RF circuit performance? Which passive components should have the priority of being replaced? Will the CMOS and LIGA fabrication processes conflict?

# 1.7 Objectives

This thesis focuses on developing a CMOS VCO circuit based on existing LIGA-MEMS capacitor designs [14], as the first attempt to integrate CMOS RF integrated circuits with LIGA-MEMS devices, and to exemplify the performance advantages of LIGA-MEMS devices over conventional CMOS passive components in RF circuits. To the author's knowledge, no LIGA passive component has been integrated with CMOS circuitries for RF applications. The specific objectives of the research are summarized as follows:

- 1. Develop a CMOS VCO circuit in the 2.6 2.7 GHz range which can use either an on-chip CMOS varactor or a LIGA-MEMS variable capacitor as the tuning component.

- 2. Investigate possible methods for integrating the LIGA-MEMS variable capacitor to the CMOS circuitry.

- 3. Simulate and compare the performance of the VCO using the on-chip CMOS variator and LIGA-MEMS variable capacitor.

- 4. Fabricate the VCO chip and integrate it with the fabricated LIGA-MEMS variable capacitor and the on-chip varactor.

- 5. Test the VCO circuit and determine the performance against the simulation results.

# 1.8 Thesis Organization

This thesis is organized into six chapters. Chapter 2 presents background theories related to CMOS RF integrated circuit design. Chapter 3 describes the VCO design procedure, including design issues to be considered and schematic design. Chapter 4 describes the VCO layout in CMOS. Chapter 5 presents simulation results and performance comparison, and test procedure and results of the fabricated VCO chip. The difficulties encountered in integration and possible solutions are also discussed. Chapter 6 presents conclusions of this research, and future work is suggested.

# 2. VCO Background

In this chapter, introduction to the voltage controlled oscillator (VCO) and background theories on various VCO concepts, such as quality factor and phase noise will be presented.

# 2.1 Voltage-Controlled Oscillator

In this section, different ways of realizing a VCO and important criteria and principles are presented.

## 2.1.1 Types of Oscillators

There are many different types of oscillators. Two major classifications are those that create sinusoidal outputs and those that create square or triangular wave outputs. Sinusoidal-output oscillators are more typical of analog or RF circuits and normally contain frequency-selective circuits. Square-wave-output oscillators are more typical of digital circuits and can be realized using feedback circuits such as relaxation oscillators or ring counters.

The ring oscillator is one of the most popular forms of digital output oscillators. A ring oscillator is realized by placing an odd number of inverters in a feedback loop. A rising edge at any node propagates through the inverters in the loop, and returns as a falling edge after the delays through the inverters. This falling edge then propagates and returns inverted as a rising edge. This repeats and generates a square wave oscillation. The oscillation frequency is determined by the delay and the number of the inverters. Assuming all the inverters have a delay of  $t_p$ , a ring oscillator with N inverters will oscillate at frequency  $1/2Nt_p$ .

Another popular method for realizing digital output VCOs is a relaxation oscilla-

tor. A relaxation oscillator is a circuit that repeatedly charges a capacitor gradually and discharges it rapidly. It is usually implemented with devices with threshold, such as a neon lamp, unijunction transistor (UJT), or Gunn diode. A relaxation oscillator often produces a square wave or sawtooth wave.

Sinusoidal-output oscillator design usually involves placing a frequency-selective circuit into a positive feedback loop in which, at the selected frequency, the loss in the tuned circuit is compensated by the feedback circuit and the loop gain becomes unity. Sinusoidal oscillators, based on different frequency-selective components, can be classified into RC oscillators, LC oscillators, switched-capacitor oscillators, and crystal oscillators. Early integrated oscillators based on tuned circuits were largely realized using switched-capacitor circuits or off-chip crystals [21]. Integrated LC filters at GHz frequencies were used in oscillators with the development of semiconductor processes in the early 1990's [22].

For low frequency applications (DC to 100 kHz), the frequency-selective circuits seldom use inductors because the required inductors are large and technically impossible to fabricate in monolithic form. Thus, inductorless filters, such as RC and switched capacitor filters are usually used. RC filters are fabricated using discrete, hybrid thick-film, or hybrid thin-film technology. However, these technologies are not as cost efficient as monolithic fabrications for large volume production. At the present time, the switched capacitor technique is the most viable approach [21]. Switched capacitor circuits use combination of switches and capacitors to simulate the effect of resistors, thus allow filters to be realized without using resistors since resistors are more difficult to implement in ICs than capacitors and switches.

For RF and microwave frequencies, crystals and LC-tuned circuits are often used. They exhibit higher Q than RC-tuned circuits. LC-tuned oscillators utilize parallel LC tank circuits as frequency selective components. These oscillators are known as self-limiting because the effective gain of the transistors reduces as the oscillation amplitude grows and eventually the loop gain becomes unity.

A piezoelectric crystal, such as quartz, has its reactance inductive over a very narrow frequency band. Replacing the inductor in the LC-tuned circuits with a crystal results a very well defined resonance frequency. When used as a high Q frequency selective component, a crystal exhibits extremely stable resonance characteristics and very accurate operation frequency. Unfortunately, being mechanical resonators, crystal oscillators are fixed-frequency circuits and cannot be easily tuned.

## 2.1.2 Barkhausen Criteria

In an amplifier circuit with feedback, if the feedback signal is in phase with the input and the magnitude of the feedback is large enough, the circuit becomes unstable. If any input, including noise, is applied to such a feedback circuit, the input grows. After a period of time, the growing transients are sufficiently large, the circuit elements produce nonlinear response and eventually the signals stop growing. In the steady-state, the circuit becomes an oscillator.

However, to obtain a useful oscillator requires more than stability. At the oscillation frequency  $\omega_0$ , the phase of the loop gain should be zero and the magnitude of the loop gain should be unity. This is known as the Barkhausen criterion. For the circuit to oscillate at one frequency, the oscillation criterion should be satisfied only at one frequency,  $\omega_0$ ; otherwise the resulting waveform will not be pure sinusoidal.

Consider a system as shown in Figure 2.1, which contains an amplifier with frequency-dependent forward loop gain  $G(j\omega)$  and a frequency-dependent feedback network  $H(j\omega)$ .

Figure 2.1: Block Diagram of Feedback Circuit

The closed-loop transfer function can be written as

$$T(j\omega) \equiv \frac{v_o(j\omega)}{v_i(j\omega)} = \frac{G(j\omega)}{1 - G(j\omega)H(j\omega)}$$

(2.1)

The loop gain  $G(j\omega)H(j\omega)$  is a complex number that can be represented by:

$$L(j\omega) \equiv G(j\omega)H(j\omega) = |G(j\omega)H(j\omega)|e^{j\phi(\omega)}$$

(2.2)

where  $L(j\omega)$  is the loop gain composed of magnitude and phase. If at a specific frequency  $\omega_0$ ,  $L(j\omega_0) = 1$ ,  $T(j\omega_0)$  will be infinite. This indicates that at this particular frequency, the circuits will have a finite output signal even with zero input. Hence, oscillation occurs when  $L(j\omega_0) = 1$ , or

$$|G(j\omega_0)H(j\omega_0)| = 1 \tag{2.3}$$

and

$$\phi(\omega_0) = arg(G(j\omega_0)H(j\omega_0)) = 2n\pi$$

for  $n = 0, 1, 2, ...$  (2.4)

Since the amplitude of oscillation is associated with the nonlinear gain of the active device, Equation 2.3, known as the open-loop gain, sets the oscillation amplitude (the amplitude at which Equation 2.3 is satisfied), and Equation 2.4, known as the loop phase, sets the oscillation frequency.

# 2.1.3 Negative Resistance Oscillator Principles

A frequency-selective oscillator is mainly composed of a resonator, represented by  $H(j\omega_0)$ , and an active circuit, represented by  $G(j\omega_0)$ . There are numerous frequency-selective components available for oscillators, including lumped elements, dielectric puck, distributed transmission line (microstrip or coaxial line), waveguide or cavity, and YIG (Yittrium Iron Garnet) sphere resonators. Most of the RF and microwave resonators can be represented by series/parallel lumped equivalent circuits, i.e., capacitors and inductors. As with all lumped components, losses exist due to finite conductivity, hysteresis, eddy currents, leakage and many other reasons. As a result, the equivalent circuits always need resistors to represent the losses in the circuits. To satisfy the Barkhausen Criteria, the active circuits must provide gains to compensate the losses. As these active devices are to counteract the positive resistance

in the resonators, they can be seen as negative resistance. If the negative resistance is able to exactly cancel out the resonator losses, steady-state oscillations are obtained. For convenient and intuitive design and analysis, active circuits in RF and microwave oscillators are often treated as negative resistance.

Figure 2.2: One-port Negative Resistance Oscillator Model

The basic principles of a negative resistance oscillator can be shown by the oneport model in Figure 2.2. The resonator has impedance of  $Z_{res} = R_{res} + jX_{res}$ , and the active device has impedance of  $Z_{active} = R_{active} + jX_{active}$ . This impedance is usually current (or voltage) and frequency dependent. Kirchhoff's voltage law gives

$$(Z_{res} + Z_{active})I = 0 (2.5)$$

When oscillating, current I is nonzero, then the following condition must be satisfied:

$$R_{res} + R_{active} = 0 (2.6)$$

and

$$X_{res} + X_{active} = 0 (2.7)$$

Since the resonator is a passive load,  $R_{res}$  is always positive. This indicates that  $R_{active}$  must be negative, which implies an energy source.

The process of oscillation depends on the nonlinear behavior of  $Z_{active}$ . Initially, the circuit must be unstable at a certain frequency, with  $R_{res}+R_{active}<0$ . Any transient excitation or noise will cause an oscillation to build up. As I increases,  $R_{active}$  becomes less negative until the current reaches  $I_0$  such that  $R_{res}+R_{active}(I_0,j\omega_0)=0$ , and  $X_{res}(j\omega_0)+X_{active}(I_0,j\omega_0)=0$ . Then the oscillation is in steady-state. The final frequency  $\omega_0$  is generally different from the startup frequency, because  $X_{active}$  is current (or voltage) dependent.

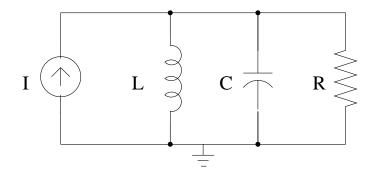

# 2.1.4 Resonator Principles

A typical resonant tank is a parallel LC circuit. Both the inductor and the capacitor have resistance associated with them, which for illustration can be modeled as a parallel RLC equivalent circuit.  $R_p$  represents the combined resistive loss of the inductor and capacitor.  $L_p$  and  $C_p$  represent the parallel equivalent inductance and capacitance, and both are purely reactive.

A parallel RLC circuit resonates when the susceptance of the inductor and capacitor cancels each other, or

$$\frac{1}{2\pi f_0 L_p} = 2\pi f_0 C_p \tag{2.8}$$

If the susceptance of the active circuit is ignored, the oscillation frequency  $f_0$  is given by the above resonant condition:

$$f_0 = \frac{1}{2\pi\sqrt{L_p C_p}}\tag{2.9}$$

For VCOs whose frequencies can be tuned, variable capacitors are usually implemented instead of fixed capacitors. The tuning ability of a VCO is determined by the ratio of maximum and minimum capacitance achievable from the variable capacitor. Replacing C in Equation 2.9 with the maximum capacitance  $C_{max}$  and the minimum capacitance  $C_{min}$ , the tuning range of the VCO can be found to be:

$$f_{ratio} = \frac{f_{max}}{f_{min}} = \sqrt{\frac{C_{min}}{C_{max}}}$$

(2.10)

# 2.2 Quality Factor (Q)

The quality factor (Q) is one of the most important descriptive parameter used in resonant systems. The fundamental definition of Q is as follows:

$$Q \equiv \omega \frac{\text{energy stored}}{\text{average power dissipated}}$$

(2.11)

This definition applies to both resonant and non-resonant systems, and both to electrical and mechanical systems.

Consider a parallel RLC circuit driven by a current source as shown in Figure 2.3. At resonant frequency  $\omega_0$ , the energy stored in the resonant circuit, E, which is equal to the peak energy stored in the capacitor, is given by

$$E = \frac{1}{2}C(I_{pk}R)^2. (2.12)$$

and average power dissipated in the resistor  $P_{avg}$  is given by

$$P_{avg} = \frac{1}{2} I_{pk}^2 R. (2.13)$$

The Q-factor of the network at resonance is then

$$Q = \omega_0 \frac{E}{P_{avg}} = \frac{1}{\sqrt{LC}} \frac{\frac{1}{2}C(I_{pk}R)^2}{\frac{1}{2}I_{pk}^2R} = \frac{R}{\sqrt{L/C}}.$$

(2.14)

Since in the frequency response, the centre frequency  $\omega_0=1/\sqrt{LC}$  and the 3 dB power bandwidth  $BW_{3dB}=1/RC$ , Q can also be expressed as

$$Q = \frac{\omega_0}{BW_{3dB}}. (2.15)$$

Q equals the ratio of the resonant frequency to the 3 dB bandwidth. The greater the Q is, the sharper and more frequency selective the frequency response is. Therefore, Q-factor represents the quality of the resonance circuit.

For a series RLC network, Q-factor at  $\omega_0$  can be derived as

$$Q = \frac{\sqrt{L/C}}{R} \tag{2.16}$$

For a single inductor or capacitor, the Q-factor is frequency dependent. By the definition shown in Equation 2.11, Q for inductor or capacitor is the ratio of

Figure 2.3: Second Order Parallel Resonator

the reactance to the equivalent parasitic series resistance at a particular frequency. Thus, for inductors and capacitors, reducing the equivalent parasitic resistance will improve their Q-factors.

#### 2.3 Phase Noise

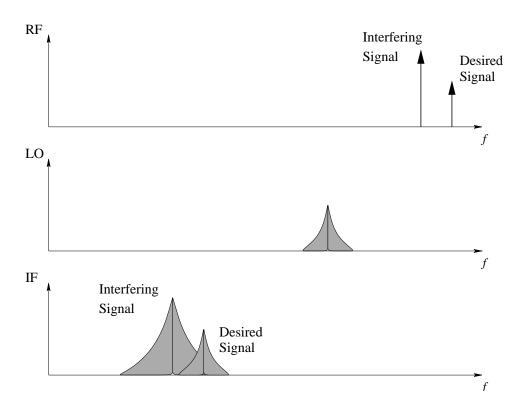

Phase noise is an important parameter in oscillators. It describes the short term random frequency fluctuations of a signal. Frequency stability is a measure of the degree to which an oscillator maintains the same value of frequency over a given time. Phase noise reduces this stability. The phase noise in the radio receiver local oscillator limits immunity against nearby interference signals and accurate timing recovery. Phase noise in the transmitter may even overwhelm nearby weak channels. In the receiver, phase noise may downconvert nearby channels onto the desired intermediate frequency (IF).

Consider the situation for a receiver, as shown by the power spectral densities in Figure 2.4. The local oscillator (LO) used for downconverting the RF signal has a noisy spectrum (shaded area). The received RF signal has an interfering signal with large power beside the desired signal with small power at adjacent frequency. After mixing with the LO, the noise from the LO will appear both around the desired signal and interfering signal in the downconverted spectrum, and form overlapping spectra. The wanted signal suffers from significant noise due to the interferer, and the signal-to noise ratio is degraded [23, 24]. In order to detect the desired signals

with large interferers presented, stringent phase noise specifications must be met in wireless communication systems.

Figure 2.4: Effect of Oscillator Phase Noise

# 2.3.1 Definition

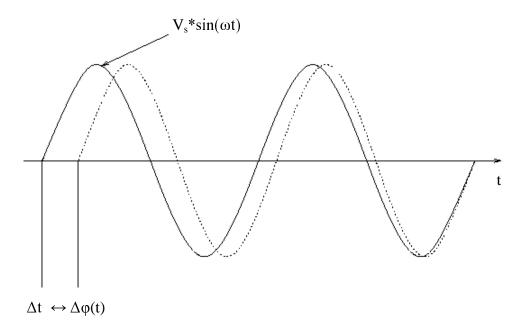

A sinusoidal signal with random phase fluctuation can be represented by

$$v(t) = v_s \sin[2\pi f_0 t + \Delta \phi(t)] \tag{2.17}$$

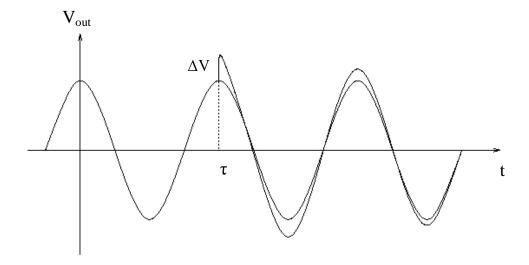

where  $\Delta \phi(t)$  represents the phase fluctuations. In the time domain, this can be observed as fluctuations of the zero crossings of the original signal, as shown in Figure 2.5.

Since frequency and phase are related by:

$$f(t) = f_0 + \frac{1}{2\pi} \frac{d\phi(t)}{dt} \tag{2.18}$$

Figure 2.5: Sine Wave with Phase Fluctuation

phase fluctuations, with respect to time, are also an indication of frequency fluctuations with respect to time.

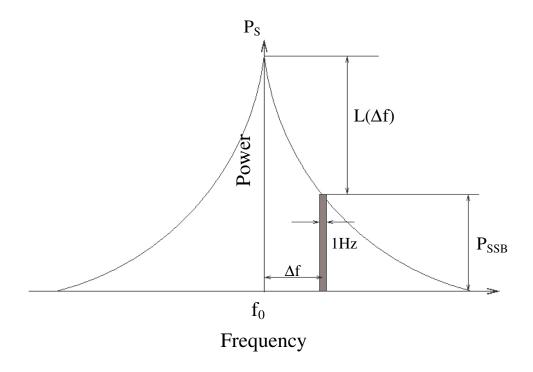

One of the most common fundamental descriptions of phase noise is the one sided spectral density of phase fluctuations per unit bandwidth. The term spectral density describes the power distributions as a continuous function, expressed in units of power per unit bandwidth. The phase noise of an oscillator is described in the frequency domain where the spectral density is characterized by measuring the noise sidebands on either side of the output signal centre frequency. Single sideband phase noise is specified in dBc/Hz at a given frequency offset from the carrier.

The National Bureau of Standards defines single sideband phase noise  $L(\Delta f)$  as the ratio of power in one phase modulation sideband per Hertz bandwidth, at an offset  $\Delta f$  Hz away from the carrier, to the total signal power, as shown in Figure 2.6, in which  $P_S$  is the carrier power and  $P_{SSB}$  is the sideband power in 1 Hz bandwidth at an offset frequency of  $\Delta f$  from the centre.

$$L(\Delta f) = 10 \log \left(\frac{P_{SSB}}{P_S}\right) \, dBc/Hz @ \Delta f \, Hz$$

(2.19)

The phase noise generated by a VCO is determined by the Q-factor of the res-

Figure 2.6: Single Sideband Phase Noise to Carrier Ratio

onator, the active transistor device used for the oscillator, the power supply noise, and the external tuning voltage supply noise. The later two noise sources can be minimized by careful choice of the power supplies. Therefore, designing a low phase noise VCO primarily involves implementing a high Q resonator and carefully operating the oscillator active devices at low phase noise bias points.

Leeson was the first to propose a simple intuitive model [25] relating to the level of phase noise in a widely used class of resonator-based oscillators in 1966. Later, different quantitative models have been established to explain the cause of phase noise, each of which focuses on different noise sources [26].

### 2.3.2 Leeson's Phase Noise Model

Consider an ideal oscillator, whose only noise source is the white thermal noise of the RLC resonant tank resistance. The current noise mean-square spectral density is

$$\frac{\overline{i_n^2}}{B} = 4kTG \tag{2.20}$$

where B is the bandwidth, k is the Boltzmann's constant, T is the temperature in degrees Kelvin, and G is the tank conductance.

This current noise can be converted to voltage noise when multiplied by the effective impedance, which is simply a perfectly lossless LC network as the energy restoration elements contribute a negative conductance that precisely cancels the positive conductance (G) of the tank.

For small displacements  $\Delta f$  from the resonant frequency  $f_0$ , the impedance of the oscillating tank can be calculated as followed:

$$Z(f_0 + \Delta f) = \left[j(\omega_0 + \Delta \omega)C + \frac{1}{j(\omega_0 + \Delta \omega)L}\right]^{-1}$$

$$= \frac{j(\omega_0 + \Delta \omega)L}{1 - (\omega_0^2 + 2\omega_0 \Delta \omega + \Delta \omega^2)LC}$$

(2.21)

Since  $LC = 1/\omega_0^2$  and  $\omega_0 \gg \Delta \omega$ , the impedance can be further approximated by

$$Z(f_0 + \Delta f) = -\frac{j(\omega_0 + \Delta\omega)L}{2\frac{\Delta\omega}{\omega_0} + (\frac{\Delta\omega}{\omega_0})^2} \approx -j\frac{\omega_0 L}{2(\Delta\omega/\omega_0)} = -j\frac{\pi f_0 L}{\Delta f/f_0}$$

(2.22)

By introducing the expression of the unloaded tank Q, where

$$Q = \frac{R}{2\pi f_0 L} = \frac{1}{2\pi f_0 LG} \tag{2.23}$$

L can be substituted and the magnitude of the tank impedance can be written as

$$|Z(f_0 + \Delta f)| \approx \frac{1}{G} \frac{f_0}{2Q\Delta f}.$$

(2.24)

Thus, for a small offset frequency, the spectral density of the mean-square noise voltage can be written as

$$\frac{\overline{v_n^2}}{B} = \frac{\overline{i_n^2}}{B} \cdot |Z|^2 = 4kTR \left(\frac{f_0}{2Q\Delta f}\right)^2$$

(2.25)

The noise power in a 1 Hz bandwidth is

$$P_n = \frac{\overline{v_n^2}}{BR} = 4kT \left(\frac{f_0}{2Q\Delta f}\right)^2. \tag{2.26}$$

The above expression includes the noise effects in both amplitude and phase. The equipartition theorem of thermodynamics states that, in equilibrium, the noise power distributes evenly among each of the quadratic degrees of freedom [27], in this case, amplitude and phase. Therefore, in the absence of amplitude limiting, the noise affecting phase is half of Equation 2.25.

Normalizing the noise voltage density to the mean-square carrier voltage  $v_s$ , where

$$P_S = \frac{\overline{v_s^2}}{R},\tag{2.27}$$

the phase noise is obtained as

$$L(\Delta f) = 10 \log \left[ \frac{2kT}{P_S} \cdot \left( \frac{f_0}{2Q\Delta f} \right)^2 \right]$$

(2.28)

This shows that the phase noise is inversely proportional to the square of the resonator Q. That is why improving resonator Q is critical in VCO design.

The phase noise predicted using Equation 2.28 considers only the thermal noise from the resonator. There are other important noise sources, which cause the measured phase noise to be greater. The predicted noise continues to drop quadratically, while in real cases, phase noise spectra always exhibits a noise floor (noise does not drop with increasing of frequency offset) at large frequency offsets. Such a noise floor may be due to the noise associated with active elements and impossible to eliminate. Also, there is a  $1/f^3$  region at small offset frequencies. Thus, Leeson developed a more involved equation which considers some of these factors:

$$L(\Delta f) = 10 \log \left\{ \frac{2FkT}{P_S} \cdot \left[ 1 + \left( \frac{f_0}{2Q\Delta f} \right)^2 \right] \cdot \left( 1 + \frac{f_{1/f^3}}{\Delta f} \right) \right\}$$

(2.29)

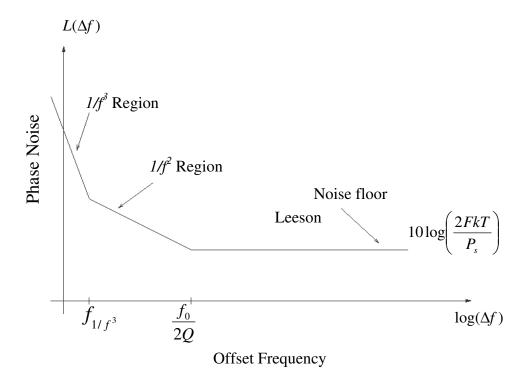

This equation, known as Leeson's Equation, consists of three modifications to Equation 2.28. A factor F (often called the "device excess noise number") is introduced to account for the noise in addition to thermal noise in the  $1/f^2$  region. An additive unity factor (inside the square brackets) accounts for the noise floor. A multiplicative factor (the last part of the equation) provides a  $1/f^3$  behavior at small offset frequencies. Figure 2.7 shows a typical phase noise Bode plot described by Leeson's Equation.

There are a few problems limiting the predictive power of Leeson's model. The factor F is an empirical fitting parameter, which must be determined from mea-

Figure 2.7: Phase Noise in Leeson's Model

surements. Although  $f_{1/f^3}$ , the boundary between the  $1/f^2$  and  $1/f^3$  regions, is asserted to equal to the 1/f corner frequency of the device (the frequency below which flicker noise dominates and above which thermal noise dominates), measurements often disagree, and thus has to be treated as an empirical fitting parameter as well. Finally, the frequency at which the noise becomes constant is not always equal to  $f_0/2Q$ .

#### 2.3.3 LTV Phase Noise Model

Leeson's phase noise model treats the oscillator as a linear, time-invariant (LTI) system. However, this assumption does not always hold true, and is addressed by Hajimiri and Lee's LTV phase noise model.

Oscillators are fundamentally nonlinear, as amplitude limiting is necessary. However, amplitude-control nonlinearity affects phase noise only incidentally, by controlling the detailed shape of the output waveform. Disturbances are always much smaller in magnitude than the carrier in oscillators. Thus, linearity would be a reasonable assumption if the noise-to-phase transfer function is concerned.

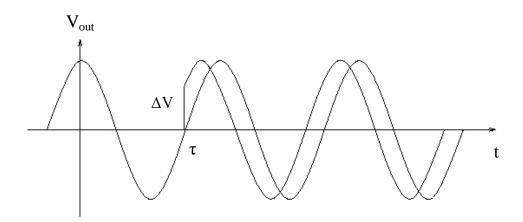

The assumption of time-invariance fails to hold for oscillator phase noise analysis. This can be shown by considering how an impulse affects the waveform of an oscillator. As shown in Figure 2.8, the oscillator system responds differently to the impulses injected into the system at different times. If the impulse occurs at a voltage maximum of the sinewave, the amplitude increases but the timing of the zero crossings does not change. On the other hand, if the impulse is injected in at some other time, both amplitude and zero crossing timing of the oscillation are affected. Since zero crossing timing is a measure of phase, one may conclude that the phase disturbance of an injected impulse depends on when the injection occurs. Thus, an oscillator is a periodically time-varying system. Hajimiri and Lee modeled phase noise theory in a linear, time-varying (LTV) system [28].

To study the time-varying nature of the oscillator, first the impulse response at time  $\tau$  for excess phase is defined.

$$h_{\phi}(t,\tau) = \frac{\Gamma(\omega_0 \tau)}{q_{max}} u(t-\tau)$$

(2.30)

where u(t) is the unit step function, and  $q_{max}$  is the maximum charge displacement across the capacitor on the node, which makes the function  $\Gamma(x)$  independent of signal amplitude.  $\Gamma(x)$  is called the impulse sensitivity function (ISF) periodic in  $2\pi$ . It describes how much phase shift results from the impulse.  $\Gamma(x)$  is a function of the waveform. In general, it is practical to determine  $\Gamma(x)$  through simulation. But there are also analytical methods for special cases [23, 29].

Consider the excess phase  $\phi(t)$  as the superposition of impulse response for all  $\tau$  values, one can compute the excess phase by superposition integral as

$$\phi(t) = \int_{-\infty}^{\infty} h_{\phi}(t,\tau)i(\tau)d\tau = \frac{1}{q_{max}} \int_{-\infty}^{t} \Gamma(\omega_0 \tau)i(\tau)d\tau$$

(2.31)

Since the ISF is periodic, it can be expressed as a Fourier series

$$\Gamma(\omega_0 \tau) = \frac{c_0}{2} + \sum_{n=1}^{\infty} c_n \cos(n\omega_0 \tau + \theta_n)$$

(2.32)

Figure 2.8: Impulse Responses of Oscillator

where the coefficients  $c_n$  are real, and  $\theta_n$  is the phase of the *n*th harmonic of the ISF.  $\theta_n$  can be ignored assuming that noise components are uncorrelated and thus, their relative phase is irrelevant.

Substituting the Fourier expansion into the superposition integral gives:

$$\phi(t) = \frac{1}{q_{max}} \left[ \frac{c_0}{2} \int_{-\infty}^t i(\tau) d\tau + \sum_{n=1}^\infty c_n \int_{-\infty}^t i(\tau) \cos(n\omega_0 \tau) d\tau \right]$$

(2.33)

Equation 2.33 allows computation of excess phase caused by an arbitrary noise current injected into the system, once the Fourier coefficients of the ISF have been found.

The fact that the system is not LTI implies that noise injected into the system

at some frequency may produce spectrum at different frequencies. This property is demonstrated below.

Consider injecting a current whose frequency is close to an integer multiple m of the oscillation frequency,

$$i(t) = I_m \cos[(m\omega_0 + \Delta\omega)t] \tag{2.34}$$

where  $\Delta\omega \ll \omega_0$ . Substituting into Equation 2.33 gives:

$$\phi(t) = \frac{c_0}{2q_{max}} \int_{-\infty}^{t} I_m \cos[(m\omega_0 + \Delta\omega)t] d\tau + \frac{1}{q_{max}} \sum_{n=1}^{\infty} c_n \int_{-\infty}^{t} I_m \cos[(m\omega_0 + \Delta\omega)\tau] \cos(n\omega_0\tau) d\tau \quad (2.35)$$

Equation 2.35 can be considerably simplified. Since  $\Delta\omega \ll \omega_0$ , and each integral in the equation has the following form:

$$c_n \int_{-\infty}^{t} I_m \cos[(m\omega_0 + \Delta\omega)\tau] \cos(n\omega_0\tau) d\tau$$

$$= \frac{I_m c_n}{2} \left[ \frac{\sin(m\omega_0 + n\omega_0 + \Delta\omega)\tau}{m\omega_0 + n\omega_0 + \Delta\omega} + \frac{\sin(m\omega_0 - n\omega_0 + \Delta\omega)\tau}{m\omega_0 - n\omega_0 + \Delta\omega} \right], \quad (2.36)$$

the contribution by terms other than when n=m are negligible. Equation 2.35 thus collapses to the following approximation:

$$\phi(t) \approx \frac{I_m c_m \sin(\Delta \omega t)}{2q_{max} \Delta \omega} \tag{2.37}$$

This shows that the injection occurs near an integer multiple of  $\omega_0$  will be converted into excess phase at  $\pm \Delta \omega$ .

Equation 2.37 shows how much phase error results from a given current i(t). To find the spectrum of the output voltage, the phase error must be converted to voltage. To obtain the sideband power around the fundamental frequency, the output may be approximated as a sinusoid, so that  $v_{out} = \cos[\omega_0 t + \phi(t)]$ . This equation may be considered as a phase-to-voltage converter. This conversion is nonlinear [28].

Performing this phase-to-voltage conversion, one can see that a current injected at frequency  $m\omega_0 + \Delta\omega$  results in a pair of equal sidebands at  $\omega_0 \pm \Delta\omega$  with a sideband power with respect to the carrier given by

$$P_{SBC}(\Delta\omega) = 10\log\left(\frac{I_m c_m}{4q_{max}\Delta\omega}\right)^2 \tag{2.38}$$

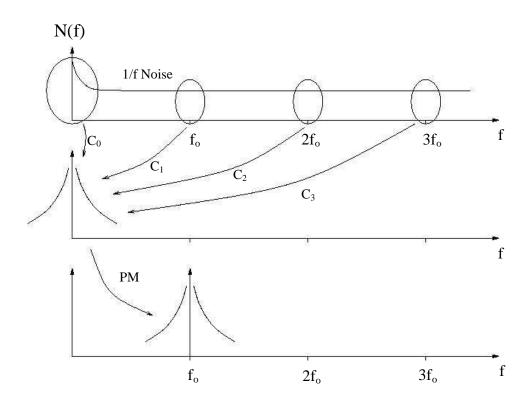

Equation 2.38 implies both upward and downward frequency translations of noise, as shown in Figure 2.9. Noise near DC is up-converted, so 1/f device noise becomes  $1/f^3$  noise near the carrier. Noise near the carrier remains the same frequency. White noise near higher integer multiplies of the carrier down-converts and turns into noise in the  $1/f^2$  region.

Figure 2.9: Evolution of Circuit Noise into Phase Noise

Consider in particular the phase noise contribution by the white thermal noise, whose spectral density is  $\overline{i_n^2}/\Delta f$ .  $I_m$  in Equation 2.38 represents the peak amplitude,  $\overline{i_n^2}/\Delta f = I_m^2/2$  for  $\Delta f = 1$  Hz. Thus, the phase noise at an offset frequency of  $\Delta \omega$

is given by

$$L(\Delta\omega) = 10 \log \left( \frac{\frac{\overline{i_n^2}}{\Delta f} \sum_{m=0}^{\infty} c_m^2}{4q_{max}^2 \Delta\omega^2} \right)$$

(2.39)

According to Parseval's theorem,

$$\sum_{m=0}^{\infty} c_m^2 = \frac{1}{\pi} \int_0^{2\pi} |\Gamma(x)|^2 dx = 2\Gamma_{rms}^2, \tag{2.40}$$

which gives a result

$$L(\Delta\omega) = 10\log\left(\frac{\Gamma_{rms}^2}{q_{max}^2} \cdot \frac{\overline{i_n^2}/\Delta f}{2\Delta\omega^2}\right)$$

(2.41)

This is the rigorous equation for the  $1/f^2$  region, similar to Leeson's model, but with no empirical curve-fitting parameters.

## 2.3.4 Figure of Merit

To compare the performance of different VCOs implemented with different technologies, the phase noise is normalized into a figure of merit (FOM) [15,18], defined as:

$$FOM = 10 \log \left[ L(\Delta f) \left( \frac{\Delta f}{f_0} \right)^2 P_{VCO} \right]$$

(2.42)

where  $L(\Delta f)$  is the single sideband noise (linear) at offset frequency  $\Delta f$  from the centre frequency  $f_0$ .  $P_{VCO}$  denotes the total power consumption of the VCO in mW. FOM generates a comparable value system from which different oscillators can be evaluated. The performance of a VCO is regarded to be better with higher absolute value of FOM. This quantity is biased towards monolithic CMOS designs, whose power consumption is minimized. For other device comparison, such as GaAs (Gallium Arsenide), the expression can be modified to concern more on power consumption.

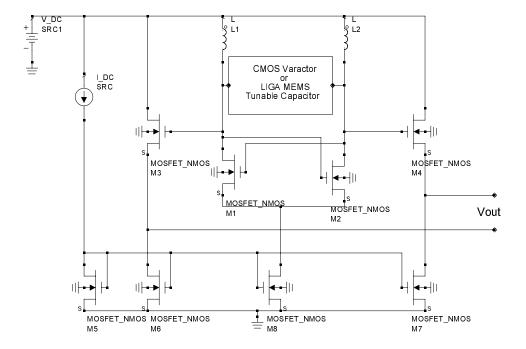

## 3. VCO Design

The goal of this research is developing a CMOS VCO circuit as a platform to integrate LIGA-MEMS capacitor to CMOS circuit and to evaluate its performance. The VCO design should provide a reasonably fair performance comparison environment for the LIGA-MEMS capacitor and the conventional CMOS varactor. Thus, the VCO design should be able to either use an on-chip CMOS varactor, or integrate with an off-chip LIGA-MEMS capacitor as a resonator component. Any effects in the VCO performance, which would be introduced by the integration, should be considered in the design so that the difference in the VCO performance merely reflects the advantage (or disadvantage) of the LIGA-MEMS capacitor over the on-chip varactor.

#### 3.1 Design Issues

In this section, various design issues, including choice of fabrication technologies, design topologies and approaches are discussed.

## 3.1.1 CMOS Fabrication Technologies

CMOS technology has become the most popular technology in IC designs, especially for digital circuits. CMOS is the ideal technology to realize system-on-chip (SOC) solutions for complex circuits and systems. Thus, research in analog, mixed-signal, and RF circuits focuses on CMOS technology as well, so that the circuits benefit from better compatibility with other circuits and systems.

CMOS technology is continuously advancing by shrinking the size of the transistors. This leads to smaller circuit size, faster response, higher operating frequencies, and in the case of digital circuits, greater calculation capability. Many

different CMOS fabrication standards are available, from 0.8 micron to the newest 65 nanometre. Among the different CMOS fabrication standards available, TSMC (Taiwan Semiconductor Manufacturing Company) 0.18 micron is a good choice in terms of performance and technology maturity. TSMC 0.18 micron is not the newest technology in fabrication, but it is an advanced mainstream technology. It features a high degree of process stability and runs on the foundry industry's largest available capacity that provides consistent support. TSMC 0.18 micron process technology provides a good combination of density, speed and power to serve a broad range of computing, communications and consumer electronics applications. This technology supports features such as deep N-well, multiple threshold voltage devices, and MIM (metal-insulator-metal) capacitor. Also, models, design kit, cell libraries, verification technology files, and technical support are well provided. It has been proven to be a mature technology for RFIC designs [20, 30, 31].

# 3.1.2 Oscillator Design Approaches

There are various approaches to design an oscillator. Traditionally, these approaches are classified either as small-signal (linear) with emphasis on start-up conditions, or large-signal (nonlinear) with emphasis on steady-state conditions.

Small-signal design approaches focus on obtaining active device scattering parameters (S-parameters) to satisfy oscillation conditions. This type of design approaches is relatively simple since device S-parameters are usually readily available. However, small-signal design approaches often suffer from inaccuracy in estimating oscillation performance, such as oscillation frequency, output power, and phase noise [32–34].

Large-signal design approaches, on the other hand, focus on predicting the correct steady-state oscillation frequency and power levels. Different methods have been presented. Some characterize the active devices as an amplifier and derive the oscillator power from input and output power of the amplifier [35]. Some estimate the saturation gain or large signal behavior based on small signal S-parameters [36, 37]. Some use a "Device Line" technique, which measures the impedance when

the device saturates and therefore utilize the large signal behaviors [38]. Large-signal design approaches usually have difficulties deriving nonlinear models for devices, and sometimes experience problems in oscillation start-up.

With the advancement of computer aided design (CAD) tools, oscillator design is taking a new approach. CAD tools are able to simulate a variety of results, such as oscillation frequency, power, phase noise, stability, and harmonic distortion. CAD tools can use different simulation technologies, such as DC simulation, AC and S-parameter simulations, transient time-domain simulation, and Harmonic Balance (HB) simulation, to ensure oscillation conditions in different aspects. The CAD approach makes oscillator design more systematic and focused. However, it is worth noting that CAD tools can only be as accurate as the models used in the simulation.

## 3.1.3 Oscillator Topologies

LC-tuned oscillators can be realized with different topologies. Figure 3.1 shows the AC model of two classic configurations common at lower frequencies, the Colpitts oscillator and Hartley oscillator (bias details are not shown). Both configurations utilize a parallel LC circuit between the collector and the base of a BJT (bipolar junction transistor), or between the drain and the gate of a FET (field effect transistor). These configurations can be realized with only one transistor and thus exhibit great simplicity.

To analyze the Colpitts oscillator, the passive components can be simplified and re-modeled in a negative resistance configuration, as shown in Figure 3.2, with the assumption that impedances of the capacitors are less than the load resistance at resonant frequency.

Figure 3.2 (a) is an AC model of the Colpitts oscillator shown in Figure 3.1 (a). The resistance  $R_L$  represents the load, the transistor output resistance, and the loss in the tank. The transistor can be modeled by a large-signal gate-source resistance  $1/G_m$ , and a current source  $G_mV_1$ , where  $G_m$  is the large-signal transconductance of the transistor, as shown in Figure 3.2 (b). The capacitive voltage divider  $C_1$  and  $C_2$  can be modeled as an ideal transformer, as shown in Figure 3.2 (c). The equivalent

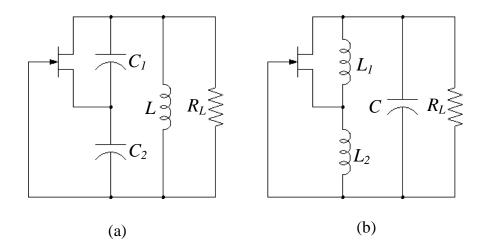

Figure 3.1: Two Common Oscillator Configurations: (a) Colpitts and (b) Hartley

Figure 3.2: Modeling Colpitts Oscillator: (a) Oscillator Circuit AC Model. (b) Modeling Transistor. (c) Modeling Transformer. (d) Simplified Model.

turns ratio is determined by the voltage-divider:

$$N = \frac{C_1}{C_1 + C_2}. (3.1)$$

The relationship between  $V_{out}$  and  $V_1$  is also determined by the capacitor divider:

$$V_1 = NV_{out}. (3.2)$$

Using the turns ratio to convert the resistance looking through the transformer, the Colpitts oscillator can be simplified into an RLC tank with the transistor modeled as a negative resistor, as shown in Figure 3.2 (d). In this simplified model, the equivalent capacitance is the series combination of the two capacitors:

$$C_{eq} = \frac{C_1 C_2}{C_1 + C_2}. (3.3)$$

The equivalent resistance is the parallel combination of the load resistance  $R_L$  and large-signal gate-source resistance looking through the capacitive transformer:

$$R_{eq} = R_L \parallel \frac{1}{N^2 G_m}.$$

(3.4)

The negative resistance is determined by the voltage-current relationship of the current source in the transistor model, looking through the transformer:

$$-R = \frac{V_{out} - V_1}{-G_m V_1} \frac{1}{(1 - N)^2} = -\frac{1}{N(1 - N)G_m}.$$

(3.5)

Thus, neglecting the transistor parasitics, the oscillation frequency of the Colpitts oscillator can be expressed as followed:

$$\omega_o = \frac{1}{\sqrt{LC_{eq}}} = \frac{1}{\sqrt{L\left(\frac{C_1C_2}{C_1 + C_2}\right)}}.$$

(3.6)

Similar analysis can be applied to the Hartley oscillator, and its oscillation frequency is:

$$\omega_o = \frac{1}{\sqrt{(L_1 + L_2)C}}. (3.7)$$

Colpitts and Hartley oscillators have good noise properties and thus potentially lower phase noise. They also achieve high voltage swing for a given bias current and resonator Q [23]. However, these configurations are rarely used in CMOS integrated circuits. This is because of the high gain required for a reliable start-up condition

and the single-ended nature, which makes them sensitive to common-mode noise sources, such as substrate and power supply noise. Recent research shows that a differential Colpitts VCO topology can overcome these shortcomings [19].

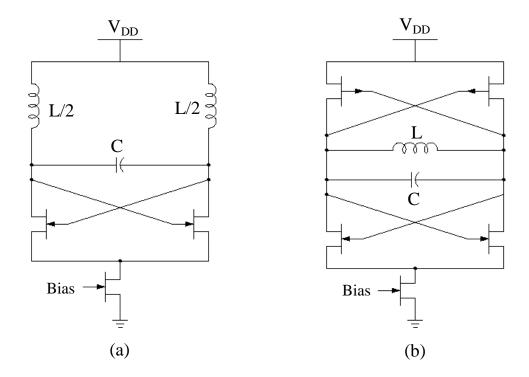

Another popular topology is the cross-coupled oscillator. Cross-coupled oscillators are easy to implement due to their relaxed start-up condition. They also provide fully differential output which reduces common-mode noise.

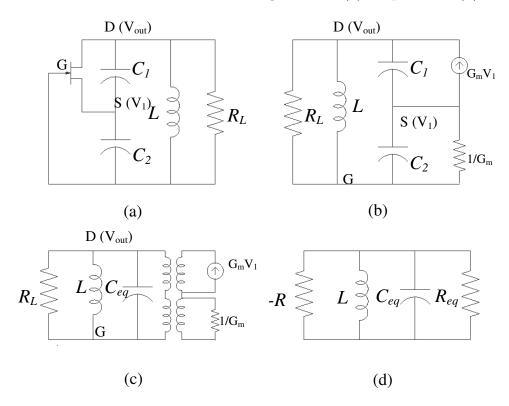

Cross-coupled oscillators can be realized with NMOS (N-type metal oxide semi-conductor) transistors only, as shown in Figure 3.3(a), or PMOS (P-type metal oxide semiconductor) only, or with both NMOS and PMOS transistors (complementary), as shown in Figure 3.3(b). The NMOS-only configuration is easy to implement, while the complementary version provides larger amplitude swing.

Figure 3.3: (a) NMOS-Only Cross-Coupled Oscillator (b) Complementary Cross-Coupled Oscillator

The cross-coupled transistor pair effectively works as a negative resistance that cancels out the resistance in the non-ideal resonant tank. This can be explained

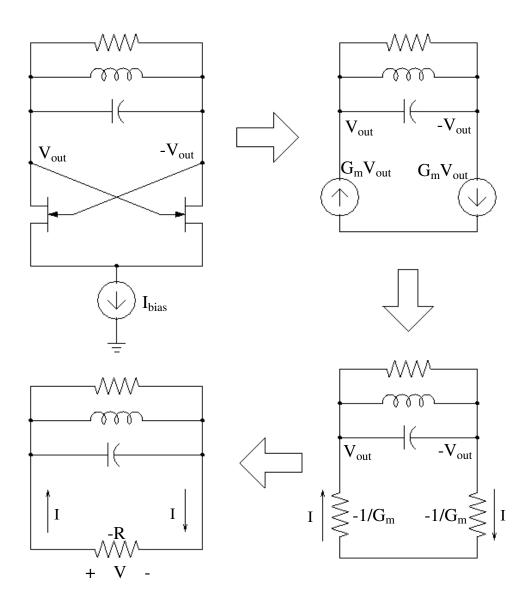

using the simplified AC large-signal model as shown in Figure 3.4, providing that the two transistors are perfectly matched.

Figure 3.4: Cross-Coupled Negative Resistance

Consider half of the cross-coupled transistor pair. Due to the inverting nature of the transistor stages, the AC voltage at the drains is the negative of that at the gates, while the drain current flows from  $-V_{out}$  to  $+V_{out}$  in the differential pair, indicating a negative resistance. By modeling the transistor as a current source  $G_mV_{out}$ , where  $G_m$  is the large-signal transconductance, the transistor can be calculated to have a

negative resistance of  $-1/G_m$ . Assuming that two transistors are identical, the total negative resistance can be described by

$$R = \frac{-2}{G_m} \tag{3.8}$$

This negative resistance technique is also used in Q-enhanced LC filters.

## 3.1.4 Resonator Components

A resonator is the frequency selective part of a VCO. An LC resonator is simply an inductor and a capacitor coupled in parallel. For CMOS RFICs, both inductor and capacitor are traditionally realized on-chip. In the CMOS process, a top layer metal trace in spiral shape forms an on-chip spiral inductor. An On-chip capacitor can be realized in various ways. Some use the capacitance between two metal plates, such as the MIM capacitor. Some use the capacitance between different regions of active devices, such as the diode varactor and the MOS varactor. Other types of inductors and capacitors can be used in RFIC, including MEMS passive components. The following section will discuss various inductive and capacitive resonator components.

#### 3.1.4.1 Spiral Inductor

The inductor is one of the most critical components in CMOS RF circuit design as the inductor Q value can dominate the loss in the resonant tank. CMOS on-chip inductors typically range around a few nanohenries. This makes it normally impractical to implement on-chip inductors at sub-gigahertz frequencies. For gigahertz range frequencies, on-chip inductors have sufficient inductance to allow utilization of these components in CMOS circuits, however, loss becomes an increasing problem with increasing frequency due to parasitics.

### 3.1.4.1.1 CMOS Spiral Inductor Modeling

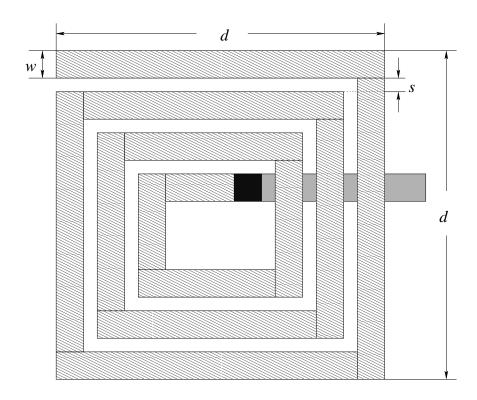

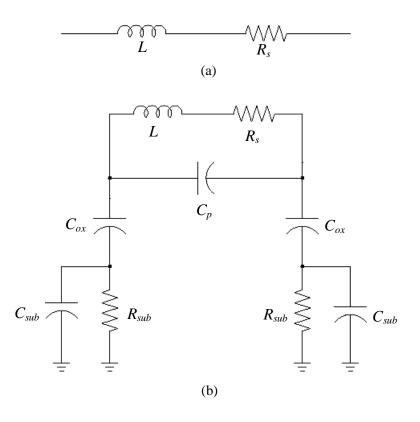

A spiral inductor can be built on a silicon substrate using today's mainstream silicon fabrication processes. A minimum of two metal layers is needed to build a basic spiral coil and connect its inner terminal to the outside. The structure of a spiral inductor

can be defined by the number of turns (n), the conductor width (w) and spacing (s), and the area it covers  $(d \times d)$ , as shown in Figure 3.5.

Figure 3.5: A Typical Spiral Inductor Layout

There are three dominating loss mechanisms in on-chip inductors in CMOS processes: the series parasitic resistance of the inductor, the eddy current loss due to the low resistivity lossy silicon substrate, and the capacitive coupling to the conducting substrate [39]. The Ohmic loss of the series parasitic resistance is the most important loss among the three at low frequencies. Thus, a typical CMOS spiral inductor at low frequencies can be modeled as a series combination of an ideal inductance L and a series resistance  $R_s$ , as shown in Figure 3.6(a). At high frequencies, the other two loss mechanisms become obvious, and the inductor can be modeled as shown in Figure 3.6(b). A capacitance in parallel with the coil  $(C_p)$  represents the capacitive coupling between the two terminals of the inductor. The oxide capacitors  $(C_{ox})$  represent the capacitance between the spiral and the substrate. And finally

there are resistances and capacitances of the silicon substrate  $(R_{sub})$  and  $C_{sub}$ .

Figure 3.6: Lumped-Element Model of an On-Chip Spiral Inductor: (a) Low Frequency Model and (b) High Frequency Model

The overall inductance of a square spiral L can be computed accurately by summing the self inductance of each wire segment and the mutual inductance between all possible wire segment pairs, using Grover's formula [40] and Greenhouse's method [41]. The equations for this calculation are complicated and not presented here. The other parameters in the model can be described as followed [42]:

$$R_s = \frac{l}{w\sigma\delta(1 - e^{-t/\sigma})} \tag{3.9}$$

$$C_p = nw^2 \frac{\epsilon_{ox}}{t_{ox}} \tag{3.10}$$

$$C_{ox} = wl \frac{\epsilon_{ox}}{t_{ox}} \tag{3.11}$$

$$R_{sub} = \frac{2}{wlG_{si}} \tag{3.12}$$

$$C_{sub} = \frac{wlC_{si}}{2} \tag{3.13}$$

where l, w, t and  $\sigma$  are the total length, width, thickness, and the conductivity of the coil metal respectively,  $\delta$  is the skin depth, which can be calculated as  $\delta = \sqrt{1/\pi f \mu_o \sigma}$  with  $\mu_o$  is the permeability, n is the number of turns of the coil,  $\epsilon_{ox}$  is the dielectric permittivity of the oxide,  $t_{ox}$  is the oxide thickness between the spiral and the underpass,  $G_{si}$  and  $C_{si}$  are the conductance and capacitance per unit area of the substrate.

The quality factor of the inductor can be approximated using the low frequency model before substrate loss effects contribute.

$$Q = \frac{\omega L}{R_c} \tag{3.14}$$

At higher frequencies, the Q-factor is normally significantly lower [43].

Simulation programs are available to greatly reduce calculation and parameter extraction work for designers. ASITIC (Analysis and Simulation of Spiral Inductors and Transformers for ICs) is a well-established simulation tool [44]. It provides lumped-element models for inductors and other types of passive components and interconnect metal structures. It takes into account skin effects, crowding effects, eddy current losses, and the models are accurate to different fabrication technologies by adapting a mini technology file that describes the substrate and metal layers of the process.

## 3.1.4.1.2 Design Guidelines for CMOS Spiral Inductors

There are a few guidelines to be considered in design and layout for CMOS spiral inductors.