# HIGH-SPEED CO-PROCESSORS BASED ON REDUNDANT NUMBER SYSTEMS

A Thesis Submitted to the College of

Graduate Studies and Research

in Partial Fulfillment of the Requirements

for the Degree of Doctor of Philosophy

in the Department of Electrical and Computer Engineering

University of Saskatchewan

Saskatoon, Saskatchewan, Canada

By AMIR KAIVANI

©Amir Kaivani, February/2015. All rights reserved.

#### PERMISSION TO USE

In presenting this thesis in partial fulfilment of the requirements for a Postgraduate degree from the University of Saskatchewan, I agree that the Libraries of this University may make it freely available for inspection. I further agree that permission for copying of this thesis in any manner, in whole or in part, for scholarly purposes may be granted by the professor or professors who supervised my thesis work or, in their absence, by the Head of the Department or the Dean of the College in which my thesis work was done. It is understood that any copying or publication or use of this thesis or parts thereof for financial gain shall not be allowed without my written permission. It is also understood that due recognition shall be given to me and to the University of Saskatchewan in any scholarly use which may be made of any material in my thesis.

Requests for permission to copy or to make other use of material in this thesis in whole or part should be addressed to:

Head of the Department of Electrical and Computer Engineering

University of Saskatchewan

57 Campus Drive

Saskatoon, Saskatchewan

Canada

S7N 5A9

#### **ABSTRACT**

There is a growing demand for high-speed arithmetic co-processors for use in applications with computationally intensive tasks. For instance, Fast Fourier Transform (FFT) co-processors are used in real-time multimedia services and financial applications use decimal co-processors to perform large amounts of decimal computations.

Using redundant number systems to eliminate word-wide carry propagation within interim operations is a well-known technique to increase the speed of arithmetic hardware units. Redundant number systems are mostly useful in applications where many consecutive arithmetic operations are performed prior to the final result, making it advantageous for arithmetic coprocessors. This thesis discusses the implementation of two popular arithmetic co-processors based on redundant number systems: namely, the binary FFT co-processor and the decimal arithmetic co-processor.

FFT co-processors consist of several consecutive multipliers and adders over complex numbers. FFT architectures are implemented based on fixed-point and floating-point arithmetic. The main advantage of floating-point over fixed-point arithmetic is the wide dynamic range it introduces. Moreover, it avoids numerical issues such as scaling and overflow/underflow concerns at the expense of higher cost. Furthermore, floating-point implementation allows for an FFT co-processor to collaborate with general purpose processors. This offloads computationally intensive tasks from the primary processor.

The first part of this thesis, which is devoted to FFT co-processors, proposes a new FFT architecture that uses a new Binary-Signed Digit (BSD) carry-limited adder, a new floating-point

BSD multiplier and a new floating-point BSD three-operand adder. Finally, a new unit labeled as Fused-Dot-Product-Add (FDPA) is designed to compute  $AB \pm CD \pm E$  over floating-point BSD operands.

The second part of the thesis discusses decimal arithmetic operations implemented in hardware using redundant number systems. These operations are popularly used in decimal floating-point co-processors. A new signed-digit decimal adder is proposed along with a sequential decimal multiplier that uses redundant number systems to increase the operational frequency of the multiplier. New redundant decimal division and square-root units are also proposed.

The architectures proposed in this thesis were all implemented using Hardware-Description-Language (Verilog) and synthesized using Synopsys Design Compiler. The evaluation results prove the speed improvement of the new arithmetic units over previous pertinent works. Consequently, the FFT and decimal co-processors designed in this thesis work with at least 10% higher speed than that of previous works. These architectures are meant to fulfill the demand for the high-speed co-processors required in various applications such as multimedia services and financial computations.

#### **ACKNOWLEDGMENTS**

All research was sponsored by the Electrical and Computer Engineering department at the University of Saskatchewan and the Natural Science and Engineering Research Council (NSERC) of Canada. All the toolkits and standard cell libraries used in this research were provided by CMC Microsystems, Canada.

I would like to thank my supervisor Dr. Seok-Bum Ko, who provided inspiration and advice during my PhD program at the University of Saskatchewan. I would also like to thank Dr. Li Chen with whom I had my VLSI course in the first year of my PhD program. Special thanks to the committee members, Dr. Joseph E. Salt, Dr. Francis M. Bui and Dr. FangXiang Wu who helped improve the quality of the research and the thesis. In the end, I would like to thank my friends in the lab, specially L. Han who helped me a lot during the first two years of my PhD program.

# **CONTENTS**

| Permi   | ission to Use                | i    |

|---------|------------------------------|------|

| Abstra  | ract                         | ji   |

| Ackno   | owledgments                  | iv   |

| Conte   | ents                         | v    |

| List of | f Tables                     | viii |

| List of | f Figures                    | ix   |

| List of | f Algorithms                 | xi   |

| List of | f Abbreviations              | xii  |

| List of | f Publications               | xiii |

| 1 IN    | TRODUCTION & BACKGROUNDS     | 1    |

| 1.1     | Fast Fourier Transform (FFT) | 2    |

| 1.2     | Butterfly unit               | 4    |

| 1.3     | Floating-Point Arithmetic    | 7    |

| 1.4     | Redundant Number Systems     | 10   |

| 1.5     | Motivation of Research       | 12   |

| 1.6     | Objectives of the Thesis     | 14   |

| 1.7    | Novelties                                                  | 14 |

|--------|------------------------------------------------------------|----|

| 1.8    | Organization of the Thesis                                 | 15 |

| Part I |                                                            |    |

| 2 PR   | EVIOUS WORKS ON FFT PROCESSORS                             | 18 |

| 2.1    | Floating-Point Complex Multipliers [19]                    | 18 |

| 2.2    | Floating-Point Fused Butterfly Arithmetic [1]              | 19 |

| 2.3    | Floating-Point Fused Butterfly with Merged Multipliers [5] | 22 |

| 2.4    | Improved Floating-Point Dot-Product Unit [2]               | 23 |

| 2.5    | Summary of Previous FFT Architectures                      | 26 |

| 3 TH   | IE PROPOSED FFT ARCHITECTURE                               | 27 |

| 3.1    | The Proposed Butterfly Architecture                        |    |

| 3.     | 1.1 Data Representation                                    |    |

| 3.2    | The Proposed Redundant Floating-Point Multiplier           |    |

|        | 2.1 Partial Product Generation (PPG)                       |    |

| 3      | 2.2 Partial Product Reduction (PPR)                        |    |

| 3.3    | The Proposed Three-Operand Redundant Floating-Point Adder  |    |

| 3.4    | Conversion to and from BSD Representation                  | 61 |

| 4 EV   | ALUATIONS AND COMPARISON OF FFT ARCHITECTURES              | 63 |

| Part I | I                                                          |    |

| 5 DE   | CIMAL ADDITION                                             |    |

| 5.1    | The Proposed Redundant Decimal Adder                       |    |

| 5.2    | Evaluations and Comparisons of Decimal Redundant Adders    | 75 |

| 5      | 2.1 Decimal Redundant Adder of [31]                        | 75 |

| 5      | 2.2 The Proposed Decimal Redundant Adder                   | 76 |

| 6 DE   | CIMAL MULTIPLICATION                                       |    |

| 6.1    | Decimal Multiplication Overview                            | 78 |

| 6.2    | The Proposed Sequential Decimal Multiplier                 | 81 |

| 6      | 2.1 Partial Product Generation                             | 81 |

| 6    | 2.2 Partial Product Accumulation                            | 82  |

|------|-------------------------------------------------------------|-----|

| 6.3  | Evaluation and Comparison of Decimal Sequential Multipliers | 85  |

| 6    | 3.1 The Proposed Architecture                               | 87  |

| 6    | 3.2 Previous Works on Decimal Sequential Multiplier         | 88  |

| 7 DE | CIMAL DIVISION                                              | 90  |

| 7.1  | Decimal Digit-Recurrence Division Algorithm                 | 92  |

| 7.2  | Quotient Digit Selection (QDS)                              | 94  |

| 7.3  | Representation of the Divisor and Partial Remainders        | 96  |

| 7.4  | The Proposed Decimal Divider                                | 99  |

| 7.5  | Evaluations and Comparison of Decimal Dividers              | 102 |

| 8 DE | CIMAL SQUARE-ROOT                                           | 104 |

| 8.1  | Decimal Digit-Recurrence Square-Root                        | 105 |

| 8.2  | The Proposed Decimal Square-Root Unit                       | 108 |

| 8    | 2.1 Proposed Architecture                                   | 110 |

| 8.3  | Evaluations and Comparisons of Decimal Square-Root Units    | 116 |

| 9 CO | NCLUSIONS & FUTURE WORKS                                    | 119 |

| 9.1  | Conclusions                                                 | 119 |

| 9.2  | Future Works                                                | 122 |

| REFE | RENCES                                                      | 124 |

# LIST OF TABLES

| 1.1 | Encodings for a Decimal Digit                                                   | 11  |

|-----|---------------------------------------------------------------------------------|-----|

| 3.1 | Generation of <i>i</i> <sup>th</sup> partial product                            | 38  |

| 3.2 | 2-bit Leading-Zero Detection                                                    |     |

| 3.3 | Comparison of Floating-Point Three-Operand Adder                                |     |

| 4.1 | Critical Path Delay of the Proposed Floating-Point Butterfly Architecture       | 63  |

| 4.2 | Comparison of the Floating-Point Butterfly Architectures                        | 65  |

| 4.3 | Critical Path Delay of the Proposed Fixed-Point Butterfly Architecture (16-bit) | 66  |

| 5.1 | Truth Table of F1                                                               | 73  |

| 5.2 | Truth Table of F2                                                               |     |

| 5.3 | Comparison of Decimal Redundant Adders                                          |     |

| 6.1 | Selection of the easy-multiples                                                 | 82  |

| 6.2 | The Critical Path Delay of the Proposed Multiplier (ns)                         |     |

| 6.3 | Area Consumption of the Proposed 16-digit multiplier (µm²)                      |     |

| 6.4 | Comparison of Decimal Sequential Multipliers (16-digit multipliers)             |     |

| 7.1 | Notations and abbreviations                                                     | 91  |

| 7.2 | Critical Path of Decimal Dividers (16 digits)                                   |     |

| 7.3 | Comparison based on the Synthesis Results                                       |     |

| 8.1 | Critical Path Delay of the Proposed Design (16 digits)                          | 116 |

| 8.2 | Area consumption of the proposed 16-digit architecture (NAND2)                  |     |

| 8.3 | Comparison of the FP architectures                                              | 117 |

|     |                                                                                 |     |

# LIST OF FIGURES

| 1.1  | Implementation of an N-point FFT                                   | 4  |

|------|--------------------------------------------------------------------|----|

| 1.2  | 8-input FFT using DIT butterfly                                    |    |

| 1.3  | Butterfly Architecture (DIT)                                       |    |

| 1.4  | DIT Butterfly architecture using conventional approach_            |    |

| 1.5  | DIT Butterfly architecture using Golub's approach                  |    |

| 2.1  | Floating-point Dot-Product unit                                    | 20 |

| 2.2  | Floating-point fused Add-Subtract unit                             | 21 |

| 2.3  | Radix-2 floating-point DIF butterfly                               | 22 |

| 2.4  | Butterfly unit using merged multipliers                            | 23 |

| 2.5  | Enhanced floating-point dot-product unit (Single path)             | 24 |

| 2.6  | Enhanced floating-point dot-product unit (Dual path)               | 25 |

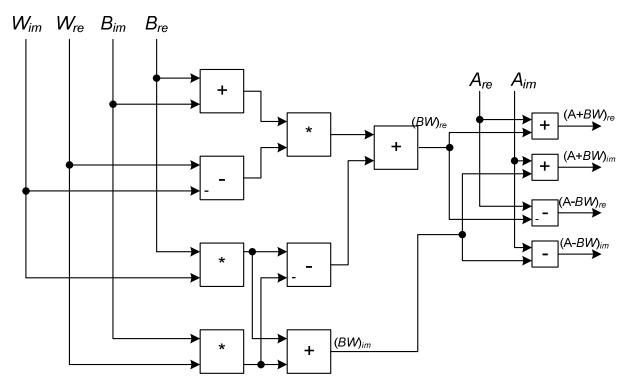

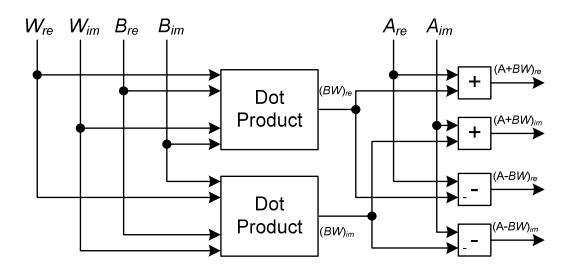

| 3.1  | Butterfly Architecture with Expanded Complex Numbers               | 28 |

| 3.2  | Butterfly Architecture with Dot-Product Units                      | 29 |

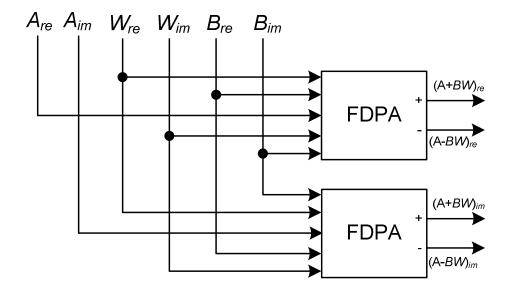

| 3.3  | Butterfly Architecture with Floating-point Fused-Dot-Product-Add   | 30 |

| 3.4  | Floating-point Fused-Dot-Product-Add (FDPA) with Dot-Product Units | 31 |

| 3.5  | Floating-point Fused-Dot-Product-Add (FDPA) with 3-Operand Adder   | 31 |

| 3.6  | Dot and symbolic notation of the significand of A <sub>re.</sub>   | 33 |

| 3.7  | Partial Product Generation of the modified Booth encoding          | 36 |

| 3.8  | Generating the Multiples of the Multiplicand                       | 36 |

| 3.9  | Generation of the <i>i</i> <sup>th</sup> partial product           | 39 |

| 3.10 | Partial Product Reduction by Rows                                  |    |

| 3.11 | [p:1] reduction block based on [p/2:1] blocks                      | 40 |

| 3.12 | [7:3] Counter by Full-Adders                                       | 42 |

|      | [7:2] Compressor by Full-Adders                                    |    |

|      | [4:2] Compressor by Full-Adders                                    |    |

| 3.15 | [16:2] Compressor by [4:2] Compressors                             | 44 |

| 3.16 | The proposed BSD adder (two digit slice)                           | 45 |

|      | Partial Product Reduction Tree                                     |    |

|      | Final Product Format with Standard Non-redundant Operands          |    |

|      | Redundant Product of the Proposed Multiplier                       |    |

|      | The Proposed Redundant Floating-Point Multiplier                   |    |

|      | Straightforward Three-Operand Floating-Point Adder                 |    |

| 3.22 | Significand Alignment Block                                                 | 51  |

|------|-----------------------------------------------------------------------------|-----|

|      | Normalization Block                                                         |     |

| 3.24 | Value x between two floating-point values F1 and F2                         | 52  |

|      | Conventional Fused Three-Operand Floating-Point Adder                       |     |

|      | Exponent Comparison with Three Inputs                                       |     |

|      | Significand Alignment of the Fused Three-Operand Floating-Point Adder       |     |

| 3.28 | The Proposed Three-Operand Alignment Scheme_                                | 56  |

|      | BSD Adder with some inputs assigned to zero                                 |     |

|      | Non-zero Digits of No Significance                                          |     |

|      | 4-bit LZD Implemented Using 2-bit LZD                                       |     |

|      | The proposed floating-point three-operand addition                          |     |

|      | Conversion to BSD representation                                            |     |

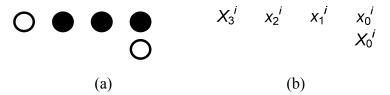

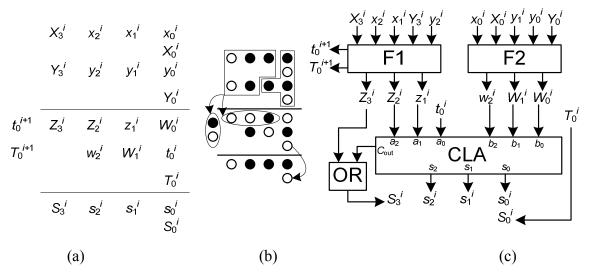

| 5.1  | Digit representation (a) Dot notation (b) Symbolic notation                 | 70  |

| 5.2  | The Proposed Adder (a) Symbolic Notation (b) Dot Notation (c) Block Diagram | 71  |

| 5.3  | Decimal Redundant Adder of [31]                                             | 75  |

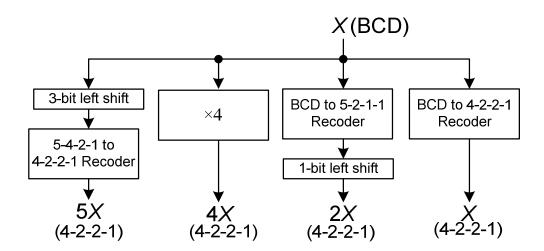

| 6.1  | Generation of the easy-multiples in the proposed multiplier                 | 81  |

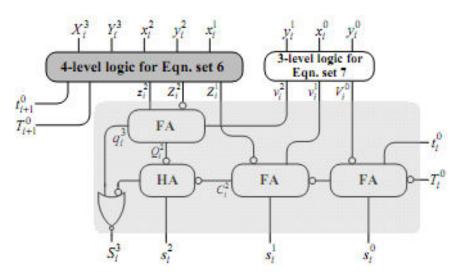

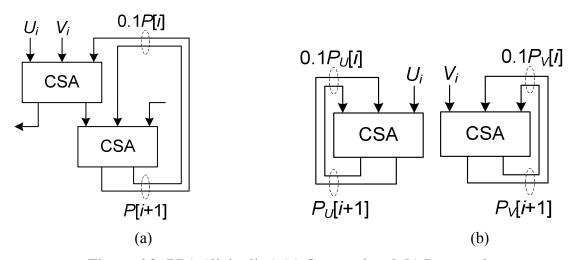

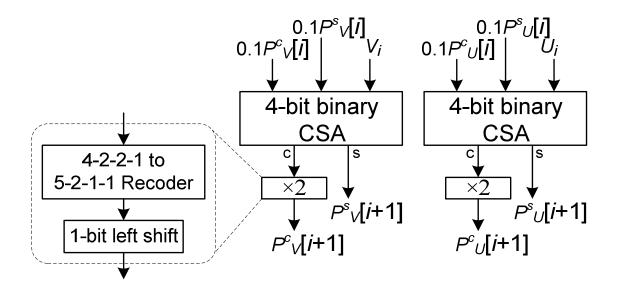

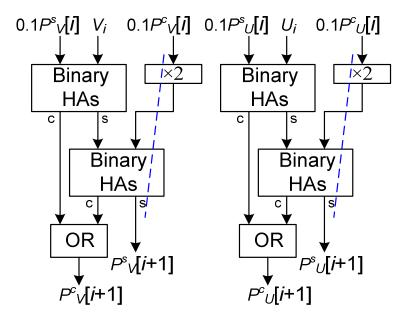

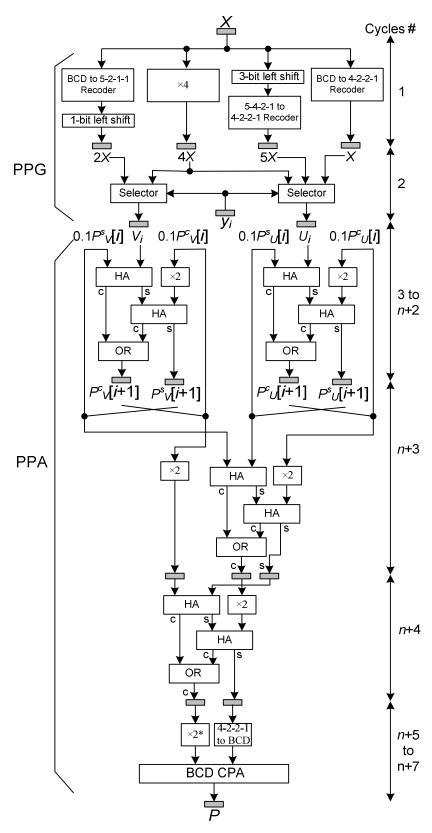

| 6.2  | PPA (digit-slice) (a) Conventional (b) Proposed                             | 83  |

| 6.3  | Implementation of Eqn. 6.5 via CSAs                                         | 84  |

| 6.4  | Modified Implementation of Eqn. 6.5                                         | 85  |

|      | The Proposed Sequential Decimal Multiplier_                                 |     |

| 6.6  | Delay Constrained Comparison                                                | 89  |

| 7.1  | The value of $\Delta_k$ shown in Robertson's Diagram                        | 95  |

| 7.2  | Digit Encodings for the Decimal Parts of the Partial Remainder and Divisor  | 100 |

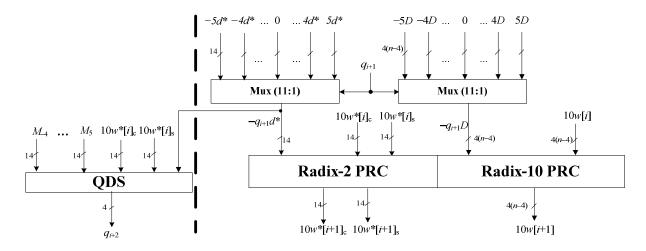

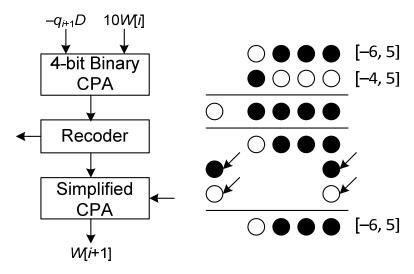

| 7.3  | The Architecture including QDS and PRC                                      | 100 |

| 7.4  | The Architecture including the Binary and Decimal QDS and PRC               | 101 |

| 7.5  | Radix-10 PRC (digit slice)                                                  | 102 |

| 8.1  | The Selection Intervals and the Comparison Multiples                        | 108 |

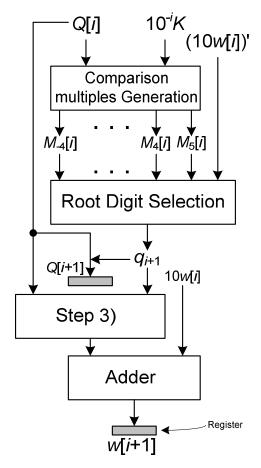

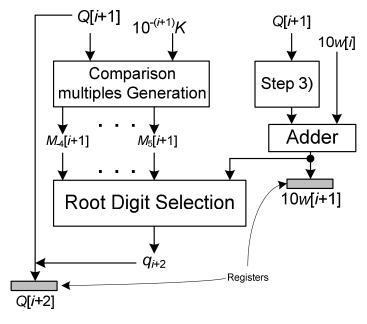

| 8.2  | The proposed decimal square root algorithm_                                 |     |

| 8.3  | The Straight-Forward Architecture                                           |     |

| 8.4  | Block Diagram of the Proposed Architecture                                  |     |

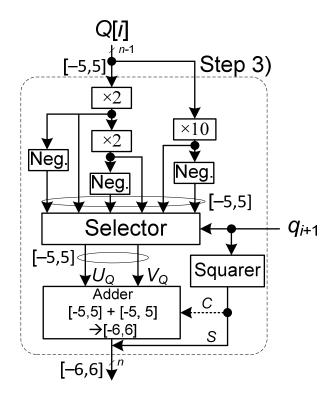

|      | Details of Step 3)                                                          |     |

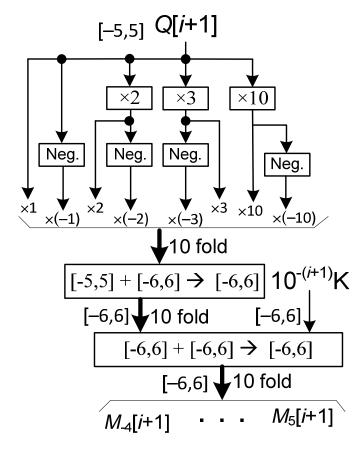

|      | Comparison Multiples Generation                                             |     |

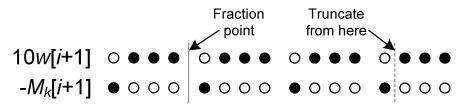

|      | Bit representations used in RDS                                             |     |

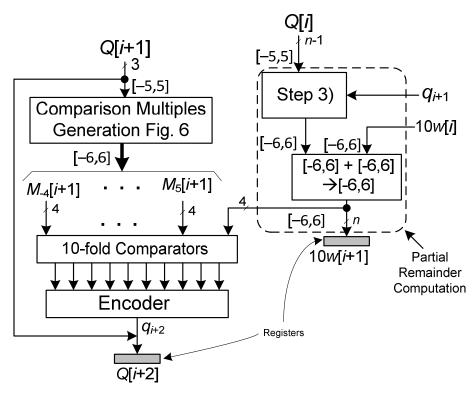

|      | The Proposed Architecture of the Recurrence Stage                           |     |

# LIST OF ALGORITHMS

| 1.1 | Carry-free addition                             | 11 |

|-----|-------------------------------------------------|----|

| 1.2 | Carry-limited addition                          | 12 |

| 5.1 | The proposed decimal addition                   | 70 |

| 6.1 | PPG based on digit-multiplication               | 79 |

|     | PPG based on easy-multiples of the multiplicand |    |

| 6.3 | The proposed PPA                                | 83 |

#### LIST OF ABBREVIATIONS

BCD Binary Coded Decimal

BSD Binary Signed Digit

CLA Carry Look-ahead Adder

CSA Carry Save Adder

DIF Decimation in Frequency

DIT Decimation in Time

DSP Digital Signal Processing

DSSD Decimal Septa Signed Digit

FA Full Adder

FDPA Fused Dot Product Add FFT Fast Fourier Transform FMA Fused Multiply Add GSD Generalized Signed Digit

HA Half Adder

LZA Leading Zero AnticipationLZD Leading Zero DetectionMCM Multiple Constant Multiplier

MMCM Merged Multiple Constant Multiplier

MSD Most Significant Digit

PP Partial Product

PPA Partial Product Accumulation

PPG Partial Product Generation

PPR Partial Product Reduction

PRC Partial Remainder Computation

QDS Quotient Digit Selection

RDS Root Digit Selection

RNS Residue Number System

WBP Weighted Binary Position

#### LIST OF PUBLICATIONS

#### Journals:

- 1. **Kaivani, A.** and S. Ko, "Floating-Point Butterfly Architecture Based on Binary Signed-Digit Representation," *IEEE Transactions on Very Large Scale Integration*, to appear, 2015.

- 2. **Kaivani, A.**, L. Han and S. Ko, "Improved design of high-frequency sequential decimal multipliers," *IET Electronics Letters*, Vol. 50, No. 7, pp. 558-560, 2014.

- 3. Han, L., **A. Kaivani** and S. Ko, "Area Efficient Sequential Decimal Fixed-point Multiplier," *Journal of Signal Processing Systems*, Vol. 75, No. 1, pp. 39-46, 2014.

- 4. **Kaivani**, **A.** and S. Ko, "Decimal Division Algorithms: The Issue of Partial Remainders," *Journal of Signal Processing Systems*, Vol. 73, No. 2, pp. 181-188, 2013.

- 5. **Kaivani, A.** and S. Ko, "Decimal SRT Square Root: Algorithm and Architecture," *Circuits, Systems and Signal Processing*, Vol. 32, No. 5, pp.2137-2150, 2013.

#### **Conferences:**

- 1. **Kaivani, A.** and S. Ko, "High-Speed FFT Processors Based on Redundant Number Systems," *IEEE International Symposium on Circuits and Systems (ISCAS'14)*, pp. 2237-2240, 2014.

- 2. **Kaivani, A.** and S. Ko, "Decimal signed digit addition using stored transfer encoding," *26th Annual IEEE Canadian Conference on Electrical and Computer Engineering (CCECE'13)*, pp.1-4, 2013.

- 3. **Kaivani, A.**, L. Chen and S. Ko, "High-frequency sequential decimal multipliers," *IEEE International Symposium on Circuits and Systems (ISCAS'12)*, pp. 3045-3048, 2012.

#### CHAPTER 1

#### INTRODUCTION & BACKGROUNDS

The need for high-speed processing greatly exceeds what general-purpose processors can handle. This is where, for instance, arithmetic co-processors can be used to offload computationally intensive tasks from the primary processor. Fast Fourier Transform (FFT) co-processors are used in real-time multimedia services and financial applications use decimal co-processors to perform large amounts of decimal computations.

A co-processor receives data from a general-purpose processor to execute time-consuming operations. After the co-processor is done processing the data, the results are sent back to the general-purpose processor. This approach saves time and offloads computationally intensive tasks from primary processors, therefore achieving higher overall performance. Of various available co-processors, the binary Fast Fourier Transform (FFT) co-processor and the decimal floating-point co-processor have received a lot of attention recently.

FFT circuitry consists of several consecutive multipliers and adders over complex numbers. Until recently, most FFT architectures used fixed-point arithmetic only, before FFTs based on floating-point operations became prominent [1, 2]. Using the IEEE-754-2008 standard [3] for floating-point arithmetic allows FFT co-processors to collaborate with general purpose processors.

Despite the fact that binary computer arithmetic improves processing speed and reduces hardware complexity, decimal computer arithmetic has recently been revived. The advantage of decimal computer arithmetic over its binary counterpart is that decimal arithmetic is capable of mirroring human computations (i.e., radix-10) and representing fractions precisely where binary

cannot (e.g., 0.2) [8]. Some applications, such as finance and banking, cannot tolerate a loss of precision; this is where decimal computer arithmetic is useful.

Decimal computer arithmetic can be implemented in hardware or software. The software implementation of decimal arithmetic operations with binary logic devices was widely used until IBM revealed an all-hardware implementation of decimal processors such as the POWER6 decimal processor [9]. Additionally, the IEEE 754-2008 [3] standard for floating-point arithmetic now supports the decimal hardware implementation. Hardware decimal arithmetic is used where high-speed computations are performed on large amounts of data.

#### 1.1 Fast Fourier Transform (FFT)

N-point FFT computation is described in Eqn. 1.1, where d(k) is the input and  $W_N = e^{-2\pi i/N}$  is the complex twiddle factor.

$$X[n] = \sum_{k=0}^{N-1} d(k) \cdot W_N^{nk}; \quad n = 0, 1, \dots, N-1$$

(1.1)

As a result of Eqn. 1.1, the outputs are as follows:

$$X[0] = d(0)W_N^0 + d(1)W_N^{0\times 1} + \dots + d(N-1)W_N^{0\times (N-1)}$$

$$X[1] = d(0)W_N^0 + d(1)W_N^{1\times 1} + \dots + d(N-1)W_N^{1\times (N-1)}$$

: (1.2)

$$X[k] = d(0)W_N^0 + d(1)W_N^{k \times 1} + \dots + d(N-1)W_N^{k \times (N-1)}$$

:

$$X[N-1] = d(0)W_N^0 + d(1)W_N^{(N-1)\times 1} + \dots + d(N-1)W_N^{(N-1)\times (N-1)}$$

Consequently, implementation of Eqn. 1.1 requires  $N^2$  complex multiplication plus N(N-1) complex additions. Given that each complex multiplication (addition) includes four (zero) real multiplications and two (two) additions, in overall  $4N^2$  real multiplications and 2N(2N-1) real additions are required to implement Eqn. 1.1.

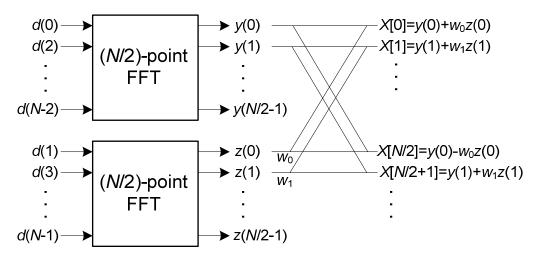

Cooley and Tukey [10] proposed an efficient algorithm which makes hardware realization of Eqn. 1.1 much easier. This algorithm, as shown in Eqn. 1.3, decomposes Eqn. 1.1 into even and odd indices. Therefore, the N-input FFT computation is simplified to the computation of two (N/2)-input FFT (see Fig. 1.1). Continuing this decomposition leads to 2-input FFT block also known as "butterfly" unit.

$$X[n] = \sum_{k=0}^{\frac{N}{2}-1} d(2k) \cdot W_N^{2nk} + \sum_{k=0}^{\frac{N}{2}-1} d(2k+1) \cdot W_N^{n(2k+1)}$$

$$= \sum_{k=0}^{\frac{N}{2}-1} d(2k) \cdot W_N^{2nk} + W_N^n \sum_{k=0}^{\frac{N}{2}-1} d(2k+1) \cdot W_N^{2nk}$$

$$= \sum_{k=0}^{\frac{N}{2}-1} d(2k) \cdot W_N^{2nk} + W_N^n \sum_{k=0}^{\frac{N}{2}-1} d(2k+1) \cdot W_N^{2nk}$$

$$\xrightarrow{W_N^{2nk} = e^{\frac{-2\pi i}{N/2}nk} = e^{\frac{-2\pi i}{N/2}nk} = W_{N/2}^{nk}} X[n] = \sum_{k=0}^{\frac{N}{2}-1} d(2k) \cdot W_{N/2}^{nk} + W_N^n \sum_{k=0}^{\frac{N}{2}-1} d(2k+1) \cdot W_{N/2}^{nk}$$

$$\xrightarrow{W_N^{k+N/2} = -W_N^k} X[n+\frac{N}{2}] = \sum_{k=0}^{\frac{N}{2}-1} d(2k) \cdot W_{N/2}^{nk} - W_N^n \sum_{k=0}^{\frac{N}{2}-1} d(2k+1) \cdot W_{N/2}^{nk}$$

There are two FFT architectures, decimation in time (DIT) and decimation in frequency (DIF). The former, shown in Fig. 1.1, consists of a complex multiplication followed by complex add/sub operations, while the latter requires the add/sub operations prior to the multiplication.

There are other FFT algorithms in the literature such as radix-3 [11], radix-4 [12], mixed radix [13], split radix [14], convolution-based (e.g., Winograd [15] and Bluestein [16]), to name

a few. However, the radix-2 Cooley-Tukey algorithm is known as the most efficient algorithm for hardware implementation due to its simplicity.

Figure 1.1: Implementation of an N-point FFT

Generally, *N*-point DIT FFT implementation using Cooley-Tukey algorithm can be summarized as:

- Number of stages =  $\log_2 N$

- Number of twiddle factors = N/2

- Number of butterfly units at each stage = N/2

- Difference between indices of the upper and lower leg of a butterfly unit =

2stage-1

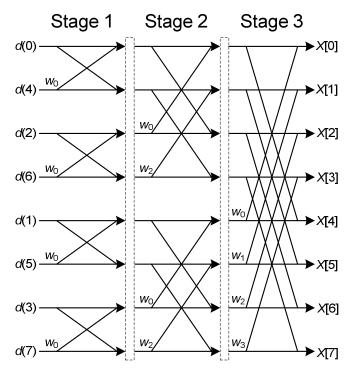

As an example, Fig. 1.2 illustrates the implementation of an 8-input DIT FFT.

# 1.2 Butterfly unit

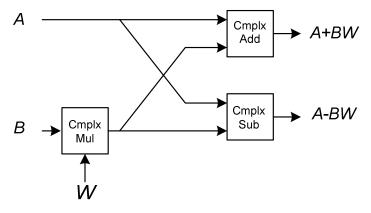

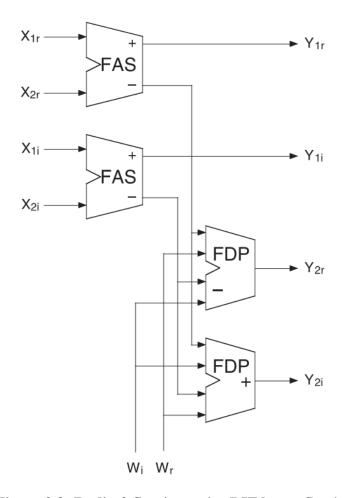

Butterfly unit is actually a fused-multiply-add/sub (FMA) over complex operands. Fig. 1.3 depicts a DIT butterfly unit which consists of a complex multiplier, a complex adder and a complex subtractor.

Figure 1.2: 8-input FFT using DIT butterfly

Figure 1.3: Butterfly Architecture (DIT)

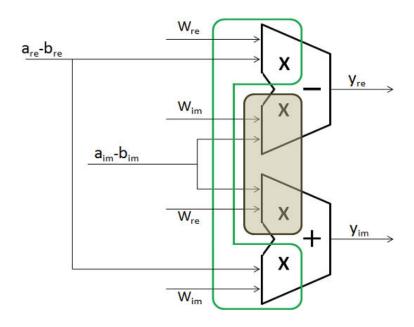

A complex number A consists of one real and one imaginary component such that  $A = d_{Re} + id_{Im}$ . Complex addition/subtraction  $\langle S_{Re}, S_{Im} \rangle = \langle A_{Re}, A_{Im} \rangle \pm \langle B_{Re}, B_{Im} \rangle$  includes two additions/subtractions over the real and imaginary components i.e.,  $S_{Re} = A_{Re} \pm B_{Re}$  and  $S_{Im} = A_{Im} \pm B_{Im}$ . Complex multiplication  $\langle P_{Re}, P_{Im} \rangle = \langle A_{Re}, A_{Im} \rangle \times \langle B_{Re}, B_{Im} \rangle$  is performed as shown in Eqn. 1.4.

$$P_{Re} = A_{Re}B_{Re} - A_{Im}B_{Im}; \quad P_{Im} = A_{Re}B_{Im} + A_{Im}B_{Re}$$

(1.4)

According to Eqn. 1.4, a complex multiplication requires four multiplications and two additions/subtractions. However, Golub algorithm introduces another equation (Eqn. 1.5) for the computation of the real component  $P_{Re}$  which, in some cases, leads to lower cost [19].

$$P_{Re} = (A_{Re} + A_{Im})(B_{Re} - B_{Im}) + A_{Re}B_{Im} - A_{Im}B_{Re}$$

(1.5)

Given that  $A_{Re}B_{Im}$  and  $A_{Im}B_{Re}$  are already computed for  $P_{Im}$ , Golub algorithm requires three multiplications and five additions/subtractions. This leads to a lower cost than the conventional method, assuming a multiplier costs at least 3 times more than an adder. Therefore, there are two methods to implement a butterfly unit: 1) conventional 2) Golub's approach.

Fig. 1.4 shows the implementation of a DIT butterfly with expanded complex numbers using the conventional approach. Accordingly, it consists of four multipliers and six adders/subtractors. It should be noted that, given the constant values of twiddle factors (*W*), the multipliers are constant and can be implemented via a series of shifters and adders in lieu of the multiplier tree. Fig. 1.5 shows the implementation of a DIT butterfly unit based on the Golub's approach. Accordingly, it consists of three multipliers and nine adders/subtractors.

Figure 1.4: DIT Butterfly architecture using conventional approach

Figure 1.5: DIT Butterfly architecture using Golub's approach

#### 1.3 Floating-Point Arithmetic

Floating-point arithmetic is being used, and preferred over fixed-point, in many applications due to the fact that it provides a large range of numbers and a high degree of precision. It is also common to be used in a variety of Digital Signal Processing (DSP) applications because it relieves the designer of numerical issues e.g., scaling, overflow, and underflow. A floating-point number, as represented in Eqn. 1.6, consists of four components; namely, *sign*, *significand*, *base* and *exponent*.

$$(-1)^{sign} \times significand \times (base)^{exponent}$$

(1.6)

The above four components for a single precision floating-point number, according to IEEE 754-2008 standard [3], take values as follows:

- $sign \in \{0,1\}$

- significand is a 24 bit number  $\in [1,2-2^{23}]$

- base = 2

- exponent is an 8 bit integer  $\in [-126,127]$

Given that *base* is always equal to two, it is only required to store the other three components. With the intention of storing these components efficiently, the following modifications are done:

- 1. It is always (exponent + bias) stored. Given bias = 127, the stored value belongs to [1,254]. The values 0 and 255 are reserved for special values.

- 2. Keeping *significand* normalized (i.e., the most significant bit is always 1), allows for storing only 23 bits of the significand. The most significant bit is known as a hidden bit.

Therefore, a single precision floating-point number covers  $[2^{-126}, 2^{128})$  and any number smaller than  $2^{-126}$  is a *denormalized* number. Consequently, 0 cannot be represented in a normalized range and a special code is assigned to represent 0 i.e., *exponent* + *bias* = 0 and *significand* = 0.

IEEE 754-2008 standard [3] imposes special codes for the following special values:

- $\pm \mathbf{0}$ : exponent + bias = 0 and significant = 0

- **Denormalized number**: exponent + bias = 0 and significand  $\neq 0$

- $\pm \infty$ :  $exponent + bias = 255 \ and \ significand = 0$

- Not a Number (NaN): exponent + bias = 255 and significant  $\neq 0$

Floating-point addition/subtraction consists of the following:

a) Exponent difference: Determine exponent difference  $\Delta$  and the smaller exponent.

- b) Alignment shift: Shift right ( $\Delta$  positions) the significand of the number having a smaller exponent. The largest exponent is the result's exponent.

- c) *Addition/subtraction over significands*: Determine and perform the actual operation; may need to swap the operands.

- d) *Normalization shift*: Shift right 1 bit, in case of addition overflow. Detect the number of leading zeros and shift left, in case of subtraction, such that there is a new hidden 1 to the left of the binary point.

- e) *Rounding*: Use extra bits (Round, Guard and Sticky) to round the result. This may lead to post normalization.

- f) Exponent adjustment: Adjust the exponent to compensate for the shifts in d) and e).

In order to improve the speed of floating-point addition, dual-path architecture is usually used which separates the slow shifts (b and d) into different paths. This, however, requires parallel significand addition/subtraction modules.

Floating-point multiplication consists of the following:

- a) Multiplication of the significands: fixed-point multiplication over the significands

- b) Addition of exponents: The exponent of the result is determined by this addition.

- c) Normalization: This involves leading-zero-detection (LZD) and shifting.

- d) Rounding: Round the significand of the product according to standard rounding methods.

- e) Exponent adjustment: The shifts in d) calls for this exponent adjustment

In floating-point fused multiply add (FMA) operation, a and b of the multiplication can be performed in parallel with a and b of the addition. Consequently, there is no need to use dual path architecture [17]. Moreover, common steps of addition and multiplication (i.e., normalization, rounding and exponent adjustment) are usually combined to save area and time.

#### 1.4 Redundant Number Systems

Carry propagation is known as the main decelerator in digital arithmetic operations. Carry digits are the consequence of the fact that the value of the ith digit of the final result (e.g., sum in addition) can depend on the values of the operands in ith position and the less significant positions (0 to i–1).

There are some techniques to reduce the carry propagating latency such as Residue Number Systems (RNS) [7] and redundant number systems.

A number system, defined by radix r and digit-set  $[\alpha, \beta]$ , is redundant if and only if  $\beta - \alpha + 1 > r$  [7]. Moreover, the redundancy index of that digit-set is defined as  $\rho = \beta - \alpha + 1 - r$ . Amongst available digit-sets for a specific redundant number system, minimally and maximally redundant digit-sets are the most popular ones due to their unique features. A minimally redundant digit-set is the one with  $\rho = 1$ ; while a maximally redundant digit-set has the maximum cardinality represented with minimum number of bits. For example, the Binary signed-digit (BSD) representation with digit-set [-1, 1] is a redundant number system.

In addition to radix and digit-set values, the encoding used to represent a digit-set has a great impact on the performance and efficiency of a redundant number system. For example, Table 1.1 shows some encodings for r=10 and digit-set [0,10].

Assuming that the transfer digits are  $t_i \in [-\lambda, \mu]$ , the  $(\lambda - \alpha \le w_i \le \beta - \mu)$  condition must be satisfied to guarantee no carry-propagation in Step c of Algorithm 1.1. In other words the maximum (minimum) value of a transfer digit plus interim sum must fit into digit-set  $[\alpha, \beta]$ .

**Table 1.1: Encodings for a Decimal Digit**

| <b>Encoding Weights</b> | Dot notation |

|-------------------------|--------------|

| 8-4-2-1                 | • • • •      |

| 8-4-2-1-1               | • • • •      |

| 4-2-2-1-1               | • • • •      |

#### Algorithm 1.1: Carry-free addition

<u>Inputs:</u> Two redundant numbers  $X: x_{n-1} \cdots x_1 x_0$  and  $Y: y_{n-1} \cdots y_1 y_0$ .

Output: Addition result represented in redundant format  $S: s_n s_{n-1} \cdots s_1 s_0$ .

Perform followings for  $0 \le i < n$ , in parallel.

- a) Compute position sums  $p_i = x_i + y_i$ .

- b) Divide  $p_i$  into a transfer digit  $t_{i+1}$  and interim sum  $w_i$  such that  $w_i = p_i rt_{i+1}$ .

- c) Compute the final result as  $s_i = w_i + t_i$ .

**Example 1.1:** Carry-free addition as s = x + y, in redundant digit-set [-5, 9].

It is proven in [18] that carry-free addition is possible iff one of the following conditions is satisfied:

- $r \ge 3, \rho \ge 3$

- $r \ge 3, \rho = 2, \alpha \ne 1, \beta \ne 1$

Therefore, carry-free addition is not applicable to binary signed-digit representation with digit-set [-1,1]. In this case a carry-limited addition is available [7].

#### Algorithm 1.2: Carry-limited addition

<u>Inputs:</u> Two redundant numbers  $X: x_{n-1} \cdots x_1 x_0$  and  $Y: y_{n-1} \cdots y_1 y_0$ .

Output: Addition result represented in redundant format  $S: s_n s_{n-1} \cdots s_1 s_0$ .

Perform following steps for  $0 \le i < n$ , in parallel.

- a) Compute position sums  $p_i = x_i + y_i$ .

- b) Compare  $p_i$  to a constant to determine whether  $e_{i+1} = low$  or high ( $e_{i+1}$  is a binary range estimate for  $t_{i+1}$ ).

- c) Given  $e_i$ , divide  $p_i$  into a transfer digit  $t_{i+1}$  and interim sum  $w_i$  such that  $w_i = p_i rt_{i+1}$ .

- d) Compute the final result as  $s_i = w_i + t_i$ .

**Example 1.2:** Carry-limited addition as s = x + y, in binary signed-digit [-1, 1].

It should be noted that in Example 1.2 p = -1(1) is kept intact when the incoming carry is in [0,1] ([-1,0]), so as to guarantee no further carry-propagation.

#### 1.5 Motivation of Research

Carry propagation decelerates digital arithmetic operations. Redundant number systems are the most popular technique to overcome this challenge. A number system, defined by radix r and digit-set  $[\alpha, \beta]$ , is redundant if and only if  $\beta - \alpha + 1 > r$ .

Redundant number systems eliminate word-wide carry propagation within interim operations. However, the conversion from a redundant format to a non-redundant one requires carry-propagation. This makes redundant number systems mostly useful in applications where many consecutive arithmetic operations are performed prior to the final result making it a suitable technique to use in computer arithmetic co-processors. This thesis discusses the implementation of the binary floating-point FFT co-processor, and the decimal arithmetic co-processor.

Floating-point FFT circuitry consists of several consecutive multipliers and adders over complex numbers. The main advantage of floating-point over fixed-point arithmetic is the wide dynamic range it introduces. The main drawback of floating-point operations is their slowness compared with their fixed-point counterparts. One way to speed up floating-point arithmetic is merging several operations in a single floating-point unit to save delay, area and power consumption [2]. Previous works on floating-point FFT architectures have used this technique [1, 4, 5] to design a dot-product unit, to compute  $(A + B) \times (C + D)$ , so as to gain performance improvement.

Using redundant number systems [6] is another well-known way of improving the speed of floating-point arithmetic units, where there is no word-wide carry propagation within interim operations. The conversion from non-redundant to redundant format is a carry-free operation; however, the reverse conversion requires carry propagation [7].

Decimal computer arithmetic is inherently slower than its binary counterpart, since it is working based on a non-power-of-two radix. Likewise for the FFT co-processor, redundant number systems are very helpful in increasing the speed of the decimal arithmetic co-processor.

#### 1.6 Objectives of the Thesis

The main objective of this thesis is to design a high-speed co-processor based on redundant number systems. In particular, the architectures of the two of most commonly used co-processors will be redesigned based on redundant number systems to achieve improved performance.

The first part of this thesis investigates the advantages and costs of designing high-speed floating-point FFT architectures using redundant number systems. New architectures are proposed and compared to previous works.

The second part is devoted to proposing decimal arithmetic co-processors with architectures based on redundant number systems comparing them with previous works. A complete decimal arithmetic unit is designed accordingly, with four basic decimal arithmetic operations: addition, subtraction, multiplication and division. An architecture based on redundant number systems is also proposed for computing decimal square-root.

#### 1.7 Novelties

Although there are other works on the use of redundant floating-point number systems, they are not optimized for FFT architectures that require both a redundant floating-point multiplier and an adder. The novel techniques used in the new floating-point FFT architecture include:

- All significands are represented in binary signed-digit (BSD) format and the corresponding carry-limited adder is designed.

- Design of floating-point constant multipliers for operands with BSD significands.

- Design of floating-point three-operand adders for operands with BSD significands.

• Design of floating-point Fused-Dot-Product-Add units (i.e.,  $AB \pm CD \pm E$ ) for operands with BSD significands.

The novel techniques used in the new decimal floating-point arithmetic units include:

- Design of a decimal redundant adder based on signed-digit and stored transfer encoding.

- Design of a high-speed sequential decimal multiplier based on unconventional representations.

- Design of a decimal divider with redundant representation of the quotient and partial remainders.

- Design of a high-speed decimal square-root based on redundant number representation.

#### 1.8 Organization of the Thesis

The rest of the thesis is divided into two main parts. Part I discusses the details of the new floating-point FFT co-processor designed based on redundant number systems. Previous works on floating-point FFT co-processors are presented in Chapter 2. In Chapter 3 (partially published in [63, 64]), the new FFT architectures are explained in detail. These architectures are designed based on the new floating-point redundant multiplier and the new Binary signed-digit (a redundant representation) three-operand adder. Chapter 4 includes the evaluation results of the new floating-point arithmetic units used in the new FFT co-processor. These results are compared with those of previous works.

Part II of this thesis presents the details of the new decimal arithmetic units designed based on redundant number systems. Chapter 5 (partially published in [65]) presents the details of the new redundant decimal adder. The new sequential decimal multiplier, based on an unconventional redundant representation, is explained in Chapter 6 (partially published in [66,

67, 68]). In Chapter 7 (partially published in [69]), a new decimal divider that represents quotient and partial remainders in a redundant format is proposed. Chapter 8 (partially published in [70]) presents the new decimal square-root unit. Finally, Chapter 9 is devoted to the conclusions and future works.

# Part I FFT Co-Processors

#### **CHAPTER 2**

#### PREVIOUS WORKS ON FFT PROCESSORS

This chapter discusses the previous works related to floating-point FFT processors which includes butterfly architectures and complex multipliers.

#### 2.1 Floating-Point Complex Multipliers [19]

This work [19] focuses on the design of a floating-point complex multiplier with the help of fused floating-point arithmetic.

Conventional and Golub's method are two approaches based on which the paper [19] designs floating-point complex multipliers. As is also mentioned in previous section, Golub's method requires fewer multipliers but more adders than the conventional approach. Authors opt for conventional method, due to the fact that the latency and cost of floating-point adders are close to those of floating-point multipliers. Consequently, Golub's method is not recommended for floating-point implementations.

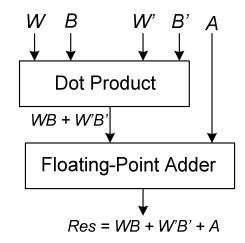

The paper [19] proposes a fused-dot-product unit which performs two multiplications and then adds the products i.e., AB + CD. With this unit, efficiency is achieved due to the elimination of the interim rounding and normalization of the fused-dot-product unit [19]. A conventional complex multiplier is then designed using two fused-dot-product units.

Floating-point fused-add-subtract is another unit designed in the paper [19]. This unit computes both floating-point sum and difference of two input operands. It combines the common parts of floating-point addition and subtraction and hence significantly lower power/area cost.

The third floating-point unit discussed in [19] is a fused-dot-product-add/subtract unit, which is a combination of the two previous units. This new unit has four inputs (A, B, C, D) and two outputs X = AB + CD and Y = AB - CD. A Golub's complex multiplier is then designed using the latter two units.

Taking advantage of the aforementioned fused units, the paper [19] concludes that "Golub's method results in a modest increase in complexity and power consumption and a large increase in delay relative to the conventional method. This is true even when fused implementations are used" [19].

# 2.2 Floating-Point Fused Butterfly Arithmetic [1]

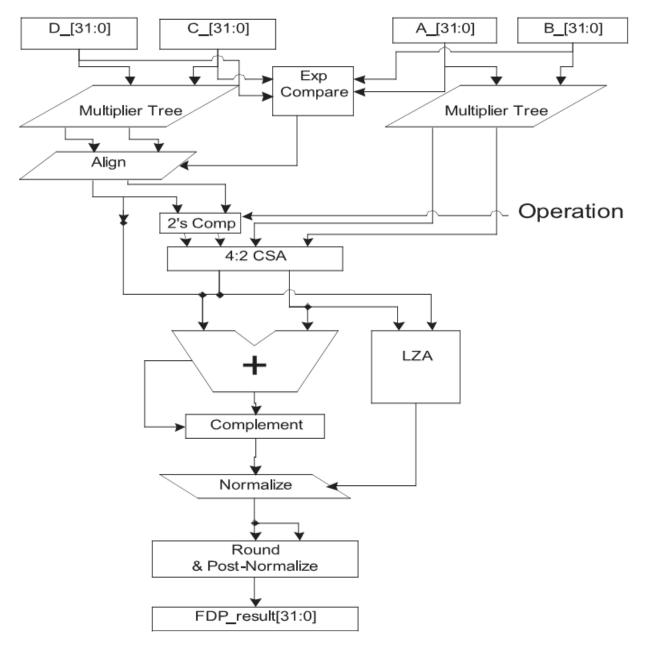

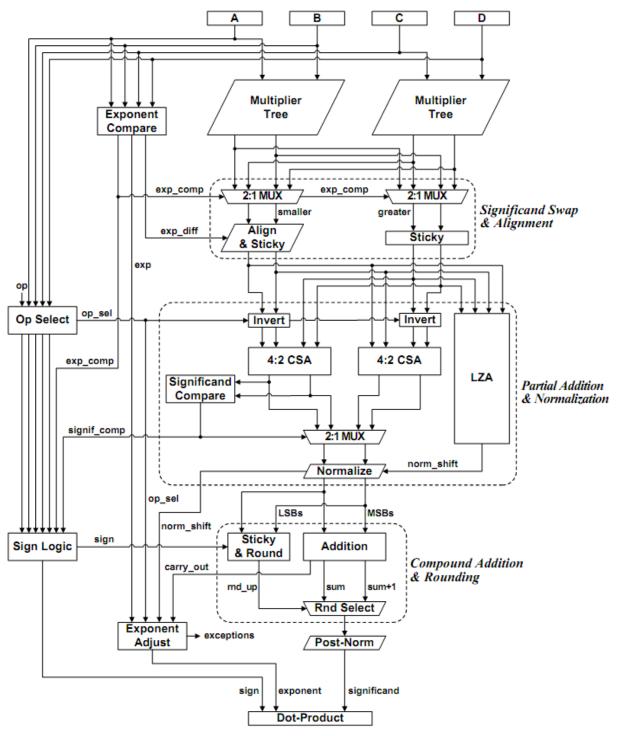

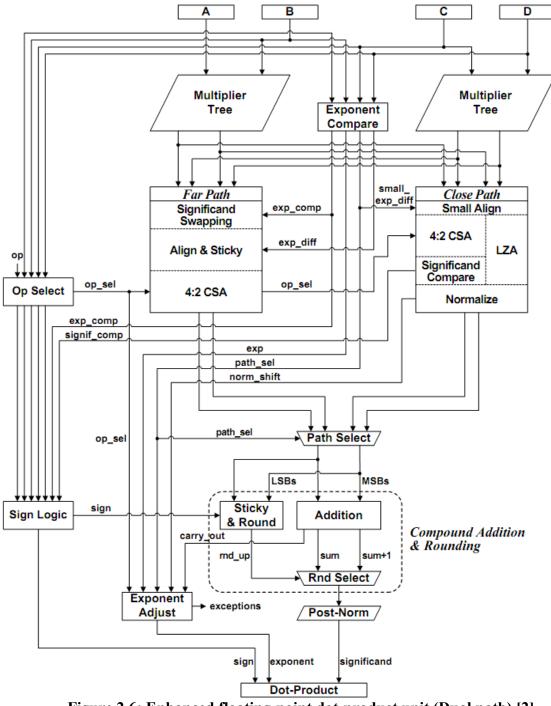

This work [1] improves the performance of butterfly unit and hence FFT processors by proposing two fused floating-point operations, namely, Dot-Product (Fig. 2.1) and Add-Subtract (Fig. 2.2).

The Dot-Product unit, compute AB+CD, consists of the following operations:

- Two floating-point multipliers, perform in parallel

- Alignment Shift

- (4:2) Compressor

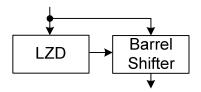

- Carry-propagating adder, performs in parallel with Leading-Zero-Detector (LZD)

- Normalization & Rounding

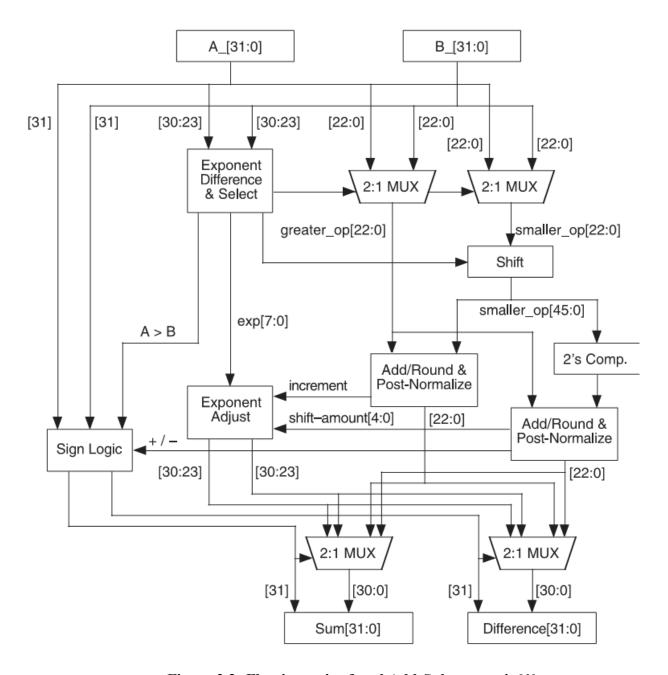

The fused Add-Subtract unit, compute  $A\pm B$ , consists of the following operations:

- Exponent difference block, perform in parallel with MUXes to select significands

- Alignment Shift

- A subtraction and an addition perform in parallel

- Exponent adjustment, perform in parallel with rounding and normalization

- MUXes to select Add/Subtract results

Figure 2.1: Floating-point Dot-Product unit [1]; Result = AB±CD

Next a radix-2 (Fig. 2.3) butterfly (Decimation in Frequency) unit is designed using Dot-Product and fused ADD-Subtract modules. It has been shown that the proposed radix-2 butterfly architecture requires 35% lower area cost and is 15% faster than its discrete (not fused) implementation.

Figure 2.2: Floating-point fused Add-Subtract unit [1]

Moreover, a radix-4 butterfly (Decimation in Time) unit is designed using Dot-Product and fused Add-Subtract modules. It has been shown that the proposed radix-4 butterfly architecture requires 26% lower area cost and is 13% faster than its discrete (not fused) implementation.

Figure 2.3: Radix-2 floating-point DIF butterfly [1]

In overall, the paper [1] shows that using fused operations to implement butterfly units (and FFT) leads to faster modules with lower area cost. This advantage is mainly achieved because of removing some extra rounding & normalization operations e.g., those of floating-point multipliers.

# 2.3 Floating-Point Fused Butterfly with Merged Multipliers [5]

Use of merged constant multipliers increases the performance of floating-point fused butterfly units. As mentioned before, given the constant values of twiddle factors, the conventional multipliers can be replaced by simple shift-add operations. In [5], it has been shown

that (for a 1024-point FFT) more than 28% percent of shift-coefficients of the shifters between real and imaginary parts of the twiddle factors are the same. For example, the shift coefficients of  $W_{re}^{798}$  are 1, 5, 8 and 11 while those of  $W_{im}^{798}$  are 0, 5, 9 and 11. Therefore, two coefficients, in this case (5 and 11), are the same [5]. Taking advantage of the same shift-coefficients reduces the power consumption of the butterfly units. Fig. 2.4 shows the butterfly unit of [5] using the merged multipliers.

Figure 2.4: Butterfly unit using merged multipliers [5]

## 2.4 Improved Floating-Point Dot-Product Unit [2]

This work [2] is a modification to floating-point dot-product unit. The major improvements include:

- Reducing the shift amount in the alignment step

- Performing early normalization so as to reduce latency

- A four-input Leading-Zero-Detector is used over redundant operands to reduce critical path delay

- The dual path algorithm is also presented for speed improvement

Figs. 2.5 and 2.6 show the single path and dual path implementations of the enhanced dot-product of this work, respectively.

Figure 2.5: Enhanced floating-point dot-product unit (Single path) [2]

It has been shown that the enhanced single (dual) path dot-product unit consumes 25% (19%) lower area and 16% (26%) lower latency compared to the conventional method. This dot-product unit can be used in the design of a high-performance butterfly unit. Replacing the dot-product unit of [1] with this faster one, leads to a high-speed butterfly unit.

Figure 2.6: Enhanced floating-point dot-product unit (Dual path) [2]

### 2.5 Summary of Previous FFT Architectures

The first paper [19] is just about complex multipliers which is used in butterfly units. It concludes that the conventional architecture is more suitable for floating-point operands than Golub's method. The reason lies within the fact that the latency and cost of floating-point adders are close to those of floating-point multipliers. Consequently, Golub's method is not recommended for floating-point implementations.

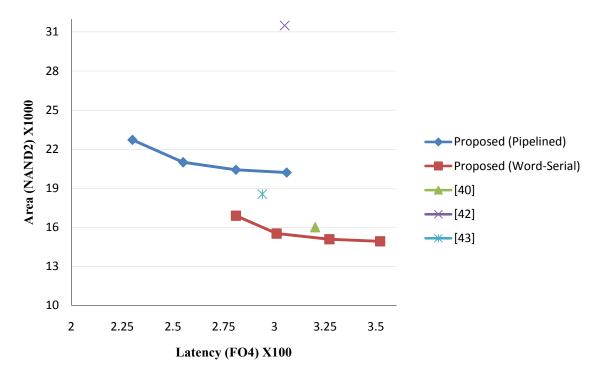

The two major works on floating-point FFT/butterfly architecture are [5, 1]. The former introduces architectures based on multiple-constant multipliers (MCM) and merged multiple-constant multiplier (MMCM), amongst which the fastest design reported to have the latency of 4.08ns with the area consumption of  $97,302\mu m^2$ , in 45nm CMOS technology.

The other work [1] designs a floating-point butterfly unit using novel dot-product blocks. This work, simulated based on 45nm CMOS technology, has the latency of 4.00ns with area cost of about  $47,489\mu m^2$ . The dot-product unit of this design is reported to have a latency of about 2.72ns with  $16,104\mu m^2$  area cost.

The most recent work [2] has proposed a very fast floating-point dot-product unit which can be used in the design of a high-performance butterfly unit. Replacing the dot-product unit of [1] with this faster one, leads to a high-speed butterfly architecture.

In a nutshell, a butterfly unit designed based on the combination of [1, 2] is the fastest architecture for both single-path and dual-path designs; while the architecture of [1] consumes the lowest area.

### CHAPTER 3

# THE PROPOSED FFT ARCHITECTURE<sup>1</sup>

The proposed FFT architecture is based on the Cooley-Tukey algorithm which is the most efficient FFT algorithm for hardware implementation. As is mentioned in the previous section, an N-point DIT FFT implementation using Cooley-Tukey algorithm has  $\log_2 N$  stages, each of which consists of N/2 butterfly units. Moreover, N/2 twiddle factors are required, which can be pre-computed and stored a look-up table.

Therefore, the butterfly unit is the major building block of an FFT processor. Having the butterfly architecture, one can design the N-point FFT block using  $\log_2 N$  stages, each of which consists of N/2 butterfly units working in parallel. Therefore, the latency of each stage is equal to that of a butterfly unit plus those of registers. Consequently, the details of the proposed butterfly architecture will be discussed in the following sub-sections.

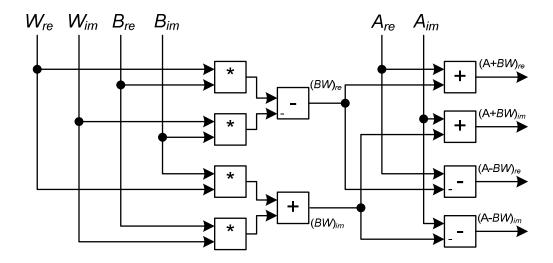

## 3.1 The Proposed Butterfly Architecture

The proposed butterfly is actually a complex Fused-Multiply-Add followed by a complex addition with floating point operands. Expanding the complex numbers, Fig. 3.1 depicts the required modules for a butterfly unit. A naive approach to implement Fig. 3.1 is to cascade floating-point operations i.e., floating-point multiplication followed by two cascaded floating-point addition/subtraction. A more efficient approach is to merge the floating-point multiplication with the first floating-point addition/subtraction. This method leads to a floating-point Fused-Multiply-Add followed by a floating-point addition/subtraction.

1

<sup>&</sup>lt;sup>1</sup> Published @ 1) IEEE Transactions on VLSI, 2) ISCAS'14

Figure 3.1: Butterfly Architecture with Expanded Complex Numbers

Using the floating-point Fused-Multiply-Add, as is discussed in Section 1.5, would save time, area and power. However, the butterfly function cannot be directly implemented by Fused-Multiply-Add (i.e., A+BC). In order to circumvent this problem a Dot-Product unit is required, which is an extension to Fused-Multiply-Add operation.

A Dot-Product unit computes AB+CD or AB-CD. This unit is capable of saving more time, area and power than Fused-Multiply-Add. The reason lies in the fact that a Dot-Product unit combines more floating-point operands and hence eliminating more intermediate Normalization, Rounding and Leading-Zero-Detection. Combining floating-point operations, although seems interesting and an easy way of saving time, area and power, leads to precision loss which need to be taken care of, meticulously.

For example, in a Fused-Multiply-Add unit the combination of the multiplication with the addition removes the intermediate Rounding, Normalization and Leading-Zero-Detection after the multiplication. However, it is important to pass wider operands (more number of bits) to the floating-point addition such that the required precision can be recovered at the end of the addition.

For a Dot-Product unit the loss of precision is more critical, given that the Rounding, Normalization and Leading-Zero-Detection of two multiplications are now removed and left to be dealt with at the end of the addition. Consequently, more bits have to be passed to the floating-point addition so as to be able to recover the required precision. Fig. 3.2 depicts a butterfly architecture implemented using Dot-Product units.

Figure 3.2: Butterfly Architecture with Dot-Product Units

According to Fig. 3.2, the constituent operations of a floating-point butterfly unit are a floating-point Dot-Product (e.g.,  $B_{re}W_{im} + B_{im}W_{re}$ ) followed by a floating-point addition/subtraction. Extending the concept of combining floating-point operations even further leads to the proposed Fused-Dot-Product-Add (FDPA) operation (e.g.,  $B_{re}W_{im} + B_{im}W_{re} + A_{im}$ ) over floating-point operands. Fig. 3.3 shows the butterfly unit implemented using the Fused-Dot-Product-Add unit.

It should be noted that in Fig. 3.3 the FDPA units provide two outputs (dubbed - and +). The - output computes  $B_{re}W_{im} + B_{im}W_{re} - A_{im}$  while the + output is the result of  $B_{re}W_{im} + B_{im}W_{re} + A_{im}$ .

Figure 3.3: Butterfly Architecture with Floating-point Fused-Dot-Product-Add

It will be shown later that given the sign embedded representation of the floating-point operands of the FDPA, generating the second output is done with no extra latency and almost no extra area cost.

The Fused-Dot-Product-Add unit can be implemented in two ways:

- a) Combining a floating-point Dot-Product unit with a floating-point addition.

- b) Combining a floating-point multiplication with a floating-point three-operand addition.

Approach a) is a direct extension of Fig. 3.2 where the intermediate Rounding, Normalization and Leading-Zero-Detection (after Dot-Product) are eliminated and left to be dealt with after the addition. Fig. 3.4 illustrates the proposed floating-point FDPA unit implemented using Dot-Product units. This makes the required circuitry to guarantee the correct precision even more complicated, given that now three consecutive operations are combined (i.e., Multiplication and two additions). Moreover, even more number of bits are required to be passed between operations so as to reach the desired precision.

Figure 3.4: Floating-point Fused-Dot-Product-Add (FDPA) with Dot-Product Units

Figure 3.5: Floating-point Fused-Dot-Product-Add (FDPA) with 3-Operand Adder

Approach b) sees the floating-point fused-dot-product-add unit as a combination of a floating-point multiplier followed by a floating-point three operand addition. This eliminates the Rounding, Normalization and Leading-Zero-Detection after the multiplication as well as the one inside the floating-point three-operand adder. Fig. 3.5 illustrates the proposed floating-point fused-dot-product-add (FDPA) unit implemented using two floating-point multiplications followed by a three-operand floating-point addition.

### 3.1.1 Data Representation

The representation of the floating-point operands has a significant impact on the number of bits (weighted positions) required to be passed to the next operation. There is a need to find the most efficient representation for the exponent and significands of the floating-point operands. Moreover, a redundant representation, at least for the significands, is desired so as to eliminate intermediate carry-propagation.

Having a redundant representation for a floating-point operation creates some other challenges specially with the rounding and normalization. For instance, in a redundant floating-point adder designed by Fahmy and Flynn [20] a radix-16 redundant representation is used.

Assuming a maximally redundant radix-16 signed digit representation, with [-15, 15] as the digit set, each digit can be represented by a 5-bit 2's complement number. However, this leads to an invalid value (i.e., -16). Therefore, the first challenge would be designing the floating-point adder such that -16 cannot be generated in the output.

Determining the rounding position is another challenge, because the binary position for inserting the round value should be determined based on the non-redundant value of the significand (i.e., IEEE format). In other words, rounding the redundant representation and then converting it to non-redundant format must lead to the same value if it is converted first and then the result is rounded.

Leading-Zero-Detection is another challenge, which is somehow related to the rounding challenge. In the process of converting to non-redundant representation, a -1 value might be propagated to the most-significant position and turn it into zero. This would also change the correct rounding position. For higher radix-representations (e.g., radix-16) this may lead to a rounding position shifted as far as four digits.

In the process of choosing a redundant representation for the significand, it should be noted that higher radix representation leads to lower number of extra bit to store a significand; however, it leads to a small carry-propagation inside each digit. For example, radix-16 redundant representation requires a 4-bit carry-propagation inside a digit. Moreover, a higher radix representation requires a more complicated digit adder.

According to the above discussion, the followings present the data representation that will be used for the proposed butterfly architecture. The exponents of all inputs are represented in two's complement, after subtracting the bias. The value of the bias is determined by the IEEE format used.

The significands of  $A_{re}$ ,  $A_{im}$ ,  $B_{re}$  and  $B_{im}$  are represented in binary signed digit (BSD). Within the BSD representation (shown in Fig. 3.6 for  $A_{re}$ ) every binary position takes values of  $\{-1,0,1\}$  represented by one negative-weighted bit (*negabit*) [6] and one positive-weighted bit (*posibit*). Negabits (Posibits) are shown in white (black) dots and capital (small) letters.

Figure 3.6: Dot and symbolic notation of the significand of  $A_{re}$

The significand of W is stored in the modified Booth encoding [7] in which every binary position takes a value of  $\{-1,0,1\}$  where there is at least one 0 in two adjacent positions. Therefore, only multiples of  $\pm B$  and  $\pm 2B$  are required which can be computed easily by shift and negation. This leads to a simpler partial product generation phase in the multiplier. The conversion to the modified Booth encoding is actually a radix-4 digit-set conversion i.e., from [0, 3] to [-2, 2].

For converting an *n*-bit binary number y ( $y_{n-1}y_{n-2}...y_0$ ) to a modified Booth representation z the first step is to put every 2 bits of y into a group such that

$$v_j = 2y_{2j+1} + y_{2j}$$

$j = \frac{n}{2} - 1, ..., 0$  (3.1)

The second step is to divide  $v_j$  into a radix-4 transfer  $t_{j+1}$  and an interim sum  $w_j$ ; such that

$$v_i = 4t_{i+1} + w_i (3.2)$$

Finally, the third step is to generate  $z_j$  by adding the same weighted transfers and interim sums such that

$$z_j = t_j + w_j \tag{3.3}$$

It should be noted that the third step has to be done in a carry-free manner i.e., the addition must not produce any further carry. This is guaranteed if the second step is performed such that

$$-2 \le w_i \le 1 \text{ and } 0 \le t_i \le 1$$

(3.4)

This is achieved if the following rules hold during the conversion:

$$w_{j} = \begin{cases} v_{j} & \text{if } v_{j} \leq 1 \\ v_{i} - 4 & \text{if } v_{i} \geq 2 \end{cases} \qquad t_{j+1} = \begin{cases} 0 & \text{if } v_{j} \leq 1 \\ 1 & \text{if } v_{i} \geq 2 \end{cases}$$

(3.5)

The details of the proposed redundant floating-point multiplier and the proposed redundant three-operand floating-point adder are presented below.

## 3.2 The Proposed Redundant Floating-Point Multiplier

Floating-point multiplication, as is discussed in Chapter 2, consists of operations on the exponents and those on the significands. The former is just a simple addition of the exponent; although, there may be a need for exponent adjustment in the normalization and rounding phase.

The latter, however, is the most time-consuming part of a floating-point multiplier. Multiplication over significands consists of three major steps called: 1) Partial Product Generation, 2) Partial Product Reduction and 3) Final Addition.

The proposed multiplier, likewise other parallel multipliers, consists of two major steps, namely, partial product generation (PPG) and partial product reduction (PPR). However, contrary to conventional multipliers, the proposed multiplier keeps the product in redundant format and hence there is no need for the final carry-propagating adder.

#### 3.2.1 Partial Product Generation (PPG)

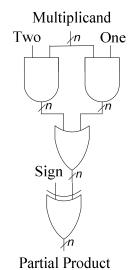

The partial product generation, in a 2's complement representation of the multiplicand and multiplier, consists of arrays of AND operation such that each bit of the multiplier is ANDed to the whole bits of the multiplicand. This is not the case if the operands are represented in redundant format and/or Booth encoding. For example, if the multiplier is represented in the modified Booth encoding, the partial product generation looks like the circuitry shown in Fig. 3.7 [17].

Partial product generation of a redundant multiplier is even more complicated, since the cardinality of the multiplier's digit-set is more than the radix. Generating the multiples of the multiplicand is easy (shift and negation) for  $\pm 2x$  and  $\pm 1x$ ; however,  $\pm 3x$  and  $\pm 5x$  (if exists) involve an addition. Fig. 3.8 shows how these multiples are generated. Consequently, higher redundancy factor (see Chapter 2) leads to more complicated partial product generation; although it provides faster redundant addition.

Figure 3.7: Partial Product Generation of the modified Booth encoding

Figure 3.8: Generating the Multiples of the Multiplicand

The PPG step of the proposed multiplier is completely different from that of the conventional one because of the representation of the input operands (B, W, B', W'). Moreover, given that  $W_{re}$  and  $W_{im}$  are constants, the multiplications over significands can be computed via a series of shifters and adders.

For example, multiplying B1 by 113 (1110001)<sub>2</sub> can be done by the following shift and add steps [7]:

Step a: B2 = Shift B1 left for 1 bit

Step *b*: B3 = R2 + B1

Step c: B6 = Shift B3 left for 1 bit

Step *d*: B7 = B6 + B1

Step e: B112 = Shift B7 left for 4 bits

Step f: B113 = B112 + B1

In order to speed-up the above operation one may use the following sets of operations; however, it requires a hardware to be able to perform shift and add, simultaneously.

Step a: B3 = (Shift B1 left for 1 bit) + B1

Step b: B7 = (Shift B3 left for 1 bit) + B1

Step c: B113 = (Shift B7 left for 4 bits) + B1

It should be noted that in order to perform the above steps, there is also a need for a barrel shifter to be able to shift an operand for various number of bits. For example, Steps a & b require 1 bit shifts however, Step c requires a 4-bit shift. The other sequence would be the one shown below, where there is a need for both addition and subtraction.

Step a: B8 = Shift B1 left for 3 bits

Step *b*: B7 = B8 - B1

Step c: B112 = Shift B7 left for 4 bits

Step d: B113 = B112 + B1

Having the ability of performing subtraction is mostly useful when the multiplier has a series of consecutive 1s in its binary representation. In this case one may need to perform lots of addition operations however, with a subtraction operation only one subtraction and one addition are required.

With the intention of reducing the number of adders, the significand of W is stored in modified Booth encoding [7] in which every binary position takes a value of  $\{-1,0,1\}$  where there is at least one 0 in two adjacent positions. Therefore,  $\left\lceil \frac{n}{2} \right\rceil$  add/sub is sufficient to compute an n-by-n multiplication.

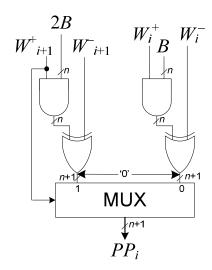

Given the modified Booth representation of  $W_{re}$  and  $W_{im}$  one partial product (PP), selected from multiplicand B, is generated per two binary positions of the multiplier W, as shown in Table 3.1. Note that each binary position (e.g.,  $W_i$ ) consists of two bits  $W_i^-W_i^+$  to represent -1, 0 or 1.

Table 3.1: Generation of  $i^{th}$  partial product

| $W_{i+1}^- W_{i+1}^+$ | $W_i^-W_i^+$ | $  W_{i+1}^{-}W_{i+1}^{+}W_{i}^{-}W_{i}^{+}  $ | $PP_i$       |

|-----------------------|--------------|------------------------------------------------|--------------|

| 0 0                   | 0 0          | 0                                              | 0            |

| 0 0                   | 0 1          | 1                                              | В            |

| 0 0                   | 1 1          | -1                                             | − <i>B</i>   |

| 0 1                   | 0 0          | 2                                              | $2 \times B$ |

| 1 1                   | 0 0          | -2                                             | -2 × B       |

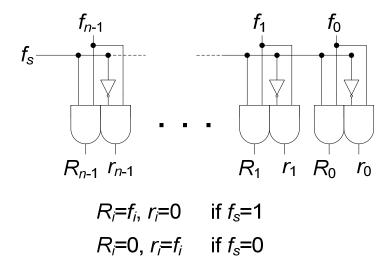

Fig. 3.9 illustrates the required circuitry for the generation of  $PP_i$  based on Table 3.1. It should be noted that given the binary-signed-digit (BSD) representation of multiplicand B, the value of -B (-2B) is generated through a simple NOT over all bits of B (2B).

Moreover, 2B is generated via a 1-bit left shift over B. Note that each partial product consists of (n+1) digits (i.e., binary positions), each of which has a negabit and a posibit.

#### 3.2.2 Partial Product Reduction (PPR)

Partial product reduction phase is actually a multi-operand addition of the partial products generated in the partial product generation phase.

Figure 3.9: Generation of the  $i^{th}$  partial product

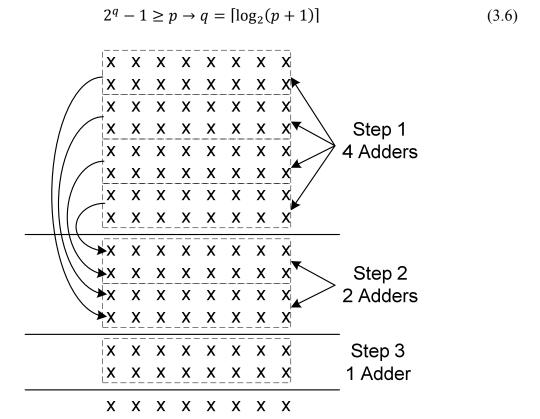

In general, there are two approaches to reduce the partial products; 1) reduction by rows and 2) reduction by columns. The former uses adders which could be either redundant adders or carry-propagating adders. Let's say 8 partial products are reduced using the adders (i.e., reduction by rows). Fig. 3.10 depicts the required steps. It takes 3 steps to reduce the 8 operands while each step has the latency of one adder. The total number of adders used in this reduction method is seven.

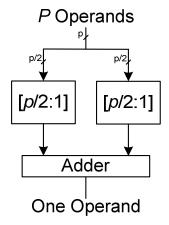

Generalizing this approach for p operands (i.e., [p:1] reduction block) is described next. Reduction of p operands can be divided into two parts, each of which reduces p/2 operands (i.e., [p/2:1] reduction block); and then add the outputs together.

Fig. 3.11 shows the reduction of p operands using reduction blocks for p/2 operands. Each of those [p/2:1] modules could be further divided into two sub modules. Continuing this approach leads to a [2:1] reduction block which is known as a carry-propagating adder. Consequently,  $\log(p)$  steps are required to reduce p operands to 1.

Reduction by columns is done by modules called counters or compressors. These modules take p bits, all at the same weighted position, and generate q bits of adjacent weights. In

other words, the number of 1s in p bits is counted and represented in a q-bit number. That is why these modules are called [p:q] counters. Therefore, the following relation between q and p holds [17].

Figure 3.10: Partial Product Reduction by Rows

Figure 3.11: [p:1] reduction block based on [p/2:1] blocks

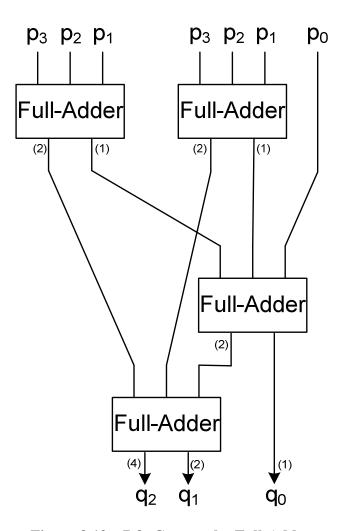

A [3:2] counter is simply a full-adder which is implemented using the following logical expressions:

$$q_1 = p_2 p_1 + p_2 p_0 + p_1 p_0, \ q_0 = p_2 \oplus p_1 \oplus p_0 \tag{3.7}$$

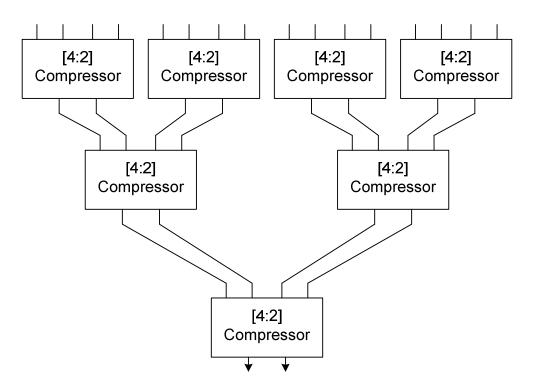

Larger counters can be built using full-adders and half-adders (i.e., [2:2] counter). For example, Fig. 3.12 depicts a [7:3] counter implemented by full-adders. The numbers next to each wire show the weight of that input/output. It should be noted that in a counter all same weighted outputs can be added together using a full-adder. The final output is a 3-bit number which counts the number of 1s in the input p.

Having multiple counters working in parallel leads to a multi-column counter which can be used to reduce several columns. In a multi-column counter, there are multiple counters each of which performing on a single weighted position and passes the carries to the next higher weighted column. For example, Fig. 3.13 shows a [7:2] compressor which passes the carries to the next higher weighted position and receives input carries from the lower weighted position. It should be noted that this module is called [7:2] compressor, because 2 bits are not enough to count 7 bits.

Therefore, partial product reduction phase of a multiplier can be taken care of by multicolumn compressors. These modules take *p* bits of a single column (same weights) and reduce it

into two bits per column. For example, a 54-by-54 bit multiplier generates 54 partial products. In

order to reduce these partial products one could design a [54:2] compressor to reduce them to

only two operands. Then a carry-propagating adder, over the two operands, generates the final

product. Large compressors/counters can be built based on smaller ones. For instance, Fig. 3.15

shows a [16:2] compressor based on [4:2] compressors (Fig. 3.14). The PPR step of the proposed

multiplier is based on the reduction by row approach, however, it is completely different from that of the conventional method.

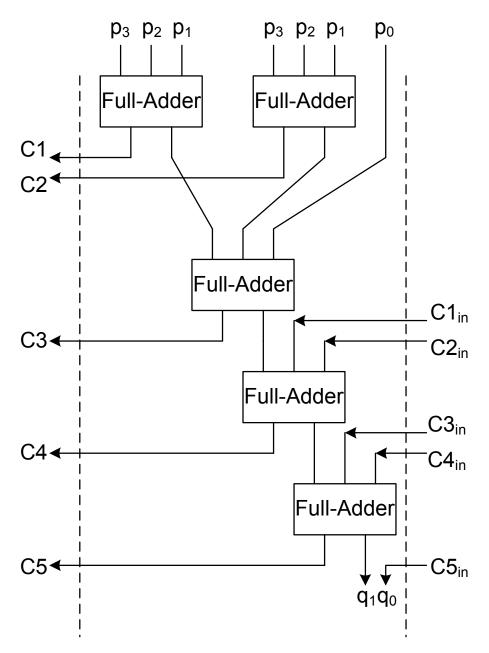

Figure 3.12: [7:3] Counter by Full-Adders

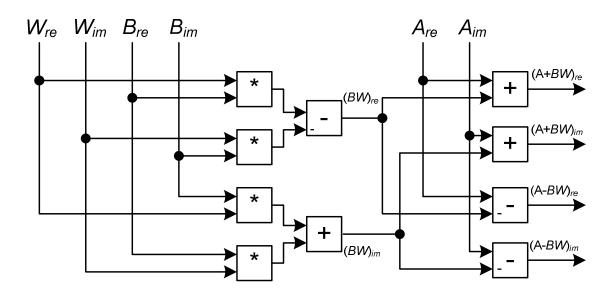

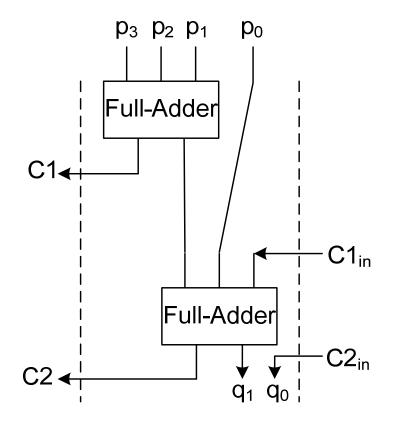

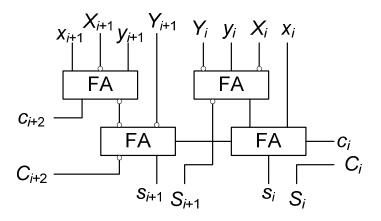

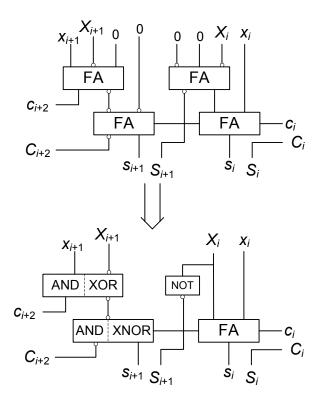

Given that partial products are all represented in a redundant encoding i.e., Binary-Signed-Digit, there is a need for an adder/counter that works on BSD digits. This carry-limited addition circuitry is shown in Fig. 3.16, where capital (small) letters symbolize negabits (posibits). The white dots are logical NOT operators required over negabit signals [6]. The critical path delay of this adder consists of three full-adders.

Figure 3.13: [7:2] Compressor by Full-Adders

Since the BSD adder is actually a carry-limited adder, reducing the partial product using this adder can be deemed as a reduction-by-column or reduction-by-row approach. In either case, the major constituent of the PPR step is the proposed carry-limited addition over the operands represented in BSD format.

Figure 3.14: [4:2] Compressor by Full-Adders

Figure 3.15: [16:2] Compressor by [4:2] Compressors

Figure 3.16: The proposed BSD adder (two digit slice)

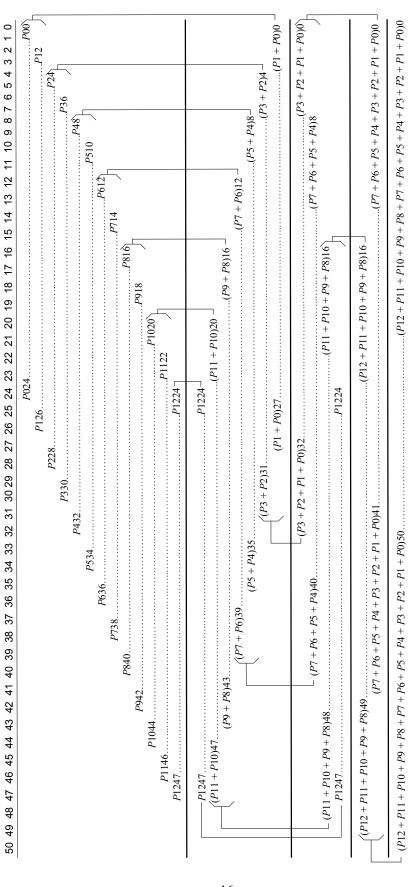

Once the partial products are generated, in PPG step, carry-limited adders (Fig. 3.16) are used to generate the final product. Therefore, for an *n*-by-*n* multiplier,  $\left\lceil \frac{n}{2} \right\rceil + 1$  (1 for the hidden bit of *W* encoded in modified Booth) partial products are generated and  $\lceil \log n \rceil - 1$  levels of BSD adders are required to produce the product.

Since each partial product  $(PP_i)$  is (n+1)-digit (n,...,0) which is either B (n-1,...,0) or 2B (n,...,1), the length of the final product may be more than 2n. For example, a 24-digit multiplier (compliant with IEEE single precision format) leads to a 51-digit product. Assuming that the sign-embedded significands of inputs A and B (24 bits) are represented in Binary-Signed-Digit; while that of W is represented in modified Booth encoding (25 bits). The last partial product has 24-(binary position) width (instead of 25), given that the most significant bit of W is always 1 (hidden bit).

The multiplication over significands is implemented using the partial product generation (PPG) unit of Fig. 3.9 and BSD adders of Fig. 3.16. The reduction of the partial products is done in four levels, as shown in Fig. 3.17, using twelve BSD adders.

Figure 3.17: Partial Product Reduction Tree

The numbers in the first row of Fig. 3.17 show the bit positions of each partial product. For example, P024 symbolizes bit position 24 of first partial product (PP0). Note that the last partial product has 24-(binary position) width (instead of 25), given that the 26th bit of W is always 1 (hidden bit).

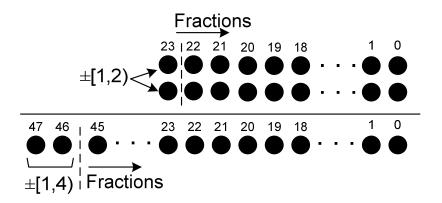

Now that the product is generated, it is required to determine how many bits are required to be passed to the three-operand adder so as to meet the precision requirements. As is shown in Fig. 3.17, the final product is a 51-bit number represented in Binary-Signed-Digit encoding. Given the normalized single precision formats of the inputs (B is in  $\pm [1, 2)$  and B in B in

If the multiplier's operands were represented in standard IEEE format (i.e., each with 24 bits), the final product would fit into 48 binary positions (47...0). Consequently, positions 45 down to 0 would be fractions (see Fig. 3.18). However, the product out of the proposed BSD multiplier has 51 binary positions. Given that the value of this number is the same as that of the standard product, the 45 least significant positions are fractions.

Figure 3.18: Final Product Format with Standard Non-redundant Operands

Similar to standard binary representation, Guard (G) and Round (R) positions are sufficient for correct rounding. Therefore, only 23+2 fractional binary positions of the final product are required to guarantee the final error less than  $2^{-23}$  (required by IEEE Standard).

Selecting 25 binary positions out of 46 fractional positions of the final product dismisses positions 0 to 20. However, the addition of the next step would produce carries to Guard and Round positions. Nevertheless, because of the carry-limited BSD addition, contrary to standard binary addition, only positions 20 and 19 may produce such carries.

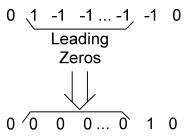

It should be noted that each position of a BSD number has the value of {-1, 0, 1}, while converting this representation to the standard non-redundant format a -1 carry could be propagated to the most-significant digit (MSD) and may turn the MSD into 0. In this case, the rounding position (determined based on the number of detected zeros) might be one position to right of the least-significant digit. Therefore, again positions 20 and 19 are enough to be passed to the three-operand adder.

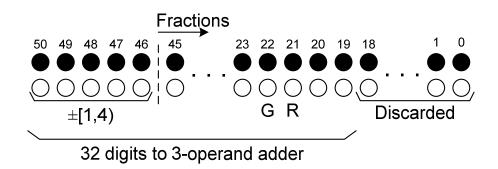

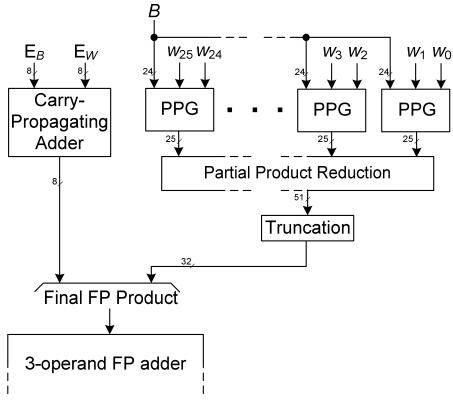

In overall, positions 0 to 18 of the final product are not used and hence a simpler PPR tree is possible. Fig. 3.19 shows the required digits passed to the three-operand adder. Fig. 3.20 illustrates the proposed redundant floating-point multiplier.

Figure 3.19: Redundant Product of the Proposed Multiplier

The exponents of the input operands are taken care of in the same way as is done in conventional floating-point multipliers; i.e., adding the exponents to get the product's exponent. However, normalization and rounding are left to be done in the next block of the butterfly architecture (i.e., three-operand adder).

Figure 3.20: The Proposed Redundant Floating-Point Multiplier

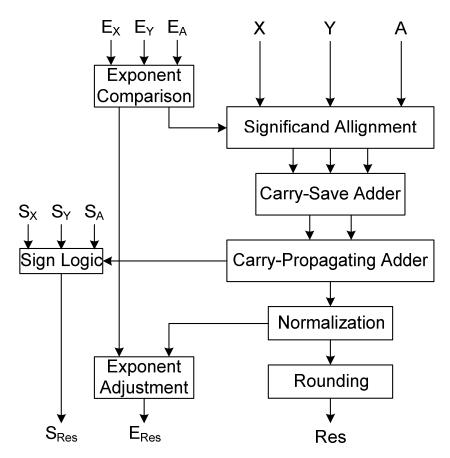

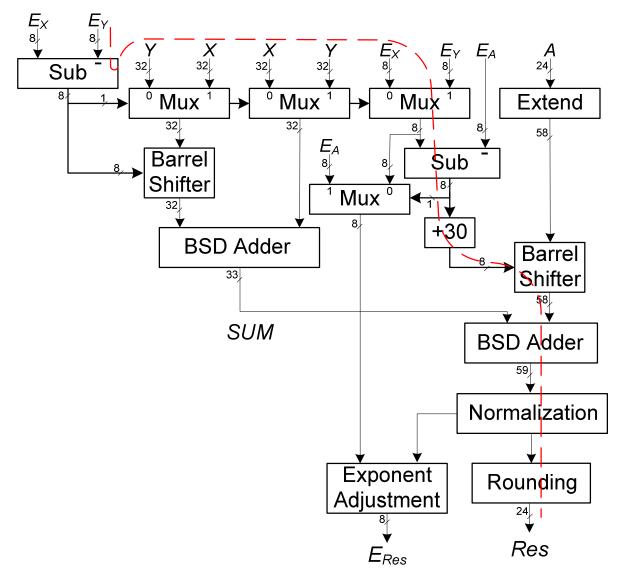

### 3.3 The Proposed Three-Operand Redundant Floating-Point Adder

The proposed three-operand floating-point adder (computing Res = X + Y + A) accepts three operands as inputs:

- X and Y: The products of the redundant floating-point multipliers, each of which with a 32-digit significand

- A: The floating-point input with a 24-digit significand

The straightforward approach to perform a three-operand floating-point addition is to cascade two floating-point adders, as shown in Fig. 3.21.

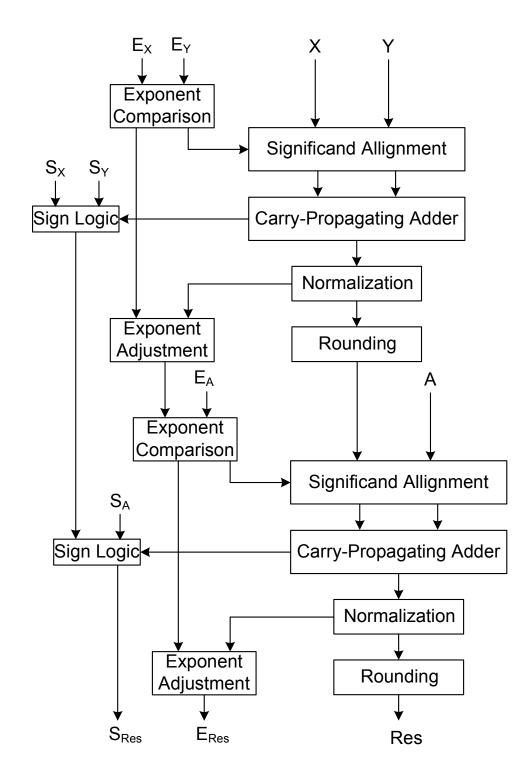

Figure 3.21: Straightforward Three-Operand Floating-Point Adder

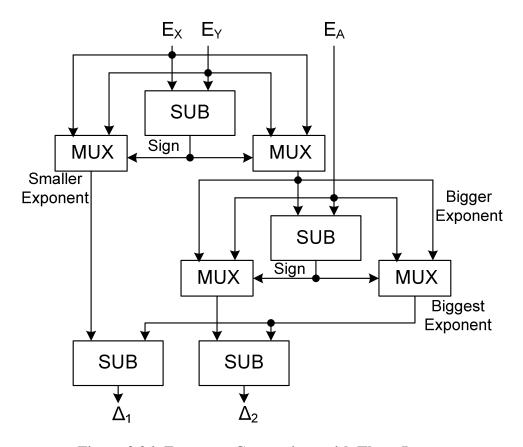

The followings discuss the details of each building block in the straightforward threeoperand floating-point adder:

- Exponent Comparison: It is a simple 8-bit subtractor. The output is the difference

Δ (could be negative or positive) between the two exponents, passed to the significand alignment block and the exponent adjustment block.

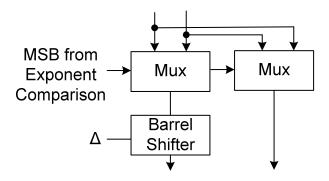

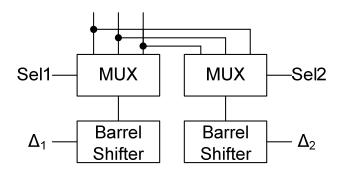

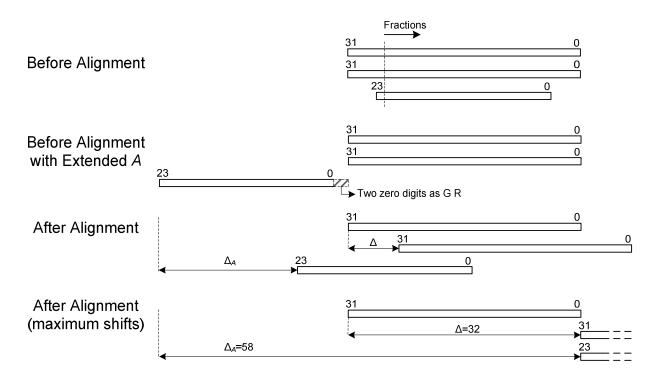

- Significand Alignment: This block consists of a multiplexer and a barrel shifter (shown in Fig. 3.22). The multiplexer selects the significand with the smaller exponent and passes it to the barrel shifter. The barrel shifter shifts the selected significand for  $\Delta$  bits to the right. The other significand goes to the output intact.

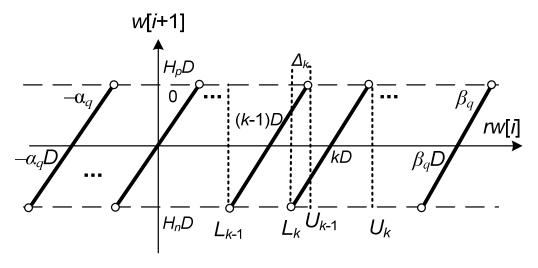

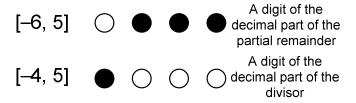

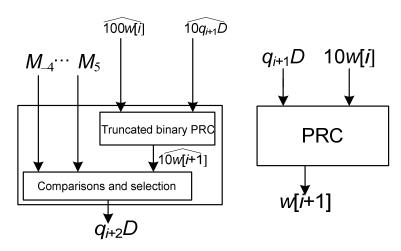

Figure 3.22: Significand Alignment Block