# FEASIBILITY STUDY OF USING A DIGITAL COMPUTER AS A VARIABLE-AMPLITUDE VARIABLE-FREQUENCY OSCILLATOR

#### A Thesis

Submitted to The College of Graduate Studies and Research in Partial Fulfillment of the Requirements for the Degree of

Master of Science

in The Department of Electrical Engineering University of Saskatchewan

by

ZAIPUNA OBEDI YONAH Saskatoon, Saskatchewan August, 1988

Copyright (C) 1988 Zaipuna Obedi Yonah

# UNIVERSITY OF SASKATCHEWAN DEPARTMENT OF ELECTRICAL ENGINEERING

## CERTIFICATION OF THESIS WORK

| We, the undersigned, certify that Zaipuna Obedi YONAH ,                        |

|--------------------------------------------------------------------------------|

| candidate for the Degree of Master of Science in Electrical Engineering, has   |

| presented his thesis on the subject Feasibility Study Of Using A Digital       |

| Computer As A Variable-Amplitude Variable Frequency Oscillator                 |

| that this thesis is acceptable in form and content, and that this student      |

| demonstrated a satisfactory knowledge of the field covered by his thesis in an |

| oral examination held on August 12, 1988 .                                     |

|                                                                                |

| external Examiner: D. Language of Computation Sel.                             |

| Internal Examiners:                                                            |

| An Self Straft                                                                 |

| Date: August 12, 1988                                                          |

# **COPYRIGHT**

The author has agreed that the library, University of Saskatchewan, shall make this thesis freely available for inspection. Moreover, the author has agreed that permission for extensive copying of this thesis for scholarly purposes may be granted by the professor or professors who supervised the thesis work recorded herein or, in their absence, by the Head of the Department or the Dean of the College in which the thesis work was done. It is understood that due recognition will be given to the author of this thesis and to the University of Saskatchewan in any use of the material in this thesis. Copying or publication or any other use of the thesis for financial gain without approval by the University of Saskatchewan and the author's written permission is prohibited. Requests for permission to copy or to make other use of material in this thesis in whole or in part should be addressed to:

Head of the Department of Electrical Engineering University of Saskatchewan Saskatoon, Saskatchewan CANADA. S7N 0W0

# **ACKNOWLEDGEMENTS**

The author expresses his thanks to Dr. A.M. El-Serafi and Professor A.E. Krause, in twofold. First, he thankfully acknowledges their advice, help, and encouragement in the preparation of this thesis. Second, he is grateful to their perception and insight which guided him to combine the ideas of electrical machines and those of computers throughout the course of this study.

The author expresses his appreciation to Keith Jeffrey for his valuable contributions during the development of the programs for the oscillator. He gives special thanks to his sister Anna Zaipuna for her encouragement during the study. He also acknowledges the moral support provided by his parents, friends and other family members.

The author gratefully acknowledges the financial help provided by the Government of Canada through The Canadian Commonwealth Scholarship and Fellowship Plan. Lastly, the author wishes to thank his employer, The University of Dar Es Salaam, Tanzania, for granting him the study leave to pursue this work.

#### UNIVERSITY OF SASKATCHEWAN Electrical Engineering Abstract No. 88A292

# FEASIBILITY STUDY OF USING A DIGITAL COMPUTER AS A VARIABLE-AMPLITUDE VARIABLE-FREQUENCY OSCILLATOR

Student: Zaipuna O. Yonah Supervisors: Dr. A.M. El-Serafi Prof. A.E. Krause

M.Sc. Thesis Presented to

The College of Graduate Studies and Research.

August, 1988

#### ABSTRACT

Previous studies have shown that a dual-excited synchronous generator (a machine which has two identical field windings on the rotor: one on the d-axis and the other on the q-axis) can run asynchronously at any speed and still generate voltage at constant frequency. This capability of the generator can be utilized for variable-speed constant-frequency operation if the windings are both excited by slip frequency alternating currents. The main problem in such schemes is the design of a source which can supply such control signals whose frequency changes with the slip.

This thesis is a feasibility study of using a digital computer as a variable-amplitude variable-frequency oscillator; which generates the two-phase sinusoidal excitation control signals for the dual-excited synchronous generator. In this thesis, the oscillator control methodology is formulated and experimentally verified. The performance of the oscillator is experimentally investigated. The experimental results of the methodology verification and the oscillator performance tests are presented. The results show that it is feasible to use a digital computer as a variable-amplitude variable-frequency oscillator. The oscillator software-based design is flexible for generating different types of signal waveforms. By a single control variable, the software can be configured to vary the oscillator frequency range, and to greatly reduce (almost eliminate) the harmonic distortion of the output signals. Some recommendations for further research are included.

# TABLE OF CONTENTS

| COPYRIGHT                                                  | i        |  |  |

|------------------------------------------------------------|----------|--|--|

| ACKNOWLEDGEMENTS                                           |          |  |  |

| ABSTRACT                                                   |          |  |  |

| TABLE OF CONTENTS                                          |          |  |  |

|                                                            |          |  |  |

| LIST OF SYMBOLS                                            | vii<br>x |  |  |

|                                                            |          |  |  |

| 1. INTRODUCTION                                            | 1        |  |  |

| 1.1. General                                               | 1        |  |  |

| 1.2. Variable-Speed Constant-Frequency Schemes             | 2        |  |  |

| 1.3. Generation of Frequency Controlled Signals            | 5        |  |  |

| 1.4. The Dual-Excited Synchronous Generator                | 5        |  |  |

| 1.4.1. Operation of the Dual-Excited Synchronous Generator | 6        |  |  |

| 1.4.2. Excitation Requirements                             | 10       |  |  |

| 1.5. Thesis Objective                                      | 11       |  |  |

| 1.5.1. Initial Specifications                              | 11       |  |  |

| 1.5.2. The Proposed Variable-Amplitude Variable-Frequency  | 12       |  |  |

| Digital Oscillator                                         |          |  |  |

| 1.5.3. The Scope of Study                                  | 12       |  |  |

| 2. THE DIGITAL VARIABLE-AMPLITUDE VARIABLE-                | 16       |  |  |

| FREQUENCY OSCILLATOR                                       |          |  |  |

| 2.1. Introduction                                          | 16       |  |  |

| 2.2. An Overview of The Oscillator                         | 17       |  |  |

| 2.2.1. The Input Unit                                      | 18       |  |  |

| 2.2.2. The Control Unit                                    | 18       |  |  |

| 2.2.3. The Output Unit                                     | 18       |  |  |

| 2.2.4. The Amplifier Unit                                  | 18       |  |  |

| 2.3. Formulation of The Digital Methodology                | 19       |  |  |

| 2.3.1. The Technique for Frequency Variation               | 20       |  |  |

| 2.3.2. Signal Waveform                                     | 22       |  |  |

| 2.3.3. Continuous Signal Generation                        | 23       |  |  |

| 2.3.4. The Dual Control of Frequency and Amplitude         | 25       |  |  |

| 2.4. The Multiplication Factor for Amplitude Control       | 26       |  |  |

| 2.5. The Frequency Control Function                        | 26       |  |  |

| 2.5.1. The General Frequency Control Function              | 27       |  |  |

| 2.5.2. Operation at Non-Zero Slip                          | 28       |  |  |

| 2.5.3. Slip Range for Technique Verification               | 29       |  |  |

|    | 2.5.4. The Actual Slip Values                                                                   | 31        |

|----|-------------------------------------------------------------------------------------------------|-----------|

|    | 2.6. Areas for Investigation                                                                    | 31        |

|    | 2.6.1. The Quality of the Generated Signals                                                     | <b>32</b> |

|    | 2.6.2. The Frequency Control                                                                    | 32        |

|    | 2.6.3. The Amplitude Control                                                                    | 32        |

|    | 2.6.4. The Data Processing                                                                      | 33        |

| 3. | OSCILLATOR IMPLEMENTATION: HARDWARE AND SOFTWARE DESCRIPTION                                    | 34        |

|    | 3.1. Introduction                                                                               | 34        |

|    | 3.2. Hardware Description                                                                       | 35        |

|    | 3.2.1. Experimental Setup                                                                       | 35        |

|    | 3.2.2. The Motivation to Use The LPAs                                                           | 37        |

|    | 3.3. Software Description                                                                       | 38        |

|    | 3.3.1. The Software Structure                                                                   | 38        |

|    | 3.3.2. Interprocess Data Flow                                                                   | 40        |

|    | 3.3.2.1. The Initialization Stage                                                               | 40        |

|    | 3.3.2.2. The Continuation Stage                                                                 | 40        |

| 4. | EXPERIMENTS, RESULTS AND DISCUSSION                                                             | 44        |

|    | 4.1. Introduction                                                                               | 44        |

|    | 4.2. The Test Procedure                                                                         | 44        |

|    | 4.3. Classification of Experiments                                                              | 46        |

|    | 4.3.1. Experiments on The Methodology                                                           | 46        |

|    | 4.3.2. Experiments for The Analysis of The Output Signals                                       | 46        |

|    | 4.3.3. Experiments on The Performance of The Digital Oscillator                                 | 47        |

|    | 4.4. Real-Time Constraints                                                                      | 47        |

|    | 4.4.1. The Host Computer                                                                        | 47        |

|    | 4.4.2. The Length of The Data Buffers                                                           | 48        |

|    | 4.4.3. The Clock Settings                                                                       | 48        |

|    | 4.4.4. The LPA Procedures                                                                       | 49        |

|    | 4.5. Verification of The Methodology                                                            | 49        |

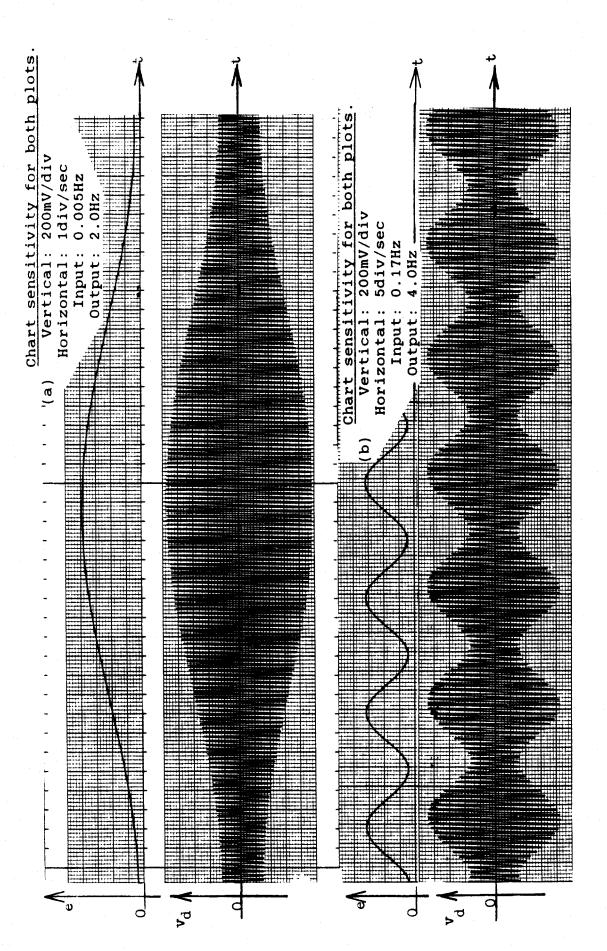

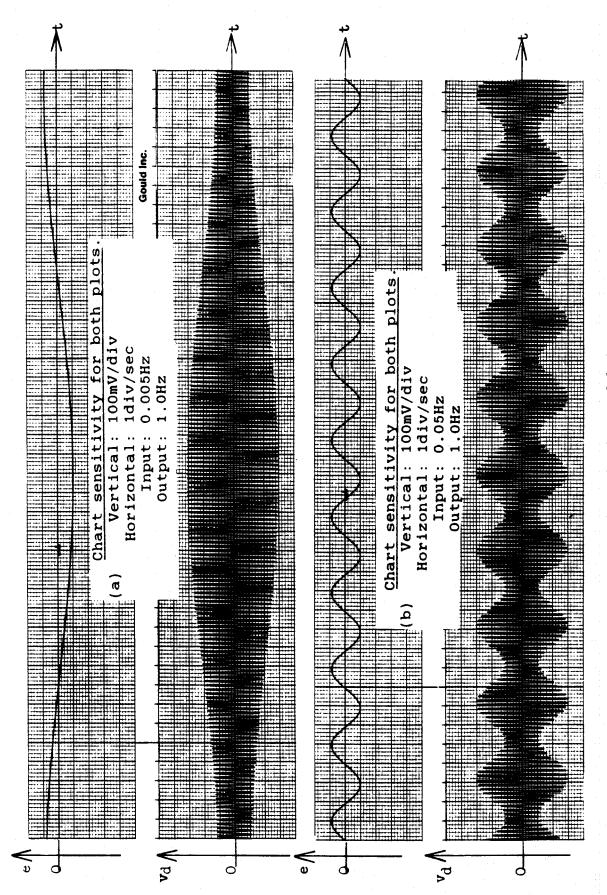

|    | 4.5.1. Waveforms of the Output Signals                                                          | 49        |

|    | 4.5.2. Effect of Changing The D/A sampling Frequency                                            | 49        |

|    | 4.5.3. Effect of Varying The Number of Samples Per Cycle                                        | 54        |

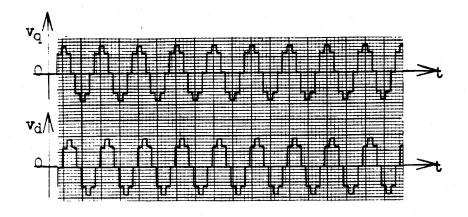

|    | 4.5.4. The Phase Shift Between The Output Signals                                               | 54        |

|    | 4.5.5. Amplitude Adjustment                                                                     | 54<br>55  |

|    | 4.5.6. Frequency Adjustment                                                                     | 55        |

|    | 4.6. Analysis of The Output Signals                                                             | 55        |

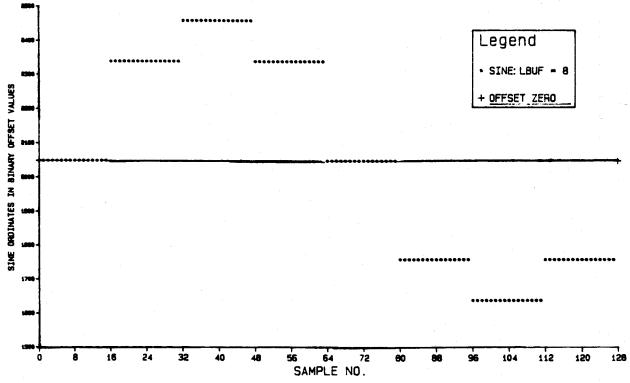

|    | 4.6.1. Generation of Data for Analysis                                                          | 56        |

|    | 4.6.2. Representation of The Response of The Digital-to-Analog                                  | 30        |

|    | Converter to a Digital Word                                                                     | 61        |

|    | 4.6.3. Analysis Results                                                                         | 61        |

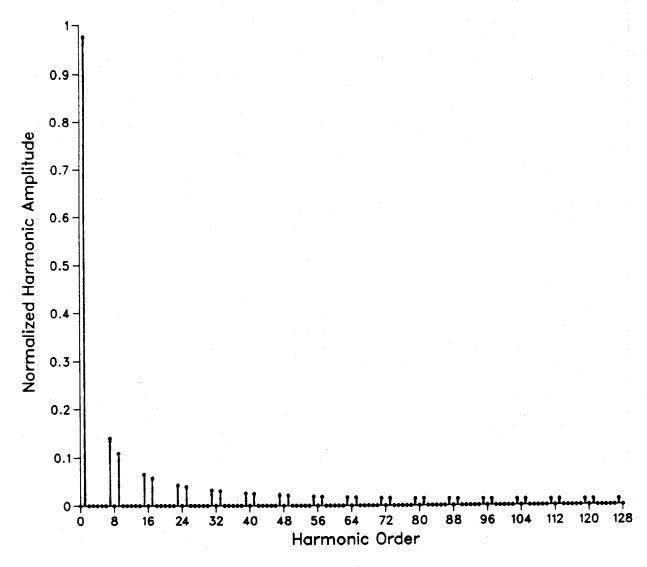

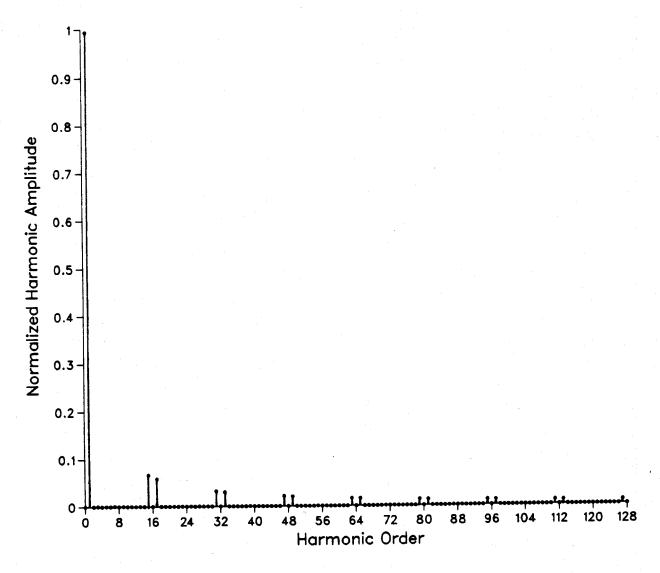

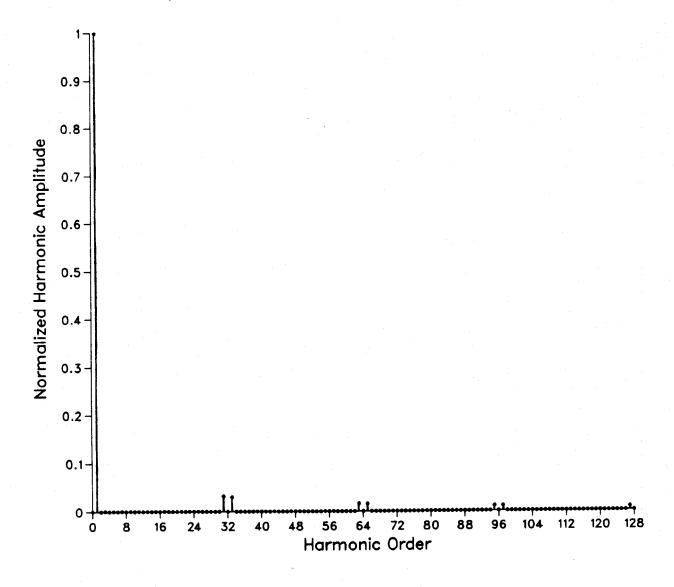

|    | 4.6.3.1. Harmonic Content                                                                       | 61        |

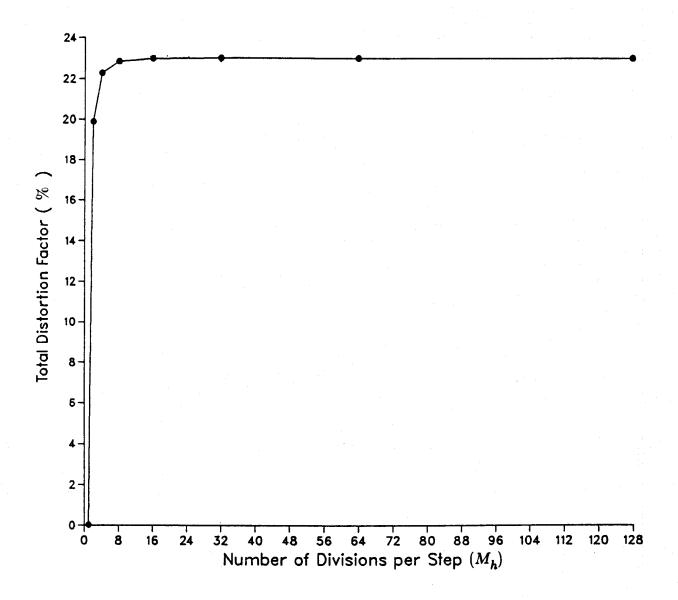

|    | 4.6.3.2. Waveform Distortion                                                                    | 66        |

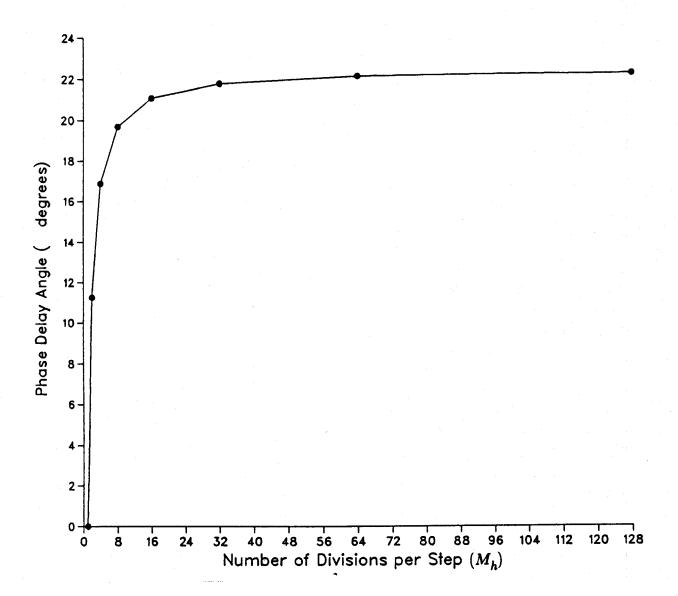

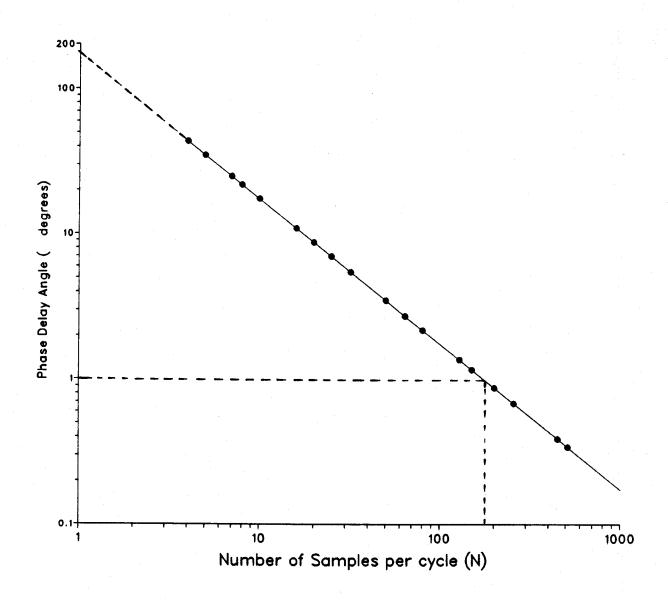

|    | 4.6.3.3. The Phase Delay Angle                                                                  | 66        |

|    | 4.6.3.4. Selection of The Digital-to-Analog Converter 4.7 Performance of the Digital Oscillator | 66        |

|    | 4/ remormance of the Digital Oscillatur                                                         | ~ ~       |

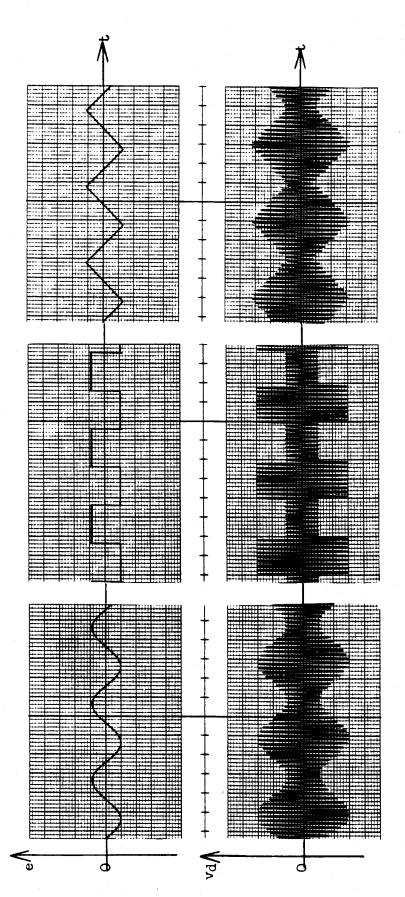

| 4.7.1. Amplitude Modulation                                                                                                                                                          | 71   |  |  |  |                                                                   |      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--|--|--|-------------------------------------------------------------------|------|

| 4.7.2. Frequency Modulation                                                                                                                                                          |      |  |  |  |                                                                   |      |

| 4.7.3. Amplitude and Frequency Modulation                                                                                                                                            | 71   |  |  |  |                                                                   |      |

| 4.7.3.1. Low Output Frequency                                                                                                                                                        | 82   |  |  |  |                                                                   |      |

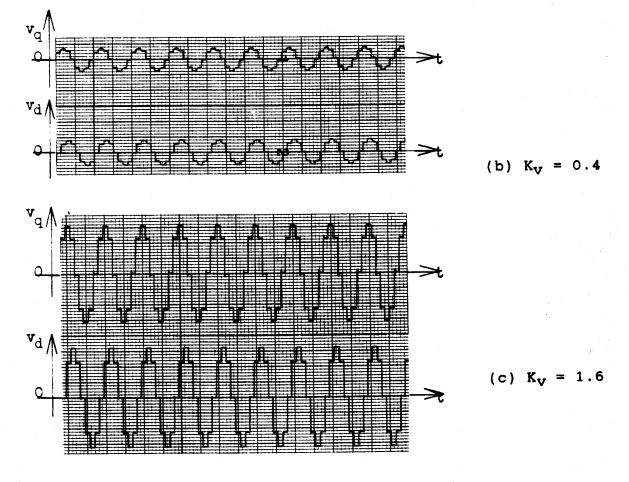

| 4.7.3.2. Small Multiplication Factors                                                                                                                                                | 82   |  |  |  |                                                                   |      |

| 4.7.3.3. Insufficient A/D Sampling Rates                                                                                                                                             | 84   |  |  |  |                                                                   |      |

| 5. CONCLUSIONS AND RECOMMENDATIONS                                                                                                                                                   | 85   |  |  |  |                                                                   |      |

| 5.1. Conclusions                                                                                                                                                                     | 86   |  |  |  |                                                                   |      |

| 5.2. Recommendations for Further Research                                                                                                                                            | 87   |  |  |  |                                                                   |      |

| 5.2.1. On The Direction of The Field Rotation                                                                                                                                        | 87   |  |  |  |                                                                   |      |

| 5.2.2. On The Waveform Distortion                                                                                                                                                    | 87   |  |  |  |                                                                   |      |

| 5.2.3. On Other Applications                                                                                                                                                         | 88   |  |  |  |                                                                   |      |

| 5.2.4. On The Power Amplifiers                                                                                                                                                       | 88   |  |  |  |                                                                   |      |

| 5.2.5. On The Implementation of The Oscillator on a Microcom                                                                                                                         | - 89 |  |  |  |                                                                   |      |

| puter                                                                                                                                                                                |      |  |  |  |                                                                   |      |

| 5.2.6. On Modelling The Oscillator                                                                                                                                                   | 89   |  |  |  |                                                                   |      |

| REFERENCES                                                                                                                                                                           |      |  |  |  |                                                                   |      |

| Appendix A. FREQUENCY CONTROL                                                                                                                                                        | 93   |  |  |  |                                                                   |      |

| A.1. General                                                                                                                                                                         |      |  |  |  |                                                                   |      |

| A.2. Loading The D/A Data Buffers                                                                                                                                                    |      |  |  |  |                                                                   |      |

| A.3. Loading D/A Buffers In terms of The Number of Full-Cycles A.4. Loading D/A Buffers In terms of The Number of Half-Cycles A.5. Loading of D/A Buffers In Terms of Quarter-Cycles |      |  |  |  |                                                                   |      |

|                                                                                                                                                                                      |      |  |  |  | A.6. Loading D/A Buffers In Terms of Cycle-Parts Multiples of Two | o 97 |

|                                                                                                                                                                                      |      |  |  |  | Appendix B. MODULES OF THE OSCILLATOR SOFTWARE                    | 102  |

| B.1. Introduction                                                                                                                                                                    | 102  |  |  |  |                                                                   |      |

| B.2. Software Description                                                                                                                                                            | 102  |  |  |  |                                                                   |      |

| B.3. Configuration and The Initialization Modules                                                                                                                                    | 105  |  |  |  |                                                                   |      |

| B.4. Data Acquisition Modules                                                                                                                                                        | 105  |  |  |  |                                                                   |      |

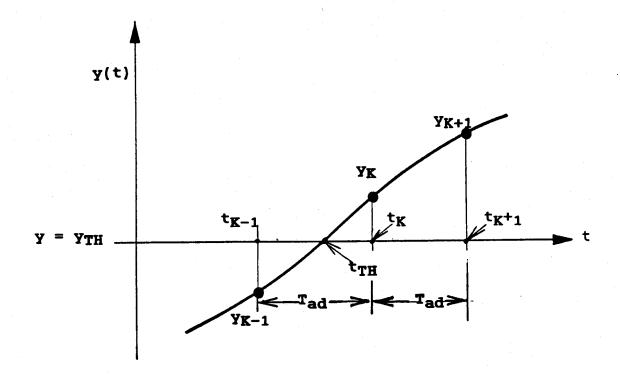

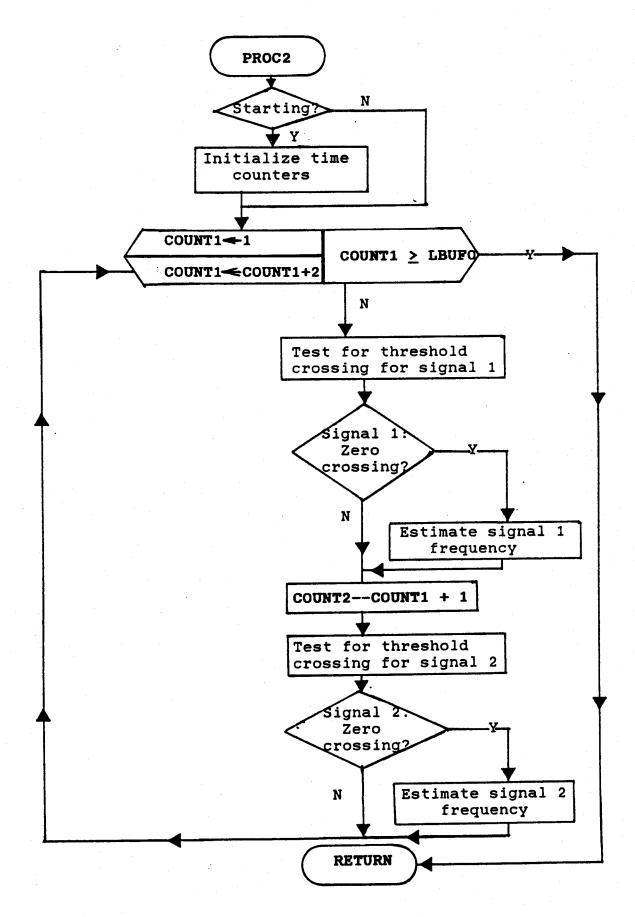

| B.5. The Principle of the Frequency Estimator                                                                                                                                        | 112  |  |  |  |                                                                   |      |

| B.6. The Clock Modules                                                                                                                                                               | 116  |  |  |  |                                                                   |      |

| Appendix C. WAVEFORM DISTORTION AND HARMONIC                                                                                                                                         | 119  |  |  |  |                                                                   |      |

| ANALYSIS                                                                                                                                                                             |      |  |  |  |                                                                   |      |

| C.1. Fourier Expansion                                                                                                                                                               | 119  |  |  |  |                                                                   |      |

| C.2. The Indicators of Waveform Distortion                                                                                                                                           | 119  |  |  |  |                                                                   |      |

| C.3. Modified Discrete-Time Fourier Expression                                                                                                                                       | 121  |  |  |  |                                                                   |      |

# LIST OF FIGURES

| Figure 1-1:             | A block diagram of variable-speed                                 | 4          |

|-------------------------|-------------------------------------------------------------------|------------|

| i iguit 1 1.            | constant-frequency set up using a                                 |            |

|                         | variable-speed driven generator.                                  |            |

| Figure 1-2:             | A schematic diagram of a dual-excited                             | 6          |

|                         | synchronous generator.                                            |            |

| Figure 1-3:             | Two orthogonal fluxes $\phi_d$ and                                | 7          |

|                         | $\phi_q$ in a d-q plane in a dual-excited                         |            |

|                         | 3                                                                 |            |

| Tr: 1 4.                | synchronous generator.  A block diagram of the proposed variable- | 13         |

| Figure 1-4:             | amplitude variable-frequency oscillator.                          |            |

| Ti 1 5.                 | A block diagram of the programmable                               | 13         |

| Figure 1-5:             | variable-amplitude variable-frequency                             |            |

|                         | two-phase excitation system.                                      |            |

| Fig. 1 &.               | A block diagram of a variable-speed                               | 15         |

| Figure 1-6:             | constant-frequency scheme employing a                             |            |

|                         | dual-excited generator.                                           | 4          |

| Figure 2 1.             | A conceptual block diagram of the                                 | 17         |

| Figure 2-1:             | proposed digital variable-amplitude                               |            |

|                         | variable-frequency oscillator.                                    |            |

| Figure 2 2.             | Oscillating voltage output from a D/A converter.                  | 21         |

| Figure 2-2: Figure 2-3: | A ring buffer structure.                                          | 24         |

| Figure 2-4:             | Operation of the dual-excited synchronous                         | 30         |

| rigure 2-4.             | generator at (a) subsynchronous speeds,                           |            |

|                         | (b) supersynchronous speeds.                                      |            |

| Figure 2-5:             | (a) Usable shaft-speeds,                                          | 30         |

| rigure 2-0.             | (b) Usable slip-range.                                            |            |

| Figure 3-1:             | A block diagram of the experimental setup.                        | 36         |

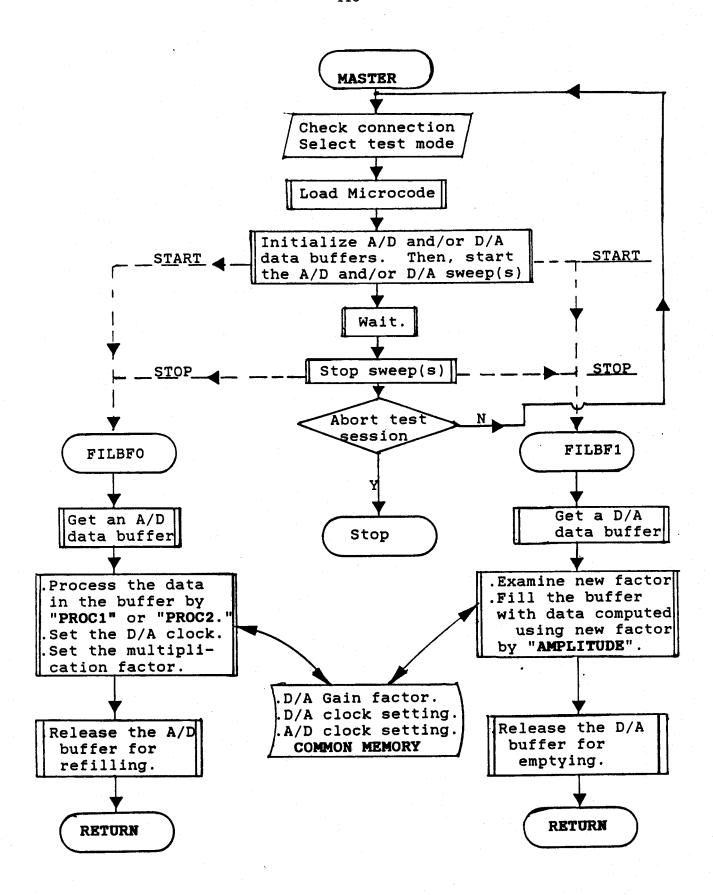

| Figure 3-2:             | Multi-process structure of the test software.                     | 39         |

| Figure 3-3:             | A flow diagram showing the flow of data                           | 42         |

| 1.80.00                 | during the initialization stage.                                  |            |

| Figure 3-4:             | A flow diagram showing the flow of data during                    | 43         |

|                         | the continuation stage.                                           |            |

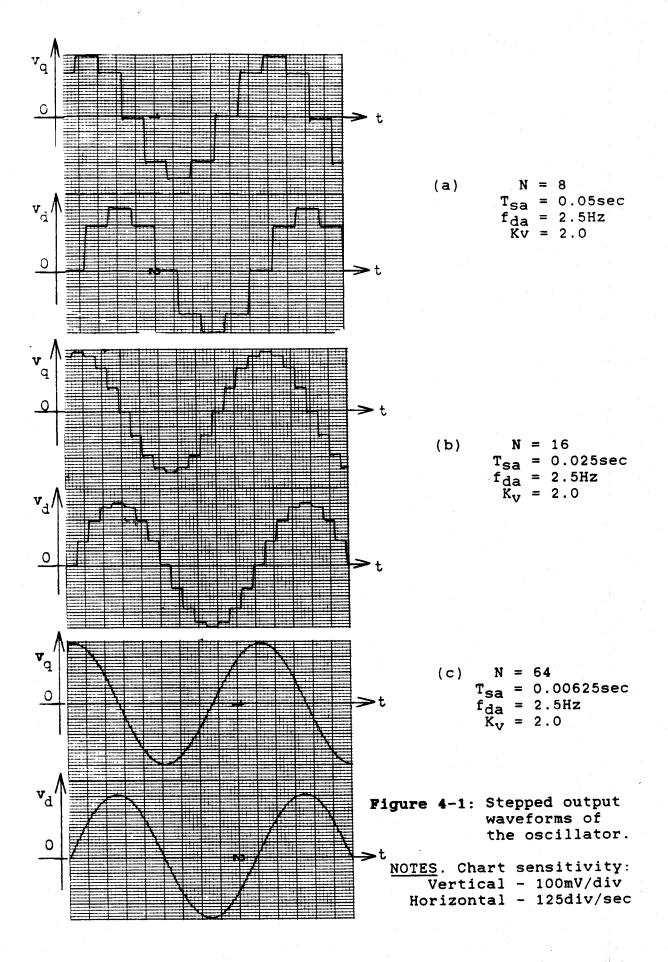

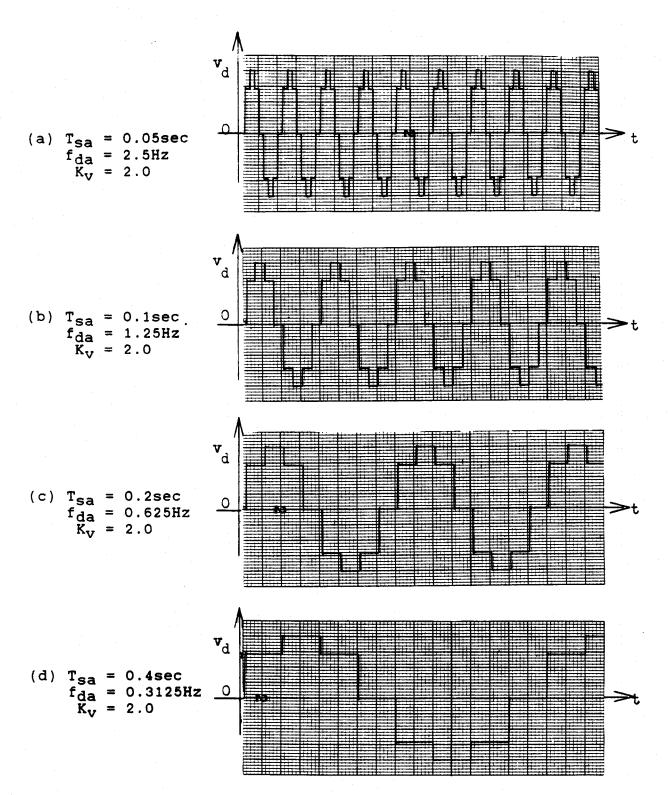

| Figure 4-1:             | Stepped output waveforms of the oscillator.                       | <b>5</b> 0 |

| Figure 4-2:             | The effects of varying the clock setting on                       | 51         |

| <del></del>             | the output frequency for $N = 8$ samples/cycle.                   |            |

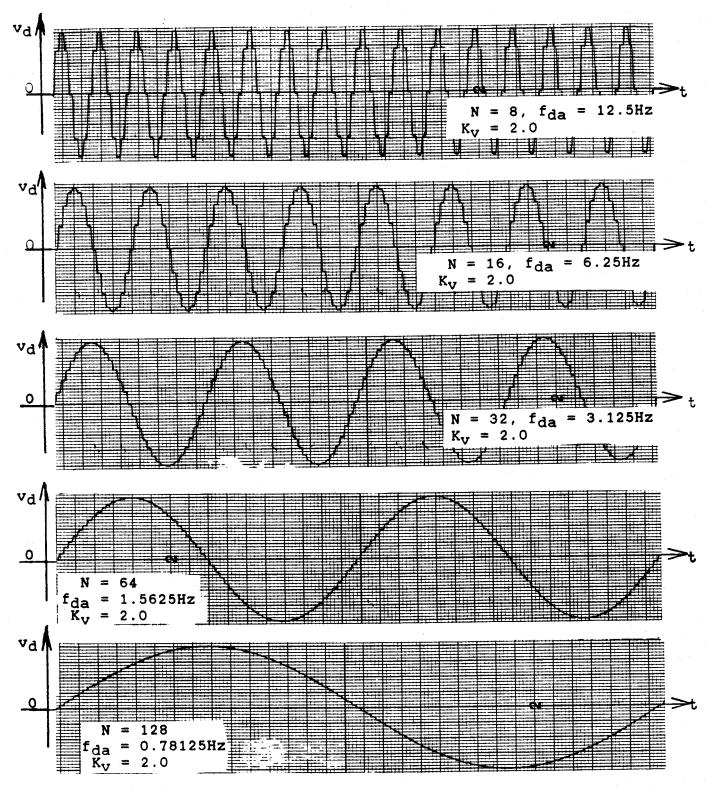

| Figure 4-3:             | The effects of varying $N$ at constant $D/A$                      | 52         |

| 3                       | sampling frequency of 100Hz.                                      | . :        |

# LIST OF SYMBOLS

phase angle of  $n^{th}$  harmonic.  $\boldsymbol{\beta_n}$ phase angle, a function of field windings parameters.  $\gamma$ angle corresponding to  $n^{th}$  sample of an oscillating signal.  $\theta_n$ generator synchronous angular frequency (radians/second).  $\omega_0$ fundamental angular frequency.  $\omega$ magnetic flux along the direct-axis.  $\phi_d$ magnetic flux along the quadrature-axis.  $\phi_q$ peak amplitude of the rotating field.  $\phi_m$  $\overline{\Phi}$ resultant magnetic field riding on the rotor.  $\phi_{dm}$ peak amplitude of  $\phi_d$ . peak amplitude of  $\phi_a$ .  $\phi_{am}$  $A_d$ peak value of amplified  $v_{fd}$ . peak value of amplified  $v_{fa}$ .  $A_a$ A/Danalog-to-digital. D/Adigital-to-analog. number of pairs of reference D/A data buffers. b

nth sample of the terminal voltage error signal.

terminal voltage error signal.

e, e(t)

e[n]

$f_{da}$  frequency of the D/A output signals.

$f_{sa}$  D/A sampling frequency.

$K_{\star}$  terminal voltage error constant with units [Volts]<sup>-1</sup>.

$K_{ref}$  reference multiplication factor.

K, multiplication factor.

$K_v[n]$  multiplication factor corresponding to the  $n^{\text{th}}$  sample of the voltage error signal.

$K_s$  slip constant with units [Volts]<sup>-1</sup>.

L length of each D/A data buffer.

m, n positive integer.

M number of samples per D/A buffer.

$M_b$  number of subdivisons per time step.

$n_0$  generator synchronous speed.

$n_r$  rotor speed.

$n_{\phi}$  speed of the rotating magnetic field relative to the rotor.

N number of samples per cycle of each output signal.

$N_P$  number of cycle parts of each output signal in a D/A data buffer.

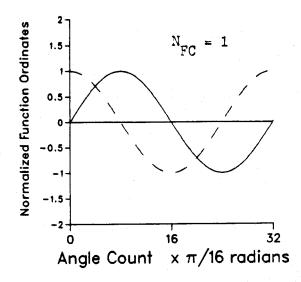

$N_{FC}$  number of full-cycles of each output signal in a D/A data buffer.

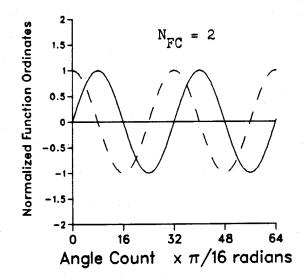

$N_{HC}$  number of half-cycles of each output signal in a D/A data buffer.

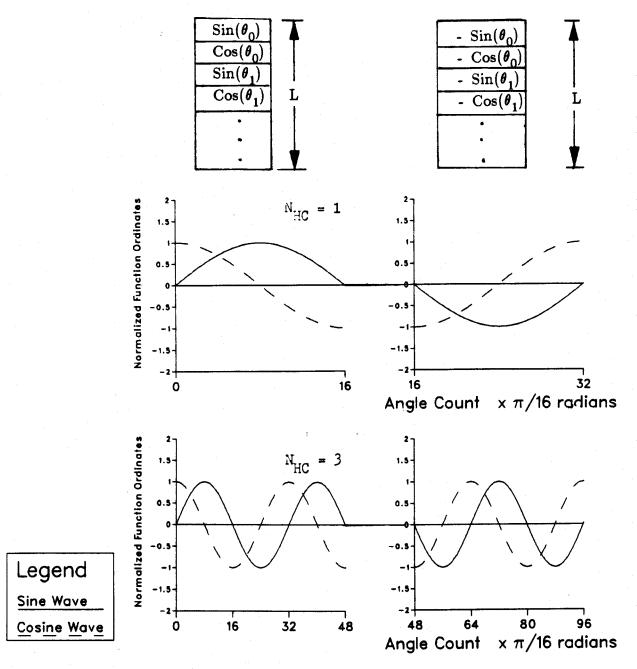

$N_{QC}$  number of quarter-cycles of each output signal in a D/A data buffer.

P number of reference D/A data buffers.

PDA phase delay angle, phase distortion.

$s_a$  dimmensionless slip variable defined as  $\frac{n_0 - n_r}{n_0}$ .

s(t) slip signal.

s[n]  $n^{\text{th}}$  sample of the slip signal.

$T_{da}$  period of the oscillator output signals.

$T_{ad}$  A/D intersample time for each sampled signal.

$T_{sa}, T_{sa}$  D/A intersample time for each output signal.

$\Delta T$  intersample time for two consecutive samples in a D/A data buffer.

$t_n$  time corresponding to  $n^{\text{th}}$  clock pulse.

v(t) A voltage signal.

$v_{fd}$  excitation voltage fed to the direct-axis field winding.

$v_{fq}$  excitation voltage fed to the quadrature-axis field winding.

$V_n$   $n^{\text{th}}$  harmonic of the voltage signal v(t).

$V_k$   $k^{\text{th}}$  DFT coefficient of the voltage signal v(t).

v[n]  $n^{\text{th}}$  sample of the voltage signal v(t).

# Chapter 1

# INTRODUCTION

#### 1.1. General

In recent years, increasing emphasis has been placed on the development and the use of renewable energy sources, such as wind [1, 2, 3, 4, 5], for electrical power generation. There is also a growing demand to generate electricity for specialized applications, such as in aircraft and mobile vehicles, using variable-speed prime movers. Wind-turbines and aircraft engines are some of the examples of variable-speed prime movers.

The power from a wind turbine or an aircraft engine is random in nature [6], and as such is not easily controllable. A conventional synchronous generator driven by a variable-speed shaft generates a variable-frequency voltage, which has limited applications. Thus, the general problem in such variable-speed schemes is to generate electricity at constant frequency as in the case of the conventional constant-speed constant-frequency (CSCF) generator systems. Several efforts have been made to design such variable-speed constant-frequency (VSCF) generator systems. These are capable of:

- 1. being driven directly from a variable-speed shaft, and

- 2. supplying alternating current (a.c.) electric energy at a constant frequency.

### 1.2. Variable-Speed Constant-Frequency Schemes

This section briefly points out several methods for designing variable-speed constant-frequency systems. One method is that of regulating the speed by mechanical techniques to obtain a constant-speed shaft from a variable-speed shaft. Variable gear-ratio units and blade position controllers are extensively used in wind powered plants [5] to convert a variable-speed variable-frequency setup to a constant-speed constant-frequency arrangement. Hydraulic pump-motor arrangements, as conversion schemes, are employed in aircraft power generation units [5, 6]. However, the drawbacks of these schemes include the following:

- 1. mechanical parts wearout,

- 2. low control speed with almost no flexibility, and

- 3. leakages in the hydraulic setups.

These factors deteriorate the effectiveness of the frequency control [7] of such schemes.

Another method employs the direct current (d.c.) links. Rectifiers are used to convert the variable-frequency a.c. power to d.c. This is then inverted to constant-frequency a.c. [4, 5, 8]. The main problem with the use of inverters is the harmonic generation [9, 10].

The third method, which is gaining attention recently, is that of using special purpose generator setups. These special purpose generators are designed to generate voltage at a constant frequency in spite of the variation in the prime mover speed. Several generator schemes have been suggested for

variable-speed constant-frequency operation. These schemes use either synchronous or induction generators.

Velayudhan [11, 12] reported a scheme employing a slip-ring induction generator. The speed-torque characteristic of the machine under constant load is adjusted to match the input power by adjusting the external resistance connected in the rotor circuit of the generator. The method is uneconomical, since electric power has to be dissipated in the external rotor resistance. This reduces the efficiency of the setup, and the heat dissipation in the rotor circuit requires special cooling systems [11].

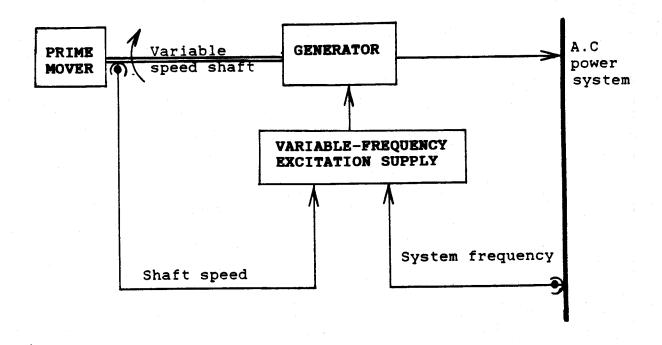

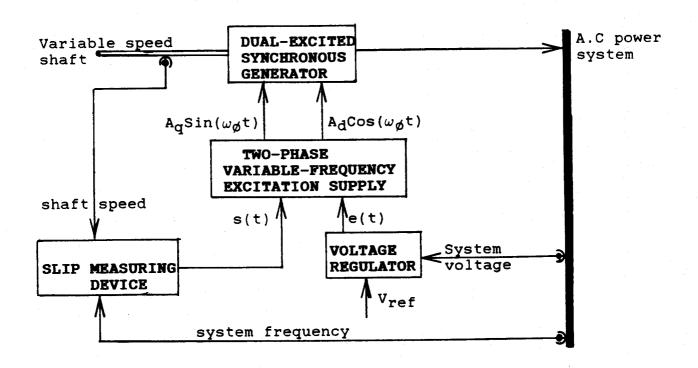

The use of induction machines as synchronous generators have been also reported in the literature [6, 13, 14]. In such a scheme, three-phase variable-frequency excitation currents are fed to the generator rotor as illustrated in Figure 1-1. The frequency of the excitation currents is proportional to the rotor slip. The underlying principle is that the variable-frequency excitation currents produce a rotating magnetic field. This field rotates in the machine airgap such that the armature frequency becomes constant. The excitation currents are supplied from a cycloconverter. The use of cycloconverters is always accompanied with the generation of undesirable harmonics. These harmonics cause heating problems in the generator [9]. Also, excessive harmonics may interfere with the performance of the control equipment [13].

A synchronous generator can be made suitable for variable-speed constant-frequency applications by the use of the two-axis rotor excitation

Figure 1-1: A block diagram of variable-speed constant-frequency setup using a variable-speed driven generator.

technique [15, 16]. For this application, the machine requires an a.c. excitation source. The excitation currents must be alternating with a frequency proportional to the rotor slip. The effect is to have a magnetic field rotating relative to the rotor speed such that a constant armature frequency is maintained.

The theoretical explanation of the two-axis machines is well presented in references [15, 16, 17, 18]. A cross-section of the many different practical systems which advocate the two-axis excitation technique is given in references [7, 19, 20, 21].

# 1.3. Generation of Frequency Controlled Signals

The two-axis generators have to be supplied from special a.c. excitation sources. Frequency controlled signals must be fed to the generator rotor in such a way that they determine the frequency at which the voltage is generated. There are several ways in which the frequency control signals may be generated. The common technique is to use cycloconverters. This technique has some disadvantages. Cycloconverters generate undesirable harmonics [9, 13, 16, 22], which cause heating problems within the generator. Practical cycloconverters have complex control circuitry. This results in poor flexibility.

# 1.4. The Dual-Excited Synchronous Generator

A dual-excited synchronous generator (DESG) [15, 16] is one of the machines which can be used for variable speed constant frequency schemes. It uses the two-axis excitation technique. The rotor of a dual-excited synchronous generator is constructed such that for each pole, it has two sets of field windings which are:

- 1. electrically in quadrature with each other (displaced a 1/2-pole pitch, that is, 90 electrical degrees from each other), and

- 2. are externally accessible.

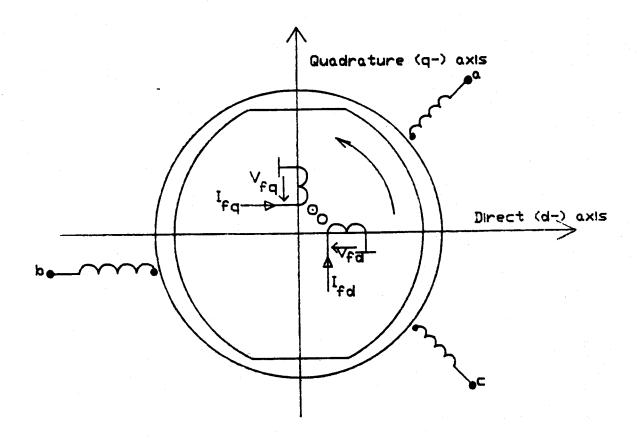

Figure 1-2 shows a typical schematic diagram of a dual-excited synchronous generator. The principle of operation and the excitation requirements of the dual-excited synchronous generator are discussed in the following sections.

Figure 1-2: A schematic diagram of a dual-excited synchronous generator.

# 1.4.1. Operation of the Dual-Excited Synchronous Generator

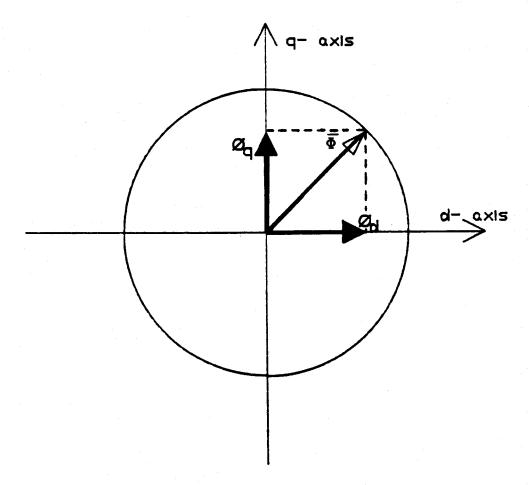

Two excitation sources  $v_{fd}$  and  $v_{fq}$  supply the d- and q- axes field windings (in the rotor) respectively. The current in the d-axis winding produces a flux  $\phi_d$  along the d-axis. The current in the q-axis winding produces a flux  $\phi_q$  along the q-axis. These two fluxes,  $\phi_d$  and  $\phi_q$ , produce a resultant flux  $\overline{\Phi}$  in the airgap of the generator (see Figure 1-3).

Due to the displacement of 90 electrical degrees between the two field windings, the flux  $\overline{\Phi}$  can be described as:

$$\overline{\Phi} = \phi_d + j\phi_q \tag{1.1}$$

$$|\overline{\Phi}| = \sqrt{\phi_d^2 + \phi_q^2} \tag{1.2}$$

where j is the complex plane notation.

Figure 1-3: Two orthogonal fluxes  $\phi_d$  and  $\phi_q$  in a d-q plane in a dual-excited synchronous generator.

When the field windings are excited by d.c. sources, the fluxes  $\phi_d$  and

$\phi_q$  are constant, and the resultant flux  $\overline{\Phi}$  is stationary with respect to the rotor [21]. When the excitation currents are alternating, the resultant flux rotates at a relative angular speed with respect to the rotor. The pattern of rotation of the resultant flux depends on the maximum values of  $\phi_d$  and  $\phi_q$ , and the phase shift between the two fluxes.

This thesis is based on the case when the two voltages  $v_{fd}$  and  $v_{fq}$  are:

- 1. sinusoidal, with respective amplitudes of  $V_{fd}$  and  $V_{fq}$ , modulated by a voltage error signal,

- 2. 90 degrees phase shifted from one another, and

- 3. are functions of the time varying angle  $\theta=2\pi(s_af_o)t$ , with the slip  $s_a$  modulating the synchronous frequency of the generator,  $f_o$ .

The two sources may be described as:

$$v_{fd} = V_{fd}(e)\cos(\omega_{\phi}t) \tag{1.3}$$

$$v_{fq} = V_{fq}(e)\sin(\omega_{\phi}t) \tag{1.4}$$

where:  $\omega_{\phi} = s_a \omega_o t$ ,  $\omega_o = 2\pi f_o$ ,

e - is the terminal voltage error.

In steady state operating conditions,  $v_{fd}$  and  $v_{fq}$  are controlled such that, the currents in the d-axis and q-axis field windings produce fluxes  $\phi_d$  and  $\phi_q$  of the form:

$$\phi_d = \phi_{dm} \cos \left( \omega_{\phi} t + \gamma \right) \tag{1.5}$$

$$\phi_{q} = \phi_{qm} \sin \left(\omega_{\phi} t + \gamma\right) \tag{1.6}$$

where  $\gamma$  is an angle which depends on the field winding parameters.

These two sinusoidal fluxes produce a resultant flux,  $\overline{\Phi}$ , of the form:

$$\overline{\Phi} = \phi_{dm} \cos(\omega_{\phi} t + \gamma) + j \phi_{qm} \sin(\omega_{\phi} t + \gamma)$$

(1.7)

For  $\phi_{dm}$  not equal to  $\phi_{qm}$ ,  $\overline{\Phi}$  traces an ellipse in the d-q plane. Elliptical rotation of  $\overline{\Phi}$  is known to cause heating problems [15, 21]. Thus a circular rotation is preferred. To achieve this, depending on the construction of the field windings, the excitation currents are adjusted so that  $\phi_{dm}$  equals  $\phi_{qm}$ . Consequently:

$$\overline{\Phi} = \phi_m \{ \cos(\omega_\phi t + \gamma) + j \sin(\omega_\phi t + \gamma) \}$$

(1.8)

or equivalently:

$$\overline{\Phi} = \phi_m \exp(j\{\omega_\phi t + \gamma\}) \tag{1.9}$$

where  $\phi_m$  is the magnitude of  $\overline{\Phi}$ .

Equations (1.8) and (1.9) describe a flux with magnitude  $\Phi_m$ , rotating at an angular speed of  $s_a\omega_o$  relative to the rotor. The dual-excited synchronous generator operates asynchronously to satisfy the relation:

$$n_o = n_r + n_\phi \tag{1.10}$$

for subsynchronous speeds and

$$n_o = n_r - n_\phi \tag{1.11}$$

for supersynchronous speeds,

where:  $n_0$  - is the synchronous speed of the generator,

$n_{\phi}$  - is the field rotation speed relative to the rotor,

$n_{\star}$  - is the rotor speed.

The variable  $n_o$  is a regulated parameter in a variable-speed constant-frequency scheme. Since  $n_r$  is variable (from a variable-speed prime mover),  $n_\phi$  is electrically controlled such that it is directly proportional to slip as in Equations (1.3) and (1.4). This means that an electrical rotation is dynamically superimposed on a mechanical rotation to realize a constant armature frequency.

#### 1.4.2. Excitation Requirements

The following are the excitation requirements of a dual-excited synchronous generator operated in asynchronous mode.

- 1. The two sources must generate sinusoidal voltages with the following properties at any instant of time.

- a. The two signals must have equal frequencies.

- b. The frequency of the signals must be proportional to the rotor slip.

- c. The two signals must be 90 degrees phase shifted from each other.

- d. The amplitudes of the signals must be controlled by the terminal voltage errors.

- 2. A power amplifier is required to amplify the signals to the rated current excitation levels of the generator.

- 3. The slip and the terminal voltage error signals must be measured continuously.

## 1.5. Thesis Objective

This thesis is a feasibility study of using a digital computer to generate excitation control signals for a dual-excited synchronous machine operated at variable speed. The computer acts as a programmable oscillator which generates the two-phase variable-frequency control signals, in accordance with the excitation requirements of the dual-excited synchronous generator.

### 1.5.1. Initial Specifications

It is assumed that the following are available:

- 1. a dual-excited synchronous generator,

- 2. the slip signal s(t), and

- 3. the voltage error signal e(t).

The main purpose of the study is to determine whether or not it is feasible to achieve the excitation requirements discussed in section 1.4.3, using direct digital control. The oscillator functions are:

- 1. to generate two sinusoidal signals of equal frequencies, preferably of equal amplitudes, and continuously (in real time) 90 degrees phase shifted from each other,

- 2. to track the slip and the voltage error signals in on-line mode, and

- 3. to change dynamically the frequency and the amplitude of the two signals, using the slip and the voltage error information.

# 1.5.2. The Proposed Variable-Amplitude Variable-Frequency Digital Oscillator

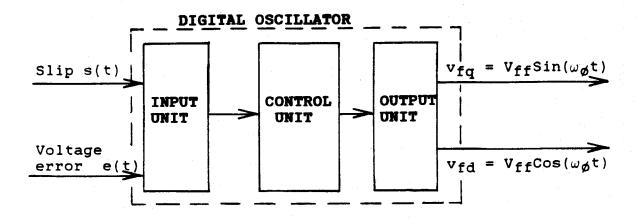

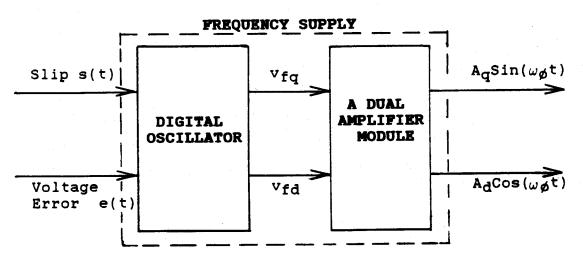

The inputs to the oscillator are two analog voltage signals. One is the slip signal s(t), and the other is the terminal voltage error signal, e(t). The outputs are two sinusoidal signals of equal frequency and amplitude, and are 90 degrees phase shifted from each other at any instant of time. The frequency of the signals is proportional to the rotor slip. The amplitude deviations from a reference value  $V_{ref}$  are proportional to the voltage error signal. A block diagram of the oscillator is shown in Figure 1-4, and that of the frequency supply is shown in Figure 1-5. A block diagram of a variable-frequency-constant-frequency scheme using a dual-excited synchronous generator and the excitation supply is shown in Figure 1-6.

### 1.5.3. The Scope of Study

The study focuses on the conceptual level of the digital oscillator, to determine the procedures to be followed by the oscillator to generate the control signals for the dual-excited synchronous generator.

The thesis describes the development of an experimental digital oscillator on a VAX-11/780 computer. The VAX computer supports two real time Laboratory Peripheral Accelerator (LPA11-K) subsystems. The setup is used to conduct tests to determine the validity of the digital technique in meeting the specified excitation conditions of the dual-excited synchronous generator. The main purpose of the tests is to establish the relevant information required for the design of a practical computer based supply unit.

Figure 1-4: A block diagram of the proposed variable-amplitude variable-frequency oscillator.

Figure 1-5: A block diagram of the programmable variable-amplitude variable-frequency two-phase excitation system.

The following are the potential areas identified for investigation:

- 1. the quality of the generated signals,

- 2. the control of the output frequency,

- 3. the control of the output amplitude, and

- 4. data processing procedures.

The proposed solution has a multi-process structure. In a multi-process system, several processes take place simultaneously. Consequently, the programs for the test setup are developed and structured on the basis of a modular programming technique. Modularity is expected to:

- 1. simplify the development task when the technique is implemented on a microcomputer,

- 2. allow each of the software components to be individually designed, documented, and tested,

- 3. allow each of the modules to be modified as parameters vary, procedures change, or system configuration is upgraded, and

- 4. provide a user with the flexibility of selecting or configuring control strategies from a pre-programmed set of algorithms contained in the computer memory.

Figure 1-6: A block diagram of a variable-speed constant-frequency scheme employing a dual-excited generator.

# Chapter 2

# THE DIGITAL VARIABLE-AMPLITUDE VARIABLE-FREQUENCY OSCILLATOR

#### 2.1. Introduction

A dual-excited synchronous generator (DESG) is used to implement a variable-speed constant-frequency generator setup. The principle of operation is to supply slip-frequency a.c. currents to the two field windings of the generator. By this means, the excitation system provides an airgap field that rotates at a constant speed relative to the stator. Under these conditions, the stator output frequency remains constant.

A direct digital approach is chosen to generate the two-phase excitation signals. This chapter presents a conceptual digital variable-amplitude variable-frequency oscillator. The digital control for both the amplitude and the frequency of the oscillator outputs is described. The real-time constraints associated with the methodology are also presented. A discussion on the areas investigated during the study is included, as well as the reasons for the investigations.

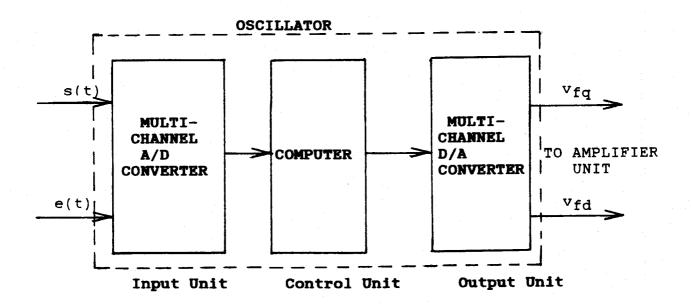

#### 2.2. An Overview of The Oscillator

The block diagram of the proposed digital variable-amplitude variable-frequency oscillator was shown in Figure 1-4. The oscillator has an input unit, a control unit, and an output unit. Figure 2-1 shows the conceptual block diagram of the oscillator. The oscillator outputs are fed into an amplifier unit. The oscillator and the amplifier unit form the excitation unit. A description of each block is given in the following sections.

Figure 2-1: A conceptual block diagram of the proposed digital variable-amplitude variable-frequency oscillator.

#### 2.2.1. The Input Unit

The input block is mainly a dedicated analog-to-digital (A/D) data acquisition system. It accepts two input signals: the slip signal s(t) and the voltage error signal e(t). The system has temporary memory buffers for storing the sampled data before it is processed.

#### 2.2.2. The Control Unit

The control unit is a microprocessor assembly. It can be a dedicated computer. This unit handles all the control and the coordination tasks. In this unit, the input data is processed to update the output variables used to adjust the amplitude and the frequency of the output signals.

#### 2.2.3. The Output Unit

The output unit has a programmable clock and a dedicated digital-toanalog (D/A) converter system. This unit performs the signal generation as explained in section 2.3.3.

#### 2.2.4. The Amplifier Unit

A power amplifier is necessary to amplify each signal to the rated excitation current levels of the generator field. The gain variation for amplification can either be superimposed on the output signals before amplification or set in programmable amplifiers. The first case requires variable-amplitude variable-frequency signals. This case depends on:

- 1. the supply of the digital-to-analog converter, and

- 2. the computational complexity involved in changing the contents of the D/A buffers before being emptied.

For the second case, programmable amplifiers should be used. This requires constant-amplitude variable-frequency signals. Furthermore, a gain signal is required to set the gains of the amplifiers.

However, no power amplifier was built or used during the study. This section emphasizes that the oscillator is useful only if a proper power amplifier is available.

# 2.3. Formulation of The Digital Methodology

This section presents the derivations of the techniques used to control the frequency and the amplitude of the output signals. Relevant to the derivations is the fact that analog information is input to the computer through an A/D interface, and the processed information is output from the computer through a D/A interface.

The A/D and D/A conversions are sampling operations. Such operations require stable driving real-time clocks. The following discussion assumes the availability of the multi-buffered devices, such as the LPAs [23], which control the A/D and D/A interfaces driven by programmable real-time clocks.

The A/D sampling process must be driven at a constant frequency, which is a requirement of data processing algorithms [24]. The A/D sampling frequency is selected high enough to avoid aliasing problems [25, 26, 27, 24, 28, 29].

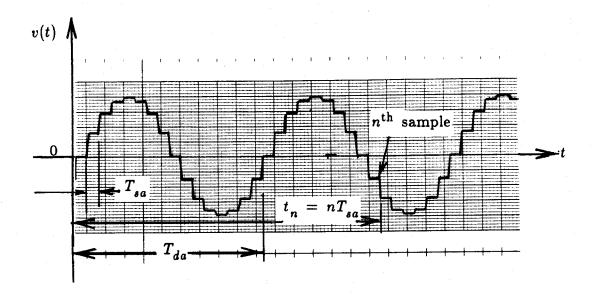

In the following sections the digital-to-analog conversion is regarded as a signal generation technique. In the discussion,  $f_{sa}$  denotes the D/A sampling rate,  $T_{sa}$  denotes the D/A intersample time per signal, and  $f_{da}$  denotes the frequency of the output signals. For the case of analog-to-digital conversion,  $f_{ad}$  denotes the A/D sampling rate, and  $T_{ad}$  denotes the A/D intersample time for each sampled input signal.

#### 2.3.1. The Technique for Frequency Variation

Consider a digital-to analog conversion process taking place under continuous sampling at a sample rate of  $f_{sa}$ . Consider also that the output of the digital-to-analog converter is a continuous alternating signal. An angle  $\theta_n$  in radians can be associated with the oscillating signal at any instant of time  $t_n$  (see Figure 2-2), such that:

$$\theta_n = 2\pi f_{da} t_n \tag{2.1}$$

where:  $\theta_n$  - is the angle corresponding to the  $n^{\rm th}$  sample,  $t_n$  - is the time corresponding to the  $n^{\rm th}$  sample, and  $f_{da}$ - is the frequency of the D/A output signal.

The reciprocal of the sampling frequency  $f_{sa}$  gives the intersample time  $T_{sa}$ :

$$T_{sa} = \frac{1}{f_{sa}} \tag{2.2}$$

At the  $n^{th}$  clock pulse, the real-time  $t_n$  is given by:

$$t_n = nT_{\epsilon n} \tag{2.3}$$

In terms of n and  $T_{sa}$ , the angle  $\theta_n$  can be expressed as:

$$\theta_n = 2\pi f_{da} n T_{sa} \tag{2.4}$$

and explicitly:

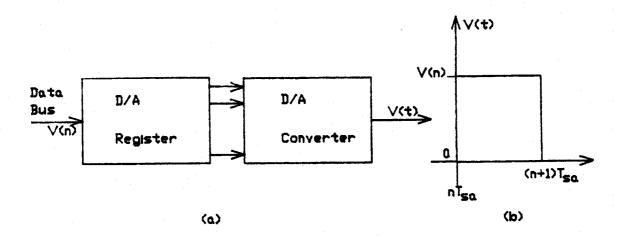

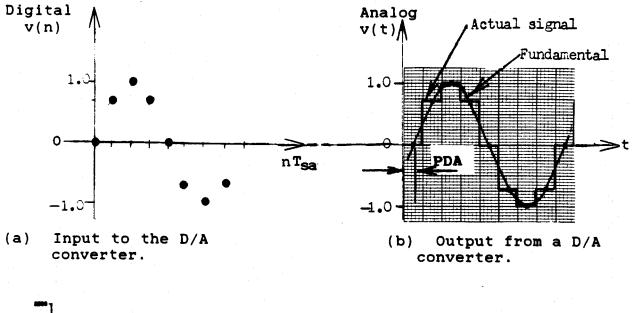

Figure 2-2: Oscillating voltage output from a D/A converter.

$$f_{da} = \frac{\theta_n}{2\pi n T_{sa}} \tag{2.5}$$

During the sampling process, n is automatically varied by the clock. The value of  $T_{sa}$  is fixed by the sampling frequency, and  $\theta_n$  is the angle at the  $n^{\text{th}}$  clock tick. If the factor  $\frac{\theta_n}{n}$  in Equation (2.5) is a constant, then, the frequency  $f_{da}$  can be varied by changing the value of  $T_{sa}$ , which is achieved by changing the sampling rate  $f_{sa}$ . Thus, changing the D/A sampling frequency changes the frequency of the output signals. This enables the generation of variable frequency signals.

The use of this technique to generate signals demands the execution of both the A/D and the D/A sampling processes continuously. This obser-

vation suggests that the two processes must not share the same driving clock.

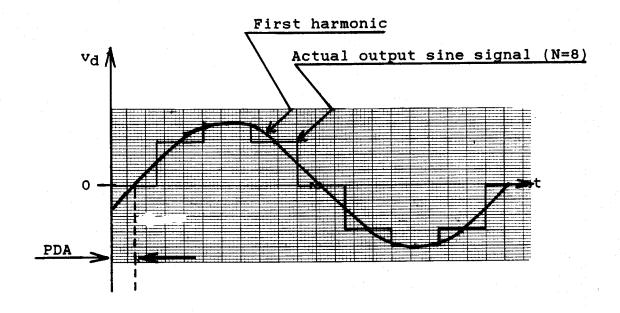

#### 2.3.2. Signal Waveform

This study uses the sine and the cosine functions. The angle  $\theta_n$  is identified as a common argument of both functions. These two functions are orthogonal [24, 28]. The choice of these two functions fulfils the excitation condition of 90 degrees phase shift between the excitation signals for a dual-excited synchronous generator. The digital sine and cosine data are numerically generated. The data is then stored in the computer memory, ready for conversion to analog values.

Numerically, a cycle of  $2\pi$  radians is divided into N subdivisions of equal size such that the  $m^{\rm th}$  subdivision correspond to an angle:

$$\theta_m = \frac{2\pi m}{N} \tag{2.6}$$

where:  $0 \le \theta_m < 2\pi, m=0,1,2,...,N-1$ .

For each angle  $\theta_m$ , there exist values of a sine and a cosine ordinate given by:

$$\cos\left(\theta_{m}\right) = \cos\left(\frac{2\pi m}{N}\right)$$

$$\sin\left(\theta_{m}\right) = \sin\left(\frac{2\pi m}{N}\right)$$

(2.7)

Apparent from Equation (2.7) is that,  $T_{sa}$  has no effect on both  $\cos{(\theta_m)}$  and  $\sin{(\theta_m)}$ . Therefore, the waveform of the output signals is

defined by setting each of the angles  $\theta_m$  to a constant. The distortion of the waveform depends only on the value of N. As well, the values of  $\cos{(\theta_m)}$  and  $\sin{(\theta_m)}$  are independent of the signal frequency,  $f_{da}$ .

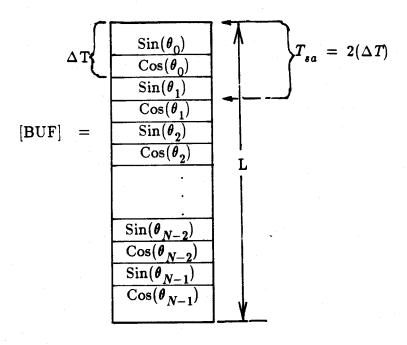

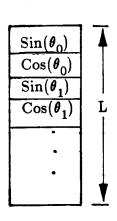

### 2.3.3. Continuous Signal Generation

A cycle of each of the two sinusoidal functions is first divided into P equal-sized integral parts. These cycle parts are labelled 0,1,2,3,...,P-1. Each of these P parts is subdivided into M equal divisions. The ordinates corresponding to M subdivisions of each function are numerically computed and then stored in a one dimension data buffer [BUF] of length L (L=2M). This process initializes a set of P data buffers. In each buffer, the ordinates are organized in alternating positions as:

$$[BUF] = \begin{bmatrix} \sin (\theta_o) \\ \cos (\theta_o) \\ \sin (\theta_1) \\ \cos (\theta_1) \\ \vdots \\ \sin (\theta_{M-1}) \\ \cos (\theta_{M-1}) \end{bmatrix}$$

$$(2.8)$$

The arrangement of the ordinates in each buffer allows simultaneous signal generation. The P buffers are contiguous. They are arranged to form a ring structure as illustrated in Figure 2-3. The total number of samples per cycle of each function is:

$$N = PM (2.9)$$

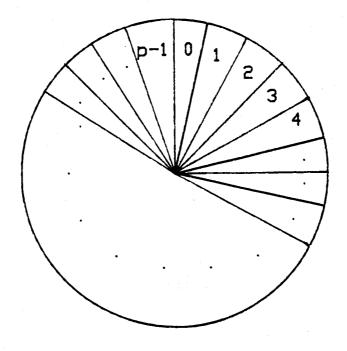

Figure 2-3: A ring buffer structure.

The ring buffer structure allows the buffers to be reused during the sampling process. In this case, a copy or a modification of each of the P buffers is emptied after every 2PM clock pulses. In this way, a continuous signal generation is achieved.

#### 2.3.4. The Dual Control of Frequency and Amplitude

The other excitation condition is that the two sinusoidal output signals should have equal frequencies at any instant of time. This is achieved by the use of one real time clock to control the D/A sweep generating the two signals. At the  $n^{\rm th}$  clock tick, the same n is used to identify  $\sin{(\theta_n)}$  and  $\cos{(\theta_n)}$ . Evident from Equation (2.5) is that changing  $T_{sa}$  changes  $f_{da}$ , which is the frequency of both signals. The control of the amplitude depends on the control option as discussed in section 2.2.4. Of interest here is the case in which the amplitude control is carried out before amplifying the output signals.

The D/A data is modified by multiplying each of the entries of a labelled buffer by a predetermined factor  $K_v$ . The result is a modified buffer [BUF]' for emptying:

$$[BUF]' = K_{v} \cdot [BUF] \tag{2.10}$$

Each time an amplitude change is to be effected, both the sine and the cosine ordinates are multiplied by the same factor  $K_v$ . As a result, the two output signals are adjusted to have equal peak amplitudes. The equal amplitude output signals are chosen for convenience purposes. Proper gains will be set on the amplifiers taking into consideration the field winding data.

## 2.4. The Multiplication Factor for Amplitude Control

The amplitude of the output signals must be varied such that the amplitude deviations from the reference value  $V_{ref}$  are proportional to the voltage error signal e(t). The reference signals in this study are of unit amplitude. The variation of the amplitude (as discussed in section 2.3.4) is achieved by multiplying the samples of the reference signals by an appropriate factor  $K_v$ . For each sample e[n] of the voltage error signal, the factor  $K_v[n]$  is determined as follows:

$$K_{v}[n] = K_{ref} \pm K_{e}e[n]$$

(2.11)

where: K<sub>ref</sub> - is the reference multiplication factor,

K<sub>e</sub> - is the voltage error constant with units [volt]<sup>-1</sup>, and

e[n] - denotes the  $n^{th}$  sample of the voltage error signal.

The positive sign in Equation (2.11) corresponds to a positive-amplitude modulation, and the negative sign corresponds to a negative-amplitude modulation [30].

# 2.5. The Frequency Control Function

This section describes the relationship between the slip and the output frequency of the oscillator. Consider the case where the ring buffer is set to have only one cycle part (P=1,N=M), that is, one full-cycle of each function. The ordinates are loaded in alternating sequence as illustrated by Equation (2.8). For this case, L=2N. The use of one driving clock to control the signal generation sets the signals to have equal periods, and therefore equal frequencies. For a D/A intersample time of  $T_{sa}$  per signal, the value of the time periods is given by:

$$T_{da} = \frac{LT_{sa}}{2} \tag{2.12}$$

Corresponding to a signal frequency:

$$f_{da} = \frac{2}{LT_{sa}} \tag{2.13}$$

For a variable-speed operation with a dual-excited synchronous generator, the D/A sampling frequency  $f_{sa}$  must be changed dynamically in proportion to the slip signal s(t). Two cases are now considered as regards to the slip interpretation. The first case is theoretical and is used to derive the general frequency control function. The second case is that of operating the generator at a non-zero slip, which is practical.

#### 2.5.1. The General Frequency Control Function

This case is evident from the functional Equations (1.3) and (1.4). The control of the frequency of the output signals can be shown to be:

$$f_{da} = s_a f_o \tag{2.14}$$

where:  $f_o$  - is the system synchronous frequency, and  $s_a$  - is the dimensionless slip variable.

Solving for  $T_{sa}$  from Equations (2.13) and (2.14), the following control expression is obtained:

$$T_{sa} = \frac{2}{Lf_0s_a} \tag{2.15}$$

This control function shows that the intersample time is inversely proportional to the slip. The variable  $T_{sa}$  can explicitly be used to update

the D/A sampling frequency as slip varies. The application of the control function has the following constraints.

- 1.  $T_{sa}$  can never be negative, but slip can.

- 2. A zero sampling frequency corresponds to zero frequency output (at zero slip). The control law would set an infinite value of  $T_{sa}$ . The setting is impractical with digital systems. Hence, d.c. excitation can not be realized by sampling control.

- 3. Infinite sampling frequency corresponds to an infinite slip. The sampling setting at such extremes equals zero  $(T_{sa}=0)$ . The setting is likely to cause a "divide by zero" error in the digital system. This condition is an obvious design constraint. The other constraint associated with large values of slip is the supply of excitation power. It is known [7, 19] that the larger the slip, the more excitation power is required. Thus, an infinite excitation power is required to generate power at an infinite slip. This is not practical.

#### 2.5.2. Operation at Non-Zero Slip

This case eludes the constraints pointed out in section 2.5.1. The dual-excited synchronous generator, performing as an asynchronous generator [15], is driven at speeds within a predetermined speed range. The speeds in this range are here referred to as usable shaft-speeds. The speeds can be supersynchronous or subsynchronous. Corresponding to the usable shaft-speed range is a usable slip-range. The slip is negative for supersynchronous speeds, and is positive for subsynchronous speeds. Since it is a problem to achieve the d.c. excitation by sampling control, the generator operation is limited to speeds either below or above the synchronous speed. Hence, the sign of the slip must be established before the generator is put into operation.

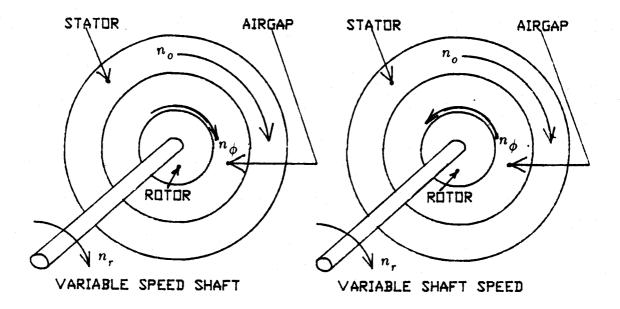

Excitation power is supplied to the rotor at slip frequency, when the slip is positive. In this case, the rotor excitation has to produce a field in the airgap rotating in the same direction as the rotor ( see Figure 2-4(a)). The direction of rotation of the field is set by the way the two-phase rotor is supplied from the two-phase excitation supply. Reversal in the connection of one of the phases reverses the direction of rotation of the field.

Excitation power flows out of the rotor at slip frequency, when the slip is negative. Now, the rotor excitation has to produce a field in the airgap rotating in a direction opposite to that of the rotor (see Figure 2-4(b)). The direction of the field rotation sets the sign of the slip. Once the sign is set, the slip information can be interpreted without the sign. Operation outside the usable slip-range is not acceptable, and shutdown may be necessary.

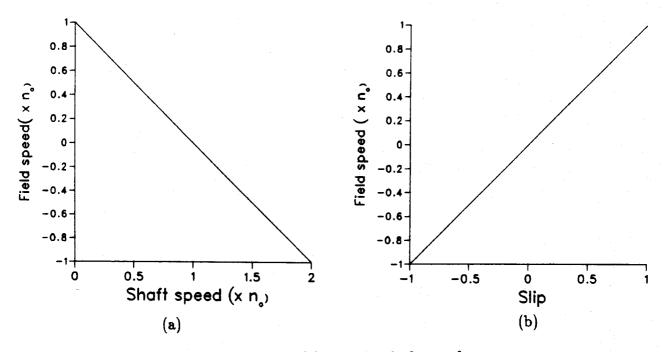

#### 2.5.3. Slip Range for Technique Verification

A slip-range of  $0 < |s_a| \le 1.0$  is considered adequate for the technique verification. The oscillator uses the absolute values of the slip. In practice, the sign of the slip has to be implemented externally, by proper choice of the phase-sequence connection to the rotor windings. Figure 2-5 shows the variation in the speed  $n_{\phi}$  of the rotating field corresponding to the usable slips and shaft-speeds for a synchronous speed  $n_o$ . The negative values of  $n_{\phi}$  correspond to the direction of rotation opposite to that of the rotor. The positive values of  $n_{\phi}$  correspond to the rotation in the same direction as that of the rotor.

- (a) Relatively  $n_o = n_r + n_\phi$

- (b) Relatively  $n_o = n_r n_\phi$

Figure 2-4: Operation of the dual-excited synchronous generator at (a) subsynchronous speeds, (b) supersynchronous speeds.

Figure 2-5: (a) Usable shaft-speeds, (b) Usable slip-range.

The choice of the direction of rotation of the airgap field relative to the direction of the rotor is dependent on the availability of an appropriate power amplifier. The power amplifier has to supply power to the rotor when operating at subsynchronous speeds. The amplifier has to facilitate the power flow out of the rotor when operating at supersynchronous speeds.

#### 2.5.4. The Actual Slip Values

The slip signal, s(t), is a voltage signal. The signal is selected such that the slip values are proportional to the instantaneous values of the signal. The actual slip values have no dimension. Therefore, each sample s[n] of the slip signal has to be converted to the actual slip value  $s_a[n]$  by multiplying it by a constant  $K_s$ , that is:

$$s_a[n] = K_s s[n] \tag{2.16}$$

where: s[n] is in volts,

$K_s$  has the units  $[volt]^{-1}$ ,

and s[n] denotes the  $n^{th}$  sample of the slip signal s(t).

When  $K_s = 1.0$  [volt]<sup>-1</sup>, the actual slip value  $s_a[n]$  is numerically equal to the sample value s[n]. In this case, the units may be ignored in programming the system.

# 2.6. Areas for Investigation

Four potential areas were identified in chapter 1 for investigation, namely, the quality of the generated signals, the frequency control, the amplitude control, and the data processing procedures. These areas are explained further in the following sections.

#### 2.6.1. The Quality of the Generated Signals

Of particular interest here is the waveform distortion. The latter is a relevant indicator on whether or not filtering is to be performed on the output signals. This area is thoroughly investigated for steady state conditions. The results are reported in Chapter 4.

#### 2.6.2. The Frequency Control

Typical of any real-time clock is that there are fixed combinations of clock frequency and integer values of counter presets. The combinations allow only a subset of possible frequencies. An investigation was necessary to establish adequate D/A sampling frequencies. It is shown that one value of the number of samples per cycle (N) and one range of clock settings  $T_{sa}$  are not adequate to provide control flexibility. A study on different combinations of N and  $T_{sa}$  exposed more control possibilities. The details of this study are reported in Appendix B.

#### 2.6.3. The Amplitude Control

The accuracy of converting a sequence of digital numbers to an analog signal is dependent on:

- 1. the number of quantization levels of the digital-to-analog converter used [29],

- 2. the hardware structure of the converter, and

- 3. the d.c. supply to the converter hardware.

The investigation of this area provides details useful for selecting a suitable size of a digital-to-analog converter. The results of this study are included in Chapter 4.

#### 2.6.4. The Data Processing

The input data has to be processed to estimate the slip and voltage errors. A study on the characteristics of the possible slip and voltage error signals would provide some details useful in the selection or the design of the real-time algorithms for data processing. Equally useful is a study on the efficiency, speed of response, and accuracy of the selected algorithms. The study of this area is recommended for future research. In this thesis, the slip and the voltage error signals are assumed to be available. The algorithms used for data processing are described in a separate Internal Report referred to as reference [31]. The overall software structure is described in section 3.3.

# Chapter 3

# OSCILLATOR IMPLEMENTATION: HARDWARE AND SOFTWARE DESCRIPTION

#### 3.1. Introduction

The digital-to-analog (D/A) conversion was discussed in section 2.3 as a technique to generate variable-frequency sinusoidal signals. The methodology uses numerically generated data for output signals. This data is to be converted to analog values by a digital-to-analog converter driven by a programmable real-time clock. In section 2.3.1, it was shown that the variation of the D/A sampling frequency varies the frequency of the output signals.

An experimental oscillator was implemented on the VAX-11/780 computer to evaluate the validity of this signal generation methodology. The VAX supports two real-time Laboratory Peripheral Accelerators (LPA11-Ks) which are 16-bit-devices. Both the LPAs are peripheral devices to the VAX-computer. Each LPA consists of two microcomputers that handle the real-time I/O processing [23]. These LPAs control a set of A/D and D/A converters, and real-time clocks. The LPAs are connected to the VAX process-

sor through a UNIBUS adapter. This chapter describes the hardware and the software components of the test setup.

### 3.2. Hardware Description

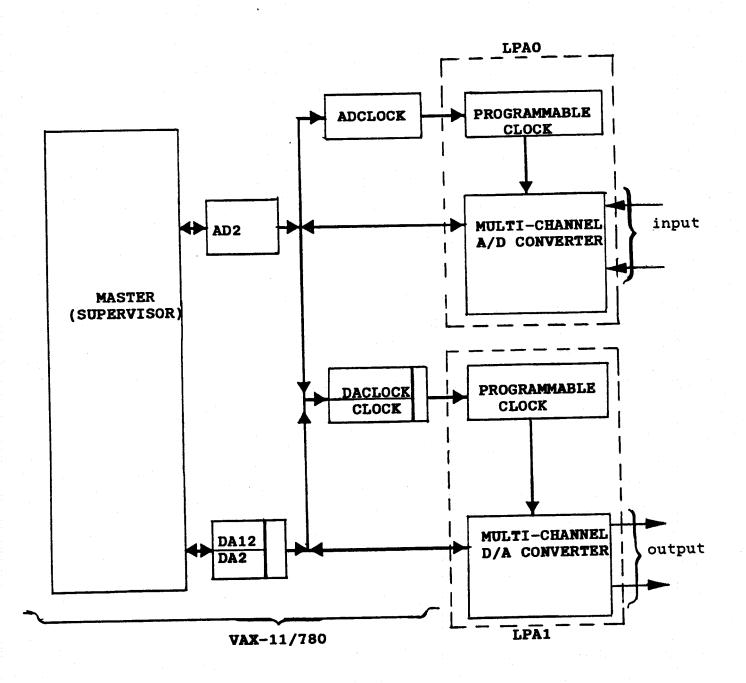

#### 3.2.1. Experimental Setup

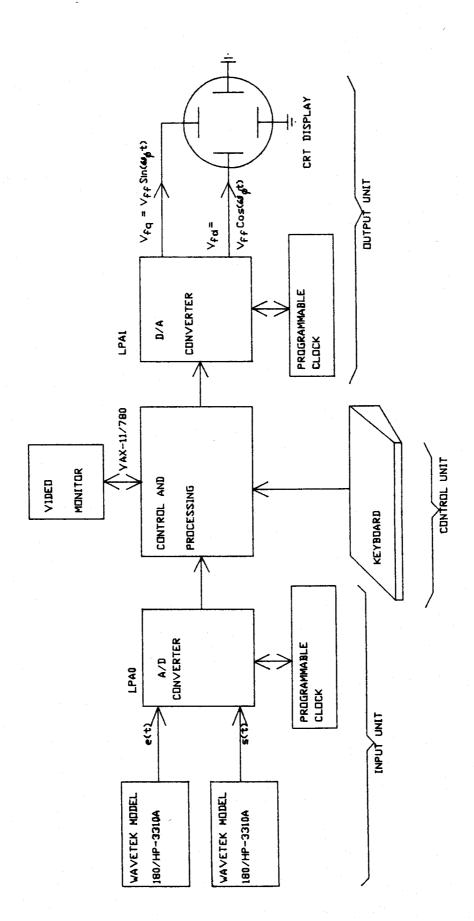

The block diagram of the experimental setup used to verify the signal generation technique is shown in Figure 3-1. The setup is organized such that the input, the control, and the output blocks are distinguishable.

The input block is comprised of:

- 1. two function generators (HP MODEL 3310A/WAVETEK MODEL 180),

- 2. a 16-channel, 12-bits, analog-to-digital converter hardware (+/-5V supply), and

- 3. a programmable clock capable of driving the A/D converter to sample up to 15,000 samples per second.

The analog-to-digital converter circuitry and the clock are controlled via one of the LPAs identified as LPA0 in Figure 3-1. The two function generators were used to simulate the slip and the voltage error signals.

The control unit is the host VAX-11/780 computer, to which a video monitor and a keyboard are interfaced for interactive user operations.

The output unit is implemented on the second LPA subsystem identified as LPA1 in Figure 3-1.

Figure 3-1: A block diagram of the experimental set up.

The components of this unit are:

- 1. a 4-channel, 12-bits, digital-to-analog converter hardware (+/- 5V supply),

- 2. a programmable clock capable of driving the D/A converter to sample up to 15,000 samples per second, and

- 3. a dual channel oscilloscope for displaying the output signals.

#### 3.2.2. The Motivation to Use The LPAs

The VAX-11/780 is a time sharing computer. Both LPA11-K subsystems have real-time hardware. Since each LPA is a separate microcomputer system that handles the I/O processing, both data acquisition and processing may be performed simultaneously. Thus, the time sharing of the VAX does not affect the data acquisition processes. Instead, the VAX, as a host processor, supervises both the acquisition and the processing operations. The other inducements are as follows.

- 1. The LPA subsystems are available.

- 2. Each LPA has a programmable clock. The rate of each clock may be changed under program control.

- 3. The LPAs operate as an integral part of the VAX/VMS operating system. These subsystems are programmable in VAX-FORTRAN. The VAX/VMS operating system supports several program-accessible procedures that provide access to the LPAs [23].

- 4. Each LPA functions as a multi-buffered device. This feature favours the use of the ring buffered structure discussed in section 2.3.3.

#### 3.3. Software Description

The LPA11-K arrangement was programmed such that the application programs run under the supervision of a real-time executive VAX-program. This section presents the structure of the test software, and the data flow when the programs are running.

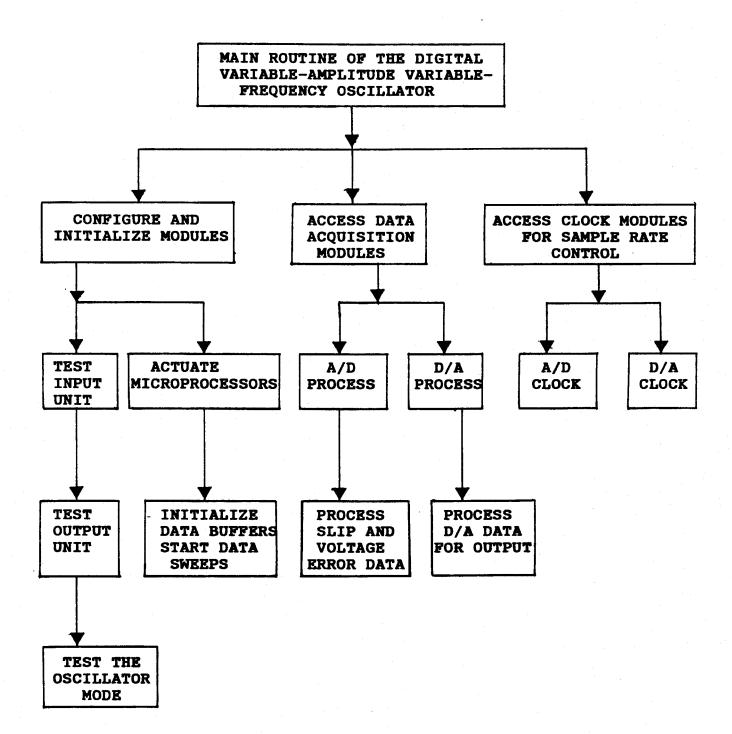

#### 3.3.1. The Software Structure

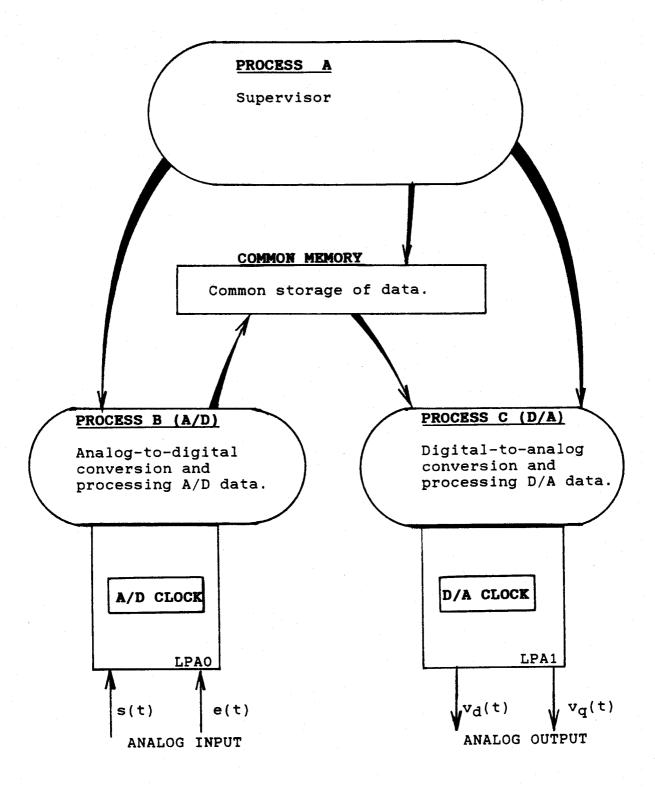

As shown in Figure 3-2, the software has a multi-process structure with three real-time processes. The processes are here referred to as process A, B, and C. Process A is the supervisor of the test software. The functions of process A are:

- 1. to initialize and configure the test software,

- 2. to start and stop processes B and C when requested, and

- 3. to generate the sine and the cosine data values for signal generation.

Process B is a real-time A/D process. This process acquires the slip and the voltage error data at a set sampling frequency. It then processes the acquired data to extract the slip and the voltage error information by using resident algorithms. The slip information is used to update the D/A sampling frequency as discussed in section 2.4. The voltage error information is used to update the D/A multiplication factor  $K_v$  as discussed in section 2.3.4. Process B drives the analog-to-digital hardware of the LPA0.

Process C is a real-time D/A process. The main function of this process is to change the amplitude of the output signals using the  $K_v$  set-

Figure 3-2: Multi-process structure of the test software.

tings from process B. First, it accesses a D/A data buffer, regarded as empty, fills it with modified D/A data; and then, releases the buffer to the LPA1 for D/A conversion to analog signals.

#### 3.3.2. Interprocess Data Flow

The test software executes in two stages, namely:

- 1. the initialization stage, and

- 2. the continuation (dynamic) stage.

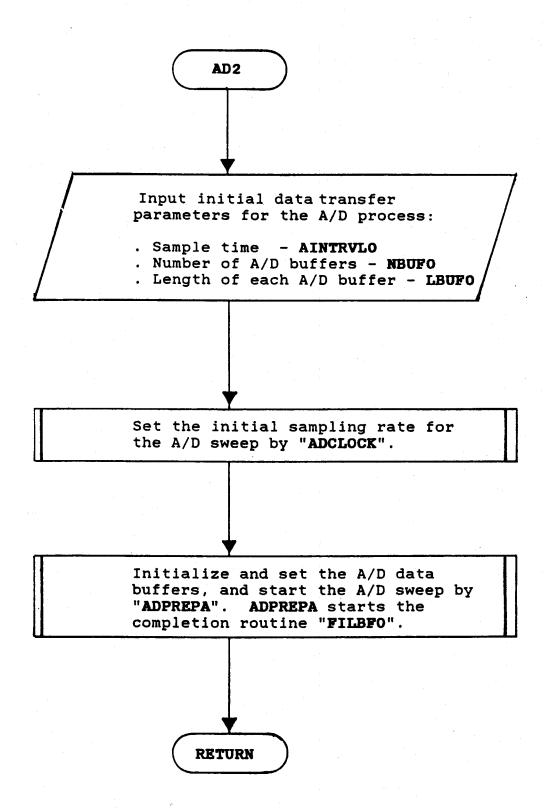

#### 3.3.2.1. The Initialization Stage

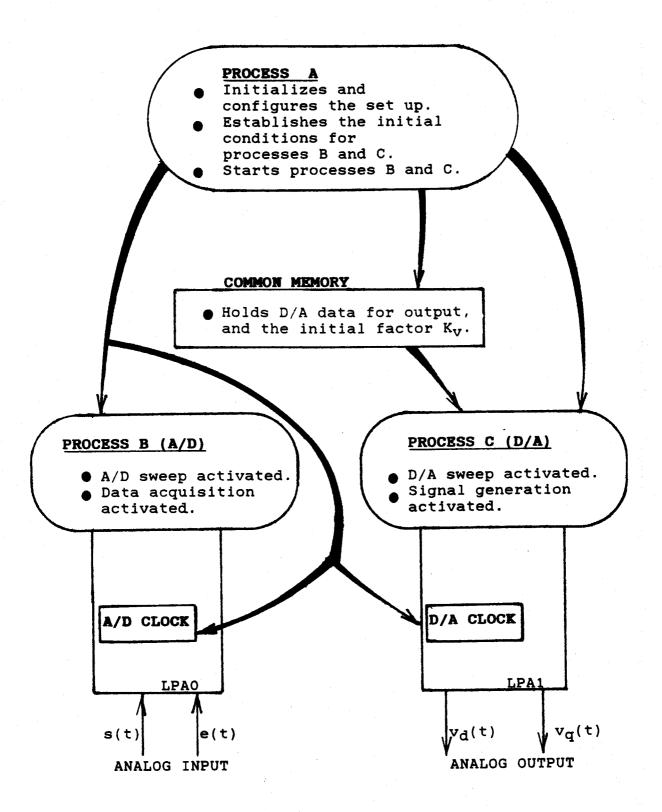

The flow diagram of Figure 3-3 shows the flow of data during the initialization stage. The supervisor, process A, performs the following tasks:

- 1. sets the initial sampling rates for processes B and C,

- 2. sets the initial multiplication factor  $K_{n}$ ,

- 3. computes the sine and the cosine ordinates, and stores the data in memory, ready to be loaded into D/A data buffers, and

- 4. starts the data transfer requests for processes B and C. When the software is configured for the oscillator mode, process C is started first. Before process B is activated, the output signals are of constant amplitude and constant frequency. The amplitude and the frequency of the output signals start to change immediately after process B is activated.

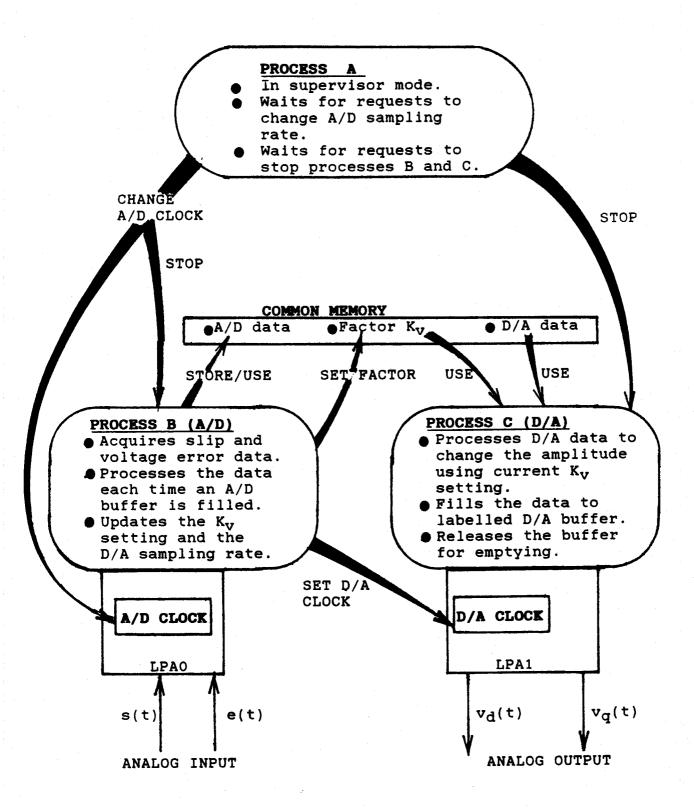

#### 3.3.2.2. The Continuation Stage

Figure 3-4 is a flow diagram showing the flow of data during the continuation stage. Both processes B and C operate under continuous sampling. Process B is activated each time an A/D data buffer is filled with data by the LPAO. While active, process B uses the A/D data to compute the slip and the voltage error corresponding to a time frame; then, it sets the D/A

sampling rate and the multiplication factor  $K_v$  for the output signals. After processing the entire A/D buffer, process B releases the buffer to the LPA0 for refilling with new data.

Similarly, process C is activated each time a D/A data buffer is emptied by the LPA1. This process adjusts the amplitude of the data in the D/A buffer. After modifying the buffer, process C releazes the buffer to the LPA1 for emptying.

The software is organized such that processes B and C execute continuously. While processes B and C are active, process A is suspended. In the waiting state, process A monitors the keyboard for requests to stop processes B and C, or change the A/D sampling rate. The details of the actual modules are summarized in Appendix B, and the listing of the programs can be found in reference [31]. Appendix B is reproduced from chapter 1 and 2 of the internal report.

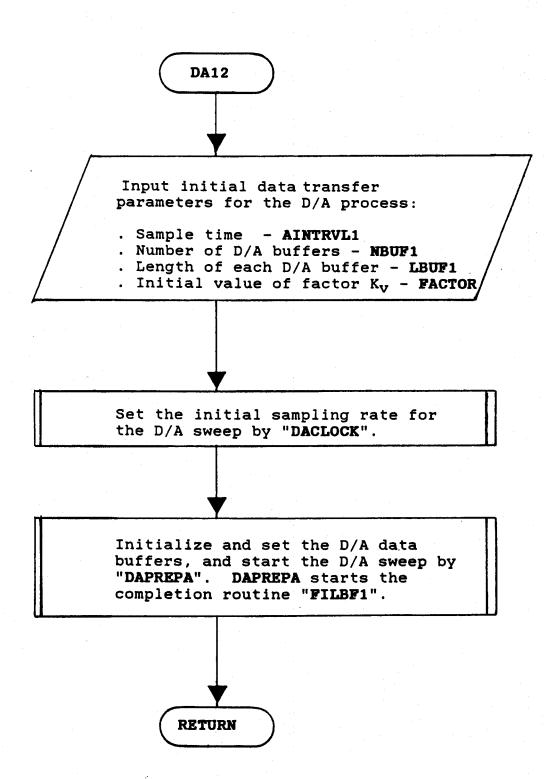

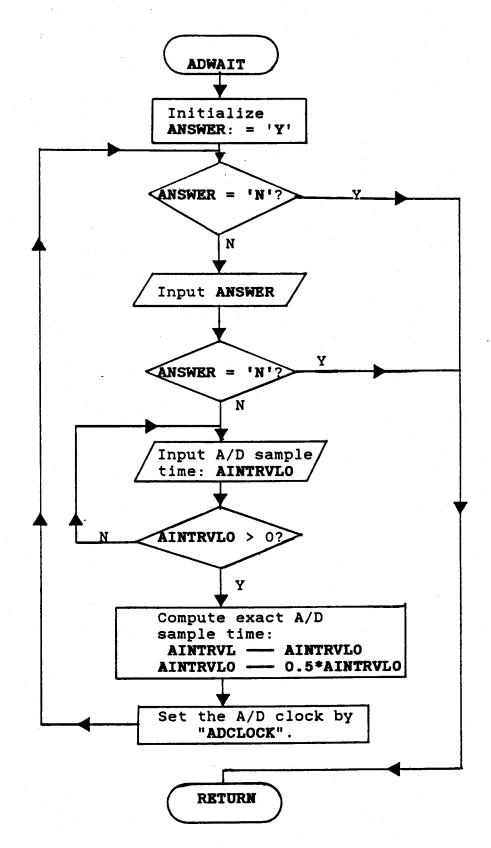

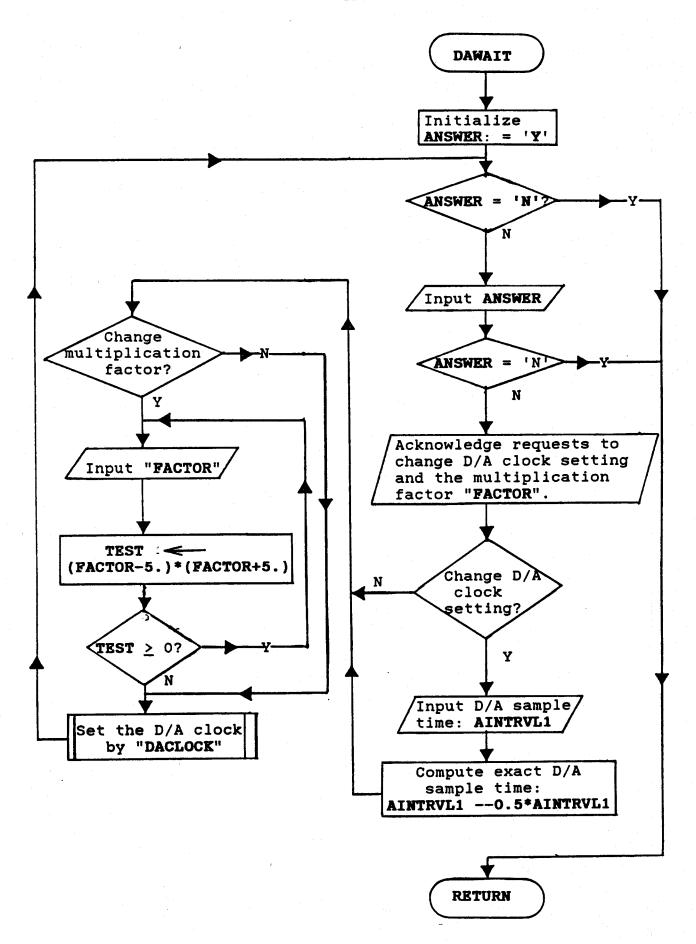

Figure 3-3: A flow diagram showing the flow of data during the initialization stage.

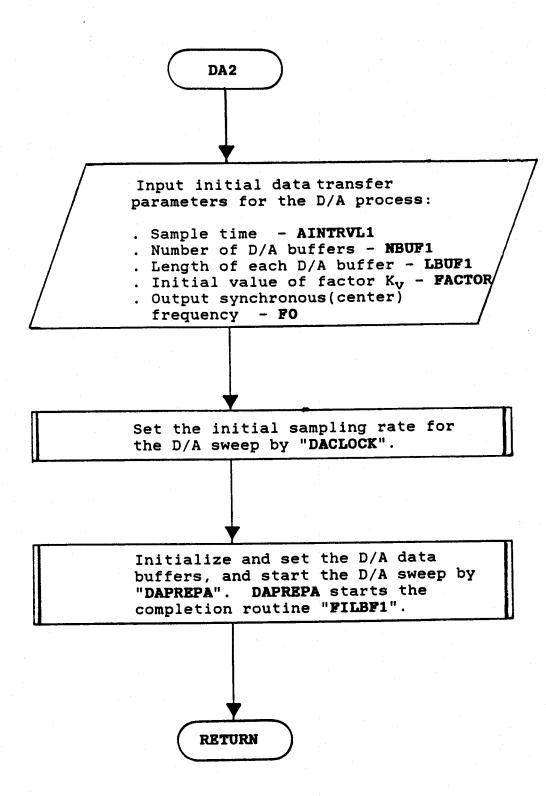

Figure 3-4: A flow diagram showing the flow of data during the continuation stage.

# Chapter 4

# EXPERIMENTS, RESULTS AND DISCUSSION

#### 4.1. Introduction

Experiments were carried out to evaluate the validity of the signal generation methodology formulated in Chapter 2, and to investigate the performance of the digital oscillator. This chapter presents and discusses the experiments, the constraints encountered while performing the tests, and the experimental results obtained.

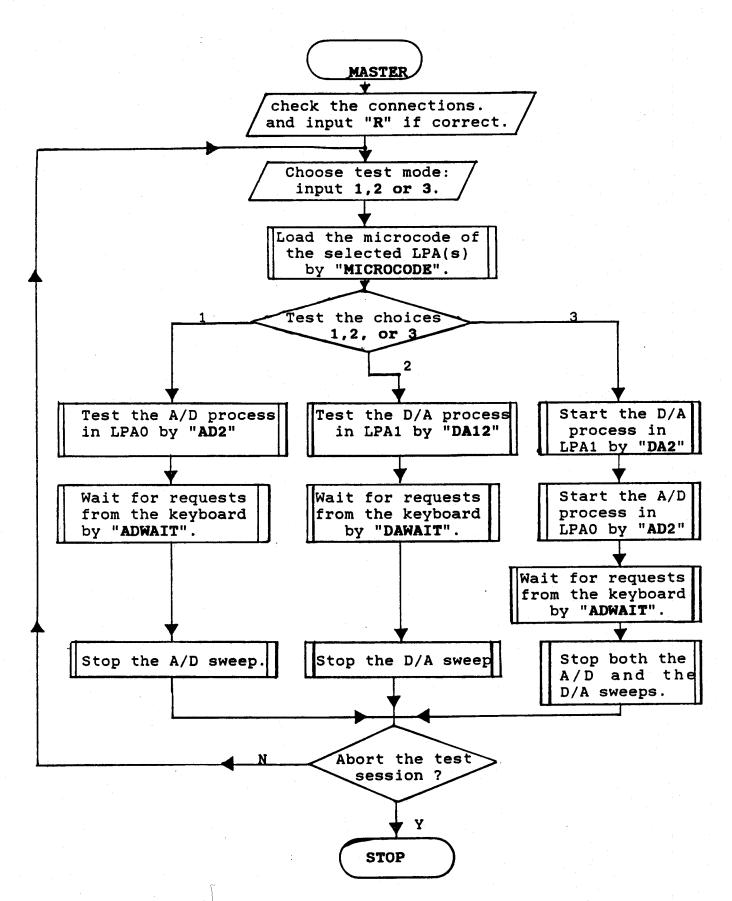

#### 4.2. The Test Procedure

The test software is designed such that several experiments can be conducted in a single experimental session. The test procedure has one major step, that is, executing the test software. While running, the program prompts the user to make choices on what to do. It may be to test process B(A/D), process C(D/A), or test the oscillator mode (running both processes B and C).

The program is documented such that it guides the user on what to enter or change. The user responses are entered through the keyboard.

The main prompts are those requesting:

- 1. the clock settings,

- 2. the reference synchronous frequency  $f_o$ ,

- 3. the length of the A/D data buffers, and

- 4. the length of the D/A data buffers and the manner these buffers are loaded with D/A data for output. The variation in the length of the D/A buffers and the manner in which they are filled with data varies the number of samples per cycle (N). Options of varying N are derived in Appendix B.

The experiments were conducted in real-time. The oscillator outputs were recorded on a plotter, and at the same time displayed on a dual channel CRT operating in the X-Y mode. The X-Y mode simulates the d-q rotor windings setup in a dual-excited synchronous generator. vector whose direction of rotation is fixed by the connections to the channels (A and B) of the CRT, can be observed on the CRT screen. the direction of rotation of the vector can be observed by interchanging the connection of one of the channels. The magnitude and frequency of the rotating vector are the visual indicators of the response of the oscillator to various types of voltage error and slip signals. The value of  $K_e$  in Equation (2.11) is set to 1.0 [volt]<sup>-1</sup>, and the value of  $K_{ref}$  is set to 1.0, for all the results presented. The input signals e(t) and s(t) are either unidirectional or alternating with frequencies as low as 0.005Hz. The user must specify the waveforms and the frequencies of the input signals and set them on the function generators.

#### 4.3. Classification of Experiments

The experiments conducted fall into three categories. The first category is of those experiments on the verification of the methodology. The second category is of those experiments on the analysis of the output signals. The third category consists of the experiments on the performance of the digital oscillator.

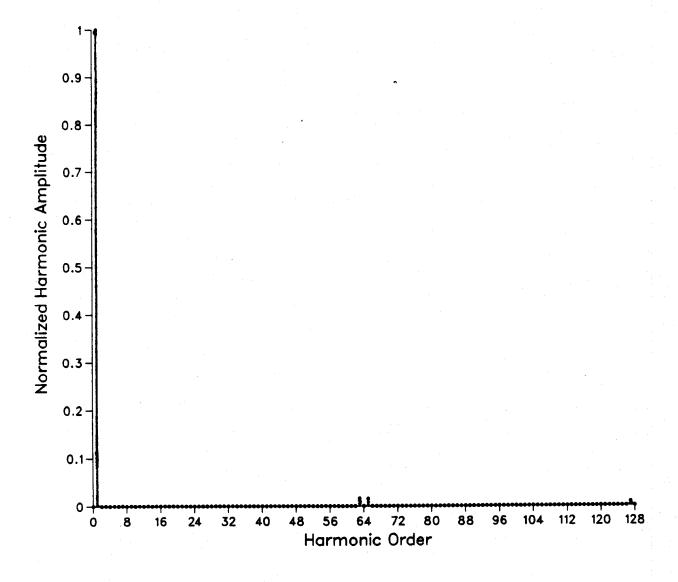

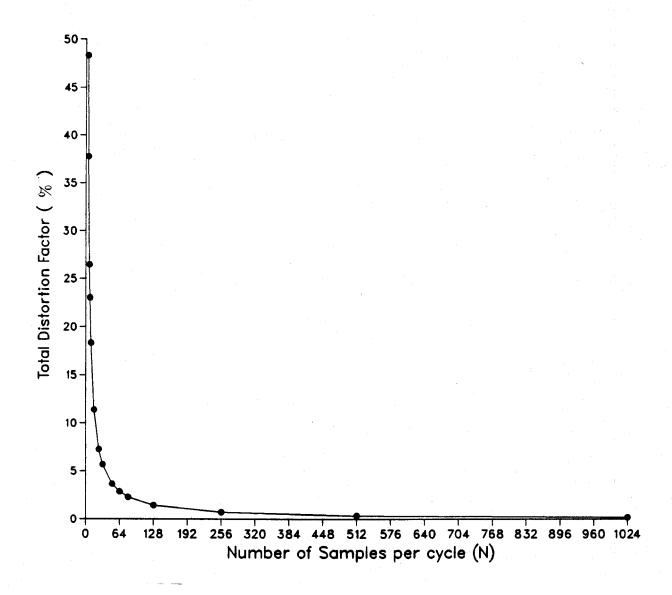

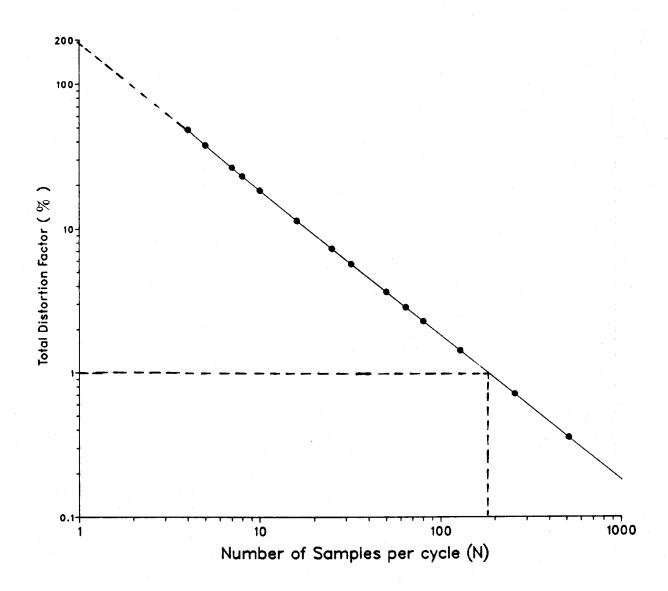

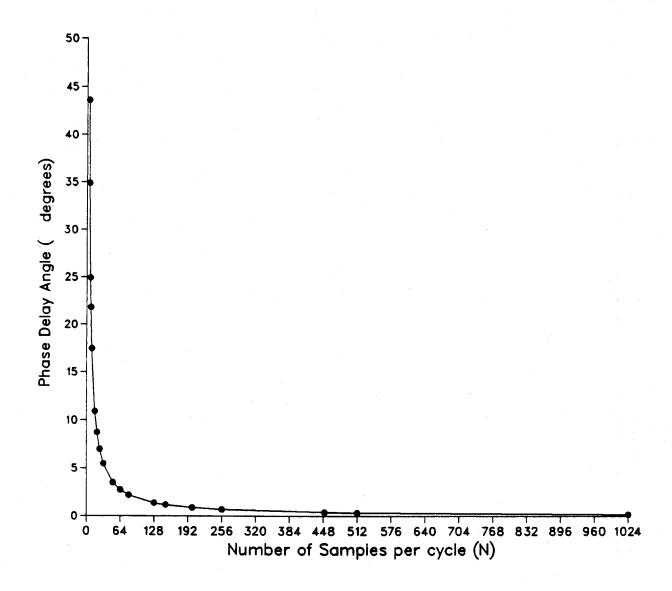

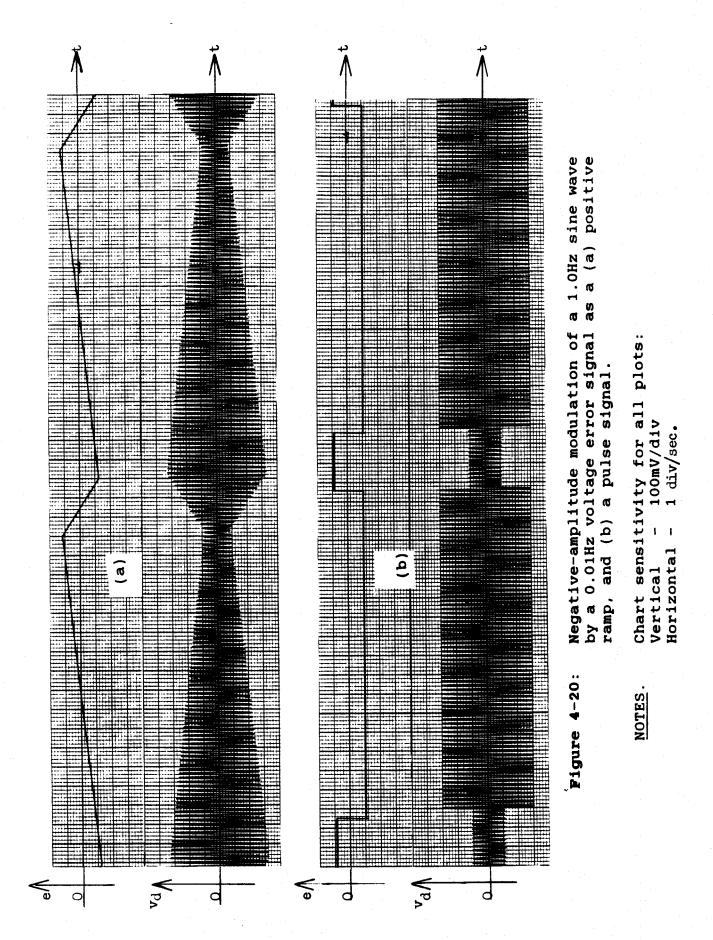

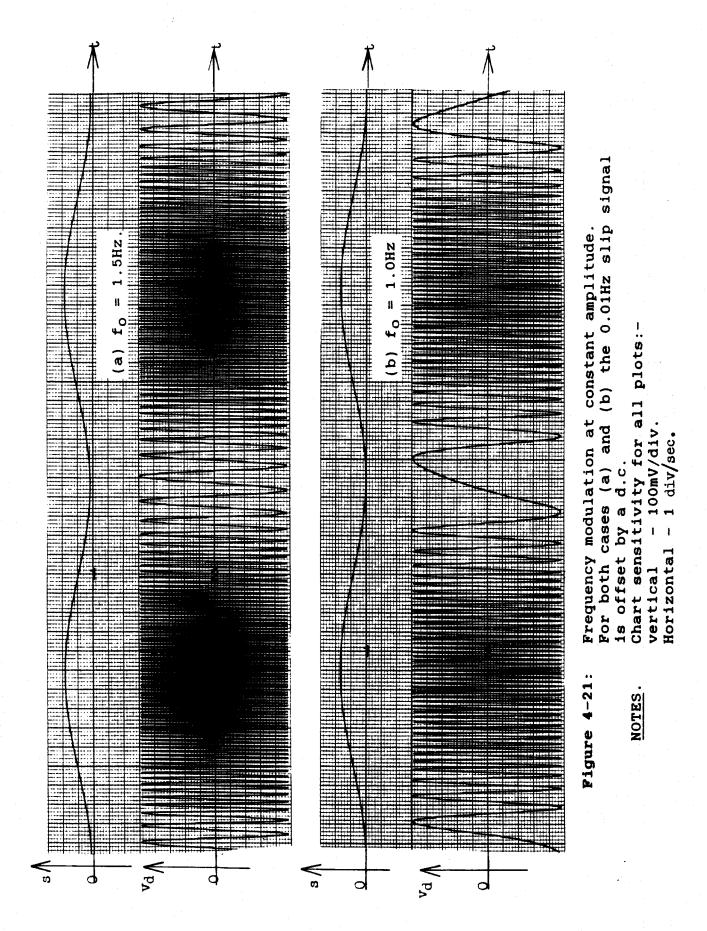

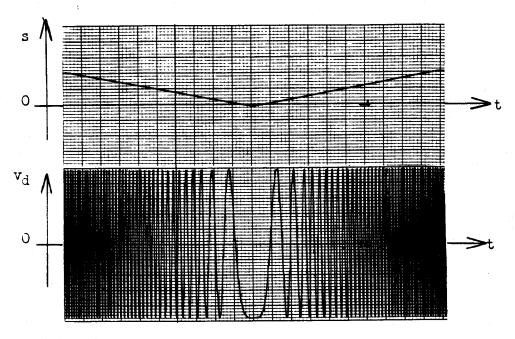

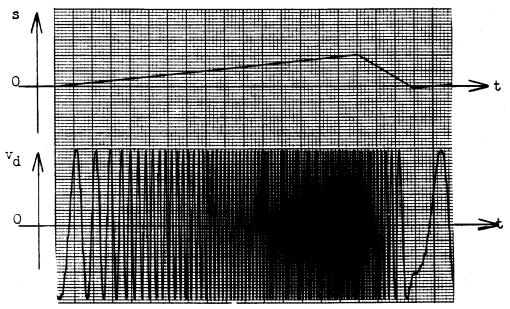

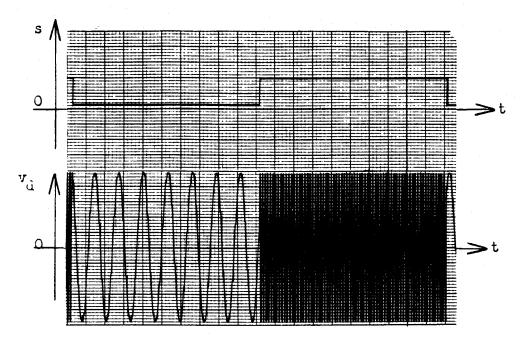

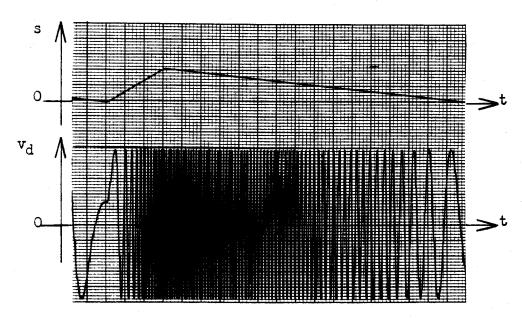

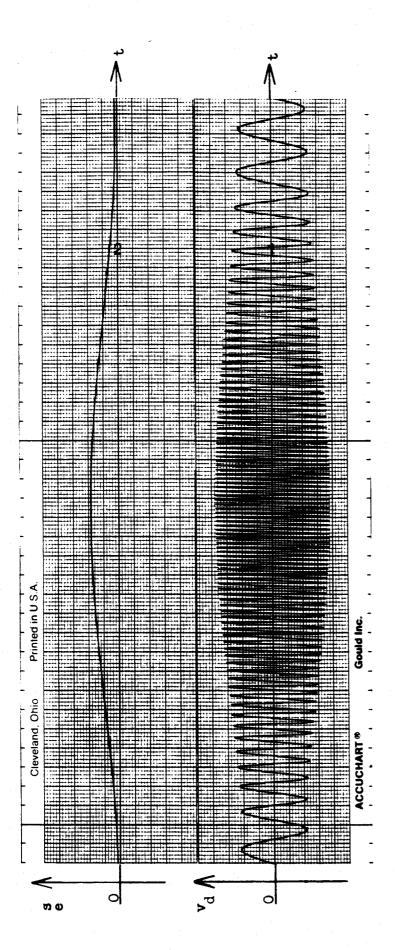

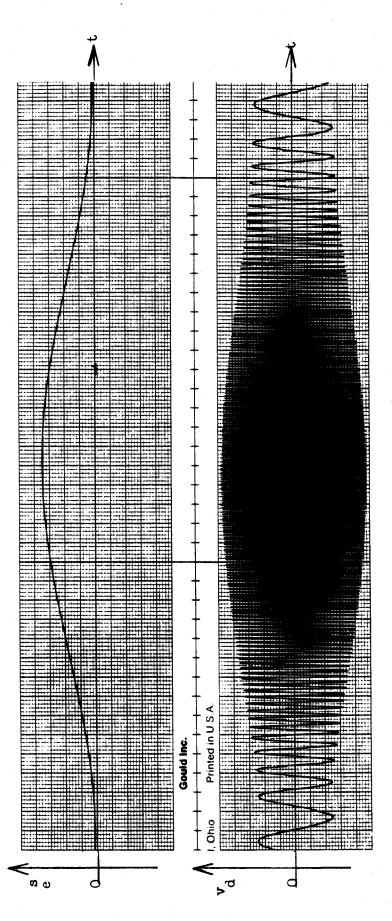

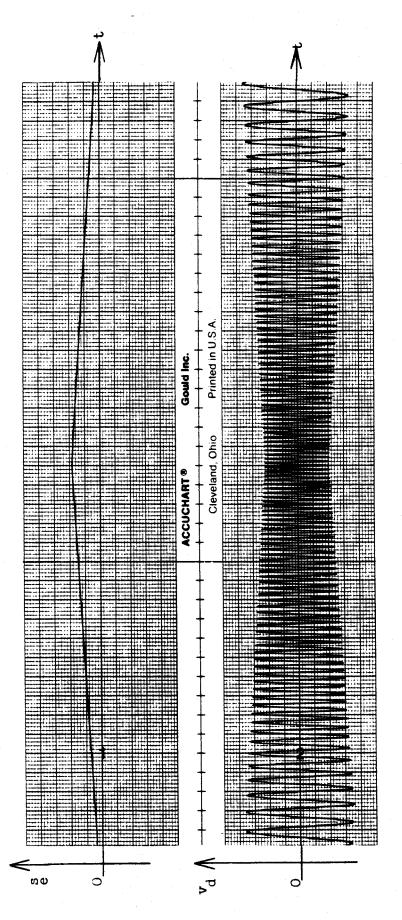

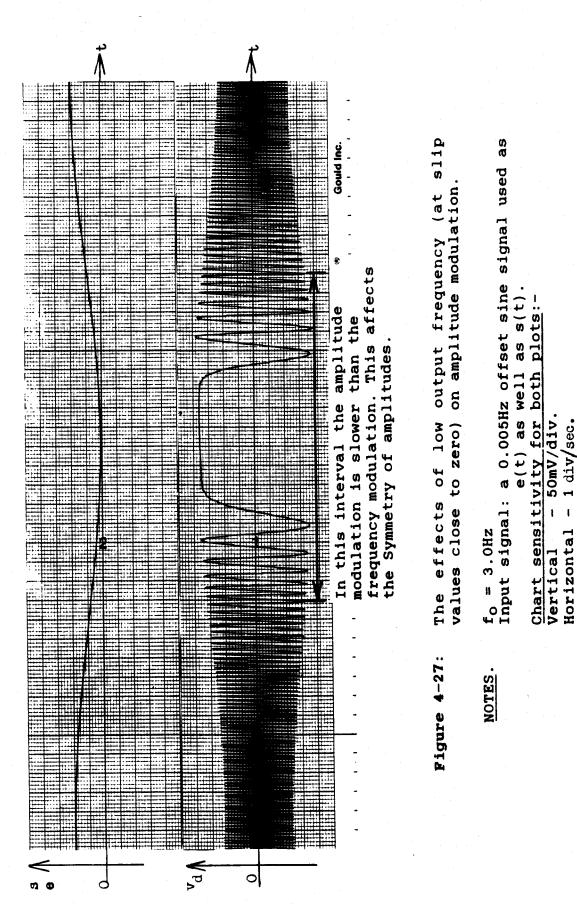

#### 4.3.1. Experiments on The Methodology