# MODELING AND ANALYSIS OF THICK SUSPENDED DEEP X-RAY LIGA INDUCTORS ON CMOS/BICMOS SUBSTRATE

A thesis Submitted to the College of

Graduate Studies and Research

in Partial Fulfillment of the requirements

for the Degree of Master of Science

in the Department of Electrical Engineering

University of Saskatchewan

Saskatoon

By Xiaoyang Yu

## **PERMISSION TO USE**

In presenting this thesis in partial fulfillment of the requirements for a Postgraduate degree from the University of Saskatchewan, I agree that the Libraries of this University may make it freely available for inspection. I further agree that permission for copying this thesis in any manner, in whole or in part, for scholarly purposes may be granted by the professors who supervised my thesis work or, in their absence, by the Head of the Department or the Dean of the College in which my thesis work was done. It is understood that any copying or publication or use of this thesis or parts thereof for financial gain shall not be allowed without my written permission. It is also understood that due recognition shall be given to me and to the University of Saskatchewan in any scholarly use which may be made of any material in my thesis.

Requests for permission to copy or to make other use of material in this thesis in whole or part should be addressed to:

Head of the Department of Electrical Engineering University of Saskatchewan Saskatoon, Saskatchewan, S7N 5A9

# **ABSTRACT**

Passive micro-scale inductors are playing an ever-increasing role in radio frequency integrated circuits (RFICs) and monolithic microwave integrated circuits (MMICs). At lower microwave frequencies, inductors on silicon (Si) substrates are a common approach, offering low process cost and possible integration with analog/digital large-scale integrated (LSI) circuits via CMOS/BiCMOS techniques. In recent years, RF MEMS (Microelectromechanical Systems) micromachinined inductors on Si substrates have received increased attention because they largely reduce not only the cost, size, and power consumption of the inductors, but also the Si conductive substrate loss and inductor metal trace resistive loss, which are two main drawbacks suffered by on chip inductors fabricated with traditional Si microelectronics processes, for instance, CMOS.

Synchrotron deep X-ray lithography (XRL, also known as LIGA) is a micromachining technique allowing the fabrication of ultra deep cavities and tall free-standing structures of arbitrary lateral shapes with high precision and high structural quality. These unique features have led to an interest in developing high performance microwave devices using LIGA. To the authors' knowledge, the LIGA microwave inductors have not been extensively explored.

This thesis presents the modeling and simulation results for two types of microwave inductors suitable for fabrication using the LIGA process. One is a suspended spiral inductor; the other is a suspended solenoid inductor. The inductors are suspended at 150  $\mu$ m height. Copper is the typical metal in the CMOS/BiCMOS technique and was used for the inductor simulations. The Si substrate and Silicon Dioxide (SiO<sub>2</sub>) isolation parameters are set up based on the TSMC 0.18  $\mu$ m CMOS/BiCMOS process data.

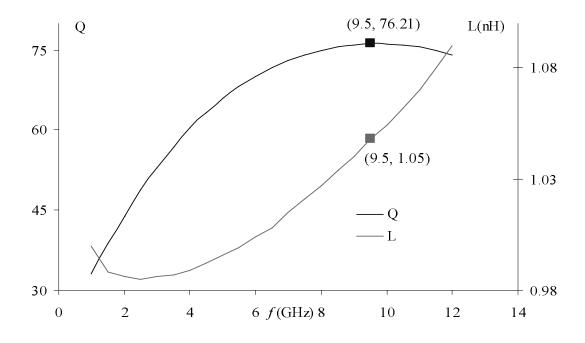

As a simulation result, one can see the suspended MEMS inductor is a good approach to reduce the substrate parasitic loss for inductors fabricated on conductive substrates like Si. When suspended at 150  $\mu$ m, a solenoid inductor can obtain a Q factor as high as 76.21 at 9.5 GHz on a simulated CMOS/BiCMOS substrate. The LIGA process is a

promising approach for fabricating such suspended structures due to its unique advantage of high aspect ratio and high quality vertical sidewall realization. By using multi-exposure LIGA and/or LIGA pattern transfer techniques, complicated 3D structures like the solenoid inductor, could potentially be fabricated on CMOS substrate with excellent performance. This result reveals the possible and promising strength of LIGA combined with CMOS for high performance inductor fabrications.

#### **ACKNOWLEDGEMENTS**

I would like to express my gratitude to my supervisor, Dr. David M. Klymyshyn, for providing me this opportunity to study for my Master's degree at the university of Saskatchewan and the cordial assistance for me to achieve the NSERC Scholarship, and for his guidance, criticism, and encouragement throughout this thesis research.

Also, I would like to extend my appreciation to NSERC, TRLabs, and all TRLabs' management and staffs for providing financial assistance and wonderful research environment for this thesis research.

Finally, I would like to acknowledge my family and friends for their great spiritual and financial support, love, friendship, understanding, and help to make the hard study life easier.

# TABLE OF CONTENTS

| PERMISSION TO USE                                                | I       |

|------------------------------------------------------------------|---------|

| ABSTRACT                                                         | II      |

| ACKNOWLEDGEMENTS                                                 | IV      |

| TABLE OF CONTENTS                                                | V       |

| LIST OF FIGURES                                                  | VII     |

| LIST OF TABLES                                                   | XII     |

| LIST OF ABBREVIATIONS                                            |         |

| 1 INTRODUCTION                                                   |         |

| 1.1 Motivation                                                   |         |

| 1.2 Importance of Inductors in Communication Circuits            |         |

| 1.3 Si / CMOS Technology                                         |         |

| 1.4 MEMS/LIGA Techniques                                         |         |

| 1.5 Research Objectives                                          | 8       |

| 1.6 Thesis Outline                                               | 10      |

| 2 PRINCIPLE OF LIGA PROCESS AND ON SILICON INDUCTOR THI          | EORY 11 |

| 2.1 Principle of LIGA Fabrication Process                        | 11      |

| 2.2 Inductor Principle                                           |         |

| 2.3 Quality Factor of the Inductor                               |         |

| 2.4 Physical Lumped Equivalent Model and Loss Mechanism          |         |

| 2.4.1 On Silicon Spiral Inductor Lumped Model and Loss Mechanism |         |

| Series Inductance $L_s$                                          |         |

| Parallel Capacitance $C_s$                                       |         |

| Substrate Parasitics and Losses                                  |         |

| 2.5 Spiral Inductor Quality Factor Frequency Analysis            |         |

| 2.6 Solenoid Inductor Lumped Model and Loss Mechanism            | 35      |

| 3 INDUCTOR LAYOUT AND PREVIOUS WORK                              | 41      |

| 3.1 Inductor Layout                                              | 41      |

| 3.1.1 Planar Inductor Structure                                  |         |

| 3.1.2 Non-Planar Inductor Structures                             | 44      |

| 3.2 Previous Work                                                |         |

| 3.2.1 Micromachining Inductors                                   |         |

| Substrate Etching                                                |         |

| Self-Assembly                                                    |         |

| 3.2.2 Previous Work in CMOS Compatible MEMS Inductors            |         |

| 4 DECICN OF LICA MEMO AID CODE INDUCTODS ON CMOS                 |         |

| 4.1 Finite Element Method and HFSS                                                              | 52 |

|-------------------------------------------------------------------------------------------------|----|

| 4.2 Inductor HFSS Simulation Model Designs                                                      |    |

| 4.2.1 Virtual HFSS Block Setup                                                                  | 56 |

| 4.2.2 Combined Substrate Simulation Setup                                                       |    |

| 4.2.3 Spiral Inductor Simulation Model Setup                                                    |    |

| 4.2.4 Anchors and Ground Ring Simulation Setup for Spiral Inductors                             |    |

| 4.2.5 Solenoid Inductor Simulation Models Setup                                                 |    |

| 4.3 Brief Discussions of the Proposed Combination with CMOS                                     | 69 |

| 5 SIMULATION, ANALYSIS, AND OPTIMIZATION FOR THE LIGA A CORE INDUCTORS ON CMOS/BICMOS SUBSTRATE |    |

| 5.1 Simulation Analysis of the Square Spiral Inductors                                          | 71 |

| 5.1.1 Varying <i>t</i> <sub>1</sub>                                                             |    |

| 5.1.2 Varying <i>w</i> <sub>1</sub>                                                             |    |

| 5.2 Simulation Analysis of the Solenoid Inductors                                               |    |

| 5.2.1 Varying $h_1$                                                                             |    |

| 5.3 Summary of The Inductor Simulations                                                         |    |

| 5.4 Optimization                                                                                | 88 |

| 6 CONCLUSIONS                                                                                   | 92 |

| 6.1 Summary                                                                                     | 92 |

| 6.2 Conclusions                                                                                 |    |

| 6.3 Future research directives                                                                  | 94 |

| REFERENCE:                                                                                      | 96 |

| APPENDIX:                                                                                       |    |

| A. Some Simulations Results for Spiral Inductor                                                 |    |

| B. Some Simulations Results for Solenoid Inductor                                               |    |

# LIST OF FIGURES

| Figure 1.1  | : Applications of passive inductors in Si IC building blocks. (a)       |      |

|-------------|-------------------------------------------------------------------------|------|

|             | Impedance matching. (b) Tuned load. (c) Emitter degeneration. (d)       |      |

|             | Filtering.                                                              | 4    |

| Figure 1.2: | Applications of passive devices in Si IC building blocks: Distributed   |      |

|             | Amplifier                                                               | 5    |

| Figure 1.3: | Illustration of aspect ratio                                            | 7    |

| Figure 2.1  | : LIGA process steps (a) Application of seed layer on substrate; b)     |      |

|             | Application of photoresist; c) X-ray exposure (lithography); d)         |      |

|             | Photoresist development after lithography; e) Metal electroplating; f)  |      |

|             | Removal of photoresist and seed layer                                   | . 12 |

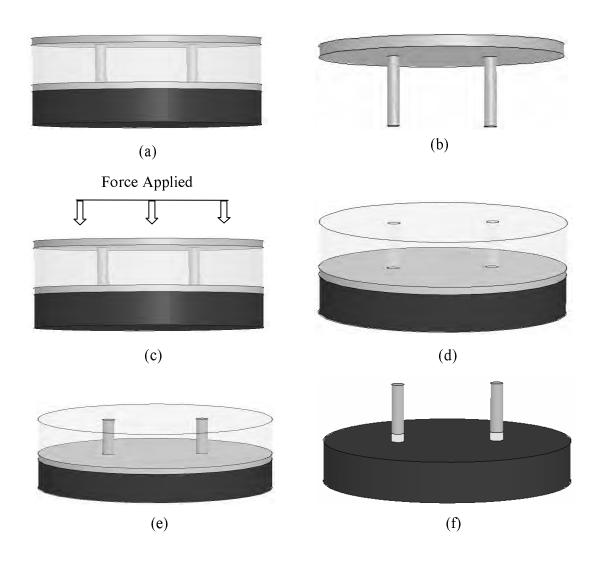

| Figure 2.2  | 2: LIGA Process with Replication by Hot Embossing: a) Metal             |      |

|             | overplating into X-ray patterned photoresist; b) Release of metal mold  |      |

|             | insert; c) Hot embossing; d) Plastic mold; e) Secondary metal           |      |

|             | deposition; f) Final metal structure                                    | . 13 |

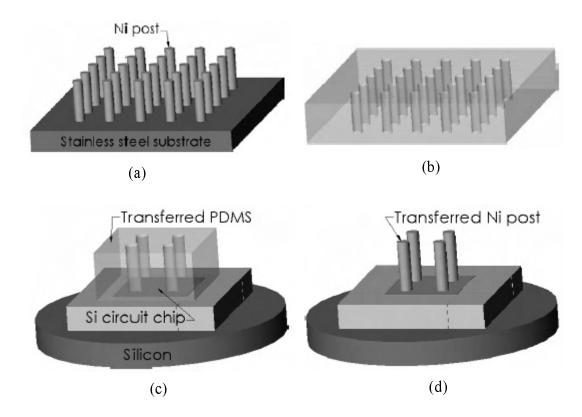

| Figure 2.3  | The process flow for the pattern transfer of a LIGA HARM [5]: (a)       |      |

|             | LIGA -processed metallic master mold; (b) The replicated PDMS           |      |

|             | mold; (c) PDMS mold on a Si circuit chip with metallic seed layer and   |      |

|             | adhesive PI layer; (d) The on chip transferred LIGA HARM                | . 15 |

| Figure 2.4  | The PDMS-based pattern transfer process sequence for a spiral           |      |

|             | inductor [5]: (a) Spin-coating of PDMS; (b) Peeled-off PDMS; (c)        |      |

|             | PDMS mold on a CMOS circuit chip with bottom electrodes, metallic       |      |

|             | seed layer, and adhesive PI layer; (d) Transferred metallic inductor on |      |

|             | a chip.                                                                 | . 16 |

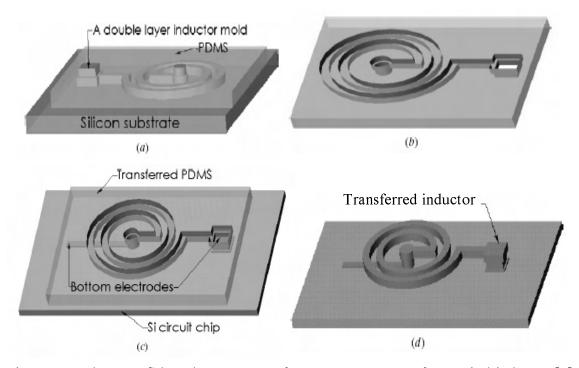

| Figure 2.5  | (a) An independent current loop (b) A magnetically coupled pair of      |      |

|             | loops. Current only exists in loop j                                    | . 17 |

| Figure 2.6  | : (a) 3-D view of a spiral inductor; (b) Lumped-element equivalent      |      |

|             | model of a spiral inductor [21]                                         | . 21 |

| Figure 2.7  | : Lumped-element equivalent model of a spiral inductor with extra       |      |

|             | elements                                                                | 22   |

| Figure 2.8: (a) Spacing S, line width W, and line pitch D=S+W of a spiral             |    |

|---------------------------------------------------------------------------------------|----|

| inductor; (b) Positive and negative mutual coupling illustration in a                 |    |

| spiral inductor                                                                       | 24 |

| Figure 2.9: Illustration of skin effect and proximity effect in terms of straight     |    |

| wires with rectangular cross-section                                                  | 25 |

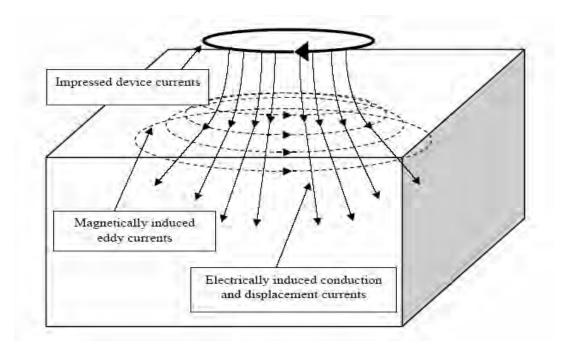

| Figure 2.10: Schematic representation of substrate currents. Eddy currents and        |    |

| electrically induced currents are represented by the dashed lines and                 |    |

| the solid lines, respectively [6].                                                    | 30 |

| Figure 2.11 : Simplified lumped equivalent circuit models                             | 31 |

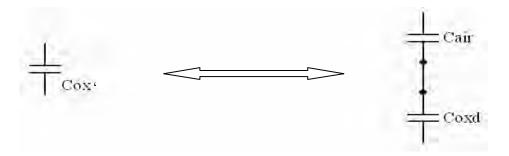

| Figure 2.12: The equivalent Cox' of a suspended spiral inductor                       | 33 |

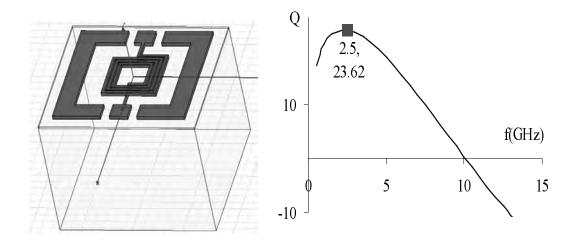

| Figure 2.13: A sample spiral inductor and its Q-factor simulation result              | 34 |

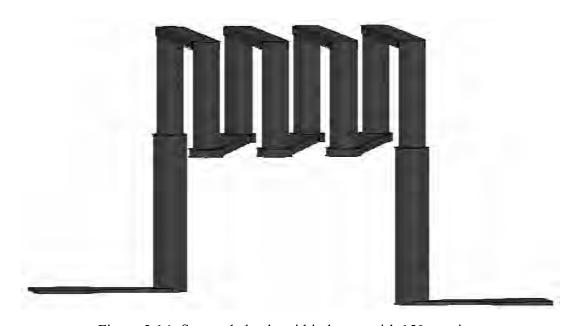

| Figure 2.14: Suspended solenoid inductor with 150µm air gap                           | 36 |

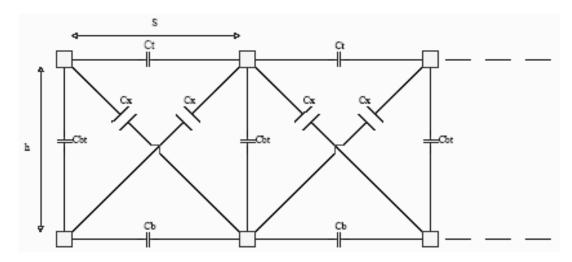

| Figure 2.15: The equivalent circuit for calculating the stray capacitances between    |    |

| conductor lines. The side cross-sectional area of the conductor lines                 |    |

| and the capacitances between these conductor lines are shown [30]                     | 38 |

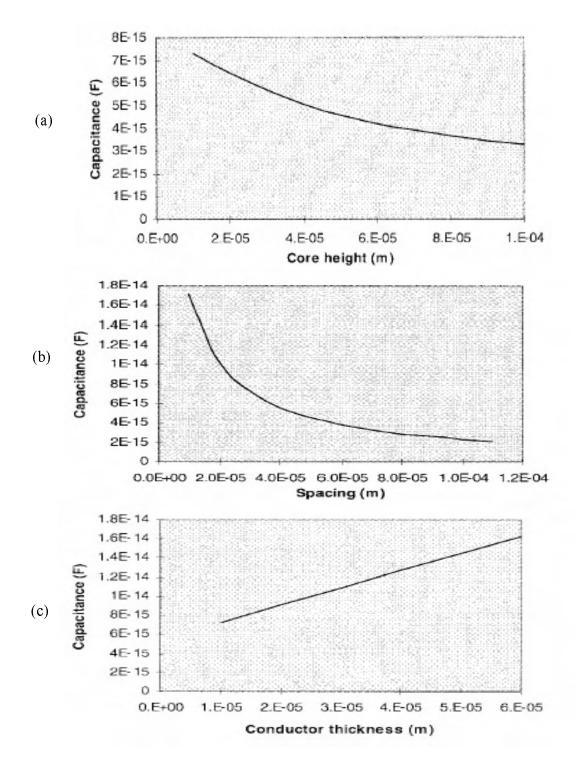

| Figure 2.16 [30]: (a) The stray capacitance change with various core heights (h);     |    |

| (b) The stray capacitance change with various line spacings (s); (c)                  |    |

| The stray capacitance change with various conductor line thicknesses                  |    |

| ( <i>b</i> )                                                                          | 40 |

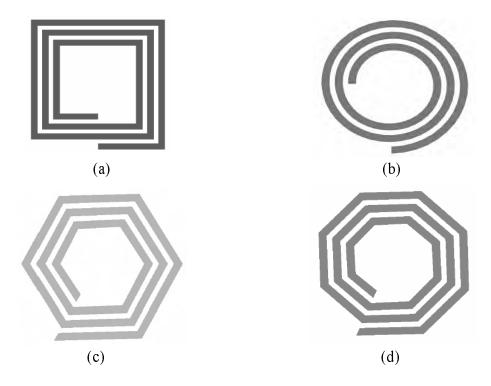

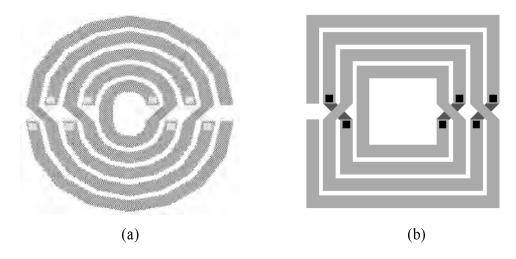

| Figure 3.1: Spiral inductor layouts. (a) A square-type; (b) A circular-type; (c), (d) |    |

| polygon-types                                                                         | 42 |

| Figure 3.2: (a) A balanced polygon spiral inductor; (b) A balanced square spiral      |    |

| inductor                                                                              | 43 |

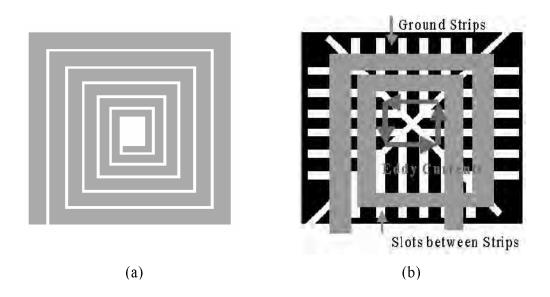

| Figure 3.3: (a) A tapered spiral inductor; (b) A patterned ground shield inductor     |    |

| with "hollow" spiral                                                                  | 43 |

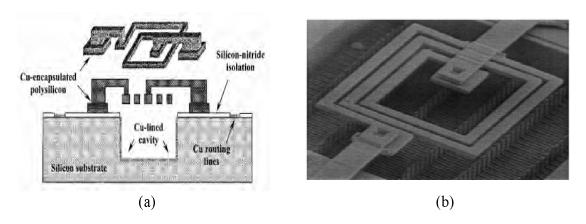

| Figure 3.4 [38]: (a) Schematic of a copper-encapsulated polysilicon inductor          |    |

| suspended over a copper-lined cavity beneath; (b) SEM image of the                    |    |

| fabricated inductor                                                                   | 45 |

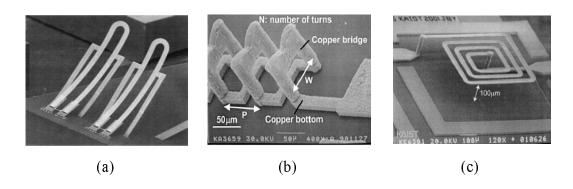

| Figure 3.5: (a) The SEM image of a self-assembled inductor; (b) The SEM image         |    |

| of a solenoid inductor; (c) The SEM image of a suspended planar                       |    |

| inductor                                                                              | 46 |

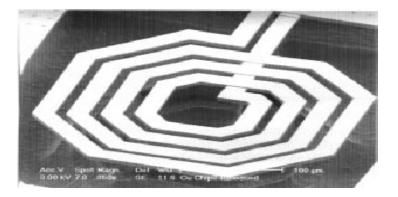

| Figure 3.6: The SEM picture of the 0.18µm CMOS compatible suspended spiral              |    |

|-----------------------------------------------------------------------------------------|----|

| inductor [40]4                                                                          | .7 |

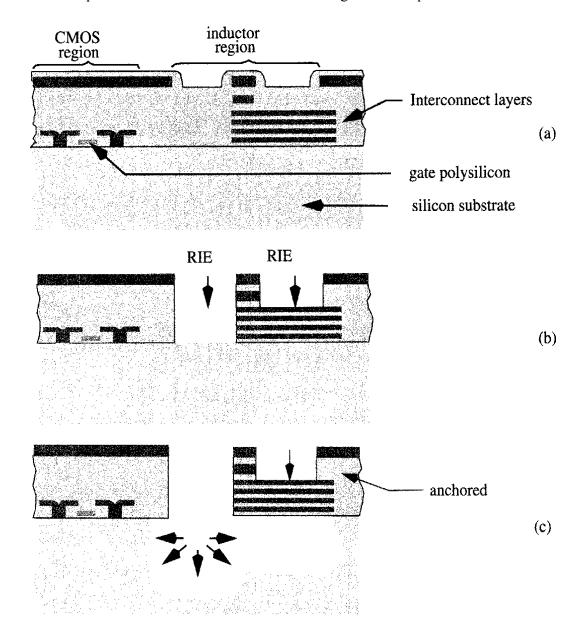

| Figure 3.7 [40]: Cross sections of the CMOS compatible inductor fabrication             |    |

| simplified process steps (a). The conventional CMOS die from the                        |    |

| foundry; (b). After removal of sidewall oxide; (c). After silicon                       |    |

| substrate removal by anisotropic and isotropic etch4                                    | 8  |

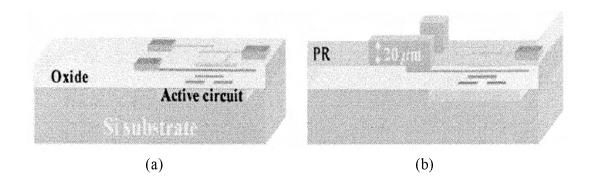

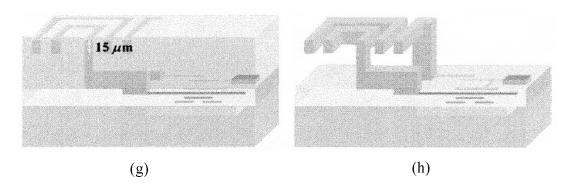

| Figure 3.8: The suspended inductor simplified fabrication process [41]                  | 0  |

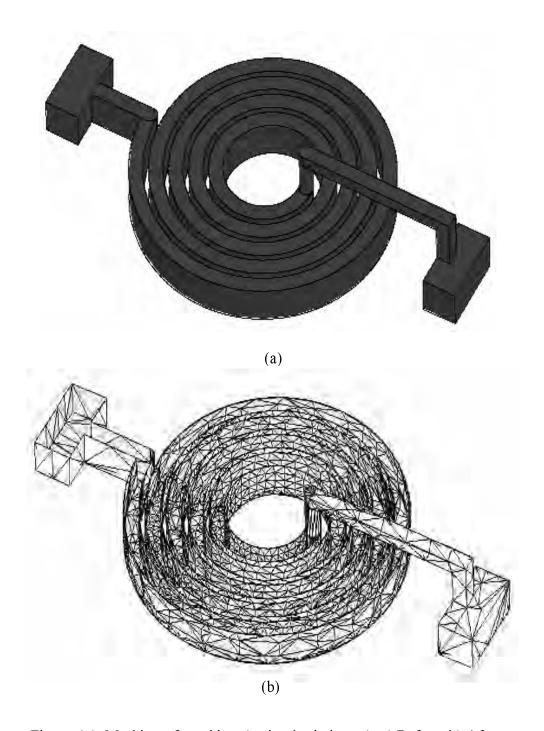

| Figure 4.1: Meshing of an object (a circular inductor): a) Before; b) After5            | 3  |

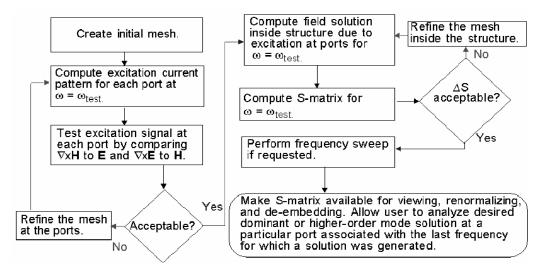

| Figure 4.2: Simplified flow chart illustration of the HFSS adaptive solution5           | 5  |

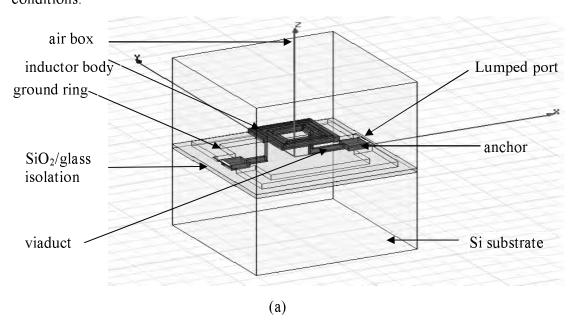

| Figure 4.3: HFSS simulation model for a suspended square spiral inductor5               | 5  |

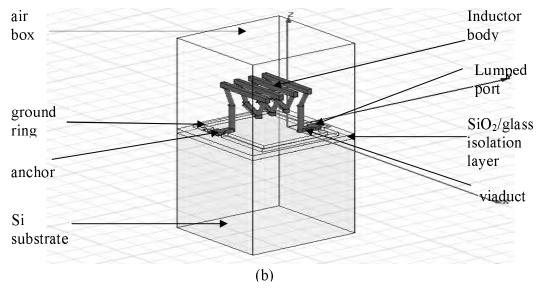

| Figure 4.4: HFSS simulation model for a suspended solenoid inductor                     | 6  |

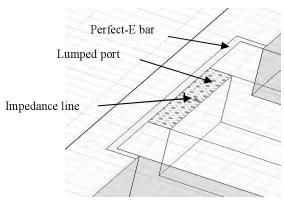

| Figure 4.5: Lumped port setup                                                           | 7  |

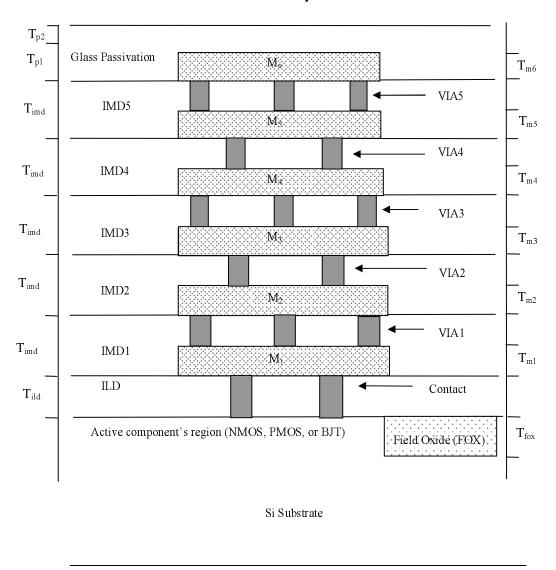

| Figure 4.6: Generic cross section view of CMOS and /or BiCMOS devices                   |    |

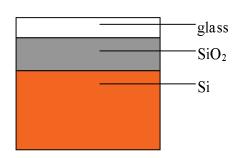

| fabricated with TSMC 0.18µm technique [46]5                                             | 8  |

| Figure 4.7: Simplified TSMC 0.18µm CMOS device substrate layers                         | 9  |

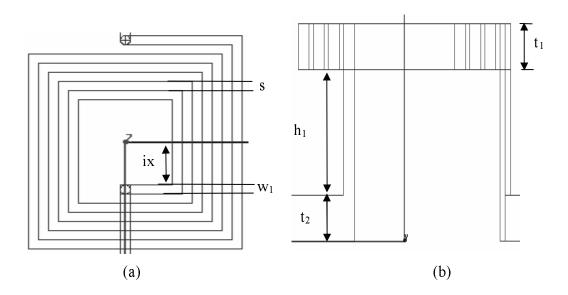

| Figure 4.8: Rectangular spiral inductor model simulation variables. (a) Simplified      |    |

| top view; (b) Simplified side view6                                                     | 0  |

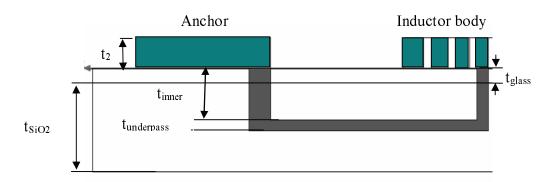

| Figure 4.9: Partial cross section situation of the substrate touching spiral inductor 6 | 2  |

| Figure 4.10: Partial cross section view of the magnetic flux and current                |    |

| distributions of the substrate touching spiral inductor6                                | 3  |

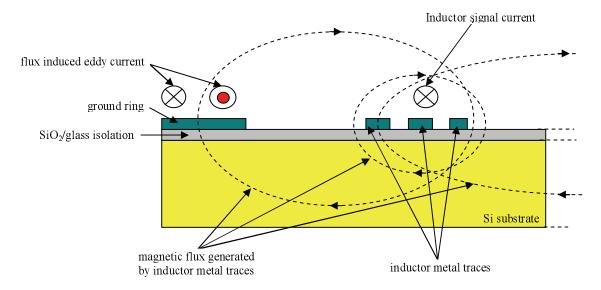

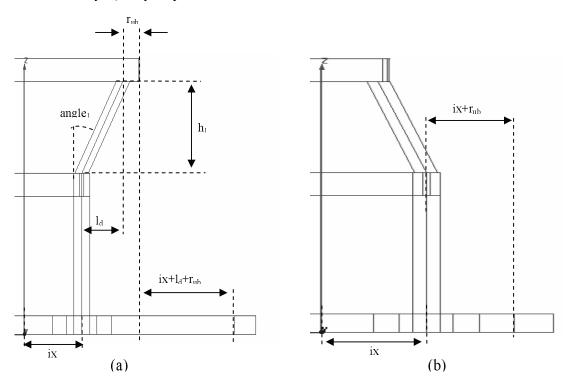

| Figure 4.11: Simplified view and simulation variable illustration of the solenoid       |    |

| inductor model (a) Side view; (b) Front view                                            | 4  |

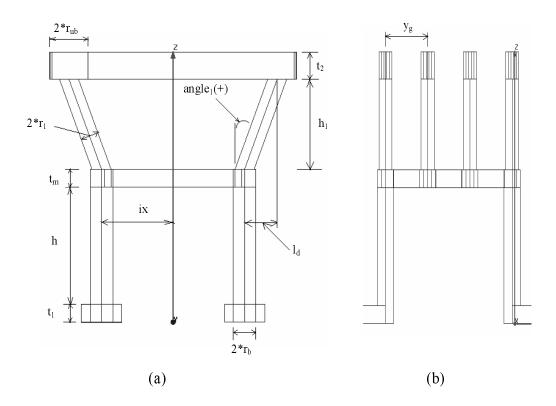

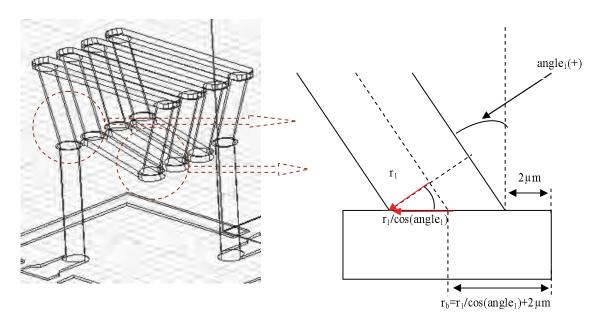

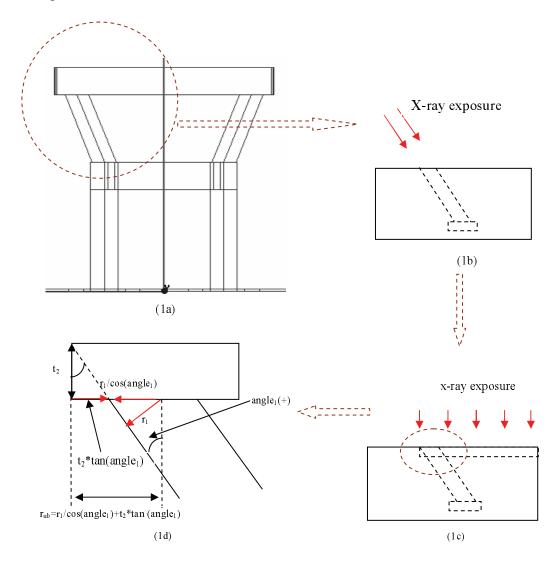

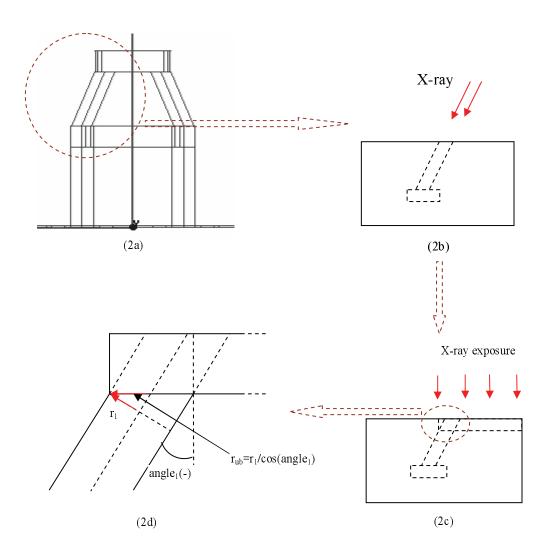

| Figure 4.12: The relationship between variable $r_l$ and $r_b$ in model design6         | 5  |

| Figure 4.13: Variable $r_{ub}$ set up when $angle_I$ is positive                        | 6  |

| Figure 4.14: Variable $r_{ub}$ set up when $angle_1$ is negative                        | 7  |

| Figure 4.15: Some detail in ground ring set up. (a) angle1 is positive; (b) angle1 is   |    |

| negative 6                                                                              | 8  |

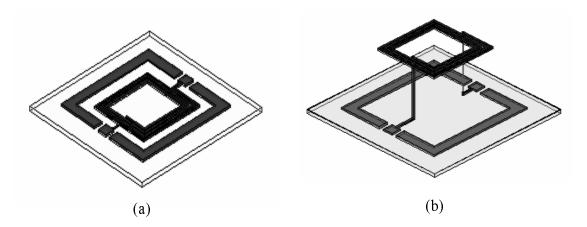

| Figure 5.1: Simplified incipient models of spiral inductor. (a) Substrate touching      |    |

| type; (b) Suspended type7                                                               | 1  |

| Figure 5.2: (a) Simulated S parameters. (b) $Q$ and $L$ curves of the spiral startup    |    |

| models 7                                                                                | 2  |

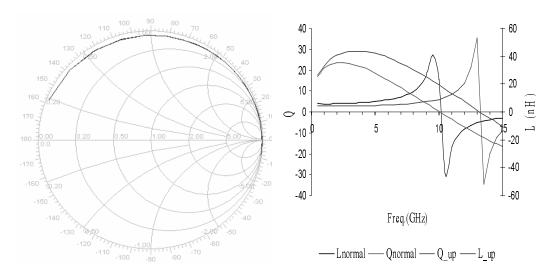

| Figure 5.3: Top view of the spiral inductor (a) Surface current distribution (b)           |     |

|--------------------------------------------------------------------------------------------|-----|

| Magnitude H field distribution                                                             | .74 |

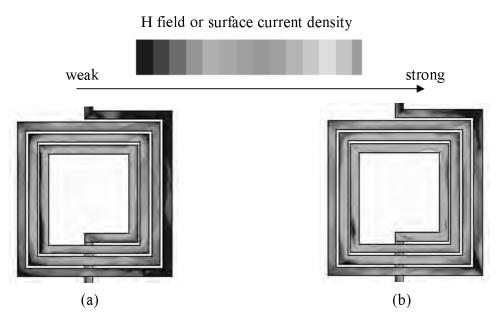

| Figure 5.4: Comparison of the simulation results for the $t_1$ variations. (a)             |     |

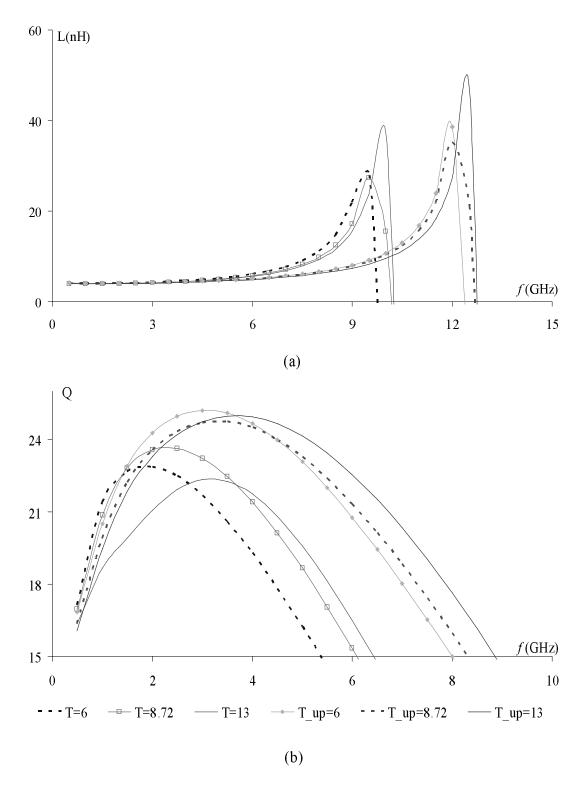

| Inductance comparisons; (b) Q factor comparisons                                           | 76  |

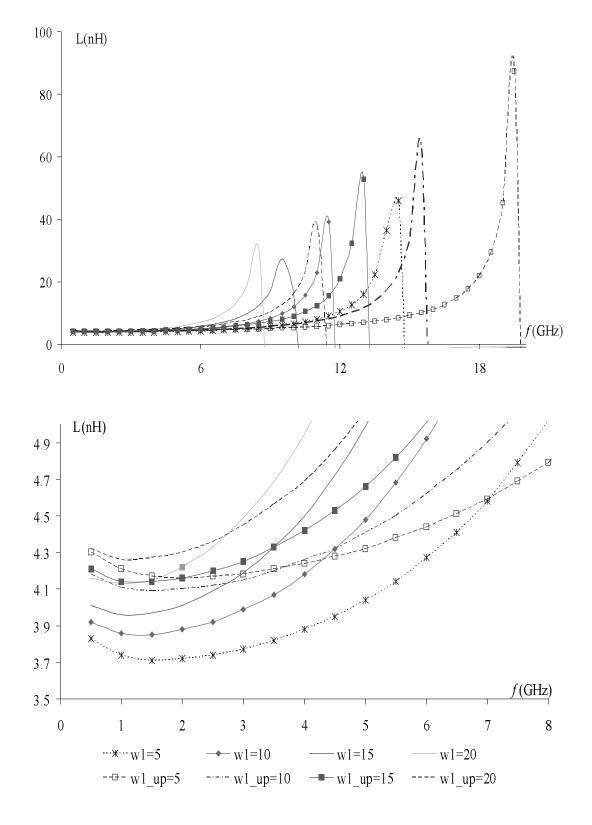

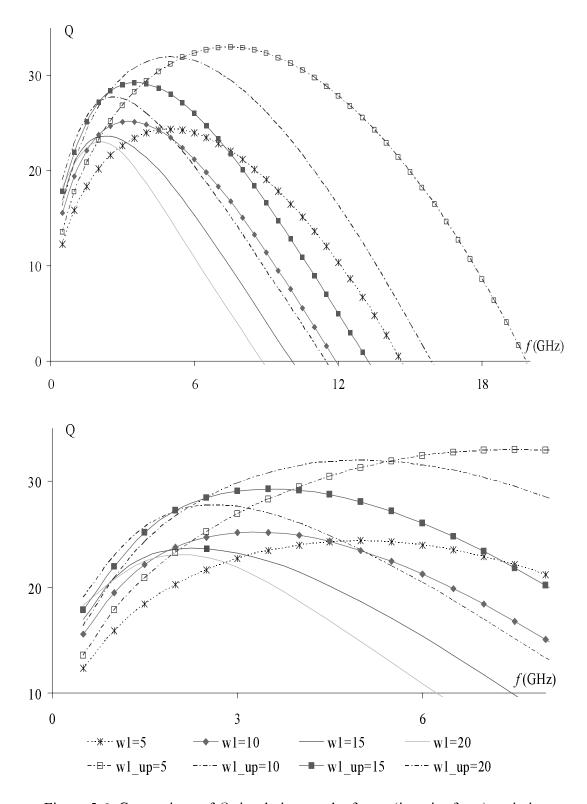

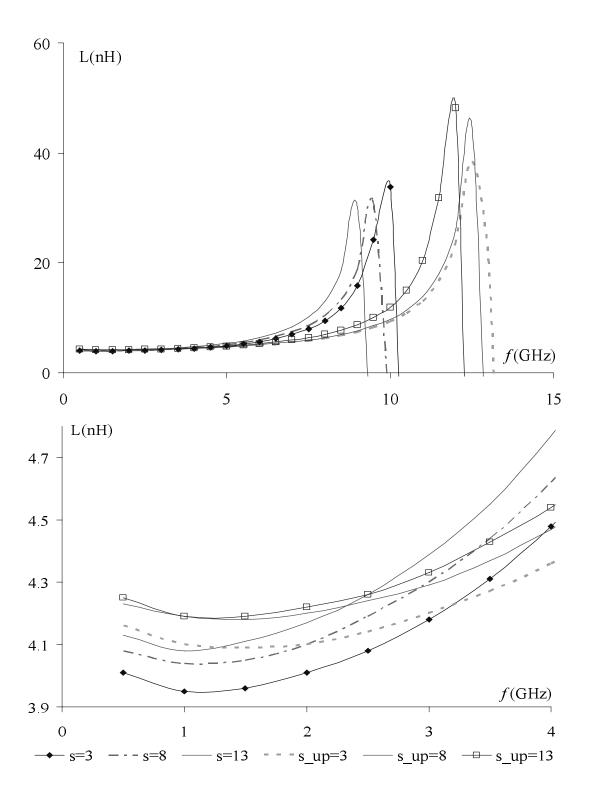

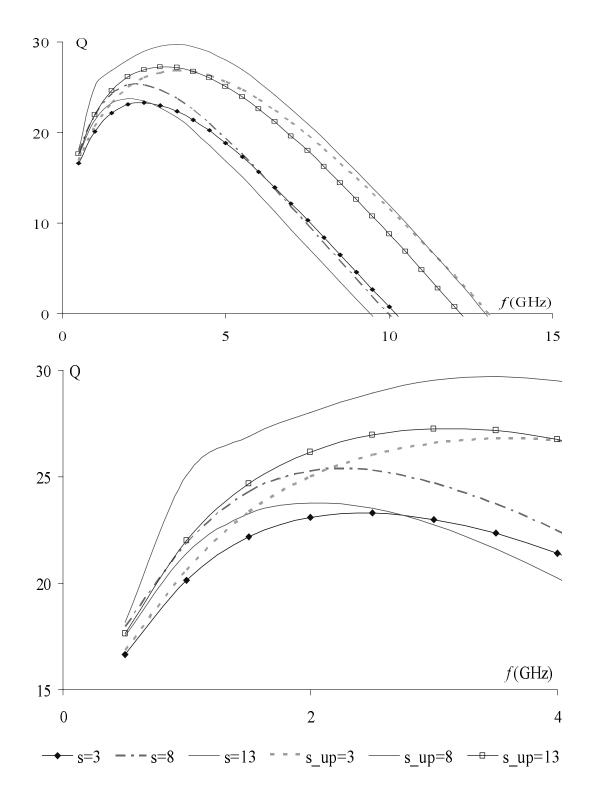

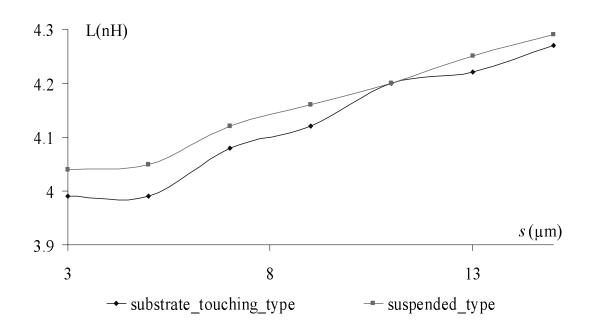

| Figure 5.5: Comparison of inductance simulation results for $w_I$ (in unit of $\mu m$ )    |     |

| variations.                                                                                | .79 |

| Figure 5.6: Comparison of $Q$ simulation results for $w_I$ (in unit of $\mu$ m) variations | .80 |

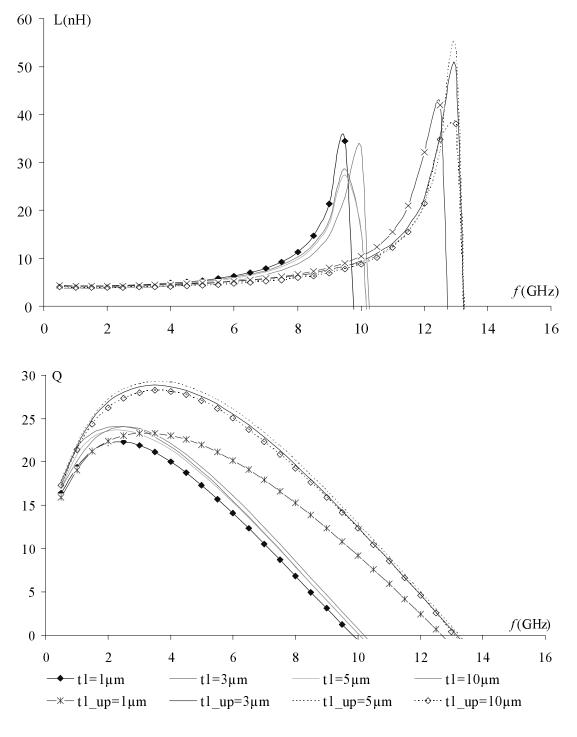

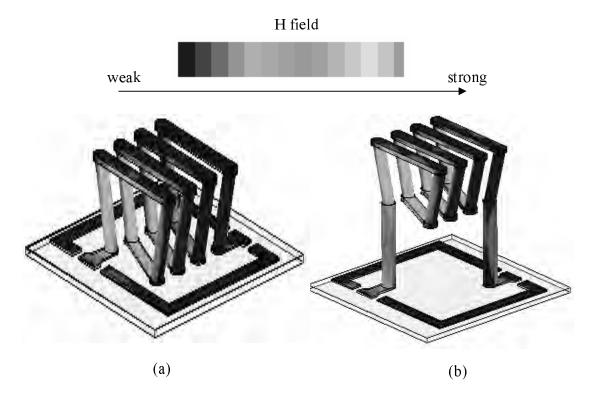

| Figure 5.7: Simplified startup models of solenoid inductor. (a) Substrate touching         |     |

| type; (b) Suspended type                                                                   | 81  |

| Figure 5.8: $Q$ and $L$ curves of the solenoid start up models                             | 82  |

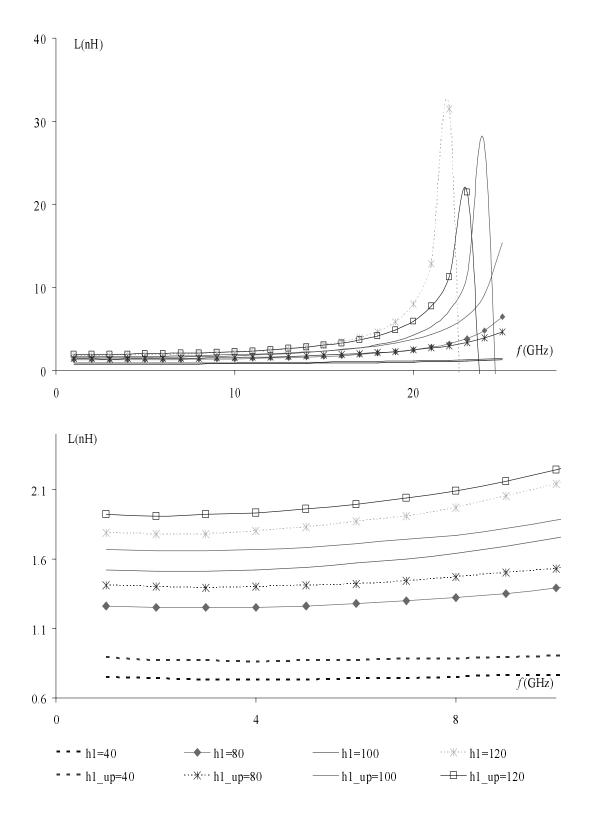

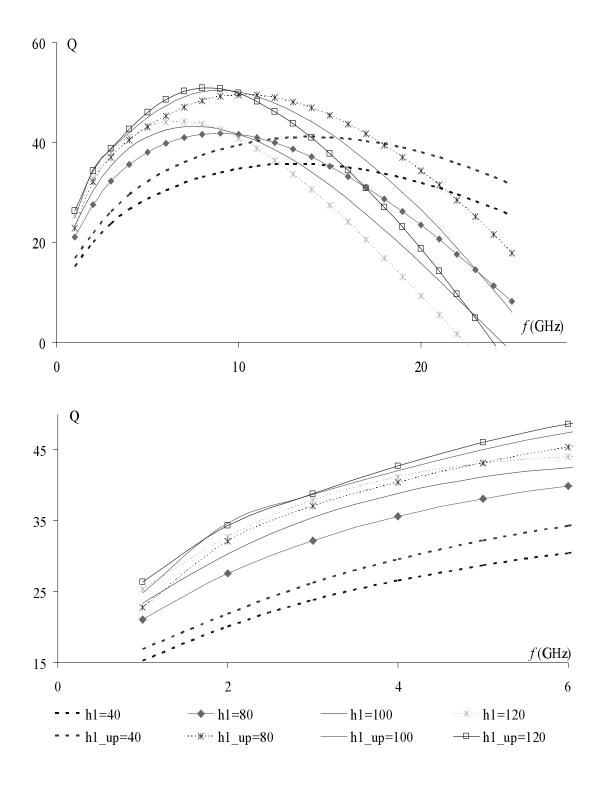

| Figure 5.9: Comparison of the inductance simulation results for $h_I$ (in the unit of      |     |

| μm) variation of solenoid inductors                                                        | 85  |

| Figure 5.10: Comparison of the $Q$ factor simulation results for $h_I$ (in the unit of     |     |

| μm) variation of solenoid inductors                                                        | 86  |

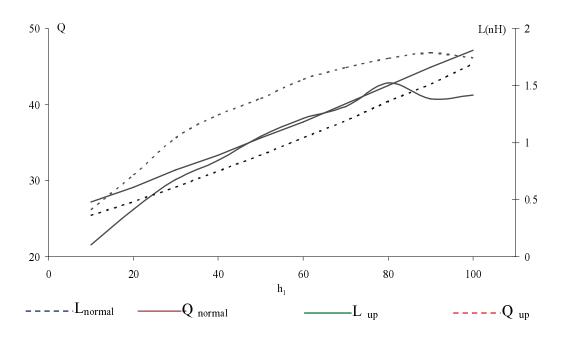

| Figure 5.11: $h_1$ parameter sweep at 9 GHz                                                | 87  |

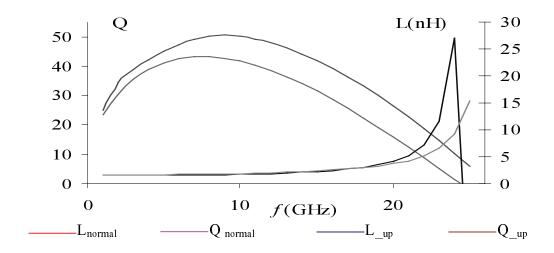

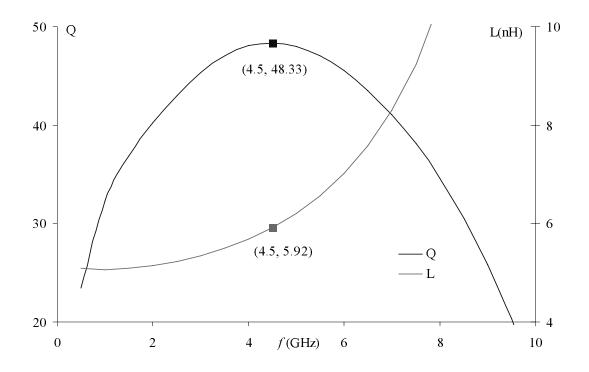

| Figure 5.12: Optimization results of designed spiral suspended inductors on                |     |

| simulated CMOS/BiCMOS substrate                                                            | 91  |

| Figure 5.13: Optimization results of designed solenoid inductors on simulated              |     |

| CMOS/BiCMOS substrate                                                                      | .91 |

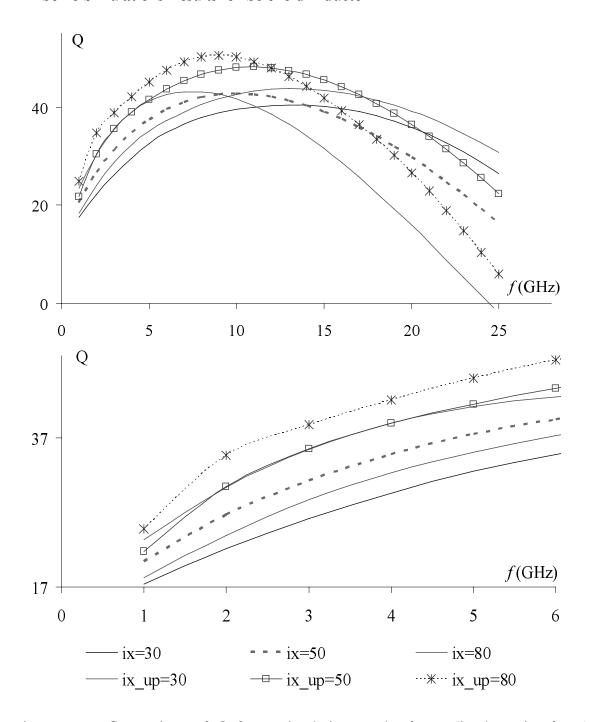

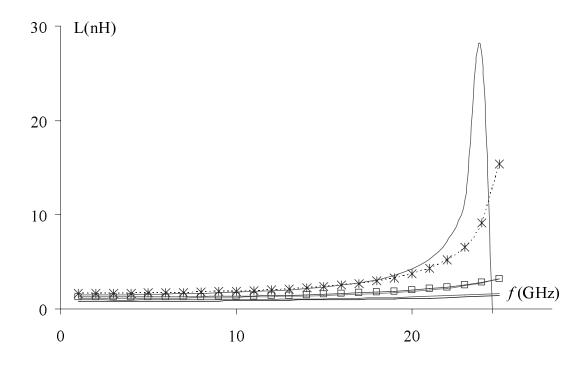

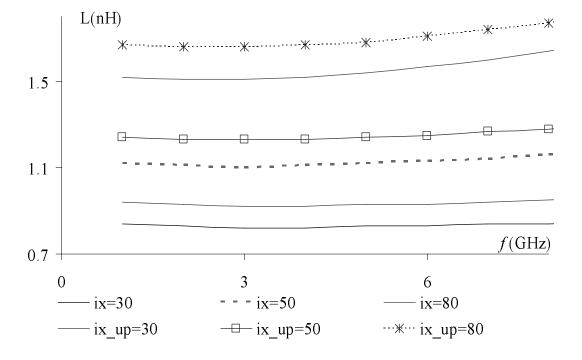

| Figure A.1: Comparison of $Q$ factor simulation results for $ix$ variations                | 03  |

| Figure A.2: Comparison of inductance simulation results for ix variations                  | l04 |

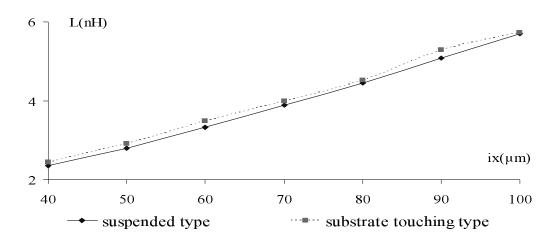

| Figure A.3: Parameter sweep of ix at 2 GHz.                                                | 105 |

| Figure A.4: Comparison of simulation results for $T = t_{SiO2}$ (in the unit of $\mu m$ )  |     |

| variations. (a) Comparisons of inductance; (b) Comparisons of $Q$ factor                   |     |

|                                                                                            | 06  |

| Figure A.5: Comparison of inductance simulation results for $s$ (in the unit of $\mu$ m)   |     |

| variations1                                                                                | 07  |

| Figure A.6: Comparison of $Q$ factor simulation results for $s$ (in the unit of $\mu$ m)   |     |

| variations1                                                                                | 08  |

| Figure A.7: S parameter sweep at 2.5 GHz.                                                  | 09  |

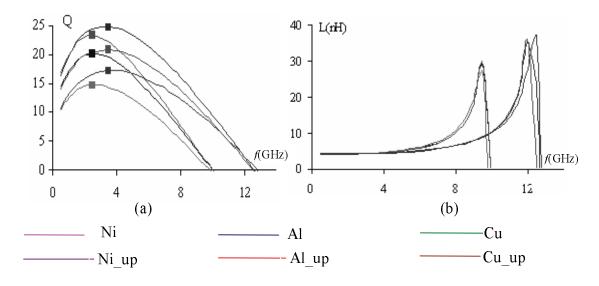

| Figure A.8: Comparison of the simulation results for spiral inductors made of              |     |

|             | different metals. (a) $Q$ comparison (b) Inductance comparison109                   |

|-------------|-------------------------------------------------------------------------------------|

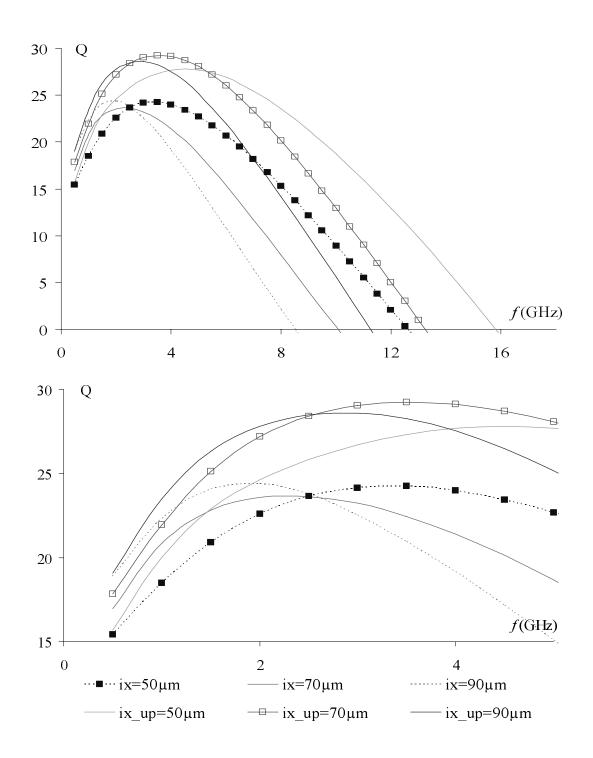

| Figure B.1: | Comparison of $Q$ factor simulation results for $ix$ (in the unit of $\mu$ m)       |

|             | variations of the solenoid inductors                                                |

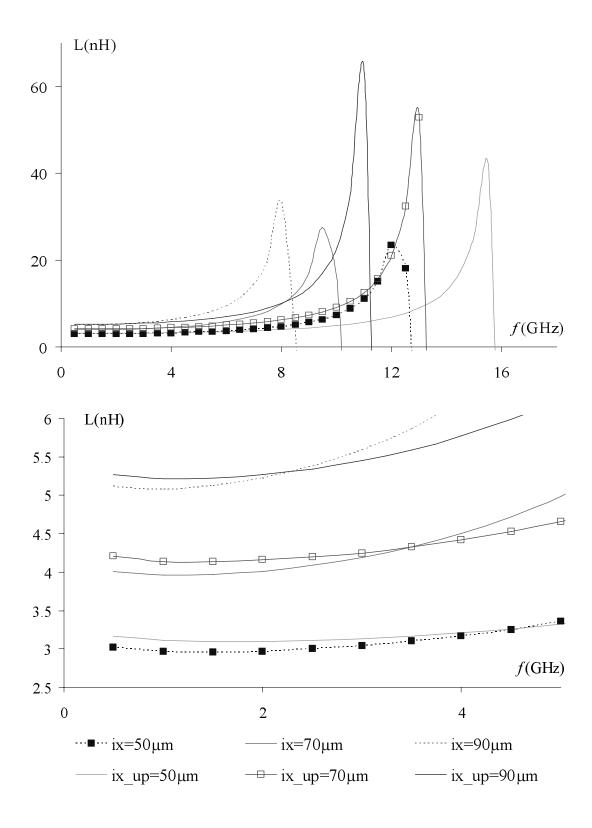

| Figure B.2: | Comparison of inductance simulation results for $ix$ (in the unit of $\mu m$ )      |

|             | variations of the solenoid inductors                                                |

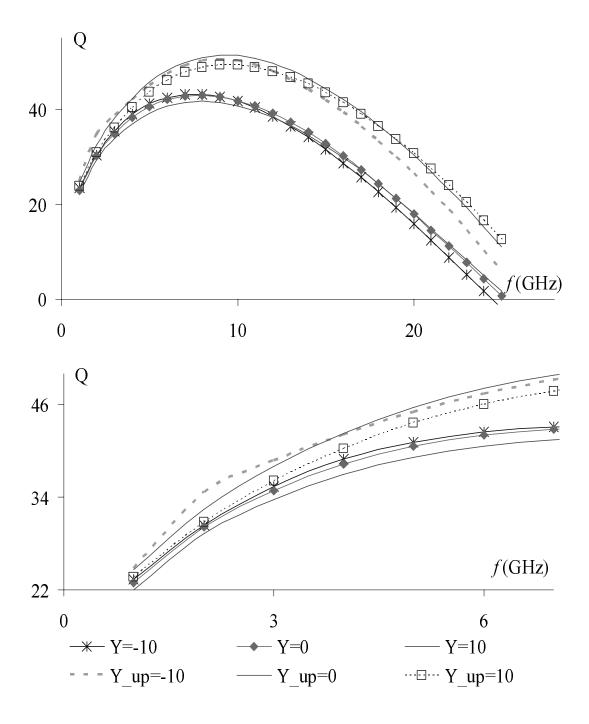

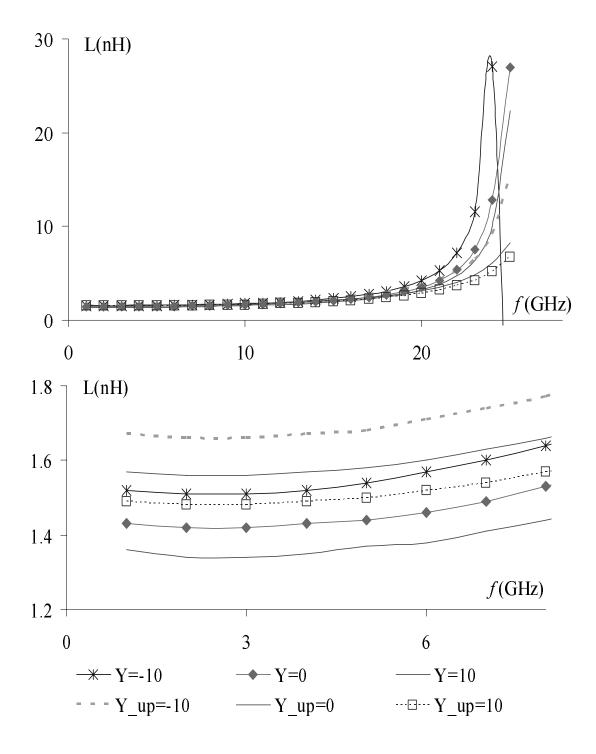

| Figure B.3: | Comparison of $Q$ factor simulation results for $Y=y_{gvari}$ (in unit of $\mu m$ ) |

|             | variations of the solenoid inductors                                                |

| Figure B.4: | Comparison of inductance simulation results for $Y=y_{gvari}$ (in the unit of       |

|             | μm) variations of the solenoid inductors                                            |

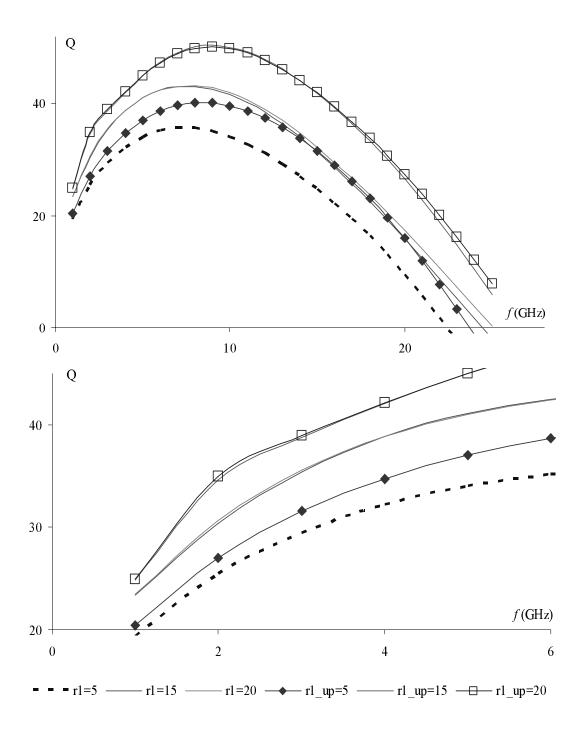

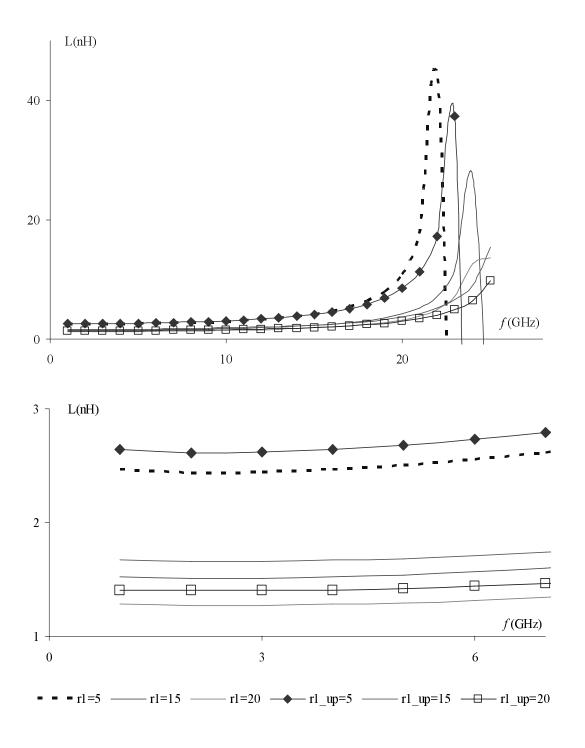

| Figure B.5: | Comparison of $Q$ factor simulation results for $r_I$ (in the unit of $\mu m$ )     |

|             | variations of the solenoid inductors                                                |

| Figure B.6: | Comparison of inductance simulation results for $r_I$ (in the unit of $\mu m$ )     |

|             | variations of the solenoid inductors                                                |

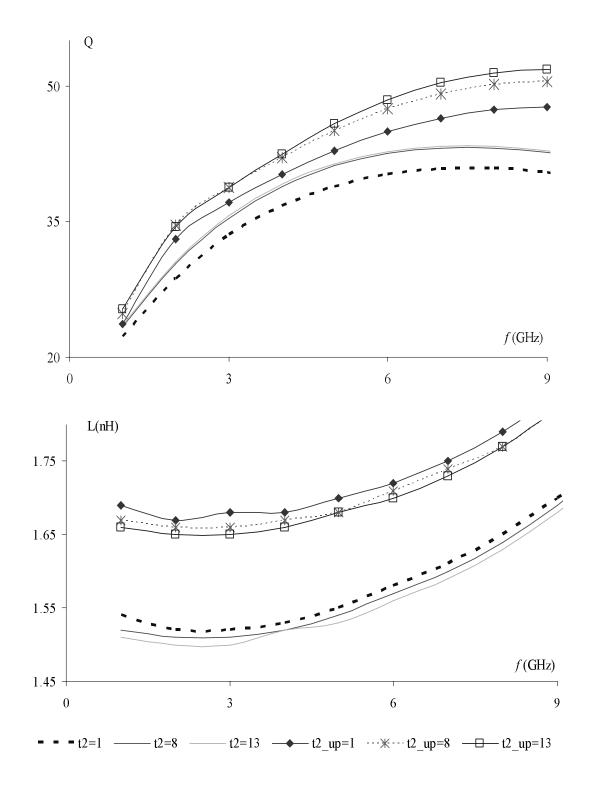

| Figure B.7: | Comparison of the simulation results for the $t_2$ (in the unit of $\mu$ m)         |

|             | variations of the solenoid inductors. (a) $Q$ factor comparisons;                   |

|             | (b) Inductance comparisons                                                          |

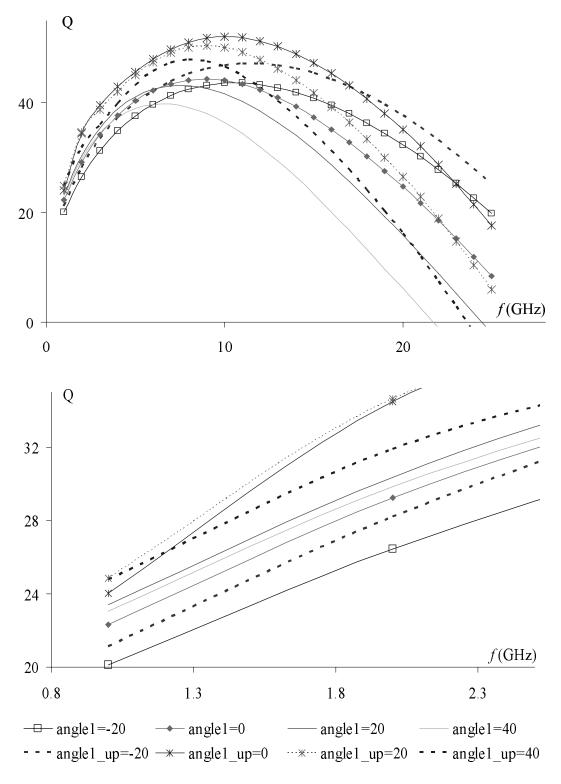

| Figure B.8: | Comparison of the Q simulation results for angle1 (in the unit of                   |

|             | degree) variation of solenoid inductors                                             |

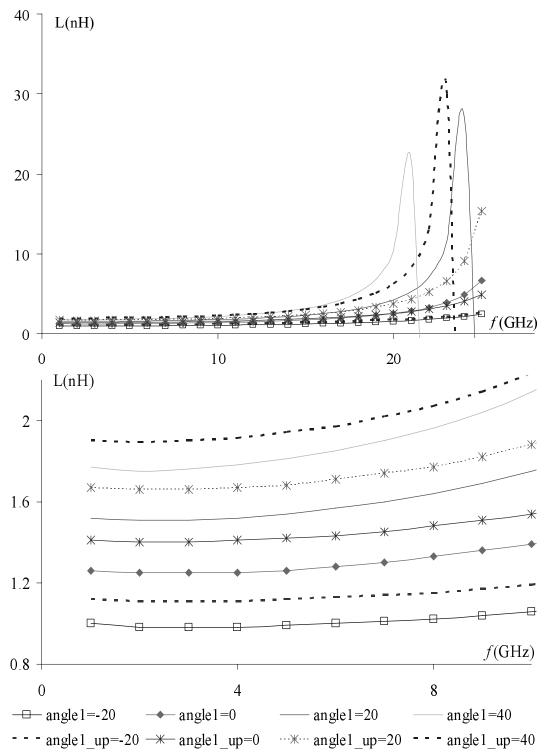

| Figure B.9: | Comparison of the inductance simulation results for angle <sub>1</sub> (in the unit |

|             | of degree) variation of solenoid inductors118                                       |

# LIST OF TABLES

| Table 5.1: | Square spiral inductor model incipient data                           | .72  |

|------------|-----------------------------------------------------------------------|------|

| Table 5.2: | The effective thickness of inductor metal trace when the metal traces |      |

|            | are 1 $\mu$ m, 3 $\mu$ m, 5 $\mu$ m, and 10 $\mu$ m                   | .77  |

| Table 5.3: | Solenoid inductor startup model data                                  | . 82 |

| Table 5.4: | List and Comparison of inductor key parameters                        | . 90 |

| Table 5.5: | Dimensions of the optimized inductors (in unit of µm)                 | .90  |

# LIST OF ABBREVIATIONS

BCB: Benzocyclobutene

BiCMOS: Bipolar Complementary Metal Oxide Semiconductor

CMOS: Complementary Metal Oxide Semiconductor

DC: Direct Current

FEM: Finite Element Method

GaAs: Gallium Arsenide

GMD: Geometric Mean Distance

GSG: Ground-Signal-Ground

HARM: High Aspect Ratio Metal

HFSS: High Frequency Structure Simulator

LIGA: German acronym for Lithography, Electroforming, and Moulding (Lithographie,

Galvanoformung, and Abformung)

LSI: Large-Scale Integrated

MEMS: Micro-Electro-Mechanical Systems

MMIC: Monolithic Microwave Integrated Circuits

Ni: Nickel

NMOS: Negative-channel Metal-Oxide Semiconductor

PDMS: Polydimethyl Siloxane

PEEC: Partial-Element-Equivalent-Circuit

PMMA: Polymethyl Methacrylate

RF: Radio Frequency

RFIC: Radio Frequency Integrated Circuits

RIE: Reactive Ion Etching

SRF: Self-Resonant Frequency

TSMC: Taiwan Semiconductor Manufacturing Company

UV: Ultraviolet

VCO: Voltage Control Oscillator

#### 1 Introduction

#### 1.1 Motivation

The boom in wireless and satellite communications in recent years has generated strongly growing demands for radio frequency integrated circuits (RFIC's) and monolithic microwave integrated circuits (MMIC's). Micro-scale inductors are playing an ever-increasing role in these circuits. Although active devices can be synthesized into an equivalent of an inductor, they usually have higher noise, distortion, and power consumption than the passive counterpart. These limitations place a severe restriction on their application. For inductors in high performance radio frequency (RF) and microwave circuits, it is often essential to use passive realizations.

In the classical radio coil, a ferrite core was used for size reduction because it can significantly strengthen the magnetic field. However, it cannot normally be applied over 1 GHz due to the high polarization losses and low permeability [1]. Soft ferromagnetic cores may be applicable in the future at high frequencies if the eddy current losses in the conductive films can be suppressed [2], [3]. Consequently, high frequency inductors are usually built with an air core, which consumes excessive chip area.

At lower RF and/or microwave (hereinafter, RF and/or microwave will be called microwave) frequencies, (ie:< 4 GHz), the use of lumped inductors greatly reduces circuit size in contrast to distributed elements. A higher density of circuits per wafer, lower cost, and higher yield can also result. Normally, micro-scale microwave inductors are built on silicon (Si), gallium arsenide (GaAs), and alumina (Al<sub>2</sub>O<sub>3</sub>) substrates. Compared with GaAs and alumina technology, which are popular for higher microwave frequencies, Si/CMOS (Complementary Metal Oxide Semiconductor) technology is a popular alternative at lower microwave frequencies as it offers low process cost and

possible integration with digital large-scale integrated (LSI) circuits. Therefore, the research of micro-scale inductors on Si substrate is significant and has been extensively conducted in recent decades. Usually, on chip passive inductors are made by conventional Si microelectronics technology. But due to the Si conductive substrate loss (eddy current loss and displacement current loss) and metal resistive loss in the inductor metal trace, they typically suffer from low quality (*Q*) factors (generally less than 10) and low self-resonant frequencies (*SRF*). Many attempts have been explored to reduce these two drawbacks. Of them, the micromachining approach has exhibited unique advantages and has already proven to be one of the leading approaches to realize inductors on Si.

Generally, there are three kinds of micromachining techniques, surface micromachining, bulk micromachining, and LIGA. They are the same techniques used to fabricate MEMS (Micro-Electro-Mechanical Systems) except the MEMS device literally includes some moving parts. Though micromachinined structures do not necessarily have moving parts, today many of these structures are loosely categorized as MEMS. The LIGA technique, a German acronym for Lithographie (deep X-ray lithography), Galvanoformung (electroforming), and Abformung (plastic molding), was first developed at the Karlsruhe Nuclear Research Center (later Research Centre Karlsruhe) in Karlsruhe, Germany [4]. LIGA is an advanced micromachining process featuring high aspect ratio, high accuracy, excellent sidewall structural quality, and potentially low cost mass production. In contrast to surface micromachining and bulk micromachining, it has advantages for building more precise, larger aspect ratio, and smaller structures. Furthermore, suspended structures can potentially be fabricated using the LIGA process because of its high aspect ratio realization property. This provides LIGA an unique advantage to potentially overcome the Si substrate loss drawback. However, the fabrication and characterization of micro-scale inductors for microwave applications using the LIGA process has not been extensively explored.

In this research, the possible integration of LIGA fabricated inductors with the Si microelectronics process, CMOS, is also considered. If passive components with high

performance cannot be fabricated on the same chip with the rest of the circuits, they must be connected externally, for instance with bonding wires. These connections introduce parasitic loss and reduce the performance of the passive component. As well, non-integrated components enlarge the volume of the whole circuitry. Direct X-ray exposure as a post-CMOS process is likely unsuitable for many CMOS chips with active circuitry due to the potential damage produced by the hard X-rays to the dielectric components of the CMOS circuits. In these situations, polymer replication and electroplating-based LIGA approaches could be viable solutions. Recently, there is some progress reported in this field [5]. An important criterion to measure the commercial value of a technique is its potential integration and performance with leading industrial techniques, in this capacity, CMOS. Therefore, it is also worthy to do some exploration by modeling the LIGA structural inductors on the simulated CMOS/BiCMOS (Bipolar Complementary Metal Oxide Semiconductor) substrate and analyze their performance and characteristics. In doing so, one can anticipate and evaluate the advantage of LIGA in possible future industrial applications combined with CMOS.

This thesis explores these issues: MEMS (Micromachining)/deep X-ray LIGA process; inductor theories and loss mechanisms; solenoid and spiral suspended inductor model designs, simulations, and performance/characteristic analysis on the simulated CMOS/BiCMOS Si substrate. Also a brief discussion of the fabrications using deep X-ray LIGA as a possible post CMOS processing step is presented.

# 1.2 Importance of Inductors in Communication Circuits

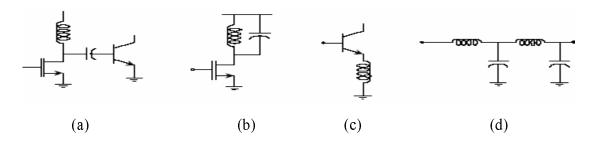

Inductors have extensive usage in wireless communications circuits. For example, the inductor is often used in resonant circuits. At sub-microwave frequencies, inductors can be realized by employing active devices, but passive inductors dominate in high frequency capacities. Several common applications of passive inductors used in Si ICs are shown as follows in Figure 1.1[6].

Figure 1.1 (a) is an impedance matching example. Through impedance matching, one can achieve, although not simultaneously, minimal noise, maximum gain, minimal reflections, and optimal efficiency. In the Figure, the input impedance of the second transistor is matched to an optimal impedance value desired by the driving transistor.

Figure 1.1 (b) shows a LC tuned load. A resistive load's frequency response is typically limited by its RC time constant. A tuned load can be used to obtain improved gain at high frequencies. The advantages of an LC passive is that it is less noisy than a resistor, consumes less voltage headroom, and obtains a larger impedance at high frequencies. A tuned load is also an essential part of oscillators.

Figure 1.1: Applications of passive inductors in Si IC building blocks. (a) Impedance matching. (b) Tuned load. (c) Emitter degeneration. (d) Filtering.

In Figure 1.1(c), an inductor is used as a series-feedback element. Series feedback can, for example, increase the input impedance, stabilize the gain, or lower the non-linearity of the amplifier. A series-feedback inductor can result in less voltage headroom, and less additional noise in contrast to a resistor. The inductance can also be used to generate real input impedance at a particular frequency, thus providing a better impedance match at the input of the amplifier.

Figure 1.1 (d) exhibits a low-pass filter realized by inductors and capacitors. Compared to active filters such as gm-C [7] or MOSFET-C filters [7], passive filters can operate at higher frequencies, have higher dynamic range due to the intrinsic linearity of the passive devices, and inject less noise while requiring no DC power to operate.

Figure 1.2: Applications of passive devices in Si IC building blocks: Distributed Amplifier

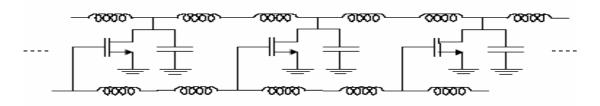

Figure 1.2 is an artificial transmission line in a section of distributed (traveling-wave) amplifier formed by inductors and capacitors. Since the LC network acts like a transmission line, it has a broadband response. A wave propagating on the gate-line is amplified and transferred onto the drain line. If the propagation velocity on the drain line matches the gate line, the signals on the drain line add in phase and the drain line delivers power to a matched load.

# 1.3 Si / CMOS Technology

Si technology is a competitive technology for realizing future microwave integrated circuits. Although GaAs offers superior gain, higher frequencies of operation, an insulating substrate, and higher Q factor realization, from the perspective of cost, CMOS is the clear winner. In addition, emerging advances in Si technology, for instance, SiGe, are closing the gap between Si and GaAs in performance in the 1–10 GHz frequency range. Si is also the best choice for integrating digital functionality in CMOS/BiCMOS technology. Thus, there is great value in integrating passive devices in CMOS technology.

The unity gain frequency of NMOS (Negative-channel Metal-Oxide Semiconductor) transistors and bipolar transistors is inversely proportional to the lateral channel length and vertical base width, respectively [8]. The vertical base width of a bipolar transistor  $W_B$  is determined by a diffusion process whereas the lateral channel length L of an MOS transistor is determined by lithographic processes. Traditionally, a diffusion process can make a shorter channel length than a lithographic process. In this case, it results in  $W_B$

shorter than L. Thereby the bipolar transistors typically exhibit advantage in speed. However, the CMOS transistor channel length has been narrowed significantly with advances in lithographic technology. Within the next decade, CMOS technology is expected to be a viable and cost-effective alternative to both bipolar and GaAs.

However, in contrast to GaAs, CMOS does suffer from the conductive loss drawback. Electromagnetic energy couples to the substrate and the lossy nature of the Si substrate limits the on chip passive Q factor severely. When the substrate is heavily conductive, magnetically induced eddy currents in the substrate can be a dominant loss mechanism. Several techniques are developing to overcome this defect. Micromachining is one of the most promising.

# 1.4 MEMS/LIGA Techniques

"Micro-Electro-Mechanical Systems". They are called MEMS mean also "Microsystems". Literally, "Micro" describes the dimensional scale; "Electro" means electricity and/or electronics; and "Mechanical" suggests moving parts of some kind. But generally, the MEMS concept is also extended to include nonmoving parts. For instance, this dissertation considers a type of nonmoving MEMS device; MEMS inductors. In recent years, RF MEMS has become an actively developing branch in the MEMS area with focus on high frequency MEMS devices and systems for RF/Microwave communications. Various high performance RF MEMS components such as RF MEMS switches, varactors, and inductors, micromachined transmission lines, high-Q resonators, filters, and antennas have been reported [9]. The inductors presented in this thesis are also in this area and operate in the frequency band from 4 GHz to 12 GHz, considerably higher than traditional CMOS based inductors which are typically limited to only a few GHz.

Normally, MEMS devices are produced using lithography-based micro-fabrication techniques, which are borrowed from the microelectronics industry and modified with specialized techniques generally called "micromachining". MEMS techniques can

typically realize more complicated microstructures with less shape/dimension restrictions than the microelectronics techniques. In addition, batch fabrication capabilities similar to the microelectronics industry provide the cost reduction potential for high volume manufacturing.

Figure 1.3: Illustration of aspect ratio

Generally speaking, there are three distinct micromachining techniques, bulk micromachining, surface micromachining, and the LIGA process. Bulk micromachining involves the removal of material from the bulk substrates, usually made of silicon, to form the desired three dimensional microstructures. In contrast, surface micromachining builds microstructure

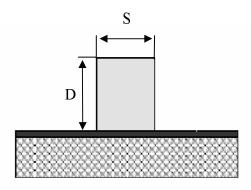

by adding materials layer by layer on top of the substrate. Both bulk micromachining and surface micromachining involve aspects borrowed from the microelectronics technology, particularly the CMOS process. In consequence, for an individual surface micromachining or bulk micromachining technique, if there is no high-temperature process involved, they can sometimes be CMOS compatible. In practice, it is sometimes advantageous for the three basic micromachining techniques to be combined together by corresponding process adjustments, and people strive for CMOS-compatible bulk micromachining or LIGA processes. The CMOS process can be regarded as a type of surface-micromaching process in essence. Thus, a CMOS compatible bulk micromachining or LIGA process implies fitting these process steps into the Si/CMOS surface micromachining process. A problem with Si based surface micromachining techniques is that they suffer from the low geometric aspect ratio limitations. Geometric aspect ratio of a microstructure is the ratio of the dimension in the depth (D) to that of the lateral surface (S), which is shown in Figure 1.3. The LIGA process overcomes this drawback.

Thanks to strong penetrating capability of X-ray radiation, deep X-ray LIGA is one of the few technologies offering high aspect ratio microstructure geometry. In contrast to UV (Ultraviolet)-LIGA, which can typically realize the vertical aspect ratios up to around 20 [10], deep X-ray LIGA can offer several hundreds [11] and with much superior sidewall structural quality. This outstanding advantage results in extremely tall and precise microstructures. Sidewall vertical slope can be better than 89.9° and with achievable sidewall roughness of 20 to 30nm, which endows the fabricated structure optical surface quality. Also the possible minimum feature size of LIGA structure can be realized as low as 0.1 µm. As a result, LIGA can potentially realize RF and microwave components with high quality and high end performance. For example, several promising high aspect ratio RF MEMS devices have already been fabricated by the TRLabs/University of Saskatchewan MEMS group, including a 2mm high millimeter wave resonator [12], vertical cantilever MEMS variable capacitors [13], and broadband coupled line couplers [14]. In this research, increasing suspended structures to an unprecedented height might mean that the parasitic electromagnetic coupling to the substrate could be almost removed, providing the mechanical robustness permits.

LIGA is a low temperature polymer process. This feature provides LIGA potential compatibility with the CMOS process. Recently, several efforts were made for the integration of LIGA microstructures onto CMOS wafers/chips with the use of Polymethyl Methacrylate (PMMA) or Polydimethyl Siloxane (PDMS) pattern transfer process and molding techniques [5], [15]. One can rationally anticipate that in the near future, a mature CMOS compatible LIGA process could be a reality.

## 1.5 Research Objectives

The purpose of this research is to explore some advantages of deep X-ray LIGA technology to microwave passive inductor fabrication on the Si substrate. Two kinds of inductors, a square spiral type and a solenoid type, are proposed with structural features considered compatible with typical LIGA processing. The Si substrate situations are set up based on the CMOS/BiCMOS substrate characteristics, thereby exploring the

possibly CMOS compatible LIGA inductor situations. If one can verify LIGA fabricated inductors also exhibit improved RF performance in the simulated CMOS/BiCMOS environment, the value and advantage of LIGA is strengthened. The working frequency band of interest for the investigated inductors in this capacity is from 4 GHz to 12 GHz. Three key parameters of inductors, namely, quality (Q) factor, self resonant frequency (SRF), and inductance (L), are focused on. This dissertation mainly engages software designs, simulations, and analyses of the inductors using Ansoft HFSS<sup>TM</sup> (version 9.1).

In order to realize the overall goal, the following specific objectives are considered:

- 1. To further investigate the advantage of LIGA processing, some analysis schemes are considered: for the spiral inductor, two structures, one suspended at 150 μm height, the other touching the substrate for comparison, are developed and investigated. These architectures are particularly well suited for LIGA due to the vertical heights involved, and especially the unprecedented suspension height. For the solenoid inductor, two kinds of structures, one suspended at 150μm, the other touching the substrate are also investigated. Due to the high aspect ratios and non-ninety degree geometrics required, such structures cannot likely be built using surface or bulk micromachining techniques, but are possible using LIGA. Various geometric and physical parameter simulations are conducted for these four structures, in an attempt to reveal LIGA advantages over other MEMS techniques.

- 2. Optimizing the inductor characteristics, namely, optimizing the *Q* factors of the inductors and trying to enlarge them as big as possible, and thereby the working frequencies as high as possible. The Si substrate models are limited to one conductive case, CMOS/BiCMOS standard substrate. If one can achieve excellent performance using LIGA under this condition, the value of integrating LIGA with CMOS for these applications is further justified.

#### 1.6 Thesis Outline

This thesis comprises the following chapters:

Chapter 2 first demonstrates general deep X-ray LIGA processes and the recent progresses in integrating the LIGA process with the CMOS technique. Then the electromagnetic mechanisms and lumped equivalent circuits of the air core spiral inductors and solenoid inductors are discussed. The discussion is focused on some key parameters, Q factor, Self Resonant Frequency (SRF), and inductance.

Chapter 3 presents various published inductor layouts. The previous works in microscale inductors are briefly reviewed, especially the recent progress in MEMS inductor design.

Chapter 4 describes the fundamental working principle of the high frequency simulation tool, Ansoft HFSS<sup>TM</sup>. Then the basic design procedures and considerations for the simulation inductor models in terms of HFSS<sup>TM</sup> environment are explained. Finally, the potential of building LIGA structural inductor on CMOS/BiCMOS substrate are briefly discussed.

Chapter 5 gives the discussions, comparisons, and analysis of the simulation and optimization results.

Chapter 6 concludes this dissertation and describes the possible future work.

# 2 Principle of LIGA Process and On Silicon Inductor Theory

## 2.1 Principle of LIGA Fabrication Process

In Chapter 1, the LIGA technique has been briefly introduced. It is necessary to extend this topic in more detail to discuss the subsequent model designs. In the LIGA process, X-rays are used as the lithographic light source because of their short wavelength, which offers higher penetration power into the photoresist materials. The X-rays come from a synchrotron radiation source, which provides high intensity in the hard X-ray spectrum. The short wavelength also allows for high resolution in lithography, at line width of 0.2µm or even possibly lower, and high aspect ratio.

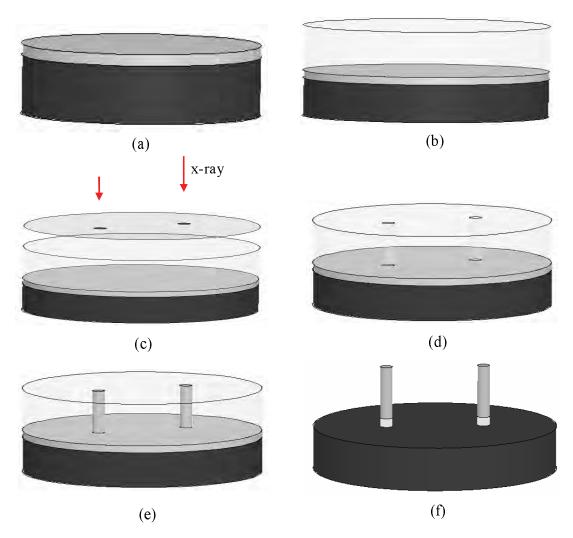

The general process steps are illustrated in Figure 2.1 for producing isolated metal structures on a substrate. The process begins from step (a) by applying a thin metal film layer on the substrate. It is called a "seed layer" and acts as the cathode attracting metal ions to the substrate during electroplating. Then, in step (b), a thick film of X-ray sensitive photoresist is deposited on the surface of the substrate. Often, the employed photoresist is polymethylmethacrylate (PMMA), but other resists are also used. After that, in step (c), the photoresist covered substrate is exposed to the high energy X-ray radiation through a patterned mask. Masking materials, for examples, SiC and Si<sub>3</sub>N<sub>4</sub>, are transparent to X-rays. A relatively thick film of gold is patterned on the membrane to absorb X-ray transmission and provide the contrast for patterning. X-ray absorption alters the resist chemistry and allows the exposed area to be dissolved in the subsequent development of the photoresist material (see step (d)). After photoresist development, the ensuing three-dimensional photoresist structure is filled with electroplated metal (see step (e)) and the photoresist is subsequently removed via X-ray flood irradiation followed by secondary development to generate a freestanding metal structure. Finally, the seed layer is etched away, typically with hydrofluoric acid and possibly reactive ion etching (RIE) to electrically isolate metal conductors (see step (f)). The demonstrated processes in Figure 2.1 represent direct X-ray lithography and typically produce best structure quality. When considering mass production and cost reduction, the complete LIGA process can be used to produce structures by hot embossing, injection molding, or pattern transfer, at possibly reduced structural quality.

Figure 2.1: LIGA process steps (a) Application of seed layer on substrate; b) Application of photoresist; c) X-ray exposure (lithography); d) Photoresist development after lithography; e) Metal electroplating; f) Removal of photoresist and seed layer

Figure 2.2: LIGA Process with Replication by Hot Embossing: a) Metal overplating into X-ray patterned photoresist; b) Release of metal mold insert; c) Hot embossing; d) Plastic mold; e) Secondary metal deposition; f) Final metal structure

Hot embossing is a mechanical technique and has been transplanted to microstructure fabrication. The summarized hot embossing procedure is illustrated in Figure 2.2 [16]. First, in step (a) and (b), a metal mould insert is created using a process similar to that shown in Figure 2.1, but during the electroplating process, the metal is deliberately overplated to form a metal bridge connecting the metal fillings. This step is called "over plating". Then in step (c), in a controlled temperature and pressure environment, an outside force applied on the metal mould insert forces it into softened plastic applied on a substrate to create the shape complimentary to the mould insert (also in this case, the

substrate has been applied with a thin layer of metal seed since final metal structures are desired). When the metal mould insert is removed, the plastic structures illustrated in step (d) result (in reality there may be a thin plastic layer on the substrate which could require further etching). Finally, a second electroplating is conducted in the created plastic mould (step (e)). This is also called "secondary metal definition". This step is performed in the context of fabricating metal parts and may not be necessary in other cases. Finally, the plastic and seed layers are stripped to obtain the final microstructure. The LIGA replication techniques allow relatively inexpensive fabrication of parts precisely replicating the shape and size of the original X-ray-patterned part.

Currently, most developed LIGA processes use Nickel (Ni) as the metal material. Ni has good mechanical structural properties, including low internal stress during electroplating of tall structures. Copper, which is a better electrical conductor, is also being developed at for instance, Sandia National Lab, USA, but is less mature. Because copper is common in the CMOS process, in order to explore the advantage of the possible combination between LIGA and CMOS, in most of the simulation and analysis occasions, copper is used as the objective metal.

A pattern transfer technique for the post-IC integration of LIGA microstructures onto CMOS chips has been proposed [5]. Figure 2.3 shows a simplified pattern transfer process flow for the integration of a LIGA HARM (high aspect ratio metal) onto a CMOS chip using PDMS replication and CMOS-compatible electroplating techniques. The process starts with a Ni master mold, in this case, an array of cylindrical posts, on a stainless steel substrate (step (a)). Then the corresponding PDMS mold can be achieved using various techniques such as embossing and molding, which is shown in (step (b)). While the PDMS mold is being fabricated, the test chip is being attached on a Si wafer and then a metal seed layer is being deposited atop. To fasten the LIGA HARM onto the test chip, an adhesive polyamide layer at 3 µm must be spin-coated between the test chip and the PDMS mold during the process. Then in step (c), the generated PDMS mold is trimmed into a smaller piece and aligned/attached to the test chip under the contact aligner. After that, the plasma etching has been continually carried out to remove the

adhesive PI layer to expose the seed layer for electroplating [17]. Subsequently, the electroplating is conducted to create metallic HARM on the testing circuit chip. Finally, after removing PDMS mold, adhesive PI layer, and the seed layer using different etching processes, the transferred metallic microstructure is generated (step (d)).

Figure 2.3: The process flow for the pattern transfer of a LIGA HARM [5]: (a) LIGA – processed metallic master mold; (b) The replicated PDMS mold; (c) PDMS mold on a Si circuit chip with metallic seed layer and adhesive PI layer; (d) The on chip transferred LIGA HARM.

This pattern transfer process has already been applied to air-suspended spiral copper inductor fabrications in the lab environment [5]. The metallic master mold in this capacity is a double-layered structure with 45 µm thick coil structures at the bottom and 45 µm thick via structures on top, which can be generated using multi-exposure LIGA process (see section 3.2.2). Accordingly, a double-layered PDMS mold is generated. After the replicated PDMS is attached to the test chip, two steps of electroplating are needed to be conducted. The first step is to fill up the bottom trenches for via posts.

After that, a second seed layer is deposited in the top PDMS trenches, and the unnecessary seed layer on the top PDMS surface should be removed. Then the second step electroplating is carried out to fill up the top trenches of the PDMS mold to generate the copper coil structures. The simplified process sequence is shown in Figure 2.4.

Figure 2.4. The PDMS-based pattern transfer process sequence for a spiral inductor [5]: (a) Spin-coating of PDMS; (b) Peeled-off PDMS; (c) PDMS mold on a CMOS circuit chip with bottom electrodes, metallic seed layer, and adhesive PI layer; (d) Transferred metallic inductor on a chip.

# 2.2 Inductor Principle

Inductors store magnetic energy. The self inductance originates from the current in the inductor. According to one of Maxwell's Equation (equation 2.1a), electrical current or changing electric field induces the magnetic field. Any change in a current also induces the change in the generated magnetic field.

$$\nabla \times \overset{\mathbf{\rho}}{H} = \overset{\mathbf{\rho}}{J} + \frac{\partial \overset{\mathbf{b}}{D}}{\partial t}$$

(2.1a)

$$D = \varepsilon E \qquad (2.1b)$$

$$B = \mu H \qquad (2.1c)$$

where H is the magnetic field intensity, J is the free current density, D is the electric flux density, E is the electric field intensity, E is the magnetic flux density, E is the permittivity, and E is the permeability. Considering an arbitrary closed-circuit formed by conductors as shown in Figure 2.5 (a), the magnetic flux of this circuit is defined as the magnetic field crossing the cross-sectional area of the circuit

$$\psi = \oint_{S} \stackrel{\omega}{\partial S} \cdot dS \qquad (2.2)$$

The origin of the magnetic field  $\stackrel{\omega}{B}$  comes from the circuit itself since there is no other current surrounding. Thus, the self-inductance of the closed conductor can be defined as

$$L = \frac{\psi}{I} \tag{2.3}$$

Figure 2.5: (a) An independent current loop (b) A magnetically coupled pair of loops. Current only exists in loop *j*

where I is the current flowing in the conductor. Now we consider two closed conductor loops in Figure 2.5 (b). Assuming there is current flowing in loop j and we measure the impinging flux from j to loop i, the mutual inductance can be defined as

$$M_{ij} = \frac{\psi_i}{I_j} \tag{2.4}$$

where

$$\psi_i = \oint_{S_i} \overset{\omega}{B_i} \cdot d\overset{\omega}{S} \tag{2.5}$$

and from Faraday's Law, the voltage induced on a loop is related to the flux

$$V = \frac{d\psi}{dt} = L\frac{dI}{dt} \ . \tag{2.6}$$

The magnetic energy stored by the inductor is given as follows

$$W_{m} = \frac{1}{2}LI^{2} \tag{2.7}$$

and the total magnetic energy stored in a physical inductor can also be calculated as [18]

$$W_{m} = \frac{1}{2} \int_{V} \overset{\varpi}{B} \cdot \overset{\varpi}{H} dV \tag{2.8}$$

where V is the volume of interest. By equating the equation (2.7) and (2.8), one can obtain the inductance.

The general equation for an arbitrary geometry inductor can be expressed as

$$L_T = L_O + \sum M \tag{2.9}$$

Where  $L_o$  is the self inductance, and the  $\sum M$  is the totaling of mutual inductances.

# 2.3 Quality Factor of the Inductor

Generally speaking, the complex power delivered to a conductor at the frequency  $\omega$ , P, is [18]

$$P = \frac{1}{2} \oint_{S} \overset{\varpi}{E} \times \overset{\varpi}{H}^{*} \cdot d\overset{\varpi}{S} = P_{l} + 2j\omega (W_{m} - W_{e})$$

(2.10)

where  $P_e$  is the average power dissipated by the conductor. As well,  $W_m$  and  $W_e$  represent the time average of the stored magnetic and electric energy, respectively. The input impedance can thus be given as follows [18]

$$Z_{in} = R + jX = \frac{V}{I} = \frac{VI^*}{|I|^2} = \frac{P}{\frac{1}{2}|I|^2} = \frac{P_I + 2j\omega(W_m - W_e)}{\frac{1}{2}|I|^2}$$

(2.11)

If  $W_m > W_{e}$ , the device is inductive, i.e., an inductor.

Quality factor (Q) is a key parameter to passive devices. The Q is defined as [19]

$$Q = 2\pi \cdot \frac{energy \ stored}{energy \ loss \ in \ one \ oscillation \ cycle}$$

(2.12)

Actually, equation (2.12) applies to all the passive devices. But the exact meanings for different devices are subtly different. For a LC tank, the energy stored is the sum of the average magnetic and electric energies. The energy stored in a (lossless) LC tank is a constant and oscillates between magnetic and electric forms. It is also equal to the peak magnetic energy, or the peak electric energy. For a lossless LC tank, Q is infinite. In contrast, for an inductor, according to its definition, only the magnetic energy is of interest. Any stored electric energy arising from the inevitable parasitic capacitances in a real inductor is counterproductive. Therefore, the inductor Q is proportional to the net magnetic energy stored, which is equal to the difference between the peak magnetic and electric energies and given as

$$Q = 2\pi \cdot \frac{peak \ magnetic \ energy - peak \ electric \ energy}{energy \ loss \ in \ one \ oscillation \ cycle} = 2 \cdot \omega \cdot \frac{(W_m - W_e)}{P_l}$$

(2.13)

When self-resonance occurs, the peak magnetic and electric energies are equal. At this point, Q vanishes. Above the self-resonant frequency, Q becomes negative because the net capacitive energy emerges after the balance between the peak magnetic and electric energies.

# 2.4 Physical Lumped Equivalent Model and Loss Mechanism

# 2.4.1 On Silicon Spiral Inductor Lumped Model and Loss Mechanism

Most of the applicable spiral inductors are square inductors since the photolithographic masks for orthogonal or circular inductors are harder to generate. However, for a circular coil, the required conductor length is shorter for achieving the given inductance value. In consequence, the parasitic resistance and capacitance of the Si substrate are comparably smaller, which results in the higher  $Q_{max}$ . In this dissertation, the focus is on square inductor designs due to the above practical constraint.

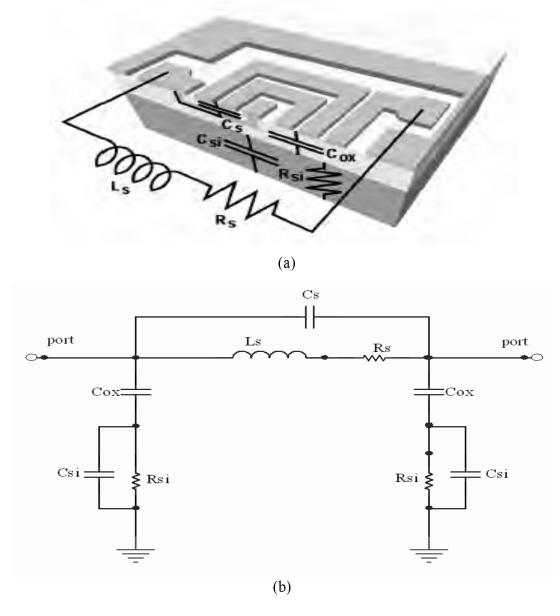

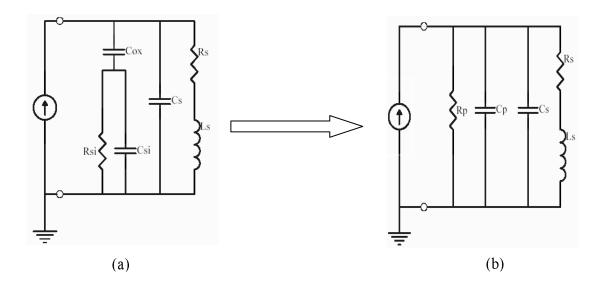

Since the inductor is to store magnetic energy only, the inevitable resistance and capacitance in an inductor are considered parasitics. The parasitic resistances dissipate energy through ohmic loss while the parasitic capacitances store electric energy. Compared with full electromagnetic field analysis, for instance, as performed by  $HFSS^{TM}$  [20], or other partial-element-equivalent-circuit (PEEC) based solvers, a lumped equivalent circuit model dramatically reduces analysis complexity. The lumpedelement model of a spiral inductor on silicon [21] is shown in Figure 2.6. It has been extensively used and quoted nowadays because of its simplicity and explicitness. Although from the accuracy viewpoint, it cannot replace HFSS and PEEC methods in simulations, it is more straight-forward for the qualitative theoretical analysis. The electrical characteristics of the spiral coil and the underpass are represented by the inductance  $L_s$ , the series resistance  $R_s$ , and the  $C_s$ , which is the combination of the interwire capacitive coupling and the overlap capacitive coupling between the spiral and the underpass. The resistance  $R_s$  is frequency-dependant due to the skin effect and the proximity effect. The skin effect depicts an increased current density near the conductor surface arising from an internal magnetic field generated by the original high frequency current. As a contrast, the proximity effect describes the changes in current density

induced by the magnetic field from neighbouring conductors. Skin effect and proximity effect are additive and cannot easily be distinguished. These two effects are also called current crowding effects. High frequency leakage current effect from the spiral to the silicon substrate is modeled by the oxide capacitance  $C_{ox}$ . The parasitic capacitance and resistance of the silicon substrate are modeled by  $C_{si}$  and  $R_{si}$  (the slight asymmetry between the two ports due to the presence of the return underpass has been neglected).

Figure 2.6: (a) 3-D view of a spiral inductor; (b) Lumped-element equivalent model of a spiral inductor [21]

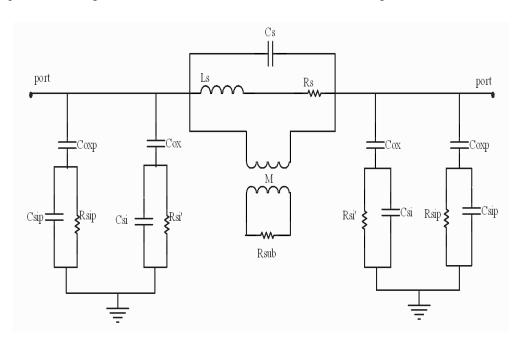

Note that the substrate is assumed grounded and it is also modeled in Figure 2.6. There are eddy currents in the substrate providing the substrate resistivity is low, as in the case of Si. They create a magnetic field to weaken the original field of the inductor coil. Consequently, the inductance  $L_s$  is reduced. In the author's opinion, the lumped model in Figure 2.6 can be improved into the lumped model in Figure 2.7. The inductance  $L_s$  is weakened due to the parasitic transformer M. The substrate loss is modeled by two  $R_{si}$ . two  $R_{sip}$ , and one  $R_{sub}$ . The substrate capacitive parasitics is modeled by two  $C_{ox}$ , two  $C_{sip}$ , two  $C_{si}$ , and two  $C_{oxp}$ . Among them, the  $C_s$ ,  $L_s$ , and  $R_s$  represent the intrinsic inductor. The two  $C_{oxp}$ , two  $C_{sip}$ , and two  $R_{sip}$  model the port distributed effects. In contrast to other components in Figure 2.7, the port modeled components are very small due to their comparably tiny physical size and thus can be ignored. To the author's knowledge, the mechanisms of M and  $R_{sub}$  have rarely been deeply investigated to date, and moreover, the transformer effect is very weak compared with  $L_s$ . In this thesis, the model in Figure 2.6 is sufficient for qualitative analysis and understanding of the effects later demonstrated using full 3D EM simulations. The influence of  $R_{sub}$  and two  $R_{si}$  are included in the two  $R_{si}$  in the Figure 2.6 model. The individual lumped model components in Figure 2.6 are further described in the following sections.

Figure 2.7: Lumped-element equivalent model of a spiral inductor with extra elements

### Series Inductance $L_{\rm s}$

As mentioned in Section 2.2, the general inductance of the inductor consists of the self inductance of the coil and all mutual inductances between pairs of conductors. The spiral inductance analysis can start from elementary single and two wire sections. The total inductance of the spiral is the sum of the self and mutual inductances of the wires that comprise it. An approximation for the DC (Direct Current) self inductance for a thin film straight conductor with rectangular cross-section is given by Greenhouse [22]

$$L = 0.002 \cdot l \cdot \left[ \ln \left( \frac{2 \cdot l}{a + b} \right) + 0.50049 + \frac{(a + b)}{3 \cdot l} \right]$$

(2.14)

where L is the inductance in micro henries; I is the conductor length in centimetres; a and b are the rectangular dimensions of the cross-section of the conductor.

The mutual inductance between two parallel wires is a function of the length of the conductors and of the *GMD* (Geometric Mean Distance) between them. It can be denoted as

$$M = 2lC (2.15)$$

where M is the mutual inductance in nanohenries (nH), I is the wire length in centimetres (cm), and C is the mutual inductance parameter, which is expressed as [22]

$$C = \ln \left[ \frac{l}{GMD} + \sqrt{1 + \left(\frac{l}{GMD}\right)^2} \right] - \sqrt{1 + \left(\frac{GMD}{l}\right)^2} + \frac{GMD}{l}, \qquad (2.16 \text{ a})$$

where GMD can be calculated using

$$\ln GMD = \ln D - \frac{W^2}{12D^2} - \frac{W^4}{60D^4} - \frac{W^6}{168D^6} - \frac{W^8}{360D^8} - \frac{W^{10}}{660D^{10}} - \cdots$$

(2.16b)

and W and D are the wire width and pitch in cm, respectively. Actually, GMD can be approximated as the pitch of the inductor wires [22], which is shown in Figure 2.8. The relationship between the self and mutual inductance is given as follows [21]

$$M = k\sqrt{L_1 L_2} \tag{2.17}$$

where  $L_1$  and  $L_2$  are the self inductances of the two wires, and k is the mutual coupling coefficient. Narrower space enlarges the mutual inductance since the magnetic coupling is enhanced. Also the metal thickness influences the inductance value.

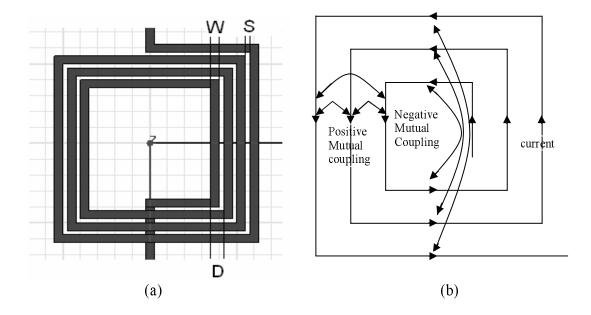

Figure 2.8: (a) Spacing S, line width W, and line pitch D=S+W of a spiral inductor; (b) Positive and negative mutual coupling illustration in a spiral inductor

Greenhouse developed a good method to estimate the planar rectangular spiral inductance [22]. The overall coil inductance is expressed in Equation (2.18) and demonstrated in Figure 2.8 (b).

$$L_S = L_O + \sum M_{+} - \sum M_{-} \tag{2.18}$$

Briefly speaking, it is equal to the summation of self inductance of each wire segment and the positive and negative mutual inductances between all possible wire segment pairs. The mutual inductance between two wires depends on their angle of intersection, length, and separation. Two mutually perpendicular wires have no mutual inductance because of the magnetic flux uncoupling. The mutual inductance is positive if the currents in the two wires are in the same direction and negative conversely.

#### Series Resistance $R_s$

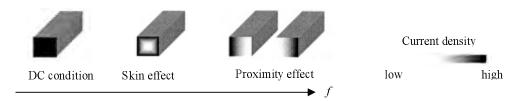

When the inductor operates at high frequencies, due to skin effect and proximity effect, the current density in its metal wire is non-uniform along the width and thickness of the conductors (see Figure 2.9). Note that Figure 2.9 is just a conceptual demonstration. The practical distribution of the eddy currents depends on the geometry of the conductor and its orientation to the actuating time-varying magnetic field. Therefore, it is not as simple as the figures shown in Figure 2.9.

Figure 2.9: Illustration of skin effect and proximity effect in terms of straight wires with rectangular cross-section

Because the spiral inductor has a multi-conductor structure, eddy currents can potentially be caused by both proximity and skin effects. Eddy current losses contribute to the ohmic losses. Skin effect is from the magnetic field of the metal trace, whereas the proximity effect arises from the magnetic fields of nearby conductors. The proximity effect also contributes to the current distribution in a conductor, leading to the strongest magnetic field in the innermost turn of the spiral. The eddy currents resulting from the skin effect and the proximity effect induce their own magnetic field to weaken the original field. Therefore, the eddy currents reduce the net current flow in the conductor and hence increase the total resistance, pushing current to the outer layers ("skin") of the conductors. A parameter called skin depth  $(\delta)$  is crucially related to this phenomenon. It describes the "depth of penetration", the degree of penetration by the electric current/field and magnetic flux into the surface of a conductor at high frequencies. The magnitude of the fields and the current decrease exponentially with penetration into the conductor, and  $\delta$  has the significance of the depth at which the fields and current have decreased to 1/e (about 36.9%) of their values at the surface [18]. As well, the phases of the current and fields lag behind their surface counterparts by  $x/\delta$  radian at the depth x into the conductor [18]. The severity of the eddy current effect is determined by the ratio

of skin depth to the conductor thickness. The eddy current effect is negligible only if the skin depth is much greater than the conductor thickness. Normally, the skin depth is defined as [18]

$$\delta = \sqrt{\frac{\rho}{\pi \mu f}} = \sqrt{\frac{2}{\omega \mu \sigma}} \tag{2.19}$$

where  $\rho$ ,  $\mu$ ,  $\omega$ ,  $\sigma$  and f denote the resistivity of the conductor in ohm·m, permeability in H/m, angular frequency of the signal in the conductor in rad/s, conductivity of the conductor in Siemens/m, and frequency in Hz, respectively.

From the above discussion, one can see the current distribution inside a spiral inductor is complicated and non-uniform, even for a single trace segment (see Figure 5.3). In contrast to skin effect, the proximity effect inside the spiral inductor is very small and is often ignored in lumped modeling [21]. Also, the wire segments can be treated as microstrip transmission lines. For the spiral inductor case, the current at high frequencies concentrates to one surface of the wire [21]. Based on these assumptions, one can see the current gradient resulting from the skin effect is in the direction away from the surface. Thus, the current density (J in  $A/m^2$ ), which is simplified to attenuate as a function of the distance (x) away from the inductor metal surface, can be roughly expressed as

$$J = J_O \cdot e^{-x/\delta} \tag{2.20}$$

Where  $J_o$  is the current density on the surface. The current (I in Ampere) is equal to the integration of J over the wire cross-sectional area. Since J only changes in the x direction, I can be calculated as

$$I = \int J \cdot dA = \int_0^t J_o \cdot e^{-x/\delta} \cdot w \cdot dx = J_o \cdot w \cdot \delta \cdot (1 - e^{-t/\delta})$$

(2.21)

where t denotes the thickness of the wire, and w is the wire width. From (2.21), the effective thickness,  $t_{eff}$ , can be defined as

$$t_{eff} = \delta \cdot (1 - e^{-t/\delta}) \tag{2.22}$$

In consequence, the series resistance  $R_s$ , can be approximated as

$$R_{S} = \frac{\rho \cdot l}{w \cdot t_{eff}} = \frac{\rho \cdot l}{w \cdot \delta \cdot (1 - e^{-t/\delta})}$$

(2.23)

where  $\rho$  and l represent the resistivity and length of the wire.

# Parallel Capacitance C<sub>s</sub>

The parasitic capacitive coupling between input and output ports of the inductor includes the cross-talk between adjacent turns and the overlaps between the spiral and underpass. This parasitic parallel capacitance can be modeled as  $C_s$  it allows the signal to flow directly from the input to output port without passing the inductor wires. Since the crosstalk capacitances can be reduced by increasing the gap between the turns, and the adjacent turns are almost equi-potential, the effect of the crosstalk capacitances can be negligible. In contrast, because of the larger potential difference between the spiral and the underpass [23], [24], the  $C_s$  is mostly contributed by the overlap capacitances. Practically, in most cases,  $C_s$  can be modeled as the sum of all overlap capacitances, which is

$$C_S = n \cdot w^2 \cdot \frac{\varepsilon_{ox}}{t_{oxM1-M2}}$$

(2.24)

where n is the number of overlaps, w is the spiral line width,  $\varepsilon_{ox}$  is the oxide dielectric permittivity, and  $t_{oxM1-M2}$  is the oxide thickness between the spiral and the underpass.

#### **Substrate Parasitics and Losses**

As shown in Figure 2.6, the characteristics of the spiral inductor structures on oxide on silicon can be modeled by a three-element network consisting of  $C_{ox}$ ,  $R_{si}$ , and  $C_{si}$ . The physical origin of  $R_{si}$  is the silicon conductivity which is mainly determined by the majority carrier concentration.  $C_{ox}$  and  $C_{si}$  model the oxide capacitance and the parasitic

capacitive effects, respectively, arising from the silicon semiconductor at high frequencies.  $C_{ox}$  is the oxide capacitance between the inductor metal traces and the substrate, whereas  $C_{si}$  represents the high frequency capacitive effects inside the substrate. Usually the substrate is tied to ground through vias to metallization that is grounded externally (off-chip). Ultimately speaking, at RF and microwave frequencies, the resistance and the finite response time of the substrate to the applied fields cause the potential throughout the substrate to exhibit a non-uniform distribution relative to the external ground applied to the circuits. This results in  $C_{si}$ . The lateral dimensions of a spiral inductor are normally comparable to the silicon substrate thickness and are much larger than the oxide thickness. The substrate capacitance and resistance are approximately proportional to the area occupied by the inductor and can be roughly expressed as

$$C_{ox} = \frac{1}{2} \cdot l \cdot w \cdot \frac{\varepsilon_{ox}}{t_{ox}}$$

(2.25)

$$C_{si} = \frac{1}{2} \cdot l \cdot w \cdot C_{sub} \tag{2.26}$$

$$R_{si} = \frac{2}{I \cdot w \cdot G_{sub}} \tag{2.27}$$

where  $C_{sub}$  and  $G_{sub}$  are the capacitance and conductance per unit area for the silicon substrate. The area of the spiral is equal to the product of the spiral length (I) and width (W). Because the substrate parasitics are assumed to be distributed equally at the two ends of the inductor, Equations (2.25)-(2.27) need to have a factor of two accounting for this concern.  $C_{sub}$  and  $G_{sub}$  are substrate doping dependant and extracted from measurement results. They do not vary significantly over the substrate if the substrate is uniformly doped. Therefore, the  $R_{si}$  and  $C_{si}$  only scale with I and W.  $\varepsilon_{ox}$  and I0 represent the dielectric constant and thickness of the oxide layer between the inductor and the substrate, respectively.

Normally, in CMOS technologies, the silicon substrate resistivity is extremely low at around 0.015 ohm cm for logic process, and is around 10 ohm cm for the mix-mode process. For the bipolar process or BiCMOS processes, it is typically 10 ohm cm to 30 ohm cm [25]. In this research, the substrate resistivity is universally set up as 10ohm cm for both CMOS mix-mode and BiCMOS cases. The conductive nature of the silicon substrate leads to various losses, which convert the electromagnetic energy into heat in the substrate volume. Figure 2.10 physically illustrates the mechanisms of the substrate induced losses for a spiral inductor. Generally speaking, there are two main loss mechanisms in the substrates. First, electric energy is coupled to the substrate in terms of displacement current because of the potential difference between the inductor coil and the substrate. This current flows through  $C_{ox}$  to nearby grounds. These currents flow vertically or laterally, but are perpendicular to the spiral traces, and are curl free (unlike the eddy current, there is no circulation in this displacement current, that is,  $\nabla \times I = 0$ ). This displacement current movement is two ways: The incident currents pass through  $C_{ox}$  from some particular traces to the substrate. Also, there are reflecting currents from the substrate returning back to the inductor metal traces via the  $C_{ox}$ . This is also the nature of high frequency current. Second, induced currents circulate in the substrate due to the time-varying magnetic field  $\overset{\omega}{B}$  penetrating the substrate. According to Maxwell's Equation [18],

$$\nabla \times \stackrel{\mathbf{v}}{E} = -\frac{\partial \stackrel{\omega}{B}}{\partial t}, \tag{2.28}$$

this magnetic field gives rise to time-varying circular electric field  $\stackrel{\omega}{E}$  which induces substrate eddy currents. These eddy currents flow parallel to the device segments.

Radiation always occurs at the frequencies where the device physical dimensions approach the wavelength at the frequencies of propagation in the medium of interest. That is why one can safely ignore the electromagnetic radiation loss into the air because even at very high frequencies, say, 100 GHz, the wavelength in free space is still 3 mm, which is considerably larger than the dimensions of the devices discussed in this thesis.

Figure 2.10: Schematic representation of substrate currents. Eddy currents and electrically induced currents are represented by the dashed lines and the solid lines, respectively [6].

# 2.5 Spiral Inductor Quality Factor Frequency Analysis

Although the inductor is a two port passive component, when expressing the inductor properties using simulation or measurement, a standard method is to ground one port because the measured parameters more directly relate to the inductance (L) and Q. In this way, the unnecessary complexity in the analysis is avoided and meantime the inductor characteristics is still preserved [26]. However, from Figure 2.6, one can see the grounding of one port in the circuit model, say port 2, removes the parasitic effect at port 2, namely,  $C_{ox}$ ,  $C_{si}$ , and  $R_{si}$ . However in practice, grounding one port does not really short these out since the real parasitics are distributed and not lumped at the port, and therefore has little influence on the performance of the inductor. However, the one port grounding does introduce error or inaccuracy between actual measurement and the lumped model. The lumped model is still useful for qualitative analysis and understanding, but a model which represents distributed effects, is more appropriate for