2011 International Symposium on Intelligent Signal Processing and Communication Systems (ISPACS) December 7-9, 2011

# A New Temperature Independent Current Controlled Oscillator

## Zheng-Yi Huang, Jen-Shiun Chiang, Wei-Bin Yang, Chi-Hsiung Wang

Department of Electrical Engineering Tamkang University Tamsui, Taipei, Taiwan enjoyable qq@hotmail.com

Abstract—This paper describes a circuit, which generates a low temperature-dependent bias currents. In this paper, low temperature coefficient reference is presented. The circuit is firstly employed to generate a current reference with temperature compensation, then, supply current to the current controlled ring oscillator (CCO). Because of the oscillation frequency of CCO is proportional to temperature, the current is designed to be inversely proportional to temperature to compensate the temperature variation of CCO. There are four different oscillation frequency temperature compensation has been completed, they are 10MHz, 20MHz, 30MHz and 40MHz respectively. The proposed circuit has been design by a 0.18um CMOS technology process and using computer simulation to evaluate the thermal drift of the reference current. The temperature coefficient of the proposed CCO is 24 ppm/°C in the temperature range between -25 and 75°C at 10MHz. In the 20MHz, 30MHz and 40MHz oscillation frequency, the temperature coefficients are 32 ppm/°C, 38 ppm/°C and 34 ppm/℃ respectively.

Keywords: temperature independent current reference, current controlled ring oscillator

#### I. INTRODUCTION

Current and voltage references are indispensable circuit in analog, digital and power electronic systems. These should be designed stable as possible, the current and voltage references with high temperature immunity for proper operation. They are usually used to determine biasing points of sensitive analog circuits, for example amplifiers, oscillators, phase-locked loops (PLLs). Many high precision, temperature-independent reference circuits have been designed in the document over the last decades [1]-[3], many approaches have been made in order to design reliable current and voltage references in CMOS technology process.

Many CMOS current and voltage references consists of bipolar junction transistors (BJTs), which have been adapted to CMOS exploiting the parasitic lateral bipolar junction transistors in CMOS processes [4]-[5]. In addition, all-MOS voltage references have been proposed which use the thermal properties of MOS transistors worked in weak inversion region [6]or, recently the threshold voltage compensate the mobility temperature drift [7]-[11]. However, current references having MOS transistors operating in this region tend to have fairly large temperature coefficients. In these solutions, the circuits

which want to obtain good temperature performance are complex and require a large area [12]-[14].

There is a design of current controlled oscillator (CCO) in the following. To achieve the goal of compensating the frequency of CCO, an independent of temperature current reference is needed. When the proper current reference is brought in to the current-controlled oscillator, the frequency of CCO is compensated as following.

In this paper, the proposed circuit introduces a low-TC CMOS current reference utilizing MOS transistors operating in the weak inversion region and the current-controlled oscillator is compensated by the proper reference. The rest of this paper is organized as follows. Analysis for the proposed CMOS reference and current-controlled oscillator are both described in section II. Section III presents simulation results of several voltage and current references and oscillator to assess the performance. Finally, conclusions are given in Section IV.

#### II. CIRCUIT STRUCTURE

### A. MOSFETs in Weak Inversion Region

A model of the proposed CMOS reference can be used to describe the working of an n-channel MOS transistor in the weak inversion region [15]. Under the characteristic of an n-channel MOS transistor operating in the weak inversion region is similar to that of a BJT transistor and can be described as

$$I_{D} = I_{D0} S e^{q(V_{GS} - V_{TH})/nkT}$$

(1)

where  $I_{DO}$  is the generation current, S is the geometrical shape factor of the transistor, q is the electron charge, n is a slope factor, k is the Boltzmann constant, T is the absolute temperature,  $V_{GS}$  is the gate-source voltage, and  $V_{th}$  is the threshold voltage of the transistor. From Eq. (1), the gate-source voltage of the MOSFET for a given drain current can be described as

$$V_{GS} = nV_T \ln \frac{I_D}{SI_D} + V_{TH}$$

(2)

where  $V_T$  is the thermal voltage which is equal to kT/q. In this equation, the threshold voltage of the MOSFET can be described as [15]

$$V_{TH} = -\frac{kT}{q} \ln \frac{N_{D,poly}}{N_A} + \frac{2\sqrt{kTN_A \varepsilon_{sl} \ln \frac{N_A}{n_i}} - Q'_{SS}}{C'_{OX}}$$

(3)

where  $N_{D,poly}$  is the doping concentration of donor atoms in the n+ poly gate and  $N_A$  is the doping concentration of acceptor atoms in the substrate,  $n_i$  is intrinsic carriers,  $\varepsilon_{si}$  is the relative dielectric constant of Silicon,  $Q'_{SS}$  is the surface-state charge, and C'ox is the oxide capacitance per area. Substituting Eq. (3) into Eq. (2) and taking the derivative of  $V_{GS}$  with respect to T, the temperature coefficient of  $V_{GS}$  can be written as

$$\frac{\partial V_{GS}}{\partial T} \approx n \frac{k}{q} \ln \frac{I_D}{SI_{D0}} - \frac{k}{q} \ln \frac{N_{D,poly}}{N_A}$$

$$= -\frac{k}{q} \ln \frac{N_{D,poly}(SI_{D0})^n}{N_A(I_D)^n}$$

(4)

which indicates that the temperature coefficient of  $V_{GS}$  is a negative quantity.

#### B. Low Temperature dependent Current Reference

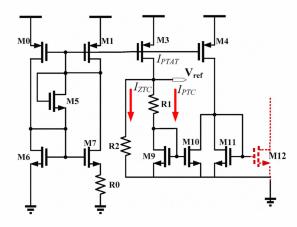

This section presents a temperature-compensated current reference, which is use an n-channel MOS transistor to operate in the weak inversion region. In Fig. 1, the circuit consists of a start-up circuit which is a PTAT current generator, a bandgap reference, and a low-TC current replication circuit. The PTAT current generator generates a current proportional to absolute temperature, the value is given by [16]

$$I_{PTAT} = \frac{nV_T}{R_0} \ln K \tag{5}$$

where K is the size ratio of  $M_0$  to  $M_1$ . The  $V_{ref}$  can be written as

$$V_{REF} = V_{GS.M9} + I_{PTC} R_{l} \tag{6}$$

The gate-source voltage of  $M_9$  and the voltage drop across  $R_1$  can be reduced by an n-channel MOS transistor work in the weak inversion region. The voltage drop across  $R_1$  can be increased by a positive current. Therefore, the temperature compensation of  $V_{ref}$  is finished and the  $I_{ZTC}$  can be written as

$$I_{ZTC} = \frac{V_{REF}}{R_2} \tag{7}$$

The current mirror comprising  $M_{11}$  and  $M_{12}$  copies  $I_{ZTC}$  to the output. The output reference current ( $I_{REF}$ ) of the proposed current reference can be written as

$$I_{REF} = I_{ZTC} \frac{(W/L)_{12}}{(W/L)_{11}}$$

$$= \frac{1}{R_2 + R_3} (V_{GS,M9} + I_{PTAT} R_3) \frac{(W/L)_{12}}{(W/L)_{11}}$$

(8)

By adjust the size ratio of M<sub>12</sub>. The different currents with low temperature coefficient are obtained. This current reference is designed to against temperature variation and inversely proportional to temperature, because of the

Fig. 1 Temperature compensation current reference

frequency of current controlled ring oscillator is positive with temperature variation.

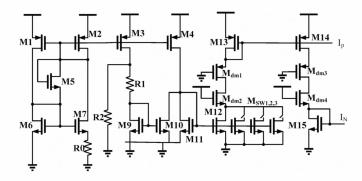

Fig. 2 shows the structure of the current reference which is used to provide four different currents for current controlled ring oscillator. Switching by four MOS(M12,  $M_{SW1,2,3}$ ), the oscillation frequency 10 MHz, 20 MHz, 30 MHz and 40 MHz are obtained. The 10 MHz of oscillation frequency is achieved by adjusting the size ratio of  $M_{12}$ . The 20 MHz of oscillation frequency is achieved by the current through the sum of  $M_{12}$  and  $M_{SW1}$ . The 30 MHz of oscillation frequency is achieved by the current through the sum of  $M_{12}$ ,  $M_{SW1}$  and  $M_{SW2}$ . The 40 MHz of oscillation frequency is achieved by the current through the sum of  $M_{12}$ ,  $M_{SW1}$ ,  $M_{SW2}$  and  $M_{SW3}$ . Where  $M_{dm1}$ ~  $M_{dm4}$  are dummy circuit to match the load in the current controlled oscillator.

Fig. 2 Temperature compensation current reference with current mirror

#### C. CURRENT CONTROLLED OSCILLATOR

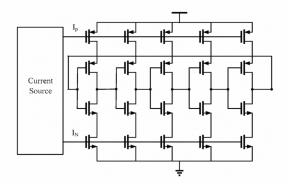

Fig. 3 Structure of CMOS ring oscillator with currentstarved inverter stages

Fig. 3 shows the structure of the ring oscillator, which is composed of an odd numbers of inverter stage with a bias current source. The rise and fall delays in the oscillator is determined by the inverter bias current source  $I_{\text{soure}}$ , the inverter trip voltage and the load capacitance  $C_{\text{load}}$ , and can be written as [17]

$$t_{PD\_rise} = \frac{C_{load} \cdot V_{trp}}{I_{source}}$$

$$t_{PD\_fall} = \frac{C_{load} \cdot (V_{DD} - V_{trp})}{I_{source}}$$

(9)

The oscillation frequency of the ring oscillator, composed of N current-starved inverter stages, can be represented as

$$f_{OSC} = \frac{1}{N \cdot (t_{PD\_rise} + t_{PD\_fall})}$$

$$= \frac{I_{source}}{N \cdot C_{load} \cdot V_{DD}}$$

(10)

The above equation indicates oscillation frequency of the current controlled oscillator is linearly dependent on the bias current. Therefore, if  $I_{\text{source}}$  is stable with temperature drift, it can reduce the variation of oscillation frequency obviously.

#### III. SIMULATION RESULTS

The temperature-compensated current reference had been designed which have been presented in the previous Sections. The current references have been designed and simulated by HSPICE with reference to the models of the devices available in a 0.18 um CMOS technology.

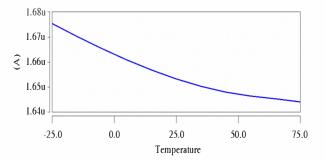

The reference current versus temperature of low temperature dependent current reference and inversely proportional to temperature is shown in Fig. 4. It can be observed that the reference current, which has a nominal value of 1.65~uA at  $25^{\circ}\text{C}$ .

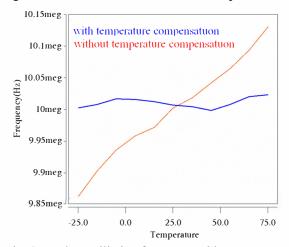

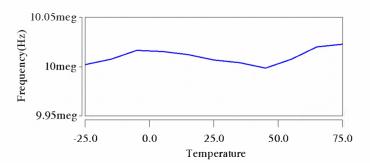

In order to compensate the temperature drift of an oscillator itself, the temperature slope of proposed temperature independent current reference is adjusted. Fig. 5 shows the oscillation frequency of oscillator is proportional to temperature without temperature compensation. Therefore the proposed current source is adjusted to complementary to temperature. Thus four reference currents are used to current controlled oscillator, which can achieve 10 MHz, 20 MHz, 30 MHz and 40 MHz oscillation frequency. The temperature drift of the proposed CCO is 0.024 MHz in the temperature range between -25 and 75°C at 10 MHz in Fig. 6. In the 20 MHz, 30 MHz and 40 MHz oscillation frequency, the temperature drift are 0.064 MHz, 0.11 MHz and 0.13 MHz respectively. Therefore, in the 10 MHz, 20 MHz, 30 MHz and 40 MHz oscillation frequency, the temperature coefficient are 24 ppm/°C, 32 ppm/°C, 38 ppm/°C and 34 ppm/°C respectively.

Fig. 4 The simulated current versus temperature

Fig. 5 The oscillation frequency with temperature compensation vs. without temperature compensation

Fig. 6 The simulated CCO versus temperature at 10MHz

#### IV. CONCLUSION

In this paper, the temperature-compensated current source have been presented and analyzed. The low temperature dependent circuit, in particular, achieves complementary to temperature in the temperature range between -25°C and 75°C. The current controlled ring oscillator using these currents can oscillate to 10 MHz, 20MHz, 30MHz and40MHz oscillation frequency, and the temperature coefficient the temperature coefficient are 24 ppm/°C, 32 ppm/°C, 38 ppm/°C and 34 ppm/°C respectively.

Both the current source and the current controlled ring oscillator have been designed by a 0.18 um CMOS technology process and their performances have been verified through computer simulations.

TABLE I

RING OSCILLATORS SPECIFICATION COMPARISON WITH REFERENCE

|            | Technology | Supply<br>Voltage | Target<br>Frequency | Temperature coefficient | Power   |

|------------|------------|-------------------|---------------------|-------------------------|---------|

| This work  |            |                   | 10 MHz              | 24 ppm/℃                | 33 uW   |

| @20Meg     | 0.10       | 1.037             | 20 MHz              | 32 ppm/°C               | 45 uW   |

| @30Meg     | 0.18 um    | 1.8 V             | 30 MHz              | 38 ppm/°C               | 56 uW   |

| @40Meg     |            |                   | 40 MHz              | 34 ppm/°C               | 67 uW   |

| YS. [18]   | 0.6 um     | 4 V               | 680 KHz             | 106 ppm/°C              | 0.4 mW  |

| R. [19]    | 0.18 um    | 1.8 V             | 625 MHz             | 683 ppm/°C              | 0.59 mw |

| G. De [20] | 0.35 um    | 1 V               | 80 KHz              | <b>824 ppm/℃</b>        | 1.14 uW |

| K. R. [21] | 0.13 um    | 3.3 V             | 1.25 GHz            | 340 ppm/°C              | 11 mW   |

#### Acknowledgments

The authors would like to thank the National Chip Implementation Center and National Science Council, Taiwan, for fabricating this chip and supporting this work, respectively.

#### V. REFERENCES

- R. J. Widlar, "New developments in IC voltage regulators," *IEEE J. Solid-State Circuits*, vol. SC-6, no. 1, pp. 2-7, Feb. 1971

- [2] K. E. Kuijk, "A precision reference voltage source," *IEEE J. Solid-State Circuits*, vol. SC-8, no. 3, pp. 222–226, Jun. 1973.

- [3] A. P. Brokaw, "A simple three-terminal IC bandgap reference," IEEE J. Solid-State Circuits, vol. SC-9, no. 6, pp. 388–393, Dec. 1974

- [4] Y. P. Tsividis and R. W. Ulmer, "A CMOS voltage reference," IEEE J.Solid-State Circuits, vol. SC-13, no. 6, pp. 774–778, Dec. 1978

- [5] R. W. Ye and Y. P. Tsividis, "Bandgap voltage reference sources in CMOS technology," *Electron. Lett.*, vol. 18, pp. 24– 25, Jan. 1982

- [6] E. Vittoz and J. Fellrath, "CMOS analog integrated circuits based on weak inversion operation," *IEEE J. Solid-State Circuits*, vol. SC-12, no. 3, pp. 224–231, Jun. 1977.

- [7] C.-H. Lee and H.-J. Park, "All-CMOS temperature-independent current reference," *Electon. Lett.*, vol. 32, pp. 1280–1281, Jul. 1996

- [8] W. M. Sansen, F. Op't Eynde, and M. Steyaert, "A CMOS temperature compensated current reference," *IEEE J. Solid-State Circuits*, vol. 23, no. 3, pp. 821–824, Jun. 1988.

- [9] J. Georgiou and C. Toumazou, "A resistorless low current reference circuit for implantable devices," in *Proc. IEEE Int. Symp. Circuits and Systems 2002. ISCAS 2002*, vol. 3, pp. III-193–III-196.

- [10] O. Cerid, S. Balkir, and G. Dundar, "Novel CMOS reference current generator," *Int. J. Electron.*, vol. 78, pp. 1113–1118, Jun. 1995.

- [11] I. M. Filanovsky and A. Allam, "Mutual compensation of mobility and threshold voltage temperature effects with applications in CMOS," *IEEE Trans. Circuits Syst. I, Fundam. Theory Appl.*, vol. 48, no. 7, pp. 876–884, Jul. 2001.

- [12] G. C. M. Meijer et al., "A new curvature corrected bandgap reference," *IEEE J. Solid-State Circuits*, vol. SC-17, no. 6, pp. 1139–1143, Dec.1982.

- [13] B. Song and P. R. Gray, "A precision curvature-compensated CMOS bandgap reference," *IEEE J. Solid-State Circuits*, vol. SC-18, no. 6, pp. 634–643, Dec. 1983.

- [14] M. Gunawan et al., "A curvature-corrected low-voltage bandgap reference," *IEEE J. Solid-State Circuits*, vol. 28, no. 6, pp. 667– 670, Jun. 1993.

- [15] R. J. Baker, "CMOS-Circuit Design, Layout and Simulation," 2nd ed., Piscataway, NJ: IEEE Press, 2005.

- [16] Yoon-Suk Park; Hyoung-Rae Kim; Jae-Hyuk Oh; Yoon-Kyung Choi; Bai-Sun Kong;" Compact 0.7-V CMOS voltage current reference with 54/29-ppm/°C temperature coefficient," SoC Design Conference (ISOCC), Page(s): 496 499,2009.

- [17] Karim Arabi and Bozena Kaminska, "Built-In Temperature Sensors forOn-Line Thermal Monitoring of Microelectronics Structures", IEEE International Conference on VLSI in computers and processors, pp. 462-467, 1997

- [18] Y.-S. Shyu and J.-C. Wu, "A process and temperature compensated ring oscillator," in *Proc. 1st IEEE Asia Pacific Conf.*, 1999, pp. 283–286.

- [19] R. Vijayaraghavan, S. K. Islam, M. R. Haider, and L. Zuo, "Wideband injection-locked frequency divider based on a process and temperature compensated ring oscillator," *IET Circuits, Devices & Syst.*, vol. 3, pp. 259–267, 2009.

- [20] G. De Vita, F. Marraccini, and G. Iannaccone, "Low-voltage low-power CMOS oscillator with low temperature and process sensitivity," in *Proc. IEEE Int. Symp. Circuits and Systems* (ISCAS 2007), 2007, pp. 2152–2155.

- [21] K. R. Lakshmikumar, V. Mukundagiri, and S. L. J. Gierkink, "A process and temperature compensated two-stage ring oscillator," in *Proc. IEEE Custom Integrated Circuits Conf.* (CICC'07), 2007, pp. 691–694