# ARCHITECTURAL IMPROVEMENTS IN IEEE-COMPLIANT

FLOATING-POINT MULTIPLICATION

## By TUAN DANH NGUYEN

Bachelor of Science in Computer Science Hanoi University of Science and Technology Hanoi, Vietnam 2008

Submitted to the Faculty of the Graduate College of the Oklahoma State University in partial fulfillment of the requirements for the Degree of DOCTOR OF PHILOSOPHY December, 2018

# ARCHITECTURAL IMPROVEMENTS IN IEEE-COMPLIANT FLOATING-POINT MULTIPLICATION

| Dissertation Approved: |  |  |  |  |

|------------------------|--|--|--|--|

|                        |  |  |  |  |

|                        |  |  |  |  |

| James E. Stine         |  |  |  |  |

| Dissertation Advisor   |  |  |  |  |

|                        |  |  |  |  |

| Dr. Keith A. Teague    |  |  |  |  |

|                        |  |  |  |  |

|                        |  |  |  |  |

| Dr. Carl D. Latino     |  |  |  |  |

|                        |  |  |  |  |

|                        |  |  |  |  |

| Dr. Camille DeYong     |  |  |  |  |

#### ACKNOWLEDGMENTS

First and foremost, I would like to thank my advisor, Dr. James E. Stine, for his continuous and invaluable support of my Ph.D. research. I can not emphasize enough my appreciation for his patience, encouragement, and immense knowledge.

I would like to thank Dr. Keith A. Teague, Dr. Carl D. Latino, and Dr. Camille DeYong for serving my committee and for their insightful comments/questions and encouragement.

I would like to thank my labmate and my friend, Dr. Son V. Bui, for his help not only in my research but also in my life in the U.S.

Last but not least, I would like to thank my family: my parents, my wife, and my daughter, for their love and unconditional support. They always believe in me and encourage me to follow my dreams.

Acknowledgments reflect the views of the author and are not endorsed by committee members or Oklahoma State University.

Name: TUAN DANH NGUYEN

Date of Degree: DECEMBER, 2018

Title of Study: ARCHITECTURAL IMPROVEMENTS IN IEEE-COMPLIANT FLOATING-POINT MULTIPLICATION

Major Field: ELECTRICAL AND COMPUTER ENGINEERING

Abstract: Multiplication has long been an important part of any computer architecture. It has usually been a common case for most computer architecture decisions to include in any microarchitecture. However, the difficulty in creating hardware for multiplication because of its inherent shifting of the radix point has been a cogent reason for the need for floating-point hardware in scientific applications. The IEEE 754 floating-point standard was originally ratified in 1985 [1] and later amended in 2008 [2] to make floating-point multiplication easier for users to implement applications. Although floating-point arithmetic creates a mechanism to make things easier for using multiplication, it is complicated both algorithmically and practically for hardware implementations.

This dissertation discusses possible architectural improvements in IEEE-compliant floating-point multiplication for Machine Learning/Deep Learning applications. First, a combined IEEE half and single precision floating-point multipliers is proposed to reduce power dissipation for Deep Learning applications. Second, a novel rounding scheme is proposed that is simpler but comparable with the state-of-the-art rounding schemes. Third, an optimized design is proposed that can handle both denormal and normal numbers. Finally, a hybrid precision design is proposed, aiming to improve the power consumption of Machine Learning/Deep Learning applications. Proposed designs are targeted to Machine Learning/Deep Learning applications-specific processors to improve the latency and power consumption. All designs are implemented in RTL-level Verilog, verified for correctness against open-source TestFloat generated test vectors, and synthesized using an ARM 32nm CMOS library for Global Foundries (GF) cmos32soi technology for estimated power, area and delay analysis.

## TABLE OF CONTENTS

| Ch | apter                                  | I                                                                                                                                                                                                                                                                                                                                                                | Pag€                                                           |

|----|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| 1. | INT                                    | RODUCTION                                                                                                                                                                                                                                                                                                                                                        | 1                                                              |

| 2. | 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6 | Floating-Point Formats Floating-Point Multiplication Mantissa Multiplication 2.3.1 Array Multipliers 2.3.2 Tree Multipliers Rounding for IEEE Floating Point Multiplication Linear Delay Analysis Chapter Summary                                                                                                                                                | 5<br>7<br>10<br>11<br>13<br>14<br>18                           |

| 3. |                                        | OMBINED IEEE HALF- AND SINGLE-PRECISION FP MUL-                                                                                                                                                                                                                                                                                                                  |                                                                |

|    | 3.1<br>3.2<br>3.3<br>3.4               | LIERS FOR DEEP LEARNING                                                                                                                                                                                                                                                                                                                                          | 20<br>20<br>21<br>22<br>25<br>28<br>29                         |

| 4. |                                        | OVEL ROUNDING SCHEME FOR IEEE-COMPLIANT FF                                                                                                                                                                                                                                                                                                                       |                                                                |

|    |                                        | LTIPLICATION                                                                                                                                                                                                                                                                                                                                                     |                                                                |

|    | 4.1                                    | Previous Work  4.1.1 Santoro, Bewick and Horowitz (SBH) Method  4.1.1.1 RZ mode  4.1.1.2 RN mode  4.1.1.3 RI mode  4.1.2 Quach, Takagi and Flynn (QTF) Method  4.1.2.1 Errors in Quach, Takagi and Flynn Hardware  4.1.2.2 Linear Delay Analysis  4.1.3 Even and Seidel (ES) Method  4.1.3.1 Optimization of Even-Seidel Rounding  4.1.3.2 Linear Delay Analysis | 30<br>30<br>31<br>32<br>35<br>36<br>38<br>40<br>41<br>42<br>43 |

|    | 4.2                                    | Proposed Method                                                                                                                                                                                                                                                                                                                                                  | 44                                                             |

|    |                                        | 4.2.1 A Simplified Special Compound Adder                                                                                                                                                                                                                                                                                                                        | 44                                                             |

| Ch         | apter                           | P                                                                                                                                                                                         | Pag€                                   |

|------------|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

|            | 4.3                             | 4.2.2       RI Mode          4.2.3       RN Mode          4.2.4       RZ Mode          4.2.5       Linear Delay Analysis          Chapter Summary                                         | 45<br>49<br>51<br>52<br>53             |

| <b>5</b> . |                                 | OPTIMIZED IEEE MULTIPLIER SUPPORTING DENOR-                                                                                                                                               |                                        |

|            | <b>MA</b> 5.1 5.2 5.3 5.4       | A Simple Design for Denormal Numbers  5.1.1 Exponent addition and adjustment  5.1.2 Rounding and packing  Proposed Multipliers  Linear Delay Analysis  Chapter Summary                    | 54<br>54<br>56<br>57<br>58<br>60<br>61 |

| 6.         |                                 | YBRID IEEE PRECISION MULTIPLIERS SUPPORTING DE-                                                                                                                                           | -                                      |

|            | NOI<br>6.1<br>6.2<br>6.3<br>6.4 | Exponent addition                                                                                                                                                                         | 63<br>64<br>67<br>69<br>70             |

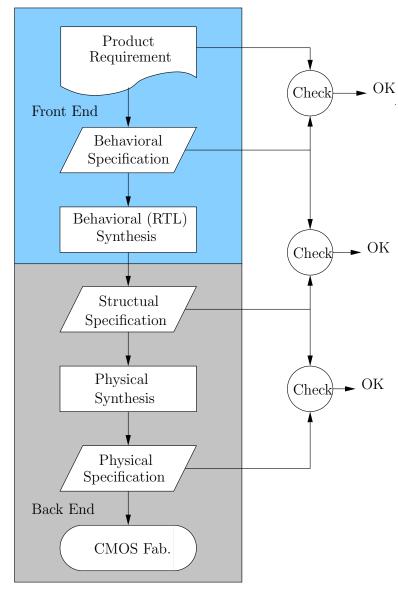

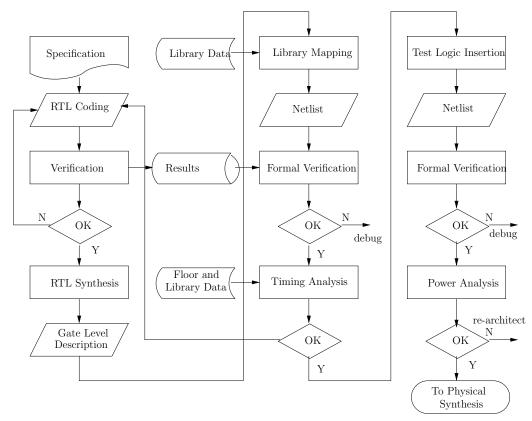

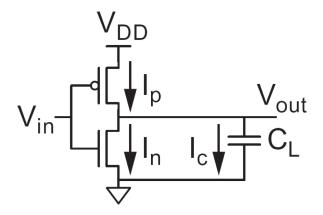

| 7.         | 7.1                             | PERIMENTAL RESULTS  Methodology 7.1.1 ASIC Design Flow 7.1.2 Logic Design and Hardware Description Languages 7.1.3 Design Verification 7.1.4 Topographical Synthesis 7.1.5 Power Analysis | 72<br>72<br>73<br>74<br>75<br>76       |

|            | 7.2                             | <ul> <li>Delay, Area, and Power Analysis</li></ul>                                                                                                                                        | 78<br>78<br>80<br>80                   |

|            | 7.3                             | Chapter Summary                                                                                                                                                                           | 81                                     |

| 8.         | COI<br>8.1<br>8.2               | Conclusions                                                                                                                                                                               | 82<br>82<br>84                         |

| рī         | וממג                            | RENCES                                                                                                                                                                                    | 25                                     |

## LIST OF TABLES

| Гable | I                                                                              | Pag€ |

|-------|--------------------------------------------------------------------------------|------|

| 2.1   | IEEE 754-2008 floating-point formats                                           | 6    |

| 3.1   | Post-synthesis results for the proposed design in cmos $32$ soi $32$ nm IBM/GI | F    |

|       | technology                                                                     | 28   |

| 4.1   | Compound adder output selection for RNU modes                                  | 35   |

| 4.2   | Decoder for special $(Sum, Sum + 1, Sum + 2)$ CA                               | 45   |

| 4.3   | Generate $sel1$ , $sel0$ from $INC$ , $p$ , $lp$                               | 48   |

| 4.4   | Boolean equations for RI mode                                                  | 50   |

| 4.5   | Boolean equations for RN mode                                                  | 50   |

| 4.6   | Boolean equations for RZ mode                                                  | 52   |

| 4.7   | Theoretical delay (logic levels) comparison                                    | 53   |

| 7.1   | Post-synthesis results for the proposed design (without denormalized           |      |

|       | numbers support) in cmos32soi 32nm GF technology at 10 GHz $$                  | 79   |

| 7.2   | Post-synthesis results for the proposed design (supporting denormal-           |      |

|       | ized numbers) in cmos32soi 32nm GF technology at 10 GHz $$                     | 79   |

| 7.3   | Post-synthesis results for the proposed hybrid design (supporting de-          |      |

|       | normalized numbers) in cmos32soi 32nm GF technology at 10 GHz $$ .             | 80   |

| 8.1   | Normalized experimental results for proposed design (without denor-            |      |

|       | malized numbers support)                                                       | 83   |

| 8.2   | Normalized experimental results for proposed design (supporting de-            |      |

|       | normalized numbers)                                                            | 83   |

## LIST OF FIGURES

| Figure |                                                                                 | Page |

|--------|---------------------------------------------------------------------------------|------|

| 2.1    | Data formats for the floating point                                             | 6    |

| 2.2    | Normalized, denormalized, and special numbers (binary16)                        | 7    |

| 2.3    | Block diagram of multiplier                                                     | 9    |

| 2.4    | Partial products matrix of multiplication                                       | 10   |

| 2.5    | Modified half adder and full adder (Adopted from [3])                           | 11   |

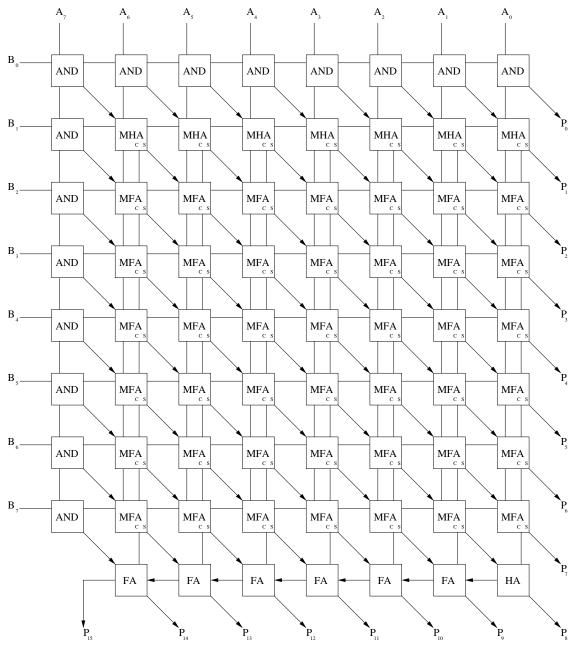

| 2.6    | Example of $8 \times 8$ -bit carry-save array multiplier [3]                    | 12   |

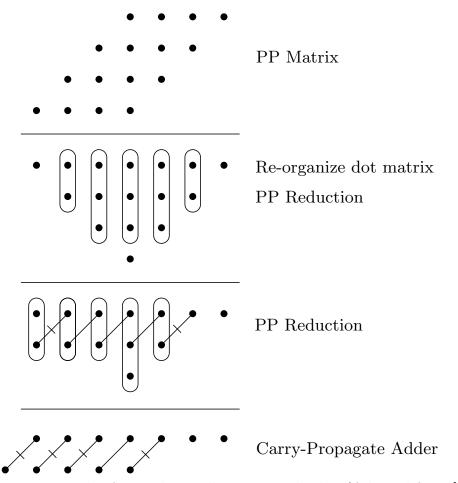

| 2.7    | Example of 4 × 4-bit Wallace tree multiplier (Adopted from [3])                 | 13   |

| 2.8    | Rounding modes definition                                                       | 15   |

| 2.9    | An implementation of four IEEE rounding modes (Adopted from [4])                | 17   |

| 2.10   | An example of delay analysis for half adder                                     | 18   |

| 3.1    | Converting binary16 exponent (5-bits) to binary32 exponent (8-bits) .           | 23   |

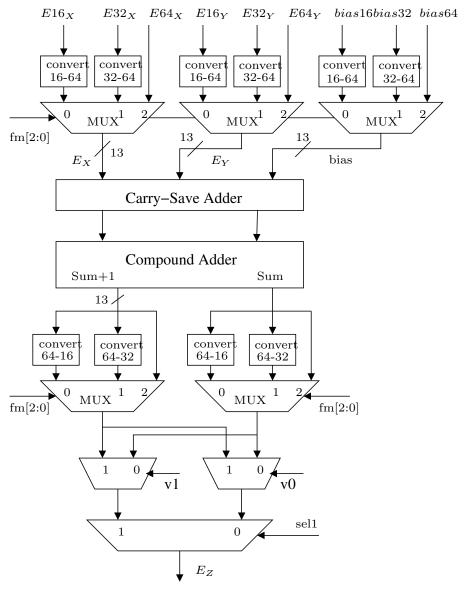

| 3.2    | A combined IEEE half and single-precision exponent addition $\ \ldots \ \ldots$ | 24   |

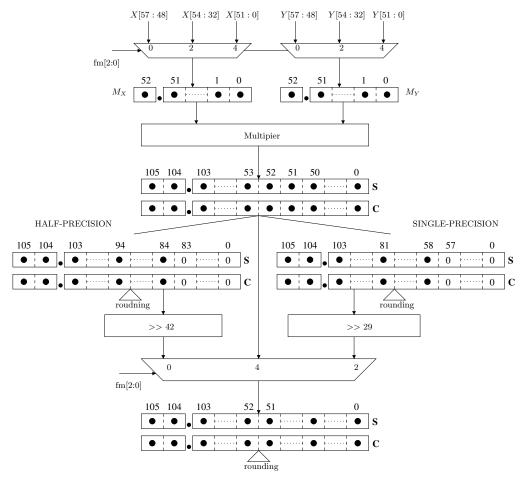

| 3.3    | Mantissa multipliers for single-precision                                       | 26   |

| 3.4    | Modifed mantissa multipliers                                                    | 27   |

| 4.1    | SBH [4] implementation of RZ mode                                               | 31   |

| 4.2    | A simple implementation of RNU mode                                             | 32   |

| 4.3    | SBH [4] method for RNU mode                                                     | 34   |

| 4.4    | QTF [5] method implementation for all IEEE modes                                | 36   |

| 4.5    | Two examles illustrating how third sum is obtained with only two carry          |      |

|        | chains                                                                          | 37   |

| 4.6    | ES [6] Method Implementation for Rounding                                       | 42   |

| Figure | ]                                                                        | Page |

|--------|--------------------------------------------------------------------------|------|

| 4.7    | The simplified special compound adder (CA)                               | 45   |

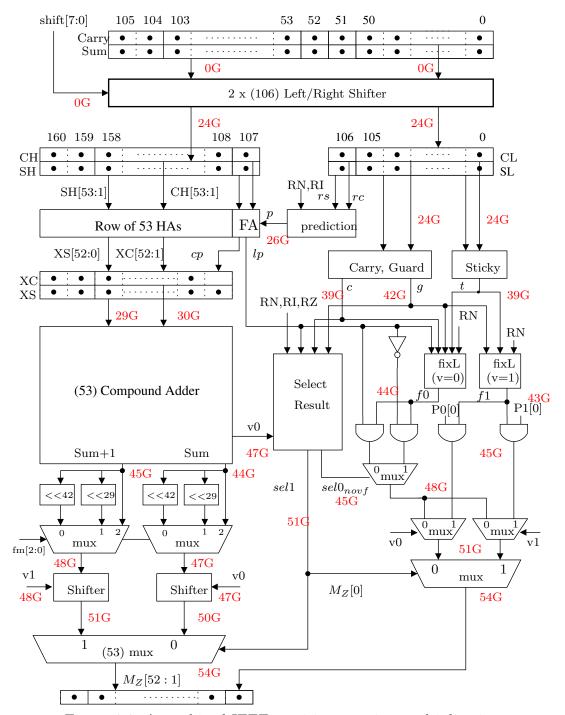

| 4.8    | Proposed method for all IEEE rounding modes                              | 47   |

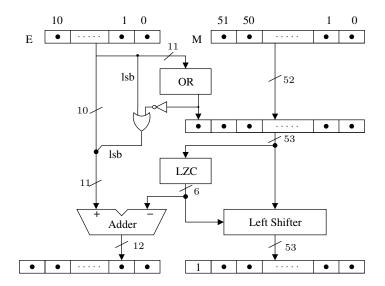

| 5.1    | Converts an IEEE 754 double precision number into the normalized         |      |

|        | representation                                                           | 55   |

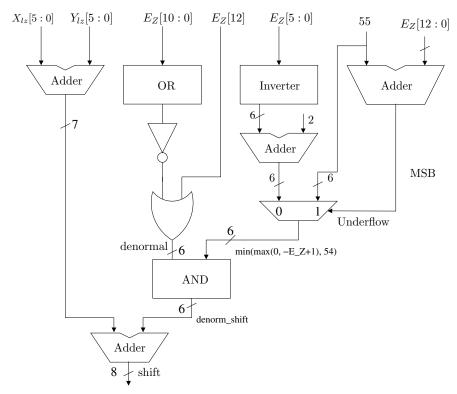

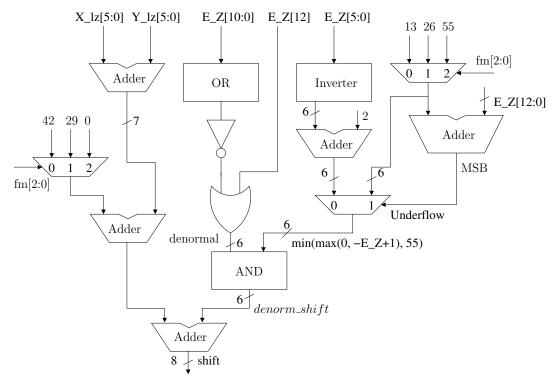

| 5.2    | Exponent addition and adjustment                                         | 56   |

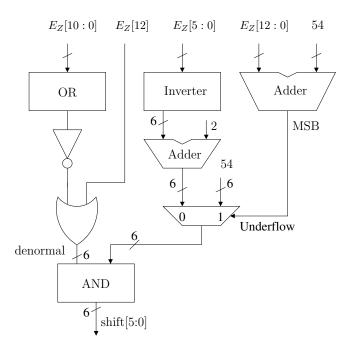

| 5.3    | Compute shift amount to denormalize the mantissa if exponent < emin      | 57   |

| 5.4    | Shift is computed by first constraining the exponent, $E_Z$ to 0 to -55  |      |

|        | and inverting the result                                                 | 59   |

| 5.5    | Block diagram of the mantissa path when shifting the carry save vectors  |      |

|        | before rounding                                                          | 61   |

| 6.1    | Converting binary16 exponent (5-bits) to binary64 exponent (11-bits)     | 64   |

| 6.2    | Converting sign-extended binary64 exponent to sign-extended binary16     |      |

|        | exponent                                                                 | 65   |

| 6.3    | A combined IEEE precision exponent addition                              | 66   |

| 6.4    | Aligning rounding position for half precision and single precision modes | 67   |

| 6.5    | A computing shift amount for half/single/double-precision design, tak-   |      |

|        | ing into account the difference between rounding positions               | 69   |

| 6.6    | A combined IEEE precision mantissa multiplication                        | 70   |

| 7.1    | Generalized design flow (Adopted from [7])                               | 73   |

| 7.2    | Typical ASIC design flow (Adopted from [7])                              | 74   |

| 7.3    | CMOS Inverter (Adopted from [7])                                         | 77   |

## LIST OF NOTATIONS AND ABBREVIATIONS

The following is a list of symbols, variables, and scripts used in this work which may not be defined as they are encountered in the body.

| $\wedge$ | logic AND      |

|----------|----------------|

| $\vee$   | logic OR       |

| $\oplus$ | logic XOR      |

| +        | addition       |

|          | multiplication |

X[n-1:0] n-bits binary number X MSB Most Significant Bit LSB Least Significant Bit ulp unit in the last place

FP Floating-Point

ML Machine Learning

DL Deep Learning

CPU Central Processing Unit GPU Graphics Processing Unit

#### CHAPTER 1

#### INTRODUCTION

In recent years, deep learning has grown tremendously in its popularity and usefulness [8]. However, deep learning is computationally intensive, power-hungry and often limited by its hardware capability. Basically, deep learning is a deep neural network, which consists in convolutions and matrix multiplications. In [9], authors show that 90% computation of convolutional neural network (CNN), a typical deep neural network, is due to convolution operations. Therefore, multipliers are the most space- and power-hungry arithmetic operators of the digital implementation of CNN. This is also true for other types of machine learning that heavily based on a matrix multiplication.

In addition, multiplication has long been an important part of any computer architecture. It has usually been a common case for most computer architecture decisions to include in any microarchitecture. However, the difficulty in creating hardware for multiplication because of its inherent shifting of the radix point has been a cogent reason for the need for floating-point hardware in scientific applications. The IEEE 754 floating-point standard was originally ratified in 1985 [1] and later amended in 2008 [2] to make floating-point multiplication easier for users to implement applications. Although floating-point arithmetic creates a mechanism to make things easier for using multiplication, it is complicated both algorithmically and practically for hardware implementations.

To account for these changes, specifically for rounding, key research was introduced to help alleviate problems related to round-to-nearest-even [4]. Good hard-

ware for rounding in IEEE-compliant floating-point arithmetic is key to expanding algorithms, numerical methods, and applications that exploit techniques to control validation in loss of precision (e.g., through interval arithmetic [10]). Although [4] is paramount in determining good rounding for IEEE 754 arithmetic, it has the deficiency of not supporting all four IEEE rounding modes. Additional work clarifies designs for improving rounding as well as giving optimal hardware [5, 11]. Although these papers give good designs, there are additional questions about verification and possible improvements. Consequently, this dissertation shows modifications that can be done to help optimize this process and efficiently correct for all four rounding modes. This dissertation presents an improved implementation described using the IEEE 754 double-precision floating-point format [1, 2] but it can be easily adapted to all other IEEE-compliant formats with a small modification. Moreover, this dissertation verifies all designs and details whether the designs are specifically IEEE 754 compliant.

In addition, correct rounding of both normal and denormal results further exacerbates the growing complexity of an IEEE 754 multiplier. Due to the importance of high precision in scientific applications [12], the precision must be preserved. Simply truncating denormal results to zero is unacceptable [13], especially with half- and single-precision floating-point numbers. Consequently, having floating-point units that can handle normalized and denormalized numbers is essential, especially for scientific computing [14]. Recently there have been several types of hardware implementations that handle floating-point denormalized IEEE-754 numbers [15, 16, 17]. This dissertation discusses methods of implementing both normalized and denormalized IEEE 754 numbers [2]. In particular, it combines the pre-normalizing and post-normalizing steps in existing methods into a simpler and faster single step.

While most general-purpose CPU/GPU utilize double-precision floating point units, single-precision floating-point is widely used in deep learning as the default

format because its advantage in a representable range that makes it suitable for a wide range of applications [2]. Moreover, recent research [18] shows that, in many applications, single-precision floating-point multipliers can be replaced by half-precision floating-point multipliers in training deep neural networks, which have little to no impact on the network accuracy. Smaller multipliers also lead to a lower overall energy footprint even in systems that have multiple IEEE 754 formats implemented in hardware. Therefore, there is a need for a new multipliers that can switch between precision numbers in implementing deep learning.

This dissertation ultimately provides an IEEE 754 compliant floating-point multiplier that can handle half-, single-, and double-precision operations. Previous implementations [19, 20] only demonstrated methods for single- and double-precision operations, however, this design extends the ideas by specifically adapting the architecture for half-precision IEEE 754 multiplication. Half-precision floating-point multipliers are new additions to the 754 standard that are specifically useful for architectures that use machine learning computations [2]. Most importantly, by utilizing smaller amounts of precision, these multipliers can speed up computations for designs that are well suited for neural networks and machine learning applications [21]. Moreover, extensions are added to the multiplier to also handle denormalized IEEE 754 floating-point numbers as well as half- and single-precision floating-point numbers.

The rest of this dissertation is organized as follows: Chapter 2 is the background about IEEE floating-point formats and multiplication. Chapter 3 is a combined IEEE half and single-precision multipliers for deep learning applications. Chapter 4 briefly summarizes and clarify the key contribution in Santoro, Bewick and Horowitz [4] (SBH) method, Quach, Takagi and Flynn [5] (QTF) method, and Even and Seidel [6] (ES) method and then shows our proposed method that can support all rounding modes. Chapter 5 is a novel design that support both normalized and denormalized floating point numbers. Chapter 6 is a hybrid precision design that can switch preci-

sion mode easily. Chapter 7 presents how all designs are implemented, verified, and simulated for delay, area, and power. Finally, Chapter 8 is the conclusions and future work.

#### CHAPTER 2

#### BACKGROUND

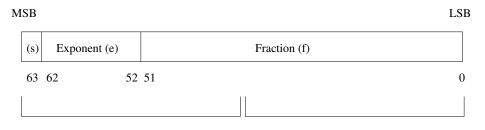

#### 2.1 Floating-Point Formats

The IEEE 754 floating-point standard, originally ratified in 1985 [1] and later ammended in 2008 [2], defines the floating-point format that consists of three parts: sign (S), exponent (E), fraction or mantissa (F) as shown in Figure 2.1. Table 2.1 shows the operand structure for the current IEEE 754-2008 formats including half-precision, single-precision, double-precision and quadruple-precision formats with the size and bias values for each format.

With the IEEE 754 format, the exponent is adjusted so that the sum of the real exponent and a constant (bias) are in a non-negative range. This is designed to avoid using two's complement encoding that can be difficult to handle for multiple fields as well as simplifying implementations for comparison. The bias is given as:

$$bias = 2^{exponent\_size-1} - 1 (2.1)$$

where the value of the exponent is set according to the representation given in the IEEE 754 standard (e.g., double-precision). This value represents the midway case between the minimum and the maximum exponent values.

Normalized (or normal) IEEE floating-point numbers are assigned a mantissa between the range of [1,2) to create a packed representation of numbers in scientific notation. The encoding assumes that the mantissa has a leading one so that its representation exists between the range of [1,2). In order to save space, the leading

Word 1 Word 0 Figure 2.1: Data formats for the floating point

| Format                      | Size | Sign (S) | Exponent (E) | Bias Value (B) | Fraction (F) |

|-----------------------------|------|----------|--------------|----------------|--------------|

| Half-Precision (binary16)   | 16   | 1        | 5            | 15             | 10           |

| Single-Precision (binary32) | 32   | 1        | 8            | 127            | 23           |

| Double-Precision (binary64) | 64   | 1        | 11           | 1023           | 52           |

| Quad-Precision (binary128)  | 128  | 1        | 15           | 16383          | 112          |

Table 2.1: IEEE 754-2008 floating-point formats

1 is not stored, but hidden. This can be represented by the following equation for a given normalized IEEE 754 floating-point number X:

$$X = (-1)^S \cdot 1.F \cdot 2^{E-bias} \tag{2.2}$$

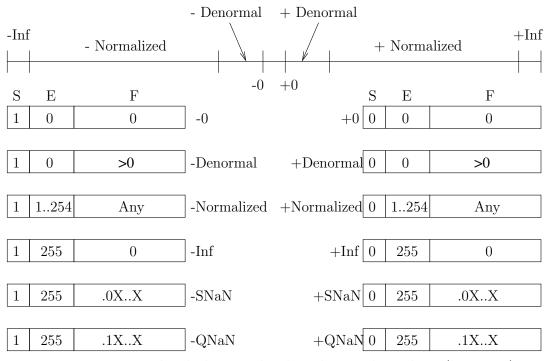

On the other hand, for denormalized (or denormal) numbers, the value of X is given by:

$$X = (-1)^S \cdot 0.F \cdot 2^{1-bias} \tag{2.3}$$

where the leading hidden bit is now 0. Some texts refer to this as subnormal numbers. A zero (0) exponent and non-zero mantissa indicates a denormalized number (i.e.,  $X_E = 0$  and  $X_F \neq 0$ ). Denormal numbers fill the gap between smallest normal numbers and zero by allowing numbers with reduced precision to exist. Ultimately, denormalized numbers are designed to limit gradual underflow [22, 23].

In addition to normalized and denormalized numbers, IEEE 754 also defines special values including zeros, infinity (Inf), quiet Not-a-Number (qNaN), and signaling Not-A-Number (sNaN). A NaN is utilized to represent numbers not possible for typ-

Figure 2.2: Normalized, denormalized, and special numbers (binary16)

ical floating-point representations. Figure 2.2 shows the definition for those special values in half-precision (binary16) format.

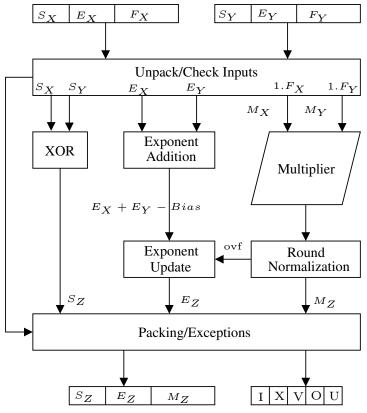

## 2.2 Floating-Point Multiplication

Floating-point multiplication complicate accuracy and precision because of the movement of the radix point during a multiplication [12]. That is, the final result must be formatted in the IEEE 754 format before it is written back to a datapath/memory unit as a result [1]. For this reason, floating-point computations can possibly produce unreliable computations due to rounding and exceptions within the IEEE 754 standard [24].

Given two floating point numbers X and Y represented by  $(S_X, E_X, M_X)$  and  $(S_Y, E_Y, M_Y)$ , respectively, the product Z represented by  $(S_Z, E_Z, M_Z)$  can be math-

ematically computed as follows:

$$Z = X \cdot Y$$

$$= (-1)^{S_X} \cdot 2^{E_X - B} \cdot M_X \cdot (-1)^{S_Y} \cdot 2^{E_Y - B} \cdot M_Y$$

$$= (-1)^{S_X + S_Y} \cdot 2^{(E_X + E_Y - B) - B} \cdot (M_X \cdot M_Y)$$

(2.4)

Since  $M_X$ ,  $M_Y$  are 53 bits number in the [1, 2) domain, the product  $M_X \cdot M_Y$  results in a 106 bit number in the [1, 4) range. Therefore, an additional round\_normalize step is needed to round and then normalize this product to a 53 bit number in the [1, 2) interval. Interestingly, if the product overflows (i.e., great than 2), the exponent should also be updated (increased by 1) to compensate for the rounding and normalization as shown in Equation 2.5.

$$S_{Z} = S_{X} + S_{Y} = S_{X} \oplus S_{Y}$$

$$M_{Z} = round\_normalize(M_{X} \cdot M_{Y})$$

$$E_{Z} = \begin{cases} E_{X} + E_{Y} - B & \text{if } M_{X} \cdot M_{Y} \in [1, 2) \\ E_{X} + E_{Y} - B + 1 & \text{if } M_{X} \cdot M_{Y} \in [2, 4) \end{cases}$$

$$(2.5)$$

Figure 2.3 shows a block diagram detailing the overall generalized IEEE 754 multiplication architecture. The design consists of several stages: unpack (hidden bit and other exception and bit testing), sign, exponent and mantissa logic blocks and final result packing. As per the IEEE 754 standard, five flags are produced Infinite or Divide by 0 (I), Inexact (X), Invalid (V), Overflow (O) and Underflow (U). Some flags, such as Divide by 0, are not appropriate for floating-point multiplication as it is not possible. Regardless if a flag makes sense, correct IEEE 754 functional units produce all five flags.

Figure 2.3: Block diagram of multiplier

The first step in floating-point multiplication unpacks the IEEE numbers by finding the hidden bit as well as checking for any special cases (e.g., NaNs). Once this step is completed, the normalized operands are separated into four sub-fields: special values, sign, exponent, and mantissas. To compute the product sign, an XOR gate combines the operand sign bits. Simultaneously, the exponents are added and the bias subtracted to produce an intermediate exponent. Finally the intermediate exponent must be adjusted if the intermediate product in mantissa multiplication overflows into position [53] (since multiplication results in values greater than 2).

The mantissas are multiplied using a binary multiplier (as described in Section 2.3) that includes three steps: partial product generation to generate the partial product bits, partial production reduction to reduce the partial product bits to sum and carry vectors, and a carry propagate addition to add the sum and vectors to produce the product. The output of this stage is then fed into the rounding and normalization step.

Figure 2.4: Partial products matrix of multiplication

Finally, the result is packed into the IEEE 754 format and exceptions are generated, if necessary. The important and critical stage of rounding is required to correctly round the final result according to its predefined rounding mode. Most general-purpose processing units store the rounding mode in a separate states register [25].

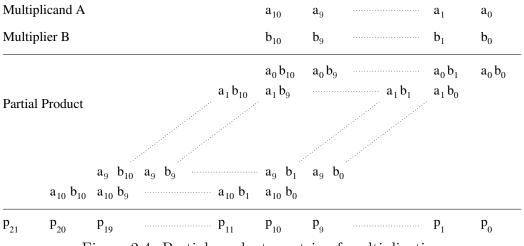

## 2.3 Mantissa Multiplication

A key step in the FP floating-point multiplication is the mantissa multiplication. Basically, given a m-bit multiplicand A and a n-bit multiplier B, the multiplication produces a (m+n)-bit product (i.e.,  $P=A\cdot B$ ). Figure 2.4 illustrates the multiplication of 11-bit half-precision mantissa using a partial product matrix diagram. In many cases when A, B, and P are large, the dot diagram, in which a dot represents a partial product bit, is often used for the sake of simplification [3].

Generally, multiplication includes three separate stages as follows:

- 1. Partial Product Generation (PPG) utilizes a collection of gates (e.g. AND gates) to generate the partial product bits  $a_i \cdot b_j$ .

- 2. Partial Product Reduction (PPR)- utilizes adders to reduce the partial products to sum and carry vectors.

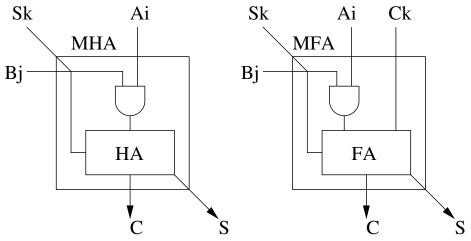

Figure 2.5: Modified half adder and full adder (Adopted from [3])

3. Final Carry Propagate Addition (CPA) - adds the sum and carry vectors to produce the final product.

High speed multipliers are typically classified into parallel multipliers and sequential multipliers. Since the mantissa multiplication is not the focus of this dissertation, only key parallel multipliers will be discussed briefly. The parallel multipliers can be classified further into array multipliers and tree multipliers.

## 2.3.1 Array Multipliers

Carry-Save Array Multipliers (CSAM) are a simple multiplier in which partial product bits are added in the array topology, similar to the paper-and-pencil multiplication process. The CSAM first generates partial product bits by utilizing AND gates and then uses an array of Carry-Save Adders (CSAs) to perform partial product reduction [3].

To perform Carry-Save Array Multiplication, adders are modified so that they can perform both partial product generation and addition. Two kind of modified adders are being used and called the modified half adder (MHA) and the modified full adder (MFA) as in Figure 2.5. The MHA consists of an AND gate to generate the partial product bit, followed by one half adder (HA) to add this partial product bit

Figure 2.6: Example of  $8 \times 8$ -bit carry-save array multiplier [3]

and another one from the previous row. Similarly, the MFA consists of an AND gate for generating partial product bit, followed by a full adder (FA) to add this partial product bit with the sum and carry from previous row. Given these modified adders, the CSAM can be implemented as in Figure 2.6.

Figure 2.7: Example of  $4 \times 4$ -bit Wallace tree multiplier (Adopted from [3])

## 2.3.2 Tree Multipliers

Tree multipliers use the tree topology for the partial product reduction stage. In particular, tree multipliers reduce the partial products down until their height is equal to 2 then apply a high-speed CPA to get the final result.

The first type of tree multiplier is called a Wallace tree multiplier that was introduced in 1964 [26]. Dadda multipliers [27] were later introduced one year after Wallace method to enhance Wallace method by reducing the number of reduction stages. Another tree multiplier to optimize the placement of adders called a column-compression multiplier has a smaller area and delay compared with both Wallace and Dadda methods [28]. Since the mantissa multiplication is not the focus of this dissertation, only Wallace multiplier will be discussed to understand the process in

tree multipliers as follows.

Basically, the Wallace method groups rows of partial product bits into sets of three [26]. Within each three row set, full adders reduce columns with three bits and half adders reduce columns with two bits. When used in multiplier trees, full adders and half adders are often referred to as (3,2) and (2,2) counters, respectively [3]. Rows that are not part of a three row set are transferred to the next reduction stage for subsequent reduction.

To visualize Wallace trees, a dot diagram of the multiplication matrix can be be used as in Figure 2.7 [3]. A dot represents a partial product bit. In addition, an uncrossed diagonal line represents the outputs of a FA (or (3,2) counter) and a crossed diagonal line represents the outputs of a HA (or (2,2) counter). An oval is also utilized to show the transition from reduction stages. As shown in Figure 2.7, this multiplier takes 2 reduction stages with matrix heights of 3 and 2. In the final stage, a fast CPA is utilized by adding these two arrays together to get final product. The total delay is proportional to the logarithm of the operand word length, therefore, tree multipliers are normally faster than array multipliers. However, they produce more congestion than CSAMs.

#### 2.4 Rounding for IEEE Floating Point Multiplication

The challenging part within IEEE 754 floating-point multiplication is the ability to round the result after the multiplier prodoes its output. Naive versions of rounding are easily implemented in hardware; however, the resulting hardware results in a long critical path due to the large carry chain lengths to produce an answer (i.e. approximately two full carry-propagate additions). Even though it is not presented in this dissertation, the IEEE 754-2008 standard has 128-bit (quad) support [2] that demands efficient hardware designs, especially for rounding within IEEE 754 floating-point multiplication. Consequently, the designs presented in this dissertation are

```

round_to_nearest (x.sig, x.rem) //RN mode

if (x.rem > 0.5)

return (x.sig + 1)

else if (x.rem < 0.5)

return (x.sig)

else if (x.rem == 0.5)

if (x.sig \text{ is even}) return x.sig

else if (x.sig \text{ is odd}) return (x.sig + 1)

round\_toward\_zero(x.sig, x.rem) //RZ mode

return x.siq

round_toward_positive(x.sig, x.rem) //RP mode

if (x.rem > 0 \text{ and } x \text{ positive})

return (x.siq + 1)

else return x.sig

round\_toward\_negative(x.sig, x.rem) //RM mode

if (x.rem > 0 \text{ and } x \text{ negative})

return (x.sig + 1)

else return x.sig

round\_toward\_infinity(x.sig, x.rem) //RI mode

if (x.rem > 0)

return (x.sig + 1)

else return x.sig

```

Figure 2.8: Rounding modes definition

important in reducing the critical path delay and optimizing the hardware.

The IEEE 754 2008 standard requires four rounding modes: roundTiesToEven(RN), roundTowardZero (RZ), roundTowardPositive (RP) and roundTowardNegative (RM) [1]. Figure 2.8 shows the pseudo-code for each rounding mode, given x.sig and x.rem are the significant part and remaining part, respectively. However, these four rounding modes can be reduced to three modes: RN, RZ and RI modes, in which RI is the

roundTowardInfinity mode [6]. In particular, the RP mode can be implemented as the RI mode for positive numbers and the RZ mode for negative numbers. Similarly, the RM mode can be implemented as the RZ mode for positive numbers and as the RI mode for negative numbers. Although the RN mode is default for the IEEE 754 standard, the other three rounding modes are important for methods for reliable computing [10, 24].

For binary implementations, three rounding modes can be implemented by using three bits named the least-significant bit 1, guard bit g and sticky bit t [12]. Subsequently, the intermediate product (P) is defined as the product of  $M_x$  and  $M_Y$ , where P is split into two sections, the mantissa  $(M_P)$  and remainder  $(REM_P)$ . The last bit 1 is defined as the least-significant bit of  $M_P$ , while the guard bit g is defined as the most significant bit of  $REM_P$ . The guard bit is utilized to avoid loss of precision usually a result of two closely representable numbers. Finally the sticky bit t is defined as the logical OR of all bits after g [12]. It is important to note that the dividing line between  $M_P$  and  $REM_P$  depends on the range of P. If P overflows the bits are all shifted to the left by 1 position. Together the three bits 1, g and t can be combined to check all comparisons required by all four rounding modes. Therefore, all rounding modes can be combined by a single rounding decision bit r to be added to the least significant bit of  $M_P$  utilizing the following simplified logic:

$$r = \begin{cases} 0 & \text{if } RZ \\ g \wedge (l \vee t) & \text{if } RN \\ g \vee t & \text{if } RI \end{cases}$$

(2.6)

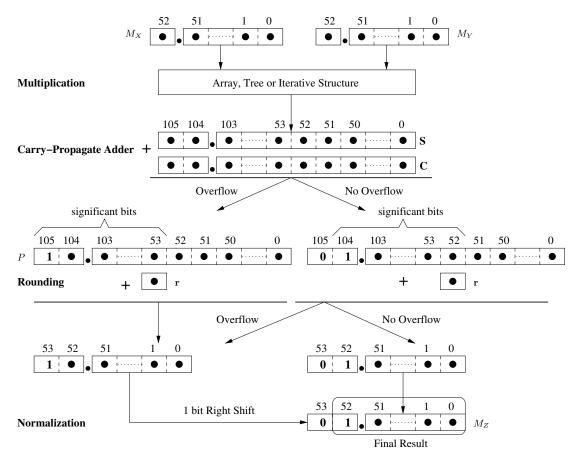

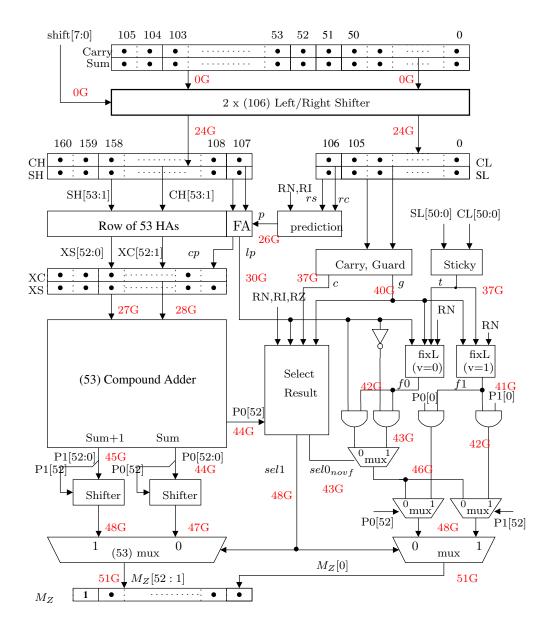

Based on this simple scheme, all IEEE rounding modes can be implemented as seen in Figure 2.9. Assuming  $M_X$  [52:0] and  $M_Y$  [52:0] are two 53-bit input-operand mantissas with hidden leading ones included  $(M_X[52] = M_Y[52] = 1)$ , a simple rounding

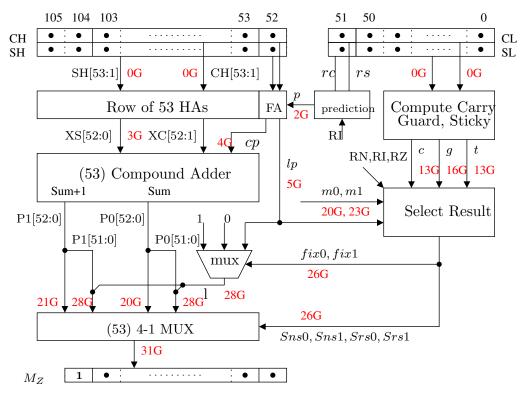

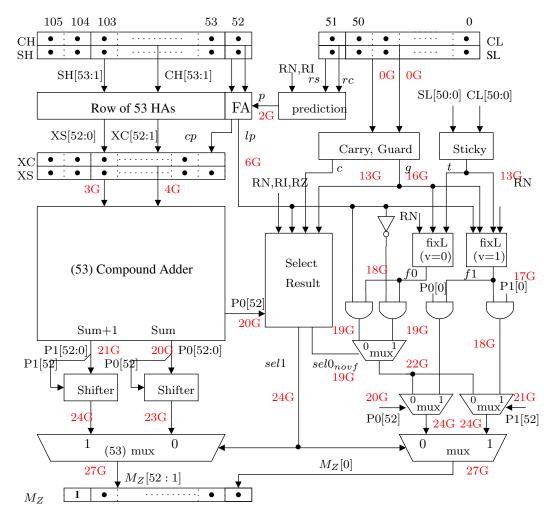

Figure 2.9: An implementation of four IEEE rounding modes (Adopted from [4]) scheme includes four steps is described as follows:

- Multiplication: The mantissa multiplication generates the partial products and then reduces to carry-save form that includes a 106-bit carry C[105:0] and a 106-bit sum S[105:0] vectors.

- Carry-Propagate Adder (CPA): The sum and carry vectors are added using a 106-bit carry-propagate adder (CPA) to generate the 106-bit exact product P[105:0].

- Rounding: P must then be rounded to 53 significant bits. First, the rounding decision bit r is computed based on (1, g, t) bits and rounding modes as in Equation 2.6. Assuming v = P[105]. If v = 0 (no overflow), l = P[52], g = P[51] and t is the logical OR of P[50:0]. if v = 1 (overflow), l = P[53], g = P[52]

Figure 2.10: An example of delay analysis for half adder

and t is the logical OR of P[51:0]. The rounding bit r is then added to the LSB (which is P[52] if there is no overflow and is P[53] if overflow) by a 54-bit carry-propagate adder (CPA).

• Normalization: Finally, the rounded product needs to be normalized (divided by 2) for the mantissa domain [1,2) by a right shift if it is equal to or larger than 2. If normalization is needed, then the exponent must be updated to not alter the final result.

This scheme is simple and straightforward. However, it requires one 106-bit CPA, another 53-bit CPA and normalization shifters that are performed in series. As a result, it is not optimal for high-performance designs.

## 2.5 Linear Delay Analysis

In this dissertation, several algorithms, including state-of-the-art algorithms and proposed algorithms, are discussed. Therefore, an important point to the presented algorithms is, how to characterize the algorithmic aspects of each implementation. Since the actual delay report from synthesis tool is technology-dependent and not always fair, in this dissertation, the linear delay analysis is also used to initially evaluate the delay of an algorithm.

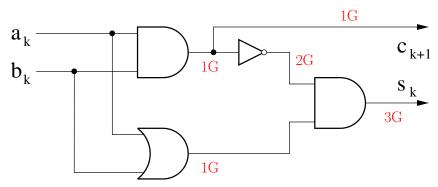

To make sure that each implementation is compared fairly, a given design will

be measured based on the gate delay unit [3]. One gate delay (1G) is the delay of AND, OR, and NOT gates. Other gates, such as XOR or MUX, will be derived from three basic gates. Although one could argue that the proposed delay numbers are not practical, these numbers give each implementation a specific cost that can allow a good algorithmic comparison. Moreover, these delay number can also be altered so that they are more practical and address circuit-level constraints.

Figure 2.10 shows an example of linear delay analysis for half adder. The delay is annotated along the way from the inputs  $(a_k, b_k)$  to the outputs  $(c_k, s_k)$ . Based on the Figure 2.10, the half adder has the following critical paths:

$$a_k, b_k \to c_k = 1G$$

$$a_k, b_k \to s_k = 3G$$

## 2.6 Chapter Summary

This chapter first introduces about the IEEE 754-2008 floating-point formats, rounding modes, and an overview about floating-point multiplication. In summary, compared to fixed-point multiplication, the IEEE 754 floating-point multiplication has a much-better range and radix point handling. However, it is also much more complicated and is the leading cause of round-off issues. In floating-point multiplication, rounding is arguably the most complicated component. Although multiplication in general and rounding in particular have been researched for many years, there are still room for architectural improvements that are discussed in following remaining chapters of this dissertation.

#### CHAPTER 3

# A COMBINED IEEE HALF- AND SINGLE-PRECISION FP MULTIPLIERS FOR DEEP LEARNING

## 3.1 Floating-Point Multipliers for Deep Learning

In recent years, deep learning has grown tremendously in its popularity and usefulness [8]. However, deep learning is computationally intensive, power-hungry and often limited by its hardware capability. Basically, deep learning is a deep neural network, which consists in convolutions and matrix multiplications. A typical example of deep learning is the convolutional neural network (CNN) that includes many convolution and max-pooling layers connected in series to extract features from input images/videos. In [9], authors show that 90% computation of CNN is due to convolution operations. Therefore, multipliers are the most space and power-hungry arithmetic operators of the digital implementation of a CNN. This is also true for other types of deep learning that heavily based on matrix multiplication.

Deep learning applications often requires computations with real numbers and therefore, requires fixed-point or floating-point representations. In comparison with fixed-point numbers, floating-point numbers have an advantage in representable range, which makes it suitable for a wider range of application [2]. Often, existing general-purpose CPUs/GPUs, and software implementations use single-precision floating-point (binary32) as the default format for these types of applications [29, 30, 31, 32].

However, recent research [18] shows that, in many applications, single-precision floating-point multipliers can be replaced by half-precision floating-point multipliers in training deep neural networks, which have little to no impact on the network accu-

racy. Because half-precision floating-point is only one-half of single-precision floating-point in terms of bit width, using half precision multipliers can save power, area, and delay. Typically, however, single-precision multipliers are still preferred in many cases when high accuracy are required or compatibility matters. Therefore, there is a need for using both single-precision and half-precision multipliers in implementing deep learning.

This chapter proposes a novel combined IEEE half-precision and single-precision multipliers for deep learning [33]. The combined multipliers is basically an IEEE-754 2008 compliant single-precision floating-point multipliers with additional logic to perform IEEE-compliant half precision multiplications. Our design can be easily configured to run in the half-precision mode for power saving or in the single-precision mode for accuracy. Compared to conventional IEEE single-precision multipliers, the combined multipliers require only a small amount of additional area and delay, while offer a significant reduction in power dissipation.

In [34], authors proposed a quadruple-precision floating-point multipliers that can perform one quadruple-precision multiplication, or two double-precision multiplication in parallel. In [35], authors proposed a double-precision floating-point multipliers that can perform one double-precision or two parallel single-precision multipliers. Here we propose a novel combined IEEE single and half-precision floating-point multipliers for deep learning applications.

#### 3.2 A Combined IEEE binary16 and binary32 Multipliers

Generally, the proposed design is an IEEE-754 2008 compliant single-precision floating-point multipliers with additional logic to perform IEEE-compliant half-precision multiplications. Our design can be easily configured to run in the half-precision mode for power saving or in the single-precision mode for accuracy. Using standard IEEE binary32 input operands, our combined multipliers include four inputs:

- 1. A 32-bit multiplicand A

- 2. A 32-bit multiplier B

- 3. A 2-bit rm control signal to select a specific mode among four supported IEEE-compliant rounding modes

- 4. A 1 bit op control logic is also enabled to switch between binary32 multipliers and binary16 multipliers

The outputs include:

- 1. A 32-bit product Z

- 2. A 5-bit IEEE-compliant floating-point flags F

When running in binary32 mode, inputs A and B and output Z are normal binary32 numbers. When running in binary16 mode, the first half the input operands of A, B and Z are binary16 numbers or word-aligned to the input operand. As described in the previous section, the sign computation is exactly the same for both binary32 and binary16 modes. Therefore, only exponent addition and mantissa multipliers need to be modified to adapt to binary16 multipliers.

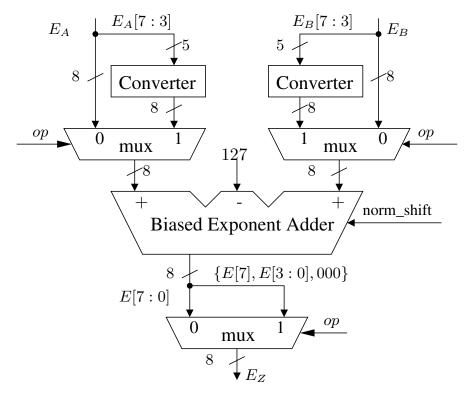

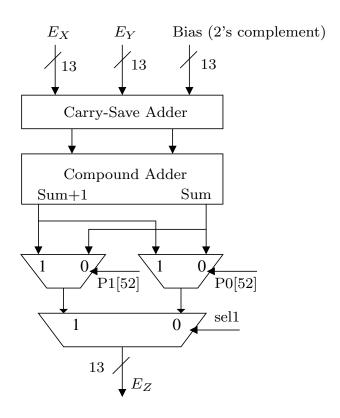

### 3.2.1 Exponent Addition

For this design,  $E_A = A[30:23]$  and  $E_B = B[30:23]$  are 8-bit input exponents. In binary32 mode, the 8-bit output exponent  $E_Z$  is basically the sum of  $E_A$  and  $E_B$  subtracted by the bias value 127. However, if there is an overflow in mantissa multiplication, the output exponent should be updated by adding 1 ulp (unit at the last place). This can be implemented effectively by using a 8-bit carry select adder (CSA) that compute the sum of biased exponent  $E_A$  and  $E_B$  with both carry in 0 and 1 in parallel. The correct output will be selected by the signal that indicate the normalization shift in the mantissa multiplication.

Figure 3.1: Converting binary16 exponent (5-bits) to binary32 exponent (8-bits)

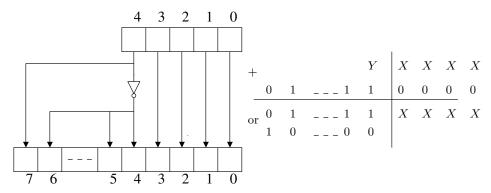

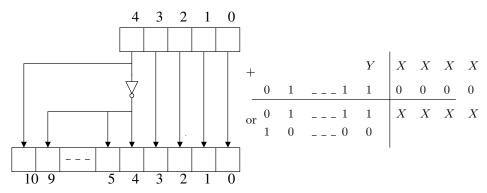

In binary16 mode, however, the exponents are only 5-bit width and the bias value is 15. Clearly, a minimum adjustment to the 8-bit CSA that can perform 5-bit exponent addition is desired. Therefore, a smart transformation is proposed to convert forward and backward between a 5-bit binary16 exponent and 8-bit binary32 exponent.

It is assumed  $E_{F16}$  and  $E_{F32}$  are the representation of the exponent  $E_F$  in the half-precision and single-precision formats respectively. Recall from the previous section that:

$$E_F = E_{F32} - 127 = E_{F16} - 15$$

As a result, the half-precision exponent can be converted to the single-precision exponent by figuring out the difference in their bias as following:

$$E_{F32} = E_{F16} - 15 + 127 = E_{F16} + 112$$

To implement this equation, a simple 8-bit adder can be used to add 112 to the half-precision exponent. However, there is a better solution. The difference of 112 (0111\_0000<sub>2</sub> in binary representation) can be adjusted in logic as in Figure 6.1. It can be seen that the last 4 significant bits of  $E_{F32}$  are the same as the last 4 significant bits of  $E_{F16}$ . The most 4 significant bits of  $E_{F32}$  can be either 0111 or 1000 when the most significant bit Y of  $E_{F16}$  is 0 or 1 correspondingly. This is implemented by

Figure 3.2: A combined IEEE half and single-precision exponent addition simply using an inverter gate as seen in the Figure 3.1.

Based on this conversion method, the combined half and single precision exponent addition design is shown in Figure 3.2. In the binary32 mode (op = 0), this design utilizes a standard binary32 exponent addition. The biased exponent adder is the 8-bit Carry-Select Adder that computes  $E_A + E_B - 127$  and  $E_A + E_B - 127 + 1$  in parallel. If a normalization shift is required in the mantissa multiplication  $(norm\_shift = 1)$ , the output exponent  $E_Z$  is  $E_A + E_B - 127 + 1$ . Otherwise, the output exponent  $E_Z$  is  $E_A + E_B - 127 + 1$ . Otherwise, the output exponent  $E_Z$  is  $E_A + E_B - 127 + 1$ .

In binary16 mode (op = 1), the 5-bit half-precision exponents  $E_A[7:3]$  and  $E_B[7:3]$  are first converted to 8-bit single precision exponents using the converters as in Figure 6.1. The 8-bit output exponent E[7:0] is finally converted back to half-precision exponent by taking only the most significant bit and the last 4 significant bits. Clearly, by using this scheme, minimal overhead is required to perform both single and half-precision exponent addition.

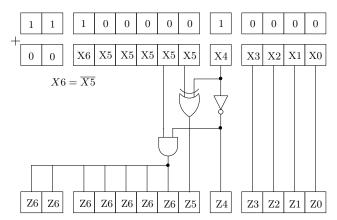

### 3.2.2 Mantissa Multipliers

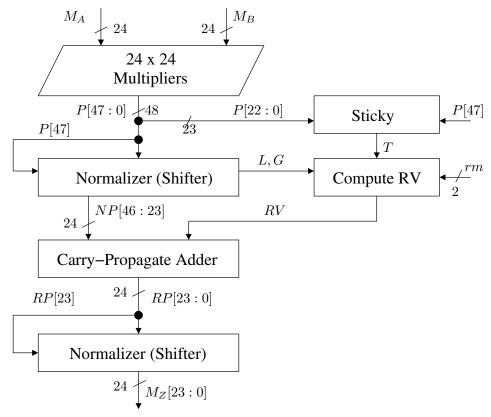

It is assumed that  $M_A[23:0]$  and  $M_B[23:0]$  are the two 24-bit input mantissas with hidden leading one included  $(M_A[23] = M_B[23] = 1)$ . In binary32 mode, the mantissa multiplication basically includes a  $24 \times 24$  multipliers that compute the product P of two input mantissas  $M_A$  and  $M_B$ , followed by a rounding and normalization logic to round and normalize P to the 24-bit output mantissa  $M_Z$ .

Recall that the IEEE 754 standard defines four rounding modes to be supported: round-to-nearest (RN), round-toward-zero (RZ), round-toward  $+\infty$  (RP) and round-toward  $-\infty$  (RM). Although RN is default for the IEEE 754 standard and most implementations, the other three rounding modes are important for methods in reliable computing [10]. In binary implementation, this can be done by using four bits named sign bit S, last bit L, guard bit G and sticky bit T [12]. Using (S, L, G, T) bits, four rounding modes can be combined by a single rounding decision bit RV to be added to the least significant bit:

$$RV = \begin{cases} 0 & \text{if } RZ \\ G \wedge (L \vee T) & \text{if } RN \\ \overline{S} \wedge (G \vee T) & \text{if } RP \end{cases}$$

$$S \wedge (G \vee T) & \text{if } RM$$

$$(3.1)$$

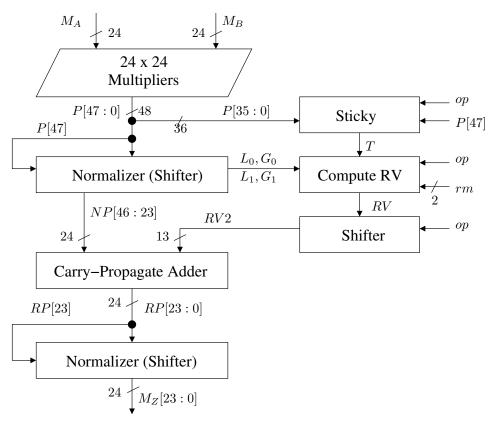

Using the rounding scheme above, the mantissa multiplication for binary32 can be implemented as in Figure 3.3. This implementation includes four steps as follows:

- 1. Compute 48-bit exact product P using a  $24 \times 24$  multipliers

- 2. Normalize P to domain [1,2) if needed. Since  $1 \le M_A$ ,  $M_B < 2$ , product P is in [1,4) range. If  $P \ge 2$  (P[47]=1), overflow occurs. A normalization by shifting one position to the right is needed to produce normalized product  $NP[47:0] \in [1,2)$ .

Figure 3.3: Mantissa multipliers for single-precision

3. Round the normalized product (NP) to a rounded product (RP). The last bit L and guard bit G are taken directly from NP as follows:

$$L = NP[23]; G = NP[22]$$

The sticky bit T is computed in parallel with normalization as follows:

$$T = \begin{cases} OR(P[21:0]) & \text{if no overflow}(P[47]=0) \\ OR(P[22:0]) & \text{if overflow}(P[47]=1) \end{cases}$$

The rounding decision (RV) is then computed based on rounding modes as in Equation 3.1. The sign S in equation is the sign  $S_Z$  of the output Z. A 24-bit Carry-Propagate Adder (CPA) is then used to add RV to normalized product NP to produce 24 -bit rounded product RP.

Figure 3.4: Modifed mantissa multipliers

4. Finally, the rounded product (RP) needs to be normalized if overflow occurs (RP[23] = 1) due to rounding. Hence, another conditional shifter is used to right shift RP one bit to produce the final result  $M_Z[23:0]$ .

This implementation can be adjusted to perform both binary32 and binary16 mantissa multiplication, as in Figure 3.4. It is worth to notice that in binary16 mode, the 11-bit mantissa is left-aligned in the 24-bit mantissas. This is commonly done with most floating-point representations in most general-purpose processors [36]. In comparison with the binary32 multipliers, the combined multipliers changes only in the rounding step (step 3 in binary32 multipliers) as follows:

1. Sticky: The Sticky logic is modified to compute stick bit T for both modes. In

binary16 mode (op = 1):

$$T = \begin{cases} OR(P[34:25]) & \text{if no overflow}(P[47]=0) \\ OR(P[35:25]) & \text{if overflow}(P[47]=1) \end{cases}$$

2. Compute RV: Use the last bit  $L_0$  and the guard bit  $G_0$  when op = 0 and  $L_1$  and  $G_1$  when op = 1.  $L_0$  and  $G_0$  are the same as L and G in binary32 multipliers while  $L_1$  and  $G_1$  are computed as follows:

$$L_1 = NP[36]; G_1 = NP[35]$$

3. Shifter: Once the rounding value RV available, it should be added to the least significant bit that is NP[23] in binary32 mode and NP[36] in binary16 mode. Therefore, a 13-bit left shifter is used to shift RV to the right position for each mode.

### 3.3 Experimental Results

The proposed multipliers are implemented in RTL- compliant Verilog and then synthesized in an ARM 32nm CMOS library in IBM/GF cmos32soi technology. The ARM standard-cell library utilizes multiple values of  $V_T$  to aid in synthesis (i.e., MTC-MOS). Synthesis was optimized for delay utilizing Synopsys<sup>®</sup> Design Compiler<sup>TM</sup> (DC) in topographical mode and loaded by ARM-based flip-flops using a PVT process

Table 3.1: Post-synthesis results for the proposed design in cmos32soi 32nm IBM/GF technology

| Multipliers                    | Power [uW] |           | Area [um <sup>2</sup> ] | Doloy [pg] |            |

|--------------------------------|------------|-----------|-------------------------|------------|------------|

| Withtipliers                   | Dynamic    | Static    | Total                   | Area [um]  | Deray [ps] |

| DW_fp_mult (binary32)          | 778.582    | 1,029.175 | 1,808.757               | 5,162.742  | 484.179    |

| Combined Mulipliers (binary32) | 558.654    | 680.775   | 1,239.429               | 3,309.228  | 454.004    |

| Combined Mulipliers (binary16) | 151.501    | 666.142   | 817.643                 | 3,309.228  | 454.004    |

at 25° C using TT corners. The average power estimation was achieved by running the simulation on 50,000 random test vectors generated by TestFloat-3b [37]. Because there are no existing similar designs, this chapter compares the results versus a Synopsys® DesignWare<sup>TM</sup> (DW) binary32 multiplier implementation. The Synopsys DW unit only contains a IEEE- compliant single-precision unit and this implementation has advantages in providing both operations configurable by input control bits. The area, delay, and power dissipation of each of these multipliers are found in Table 3.1. As shown in the Table 3.1, the binary 16 mode can save 44% power compared to binary 32 mode and save 55% power compared to Synopsys DesignWare multipliers. Technically, the RTL-level implementations also employ DesignWare elements as they are coded to take ad- vantage of DesignWare, but at a lower level of hierarchy and an with some additional ancillary logic discussed in this chapter.

## 3.4 Chapter Summary

In summary, a combined IEEE binary32 and binary16 multipliers is presented for many deep learning implementations in which binary16 can be safely used to train and run a network. With a configurable control signal, our proposed multipliers can be easily configured to switch between single and half-precision IEEE floating-point modes. This design is completely verified with Hauser's SoftFloat scheme for the correctness. Compared to the IEEE standard binary32 multipliers, the proposed multipliers has a small overhead while provide a significant savings of 44% in power dissipation when running in binary16 mode.

#### CHAPTER 4

# A NOVEL ROUNDING SCHEME FOR IEEE-COMPLIANT FP MULTIPLICATION

This chapter first introduces the state-of-the-art in rounding for IEEE 754 Floating Point Multiplication. The previously-used methods described in Section 4.1 all optimize on the most delay-intensive portion of the computation: rounding. Consequently, most of the methods for optimizing here are optimizing rounding for the output of the multiplier unit, usually produced in carry-save notation (i.e., carry/sum). Any of these method can be utilized with different multiplier algorithms and consequently impact other areas related to use of floating-point multiplication such as energy and power dissipation. However, the major contribution of this dissertation is improving the rounding unit for delay optimization [19, 38].

### 4.1 Previous Work

## 4.1.1 Santoro, Bewick and Horowitz (SBH) Method

An early optimization for floating-point multiplication architectures, Santoro, Bewick and Horowitz [4] (SBH) demonstrate a method that reduces the hardware requirements to a single compound adder (CA) and small amount of support logic. The most significant contribution of their work demonstrates how to perform most of the rounding and post-normalization in parallel, thereby, removing a carry propagate adder from the critical path. Compound adders take advantage of utilizing redundant hardware and its use is critical in optimizing hardware for any implementation [39]. Normally, compound adders use the same hardware except for critical components,

Figure 4.1: SBH [4] implementation of RZ mode

such as the carry-chain logic [4].

As with most floating-point units, designs can optimize the critical path by computing the carry and save portions of the multiplier [12]. Consequently, SBH's method utilizes the upper 54 most significant bits for SH, CH (PH = SH + CH) and the the 52 least significant bits for SL, CL (PL = SL + CL), respectively. Additional bits are utilized to help optimize the final result, such as the MSB (v), LSB (1), guard bit (g) and the sticky bit (t) of the exact product P.

#### 4.1.1.1 RZ mode

For RZ mode, since the rounding bit r=0, the rounded product is simply the exact product truncated to the 52 least-significant bits. To speed up performance, it is desirable to perform the computation of significant part SH, CH and remaining part SL, CL in parallel. Since c is only available after the addition of SL and CL, a compound adder (CA) can be used to pre-compute both PH and PH+1 in parallel as shown in Figure 4.1. Subsequently, two right shifters are used to normalize PH and PH+1, respectively, if they overflow. The carry-in c can then be used to select the correct output from the two normalized products.

Figure 4.2: A simple implementation of RNU mode

## 4.1.1.2 RN mode

The RN mode is arguably the most complicated mode compared to RZ and RI modes. The method within SBH smartly designs for round-to-nearest/up (RNU) mode (roundTiesToAway mode in IEEE 754-2008 standard) and then modifies the design to produce RN mode. The RNU mode is RN mode except in case of tie (x.rem = 0.5) where RNU mode always rounds up. In terms of implementation, RNU can be implemented by simply adding 1 to the guard bit position. The implementation in Figure 2.9 can be modified to perform RNU mode as shown in Figure 4.2.

Although simpler than RN, RNU mode is still far more complicated than RZ mode. To compute SH, CH in parallel with SL, CL, the total value *INC* is required to add to the ulp of SH, CH. This INC is the sum of carry c from SL, CL and the rounding value to be added to the exact product as illustrated in Claim 1.

Claim 1. In RNU mode,

$$INC = \begin{cases} c+g & \text{if no overflow } v=0\\ c+1 & \text{if overflow } v=1 \end{cases}$$

(4.1)

*Proof.* If there is no overflow, RNU rounds up (i.e., adds 1 to the LSB of SH, CH) if and only if g = 1. Therefore, INC = c + g. If overflow occurs, rounding then adds 1 to the guard bit position, which is now the LSB of SH and CH. Therefore, INC = c + 1.

From Equation 4.1, *INC* can be 0, 1, or 2. The naive solution pre-computes all three possible outputs PH, PH+1 and PH+2 using INC to select the correct rounded product. However, based on Claim 2 below, the standard CA can be used as in RZ mode.

Claim 2. Assuming rs, rc is the MSB of SL, CL, respectively, the prediction bit  $p = rs \lor rc$  produces:

$$INC \in \begin{cases} \{0,1\} & \text{if } p = 0\\ \{1,2\} & \text{if } p = 1 \end{cases}$$

(4.2)

Proof. If p=0, then rs=rc=0. As a result, the sum of SL and CL produces no carry out. In other words, c=0. Therefore, INC is INC=g or INC=1 and in both cases,  $INC \in 0, 1$ . If p=1, it is obvious for the overflow case to compute  $INC \in 1, 2$ . In the no overflow case, because  $rs+rc \geq 1$ , c and g cannot be both zeros. As a result,  $INC \in 1, 2$ .

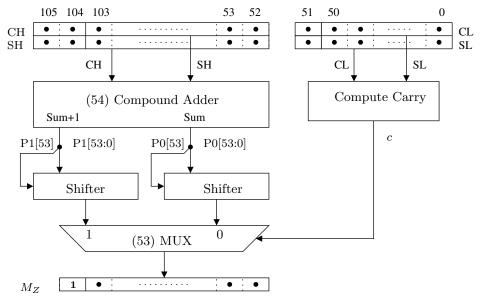

Based on this observation, SBH's method uses the 2 outputs of a CA as shown in Figure 4.3. A row of 54 half-adders (HAs) is used to make room for a prediction bit p before the CA. If p = 0, the outputs P0, P1 of the CA are (PH, PH+1). If p = 1,

Figure 4.3: SBH [4] method for RNU mode

the outputs of CA are effectively (PH+1, PH+2).

Once all possible rounded products P0 and P1 have been computed, the correct result can be selected. As explained in [4], the correct rounded product depends on INC, which in turn depends on c, g and the overflow bit v, as in Equation 4.1. At this point, both g, c bits should be available from the **Compute Carry Guard** module. However, a designer still needs to identify the correct overflow bit v, which is the MSB of the exact product P. The original SBH method requires additional logic to select the correct overflow bit v between two MSBs  $v_0$ ,  $v_1$  of P0 and P1. However, based on the Claim 3 below, this logic can be removed safely for optimization.

Claim 3. To select the correct output,  $v_0 = P0[53]$  can be treated as v in Equation 4.1.

*Proof.* Recall that v is the MSB of the exact product P (PH+c) while v0 is the MSB

Table 4.1: Compound adder output selection for RNU modes

| p | INC | Correct Output | sel |

|---|-----|----------------|-----|

| 0 | 0   | PH             | 0   |

| 0 | 1   | PH+1           | 1   |

| 1 | 1   | PH+1           | 0   |

| 1 | 2   | PH+2           | 1   |

of PH + p. Therefore, the claim is obvious if p = c and p and c need to be examined whether they are different. This happens only when p = 1 and c = 0. However, in this case, g = 1 because rs + rc = 1. Therefore, according to Equation 4.1, INC = 1 regardless of the value of v.

Based on this observation, Table 4.1 shows the value of sel to select the CA output correctly. Interestingly, if p = 0 then sel equals INC, whereas, if p = 1, because a prediction bit 1 is pre-added, the sel should be equal to INC - 1. This can be implemented by using an XOR gate. Moreover, post-normalization can be performed before the final selection to speed up the performance.

## 4.1.1.3 RI mode

For designs based on RNU mode instead of the original RN mode, SBH's method requires only a single CA that can produce 2 rounded products (PH, PH+1) or (PH+1, PH+2) in parallel. However, this design does not work for RI mode.

#### Claim 4. In RI mode:

$$INC = \begin{cases} c + (g \lor t) & \text{if no overflow } v = 0\\ c + 2 \cdot (l \lor g \lor t) & \text{if overflow } v = 1 \end{cases}$$

$$(4.3)$$

*Proof.* If no overflow occurs, from Equation 2.6, a rounding decision is added  $r = (g \lor t)$  to last bit position 52. Therefore, in this case,  $INC = c + (g \lor t)$ . If overflow occurs, because of a normalization shift, the last bit position now is 53. Therefore,

Figure 4.4: QTF [5] method implementation for all IEEE modes

the rounding decision  $r = (l \lor g \lor t)$  is added to bit 53. This is equivalent to adding  $2 \cdot (l \lor g \lor t)$  to INC.

From Equation 4.3, it can be seen that the total carry INC can be 0, 1, 2 or 3. As a result, the significant part logic has to be able to pre-compute all 4 outputs from PH to PH+3 to implement the RI mode. However, as described in the previous section, SBH's method only determines 3 outputs from PH to PH+2 and, therefore, it does not work for RI mode.

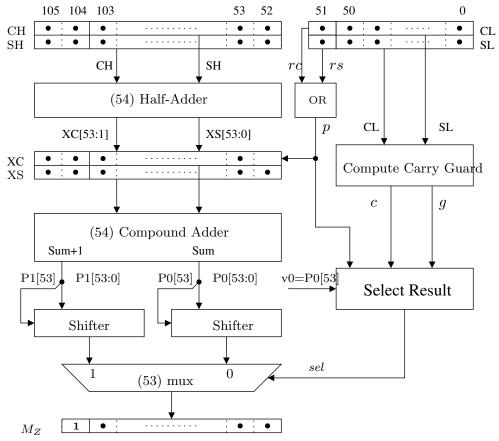

## 4.1.2 Quach, Takagi and Flynn (QTF) Method

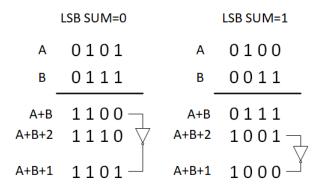

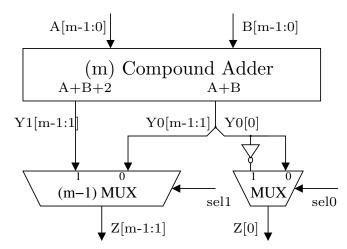

The limitation of SBH's method in implementing RI mode comes from the limitation of the original 2 outputs from the CA (Sum, Sum+1). To solve this problem, QTF's method proposes a special CA that is able to pre-compute 3 outputs (Sum, Sum+1, Sum+2) in parallel [5]. In general, this special compound adder computes only (Sum,

Figure 4.5: Two examles illustrating how third sum is obtained with only two carry chains

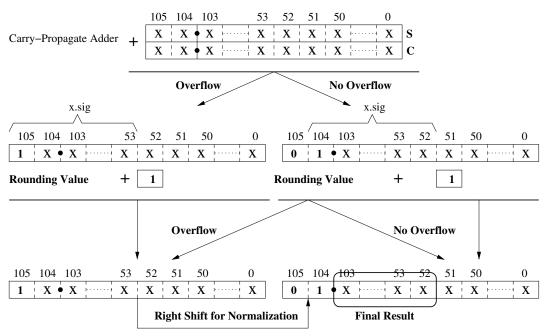

Sum+2) in parallel and includes a small amount of additional logic to generate (Sum+1) from Sum and Sum+2. Given 1 is the LSB of output Sum, it is easy to see that 1 is also the LSB of output Sum+2. When l=0, Sum+1 can be generated by selecting Sum that changes the last bit from 0 to 1. When l=1,Sum+1 can be generated by selecting Sum+2 that changes the last bit from 1 to 0. This trick is useful in that it can be utilized instead of using another adder (e.g., carry-select/increment adder) by inverting the least-significant bit of the calculated sums. It also has the advantage of consuming a small amount of additional logic (i.e., an inverter) and no impact upon the critical path. This is shown in Figure 4.5 where the LSB is used to determine if the LSB is inverted or not depending on whether the LSB is even or odd.

The method by Quach, Takagi and Flynn (QTF) replaces the LSB of the half adder row in the SBH method by a full adder (FA) [5]. The inputs to this FA are CH[0], SH[0] and the prediction bit p. The carry out cp of the FA feeds into the LSB of the CA while the sum of the FA serves as the 1p bit. The 54-bit CA in the SBH method is subsequently reduced to a 53-bit compound adder (CA). The input to this CA comes from a 53-bit half adder row. This arrangement allows the CA to effectively compute PH and PH+2 directly and generate PH+1 from PH and PH+2. A 3:1 multiplexor (mux) is used to select the correct LSB by keeping the 1p or setting it to 0 or 1. The fix0, fix1 signals determine when 1p should be not changed or set

to 0 and 1, respectively.

## 4.1.2.1 Errors in Quach, Takagi and Flynn Hardware

To produce the correct result, a final-selection 4:1 mux selects from the high order 53 bits of P0 and P1 (if overflow occurs) and the lower order 53 bits of P0 and P1 (if no overflow occurs). It is worth noticing that the LSB of the lower order values are from the 3:1 mux as shown in Figure 4.4. Four control signals Sns0, Sns1, Srs0, Srs1 are used to select the correct output. For Sns0 = 1 and Sns1 = 0, the lower order bits of P0 and P1 are selected if there is no overflow. Similarly, Srs0 = 1 and Srs1 = 1 select the higher order bits of P0, P1, respectively, if an overflow occurs. To examine the no overflow/overflow condition, QTF's method uses two bits m0, m1 that are selected as the MSB of P0 and P1, respectively. Two bits n0, n1 are the second-to-least significant bits of P0 and P1 and serve as the last bit in an overflow case. However, QTF's assertion is false with m0 = 0 and m1 = 1 as shown as shown in Claim 5 below:

Claim 5. The QTF method utilizes control signals in RN mode as follows (also,

given in [5] and verified/corrected as discussed later):

$$p = 0$$

$$l = lp$$

$$Sns0 = \overline{m0} \wedge \overline{c} \wedge (\overline{g} \vee \overline{l}) \vee \overline{m1} \wedge c \wedge \overline{g} \wedge \overline{l}$$

$$Sns1 = \overline{m0} \wedge \overline{c} \wedge g \wedge l \vee \overline{m1} \wedge c \wedge (g \vee l)$$

$$Srs0 = m0 \wedge \overline{c} \wedge (\overline{l} \vee \overline{g} \wedge \overline{n0} \wedge \overline{t})$$

$$\vee m1 \wedge c \wedge \overline{g} \wedge \overline{n1} \wedge \overline{l} \wedge \overline{t}$$

$$Srs1 = m0 \wedge l \wedge \overline{c} \wedge (n0 \vee t \vee g) \vee$$

$$m1 \wedge c \wedge (n1 \vee l \vee t \vee g)$$

$$fix0 = \overline{m0} \wedge l \wedge \overline{c} \wedge g \vee \overline{m1} \wedge l \wedge c \wedge (\overline{g} \vee \overline{t})$$

$$fix1 = \overline{m0} \wedge \overline{l} \wedge \overline{c} \wedge g \wedge t \vee \overline{m1} \wedge \overline{l} \wedge c \wedge \overline{g} \qquad (4.4)$$

Unfortunately, QTF's method produces false assertions when t = 1, g = 0, lp = 0, c = 1, m0 = 0 and m1 = 1.

Proof. When t = 1, g = 0, lp = 0, c = 1, m0 = 0 and m1 = 1, the correct output should be PH+1 because c = 1 and g = 0. Since lp = 0, PH+1 should be selected from PH (then assert lp = 1). In other words, Sns0 = 1 and fix1 = 1. However, according to the equations above, when the control signals Sns0 = 0, fix1 = 0 Srs1 = 1, results in selecting the wrong output PH+2.

The main reason for this is that with the special CA, the MSB of P1 can not be selected as m1 (i.e., defined as the MSB of PH+1). Recall that with a special CA, the output PH+1 can be selected from either PH or PH+2. Therefore, if lp = 0 (which means m1 should be the MSB of P0 instead), the equation will take the wrong m1 and then the wrong output. To fix this issue, additional logic is required to generate the

true m1 from the MSB of P0 and P1 as follows:

$$m1 = (lp \wedge P1[53]) \vee (\overline{lp} \wedge P0[53]) \tag{4.5}$$

This can introduce some delay and complicate the Boolean equation for this control signal but only minimally.

## 4.1.2.2 Linear Delay Analysis

Since the actual delay is technology-dependent and not always fair and intuitive, in this section, we perform the linear delay analysis that based on the gate delay unit. One gate delay (1G) is the delay of AND, OR and NOT gates. The Carry and Sum vector bits are assumed available at the same time 0G

- MUX and XOR gates take 3 gate delay (3G)

- The 53-bit Compound Adder is implemented using parallel prefix adder. The output Sum is valid after  $4+2\cdot\log_2(53)=16$  gate delay. The output Sum+1 is valid after  $5+2\cdot\log_2(53)=17$  gate delay.

- Similarly, Carry c and Guard g are also generated using 52 -bit parallel prefix adder. The Guard g is valid after  $4 + 2 \cdot \log_2(52) = 16$  gate delay. The Carry c is valid after  $1 + 2 \cdot \log_2(52) = 13$  gate delay.

- Sticky t is generated using the trick as in [40]. The delay is  $7 + \log_2(52) = 13$  gate delay.

Based on these assumptions, the timing estimation of QTF method is annotated in Figure 4.4. Since prediction bit p is valid after 2 gate delay and CH[0], SH[0] is valid after 0 gate delay, the FA carry out cp is valid after 4 gate delay make XC vector valid after 4 gate delay. The Compound Adder will provide P0 and P1 after 16 and

17 gate delay respectively. As a result, m0 is valid after 20 gate delay and m1 is valid after 23 gate delay based on Equation 4.5.

Carry c, Guard g and Sticky t are ready after 13, 16, 13 gate delay respectively. Because fix0, fix1 are computed using m0, m1, which adds 2 more gate delay, they are valid after 26 logic levels. Similarly, Sns0, Sns1, Srs0, Srs1 are valid after 26 logic levels.

fix0 and fix1 are used to select correct l that is only valid after 28 gate delay. Finally, the 4:1 mux will output  $M_Z$  after 31 gate delay.

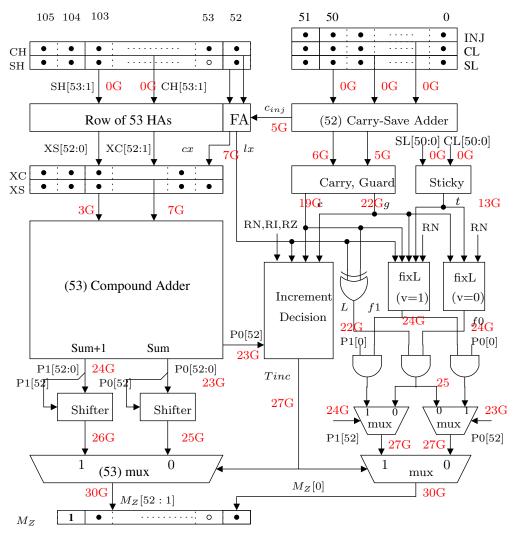

## 4.1.3 Even and Seidel (ES) Method

An efficient method called the Even/Seidel rounding algorithm (ES) works by reducing all rounding modes to a single truncation operation [41, 6]. The ES method adds an injection constant, depending only on the rounding mode, to the intermediate product such that all modes reduce to truncation at the rounding bit position. The injection constant (INJ) is defined as:

$$INJ = \begin{cases} 2^{-53} & \text{if RN} \\ 2^{-52} - 2^{-104} & \text{if RI} \\ 0 & \text{if RZ} \end{cases}$$

(4.6)

The ES algorithm provides little advice about implementing injection bits as well as computing the sticky t, guard g and carry c bits. For convenience, a block diagram of the injection hardware has been included in Figure 4.6. The vector INJ[51:0], whose value is assigned depending on each rounding mode, as in Equation 4.6, is injected into the lower part of the vector through a Carry-Save Adder. The carry out  $c_{inj}$  of this adder then feeds into a FA together with two LSBs of CH and SH, similar to the QTF method. The row of 53 HAs makes room for injecting the carry out of

Figure 4.6: ES [6] Method Implementation for Rounding

this FA. Finding g and c requires computing the carry propagate chain through all bits in the lower path (51:0), however, only the sum bit needs be generated at bit 51. Using the technique from [40], the sticky bit can be computed directly from its carry-save format as shown in Figure 4.6.

# 4.1.3.1 Optimization of Even-Seidel Rounding

To account for c carrying into the upper datapath and the overflow, the ES paper utilizes a special increment decision, Tinc (INC in [6]). The equation definition in the ES paper is correct; however, there is a small change in the implementation logic that

is needed within [6]. Tinc should increment when the majority of g, c, and 1x are high, and the mantissa has overflowed P0[52] = 1, and the rounding mode is RN. In the case of lx = 1, g = 1, and c = 0 the logic incorrectly sets Tinc = 0. The following equation correctly implements Tinc:

$$Tinc = \begin{cases} (c \land g \land RN) \lor (lx \land g \land RN) \\ \lor (c \land l \land (RZ \lor RN)) \\ \lor ((lx \lor c) \land RI) & \text{if } P0[52] = 0 \\ lx \land c & \text{if } P0[52] = 1 \end{cases}$$

$$(4.7)$$

In the case when the rounding mode is RN, the LSB needs to be corrected in a tie case (x.rem = 0.5 or g = 1, t = 0) and the LSB of exact product l = 1. This LSB is pulled down to 0 (even) by AND-ing it with a bit that equals to 0 only for a tie-case of RN. Two blocks fixL(v=1) and fixL(v=0) generate f1 and f0 to fix the LSB in case of overflow and no overflow, respectively.

$$f0 = \overline{g} \vee t \vee \overline{RN}$$