# Verilog implementation of the VESA DSC compression algorithm

Carlos Alberto Pereira Ferreira

Mestrado Integrado em Engenharia Eletrotécnica e de Computadores

Supervisor at FEUP: Prof. José Carlos Alves

Supervisor at Synopsys: Eng. Rui Raínho Almeida

# Resumo

Ao longo do tempo, tem havido um aumento das resoluções suportadas pelos dispositivos multimédia. Para além disso, do ponto de vista da indústria, é vantajoso prolongar o uso das interfaces de vídeo existentes, o que garante a compatibilidade com dispositivos existentes e ao mesmo tempo assegurar o suporte de novos formatos de vídeo de maior resolução.

As técnicas de compressão permitem reduzir a informação redundante existente em sinais de vídeo. Os sinais de vídeo possuem informação que o sistema visual humano não consegue processar, logo, ao eliminar essa informação, os requisitos de largura de banda diminuem. Esta diminuição de largura de banda necessária, permite prolongar a longevidade das interfaces existentes como por exemplo, o HDMI.

O objectivo desta dissertação é implementar o algoritmo de compressão VESA DSC. É necessário que a implementação seja capaz de processar o formato de vídeo 4K (no caso das tecnologias de 28nm e 40nm) e o formato de vídeo FullHD no caso da implementação em FPGA (Xilinx Virtex-7 XC7VX690TFFG1926-2).

Antes de descrever o funcionamento do codificador DSC, são apresentados conceitos básicos da teoria de compressão de vídeo, assim como, algum trabalho na área. A descrição do funcionamento do DSC é complementada com a exposição de detalhes de implementação que requerem alguma tomada de decisão ou que implicam um trade-off entre requisitos incompatíveis.

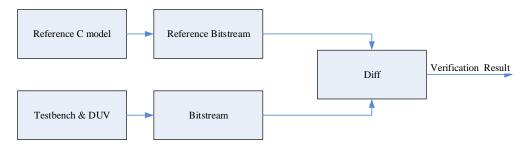

O algoritmo foi validado funcionalmente através da comparação com os resultados produzidos por um modelo de referência em C. Fazendo uma média entre os diversos tipos de "cobertura" de código, a pontuação obtida é de 83.58%. Trabalho futuro irá melhorar estes resultados.

A frequência máxima de relógio para a tecnologia de 28nm é de 200MHz enquanto que para a de 40nm é de 145 MHz. No caso da FPGA, a frequência máxima é de 47 MHz. Conclui-se que é necessário usar várias instâncias do codificador a funcionar em paralelo para poder processar os formatos de vídeo exigidos.

# **Abstract**

Over the years, the demand for multimedia devices with higher resolutions has been increasing. Besides that, from the industry point of view, there is an interest in prolonging the use of existing video interfaces to guarantee the interoperability with existing devices while guaranteeing the support of new video formats with higher resolutions.

Compression techniques offer the opportunity of reducing the redundant information existing in video signals. Video signals possess information that the human visual system can not process, so, by eliminating it, the bandwidth requirements diminish. This diminish of bandwidth requirements, permits prolonging the longevity of existing interfaces, such as HDMI.

The dissertation objective is to implement the DSC encoder algorithm. It is required to be able to process 4K video signals in the 28nm and 40nm technologies and FullHD video signals in a FPGA (Xilinx Virtex-7 XC7VX690TFFG1926-2). Before discussing the operation of the DSC encoder, some basic concepts of video compression theory are discussed, and some work on the field is presented. The discussion of the basic principles of operation of the DSC encoder is complemented with a discussion of relevant implementation details that require some decision taking or imply trade-offs between conflicting requirements.

The algorithm was functionally validated by comparing it with the output of a reference C model. The tests performed permitted a score of 83.58%. This score value results from taking the average between the different types of coverage metrics. Future work will improve this result.

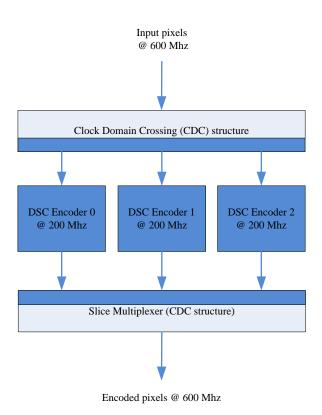

The maximum clock frequency achievable is 200 MHz for the 28nm technology and 145 MHz for the 40nm technology. Relative to the FPGA, the maximum achievable frequency is 47 MHz. It is concluded that it is necessary to use several encoder instances working in parallel to be able to process video signals with the desired resolutions.

# Acknowledgements

I would like to express my gratitude to my supervisor at FEUP, Professor José Carlos Alves for always being available to guide me through my dissertation. His insightful comments and writing revisions were of invaluable importance to me.

I would like to also express my gratitude to my supervisor at Synopsys, Eng. Rui Raínho Almeida for all the invaluable help he provided me in the implementation phase of my dissertation.

I thank all my colleagues at Synopsys. In particular, I am grateful to Eng. Tiago Campos for all the support he provided me.

To all my friends, a thank you very much, for all the support and motivation.

Last but not the least I want to thank my family for supporting me throughout my life. Without them I would not be able to stand where I am.

Carlos Alberto Pereira Ferreira

| "A common mistake that people make when | n trying to design something completely foolproof is<br>to underestimate the ingenuity of complete fools." |

|-----------------------------------------|------------------------------------------------------------------------------------------------------------|

|                                         | Douglas Noel Adams                                                                                         |

|                                         | Douglus I voel / Idulius                                                                                   |

|                                         |                                                                                                            |

|                                         |                                                                                                            |

|                                         |                                                                                                            |

|                                         |                                                                                                            |

|                                         |                                                                                                            |

|                                         |                                                                                                            |

# **Contents**

| 1 | Intr | oduction 1                                       |

|---|------|--------------------------------------------------|

|   | 1.1  | Context                                          |

|   | 1.2  | Motivation                                       |

|   | 1.3  | Objectives                                       |

|   | 1.4  | Document Outline                                 |

| 2 | Vide | eo compression 5                                 |

|   | 2.1  | Introduction                                     |

|   | 2.2  | Lossless compression                             |

|   | 2.3  | Lossy compression                                |

|   |      | 2.3.1 Spacial redundancy reduction               |

|   |      | 2.3.2 Temporal redundancy reduction              |

|   |      | 2.3.3 Transform Coding                           |

|   |      | 2.3.4 Quantization                               |

|   | 2.4  | Requirements                                     |

|   | 2.5  | Video Coding standards                           |

|   |      | 2.5.1 H.264/AVC                                  |

|   |      | 2.5.2 HEVC/H.265                                 |

|   |      | 2.5.3 MJPEG                                      |

|   | 2.6  | Distributed Video Coding                         |

|   | 2.7  | Machine Learning in Video Coding                 |

|   |      |                                                  |

| 3 | -    | olay Stream Compression 21                       |

|   | 3.1  | Overview                                         |

|   | 3.2  | RGB to YCoCg-R                                   |

|   | 3.3  | Buffer                                           |

|   | 3.4  | Predictors, Quantization and Reconstruction      |

|   |      | 3.4.1 Modified Median-Adaptive Prediction (MMAP) |

|   |      | 3.4.2 Block Prediction (BP)                      |

|   |      | 3.4.3 Midpoint Prediction (MPP)                  |

|   |      | 3.4.4 BP vs MMAP decision                        |

|   |      | 3.4.5 BP/MMAP vs MPP decision                    |

|   |      | 3.4.6 Quantization                               |

|   |      | 3.4.7 Inverse Quantization and Reconstruction    |

|   | 3.5  | Indexed Color History (ICH)                      |

|   | 3.6  | Line Buffer                                      |

|   | 3.7  | Entropy Encoder                                  |

|   | 3.8  | Substream Multiplexing                           |

X CONTENTS

|    | 3.9   |                                                  | 39         |

|----|-------|--------------------------------------------------|------------|

|    | 3.10  | Flatness Determination                           | 40         |

|    | 3.11  | Rate Control                                     | 41         |

| 4  | DSC   | Implementation                                   | 43         |

|    | 4.1   | Introduction                                     | 43         |

|    |       | 4.1.1 High-level Timing Diagram                  | 43         |

|    | 4.2   | RGB to YCoCg-R                                   | 45         |

|    | 4.3   | Buffer                                           | 45         |

|    | 4.4   | Predictors, Quantization and Reconstruction      | 45         |

|    |       | 4.4.1 Modified Median-Adaptive Prediction (MMAP) | 47         |

|    |       | 4.4.2 Block Prediction (BP)                      | 48         |

|    |       |                                                  | 48         |

|    |       | 4.4.4 BP vs MMAP decision                        | 48         |

|    |       | 4.4.5 BP/MMAP vs MPP decision                    | 48         |

|    |       | 4.4.6 Quantization                               | 48         |

|    |       | 4.4.7 Inverse Quantization and Reconstruction    | 49         |

|    | 4.5   | Indexed Color History (ICH)                      | 49         |

|    | 4.6   |                                                  | 51         |

|    | 4.7   |                                                  | 52         |

|    | 4.8   |                                                  | 54         |

|    | 4.9   |                                                  | 58         |

|    | 4.10  |                                                  | 59         |

|    |       |                                                  | 62         |

|    |       |                                                  | 63         |

| 5  | Resu  | ılts                                             | 65         |

|    | 5.1   | Test Results                                     | 65         |

|    | 5.2   |                                                  | 67         |

| 6  | Cone  | clusion                                          | <b>7</b> 1 |

| Re | feren | ces                                              | <b>73</b>  |

# **List of Figures**

| Typical video encoder block diagram                                       |

|---------------------------------------------------------------------------|

| Predictive coding example                                                 |

| Predictive coding example - cont                                          |

| DCT 8x8 Basis Images                                                      |

| Uniform quantizers                                                        |

| Raster scan order                                                         |

| Frame partitioned in slices                                               |

| DSC Encoder Architecture                                                  |

| The coding techniques of the DSC algorithm                                |

| Two images with distinct spatial frequency contents                       |

| Possible construction of the bitstream between the encoder and decoder 25 |

| Pixels require to predict the current group                               |

| Block Prediction application example                                      |

| Blocks of pixels used to perform the decision between MMAP/BP             |

| BP/MMAP vs MPP decision                                                   |

| ICH memory structure                                                      |

| ICH history entries update (P-mode group)                                 |

| ICH history entries update (ICH-group)                                    |

| ICH last line pixels update                                               |

| Entropy Encoder Unit for P-coded groups                                   |

| Substream multiplexer block diagram                                       |

| Decoder model                                                             |

| Pixes used in the flatness tests                                          |

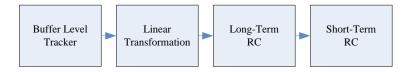

| Rate Control sub-blocks                                                   |

| Architecture of the DSC Encoder block implementation                      |

| DSC Encoder timing diagram                                                |

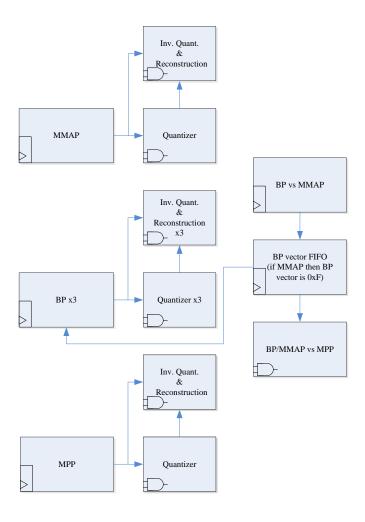

| Predictive coding top block                                               |

| Data dependencies between groups                                          |

| ICH block diagram                                                         |

| ICH timing diagram                                                        |

| ICH memory organization                                                   |

| "Divide-and-conquer" search algorithm                                     |

| ceil <sub>log2</sub> computation example                                  |

| Bitmask operations                                                        |

| Substream multiplexer top block                                           |

| Balance FIFO fragmentation                                                |

|                                                                           |

xii LIST OF FIGURES

| 4.13 | Balance FIFO operation                                   |

|------|----------------------------------------------------------|

| 4.14 | Substream multiplexer block timing example               |

| 4.15 | Substream Multiplexer FSM                                |

| 4.16 | One mux word per memory address                          |

| 4.17 | Several mux word per memory address                      |

| 4.18 | Read from two mux words at the same time 61              |

| 4.19 | Auxiliary buffers                                        |

| 4.20 | Rate Buffer FSM                                          |

| 4.21 | Rate Control block diagram                               |

| 4.22 | Flatness Determination timing                            |

| 4.23 | Flatness Determination block                             |

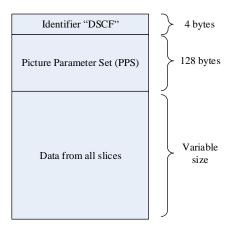

| 5.1  | .DSC file format                                         |

| 5.2  | Verification procedure                                   |

| 5.3  | Data dependencies between groups                         |

| 5.4  | Circuit representation of the operations being scheduled |

| 5.5  | Multiple encoder instances                               |

# **List of Tables**

| 2.1 | Storage/Transmission requirements for uncompressed data | 5  |

|-----|---------------------------------------------------------|----|

| 2.2 | ME algorithms comparison                                | 11 |

| 5.1 | Coverage results                                        | 66 |

| 5.2 | Synthesis results for the ASIC technologies             | 67 |

| 5.3 | FPGA (Xilinx Virtex-7 XC7VX690TFFG1926-2) results       | 67 |

| 5.4 | Schedule of operations                                  | 68 |

xiv LIST OF TABLES

# **Abbreviations**

ASIC Application Specific Integrated Circuit

AVC Advanced Video Coding

BP Block Prediction

bpc bits per component

bpp bits per pixel

CBR Constant Bit Rate

CODEC COderDECoder

DCT Discrete Cosine Transform

DP DisplayPort

DSC Display Stream Compression

DUV Device Under Verification

DVC Distributed Video Coding

DWT Discrete Walsh Transform

FIFO First In First Out

FPGA Field Programmable Gate Array

FSM Finit State Machine

HDMI High Definition Multimedia Interface

HEVC High Efficiency Video Coding

HVS Human Visual System ICH Indexed Color History

IEC International Electrotechnical Commission ISO International Organization for Standardization

ITU-T Telecommunication Standardization Sector of the International Telecommuni-

cations Union

JPEG Joint Photographic Experts Group MAD Mean Absolute Difference (MAD)

MB Macro Block

MCP Motion-compensated Prediction

ME Motion Estimation

MIPI CSI Mobile Industry Processor Interface Camera Serial Interface MIPI DSI Mobile Industry Processor Interface Display Serial Interface

MMAP Modified Median-Adaptive Prediction

MPEG Moving Picture Experts Group

MPP Midpoint Prediction

xvi Abbreviations

MSE Mean Square Error MV Motion Vector

PPS Picture Parameter Set

QoE Quality of Experience

QP Quantization Parameter

RC Rate Control

ROI Region-of-Interest

SAD Sum of Absolute Difference SIFT Scale Invariant Feature Transform

SR Shift Register

SSP Substream Processor

UHDTV Ultra High Definition Television

VBR Variable Bit Rate

VESA Video Electronics Standards Association

VLC Variable Length Code

VLSI Very-large-scale integration

# Chapter 1

# Introduction

#### 1.1 Context

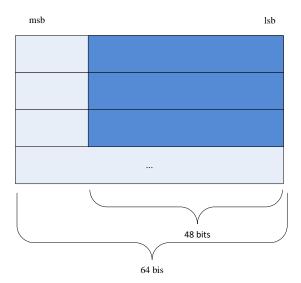

Over the years, display manufacturers have been increasing the resolution of their products to attend to the more exigent user requirements and of course to differentiate from other products in the market [1]. For example, High Definition Multimedia Interface 2.0 (HDMI 2.0), that implements the CEA-861F standard supports resolutions of 4096 x 2160p @ 60Hz [2] with 16 bits per pixel component (48 bits per pixel) which requires high a bandwidth (530.8 Mpixel/s which is approximately 25.48 Gbit/s) from the transport layer. Higher resolutions will be widely available in the future such as 8K, which means more exigent requirements for the transport layer, that implies more expensive data links, that consume more power and are much harder to implement [1].

One possible solution is to increase the number of data links between the source device and the sink device [1]. For example, if we increase four times the number of data lanes, then we can increase four times the number of bits per second or reduce the clock speed four times. The problem with this approach is that not only we increase the complexity of the hardware, but also existing connectors and cables (the physical layer) would not be compatible, which means that a new physical layer would have to be implemented.

Another approach to deal with the increasing bandwidth requirements, is to compress the video stream. Instead of sending raw data through the data link, as it is currently done with HDMI, we can take advantage of the characteristics of the Human Visual System (HVS) and remove information from the video stream that people will not perceive. For example, we can compress high frequency content without that being noticeable, but we must preserve low frequency content such as uniform regions in a video frame. Compression allows us to reduce the bandwidth requirements by reducing the amount of information being send through the data links, so changes aren't necessary to the physical layer of nowadays interfaces such as HDMI, DP e MIPI DSI/CSI.

VESA Display Stream Compression (DSC) standard specifies algorithms for compression and decompression of video streams [3]. Those streams are between two devices [3] such as BluRay disc player and a display. VESA DSC is compatible with HDMI, DP and MIPI DSI/CSI interfaces and is designed for working in real-time [3].

2 Introduction

## 1.2 Motivation

There are several video compression techniques available. Transform techniques map the input signal from the space-time domain representation to the frequency domain representation. The idea is to concentrate the energy of the input signal in the lower frequency components (the HVS is more sensible to low frequencies) and discard the high frequency coefficients [4]. Choosing a suitable transform function depends on the statistical properties of the signal. A popular transform function is the Discrete Cosine Transform (DCT) [4] and is used in many compression schemes such as H.264, MPEG-2, and JPEG.

Another type of transform is the wavelet transform, that maps the input signal to the time-scale domain [4], and has good performance with transient signals and is used, for example, in JPEG 2000.

Compression can also be lossless by reducing the statistical redundancy, which means representing the same information using fewer bits, using for example, Huffman codes, but the compression ratios are lower than lossy schemes. Lossless compression is based on information theory and is used in many compression schemes for audio and video, in conjunction with lossy techniques.

Movement estimation techniques can be used to remove redundancy between different frames of a video. If two consecutive frames are very similar, we only need to transmit the differences between them, which requires much less information than the whole frame.

As the reader can see, there are many compression schemes available that exploit the HVS and different types of redundancy existing in video signals, so at this point it is relevant to analyze why the necessity of another compression scheme, namely, the VESA DSC.

Many existing compression schemes are not visually lossless, which means the user can observe the degradation of quality. The current video compression methods are computationally expensive to implement because require storing many pixels in a buffer which increases the area of a integrated circuit, and some of them are proprietary [1]. If an algorithm is proprietary then the company who is making a new product may need to pay royalties for the algorithm, or instead use another algorithm, and the product will not be compatible with other products that implement the first algorithm. VESA DSC is a new video compression algorithm designed to be widely used in the industry (interoperable), visually lossless and low cost. The requirements that lead to the development of the VESA DSC, and that the existing compression schemes do not meet can be found on [1] and are:

- Compression should be visually lossless, which means that the user shouldn't perceive any degradation of video quality

- The algorithm should be able to work at low rates and support a constant data rate of compressed video

- Support handling sub-regions of a image (slices) that work as a single picture independent from other slices

1.3 Objectives 3

- Support different colour spaces, bits per pixel and sub-sampling schemes

- Work in real-time and inexpensive (in terms of memory requirements) to implement in hardware

# 1.3 Objectives

The objective of this dissertation is to build a digital implementation in Verilog HDL of the VESA DSC v1.1 Standard. The implementation must be synthesizable for ASIC (TSMC28 and TSMC40LP) and FPGA (Xilinx Virtex-7 XC7VX690TFFG1926-2) technologies.

It is desired to be able to process process 4K video signals in the ASIC technologies and FullHD<sup>1</sup> video in the FPGA implementation. This roughly corresponds to a pixel frequency of 600 MHz for the ASIC technologies and 300 MHz for the FPGA technology. It will be verified if it is possible to achieve this performance with one encoder instance. This implies that the implementation must be able to achieve a clock frequency of at least 600 MHz in the 28nm technology (ASIC) and 300 MHz in the FPGA. If it is not possible to achieve such frequency values, other solutions to overcome this problem will be explored, namely, the parallelization of the algorithm. Using several encoders in parallel it is possible to lower the clock frequency requirements at the expense of an increase in the circuit area.

## 1.4 Document Outline

This dissertation is organized as follows:

Chapter 2 discusses some basic concepts related to video compression theory. Some work related to other compression algorithms is also presented.

Chapter 3 explains the basic principles of working of the DSC encoder.

Chapter 4 deepens the discussion in chapter 3. It will be presented to the reader some interesting implementation details, that involve some decision making. Operations that are simply a direct implementation of the Standard are not discussed.

Chapter 5 starts by a discussion of the test procedure followed by the test coverage results. Finally, the synthesis results are exposed and discussed.

The document ends with the Conclusion chapter.

<sup>&</sup>lt;sup>1</sup>It is being considered a resolution of 1920 x 1080p @ 100 Hz.

4 Introduction

# Chapter 2

# Video compression

This chapter reviews some concepts about video compression theory. The requirements and challenges imposed by the recent ultra-hight resolution video formats will also be discussed. This chapter ends with a discussion of some existing solutions in the field of video compression and a brief reference to machine learning approaches to video compression, that significantly differ from "traditional" approaches.

## 2.1 Introduction

The amount of data needed to be stored and transmitted has been increasing over the time and nowadays it is almost impossible to do it without compression. Table 2.1 shows some requirements in terms of storage/transmission of typical applications, assuming that compression is not being used. In the case of the video stream, it is assumed that sub-sampling scheme is 4:4:4 and no blanking pixels are being used, which is a simplification that may not be valid in practice. Nevertheless it shows that compression schemes are essential.

Data compression algorithms, are used to reduce the number of bits required to represent data. There are two types of compression: *lossy* compression and *lossless* compression. In the case of lossy compression, the reconstructed data is different from the original data. In the case of lossless compression, the reconstructed data is the same as the original data. Typically lossy compression provides higher compression ratios (relationship between the original video data rate and the encoded video data rate) than lossless compression [5].

Table 2.1: Storage/Transmission requirements for uncompressed data.

| Application                                      | Bit rate       | Debit      |

|--------------------------------------------------|----------------|------------|

| (Standard Audio CD) 2 channel, 16 bit @ 44100 Hz | 1411.2 Kbits/s | 620.2 MB/h |

| 4k video (4096 x 2160p @ 60 Hz, 48 bit/pixel)    | 25.48 Gbit/s   | 11.47 TB/h |

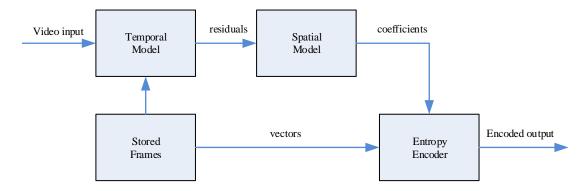

A typical encoder based from [6] is shown on figure 2.1. The decoder must take the inverse steps to recover the video sequence. The coder and decoder together are referred as CODEC [7]. Typically video compression schemes explore temporal and spacial redundancies existing

in video signals to reduce the bit rate. The entropy encoder in figure 2.1 reduces the amount of redundancies existing in the representation of information by representing the same information using fewer bits. In the following sections these topics will be further discussed.

Figure 2.1: Typical video encoder block diagram.

# 2.2 Lossless compression

When lossless compression is used, no information is lost. The decompressed signal is equal to the original one. To understand how lossless compression works, the must know some concepts of information theory. Information theory is a very complex and broad subject so, only some very rudimentary information will be presented here. More information can be found on Information Theory literature such as [8].

Equation 2.1, extracted from [8] represents the entropy of a random variable X whose probability density function (pdf) is p(x). Since the logarithm is in base two, the entropy is measured in bits.

$$H(X) = -\sum_{x} p(x) \log_2 p(x)$$

(2.1)

Analyzing equation 2.1 it resembles the equation of the expected value of a random variable. Indeed, entropy is the expected value of information because  $-log_2p(x) = log_2\frac{1}{p(x)}$  represents the amount of information of a given symbol x produce by source X, so entropy gives the minimum average number of bits to represent each x [9].

It is shown in [8] that the average number of bits L to represent some random variable X is greater or equal than the entropy:

$$L \ge H(X) \tag{2.2}$$

To understand the role of the previous results in data compression consider an example extracted from [9]. If a given picture as an uniform histogram and has 256 gray-level values, then the entropy is 8 bits. This result was expected because if there are 256 possible values, then with 8

bits we can "encode" exactly 256 "things". One should notice that in this example it is impossible to use less bits to represent each gray-level. This result agrees with equation 2.2.

Now let's consider another example extracted from [8] where p(x) is not uniform. The example consists of a horse race between 8 horses. Not all horses have the same probability of winning. The probability of each one winning is  $(\frac{1}{2}, \frac{1}{4}, \frac{1}{8}, \frac{1}{16}, \frac{1}{64}, \frac{1}{64}, \frac{1}{64}, \frac{1}{64}, \frac{1}{64})$ . The entropy is straightforward to compute and is 2 bits. Now consider the problem of sending the information which horse won the race. One can say that by using 3 bits, it is possible to transmit that information because  $2^3 = 8$ . But, if we use a variable number of bits, namely, using less bits to represent the horses which are more likely to win, then, on average less bits need to be transmitted. Using the result on equation 2.2 the average number of bits necessary is 2, which corresponds to the entropy.

Variable length coding (VLC) is used in many compression algorithms to reduce coding redundancy, which means using fewer bits to represent the same information without any information loss [6]. Huffman coding and arithmetic coding are two examples of variable length codes. Even lossy compression schemes typically use lossless techniques to achieve a further reduction in the bit rate, without diminishing the video quality. Lossless compression works well with synthetic images that have large areas of uniform color.

# 2.3 Lossy compression

As the name suggests, lossy compression implies loss of information. When developing a lossy compression scheme it is important to study the statistical properties of the signals that are going to be processed (in this dissertation it's video signals), to identify irrelevant information (redundant) that can be discarded without a major prejudice to the perceived quality. In video signals, spatial and temporal redundancies can be exploited for video compression [10].

Spatial redundancy is related to the similarity between pixels that are near each other within a frame. The more uniform a given region within a frame is, the more correlated the pixels are, and more opportunities for compression are available. In an extreme but unrealistic case, if in a given frame, all pixels are equal then only one pixel would be necessary to represent the frame, because the others pixels would be a replication of that same pixel.

Temporal redundancy is related to the similarity (correlation) between successive frames which tends to increase with the frame rate [10]. When the frame rate is high with respect to the movement of objects in the video scene, a substantial portion of two successive frames may be very similar. If instead of coding each frame individually, only the displacement is coded [7], then the amount of information to transmit/store diminishes. The information in the difference between adjacent frames may be further reduced by combining motion estimation with frame differentiating.

If we consider the characteristics of the Human Visual System (HVS), we have more opportunities to remove redundant data, namely, psychovisual redundant data [11]. Let's review some of the characteristics of the HVS and opportunities to eliminate unnecessary information:

• Contrast Sensitivity - If a signal has contrast below a threshold for a given frequency, the signal won't be detected by the HVS. The model used do describe this behavior is a low-pass filter. The HVS is less sensitive to errors in high frequency regions than in low frequency regions [12]. A high frequency region is described by rapid changes in color or brightness, while in low frequency regions, these changes are more smooth. Since our eyes behave like a low pass filter, high frequency content can be eliminated without diminishing the perceived quality.

- Masking The presence of a signal reduces the visibility of another signal. In the spatial

domain this means that a set of pixels with a small deviation from their correct values is

much harder to detect in a image region rich in textures than in a smooth area. In the

temporal domain, the masking effect is related to the difference in luminance between video

frames [12].

- Visual attention The HVS tends to focus on certain objects or regions of the video frame. For example, studies show that there is a natural tendency to look at the center of the scene and also to give attention to human faces. These regions that attract more attention are know as ROI (region-of-interest). The ROI should be encoded with higher quality, to diminish the compression impact in the perceived quality. There are several difficulties related to using the ROI because it requires using specialized hardware like a eye tracker or an expert must identify *a priori* these regions [13].

#### 2.3.1 Spacial redundancy reduction

In this section differential coding also know as predictive coding will be described.

As described earlier, video signals usually present high spatial and temporal redundancies. Due to these redundancies, it is more efficient to encode the difference between the input signal and it's prediction<sup>1</sup> instead of coding the input signal directly [14], as long as the prediction is a good representation of the pixel being coded. These "differential" pixels have a high probability of assuming small amplitudes (near zero), so less bits are required to represent the original information. It is important to underline the fact that differential coding by itself doesn't compress data, it's the quantization process, to be described later, that in fact compresses data.

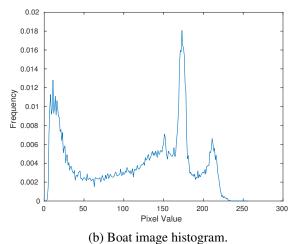

As an example of application, consider figure 2.2a and figure 2.2b that show the original image being coded and the respective histogram. As the reader can observe, the pixel values are well distributed in the range [0,255].

<sup>&</sup>lt;sup>1</sup>The prediction is constructed using information of previous pixels only.

(a) Original boat image.

(b) Boat illiage liistografi

Figure 2.2: Predictive coding example.

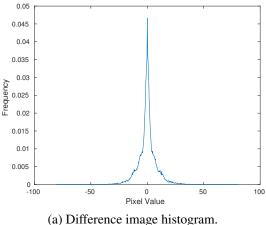

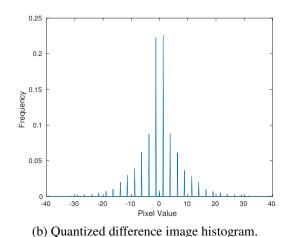

The difference image was determined, and the respective histogram is shown on figure 2.3a. As the reader can confirm, the pixel values are concentrated near zero, which implies a low variance. Figure 2.3b shows the histogram after applying a quantization operation on the difference image. The number of bits used to represent the information is 5, so, only 32 values of amplitude are available, which modifies the histogram.

Figure 2.3: Predictive coding example - cont.

## 2.3.2 Temporal redundancy reduction

As stated earlier, video signals usually possess high temporal redundancy. The frame rate of a video is typically high with respect to the image moving scenes, and by that reason, most of the contents of consecutive frames are very identical. Instead of coding the two consecutive frames as being independent [9], it is possible to take an approach similar to the one described in section 2.3.1 but this time applied to pixels in different frames.

Another approach that gives better compression ratios is to detect the regions that suffered a displacement between successive frames and calculate the vector that describes the movement, motion vector (MV). Thus a given region in a frame, can be predicted by displacement of a region, in another frame. This technique is known as motion-compensated prediction (MCP) [7]. Motion estimation (ME) is the process of finding suitable MVs, and the coding of the resulting difference signal, is known as MCP residual coding. The disadvantage of this approach is the added complexity requirements.

The basic steps are:

- Search for motion vectors The idea is to find the best MVs according to a given criteria as shown later on this section.

- Prediction and differentiation The present frame is predicted by the calculated MV in the previous step, and the previous frame. Prediction error is also calculated which is the present frame minus the predicted present frame [6].

- Encoding of the prediction error and motion vectors.

Motion compensation is performed by dividing the image into blocks know as *macroblocks* (MBs) of size  $N \times N$  [9]. For example, if luminance images have size 16 x 16, then if a 4:2:0 chrominance scheme is used (horizontal sub-sampling), the MBs of the chrominance image will have a size of 8 x 8. If the 4:2:0 scheme is used (horizontal and vertical sub-sampling), then the MBs for chrominance images will have size 4 x 4. It is important to emphasize that the choice of the MBs size affects the performance of the algorithm. When smaller MBs are used, the estimation of movement is more precise, but that means an increase in the number of computations, number of MVs and information that is encoded and transmitted [6].

The task of finding the "best" MVs is an expensive one, so, usually the search is made in a small search window of known size. To decide the "best" match, several criteria exist like for example, Mean Absolute Difference (MAD), Sum of Absolute Difference (SAD) and Mean Square Error(MSE).

The MAD criteria is defined in equation 2.3, extracted from [9].

$$MAD(i,j) = \frac{1}{N^2} \sum_{k=0}^{N-1} \sum_{l=0}^{N-1} |C(x+k,y+l) - R(x+i+k,y+j+l)|$$

(2.3)

A word about notation: p is an integer that will define the window size; k and l are indices for pixels in the MB; i and j represent the horizontal and vertical displacement; C(x+k,y+l) are the pixels in the MB in the target frame; R(x+i+k,y+j+l) are the pixels in the MB in the reference frame.

The objective is to find de MV (i, j) that minimizes a given criteria, in this case, the MAD(i, j), for  $i, j \in [-p, p]$ .

There are several search algorithms. In table 2.2 some existing search algorithm and the required number of operations for second are shown.

As we can see on table 2.2 the Hierarchical Search is the search method that requires less operation per second. Sequential search is to heavy for real time encoding.

| Search algorithm      | Number of operations per second                                                                                                                          |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Sequential Search     | $(2p+1)^2 * N^2 * 3$                                                                                                                                     |

| 2D Logarithmic Search | $8*(\lceil log_2p \rceil + 1) + 1$                                                                                                                       |

| Hierarchical Search   | $\left[ \left( 2 * \left\lceil \frac{p}{4} \right\rceil + 1 \right)^2 \left( \frac{N}{4} \right)^2 + 9 \left( \frac{N}{2} \right)^2 + 9 N^2 \right] * 3$ |

Table 2.2: ME algorithms comparison.

## 2.3.3 Transform Coding

Transform coding is based on applying a mathematical transform to the image pixels so that the relevant image information is concentrated in a small number of transform values. Let g(x,y) represent the gray level of the pixel at coordinates (x,y) and T(u,v) represent a 2-D transformation where (u,v) are the pixel coordinates in the new domain [6].

The equations that represent the forward and inverse transformations were extracted from [6] and are respectively:

$$T(u,v) = \sum_{x=0}^{N-1} \sum_{y=0}^{N-1} g(x,y) f(x,y,u,v)$$

(2.4)

and

$$g(x,y) = \sum_{u=0}^{N-1} \sum_{v=0}^{N-1} T(u,v)i(x,y,u,v)$$

(2.5)

It can be shown that if the transformation kernel is symmetric, than the equation 2.5 can be represented as:

$$G = \sum_{u=0}^{N-1} \sum_{v=0}^{N-1} T(u, v) I_{u,v}$$

(2.6)

where  $I_{u,v}$  is the basis image:

$$I_{u,v} = \begin{pmatrix} i(0,0,u,v) & i(0,1,u,v) & \cdots & i(0,N-1,u,v) \\ i(1,0,u,v) & i(1,1,u,v) & \cdots & i(1,N-1,u,v) \\ \vdots & \vdots & \ddots & \vdots \\ i(N-1,0,u,v) & i(N-1,1,u,v) & \cdots & i(N-1,N-1,u,v) \end{pmatrix}$$

(2.7)

Equation 2.6 means that the picture G (which is the collection of g(x,y) for all possible values of x and y) can be represented as a weighted sum of the basis pictures  $I_{u,v}$ , where T(u,v) represents the weights used in the summation. These weights measure the amount of correlation between the image G and the basis  $I_{u,v}$ , as described in [6, 15].

It is shown on [15] that for some choices of basis images, after a certain number of terms, the contribution of the weighing coefficients becomes negligible to the summation, so they can be discarded. The mean-square error (MSE) is also shown to be, the sum of the variances of the discarded weighing coefficients.

To achieve compression, it is important to choose a transformation (set of basis images) that concentrates the variance in a small number of weighing coefficients, which means, concentrating the energy of the signal in a small number of terms, and discard the terms that are irrelevant [15]. The weighing coefficients are then quantized and encoded.

There are some considerations that must be taken into account when quantizing the coefficients. The coefficients with higher variance, have more impact on the quality of the decompressed image, so, more bits should be used to represent those coefficients. The other ones can be represented with less bits, because they have less impact in the perceived quality of the decompressed image. The characteristics of the HVS can also be taken into account, namely, the frequency response of the eye, and so, coefficients whose frequencies correspond to the ones which our eyes are sensible, should be encoded with more bits [15]. It is important to emphasize that the transformation by itself doesn't compress data, it's the quantization process that indeed removes information.

There are several transformation functions in the literature, used for static image compression and video compression, like the discrete cosine transform (DCT), the discrete Walsh transform (DWT) and the discrete Hadamard transform. The DCT is used in several video coding standards such as H.264, MPEG 1, 2, 4 due to it's properties, like the decorrelation property [16] and energy compaction property.

Equations 2.8 and 2.9 were extracted from [6] and represent the 2-D DCT transformation kernel. C(v) in equation 2.8 is the same as C(u) in equation 2.9.

$$f(x,y,u,v) = i(x,y,u,v) = C(u)C(v)\cos\left(\frac{(2x+1)u\pi}{2N}\right)\cos\left(\frac{(2y+1)v\pi}{2N}\right)$$

(2.8)

$$C(u) = \begin{cases} \sqrt{\frac{1}{N}} & , u = 0\\ \sqrt{\frac{2}{N}} & , u = 1, \dots, N - 1 \end{cases}$$

(2.9)

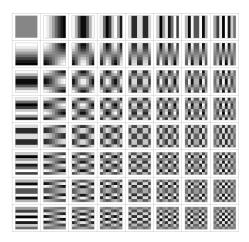

Figure 2.4 shows the 8x8 DCT basis images.

Figure 2.4: DCT 8x8 Basis Images.

# 2.3.4 Quantization

A quantizer partitions the range of input values into a finite number of intervals. The endpoints of a interval are known as *decision boundaries*. The  $\Delta$  symbol is used to represent the *step size* which is the length of the interval [9].

#### 2.3.4.1 Uniform scalar quantization

In an uniform scalar quantizer, the step size is the same for all intervals. The output value of each interval is the midpoint of the interval [9].

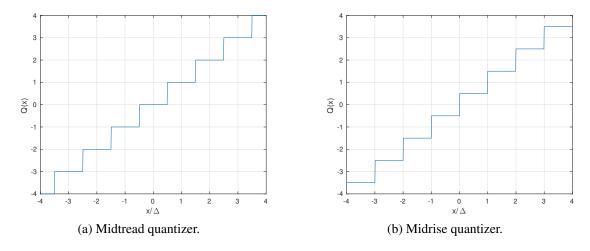

We can distinguish two types of uniform scalar quantizers, namely, *midtread* and *midrise*. If the value zero is a possible output value, then the quantizer is of the midtread type, otherwise is midrise type. Figure 2.5a illustrates a input-output map of a midtread quantizer, while figure 2.5b shows the input-output map of a midrise quantizer.

Figure 2.5: Uniform quantizers.

As wee can see, the number of possible values at the quantizer output, is less than at the input side, which means that the quantization operation inserts distortion. When we increase the number of intervals, intuitively we expect that the distortion due to quantization will be lower, however, since each level is coded with a binary code, more bits will be necessary to represent the data. These concepts will be proved mathematically.

If the quantizer has M possible output values, then, the output binary rate is:

$$R = \lceil \log_2 M \rceil \tag{2.10}$$

Assuming that the range of the input signal belongs to the interval  $[-X_{max}, X_{max}]$  and the values are uniformly distributed, then:

$$\Delta = \frac{X_{max} - (-X_{max})}{M} = \frac{2X_{max}}{M} \tag{2.11}$$

It is shown on [9] that, when the input values are uniformly distributed, the quantization error  $e(x) = x - \frac{\Delta}{2}$  is also uniformly distributed on the interval  $[-\frac{\Delta}{2}, \frac{\Delta}{2}]$ . The mean value of e(x) is  $\bar{e}$  which is zero, and so, the MSE is equal to the variance which is given by:

$$\sigma_e^2 = \frac{1}{\Delta} \int_0^{\Delta} (e(x) - \bar{e})^2 dx = \frac{\Delta^2}{12}$$

(2.12)

The signal variance is given by:

$$\sigma_x^2 = \frac{(2X_{max})^2}{12} \tag{2.13}$$

With the two previous equations we can compute the signal-to-quantization noise [9]:

$$SQNR = 10log_{10} \left( \frac{\sigma_x^2}{\sigma_e^2} \right) = 6.02n(dB)$$

(2.14)

The previous equation, permits us, for a desired SQNR value, find the necessary number of bits used to represent the output values of the quantizer, under the assumptions in which the equation was derived.

### 2.3.4.2 Nonuniform Scalar Quantization

Sometimes the assumptions that were used on uniform quantization don't apply. The distribution of input signal levels may be more dense near some decision levels. In that case a nonuniform quantizer should be used. The number of decision levels in those dense regions should be higher to have a finer quantization [9]. In the remaining regions, the number of decision levels can be lower (which will give a coarser quantization).

Lets consider the Lloyd-Max quantizer. Let  $\beta = (\beta_0, \beta_1, \dots, \beta_M)$  represent the set of the possible decision boundaries and  $Y = (y_1, y_2, \dots, y_M)$  represent the possible output values. Then it

2.4 Requirements

can be shown that the optimal values for each  $\beta_j$  and  $y_j$  (that give the lower distortion) are given respectively by:

$$y_{j} = \frac{\int_{j-1}^{\beta_{j}} x f_{X}(x) dx}{\int_{\beta_{j-1}}^{\beta_{j}} f_{X}(x) dx}$$

(2.15)

and

$$\beta_j = \frac{y_{j+1} + y_j}{2} \tag{2.16}$$

where  $f_X(x)$  is the probability density function of the input signal's levels.

# 2.4 Requirements

When designing or using a compression scheme it is important to consider the application's requirements that obligate to use image compression and the impact of the compression performance in meeting those requirements. Some typical requirements [17] are shown next.

- Real time constraints

- Visual quality

- Power consumption

- Memory requirements

- Maximum bit rate of the compressed bit stream

The encoding and decoding operations take some time that depends on the complexity of the compression scheme. Some applications like video conferencing and streaming have real time constraints, namely the delay between successive video frames should be constant, otherwise it will be perceived by the user, lowering the *QoE* (Quality of Experience). Other applications such as a video game console connected to a TV, have higher requirements related to the delay inserted. Not only the delay must be constant, but also, it must be small, to ensure the timeliness of the player's response to a given game event for example.

Lossy compression deteriorates the quality of the original video sequence by introducing compression artifacts such as blocking, ringing [18] and temporal artifacts like flickering [19]. These coding artifacts can be more or less pronounced depending on the data rate at the output of the encoder. When the data rate is lowered, the compression ratio is higher, but the video quality lowers. So, for a given application there is a trade-off between the compression ratio and the visual quality, that imposes restrictions in selecting a compression scheme.

Memory requirements can also be a limitation when choosing a compression scheme. For example, let's consider that for a given algorithm it is necessary to store a complete frame and the video resolution is 4096 x 2160p. Even if the blanking pixels are not considered, the memory buffer must store 8,847,360 pixels, which means, if each pixel is encoded with 36 bits (12 bits per pixel component) it's necessary to have approximately 38 MB which can be a problem if the algorithm is to be implemented in an integrated circuit.

Power consumption considerations must be taken account is some cases, specially for mobile devices. In that situations special attention must be given to the complexity of the encoder and decoder to ensure that power consumption requirements are met [20].

Other requirements can be related to error resilience capabilities, that is, how errors inserted by the communication channel affect the decompressed video quality, supported video formats and frame rates.

# 2.5 Video Coding standards

Over the years several video coding standards have been proposed. A standard specifies the data format at the output of the encoder and specifies the conforming decoder output results [21]. The objective of the standards is to guarantee interoperability between devices only. This dissertation is about VESA DSC which is a recent video coding standard. Although no relevant work has been published yet, Hardent has an implementation of the encoder and decoder already available in the market.

In the next sections some work related to popular video coding standards will be presented. Distributed video coding and machine learning approaches are alternative approaches to the "traditional" video compression standards, and are briefly discussed in section 2.6 and 2.7 respectively.

#### 2.5.1 H.264/AVC

The H.264/AVC is one of the most used video coding standards and has applications in video telephony, storage, streaming and broadcast applications [22]. H.264/AVC uses the tools described in chapter 2, namely, intra-frame prediction, transform coding, quantization, entropy coding and inter-frame prediction. Some pertinent work on this standard will be described next.

The paper [23] proposes an H.264 intra-encoding architecture capable of handling 4 FullHD video streams at 25 fps in real-time. The solution addresses the problem of encoding simultaneously views in multicast video applications. To achieve an area efficient solution, the hardware is shared in a time-multiplexed way between the different views.

Motion estimation and compensation might not be adequate in some applications, specially when low power requirements are considered [24]. Designing a intra-frame architecture to reduce the spatial redundancy at high resolutions is a challenging task. It is difficult to use parallel and pipelined architectures because of data dependencies, and the amount of data involved. In [24] was proposed an intra-prediction implementation in 65*nm* lithography that supports resolutions of 7680 x 4320 @ 60 fps running at 273 MHz.

A perception-based video coding that detects human faces was proposed on [25]. Remember from the discussion on chapter 2, that the HVS as a tendency to focus on some regions (ROI) of the frame and human faces are generally a ROI. The algorithm proposed, uses an adaptive boosting (AdaBoost) classifier to detect the human faces. The macroblocks (MB) corresponding to the ROIs are then coded with more bits, while the other regions are more compressed, so it's possible to have lower bit rates, while maintaining the same subjective visual quality if this technique wasn't used.

#### 2.5.2 HEVC/H.265

HEVC/H.265 operation is based on the same principles of the H.264/AVC standard. This is the most recent video coding standard of the ITU-T Video Coding Experts Group and the ISO/IEC Moving Picture Experts Group and can provided up to 50% bit rate reduction relatively to prior standards like the H.264/AVC for the same visual quality [26]. Some work relative to this standard will be discussed next.

The work presented in [27] proposes a 4K x 2K H.265/HEVC video codec chip implementation in a 28nm CMOS process. This an interesting implementation that not only implements the H.265 coder/decoder, but also, supports 13 additional video standard formats such as MPEG-2/4 and H.264. The implementation supports 4096 x 2160 (4K) @ 30 fps encoding/decoding. The power consumption is 126.73 mW when processing 4K @ 30 fps video. The die area is 1.49 x 1.45 mm<sup>2</sup>. This implementation is adequate for smart-phone applications due to it's low power requirements. Further details about the implementation are found on the same article.

In [28] is proposed an intra encoder capable of handling resolutions up to 2160p @ 30 fps. This architecture uses 1086k gates and on-chip 52 kB of memory. The chip was fabricated using 90nm lithography.

As discussed on chapter 2, motion estimation and compensation are computational complex operations that normally dominate the overall complexity of a codec but that can have a very significant impact on the compression ratio. In work [29] was proposed a VLSI implementation of the HEVC motion compensation that supports Ultra High Definition Television (UHDTV) resolutions, namely, supports 7680 x 4320 @ 60 fps resolutions in real-time with 10 bit per pixel component. The maximum clock speed is 400 Mhz. The proposed solution was fabricated in a 40nm process. The total gate count is 419k gates. Further details about the implementation architecture can be found in the paper.

#### **2.5.3** MJPEG

Motion JPEG (MJPEG) compresses each video frame using the JPEG standard as if no relationship exists between successive frames, so only intra-frame redundancy is explored which diminishes the efficiency of the codec. Since no motion estimation and compensation techniques are used in MJPEG, it requires lower requirements in terms of CPU performance and power, making it adequate for embedded systems [30].

The paper [30] proposes a low complexity motion detection algorithm known as Zipfian estimation, to be applied to the MJPEG. It is shown in the same paper that this technique doubles the compression ratio, and, has an approximate performance in terms of quality and bit rate to the H.264 codec when used in Intra mode, but with lower computational complexity.

# 2.6 Distributed Video Coding

As was discussed in chapter 2, sometimes the encoder and decoder complexity are not equal (asymmetric compression). In "traditional" video coding algorithms such as H.264, the encoder complexity is normally greater than the decoder complexity, basically, because the encoder is responsible for motion compensation which is a computationally complex operation [20].

Some applications require the complexity to be shifted from the encoder side to the decoder side, as in the example referred in [20], where the example given is a wireless camera that uploads data to a base station. Since the camera is the video source, the camera must be the responsible for compressing the video, but, due to hardware limitations in terms of memory and computational power, the encoding operation should be computationally simpler than the decoding operation.

Distributed Video Coding (DVC) is a video coding approach that accomplishes the above requirements. It is based on two Information Theory theorems, namely, Slepian and Wolf's theorem and Wyner-Ziv theorem.

Several architectures have been proposed in the literature [31], adequate for VLSI implementation. Further information about the above architectures can be found on the same article.

# 2.7 Machine Learning in Video Coding

In this section it will be discussed the Machine Learning approach to video compression. Machine Learning techniques can be used to analyze the video frames in a statistical point of view and create opportunities to compress data. Several approaches have been proposed in [13]:

- Inpainting related approaches The idea is to not transmit all image blocks saving bits that

way. Given the spatial and temporal redundancy of video signals, at the decoder side that

missing blocks can be reconstructed based on the neighbors.

- Dictionary learning related approaches This approach is based on the fact that most image patches (regions) are constituted by some basic textures patterns. By constructing a dictionary of texture patterns, it is possible to construct an image block by using a linear combination of the basic textures, present on the dictionary. On [32] was proposed an online learning based codec (ODL). The dictionary gets richer in basic textures as the codec runs, thus, the more video frames it processes, the more efficient it gets. It is also shown that the rate distortion performance at low bit rates for intra-frame video is superior to the H.264. It is shown on [13] that the dictionary approach only works with low bit rates and the coder is computationally exigent.

19

• SIFT related approaches - It's based on the premise that an image can be seen as collection of objects, and it is possible to identity each one of the objects and describe them using SIFT descriptors. Then by knowing the objects that constitute a given image it is possible to reconstruct it by using similar objects that exist on a given database. The problem is that the reconstructed image can be very different from the original one, and the SIFT descriptors may require prohibitive amounts of data to have practical application. Although in [13] is shown a alternative approach to overcome the above problems, the encoding and decoding times limit the application of SIFT related approaches in practice.

## **Chapter 3**

# **Display Stream Compression**

In this chapter it will be shown how the DSC algorithm works from a "high level" point of view without entering into low level implementation details. This chapter starts by a quick overview of the DSC compression procedure and then each block that constitutes the DSC encoder will be further analyzed and discussed. Much of the information on this chapter is based on the VESA DSC Standard[3]. Although the discussion is focused on the encoder, most of the blocks are common to the encoder and decoder.

### 3.1 Overview

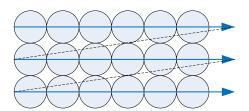

The DSC algorithm receives pixels from a given video source in raster scan order, which is from the left to the right and from the top to the bottom of the frame as illustrated in figure 3.1.

Figure 3.1: Raster scan order.

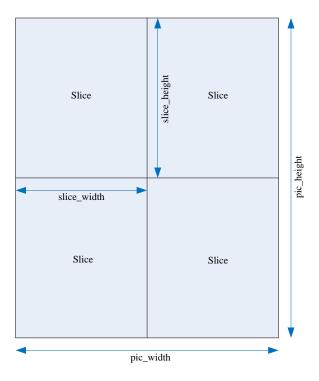

The DSC algorithm divides a video frame in equal slices. A slice is a rectangular portion of the frame, and its dimensions can be configured. In a given configuration the slice dimensions might be the same of the frame, while in another configuration the slice height (width) might be, for example, half of the frame height (width). Figure 3.2 shows a example where 4 slices per frame are used.

Figure 3.2: Frame partitioned in slices. The names slice\_width, slice\_height, pic\_width and pic\_height correspond to parameters defined in the Standard.

A slice can be encoded and decoded independently of another slice which can reduce the propagation of errors (and their impact in the perception of visual quality) and allow the parallelization of the algorithm, by having multiples encoder instances processing several slices in parallel. Relative to slice height, to reduce the impact of artifacts at the slice boundaries, extra bits are allocated to the first line of each slice. The problem is, the number of bits available to the other lines must be reduced so the total number of bits that encode a slice is equal to the desired bit rate times the number of pixels that constitute the slice, so, dividing a frame in several tiny slices prejudices the overall compression and perceived quality.

Relative to the slice width, using slices whose width is less than the frame width, offers the opportunity to have several encoder instances, each one responsible for updating the corresponding slice, which provides a way of processing video streams that require a clock frequency superior to the one the encoder can work. Consider for example a encoder capable of achieving a clock frequency of 100 MHz and a video format that requires a pixel frequency of 200 MHz. Using only one encoder, it is impossible to encode the video stream, but if a configuration that uses 2 slices per line is used with 2 encoder instances, then, each one of the encoders must only process half the pixels and it is now possible to successfully encode the video stream. More on this topic will be discussed in the chapter 5.

3.1 Overview 23

Besides providing a video stream to be encoded, first it is necessary to configure the encoder for proper operation. This task is performed by providing the encoder (and decoder) with what is known as the Picture Parameter Set (PPS). The PPS is a collection of parameters such as the slice width (slice\_width) and the frame width (pic\_width). For further details the reader is referred to the DSC Standard [3].

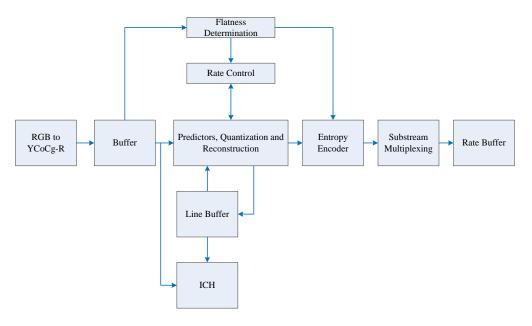

Figure 3.3 shows the DSC encoder architecture.

Figure 3.3: DSC Encoder Architecture.

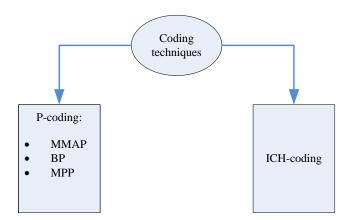

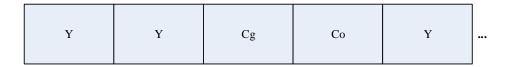

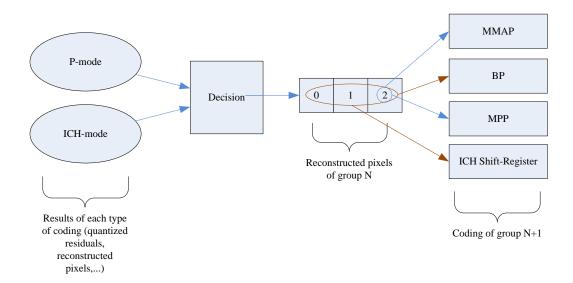

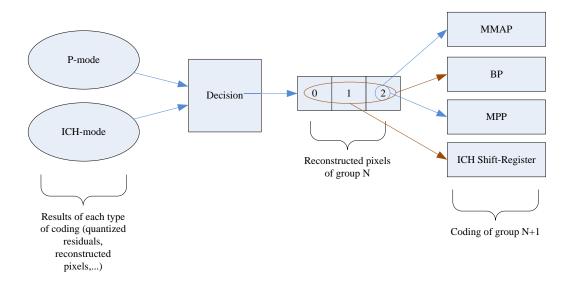

The DSC reduces the redundancy of video signals and thus compresses the video stream, by using 2 techniques: Prediction coding (P-coding) and Indexed Color History (ICH) coding. The prediction techniques follow the theory described in chapter 2. There are 3 types of prediction: Modified Median-Adaptive Prediction (MMAP), Block Prediction (BP) and Midpoint Prediction (MPP). Figure 3.4 illustrates this discussion.

Each sample of a pixel is predicted by each one the predictors mentioned above, and the residual (difference between the original sample and the prediction result) is then quantized. For each group of 3 adjacent pixels in a line it is necessary to choose which prediction type to use. First, a decision is taken between using BP or MMAP. After that, it is necessary to choose between BP/MMAP and MPP. The criteria for these decisions will be described later on this chapter. The operations so far described are performed by the Prediction, Inverse Quantization and Reconstruction blocks.

Figure 3.4: The coding techniques of the DSC algorithm.

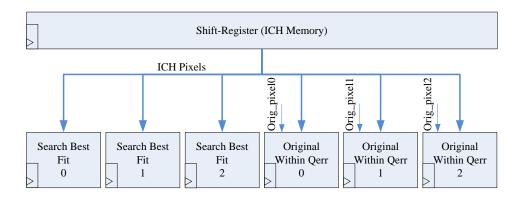

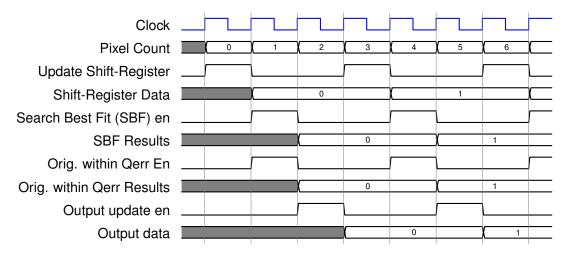

The other technique used by DSC to reduce redundant information is the ICH coding. The basic idea consists of storing the most recent 32 reconstructed pixels in a memory, and then, a search is done over the 32 entries to find the best ones that represent each pixel within the group. Since the encoder and decoder maintain the same ICH state, it is only necessary to send the 5 bit index for each pixel, achieving that way, compression. There are 3 operations associated to ICH, namely, the update/storage of the reconstructed pixels in the shift register, the search for best fit, and the decision between prediction and ICH coding (P-mode vs ICH-mode). The ICH block is responsible for these operations, although in the implementation the selection between P-mode and ICH-mode, is performed by a dedicated block as described in chapter 4.

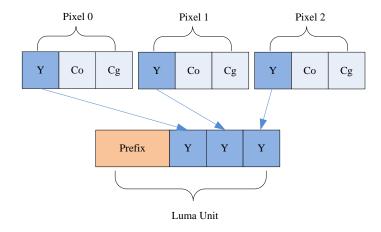

The Entropy Encoder is responsible for removing redundancies in the data representation and generates variable length codes (VLC). The entropy encoder organizes samples into units. One group is constituted by 3 pixels. A unit contains information of a component's group (so it contains 3 samples of a group, for example, 3 samples of luminance component (Y) plus a prefix. The prefix as indicated in the DSC 1.1 Standard, is a unary code (thermometer code) that indicates the non-negative difference between the size of the largest residual in the unit and the predicted size if P-coding is used, otherwise is a special code that indicates that ICH-coding is being use for the current group. The Entropy Encoder is also responsible for constructing the syntax elements, which correspond to the smallest portion of the bitstream, with a meaning in the context of the DSC operation.

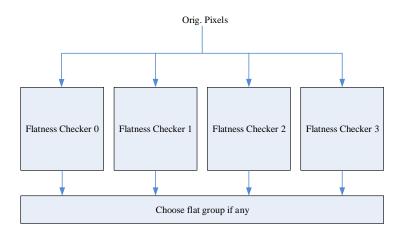

One of the objectives of the DSC is to maximize subjective video quality (Visually lossless). As described on chapter 2, it is known that the Human Visual System (HVS) is more sensitive to low frequency content (in the sense of uniform regions) than high frequency content, so, in "flat" regions, the quantization parameter should diminish, otherwise, quality degradation may be perceived in that regions. The flatness determination block analyzes the "future" incoming pixels to detect the presence of flat pixels. That information is used in the Rate Control block to adjust the quantization parameter and is also sent to the decoder. Figure 3.5 shows two distinct images

in terms of spatial frequency contents. Figure 3.5a shows an image that has several "flat" regions, while figure 3.5b shows an image rich in high frequency content due to the presence of many small details and sharp transitions between colors. The figure 3.5b besides generating less flatness adjustments than figure 3.5a, provides more opportunities to reduce redundant information.

(b) Image with high spatial frequency content.

Figure 3.5: Two images with distinct spatial frequency contents.

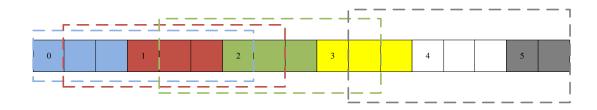

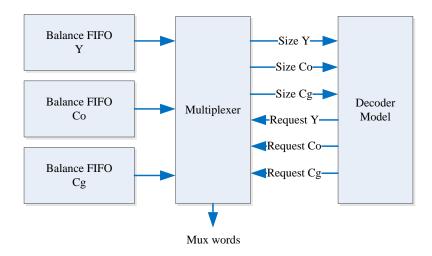

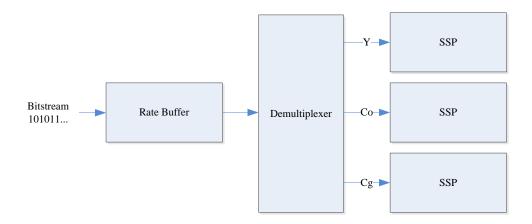

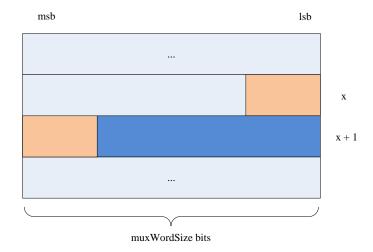

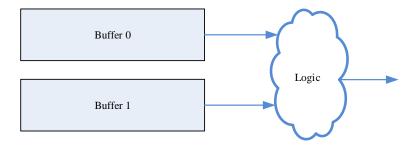

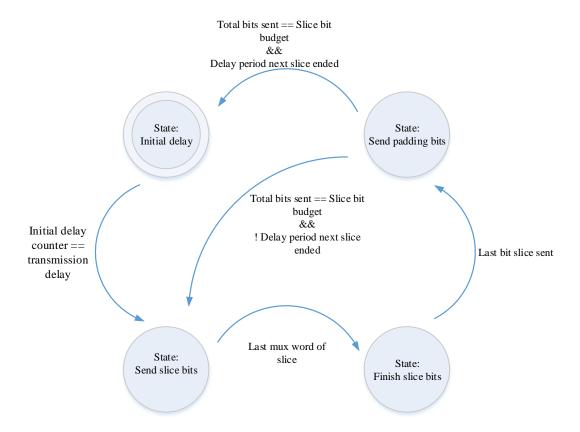

The Substream Multiplexer packs the information (syntax elements) generated by the Entropy Encoder, in words of fixed size, known as mux words. This process is performed for each component type. Finally, the Substream Multiplexer multiplexes each of the component streams<sup>1</sup> generated by the Entropy Encoder, to produce the bitstream that is sent to the decoder. Figure shows an example of the contents of the bitstream between the encoder and decoder. The process that determines the order in which the mux words are inserted is discussed in section 3.8.

Figure 3.6: Possible construction of the bitstream between the encoder and decoder.

Since the number of bits to encode each unit varies from unit to unit, the data is first stored in the Rate Buffer to damp the bitrate variations. The data is removed from the Rate Buffer at a constant bit rate (CBR). Although variable bit rate (VBR) is described in the DSC Standard, it is not implemented at this time due to the HDMI transport layer limitations for VBR usage. To ensure that there is always data in the Rate Buffer to sustain the desired bitrate (i.e to avoid underflow) and to ensure that the Rate Buffer does not overflow, the DSC has a Rate Control block. The control is

<sup>&</sup>lt;sup>1</sup>Each component stream is constituted by a series of syntax elements of that component.

made on the quantization parameter<sup>2</sup> (Qp). The idea is to maximize subjective quality so lower Qp values are privileged, but, when lower Qp values are used, the Rate Buffer will tend to overflow, so, eventually the Qp value is increased to diminish the buffer fullness. One can understand that frames that are difficult to encode (with many "flat" pixels) will have a tendency to make the buffer approach the overflow condition, while in oppose, easy frames to compress, will have a tendency to make the buffer approach the underflow condition. The Rate Control block decides the Qp to be used for each group. As discussed earlier, flatness information permits the Qp to drop quickly, so, the Rate Control block takes it into account before deciding the final Qp value to use in the next group.

In the following subsections it will be discussed how each one of the sub-blocks works. The approach chosen is to follow the video stream from the moment it enters the encoder and discuss each one of the operations performed on the video stream, until it is outputted. Before proceeding it is worthwhile to first discuss some parameters/operations that are used in the rest of this text:

- bits\_per\_pixel PPS parameter that defines the number of bits used to represent each encoded pixel. The gain of compression is determined by this parameter, as shown on section 3.9.

- masterQp Master quantization parameter. This parameter was introduced earlier with the generic name "quantization parameter". This parameter is not used directly in most of the blocks. First it is first mapped into two other quantization parameters that are different for luminance and chrominance components (qlevely and qlevelC respectively).

- mapQptoQlevel The operation of mapping the masterQp value into the quantization parameter qlevelY and qlevelC.

## 3.2 RGB to YCoCg-R

The DSC algorithm supports an input RGB or YCbCr video sequence with a component bit depth of 8,10 or 12 bits per component although the encoding and decoding process cannot be performed in the RGB color space. In that case, the first step consists of a color space conversion from RGB to YCoCg that is signaled by setting the convert\_rgb PPS parameter to 1. If the input video color space is YCbCr then the convert\_rgb should be cleared to 0 and the first RGB to YCoCg conversion block is bypassed.

### 3.3 Buffer

The Buffer block on figure 3.3 stores temporarily pixels from the RGB to YCoCg-R block. The reason for this is that the Flatness Determination block for processing a given pixel, requires information from "future" pixels. This can be accomplished by delaying the encoding process and store the color space converted pixels.

<sup>&</sup>lt;sup>2</sup>The name used in the DSC Standard is masterQp and will be introduced shortly.

### 3.4 Predictors, Quantization and Reconstruction

### 3.4.1 Modified Median-Adaptive Prediction (MMAP)

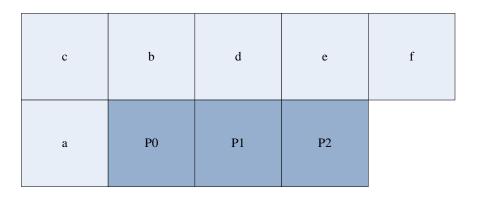

The MMAP method generates a prediction using information from previously coded pixels to the left and above, of the current group being predicted. Figure 3.7 illustrates this concept and defines names for the pixels involved, which will be useful to understand the equations.

Figure 3.7: Pixels require to predict the current group. The letters "c", "b", "d", "e" and "f" represent reconstructed pixels from the previous line. The letter "a" represents the rightmost reconstructed pixel of the previous group. "P0", "P1" and "P2" symbolize the pixels of the current group that are being predicted.

The first step consists of applying a low-pass filter with coefficients [0.25 0.5 0.25] to each one of the pixels from the previous line (c,b,d and e). As an example, equations 3.1 and 3.2 show how the filter should be applied to pixel b and d respectively.

$$filt_b = \frac{c + 2b + d + 2}{4} \tag{3.1}$$

$$filt_d = \frac{b + 2d + e + 2}{4} \tag{3.2}$$

Once the pixels are filtered, they are blended with the original pixels as follows (example for pixel b):

$$diff_b = CLAMP\left(filt_b - b, -2^{qlevel-1}, 2^{qlevel-1}\right)$$

(3.3)

$$blend_b = b + diff_b (3.4)$$

Where the clamp operation consists of saturating the first argument  $(filt_b - b)$  between the second an the third argument, so, the equation saturates the difference to the binary range of

*qlevel*. For example, consider that qlevel = 6, then, if the first argument value is greater than 32, the clamp result is 32. The same reasoning applies to negative values.

Equations 3.5, 3.6 and 3.7 give the prediction value for each pixel of the group for lines that are the not the first line of each slice.

$$P0 = CLAMP(a + blend_b - blend_c, MIN(a, blend_b), MAX(a, blend_b))$$

(3.5)

$$P1 = CLAMP(a + blend_d - blend_c + R0,$$

$$MIN(a, blend_h, blend_d), MAX(a, blend_h, blend_d))$$

(3.6)

$$P2 = CLAMP(a + blend_e - blend_c + R0 + + R1, MIN(a, blend_b, blend_d, blend_e), MAX(a, blend_b, blend_d, blend_e))$$

(3.7)

The variables R0 and R1 represent the inverse quantized residuals that result from encoding the first and second pixel, respectively, of the current group.

Since slices can be independently encoded and decoded, when the first line of a slice is being processed, the pixels from the previous line are not available. In this case, equations 3.8, 3.9 and 3.10 should be used instead.

$$P0 = a \tag{3.8}$$

$$P1 = CLAMP\left(a + R0, 0, 2^{cpntBitDepth} - 1\right)$$

(3.9)

$$P2 = CLAMP\left(a + R0 + R1, 0, 2^{cpntBitDepth} - 1\right)$$

(3.10)

where *cpntBitDepth* represents the bit depth of the component being processed.

### 3.4.2 Block Prediction (BP)

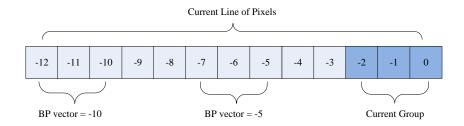

The BP predictor is simply a reconstructed pixel that is to the left of the current pixel being predicted in the same slice line. The pixel to use is determined by the BP vector that is the same for all pixels of a given group. The BP vetor is constituted by a single value in the range [-3, -10], that indicates the displacement that should be applied to each pixel of the group. Figure 3.8 clarifies this concepts.

Figure 3.8 shows the reconstructed pixels of the current slice line and the current group being predicted. The negative numbers represent the offset value relative to the 3rd pixel of the current group. The figure also shows the prediction results for two possible BP vectors. For example, if BP vector is -5, then the prediction result for the first pixel of the current group is the pixel represented by -7, which corresponds to the 5th previous pixel of the current slice line. The same reasoning applies to the remaining pixels of the group.

In section 3.4.4 it will be described the algorithm to determine the BP vector value. Before leaving this section, it is important to mention that the BP predictor cannot be used when the horizontal position within the slice line is less than 10 because in that case, some vectors would address pixels outside of the current slice line.

Figure 3.8: Block Prediction application example.

### 3.4.3 Midpoint Prediction (MPP)

The third prediction method available is the midpoint prediction. The prediction value obtained with this method is a value near half of the range of the component being predicted, hence the name midpoint.

The following equation determines the prediction value:

$$P = \frac{2^{cpntBitDepth}}{2} + prevRecon \% 2^{qlevel}$$

(3.11)

where *cpntBitDepth* represents the bit depth of the component being predicted and *prevRecon* is the rightmost reconstructed pixel from the previous group, which was not necessarily obtained by the MPP method. The *qlevel* parameter represents the current quantization level being used for the component being processed. Notice that for the first group of each slice, *prevRecon* is not available, so, it should be set to 0.

#### 3.4.4 BP vs MMAP decision

For each group it is necessary to select a predictor to use. First a decision is taken between using BP or MMAP, then in section 3.4.5 it will be described how the selection between the result of BP/MMAP decision and MPP is performed.

The BP/MMAP decision is made on the previous line<sup>3</sup>, which is useful from the implementation point of view, because it provides sufficient time to perform the required operations which are time consuming and would be difficult to be done in a group time. The are two possible outcomes

<sup>&</sup>lt;sup>3</sup>When the slice line x is being processed, the results of the decision process apply to line x + 1.

of this decision process. If BP is selected, then the algorithm provides the BP vector that should be used when processing the group on the next line of the slice, otherwise MMAP is selected.

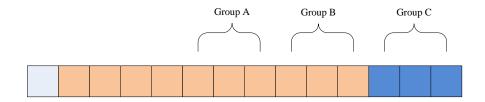

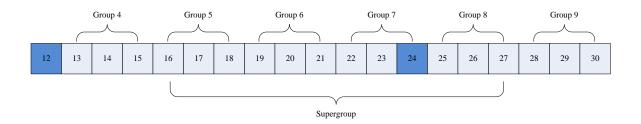

The decision algorithm involves determining the Sum of Absolute differences (SAD) for 3 groups of pixels. Figure 3.9 shows the groups involved in the decision process. To determine the SAD for each group, it is necessary to compare each pixel of the group, with each one of the 10 pixels to the left of the current pixel being processed. This is exemplified in figure 3.9 for the first pixel of the current group (group C). The pixels involved in this operation are shown with orange color. After applying some mathematical operations, a decision is generated. If BP is selected, then the selected vector is the one with the lowest SAD. Further details are found in the Standard.

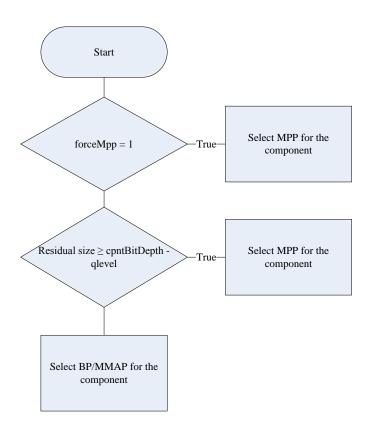

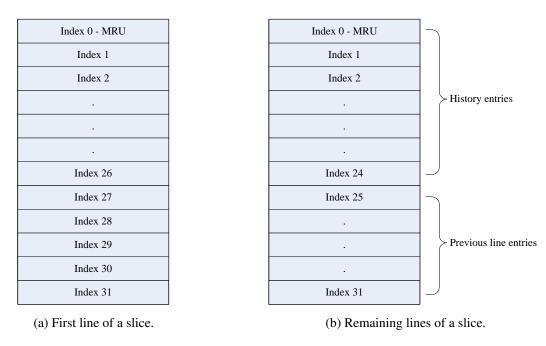

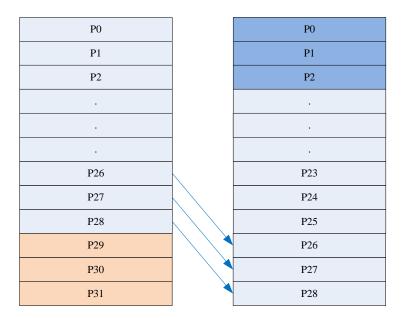

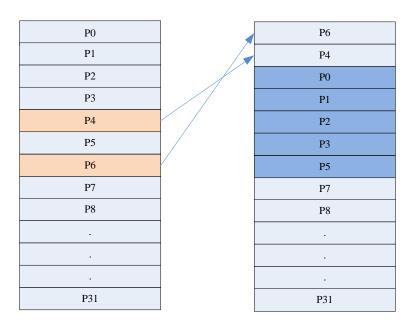

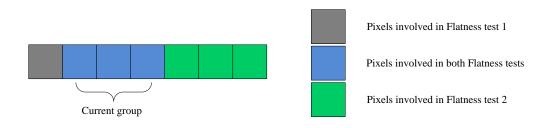

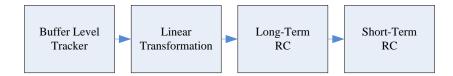

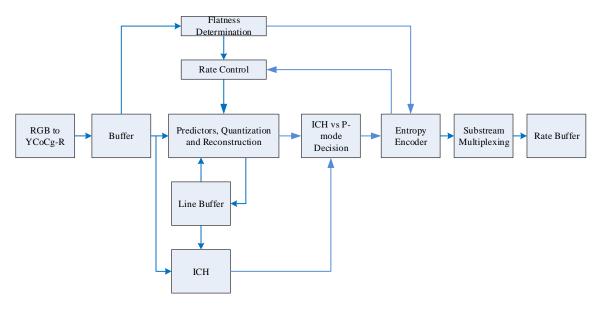

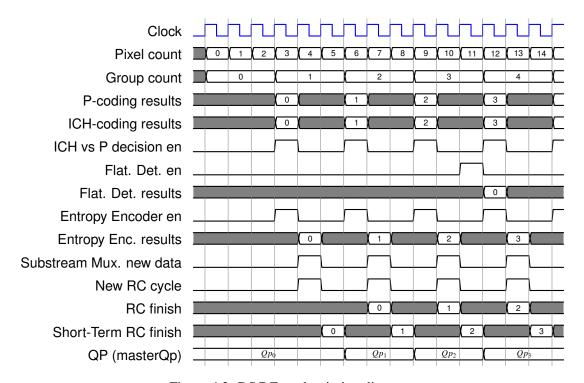

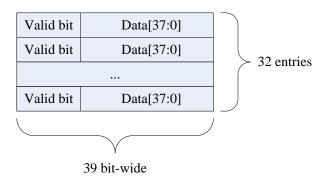

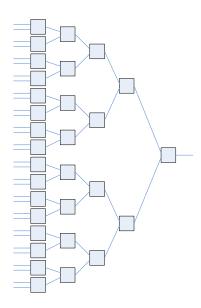

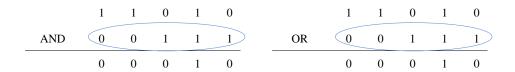

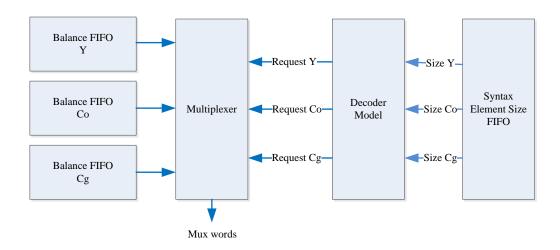

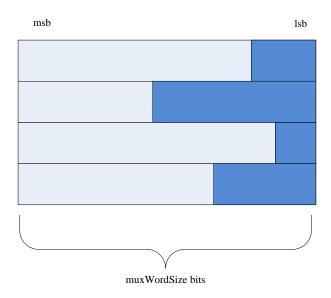

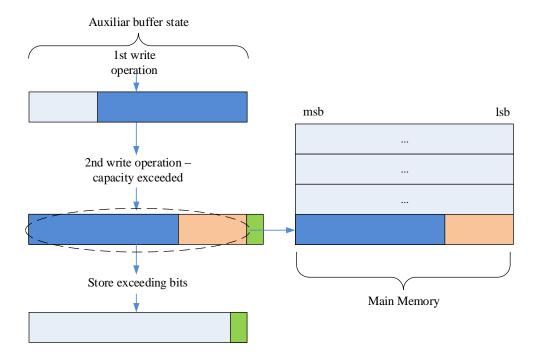

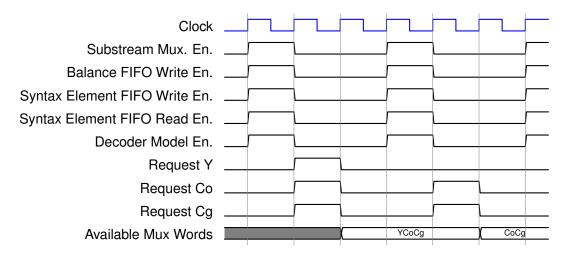

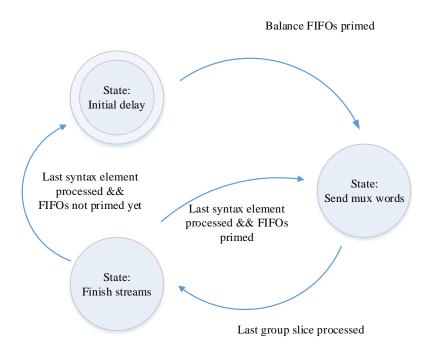

Figure 3.9: The letters A,B and C represent the groups of pixels used to perform the decision between MMAP/BP for group C.