# Digitally-Modulated Transmitter for Wireless Communications

**Rui Filipe Pinho Gomes**

MSC DISSERTATION

MESTRADO INTEGRADO EM ENGENHARIA ELETROTÉCNICA E DE COMPUTADORES

Supervisor: Professor Cândido Duarte (FEUP)

Co-Supervisor: Professor José Carlos Pedro (UA)

# Digitally-Modulated Transmitter for Wireless Communications

# **Rui Filipe Pinho Gomes**

MESTRADO INTEGRADO EM ENGENHARIA ELETROTÉCNICA E DE COMPUTADORES

### Resumo

Transmissores digitais permitem a muito desejada integração do andar de saída de radio-frequência e da banda base digital numa única tecnologia de baixo custo. Extender esta abordagem para a generalidade dos transmissores de baixa potência é assim desejado. Além do mais, como resposta à sempre crescente demanda de troca de informação, transferências de dados eficientes e operação em diferentes standards são uma situação mandatária. Consequentemente, novos standards sem fios que permitam uma utilização mais eficiente do espectro saturado são necessários. Estes sinais geralmente forçam a operação do amplificador de potência num regime de potência médio muito longe da potência de pico. Esta condição gera a ocorrência de perda de eficiência, provocando assim a diminuição do tempo de vida útil das baterias dos dispositivos móveis. Assim sendo, esta dissertação tem como objectivo implementar um amplificador de potência digital com perda de eficiência reduzida. De modo a ultrapassar o decréscimo de eficiência observado quando o amplificador opera com modulações complexas, técnicas de aumento de eficiência serão também necessárias.

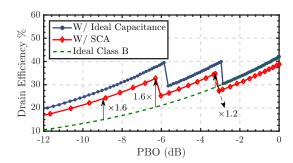

A dissertação começa por efectuar uma revisão dos últimos trabalhos relacionados com arquitecturas de transmissores digitais. Após isto, a técnica de modulação dinâmica de carga é estudada, verificando quais as vantagens e limitações das correntes implementações em CMOS. Tendo isto como suporte, a tipologia polar digital de amplificação de potência é seleccionada para ser implementada. De modo a possibilitar o desenho de um amplificador linear e eficiente, esta dissertação propõe o uso de uma tipologia de ângulo de condução reduzido baseada em fontes de corrente comutadas. Adoptando um ângulo de condução de 25%, um compromisso é assumido entre potência máxima de pico e eficiência do amplificador. Através de resultados de simulação, uma potência máxima de 17.92 dBm e uma eficiência de 43% são atingidas à frequência de operação de 2GHz. O ponto de compressão de largura de banda de 1dB em frequência é de aproximadamente 200 MHz, atingindo um pico de eficiência máxima de 48%. O incremento de eficiência para condição de operação de baixa potência foi conseguido através do uso de uma nova tipologia de modulação de carga dinâmica. Recorrendo a um algoritmo de optimização, operação multi-estado é realizada com uma rede de carga adaptativa. Resultados de simulação indicam um incremento de eficiência de ×1.2 a ×1.6 entre 3 dB e 12 dB de recúo de potência, tendo como referência um amplificador class B ideal, apresentando o mesmo uma eficiência de pico normalizada à operação com uma rede de carga com capacidades ideais. Em conclusão, os resultados obtidos durante o decurso desta dissertação demonstram a viabilidade do uso de modulação de carga dinâmica multi-nível em nós avançados de tecnologia CMOS.

# **Abstract**

All-digital transmitters enable the constantly desired integration of both radio-frequency front ends and digital baseband in a single low-cost monolithic chip. Thus, the widespread of this well-founded approach over the generality of low-power wireless devices is appealing. Furthermore, as a response to the ever increasing user data rate transfer, efficient throughputs and multi-standard operation are required. Consequently, more demanding wireless standards are usually mandatory to allow a reasonable share between the overcrowded frequency spectrum. These signals usually present high crest factors, thereby pushing the transmitter operation away from the maximum output power, which imposes severe power losses. This, in turn, decreases the battery lifetime of portable devices. Hence, aiming the formerly evidenced challenges, this dissertation targets the development of a digital Power Amplifier solution with reduced power losses. To circumvent the typical efficiency degradation reported for complex modulated signals' amplification, an efficiency enhancement technique is also mandatory.

This dissertation begins by reviewing the latest works regarding all-digital transmitter architectures. Then, dynamic load modulation is also studied, assessing the benefits and limitations of current CMOS works. Based on that, the polar digital Power Amplifier is selected as the topology to be designed. To ease a linear and efficient digital Power Amplifier design, this dissertation proposes an approach based on reduced conduction angle switched-current sources. By adopting a 25% duty-cycle, a compromise is made between achievable peak output power and efficiency. From simulation results, maximum output power of 17.92dBm and 43% peak efficiency are attained at 2 GHz. Moreover, the simulated point of 1 dB compression over frequency is approximately 200MHz wide, achieving 48% of maximum efficiency. The efficiency enhancement for low-power operation was accomplished by resorting to a novel digitally amenable dynamic load modulation methodology. Relying on an optimisation algorithm, multi-level dynamic load modulation is achieved by employing a tunable matching network. Simulation results show an efficiency enhancement of  $\times 1.2$  to  $\times 1.6$  between 3 dB and 12 dB in power back-off over class-B operation, which was normalised to the peak performance of the static matching network under ideal capacitance elements. Hence, the results achieved during the course of this dissertation indicate the feasibility of multi-state dynamic load modulation in sub-micrometer CMOS nodes.

# **Acknowledgements**

First of all, I would like to convoy my sincere gratitude to my supervisor, Professor Cândido Duarte, for always being supportive and for providing an optimistic perspective about this work. His perseverance, guidance and knowledge were vital to achieve the results exposed in this dissertation. Secondly, I am also grateful to my co-supervisor, Professor José Carlos Pedro, for always putting his exceptional expertise, scientific knowledge as well as his experience to the best of this work interest.

For being literally my second home, I would like to thank the Microelectronics Students' Group, specially to its members. All the moments of joy and laughter were fundamental to avoid the depression felt due to the excessive amount of light produced by light-emitting diodes and cold cathode fluorescent lamps, as well as the lack of sunlight and fresh air. To the Microelectronics Students' Group fan, I would like to give my sincere appreciation for the air support provided in this last few weeks of holiday like weather.

I also would like to thank to FEUP. All the resources provided by this institution were fundamental throughout my academic path.

To SuperBock, I would like to provide my greatest acknowledgement for the relaxation times. Its characteristic cold temperature helped to surpass the antithetic work temperatures I felt.

To caffeine, I also would like to give my appreciation for all the energy and support. Never have I felt that such a psychoactive drug could have this amount of importance in the course of these last 5 years.

To the technical staff of FEUP, specially engineer Vítor Pinto, I would like to show my gratitude for the all the lunch breaks and joyful times.

I would like to give a special appreciation to all of my friends and colleagues. Despite the enormous amount of names that could have been enumerated here, I feel the necessity to itemize some of them, namely the ones whose path was drawn side by side with me: Francisco Valente, Maria Miranda, Wilson Silva, Carlos Ferreira, Hugo Santos, Luís Perestrelo, Júnio Silva, Miguel Rodrigues, Guilherme Carvalho, Francisco Gonçalves, Carlos Sousa, Erick Lima among many others. If any one of you was forgotten, the enormous lack of sleep evidenced in the last few weeks must I blame. I also wish to never lose contact with the awesome group of friends I had the chance to be member during these last years in FEUP: to them, I wish the very best.

To my parents, I must provide an honest and sincere thank you. All of their positiveness and support through my life were the key to the person I am today. All theirs lessons and dull punishments built the person I have become. Resorting again to a serious tone, I must deeply acknowledge all their efforts to provide me an easy life and always keeping me aware of the reality around me. Their loving acts will never be forgotten.

At last, but not least, I have to write something to my bothersome girlfriend, whose major occupation was pressure me to write the acknowledgements. Hence, I shall put my best efforts onto it: All her positiveness and never ending support were crucial to both my academic and personal life evolution. Being my yang, she always fulfilled my short and long term needs by

supportive talks and never ending healthy discussions. Contrastingly with all the persons have I known in my life, she can make the best and the worst out of me. Obviously, most of the time, is the last one that arises. Steeping aside her lack of taste in occupational activities, she can sometimes be a worthy opponent in video games. However, when it comes to *nerf guns*, her lack of ability makes me roll-off on the floor laughing. That being said, I have no enough words to describe how important is her presence in my life, always keeping my head on the water's surface. I also must show my gratitude to her for being one of the main reasons of my academic success. For the years to come, I expect nothing more, also never less, from her.

Rui Filipe Pinho Gomes

| "Only the unknown frightens men. | But once a man has faced the unknown, that terror becomes the known' |

|----------------------------------|----------------------------------------------------------------------|

|                                  | Antoine de Saint-Exupery                                             |

|                                  |                                                                      |

|                                  |                                                                      |

|                                  |                                                                      |

|                                  |                                                                      |

|                                  |                                                                      |

|                                  |                                                                      |

|                                  |                                                                      |

# **Contents**

| 1 | Intr | oduction                                                                    |

|---|------|-----------------------------------------------------------------------------|

|   | 1.1  | Towards All-Digital Transmitters                                            |

|   | 1.2  | Problem Statement                                                           |

|   |      | 1.2.1 Dissertation Objectives                                               |

|   | 1.3  | Document Outline                                                            |

| 2 | All- | Digital Transmitters                                                        |

|   | 2.1  | RF-DAC Fundamentals                                                         |

|   | 2.2  | All-Digital Transmitters Architectures                                      |

|   |      | 2.2.1 Digital Polar Transmitter                                             |

|   |      | 2.2.2 I/Q Digital Transmitter                                               |

|   |      | 2.2.3 Outphasing Digital Transmitter                                        |

|   | 2.3  | Conclusions                                                                 |

| 3 | Dyn  | amic Load Modulation 2                                                      |

|   | 3.1  | Fundamentals of Dynamic Load Modulation                                     |

|   | 3.2  | Previous Work                                                               |

|   |      | 3.2.1 Non-CMOS Designs                                                      |

|   |      | 3.2.2 CMOS Designs                                                          |

|   | 3.3  | Conclusions                                                                 |

| 4 | Proj | posed Digital Transmitter 3                                                 |

|   | 4.1  | Switched-Current Sources: Theoretical Analysis                              |

|   | 4.2  | Switched-Current Sources: Non-Ideal Analysis                                |

|   |      | 4.2.1 NMOS I-V Characteristic                                               |

|   |      | 4.2.2 DRAC Loadline                                                         |

|   |      | 4.2.3 DRAC Loadline under CLM and Soft- $V_{knee}$ Voltage                  |

|   | 4.3  | Switched-Current Sources: Simulation Results                                |

|   |      | 4.3.1 DRAC Design                                                           |

|   |      | 4.3.2 Assessing CLM and Soft Triode-Saturation Transition Impact 5          |

|   |      | 4.3.3 25% Duty-Cycle Clock Generation and Digital Domain Implicit Mixer . 5 |

|   | 4.4  | Conclusions                                                                 |

| 5 | Tow  | eards High PBO Efficiency                                                   |

| - | 5.1  | Dynamic Load Modulation                                                     |

|   |      | 5.1.1 DLM Challanges: Design Perspective                                    |

|   | 5.2  | Efficient Optimisation Algorithm: PSO-Based Approach                        |

|   |      | 5.2.1 Algorithm Evaluation                                                  |

X CONTENTS

|   | 5.3 | Simulation Results                 | 71 |

|---|-----|------------------------------------|----|

|   |     | 5.3.1 AM-AM Linearisation          | 73 |

|   |     | 5.3.2 Variable Capacitor           | 75 |

|   | 5.4 | Conclusions                        | 81 |

| 6 | Con | clusion                            | 83 |

|   | 6.1 | Dissertation Outcomes              | 83 |

|   | 6.2 | Future Work                        | 84 |

| A | App | endix                              | 85 |

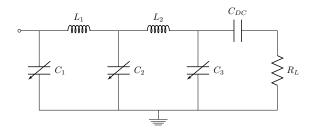

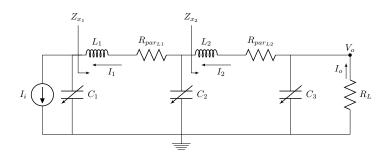

|   | A.1 | Double $\pi$ MNT Transfer Function | 85 |

| В | App | endix                              | 87 |

|   |     | Optimisation Algorithm Code        | 87 |

# **List of Figures**

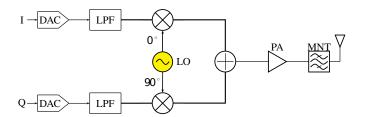

| 1.1  | Typical analog direct conversion transmitter                                                      | 2  |

|------|---------------------------------------------------------------------------------------------------|----|

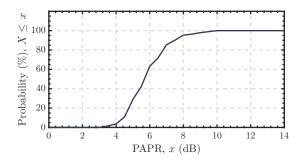

| 1.2  | Cumulative distribution function of PAPR of OFDM IEEE 802.11a                                     | 2  |

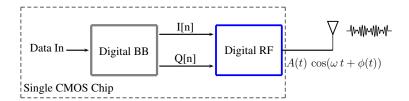

| 1.3  | System level overview of all-digital transmitters architecture                                    | 3  |

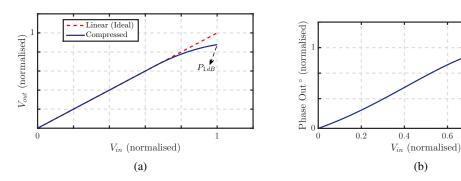

| 2.1  | AM-to-AM and AM-to-PM distortion transfer curves                                                  | 7  |

| 2.2  | RF-DAC conceptual system level                                                                    | 9  |

| 2.3  | One of the RF-DAC eight unit cells based on current steering                                      | 9  |

| 2.4  | Digital polar architecture emplyoing switched current array                                       | 10 |

| 2.5  | DRAC implementation as switched-current array and switched-resistances                            | 11 |

| 2.6  | DRAC based digital polar transmitter                                                              | 12 |

| 2.7  | SC unit cell based on cascode Class D and MiM capacitor                                           | 12 |

| 2.8  | DRAC based digital polar transmitter with extended dynamic range and frequency                    |    |

|      | tunable MNT                                                                                       | 13 |

| 2.9  | Digital I/Q transmitter DRAC based                                                                | 14 |

| 2.10 |                                                                                                   | 15 |

| 2.11 | System level schematic of an all-digital outphasing system                                        | 16 |

| 3.1  | Basic schematic of class B power amplifier with idealized transistor                              | 21 |

| 3.2  | I-V characteristic of idealized n-channel MOSFET                                                  | 22 |

| 3.3  | Ideal half-wave rectified sinusoid for a class B PA                                               | 23 |

| 3.4  | Drain efficiency evolution as a function of the normalized input power                            | 24 |

| 3.5  | Different loadlines for different $v_{GS}$ and $i_{DS}$ values                                    | 25 |

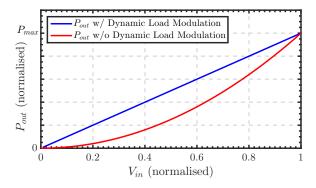

| 3.6  | Different theoretical drain efficiency profiles when operating the class B PA with or without DLM | 26 |

| 3.7  | Different theoretical output power profiles when operating the class B PA with or                 |    |

|      | without DLM                                                                                       | 26 |

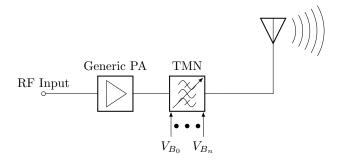

| 3.8  | Simplified system level schematic of DLM                                                          | 27 |

| 3.9  | Simplified schematic of a dynamic load modulation architecture                                    | 28 |

| 3.10 | · ·                                                                                               |    |

|      | products                                                                                          | 28 |

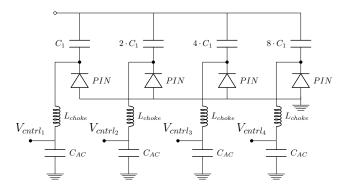

| 3.11 | Discrete tunable element configuration used to increase linearity                                 | 29 |

| 3.12 | Simplified schematic of DLM with the <i>separated design</i> approach                             | 29 |

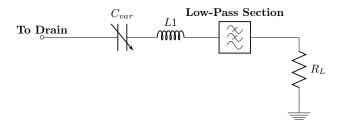

|      | Matching network composed by a low-pass section followed by a tunable element                     | 30 |

| 3.14 | Matching network used to implement switched array capacitor in bulk CMOS                          | 31 |

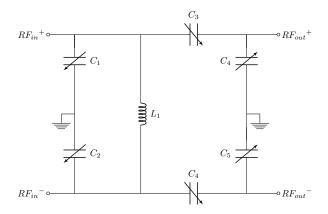

| 3.15 | Differential matching network for discrete DLM in CMOS                                            | 32 |

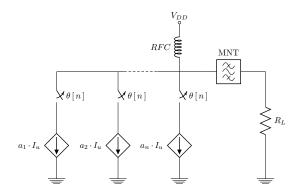

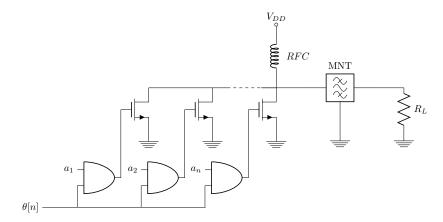

| 4.1  | Single-ended switched-current source array                                                        | 36 |

| 4.2  | CMOS Single-ended switched-resistance array                                                       | 37 |

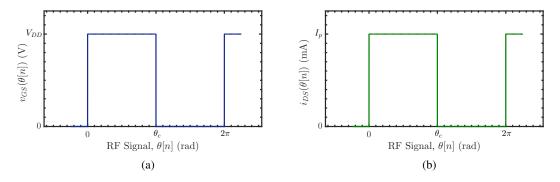

| 4.3  | $v_{GS}$ voltage and $i_{DS}$ current waveform as a function of RF phase modulated signal         | 37 |

xii LIST OF FIGURES

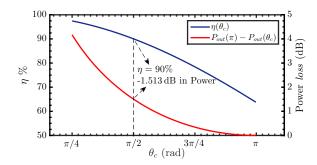

| 4.4        | Evolution of both efficiency and output power <i>loss</i> as a function of the the con- |

|------------|-----------------------------------------------------------------------------------------|

|            | duction angle                                                                           |

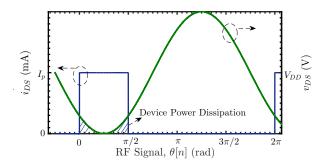

| 4.5        | Idealised waveforms of DRAC topology                                                    |

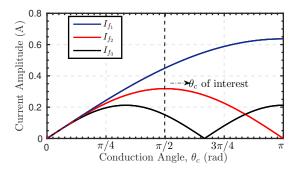

| 4.6        | Fundamental and harmonics evolution as a function of the conduction angle               |

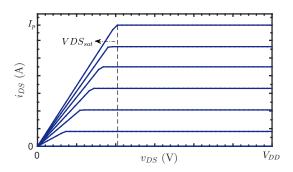

| 4.7        | I-V characteristic of an idealized n-channel MOSFET                                     |

| 4.8        | Drain current and voltage waveform under resistive load                                 |

| 4.9        | Loadline under resistive drain load                                                     |

| 4.10       | Output power as a function of the ratio between resistive and reactive load com-        |

|            | ponents                                                                                 |

|            | Reduced conduction angle DRAC under lightly capacitive and inductive loadlines          |

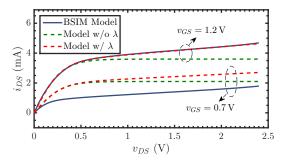

|            | Fitting of the proposed model to describe BSIM $i_{DS}(v_{DS})$ behaviour               |

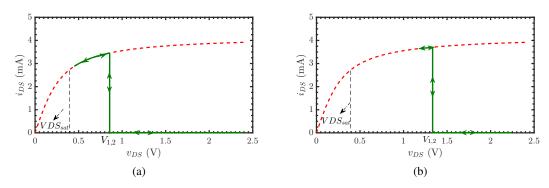

| 4.13       | Resistive loadlines for differente $v_{DS}$ conditions                                  |

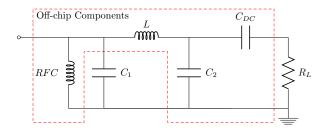

|            | $\pi$ MNT with the inclusion of the RF choke and dc de-coupling capacitor               |

| 4.15       | Current and voltage waveforms under ideal driving conditions                            |

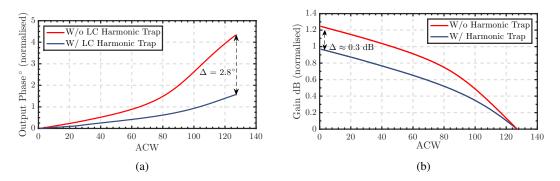

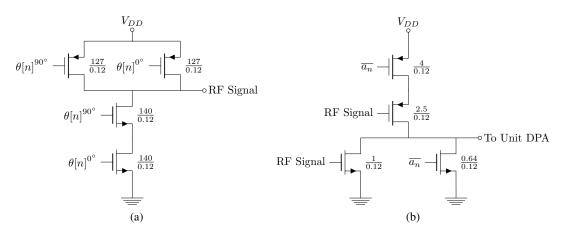

| 4.16       | Output phase and amplitude as a function of the amplitude code word                     |

|            | Proposed DRAC with additional LC harmonic trap                                          |

|            | Drain voltage influence under second harmonic trap                                      |

| 4.19       | DRAC output power and efficiency under second harmonic termination                      |

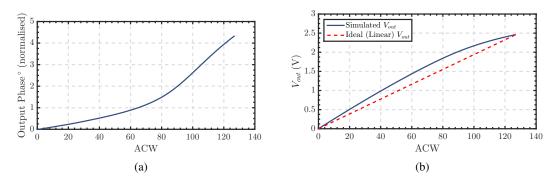

| 4.20       | Output phase and amplitude as a function of the ACW                                     |

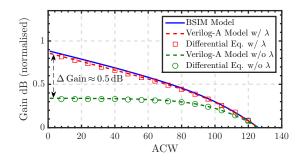

| 4.21       | Simulated gain characteristic with BSIM, verilog-A models and by solving the            |

|            | differential equation                                                                   |

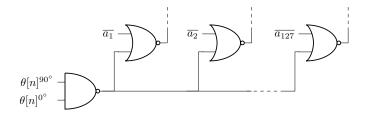

| 4.22       | 25% duty-cycle converter and implicit mixer                                             |

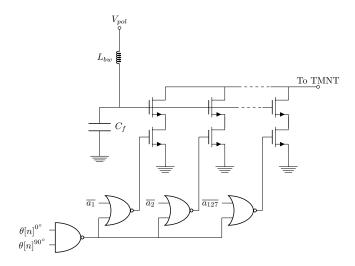

| 4.23       | Transisor level implementation of 25% DT and implicit mixer                             |

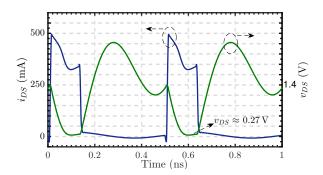

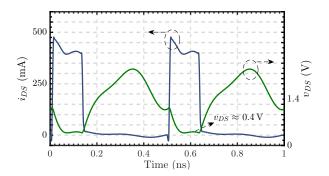

|            | Input signal and its resulting $i_{DS}$ and $v_{DS}$ waveforms                          |

| 4.25       | Efficiency and output power evolution as a function of the DRAC width and duty-         |

|            | cycle                                                                                   |

| 4.26       | Drain current evolution for various widths and duty-cycles                              |

|            | Final schematic of the proposed reduced conduction angle DRAC                           |

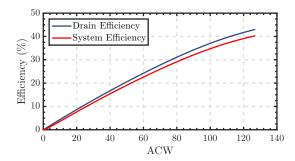

|            | Drain and system efficiency                                                             |

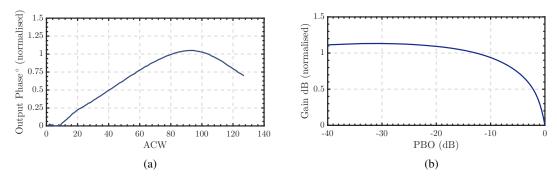

| 4.29       | Phase and gain profile for the final implementation                                     |

| 4.30       | Power and drain efficiency as a function of frequency                                   |

| <b>7</b> 1 | D. H. MOVIII. M. C.                                                                     |

| 5.1        | 1                                                                                       |

|            | Proposed cascode based DRAC                                                             |

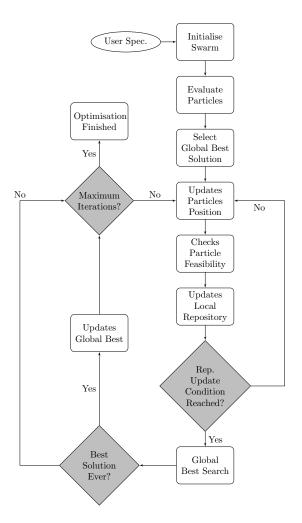

| 5.3        | Proposed PSO based algorithm flowchart                                                  |

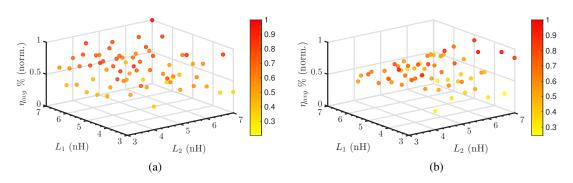

| 5.4        | Average efficiency as a function of inductors $L_1$ and $L_2$                           |

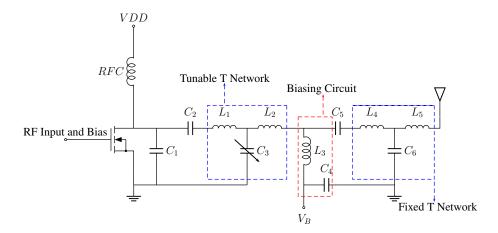

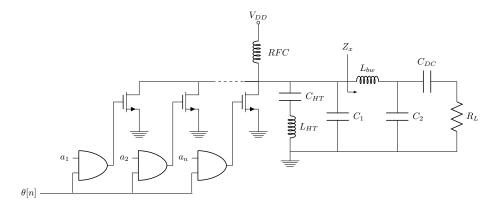

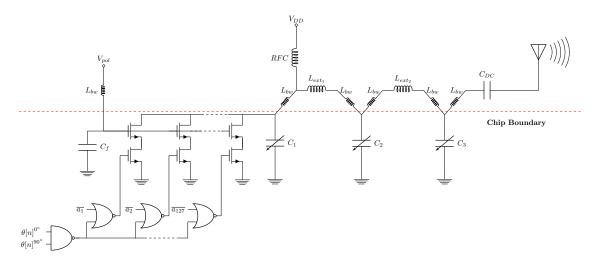

| 5.5        | Proposed DRAC architecture with DLM                                                     |

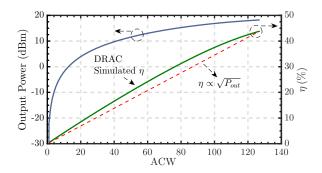

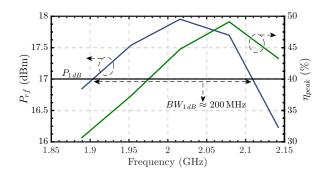

| 5.6        | Output power and efficiency evolution under 3-state DLM                                 |

| 5.7        | Gain and phase evolution under 3-state DLM                                              |

| 5.8        | Output voltage and efficiency after AM-AM linearisation                                 |

| 5.9        | AM-AM linearisation effectiveness both in gain and output phase profiles                |

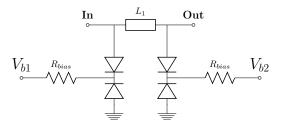

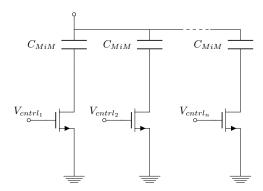

| 5.10       | Tunable capacitor implementation based on MiM and accumulation mode varactor            |

| 5.11       | Switched-capacitor to be implemented in the proposed DLM architecture                   |

| 5.12       | Capacitance and $Q$ evolution in both ON and OFF states as a function of the            |

| <b>.</b>   | NMOS width                                                                              |

|            | Gain and phase variation profile under SCA                                              |

| 5.14       | Drain efficiency comparison between ideal and non-ideal variable capacitors             |

| Д 1        | Double $\pi$ MNT with inductors parasitics                                              |

|            |                                                                                         |

# **List of Tables**

| 2.1 | Comparision of most relevant all-digital transmitters architectures                                                                   | 19       |

|-----|---------------------------------------------------------------------------------------------------------------------------------------|----------|

| 3.1 | Comparision of DLM based transmitters performance                                                                                     | 34       |

|     | Parameters obtained using MATLAB $^{\textcircled{R}}$ non-linear curve fitting Ideal and optimised components values of the $\pi$ MNT | 46<br>49 |

| 5.1 | Inductors employed in the double $\pi$ MNT                                                                                            | 71       |

| 5.2 | Capacitors values found by the algorithm for each one of the sets                                                                     | 71       |

| 5.3 | Comparison of MiM and MoM capacitors provided by technology in use                                                                    | 77       |

| 5.4 | Capacitors values found by the algorithm for each one of the tanks                                                                    | 80       |

xiv LIST OF TABLES

# **Abbreviations**

ACPR Adjacent Channel Power Ratio

AM-to-AM Amplitude-to-Amplitude Modulation AM-to-PM Amplitude-to-Phase Modulation

ac alternating current BOM Bill of Materials

CLM Channel Length Modulation

CS Common-Source

CMOS Complementary Metal-Oxide Semiconductor CORDIC Coordinate Rotation for Digital Computer

CMDC Current-Mode Class D

DCO Digitally-Controlled Oscillator

DPD Digital Pre-Distortion

DSP Digital Signal Processing

DAC Digital-to-Analog Converter

DR Dynamic Range

DRAC Digital-to-RF-Amplitude Converter

dc direct current

DCR Direct Current Resistance

DT Duty-Cycle

DLM Dynamic Load Modulation

EER Envelope Elimination and Restoration

ET Envelope Tracking

EVM Error Vector Magnitude

FoM Figure of Merit GaN Gallium Nitride

HEMT High-Electron-Mobility Transistor

IoT Internet-of-things

LDMOS Laterally Diffused MOSFET

LTE Long Term Evolution

LUT Look-Up Table

LPF Low-Pass Filter

M2M Machine-to-Machine

MNT Matching Network

MiM Metal-Insulator-Metal

MoM Metal-oxide-Metal

MOSFET Metal-Oxide-Semiconductor Field-Effect Transistor

xvi Abbreviations

OFDM Orthogonal Frequency-Division Multiplexing

PAE Power Added Efficiency

PA Power Amplifier

PAPR Peak-to-Average Power Ratio

PBO Power Back-Off

PSO Particle Swarm Optimisation PUF Power Utilization Factor

QAM Quadrature Amplitude Modulation

Q Quality factorRF Radio-Frequency

RF-DAC Radio-Frequency Digital-to-Analog Converter

SOI Silicon-on-Insulator

SDR Software Defined Radio

SC Switched-Capacitor

SCA Switched-Capacitor Array

SCS Switched-Current Sources

SRA Switched-Resistances Array

SoC System-on-Chip

TMNT Tunable Matching NetworkIM3 Third-order IntermodulationPDLM Pulse Dynamic Load Modulation

WCDMA Wideband Code Division Multiple Access

# **Chapter 1**

# Introduction

Since the dawn of the mobile phone, wireless communication has progressively been a natural part of our daily life. From smart-phones to tablets or even smart watches, portability and connectivity are now a key feature of almost all technological devices. It is estimated that by 2020 it will exist more than 24 billion devices connected to the cloud, in which internet-of-things (IoT) gadgets will nearly consist of 70%, while traditional mobile devices will comprise merely 10 billion [1]. IoT applications encompass machine-to-machine (M2M) interfaces and software defined radio (SDR) [2], both expecting a substantial leap in consumer electronics. As an astonishing example, some of the world's biggest electronics vendors are already providing electro-domestics that allow a direct connection to the internet [3]. This phenomenal growth is only partially possible due to the reduced cost of digital signal processing (DSP) blocks, which are traditionally implemented in complementary metal-oxide semiconductor (CMOS) technology, owing to low production costs and process maturity. Additionally, CMOS enables increased system complexity and higher integration, while maintaining a relatively small chip area.

#### 1.1 Towards All-Digital Transmitters

Seeing such an uprising in the number of internet dependent devices, the market and research community are focused on finding new ways to deploy low-cost multi-mode transmitters. In order to enable this ferocious growth, these devices must be compliant with the new wave of wireless standards, while attaining reduced size and cost. CMOS technology appears as the number one option to enable this ambitious goal. Consequently, several efforts have been invested into a complete system-on-chip (SoC) realization of fully integrated multi-mode transmitter in bulk CMOS [4]. However, the power amplifier (PA) block still remains a major roadblock due to its inherent paltry performance in CMOS [5]. In modern nanometre nodes, *traditional* PA design imposes several technical challenges that radio-frequency (RF) engineers must deal with, such as: lossy substrate, low breakdown voltage, low carrier mobility and relatively large output capacitance [6]. Hence, the PA will achieve inadequate performance, degrading the energetic efficiency of the system as a result of its dominance in total device power consumption.

2 Introduction

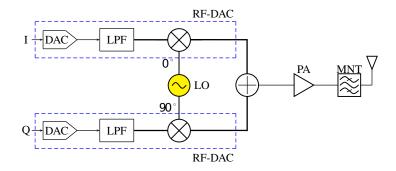

Figure 1.1: Typical analog direct conversion transmitter.

Figure 1.1 shows a typical analog direct conversion transmitter architecture. This architecture presents both in phase (I) and in quadrature (Q) paths, each one with a dedicated digital-to-analog converter (DAC) and low-pass filter (LPF) followed by a mixer. After the filtering and multiplication processes, both paths should be combined to drive the linear (*traditional*) PA. As we can see, from baseband (BB) to the antenna, the data needs to go across several blocks before reaching the PA. For instance, DACs and mixers are known for being either power hungry or quite lossy, imposing several design constraints in advanced CMOS nodes. Hence, this conventional architecture is not as amenable to be implemented in nanometre CMOS nodes due to the inherent poor performance and linearity of the traditional analog blocks [7].

As the available RF spectrum gets more and more crowded, new modulation formats, such as orthogonal frequency-division multiplexing (OFDM), aiming to achieve better spectral efficiency and higher throughputs are being widely adopted [9]. These complex modulation formats often require the transmitter to operate in large power back-off (PBO) regime. Figure 1.2 shows a typical PAPR cumulative distribution function of the OFDM IEEE 802.11a standard for wireless communications [10]. The depicted curve indicates that the probability of the output power being backed-off is considerably high, thus forcing the PA to operate in PBO during large periods of time. Conventional transmitters, as the one presented in figure 1.1, only present the highest dc to RF conversion efficiency when operating close to the peak power. As the transmitter enters in PBO, its efficiency is severely degraded, therefore, shortening the battery life-time. As a consequence, several architectures that propose efficiency enhancement in PBO were developed during the last few decades, namely Doherty, outphasing [11] and envelope tracking (ET) [12]. Due to the non-linear nature of most of these transmitters, digital signal processing techniques are either used to compensate the non-linear behaviour or to generate the desired control signals. More-

Figure 1.2: Cumulative distribution function of PAPR of OFDM IEEE 802.11a [8].

Figure 1.3: System level overview of all-digital transmitters architecture.

over, these architectures are not amenable for nanometre CMOS integration as a consequence of their analog operation nature, inasmuch as they rely on the use of bulky analog blocks. For this reason, the desire for performance enhancement of these traditional architectures is driving the scientific community onto new paradigms that intend to empower amenable nanometre CMOS RF transmitters.

CMOS active devices have been experiencing a tremendous scaling in size, while still increasing even further the current and power gain bandwidths ( $f_T$  and  $f_{max}$ ) [13]. Thus, digital circuitry is more suitable to be implemented in the most advanced nodes than the bulky analog blocks. These features are enabling new research paradigms where digital integration and programmability are being used to overcome the inherent paltry performance of traditional analog blocks in the RF transceiver chain [4]. Furthermore, intensive digital approaches that enable the successful integration and merge of the PA simultaneously with traditional analog blocks in advanced CMOS nodes were reported [14]. Besides, by taking advantage of the CMOS increase in digital signal processing capabilities, numerous novel architectures that intend to overcome the well-known backoff efficiency problem are emerging. For instance, dynamic load modulation (DLM) [9, 15–18], digital outphasing [19], or digital Doherty [20, 21] are among the recent trending architectures that are suitable for large scale integration in nanometre CMOS nodes. Figure 1.3 illustrates the basic conceptual system level overview of an all-digital transmitter architecture, where both digital BB and RF front end are integrated together in a single bulk CMOS chip.

As a consequence, pushing the digital world towards the antenna is becoming more and more attractive. By exploiting these concepts is possible, as amenable to integrate baseband and RF digital-like front ends in a single chip, hence lowering the system final cost, improving the transmitter efficiency and, at the same time, allowing higher programmability. A whole new world of architectures and re-use of traditional analog concepts in digital fashion is right ahead of us. As a summary, the main advantages of utilizing these intensive RF digital approaches are:

- Suitability of integration in advanced bulk CMOS processes;

- System efficiency can be improved eliminating some traditional analog blocks (as we will see further in section 2.1);

- Allows reconfigurable multi-standard operation;

- Amenable to efficiency enhancement methods that rely on signal processing techniques.

4 Introduction

#### 1.2 Problem Statement

The increase in digital circuitry density is paving the way for *cost-free* signal processing capabilities in CMOS SoC. This, in turn, enables numerous untapped techniques that can resort to digital control to enhance the linearity of PBO efficient architectures [19, 22]. Low-power applications have recently been emerging [18], where the peak output power is in the range of 13 dBm to 20 dBm. Furthermore, the required modulation bandwidth is usually between 5 to 20 MHz [18, 23], which somewhat alleviates the design constraints. Thus, digital polar architectures seem to be a reasonable approach to achieve the desired operating conditions. Since long-term lifetime is an appreciable feature for portable devices, empowering a highly-efficient transmitter is a must have characteristic. Moreover, this aspect is of higher importance, considering the sparse efficiency performance of all-digital transmitters in PBO. Thus, exploring techniques whose principles rely on digital control seems a logical approach. Unfortunately, leaving all the linearisation burden to the BB may affect the system efficiency. Considering that the transmitter operates at a relatively low power, employing advanced digital pre-distortion (DPD) techniques [24, 25] may require significant BB power consumption. Additionally, the necessity of a sophisticated DPD is conflicting with multi-mode/standard operation [16].

#### 1.2.1 Dissertation Objectives

Based on the aforementioned challenges and requirements, this dissertation targets the design of an efficient and linear all-digital transmitter. By virtue of its characteristics, digital polar architectures seem the best candidate (as we will shortly see), hence, being the focus of this implementation. Furthermore, the attained peak output power must be located between 17 dBm and 20 dBm. Resorting to a 130 nm CMOS technology, a linear and efficient polar transmitter is predicted to be presented. In order to address the PBO dilemma, an efficiency enhancement technique must also be explored. Moreover, the selected approach is expected to require little overhead in terms of both DPD and complexity. This condition is necessary to allow seamless multi-standard operation.

To summarize, this dissertation's main objectives are:

- Implementation of a polar based digital PA;

- RF peak output power in between 17dBm and 20dBm;

- Must present arguably good linearity;

- Good peak power efficiency;

- PBO efficient:

- Minimise the linearity degradation;

As complementary goals, i.e. sub-objectives, the targets are:

• An innovative polar digital PA shall be investigated;

1.3 Document Outline 5

• Some means will be investigated to overcome the efficiency degradation noticed in all digital PAs:

#### 1.3 Document Outline

This dissertation is organized as follows:

Chapter 2 presents the concept of all-digital transmitters and highlights the advantages over its analog counterpart. RF-DAC and DRAC concepts are also object of discussion for as they are the heart of the RF digitalization concept. The most widely adopted all-digital transmitter architectures are also reviewed, followed by a discussion of the paramount state-of-the-art works.

Chapter 3 is dedicated to dynamic load modulation. A theoretical analysis using a class B PA is first presented in order to provide a solid background, while discussing the power matching condition that ensures device minimum power dissipation. Afterwards, the paramount works related to non-CMOS designs are reviewed along with their pros and cons. Subsequently, CMOS designs that rely on DLM are presented and the advantages of each topology are also analysed.

Chapter 4 proposes a digital PA to be integrated in all-digital polar transmitters. The presented architecture resorts to a novel reduced conduction angle topology to achieve a satisfactory trade-off between peak output power and peak drain efficiency. Section 4.1 presents the theoretical foundations of the proposed architecture, while section 4.2 documents its non-ideal operation as well as the distortion origins. Finally, section 4.3 presents the simulation results of the introduced DPA.

Chapter 5 addresses the PBO efficiency enhancement method. A dynamic load modulation based approach is initially discussed. To deal with the design requirements, an optimisation procedure is introduced in section 5.2. To validate the methodology, a double  $\pi$  matching network is used. Section 5.3 portrays the simulations results of the proposed approach.

At last, but not least, the chapter 6 draws the dissertation final conclusions. The outcome is highlighted as well as future research directions are suggested.

6 Introduction

# Chapter 2

# **All-Digital Transmitters**

Figure 2.1: The two most common forms of distortion in transmitters: AM-to-AM distortion is depicted in (a), while AM-to-PM is illustrated in (b).

Energetic awareness is the today's hot topic due to the ever growing number of electronic devices that the average person owns. Forasmuch as the efficiency of almost all smart devices is dominated by the transmitter performance, its efficiency is used as a fruitful figure of merit (FoM). Drain efficiency,  $\eta$ , is defined in (2.1) as the ratio of the RF output power at the fundamental frequency delivered to the load and the power drawn from the supply.

$$\eta = \frac{P_{RF_{out}}}{P_{dc}} \tag{2.1}$$

Another well-known FoM is the power-added efficiency (PAE), which takes into account the power wasted in driving the transmitter,  $P_{RF_{in}}$ , and is generally defined as:

$$PAE = \frac{P_{RF_{out}} - P_{RF_{in}}}{P_{dc}} \tag{2.2}$$

Figure 2.1a portrays a typical transmitter transfer curve, which depicts the evolution of the output amplitude as a function of the input signal amplitude. When the transmitter is driven with small amplitude, i.e. small signal approximation, the system can be considered approximately linear. However, as soon as the input voltage approaches the upper limit, the transfer curve starts

to compress, yielding non-linear operation. Beyond this point, the transmitter starts to generate additional harmonic content. This phenomena is know as AM-to-AM distortion [26]. To ensure proper operation when amplifying complex modulated signals, the transmitter must be backed-off from the point where the gain drops by 1 dB, also referred as one decibel compression point,  $P_{1 \text{dB}}$ . In linear PAs this phenomenon arises from the fact that after a certain input power level the output voltage swing exceeds the maximum allowed, thus forcing the transistor into triode region (compression) [27]. Although there exists several different forms and causes for AM-to-AM distortion, this one is the most simple and is intended to be used as an introductory example.

Another typical signal distortion source is the amplitude to phase conversion, or AM-to-PM. For instance, let us start by assuming that the system is being excited by the following signal,  $f_{in}(t) = V_{in}(t) \cdot \cos(2\pi\omega_c t + \phi_{in}(t))$ . The envelope of the signal reveals a dependency of  $V_{in}(t)^1$ , which is variable over time. For simplicity, it will be assumed that the input phase is set fixed,  $\phi_{in}(t) = const$ . Consequently, the only variable in the system that is changing over time is the signal amplitude,  $V_{in}(t)$ . If we measure the output signal and observe a time varying phase,  $\phi_{out}(t)$ , the signal is said to be under AM-to-PM conversion, and again, non-linear operation is attained. Voltage dependent capacitances are partially responsible for this amplitude induced phase modulation [26]. As an example, figure 2.1b illustrates an amplitude to phase conversion transfer curve. Both axes are set normalized to peak values, respectively.

Complex modulated signals employ both phase and amplitude modulation, thusly requesting highly linear transmitters. As previously seen, transmitters can (usually) only be approximated as *quasi-linear* systems in a well defined region of operation. Therefore, methods to check the signal integrity (linearity) after being conveniently amplified are needed. Since AM-to-AM and AM-to-PM are some of the responsible for spectral regrowth and signal distortion, error vector magnitude (EVM) and adjacent channel power ratio (ACPR) are useful tools to test the robustness of the signal after the transmitter [28]. As it will be promptly addressed in chapter 2.1, the previously enumerated tests also measure the influence of the output noise in the signal integrity and out-of-band noise.

#### 2.1 RF-DAC Fundamentals

As it was previously observed, conventional analog blocks and linear PAs present sparse performance in advanced low power CMOS nodes. Hence, the development of new architectures that are amenable for digital integration is currently driving the scientific community onto new paradigms. Figure 2.2 illustrates a digital direct conversion architecture employing an RF-DAC block, as proposed in [29]. This revolutionary concept proposes the merge of the DAC and mixer in just one mixed-signal block, obviating the need for a LPF. The goal of this novel topology is to promote a unit that can effectively produce an RF phase and amplitude modulated carrier, while enabling efficient linear modulation. By employing a sigma-delta ( $\Sigma\Delta$ ) RF-DAC based on eight current steering cells [29], a successful prototype was built to demonstrate the concept. The unit-cell

<sup>&</sup>lt;sup>1</sup>Although not stated,  $V_{in}(t)$  could be assumed to present a sinusoidal waveform.

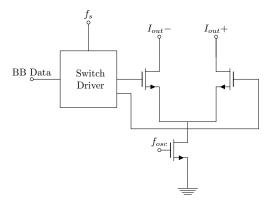

Figure 2.2: RF-DAC conceptual system level as proposed in [29].

differential-pair, as depicted in figure 2.3, is driven by a differential data path (1 bit control) that modulates the output current on and off. This way, it is possible to reconstruct an RF output signal whose amplitude is time varying and digitally controlled by the data path. Hence, this RF-DAC works as an amplitude modulator for the RF carrier signal,  $f_{osc}$ , thus also acting like a *mixer* between the digital data and the RF signal. The switching action of the data path must be timely accurate with the  $f_{osc}$  signal in order to reduce glitches. Hence,  $f_s = \frac{f_{osc}}{n}$ , where n is a fixed integer that ensures the required timing. Also, the phase between  $f_s$  and  $f_{osc}$  should be aligned to guarantee on-off action in the zero crossing of the oscillator signal. Suppressing the LPF enables better performance while reducing even further the number of elements in the transmitter. As a matter of fact, this novel topology has the potential to allow better noise performance and, concurrently, providing hardware reduction [29].

Figure 2.3: One of the RF-DAC eight unit cells based on current steering [29].

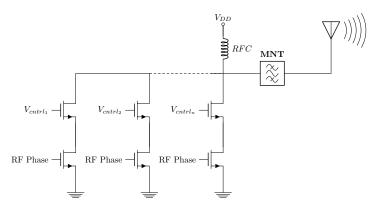

Although this concept was revolutionary, one piece of the puzzle was still missing. In [14] a modified RF-DAC architecture was proposed, including now the PA in the same block. The key difference here is that the unit cell is now comprised by a *miniaturized* PA, thus the digital-to-analog conversion is now performed by acting on the several PAs units. From now on, we will also address this topology as digital-to-RF-amplitude converter (DRAC) (i.e. power RF-DAC). The authors propose a current summation at the output, as depicted in figure 2.4. By controlling the applied digital signal in the 64 cascode transistors,  $V_{ctr_n}$ , digital amplitude modulation is

performed similar as in an RF-DAC. Considering that now the power RF-DAC is comprised by several small PA units, it allows a direct connection to the antenna, hence performing digital-to-RF up-conversion in the *power domain*. Each unit cell was implemented using cascode class A PAs,

Figure 2.4: Digital polar architecture employing switched current array as proposed in [14].

thus leading to an inadequate average PAE of 6.7% while transmitting an OFDM signal. Nonetheless, a peak output power of 13.6dBm was achieved and superior performance in comparison with analog class A PA is verified. Besides the paltry performance of the proposed architecture, this work cleared the way for the crave digitalization of the entire RF transmitter chain, demonstrating the superior performance of this digital approach over the analog counterpart due to the suppression/merge of several bulky analog blocks.

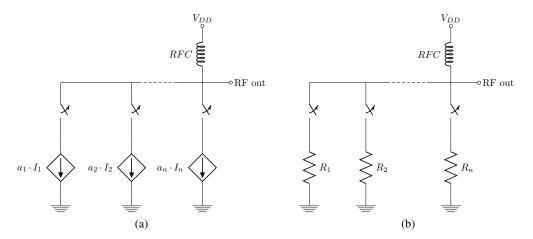

A more power efficient solution to implement a DRAC can be accomplished by switching several resistances in parallel, thus taking advantage of CMOS switching speed [4]. This allows the use of non-linear PAs classes, which are inherently more efficient [30]. Conceptually, the architecture is the same as adopted in figure 2.4. Now, instead of class A PAs, the authors use near-class E unit cells without cascode topology, therefore improving the power efficiency. However, this switching resistance topology yields highly non-linear operation, thus degrading the system linearity [6].

As it was previously stated, adopting the RF-DAC/DRAC topology obviates the need for a LPF, an advantage that, unfortunately, does not come for free. Since the LPF was responsible for the so-called reconstruction process, where the replicas at the multiples of the sampling frequency were erased, the output spectrum will now present extra undesired content around the RF frequency [31]. Furthermore, due to the zero-hold-order nature of the DRAC, the output spectrum will also present noise-floor that is dependent of the resolution of the transmitter, similar as in a DAC [31]. All this unwanted emissions will be redirected to the antenna, thusly degrading the signal quality. However, due to the presence of a bandpass filter between the all-digital transmitter and antenna, the constraints are somewhat relaxed, but not completely eliminated. Therefore, DRAC based all-digital transmitters must the carefully designed in order to ensure that EVM and ACPR wireless standards specifications are fulfilled.

A diversity of digital processing techniques are widely adopted to reinforce the performance of all-digital transmitters. In [14] discrete-time digital interpolation and up-sampling methods are

Figure 2.5: DRAC implementation as: (a) switched-current array or (b) switched-resistances as depicted in [27].

presented in order to mitigate the output spectral images generated by the DRAC. To tackle the noise floor adversity, the resolution of the DRAC must be properly selected. Generally, a trade-off between binary and unit weighted cells is used to achieve a satisfactory performance and, at the same time, low complexity [32].

To summarize, as depicted in figure 2.5, DRAC based transmitters usually rely either on switched-current sources or switched-resistances [27]. While the first one usually reconstructs the output envelope more accurately, the later achieves higher efficiency and is the most amenable for implementation in advanced CMOS nodes. As a matter of fact, none of the above is a panacea for all applications, and the right choice is influenced by several factors, such as modulation format, frequency, etc.

#### 2.2 All-Digital Transmitters Architectures

Transmitter architectures suited for digital integration comprise the ultimate goal of CMOS SoC transmitters. Therefore, some of the most widely used digital approaches will be presented. Subsections 2.2.1 and 2.2.2 intend to present the state-of-the-art works related to digitally enhanced polar and I/Q DRACs, respectively, while the subsection 2.2.3 has the purpose of reporting all-digital outphasing architectures. The various trade-offs are also analysed, while highlighting the novel aspects of each one of the proposed works.

#### 2.2.1 Digital Polar Transmitter

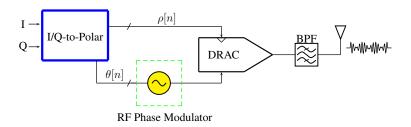

Figure 2.6 depicts a generalized digital polar architecture. Instead of the typical I and Q paths, this approach uses digital signal processing to originate separated phase,  $\theta$ , and amplitude,  $\rho$ , paths. This way, the phase modulated carrier drives a DRAC, which is then responsible to perform amplitude modulation, thus, originating at the output the required complex-envelope signal,  $S = \frac{1}{2} \frac{1}$

$\rho e^{j\theta}$  [31]. A coordinate rotation digital computer (CORDIC) algorithm [33] is normally used for I/Q-to-polar conversion. This non-linear conversion, stated in (2.3) and (2.4), gives rise to bandwidth expansion, hence, degrading the system performance [31]. Regardless, this architecture shows the most promising power efficiencies, as we will promptly see.

Figure 2.6: DRAC based digital polar transmitter.

$$\rho[n] = \sqrt{I^2 + Q^2} \tag{2.3}$$

$$\theta[n] = \tan^{-1}\left(\frac{Q}{I}\right) \tag{2.4}$$

In [14], a novel switched current DRAC is presented, achieving high linearity but poor efficiency. To solve this efficiency issue, various digital polar architectures were recently presented.

In [34], a switched resistance DRAC is proposed with enhanced dynamic range. Cascode topology is adopted with a bias controlled voltage that allows the extension of the output power dynamic range. Furthermore, 43% peak efficiency is achieved at 800MHz, attaining 24.4dBm peak output power.

Figure 2.7: SC unit cell based on cascode Class D and MiM capacitor as proposed in [35]

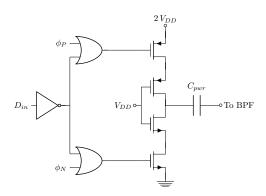

Switched-capacitor (SC) DRAC [35] also appears as an appealing solution for digitally enhanced polar transmitters. Instead of using switched current/resistance arrays, the proposed solution uses a bank of binary and unitary weighted capacitors, whose charging process is accomplished using unit class D PAs acting as switches. As depicted in figure 2.7<sup>2</sup>, each unit cell is

<sup>&</sup>lt;sup>2</sup>Although proposed in the original work, the required level shifter is omitted in this figure.

Figure 2.8: DRAC based digital polar transmitter with extended dynamic range and frequency tunable MNT as proposed in [36].

composed by a stacked class D driver and capacitor,  $C_{pwr}$ . If the unit cell is on (signal  $D_{in}$ ), the class D unit is switching between ground and supply at the carrier frequency,  $\phi_P/\phi_N$ , otherwise it is constantly connected to one of them. Clock signals,  $\phi_P$  and  $\phi_N$ , are digitally controlled in order to avoid the overlapping switching process, hence improving the transmitter performance. The output power is a function of how many capacitors are being charged, therefore amplitude modulation is performed. This architecture presents an average efficiency of 27% when transmitting an OFDM 802.11g 64-QAM signal. Furthermore, on-chip matching is included, which lowers the bill of materials (BOM) of the transmitter.

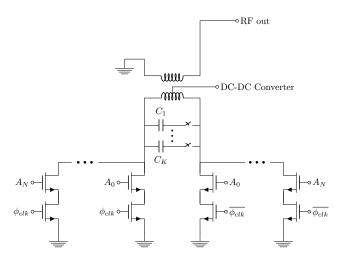

Nakatani *et al.* [36] presented a digital polar transmitter based on current-mode class D (CMDC) unit cells with a digitally controlled buck converter. Figure 2.8 depicts the simplified structure of the DRAC core. Phase modulated signals,  $\overline{\phi_{clk}}$  and  $\phi_{clk}$ , are responsible for the switching action of the bottom transistors of the cascode, while the control voltage,  $A_N$ , digitally modulates the amplitude. By adopting stacked unit cells, the feed-through due to  $C_{GD}$  capacitance is reduced, which improves the polar transmitter performance. The proposed topology intends to overcome the dynamic range issue imposed by recent modulation standards. In order to do so, tri-state CMCD unit cells are employed jointly with a digitally controlled DC-DC converter. Capacitors  $C_1$  to  $C_K$  are used in shunt with the transformer to enable frequency operation between 0.75 GHz and 2 GHz. This architecture achieves peak efficiency of 11.5% at 850 MHz, while the upper band (1.75 GHz) efficiency is near 22%. Improved PBO performance is also claimed and a remarkable output power of 29 dBm is disclosed. Ineptly, the overall transmitter efficiency is one of the lowest among the recent proposed works, which negatively affects the approach followed by the authors.

In [16], the authors proposed a polar transmitter based on a CMCD switched array PA. Instead of using a digital algorithm for phase digital code generation (i.e. CORDIC), this work presents an integrated 9-bit phase modulator. This is achieved using a fully differential RF-DAC structure and, afterwards, limiting the amplitude variation. Employing a 1-bit dynamic load modulation, this design achieves an 50-60% improvement at 6dB PBO. Complete linearisation is also presented

and the reported peak efficiency is 43% when delivering 23.3 dBm output power.

Another possible approach to implement a digital polar architecture can be accomplished using a digital approach to the conventional Doherty topology [20]. This approach uses a digital main amplifier based on CMDC that is powered on for the entire time. The peak digital amplifier is only toggled on from 0dB to 6dB, hence performing the active load modulation. This implementation achieves good performance between 3.10GHz and 3.98GHz. The measured peak efficiency is above 25% in the entire frequency spawn, while attaining an average improvement of 40-50% in comparison with ideal class B operation [12]. Moreover, the obtained output power is 27.3dBm.

In [22], the authors propose a dual supply digital Doherty. The core of the transmitter is based on the architecture proposed in [20] and the superior performance observed in this implementation is related to the usage of supply switching. By switching from  $V_{DD}$  to  $V_{DD}/2$  at 12dB PBO, the efficiency is greatly improved. This design also reports an incredible fractional bandwidth of 48%, which is claimed by the authors to be the best in class between fully integrated CMOS Doherty PAs. In order to accomplish this phenomenal fractional bandwidth, the authors propose a linearisation scheme that compensates the mismatch verified in the quadrature signals. By placing varactors at the output of the drivers, controlling their biasing introduces adjustments in the phase of the signals, hence maintaining the quadrature over the entire spawn. Furthermore, these same varactors can be used to compensate the AM-PM non-linearity of the transmitter. Peak efficiency of 42% while producing 26.7 dBm output power is reported.

#### 2.2.2 I/Q Digital Transmitter

Figure 2.9: Digital I/Q transmitter DRAC based.

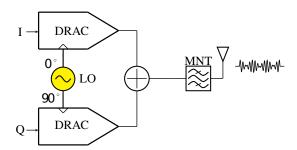

Although digital polar architectures present state-of-the-art efficiency results, the bandwidth expansion problem imposes a limit on the instantaneous bandwidth that the transmitter can support. Digital quadrature transmitter (I/Q) shows an auspicious position to solve this issue. Figure 2.9 presents the typical all digital I/Q transmitter. Both in-phase and in-quadrature signals are up-converted and amplified by two different DRACs. This ensures minimum signal expansion, since the out-coming signal is summed right upon amplification, forming then the desired complex modulated signal without non-linear conversion processes involved.

In [21], a four-phase I/Q Doherty digital transmitter is proposed. Each path has an own dedicated differential DRAC, being the output power combined in a main and peak transformer. The

Figure 2.10: Quadrature digital transmitter with four quadrant control based on class E unit cells propsed in [37].

achieved output power is 24.8 dBm with a peak drain efficiency of 26%. Despite the peak efficiency being very poor, due to the load modulation nature of the Doherty architecture, the quadrature transmitter achieves 26% efficiency at 6dB PBO. Furthermore, the transformer network is modulated with tuning capacitors to further enhance the efficiency below 6dB. Even though the metrics are promising, the reported signal instantaneous bandwidth is limited to 10MHz.

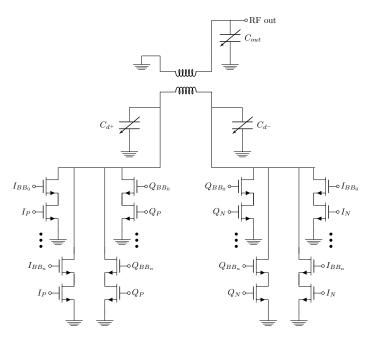

Alavi *et al.* presented in [37] a wideband  $2 \times 13$ -bit quadrature digital transmitter that addresses the four quadrants. The DRAC core reported in this work is illustrated in figure 2.10. Based on a novel approach employing 25% duty-cycle (DT) in each data path, i.e.  $I_P$ ,  $I_N$ ,  $Q_P$  and  $Q_N$ , orthogonal summation is performed, thereby reducing I/Q load interaction. Signals  $I_{BB}$  and  $Q_{BB}$  control the amplitude modulation of each baseband data path, in which a blend of binary and unitary weighted unit cells is adopted. Since the signal reconstruction is performed in quadrature, the carrier phase modulation process is no longer needed, therefore reducing the system complexity and related bandwidth extension issues reported in the polar architecture. Capacitors  $C_{out}$ ,  $C_d^+$  and  $C_d^-$  are employed here to ensure that the load interaction between each data path is minimized within the intended operation frequency range. Each DRAC unit cell is designed to work in class E PA. Unfortunately, this condition is only achieved when the transmitter is operating in peak power. The maximum output power and efficiency are 22.8 dBm and 42%, respectively. A remarkable maximum channel bandwidth of 154 MHz is reported, being the profile efficiency the downside of this approach, which is quite similar to a class B.

In [38] another I/Q quadrature digital transmitter is successfully deployed. Based on CMCD unit cells, the transmitter is able to reconstruct signals with bandwidth as high as 80MHz, while still attaining an impressive 17% average drain efficiency. Authors also state that this transmitter

is able to amplify signals with 160MHz while still presenting satisfactory EVM performance.

Once again, the SC topology is reported in the implementation of a DRAC based transmitter [39]. Similar as in the polar architecture [35], the core of the DRAC cell is the same. Instead of a polar architecture, the DRAC is now divided in four different sections, comprising the  $I^-$ ,  $I^+$ ,  $Q^-$  and  $Q^+$ , therefore, addressing all the four quadrants. Peak reported efficiency is only 21%, thus supply switch is adopted for efficiency enhancement. The maximum reported channel bandwidth is only 10MHz. Moreover, the output power achieved is 20.5 dBm.

#### 2.2.3 Outphasing Digital Transmitter

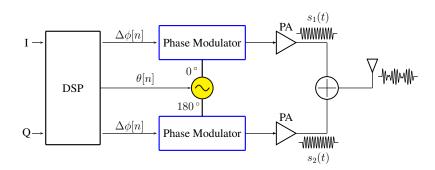

The outphasing concept was born in 1935 by the hand of H. Chireix [40]. The basic principle of the contemporary version of this architecture is the reconstruction of the complex signal at the output at the expense of summing two phase modulated RF signals with constant envelope,  $s_1(t)$  and  $s_2(t)$ . Baseband signals, I and Q, are pushed into a DSP block that generates two phase modulated signals,  $\theta + \Delta \phi$  and  $\theta - \Delta \phi$ , which are time varying. The phase information is encoded in the variable  $\theta$ , similarly as in the polar architecture, while the amplitude modulation is now performed by  $2\Delta \phi$  out-phase angle. This information must be used to modulate two RF carriers

Figure 2.11: System level schematic of an all-digital outphasing system.

with constant envelope, giving origin to the desired signals  $s_1(t)$  and  $s_2(t)$  as in (2.5) and (2.6), respectively [11]. Each phase modulated carrier drives a separated high efficiency PA (generally switched PA), whose output power must be summed. Due to the *out-phase* action of the  $2\Delta\phi$  angle between the two RF carriers, amplitude modulation is performed when both are added.

Despite of presenting an excellent theoretical efficiency performance in PBO, this architecture presents two main drawbacks: how to efficiently perform the output power summation from each PA and how to modulate the RF carriers. Since nanometre CMOS nodes present high capabilities for enhanced time resolution [4], digital processing capabilities are bringing new approaches to the phase modulators. Hence, all-digital phase modulators can be successfully accomplished. As the digital polar architecture, the outphasing also suffers from bandwidth expansion issue due to the non-linear nature of the I/Q-to-outphasing conversion process [11]. Figure 2.11 illustrates a typical digital outphasing modulator architecture. As previously stated, the DSP block generates the

2.3 Conclusions

digital phase signals, which now feed two different digital phase modulators. After this process, the following part is similar as in the analog version.

$$s_1(t) = 0.5V_o \cdot \sin(2\pi\omega_c t + \theta[n] + \Delta\phi[n]) \tag{2.5}$$

$$s_2(t) = -0.5V_o \cdot \sin(2\pi\omega_c t + \theta[n] - \Delta\phi[n])$$

(2.6)

In [19] a digitally outphasing approach for wideband applications was successfully presented. The phase modulation is decomposed in two sequential tasks. First, the RF carrier is phase modulated ( $\theta[n]$ ) using a digitally-controlled oscillator (DCO) [4], which is then used to feed two digital modulators that are now responsible to perform the desire additional phase modulation that enables the time varying amplitude at the output (after summation). These two digital modulators are based on delay-locked-loops, thus taking advantage of digital integration and enhanced time resolution of advanced nanometre CMOS nodes. By adopting this approach,  $1-5\,\text{GHz}$  wideband<sup>3</sup> operation is attained. It is worth to note that the focus of this work is the digital phase modulator instead of the following PAs. Another reported digitally intensive outphasing modulator can be found in [41]. The peak output power is 20 dBm with 22% PAE when implemented in 32 nm CMOS process.

Although this architecture seems very promising to achieve higher levels of integration than its analog counter part, the research work with a complete all-digital outphasing transmitter is still scarce. Moreover, when compared with the quadrature or polar all-digital approaches, this implementation requires more system level blocks, which may imply more complexity and a overall lower system efficiency.

### 2.3 Conclusions

Resorting to the peak efficiencies attained, it is clear that the digital polar is the most strong candidate to accomplish the highest transmitter power efficiency. Moreover, they also present the best enhanced efficiencies in PBO. Also, a novel multi-band polar transmitter is reported, being able to operate between a large frequency spawn. Despite the enumerated advantages, the bandwidth expansion issue as well as the timing mismatch verified in the combination of both paths at the output are still a major roadblock for the deployment of wideband polar architectures.

Quadrature modulators present the best in class instantaneous channel bandwidth at the expense of orthogonal I/Q summing. A record 154MHz modulated instantaneous bandwidth is reported, while other work meets the EVM requirements for 160MHz channel bandwidth. Since nothing comes for free, this excellent *linearity* comes at the expense of lower average efficiencies than the polar counter parts.

<sup>&</sup>lt;sup>3</sup>This frequency spawn is related to the frequency range that this architecture can address, opposing to the instantaneous modulated bandwidth.

All-digital outphasing appears as a promising candidate to meet in between the quadrature and polar digital transmitters. Although few research is found in literature, this architecture seems very promising to achieve higher channel bandwidths than the digital polar architecture, while still showing a better efficiency profile than digital quadrature transmitters.

Each architecture presents its pros and cons and the desired transmitter architecture must be selected in order to achieve the required specifications. Despite everything, it is clear that by relying on this new wave of digital transmitter architectures and resorting to digital signal processing techniques for linearisation, which are native of CMOS processes, pleasant performances can be attained. Table 2.1 presents a summary of the reported state-of-the-art all-digital transmitters.

Table 2.1: Comparision of most relevant all-digital transmitters architectures.

| ulated signal                     | 8)) PAE DPD Eff. Enhanced                     | .5) 24.5% Yes Discrete DLM |                   | 28.8% <sup>+</sup> Yes Active Load Modulation | 28.8% <sup>+</sup> <b>Yes</b> 18.8% <sup>+</sup> <b>Yes</b> 2 | 28.8%+ <b>Yes</b> / 18.8%+ <b>Yes</b> / 35%* <b>Yes</b> | 28.8% <sup>+</sup> Yes 1<br>18.8% <sup>+</sup> Yes 25.6% Yes 27.7% Yes | 28.8% <sup>+</sup> Yes 18.8% <sup>+</sup> Yes 25.7% Yes 27.7% Yes | 28.8% <sup>+</sup> Yes 18.8% <sup>+</sup> Yes 27.7% Yes 27.7% Yes 28.8% <sup>+</sup> Yes | 28.8% <sup>+</sup> Yes 18.8% <sup>+</sup> Yes 27.7% Yes 27.7% Yes 27.7% Yes 18.8% <sup>+</sup> Yes N.A. Yes | 28.8%+ Yes 18.8%+ Yes 18.8%+ Yes 27.7% Yes 27.7% Yes 28.8%+ Yes N.A. Yes 12.2% Yes      | 28.8% <sup>+</sup> Yes 18.8% <sup>+</sup> Yes 18.8% <sup>+</sup> Yes 27.7% Yes 27.7% Yes N.A. Yes N.A. Yes 12.2% Yes 17% <sup>+</sup> Yes |

|-----------------------------------|-----------------------------------------------|----------------------------|-------------------|-----------------------------------------------|---------------------------------------------------------------|---------------------------------------------------------|------------------------------------------------------------------------|-------------------------------------------------------------------|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Measurement with modulated signal | Iz) Signal (PAPR (dB))                        | 64-QAM OFDM (6.5)          | 16 OAMON A        | 10-CA:VI)IVIA)                                | Multi tone OFDM                                               | Multi tone OFDM WCDMA(3.4)                              | Multi tone OFDM WCDMA(3.4) 64 OFDM(6.5)                                | Multi tone OFDM WCDMA(3.4) 64 OFDM(6.5)                           | Multi tone OFDM<br>WCDMA(3.4)<br>64 OFDM(6.5)                                            |                                                                                                             | 9                                                                                       |                                                                                                                                           |

|                                   | (z) Peak $P_{out}$ (dBm)/ $\eta$ (%) BW (MHz) | 23.3/43 20                 | 27/32.5 N.A.      |                                               | 24.8/26 10                                                    | 24.8/26 10<br>24.4/43* N.A.                             |                                                                        |                                                                   |                                                                                          | 31                                                                                                          | _                                                                                       | -                                                                                                                                         |

|                                   | $^{7}$ req. (GHz) Peak $P_{out}$ (dBm)        |                            | 3.10-3.98 27/32.5 |                                               |                                                               |                                                         | .,                                                                     | ‡                                                                 | ±                                                                                        | ‡ .                                                                                                         | ±                                                                                       | ±                                                                                                                                         |

|                                   | Architecture                                  | Polar                      | Polar Doherty     |                                               | I/Q Doherty                                                   | >                                                       |                                                                        |                                                                   | _                                                                                        |                                                                                                             |                                                                                         |                                                                                                                                           |

|                                   | CMOS Tech.                                    | 65 nm                      | 65nm              |                                               | 90nm                                                          | 90 nm<br>65 nm                                          | 90 nm<br>65 nm<br>90 nm                                                | 90nm<br>65nm<br>90nm<br>150nm                                     | 90nm<br>65nm<br>90nm<br>150nm<br>65nm                                                    | 90 nm<br>65 nm<br>90 nm<br>150 nm<br>65 nm                                                                  | 90 nm<br>65 nm<br>90 nm<br>150 nm<br>65 nm<br>65 nm                                     | 90 nm<br>65 nm<br>90 nm<br>150 nm<br>65 nm<br>65 nm<br>65 nm                                                                              |

|                                   |                                               | [16]-2013                  | [20]-2015         |                                               | [21]-2012                                                     | [21]-2012<br>[34]-2014                                  | [21]-2012<br>[34]-2014<br>[35]-2011                                    | [21]-2012<br>[34]-2014<br>[35]-2011<br>[36]-2016                  | [21]-2012<br>[34]-2014<br>[35]-2011<br>[36]-2016<br>[22]-2016                            | [21]-2012<br>[34]-2014<br>[35]-2011<br>[36]-2016<br>[22]-2016<br>[37]-2014                                  | [21]-2012<br>[34]-2014<br>[35]-2011<br>[36]-2016<br>[22]-2016<br>[37]-2014<br>[39]-2016 | [21]-2012<br>[34]-2014<br>[35]-2011<br>[36]-2016<br>[22]-2016<br>[37]-2014<br>[39]-2016<br>[38]-2013                                      |

N.A. - Not available

\* - External matching network/balun

\*\* - PAE

+ - Drain efficiency

++ - Frequency tunable matching network

# **Chapter 3**

# **Dynamic Load Modulation**

Several approaches that enhance the PA PBO efficiency have been proposed, such as Doherty [42], outphasing [43], envelope elimination and restoration (EER) [44] and ET [45]. Doherty and outphasing are inherently narrow-band, so RF scientists are working towards highly integrated approaches that increase the bandwidth [19, 20, 22, 41, 46]. EER and ET rely on the use of power supply modulators, which moves the problem of efficiency and complexity from the PA itself to the envelope modulator. Despite the good results achieved in this approach, circuitry overhead and complexity along with bandwidth concerns are severe [47].

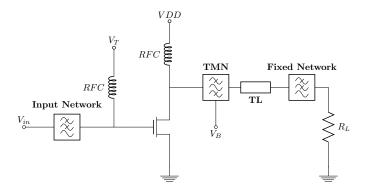

Figure 3.1: Basic schematic of class B power amplifier with idealized transistor.

## 3.1 Fundamentals of Dynamic Load Modulation

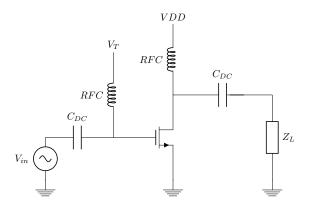

An alternative approach for efficiency enhancement is the use of dynamic load modulation. This technique makes use of a tunable matching network (TMNT) for proper adjustment of the PA load impedance according to the instantaneous magnitude of the signal envelope. The power amplifier schematic depicted in figure 3.1 shows us a n-channel MOSFET with the gate properly biased at

Figure 3.2: I-V characteristic of idealized n-channel MOSFET.

$V_T$  and with a given complex drain load impedance,

$$Z_{L} = \begin{cases} R_{L} + j0 \ \Omega & : f = f_{1} \\ 0 \ \Omega & : f \neq f_{1} \end{cases}$$

(3.1)

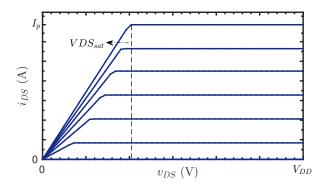

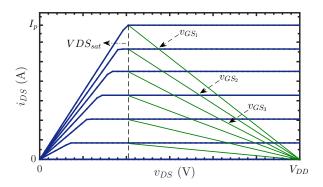

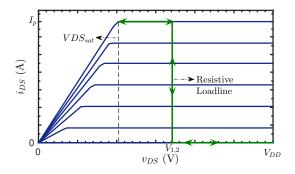

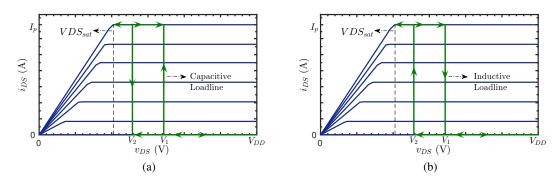

For the time being, we will assume that the n-channel MOSFET behaves solely as an ideal voltage controlled current source, whose ideal I-V curve is portrayed in figure 4.7. In the interest of simplifying the following analysis, it shall be assumed that the evolution of the  $i_{DS}$  current has a linear dependency of  $v_{GS}$  (in saturation).

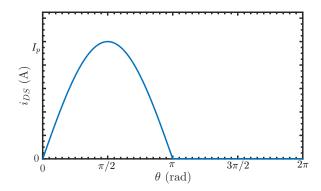

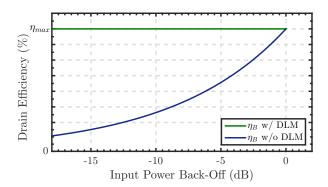

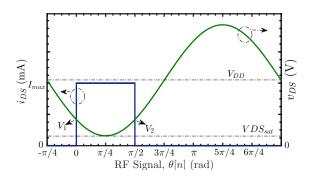

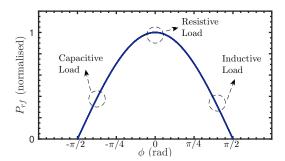

Since the transistor in figure 3.1 is biased at the pinch-off voltage, and for the case where  $v_{GS} \le V_{DD}$  considering sinusoidal input excitation, one can verify that the drain current has the waveform depicted in figure 3.3, which corresponds to the classical half-wave rectified sinusoid given as a function of the conduction angle,  $\theta \in [0, 2\pi]$ . From now on,  $v_{GS}$  will be used to represent the actual peak value of the combined dc plus ac signal magnitude of the gate to source voltage value, and  $i_{DS}$  to identify the actual peak magnitude value of the composite dc plus ac current signal. This classical class B configuration is usually designed to operate under the maximum possible (peak) power that the given MOSFET can support. Considering that the drain load impedance,  $Z_L$ , is given by (3.1),  $R_L$  must be designed according to the loadline theory [12], which leads to,

$$R_L = \frac{\Delta V_{ac}}{\Delta I_{ac}} = \frac{2 \cdot (V_{DD} - VDS_{sat})}{I_p} = \frac{2 \cdot \Delta V_{max}}{I_p}$$

(3.2)

where  $I_p = I_{max}$  is the maximum peak drain current and  $\Delta V_{max} = (V_{DD} - VDS_{sat})$  is the peak allowable output (i.e. drain) voltage swing  $(v_{DS})$  that guarantees that the MOSFET still behaves as an ideal current source (transistor does not enter the ohmic region). One can define the highest output power at the fundamental frequency as

$$P_{out_{max}} = \frac{i_{DS_{max}} \cdot \Delta V_{max}}{4} = \frac{R_L \cdot I_p^2}{8}$$

(3.3)

Figure 3.3: Ideal half-wave rectified sinusoid for a class B PA.

and the dc power consumption,  $P_{dc_{max}}$ , as

$$P_{dc_{max}} = \frac{V_{DD} \cdot i_{DS_{max}}}{\pi} = \frac{V_{DD} \cdot I_p}{\pi}$$

(3.4)

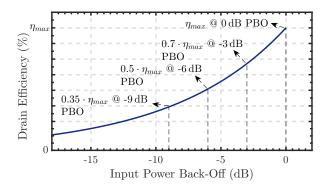

Given (3.3), (3.4) and recalling (2.1) we shall now determine the peak drain efficiency,  $\eta_{max}$ , with

$$\eta_{max} = \frac{P_{out_{max}}}{P_{dc_{max}}} = \frac{\pi R_L I_p^2}{8 V_{DD} I_p} = \frac{\pi}{4 V_{DD}} \times \frac{R_L I_p}{2} = \frac{\pi}{4} \times \frac{\Delta V_{max}}{V_{DD}}$$

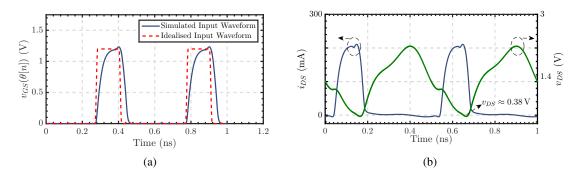

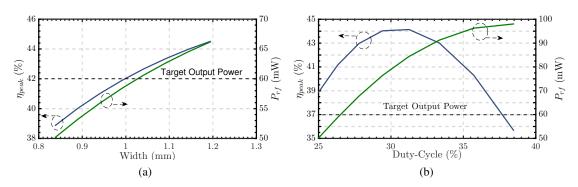

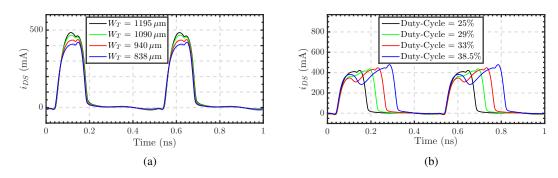

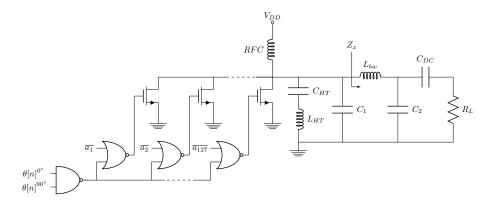

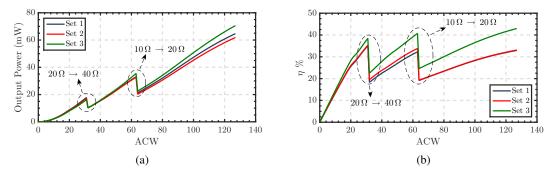

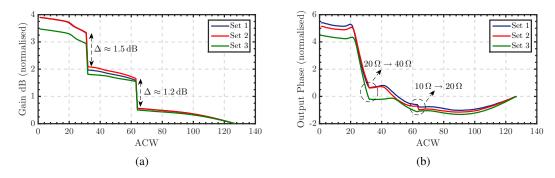

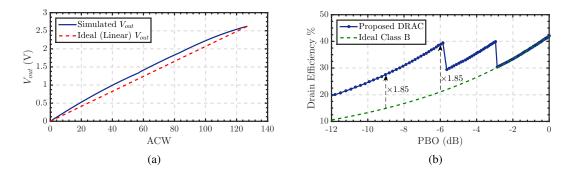

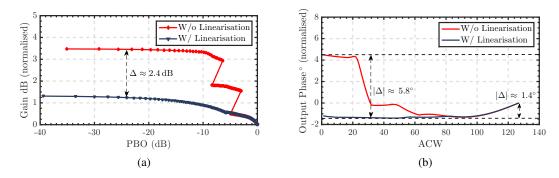

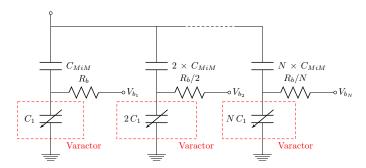

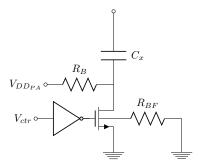

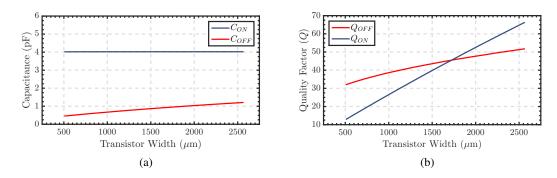

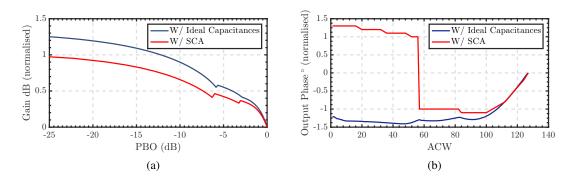

(3.5)