# PROFET: Modeling System Performance and Energy Without Simulating the CPU

Milan Radulovic

Barcelona Supercomputing Center

(BSC) & Universitat Politècnica de

Catalunya (UPC)

Barcelona, Spain

milan.radulovic@bsc.es

Rommel Sánchez Verdejo BSC & UPC Barcelona, Spain rommel.sanchez@bsc.es Paul Carpenter BSC Barcelona, Spain paul.carpenter@bsc.es

Petar Radojković BSC Barcelona, Spain petar.radojkovic@bsc.es Bruce Jacob University of Maryland College Park, Maryland, USA blj@umd.edu Eduard Ayguadé BSC & UPC Barcelona, Spain eduard@ac.upc.edu

# **ABSTRACT**

The approaching end of DRAM scaling and expansion of emerging memory technologies is motivating a lot of research in future memory systems. Novel memory systems are typically explored by hardware simulators that are slow and often have a simplified or obsolete abstraction of the CPU. This study presents PROFET, an analytical model that predicts how an application's performance and energy consumption changes when it is executed on different memory systems. The model is based on instrumentation of an application execution on actual hardware, so it already takes into account CPU microarchitectural details such as the data prefetcher and out-of-order engine. PROFET is evaluated on two real platforms: Sandy Bridge-EP E5-2670 and Knights Landing Xeon Phi platforms with various memory configurations. The evaluation results show that PROFET's predictions are accurate, typically with only 2% difference from the values measured on actual hardware. We release the PROFET source code and all input data required for memory system and application profiling. The released package can be seamlessly installed and used on high-end Intel platforms.

# **CCS CONCEPTS**

• Computing methodologies → Model development and analysis; • Hardware → Dynamic memory.

## **KEYWORDS**

Memory bandwidth; Memory access latency; DRAM; MCDRAM; Performance; Power; Energy; Modeling

# 1 INTRODUCTION

The memory system is a major contributor to the deployment and operational costs of a large-scale high-performance computing (HPC) cluster [24, 35, 38], and in terms of system performance it is one of the most critical aspects of the system's design [20, 41]. For decades, most server and HPC cluster memory systems have been based on DRAM DIMMs. However, it is becoming questionable whether DRAM DIMMs will continue to scale and meet the

industry's demand for high performance and high capacity memory. Significant effort is therefore being invested into the research and development of future memory systems.

Application performance on novel memory systems is typically estimated using a hardware simulator. The simulation is, however, time consuming, which limits the number of design options that can be explored within a practical length of time. Also, although memory simulators are typically well validated [23, 32], current CPU simulators have various shortcomings, such as simplified out-of-order execution, an obsolete data prefetcher and a lack of virtual-to-physical memory translation, all of which can make a huge difference between the simulated and actual memory system, in terms of behavior and performance.

This study proposes PROFET (PROFiling-based EsTimation of performance and energy), an analytical model that predicts how an application's performance, power and energy consumption would change when it is executed on a new memory system. The method is based on instrumentation of an application running on actual hardware, so it already takes account of CPU microarchitectural details such as the real (and not publicly disclosed) data prefetcher and out-of-order engine. Therefore, it can be used to model various platforms as long as they support the required application profiling. PROFET was initially developed for the Sandy Bridge platform, and later we evaluated it for the Knights Landing (KNL) server. Adjustment of the PROFET model to the KNL system was trivial, as it required changes to only a few hardware parameters, such as, for example the reorder buffer size.

We evaluated PROFET on two actual platforms: Sandy Bridge-EP E5-2670 with four DRAM configurations DDR3-800/1066/1333/1600, and Knights Landing Xeon Phi with DDR4 and 3D-stacked MCDRAM. The evaluation results show that PROFET's predictions are very accurate: the average difference from the performance, power and energy measured on the actual hardware is only 2%, 1.1% and 1.7%, respectively. We also compare PROFET's performance predictions with simulation results for the Sandy Bridge-EP E5-2670 system with ZSim [33, 40] and DRAMSim2 [32], and PROFET shows significantly better accuracy over the simulator. PROFET is also faster than the hardware simulators by *three orders of magnitude*, so it can be used to analyze production HPC applications, on arbitrarily sized systems.

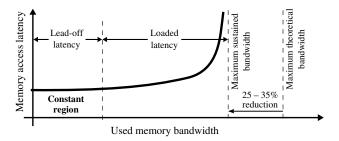

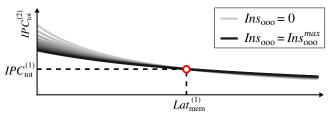

Figure 1: Bandwidth-latency curve showing how the memory access latency depends on the used memory bandwidth. It is critical to distinguish between the *lead-off* and *loaded* memory access latency regions [20].

We release the PROFET source code as open source [31]. The release includes all inputs and outputs and evaluation results for the case study that is used in the rest of this paper. The package includes the memory system profiles, CPU parameters, application profiles and memory power parameters, as well as the power, performance and energy outputs from PROFET and the measurements on the baseline and target platforms. The released PROFET model is ready to be used on high-end Intel platforms, and we would encourage the community to use it, adapt it to other platforms, and share their own evaluations.

#### 2 PROFET OVERVIEW

This section summarizes the main idea behind PROFET's analytical models and it describes the inputs and outputs to PROFET.

# 2.1 Background: Memory bandwidth and latency

The memory access latency and used bandwidth are often described as independent concepts, but they are in fact inherently interrelated [20]. We start by clarifying what is meant by the lead-off and loaded memory access latencies, and then we address the connection between memory access latency and used memory bandwidth. Lead-off memory access latency corresponds to the single-access read latency in an idle system. This latency includes the time spent in the CPU load/store queues, cache memory, memory controller, memory channel and main memory. Loaded memory access latency corresponds to the read latency in a loaded system. In addition to all timings included in the lead-off latency, the loaded memory latency includes shared-resource contention among concurrent memory requests. As illustrated in Figure 1, the loaded memory access latency increases (non-linearly) with the used bandwidth, due to increasing contention among concurrent memory requests. It is critical to distinguish between the lead-off and loaded latencies because the difference between them can be on the order of hundreds of nanoseconds.

# 2.2 The idea: Moving between memory curves

The main idea of this paper is that we can understand the effect of changing the memory system by understanding how the application moves from one bandwidth–latency curve to another. We illustrate this idea using the DDR4 and MCDRAM memories on

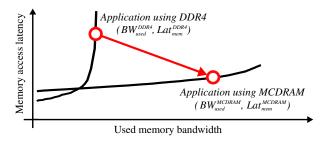

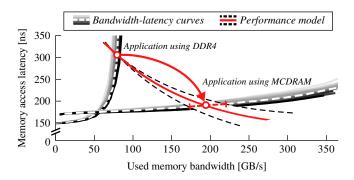

Figure 2: High-level view of the transition from DDR4 to high-bandwidth MCDRAM memory on the KNL platform.

Intel's Knights Landing platform. This platform has two memory systems, so there are two bandwidth–latency curves, shown together on the same plot in Figure 2.<sup>1</sup> When used bandwidth is high, as seen towards the right of the figure, MCDRAM is clearly better. In contrast, when used bandwidth is low, as seen towards the left, DDR4 has lower latency due to its lower lead-off latency.

When an application (or application phase) executes on the DDR4 main memory, it will be positioned at some point on the DDR4 curve; e.g.  $(BW_{used}^{DDR4}, lat_{mem}^{DDR4})$  illustrated in Figure 2. Analogously, when the same application is executed on the MCDRAM memory, it will be positioned at some point on the MCDRAM curve, e.g.  $(BW_{used}^{MCDRAM}, lat_{mem}^{MCDRAM})$ . We see that the application in Figure 2 benefits from running on the MCDRAM through a lower memory latency (MCDRAM point is lower) and a higher used bandwidth (MCDRAM point is to the right). This idea, of moving between bandwidth–latency curves, is central to the PROFET performance, power and energy models presented in this paper.

# 2.3 PROFET inputs

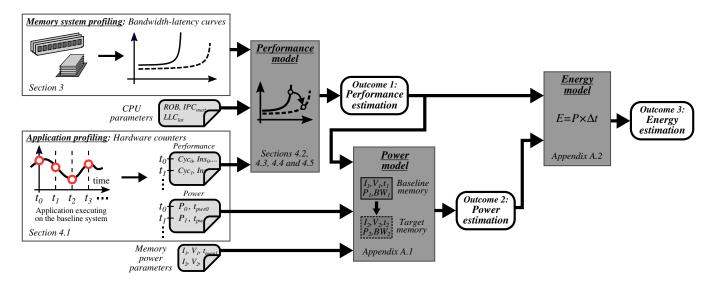

Figure 3 gives a high-level overview of the whole process of performance, power and energy estimation. The inputs to PROFET, shown towards the left of the figure, are the bandwidth-latency curves, measured for the *baseline memory system* and the *target memory system*, parameters for the CPU (which is the same for both memory systems), as well as the application profiles on the baseline memory system. These inputs can all be easily obtained on mainstream platforms and many emerging platforms. The outputs from PROFET will be the predicted performance, power and energy consumption on the target memory system.

**Memory system profiling** is done via bandwidth–latency curves, for the baseline and target memory systems, along the lines outlined in Section 2.1. The precise method for obtaining these curves is given in Section 3, which describes the memory profiling microbenchmarks and their outputs.

**CPU parameters** are needed, alongside the application profiling (see below), to characterize the relationship between memory system latency and execution time. This relationship is dependent on the processor's ability to hide memory latency by overlapping memory accesses with independent instructions. As detailed in Section 4.3, the PROFET performance model therefore requires some basic parameters of the processor under study: re-order buffer (ROB)

$<sup>^1{\</sup>rm Figure~2}$  shows a simplified bandwidth–latency curve, as discussed in Section 2.1. Detailed curves are given in Figure 4 in Section 3.

Figure 3: Diagram of the whole process of performance, power and energy estimation. The cross-references indicate which section describes which part of the estimation process.

capacity, miss information status holding register (MSHR) capacity and minimum theoretical cycles-per-instruction (CPI).

Application profiling is done on the baseline memory system, and consists of executing the application and profiling it using hardware performance counters. Application performance profiling obtains the number of CPU cycles, number of instructions, number of last-level cache (LLC) misses and the read and write memory bandwidths. Application power profiling measures the total power consumption using integrated or external power measurement infrastructure, and memory-related power parameters using performance counters. Since the application's behavior changes over time, application profiling is done by sampling over regular time intervals, which we refer to as segments. Further details on application profiling are given in Section 4.1.

**Memory power parameters** characterize the baseline and target memory systems, in terms of the power consumption in various operational modes, idle state and power-down states, as well as the energy consumption for various operations such as read and write transfers, row buffer hits and misses. These figures are typically provided by the memory device manufacturers [28].

#### 2.4 Performance, power and energy estimation

Figure 3 gives an overview of the whole process of performance, power and energy estimation. Since application profiling involves collecting a trace over the program's execution, the PROFET performance and power models are run for each segment (time interval) in the trace. This gives the predicted execution time, power and energy consumption of each segment. Summing over time gives the final execution time and energy for the whole application. The application's average power demand is total energy divided by total execution time.

The **PROFET performance model** reads the application performance information from the profiling trace-file and determines the application's position on the bandwidth-latency curve for the baseline memory system. As described in detail in Sections 4.2, 4.3 and 4.5, PROFET then estimates the application's position on the memory bandwidth–latency curve for the target memory system, and uses it to predict the application's performance on the target memory system.

The **PROFET power model** estimates the power consumption of the target memory system using the application performance profiling and the memory power parameters. Finally, the **PROFET energy model** is done based on the output of the performance and power models. Due to a lack of space, the detailed description and evaluation of the PROFET power and energy models are presented in Appendices A.1, A.2 and B.1.

# 3 MEMORY SYSTEM PROFILING

The baseline and target memory systems are characterized using bandwidth–latency curves. For mature technologies, these curves are measured on a real platform. For emerging memory devices that are not yet available in off-the-shelf servers, the bandwidth–latency curve can be measured on a developer board with a prototype of the new device [2], or alternatively it can be provided by the manufacturer.

The bandwidth-latency curve is determined using a pointer-chasing microbenchmark designed to measure latency [34] running concurrently with a derivative of the STREAM benchmark [27] that was modified to vary the load on the memory system. Currently, profiling of a single memory system configuration, e.g., DDR3-1600, is performed in approximately 15 minutes (see Appendix B.2.3).

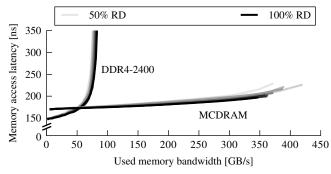

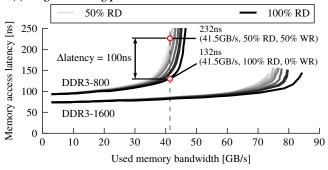

Although Section 2.1 plots a single bandwidth–latency curve, in reality a single memory system has a family of curves that depend on the ratio between read and writes in the overall memory traffic. As an example, Figure 4 shows the measured bandwidth–latency curves for the Knights Landing and Sandy Bridge platforms, as the proportion of reads is varied between 50% and 100%. The lightest curves correspond to 50% reads and the darkest curves correspond

to 100% reads. Instead of the single bandwidth-latency curve per memory system that was illustrated in Figure 1, we now see a family of curves. When the used memory bandwidth is low or moderate, the read fraction has negligible impact on the memory access latency and the bandwidth-latency curves practically overlap. As the stress to the memory system increases, however, the read fraction starts to have a significant impact on latency. For example, in Figure 4b, at an aggregate bandwidth of 41.5 GB/s, the (read) latency with 100% reads is 132 ns, but the read latency with 50% reads and 50% writes is 232 ns, an increase of 100 ns (76%). In general, for all experiments we did, shown in Figure 4, curves with a higher percentage of writes (lighter curves) are located higher (at higher latency) on the chart. The main reason is that write requests incur additional delays that are not required by memory reads [19].<sup>2</sup> Increasing the proportion of write requests therefore reduces the sustainable bandwidth and increases the loaded latency.

Recently, Clapp et al. [4] also did a preliminary analysis of bandwidth-latency curves for different memory frequencies (DDR3-1333 and DDR3-1600) and different read-to-write ratios (3:1 and 2:1). Based on an analysis of four curves, the authors conclude that it is sufficient to use a single, generic memory bandwidth-latency curve for different frequencies and memory traffic compositions. Our analysis is based on numerous measurements on a wide range of DDR3, DDR4 and MCDRAM frequencies, with fine-grain changes in the read-to-write ratio. Our findings show that different memory frequencies have fundamentally different bandwidth-latency curves with different shapes and different lead-off and maximum memory access latencies. We also show that the read-to-write ratio may have a significant impact on memory access latency. Directly contrary to the conclusion of Clapp et al. [4], our study shows that the relationship between bandwidth and latency cannot be approximated with a single curve. To the best of our knowledge, ours is the first study of memory system read latency that makes this conclusion.

# 4 PERFORMANCE MODEL

This section presents the PROFET analytical model that predicts the application's performance. We start, in Section 4.1, by outlining the application characteristics that must be measured on the baseline system. Then, in Section 4.2, we introduce the problem with a simple case, that of an in-order processor. Next, in Section 4.3, we analyse a complex out-of-order processor. Section 4.4 completes the analysis of out-of-order processor performance as a function of latency. Finally, in Section 4.5, we explain how PROFET combines this latency—performance characterization with the bandwidth—latency curves to obtain the estimate, with error bars, of the application performance on the target memory system.

# 4.1 Application profiling

As outlined in Section 2.3, the application's execution is divided into segments at regular time intervals. For each segment, we measure, using performance measuring counters, the number of cycles, number of instructions, read last-level cache (LLC) misses, used memory

(b) Sandy Bridge platform with DDR3-800/1066/1333/1600. DDR3-1066 and DDR3-1333 are excluded to improve the visibility.

Figure 4: Bandwidth-latency curves for the platforms under study. Memory access latency w.r.t. used memory bandwidth cannot be approximated with a single curve — as the used memory bandwidth increases, memory traffic read/write composition makes a significant latency impact.

bandwidth, and the overall fraction of reads. These parameters and the notation used in the paper are listed in Table 1.

Table 1: PROFET performance model input parameters

| Input parameter                                    | Symbol                                    |

|----------------------------------------------------|-------------------------------------------|

| Number of cycles                                   | $Cyc_{tot}$                               |

| Number of Instructions Application read LLC misses | Ins <sub>tot</sub><br>Miss <sub>IIC</sub> |

| Used memory bandwidth for total traffic            | $BW_{\text{used}}^{(1)}$                  |

| Fraction of reads in total traffic                 | $Ratio_{ m R/W}$                          |

The used memory bandwidth,  $BW_{used}$ , and fraction of reads,  $Ratio_{\rm R/W}$ , include all memory accesses, whether issued by the application or the prefetcher, since both types of accesses cause contention and have a similar impact on memory system read latency. In contrast,  $Miss_{\rm LLC}$  only includes LLC read misses issued by the application. This parameter is used to estimate how the memory read latency impacts application performance, and only application read misses have a direct performance impact.

In order to determine the duration of the sampling interval, we analyzed the tradeoff among the measurement overhead, trace-file size and PROFET accuracy. An interval of 1 s was selected because it

$<sup>^2</sup>$  Write Recovery time or  $t_{\rm WR}$  is the minimum delay between the end of a write and the next precharge command. The Write To Read delay time or  $t_{\rm WTR}$  is the minimum time interval between a memory write and a consecutive read.

provided high accuracy (see Section 7) while introducing negligible measurement overhead of below 1%. With this sampling interval, the trace-file size of the benchmarks used in the study is in the range of hundreds of megabytes, which is acceptable.

# 4.2 In-order processors

This section derives the relationship between latency and performance for a simple in-order CPU. In the interest of helping the reader to follow the formulas, we start by summarizing PROFET's inputs and outputs in Table 2.

Table 2: Notation used in formulas: In-order processors

| Description                                                | Symbol               |

|------------------------------------------------------------|----------------------|

| Inputs (in addition to Table 1)                            |                      |

| Memory access latency from bandwidth-latency curve         | $Lat_{\mathrm{mem}}$ |

| Memory access penalty ( $Lat_{mem}$ minus LLC hit latency) | $Pen_{\mathrm{mem}}$ |

| Intermediate outputs                                       |                      |

| Single LLC miss penalty (number of CPU stall cycles)       | $Stalls_{ m LLC}$    |

| Application cycles-per-instruction                         | $CPI_{tot}$          |

| CPI component in the case of perfect LLC                   | $CPI_0$              |

| CPI component due to LLC misses penalties                  | $CPI_{ m LLC}$       |

| Outputs                                                    |                      |

| Application instructions-per-cycle (1/CPItot)              | $IPC_{tot}$          |

Our analysis distinguishes between *Memory access latency*, *Memory access penalty* and *LLC miss penalty*. **Memory access latency**, *Lat*<sub>mem</sub>, is the number of CPU cycles necessary for a single load instruction that reads data from the main memory. It is measured as part of the memory system profiling and given in the memory bandwidth–latency curve. **Memory access penalty**, *Pen*<sub>mem</sub>, is the difference between the latency of a main memory access and the latency of an LLC hit. The values of *Lat*<sub>mem</sub> and *Pen*<sub>mem</sub> are inputs to PROFET. The values for the baseline memory system are found by looking up the application's used bandwidth, measured on the baseline memory system. The values for the target memory system are generated as explained in Section 4.5. Finally, **LLC miss penalty**, *Stalls*<sub>LLC</sub>, is calculated by PROFET as the average number of cycles for which the CPU pipeline is stalled because of each LLC miss.

We start by partitioning the application cycles-per-instruction,  $CPI_{\text{tot}}$ , into two components [4, 8, 14, 22]:  $CPI_{\text{tot}} = CPI_0 + CPI_{\text{LLC}}$ . The first component,  $CPI_0$ , is the application's CPI for the hypothetical case of a 100% LLC hit rate. This component is not affected by the memory access latency. The second component,  $CPI_{\text{LLC}}$ , is due to execution stalls due to the LLC misses. Once we know the number of stall cycles to be attributed to each LLC miss, we can calculate its value as [3, 14]:

$$CPI_{\rm LLC} = \frac{Miss_{\rm LLC} \times Stalls_{\rm LLC}}{Ins_{\rm tot}} \tag{1}$$

We use the superscripts (1) and (2) to distinguish between the baseline and target memory systems, respectively:

Baseline memory:

$$CPI_{\text{tot}}^{(1)} = CPI_0^{(1)} + CPI_{\text{LLC}}^{(1)}$$

Target memory:  $CPI_{\text{tot}}^{(2)} = CPI_0^{(2)} + CPI_{\text{LLC}}^{(2)}$  (2)

Since the memory access latency does not affect  $CPI_0$ , we have  $CPI_0^{(1)} = CPI_0^{(2)}$ . Therefore,  $CPI_{\text{tot}}^{(2)}$  from Eq. 2 can be expressed as:

$$CPI_{\text{tot}}^{(2)} = CPI_{\text{tot}}^{(1)} + \left(CPI_{\text{LLC}}^{(2)} - CPI_{\text{LLC}}^{(1)}\right) \tag{3}$$

Next, we assume that a change in the memory system, which for this section is a change in the read access latency, does not change the number of instructions,  $Ins_{tot}$ , or the application's memory access pattern. This is a reasonable assumption for applications or computational kernels that do not use busy-waiting or dynamic scheduling. The assumption is valid for both in-order and out-of-order processors. A change in the memory access latency may affect the timeliness of the prefetcher, but it should not consistently affect its coverage or accuracy; in any case, we found this effect to be small.<sup>3</sup> We therefore also assume that the LLC miss rate is unaffected by the change in memory latency. In summary, we conclude that we do not need superscripts (1) or (2) on  $Ins_{tot}$  and  $Miss_{LLC}$ . We can therefore substitute Eq. 1 into Eq. 3 to obtain:

$$CPI_{\rm tot}^{(2)} = CPI_{\rm tot}^{(1)} + \frac{Miss_{\rm LLC}}{Ins_{\rm tot}} \times \left(Stalls_{\rm LLC}^{(2)} - Stalls_{\rm LLC}^{(1)}\right) \tag{4}$$

We have not yet assumed an in-order processor, so all the above equations are also true for out-of-order processors. For an in-order processor, we make the single observation that LLC misses directly lead to pipeline stalls, i.e.:  $Stalls_{LLC} = Pen_{mem}$ . Substituting this into Eq. 4 gives:

$$CPI_{\text{tot}}^{(2)} = CPI_{\text{tot}}^{(1)} + \frac{Miss_{\text{LLC}}}{Ins_{\text{tot}}} \times \left(Pen_{\text{mem}}^{(2)} - Pen_{\text{mem}}^{(1)}\right)$$

for an in-order processor (5)

Eq. 5 is important because it shows that the difference in application CPI for different memory systems,  $CPI_{\rm tot}^{(2)}$  and  $CPI_{\rm tot}^{(1)}$ , can be calculated based on the corresponding memory access penalties,  $Pen_{\rm mem}^{(2)}$  and  $Pen_{\rm mem}^{(1)}$ . Finally, by replacing IPC = 1/CPI, the application performance on the target memory system is calculated as:

$$IPC_{\text{tot}}^{(2)} = \frac{1}{\frac{1}{IPC_{\text{tot}}^{(1)}} + \frac{Miss_{\text{LLC}}}{Ins_{\text{tot}}} \times (Pen_{\text{mem}}^{(2)} - Pen_{\text{mem}}^{(1)})}$$

for an in-order processor (6)

## 4.3 Out-of-order processors

The analysis for out-of-order (OOO) processors is more complex because following an LLC miss the processor can continue executing independent instructions without immediately being stalled. In consequence, the number of stalls per LLC miss is no longer equal to the full memory access penalty, and it is typically strictly lower than it:  $Stalls_{\rm LLC} < Pen_{\rm mem}$ . In order to handle this inequality, it is necessary to introduce the additional symbols given in Table 3.

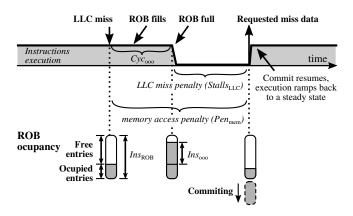

4.3.1 **Isolated LLC miss.** We first consider an isolated LLC miss. As illustrated in Figure 5, when an LLC miss occurs (isolated or not), the corresponding instruction must wait for data from memory, but the CPU pipeline continues issuing and executing independent instructions. Execution may halt, however, before the LLC miss is resolved, for two reasons. First, instruction issue may stop because the instruction window has filled with instructions, all of which are dependent, directly or indirectly, on the instruction waiting for data

$<sup>^3</sup>$  We measured the number of prefetches per instruction on our Sandy Bridge evaluation platform (Section 6.1). The overall difference between DDR3-800 and DDR3-1600 memory configurations across all benchmarks is less than 5%.

Table 3: Notation used in formulas: Out-of-order processors

| Description                                             | Symbol       |  |

|---------------------------------------------------------|--------------|--|

| Inputs                                                  |              |  |

| Instructions in reorder buffer                          | $Ins_{ROB}$  |  |

| Size of miss information status holding register (MSHR) | MSHR         |  |

| Minimum CPI, equal to reciprocal of maximum IPC         | $CPI_{\min}$ |  |

| Intermediate outputs                                    |              |  |

| Number of execution cycles overlapped with              | Cua          |  |

| LLC miss stalls, due to OOO mechanism                   | $Cyc_{000}$  |  |

| Number of instructions executed during                  | Ino          |  |

| LLC miss stalls, due to OOO mechanism                   | $Ins_{000}$  |  |

| $Cyc_{tot}$ component in the case of perfect LLC        | $Cyc_0$      |  |

| Memory level parallelism:                               | MLP          |  |

| Number of concurrent LLC misses (memory accesses)       | IVI L.F      |  |

from main memory. Second, instruction commit may stop because the reorder buffer (ROB) has filled with instructions that cannot be committed until after the waiting instruction has itself been committed. The upper part of Figure 5 shows a timeline indicating whether instruction execution has halted, while the lower part of the figure shows snapshots of the ROB occupancy before an isolated LLC miss, while the processor is waiting for data, and after the data has been received. Following the LLC miss, the ROB is occupied with a certain number of instructions. The ROB begins to fill, as the processor executes independent instructions. At some point, either there are no more independent instructions or the ROB becomes full. In either case, instruction execution will stall. Once the LLC miss has been resolved and the LLC miss data are available, the instructions waiting for the data can be executed and committed. This allows the instructions in the ROB to be committed, so the processor can resume issuing and executing new instructions.

In Figure 5, the period after the LLC miss in which the processor is executing new independent instructions is labeled as  $Cyc_{000}$ . So, the number of stall cycles is given by [14, 22]:

$$Stalls_{LLC} = Pen_{mem} - Cyc_{ooo}$$

for an isolated miss (7)

If execution is immediately halted following the LLC miss, then  $Cyc_{000}$  would equal zero, and the LLC miss penalty would equal the memory access penalty, as for the in-order case in Section 4.2.

The number of independent instructions that are executed during this period, of  $Cyc_{000}$ , is referred to as  $Ins_{000}$ , and indicated in the lower half of Figure 5. The connection between  $Cyc_{000}$  and  $Ins_{000}$  requires knowledge of the CPI over the period. Our analysis partitions the application execution in sampling segments of 1 second (detailed in Section 4.1), and considers there to be a steady average execution rate. So, during these execution segments the CPI equals its average rate of  $CPI_0$ , as detailed in Table 2 and the corresponding text. Therefore,  $Cyc_{000}$  can be calculated as:

$$Cyc_{000} = CPI_0 \times Ins_{000}$$

for an isolated miss (8)

The factor of  $Ins_{000}$  depends on the number of independent instructions and the number of free instruction slots in the ROB. It is analyzed in detail in the next section.

4.3.2 **Estimating Ins**<sub>000</sub>. State-of-the-art architectures do not incorporate counters that can be used to measure the value of Ins<sub>000</sub>. We therefore calculate bounds on its value and incorporate

Figure 5: In OOO processors, LLC misses overlap with the execution of the instructions independent of the missing data. The overlap depends on the number of independent instructions in the instruction window and number of free entries in ROB [22].

these bounds into the PROFET error estimate. We use the platformspecific parameters and the application's measured CPI.

**The**  $Ins_{000}$  **lower bound** is trivial:  $Ins_{000} \ge 0$ , since OOO execution may stop immediately after the LLC miss and continue being stalled until the requested miss data arrives.

The  $Ins_{000}$  upper bound is calculated as the lower of two constraints. The first is the reorder buffer size,  $Ins_{ROB}$ , which corresponds to the maximum number of instructions that can be stored in the ROB [22]:

$$Ins_{000}^{\max 1} = Ins_{ROB} \tag{9}$$

The ROB size is a characteristic on the target architecture. In our study, we analyze two architectures, as described in Section 6. In Sandy Bridge EP-2670 CPU the ROB comprises 168 entries, while in Intel Knights Landing Xeon Phi 7230 it has 72 entries.

The second upper bound is determined by the maximum number of instructions that can be executed during the LLC miss. In this scenario, the whole  $Pen_{\rm mem}$  is covered by the OOO execution, so  $Cyc_{\rm 000}$  would equal  $Pen_{\rm mem}$ . Therefore, since  $Ins_{\rm 000}$  is calculated as  $Cyc_{\rm 000}/CPI_0$  (Eg. 8), we can combine the two equations to find that the maximum number of instructions that the processor will execute in this time is  $Pen_{\rm mem}/CPI_0$ . Since the second upper bound assumes that OOO execution covers the whole memory access penalty, there cannot be any stalls due to LLC misses, i.e.,  $CPI_{\rm LLC}$  would equal 0. Therefore, since the application's overall CPI is defined to be  $CPI_{\rm tot} = CPI_0 + CPI_{\rm LLC}$ , it must be (in this case) that  $CPI_{\rm tot}$  equals  $CPI_0$ . Combining these facts, the final form of the second upper-bound, given in terms of inputs to PROFET, becomes:

$$Ins_{000}^{\text{max2}} = Pen_{\text{mem}} \times \frac{Ins_{\text{tot}}}{Cyc_{\text{tot}}}$$

(10)

The overall upper bound on *Ins*<sub>000</sub> is the minimum of the two limits:

$$Ins_{000}^{max} = \min \left( Ins_{ROB}, \quad Pen_{mem} \times \frac{Ins_{tot}}{Cyc_{tot}} \right)$$

(11)

Figure 6: Handling overlapping LLC misses in an OOO processor: the penalty of a single miss is divided by a number of concurrent LLC misses [22].

Since the value of *Ins*<sub>000</sub> can be anywhere between its bounds we consider *Ins*<sub>000</sub> to be a free parameter and perform a sensitivity analysis when calculating other dependent parameters.

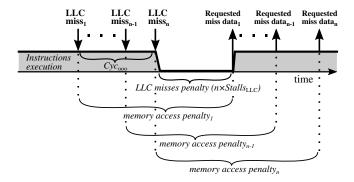

4.3.3 Overlapping LLC misses: Impact of memory level parallelism. Previously, in Section 4.3.1, specifically in Eq. 7, we considered the case of an isolated read LLC miss. This section now considers the general case, in which after an LLC miss occurs, and while the corresponding instruction is waiting for data from memory, the CPU pipeline generates one or more additional LLC misses. This situation is illustrated in Figure 6. Any stall cycles that occur should be counted once per group of overlapping LLC misses rather than once per LLC miss, which was the case for Eq. 7. The number of concurrent LLC misses is typically known as the memory level parallelism, and is denoted MLP [3, 13]. The penalty per LLC miss is therefore given by the number of stall cycles divided by MLP [3, 22]:<sup>4</sup>

$$Stalls_{LLC} = \frac{1}{MLP} \times (Pen_{\text{mem}} - Cyc_{\text{ooo}})$$

$$= \frac{1}{MLP} \times (Pen_{\text{mem}} - CPI_0 \times Ins_{\text{ooo}})$$

(12)

Karkhanis et al. [22] analyze this in detail and show that Eq. 12 is correct independently of the moment in which second, third, or subsequent LLC misses occur, as long as they occur within the  $Cyc_{000}$  interval. If MLP equals 1, then the above equation becomes identical to Eq. 7; so Eq. 12 covers both cases, that of isolated and overlapping LLC misses.

Current processors cannot directly measure MLP, so it must be estimated based on the parameters that are available. We derive lower and upper bounds on MLP and a point estimate.

The *MLP* lower and upper bounds can be computed starting from the equation  $CPI_{\text{tot}}^{(1)} = CPI_0 + CPI_{\text{LLC}}^{(1)}$ , then substituting  $CPI_{\text{LLC}}^{(1)}$  from Eq. 1 and  $Stalls_{\text{LLC}}^{(1)}$  from Eq. 12:

$$CPI_{\rm tot}^{(1)} = CPI_0 + \frac{Miss_{\rm LLC} \times \left(Pen_{\rm mem}^{(1)} - CPI_0 \times Ins_{\rm ooo}\right)}{Ins_{\rm tot} \times MLP} \tag{13}$$

Rearranging to isolate *MLP* and writing as a function to make clear which values are unknown gives:

$$MLP(Ins_{000}, CPI_0) = \frac{\frac{Miss_{LLC}}{Ins_{tot}} \times (Pen_{mem}^{(1)} - CPI_0 \times Ins_{000})}{CPI_{tot}^{(1)} - CPI_0}$$

(14)

This equation expresses MLP, which we want to know, in terms of  $Ins_{000}$ , the free variable that we will vary later, and  $CPI_0$ , which is unknown but can be bounded. The lower bound on  $CPI_0$  is  $CPI_{\min}$ , the reciprocal of the processor's highest theoretical IPC. The upper bound on  $CPI_0$  is  $CPI_{\text{tot}}^{(1)}$ , since  $CPI_0$  was defined to be one (of two) components contributing to  $CPI_{\text{tot}}^{(1)}$ . Now that  $CPI_0$  is bounded, and assuming a value of  $Ins_{000}$ , it is possible to use Eq. 14 to obtain the range of potential values of MLP, either via a sweep on  $CPI_0$  between its lower and upper bounds or using differential calculus.

A second upper bound on MLP is the size of the Miss Information Status Holding register (MSHR) [25]. The MSHR is the hardware structure that keeps information about in-flight cache misses, so they can be resolved once the corresponding data arrives. Its size is CPU-specific; e.g. it is 10 for Sandy Bridge [17] and 12 for KNL [21].

The *MLP* point estimate is derived by assuming that the application's behavior is uniform (in a sense to be clarified below) over the sampling segment. Specifically, we assume that the number of LLC misses per instruction is homogeneous across the time segment, in which case it must equal  $Miss_{\rm LLC}/Ins_{\rm tot}$ . In the period between the LLC miss and the arrival of its data, the processor executes  $Ins_{\rm 000}$  instructions, so with a constant rate of LLC misses, the total number of additional LLC misses is  $\frac{Miss_{\rm LLC}}{Ins_{\rm tot}} \times Ins_{\rm 000}$ . The value of  $Ins_{\rm 000}$  is a free parameter, as described in Section 4.3.2, so the value being calculated here is a function of that parameter. In order to account for the first LLC miss, which has not yet been counted, the point estimate for the total number of LLC misses, as a function of  $Ins_{\rm 000}$ , to which the stall cycles must be attributed, is:

$$\widehat{MLP}(Ins_{000}) = \frac{Miss_{LLC}}{Ins_{tot}} \times Ins_{000} + 1$$

(15)

Note that  $\widehat{MLP}(Ins_{000})$  is a point estimate for MLP based on the available information. If the point estimate is outside the valid range, between the lower and upper bounds described above, then it is corrected to lie in the range.

#### 4.4 Performance as a function of latency

This section completes the analysis of out-of-order processor performance as a function of latency. We start by repeating Eq. 4, which gives the predicted CPI in terms of *Stalls*<sub>LLC</sub>:

$$CPI_{\rm tot}^{(2)} = CPI_{\rm tot}^{(1)} + \frac{Miss_{\rm LLC}}{Ins_{\rm tot}} \times \left(Stalls_{\rm LLC}^{(2)} - Stalls_{\rm LLC}^{(1)}\right) \quad (4 \text{ again})$$

As remarked at the beginning of Section 4.3, in comparison with an in-order processor, an out-of-order processor has a more complex expression for  $Stalls_{LLC}$ , and this was given in Eq. 12:

$$Stalls_{LLC} = \frac{1}{MLP} \times (Pen_{mem} - CPI_0 \times Ins_{ooo})$$

(12 again)

Finally we replace the MLP parameter in this equation with the point estimate in Eq. 15:

$$\widehat{MLP}(Ins_{000}) = \frac{Miss_{LLC}}{Ins_{tot}} \times Ins_{000} + 1$$

(15 again)

<sup>&</sup>lt;sup>4</sup>LLC misses can also overlap with front-end miss events such as instruction cache miss, branch misprediction, etc. These overlaps, however, tend to be rare leading to an insignificant performance impact [9].

Memory access latency on the target memory system

Figure 7: Performance as a function of the memory access latency. The different curves arise by varying the unknown parameter  $Ins_{000}$  within its bounds. Please read the text before interpreting this figure.

In fact, as explained in Section 4.3.3, this value is restricted to lie between the lower and upper bounds given in that section. For the sake of clarity, we consider the more common case for which it is not necessary.

Combining Eq. 4, Eq.12 and Eq.15, and assuming that  $Ins_{tot}$ ,  $Miss_{LLC}$ ,  $CPI_0$ ,  $Ins_{ooo}$  and MLP do not change when moving from one memory system configuration to another, then  $CPI_{tot}^{(2)}$  can be calculated as:

$$CPI_{\text{tot}}^{(2)} = CPI_{\text{tot}}^{(1)} + \frac{Pen_{\text{mem}}^{(2)} - Pen_{\text{mem}}^{(1)}}{Ins_{\text{ooo}} + Ins_{\text{tot}}/Miss_{\text{LLC}}}$$

(16)

This equation is written in terms of the memory access penalty,  $Pen_{\rm mem}$ , but at the system level, outside a detailed analysis of a particular processor's pipeline, only  $Lat_{\rm mem}$  is relevant. Recall that  $Pen_{\rm mem}$  was defined to be the memory access latency,  $Lat_{\rm mem}$  minus the cost of an LLC hit. We note, therefore, that the expression  $Pen_{\rm mem}^{(1)} - Pen_{\rm mem}^{(1)}$  is equal to  $Lat_{\rm mem}^{(2)} - Lat_{\rm mem}^{(1)}$ . Taking account of this and rewriting in terms of the IPC instead of the CPI gives:

$$IPC_{\text{tot}}^{(2)} = \frac{IPC_{\text{tot}}^{(1)}}{1 + IPC_{\text{tot}}^{(1)} \times \frac{Lat_{\text{mem}}^{(2)} - Lat_{\text{mem}}^{(1)}}{Ins_{\text{ooo}} + Ins_{\text{tot}} / Miss_{\text{LLC}}}}$$

(17)

The various values in Eq. 17,  $IPC_{\text{tot}}^{(1)}$ ,  $Ins_{\text{tot}}$ , and  $Miss_{\text{LLC}}$  are known because they were measured on the baseline memory configuration. All other inputs to PROFET, such as  $Ins_{\text{ROB}}$ , MSHR,  $CPI_{\text{min}}$  (see Table 3) appear in the upper and lower bounds of  $Ins_{\text{ooo}}$ .

Eq. 17 is plotted in Figure 7. The x axis is the target system memory latency,  $Lat_{\rm mem}^{(2)}$ , and the y axis is the predicted IPC,  $IPC_{\rm tot}^{(2)}$ . Eq. 17 is a function of the independent parameter  $Ins_{\rm 000}$ , which we cannot measure or calculate exactly. We bounded its value in the previous section, and varying it between the lower and upper bounds gives the family of curves shown in the figure. Note that the case of  $Ins_{\rm 000}=0$  corresponds to an in-order processor. This can be seen by comparing Eq. 17 and Eq. 6. As indicated on the figure, when the target memory latency is the same as the baseline memory latency,  $Lat_{\rm mem}^{(1)}$ , PROFET correctly "predicts" the measured IPC to be that of the baseline system,  $IPC_{\rm tot}^{(1)}$ . It is easy to be misled by Figure 7. For instance, a decrease in

It is easy to be misled by Figure 7. For instance, a decrease in the memory latency by a fixed value, e.g. reducing the lead-off load penalty by 10 ns, is **not** equivalent to simply moving by 10 ns to

Figure 8: Graphical interpretation of a performance estimation as a merged solution of Sections 3 and 4.4.

the left on the *x* axis. This is because, as seen in the figure, such a change will result in an increase in the IPC, which will itself cause an *increase in the used memory bandwidth*, for reasons explained in the next section. This increase in used bandwidth will cause a movement to the right in the memory's bandwidth–latency curve and therefore *increase the memory system latency*, counterbalancing the original decrease in memory system latency. We address this problem in the next section.

# 4.5 Performance estimation — the ultimate step

This section completes the PROFET performance model. We start from the bandwidth–latency curves described in Section 3, which give the loaded memory access latency as a function of used memory bandwidth. We then combine these curves with the analysis in Section 4.4, which gives application performance as a function of the loaded memory latency. Doing so, in the right way, gives a prediction of the performance on the target memory system, with error bars.

The solution will be explained through Figure 8. The x axis is the used memory bandwidth and the y axis is the memory access latency. We show the measured bandwidth–latency curves for the Knights Landing platform, exactly as in Figure 4a. As before, the lightest curves correspond to 50% reads and 50% writes, and the darkest curves correspond to 100% reads. Now, however, since we are analysing a specific application segment, the proportion of reads is known (it is  $Ratio_{\rm R/W}$ ), so we know which curve from the family to select. The selected curve, which corresponds to  $Ratio_{\rm R/W}$ , is shown as a dashed white curve.

We now turn to Figure 7, and use the latency–performance plot to construct a latency–bandwidth plot, i.e. to find the used memory bandwidth as a function of the memory access latency. This is because the total number of memory accesses performed over the application's execution is a constant as argued in Section 4.2. The total number of accesses is evaluated, for the baseline memory system, by multiplying bandwidth by time, giving  $BW_{\rm used}^{(1)} \times (Cyc_{\rm tot}^{(1)}/Freq_{\rm CPU})$ . Dividing this expression by the execution time on the target memory system gives:

$<sup>^5 \</sup>rm Some$  of the input parameters appear only in the upper or lower bounds of MLP, which are not in Eq. 17 but considered in the full PROFET model.

$$BW_{\text{used}}^{(2)} = \frac{BW_{\text{used}}^{(1)} \times (Cyc_{\text{tot}}^{(1)}/Freq_{\text{CPU}})}{(Cyc_{\text{tot}}^{(2)}/Freq_{\text{CPU}})} = \frac{BW_{\text{used}}^{(1)}}{IPC_{\text{tot}}^{(1)}} \times IPC_{\text{tot}}^{(2)}$$

(18)

We therefore obtain a plot of bandwidth vs. latency simply by multiplying the value on the y axis of Figure 7 by the factor  $BW_{\rm used}^{(1)}/IPC_{\rm tot}^{(1)}$ . The axes now match those in Figure 8 except they are transposed. We therefore transpose the bandwidth vs. latency plot, by swapping the x and y axes, and superimpose it onto Figure 8. This gives the family of lines for the PROFET performance model.

When the application runs on a memory system, it must be located on the memory system's bandwidth–latency curve and on one of the PROFET performance model curves that was just added. It must therefore be located on the intersection of these curves, as indicated in Figure 8. For the baseline memory system, we find that all PROFET performance model curves intersect the bandwidth–latency curve in the same place, at the bandwidth measured on the real system.

Each pair of bandwidth—latency and PROFET performance model curves will intersect in exactly one place. There cannot be more than one intersection because the memory system's bandwidth—latency curve is increasing (as a function of latency) whereas the application's performance model curve is decreasing (as a function of latency). In addition, there must be an intersection point, since the application's curve decreases from a very high latency necessary to get a small used memory bandwidth whereas the memory's bandwidth—latency curve increases to a very high latency close to the maximum sustainable bandwidth.

In summary, we start from the target memory system's bandwidthlatency curve and Eq. 17, which defines a family of PROFET performance model curves. We perform a sweep of the valid range for Insooo, and for each value, find the intersection of its performance model curve with the target bandwidth-latency curve. To find this intersection we use the bisection method. This point gives a bandwidth on the y axis, which can be converted to an IPC by rearranging Eq. 18. Varying Insooo in this way gives the minimum, maximum and point estimate for IPC, from which the number of cycles and execution time can also be easily deduced. Recall that the discussion so far is related to a single segment (time interval) of the application. Summing over all segments gives the predicted minimum, maximum and point estimate execution time for the whole application. Execution of the complete PROFET prediction for the whole application is very fast. For example, for the benchmarks under study the performance estimate for each target memory system is completed within seconds.

# 4.6 Novelties of the presented analytical model

Since our PROFET analytical model is based on CPI stack analysis as widely used for performance modeling [14], it is important to emphasize the contributions of our work beyond the previous studies.

Computation of the CPI component that corresponds to the execution stalls due to the LLC misses (Eq. 1) is described by previous studies [3, 4, 14]. Hennessy and Patterson [14] and Karkhanis and Smith [22] also analyze execution of independent instructions  $Ins_{000}$  after the LLC miss (Eq. 7) and define some of the  $Ins_{000}$

bounds (Eq. 9). Finally, the MLP and its impact on CPI stack analysis (Eq. 12) are also well explored by the community [3, 4, 6, 10, 22].

CPI stack,  $Ins_{000}$  and MLP are the foundation of various analytical models that quantify the performance impact of the main memory latency [3, 6, 10, 22]. The previous analytical models, however, have one great challenge: they require detailed application profiling, which can be performed only with hardware simulators. The main objective of our work is to avoid the use of the simulators, and to develop an analytical model based only on the parameters that can be obtained or derived from performance counters measurements on actual platforms. This requires a novel approach to the MLP estimate, presented in Eq. 13–15. In addition to this, we also present additional  $Ins_{000}$  bounds in Eq. 10 and Eq. 11. Finally, to the best of our knowledge, this is the first study that combines analysis of application performance as a function of memory access latency (Sec 4.4) with bandwidth–latency curves (Sec 4.5) and that shows that its analysis leads to a unique solution.

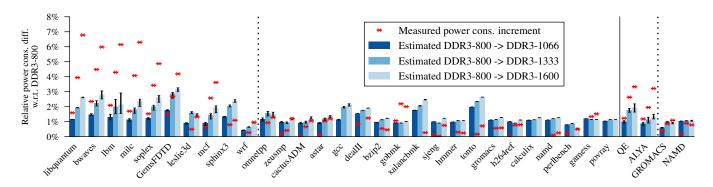

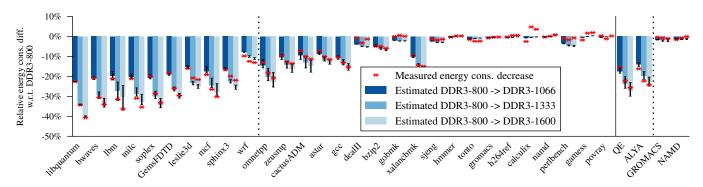

### 5 POWER AND ENERGY ESTIMATION

Similarly to performance estimation, we develop the PROFET power and energy models. Based on the application profiling and memory power parameters, these models predict the variation of the system power and energy consumption due to the change of the memory systems. PROFET's power and energy models are both validated on the Sandy Bridge E5-2670 server running SPEC2006 and scientific HPC applications.<sup>6</sup> As for the PROFET performance model, the error of the power and energy estimation is low: less than 2% for power and less than 3% for energy consumption. Due to the lack of space, the detailed description of the PROFET power and energy models is moved to Appendix A, while their evaluation is given in Appendix B.1.

#### 6 METHODOLOGY

In this section, we present the hardware platforms and benchmarks used in the evaluation of PROFET. We also list the tools used for the application profiling and server power measurements. Finally, we summarize the main steps of the PROFET evaluation process.

# 6.1 Hardware platforms

We evaluate PROFET on Sandy Bridge-EP E5-2670 and Knights Landing (KNL) Xeon Phi platforms. The most important features of the platforms are summarized in Table 4.

The Sandy Bridge-EP server is a representative of mainstream high-performance computing (HPC) servers, and it is still in use, especially in smaller Tier-0 systems [1]. In the server under study, we were able to test four memory frequencies: DDR3-800, DDR3-1066, DDR3-1333 and DDR3-1600, and we used these configurations to evaluate PROFET's performance, power and energy models.

The Intel Knights Landing (KNL) Xeon Phi platform [36] is an emerging platform that combines two types of memory with different memory bandwidths and access latencies: DDR4 DIMMs and 3D-stacked MCDRAM [36]. Since it uses two types of memories, the system offers three modes of operation: *cache* mode, *flat* mode and

<sup>&</sup>lt;sup>6</sup>The PROFET power and energy models were not developed for the KNL server, because we lacked reliable MCDRAM power parameters. This research is a part of ongoing work.

Table 4: The most important features of experimental platforms

| Platforms        | Sandy Bridge<br>E5-2670 | Knights Landing<br>Xeon Phi 7230 |

|------------------|-------------------------|----------------------------------|

| Sockets          | 2                       | 1                                |

| Cores per socket | 8                       | 64                               |

| CPU freq. [GHz]  | 3.0                     | 1.3                              |

| L1i, L1d         | 32 kB, 32 kB            | 32 kB, 32 kB                     |

| L2               | 512 kB                  | 1 MB                             |

| L3               | 20 MB                   | /                                |

| Memory conf.     | 4 chann.                | 8 chann. MCDRAM                  |

| per socket       | DDR3-800/1066/1333/1600 | 6 chann. DDR4-2400               |

| Memory capacity  | 64 GB                   | 16 GB MCDRAM<br>96 GB DDR4       |

hybrid mode. In our experiments, we use *flat* mode, in which the DDR4 and MCDRAM are configured as separate NUMA nodes, and we execute our workloads either in DDR4 or MCDRAM memory.

#### 6.2 Benchmarks

We evaluated PROFET on a set of SPEC CPU2006 benchmarks [37] and scientific HPC applications. The scientific applications are selected from the Unified European Application Benchmark Suite (UE-ABS) [30]. These applications are parallelized using Message Passing Interface (MPI) and are representative of production applications running on HPC systems in Europe. We choose four applications: ALYA, representative of the computational mechanics codes, and GROMACS, NAMD, and Quantum Espresso (QE) computational chemistry applications. The remaining UEABS applications could not be executed because their input dataset sizes exceed the main memory capacity of our hardware platforms.

In all the experiments on Sandy Bridge platform, we fully utilize the available 16 CPU cores (2 sockets, 8 cores each): we execute 16 copies of each SPEC CPU2006 benchmark, or 16 application processes for each UEABS applications. The KNL platform comprises 16 GB of the MCDRAM, which was insufficient to execute any of the UEABS application. Also, for each SPEC CPU2006 benchmark, we had to determine the maximum number of the instances whose cumulative memory footprint would fit into the MCDRAM. In the charts, this number of benchmark instances is specified in parentheses after the benchmark name.

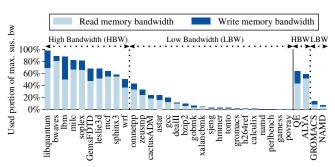

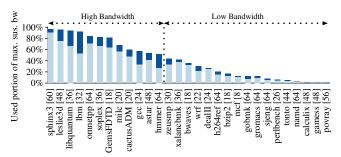

In order to quantify the level of stress that our workloads put on the memory system, we measure their memory bandwidth on the platforms under study. Figure 9 shows the bandwidth utilization, relative to the maximum sustained memory bandwidth measured with STREAM benchmark [27]. When reporting the evaluation of PROFET in Section 7, we emphasize the results for the high-bandwidth benchmarks with over 50% of the used memory bandwidth. These benchmarks are the most affected by the changes in the memory system, and therefore the most challenging to model.

#### 6.3 Tools and methodology

Application profiling requires measurements of the CPU cycles, instructions, LLC misses, read and write memory bandwidths, as well as the row-buffer access statistics, number of page activations and

(a) Sandy Bridge E5-2670. Fully utilized server: 16 SPEC CPU2006 instances or 16 UEABS MPI processes.

(b) Knights Landing Xeon Phi. The MCDRAM capacity limits the number of the benchmarks instances, specified in the square brackets

Figure 9: The workloads under study show a wide range of memory bandwidth utilization, and different ratios of the Read and Write memory traffic.

page misses, and number of cycles spent in memory power-down states. All these inputs are measured by the hardware counters and the LIKWID performance tool suite [39]. The counters used in the study are widely available in mainstream HPC servers [16, 18].

We used a Yokogawa WT230 [5] power meter to measure the server power consumption. The power meter measures the voltage and current at the power plug to calculate the power consumption of the whole server, including power supply, motherboard with all its components, CPUs, and memory. The measurements were sampled on one second time period. The energy consumption was calculated by summing the power consumption over the execution time

# 7 EVALUATION

Evaluation of PROFET is done in four steps. First, we execute a benchmark on the *baseline memory system*, e.g., Sandy Bridge server with DDR3-800. In this run, we measure the benchmark performance, power and energy consumption, and collect all the hardware counters needed for prediction using PROFET. Second, we use PROFET to *estimate* the benchmark performance, power and energy on the *target memory configuration*, e.g., DDR3-1600. Third, we change the platform memory configuration from the baseline to the target memory, e.g., from DDR3-800 to DDR3-1600. This requires changing the BIOS settings for the Sandy Bridge, and changing the execution NUMA node for the Knights Landing platform. Finally,

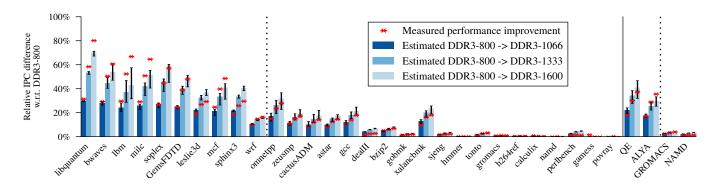

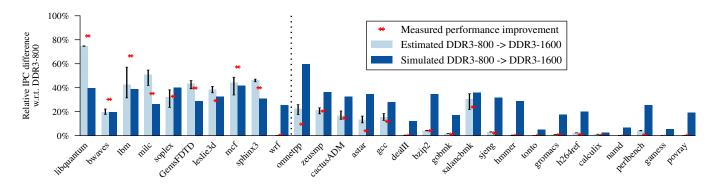

Figure 10: Sandy Bridge, DDR3-800  $\rightarrow$  1066/1333/1600: Changing the DRAM frequency has a significant performance impact. PROFET's performance model estimations are precise, with low error bars, and accurate, with small difference from the values measured on the actual hardware.

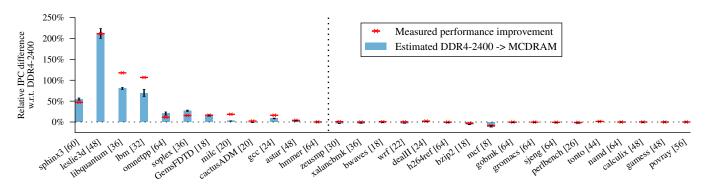

Figure 11: Knights Landing, DDR4-2400  $\rightarrow$  MCDRAM: Despite the wide range of the performance variation, between -9% (mcf) and 212% (leslie3d), the model shows high accuracy. Smaller KNL reorder buffer leads to a smaller range of the  $Ins_{000}$  sensitivity analysis, and therefore more precise performance prediction, i.e., smaller error bars.

we *execute* the benchmark on the *target memory system*, measure the *actual* performance, power and energy consumption, and compare them with the values estimated by PROFET.

#### 7.1 Sandy Bridge: DDR3-800 $\rightarrow$ 1066/1333/1600

The results for the Sandy Bridge server are displayed in Figure 10. For each benchmark we plot three sets of bars, one per DRAM frequency change: DDR3-800 $\rightarrow$ 1066/1333/1600. As described in Section 4.3, since we could not determine the exact value of the  $Ins_{000}$  parameter in the experimental platform, we performed a sensitivity analysis by varying  $Ins_{000}$  between 0 and  $Ins_{000}^{max}$ , and doing the performance estimate for each possible value. The solid bars correspond to the mean performance estimate, while the error bars show the lowest and highest estimated performance. In addition, we plot the actual performance improvement measured on the real platform, marked with a (red) cross marker for each experiment.

First, we can see that the error bars, i.e., ranges of the estimated performance are narrow. Across the high-bandwidth benchmarks, the average width of the error bars is only 2.6%, 5.5% and 7.4%, for DDR3-1066/1333/1600 respectively. Across the low-bandwidth benchmarks, the average width of the error bars is even lower, at 1.1%, 1.6% and 2%. This means that, although for the architectures

under study we cannot determine the precise value of the Ins<sub>000</sub> parameter, we can, in all cases, apply a sensitivity analysis and obtain a narrow range of estimated performance. As expected, the highbandwidth benchmarks, which are more sensitive to the CPU's ability to hide memory latencies through memory parallelism, have a greater sensitivity to Insooo, leading to wider, but still acceptable, error bars. Second, PROFET's predictions are highly accurate. The average difference from the performance measured on the actual hardware for DDR3-1066/1333/1600 frequencies is 1.8%, 3.8% and 5.1% for the high-bandwidth benchmarks, and it drops to just 1%, 1.3% and 1.6% over the low-bandwidth benchmarks. Finally, the presented results show that the DRAM frequency increase indeed has a significant performance impact. For example, increasing the DRAM frequency from the baseline DDR3-800 to the target DDR3-1600 causes average performance improvement of 22%, and it reaches 80% for the libquantum benchmark. Therefore it is important to understand the relation between the available memory bandwidth and the overall application performance, which is the main objective of our work.

# 7.2 Knights Landing: DDR4-2400 → MCDRAM

Figure 11 shows the estimated and measured performance improvement of the Knights Landing Xeon Phi with high-bandwidth

MCDRAM with respect to the DDR4-2400 memory. Again, PROFET shows high precision. Actually, the width of the estimation error bars is only 3.2% for high-bandwidth benchmarks and 0.4% for lowbandwidth benchmarks, both of which are significantly smaller than the corresponding figures for the Sandy Bridge system. The main reason for this is the 72-instruction reorder buffer in the KNL platform, w.r.t. the 168 instructions in the Sandy Bridge. A smaller reorder buffer leads to a narrower range for the Insooo sensitivity analysis, and therefore a more precise performance prediction. In the case of low-bandwidth benchmarks, additional reason for small error bars is that their overall performance sensitivity on the change from the baseline to the target memory system is low. Therefore, PROFET also predicts low performance difference with close values for minimum and maximum of the Insooo sensitivity analysis. In their case, Insooo parameter from Eq. 17 has negligible impact on the estimation result, either because of the close values of  $Lat_{mem}^{(2)}$ and  $Lat_{\text{mem}}^{(1)}$  or because of the low number of LLC misses in Eq. 17.

The MCDRAM provides 4.2-fold higher bandwidth over DDR4, which leads to significant performance improvement for the high-bandwidth benchmarks, up to 212% improvement for the *leslie3d*. However, the MCDRAM also has a 23 ns higher lead-off latency (see Figure 4a), that penalizes benchmarks with low and moderate memory bandwidth requirements. Actually, for *bzip* and *mcf*, execution on the MCDRAM leads to performance loss. For the *mcf* benchmark, this performance loss reaches a non-negligible 9%.

Despite the wide range of the performance variation, between -9% and 212%, when moving from DDR4 to the MCDRAM, PROFET shows high accuracy. The difference between PROFET's performance estimates and the measurements on the actual hardware is 7% for high-bandwidth benchmarks, and drops down to 1.6% for the low-bandwidth benchmarks. Also, PROFET's predictions accurately distinguish between the benchmarks that significantly benefit from the MCDRAM, and the benchmarks that show negligible performance improvements or even performance loss. This confirms that PROFET properly considers both segments of the memory bandwidth—latency curves: the constant latency segment, close to the lead-off memory latency, and the exponential segment, close to the memory bandwidth saturation point.

# 7.3 Additional evaluations

Section 7.1 summarizes the evaluation of the **performance model** on the Sandy Bridge when increasing the DRAM frequency from DDR3-800 to DDR3-1066/1333/1600. Appendix B.1 extends these results with the evaluation of the **power and energy model** on the same platform and DRAM configurations. PROFET's power and energy estimates are evaluated versus measurements of an external power meter taken on the actual Sandy Bridge server. As remarked above, PROFET's power and energy models were not developed for the KNL server, because we lacked the reliable MCDRAM power parameters. As a part of the ongoing work, we are exploring different ways to estimate these parameters.

The evaluation results show that PROFET's predictions are **highly-accurate**, typically with only 2% difference from the performance, power and energy consumption measurements on the actual hardware. PROFET provides accurate estimations even when the baseline and target memory systems have **fundamentally different**

**bandwidth–latency curves**, with different lead-off latency and with an *n*-fold difference in the available bandwidth.

In Appendix B.2, we compare the performance estimates of PRO-FET with ZSim+DRAMSim2 hardware simulators. The comparison is done based on the actual measurements on the Sandy Bridge platform. The presented results show that PROFET has much better accuracy than the simulators. Also, PROFET's estimations closely follow the trend of the actual measurements, while the simulated results show completely different trends. Appendix B.2 also summarizes additional advantages of PROFET. PROFET is faster than the hardware simulators by three orders of magnitude, so it can be used to analyze production HPC applications, arbitrarily sized systems, and numerous design options, within a practical length of time. Also, PROFET does not require detailed CPU modeling since the CPU functionality, including actual data prefetcher and out-oforder engine, is already accounted for by the application profiling. Finally, PROFET can be used on various platforms as long as they support the required application profiling. PROFET was initially developed for the Sandy Bridge platform, and later we evaluated it for the KNL server. Adjustment of PROFET to the KNL system was trivial, requiring changes to only a few hardware parameters.

# 8 RELATED WORK

**CPU** and memory analytical models: Numerous studies propose analytical models as an alternative to cycle-accurate hardware simulation. We summarize the ones that are directly related to our work.

Karkhanis and Smith [22] present an OOO processor model that estimates the performance impact of instruction window size, branch misprediction, instruction cache misses and data cache misses. The model is validated versus detailed superscalar OOO CPU simulation and the authors conclude that, although the model provides much less data than detailed simulation, it still provides insights on what is going on inside the processor. Published in 2004, this work became the foundation for numerous advanced processor modeling approaches. Eyerman et al. [10] extend the work of Karkhanis and Smith [22] and develop the mechanistic model and interval analysis. The interval analysis breaks the total execution time into intervals based on the miss events, branch mispredictions and TLB/cache misses, and then predicts the execution time of each interval. Genbrugge et al. [12] propose interval simulation which accelerates multi-core simulation via a combination of the highlevel mechanistic analytical model [10] and detailed simulation. The mechanic analytical model is used to estimate the core-level performance between two miss events, while the miss events are determined through the simulation of branch predictor and the entire memory hierarchy: private per-core caches and TLBs, shared caches, cache coherence, network on chip, memory controller, and main memory. Finally, Van den Steen et al. [6] present various enhancements of the interval model [10]. First, the study incorporates architecture-independent application profiling, so the application can be profiled once and then simulated on any given platform. The authors also demonstrate that the analytical model can be connected to the McPAT power tool [26] for estimation of the processor power and energy consumption. Finally, the authors make first steps in memory system modeling by considering congestion

on the memory bus. Unlike our study, however, they do not take into account contention in the memory controller and memory device itself, which are more challenging.

The greatest challenge of the presented modeling approaches is that, although they do not require simulation to carry out the performance prediction, they do require detailed application profiling, which can be performed only with hardware simulators. Even with recent advances in hardware performance counters, we are still far away from being able to read values such as, for example, the number of cold, capacity and conflict cache miss. Since these methods require simulation results, even for application profiling, a significant effort is required to set up and tune for a target architecture, a serious amount of simulation time, and potentially high simulation errors. Our approach avoids these issues by using only those parameters that can be read using performance counters on real hardware. This is the greatest advantage of our work compared with previously-mentioned studies. Limiting the application profiling to the performance counters available on real hardware requires a novel approach to infer various application parameters, such as the MLP or number of executed OOO instructions. Therefore, although we start with the same foundation as the previous studies, as detailed in Section 4.6, estimation of the important application parameters and the overall performance calculation are fundamentally different from previously-presented models.

The second important difference of our work compared with the previous studies is the treatment of the main memory access latency. The previous studies use the memory access latency obtained from a detailed simulation of the whole memory hierarchy [12] or simply use a constant latency [6, 10, 22]. Our study performs a detailed analysis of memory bandwidth–latency curves and uses these curves as an intrinsic part of the overall performance estimation, as detailed in Section 4.5.

Third, unlike previous studies, PROFET encompasses data prefetching. This is an important difference because prefetching may have significant impact on the application performance, behavior and memory bandwidth usage.

Fourth, we complement the PROFET performance model with power and energy consumption estimates, and evaluate all three PROFET models against fully-utilized actual HPC servers with multi-threaded or multi-programmed benchmark execution. The previous models are validated versus the same simulators used for the application profiling. This means that the previous evaluations overlook potentially high errors of application profiling on a simulation versus the actual hardware. Finally, most of the previous studies [6, 10, 22] build and validate the models for single-core processors.

Workload characterization and memory DVFS: The performance impact of memory bandwidth and latency is frequently estimated by workload characterization studies and memory DVFS proposals. Memory models that could quantify this impact are missing, or not publicly available, so some studies develop their own models [4, 7]. These models are developed for very specific tasks in the context of the larger studies and they successfully fulfil their objectives. Still it is questionable whether they can be applied generally because of two main limitations. First, the modeled CPU and memory systems are much simpler than state-of-the-art production

platforms. Second, the models are not validated versus any real hardware or hardware simulators, so it is difficult to quantify the errors they may introduce. Even so, we consider these studies as very valuable for any follow-up on this topic because they analyze different approaches for main memory modeling and share their experiences.

#### 9 CONCLUSIONS

This study presents PROFET, an analytical model that quantifies the impact of the main memory on application performance and system power and energy consumption. PROFET is based on memory system profiling and instrumentation of an application execution on a real platform with a baseline memory system. By running on the real platform, PROFET handles many aspects (e.g. prefetcher and out-of-order engine) that are oversimplified in state-of-the-art methods. The outputs from PROFET are the predicted performance, power and energy consumption on the target memory.

PROFET is evaluated on two actual platforms: Sandy Bridge-EP E5-2670 and Knights Landing Xeon Phi platforms with various memory configurations. The evaluation results show that PROFET's predictions are very accurate — the average difference from the performance, power and energy measured on the actual hardware is typically only about 2%. We also compare PROFET's performance predictions with simulation results for the Sandy Bridge-EP E5-2670 system with ZSim and DRAMSim2 simulators. PROFET shows significantly better accuracy while being three orders of magnitude faster than the hardware simulators. We release PROFET's source code and all input data required for memory system and application profiling [31]. The released model is ready to be used on high-end Intel platforms, and we would encourage the community to use it, adapt it to other platforms, and share their own evaluations.

#### **ACKNOWLEDGMENTS**

This work was supported by the Spanish Ministry of Science and Technology (project TIN2015-65316-P), Generalitat de Catalunya (contracts 2014-SGR-1051 and 2014-SGR-1272), Severo Ochoa Programme (SEV-2015-0493) of the Spanish Government; and the European Union's Horizon 2020 research and innovation programme under ExaNoDe project (grant agreement No 671578) and EuroEXA project (grant agreement No 754337); the U.S. Department of Defense under Contract FA8075-14-D-0002-0007, TAT 15-1158; and the U.S. National Science Foundation under Award 1642424.

#### A POWER AND ENERGY MODELING

In this appendix, we give the detailed description of the PROFET power and energy models.

# A.1 Power modeling

Apart from performance, power and energy demand are important system constraints. In modern HPC systems, the memory subsystem contributes 10–16% of the total server power consumption [11]. It is therefore valuable to quantify the trade-offs in power and energy consumption due to the change of the memory system.

As mentioned in Section 5, we analyse the difference in total system power consumption when we move from baseline to target memory system. In our study, we assume that when the memory system changes, the biggest impact on total system power consumption is the change of the main memory power consumption. Hence, we focus on modeling the power consumption of the memory subsystem and consider that power consumption of the rest of the system does not change [7]. Estimating power and energy consumption requires measurements of the total platform power consumption, ratio of time spent in memory power-down states (active standby, precharge power-down and self-refresh states in our system) and row-buffer access statistics (rate of page hits and page misses). Table 5 summarizes the symbols used in the formulas for power and energy estimation.

Table 5: Notation used in formulas: Power modeling

| Description                                      | Symbol                         |  |

|--------------------------------------------------|--------------------------------|--|

| Input parameters                                 |                                |  |

| Total platform power consumption                 | $P_{tot}$                      |  |

| Percentage of time spent in active standby state | $t_{ m act}$                   |  |

| Percentage of time spent                         | 4 .                            |  |

| in precharge power-down state                    | $t_{ m ppd}$                   |  |

| Percentage of time spent in self-refresh state   | $t_{ m sr}$                    |  |

| Percentage of row-buffer hits                    | $p_{ m hit}$                   |  |

| Percentage of row-buffer misses                  | $p_{ m miss}$                  |  |

| Used memory bandwidth for read/write traffic     | $BW_{\text{used}}^{rd/wr,(1)}$ |  |

| Intermediate outputs                             | useu                           |  |

| Total memory power                               | $P_{ m mem}$                   |  |

| Power consumption of the rest of the system,     | D                              |  |

| apart from the memory                            | $P_{ m rest}$                  |  |

| Operational memory power                         | $P_{ m op}$                    |  |

| Background memory power                          | $P_{ m bg}$                    |  |

| Memory power in active standby state             | $P_{ m act}$                   |  |

| Memory power in precharge power-down state       | $P_{ m ppd}$                   |  |

| Memory power in self-refresh state               | $P_{\rm sr}$                   |  |

| Total memory read/write operations power         | $P_{ m rd/wr}$                 |  |

| Power of memory refresh operations               | $P_{ m ref}$                   |  |

| Duration of sampling segment                     | $T_{ m sample}$                |  |

| Number of read/write memory accesses             | $N_{ m access}^{rd/wr}$        |  |

| on a sampling segment                            | access                         |  |

| Energy on termination resistors                  | $E_{\mathrm{term}}^{rd/wr}$    |  |

| for a single read/write memory access            |                                |  |

| Single memory read/write access energy           | $E_{ m access}^{rd/wr}$        |  |

| Energy of a read/write row buffer miss access    | $E_{\rm miss}^{rd/wr}$         |  |

| Energy of a read/write row buffer hit access     | $E_{\rm bit}^{rd/wr}$          |  |

To calculate the components of memory power consumption, we use Micron's guide for calculating power consumption of DDR3 memory systems [28]. Apart from the parameters in Table 5, Micron's power consumption guide requires *IDD* currents, memory system voltage and DIMM timing parameters, which are detailed in DIMMs documentation [29]. The PROFET power model was not developed for the KNL server, because we lacked of the reliable MCDRAM power parameters. The estimation of these power parameters is part of ongoing work.

Micron's power consumption guide defines how to calculate power consumption of individual read or write memory accesses and DRAM power-down states. In our power analysis, we begin from total platform power consumption and expand its components down to these basic DRAM operations. We start by dividing the total platform power consumption into two components, power of the memory system and power of the rest of the platform apart from the memory [7]:  $P_{\text{tot}} = P_{\text{mem}} + P_{\text{rest}}$ . As in the analysis of the performance in Section 4, we use the superscripts (1) and (2) to distinguish between the  $P_{\text{tot}}$  and its components in the baseline and target memory systems, respectively:

Baseline memory:

$$P_{\text{tot}}^{(1)} = P_{\text{mem}}^{(1)} + P_{\text{rest}}^{(1)}$$

Target memory:  $P_{\text{tot}}^{(2)} = P_{\text{mem}}^{(2)} + P_{\text{rest}}^{(2)}$  (19)

Since we assume that the power of the rest of the system stays the same, we can write  $P_{\rm rest}^{(2)} = P_{\rm rest}^{(1)}$ . 8 Therefore, total platform power consumption in the target memory system can be expressed as:

$$P_{\text{tot}}^{(2)} = P_{\text{tot}}^{(1)} + (P_{\text{mem}}^{(2)} - P_{\text{mem}}^{(1)}) \tag{20}$$

In further analysis we focus on the  $P_{\rm mem}$ . It comprises two components, background power  $P_{\rm bg}$  and operational power  $P_{\rm op}$ :

$$P_{\text{mem}} = P_{\text{bg}} + P_{\text{op}} \tag{21}$$