## Fault Tolerant Multilevel Inverter Topologies with Energy Balancing Capability: Photovoltaic Application

Madhukar Rao A

A Dissertation Submitted to Indian Institute of Technology Hyderabad In Partial Fulfillment of the Requirements for The Degree of Doctor of Philosophy

भारतीय प्रौद्योगिकी संस्थान हैदराबाद Indian Institute of Technology Hyderabad

Department of Electrical Engineering

June, 2017

## Declaration

I declare that this written submission represents my ideas in my own words, and where others' ideas or words have been included, I have adequately cited and referenced the original sources. I also declare that I have adhered to all principles of academic honesty and integrity and have not misrepresented or fabricated or falsified any idea/data/fact/source in my submission. I understand that any violation of the above will be a cause for disciplinary action by the Institute and can also evoke penal action from the sources that have thus not been properly cited, or from whom proper permission has not been taken when needed.

(Madhukar Rao A)

(EE12P1001)

## **Approval Sheet**

This thesis entitled "Fault Tolerant Multilevel Inverter Topologies with Energy Balancing Capability: Photovoltaic Application" by Madhukar Rao A is approved for the degree of Doctor of Philosophy from IIT Hyderabad.

Professor Kishore Chatterjee Department of Electrical Engineering, Indian Institute of Technology Bombay, Powai

Professor L Umanand Department of Electronic Systems Engineering Indian Institute of Science, Bangalore

Bland

Dr. Ravikumar Bhimasingu

Department of Electrical Engineering Indian Institute of Technology Hyderabad (Internal Examiner)

Dr. Sivakumar K

Department of Electrical Engineering Indian Institute of Technology Hyderabad (Adviser/Guide)

Neut 2

Dr. Venku Naidu Dogga Department of Mathematics Indian Institute of Technology Hyderabad (Chairman)

### Acknowledgements

My deepest thankfulness goes to my supervisor, Dr. K.Siva kumar for his guidance, encouragement and continuous support throughout my Ph.D. work. I will always remember his great human nature, enthusiastic approach and dedication to research during this important time. During my PhD program besides being my academic supervisor, he was a great friend, an insightful mentor, and an encouraging person. I am sure that the rigorous research attitude I learned from him will benefit in every aspect of my life. I do consider myself privileged to have the opportunity to work with him.

I am grateful to my doctoral committee member (Dr. Vaskar Sarkar, Dr. Ravikumar B, Dr. J Suryanarayana) for their precious suggestion and technical discussions during annual reviews.

I am highly grateful to Prof. Gopakumar K, DESE, IISC Bangalore and Prof. V.T. Somasekhar, Department of Electrical Engineering, NIT Warangal for their valuable suggestion during his visit to our Lab.

I am grateful to the faculty and support staff at IIT Hyderabad for helping and assisting me in many different ways.

It has been a great pleasure to work with so many talented, creative, helpful Colleagues like Dr. Kiran Kumar N, Dr. Umesh B S, Manoranjan Sahoo, Naga Yatendra Babu, Prathap Reddy B, Mehar Kalyan, Parth Sarathi, Dr.Manjunath K, Naga Sekhar, SSR Sarath Babu, Kranthi Kumar, Subash, Charan Tej, Kishore and Pavan Kumar, Nalla Reddy, Anil kumar, Nagaraj, Balajose, Chandra shekar Palla, Sriram Vyshya,Vishnu and Amal Sebastian.

Especially I want to express my special thanks to Dr. Kiran kumar N, Dr. Umesh B S, Mr. Manoranjan Sahoo, Prathap Reddy, and Naga Yatendra, Parth Sarathi for their whole hearted help, support during technical discussions, experimental work and thesis writing.

With bowed head I want to convey my reverences to my parent's Shri. Malhal Rao, Smt. Bhagyamma and Grandparents Late Shri. Chander Rao, Smt. Chilakamma at this cherished moment of my life. I owe them for their unconditional love, care and blessings. Whatever I am today is all because of you.

With lots of love I would like to thank my wife Swapna for her unconditional love, constant support and encouragement in accomplishment of this dream.

I am also very much thankful to my brothers Vishnu Vardhan, Jithendar, Sravan, Sandeep, Navaneeth and Rakesh and whole Airineni family without their support I would not have been able to undertake this task.

I am also thankful to my sister Kavitha, my brother-in-law Santhosh and their daughter Sahasrika for their love and support.

I am also very much thankful my sister in-law Sandhya Rani and brother Raj Kumar for their love and support.

I would also like to thank Dr. Rajagopal, Tirupati, Nagarjun Reddy P, Uday and Rajendra Naik for their encouragement towards research.

I thank the Government of India and all the honest taxpayers of India for the financial support provided to me.

Finally, I would like to express my thanks to all those who helped me directly or indirectly in the progress and completion of this work.

Madhukar Rao A

Dedicated to My Parents....

### Abstract

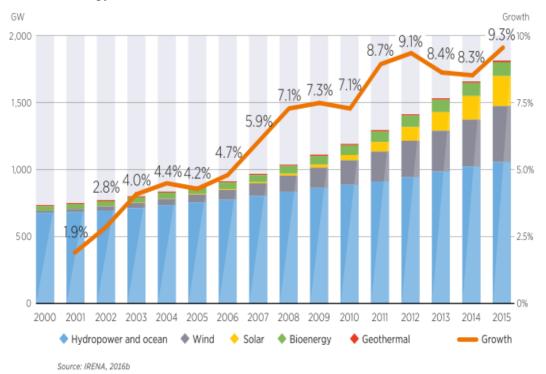

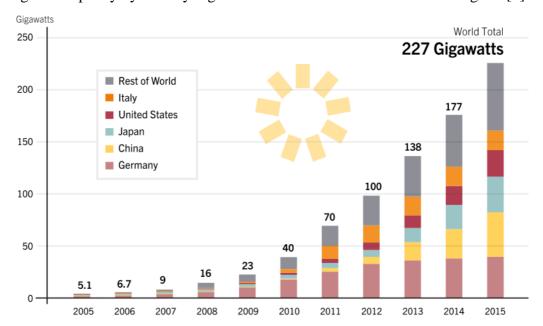

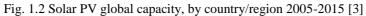

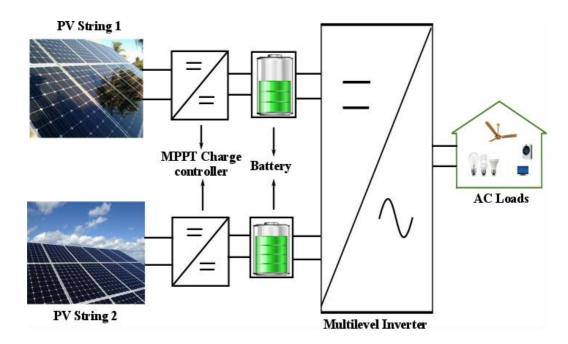

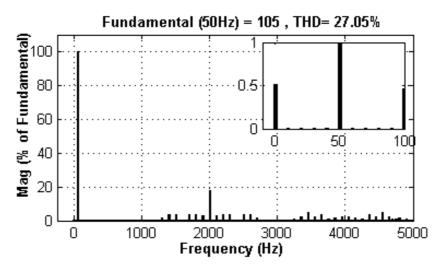

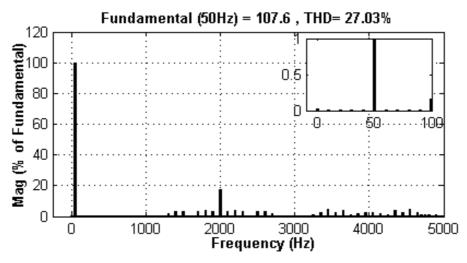

The continuous increase in energy demand and depletion of conventional resources motivates the research towards the environment friendly renewable energy sources like solar and wind energy. These sources are best suitable for rural, urban and offshore locations, because of easy installation, less running cost and ample resources (sun light and wind). The remote locations are mostly islanded in nature and far away from technical expertise in case of troubleshooting. This motivates the research on development of fault tolerant converters. These fault tolerant converters increases the reliability, which provides the continuous power supply to critical loads. From the last few decades, the integration of multilevel inverters with renewable energy systems is also increasing because of advantages like, improved power quality, total harmonic distortion (THD) and reduced output filter size requirement. Employing conventional multilevel inverters for increasing the number of voltage levels increases the device count and isolated DC sources. As a result probability of semiconductor switch failure is more and energy balancing issue between sources, which in-turn degrades the reliability and performance of the inverter. The majority of conventional multilevel inverter topologies cannot address energy balancing issues between multiple photovoltaic (PV) sources, which may need because of partial shading, hotspots, uneven charging and discharging of associated batteries etc. If energy sharing not addressed effectively, the batteries which are connected to the shaded or faulty PV system will discharge faster which may cause total system shutdown and leads to under-utilization of healthier part of the system. To address these issues, fault tolerant multilevel inverter topologies with energy balancing capability are presented in this thesis.

The major contributions of the proposed work are

• Single phase and three phase fault tolerant multilevel inverter topologies.

- Energy balancing between sources and dc off set minimization (or batteries) due to uneven charging and discharging of batteries for five-level inverter.

- Extending the fault tolerance and energy balancing for higher number of voltage levels.

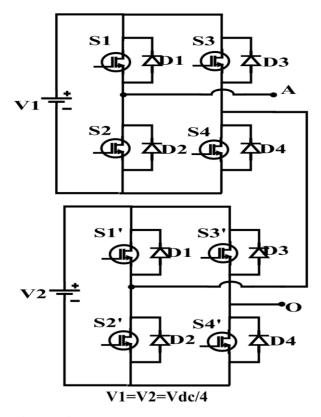

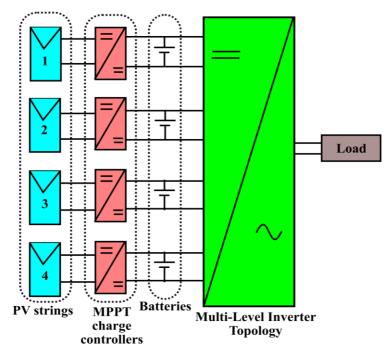

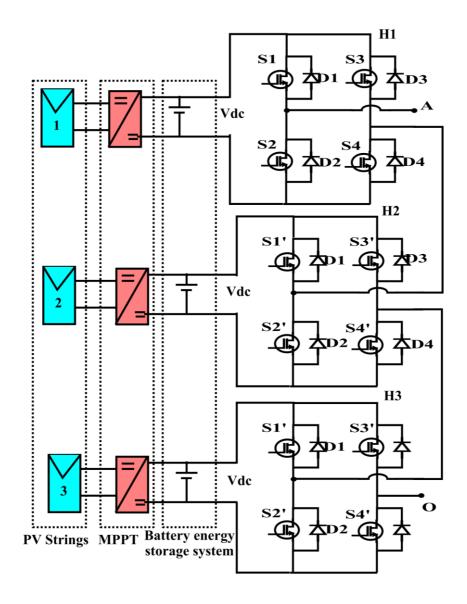

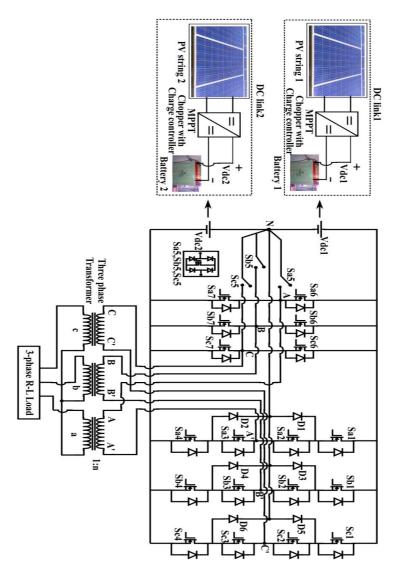

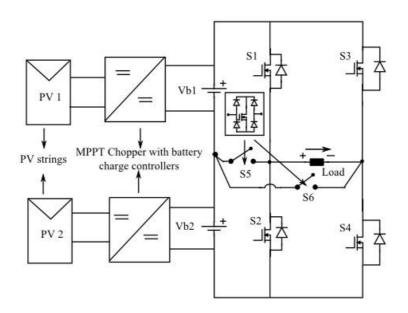

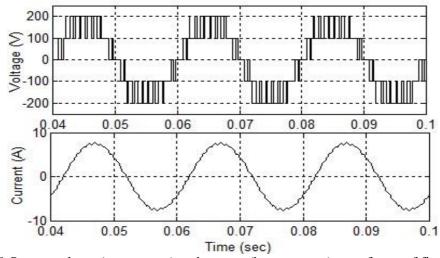

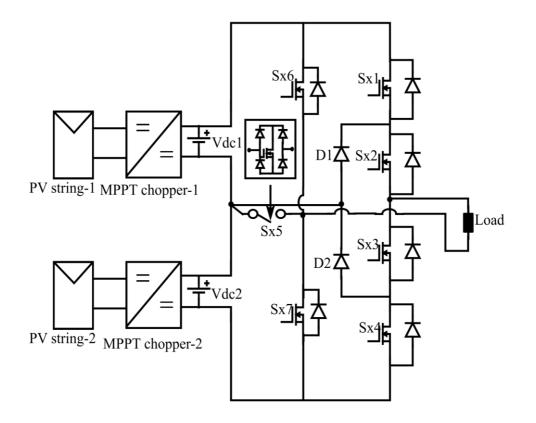

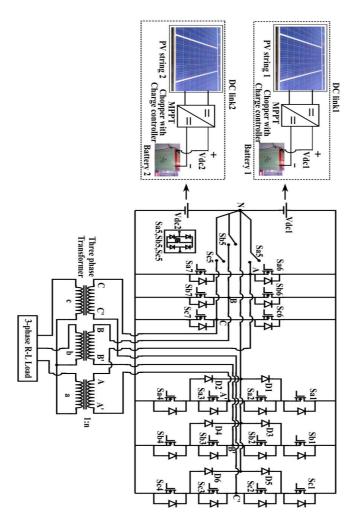

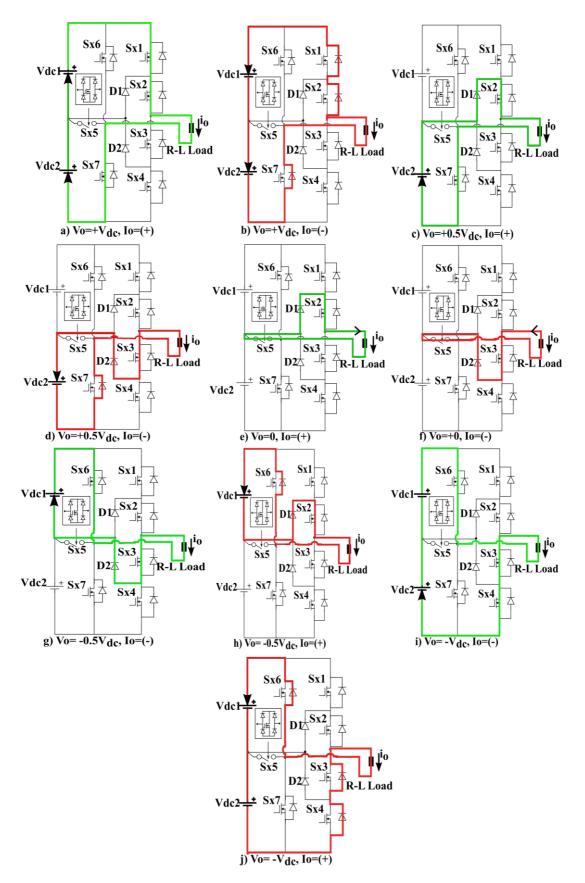

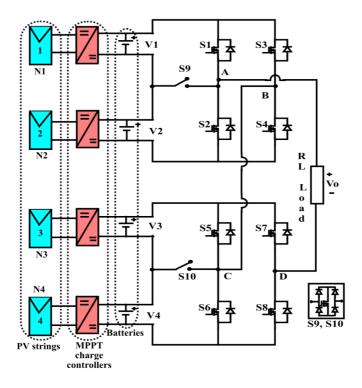

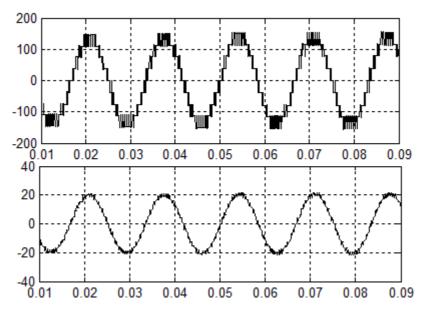

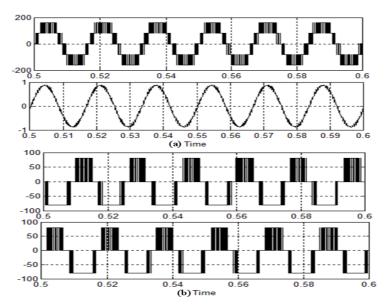

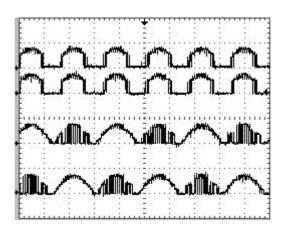

The first work of this thesis is focused to develop fault tolerant single phase and three phase multilevel inverter topologies for grid independent photovoltaic systems. The topologies are formed by using three-level and two-level half bridge inverters. The topology fed with multiple voltage sources formed by separate PV strings with MPPT charge controllers and associated batteries. Here the topologies are analyzed for different switch open circuit and/or source failures. The switching redundancy of the proposed inverters is utilized during fault condition for supplying power with lower voltage level so that critical loads are not affected.

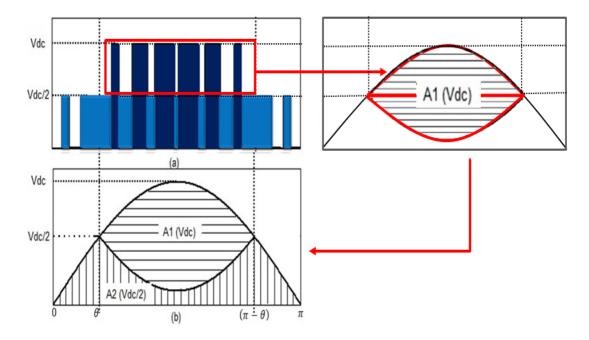

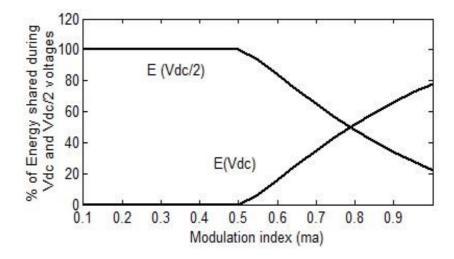

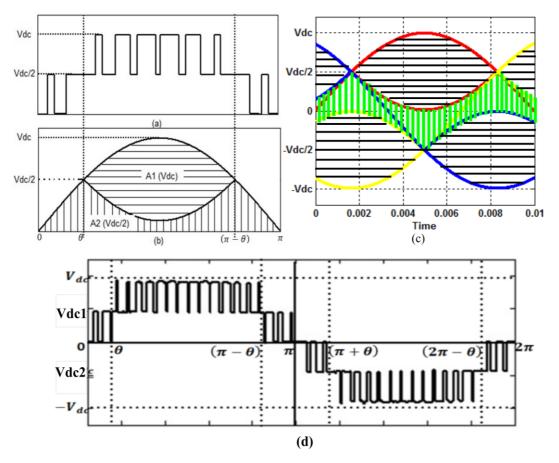

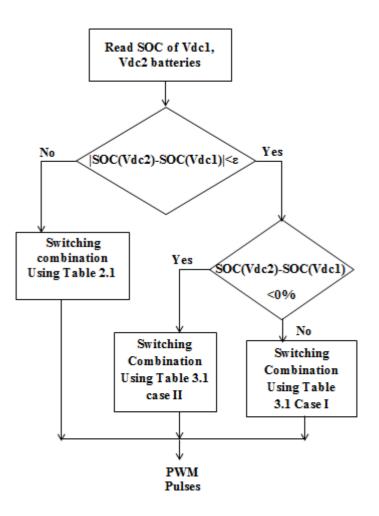

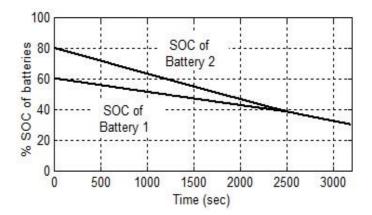

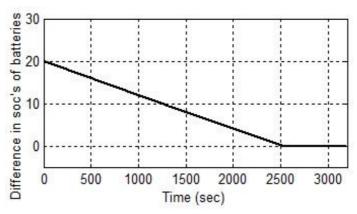

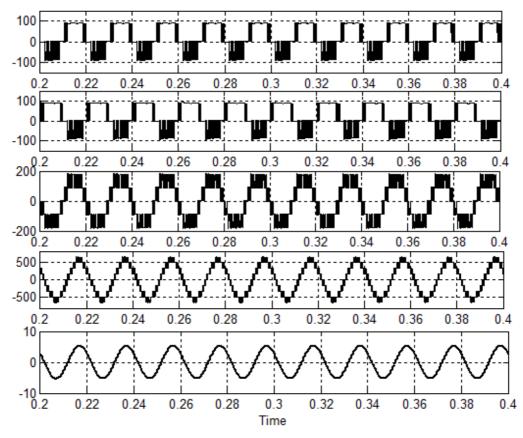

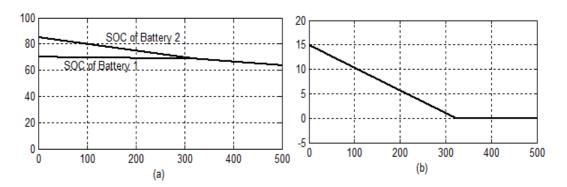

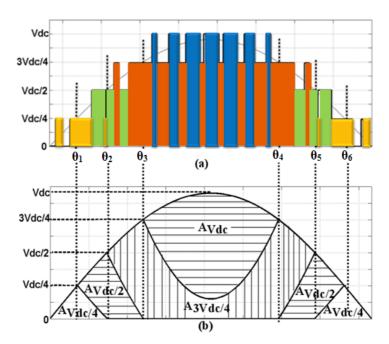

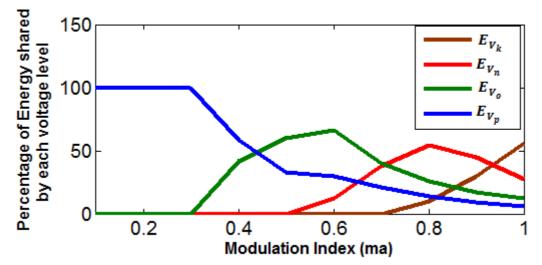

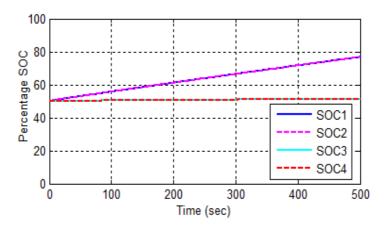

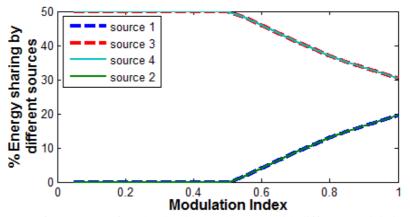

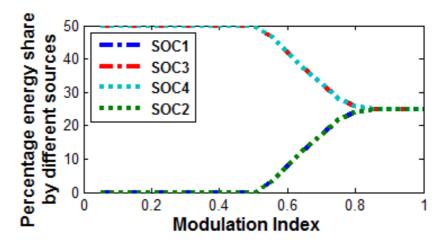

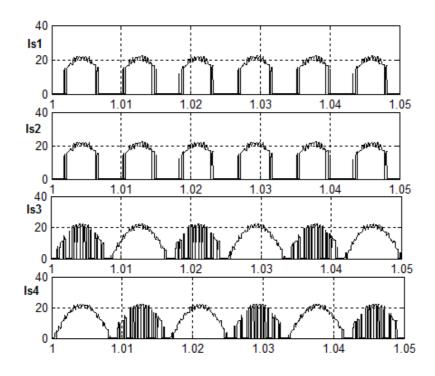

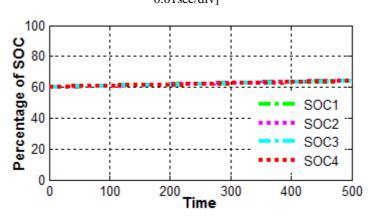

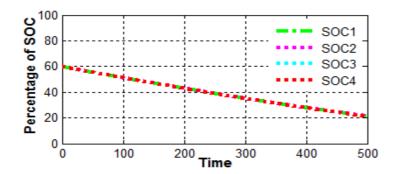

In general, the power generation in the individual PV systems may not be same at all the times, because of partial shading, local hotspots, wrong maximum power point tracking, dirt accumulation, aging etc. To address this issue energy balancing between individual sources is taken care with the help of redundant switching combinations of proposed five-level inverter carried out in second work. Because of partial shading the associated batteries with these panels will charge and discharge unevenly, which results voltage difference between terminal voltages of sources because of SOC difference. The energy balance between batteries is achieved for all operating conditions by selecting appropriate switching combination. For example during partial shading the associated battery with low SOC is discharged at slower rate than the battery with more SOC until both SOC's are equal. This also helps in minimization of DC offset into the ac side output voltage. The mathematical analysis is presented for possible percentage of energy shared to load by both the sources during each voltage level.

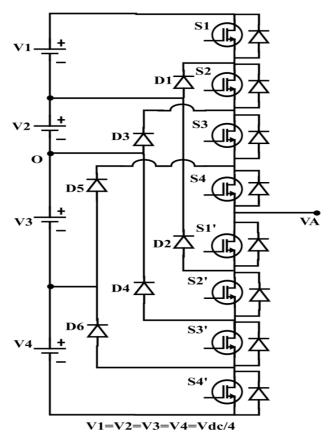

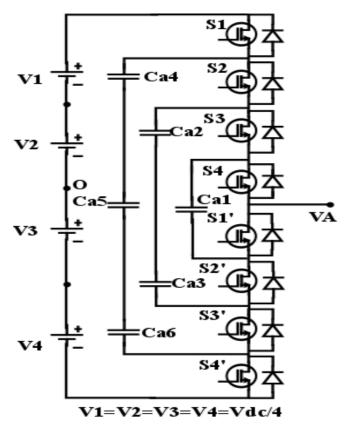

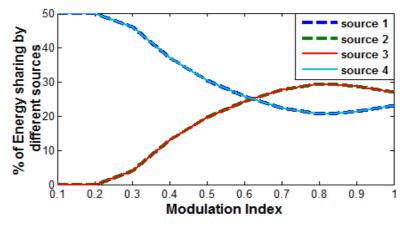

The third work provides single phase multilevel inverter with improved fault tolerance in terms of switch open circuit failures and energy balancing between sources. Generally multilevel inverters for photovoltaic (PV) applications are fed with multiple voltage sources. For majority of the multilevel inverters the load shared to individual voltage sources is not equal due to inverter structure and switching combination. This leads to under-utilization of the voltage sources. To address this issue optimal PV module distribution for multilevel inverters is proposed. Mathematical analysis is carried out for optimal sharing of PV resources for each voltage source. The proposed source distribution strategy ensures better utilization of each voltage source, as well as minimizes the control complexity for energy balancing issues. This topology requires four isolated DC-sources with a voltage magnitude of Vdc/4 (where Vdc is the voltage requirement for the conventional NPC multilevel inverter). These isolated DC voltage sources are realized with multiple PV strings. The operation of proposed multilevel single phase inverter is analyzed for different switch open-circuit failures.

All the presented topologies are simulated using MATLAB/Simulink and the results are verified with laboratory prototype.

## Nomenclature

| Abbreviations            |                                                     |  |  |

|--------------------------|-----------------------------------------------------|--|--|

| SOC                      | : State of Charge                                   |  |  |

| PV                       | : Photovoltaic                                      |  |  |

| THD                      | : Total Harmonic Distortion                         |  |  |

| MPPT                     | : Maximum Power Point Tracking                      |  |  |

| SVPWM                    | : Space Vector Pulse Width Modulation               |  |  |

| MLI                      | : Multilevel Inverter                               |  |  |

| NPC                      | : Neutral Point Clamped                             |  |  |

| FC                       | : Flying Capacitor                                  |  |  |

| DER                      | : Distributed Energy Resource                       |  |  |

| РСВ                      | : Printed Circuit Board                             |  |  |

| IGBT                     | : Insulated Gate Bipolar Transistor                 |  |  |

| MOSFET                   | : Metal Oxide Semiconductor Field Effect Transistor |  |  |

| TRAIC                    | : Triode for alternating current                    |  |  |

| SVC                      | : Space Vector Control                              |  |  |

| SHE                      | : Selective Harmonic Elimination                    |  |  |

| SPWM                     | : Sinusoidal Pulse Width Modulation                 |  |  |

| LED                      | : Light Emitting Diode                              |  |  |

| FPGA                     | : Field Programmable Gate Array                     |  |  |

| VHDL                     | : VHSIC Hardware Description Language               |  |  |

| PD                       | : Phase Disposition                                 |  |  |

| POD                      | : Phase Opposition Disposition                      |  |  |

| DSPACE                   | : Digital Signal Processing and Control Engineering |  |  |

| Symbols                  | : Definitions                                       |  |  |

| F1, F2                   | : Fuse                                              |  |  |

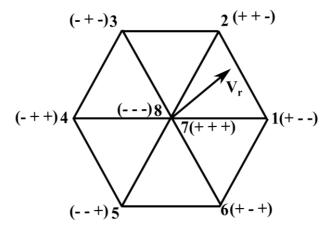

| Vr                       | : Space vector                                      |  |  |

| $V_{\alpha}, V_{\beta}$  | : Two dimensional space vectors                     |  |  |

| $V_{AO}, V_{BO}, V_{CO}$ | : Three phase voltages                              |  |  |

| I <sub>sa</sub>          | : PV module output current                          |  |  |

| V <sub>sa</sub>          | : PV module output voltage                          |  |  |

| N <sub>P</sub>                       | : Number of parallel connected cells                     |

|--------------------------------------|----------------------------------------------------------|

| $N_S$                                | : Number of series connected cells                       |

| R <sub>s</sub>                       | : Series resistance                                      |

| R <sub>sh</sub>                      | : Shunt resistance                                       |

| I <sub>ph</sub>                      | : Light generated current                                |

| I <sub>sat</sub>                     | : Reverse saturation current                             |

| Α                                    | : Ideality factor                                        |

| K                                    | : Boltzmann's constant                                   |

| Т                                    | : Cell temperature                                       |

| Q                                    | : Electronic charge                                      |

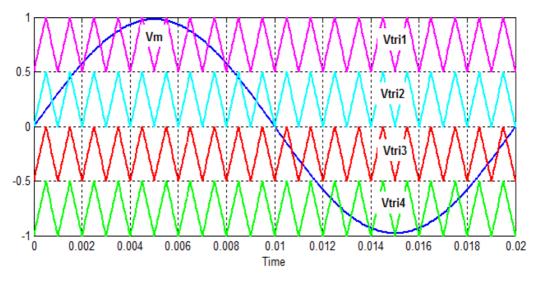

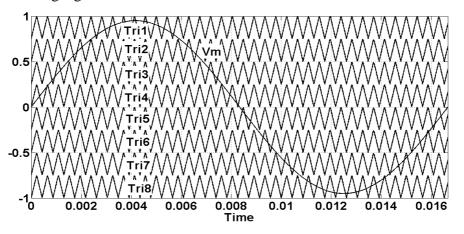

| Vm                                   | : Modulating signal                                      |

| Vtri                                 | : Triangular signal                                      |

| m <sub>a</sub>                       | : Modulation index                                       |

| f <sub>m</sub>                       | : Modulation signal frequency                            |

| $\mathbf{f}_{\mathbf{s}}$            | : Switching frequency                                    |

| M1, M2                               | : Relays                                                 |

| V <sub>dc-min</sub>                  | : Minimum battery voltage                                |

| $S_{f1}, S_{f2}$                     | : Switch fault signal                                    |

| $\mathbf{V_{1a,}V_{1b,}V_{1c}}$      | : Higher voltage level for a, b, c phases                |

| $V_{2a},V_{2b},V_{2c}$               | : Middle voltage level for a, b, c phases                |

| Ε                                    | : Energy transferred to load                             |

| $E_{V_{1a}}, E_{V_{1b}}, E_{V_{1c}}$ | : Energy transferred to load during higher voltage level |

| $E_{V_{2a}}, E_{V_{2b}}, E_{V_{2c}}$ | : Energy transferred to load during middle voltage level |

| V <sub>avg</sub>                     | : Average output voltage                                 |

|                                      |                                                          |

# Contents

| Declaration        | n                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ii  |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Approval S         | Sheet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | iii |

| Acknowled          | dgements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | iv  |

| Abstract           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | vii |

| Nomenclatu         | ıre                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | X   |

| 1 Introduct        | ion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1   |

| 1.1 Import         | ance of renewable energy systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1   |

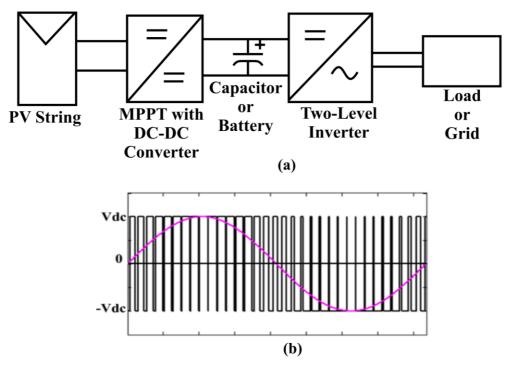

| 1.2 In             | nportance of Power converter for renewable energy systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2   |

| 1.3 In             | troduction to multilevel inverters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4   |

| 1.3.1 Di           | ode clamped multilevel inverter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4   |

| 1.3.2 Fl           | ying capacitor multilevel inverter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5   |

| 1.3.3 Ca           | scaded H-bridge multilevel inverter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 7   |

| 1.3.4 Inv          | verter topologies with reduced number of switches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 8   |

| 1.4 Import         | ance of fault tolerant multilevel inverter for stand alone PV system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 10  |

| 1.4.1 Fa           | ult tolerant multilevel inverter configurations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 11  |

| 1.5 Energy         | y balancing issue of multilevel inverter for stand alone PV system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 16  |

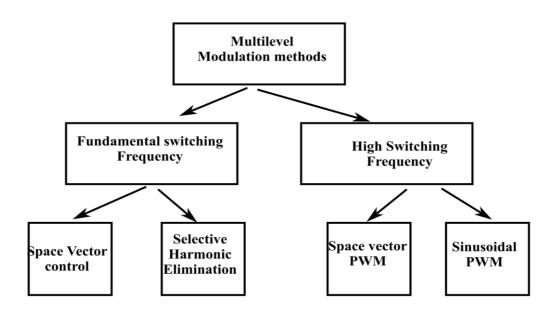

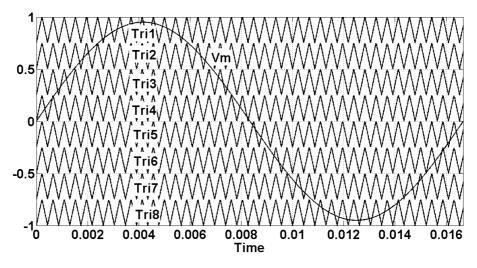

| 1.6 Pulse          | width modulation strategies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 20  |

| 1.7 Scope          | of the thesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 23  |

| 2 Fault toler      | ant Multilevel inverter Topologies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 27  |

| 2.1 Introd         | luction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 27  |

| 2.2 Fault          | tolerant single phase and three phase five-level inverter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

| 2.2.1              | Fault analysis of five-level inverter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

| 2.2.2<br>level inv | Pulse width modulation technique and comparison with single potential entry of the second sec |     |

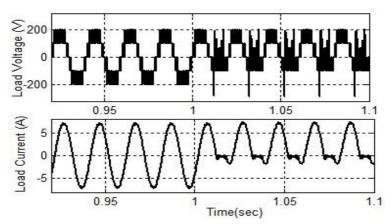

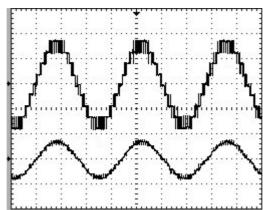

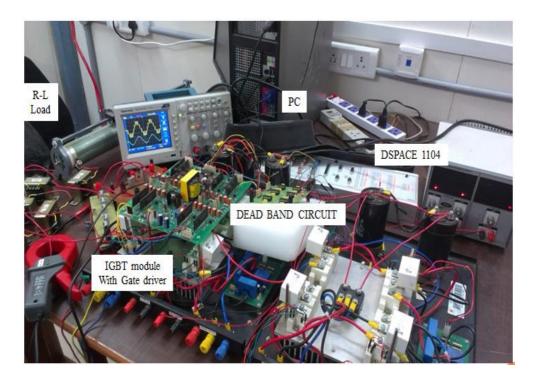

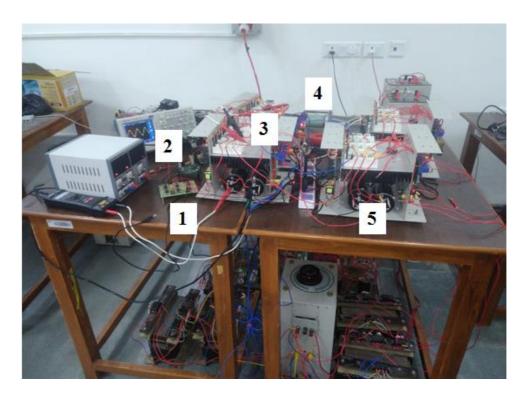

| 2.2.3              | Single phase five-level inverter Results and Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 35  |

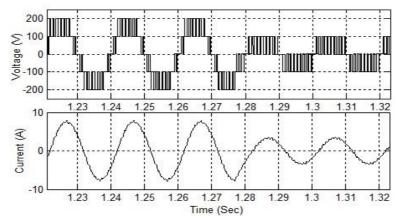

| 2.2.4              | Three phase five-level inverters Results and Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| 2.3 Impro          | oved single phase five-level inverter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 42  |

| 2.3.1              | Fault analysis of improved single phase five-level inverter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 43  |

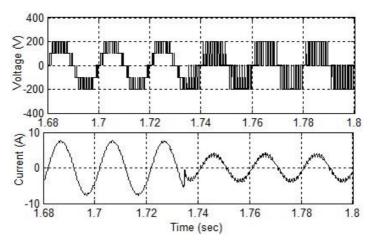

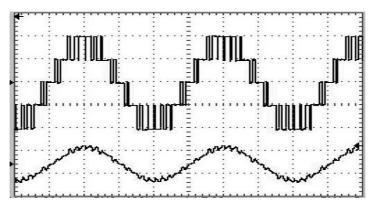

| 2.3.2              | Results and Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 44  |

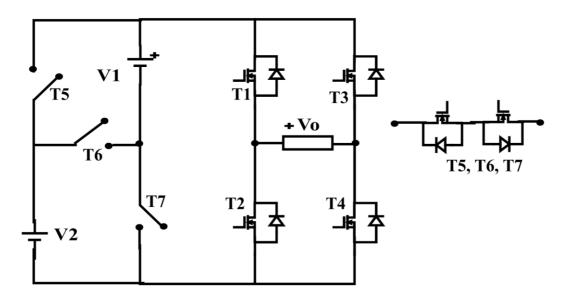

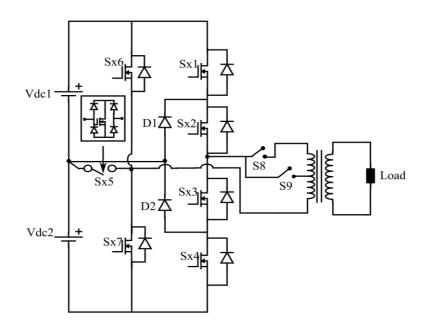

| 2.4 Fault          | tolerant dual inverter configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 46  |

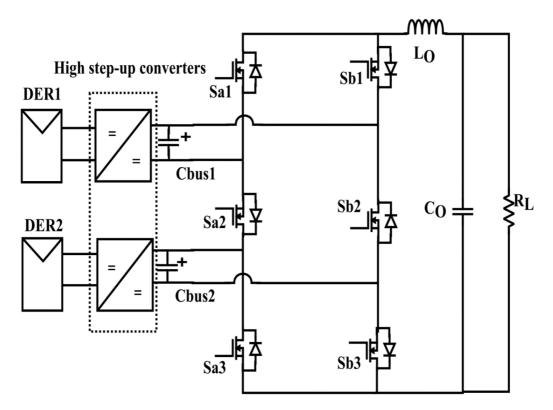

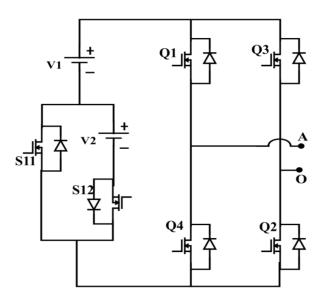

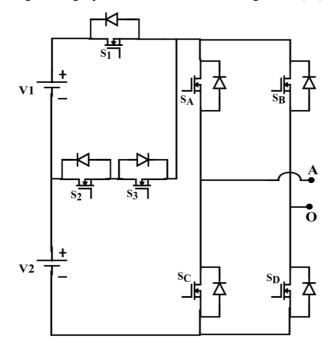

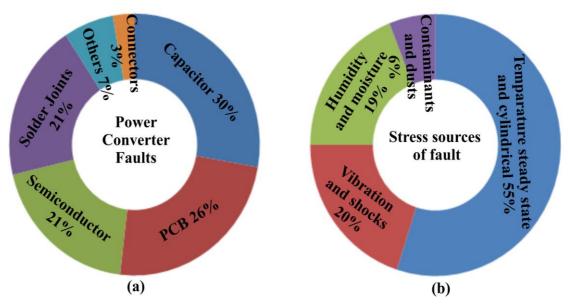

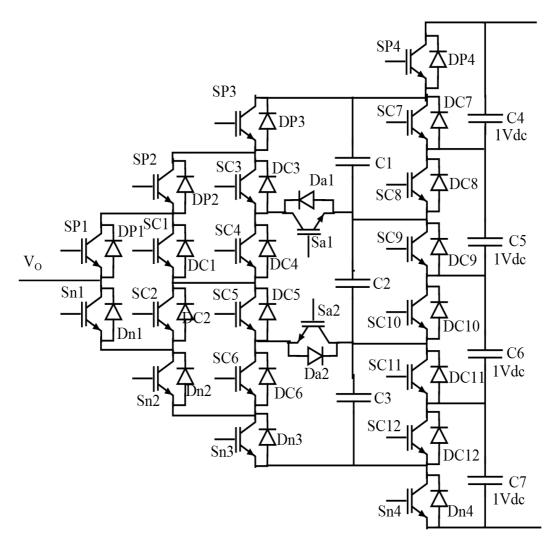

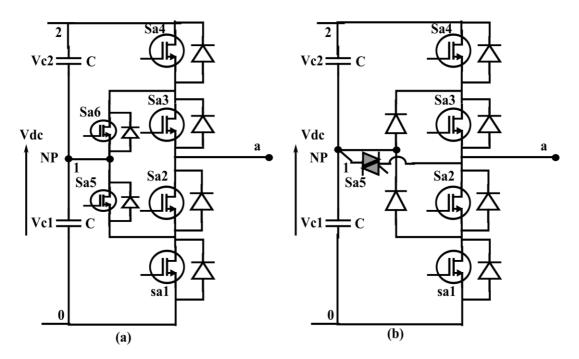

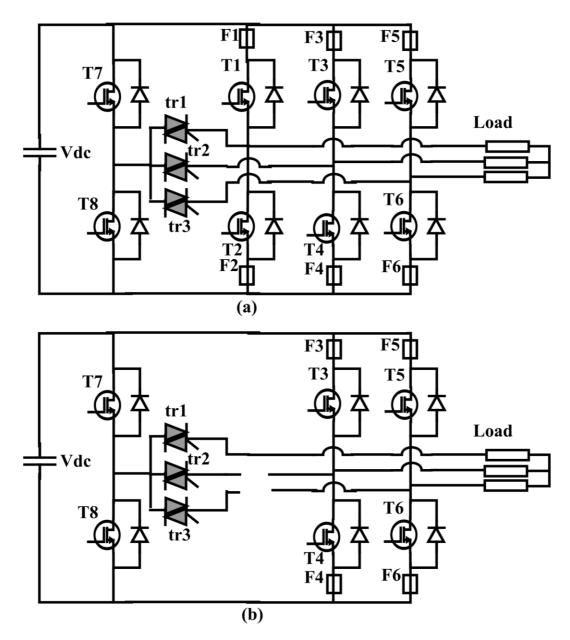

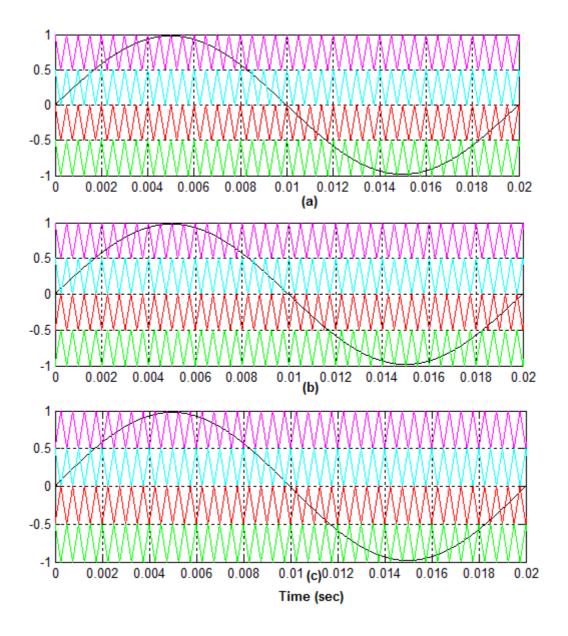

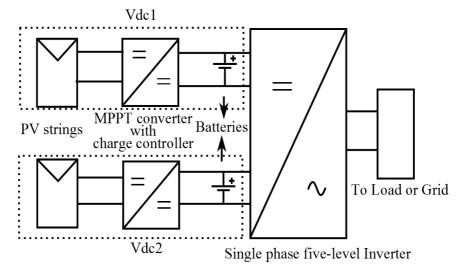

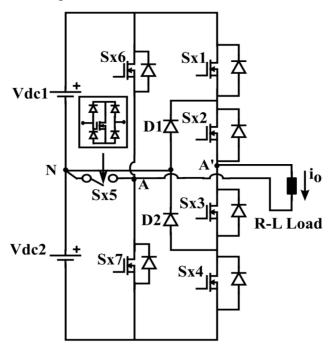

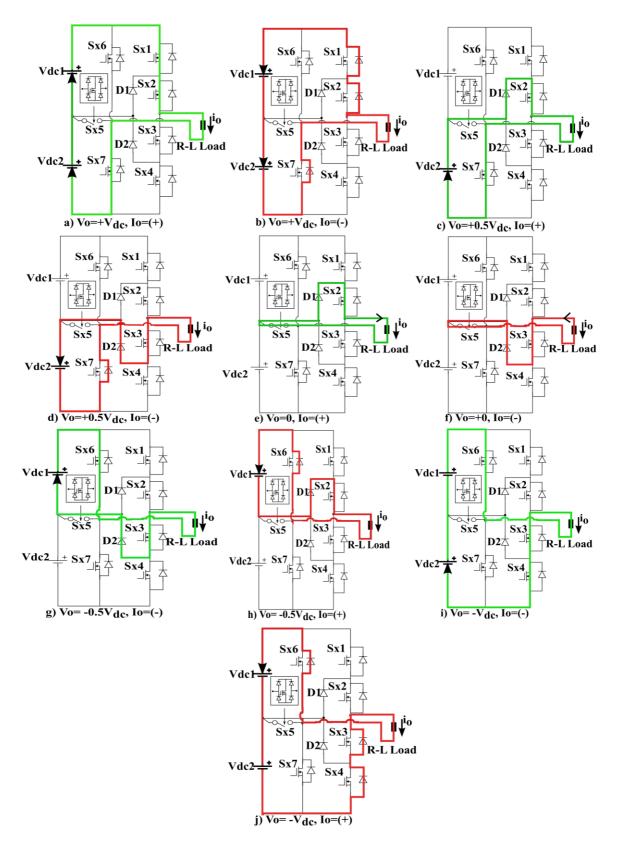

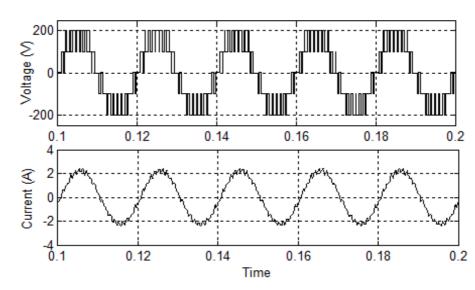

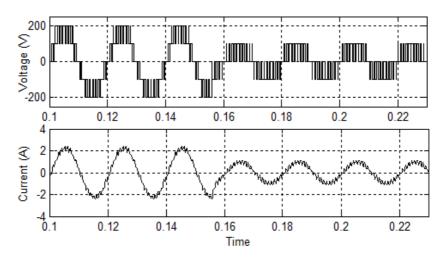

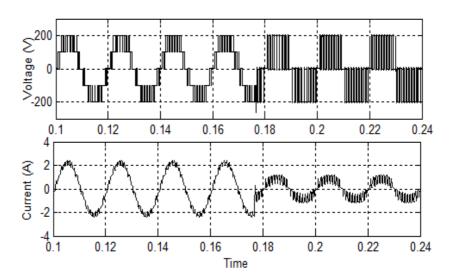

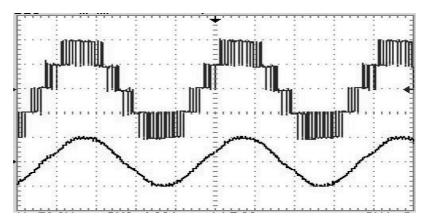

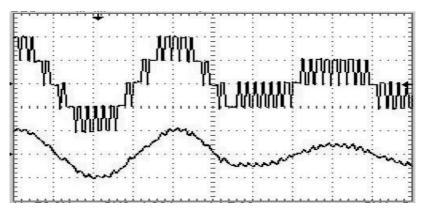

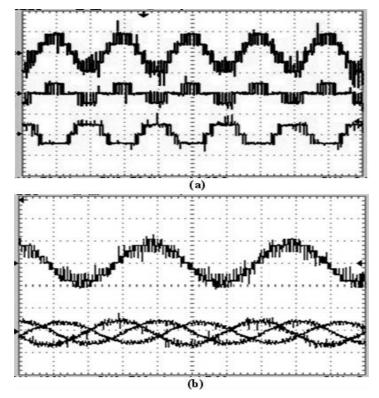

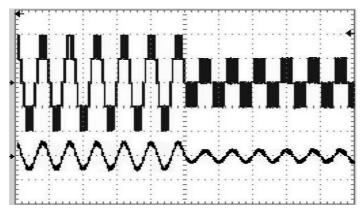

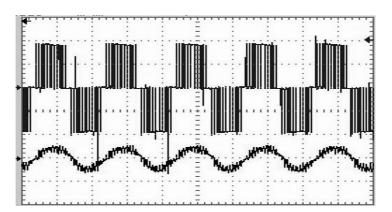

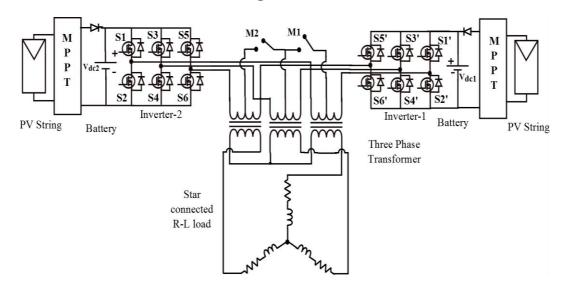

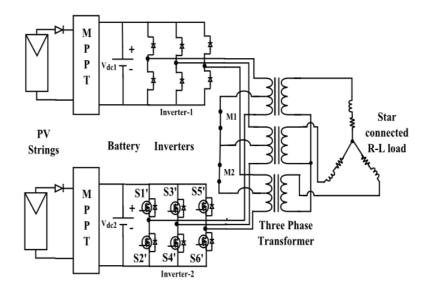

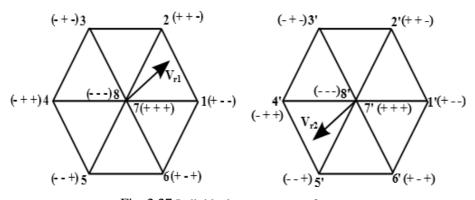

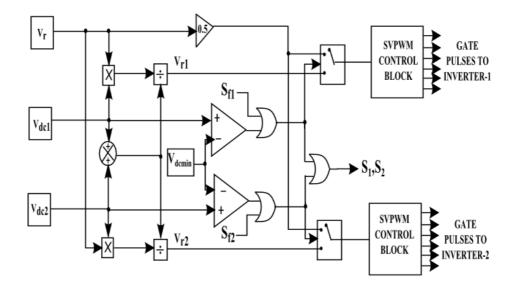

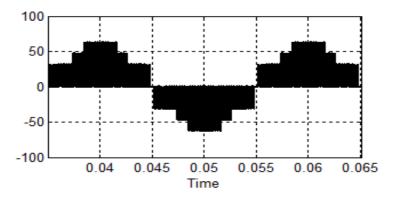

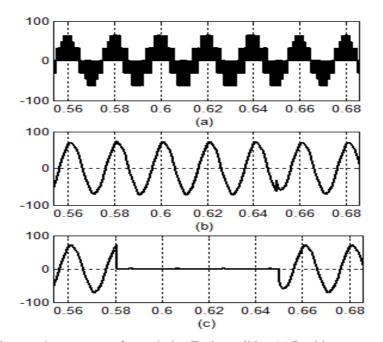

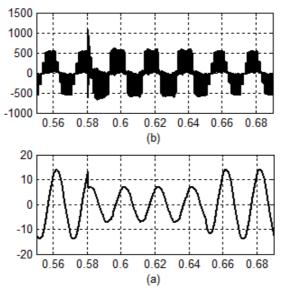

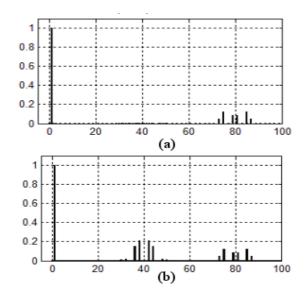

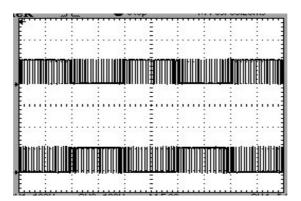

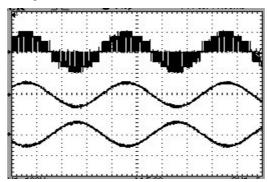

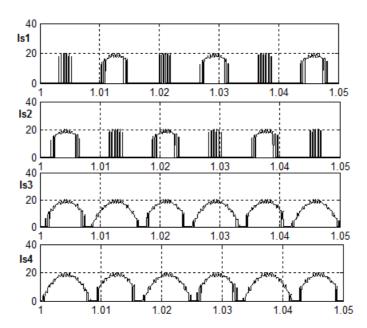

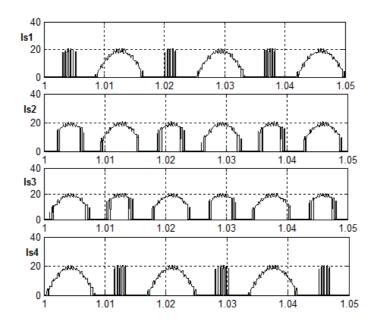

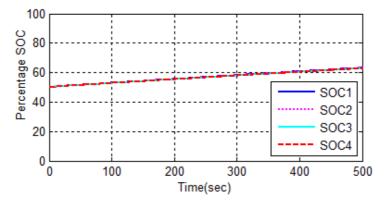

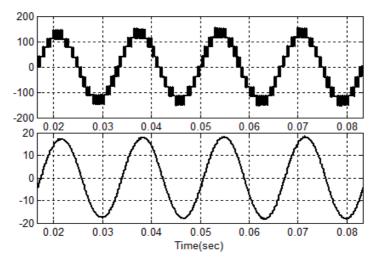

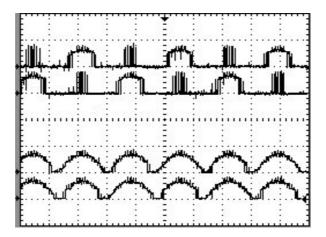

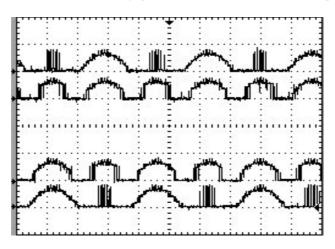

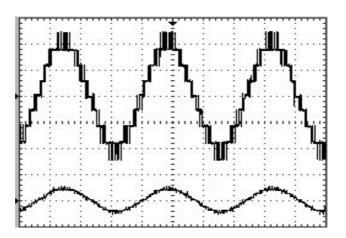

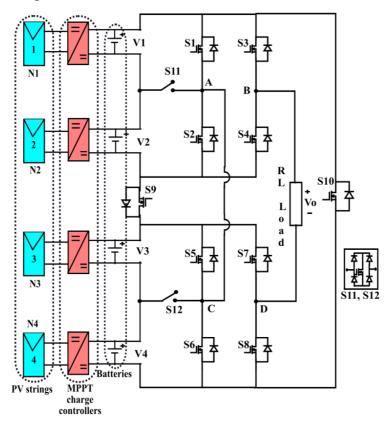

| 2.4.1              | Fault Analysis of dual inverter configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |