Faculty of Computer Science and Automation Integrated HW/SW Systems Group Prof. Dr.-Ing. habil. Andreas Mitschele-Thiel

# **Master Thesis**

# A Generic Debug Interface for IP-Integrated Assertions

# Christoph Kuznik

This master thesis was submitted in fulfillment of the requirements for the degree

## **DIPLOMINGENIEUR**

(Dipl.-Ing.)

**Tutor** Dr.-Ing. Volkan Esen

**Professor in charge** Prof. Dr.-Ing. habil. Andreas Mitschele-Thiel

University adviser Dr.-Ing. Dieter Wuttke

Submission

Ilmenau, 9. December 2008

Inventory no.

2008-12-09/161/II03/2235

Integrated HW/SW Systems Group

Prof. Dr.-Ing. habil. Andreas Mitschele-Thiel

Faculty of Computer Science and Automation

## Ilmenau University of Technology

in Cooperation with

## Infineon Technologies AG Munich

IFAG ETS DMI AFS SFV

Prof. Dr.-Ing. Wolfgang Ecker

Dr.-Ing. Volkan Esen

#### **Declarations**

Herewith I declare, that I have made the presented master thesis myself and solely with the aid of the means permitted by the examination regulations of the Ilmenau University of Technology. The literature used is indicated in the bibliography. I have indicated literally or correspondingly assumed contents as such.

#### Eidesstattliche Erklärung

Hiermit erkläre ich an Eides statt, diese Diplomarbeit eigenhändig und selbständig verfasst, keine als die angegebenen Hilfsmittel und Quellen verwendet und direkt oder indirekt übernommene Gedanken als solche gekennzeichnet zu haben. Diese Arbeit wurde bisher in dieser oder ähnlicher Form keiner anderen Prüfungsbehörde vorgelegt noch anderweitig veröffentlicht.

Ilmenau, 9. December 2008

Christoph Kuznik

# Theses

- 1. Verification of complex heterogeneous electronic systems like System-on-Chip is the bottleneck of every design flow. Due to the design-verification gap and in general a methodology gap, it is unlikely that future designs can be verified to a large extend pre-silicon while keeping track in the time to market.

- Moreover, assertion-based verification methodology enables early error discovery and information on where and when assertions fail. This information is an important aid in the debugging process and the fundamental reasoning behind the ABV methodology.

- 3. Therefore, in-system, at-speed silicon validation using assertion checkers will be the next step for successful electronic systems design flows.

- 4. As electronic system design moves towards software engineering, there is emerging interest for model based approaches to cope with the growing complexity. A promising approach is the usage of meta modeling and the concept of domain-specific code-generation, for example using templates.

- 5. Using template based code-generation an abstract modeled functionality can be generated for a chosen architecture in an ideal way for every target language.

- 6. The model representation for a debuggable assertion interface makes usage of these two approaches and generates an interface to access on-silicon assertion. This allows the designer to optionally include silicon checkers within the design.

- 7. The capture of the debuggable assertion interface within a meta model allows implementation independent specification. Besides, the assertion interface allows the consistent modeling of assertion across multiple abstraction levels.

- 8. With help of the debuggable assertion interface correct module integration can be verified. Moreover, the monitoring of IP-internal assertion checker significantly improves the observability of internal signals, which may escaped previous pre-silicon verification and simulation steps.

| Ilmenau, 9. December 2008 |                  |  |

|---------------------------|------------------|--|

|                           |                  |  |

|                           | Christoph Kuznik |  |

# Acknowledgments

I am delighted to thank Prof. Dr.-Ing. habil. Andreas Mitschele-Thiel from the Faculty of Computer Science and Automation at the Ilmenau University of Technology for the opportunity to write a diploma thesis at Infineon Technologies AG Munich and Dr.-Ing. Heinz-Dietrich Wuttke from Ilmenau University of Technology for his kindly willingness to supervise it.

Besides, I also sincerely thank Prof. Dr.-Ing. Wolfgang Ecker of Infineon Technologies AG for giving me the possibility to process a research thesis topic within the System Design Methodologies department at Infineon. Moreover, I would like to express my deep gratitude to my tutor Dr.-Ing. Volkan Esen for his invaluable suggestions and support. I also want to thank my Infineon colleagues Dipl.-Ing. Michael Velten and Dipl.-Ing. Thomas Steininger for their help, support and encouragement.

Finally I thank the Infineon students of the department and my girlfriend Nicole for the enjoyable time in Munich as well as my family which always supported me during my studies.

#### Abstract

Nowadays electronic systems design requires fast time to market and solid verification throughout the entire design flow. Many concepts have been researched to raise the level of abstraction during the design entry phase, whereas model-based design is the most promising one. Assertion-based verification enables the developer to specify properties of the design and to get report if these are violated. Assertions are common during development and simulation of electronic products but often are not included in the final silicon. In this thesis an UML-based model defined at Infineon Technologies for capturing design specification information and to generate code automatically using templates, will be extended to allow the description of an abstract debuggable assertion interface for silicon assertions. With help of the assertion interface it shall be possible to verify the correct module integration and to monitor IP-internal assertion checker results. Besides, the code-generation templates for the assertion interface model will be described. To demonstrate the usability of the developed concepts an example system will be introduced to validate the approach.

## Kurzfassung

Der Entwurf von Hardware/Software Systemen ist auf eine solide Verifikationsmethodik angewiesen, die den ganzen Design Flow durchzieht. Viele Konzepte haben eine Erhöhung des Abstraktionsniveaus bei der Entwurfseingabe gemeinsam, wobei der modell-basierte Hardware-Entwurf einen vielversprechenden und sich verbreitenenden Ansatz darstellt. Assertion basierte Verifikation ermöglicht dem Entwickler die Spezifikation von Eigenschaften des Entwurfes und die Aufdeckung von Fällen, in denen diese verletzt werden. Während Assertions in Entwurfs- und Simulationsstadien weit verbreitet sind, ist der Ansatz, diese mit auf dem integrierten Schaltkreis (IC) zu fertigen, neuartig. In dieser Diplomarbeit soll ein von Infineon Technologies entwickeltes, auf UML basierendes Datenmodell, welches zur Erfassung von Entwurfsspezifikation und zur automatischen Code-Generierung genutzt wird dahingehend erweitert werden, die Beschreibung für im IC integrierte Assertions zu ermöglichen. Für diese Zwecke wird ein abstraktes Datenmodell beschrieben werden. Das Assertion Interface soll die spezifikationsgetreue Modellintegration gewährleisten, sowie IC interne Assertionresultate dem umgebenen System über das Interface zugänglich machen und damit zum Debugging während der Laufzeit ermöglichen. Ferner werden die Codegenerierungs Templates erläutert und ein Beispielsystem eingeführt, um die beschriebenden Konzepte zu validieren.

## **Nomenclature**

ABV ..... Assertion-based Verification

AHB ..... Advanced High-performance Bus

AMBA ...... Advanced Microprocessor Bus Architecture

APB ..... Advanced Peripheral Bus

API ..... Application Programming Interface

ECSI ..... European Electronic Chips & Systems design Initiative

EDA ..... Electronic Design Automation

FSM ..... Finite State Machine

HTML ..... Hypertext Markup Language

IC ..... Integrated circuit

IP ...... Intellectual Property, in this context hardware or software modules

IP-XACT ...... The new name of the SPIRIT schema, which will be standardized as

**IEEE 1685**

ITRS ..... International Technology Roadmap for Semiconductors

MARTE ...... Modeling and Analysis of Real-Time Embedded Systems

MOF ..... Meta-Object Facility

OMG ..... Object Management Group

OVL ..... Open Verification Library

PSL ..... Property Specification Language

RTL ..... Register Transfer Language

SIF ..... Serial InterFace

SoC ..... System-on-Chip

SPRINT ...... Open SoC Design Platform for Reuse and Integration of IPs

SVA ..... SystemVerilog Assertions

TLM ..... Transaction Level Modeling

UART ...... Universal Asynchronous Receiver Transmitter

UML ...... Unified Markup Language

VCD ...... Value Change Dump

VHDL ...... Very High Speed Integrated Circuit Hardware Description Language

W3C ..... World Wide Web Consortium

WLF ..... Wave Log Format

XMI ..... XML Metadata Interchange

XML ..... Extensible Markup Language

# Contents

|    | List  | of Figu  | res                             | xiv |

|----|-------|----------|---------------------------------|-----|

|    | List  | of Table | es                              | XV  |

|    | List  | of Algo  | rithms                          | xvi |

| 1. | Intro | oductio  | n                               | 1   |

|    | 1.1.  | Motiva   | ation                           | 1   |

|    | 1.2.  | Chapte   | er Overview                     | 2   |

| 2. | Rela  | ted Wo   | ork                             | 4   |

|    | 2.1.  | Asserti  | ion based Verification          | 4   |

|    |       | 2.1.1.   | What is an Assertion            | 4   |

|    |       | 2.1.2.   | Assertions in Silicon Debug     | 6   |

|    | 2.2.  | Similar  | r Approaches                    | 8   |

| 3. | Infin | eon XC   | Change Flow                     | 10  |

|    | 3.1.  | Funda    | mentals                         | 11  |

|    |       | 3.1.1.   | Meta data and meta models       | 12  |

|    |       | 3.1.2.   | SPIRIT                          | 13  |

|    |       | 3.1.3.   | SPRINT                          | 14  |

|    |       | 3.1.4.   | Unified Modeling Language       | 15  |

|    |       | 3.1.5.   | Extensible Markup Language      | 17  |

|    |       | 3.1.6.   | XML Metadata Interchange        | 17  |

|    |       | 3.1.7.   | Python                          | 19  |

|    |       | 3.1.8.   | Templating with MAKO            | 20  |

|    |       | 3.1.9.   | AMBA Overview                   | 23  |

|    |       | 3.1.10.  | AMBA APB                        | 24  |

|    | 3.2.  | The Es   | ssence Meta Model               | 25  |

|    |       | 3.2.1.   | Component Data Model            | 26  |

|    |       | 3.2.2.   | Interface Definition Data Model | 26  |

|    |       | 3.2.3.   | XRef Data Model                 | 27  |

|    |       | 3.2.4.   | Bus Data Model                  | 28  |

|    |       | 3.2.5.   | System Data Model               | 28  |

|    |       | 3.2.6.   | ModelConfig Data model          | 28  |

|    |       | 327      | Other Data Models               | 20  |

|            | 3.3.  | Toolch   | n <mark>ain</mark>                          | 0 |

|------------|-------|----------|---------------------------------------------|---|

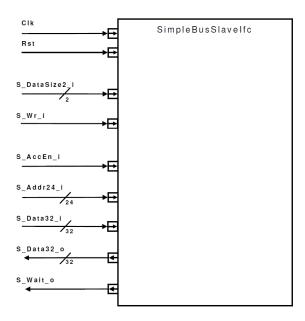

|            |       | 3.3.1.   | Essimport                                   | 0 |

|            |       | 3.3.2.   | Essemplate                                  | 2 |

| 4.         | Infin | eon SF   | PINNI Example System 3:                     | 3 |

|            | 4.1.  | Existin  | ng System                                   | 3 |

|            |       | 4.1.1.   | Architecture                                | 3 |

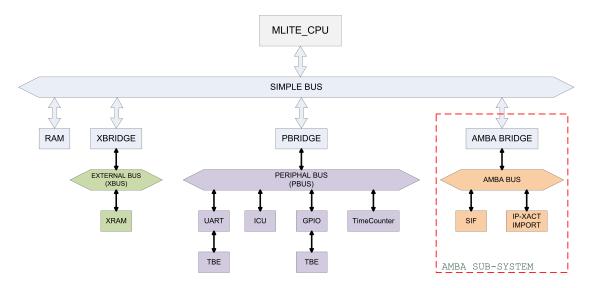

|            |       | 4.1.2.   | Simple Bus Specification                    | 4 |

|            | 4.2.  | Extens   | sions to the SPINNI System                  | 5 |

|            |       | 4.2.1.   | APB Bridge Architecture                     | 6 |

|            |       | 4.2.2.   | APB Bridge Behavior                         | 7 |

|            |       | 4.2.3.   | APB                                         | 0 |

|            |       | 4.2.4.   | APB Peripheral                              | 0 |

|            |       | 4.2.5.   | APB Subsystem                               | 2 |

|            |       | 4.2.6.   | Interface Mapping                           | 3 |

| <b>5</b> . | Deb   | uggabl   | e Assertion Interface 40                    | 6 |

|            | 5.1.  | Requir   | rement Analysis                             | 6 |

|            |       | 5.1.1.   | Hardware                                    | 7 |

|            |       | 5.1.2.   | Architecture                                | 7 |

|            |       | 5.1.3.   | Bus Interfacing                             | 8 |

|            |       | 5.1.4.   | Multiple Assertion Interfaces per component | 9 |

|            | 5.2.  | Assert   | ion Interface Meta Model                    | 0 |

|            |       | 5.2.1.   | AssertionInterface                          | 1 |

|            |       | 5.2.2.   | Scope                                       | 2 |

|            |       | 5.2.3.   | Assertion                                   | 2 |

|            |       | 5.2.4.   | RefInterfaceAssertion                       | 3 |

|            |       | 5.2.5.   | RefSensitivityPort                          | 3 |

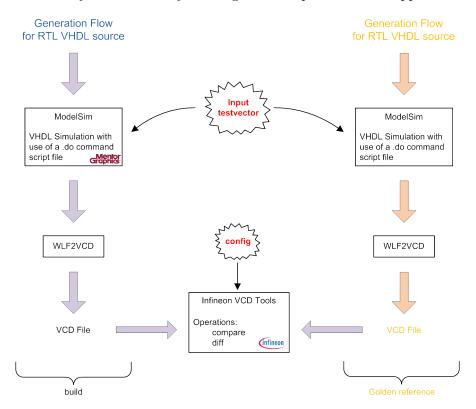

|            | 5.3.  | Target   | Code Architecture                           | 3 |

|            |       | 5.3.1.   | Assertion Register Constraints              | 4 |

|            | 5.4.  | Requir   | rement fulfillment                          | 5 |

| 6.         | Asse  | ertion I | nterface Generation 5                       | 7 |

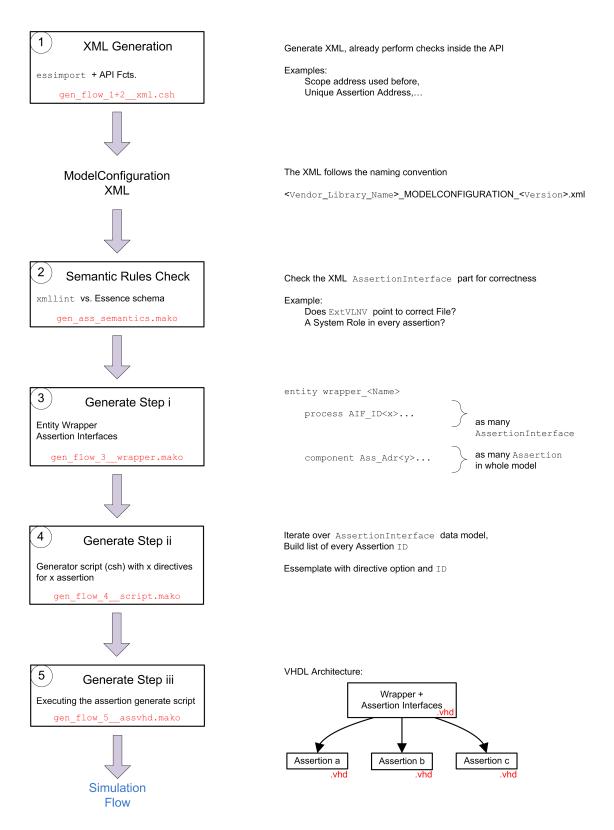

|            | 6.1.  | Challe   | nges on Template development                | 0 |

|            |       |          | General Coding Style                        | 0 |

|            |       | 6.1.2.   | Wrapper Part                                | 2 |

|            |       | 6.1.3.   |                                             | 2 |

|            | 6.1.4. Assertion Part                      |      |   |       |   |   |   |     |

|------------|--------------------------------------------|------|---|-------|---|---|---|-----|

| <b>7</b> . | 7. Simulation                              |      |   |       |   |   |   | 68  |

|            | 7.1. Enhanced SPINNI System                | <br> |   |       |   |   |   | 69  |

|            | 7.2. Mixed Language Simulation             | <br> |   |       |   |   |   | 71  |

|            | 7.3. Assertion Interface                   | <br> |   |       |   |   |   | 72  |

|            | 7.4. Application Results                   | <br> |   |       |   | • |   | 73  |

| 8.         | 8. Summary and Outlook                     |      |   |       |   |   |   | 75  |

| Re         | References                                 |      |   |       |   |   |   | 76  |

| Α.         | A. Appendix                                |      |   |       |   |   |   | 84  |

|            | A.1. Essence ModelConfiguration data model | <br> |   |       |   |   |   | 84  |

|            | A.2. AMBA APB Bridge Example               | <br> |   |       |   |   |   | 86  |

|            | A.3. AMBA APB Slave Example                | <br> |   |       |   |   |   | 92  |

|            | A.4. AssertionInterface XML Example        |      |   |       |   |   |   | 94  |

|            | A.4. Assertioninterface AML Example        | <br> | • | <br>• | • | • | • | 0 1 |

|            | A.5. Assertion Wrapper Example             |      |   |       |   |   |   |     |

# List of Figures

| 1.1. | Design-Verification Gap[14, P. 3]                                      | 2  |

|------|------------------------------------------------------------------------|----|

| 2.1. | Usage scenarios for hardware assertion checkers[9]                     | 7  |

| 3.1. | Infineon XChange, based on a single-source XML-Methodology[30, P. 9] . | 11 |

| 3.2. | Example for the MOF architecture[49]                                   | 13 |

| 3.3. | Example UML diagram[39]                                                | 16 |

| 3.4. | A typical AMBA enabled system[38]                                      | 24 |

| 3.5. | APB Bus Transaction State diagram[38]                                  | 25 |

| 3.6. | Relation of Essence model and ModelConfig model                        | 29 |

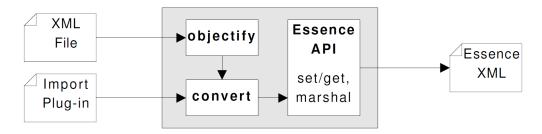

| 3.7. | Essimport Flow[31, P. 7]                                               | 31 |

| 3.8. | Essemplate Flow[31, P. 15]                                             | 32 |

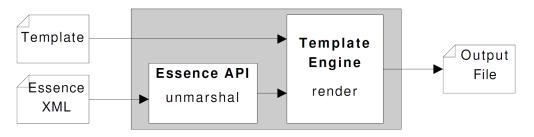

| 4.1. | Infineon SPINNI System with intended enhancements                      | 34 |

| 4.2. | Interfaces of a SimpleBus slave[27]                                    | 35 |

| 4.3. | APB Bridge Overview                                                    | 37 |

| 4.4. | SimpleBus to APB finite state machine for bridge                       | 38 |

| 4.5. | APB InterfaceDefinition XML snapshot                                   | 41 |

| 4.6. | The AMBA subsystem in detail                                           | 42 |

| 4.7. | Constraint violation on Interface Mapping                              | 45 |

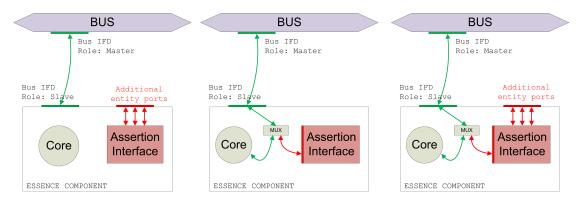

| 5.1. | Possible ways to access the Assertion Interface                        | 48 |

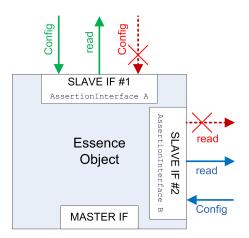

| 5.2. | Allowed accesses to the AssertionInterface                             | 50 |

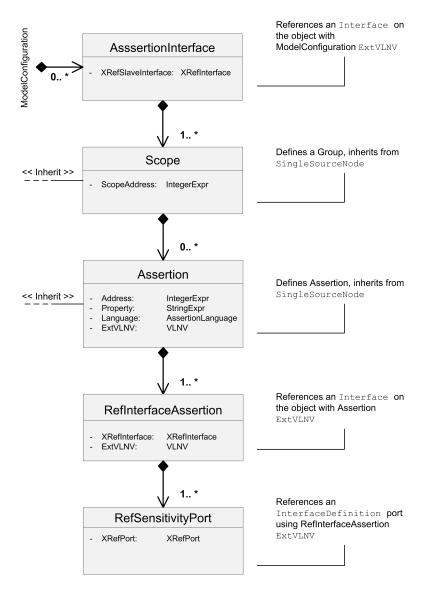

| 5.3. | AssertionInterface data model                                          | 51 |

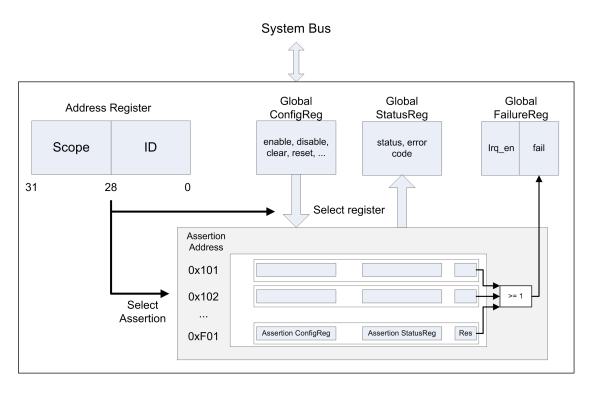

| 5.4. | The AssertionInterface architecture                                    | 54 |

| 6.1. | AssertionInterface generation flow                                     | 59 |

| 6.2. | Main and sub templates                                                 | 61 |

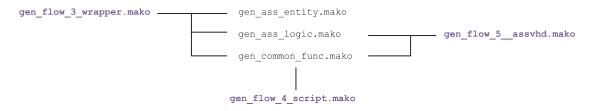

| 6.3. | Temporary signal mapping on asserted out / inout signals               | 65 |

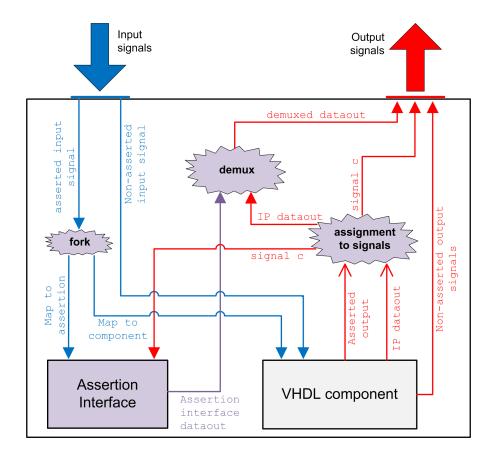

| 7.1. | Simulation and Verification Flow                                       | 68 |

| 7.2. | Example input file for simulation                                      | 70 |

| A 1  | Infineon Essence ModelConfiguration data model                         | 85 |

# **List of Tables**

| 3.1. | Differences between meta model and model [21]      | 12 |

|------|----------------------------------------------------|----|

| 4.1. | Essence Interface Parameters                       | 44 |

| 5.1. | Fulfillment of the AssertionInterface requirements | 56 |

| 6.1. | Static Assertion VHDL ports                        | 66 |

| 6.2. | Overview about developed plugins                   | 67 |

| 6.3. | Overview about developed templates                 | 67 |

# List of Algorithms

| 3.1. | Example for a well-formed XML                                      | 17 |

|------|--------------------------------------------------------------------|----|

| 3.2. | XMI description of the address UML class (figure 3.3)[39]          | 18 |

| 3.3. | Example for Python Code                                            | 19 |

| 3.4. | Simple Text substitution using MAKO template                       | 21 |

| 3.5. | Output of algorithm for $x=10, y=5$                                | 21 |

| 3.6. | MAKO Control structures                                            | 22 |

| 3.7. | MAKO def statement                                                 | 22 |

| 3.8. | Example of an essimport plugin with set of an attribute(written in |    |

|      | Python)[31, P. 12]                                                 | 31 |

| 7.1. | Example validation code for SPINNI system                          | 71 |

# 1. Introduction

#### 1.1. Motivation

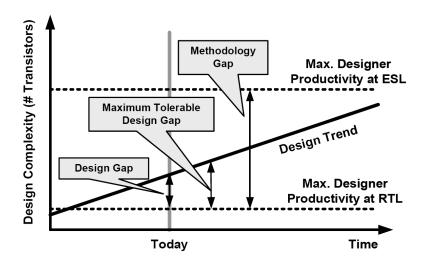

The famous Moore's law describes a long-term trend in the history of computing hardware. Since the invention of the Integrated Circuit (IC) in 1958, the number of transistors that can be placed inexpensively on an integrated circuit has increased exponentially, doubling approximately every two years. This trend has continued for almost half of a century and is not expected to stop for another decade at least and perhaps much longer. [59] Therefore, more and more heterogeneous parts of an electronic system can be integrated on a single IC. This System-on-a-chip (SoC) may contain digital, analog, mixed-signal or radio-frequency functions – all on one chip. Unfortunately, this situation leads to more complex electronic systems design, as designers face a combination of various disciplines, the coexistence of multiple design languages, and several abstraction levels. For example, it is now common that software is an integral part of semiconductor products. The customer expects to have a high-level access to the product. Otherwise the necessary low level design of the system would take too much time. Examples are protocol stacks for communication ICs or software APIs.[33] In this multi-disciplinary context, several gaps in a joint unified software and hardware design flow can be identified. For example, traditional HDL-based designs do no longer suffice to leverage the logical resources on improved manufacturing within the shortening time-to-market windows. Moreover, it is indeed also much more unlikely that such large designs can be verified to a large extend while keeping track in the time to market. Therefore, nowadays verification is the bottleneck and the most costly stage within the entire design flow. Figure 1.1 illustrates this so called design-manufacturing gap. In fact, one can also speak from a methodology gap. Therefore, new methodologies for development and verification are necessary for example starting the implementation from higher level modeling. As electronic system design moves towards software engineering, there is emerging interest for model based approaches within the hardware community. For example, different *Unified Modeling Language* (UML) diagrams and their variations found their application in requirements specification, testbenches, architectural descriptions, and behavioral modeling of electronic systems. Moreover, extensive IP Reuse and early verification must be supported by emerging standards like SPIRIT IP-XACT. [52, 51] The International Technology Roadmap for Semiconductor (ITRS) report from 2007[1] affirms these requirements for future verification and design flows. Since perfect logic and timing verification of a complex SoC is practically impossible pre-silicon, postsilicon validation

Figure 1.1: Design-Verification Gap[14, P. 3]

has become an essential step in the design implementation methodology. Therefore, in this thesis a meta-model based approach to describe hardware and to generate code automatically using templates, will be extended to allow the description of an abstract assertion interface. This assertion interface will allow to specify properties of a digital design and shall also be expressed via a data model. With help of the assertion interface it shall be possible to verify the correct module integration and to monitor IP-internal assertion checker results. To demonstrate the usability of the developed concepts a widely used bus architecture was implemented in an existing Infineon example system. For the RTL level code generation work VHDL has been chosen.

This thesis was the result of work in the **IFAG ETS DMI AFS SFV** department at Infineon Technologies, headquartered in Munich. The department is dealing with System Design Methodologies including System Verification, TLM Modeling and XML Single Source Methodology.

#### 1.2. Chapter Overview

Chapter 2 briefly describes related concepts and related work of this thesis topic. In chapter 2.1 the aspects of assertion-based verification will be analyzed. Moreover, this chapter will describe the concept and advantages of in-system validation and debug. Apart from that, chapter 2.2 will refer to similar approaches of this thesis work.

In chapter 3 the underlying Infine on design flow for this thesis work will be explained. First

#### 1. Introduction

the related fundamentals will be briefly described. Apart from that, an overview about the SPIRIT IP-XACT[51, 52] oriented Infineon Essence meta model, the fundamental concept of the flow, will be illustrated in sub-chapters 3.2 and 3.3.

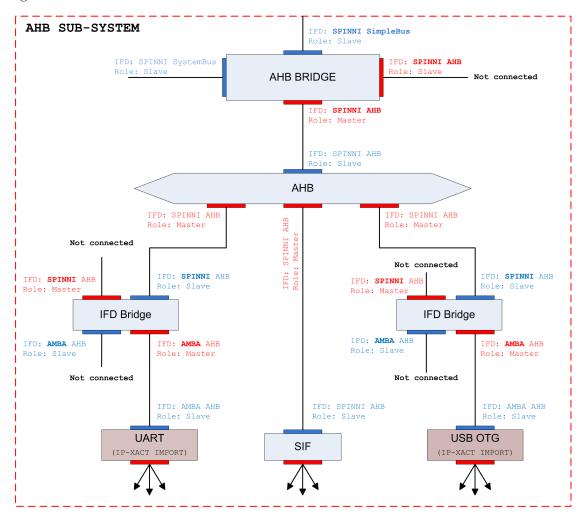

In chapter 4 the Infineon SPINNI example system for the proof-of-concept will be described. Moreover, the system elements and architecture will be explained. Besides, the additions and enhancements to the example system are introduced in chapter 4.2.

In chapter 5 a requirement analysis for the to be modeled assertion interface meta-model will take place. After the requirement collection chapter 5.2 will present the proposed data model solution. Thereafter, chapter 5.3 describes the target code architecture. Besides, chapter 5.4 will validate the proposed solution against the requirements.

In chapter 6 the template generation will be introduced. Therefore, section 6.1 describes challenges on template development. Moreover, the final templates architecture and the resulting VHDL code will be explained. Besides, section 6.2 will summarize the created plugins and templates during the thesis work.

In chapter 7 the simulation and verification flow for the assertion interface development is introduced. Moreover, the general validation approach and application results of the assertion interface generation are described.

Chapter 8 summarizes the thesis development and gives a short outlook for the possible usage of this approach in the near future.

This thesis work deals about the development of a hardware debug interface for silicon assertions using a meta model approach. Moreover, in the implementation stage a proof-of-concept example system will be generated. The various related concepts to this overall approach will be briefly described in the following sections. Besides, an overview about existing similar approaches and the differences to this thesis shall be given.

#### 2.1. Assertion based Verification

Assertion based design and more specifically <u>Assertion based Verification</u> (ABV) is gaining wide acceptance in the design community. It has been identified as a modern, powerful verification paradigm that can assure enhanced productivity, higher design quality and, ultimately, faster time to market and higher value to engineers and end-users of electronics products.

#### 2.1.1. What is an Assertion

In general, an assertion is an expression for an intended behavior, also called property which can be understood as "descriptions of valid temporal state".[54] This means that assertions can verify combinatorial as well as temporal properties. The assertion statement itself does not contribute any functionality to the element it is being used with. The purpose of an assertion is to ensure the consistency between specification and what is actually created.[20] Assertions are specified using a variety of Boolean expressions as primitives, along with regular expressions and numerous temporal operators. This concept has been used in software engineering for decades. But as the systems to be designed became more and more complex there was the demand to cope with the growing verification problem. So the concept of assertions also was introduced in the field of hardware or hardware-software co-design. If a specified property is violated then the assertion fires. In case, there is a scenario in which the design is not working correctly. Information on where and when assertions fail is an important aid in the debugging process, and is the fundamental reasoning behind the ABV methodology.

Assertions for hardware are typically written in a verification language such as PSL (Property Specification Language, IEEE 1850 standard) or SVA (SystemVerilog Assertions), but also HDL have assertion functions which are inner part of the language, but with much less functionality. Another approach is the use of assertion libraries

that can be invoked with common languages like VHDL or Verilog and provide in-built assertion functionality. An example is the <u>Open Verification Library</u> (OVL) maintained by Accellera[3] which provides checkers whose functionality can be even modified by adjusting checker parameters. The benefits of use of assertion can be summarized to:[20]

#### • error detection

Despite the output in case of a black box testing is correct, there are maybe design flaws that affect internal signals in certain conditions. The black box testing approach will not reveal these possible malfunctions. These internal violations can only be discovered with help of assertions.

#### • Improving observability, error isolation

With help of assertions the source of the bug can be caught closer then before. Even the basic assertion functionality of HDL supports the output of a text message along with the information that the assertion failed. In an ABV enabled design flow tools help to keep track of assertions results and the overall coverage. With all these benefits proper or unexpected behavior of the design can be isolated and fixed.

#### • error notification

If an assertion modeled property is violated, the assertion fires at once. If used in simulation the simulation kernel will halt and give report to the designer. For silicon-integrated assertion (see chapter 2.1.2) the automatic throws of IRQ are imaginable. In a design flow without assertion it is more difficult to find out where an error is originating from.

#### • correct usage checking of interfaces

More and more designs make use of third-party IP. With assertions the external vendor of IP cores can take care of the correct usage of the interface to the IP. Using assertions the interface protocols are monitored (mostly only during simulation) and validated using modeled properties.

#### • reduced debug time

It is easy to see that with help of ABV the overall design productivity is enhanced. Especially in case of errors and debug activities the needed amount of time decreases.

#### • faster time to market

Assertions are used at various stages of the design process. They are mostly used for pre-silicon simulation and verification. In design-entry and simulation tools such as Mentor Graphics Questa[41] the assertions are monitored by the simulation kernel when

a circuit is simulated. If designs are to be emulated in hardware, assertions can not be directly mapped into the hardware because they are written in a higher-level language that is not necessarily amenable to synthesis (see chapter 2.1.2).

Assertion-Based Design practices also advocate the use of assertions as part of the design effort, when used as a formal specification (describing designer intent).[9] The difference between assertions and formal verification is that an assertion models a property which has to be tested with a lot of testbench input to gain acceptable coverage. If the assertion never fails the assumption is that the design is stable and bug free. In formal verification it is calculated if the modeled property will *ever* be false.

#### 2.1.2. Assertions in Silicon Debug

In this thesis work the interface for (silicon debug) assertion shall be developed and modeled via the Essence meta model. Therefore, the benefits of silicon-debug shall be discussed first. For an in detail view about assertion checkers and checker generators please refer to [8]. Detailed resources for in-system debug can be found in [9, 2].

Normally assertions are only used during simulation and pre-silicon verification of a newly developed design. If an assertion fails then the designer knows that the property which is modeled by the assertion is violated. If so, a scenario has been revealed in which the design is not working correctly. So assertions help to discover potential problems within the design. But complete system-level verification of a complex SoC is not feasible pre-silicon, therefore in-system, at-speed silicon validation has become an essential step in the design implementation methodology. This is why assertion checker are useful and also necessary, because the common verification methods

- simulation

- emulation

- FPGA prototyping

- timing analysis

- and formal verification

will not reveal deepsubmicron problems that only occur in the actual device in the desired technology. So special corner cases and analog influences in the real system maybe stay undiscovered. Moreover, just a few minutes of real-time system operation generate more stimuli for an assertion "then it would get in weeks of simulation or days of emulation,"

thus extending the coverage and the usage of assertion for in-system validation."[2] That is because at-speed, in-system usage under stress conditions introduces many new functional patterns and explores deep states and corner cases not previously encountered, thereby exposing errors that escaped pre-silicon verification.[2]

But how can assertion statements be put on silicon? When the power of assertions is to be used in hardware, a checker generator is used to automatically produce monitoring circuits (also called assertion checkers), from the given assertion statements. The resulting assertion checker is a circuit that captures the behavior of the source assertion. At the moment there are only two established checker generators existing, MBAC[40] from the McGill University Montreal and FoCs[24] from IBM.¹ With help of a checker generator assertions can be applied beyond design and verification. Therefore, the checker generator produces permanent circuitry, e.g. HDL code that can be synthesized and incorporated into the design. This allows the observability of internal signals without requiring new pin and leads to enhanced debug functionality. For example a firing assertion could serve as a trigger to stop the recording in a trace buffer. Using this concept the designer can investigate the history of the input code.[2] These concepts of self-test, on-line silicon monitoring and diagnosis assistance can be used during the *complete lifespan* of the IC.

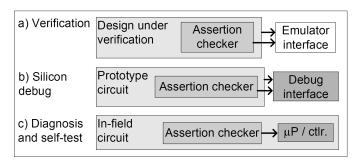

Figure 2.1: Usage scenarios for hardware assertion checkers[9]

There are three scenarios for the usage of assertion checkers (figure 2.1):

#### • Verification

The checkers are used only in the verification stage when the design is to be simulated, emulated in hardware (other technology) or executed on a simulation accelerator. Therefore, it will not be included in the final silicon.

## • Silicon Debug

The assertion checkers are used to perform post-fabrication in-circuit debugging

<sup>&</sup>lt;sup>1</sup>As per November, 2008

for prototypes. The results of the checker can only be validated using external debug hardware. The design is implemented in its intended technology, as opposed to being implemented in reprogrammable logic during hardware emulation. This allows at-speed debugging under expected operating conditions.

#### • Diagnosis and self test

The assertion checkers are incorporated in final silicon and can be queried from the system. This allows the design to assess its operating conditions inline in real time. Besides, this concept allows in-field in-chip diagnosis and self test of the design and is from big interest for harsh environments where systems need to check themselves and, in case of failure, make use of redundant parts or perform error correction.

As mentioned above incorporated checkers can test for functional faults and timing issues which can not be fully tested pre-fabrication. By connecting the checker outputs to the proper external equipment or on-board read-back circuits, the user can get immediate feedback on assertion failures in order to start the debugging process.[9]

## 2.2. Similar Approaches

Within the electronic design community several approaches are existing to either support in-silicon debug or code generation. A public available approach for model based design and code generation is SPIRIT IP-XACT. The complete standard manual can be found in [51, 52]. By now the model-based hardware flow is prototyped at various companies [35] and is being researched within the european SPRINT project.[17, 16] The underlying concept of the Infineon flow, the Essence data model, can be compared to IP-XACT.

An advanced verification approach can be found in [12]. The patented DAFCA ClearBlue technology can be seen as comprehensive approach to in-system silicon validation and debug. Using a software the user can insert reconfigurable instruments for validation. This insertion is done at RTL and the instrumented SoC is processed by standard synthesis-based design flows. The approach supports many validation paradigms such as on-chip signal capture and logic analysis, assertions, stimulate-and-capture, performance monitoring and fault and error injection. Moreover, in case of assertions they can be used in conjunction with embedded logic analyzers to aid the debugging process. For example, an assertion firing can be employed as a trigger to stop recording in the trace buffer; the recorded signals provide a window into activity preceding the malfunction detected by the assertion. [12] Despite this approach is really advanced, comprehensive and powerful, the explanations concerning the underlying generation concept are vague.

Moreover, the DAFCA technology seems to be only target at RTL implementations, whereas assertion can also be used in higher abstraction levels like TLM. Moreover, the main focus is about the checker functionality not the description of a general underlying interface. Two examples for the definition of transaction-level assertions are [22, 15]. But again the concepts are not combined with interface code generation. In general it can be stated that various approaches like [34] introduce the silicon debug assertion functionality, but do more focus on assertion checker generation. Therefore, synthesis of assertion languages is the main objective, not the modeling of an universal interface to them. In this thesis work the main focus is the template based interface generation and the modeling of the interface in an abstract, implementation-independent manner.

# 3. Infineon XChange Flow

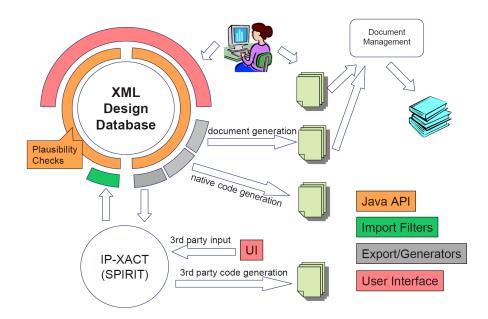

The XML-Methodology project XChange aims to provide an Infineon-wide solution for a single-source design of electronic systems. The most important goals are: [28, P. 12]

- Provision of single source design methodology for whole Infineon

- an unified and consistent data model for Infineon product design data

- Unification of Infineon code generation approaches

- I/O with the SPIRIT Consortium IP-XACT standard[52, 51] to ensure interoperability with third party IP

The proposed approach by Infineon, called Essence, is based on a meta model which can be compared to the public SPIRIT IP-XACT[6] standard. This new design flow concept has several benefits. The single source for component design data, which is reused at different design stages in different groups, allows better consistency of designs and specifications and reduces the error rate of the design process. Moreover, automated code generation reduces design effort and time as well as eases functional redesigns. The design information within the XChange flow is expressed via the Essence meta data model and represented via the use of XMI and XML. Figure 3.1 gives an overview about the database architecture concept. The Essence and IP-XACT meta models are familiar but differ in their main architecture concept. IP-XACT focus is to describe IP, however, Essence has the concept to generate IP and documentation. Moreover, Essence supports more features, but is proprietary and thus only used at Infineon Technologies. Within the Essence meta model an information will not appear twice. The redundancy within the meta model is to be minimized. This has a lot of advantages when it comes to data model consistency and effectiveness. On the contrary, it is possible that within an IP-XACT meta data description the same information appears several times. In both meta models Intellectual Property (IP) is specified and documented using meta-data. In the XChange Flow it is possible to import SPIRIT IP-XACT descriptions and convert them to the Essence meta model. The Infineon Essence meta model consists of nine UML diagrams<sup>2</sup> whereas each of them models different aspects of the overall system. The UML models provide the elements and rules to describe functionality and architecture in a very abstract and object-oriented way. Specific systems whose models are built to the Infineon meta model standard are represented via a XMI scheme inside a XML data file.

<sup>&</sup>lt;sup>2</sup>As per November 2008

Figure 3.1: Infineon XChange, based on a single-source XML-Methodology[30, P. 9]

It is important to understand the architecture and concept of the XChange flow because requirements for the SPRINT project are proved and tested with help of Essence. If the proof-of-concept is successfully the technical expertise then can be used to issue suggestions for the further development of SPIRIT IP-XACT.

#### 3.1. Fundamentals

In the following sub-chapters the fundamentals and underlying concepts of the XChange and the Essence meta model flow will be discussed. The experienced reader may skip this introductory sections and continues at chapter 3.2.

In chapter 3.1.1 the concept of meta data and meta modeling will be explained. Chapters 3.1.2 and 3.1.3 will provide additional information about the project. Chapter 3.1.4 will give a briefly overview about the <u>Unified Modeling Language</u> (UML). Moreover, chapters 3.1.6 to 3.1.8 will give an overview about the tool flow and the underlying concepts of Essence as well as the principle of code generation using templates. Because it was decided to implement a public used bus standard chapter 3.1.9 will give an overview about the AMBA bus protocol family. Moreover, chapter 3.1.10 will focus on the AMBA APB standard which was chosen to be implemented in the example system.

#### 3.1.1. Meta data and meta models

Meta data (metadata, or sometimes metainformation) is "data about data", of any sort in any media. An item of meta data may describe an individual date, or content item, or a collection of data including multiple content items and hierarchical levels, for example a database schema. This hierarchy is used in XML files (see chapter 3.1.5). In data processing, meta data is definitional data that provides (additional) information about or documentation of other data managed within an application or environment.[58]

In general a meta model sets foundations on how to build a model. This includes the definition of means of modeling as well as constraints and assertions to define the allowed expression. This definition is the core functionality of the meta model and therefore also the core part of tools. A concrete model itself is based on a meta model and build with the allowed means for modeling. Classes get instantiated and attributes get filled with real-world content. So the concrete model is the desired output of a meta model tool. For a summary please refer to table 3.1.

| Meta model                      | model                      |  |  |  |

|---------------------------------|----------------------------|--|--|--|

| foundation for a model          | based on meta model        |  |  |  |

| model on how to build a model   | model to a concrete system |  |  |  |

| definition of the means for the | modeled with defined means |  |  |  |

| modeling                        |                            |  |  |  |

| description of meta classes     | instantiation of classes   |  |  |  |

| core of the tool                | results of the tools use   |  |  |  |

Table 3.1: Differences between meta model and model [21]

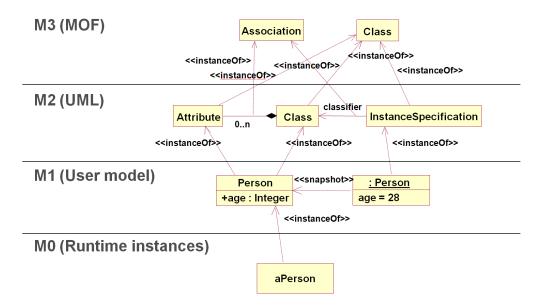

An easy example is a dictionary where the model of a language (with its defined semantic and syntax rules) is explained with the means of the same model. The <u>Object Management Group</u> (OMG) defines four layers of meta-modeling. Each level of modeling is validated by the next layer. The Level M0 is the runtime level. It contains instances of objects, for example a record. Level M1 defines the model and schema. Level M2 defines the meta model, for example the <u>Unified Modeling Language</u> (UML). The most abstract level M3 defines the meta-metamodel, a model that defines a metamodel. More abstractions are imaginable but do not lead to better strength of expression.

The Level M3 is used by the <u>Meta-Object Facility</u> (MOF), This concept is applied by XMI (see chapter 3.1.6). MOF can be considered as a standard to write meta models, for example in order to model the abstract syntax of Domain Specific Languages. For more information about MOF please refer to [44, 47]. An example for the MOF hierarchy is

Figure 3.2: Example for the MOF architecture [49]

shown in figure 3.2.

So in the Essence flow, an UML tool is used to capture the meta model as a class diagram. After this java code is generated out of the UML meta model as well as an API for filling the model with information or respectively retrieving the information. The resulting java classes build the foundations for the usage of the Essence meta model. The Java part of Essence is bound with the later explained Python scripting programming language (see chapter 3.1.7).

#### 3.1.2. **SPIRIT**

The "Structure for Packaging, Integration and Reuse IP within Tool-Flows" (SPIRIT) consortium consists of numerous semiconductor and EDA companies as well as fab-less IP creators. The objective was to develop a standard for more efficient integration of IP in System-on-Chip (SoC). To ensure consistency and efficiency on integration of third-party IP there had to be a widely adopted standard existing. Therefore, the Spirit Consortium is developing the meta model based IP-XACT specification within the IEEE P1685 SPIRIT Standardization Working Group.[51] All components of an IP library are incorporated and specified using human-legible text information in XML files which are built in accordance to a specific XML schema. The Essence meta model schema differs from IP-XACT but the general approach to group information into meta data is the

same. Meanwhile numerous companies do rely on IP-XACT, with positive results. In the next versions of IP-XACT more advanced modeling shall be supported. Some of the proposed improvements are currently prototyped in the european SPRINT project.[35]

#### 3.1.3. **SPRINT**

The SPRINT project<sup>3</sup> is funded by the European Commission's 6th Framework Program under the IST (Information Science Technology) priority which started at the 1st of February 2006.[55] The consortium is supported by the major european semiconductor companies Infineon Technologies and Philips Semiconductors (including research groups at Philips Research) as well as ST Microelectronics. Moreover, several IP Vendors are participating. Among them are ARM, Evatronix S.A. and Syosil. Also EDA vendors and universities do engage in the development. Examples are research groups at Paderborn University, TIMA[53] and the Royal Institute of Technology Sweden (KTH). The global objective is to "enable Europe to be the leader in design productivity and quality in Systemson-Chip (SoC) design, by mastering the SoC design complexity with effective standards and design technology for reuse and integration of IP".[17] Recent global standards such as SystemC/TLM and SPIRIT IP-XACT, which have been driven successfully by SPRINT partners, will be taken as starting point. [18, P. 7] Building on this existing infrastructures, the SPRINT Project will develop new methodologies and standards for interoperability and integration of the high-level IP modules from which modern SoC designs are assembled.[19]

Summarized the key SPRINT objectives are: [18]

- Techniques and standards for IP module modeling that allow the fast simulations required for architecture exploration and early software development, as well as provision of reference models in SystemC/TLM for hardware functional verification

- Definition of standard communication interfaces that simplify the integration of IP modules while also resolving Quality-of-Service (QoS) issues

- Creation of an open SoC design platform that is based upon these standards

- Development of a SoC design methodology, with matching tools and IP modules to automate SoC design, verification and debug

- To enable European companies to be the first in the world to demonstrate and subsequently exploit the new standards-based SoC design environments in an

<sup>&</sup>lt;sup>3</sup>SPRINT: Open SoC Design Platform for Reuse and Integration of IPs (IST-2004-027580)

#### 3. Infineon XChange Flow

interoperable way in order to improve on design productivity and the quality in SoC design

More information can be found on the <u>European Electronic Chips & Systems design Initiative</u> (ECSI) website.[16]

#### 3.1.4. Unified Modeling Language

The <u>Unified Modeling Language</u> (UML) is a standardized language for modeling software and other systems. It is being developed and standardized by the <u>Object Management Group</u> (OMG). UML is a very expressive language and allows in detail modeling of systems without setting constraints about a possible implementation. The information about a system is expressed with the help of several diagram types. Using these UML diagrams the relations and actions in a system can be modeled in an abstract way. To compare it to electronics design, a design can be expressed in a very high level. The different diagram types express different views on the same problem. So the complexity of a given system is reduced.

UML is based on principles of the object technology. The object technology reflects real world objects and offers elements, methods and functions to describe these objects and systems as a bunch of cooperating elements and relations between them. The basic principles of the object technology are

- classification vs. instantiation

- composition vs. decomposition

- generalization vs. specialization

- aggregation

- inheritance

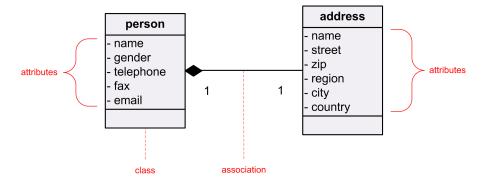

The figure 3.3 shows an example diagram. It contains two classes with their corresponding attributes. The class address stays in a "is part of" association with class person.

In general the use of UML is not restricted to modeling of software systems. Besides, all kinds of relationships between objects can be modeled due to the generous approach of UML. So for example UML can also be used to model biological, electronic (hardware) or hydraulic systems. Since electronic systems design moved towards software engineering, there is emerging interest to use UML for the hardware engineering. Different UML diagrams and their variations found their application in requirements specification,

#### 3. Infineon XChange Flow

testbenches, architectural descriptions, and behavioral modeling.[42] These descriptions are platform independent and therefore offer an ideal start for platform-specific code generation.

Figure 3.3: Example UML diagram[39]

One of the of the key strengths of UML 2.0[48] is the flexible foundation for customization and extensions of the modeling elements. In detail UML provides a meta model of the modeling elements. So different application domains can be make accessible via so-called UML profiles, which currently receives increasing tool support and give UML great potential to complement current C++-oriented languages for ESL design. In this context

- SysML [45]

- UML for SoC extension [46]

- MARTE [43]

- UML 2.0 Profile for SystemC (ST Microelectronics)

are already available as OMG profiles for Systems Engineering and SoC application and several proprietary profiles are under development. [7] Regarding model exchange between tools, the UML-related XMI (XML Metadata Interchange) format and its relationship to SPIRIT IP-XACT, the emerging IEEE standard, are of additional particular interest. Partial overlaps can be identified and are currently under investigations by some projects, like SPRINT.

Within the Essence flow mainly UML class diagrams are used to define the meta model. For an in detail view about all UML diagram types please refer to [37, 56]. For a comprehensive overview about the usage of UML for electronic system design please refer to [63].

#### 3.1.5. Extensible Markup Language

The  $E\underline{x}$ tensible  $\underline{M}$ arkup  $\underline{L}$ anguage (XML) is a human-legible specification for creation of custom markup languages. A markup language is an artificial language using a set of annotations to text that give instructions regarding the structure of text or how it is to be displayed.[61] Thus, data is structured in a hierarchical way. XML was developed by the  $\underline{W}$ orld  $\underline{W}$ ide  $\underline{W}$ eb  $\underline{C}$ onsortium (W3C) and allows the specification of custom languages using XML-schemata. A XML-schema sets semantic constraints, like specifying the hierarchical structure and the allowed content in fields. This benefited the existence of many custom XML languages for information interchange based on meta-date, for example HTML. With help of tools it is possible to check if a XML file complies to a given schema.

#### Algorithm 3.1 Example for a well-formed XML

```

<?xml version="1.0" encoding="ISO-8859-1" standalone="yes"?>

1

2

<thesis>

3

<title>example_thesis</titel>

<content>

4

5

<focus>

<name>Engineering</name>

6

7

<picture>verification_gap</picture>

8

</focus>

9

<focus>

<name>Related_work</name>

10

<picture>IEEE</picture>

11

12

</focus>

13

</content>

14

</ thesis>

```

A XML file is called well-formed if it fulfills all XML rules. The most important rules are

- one element, the root node, contains all other elements; there is only one root node

- all elements have a begin and end markup

- one element must not have several attributes with identical name

The example shown in algorithm 3.1 is well-formed.

#### 3.1.6. XML Metadata Interchange

The  $\underline{X}ML$   $\underline{M}$  etadata  $\underline{I}$ nterchange (XMI) is an OMG standard for exchanging metadata information via XML.[47, 62] It can be used for any metadata whose meta model can

#### 3. Infineon XChange Flow

be expressed in <u>Meta-Object Facility</u> (MOF). The most common use of XMI is as an interchange format for UML models, although it can also be used for serialization of models of other languages (metamodels).

XMI integrates four industry standards:

- XML eXtensible Markup Language, a W3C standard.

- UML Unified Modeling Language

- MOF Meta Object Facility, an OMG language for specifying metamodels

- MOF Mapping to XMI

The integration of these four standards into XMI allows tool developers of distributed systems to share object models and other metadata. The XMI source code in listing 3.2 corresponds to the class address of the example UML diagram in figure 3.3 on page 16. It is easy to see the even a simple and small "piece of UML" results in many lines of XML syntax with XMI.

### Algorithm 3.2 XMI description of the address UML class (figure 3.3)[39]

```

<?xml version="1.0"?>

<XMI xmi.version="1.2" xmlns:UML="org.omg/UML/1.4">

3

<XMI.header>

<XMI.metamodel xmi.name="UML" xmi.version="1.4"/>

4

5

</XMI.header>

6

7

<UML:Model xmi.id="M.1" name="address" visibility="public"</pre>

isSpecification="false" isRoot="false" isLeaf="false" isAbstract="false">

8

9

<UML:Namespace.ownedElement>

<UML:Class xmi.id="C.1" name="address" visibility="public"</pre>

10

isSpecification="false" namespace="M.1" isRoot="true" isLeaf="true"

11

12

isAbstract="false" isActive="false">

13

<UML:Classifier.feature>

<UML:Attribute xmi.id="A.1" name="name" visibility="private"</pre>

14

15

isSpecification="false" ownerScope="instance"/>

<UML:Attribute xmi.id="A.2" name="street" visibility="private"</pre>

16

isSpecification="false" ownerScope="instance"/>

17

<UML:Attribute xmi.id="A.3" name="zip" visibility="private"</pre>

18

isSpecification="false" ownerScope="instance"/>

19

<UML:Attribute xmi.id="A.4" name="region" visibility="private"</pre>

20

isSpecification="false" ownerScope="instance"/>

21

22

<UML:Attribute xmi.id="A.5" name="city" visibility="private"</pre>

isSpecification="false" ownerScope="instance"/>

23

<UML:Attribute xmi.id="A.6" name="country" visibility="private"</pre>

24

25

isSpecification="false" ownerScope="instance"/>

26

</UML:Classifier.feature>

27

</UML:Class>

28

</UML:Namespace.ownedElement>

29

</UML:Model>

30

</XMI.content>

31

</XMI>

```

#### 3.1.7. Python

Python is a general-purpose, high-level programming language which was intended to be highly readable. It aims toward an uncluttered visual layout for example its use of whitespace as block delimiters is unusual among popular programming languages. This design philosophy emphasizes programmer productivity and code readability.[60] Python's core syntax and semantics are minimalistic, while the standard library is large and comprehensive. This large standard library, one of Python's greatest strengths, providing pre-written tools suited to many tasks. Python allows binding and can be a powerful glue language between other programming languages and tools. Algorithm example 3.3 shows the typical whitespace indentation, rather than curly braces or keywords, to delimit statement blocks. An increase in indentation comes after certain statements; a decrease in indentation signifies the end of the current block.

#### Algorithm 3.3 Example for Python Code

```

# Including functions of library sys

1

import sys

3

4

# definition of a function

5

def run_code():

6

print "Example_Code"

7

# Example for Indentation

8

9

arg = len(sys.argv)

if arg == 1:

10

11

print sys.argv[0]

12

else:

13

for i in len(sys.argv):

14

print sys.argv [i-1]

15

if sys.platform.lower() == "win32":

16

17

run_code()

18

else:

19

pass

20

21

sys.exit(0)

```

Python allows to split programs into modules that can be reused in other Python programs. Furthermore, Python is an interpreted language, which can save considerable amount of time during code development because no compilation and linking is necessary. This allows the Python programs to be always read-able and platform independent. The interpreter can be used interactively, which makes it easy to experiment with features of the language, to write throw-away programs, or to test functions during bottom-up

program development.

Python has numerous advantages in comparison to other high-level languages like C++.[36]

- clean syntax due to indentation concept, no variable or argument declarations are necessary

- less coding necessary due to high level data types that allow to express complex operations in a single statement

- object-oriented programming

- support for scientific computing (for example numeric)

- binding to other programming languages, C++, Java well supported

One of the most important modules to ease usage of Essence is GNOSIS.[13] It contains several Python modules for XML processing, plus other generally useful tools. An example is xml.objectify which turns arbitrary XML documents into Python objects. So the objects of the Essence meta model that are expressed via a XML schema can be handled the same way like objects from the Essence java class (through Java binding). With help of these two concepts an universal flow of IP is possible. First IP can be captured using the meta model and exported as XML file. Later on the same source can be read in using templates which make use of the GNOSIS module.[31, P. 11]

### 3.1.8. Templating with MAKO

Mako is a template library written in Python which provides a familiar non-XML syntax. For maximum performance MAKO compiles into Python modules. The syntax and API borrows from the best ideas of many other template engines, including Django templates, Cheetah, Myghty, and Genshi.[5]

In the concept of templating a template engine combines one ore more templates with a data model. The template consists of placeholders where information from the data model can be inserted. Moreover, its possible to have more advanced templates. For example, the template can further contain Mako-specific directives which represent variable and/or expression substitutions, control structures (i.e. conditionals and loops), server-side comments, full blocks of Python code, as well as various tags that offer additional functionality. All of these constructs compile into real Python code. This means that you can leverage the full of power of Python in almost every aspect of a Mako

#### 3. Infineon XChange Flow

template. Therefore, the kind output (Text, HDL-Code, HTML, XML etc.) depends on the template itself. The usage of a template engine has benefits:

- enhances productivity by reducing unnecessary reproduction of effort

- enhances teamwork by allowing separation of work (sub-templates)

Conceptually, MAKO is an embedded Python (i.e. Python Server Page) language. This allows the developer to make use of a template engine and Python at the same time.

In the implementation stage of this thesis work the code-generation templates were all written in MAKO. Therefore, its necessary to have fundamental knowledge about syntax and semantics of the language. For a complete reference please refer to the MAKO Documentation.[5]

## **Syntax**

The simplest expression is just a variable substitution using the \${}} construct. In order to work, x has to be known before the substitution. For instance it can be derived from the data model first. Within the substitution all of the functionality provided by Python can be used. Algorithm 3.4 illustrates an easy example.

# Algorithm 3.4 Simple Text substitution using MAKO template

The python function pow(x,y) returns x to the power of y. The algorithm 3.5 shows the generated "code" of the template in the case of x = 10 and y = 5.

# Algorithm 3.5 Output of algorithm for x=10, y=5

```

1 the value of x: 10

2 pythagorean theorem: 125

```

Furthermore, the MAKO template language allows the use of control structures and inline python blocks. So the code-generation process can be done in a very flexible way and with help of the comprehensive functions of Python. Algorithm 3.6 shows an example. In contrast to Python where comments are indicated using a single # character, MAKO

comments are specified using two ## characters. Inline Python blocks start with the <% and end with the %> marker. MAKO control structures are identified using the % marker. A noticeable difference between the Python coding style and the MAKO coding style is that indentation is only necessary for Python. In MAKO its not a must and sometimes unrequested. The reason is that every space or tabulator inside the template will also appear in the output, because all content of the input file that is not prefixed with markers or is commented will just appear in the output file. This impedes the generation of output code where positions of the output do matter. Moreover, it makes this kind of MAKO templates harder to read, because there is no indentation used. Fortunately recent design entry tools, in the easiest case text editors, support the developer with hierarchy folding and therefore significant ease template development.

# Algorithm 3.6 MAKO Control structures

```

## the next line will appear as it is in the output

2

this is a template

3

4

<%

5

# This is a Python block which calls a somewhere

6

# else defined function that returns a list

7

8

x = get_x_list_fct()

9

%>

10

\% if len(x) > 1:

11

12

% for elem in x:

13

element: ${elem}

14

% endfor

15

\% else:

only one element \{x\}

16

17

% endif

```

A template can be composed of sub-functions and sub-templates. Inside the template a function is declared using the <%def> and </def%> markers. It exists within generated Python as a callable function.

# Algorithm 3.7 MAKO def statement

#### 3.1.9. AMBA Overview

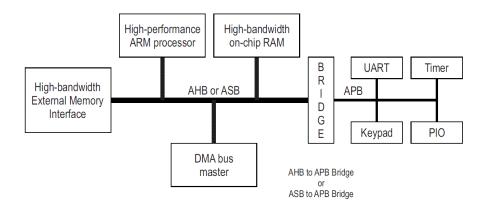

The <u>Advanced Microprocessor Bus Architecture</u> (AMBA) is a widely used open standard for an on-chip bus system which is defined by ARM Limited. The AMBA standard was introduced in 1996 and aims to ease the component design, by allowing the combination of interchangeable components in the SoC design. It promotes the reuse of intellectual property components and is the de-facto standard for 32-bit embedded processors because it is well documented and can be used without royalties.[57, 23] Therefore, many third party IP providers use an AMBA bus for interfacing to their IP. Within the SPINNI System it shall be possible to include these IPs, assumed an Essence (or at least IP-XACT) description is existent. The AMBA standard defines different groups of buses

- Advanced eXtensible Interface (AXI)

all from below plus more abstract, channels etc.

- Advanced High-performance Bus (AHB) high performance, pipelined transfers, burst transfer, split transfers, multiple bus master, bus arbiter

- Advanced System Bus (ASB) multiple bus masters, high performance

- Advanced Peripheral Bus (APB)

one bus master, simple interface, limited functionality, designed for low power

which are typically used in a hierarchical fashion. The figure 3.4 shows an example. The AXI standard is the most powerful bus with elaborated functions. The APB is the most basic bus for peripheral components that do not require massive data throughput. The AMBA specification is technology independent. So physical implementation details like voltage levels are not dictated by the specifications. In fact, it gives an overview about the architecture, the signal count, their names, transfer timing diagrams as well as basic state machines.

For the proof-of-concept work both APB and AHB shall be bridged within the SPINNI system. But the functionality of the AHB shall be reduced significantly. First of all some concepts of the AHB, like pipelined transfers and multi-master, are not meaningful within the SPINNI system because then the peripheral bus would be much more powerful than the central system bus, called SimpleBus. The SPINNI Example system is described in chapter 4. So as long as the SimpleBus is a "functionality bottleneck" inside the SPINNI system the AHB bridge shall have the same functionality as the APB bridge. The AHB

Figure 3.4: A typical AMBA enabled system[38]

components are very similar to the APB ones, but differ in the used interface definition. Therefore, the signal names will differ. For this reasons only the APB protocol will be explained in detail.

#### 3.1.10. AMBA APB

The APB is part of the AMBA 3 protocol family and is optimized for minimal power consumption and reduced interface complexity. The APB has an unpipelined protocol where every transfer takes at least two clock cycles. Furthermore, transfers can be extended via low on the PREADY signal. All signal transitions are only related to the rising edge of the clock to enable the integration of APB peripherals easily into any design flow.[38]

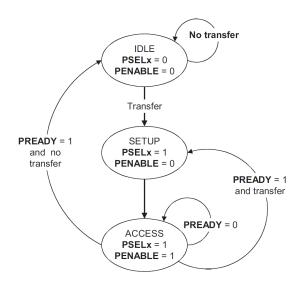

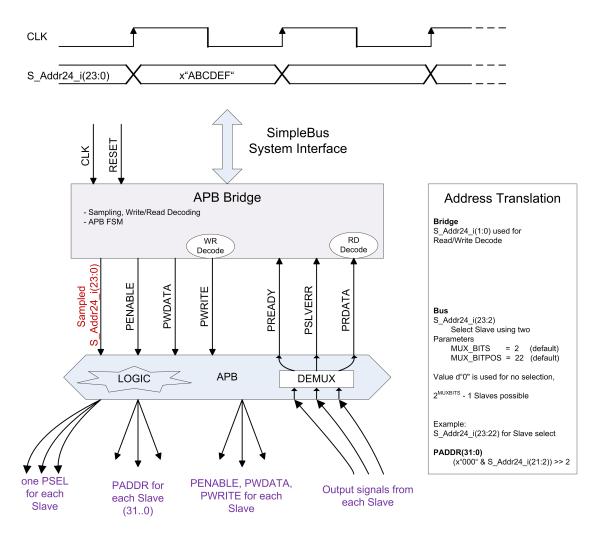

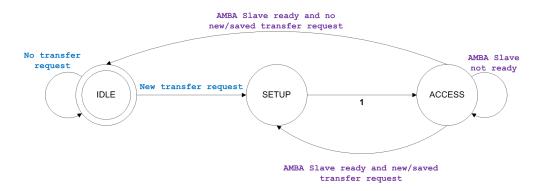

The figure 3.5 shows the state diagram of the operating states of the AMBA APB protocol. If no transfer is requested the FSM remains in the IDLE state. The bus slave select signal PSELx stays low. Therefore, no slave is selected. The signal is named PSELx to indicate that there are actually several select signals, one for every APB slave. If there is a transfer requested the FSM changes the state from IDLE to SETUP. The select signal of the desired APB slave will get HIGH. The AMBA APB specification gives no proposal how this slave is determined. In the SPINNI Example System several bits of the address signal are used for an address decoder.

In the second cycle the FSM will always move to the ACCESS state. The enable strobe signal PENABLE will get HIGH. Moreover, the address, write, select and write data signals must remain stable during the transition to the ACCESS state.

Figure 3.5: APB Bus Transaction State diagram[38]

Now the data to be written is read on the selected slave or in the other case, the to read data is put on the bus by the selected slave. If the two cycle flow of the APB can be met, the PREADY signal will be HIGH. If the data phase takes more than one cycle the PREADY signal will stay LOW. When the transfer is completed the next action depends if there is a new transfer request. If so, the FSM will go directly to the SETUP state and save one cycle. If not it will go to the IDLE state again. In order to reduce power consumption the address signal and the write signal will not change after a transfer until the next access occurs.[38, P. 5-5]

More information about the APB protocol, for example timing diagrams for read or write transfers, can be found in the AMBA APB specification.[38] In chapter 4.2 a SimpleBus-to-APB bridge will be implemented for the SPINNI Example System.

### 3.2. The Essence Meta Model

In the following the Essence data models will be briefly described. Despite the additional SPINNI system enhancements are expressed by means of the core Essence data models, the additional ModelConfig data model (see figure A.1 on page 85) is the most important one for this thesis work. Therefore, the explanations will not focus in the other data model but will still try to give an overview about the architecture. The Essence data model is intellectual property of Infineon Technologies. Therefore, the core data models are not shown within the thesis or appendix.

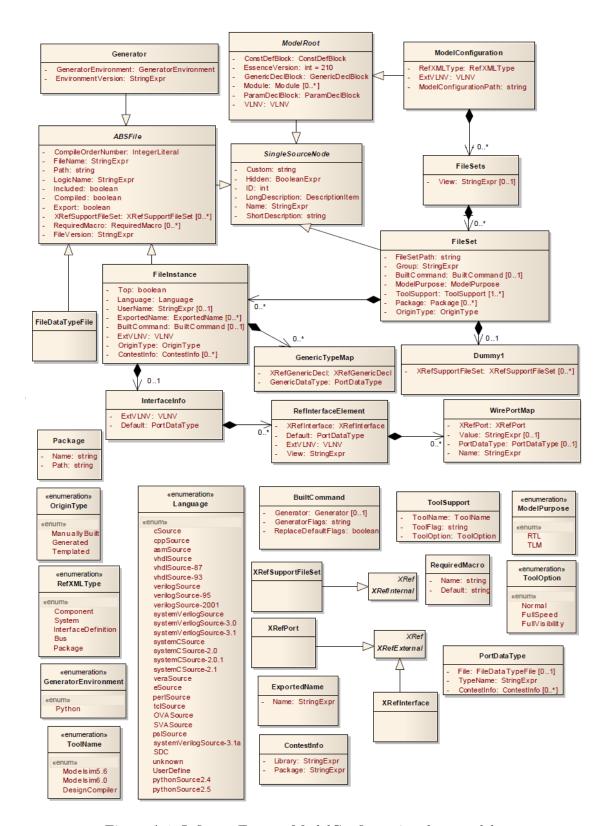

The Essence Meta Model contains nine basic model types. All of these models make usage of the principles of the object technology. So inheritance and composition are widely used. If an object is inherited from an existing one, it inherits all attributes and methods from the existing one. Apart from that, it can contain additional attributes and methods. This concept is called specialism. In nearly every Essence model all objects inherit attributes from the class SingleSourceNode. This class provides basic attributes like Identifier, Name, Description. The ID is of particular interest, because each element within a single Essence model XML file representation has an unique ID. These basic attributes will then be inherited to derived classes. The composition is a part-whole relation. In a graphical UML notation the rhomb points to the whole, the opposite side to the part. The existence of the part objects depends on the existence of the whole objects. In Essence the method of composition is used to declare which elements can contain one-to-many other elements. For instance in the UML example in figure 3.3 on page 16 a person has exactly one address. So the resulting XML structure of the datamodel is declared implicit. The meta model itself was designed and modeled with help of Enterprise Architect[50], an UML tool capable of generating Java source code. The documentation for the Essence meta model is also generated automatically. It is derived directly from the Java source code with help of javadoc. Javadoc is a documentation generator from Sun Microsystems for generating API documentation in HTML format. The work of this thesis is especially related to the ModelConfig data model because the functionality of the debuggable assertion interface was incorporated into it.

#### 3.2.1. Component Data Model

Components are the only design elements that can contain collections of registers or memories. These internal structures can be modeled in a very detailed manner. Therefore, Component Data Model XMLs are often very large. Moreover, Components can have several Interfaces.[26] For each Interface the Role, i.e. Master or Slave, is specified. The properties of the Interface are modeled in the Interface Definition data model. With help of the Role information a code generator then can determine what ports to generate.

### 3.2.2. Interface Definition Data Model

The <u>Interface Definition</u> (IFD) data model defines the interface of a component/system. So a component XML and the interface definition XML are in close relation to each other. Using an IFD it is possible to declare interface protocols once, and reuse them

later in other components. This strategy speeds up design and makes coding less errorprone. Moreover, the interface can be modeled as seen from different views/abstractions

called, InterfaceDefView. Examples are RTL and TLM level. In TLM the protocol

is described very abstract via function calls and not via physical signals. Within the

InterfaceDefView all signals of the interface. e.g. the protocol are specified. Each signal

has a Name, DataType and unique ID. Protocols often have Master and Slave Roles. This

information is specified in the InterfaceDefRole. For each Role, for example Master,

the used signals of the protocol, and their directions are specified. With all these model

elements it is possible to express very complex and different protocols within the Essence

meta model. The references to elements in the data model and the relation between

different data models are expressed via the XRef data model which will be declared next.

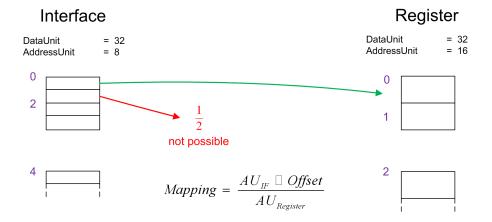

In the implementation stage of this thesis work the proof-of-concept system was modeled in the RTL level, because VHDL code-generation was projected. The figure 4.5 on page 41 illustrates the architecture of a resulting example InterfaceDefinition XML file.

#### 3.2.3. XRef Data Model

The XRef data model contains all references from one element to other ones. The target identifier for a reference is always the ID. Note that the IDs are only unique per XML file. For each XRef there is a corresponding ExtVLNV field in the superior hierarchy. Therefore, a references needs a pair of ExtVLNV and XRef. An example can be seen within the ModelConfig data model on figure A.1 on page 85 and in the developed assertion interface model illustrated in figure 5.3 on page 51. So using the ExtVLNV the corresponding XML file can be determined and opened. The next step would be to search for the declared ID within that file. Fortunately, there are several convenience functions, like getXRefTarget(), available withing the Essence API that ease the reference retrieval. The data mode itself offers varies types of references. Examples are XRefSlaveInterface, XRefInterfacePort or XRefSignal. VLNV has the meaning of Vendor, Library, Name, Version and can be seen as the identifier of the XML file. An Essence XML file must be named like the VLNV of the RootNode.

For example, the XRef data model is used for assigning signals to an interface definition. Moreover, it is also of use within an abstract assertion interface data model to associate signals to an assertion.

#### 3.2.4. Bus Data Model

The bus data model only consists of a SingleSourceNode and ModelRoot pair as well as the object Bus. Using attributes of the object Bus the minimum and maximum participants of the to be designed bus can be specified. With use of the ExtVLNV field this model points to an external Interface Definition that declares all types of signals and ports of that bus.

Within a system, such a bus component can be instantiated and other elements can be connected to it.

# 3.2.5. System Data Model

The system data model is properly the most complex essence data model. It is the only model that allows instances of other data models to be instantiated and connected. [26] Consequently within the system, there can be instances of components, buses and subsystems whose interfaces are might connected. So an Essence system data model can be compared to a VHDL top level entity, in which VHDL entities get instantiated and wired. Furthermore, the system can have Interfaces too. Using the LocalInterfaceMap the System's interfaces can be mapped to internal instances of objects using the Connection. A connection is a 1-to-1 mapping relation. For example the clk port of a system interface can be mapped to a component instances interface that is instantiated within the system.

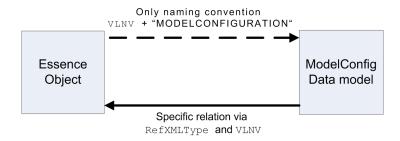

### 3.2.6. ModelConfig Data model

The Essence data model holds on implementation independent information. However, it is also necessary to provide implementation and flow data as meta data as well. Therefore, the XChange Flow has an additional data model called ModelConfiguration. The figure A.1 on page 85 shows the data model architecture. Its purpose is to store all language dependent and flow specific information. For example special tool flows (the generator environment) and batch command flows that are necessary for a generation can be put into that model. Other examples are language dependent port types like std\_logic and bit\_vector for VHDL respectively. Despite not being language dependent the AssertionInterface model shall also be included in the ModelConfiguration data model because at the moment it is the only allowed place to add extensions to the Essence data model.<sup>4</sup> The ModelConfiguration model is not mandatory for an Essence

<sup>&</sup>lt;sup>4</sup>As per November 2008