# Entwurfsregeln für Supraleitende Analog-Digital-Wandler

# Dissertation zur Erlangung des akademischen Grades Doktoringenieur (Dr.-Ing.)

vorgelegt der Fakultät für Elektrotechnik und Informationstechnik der Technischen Universität Ilmenau

von

Dipl.-Ing. Taghrid Haddad

geboren am 26.02.1977 in Latakia

vorgelegt am: 05.12.2014

Gutachter: 1. Univ.-Prof. Dr.-Ing. habil. Hannes Töpfer (TU Ilmenau)

2. Prof. Dr.-Ing. habil. Ute Diemar (FH Furtwangen)

3. Prof. Dr.-Ing. habil. Thomas Ortlepp (CiS Erfurt)

Verteidigung am: 29.05.2015

URN:urn:nbn:de:gbv:ilm1-2015000190

# Inhaltsverzeichnis

| K | urzfa | ssung   |                                                                    | III |

|---|-------|---------|--------------------------------------------------------------------|-----|

| D | anks  | agung   |                                                                    | VII |

| 1 | Ein   | leitung | 5                                                                  | 1   |

| 2 | Gru   | ındlage | e <b>n</b>                                                         | 5   |

|   | 2.1   | Grund   | llagen der supraleitenden Elektronik                               | 5   |

|   |       | 2.1.1   | Josephson-Effekt                                                   | 6   |

|   |       | 2.1.2   | RCSJ-Modell des Josephson-Kontaktes                                | 7   |

|   |       | 2.1.3   | Charakteristische Parameter eines realen Josephson-Kontaktes       | 8   |

|   |       | 2.1.4   | Flussquantisierung in supraleitender Schleife                      | 10  |

|   |       | 2.1.5   | Grundstrukturen supraleitender Elektronik                          | 10  |

|   |       | 2.1.6   | Eingangsinterface-Wandler                                          | 12  |

|   | 2.2   | Grund   | llagen der AD-Wandler                                              | 14  |

|   |       | 2.2.1   | Parallelverfahren                                                  | 15  |

|   |       | 2.2.2   | Wägeverfahren                                                      | 17  |

|   |       | 2.2.3   | Zählverfahren (Serielle AD-Wandler)                                | 19  |

|   |       | 2.2.4   | Kenngrößen der AD-Wandler                                          | 21  |

|   |       | 2.2.5   | Stand der Technik                                                  | 27  |

| 3 | Kor   | nparat  | oren in der supraleitenden Elektronik                              | 31  |

|   | 3.1   | Grund   | llagen von Komparatoren                                            | 31  |

|   | 3.2   | Joseph  | nson-Komparator                                                    | 32  |

|   |       | 3.2.1   | Die Schaltung des Josephson-Komparators                            | 32  |

|   |       | 3.2.2   | Die Grauzone als Kenngröße des Josephson-Komparators $\ .\ .\ .$ . | 35  |

|   |       | 3.2.3   | Einflussgrößen auf das Verhalten des Josephson-Komparators         | 37  |

|   |       | 3 2 4   | Praktische Relevanz                                                | 45  |

II Inhaltsverzeichnis

|              |                             | 3.2.5 Experimentelle Analyse der Abhängigkeit zwischen dem Biasstrom       |       |  |  |  |

|--------------|-----------------------------|----------------------------------------------------------------------------|-------|--|--|--|

|              |                             | und der Empfindlichkeit eines Josephson-Komparators                        | 50    |  |  |  |

|              |                             | 3.2.6 Entwurfsregeln für Komparatoren                                      | 57    |  |  |  |

|              | 3.3                         | Quasi-One-Junction-SQUID-Komparator                                        | 58    |  |  |  |

|              |                             | 3.3.1 Elektrisches Ersatzschaltbild des QOJS-Komparators                   | 58    |  |  |  |

|              |                             | 3.3.2 Kenngrößen des QOJS-Komparators                                      | 60    |  |  |  |

|              |                             | 3.3.3 Einflussgrößen auf das Verhalten des QOJS-Komparators                | 63    |  |  |  |

|              | 3.4                         | Experimentelle Ergebnisse                                                  | 68    |  |  |  |

| 4            | Sup                         | oraleitender Analog-Digital-Wandler nach dem Prinzip des Zählver-          |       |  |  |  |

|              | fahr                        | rens                                                                       | 71    |  |  |  |

|              | 4.1                         | Konstruktion eines supraleitenden $\Sigma - \Delta$ -AD-Wandlers           | 71    |  |  |  |

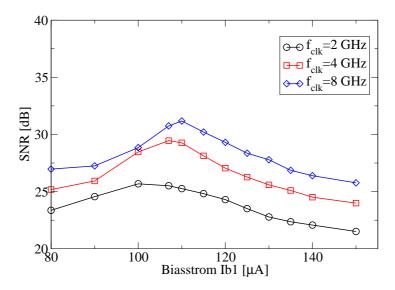

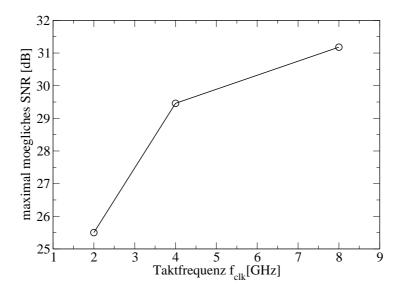

|              | 4.2                         | Einfluss der Taktfrequenz                                                  | 74    |  |  |  |

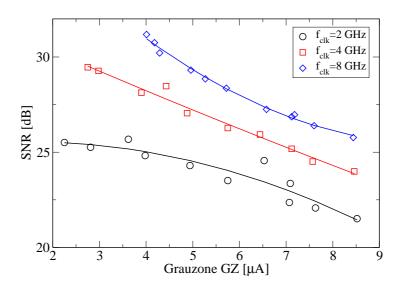

|              | 4.3                         | Einfluss der Grauzone                                                      | 76    |  |  |  |

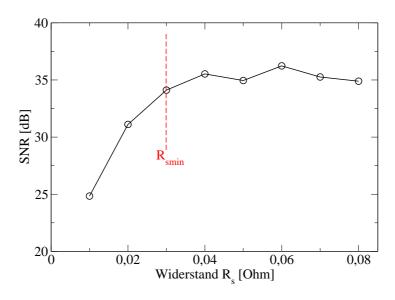

|              | 4.4                         | Einfluss des Integrators                                                   | 77    |  |  |  |

|              |                             | 4.4.1 Einfluss des Widerstandes                                            | 77    |  |  |  |

|              |                             | 4.4.2 Einfluss der Induktivität des Integrators beim konstanten Widerstand |       |  |  |  |

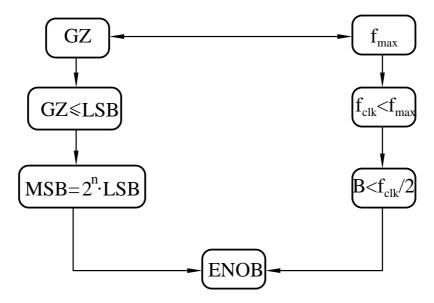

|              | 4.5                         | Entwurfsregeln für $\Sigma - \Delta$ -AD-Wandler                           | 79    |  |  |  |

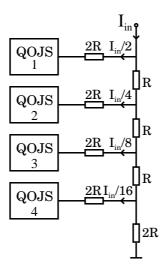

| 5            | Sup                         | oraleitender Flash-Analog-Digital-Wandler                                  | 83    |  |  |  |

|              | 5.1                         | QOJS-Komparator mit Ausgangserweiterung                                    | 83    |  |  |  |

|              |                             | 5.1.1 Josephson-Komparator mit periodischer Kennlinie (QOJS-Komparato      | r) 83 |  |  |  |

|              |                             | 5.1.2 Die robustere Version des 1bit-QOJS-Komparators                      | 85    |  |  |  |

|              | 5.2                         | Vor- und Nachteile des QOJS-Komparators im Vergleich zum Josephson-        |       |  |  |  |

|              |                             | Komparator                                                                 | 88    |  |  |  |

|              | 5.3                         | Aufbau eines supraleitenden 4-bit Flash-AD-Wandlers mit QOJS-Komparator    |       |  |  |  |

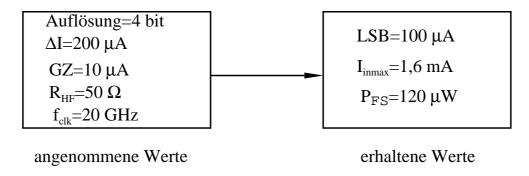

|              |                             | en                                                                         | 88    |  |  |  |

|              | 5.4                         | Simulationsergebnisse zum supraleitenden 4-bit Flash-AD-Wandler            | 90    |  |  |  |

|              | 5.5                         | Entwurfsregeln für einen supraleitenden Flash-AD-Wandler                   | 92    |  |  |  |

| 6            | Zus                         | ammenfassung                                                               | 97    |  |  |  |

| Li           | Literaturverzeichnis 99     |                                                                            |       |  |  |  |

| $\mathbf{T}$ | Thesen zur Dissertation 112 |                                                                            |       |  |  |  |

| Εı           | rklär                       | ung 1                                                                      | 113   |  |  |  |

# Kurzfassung

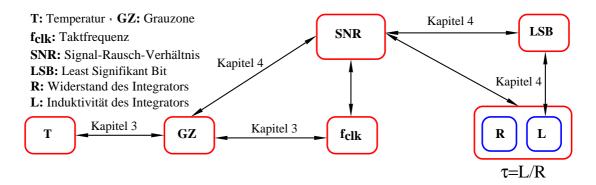

Die vorliegende Dissertationsschrift liefert einen Beitrag zu Dimensionierungsaspekten des Schaltungsentwurfs in der supraleitender Elektronik. Dazu werden supraleitende Komparatoren, d. h. Josephson-Komparator und QOJS-Komparator bezüglich der Geschwindigkeit und der Empfindlichkeit untersucht. Der Einfluss des thermischen Rauschens auf den Entscheidungsprozess der Komparatoren repräsentiert die so genannte Grauzone. Sie wird in der Arbeit als wichtige Kennzahl ausführlich analysiert. Daraus werden verschiedene Parameterabhängigkeiten dargestellt. Eine Modellierung eines Josephson-Komparator wurde experimentell bestätigt.

Darauf aufbauend werden Konzepte von supraleitenden Analog-Digital-Wandlern in der Arbeit untersucht und daraus Entwurfsregeln abgeleitet. Durch die Reduzierung der Schaltenegie wird das Signal-Rausch-Verhältnis (SNR) der Schaltungen und damit die Zuverlässigkeit von Entscheidungsprozessen und Schaltvorgängen beeinflusst. Für Spezialanwendungen mit sehr hohen Anforderungen bezüglich der Geschwindigkeit oder Genauigkeit bieten supraleitende AD-Wandler ausgezeichnete Leistungsmerkmale an. Die Arbeit liefert konkrete Zusammenhänge zwischen den unterschiedlichen Entwurfsparametern und zeigt mögliche Kompromisse auf. Die Methoden sind transparent dargestellt und lassen sich leicht auf andere Schaltungstopologien übertragen. Im Ergebnis wird ein Werkzeug zur objektiven Dimensionierung von supraleitenden AD-Wandlern bereitgestellt.

## Abstract

This Thesis is a contribution for dimensioning aspects of circuits designs in superconductor electronics. Mainly superconductor comparators inclusive Josephson comparators as well as QOJS-Comparators are investigated. Both types were investigated in terms of speed and sensitivity. The influence of the thermal noise on the decision process of the comparators represent in so called gray zone, which is analysed in this thesis. Thereby, different relations between design parameters were derived. A circuit model of the Josephson comparator was verified by experiments.

Concepts of superconductor analog-to-digital converters, which are based on above called comparators, were investigated in detail. From the comparator design rules, new rules for AD-converters were derived. Because of the reduced switching energy, the signal to noise ratio (SNR) of the circuits is affected and therefore the reliability of the decision-process is affected. For special applications with very demanding requirements in terms of the speed and accuracy superconductor analog-to-digital converters offer an excellent performance. This thesis provides relations between different design parameters and shows resulting trade-offs, This method is transparent and easy to transfer to other circuit topologies. As a main result, a highly predictive tool for dimensioning of superconducing ADC's is proved.

# Danksagung

Die vorliegende Arbeit entstand während meiner Tätigkeit als Promotionsstudentin am Fachgebiet Theoretische Elektrotechnik und als wissenschaftliche Mitarbeiterin am Fachgebiet Grundlagen der Elektrotechnik der Technischen Universität Ilmenau.

Hiermit möchte ich mich bei allen bedanken, die zur Entstehung dieser Arbeit beigetragen haben.

Besonderer Dank gilt Univ.-Prof. Dr.-Ing. habil. Hannes Töpfer sowohl für seine Betreuung meiner Arbeit und fachliche Unterstützung während der gesamten Zeit als auch für die Begutachtung dieser Arbeit.

Ganz besonders herzlich möchte ich mich bei Priv.-Doz. Dr.-Ing. habil. Thomas Ortlepp bedanken. Mit vielen Ideen, Lösungsansätze und fruchtbaren Diskussionen hat er zum Gelingen dieser Arbeit beigetragen. Bei ihm möchte ich mich auch herzlich für die Begutachtung meiner Arbeit bedanken.

Ebenfalls bedanken möchte ich mich bei Prof. Dr.-Ing. habil. Ute Diemar für die Anfertigung ihres Gutachtens.

Herzlicher Dank gilt auch meinem ehemaligen Kollegen Dr.-Ing. Olaf Wetzstein sowohl für seine Ideen und fachliche Unterstützung als auch für seine hilfreichen Hinweise bei der Ausarbeitung dieser Arbeit. Für seine moralische Unterstützung danke ich ihm auch sehr.

Ebenfalls möchte ich bei meiner ehemaligen Kollegin Dipl.-Math. Sonja Engert herzlich bedanken für ihre hifreichen Kommentare und Hinweise bei der Ausarbeitung des Manuskripts sowie für ihre moralische Unterstützung.

Meiner ehemaligen Kollegin Dr.-Ing. Imke Haverkamp gilt auch mein herzlicher Dank für ihre moralische Unterstützung.

Ich möchte mich auch ganz herzlich bei meinem ehemaligen Kollegen Dr.-Ing. Björn Ebert für die Zusammenarbeit und angenehme gemeinsame Zeit bedanken.

Besonderer Dank gilt auch meinen Kollegen aus der "Kaffeerunde" Dr.-Ing. Stefan Humbla, Dipl.-Ing. Jens Jebramcik, Dipl.-Ing. Gabor Vogt. Sie haben mich mit hilfreichen

VIII Danksagung

Diskussionen fachlich und moralisch unterstützt. Insbesondere danke ich Dipl.-Ing. Jens Jebramcik für seine Hilfe beim Schwimmenlernen, was mir sehr gut geholfen hat, den Arbeitsalltag auch mal zu vergessen.

Ganz herzlich möchte ich mich bei Dipl.-Ing. Carola Ebert und Dr.-Ing. Valentin Nakov für ihre hilfreichen Kommentare und Hinweise beim Durchlesen des Textes bedanken.

Bei Dipl.-Ing. Oliver Brandel möchte ich mich herzlich für seine Hinweise zum Text bedanken.

Bei meinem Kumpel Wared Mualla bedanke ich mich herzlich für die hilfreiche Diskussion in MATLAB.

Auch möchte ich mich bei allen meinen Kollegen im Fachgebiet Grundlagen der Elektrotechnik ganz herzlich für ihre Unterstützung bedanken.

Bei meinen Kollegen Dipl.-Ing. Christian Drebenstedt bedanke ich mich ganz herzlich für seine Unterstützung.

Zuletzt möchte ich mich ganz herzlich und ganz besonders bei meinen Eltern und meinen Geschwistern für ihre ständige Unterstützung bedanken. An dieser Stelle bin ich meiner jüngsten Schwester Boushra zu tiefstem Dank verpflichtet, denn sie hat mir immer beigestanden und mit ihrer ständigen und herzlichen Unterstützung hat sie mich aufgemuntert alle Anstrengungen zu meistern.

# Kapitel 1

# Einleitung

Die Informations- und Kommunikationstechnik spielt eine große Rolle in unserem heutigen Leben. Die Nutzung aller Informationsmedien wie z. B. Radio, Telefon, Fernseher, Internet, Mobiltelefon, Smartphone, Cloud, etc. wächst immer schneller an. Der maximale Datenverkehr im größten kommerziellen Internetknoten ist in den letzten 5 Jahren auf 3 Tbit/s angestiegen [1]. Neben diesem riesigen Übertragungsbedarf wächst auch die Anforderung an die Informationsverarbeitung ständig. Da heute alle Daten in digitaler Form übertragen und verarbeitet werden, benötigt man für nahezu alle Signale zunächst eine Umwandlung der analogen Signale in digitale Daten.

In unserer heutigen Zeit ist das Thema "Energieverbrauch" ein wichtiges Kriterium für den Entwurf der elektronischen Schaltungen, besonders im Bereich der Mobilkommunikation. Weltweit beschäftigen sich Wissenschaftler mit der Entwicklung von energieeffizienten Hochleistungscomputern [2, 3]. In D.S. Holmes et. al. [2] wurden Konzepte für Computersysteme untersucht, die eine Leistungsfähigkeit von 1 bis 1000 PFLOP/s¹ haben. In N. Takeuchi et al. [3] wurde eine Verlustleistung von etwa 0,1 aJ/bit für ein Quantum-Flux-Parametron berechnet und daraus ergibt sich ein kleines Produkt Energie und Verzögerung von 20 aJ·ps.

Für solche Supercomputer bietet die supraleitende Elektronik eine vielversprechende Alternative zur Halbleiterelektronik [4]. Eine Mobilfunk-Basisstation besteht heute aus mehr als 100 leistungsfähigen Einzelcomputern mit einer Leistungsaufnahme von mehr als 7 kW [5]. Da alle Datennetzwerke in den kommenden Jahren weiter anwachsen, ist die Energieeffizienz an diesen Knotenpunkten besonders wichtig [2].

Die supraleitende Elektronik kombiniert eine niedrige Schaltenergie mit einer hohen

<sup>&</sup>lt;sup>1</sup>engl. Peta FLoating-point Operations per Second

1. Einleitung

Schaltgeschwindigkeit und besitzt damit ein hohes Potential für energieeffiziente Elektroniklösungen der Zukunft. Bis 2009 war die supraleitende Einzelflussquantenelektronik (RSFQ<sup>2</sup>-Elektronik) die einzige supraleitende Schaltungsfamilie. Heute gibt es aber weitere Schaltungsfamilien [2]. Durch die Reduzierung der Schaltenergie wird aber auch das Signal-Rausch-Verhältnis der Schaltungen beeinflusst und damit die Zuverlässigkeit von Entscheidungsprozessen und Schaltvorgängen verringert. Supraleitende Elektronik arbeitet naturgemäß bei einer geringen Betriebstemperatur von lediglich  $T=4,2\,\mathrm{K}.$  In dieser Arbeit wird der Einfluss des thermischen Rauschens auf analoge Entscheidungselemente untersucht. Dabei ist speziell der Entscheidungsprozess eines Komparators von großem Interesse, da diese Komponente ein grundlegendes Bauelement in allen analogen und digitalen Schaltungen bildet. Die Grauzone beschreibt die Schaltunsicherheit und ist ein Maß für die Empfindlichkeit eines supraleitenden Komparators. Diese Unsicherheit in Kombination mit der Schaltzeit ist der wichtigste Parameter für die Bewertung der Leistungsfähigkeit von Komparatoren. In der vorliegenden Dissertationsschrift werden unterschiedliche Abhängigkeiten und Wechselwirkungen zwischen der Grauzone und unterschiedlichen Parametern, wie z. B. Schaltzeit, Versorgungsströme, Bauteilparameter, Technologieparameter etc. untersucht. Davon werden Entwurfsregeln für supraleitende Komparatoren und darauf basierende supraleitende Analog-Digital-Wandler (AD-Wandler) abgeleitet. Die Arbeit gliedert sich in die folgenden Kapitel:

- In Kapitel 2 werden die Grundlagen der supraleitenden Elektronik und der AD-Wandler dargestellt. Dabei wird die Ausführung im Wesentlichen auf supraleitende AD-Wandler eingeschränkt. Am Ende des Kapitels gibt es einen Überblick über verschiedene Realisierungen von AD-Wandlern in unterschiedlichen Technologien. In diesem Kapitel wird eine Studie zur Klassifizierung der AD-Wandler in Abhängigkeit von ihren Eigenschaften durchgeführt.

- Kapitel 3 liefert eine umfangreiche Analyse supraleitender Komparatoren. Es wird die Abhängigkeit zwischen der Empfindlichkeit eines Josephson-Komparators unter dem Einfluss verschiedener Parameter mit Hilfe von Simulationen untersucht. Das Josephson-Komparator-Modell wird entwickelt und analysiert. Dieses Modell wird experimentell bestätigt, wodurch die mit dem Modell getroffenen Vorhersagen bekräftigt werden. Weiterhin wird eine Untersuchung der Abhängigkeit zwischen der Grauzone und anderen Systemparametern für einen Quasi-One-Junction-SQUID³ (QOJS)-Komparator [6] durchgeführt.

<sup>&</sup>lt;sup>2</sup>engl. Rapid Single Flux Quantum

<sup>&</sup>lt;sup>3</sup>engl. Superconducting Quantum Interference Device

- In Kapitel 4 wird eine Schaltung eines supraleitenden Σ Δ-AD-Wandlers basierend auf dem Josephson-Komparator untersucht. Insbesondere werden die Einflüsse der Eigenschaften des Komparators auf das Gesamtsystem untersucht. Dabei wird ein besonderes Augenmerk auf den Zusammenhang zwischen Geschwindigkeit (repräsentiert durch die Taktfrequenz) und Genauigkeit (repräsentiert durch die Grauzone) gelegt. Am Ende des Kapitels werden Entwurfsregeln für den Σ Δ-AD-Wandlers abgeleitet.

- Kapitel 5 befasst sich mit einem supraleitenden Flash-AD-Wandler, der auf QOJS-Komparatoren basiert. Ebenso wie im Kapitel 4 wird die Schaltung des Wandlers untersucht. Anhand der Ergebnisse werden Entwurfsregeln für den supraleitenen Flash-AD-Wandler abgeleitet.

- Zum Abschluss dieser Arbeit fasst **Kapitel 6** die Ergebnisse der Analyse der Entscheidungselemente und die abgeleiteten Entwurfsregeln für supraleitende  $\Sigma \Delta$ und Flash-AD-Wandler zusammen.

# Kapitel 2

# Grundlagen

Das Ziel der vorliegenden Arbeit besteht darin, Entwurfsregeln für supraleitende AD-Wandler abzuleiten. Deshalb wird in diesem Kapitel auf die Grundlagen supraleitender Elektronik und von AD-Wandlern eingegangen.

## 2.1 Grundlagen der supraleitenden Elektronik

Supraleiter sind Materialien, deren elektrischer Widerstand beim Unterschreiten einer kritischen Temperatur  $T_c$  (auch Sprungtemperatur genannt) auf exakt Null fällt. Die Supraleitung wurde 1911 von K. Onnes nach seiner Helium-Verflüssigung bei Messungen am Metall Quecksilber entdeckt [7].

Die Eigenschaft der Supraleitung kann unterhalb der kritischen Temperatur  $T_c$  auftreten. Im Supraleiter schließen sich unterhalb  $T_c$  2 Elektronen zu einem sogenannten Cooper-Paar zusammen. Die Cooper-Paare sind Teilchen (auch Bosonen genannt), die dem Pauli-Prinzip nicht mehr unterliegen [8]. Mit anderen Worten: alle Cooper-Paare im Supraleiter sind im gleichen quantenmechanischen Zustand. In der Quantenmechanik wird der Zustand eines Teilchens durch den Betrag  $\Psi$  und die Phase  $\phi$  einer Wellenfunktion beschrieben. Das heißt, jeder Supraleiter wird durch eine Wellenfunktion entsprechend der Gleichung (2.1) dargestellt. Mit dieser Wellenfunktion können Betrag und Phasenlage zu jedem Zeitpunkt t und an jedem Ort  $\vec{r}$  angegeben werden:

$$\Psi(\vec{r},t) = \overline{\Psi} \cdot e^{j(\vec{k}\vec{r} - \omega t)} = \overline{\Psi} \cdot e^{j(\vec{k}\vec{r} - \phi)}, \tag{2.1}$$

6 2. Grundlagen

wobei  $\omega$  die Kreisfrequenz,  $\vec{k}$  der Wellenzahlvektor und  $\overline{\Psi}$  der Betrag der Wellenfunktion ist.

## 2.1.1 Josephson-Effekt

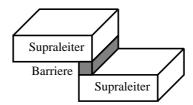

Jeder Supraleiter wird durch eine Wellenfunktion charakterisiert [9]. Werden zwei Supraleiter durch eine wenige Nanometer dünne, nicht-supraleitende Barriere (Isolator oder Normalleiter) getrennt, entsteht eine Phasendifferenz  $\varphi$  zwischen den beiden Wellenfunktionen. Dieser Effekt wurde 1962 von Brian Josephson vorhergesagt und durch die Josephson-Gleichungen beschrieben. Die Abbildung 2.1 zeigt schematisch diese Anordnung, die als Josephson-Kontakt (JK) bezeichnet wird. Hier wird die Barriere als Isolator dargestellt, weil die in der Arbeit verwendeten Josephson-Kontakte dieser Anordnung entsprechen.  $\varphi$  ist eine neue Zustandsvariable, die das Verhalten des Josephson-Kontaktes

Abbildung 2.1: Der schematische Aufbau eines Josephson-Kontaktes.

beschreibt. Der Tunnelstrom  $I_J$ , der durch die dünne Barriere fließt, wird durch die erste Josephson-Gleichung beschrieben:

$$I_J = I_c \cdot \sin(\varphi), \tag{2.2}$$

wobei  $I_c$  der kritische Strom des Kontaktes ist, der eine wesentliche Kenngröße des Josephson-Kontaktes darstellt. Dieser kritische Strom repräsentiert den maximalen Tunnelstrom, der supraleitend durch den JK fließen kann. Die Stärke des Stromes wird durch die Geometrie bestimmt, wobei er von der Dicke und der Querschnittsfläche der isolierenden Barriere abhängt. Eine Änderung des Stromes im JK führt zu einer Phasenänderung und damit zu einer Spannung über dem Kontakt, die durch die zweite Josephson-Gleichung angegeben wird:

$$\frac{\mathrm{d}\varphi(t)}{\mathrm{d}t} = \frac{2\pi}{\Phi_0} \cdot u(t) \tag{2.3}$$

$\Phi_0 = h/2e \approx 2,067 \cdot 10^{-15} \text{Vs}$  ist das magnetische Flussquant, wobei h das Plancksche Wirkungsquantum und e die Elementarladung ist. Der JK hat gemäß seiner Geometrie im

Allgemeinen eine parasitäre Kapazität  $C_J$  zwischen den beiden Supraleitern. Der Tunnelstrom  $I_J$ , der durch die Isolationsbarriere fließt, führt zu einem elektrischen Widerstand der Barriere  $R_J$ . Mit Hilfe von Gleichungen (2.2) und (2.3) wird der JK modelliert. Das Modell wird in der späteren Simulation von kryogenen Schaltungen verwendet.

## 2.1.2 RCSJ-Modell des Josephson-Kontaktes

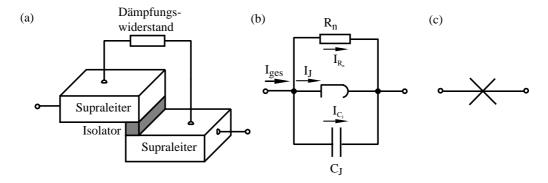

Der JK wird durch drei Stromkomponenten beschrieben. Den Suprastrom  $I_J$ , den Strom durch die Kapazität  $C_J$  und den Strom durch den Widerstand der Barriere  $R_J$ . Die elektrischen Eigenschaften werden oft durch einen zusätzlichen Widerstand  $R_s$  als Dämpfungs-Widerstand beeinflusst [10], der parallel zu  $R_J$  geschaltet wird. Der Gesamtwiderstand wird  $R_n = \frac{R_J \cdot R_s}{R_J + R_s}$  bezeichnet. Da der Widerstand der Barriere  $R_J$  viel größer als der Dämpfungswiderstand  $R_s$  ist, kann  $R_J$  in vielen Fällen vernachlässigt werden  $(R_n \approx R_s)$ . Das Ersatzschaltbild wird als RCSJ-Modell (engl. Resistively and Capacitively Shunted Junction) bezeichnet, welches das am häufigsten verwendete Modell in der Schaltungssimulation ist. Die Abbildung 2.2 zeigt das Dämpfungsprinzip, das RCSJ-Modell und das in dieser Arbeit verwendete Symbol für den JK. Der Gesamtstrom  $I_{ges}$ , der im Ersatzschalt-

**Abbildung 2.2:** (a) Dämpfungsprinzip (b) RCSJ-Modell (c) das Schaltzeichen für den JK mit zusätzlichem Widerstand  $R_s$ .

bild fließt, besteht aus drei Komponenten: dem Tunnelstrom  $I_J$ , dem Kondensatorstrom  $I_{C_J}$  und dem Strom  $I_{R_n}$ , welcher durch den Widerstand  $R_n$  fließt. Laut des ersten Kirchhoffscher Gesetzes ist  $I_{qes}$ :

$$I_{ges} = I_J + I_{C_J} + I_{R_n}. (2.4)$$

8 2. Grundlagen

Der Tunnelstrom  $I_J$  wird durch die erste Josephson-Gleichung (2.2) definiert. Beim Spannungsabfall über dem Josephson-Kontakt ergibt sich ein Strom  $I_{C_J}$ :

$$I_{C_J} = C_J \cdot \frac{\mathrm{d}u(t)}{\mathrm{d}t}.\tag{2.5}$$

Der Strom durch den Gesamtwiderstand  $R_n$  ist durch

$$I_{R_n} = \frac{u(t)}{R_n} \tag{2.6}$$

gegeben. Beim Einsetzen der Gleichungen (2.2), (2.5), (2.6) in die Gleichung (2.4) erhält man:

$$I_{ges} = I_c \cdot \sin(\varphi) + C_J \cdot \frac{\mathrm{d}u(t)}{\mathrm{d}t} + \frac{u(t)}{R_n}.$$

(2.7)

Für den Gesamtstrom  $I_{ges}$  erhält man somit eine Differentialgleichung 1. Ordnung.

# 2.1.3 Charakteristische Parameter eines realen Josephson-Kontaktes

Der Josephson-Kontakt ist das aktive Schaltungselement in der supraleitenden Elektronik [11]. Die Herstellung erfolgt für den in dieser Arbeit verwendeten 1 kA/cm²-Prozess (IPHT¹-Technologie) durch einen mehrlagigen Dünnschichtprozess. Der Josephson-Kontakt wird zwischen zwei Metallisierungsschichten von Niobium (Nb) hergestellt und durch eine 2 nm dicke Aluminiumoxidschicht (Al<sub>2</sub>O<sub>3</sub>) definiert. Das Nioboxid und die Siliziumdioxidschichten dienen zwischen den Metallisierungsschichten als Isolator. Die Technologie lässt sich durch zwei Parameter, die kritische Stromdichte  $J_c$  und die Flächenkapazität  $C_F$  des JK, charakterisieren. Weiterhin gibt es Designparameter. Der erste Designparameter ist der kritische Strom  $I_c$ . Mit Hilfe dieses Parameters kann man die Kapazität  $C_J$  des JK bestimmen. Der kritische Strom und die Kapazität des JK werden mit folgenden Gleichungen dargestellt:

$$I_c = A \cdot J_c,$$

$$C_J = A \cdot C_F.$$

(2.8)

A ist die Querschnittsfläche des JK. Basierend auf dem McCumber-Parameter  $\beta_c$  (Gleichung (2.9)) als zweiten Designparameter, der die Hysterese des JK beschreibt, kann man

<sup>&</sup>lt;sup>1</sup>am Leibniz Institut für Photonische Technologien Jena [12]

den Dämpfungswiderstand wie folgt berechnen. Aus

$$\beta_c = \frac{2\pi I_c R_n^2 C_J}{\Phi_0} \tag{2.9}$$

folgt

$$R_n = \sqrt{\frac{\beta_c \Phi_0}{2\pi I_c C_J}}. (2.10)$$

Für die IPHT-Technologie ist  $\beta_c=1$  [13] und daraus folgt:

$$R_n = \sqrt{\frac{\Phi_0}{2\pi I_c C_J}}. (2.11)$$

Beim Einsetzen von (2.8) in (2.11) erhält man:

$$R_n = \frac{J_c}{I_c} \sqrt{\frac{\Phi_0}{2\pi J_c C_F}}. (2.12)$$

Für die Simulationen von anderen Technologien spielt die charakteristische Spannung  $V_c = R_n \cdot I_c$  neben dem McCumber-Parameter eine große Rolle [14]. Für die IPHT-Technologie ergibt sich:

$$V_c = R_n \cdot I_c = \sqrt{\frac{\Phi_0 \cdot J_c}{2\pi C_F}} = 256\mu V$$

(2.13)

Es ist zu sehen, dass diese Spannung unabhängig von den Designparametern ist. Sie ergibt sich aus der Technologie. Die Tabelle 2.1 fasst die Technologie- und Designparameter und daraus resultierende Größen zusammen.

| Technologie | Design    | Resultierende Größen |

|-------------|-----------|----------------------|

| $J_c$       | $I_c$     | A                    |

| $C_F$       | $\beta_c$ | $C_J$                |

|             |           | $R_n$                |

|             |           | $V_c$                |

Tabelle 2.1: Die Technologie- und Designparameter und daraus resultierende Größen.

10 2. Grundlagen

## 2.1.4 Flussquantisierung in supraleitender Schleife

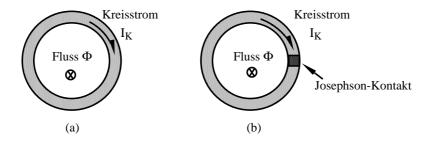

Der Effekt der Flussquantisierung wurde 1948 von F. London vorhergesagt [15] und 1961 experimentell bestätigt [16, 17]. Nimmt man eine supraleitende Schleife, entsprechend Abbildung 2.3(a) an, kann die Bedingung für die Flussquantisierung folgendermaßen formuliert werden:

$$\Phi = LI_K = \Phi_0 k. \tag{2.14}$$

k ist eine beliebige ganze Zahl. Diese Bedingung erläutert, dass der magnetische Fluss

Abbildung 2.3: (a) Schematische Darstellung einer supraleitenden Schleife. (b) Schematische Darstellung der Unterbrechung einer supraleitenden Leiterschleife mit einem Josephson-Kontakt.

$\Phi$  durch eine Leiterschleife nur ein ganzzahliges Vielfaches von  $\Phi_0$  annehmen kann. Unterbricht man die Leiterschleife mit einem JK, wie in Abbildung 2.3(b) gezeigt, ergibt sich eine Begrenzung des Kreisstromes nach der ersten Josephson-Gleichung (2.2). Der JK wirkt als Tor, durch welches die Flussquanten in die supraleitende Schleife hinein und aus der supraleitenden Schleife heraus kommen. In der supraleitenden Elektronik werden die digitalen Informationen durch Anwesenheit oder Abwesenheit der Flussquanten in einer supraleitenden Schleife repräsentiert [18]. Es gibt aber auch passive Bauelemente, die durch Widerstände und Induktivitäten repräsentiert werden.

## 2.1.5 Grundstrukturen supraleitender Elektronik

## 2.1.5.1 Übertragung der Flussquanten

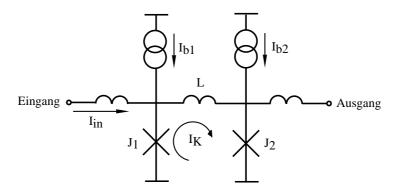

Die Übertragung der Flussquanten erfolgt durch eine bestimmte Elektronik-Zelle, die als Josephson-Übertragungsleitung (JTL<sup>2</sup>) bezeichnet wird (siehe Abbildung 2.4). Der Josephson-Kontakt schaltet, wenn sein kritischer Strom  $I_c$  überschritten wird. Im Fall der JTL bedeutet das, wenn der Strom durch  $J_1$  größer als sein kritischer Strom ist,

<sup>&</sup>lt;sup>2</sup>engl. Josephson Transmission Line

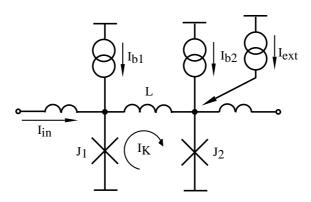

schaltet  $J_1$ . Dabei wird ein Flussquant erzeugt und ein Kreisstrom  $I_K = \frac{\Phi_0}{L}$  in der mittleren Schleife induziert.  $I_K$  und  $I_{b2}$  überlagern sich. Mit  $I_K$  und dem zusätzlichen Biasstrom  $I_{b2}$  überschreitet der Strom durch  $J_2$  seinen kritischen Strom und es wird auch  $J_2$  schalten. Das Flussquant verlässt durch  $J_2$  die Schleife und wird in die benachbarte Schleife weitergeleitet. Damit der Kreisstrom ausreichend ist, muss die Induktivität L die Bedingung  $L < \frac{\Phi_0}{I_c}$  erfüllen [19].

Abbildung 2.4: Übertragung der Flussquanten in einer JTL.

#### 2.1.5.2 Speicherung der Flussquanten

Zu den Grundstrukturen der supraleitenden Elektronik gehört auch die Speicherung der Flussquanten. Wenn der Kreisstrom den kritischen Strom von  $J_2$  nicht überschreitet, kann  $J_2$  nicht schalten und das Flussquant bleibt in der Schleife gespeichert, weil die Induktivität in der mittleren Schleife groß ist, wie in Abbildung 2.5 gezeigt wird. Vergrößert man die Induktivität, kann mehr als ein Flussquant in der Schleife gespeichert werden. Um eine zweistufige Logik für digitale Schaltungen zu bekommen, muss L so gewählt werden, dass genau nur ein Flussquant in der Schleife gespeichert werden kann. Das geschieht unter der Bedingung  $\frac{\Phi_0}{I_c} < L < \frac{2\Phi_0}{I_c}$ . Um die Informationen repräsentiert in Spannungsimpulsen (Flussquanten) am Ausgang auszulesen, muss der kritische Strom von  $J_2$  überschritten werden. Es wird ein zusätzlicher Strom  $I_{\rm ext}$  eingespeist, der in Summe mit dem Kreisstrom  $I_K$  den kritischen Strom von  $J_2$  überschreitet und diesen somit zum Schalten zwingt. Dadurch verlässt das Flussquant die Schleife (siehe Abbildung 2.5).

## 2.1.5.3 Grundstruktur für die Entscheidung

Der Josephson-Komparator ist das Entscheidungselement und eine grundlegende Schaltung in der supraleitenden Elektronik [11]. Die Entscheidung ist abhängig vom Eingangs-

12 2. Grundlagen

Abbildung 2.5: Speicherung der Flussquanten.

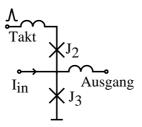

strom, der einen Schwellwert besitzt. Die Abbildung 2.6 stellt eine einfache Komparator-Schaltung dar. Sie wird von Taktimpulsen am Eingang getrieben, um Impulse am Ausgang auszugeben. Die Schaltung besteht aus zwei Kontakten  $J_1$  und  $J_2$ . Einer der beiden Kontakte muss schalten, wenn ein Taktimpuls auftritt. Der Eingangsstrom  $I_{\rm in}$  ist ein Steuerstrom und bestimmt, welcher Kontakt schaltet. Wenn  $I_{\rm in}$  größer als der Schwellwert ist, schaltet  $J_2$  andernfalls schaltet  $J_1$ .

Abbildung 2.6: Die Grundschaltung eines Josephson-Komparators.

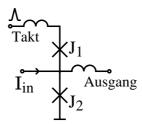

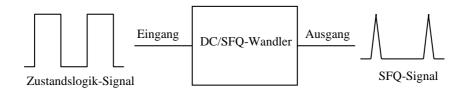

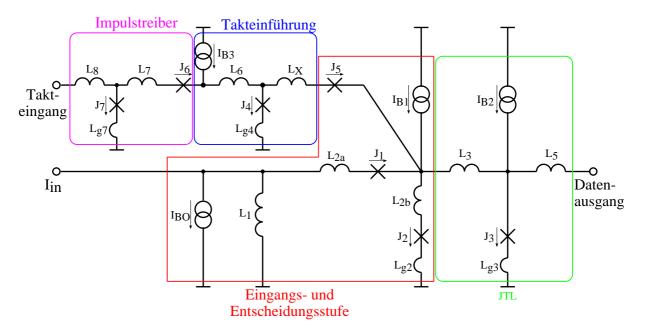

## 2.1.6 Eingangsinterface-Wandler

Zum Aufbau von Schaltungen in der supraleitenden Elektronik wird ein Zell-basierter Entwurf verwendet. Einige Grundzellen werden in diesem Kapitel kurz beschrieben. Weitere Zellen sind in [20] zu finden. Die erste Grundzelle, die Josephson-Übertragungsleitung, dient zur Weiterleitung der Flussquanten. Sie wurde im Abschnitt 2.1.5.1 beschrieben. Die zweite Grunzelle ist der Eingangsinterface-Wandler (DC/SFQ-Wandler), der zur Wandlung eines halbleitenden digitalen Zustandslogik-Spannungssignals in ein Einzelflussquanten (SFQ)<sup>3</sup>-Signal, wie in Abbildung 2.7 dargestellt, eingesetzt wird. Die Ab-

<sup>&</sup>lt;sup>3</sup>engl. Single Flux Quantum

Abbildung 2.7: Schematische Darstellung der Funktionsweise des DC/SFQ-Wandlers.

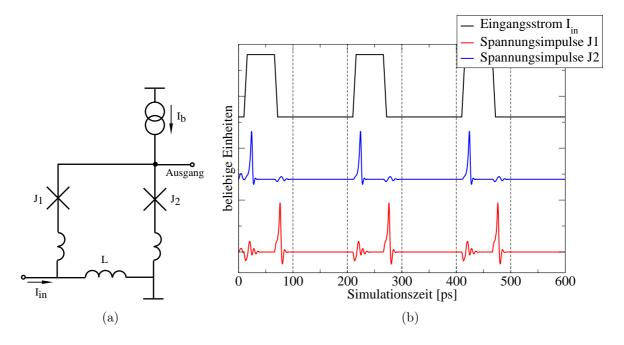

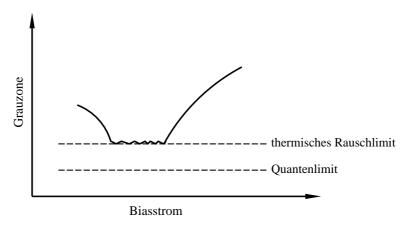

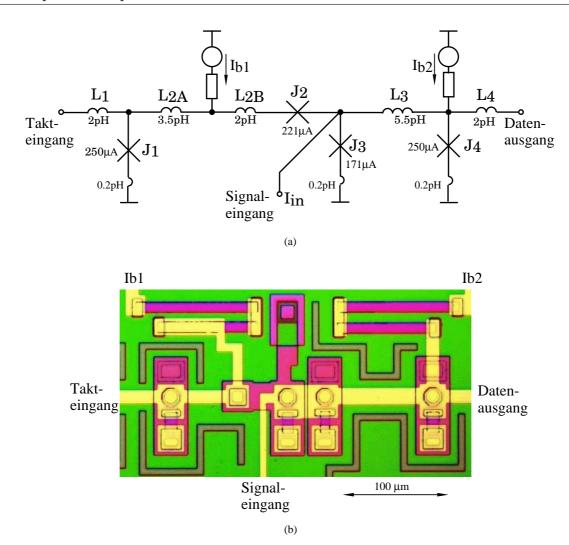

bildung 2.8(a) stellt die Schaltung des DC/SFQ-Wandlers dar. Sie besteht aus einer supraleitenden Schleife mit einer speichernden Induktivität L, zwei Josephson-Kontakten  $J_1$  und  $J_2$ , einem Eingangsstrom  $I_{in}$  als Rechtecksignal, einer Biasstromquelle  $I_b$  und einem Ausgang. Der DC/SFQ-Wandler repräsentiert die Interfaceschaltung in der RSFQ-

**Abbildung 2.8:** (a) Die Schaltung eines DC/SFQ-Wandlers, (b) Simulierte Schaltvorgänge von  $J_1$ ,  $J_2$  eines DC/SFQ-Wandlers in Abhängigkeit vom Eingangsstrom, Spannungsimpulse von  $J_2$  bei der steigenden Flanke des  $I_{\rm in}$  und von  $J_1$  bei der fallenden Flanke des  $I_{\rm in}$ .

Elektronik, die mit der steigenden Flanke des Eingangsstromes einen Spannungsimpuls am Ausgang erzeugt. Mit der steigenden Flanke des Eingangsstromes fließt der Hauptteil des Stromes über  $J_1$  und  $J_2$  auf Masse ab. Der kleine Anteil über L kann vernachlässigt werden. Der Biasstrom fließt zum größten Teil über  $J_2$  und zu einem geringen Teil über  $J_1$  und L über die Masse ab. Durch die Summe der Ströme wird der kritische Strom von  $J_2$  überschritten. Dadurch schaltet  $J_2$ , es wird ein Spannungsimpuls am Ausgang erzeugt und damit ein Flussquant aus der Schleife entfernt. Es ergibt sich eine Umverteilung der Ströme in der Schleife und damit wird ein Kreisstrom entgegen dem Uhrzeigersinn in-

14 2. Grundlagen

duziert. Dieser Kreisstrom und der Teil des Eingangsstromes, der über  $J_1$  fließt, heben sich gegenseitig auf. Die Schaltung bleibt im stabilen Zustand, wenn keine Änderung des Eingangsstromes vorgenommen wird. Wenn der Eingangsstrom  $I_{\rm in}$  verringert wird, bringen der Kreisstrom und der Biasstrom, die über  $J_1$  fließen,  $J_1$  zum Schalten. Dabei wird wieder ein Flussquant in der Schleife erzeugt und ein Kreisstrom induziert, der sich mit dem zuvor erzeugten Kreisstrom aufhebt. Das entspricht dem Verhalten der Schaltung bei fallender Flanke des Eingangsstromes. Die Abbildung 2.8(b) zeigt typische Simulationsergebnisse eines DC/SFQ-Wandlers, wobei  $J_2$  mit steigender Flanke des Eingangsstromes und  $J_1$  mit fallender Flanke schalten.

## 2.2 Grundlagen der AD-Wandler

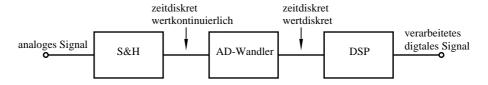

Der Analog-Digital-Wandler (AD-Wandler) ist eine fundamentale Komponente in einem digitalen Signalverarbeitungssystem, wie es in Abbildung 2.9 dargestellt wird. Das System besteht aus den Komponenten: Abtast-Halte-Glied (S&H<sup>4</sup>), Analog-Digital-Wandler (AD-Wandler) [21], [22] und digitaler Signalprozessor (DSP). Das Abtast-Halte-Glied tastet das Analogsignal in bestimmten Zeitintervallen ab und hält es während eines Zeit-intervalls konstant. Aus einem zeitkontinuierlichen Signal wird ein zeitdiskretes Signal. Zur Realisierung der digitalen Werte wird vom AD-Wandler ein Signal benötigt, welches eine gewisse Zeit konstant ist. Die digitalen Werte werden dann vom digitalen Signalprozessor verarbeitet. AD-Wandler sind Funktionselemente, die einer analogen Eingangsgröße eine

Abbildung 2.9: Digtales Signalverarbeitungssystem.

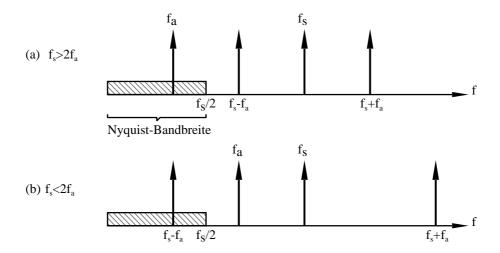

digitale Ausgangsgröße zuordnen. Typische Verarbeitungsschritte für den analog-digitalen Wandlungsprozess sind die Abtastung und die Quantisierung. Das Analogsignal muss das Nyquist-Kriterium erfüllen, damit das Digitalsignal das analoge repräsentiert [23]. Das Nyquist-Kriterium besagt, dass das Analogsignal mit einer Frequenz  $f_a$  mit Abtastrate  $f_s > 2f_a$  abgetastet werden muss, um den Verlust der Informationen zu vermeiden. Ist  $f_s < 2f_a$ , entstehen nicht-lineare Verzerrungen, die auch als Aliasing bezeichnet werden,

<sup>&</sup>lt;sup>4</sup>engl. Sample and Hold

wobei die Frequenzkomponenten innerhalb der Nyquist-Bandbreite  $(0 \rightarrow f_s/2)$  verzerrt werden [24]. Dies kann man in Abbildung 2.10 sehen. Zur Vermeidung des Aliasing-

**Abbildung 2.10:** (a) Nyquist-Kriterium, (b) Aliasing-Effekt. Frequenzkomponenten werden immer bei Frequenzen  $Kf_s \pm f_a$  gespiegelt, wobei  $K = 1, 2, 3, \cdots$ . Deshalb kommt beim Aliasing-Effekt eine Verzerrung, wenn  $f_s - f_a$  in der Nyquist-Bandbreite liegt.

Effektes muss sich die Frequenz des Analogsignals innerhalb der Nyquist-Bandbreite befinden. Ist  $f_s \gg 2f_a$ , spricht man von Überabtastung.

Im Folgenden werden einige Wandlungsprinzipien dargestellt.

## 2.2.1 Parallelverfahren

Im Parallelverfahren findet die Quantisierung in einem Verarbeitungszyklus statt, d. h. alle Bits werden gleichzeitig ausgegeben. Parallelverfahren basieren auf Vergleichsnormalen (Referenzspannungen) und Messgrößen (Anzahl der Quantisierungsstufen). Die Referenzspannungen werden gleichzeitig parallel mit der zu messenden Größe verglichen. Die AD-Wandler mit parallelen Verfahren weisen einerseits die kürzeste Umwandlungzeit aller AD-Wandler auf, andererseits haben sie aber eine große Schaltungskomplexität [25]. Zu diesen Verfahren gehört der Flash-AD-Wandler, der nachfolgend ausführlicher erklärt wird.

#### 2.2.1.1 Flash-AD-Wandler

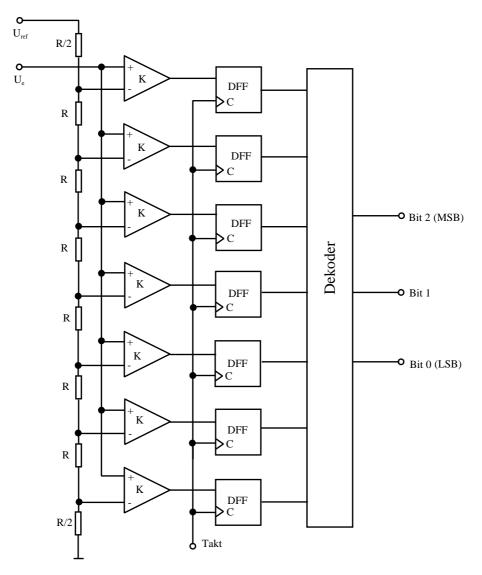

Wie oben erwähnt, sind die Flash-AD-Wandler die schnellsten Wandler, jedoch mit einer aufwändigen Struktur. Für einen Flash-AD-Wandler mit n-bit Auflösung werden  $2^n - 1$

2. Grundlagen

Komparatoren benötigt, die in einem Schritt zeitgleich die analoge Eingangsspannung  $U_e$  mit  $2^n - 1$  Referenzspannungen vergleichen und bestimmen, welche dieser  $2^n - 1$  Referenzspannungen die geringste Abweichung zur Eingangsspannung besitzt. Die  $2^n - 1$  Referenzspannungen werden mit Hilfe eines Spannungsteilers ( $2^n$  Widerstände) aus einer Referenzspannung  $U_{ref}$  erzeugt. Das Resultat wird getaktet, von flankengetriggerten D-Flip-Flops übernommen und in Dekoder in die entspechende Dualzahl umgewandelt. Abbildung 2.11 zeigt das Schaltbild eines 3-Bit Flash AD-Wandlers, wo Bit 0 dem niederwertigsten Bit (LSB<sup>5</sup>) entspricht und Bit 2 dem höchstwertige Bit (MSB<sup>6</sup>). Da die Anzahl

Abbildung 2.11: Schaltbild einer Realisierung eines Flash AD-Wandlers mit 3-Bit Auflösung.

<sup>&</sup>lt;sup>5</sup>engl. Least Signifikant Bit

<sup>&</sup>lt;sup>6</sup>engl. Most Signifikant Bit

der Komparatoren mit der Zunahme der Auflösung des Flash-AD-Wandlers zunimmt, steigt die Schaltungskomplexität ebenfalls. Wegen der Nichtlinearitäten der Komponenten des Flash AD-Wandlers ist die Auflösung oft auf 10 Bit begrenzt [26].

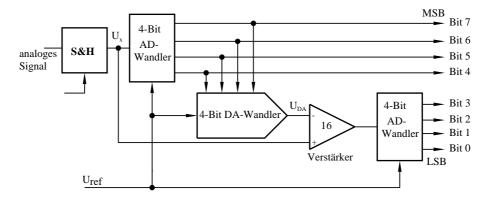

## 2.2.1.2 Mehrstufen-Wandler (Pipeline-AD-Wandler)

Die Prinzipschaltung des Pipeline-AD-Wandlers beruht auf der Aufteilung des Wandlungsvorganges in mehreren Schritten mit Hilfe der Parallel-Serien-Methode [27]. Es ist üblich, Pipeline-AD-Wandler zu verwenden, wenn man AD-Wandler mit hoher Auflösung und hoher Abtastrate mit vertretbarem Aufwand benötigt. Abbildung 2.12 stellt die Prinzipschaltung eines 8-Bit Pipeline-AD-Wandlers dar. Sie beinhaltet unter anderem ein Abtast-Halte-Glied (S&H), da das Analogsignal für die Wandlungszeit konstant gehalten werden muss. Zuerst werden die 4 höchstwertigen Stellen des 8-Bit-Ausgangswortes definiert. Ein 4-Bit DA-Wandler wandelt diese in eine wertentsprechende Analogspannung zurück. Im zweiten Wandeltakt wird der Fehler  $U_f = U_x - U_{DA}$  (siehe Abbildung 2.12) rekonstruiert. Er wird mit dem Faktor 16 verstärkt und weiter im zweiten 4-Bit AD-Wandler in die 4 niederwertigen Stellen gewandelt. Weitere Informationen über Mehrstufen-Wandler findet man in [27].

Abbildung 2.12: Schaltbild eines 8-Bit Pipeline-AD-Wandlers.

## 2.2.2 Wägeverfahren

Beim Wägeverfahren wird nicht das ganze Wandlungsergebnis in einem Schritt gebildet, sondern jeweils nur ein Bit des zugehörigen digitalen Ausgangswortes. Zu den Wägeverfahren gehört das Verfahren der sukzessiven Approximation und der algorithmischen AD-Wandler. Letzteres wird in der Arbeit nicht weiter betrachtet. Weitere Details sind in [28]

18 2. Grundlagen

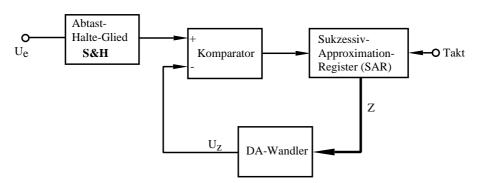

zu finden. Die AD-Wandler, die das Prinzip der sukzessiven Approximation verwenden, kombinieren relativ kurze Umwandlungzeiten und hohe Genauigkeit bei vertretbarem Schaltungsaufwand [28]. Die vom Eingangssignal unabhängige konstante Wandlungszeit liefert einen wesentlichen Vorteil gegenüber dem zuvor beschriebenen AD-Wandler. Eine bevorzugte Anwendung für solche AD-Wandler sind Datenerfassungssysteme. Ihre Wandelrate ist zwar geringer als bei Flash-AD-Wandlern, aber Schaltungsaufwand und Stromverbrauch sind deutlich geringer. Es gibt Typen bis zu 16 Bit Auflösung und andere mit  $1\mu$ s Wandlungszeit [28]. Dieser AD-Wandler braucht für die Zeit der Wandlung ein konstantes Eingangssignal, andernfalls sinkt seine Auflösung. Es wird daher die Verwendung eines Abtast-Halte-Gliedes (S&H) benötigt. Die schrittweise Annährung der in einem Digital-Analog(DA)-Wandler aus einem Digitalwert erzeugten Spannung an die Eingangsspannung fasst das Prinzip der sukzessiven Approximation zusammen. Das Blockschaltbild eines AD-Wandlers, der nach dem Verfahren der sukzessiven Approximation arbeitet, stellt die Abbildung 2.13 dar. Es besteht aus mehreren Komponenten, dem DA-Wandlern, dem Komparator, dem sukzessiven Approximationsregister und dem Abtast-Halte-Glied. Die Funktionsweise eines AD-Wandlers, der nach dem Prinzip der sukzessiven Approximation arbeitet, wird in Stufen geteilt und die Schrittweite, bei der die Ausgangsspannung des DA-Wandles verändert wird, wird um die Hälfte verringert.

**Abbildung 2.13:** Blockschaltbild eines AD-Wandlers nach dem Verfahren der sukzessiven Approximation.

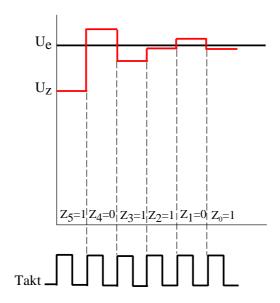

Abbildung 2.14 zeigt den Wandlungsvorgang eines 6-Bit AD-Wandlers nach dem Verfahren der sukzessiven Approximation. Zunächst werden alle Bits in einem Datenspeicher (Sukzessiv-Approximation-Register, SAR) auf Null gesetzt. Beginnend beim höchstwertigen Bit (MSB) werden abwärts bis zum niederwertigsten Bit (LSB) nacheinander alle Bits des Digitalwertes ermittelt. Dann wird das jeweilige Bit probeweise auf Eins gesetzt. Der DA-Wandler erzeugt die dem aktuellen Digitalwert entsprechende Spannung  $U_z$ . Der Komparator vergleicht diese mit der Eingangsspannung  $U_e$  und veranlasst, dass

im SAR das entsprechende Bit wieder auf Null zurückgesetzt wird, wenn  $U_z > U_e$  ist, ansonsten bleibt das Bit auf 1 gesetzt. Der digitale Eingang Z des DA-Wandlers wird solange geändert, bis die Signale mit 1 LSB Genauigkeit übereinstimmen. Dann ist die

**Abbildung 2.14:** Wandlungvorgang eines AD-Wandlers nach dem Verfahren der sukzessiven Approximation.

Digitalzahl Z an den Eingängen des DA-Wandlers das Äquivalent zur Eingangsspannung und repräsentiert das Ausgangswort des AD-Wandlers [25].

## 2.2.3 Zählverfahren (Serielle AD-Wandler)

AD-Wandler, die nach dem Zählverfahren arbeiten, sind praktisch sehr verbreitet. Ihre Vorteile bestehen in einem einfachen Schaltungsaufbau, der erreichbaren sehr hohen Genauigkeit, der Auflösung und der Linearität. Ihr einziger Nachteil ist die relativ hohe Wandlungszeit in (ms-Bereich). Zählverfahren sind serielle Umwandlungsverfahren, weil sie nur einen Quantisierer benötigen. Zu den Zählverfahren gehört der Sigma-Delta-AD-Wandler, der in dieser Arbeit in der supraleitenden Technologie diskutiert wird. AD-Wandler, die nach dem Zählverfahren arbeiten, sind in der Literatur z. B. [25, 28] beschrieben.

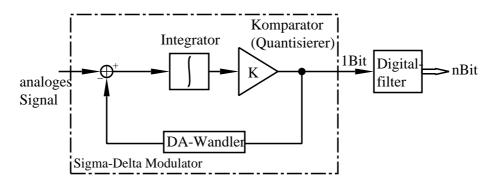

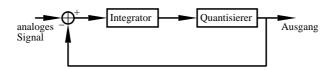

## 2.2.3.1 Sigma-Delta-AD-Wandler

Der Sigma-Delta-AD-Wandler wird kommerziell hauptsächlich in der Digitalisierung von Audiosignalen (Sprache, Musik) eingesetzt. Seine hohe Auflösung, hohe Umsetzrate und

2. Grundlagen

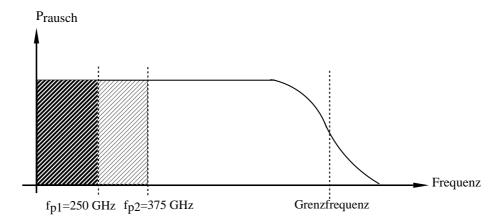

kostengünstigen Realisierungen in der VLSI-Technik (Very-Large-Scale Integration) sind die Gründe für den Einsatz. Die zwei hauptsächlichen Komponenten des Sigma-Delta-AD-Wandlers sind der Sigma-Delta-Modulator und der Digitalfilter. Der Modulator besteht aus einem Komparator und einem Integrator. Der Komparator digitalisiert die Summe ( $\Sigma$ ) der Differenzen ( $\Delta$ ) zwischen dem Eingangssignal und dem Rückkopplungssignal [29]. Somit wandelt der Sigma-Delta-Modulator das analoge Eingangssignal in eine hochfrequente serielle Bitfolge mit 1 Bit Auflösung um. Dieses Modulator-Ausgangssignal wird durch digitale Tiefpassfilterung in hochauflösende Parallelworte mit geringer Abtastrate umgewandelt. Abbildung 2.15 stellt das Blockschaltbild eines Sigma-Delta-AD-Wandlers dar. Die hohe Auflösung (typisch 20 Bits), die Sigma-Delta-Wandler erreichen können, sind

Abbildung 2.15: Blockschaltbild eines Sigma-Delta-AD-Wandlers.

durch die Kombination der Prinzipien Überabtastung (Oversampling), Rauschformung (noise shaping) und Dezimierung realisierbar [30]. In Abbildung 2.15 wird die Differenz zwischen der analogen Eingangsspannung und der rückgekoppelten Referenzspannung integriert. Der Komparator quantisiert das Ergebnis der Integration durch Schwellwertvergleich und tastet es gleichzeitig mit einer Frequenz  $f_s$ , die höher als die Nyquist-Frequenz ist (Überabtastung), ab. Durch den Digitalfilter wird aus einer Folge von Abtastwerten ein Digitalwort mit entsprechend hoher Auflösung gebildet.

Alle oben genannten AD-Wandler sind für die Realisierung in Halbleitertechnik geeignet. Jedoch können keine komplexen AD-Wandler realisiert werden, z. B. Pipeline-AD-Wandler, in der supraleitenden Elektronik, weil die Integrationsdichte in der Supraleitung limitiert ist. Deshalb können keine komplexen AD-Wandler realisiert werden. Zwei gut zu realisierende Wandler sind:

• der supraleitene Flash-AD-Wandler, da er eine hohe Bitzahl mit wenigen Komparatoren n ermöglichen kann, im Gegensatz zum halbleitenden Flash-AD-Wandler, der  $2^n - 1$  Komparatoren benötigt, wobei n die Auflösung des AD-Wandlers ist,

• der  $\Sigma - \Delta$ -AD-Wandler ist ein sehr typischer supraleitender AD-Wandler, weil er eine einfache Schaltung aufweist. Er findet im z. B. Digital-SQUID Anwendung [6,31,32].

## 2.2.4 Kenngrößen der AD-Wandler

## 2.2.4.1 Statische Kenngrößen

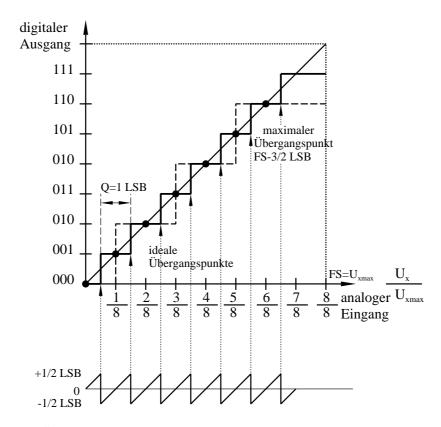

## • Quantisierungsfehler

Die Quantisierung ist die Aufteilung eines Wertebereiches in eine bestimmte Anzahl von Teilbereichen, die in der Regel gleich groß sind und als Quantisierungsstufen bezeichnet werden. Die Spannung, die einer Quantisierungstufe Q entspricht, ist identisch mit 1 LSB und wird für einen AD-Wandler mit Auflösung n anhand der Gleichung:

$$Q = \frac{FSR}{2^n},\tag{2.15}$$

gegeben. Ändert sich der Eingangswert um Q, ändert sich erst die Ausgangsbelegung [22], wobei FSR für Full Scale Range steht und dem maximalen Wertebereich des Eingangssignals entspricht. Der Effektivwert des Quantisierungfehlers wird mit  $Q/\sqrt{2}$  approxmiert. Alle Eingangswerte, die sich im Bereich einer Quantisierungsstufe befinden, liefern den selben Ausgabewert. Dadurch tritt ein Fehler bis zu einem halben LSB auf, der als Quantisierungfehler bezeichnet wird. Deswegen entspricht ein Ausgangswort nicht präzise einem Eingangswert, sondern einem bestimmten Bereich der Eingangsgröße. Der maximale Quantisierungfehler  $x_f$  ergibt sich aus:

$$x_f = \frac{Q}{2} = \frac{FSR}{2^{n+1}}. (2.16)$$

Abbildung 2.16 illustriert anhand der Übertragungskennlinie den Quantisierungsfehler [33]. Die idealen Übergänge sind bei der Hälfte des Abstandes zwischen zwei Quantisierungsstufen.

#### Genauigkeit und Auflösung

## - Absolute Genauigkeit

Die Abweichung der Übertragungsfunktion von den idealen berechneten Werten wird als Fehler in der absoluten Genauigkeit bezeichnet.

2. Grundlagen

Abbildung 2.16: Übertragungskennlinie und Quantisierungsfehler für einen 3-Bit AD-Wandler.

## - Relative Genauigkeit

Die Funktion eines AD-Wandlers in Abhängigkeit von seiner Nichlinearität bezeichnet man als relative Genauigkeit. Diese relative Genauigkeit ist unabhängig vom Offset- und vom Verstärkungsfehler. Wird dieser Fehler abgeglichen, bekommt man einen AD-Wandler mit absoluter Genauigkeit [33].

## - Auflösung

Die Auflösung eines AD-Wandlers wird vom kleinsten Schritt (LSB), den er verarbeiten kann, bestimmt. Die Auflösung steigt mit der Bitzahl n des AD-Wandlers [33].

## • Verstärkungs- und Offsetfehler

## - Verstärkungsfehler

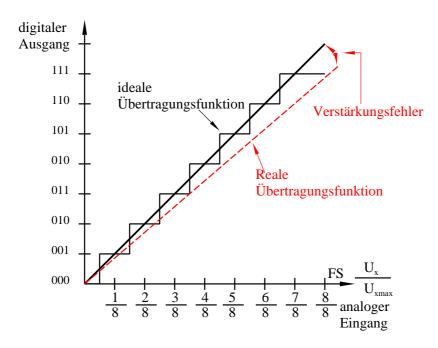

Der Verstärkungsfehler ist die Abweichung vom Anstieg der idealen Übertragungskennlinie (Siehe Abbildung 2.17).

## - Offsetfehler

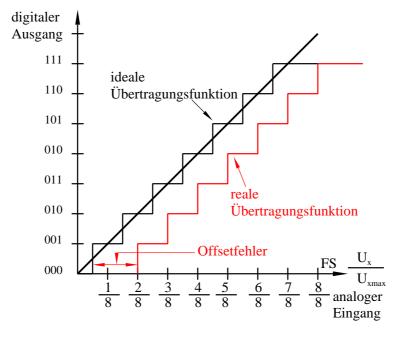

Der Offsetfehler charakterisiert die Verschiebung der idealen Übertragungs-

Abbildung 2.17: Illustration des Verstärkungsfehlers.

kennlinie eines AD-Wandlers aus dem Ursprung. Abbildung 2.18 stellt den Offsetfehler dar [33].

Abbildung 2.18: Illustration des Offsetfehlers.

## • Integrale und differentielle Nichtlinearität

2. Grundlagen

## - Integrale Nichtlinearität (INL oder NL)

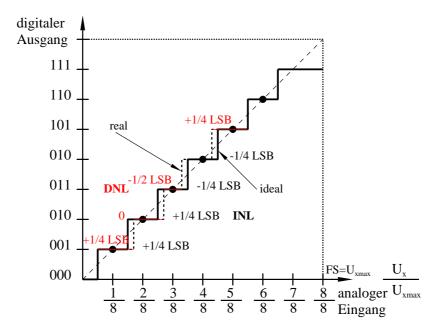

Die Abweichung der Übertragungskennlinie eines AD-Wandlers von der festgelegten Geraden zwischen Null- und Endpunkt bezeichnet man als integrale Nichtlinearität INL bzw. der Linearitätsfehler NL. Dieser Fehler wird in Teilen von LSB gegeben.

## - Differentielle Nichtlinearität (DNL)

Die differentielle Nichtlinearität (DNL) charakterisiert die Abweichung einer Stufenbreite vom Idealwert 1  $U_{LSB}$  an den Umschaltstellen im Inneren des Wandlungsbereiches. Abbildung 2.19 zeigt die integrale und differentielle Nichtlinearität eines AD-Wandlers.

Abbildung 2.19: Integrale und differentielle Nichtlinearität.

## 2.2.4.2 Dynamische Kenngrößen

#### • Umsetzzeit und Umsetzrate

#### - Umsetzzeit

Die Umsetzzeit ist die Zeit, die der AD-Wandler für einen Wandlungszyklus benötigt, vom Eingangsimpuls bis Zur Lieferung des Ausgangssignals.

## - Umsetzrate

Die Umsetzrate bezeichnet die Frequenz, mit der der AD-Wandler die Wandlungszyklen wiederholen kann. Sie ist der Kehrwert der Umsetzzeit.

## • Signal-Rausch-Verhältnis (SNR<sup>7</sup>)

Das SNR ist festgelegt als der Quotient aus der mittleren Signalleistung  $P_S$  und der mittleren Rauschleistung  $P_R$  in einem gegebenen Frequenzbereich. Alternativ kann es als der Quotient aus dem Effektivwert der Signalamplitude (fundamentale Frequenzkomponente) und dem quadratischen Mittelwert von allen anderen Frequenzkomponenten, ausschließlich der ersten fünf Oberwellen und Gleichanteilkomponente, definiert werden [24]. Das Signal-Rausch-Verhältnis wird durch das Abtasten eines sinusförmigen Signals und der nachfolgenden Anwendung der FFT auf die gesammelten Daten, charakterisiert [33]. Das SNR wird anhand der Gleichung:

$$SNR = \frac{P_S}{P_R} = \frac{A_S^2}{A_R^2},$$

(2.17)

bestimmt, wobei  $A_S$ ,  $A_R$  die Effektivwerte der Signal- und Rauschgröße sind. Unter Einbeziehung des Quantisierungsfehlers ist der theoretische SNR-Wert für den idealen AD-Wandler allerdings durch die Gleichung [34]:

$$SNR = (6, 02 \cdot n + 1, 76) \text{ dB}, \tag{2.18}$$

gegeben, wobei n die Bitzahl des AD-Wandlers ist. Diese Gleichung gilt unter der Bedingung, dass das Rauschen über die gesamte Nyquist-Bandbreite von 0 bis zum Wert  $f_s/2$  gemessen wird. Das Quantisierungsrauschen ist in diesem Bereich gleichmäßig verteilt. Ist die Signalbandbreite BW<sup>8</sup>, die sich auf die Differenz zwischen der höchsten Frequenzkomponente eines Signals und der niedrigsten Frequenzkomponente bezieht, kleiner als  $f_s/2$  nimmt das SNR zu, da der Anteil des Quantisierungsrauschens über die Signalbandbreite kleiner ist. In diesem Fall ändert sich (2.18) zur folgenden Gleichung für das Full Scale Sinussignal [34]:

SNR =

$$\left(6,02 \cdot n + 1,76 + 10 \log \left(\frac{f_s}{2 \cdot \text{BW}}\right)\right) \text{ dB.}$$

(2.19)

## • Signal-Rausch-Verhältnis und Verzerrung (SNDR<sup>9</sup>)

In der Gleichung (2.18) wird für das SNR nur das Quantisierungsrauschen berücksichtigt. Werden die anderen Rauschquellen, wie integrale und differentielle Nichtlinearitäten, Verzerrung, und interne Rauschquellen des AD-Wandlers berücksich-

<sup>&</sup>lt;sup>7</sup>engl. Signal-to-Noise Ratio SNR

<sup>&</sup>lt;sup>8</sup>engl. Band Width

<sup>&</sup>lt;sup>9</sup>engl. Signal-to-Noise and Distortion Ratio

2. Grundlagen

tigt, lässt sich der Begriff Signal-Rausch-Verhältnis und Verzerrung SNDR einführen. SNDR wird definiert als Quotient aus dem Effektivwert der Signalamplitude und dem Mittelwert der Wurzel der Summe der Quadrate von allen anderen Frequenzkomponenten einschließlich der ersten fünf Oberwellen aber ausschließlich der Gleichanteilkomponente. Deshalb weicht das SNR von seinem theoretischen Wert in der Gleichung (2.17) ab und sein Messwert wird kleiner [34]. Der reale SNR-Wert (SNDR) wird mit der folgenden Gleichung (2.20) beschrieben.

$$SNDR = (6,02 \cdot ENOB + 1,76) dB,$$

(2.20)

wobei ENOB<sup>10</sup> die effektive Anzahl von Bits ist. Zum Beispiel enspricht ein 12-bit AD-Wandler einem theoretischen SNR-Wert von 74 dB, während der gemessene SNR-Wert (SNDR) 68 dB beträgt und dem ENOB-Wert von 11 Bits entspricht (ENOB = (SNDR - 1, 76)/6, 02) [34].

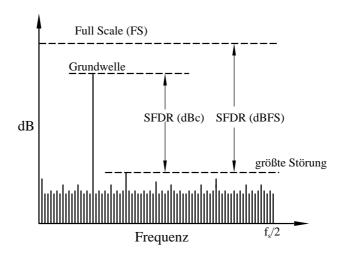

## • Störungsfreier dynamischer Bereich (SFDR<sup>11</sup>)

Der SFDR wird definiert als das Verhältnis der Amplitude der Grundwelle (Eingangssignal) zu der Amplitude der größten Störung (Eingangssignal-unabhängige Komponente) in einem Spektrum. Der SFDR kennzeichnet den dynamischen Bereich eines AD-Wandlers. Er kann relativ zur Signalamplitude (dBc) oder zur AD-Wandler Full Scale (dBFS) angegeben werden, wie in Abbildung 2.20 dargestellt wird.

**Abbildung 2.20:** Illustration des SFDR.

<sup>&</sup>lt;sup>10</sup>engl. Effective Number Of Bits

<sup>&</sup>lt;sup>11</sup>engl. Spurious-Free Dynamic Range

Weitere dynamische Kenngrößen der AD-Wandler sind die gesamte harmonische Verzerrung (THD<sup>12</sup>), gesamte harmonische Verzerrung plus Rauschen (THD+N<sup>13</sup>), etc. Weiterführende Informationen dazu findet man z. B. in [34].

#### 2.2.5 Stand der Technik

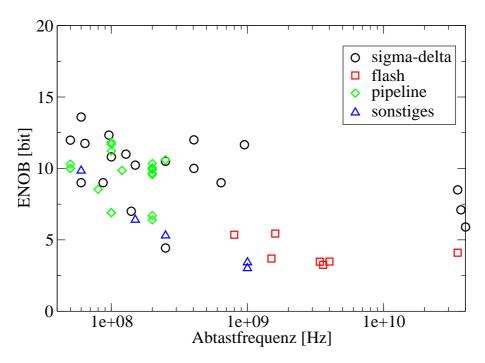

Die verschiedenen Arten von AD-Wandlern haben in den vergangenen 10 Jahren erheblich zum Fortschritt in vielen Anwendungsbereichen beigetragen. 1999 hat Walden [35] in einer Übersicht der AD-Wandler und die Beziehung zwischen ihren Kenngrößen erfasst. Seine Art der Darstellung wird bis heute verwendet. Murmann ergänzte die Übersicht für die Jahre 1997 bis zum 2011 [36], [37]. In dieser Arbeit habe ich eine Studie über die Bewertung und die Klassifizierung von halbleitenden AD-Wandlern in Abhängigkeit von ihren Eigenschaften (oder Kenngrößen) durchgeführt. Diese Studie enthält Informationen über halbleitende AD-Wandler von 2004 bis 2011 [38–84]. Abbildung 2.21 zeigt die Ergebnisse dieser Studie bezüglich der Abhängigkeit zwischen ENOB und Abtastrate für mehrere Arten von AD-Wandlern. Aus der Abbildung kann man entnehmen, dass die Sigma-Delta-AD-Wandler eine hohe Auflösung schaffen, im Gegensatz zu Flash AD-Wandlern, die für höhere Abtastraten mit kleineren Auflösungen geeignet sind. Die Pipeline-AD-Wandler stehen dazwischen. Im Folgenden sind exemplarische Realisierungen von AD-Wandlern in der Halbleitertechnik und Supraleitertechnik aufgeführt:

- In [39] hat eine Gruppe der Pohang University of Science and Technology (PO-STECH) aus Korea einen AD-Wandler mit einer Auflösung von 10 Bit und einer Abtastrate von 100 kS/s (kilosample pro Sekunde) entworfen. Der Wandler wurde in einem  $0.18\,\mu\mathrm{m}$  CMOS-Prozess hergestellt. Dabei wurden  $1.3\,\mu\mathrm{W}$  Leistung bei der maximalen Abtastrate umgesetzt. Das gemessene ENOB beträgt  $9.3\,\mathrm{Bit}$ .

- Eine Serie von Nulldurchgang-AD-Wandlern mit 8 Bit Auflösung und einer Abtastrate von 200 MS/s bis hinzu 12 Bit und 50 MS/s werden in [40] vorgestellt. Diese Art von AD-Wandlern zeigt einen sehr niedrigen Leistungsumsatz.

- Der Entwurf von AD-Wandlern, die nicht auf Spannungskompratoren basieren sondern auf Verzögerungsleitungen (engl. delay lines), wird in [43] dargestellt. Zwei 4-Bit , 1-GS/s-Prototypen in 0,13- $\mu$ m und 65-nm CMOS Prozessen, die einen niedrigen Leistungsumsatz (< 2,4 mW) zeigen, werden vorgestellt.

<sup>&</sup>lt;sup>12</sup>engl. Total Harmonic Distortion

<sup>&</sup>lt;sup>13</sup>engl. Total Harmonic distortion plus Noise

2. Grundlagen

Abbildung 2.21: ENOB in Abhängigkeit von der Abtastrate für mehrere Arten von AD-Wandlern.

- Eine experimentelle Studie in [44] zeigt, wie man die Zunahme der Prozessänderungen in Nano-CMOS-Technologien nutzt, um AD-Wandler mit niedriger Energie und hoher Geschwindigkeit zu realisieren. Insbesondere kann man auf ein Referenzspannungsnetzwerk von 4-Bit Flash AD-Wandlern in 90-nm CMOS verzichten und gegen kleine Komparatoren austauschen. Die gemessene Leistung eines 1,5-GS/s AD-Wandlers ist vergleichbar mit traditionellen state-of-the-art AD-Wandlern und hat eine Verlustleistung von 23 mW.

- In [48] wird ein 0,9-V 1-Bit Sigma-Delta-Modulator vierter Ordnung mit einer Abtastfrequenz von 2 MHz und einer Signalbandbreite von 2 kHz vorgestellt. Der Modulator zeigt einen Leistungsumsatz von  $60\,\mu\mathrm{W}$  und einen Dynamikbereich von 83 dB.

- Ein 0,6-V Sigma-Delta-Modulator Modulator wird in [47] diskutiert. Der Modulator wird mittels einer 0,13-μm komplementären Metal-Oxid Halbleitertechnologie implementiert. Das Subthreshold-leakage-Strom Problem in Switched-Capacitor-Schaltungen wird analysiert und es werden neue Switches für die Subthreshold-leakage Unterdrückung verwendet, um das Problem zu lösen. Mit den neuen Switches hat der Modulator einen Dynamikbereich von 83 dB, ein SNR von 82 dB und

ein SNDR von 34 dB bei einer Bandbreite von 20kHz und einen Leistungsumsatz von 34  $\mu$ W.

- In [85] hat eine Forschungsgruppe des Superconductivity Research Laboratory des International Superconductivity Technology Center in Tokyo (Japan), einen 5-bit Flash SFQ AD-Wandler entworfen und geprüft, welcher CQOS (complementary Quasi One Junction SQUID) Komparatoren benutzt. Die CQOS-Komparatoren sind mit Fehlerkorrektur und Bit-Interleaving-Schaltungen integriert. Sie haben die 3-Bit binär-Operation bei einer Taktfrequenz von 15 GHz und 4-bit Gray Operation bei 15 GHz mittels der beat-Frequenz Methode [86] in einem 4-bit Komparator bestätigt. Sie sind extra schnell: bis zu 32 GHz bei J<sub>c</sub> = 2,5 kA/cm² und bis zu 50 GHz bei J<sub>c</sub> = 10 kA/cm².

- Eine Forschergruppe des Superconductivity Research Laboratory des International Superconductivity Technology Center (SRL-ISTEC) (Japan) hat einen neuen Entwurf eines supraleitenden Flash AD-Wandlers mit einer optimierten Linearität vorgestellt. Die Schaltung besteht aus zwei Quasi-One-Junction-SQUIDs, die mit dem Komparator verbunden sind. In Simulationen zeigt der AD-Wandler die Möglichkeit für eine Abtastrate von  $150 \, \text{GS/s}$  bei einer kritischen Stromdichte  $J_c$  von  $40 \, \text{kA/cm}^2$  [87].

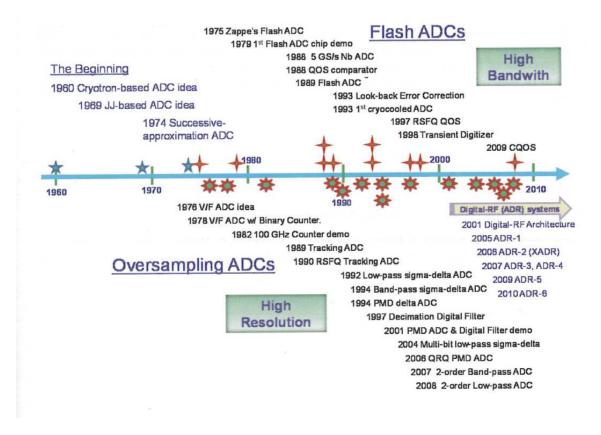

Die hier zusammengefassten Realisierungen sind eine gute Zusammenstellung. Sie sind leider nicht vergleichbar, da die Artikel keine ausreichenden Informationen über gleiche Eigenschaften beinhalten. Eine andere Art der Darstellung findet man auch in der Abbildung 2.22, die aus [18] entnommen wurde und die Entwicklung der supraleitende AD-Wandler von 1960 bis 2010 darstellt.

30 2. Grundlagen

Abbildung 2.22: Die Entwicklung der supraleitenden AD-Wandler [18].

## Kapitel 3

# Komparatoren in der supraleitenden Elektronik

Ein supraleitender Komparator ist das Entscheidungselement in supraleitenden Schaltungen [88]. Er entscheidet, ob ein Strom größer oder kleiner als ein bestimmter Schwellwert ist. Die Leistungsfähigkeit einer Schaltung in Bezug auf Empfindlichkeit, Geschwindigkeit und Zuverlässigkeit wird entscheidend durch die Eigenschaften des Komparators bestimmt. Der Josephson-Komparator ist ein Bestandteil aller digitalen Logikschaltungen und wird unter anderem in supraleitenden AD-Wandlern [89] und in Josephson-Abtast-Schaltungen [90] verwendet.

## 3.1 Grundlagen von Komparatoren

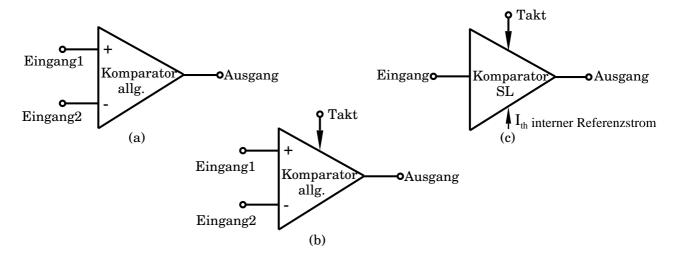

Als Komparator bezeichnet man im Allgemeinen eine Funktionseinheit, die zwei Eingangsgrößen vergleicht und daraus ein Ergebnis bildet. In Abbildung 3.1 sind die Ersatzschaltbilder von drei Komparatorvarianten dargestellt. In der analogen Halbleiterschaltungstechnik ist der Komparator eine ungetaktete Schaltung, die zwei Spannungen vergleicht. Wenn die Differenz dieser Spannungen positiv ist, ist der Ausgangspegel "High", ansonsten ist er "Low". Halbleitende Schaltungen basieren auf Zustandslogik, d. h. alle Gatter ändern ihren Ausgang sofort (oder nach einer Verzögerung) nach der Änderung des Eingangssignales. Supraleitende Schaltungen hingegen basieren auf einer Impulslogik, d. h. es gibt einen Takteingang und die Gatter ändern ihren Ausgang erst wenn die Taktimpulse auftreten. Dabei ist der Josephson-Komparator die am häufigsten verwendete Zelle. In einigen supraleitenden mixed-Signal Schaltungen wird aber auch der

Quasi-One-Junction-SQUID (QOJS)-Komparator [91] verwendet, welcher im Abschnitt 3.3 detaillierter beschrieben wird.

**Abbildung 3.1:** Komparatorschaltbild: (a) analog ohne Takt. (b) analog mit Takt. (c) supraleitender Komparator (immer mit Takt),  $I_{th}$  repräsentiert einen internen Referenzstrom und wird nicht elektrisch eingespeist.

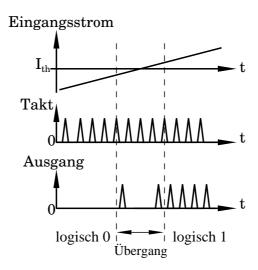

Abbildung 3.2 stellt schematisch die Funktionsweise eines supraleitenden Komparators dar. Ist der Eingangsstrom  $I_{\rm in}$  kleiner als der Schwellwert  $I_{\rm th}$ , werden keine Spannungsimpulse ( $\int u {\rm d}t = \Phi_0$ ) am Ausgang erzeugt. Ist der Eingangsstrom größer als  $I_{\rm th}$ , werden Spannungsimpulse am Ausgang erzeugt. Die Anwesenheit eines Impulses am Ausgang entspricht dem logischen Zustand 1, während seine Abwesenheit den logischen Zustand 0 bedeutet. Im Übergangsbereich in der Nähe von  $I_{\rm th}$  werden die Impulse mit einer Wahrscheinlichkeit zwischen 0 und 1 am Ausgang erzeugt.

## 3.2 Josephson-Komparator

## 3.2.1 Die Schaltung des Josephson-Komparators

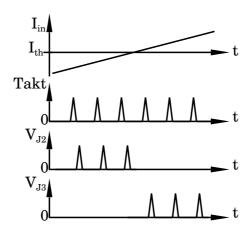

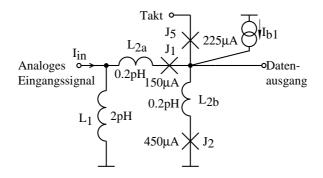

Die Abbildung 3.3 stellt das elektrische Ersatzschaltbild eines Josephson-Komparators dar. Er wird von Taktimpulsen am Takteingang getrieben, um Impulse am Ausgang auszugeben. Die Funktionsweise des Komparators wurde bereits in 2.1.5.3 erklärt. Das folgende Schema 3.4 veranschaulicht die Funktionsweise des Komparators und zeigt schematisch die SFQ-Taktimpulse und die SFQ-Impulse, die durch das Schalten der Kontakte  $J_2$  oder  $J_3$ , in Abhängigkeit vom Eingangsstrom  $I_{\rm in}$ , erzeugt werden. Für Stromwerte  $I_{\rm in} > I_{\rm th}$  gilt,

Abbildung 3.2: Schematische Darstellung der Funktionsweise des supraleitenden Komparators.

Abbildung 3.3: Die Josephson-Komparatorschaltung.

dass ein Taktimpuls zu einem Ausgangsimpuls führt. Dieser wird durch einen Spannungsimpuls am Kontakt  $J_3$  dargestellt. Abbildung 3.5 zeigt die Gesamtschaltung des unter-

**Abbildung 3.4:** Transientes Schaltverhalten eines Josephson-Komparators in Abhängigkeit vom Eingangsstrom.

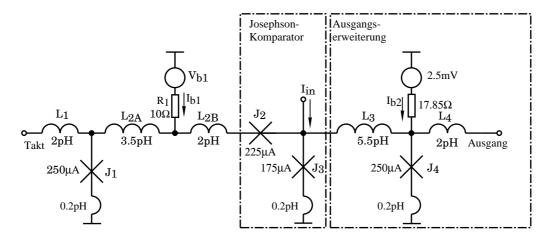

suchten Josephson-Komparators, welche für die Simulation verwendet wurde. Sie ist eine

Erweiterung der in Abbildung 3.3 dargestellten Grundschaltung und beinhaltet sowohl parasitäre Schaltungskomponenten, als auch zusätzliche Josephson-Kontakte, die zur Verringerung von Wechslwirkungen mit angrenzenden Strukturen notwendig sind. Alle

**Abbildung 3.5:** Das elektrische Ersatzschaltbild des untersuchten Josephson-Komparators. Es enthält auch Layout-bedingte parasitäre Induktivitäten. Die Parameter sind real und passen zur IPHT-Technologie mit einer kritischen Stromdichte von  $1 \, \text{kA/cm}^2$ . Das Layout ist in Abbildung 3.22 dargestellt [12].

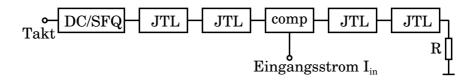

verwendeten Josephson-Kontakte der Schaltung wurden mit dem McCumber-Parameter  $\beta_c = 1$  in IPHT-Technologie entworfen. Parasitäre Induktivitäten sind in Reihe mit den Bedämpfungswiderständen geschaltet, wie in [92] beschrieben wird. Die Untersuchungen wurden mittels des Schaltungssimulators JSIM\_n durchgeführt. Das Programm JSIM\_n ist in der Lage, das thermische Rauschen im Zeitbereich zu simulieren [93]. Die Ergebnisse werden in den nächsten Abschnitten diskutiert. Das Blockschaltbild der verwendeten Simulationsumgebung zeigt die Abbildung 3.6. Sie besteht aus dem Komparator, einem

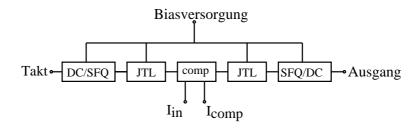

Abbildung 3.6: Die Simulationsumgebung der untersuchten Schaltung.

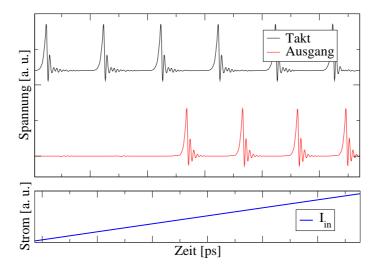

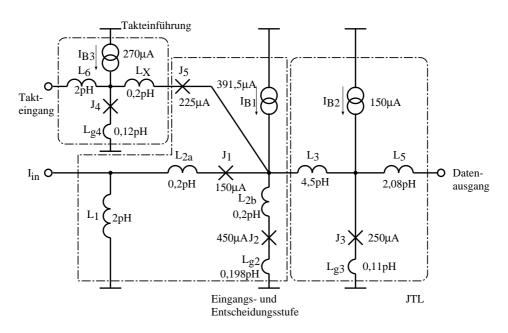

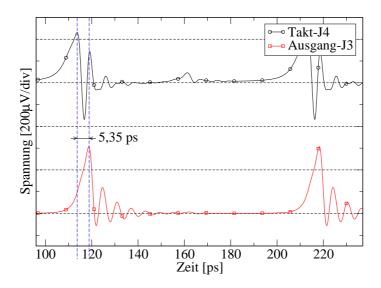

DC/SFQ-Wandler, der die SFQ-Impulse erzeugt und Josephson-Übertragungsleitungen (JTL), die zur Übertragung der Flussquanten und zur Entkopplung der Schaltungsteile dienen. Für einen angepassten Abschluss wird ein Widerstand R verwendet. Der Biasstrom  $I_{b1}$  wird bei der Messung auch extern eingestellt. Abbildung 3.7 zeigt das Simulationsergebnis bestehend aus Takt- und Ausgangsimpulsen gesteuert durch den Ein-

gangsstrom. In der Abbildung sieht man, dass der Komparator ab einem bestimmten Eingangsstrom Spannungsimpulse am Ausgang erzeugt, wenn Taktimpulse auftreten.

Abbildung 3.7: Die simulierte Funktionsweise des Josephson-Komparators mit den Spannungsimpulsen des Takt- und Ausgangssignales in Abhängigkeit vom Eingangsstrom.

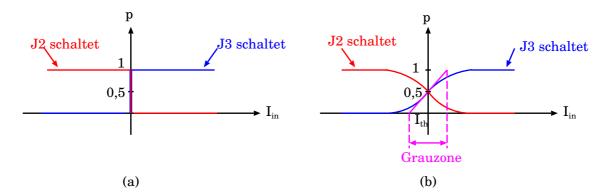

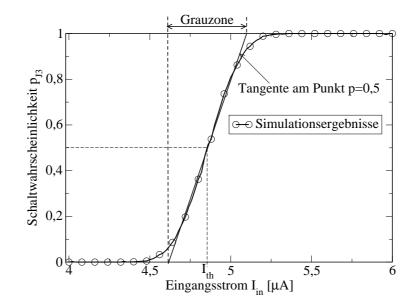

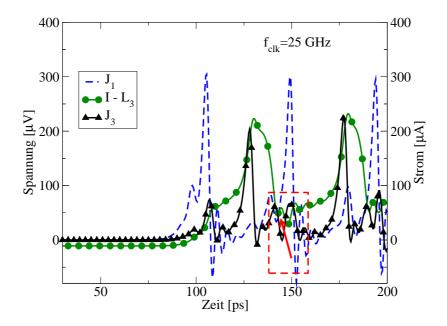

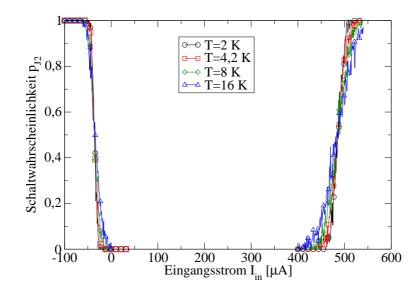

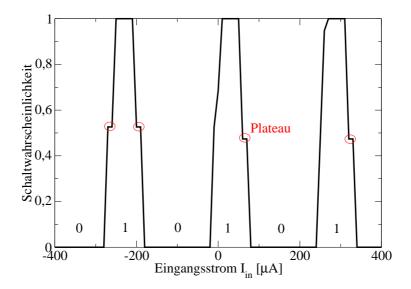

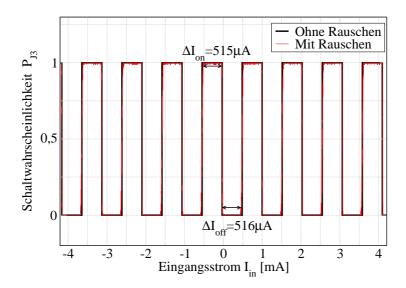

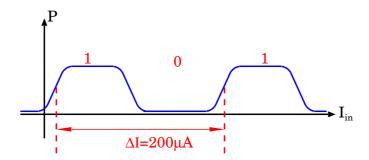

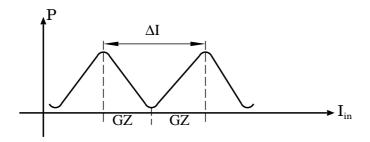

### 3.2.2 Die Grauzone als Kenngröße des Josephson-Komparators

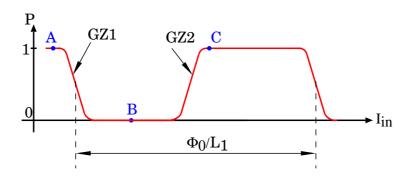

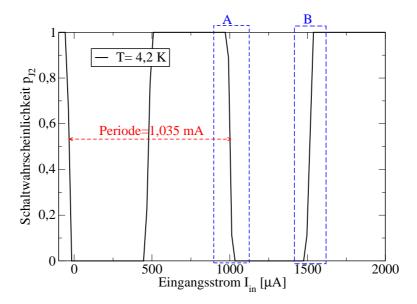

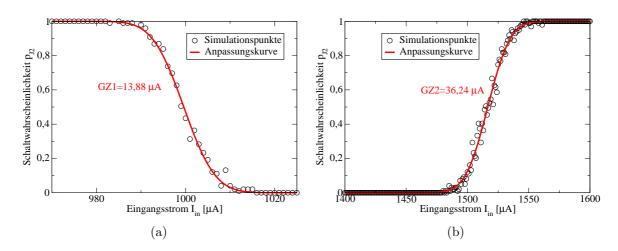

Einer der wichtigsten Begrenzungsparameter eines Josephson-Komparators ist die Breite der Grauzone, welche die Entscheidungsunsicherheit des Komparators beschreibt. Bei der Datenverarbeitung in supraleitenden Schaltungen wird die Entscheidung des Komparators hauptsächlich durch das thermische Rauschen beeinflusst, wodurch ein Übergangsbereich mit endlicher Breite, die sogenannte Grauzone, entsteht [94]. Das thermische Rauschen entsteht sowohl durch die Bedämpfungswiderstände der Josephson-Kontakte als auch durch die Widerstände des Biasnetzwerkes. Abbildung 3.8 zeigt schematisch den Übergangsbereich zwischen 1-0 und 0-1 beim Schalten von  $J_2$  und  $J_3$ , der im idealen Fall scharf sein muss. In realen Schaltungen entsteht ein kontinuierlicher Übergang, den man die Grauzone nennt. Eine typische Simulation der Schaltwahrscheinlichkeit des Komparator-Kontaktes  $J_3$  in Abhängigkeit vom Eingangsstrom wird in Abbildung 3.9 dargestellt. Die mathematische Definition der Grauzone (GZ) erfolgt durch den Anstieg m der Tangente an die Kurve (siehe Abbildung 3.9) am Punkt p=0,5 wie folgt:

$$m = \frac{1}{GZ} \Rightarrow GZ = \frac{1}{m}. (3.1)$$

**Abbildung 3.8:** Schematische Darstellung der Schaltwahrscheinlichkeit von  $J_2$  und  $J_3$  gegenüber dem Eingangsstrom  $I_{in}$ : (a) idealer Fall, (b) realer Fall.

**Abbildung 3.9:** Schaltwahrscheinlichkeit  $p_{J3}$  gegenüber dem Eingangsstrom  $I_{in}$ .

Die Kurve in Abbildung 3.9 kann mittels einer Fehlerfunktion beschrieben werden, die die Grauzone (GZ) als Parameter enthält (siehe [95]).

$$p_3(I_{\rm in}) = 0, 5 + 0, 5 \cdot \text{erf}\left((I_{\rm in} - I_{\rm th}) \cdot \frac{\sqrt{\pi}}{GZ}\right),$$

(3.2)

In der Gleichung (3.2) beschreibt  $I_{\text{in}}$  den Eingangsstrom (siehe Abbildung 3.6) und erf die Fehlerfunktion.

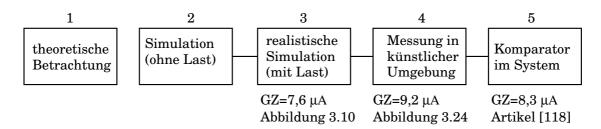

# 3.2.3 Einflussgrößen auf das Verhalten des Josephson-Komparators

Die vorangegangenen Untersuchungen behandelten die Parametereinflüsse auf die Grauzone und die Schaltgeschwindigkeit des Komparators. Davon wurden Entwurfsregeln abgeleitet, um die Grauzone zu minimieren [96, 97]. Diese Regeln wurden experimentell bestätigt. In den nächsten Abschnitten werden die Untersuchungen der Grauzone und der Taktfrequenz, des Biastromes, etc. gezeigt.

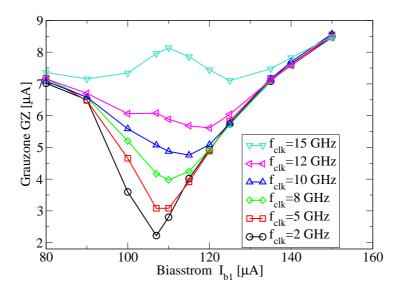

# 3.2.3.1 Untersuchung der Abhängigkeit zwischen der Grauzone und dem Biasstrom $I_{\rm b1}$

Die Beziehung zwischen der Grauzone und dem Biasstrom  $I_{\rm b1}$  für verschiedene Taktfrequenzen eines Josephson-Komparators wurde untersucht. Abbildung 3.10 zeigt die dazu gehörigen Simulationsergebnisse. Diese Illustration ist besonders hilfreich, um einen Komparator für eine Anwendung mit vorgegebener Taktfrequenz zu entwerfen, z. B. die Anwendungen der AD-Wandler. Ein Arbeitspunkt mit möglichst niedriger Grauzone kann

**Abbildung 3.10:** Grauzone gegen den Biasstrom  $I_{\rm b1}$  für verschiedene Taktfrequenzen.

für eine definierte Taktfrequenz gewählt werden. Der analysierte Komparator nach Abbildung 3.5 liefert eine kleinste Grauzone von  $2,2\,\mu\mathrm{A}$  nur für einen einzelnen Arbeitspunkt und für niedrige Frequenzen. Wegen der aus dem Herstellungsprozess resultierenden Parameterstreuung ist es unwahrscheinlich, diesen Arbeitspunkt genau zu treffen.

Für AD-Wandler mit einer kleinen Zahl von Quantisierern ist es praktisch, getrennte Abstimmungsströme zu verwenden, um den Arbeitspunkt individuell justieren zu können. Infolgedessen ist  $GZ=2,2 \mu A$  eine realistische Untergrenze für die Empfindlichkeit eines Quantisierers in der analysierten Schaltungstopologie. Bezüglich der Empfindlichkeit gibt es einen optimalen  $I_{\rm b1}$ , der die kleinste Grauzone gewährleistet. Für diese bestimmte Topologie ist der optimale Wert  $I_{\rm b1}=107\,\mu{\rm A}$  mit einer  $2,2\,\mu{\rm A}$  Grauzone. Für größere Werte von  $I_{\rm b1}$  nimmt die Grauzone zu. Der Biasstrom beeinflusst die Entscheidungsgeschwindigkeit am Komparator. Der nominale Arbeitspunkt liegt bei  $I_{\rm b1}=140\,\mu{\rm A}.$  Je höher der Strom ist, desto schneller ist die Entscheidung. Das entspricht einer größeren Bandbreite und somit einer Vergrößerung des integralen Rauschens. Daraus folgt eine größere Grauzone. Für kleinere Stromwerte verkleinert sich die Grauzone, weil die Entscheidungszeit am Komparator zunimmt, d. h. der Komparator wird langsamer. Die längere Zeit erlaubt, den Einfluss des Rauschens bei hohen Frequenzen durch die Mittlung zu beseitigen und dabei die Bandbreite (siehe [93]) zu reduzieren. Damit nimmt die Grauzone mit Abnahme des Biasstromes ab. Unterhalb des minimalen Grauzonenwertes  $(I_{\rm b1} < 107 \,\mu{\rm A})$  ist die normale Funktion des Komparators gestört. Es wird ein Flussquant gespeichert, was zu einer Verschiebung des Biasstromes führt. Genauere Untersuchung dieser Verschiebung ist in [32] zu finden.

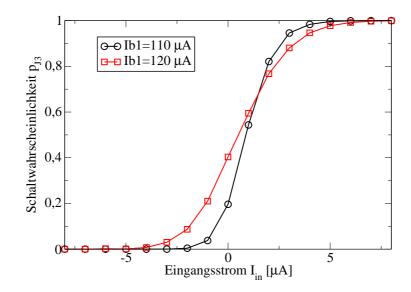

Der Schaltungsentwurf hat Parameter und die hergestellt Schaltung besitzt ungefähr diese Parameter. Auch in supraleitenden Schaltungen muss jeder Entwurfsparameter einen ausreichenden breiten Toleranzbereich (Margin) besitzen, in dem die Schaltungsfunktionalität erhalten bleibt. Oder auch in dem Fall, wenn die Schaltung mit der gleichen Charaktersitik bei verschiedenen Frequenzen arbeiten muss. In beiden Fällen ist es ratsam, eine höhere Grauzone zu akzeptieren und einen höheren Biasstrom zu verwenden, weil bei diesem Strom ein breiterer Frequenzbereich mit einer konstanten Grauzone besteht. Zum Beispiel kann ein Biasstrom  $I_{b1}=140\,\mu\text{A}$  mit einer akzeptablen Grauzone (GZ=7,6  $\mu$ A) für alle Taktfrequenzen bis 15 GHz vorgeschlagen werden. Für einen kleineren Biasstrom z. B.  $I_{b1}=120\,\mu\text{A}$  erhält man zwar eine kleinere Grauzone aber damit muss der Komparator mit kleineren Taktfrequenzen bis 8 GHz arbeiten. Abbildung 3.11 zeigt Simulationen der Schaltwahrscheinlichkeit in Abhängigkeit vom Eingangsstrom für zwei Biasströme  $I_{b1}=110\,\mu\text{A}$  und 120  $\mu\text{A}$  für eine Taktfrequenz von 2 GHz. Man kann sehen, dass die Kurve für 110  $\mu\text{A}$  steiler und damit die Grauzone für 110  $\mu\text{A}$  kleiner ist als die für 120  $\mu\text{A}$ .

**Abbildung 3.11:** Schaltwahrscheinlichkeit von  $J_3$  in Abhängigkeit vom Eingangsstrom für zwei Biasströme  $I_{\rm b1}$ =110  $\mu A$  und 120  $\mu A$  für eine Taktfrequenz von 2 GHz.

# 3.2.3.2 Untersuchung der Grauzone in Abhängigkeit von der Taktfrequenz eines Josephson-Komparators

Die Komparatorschaltung in Abbildung 3.5 wurde untersucht, um die Abhängigkeit der Grauzone von der Taktfrequez für einen vorgegebenen Biasstrom  $I_{\rm b1}$  zu bestimmen. Die Motivation besteht darin, eine maximale Taktfrequenz  $f_{\text{max}}$  herauszufinden, bis zu der die Grauzone konstant bleibt. Die Analysen von verschiedenen Komparatorschaltungen [97] zeigen, dass die Grauzone für festgesetzte kritische Ströme von Josephson-Kontakten am empfindlichsten bezüglich  $I_{\rm b1}$  ist. Der zweite Biasstrom  $I_{\rm b2}$  beeinflusst lediglich den Schwellstrom  $I_{th}$ . Für die im Artikel [97] behandelte Technologie habe ich eine Untersuchung der Frequenzabhängigkeit der Grauzone durchgeführt. Die Schaltung wurde für 10000 Taktzyklen simuliert, die 10000 Schaltvorgänge von J<sub>1</sub> gewährleistet. Zählt man die Anzahl der Schaltvorgänge von  $J_3$  ( $n_{J3}$ ), kann die Schaltwahrscheinlichkeit anhand der folgenden Formel  $p(I_{in}) = \frac{n_{J3}}{10000}$  ermittelt werden. Die Schaltung wurde für drei Technologien (IPHT Deutschland [98], AIST Japan [99] und CEA Frankreich [100]) untersucht. Die Parameter dieser Technologien werden in der folgenden Tabelle 3.1 dargestellt. Es ist erwähnenswert in Bezug auf diese Tabelle, dass der McCumber-Parameter für die Technologien IPHT und AIST durch den Dämpfungswiderstand eingestellt werden kann. Im Gegensatz dazu ist der McCumber-Parameter für die Technologie CEA nicht einstellbar und technologiebedingt, wodurch die Schaltung stabil funktioniert. Unter der Annahme, dass der kritische Strom jedes Josephson-Kontaktes für alle Technologien gleich bleibt, kann man die Fläche der Barriere A mittels der folgenden Gleichung berechnen.

$$A = I_c/J_c. (3.3)$$

Weiterhin ergeben sich die Kapazität des Josephson-Kontaktes  $C_J$  und der Dämpfungswiderstand  $R_n$  mit Hilfe der folgenden Gleichungen [101]:

$$C_J[pF] = 0.01 \cdot A/(0.20 - 0.043) \log_{10}(J_c),$$

(3.4)

$$R_n = \sqrt{\phi_0/2\pi C_J I_c},\tag{3.5}$$

wobei die Einheiten für  $A \mu m^2$  und  $J_c kA/cm^2$  sind. Mittels der Gleichung (2.9) lässt sich  $\beta_c$  berechnen.

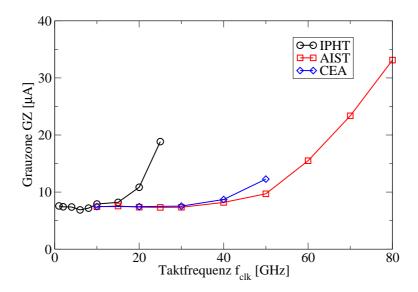

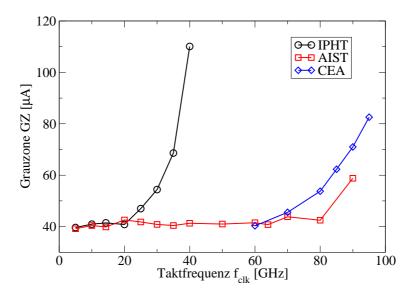

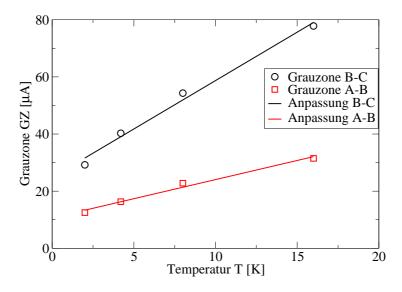

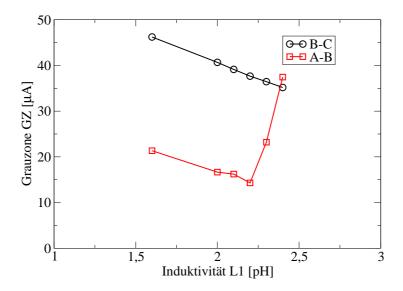

Abbildung 3.12 zeigt die Simulationsergebnisse für die Abhängigkeit der Grauzone von

| Technologie                     | $J_c [{ m kA/cm^2}]$ | $I_c \cdot R_n[\text{mV}]$ | $\beta_c$ |

|---------------------------------|----------------------|----------------------------|-----------|

| IPHT [98]                       | 1                    | 0,256                      | 1         |

| MIT-LincolnLab [102], AIST [99] | 10                   | 0,7175                     | 1-2       |

| CEA [100]                       | 30                   | 0,6                        | 0,04      |

**Tabelle 3.1:** Die kritische Stromdichte und die charakteristische Spannung der drei Technologien und der berechnete McCumber-Parameter.

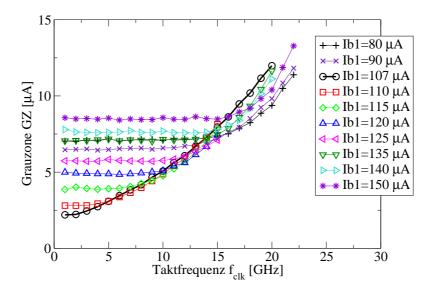

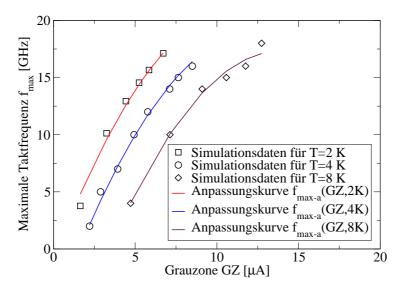

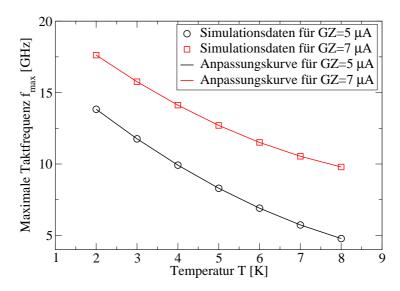

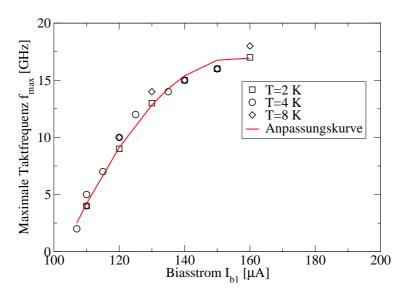

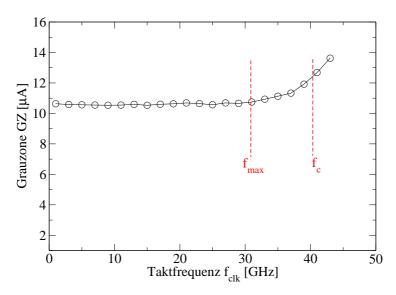

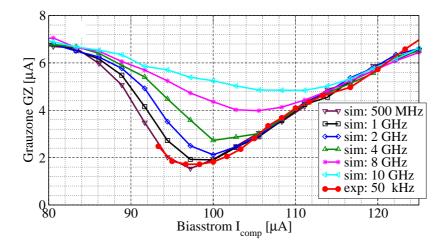

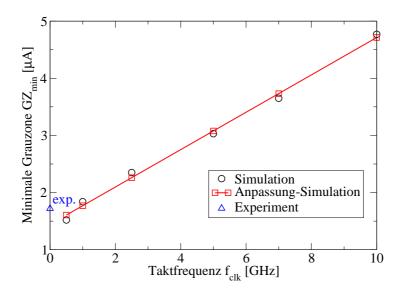

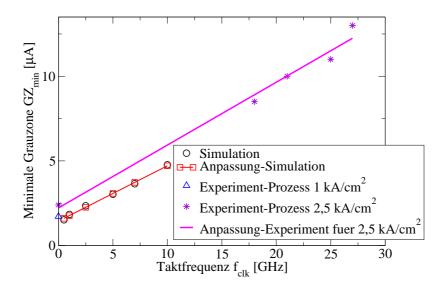

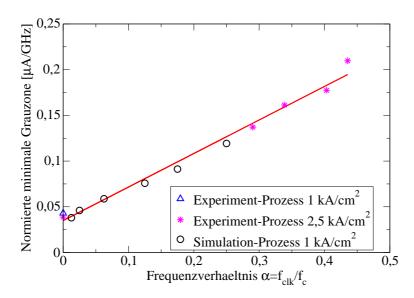

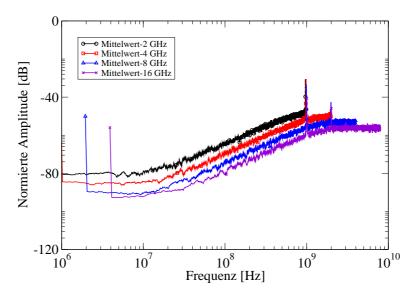

der Taktfrequenz für die drei obengenannten Technologien. Bei der IPHT-Technologie bleibt die Grauzone konstant bis zu einer Taktfrequenz von  $f_{\rm max}=10\,{\rm GHz}$ . Bei der AIST-Technologie und der CEA-Technologie kann der Komparator bis zu einer Taktfrequenz  $f_{\rm max}=35\,{\rm GHz}$  und  $f_{\rm max}=30\,{\rm GHz}$  entsprechend betrieben werden, ohne die Empfindlichkeit zu beeinflussen. Am Beispiel der IPHT-Technologie werden in dieser Arbeit genauere Analysen durchgeführt. Die Simulationen erfolgten für verschiedene Biasströme  $I_{\rm b1}$  und für verschiedene Taktfrequenzen. Der Biasstrom wurde von  $80\,\mu{\rm A}$  bis  $150\,\mu{\rm A}$  variiert. Die Abbildung 3.13 zeigt die Ergebnisse dieser Simulation. Allerdings zeigen die Untersuchungen auch, dass die Grauzone bis zu einer bestimmten Taktfrequenz, die als  $f_{\rm max}$  bezeichnet wurde, konstant ist. Im Gegensatz zu den Ergebnissen des Komparators ohne Schnittstelle zur supraleitenden Elektronik (Abbildung 3.18) wird  $f_{\rm max}$  von 35 GHz zu 18 GHz reduziert. Von den Kurven in Abbildung 3.13 wurde der Wert von  $f_{\rm max}$  so bestimmt, dass die Differenz benachbarter Grauzonenwerte nicht größer als  $0.2\,\mu{\rm A}$  ist. Dieses Kriterium von  $0.2\,\mu{\rm A}$  wurde gewählt, um kleine zufällige Variationen der Grau-

**Abbildung 3.12:** Die Grauzone des Komparators in Abhängigkeit von der Taktfrequenz für drei Technologien bei einem Biasstrom von  $I_{\rm b1}=140\,\mu A$ .

**Abbildung 3.13:** Die Grauzone gegenüber der Taktfrequenz für verschiedene Biasströme  $I_{\rm b1}$  des in Abbildung 3.5 dargestellten Komparators.

zone, die in den Simulationen auftreten, vernachlässigen zu können. Für  $I_{\rm b1}=100\,\mu{\rm A}$  existiert kein Plateau in der Funktion der Grauzone gegen die Taktfrequenz, da die Schaltung für diesen Wert nicht mehr richtig funktioniert. Folglich kann kein Wert von  $f_{\rm max}$  definiert werden. Die folgende Tabelle 3.2 und die Abbildung 3.14 fassen die Werte der Biasströme,  $f_{\rm max}$  und Grauzone zusammen. Innerhalb des Bereiches, in dem die Grauzone konstant ist, wurde der Mittelwert der Grauzonenwerte berechnet.

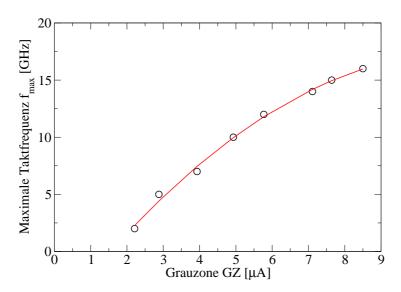

Der Zusammenhang zwischen  $f_{\text{max}}$  und der Grauzone wird durch eine quadratische Funk-

| $I_{\rm b1}[\mu{\rm A}]$ | $GZ [\mu A]$ | $f_{\rm max}  [{ m GHz}]$ |

|--------------------------|--------------|---------------------------|

| 80                       | 7,15         | 16                        |

| 90                       | 6,55         | 13                        |

| 107                      | 2,21         | 2                         |

| 110                      | 2,88         | 5                         |

| 115                      | 3,93         | 7                         |

| 120                      | 4,93         | 10                        |

| 125                      | 5,77         | 12                        |

| 135                      | 7,11         | 14                        |

| 140                      | 7,64         | 15                        |

| 150                      | 8,5          | 16                        |

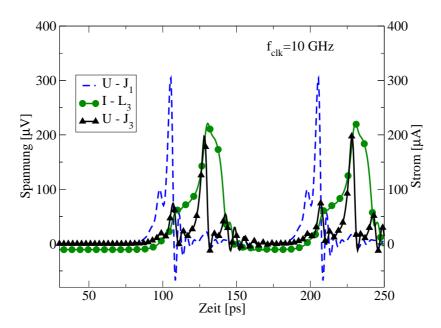

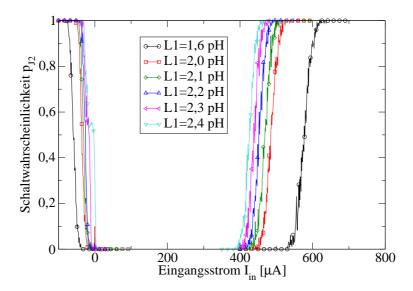

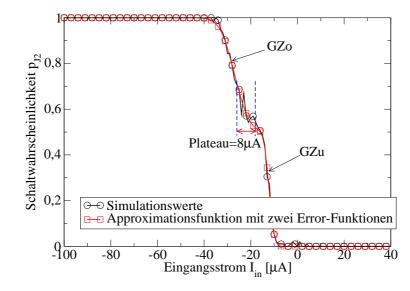

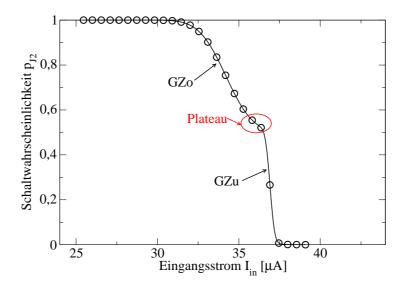

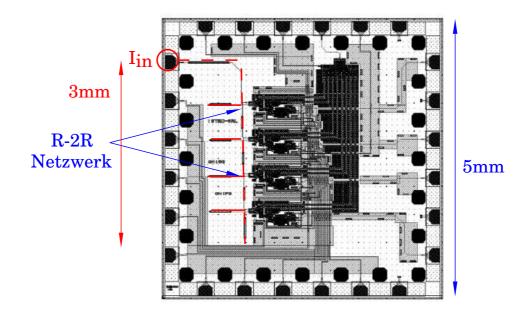

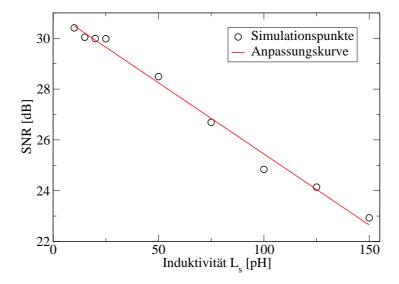

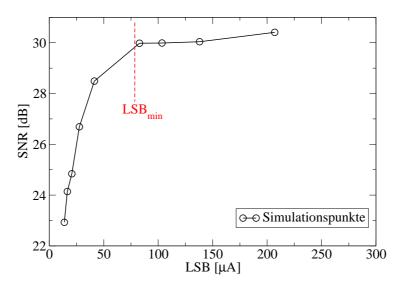

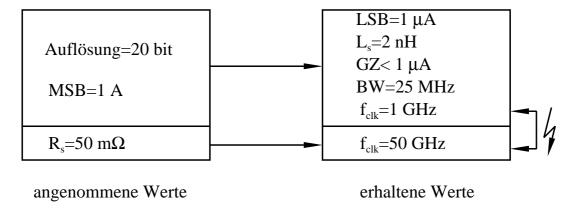

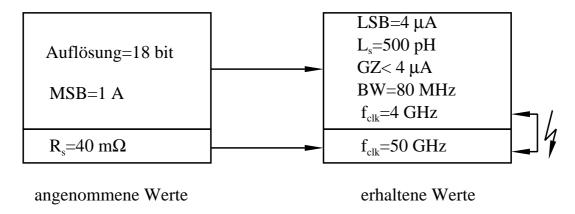

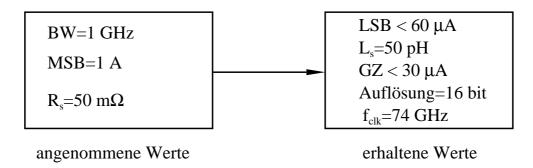

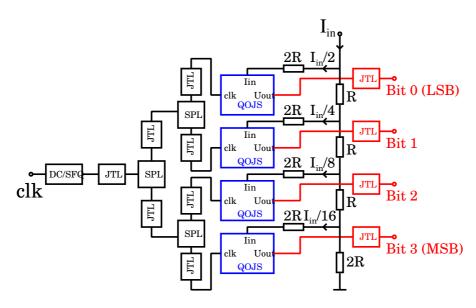

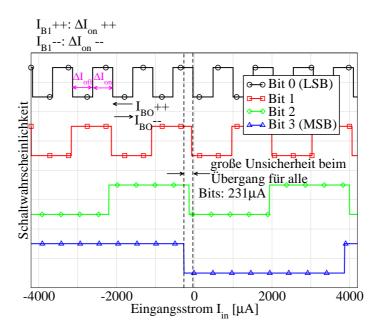

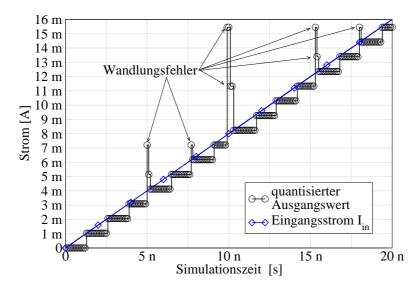

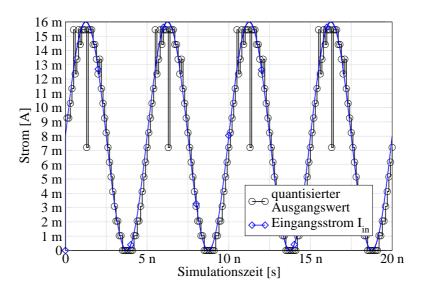

**Tabelle 3.2:** Die Simulationsergebnisse  $(f_{\text{max}}, GZ)$  für verschiedene Biasströme.