# Zertifizierbarer Entwicklungsprozess für komplexe Informationsverarbeitungssysteme in der Wägetechnik

**Irina Kaiser** Vorläufersystem Prototypenentwicklung flexible leistungsfähige Plattform **Produktentwicklung** ZEfIRA systemoptimierte und angepasste Plattform

Zertifizierbarer Entwicklungsprozess für komplexe Informationsverarbeitungssysteme in der Wägetechnik

# Zertifizierbarer Entwicklungsprozess für komplexe Informationsverarbeitungssysteme in der Wägetechnik

#### DISSERTATION

# zur Erlangung des akademischen Grades Doktoringenieur (Dr.-Ing.)

vorgelegt der

Fakultät für Informatik und Automatisierung

der Technischen Universität Ilmenau

von

MSc. Dipl.-Ing. Irina Kaiser (geb. Gushchina)

geboren am 12. Mai 1986 in Moskau

vorgelegt am: 09.04.2015

Tag der wissenschaftlichen Aussprache: 26.10.2015

Gutachter: 1) Univ.-Prof. Dr.-Ing. habil. Wolfgang Fengler

2) Univ.-Prof. Dr.-Ing. habil. Thomas Fröhlich

3) Prof. Dr.-Ing. Klaus-Dietrich Kramer

urn:nbn:de:gbv:ilm1-2015000588

#### Kurzfassung

Die vorliegende Dissertation befasst sich mit Prinzipien, Methoden und Techniken der systematischen Entwicklung von komplexen Eingebetteten Systemen, vorwiegend für den Einsatz in der Messtechnik. Die betrachtete Domäne besitzt Anwendungsbereiche mit anspruchsvollen und besonderen Anforderungen an die Informationsverarbeitung. In der dynamischen Wägetechnik sind z.B. Lösungen mit sehr hohen Auflösungen und kleiner Messunsicherheit bei schnellen Messungen in einem mechanisch gestörten Umfeld notwendig. Die Anforderungen an die Eichfähigkeit und die Metrologische Sicherheit sind Besonderheiten dieser Domäne. Es werden komplexe und hochleistungsfähige Funktionen zur Erzeugung der Messergebnisse verlangt, deren Implementierung mit entsprechender Reaktionszeiten, Rechen- und Kommunikationsleistungen realisiert werden muss. In der Arbeit werden dafür vorwiegend FPGA-basierte Eingebettete Systeme verwendet.

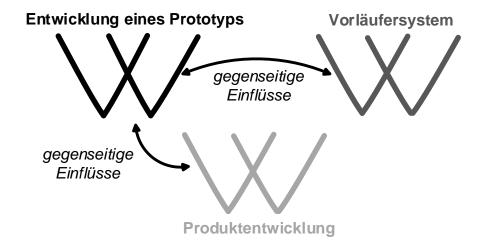

Der entworfene zertifizierbare Prozess (ZEfIRA) bietet eine Vorgehensweise für die Entwicklung von Eingebetteten Systemen. Die Metrologische Sicherheit, die Eichfähigkeit, die Validier- und der Verifizierbarkeit werden als Kriterien im gesamten Entwurfsprozess berücksichtigt. ZEfIRA basiert auf einem 3W-Modell und ist evolutionär angelegt. Innerhalb des Prozesses werden die Analyse eines eventuellen Vorläufersystems sowie die modellbasierte prototypische Entwicklung bis hin zu einer produzierbaren Lösung (Produkt) durchgeführt.

Die vorliegende Arbeit verdeutlicht den großen Einfluss der spezifischen Anforderungen an das Messsystem. Es wird gezeigt, wie diese bereits zu der Entwurfszeit auf Modellebene und im Weiteren bei der Implementierung in einer FPGA-basierten Zielplattform berücksichtigt werden. In der Arbeit werden verschiedene Schritte des funktionalen und technischen Systementwurfs untersucht, wobei ausführlich die Realisierungspartitionen "FPGA-Logik" und "FPGA-Softcore-Lösungen" betrachtet.

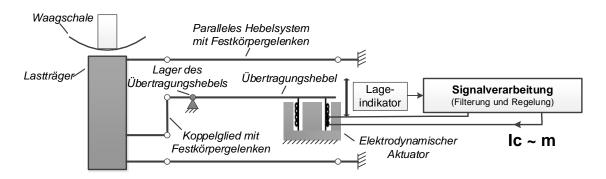

Als Demonstrationsbeispiel zum Nachweis der Anwendbarkeit des Prozesses ZEfIRA inklusive der erarbeiteten Methoden und Prinzipien dient die prototypische Entwicklung des Informationsverarbeitungssystems einer elektromagnetischen Kraftkompensationswaage (EMKW). Ausschlaggebend sind zum einen die optimal an das Gesamtsystem angepassten Signalverarbeitungs-, Regelungs- und Sicherheitsalgorithmen und zum anderen deren technische Umsetzung. Dieses wurde mit verschiedenen Leistungsparametern, wie z.B. Latenz, Verarbeitungskomplexität und Genauigkeit realisiert. Ergänzend ermöglicht der Prototyp umfassende Analysemöglichkeiten für das Einbettende System. Die abschließende Wertung ist eine Abschätzung der Leistungsfähigkeit von ZEfIRA auf Basis dieser prototypischen Entwicklung.

#### **Abstract**

The dissertation is about principles, methods and techniques during the systematic development of embedded systems in the domain of measurement techniques. The considered domain contains fields of application with challenging and specific requirements of the information processing system. For example, the dynamic weighing systems need solutions with very high resolution and lowest achievable measurement uncertainty in order to perform high-speed-measurements in a mechanically disturbed environment. In particular, the abilities for official calibration and metrologic reliability are considered. The complex and high-performance functions are required to guarantee measurement results with appropriate computation power, response time and communication performance. FPGA-based embedded systems are used for the implementation of these functions.

The especially designed certifiable development process (ZEfIRA) provides a procedural method for the development of complex embedded systems. The metrologic reliability, the legal requirements like calibratability, the validation and the verification are included as a general criteria in the entire development process. ZEfIRA is based on the 3W-model and is designed in an evolutionary manner. This process starts with the analysis of a predecessor system followed by the model-based development of a prototype, which leads into an optimized and application-specific product solution.

The study emphasizes the influence of challenging requirements on the measurement system. It will be presented, how these can be integrated into the modelling level during the design and the implementation on a FPGA-based target platform. The stages of the functional and technical design of the system are analysed, whereas the realization of the partitions "FPGA logic" and "FPGA softcore solutions" are discussed in detail.

Based on the preliminary design of the information processing in an electromagnetic force compensation (EMC) scale, the applicability of the process ZEfIRA and its developed methods and principles are proved. On the one hand, the optimal system-specific algorithms of signal processing, control and safety and on the other hand whose technical implementation are essential. This was realized with different performance parameters, for example short latency, processing complexity and precision. In addition, the prototype allows the possible comprehensive analysis for embedding system. In the conclusion, the performance of ZEfIRA based on the prototype development is evaluated.

#### Inhaltsverzeichnis

| Kurz         | zfassung                                                                                                                    | III  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------|------|

| Abst         | ract                                                                                                                        | IV   |

| Inha         | ltsverzeichnis                                                                                                              | V    |

| Abbi         | ildungsverzeichnis                                                                                                          | VIII |

| Tabe         | ellenverzeichnis                                                                                                            | X    |

| Abk          | ürzungsverzeichnis                                                                                                          | .XI  |

| Danl         | ksagung                                                                                                                     | KIII |

| 1 <b>E</b> i | inleitung                                                                                                                   | 1    |

| 1.1          | Aufgabenstellung und Motivation                                                                                             | 2    |

| 1.2          | Ziele des Forschungsvorhabens                                                                                               | 4    |

| 1.3          | Inhalt der Arbeit                                                                                                           | 5    |

|              | llgemeine Aspekte der Informationsverarbeitung in der Messtechnik<br>nhand der Wägetechnik                                  | 7    |

| 2.1          | Grundbegriffe und Definitionen in der Messtechnik                                                                           | 8    |

| 2.2          | Eichfähigkeitsanforderungen: Gesetze, Vorschriften und Richtlinien                                                          | 12   |

| 2.3          | Digitale Informationsverarbeitung in der Messtechnik                                                                        |      |

|              | 2.3.1 Bestehende Prinzipien der digitalen Informationsverarbeitung in der Mess- und Wägetechnik                             |      |

|              | 2.3.2 Gesichtspunkt der Eichfähigkeit und anderer Empfehlungen für die digitale Informationsverarbeitung in der Wägetechnik | 21   |

| 2.4          | Entwicklungsprozesse für die Informationsverarbeitung mit Eingebetteten Systemen                                            | 24   |

|              | 2.4.1 Vorgehensweisen bei der Entwicklung                                                                                   |      |

|              | 2.4.2 Modellbasierte Entwicklung von Eingebetteten Systemen                                                                 |      |

|              | 2.4.2.1 Modelldefinition                                                                                                    | 32   |

|              | 2.4.2.2 Modellbasierter Entwurf und modellbasiertes Testen                                                                  | 33   |

|              | 2.4.2.3 Modellierungswerkzeuge                                                                                              | 36   |

|              | 2.4.3 Implementierungsarten für Hardware-Software-Systeme                                                                   | 38   |

|              | 2.4.3.1 Konventionelle Arten                                                                                                | 39   |

|              | 2.4.3.2 FPGA-basierte Systeme                                                                                               |      |

|              | 2.4.4 Verifikation und Validierung einschließlich Testen                                                                    |      |

|              | 2.4.5 Produktlinien                                                                                                         |      |

| 2.5          | Zusammenfassung und Ableitung der eigenen Arbeiten                                                                          | 48   |

|     | ertifizierbarer Entwicklungsprozesses für<br>nformationsverarbeitungssysteme in der Messtechnik (ZEfIRA) | 52  |

|-----|----------------------------------------------------------------------------------------------------------|-----|

| 3.1 | W-Prozess zur Entwicklung eines Prototyps                                                                |     |

| 3.2 | W-Prozess eines Vorläufersystems.                                                                        |     |

| 3.3 | W-Prozess einer produzierbaren Lösung                                                                    |     |

| 3.4 | Fazit zum 3W-Modell                                                                                      |     |

| 3.5 | Eichfähigkeit und Metrologische Sicherheit in ZEfIRA                                                     |     |

| 3.3 | 3.5.1 Definition und Kriterien                                                                           |     |

|     | 3.5.2 Berücksichtigung der Metrologischen Sicherheit in der Messkette                                    |     |

| 4 P | rozessschritte der effektiven Prototypenentwicklung                                                      | 64  |

| 4.1 | Anforderungsanalyse mit Validierung und Verifikation                                                     |     |

| 4.2 | Funktionaler Systementwurf mit Validierung und Verifikation                                              |     |

|     | 4.2.1 Strukturelle Verfeinerung der Spezifikation                                                        |     |

|     | 4.2.2 Modul zur Analyse von Analog-Digital-Wandlern                                                      |     |

|     | 4.2.3 Funktionen für die Metrologische Sicherheit                                                        | 77  |

| 4.3 | Technischer Systementwurf mit Validierung und Verifikation                                               | 78  |

|     | 4.3.1 Modellbasierter Entwurf des Informationsverarbeitungssystems                                       |     |

|     | 4.3.1.1 Modell des messtechnischen Systems                                                               | 81  |

|     | 4.3.1.2 Modelle von Sicherheitsfunktionen                                                                | 85  |

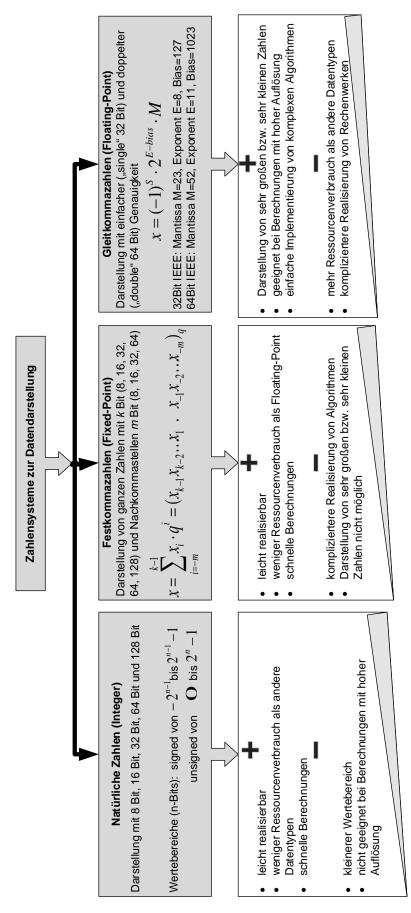

|     | 4.3.2 Plattformunabhängige Datentypanalyse                                                               |     |

|     | 4.3.3 Fehleranalyse                                                                                      |     |

|     | 4.3.3.1 Modul zur Berechnung der Genauigkeit eines AD-Wandlers                                           |     |

|     | 4.3.3.2 Fehlerfortpflanzung durch mathematische Operationen                                              |     |

|     | 4.3.4 Zeitanalyse                                                                                        |     |

|     | 4.3.5 Realisierung von wiederverwendbaren Modellen                                                       |     |

| 4.4 | Verfeinerter technischer Entwurf für rekonfigurierbare Hardware                                          |     |

|     | 4.4.1 Plattformspezifische Datentypaspekte                                                               |     |

|     | 4.4.1.1 Eignung von Datentypen bei der FPGA-Realisierung                                                 |     |

|     | 4.4.1.2 Realisierung der wiederverwendbaren Floating-Point-Bibliothe                                     |     |

|     | 4.4.1.3 Realisierung eines FPGA-basierten Softcore-Prozessors                                            |     |

|     | 4.4.3 Plattformspezifische Zeitanalyse                                                                   |     |

| 4.5 | Modulentwurf und FPGA-Implementierung                                                                    |     |

| 4.6 | Testen des realisierten und implementierten Systems auf den behandelten                                  | 113 |

| 4.0 | Abstraktionsebenen                                                                                       | 117 |

| 5 N | achweis der Anwendbarkeit von ZEfIRA                                                                     | 123 |

| 5.1 | Beschreibung des Vorläufersystems                                                                        | 124 |

| 5.2 | Exemplarische Umsetzung von ausgewählten Schritten der                                                   |     |

|     | Prototypenentwicklung                                                                                    | 126 |

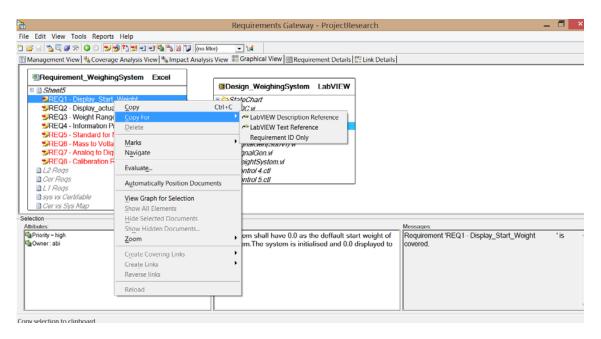

|               | 5.2.1 Konzept und Werkzeugunterstützung zur Anforderungsanalyse                           | 126 |

|---------------|-------------------------------------------------------------------------------------------|-----|

|               | 5.2.2 Funktionaler und technischer Systementwurf                                          | 128 |

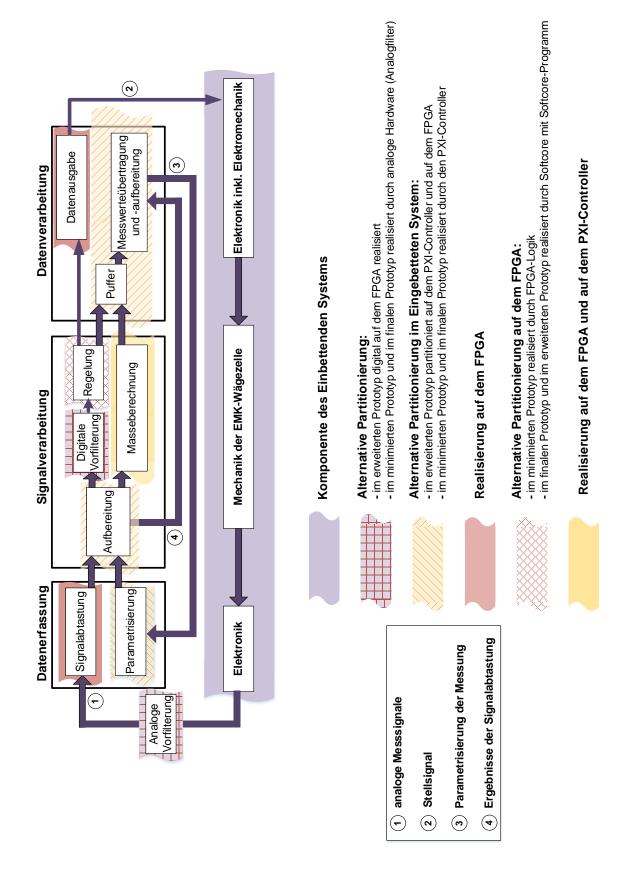

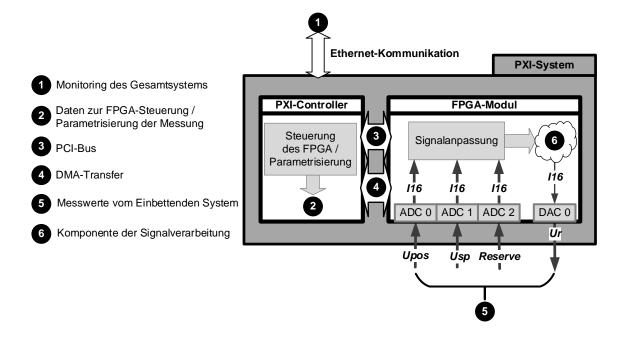

|               | 5.2.2.1 Entwurf des Messdatenerfassungssystems                                            | 130 |

|               | 5.2.2.2 Entwurf des Signalverarbeitungssystems                                            | 131 |

|               | 5.2.3 Verfeinerter technischer Entwurf und Synthese zur Realisierung der                  |     |

|               | Signalverarbeitungsaufgaben                                                               |     |

|               | 5.2.3.1 Messdatenerfassungssystem und Datenausgabe                                        |     |

|               | 5.2.3.2 Vorfilter                                                                         |     |

|               | 5.2.3.4 Masseberechnung durch Software oder FPGA-basierte                                 | 143 |

|               | Hardware                                                                                  | 148 |

|               | 5.2.4 Sicherheitsfunktionen für die Metrologische Sicherheit                              | 150 |

|               | 5.2.5 Werkzeugunterstütze Validierung und Verifikation in verschiedenen Entwurfsschritten | 152 |

|               | 5.2.6 Ergebnisse der digitalen Informationsverarbeitung in der Waage                      |     |

|               | 5.2.6.1 Details zur Implementierung                                                       | 154 |

|               | 5.2.6.2 Messergebnisse                                                                    | 158 |

| 5.3           | Einschätzung der Effektivität von ZEfIRA                                                  | 162 |

| 6 A           | tze zum Produktlinienentwurf in ZEfIRA                                                    | 166 |

| 7 Zı          | mmenfassung und Ausblick                                                                  | 169 |

| 7.1           | Forschungsergebnisse                                                                      | 170 |

| 7.2           | Zukünftige Arbeiten                                                                       | 173 |

| <b>A. A</b> : | ang                                                                                       | 177 |

| A.1.          | nktionaler Systementwurf                                                                  | 177 |

| A.2.          | chnischer Systementwurf                                                                   | 179 |

| A.3.          | rfeinerter technischer Systementwurf                                                      | 185 |

| A.4.          | forderungsanalyse im Projekt                                                              | 188 |

| A.5.          | alisierung des Regelungssystems                                                           | 189 |

| A.6.          | alisierung von Funktionen der Masseberechnung                                             | 194 |

| A.7.          | alisierung von Testmodulen                                                                | 195 |

| A.8.          | GA-Implementierung                                                                        | 196 |

|               | ssergebnisse                                                                              |     |

|               | nsätze zum Produktlinienentwurf                                                           |     |

| Liter         | ırverzeichnis                                                                             | 200 |

### Abbildungsverzeichnis

| Abbildung 1.1: Beispielhafte Einordnung eines Eingebetteten Systems            | 1   |

|--------------------------------------------------------------------------------|-----|

| Abbildung 2.1: Entstehungsmechanismen für Messabweichungen                     | 9   |

| Abbildung 2.2: Signalverarbeitungskette mit digitaler Informationsverarbeitung | 16  |

| Abbildung 2.3: Schematischer Aufbau einer EMK-Waage                            | 19  |

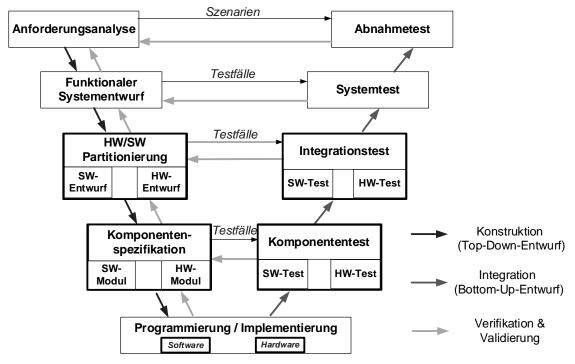

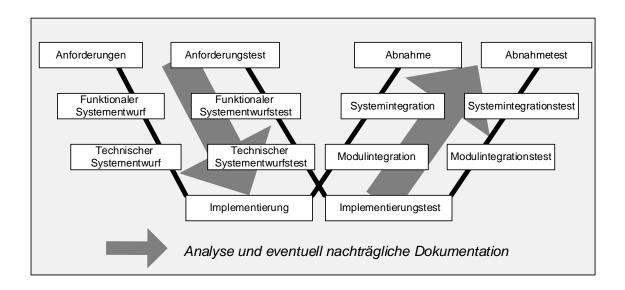

| Abbildung 2.4: Klassische Darstellung des V-Modells für Eingebettete Systeme   | 27  |

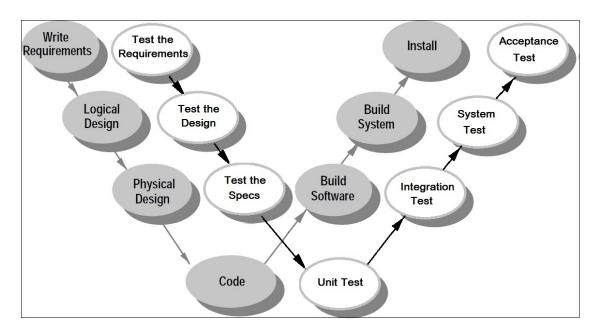

| Abbildung 2.5: W-Modell von Herzlich, aus [GT02]                               | 30  |

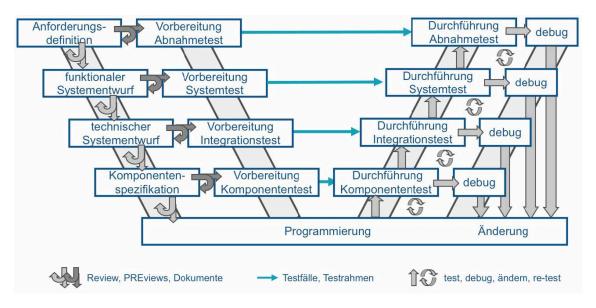

| Abbildung 2.6: W-Modell von Spillner, aus [SRWL11]                             | 31  |

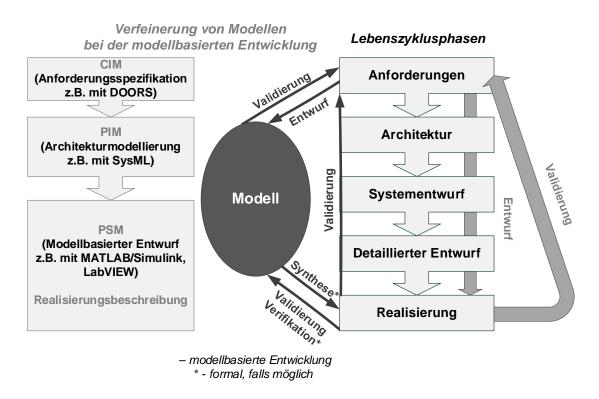

| Abbildung 2.7: Prinzip des modellbasierten Entwurfs                            | 34  |

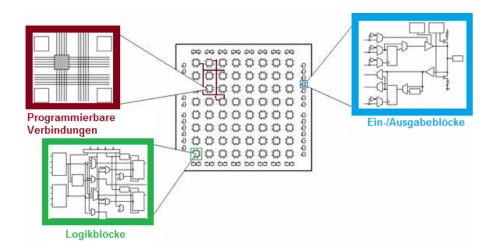

| Abbildung 2.8: Bestandteile eines FPGAs, aus [NI14]                            | 40  |

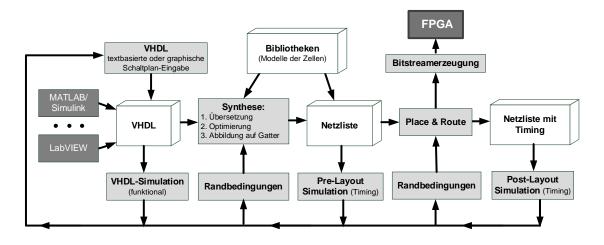

| Abbildung 2.9: Ablaufprozess der FPGA-Implementierung                          | 41  |

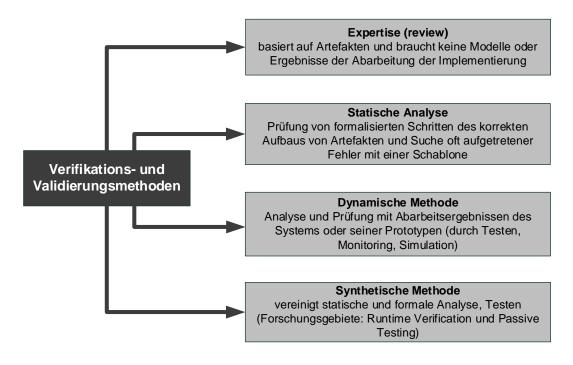

| Abbildung 2.10: Klassifizierung von Verifikations- und Validierungsmethoden    | 43  |

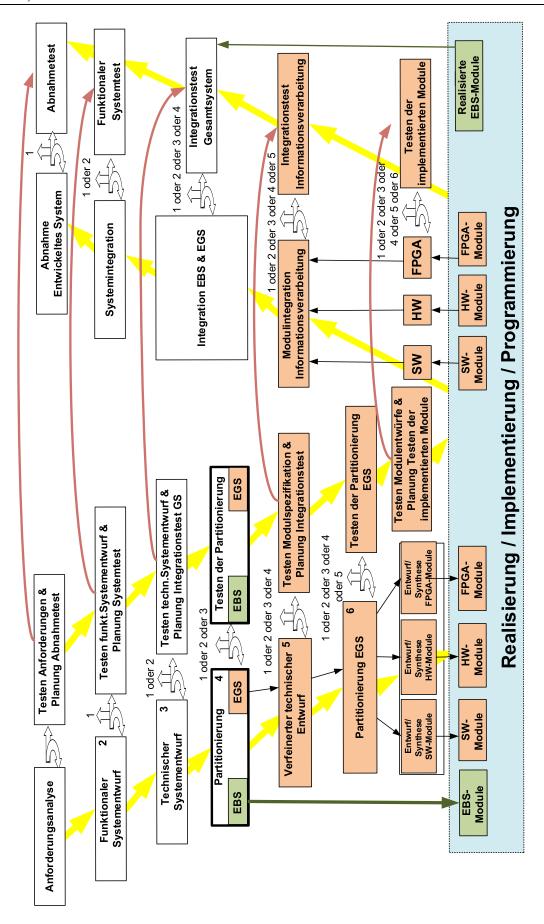

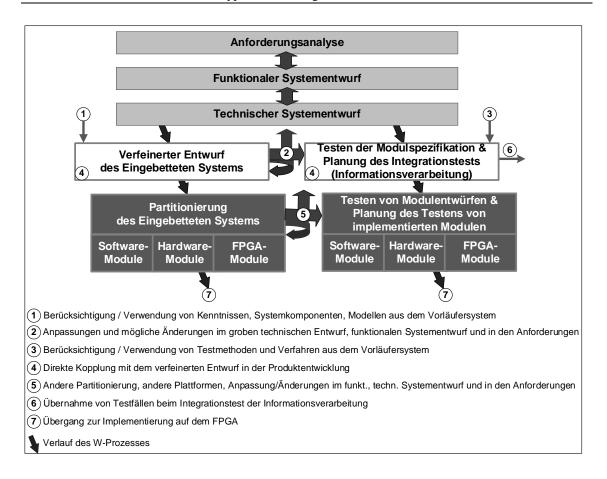

| Abbildung 3.1: Konzept des 3W-Modells (allgemein)                              | 52  |

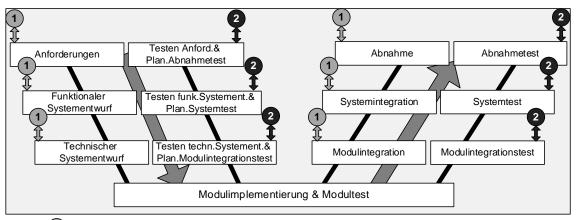

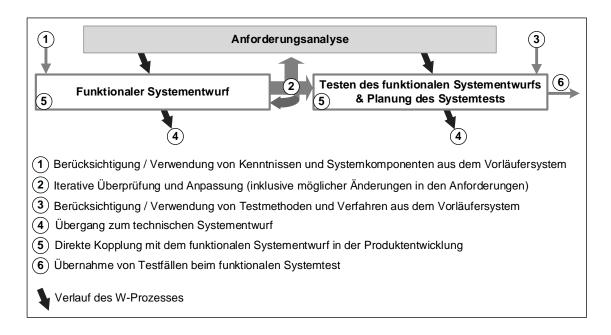

| Abbildung 3.2: W-Modell der Entwicklung eines Prototyps                        | 55  |

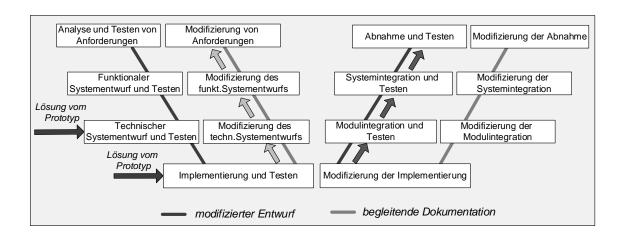

| Abbildung 3.3: W-Modell eines Vorläufersystems (Prototyp und Produkt)          | 57  |

| Abbildung 3.4: W-Modell der modifizierten Entwicklung im Vorläufersystem       | 58  |

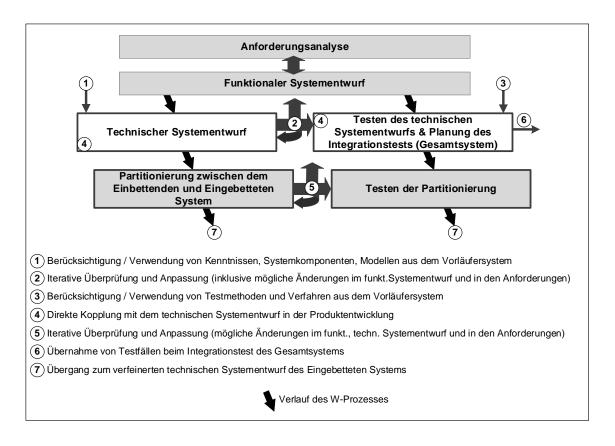

| Abbildung 3.5: W-Modell der Produktentwicklung                                 | 59  |

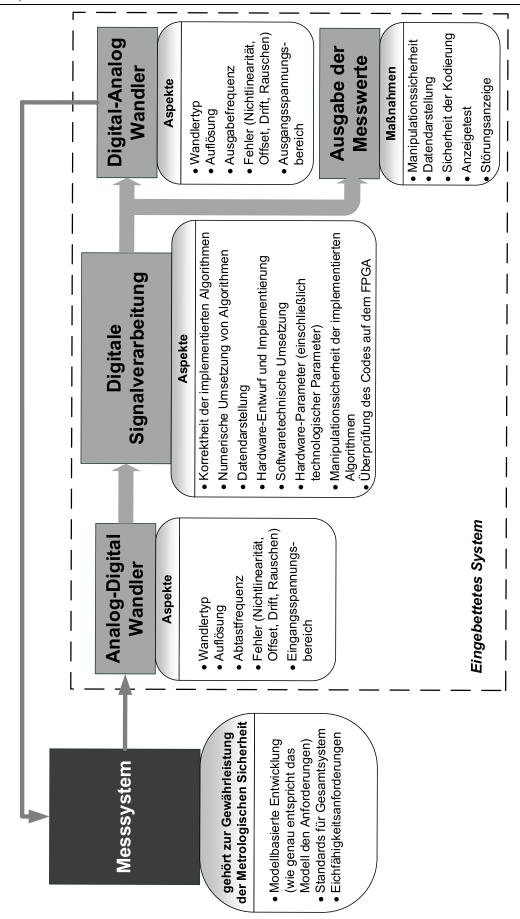

| Abbildung 3.6: Betrachtung der Metrologischen Sicherheit in der Messkette      |     |

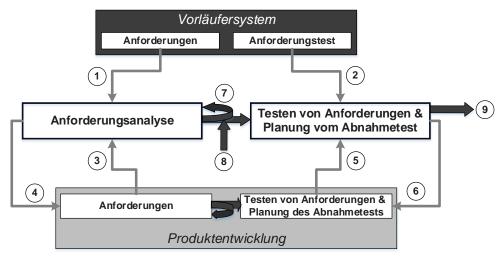

| Abbildung 4.1: Anforderungsanalyse im Prototyp                                 | 66  |

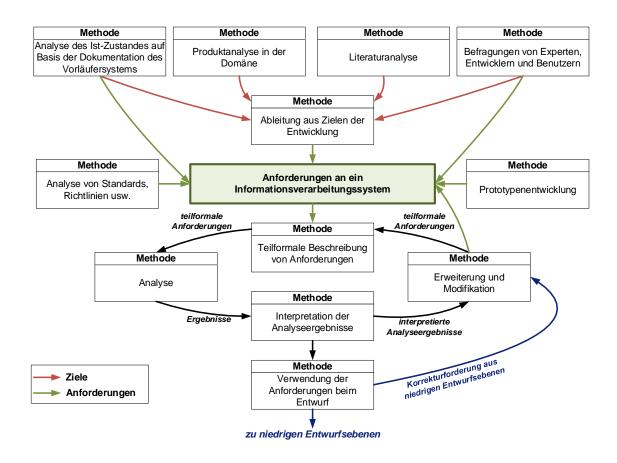

| Abbildung 4.2: Methoden zur Ermittlung von Anforderungen                       | 67  |

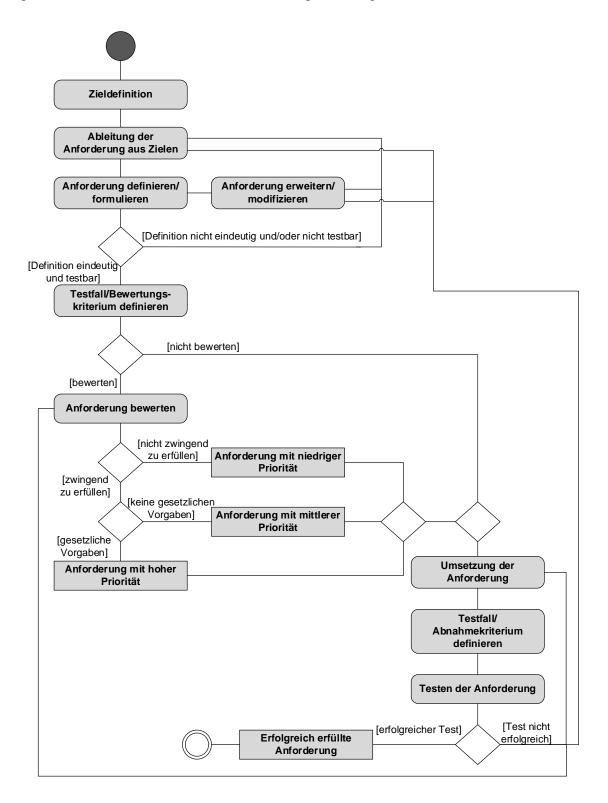

| Abbildung 4.3: Lebenszyklus einer Anforderung                                  |     |

| Abbildung 4.4: Etappe des funktionalen Systementwurfs                          | 71  |

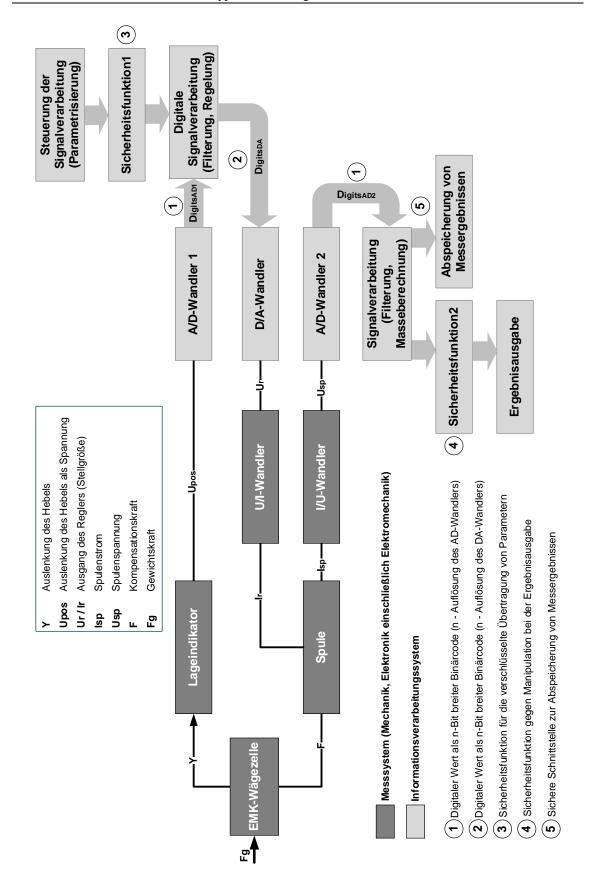

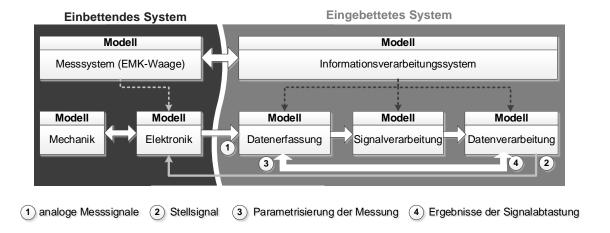

| Abbildung 4.5: Komponenten der Messkette für ein EMK-Wägesystem                | 73  |

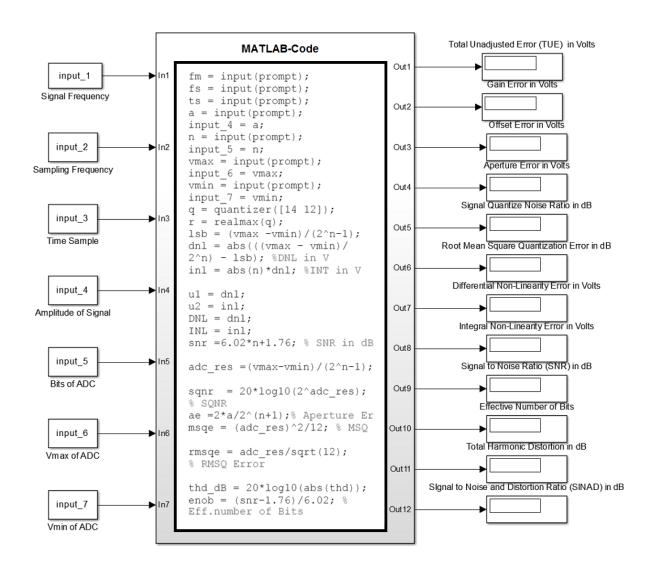

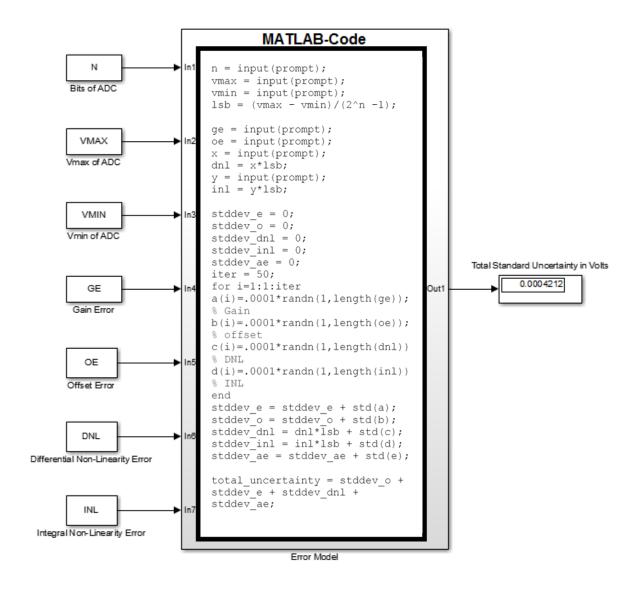

| Abbildung 4.6: Modul zur Analyse von Analog-Digital-Wandlern                   | 76  |

| Abbildung 4.7: Etappe des technischen Systementwurfs                           |     |

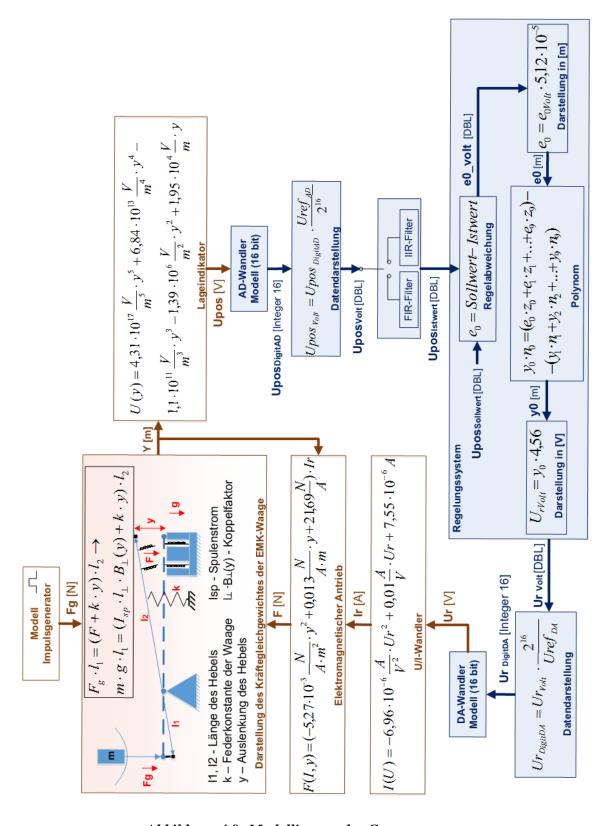

| Abbildung 4.8: Modellierung des Gesamtsystems                                  | 82  |

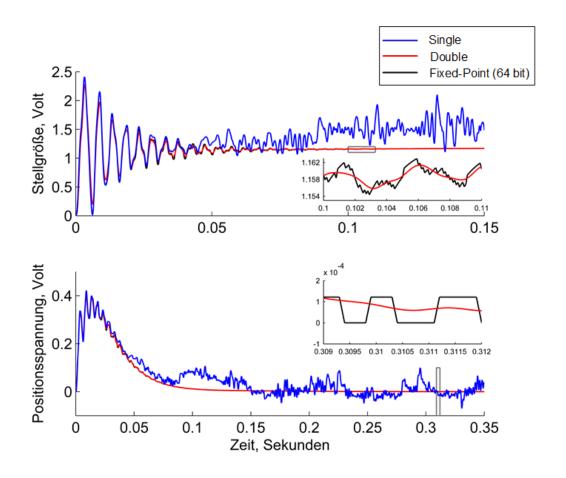

| Abbildung 4.9: Unterschiedliche Zeitverläufe des simulierten Regelungssystems  | 89  |

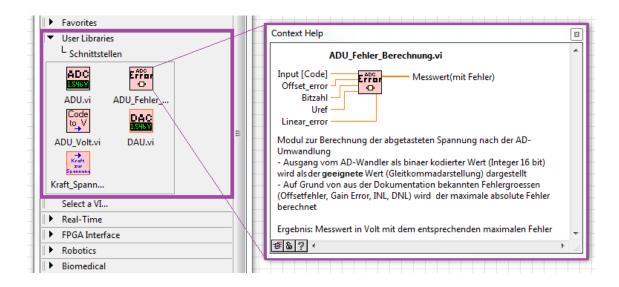

| Abbildung 4.10: Modul zur Berechnung des Fehlers eines AD-Wandlers             | 92  |

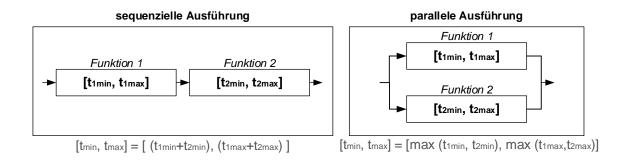

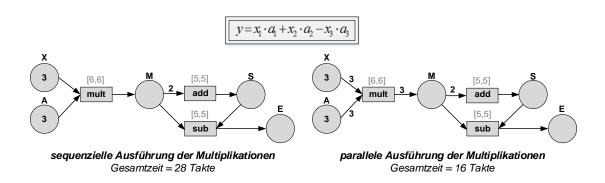

| Abbildung 4.11: Zeitbestimmung bei sequentieller und paralleler Ausführung     | 94  |

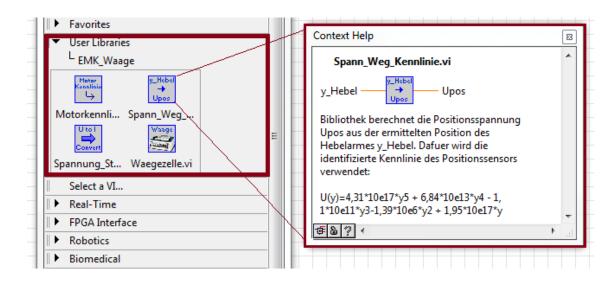

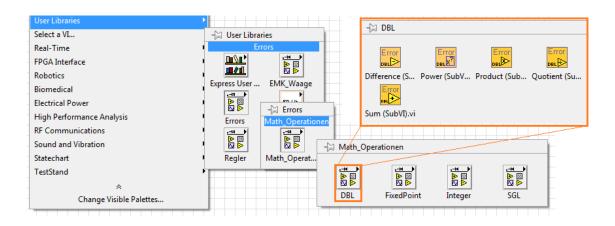

| Abbildung 4.12: Ausschnitt aus den Bibliotheken des Einbettenden Systems       | 95  |

| Abbildung 4.13: Bibliotheken von Schnittstellen                                | 96  |

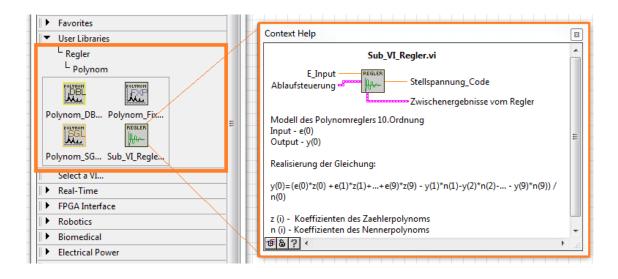

| Abbildung 4.14: Bibliotheken der Signalverarbeitung (Regler)                   | 96  |

| Abbildung 4.15: Bibliotheken der Fehleranalyse von mathematischen Operationen  | 97  |

| Abbildung 4.16: Verfeinerter technischer Entwurf des Eingebetteten Systems     | 99  |

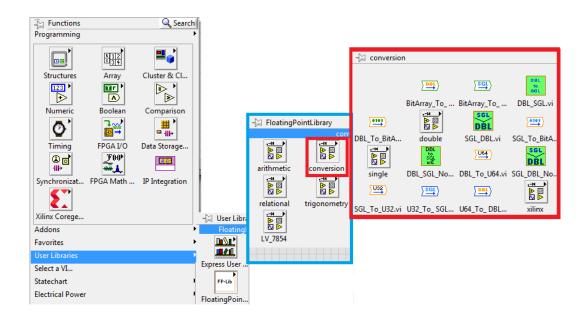

| Abbildung 4.17: Überblick zur Floating-Point-Bibliothek in LabVIEW             | 102 |

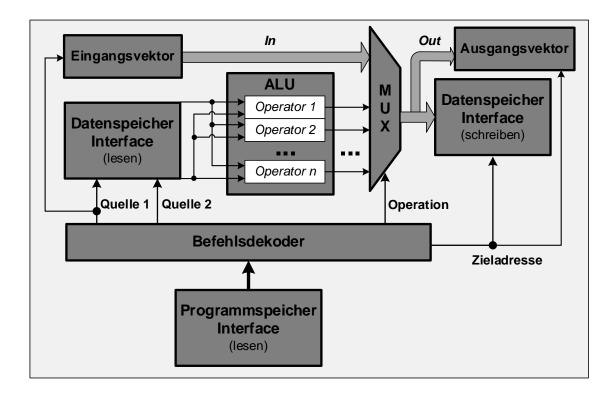

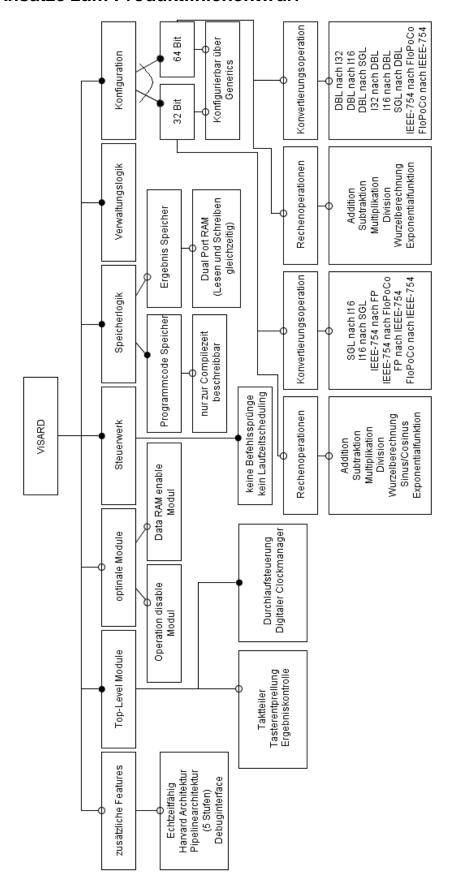

| Abbildung 4.18: Struktur des Softcore-Prozessors                               | 104 |

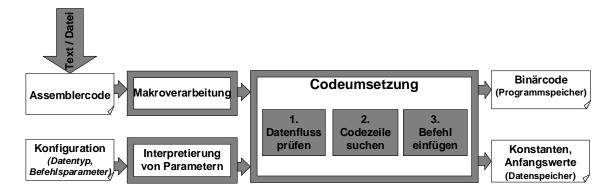

| Abbildung 4.19: Ablauf der Codekonvertierung                                   | 107 |

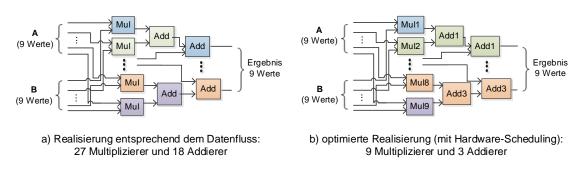

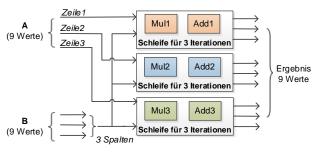

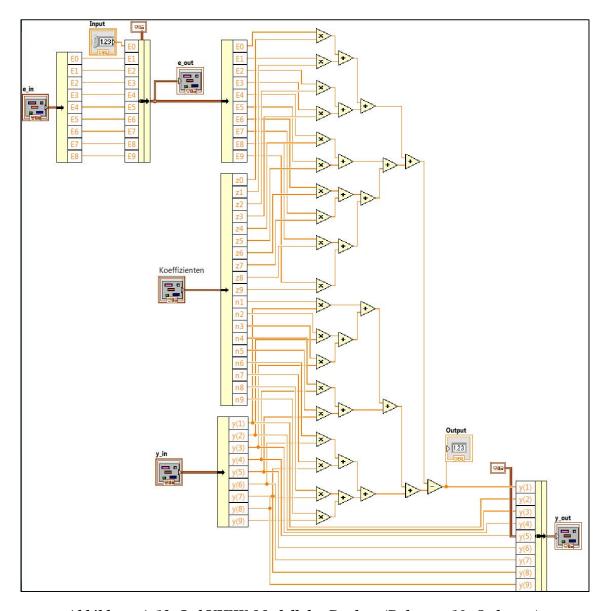

| Abbildung 4.20: Realisierungsbeispiel zur Multiplikation zweier 3x3-Matrizen   | 109 |

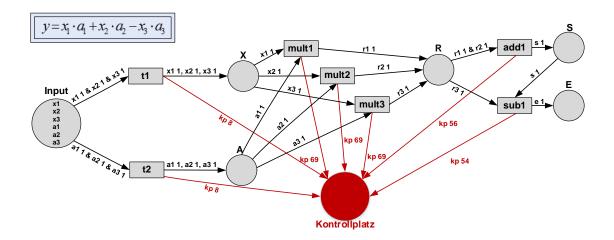

| Abbildung 4.21: Beispiel eines Petri-Netzes zur Ressourcenanalyse              | 110 |

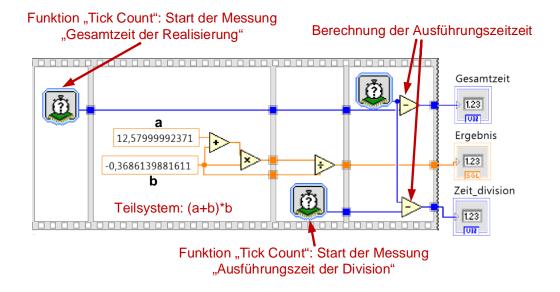

| Abbildung 4.22: Beispiel der Zeitmessung in LabVIEW                            | 112 |

| Abbildung 4.23: Beispiel des modellierten Petri-Netzes zur Zeitanalyse         | 113 |

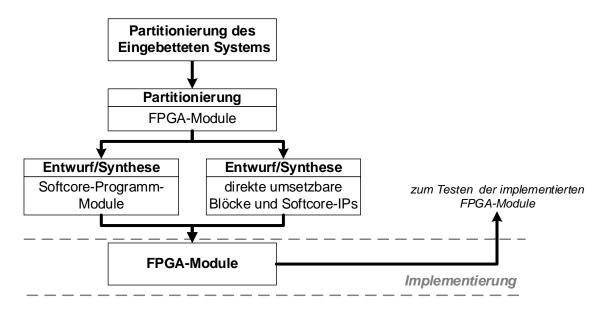

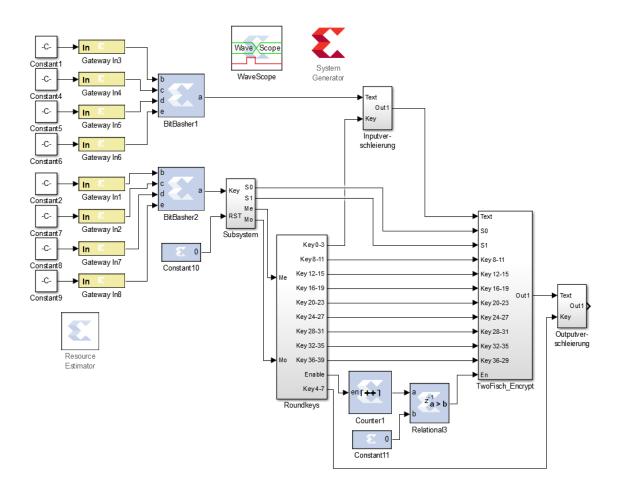

| Abbildung 4.24: Implementierung der FPGA-Module                                         | 114 |

|-----------------------------------------------------------------------------------------|-----|

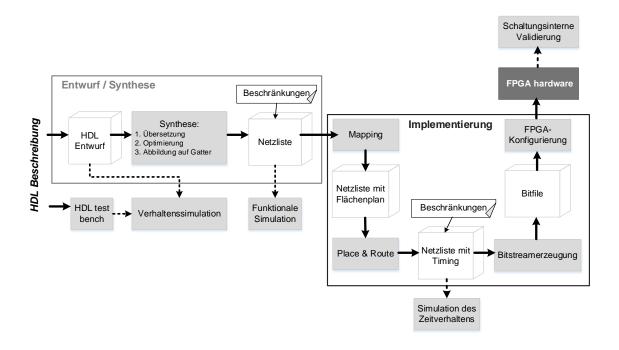

| Abbildung 4.25: Implementierungsprozess für FPGAs                                       | 115 |

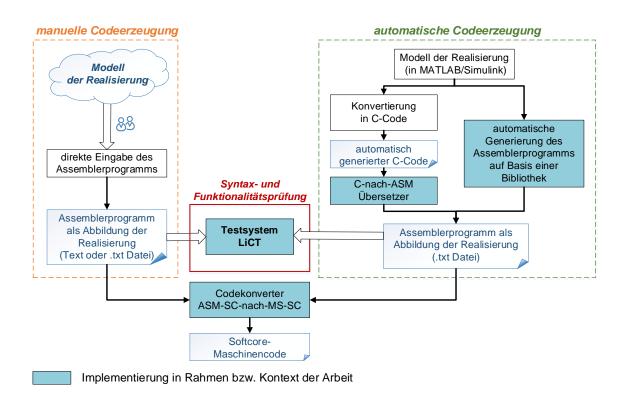

| Abbildung 4.26: Werkzeugkette zur Erzeugung von Softcore-Code                           | 116 |

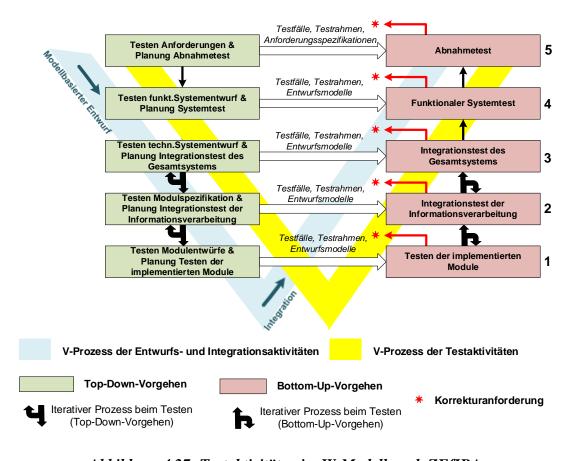

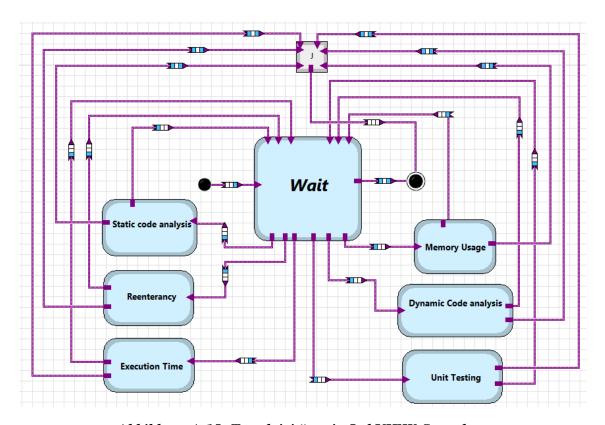

| Abbildung 4.27: Testaktivitäten im W-Modell nach ZEfIRA                                 | 117 |

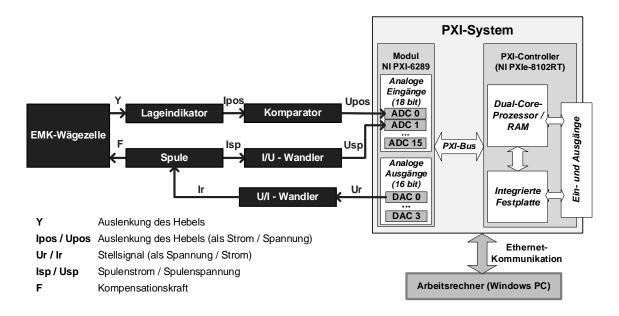

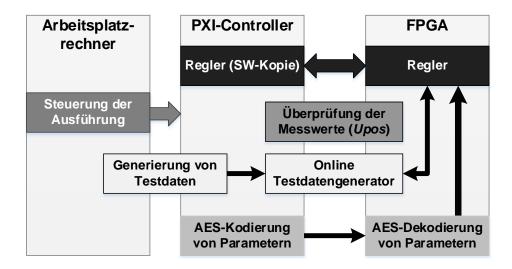

| Abbildung 5.1: Schematische Darstellung des Vorläufersystems                            | 124 |

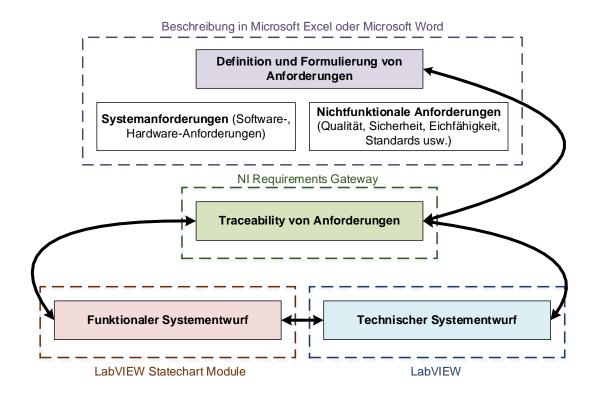

| Abbildung 5.2: Konzept der Anforderungsanalyse in LabVIEW                               | 127 |

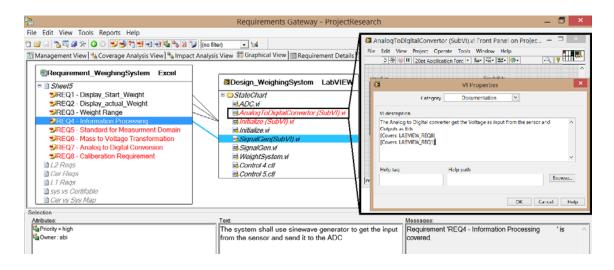

| Abbildung 5.3: Anforderungsanalyse mittels NI Requirements Gateway                      | 128 |

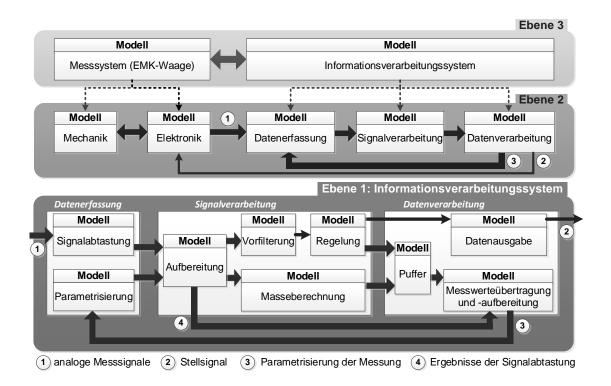

| Abbildung 5.4: Systemkomponenten auf unterschiedlichen Abstraktionsebenen               | 129 |

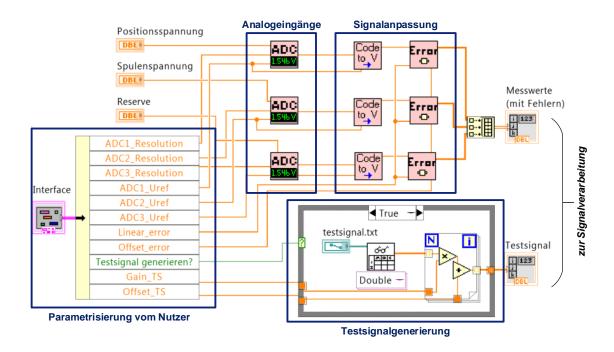

| Abbildung 5.5: Modellierung des Messdatenerfassungssystems                              | 130 |

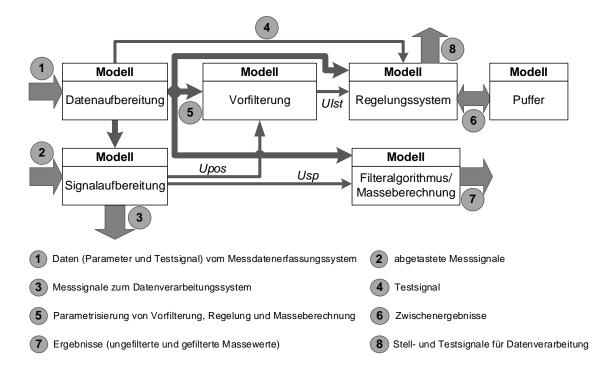

| Abbildung 5.6: Komponenten des Signalverarbeitungssystems                               | 132 |

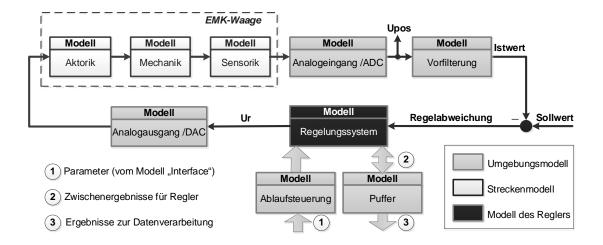

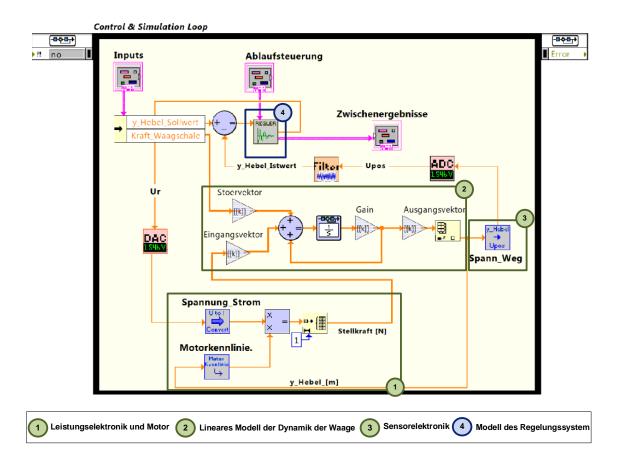

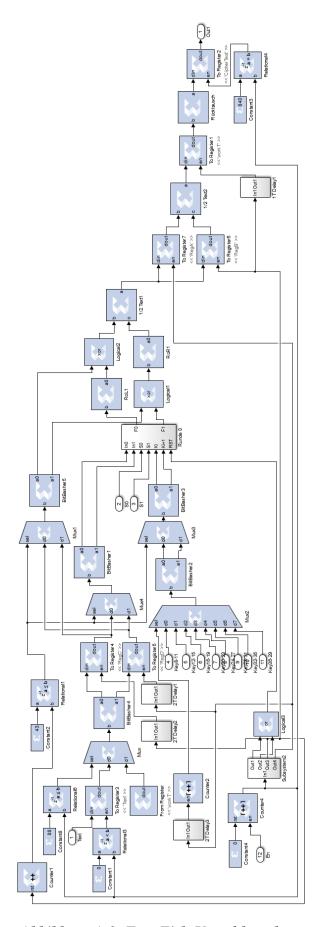

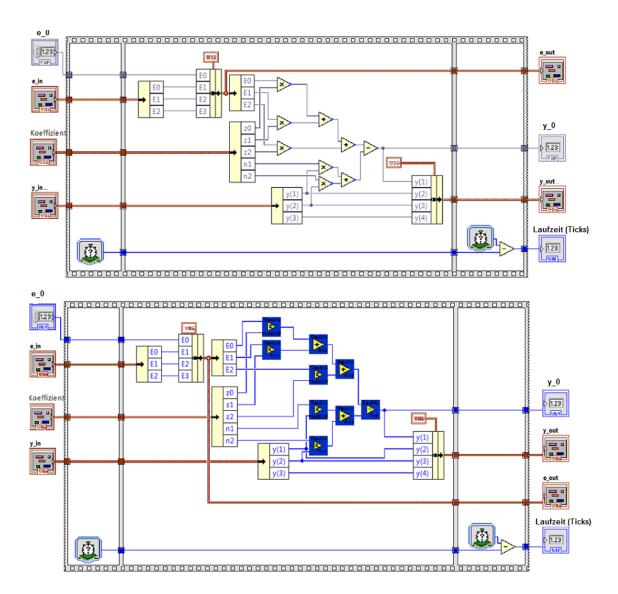

| Abbildung 5.7: Systemmodell des Regelsystems                                            | 134 |

| Abbildung 5.8: Simulationsmodell des modellierten Systems                               | 135 |

| Abbildung 5.9: Partitionierung des Gesamtsystems                                        | 136 |

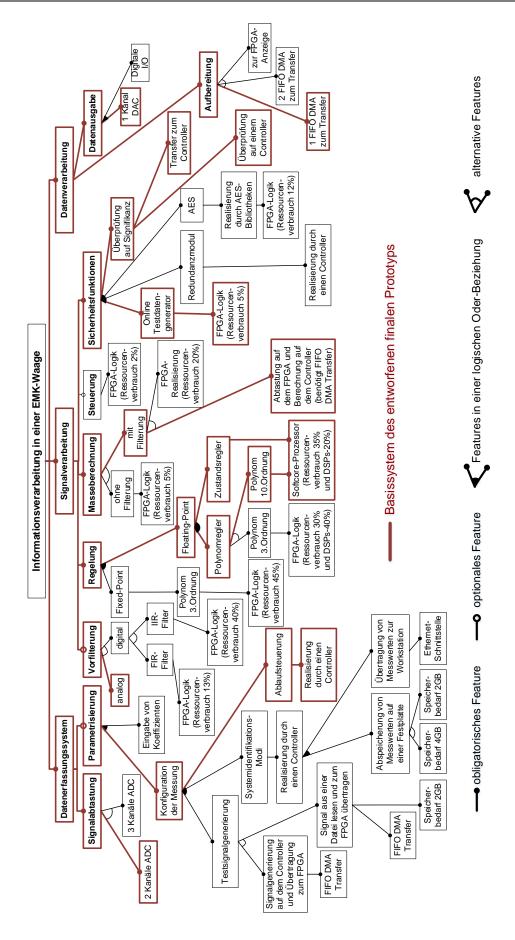

| Abbildung 5.10: Partitionierungsmöglichkeiten im Informationsverarbeitungssystem .      | 138 |

| Abbildung 5.11: Übersicht des gesamten Messdatenerfassungssystems                       |     |

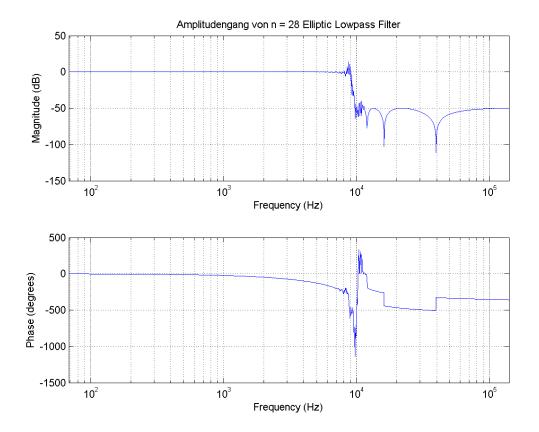

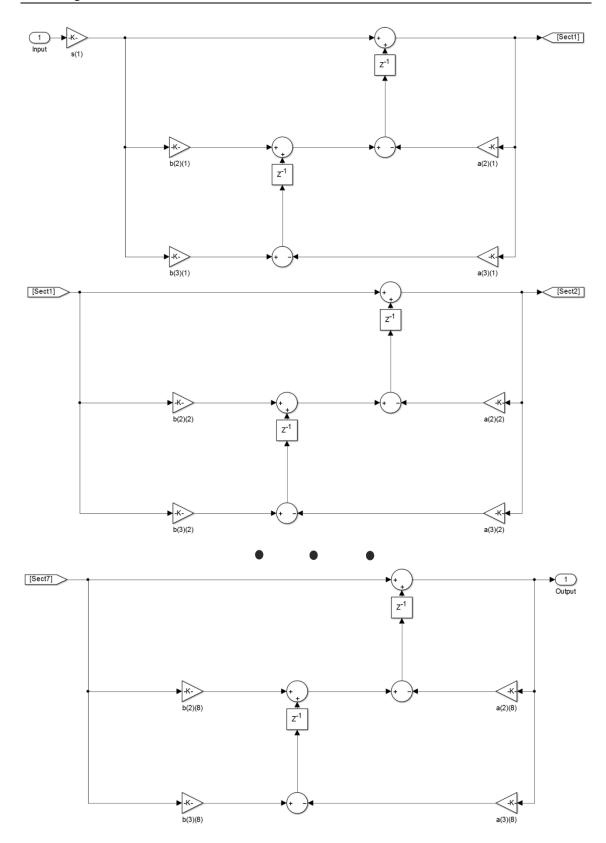

| Abbildung 5.12: Elliptischer IIR-Filter                                                 | 143 |

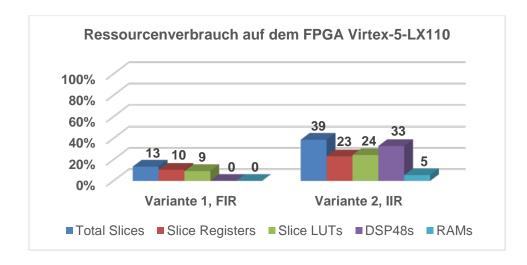

| Abbildung 5.13: Ressourcenvergleich der Vorfilter-Implementierungen                     | 145 |

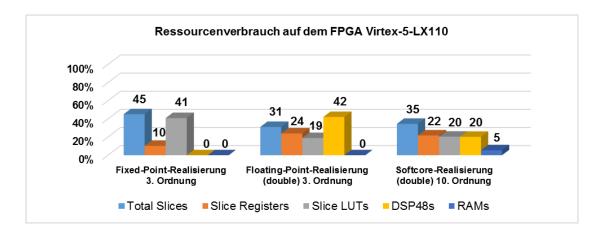

| Abbildung 5.14: Ressourcenvergleich von Implementierungen des Regelungssystems          | 148 |

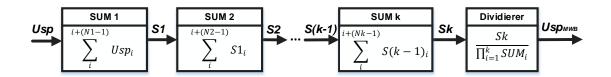

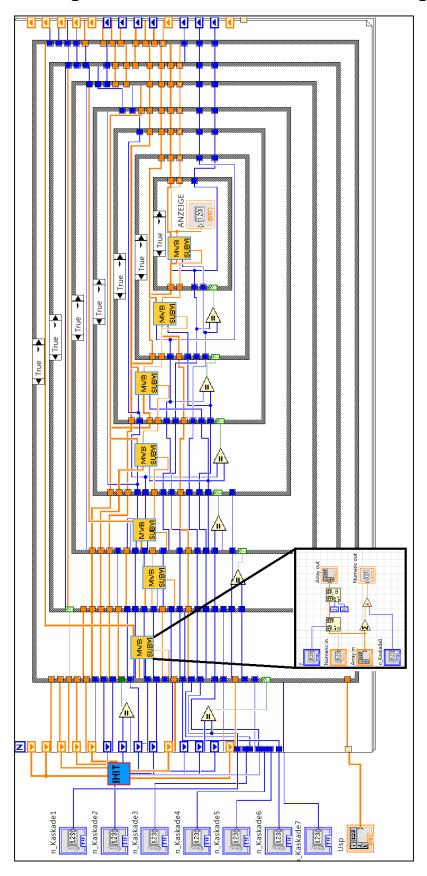

| Abbildung 5.15: Filterkonzept des kaskadierten Mittelwertbildners                       | 149 |

| Abbildung 5.16: Realisierte Sicherheitsfunktionen                                       | 150 |

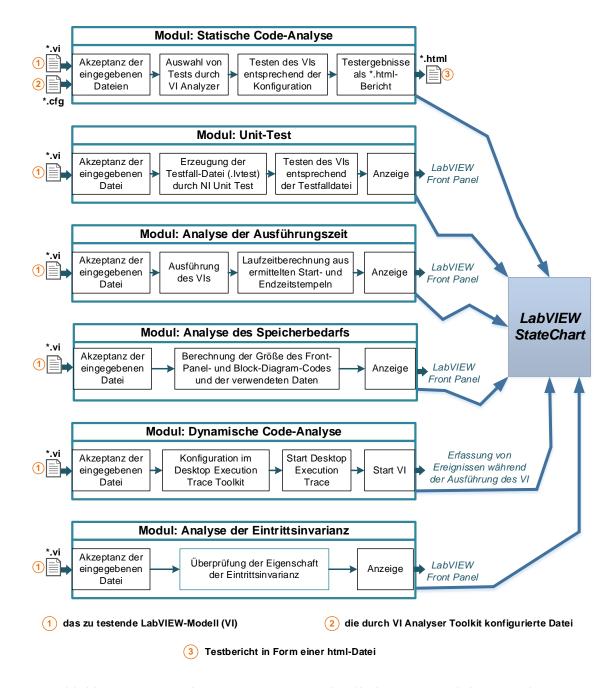

| Abbildung 5.17: Realisierung von unterschiedlichen Testmodulen in LabVIEW               | 153 |

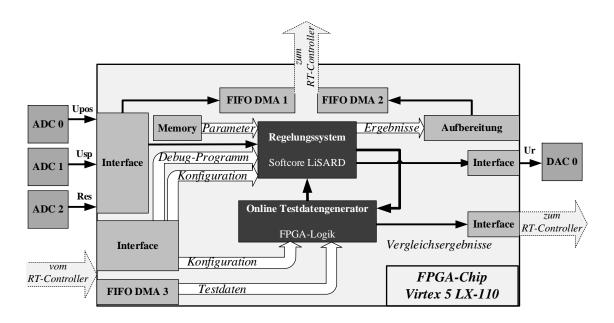

| Abbildung 5.18: Schematische Darstellung der FPGA-Implementierung                       | 154 |

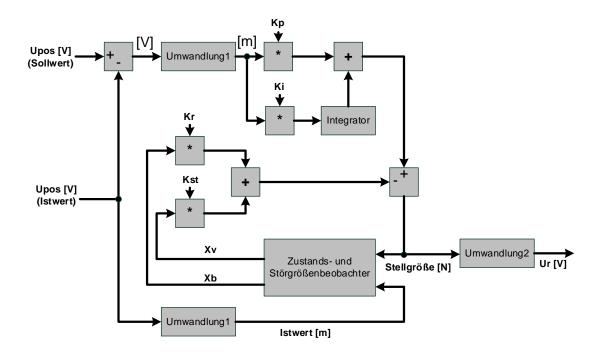

| Abbildung 5.19: Struktur des implementierten Zustandsreglers                            | 156 |

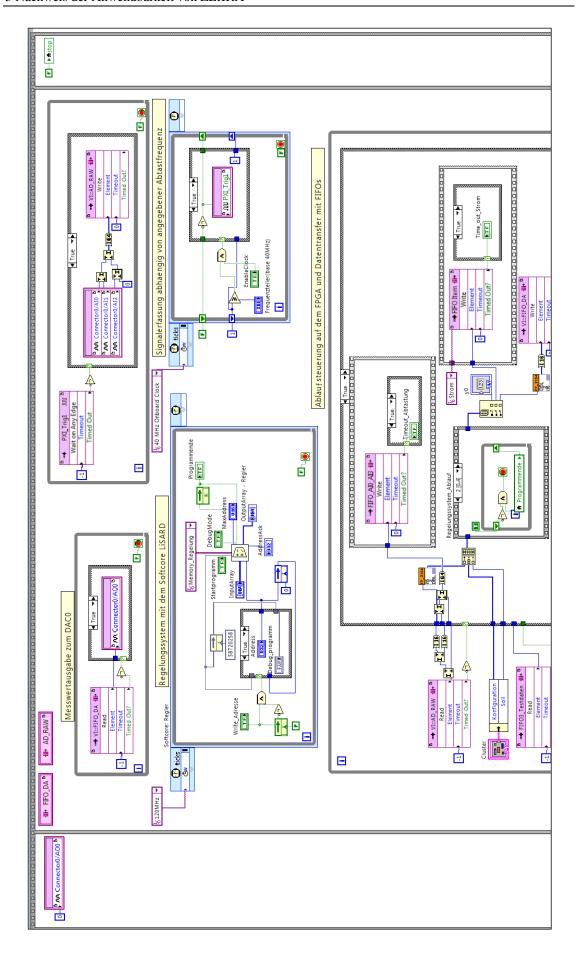

| Abbildung 5.20: LabVIEW-Programm der Implementierung auf dem FPGA                       | 157 |

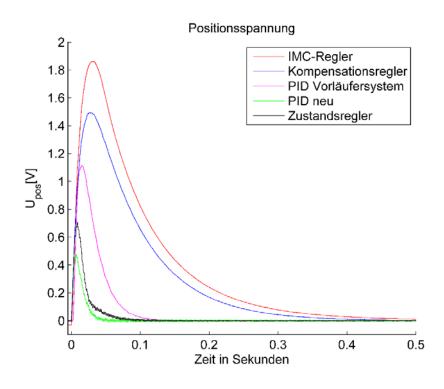

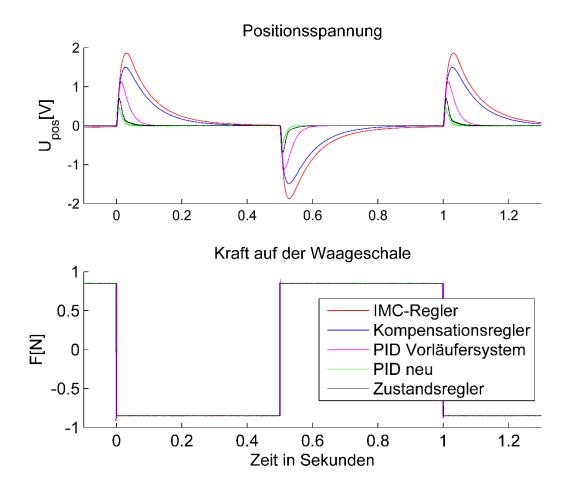

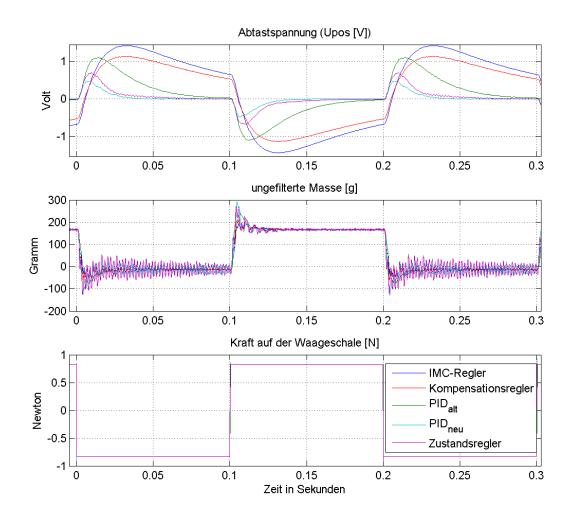

| Abbildung 5.21: Positionsspannung während einer Lastwechselfolge mit 1 Hz               | 158 |

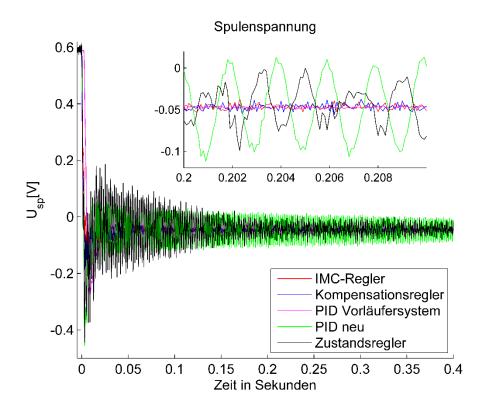

| Abbildung 5.22: Spulenspannung während einer Lastwechselfolge mit 1 Hz                  | 159 |

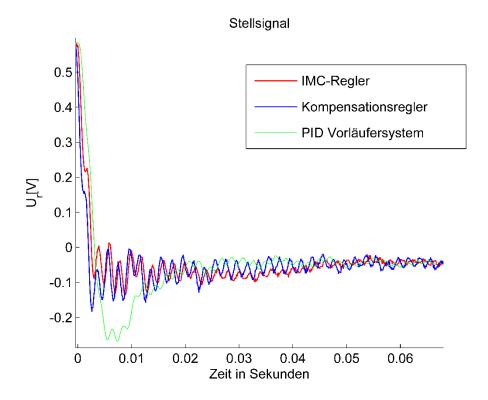

| Abbildung 5.23: Vergleich des Stellsignals (ohne PID <sub>neu</sub> und Zustandsregler) | 160 |

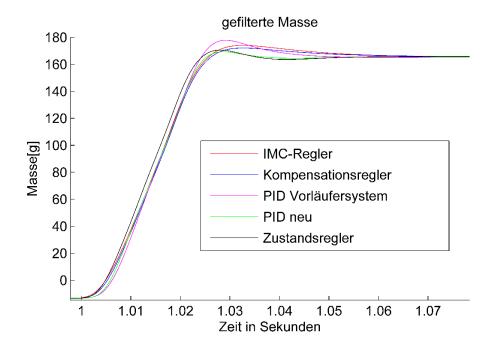

| Abbildung 5.24: Ermittelte Masseergebnisse (Filterstufe 5)                              | 160 |

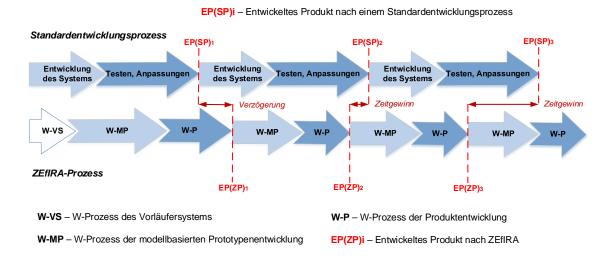

| Abbildung 5.25: Vergleich des ZEfIRA- und eines Standardentwicklungsprozesses           |     |

| Abbildung 6.1: Feature Diagramm unterschiedlicher Basissysteme                          | 168 |

#### **Tabellenverzeichnis**

| Tabelle 2.1: Spezielle Software-Anforderungen nach WELMEC 2.3                  | 23  |

|--------------------------------------------------------------------------------|-----|

| Tabelle 4.1: Fehlerfortpflanzung von mathematischen Operationen (nach [Si04])  | 93  |

| Tabelle 5.1: Ressourcenverbrauch der Vorfilterung auf dem FPGA Virtex-5-LX110. | 145 |

| Tabelle 5.2: Ressourcenverbrauch des implementierten Regelungssystems          | 148 |

| Tabelle 5.3: Ressourcenverbrauch der realisierten Sicherheitsfunktionen        | 151 |

| Tabelle 5.4: Ressourcenverbrauch des Informationsverarbeitungssystems          | 156 |

| Tabelle 5.5: Abweichungen der ermittelten Massedifferenzen, Filterstufe 5      | 161 |

#### Abkürzungsverzeichnis

AD Analog-Digital

ADC (ADU) Analog-to-Digital-Converter (Analog-Digital-Umsetzer)

AES Advanced Encryption Standard

ALU Arithmetic Logic Unit

ASIC Application-Specific Integrated Circuit

ASIP Application-Specific Instruction Set Processor

ASM Assembler

AUTOSAR AUTomotive Open System Architecture

CDFG Control/Data Flow Graph

CIM Computation Independent Model

DA Digital-Analog

DAC (DAU) Digital-to-Analog-Converter (Digital-Analog-Umsetzer)

DFG Deutsche Forschungsgemeinschaft

DIN Deutsche Institut für Normierung

DLL Dynamic Link Library

DMA Direct Memory Access

DMS-WZ Wägezelle mit Dehnungsmessstreifen

DNL Differentielle Nichtlinearität

DOORS Dynamic Object Oriented Requirements System

DSP Digital Signal Processor

EBS Einbettendes System

EGS Eingebettetes System

EMKW elektromagnetische Kraftkompensationswaage

EU Europäische Union

FDA Food and Drug Administration FDM Finite-Differenzen-Modelle FEM Finite-Elemente-Modelle

FF Flip-Flop

FFT Fast Fourier Transform

FG Fachgebiet

FIFO First In – First Out

FIR-Filter Finite Impulse Response Filter FPGA Field Programmable Gate Array

FSM Finite State Machine

HCFSM Hierarchical Concurrent Finite-State Machine

HDL Hardware Description Language

HiL Hardware in the Loop

IIR-Filter Infinite Impulse Response Filter

IMC Internal Model ControlINL Integraler Linearitätsfehler

IP Intellectual Property

LiCT LiSARD Code Tester

LiSARD LabVIEW-integrated Softcore Architecture for Reconfigurable Devices

LSB Least Signifikant Bit

LUT Look-up Table

MID Measurung Instruments Directive

MiL Model in the Loop

MUX Multiplexer

MWB Mittelwertbildner NaN Not-a-Number

NI National Instruments

NPMM Nanopositionier- und Messmaschine

OIML International Organisation of Legal Metrology

PC Personal Computer

PENECA Petri-Netz-CASE-System

PID-Regler Proportional–Integral–Derivative Controller

PiL Processor in the Loop

PIM Platform Independet Model PSM Platform Specific Model

PTB Physikalisch-Technische Bundesanstalt

PXI PCI eXtensions for Instrumentation

RAM Random-Access Memory

RISC Reduced Instruction Set Computer

ROM Read-Only Memory

SC Softcore

SiL Software in the Loop SoC System-on-Chip

SUM Summierer

SysML Systems Modeling Language

TINA TIme petri Net Analyzer

UML Unified Modeling Language

VHDL Very High Speed Integrated Circuit Hardware Description Language

VI Virtual Instrument

ViSARD VHDL-integrated Softcore Architecture for Reconfigurable Devices

WDF Wellen-Digital-Filter

WELMEC Western European Legal Metrology Cooperation

ZEfIRA Zertifizierbarer Entwicklungsprozess für Informationsverarbeitungssys-

teme mit speziellen Rechnerarchitekturen

#### **Danksagung**

Nach Jahren intensiver Arbeit ist die Dissertation nie das Werk einer einzelnen Person. Deswegen möchte ich mich an dieser Stelle bei denjenigen bedanke, die mich in dieser spannenden wissenschaftlichen Tätigkeit begleitet haben.

Ein besonderer Dank geht an meinen Doktorvater Prof. Wolfgang Fengler für die Möglichkeit, am Fachgebiet Rechnerarchitektur und Eingebettete Systeme der Technischen Universität Ilmenau zu arbeiten und promovieren zu können. Außerdem bedanke ich mich, dass er mir mit seinem Fachwissen immer zur Seite stand, viele seiner Feierabende für mich opferte und mir durch Gespräche zu einem wertvollen und freundschaftlichen Wegbegleiter wurde.

Für die Gelegenheit, an den Arbeiten im Bereich der dynamischen Wägetechnik im Fachgebiet Prozessmesstechnik beteiligt sein zu dürfen, möchte ich dem Prof. Thomas Fröhlich und seinen Mitarbeitern Hanna Baumgartl, Norbert Rogge und Gunter Krapf danken. Sie waren mir stets sehr gute Ansprechpartner und bereicherten meine Forschung durch ihre Anregungen und Ideen.

Des Weiteren bin ich dem Prof. Klaus-Dietrich Kramer für sein zweites Gutachten zu Dank verpflichtet. Ihre Einladung nach Wernigerode zur wissenschaftlichen Diskussion war wertvoll und sehr konstruktiv.

Ebenso geht mein Dank an meine wertvollen Kollegen Prof. Detlef Streitferdt, Dr. Bernd Däne, Dr. Oswald Kowalski, Dr. Todor Vangelov, Johannes Klöckner, Dr. Marcus Müller, Dr. Arvid Amthor, Andriy Osadchuk, Hans-Christian Schwannecke, Heiko Weiß, Dr. Patrick Mäder, Dr. Alexander Pacholik und Nils Würfel für die ausgezeichnete Zusammenarbeit, den vielen gemeinsamen Projekten und Diskussionen. Sie haben mir stets Mut zugesprochen und mich in meiner Arbeit bestärkt.

Den vielen Studenten, die ich während ihrer Studienzeit bei Projekt- und Abschlussarbeiten im Rahmen meiner Tätigkeit im Fachgebiet Rechnerarchitektur und Eingebettete Systeme betreute, gilt mein besonderer Dank. Sie leisteten einen großen Beitrag zu den erfolgreichen Untersuchungen und den Ergebnissen dieser Arbeit.

Eine herausragende Stellung in jeglicher Hinsicht nehmen meine Familie und mein lieber Mann ein, die mich in den vergangenen Jahren vielseitig unterstützt haben. Ich danke meinen Eltern, die die Grundsteine und sehr viel Hoffnung für meinen Weg gelegt haben. Lieber Robert, ohne deine liebevolle Fürsorge wäre diese Arbeit nicht zu dem Werk geworden.

#### 1 Einleitung

Zunehmend spielt die Informationsverarbeitung eine wichtige Rolle in modernen Erzeugnissen. Diese Position wird auch durch permanente Forschung im Bereich der Messtechnik vorangetrieben. Von besonderem wissenschaftlichem Interesse sind dabei sehr komplexe Mess- und Automatisierungsalgorithmen, die effektiv realisiert und implementiert werden müssen. Es werden vor allem hohe Anforderungen an Qualität, messtechnische Eigenschaften, Verarbeitungsleistung, Echtzeitverhalten, Sicherheit und Kosten der Systeme gestellt.

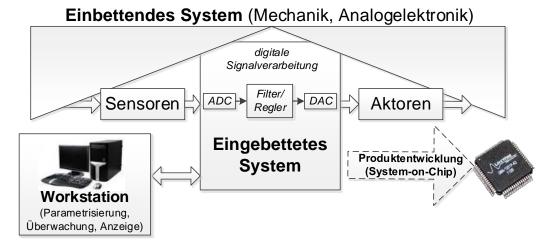

In den letzten Jahren steigerte sich ständig die Komplexität der zu entwickelnden Informationsverarbeitungssysteme, so dass die verwendeten Entwicklungsmethoden verbessert und optimiert werden müssen. Dabei sind Eingebettete Systeme aus Software und Hardware heutzutage auf vielen Gebieten der Stand der Technik. Unter einem Eingebetteten System (engl. *embedded system*) versteht man ein Gerät, in dem ein Rechner integriert ist, wobei dieser weitgehend unsichtbar für den Anwender ist. Dabei ist dieses die Komponente eines technischen Systems, das über Sensoren und Aktoren mit einem Einbettenden System, z.B. den elektrisch-mechanischen Komponenten eines Messgeräts, interagiert (Abb. 1.1). Für die Entwicklung von solchen Systemen befasst sich die Forschung mit Prozessen, Methoden, Techniken und Werkzeugen zum Software-, Hardware-und Hardware-Software-Co-Entwurf (auch Hardware-Software-Codesign). [GM07]

Der Stand der Technik für eingebettete Hochleistungsplattformen für die Informationsverarbeitung wird zukünftig vor allem auch durch rekonfigurierbare Hardware charakterisiert werden, deren Einsatz modulare, flexible, leistungsstarke Systemkompositionen erlaubt [MB07]. Durch die Möglichkeit, mit hoher Parallelität in diesen Hardwarestrukturen zu arbeiten, sind Lösungen mit ihnen zumeist den sequentiell arbeitenden Prozessoren überlegen, selbst wenn diese als Parallelarchitekturen (Multicorearchitekturen oder ähnliches) betrieben werden.

Abbildung 1.1: Beispielhafte Einordnung eines Eingebetteten Systems

Um eine systematische Entwicklung, und damit verbunden die Fehlervermeidung und Maßnahmen für die möglichst frühzeitige Fehlererkennung und –beseitigung beim Entwurf von komplexen Informationsverarbeitungssystemen zu fördern, werden Entwicklungsprozesse gebraucht. Dies ist auch für die messtechnischen mechatronischen Systeme mit ihrer hohen Dynamik bei Entwicklung, Komplexität und Technologievielfalt eine immer wieder neue Herausforderung. Bei der gemeinsamen gleichzeitigen Entwicklung von Eingebetteten und Einbettenden Systemen regeln die Entwicklungsprozesse die Technikorganisation von Arbeitsabläufen in der Hardware- und Software–Entwicklung und die in diesem Fall notwendigen Schritte, genauso wie bei der Integration von entwickelten Teilen in das Gesamtsystem. Es existieren Abhängigkeiten zwischen der Entwicklung von Eingebettetem und Einbettendem System.

#### 1.1 Aufgabenstellung und Motivation

Eingebettete Systeme mit steigendem Funktionsumfang erobern immer neue Anwendungsgebiete in der industriellen Messtechnik. Einen besonderen Platz nimmt die Wägetechnik ein, die zu den ältesten Gebieten (mehrere 1000 Jahre) zählt.

Waagen haben eine große Bedeutung für die Massebestimmung in vielen Bereichen und unterliegen in den meisten Einsatzfällen der staatlichen Gesetzgebung. Im Vergleich mit anderen Messgebieten liegen die Anforderungen an die Einhaltung der geforderten Messunsicherheit in der Wägetechnik oft wesentlich höher. Eine entsprechende Rolle spielen Waagen bei der Automatisierung von Produktionsprozessen, besonders die selbsttätigen Waagen, die nach einer vorgegebenen Rezeptur verschiedene Komponenten zusammenführen können [Kr04].

Weiterhin sind die bisher eingesetzten Lösungen der Informationsverarbeitung nicht ausreichend, um Messunsicherheit und Dynamik deutlich zu verbessern. Die Qualität des wägetechnischen (mechatronischen) Teils und deren Steuerung und Signalverarbeitung beeinflussen das Endprodukt maßgeblich. Es ist eine sorgfältige Planung mit eindeutig definierten Schnittstellen unerlässlich. Auf dem Gebiet der Präzisionswaagen und Wägezellen für industriellen Einsatz sind viele Probleme erst ansatzweise erforscht. Die Wägezellen benötigen für ihre Funktion neue Ansätze zur komplexen und hochleistungsfähigen Informationsverarbeitung, die mit Eingebetteten Systemen realisiert werden können.

Die Lösungen für eingebettete Hardware-Software-Systeme müssen die folgenden wichtigen Funktionen realisieren: Unterstützung der Gewichtsermittlung, Signalverarbeitung einschließlich Regelung und/oder Steuerung. Weitere wichtige Kriterien für die Entwicklung des Systems sind Bedienelemente, Anzeigen, sowie Schnittstellen zur Kommunikation mit anderen Systemkomponenten. Basierend auf den oben genannten Anforderungen beschäftigt sich die vorliegende Arbeit mit der Erforschung eines qualifizierten Entwicklungsprozesses für derartige Informationsverarbeitungssysteme unter Berücksichtigung

der in der Wägetechnik geforderten Eichfähigkeit. In einer Reihe von Veröffentlichungen wird in diesem Zusammenhang von notwendiger Metrologischer Sicherheit gesprochen (z.B. in [BS10]), wobei der Begriff nicht klar definiert ist. Für die vorliegende Arbeit wurde dazu eine Definition erarbeitet, die im Kapitel 3.5 enthalten ist. Der eben genannte Prozess soll die gesamten Abläufe bei der Entwicklung der Informationsverarbeitung regeln, die Möglichkeit enthalten schnell und flexibel auf die messtechnischen Anforderungen zu reagieren und eine weitgehend optimale Entwurfslösung für das konkrete Messsystem zu erzeugen.

Es existieren mehrere wirtschaftliche, gesetzliche und technische Gründe für einen qualifizierten Entwicklungsprozess. Eine besonders wichtige Rolle spielen solche Prozesse in der Lebensmittel-, chemischen und pharmazeutischen Industrie, die außergewöhnlich hohe Anforderungen an Metrologische Sicherheit und Eichfähigkeit stellen. In diesem Zusammenhang wird auch ein systematischer Entwicklungsprozess notwendig, der zertifiziert sein sollte.

In den USA existiert eine Behörde, die "Food and Drug Administration" (FDA), die für die Arzneimittelzulassung und die Lebensmittelüberwachung zuständig ist. Eine wichtige Aufgabe der FDA ist die Erarbeitung von Vorschriften und die Durchführung von Kontrollen der Herstellung von Medizinprodukten und Lebensmitteln. Es werden durch die FDA u. a. Forderungen an die verwendete Wägetechnik bei der Herstellung von Arzneiund Nahrungsmitteln gestellt, die von den Herstellern von Messgeräten für diese Prozesse u.a. auch beim Export in die USA realisiert werden müssen. Eine Forderung ist die Anwendung eines definierten und dokumentierten Entwicklungsprozesses. Ähnliches gibt es auch in anderen Ländern, wobei die Vorschriften und Kontrollen der FDA die systematischsten und konsequentesten Forderungen stellen [FDA14].

In Deutschland ist die Regelung, welche Messgeräte der Eichpflicht unterliegen, in Rechtsvorschriften geregelt: Gesetze (Eichgesetz, Einheitengesetz), Verordnungen/Vorschriften über die Eichpflicht von Messgeräten [ME09] und Eichpflichtausnahmeverordnung, Richtlinien (PTB - Physikalisch-Technische Bundesanstalt Prüfregeln [PTB14]).

Die zunehmende Rationalisierung und Automatisierung hat Einfluss auf die Qualitätserhöhung und die Kostenreduzierung der Erzeugnisse. Der qualifizierte Entwicklungsprozess hat nicht nur die Aufgabe, eine effektive Entwicklung zu ermöglichen, sondern auch auf gesetzliche Anforderungen reagieren zu können. Weiterhin sollen wirtschaftliche Ziele, wie die Senkung von Entwicklungskosten und die damit verbundene Steigerung des Gewinns verfolgt werden. Ein zusätzlicher wirtschaftlicher Aspekt der Entwicklung eines qualifizierten Prozesses ist die Betrachtung und die Integration von Aufgaben des Projektmanagements. Dieses soll sicherstellen, dass die entwickelten Messsysteme und die gestellten Projektziele die technischen, finanziellen, personellen und zeitlichen Randbedingungen erreichen. [Be05]

#### 1.2 Ziele des Forschungsvorhabens

Das Hauptziel der Arbeit ist die Untersuchung und Entwicklung von Entwurfsmethoden, die für die Anforderungen der Messtechnik (im Weiteren am Beispiel der Wägetechnik) speziell weiterentwickelt, entworfen und angepasst sind. Diese werden in einen in der vorliegenden Dissertation erarbeiteten Entwicklungsprozess für die komplexe Informationsverarbeitung von Waagen mit eingebetteten Hardware-Software-Systemen integriert. Der Entwicklungsprozess soll die speziellen Anforderungen an Metrologische Sicherheit und Eichfähigkeit, gewährleistet durch Qualitätssicherung sowie durch andere Maßnahmen, schon zur Entwurfszeit auf Modellebene berücksichtigen und bis zur Implementierung verfolgen. Dabei sind Validier- und Verifizierbarkeit als Entwurfskriterien im gesamten Prozess zu integrieren. Dafür soll die Gewährleistung der Metrologischen Sicherheit mit ihren speziellen Qualitätsanforderungen für eingebettete Informationsverarbeitungssysteme der Wägetechnik definiert und für Hardware-Software-Systeme als Bearbeitungsgegenstand untersucht werden.

Sehr anspruchsvolle Lösungen im Bereich der Wägetechnik sind entweder dadurch gekennzeichnet, dass sie mit sehr hohen Auflösungen bei sehr kleinen Messunsicherheiten arbeiten oder in industriellen Prozessen eingesetzt werden. Im zweiten Fall sollen sehr schnelle Messungen in einem mechanisch gestörten Umfeld durchgeführt werden. In beiden Fällen bewegt man sich in Grenzbereichen der Wägetechnik. Um diese Grenzen zu noch kleineren Messunsicherheiten beziehungsweise zu einem schnelleren dynamischen Wägen unter starken und auch veränderlichen Störungen zu verschieben, ist eine Grundlagenforschung notwendig. Hierbei steht die Untersuchung von Prinzipien und Methoden im Vordergrund, die notwendig sind, um diese Ziele zu erreichen.

Zur Gewährleistung von korrektem Messen sollen aufwändige Algorithmen der komplexen digitalen Signalverarbeitung entwickelt und deren optimierte Implementierung untersucht werden. Ein Verschieben der messtechnischen Grenzen, wie oben genannt, zieht

unmittelbar höhere Leistungsanforderungen sowie kürzere Reaktionszeiten der Informationsverarbeitung nach sich. Es werden Eingebettete Systeme notwendig sein, die eine

entsprechende Rechenleistung, Reaktionszeit und Kommunikationsleistung realisieren.

Die optimalen Lösungen bezüglich dieser Parameter für die nötigen eingebetteten Hochleistungsplattformen werden, vor allem durch rekonfigurierbare Hardware charakterisiert. Diese können die eben genannten Eigenschaften realisieren und sind damit im

Hochleistungssektor in diesem Gebiet angesiedelt. Für die Beherrschung des Entwurfs

solcher Systeme sind modellbasierte Methoden erforderlich, da sie zur Entwurfszeit die

Optimierung der Plattformstruktur und der Funktionsverteilung erlauben, die von entscheidender Bedeutung für die Leistungsfähigkeit des Gesamtsystems sind.

Die Anforderungen sollen bereits frühzeitig im Entwicklungsprozess auf Modellniveau berücksichtigt werden. Dann sind optimale und fehlerärmere Lösungen möglich, wobei

sich gleichzeitig die Entwicklungszeiten verkürzen. Weiterhin soll die Optimierung der Leistungskennwerte im Sinne der Anforderungen unter Berücksichtigung der Restriktionen durchgeführt werden. Dadurch soll erreicht werden, dass das realisierte System alle notwendigen Funktionalitäten im Sinne der Spezifikation und der geforderten Systemparameter erfüllt und gleichzeitig eine möglichst wirtschaftlich günstige Lösung, sowohl für den Entwicklungsprozess als auch für das Zielerzeugnis entsteht. Deshalb sollen geeignete Methoden ausgewählt beziehungsweise entwickelt und in den Prozess integriert und validiert werden. Dabei soll dieser definiert und seine wichtigen Schritte erarbeitet werden. Es werden insbesondere betrachtet:

- Anforderungsanalyse und Testen von Anforderungen;

- Anforderungen der Eichfähigkeit und Metrologischen Sicherheit;

- Modellbasierter Entwurf einschließlich Verifikation und Validierung der Modelle und der eventuellen Nutzung von Modellen des Einbettenden Systems;

- Berücksichtigung der Eichfähigkeit und Metrologischen Sicherheit auf Modellebene;

- Implementierung in Hardware, rekonfigurierbare Hardware und Software (z.B. über Softcore-Prozessoren) als optimale Lösung für konkreten Anwendungsfall;

- Ableitung von Testfällen für das implementierte System aus den Modelltestfällen.

Bei der Eichfähigkeit von Software in eingebetteten Informationsverarbeitungssystemen gibt es bereits gesetzliche Regelungen und Empfehlungen [PTB06][WEL14]. Das gilt für die Metrologische Sicherheit jedoch noch nicht. Für rekonfigurierbare Hardware (FPGAs) sind zurzeit beide Probleme nicht gelöst und sind für diese Realisierungsform Bearbeitungsgegenstand der Dissertation.

Als letzte Etappe der Arbeit soll der Nachweis der Realisierbarkeit und der Effektivität des entworfenen Entwicklungsprozesses an einem Beispiel aus dem messtechnischen Bereich durchgeführt werden. Aus diesem Grund beschäftigt sich die Dissertation mit der Entwicklung eines Prototyps, der als Demonstrator für die Informationsverarbeitungsaufgaben in einem Messsystem eingesetzt wird.

#### 1.3 Inhalt der Arbeit

Diese Arbeit ist wie folgt gegliedert. Das zweite Kapitel widmet sich dem Stand der Technik zu ausgewählten Aspekten. Dabei werden die allgemeinen Grundbegriffe und Definitionen aus dem messtechnischen Gebiet dargestellt. Die bestehenden Prinzipien der digitalen Informationsverarbeitung einschließlich spezifischer gesetzlicher und Sicherheitsanforderungen werden näher betrachtet und analysiert. Anschließend wird auf die

unterschiedlichen Arten von bekannten Vorgehensweisen zur Entwicklung von Eingebetteten Systemen eingegangen. Vorhandene Techniken des modellbasierten Entwurfs mit begleitenden Verifikations- und Validierungsaktivitäten werden detailliert dargestellt. Bezogen auf den plattformspezifischen Entwurf werden Informationen zu verschiedenen Implementierungsarten und eine besondere Betrachtung der FPGA-basierten Eingebetteten Systeme dargestellt. Der Abschnitt 2.5 fasst die Forschungsvorgaben der vorliegenden Dissertation aus den Untersuchungen zum Stand der Technik zusammen. Darauf aufbauend erfolgt im dritten Kapitel die Formulierung des zertifizierbaren Prozesses (ZEfIRA) für die Informationsverarbeitung in messtechnischen Systemen. Es wird eine spezielle Vorgehensweise für die Entwicklung von Eingebetteten Systemen präsentiert. Die Berücksichtigung der Metrologischen Sicherheit und der Eichfähigkeit sowie die Integration der Validierung und Verifikation im gesamten Entwurfsprozess werden erläutert.

Als Schwerpunkt der Arbeit werden im Kapitel 4 die Prozessschritte der effektiven Prototypenentwicklung nach ZEfIRA genauer beschrieben. Ausgehend von der werkzeugunterstützten Anforderungsanalyse bis zur Implementierung mit dazugehörigen Verifikations- und Validierungsaktivitäten wird das Eingebettete System (Informationsverarbeitungssystem) abhängig von den Forderungen des Einbettenden Systems (Messsystem) modellbasiert entwickelt. Die Methoden, Prinzipien und Techniken des durchgängigen Entwurfes, die im Kapitel 4 formuliert werden, unterstützen vorwiegend die Entwicklung von komplexen FPGA-basierten Eingebetteten Systemen. Die Anwendung des erarbeiteten Konzeptes der systematischen Entwicklung in einem Projekt wird im Kapitel 5 gezeigt. Anhand des prototypischen Entwurfs eines Informationsverarbeitungssystems in der elektromagnetischen Kraftkompensationswaage werden eine Leistungssteigerung und eine effektive Entwicklung, bezogen auf den personellen und Zeitaufwand, im Vergleich zum vorgestellten Vorläufersystem demonstriert. Im Abschnitt 5.3 wird die Einschätzung der Effektivität von ZEfIRA gegeben, wobei ein abgeschätzter zeitlicher Verlauf im Gegensatz zu einem Standardentwicklungsprozess (nach dem V-Vorgehen) dargestellt wird. Abschließend wird im Kapitel 6 der in der Dissertation ansatzweise bearbeitete Aspekt zur Erweiterung des Konzeptes ZEfIRA für den Produktlinienentwurf präsentiert. Eine Zusammenfassung der Forschungsergebnisse, eine Wertung derselben und ein Ausblick zu zukünftigen Arbeiten beschließen diese Arbeit.

#### 2 Allgemeine Aspekte der Informationsverarbeitung in der Messtechnik anhand der Wägetechnik

Im modernen Leben existiert praktisch kein Gebiet, in dem das Messen keine Anwendung findet. Das einfache Messen verfolgt uns täglich im Haushalt, beim Einkaufen und Autofahren. Dabei werden unterschiedliche messtechnische Geräte eingesetzt, die in der gewünschten Genauigkeit den Messwert abschätzen können. Das Messen in Natur, Technik und Handel mit vorgegebenen Parametern war und ist für die Entwicklung dieser Anwendungsgebiete von maßgeblicher Bedeutung und verlangt wissenschaftliche Untersuchungen.

Das Gebiet der Messtechnik befasst sich mit Geräten und Methoden zur Erfassung von verschiedenen physikalischen Messgrößen (z.B. elektrische Größen, Länge, Temperatur, Masse, Kraft usw.). Die Entwicklung von Messmethoden und Messsystemen, sowie die Prinzipien bei der Erfassung von Messdaten mit verringerter Messunsicherheit sind die wichtigsten Teilgebiete der Messtechnik [WW10][Am10].

Im Allgemeinen bietet die Messtechnik zur Realisierung eines Messverfahrens zwei sehr unterschiedliche Prinzipien an, die gleichberechtigt nebeneinander stehen: Ausschlagprinzip und Kompensationsprinzip. Beim Ersten wird die Messgröße direkt oder indirekt in mehreren Stufen in die Ausgangsgröße umgeformt, dementsprechend liegt eine geradlinige Messkettenstruktur vor. Beim Kompensationsprinzip wird die Wirkung der Messgröße durch Ausgleichen mit einer gleichartigen stellbaren Kompensationsgröße ermittelt. Dabei ist die Messkette als kreisartige Struktur ausgelegt [WW10][PP94].

Das folgende Kapitel enthält die allgemeinen Aspekte der Informationsverarbeitung in der Messtechnik. Im Abschnitt 2.1 werden die wichtigsten Grundbegriffe und Definitionen des messtechnischen Gebietes dargestellt, die im Laufe der Jahre als eigene Fachsprache für exaktes Arbeiten und Beschreiben in Abhängigkeit von Naturwissenschaft und Technik entwickelt wurden. Die begrifflichen Festlegungen wurden unter anderem in [JCGM10][DIN1319] beschrieben.

In den Kapiteln zu den eigenen Forschungsergebnissen wird sich die Arbeit zumeist auf die Wägetechnik konzentrieren. Das liegt vor allem daran, dass in diesem Gebiet sehr viele Aspekte der Messtechnik in Kombination auftreten, wie z.B. dynamisches Verhalten und Eichfähigkeit. Es führt dazu, dass relativ komplexe Gesamtlösungen notwendig sind und die Entwicklung der Geräte ein systematisches Vorgehen verlangt. Darauf basierend werden in den folgenden Abschnitten zum Stand der Technik zumeist die Informationen zur Masse- und Gewichtsbestimmung detaillierter dargestellt.

#### 2.1 Grundbegriffe und Definitionen in der Messtechnik

Der Vorgang des Messens hat zwei Aspekte. Einerseits wird die physikalische Größe erfasst und dargestellt, andererseits normiert oder einer Maßzahl zugeordnet. Dabei muss die zu messende Größe qualitativ eindeutig definiert und quantitativ bestimmbar sein. Das Messnormal muss dazu aber durch eine Konvention festgelegt werden. Eine Größe wird als Vielfaches oder Teil einer zu dieser Größe festgelegten Einheit angegeben. Größen, die durch eine Messung bestimmt werden, sind Messgrößen. Die voneinander unabhängig definierten Normale werden Grundnormale (oder Basiseinheiten) genannt. Durch die "Conference Generale des Poids et Mesures" sind die sieben Grundnormale des internationalen Einheitssystems (SI) definiert: das Meter [m], das Kilogramm [kg], die Sekunde [s], das Ampere [A], das Kelvin [K], die Candela [Cd] und das Mol [mol]. [PP94]

Es existieren noch viele weitere Einheiten, die über physikalische Gesetze auf die Basiseinheiten zurückgeführt werden. Z.B. wird bei der Bestimmung der Masse eines Körpers zwischen Masse- und Kraftbestimmung unterschieden [Ko89].

Der folgende Absatz wurde wörtlich aus [Fin64] entnommen, da er diesen Sachverhalt sehr prägnant beschreibt:

"Die Masse eines Körpers ist die Gesamtheit seiner materiellen Teilchen. Diese Masse (Einheit = kg) ist konstant und unabhängig von dem Ort, an dem sich der Körper gerade befindet. Da sich der Körper mit seiner konstanten Masse gewöhnlich in einem Schwerefeld befindet, wird er von diesem angezogen und übt dabei eine Kraft (Einheit = N oder kp) auf seine Unterlage aus. Je nach dem Ort, wo sich der Körper gerade befindet, kann diese Kraft (oder auch Last) verschieden groß sein; denn die Schwerebeschleunigung ist nicht an allen Orten der Erdoberfläche gleich. Da wir aber einen Wert des Körpers ermitteln wollen, der überall gleich ist, müssen wir seine Masse bestimmen."

Die Einheit der Kraft wird über das zweite Newtonsche Axiom (F=m\*a) definiert, als Maßeinheit ergibt sich dafür  $kg \ m \ s^{-2}$ . Diese Einheit wird häufig gebraucht und erhält einen eigenen Namen: 1 Newton mit der Abkürzung N [WW10][Bo88].

Das Messen als Vergleich mit einem Normal wird nur in seltenen Fällen durchgeführt. Meistens werden Messgeräte verwendet, die die gewünschten Messwerte nach einem physikalischen Effekt anzeigen. Dabei werden unterschiedliche Messprinzipien gebraucht, um eine Messgröße in die Anzeige eines Messgerätes zu wandeln. Der quantitative Zusammenhang zwischen der Anzeige oder dem Ausgangssignal einer Messeinrichtung und dem wahren Wert der Messgröße über den gesamten Messbereich der Messeinrichtung wird durch Kalibrieren bestimmt [DIN1319]. Der eigentliche Messeffekt wird mit dem Hilfsmittel (heute zumeist Elektronik) auf einer Anzeige (analog - Skala mit Zeiger oder digital – mit Ziffern) als Messwert dargestellt. Dabei wird die Zusammen-

schaltung von Komponenten für die Wandlung einer nichtelektrischen Größe in ein elektrisches Signal bis zur Anzeige als Messkette bezeichnet [WW10]. An dieser Stelle muss die Definition für die Auflösung eines anzeigenden Messgerätes gegeben werden. Unter der Auflösung wird allgemein die erforderliche Änderung der Messgröße verstanden, um eine festgelegte Änderung der Anzeige zu bewirken [PP94][DIN1319]. In der digitalen Signalverarbeitung wird dieser Begriff im Zusammenhang mit der Quantisierung verwendet.

#### In der Wägetechnik gilt nach [Be96]:

"Die Waage ist ein Meßgerät für Massen. Die modernen elektronischen Waagen bestimmen die Masse über die Wirkung der Schwerkraft der Erde auf diese Masse, das heißt, sie messen die Gewichtskraft G."… "Eine Waage kann auch eingesetzt werden, um andere, mit der Masse zusammenhängende Größen zu messen, z. B. Stückzählung von gewichtsgleichen Teilen oder Dichtebestimmung, oder um Kräfte zu messen, z. B. Oberflächenspannungen oder Federkräfte."

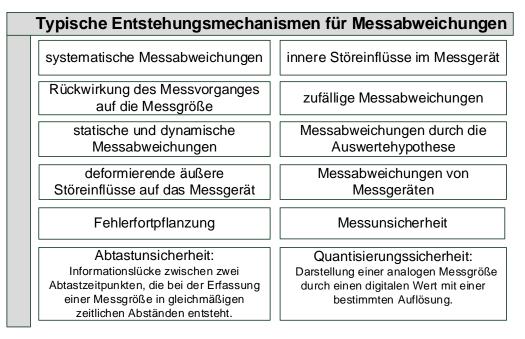

Das Ziel jeder Messung ist es immer eine genaue Bestimmung der Messgröße mit einer dem Problem angepassten Genauigkeit durchzuführen. Ohne Genauigkeitsabschätzung ist die eigentliche Angabe des Messwertes wenig aussagefähig. Grundsätzlich ist aber jede Messung mit Fehlern behaftet. Die Messgröße selbst aber auch die verwendeten Messverfahren und Messgeräte sind ungenau, sodass eine tatsächlich existierte Größe von ihrem gemessenen Wert abweicht. Diese Differenz wird als Messabweichung bezeichnet. Die Abbildung 2.1 stellt die unterschiedlichen Ursachen der Messabweichungen dar (angelehnt an [PP94][WW10]).

Abbildung 2.1: Entstehungsmechanismen für Messabweichungen

Da der richtige (wahre) Wert in der Praxis nicht ermittelt werden kann, führt die Genauigkeitsabschätzung zu einem Wahrscheinlichkeitsintervall. Dieses Intervall um ein Messergebnis, das den geschätzten Bereich angibt, innerhalb dessen der wahre Wert mit einer bestimmten Wahrscheinlichkeit liegt, wird als Messunsicherheit [DIN1319] bezeichnet.

Eine besondere Betrachtung ist notwendig, wenn mehrere Glieder der Messkette zum Messergebnis beitragen. Dabei liefern alle Messunsicherheiten dieser Glieder einen Beitrag zur Messunsicherheit des gesamten Messergebnisses. Dieses wird als Fehlerfortpflanzung bezeichnet. Der Einfluss der verschiedenen Glieder auf das Messergebnis kann von sehr unterschiedlichem Gewicht sein. Auf Grund der verschiedenen Art von systematischen (deterministischen) und zufälligen (stochastischen) Fehlern sind auch deren Fortpflanzungsgesetzte unterschiedlich. Die maximale Messunsicherheit ergibt sich durch Addition der abgeschätzten Größtwerte der unbekannten systematischen und der zufälligen Abweichung (auch Fehler in [PP94] genannt) der einzelnen Messglieder. Zur Schätzung der daraus resultierenden Messunsicherheiten verwendet man die zwei folgenden Definitionen [WW10]:

- 1. Absoluter Fehler  $\Delta x_i$  einer Einzelmessung ist gleich der Abweichung vom Mittelwert  $\overline{x}$  aller n Messungen  $x_i$  mit  $i = \{1, ..., n\}$

- 2. **Relativer Fehler** ist das Verhältnis vom absoluten Fehler zum Messwert:  $\frac{\Delta x_i}{x_i}$

Systematische Fehler treten bei wiederholten Messungen unter gleichen Bedingungen immer mit dem gleichen Betrag und Vorzeichen auf. Diese lassen sich durch eine sorgfältige Untersuchung möglicher Fehlerquellen beeinflussen, z.B. reduzieren oder korrigieren.

Hingegen werden zufällige Fehler durch nicht vorhersagbare Störungen (zufällige Einflüsse während der Messung) verursacht. In der Messwertanalyse werden diese nach den Methoden der Statistik erfasst und behandelt. Es werden wiederholte Messungen durchgeführt, und die Menge von Einzelmessungen wird Stichprobe genannt. Aus den Einzelmessungen erhält man einen Schätzwert nach der mathematischen Grundlagen der Normalverteilung von Zufallsgrößen von Gauss [JCGM10][BST10][DIN1319].

Daraus folgend kann die beste Abschätzung des Messwertes x durch das arithmetische Mittel realisiert werden:

$$\overline{x} = \frac{1}{n} \sum_{i=1}^{n} x_i \tag{2.1}$$

Dann ist der durchschnittliche (mittlere) Fehler bei der Einzelmessung:

$$\sigma^2 = (\Delta x)^2 = \frac{1}{n-1} \sum_{i=1}^n (\Delta x_i)^2 = \frac{1}{n-1} \sum_{i=1}^n (x_i - \overline{x})^2$$

(2.2)

Dabei ergibt sich als mittlerer Fehler (auch als Standardabweichung bezeichnet):

$$\sigma_{\overline{x}} = \Delta \overline{x} = \sqrt{\frac{1}{n(n-1)} \sum_{i=1}^{n} (x_i - \overline{x})^2} = \frac{\Delta x}{\sqrt{n}} = \frac{\sigma}{\sqrt{n}}$$

(2.3)

Die Messung von dynamischen Messgrößen, die sich zeitabhängig ändern, ist sowohl vom Messgerät als auch vom zeitlichen Verlauf des Messsignals abhängig. In diesem Fall spricht man über dynamische Messabweichungen der Messgröße. Diese Abweichungen sind zeitlich veränderlich. Aus diesem Grund benötigt man eine besondere Analyse des zeitlichen Verhaltens des Messsystems beziehungsweise des Messgerätes [Ja10]. Mathematisch kann man das zeitliche Verhalten mit Differenzialgleichungen beschreiben. Es ist theoretisch möglich, ein beliebiges Messsignal aus dem beobachteten Ausgangssignal zu rekonstruieren. In der Praxis werden zumeist Testfunktionen benutzt. Im Fall einer Sprungfunktion wird beispielsweise die Einstellzeit oder Einschwingzeit gemessen. Das ist die Zeitdauer, die gebraucht wird, bis die angezeigte Messgröße endgültig innerhalb eines gegebenen Toleranzbereiches verbleibt [PP94]. Eine andere Funktion ist ein sinusförmiges Eingangssignal variabler Frequenz. Dabei wird die Reaktion des Messsystems im Frequenzbereich untersucht [WW10]. Hier ist die sogenannte Grenzfrequenz des Messsystems als diejenige Frequenz einer harmonischen Anregung definiert, für welche das Amplitudenverhältnis zum Ausgangssignal festgelegte Toleranzwerte, in der Regel entspricht das ±3dB in der Bode-Darstellung [PP94], erreicht.

Die technischen Parameter und vor allem die messtechnischen Eigenschaften des Messsystems stehen immer im Vordergrund bei der Entwicklung. Für Messgeräte, die den zahlreichen internationalen und nationalen Vorschriften und Gesetzen entsprechen sollen, werden in diesen die messtechnischen Mindestanforderungen gestellt. Der folgende Abschnitt 2.2 stellt eine Zusammenfassung der Gesetze, Vorschriften und Richtlinien dar. Diese müssen bei der Entwicklung von derartigen Messgeräten, detailliert am Beispiel der Wägetechnik, berücksichtigt werden, wobei hier vorwiegend die für die danach folgenden Darstellungen wichtigen Aspekte betrachtet werden.

# 2.2 Eichfähigkeitsanforderungen: Gesetze, Vorschriften und Richtlinien

Wenn es um Messgeräte geht, spricht man von Messbeständigkeit. Die Funktionstüchtigkeit muss während deren gesamten Lebensdauer gewährleistet sein [DIN1319]. In der vorliegenden Arbeit werden geeichte Messgeräte (am Beispiel der Wägetechnik) betrachtet, deren Anforderungen an die Richtigkeit und Messbeständigkeit durch das Eichgesetz festgelegt sind. Nach [DIN1319][WW10] wird das Eichen als Kalibrieren durch amtliche Institutionen definiert. Dabei wird eine Prüfung des Messgerätes durchgeführt, ob seine Beschaffenheit und seine messtechnischen Eigenschaften den Forderungen der Eichvorschriften genügen. Insbesondere wird nachgewiesen, dass die Beträge der Messabweichungen die Fehlergrenze nicht überschreiten. Anschließend wird die Stempelung des Messgerätes durchgeführt. Durch diese wird beurkundet, dass das Messgerät zur Prüfungszeit den Eichfähigkeitsanforderungen genügt und bei einer Handhabung innerhalb der Nacheichfrist "richtig" bleibt.

Waagen werden seit vielen Jahren im eichpflichtigen Verkehr eingesetzt. Dabei werden sie in Genauigkeitsklassen eingeteilt, welche beispielsweise Mindestlast und Fehlergrenzen bestimmen [Be96]. Die Zulassung eines Wägesystems erfolgt nach der Eichpflicht in zwei Schritten. Zuerst wird ein Produktionsmuster vom Hersteller zur Bauprüfung an die Physikalisch-Technische Bundesanstalt [PTB14] eingereicht. Im zweiten Schritt wird jede individuelle Waage auf die Einhaltung der gesetzlichen Fehlergrenzen geprüft. In diesem Zusammenhang müssen die folgenden Anforderungen erfüllt werden [Ko89]:

- Richtigkeit des Messergebnisses (innerhalb der Fehlergrenze);

- Beständigkeit des Messwertes während der Eichgültigkeitsdauer;

- Sicherheit der Arbeitsweise unter dem Einfluss von Störgrößen;

- Ständige Einsatzbereitschaft der Waage;

- Gleichbehandlung aller Bauarten hinsichtlich der gestellten technischen Anforderungen ohne Beachtung des physikalischen Wirkungsprinzips;

- Harmonisierung in der europäischen Gemeinschaft (s. unten OIML [O14])

Nach erfolgreicher Prüfung kann die geeichte Waage für die Gültigkeitsdauer der Eichung im eichpflichtigen Verkehr verwendet werden. Nach Ablauf dieser Frist erfolgt die Nacheichung [Be96].

Die internationale Harmonisierung wird auf europäischer Ebene durch EU-Richtlinien vorangetrieben. Für die Messgeräte ist die allgemeine Richtlinie 2004/22/EG zuständig [ME09]. Diese wird als Messgerätenrichtlinie oder als Measurung Instruments Directive (MID) bezeichnet. Zusätzlich wird in der Wägetechnik die Richtlinie 2009/23/EG von der PTB gefordert [Am09].

#### In [Tr15] steht der Zweck der Harmonisierung:

"Die weltweite Vereinheitlichung der Vorschriften im Bereich des Eichwesens hat eine Doppelfunktion: auf einer Seite die Schaffung international anwendbarer, wiederholbarer wissenschaftlicher Maßeinheiten und zweitens die Gewährleistung der Einhaltung dieser Maße und Gewichte sowie der diesbezüglichen gesetzlichen Vorschriften in der Praxis des internationalen Warenverkehrs".

Es existieren die internationalen Empfehlungen der "International Organisation of Legal Metrology" (OIML). Zu metrologischen Aspekten nichtselbsttätiger Waagen gibt es die europäische Norm EN 45501 [DN92]. Diese ist nahezu gleich mit der internationalen Empfehlung R76 der OIML.

Eine weitere europäische Vereinigung der nationalen Behörden, die im gesetzlichen Messwesen tätig sind, ist WELMEC (Western European Legal Metrology Cooperation). Die WELMEC-Dokumente und Leitfäden stellen den Stand der Technik dar, haben aber nur einen empfehlenden Charakter [WEL14]. Im Abschnitt 2.3.2 werden die Empfehlungen von WELMEC bezüglich der Informationsverarbeitung in Messsystemen detaillierter dargestellt.

Neben der nationalen Eichbehörde gibt es in anderen Länder auch Organisationen, die zusätzliche Forderungen für Messgeräte aufstellen. In der Wägetechnik müssen die Waagen, die in Medizin- oder Lebensmittelindustriebereichen eingesetzt werden, auch andere besondere Bestimmungen erfüllen. Dazu zählt man die Richtlinien und die Zertifizierungsvorschriften der FDA [FDA14]. Außerdem werden von dem Hersteller des Messgerätes die detaillierte Beschreibung aller Entwicklungsphasen und die Spezifikation des Produktes abgefragt. Diese werden normalerweise in Form eines Entwicklungsprozesses dokumentiert, und durch die FDA wird das Messgerät nach den beschriebenen Etappen überprüft. Die Hauptphasen des zertifizierten Entwicklungsprozesses sind dabei: Anforderungen und Spezifikation, Entwurf und Entwicklungsplanung, Verifikation und Validierung, Fertigung, Verpackung und Kennzeichnung, Kommerzialisierung. [MJZ13]

Diese und noch weitere spezielle Software- und Hardware-Standards müssen bei der Entwicklung von Messsystemen (hier Waagen) berücksichtigt werden. Es wird dabei nicht nur die Einhaltung von bestehenden Eichvorschriften und Sicherheitsvorschriften, sondern auch die Gewährleistung eines kontinuierlich ablaufenden Produktionsprozesses gefordert. Deswegen müssen diese bereits bei der Entwicklung von Prototypen integriert werden. In dieser Arbeit wird ein Weg vorgestellt, welcher die systematische Abarbeitung der einzelnen Forderungspunkte beschreibt.

#### 2.3 Digitale Informationsverarbeitung in der Messtechnik

Die Informationsverarbeitung in der Messtechnik besteht nicht nur aus der Signalverarbeitung in einem Messsystem, sondern auch aus der Regelungs- und Steuerungstechnik,

Datenübertragung, Speicherung und Messdatenaufbereitung. Diese Aufgaben können mit analoger Elektronik oder unter Nutzung von digitaler Technik realisiert werden [Ja10].

Die analoge Informationsverarbeitung benutzt zumeist den zeitlichen Verlauf eines Signals (abgebildet auf eine Spannung) als Darstellung für Mess- und Zwischengrößen. Dabei existieren die folgenden Anforderungen an die analoge Elektronik [Hü96][Ja10]:

- Realisierung von Filterfunktionen, einfachen Regelalgorithmen, elementaren arithmetischen Operationen und Übertragung elektrischer Signale;

- Realisierung der Funktionen in den geforderten Genauigkeiten und in dem notwendigen Zeitverhalten.

Dabei treten die für analoge Elektronik bekannten Probleme auf [PP94][Hü96][Ja10]:

- geringe Funktionsvielfalt;

- nicht veränderbare Funktionsfestlegung durch Verdrahtung;

- Nichtlinearitäten des Ausgangs-/Eingangsverhaltens über den Darstellungsbereich des Signals;

- Frequenzabhängigkeit des Ausgangs-/Eingangsverhaltens;

- begrenzte Auflösung;

- Störempfindlichkeit (z.B. durch elektromagnetische Felder oder durch Beeinflussung der elektrischen Signale untereinander);

- Temperaturveränderung;

- Signalrauschen;

- Fertigungstoleranzen der Bauelemente;

- Begrenzte oder fehlende Möglichkeiten zur Abspeicherung der Signalwerte;

- Spezielle konstruktive Probleme (z.B. Platzbedarf, Stromaufnahme und Wärmeentwicklung).

Im Gegensatz zur analogen Signaltechnik werden in der digitalen Signalverarbeitung kontinuierlich verlaufende Signale in diskrete Signalwerte kodiert. In diesem Fall muss jede kodierte Größe durch mehrere geordnete Binärsignale beschrieben werden [WW10]. Die digitale Darstellung und Verarbeitung von Informationen benötigt deshalb die Analog-Digital-Wandlung der Eingangs- und gegebenenfalls die Digital-Analog-Wandlung der Ausgangssignale. Eventuelle Nachteile, die durch eine kodierte Darstellung entstehen, werden jedoch in dem messtechnischen Bereich durch die Vorteile der digitalen Informationsverarbeitung mehr als kompensiert [Sa12].

Verfahren der digitalen Informationsverarbeitung existieren bereits seit den letzten Jahrzehnten. Grundlagen von numerischen Techniken wurden schon im 19. Jahrhundert verwendet. Hier kann man die bekannte mathematische Theorie (Fourier-Analyse oder klassische harmonische Analyse) von Fourier nennen, die es ermöglicht, eine Zeitfunktion in eine Fourier-Reihe zu zerlegen und somit deren Frequenzspektrum diskret darzustellen [Br96]. Eine weitere wichtige Erfindung ist die Theorie der Signalabtastung von Nyquist und Shannon (in der russischen Literatur: Abtasttheorem von Kotelnikow) [BR13]. In der Mitte und am Ende des 20. Jahrhunderts verursachte die rasante Entwicklung der Rechentechnik eine stark zunehmende Bedeutung der digitalen Informationsverarbeitung in verschiedensten technischen Bereichen. Eines dieser Anwendungsgebiete ist seit längerer Zeit die Messtechnik [PP94], wobei mehrere wesentliche Vorteile auftreten [GM07].

Mit der digitalen Informationsverarbeitung wird es möglich komplexe Algorithmen mit einem hohen Maß an Flexibilität in kürzerer Zeit berechnen zu können. Dabei wird eine Software- und Hardware-gesteuerte Verarbeitung mit der Rechentechnik realisiert. Außerdem sind verschiedene Strategien der Signalverarbeitung möglich, z.B. in der Wägetechnik - nichtlineare oder adaptive Regelung im Gegensatz zur klassischen Analogregelung [WGA13]. Die Funktionen sind durch Programmierung leicht änderbar. Nichtlinearitäten des Ausgangs-/Eingangsverhaltens verschieben sich zu deutlich höheren Frequenzen [Ja10]. Als Weiteres ist die Darstellung von Daten mit deutlich höherer und anpassbarer Genauigkeit möglich.

Als einen Vorteil kann man auch hohe Sicherheit nennen. In [Sa12] steht:

"Während sich die analoge Information durch jede - auch noch so kleine - Störung verändert, wird die digital kodierte Information erst dann verfälscht, wenn ein Störimpuls größer ist als der Störabstand des jeweiligen digitalen Pegels. Der Störabstand ergibt sich aus der Differenz von Sende- und Empfangspegel.... Durch die Wahl der binären Informationsdarstellung ist es möglich, den Störabstand in weiten Grenzen auf die Gegebenheit des Umfeldes abzustimmen".

Damit haben die Fertigungstoleranzen und die Temperaturabhängigkeiten der Bauelemente, das Rauschen und die gegenseitige Beeinflussung der Signale praktisch keinen Einfluss mehr.

Ein weiterer Vorteil ist die einfache Datenspeicherung. Außerdem sind kurz- und langzeitige Speicherungen möglich. Hiermit ist die Anforderung der Messtechnik, große Datenmengen sicher und preiswert zu speichern, effektiv realisierbar [Ja10].

Als besonders wichtig werden die vielfältigen Übertragungsmöglichkeiten in der digitalen Informationsverarbeitung genannt. Die digitalen Werte lassen sich einfach auf vielfältige Weise kodieren. Aus diesem Grund sind große Distanzen und geringer Aufwand bei der Übertragung möglich [PP94]. Bei den konstruktiven Parametern erweist sich

ebenfalls die digitale Realisierung zumeist als günstiger. Das gilt nicht unbedingt für deren Kosten [Be91].

Die bereits benannten Funktionen, Analog-Digital-Wandlung und Digital-Analog-Wandlung, benötigen eine hybride Realisierung und weisen damit Vor- und Nachteile beider Realisierungstechnologien (analog und digital) auf [Ja10][PP94][BST10].

In den folgenden Abschnitten werden bestehende Prinzipien der digitalen Informationsverarbeitung in der Messtechnik näher erläutert. Der Hauptgesichtspunkt der Arbeit liegt in der dynamischen Wägetechnik. Deswegen werden deren bekannte Lösungen im Bereich der Signalverarbeitung detaillierter dargestellt und im Abschnitt 2.3.2 die Besonderheiten unter Berücksichtigung der Eichfähigkeit und anderer Forderungen diskutiert.

# 2.3.1 Bestehende Prinzipien der digitalen Informationsverarbeitung in der Mess- und Wägetechnik

Die Aufgabe der Messtechnik besteht darin, die eindimensionalen und mehrdimensionalen Messgrößen technischer Prozesse aufzunehmen. Weiterhin werden die erhaltenden umgeformten Messsignale als Messwerte so verarbeitet, dass die Zielgröße (Messergebnis) gewonnen wird [Hü96]. In diesem Zusammenhang werden die speziellen Aufgaben eines mechatronischen Systems in fundamentaler Weise durch die Informationsverarbeitung der Eingangssignale (Sensor und Bediensignale) und durch die Ausgabe der Information (in Form von Messergebnissen oder als Stellsignale) bestimmt [Ja10].

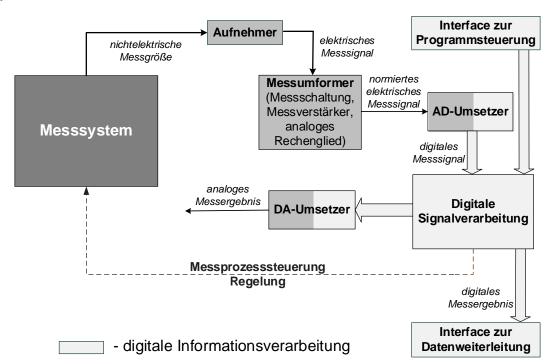

Die Abbildung 2.2 stellt die Messglieder einer Signalverarbeitungskette in einem Messsystem dar.

Abbildung 2.2: Signalverarbeitungskette mit digitaler Informationsverarbeitung

Zunächst formen Sensoren (Aufnehmer) die im Allgemeinen nichtelektrische Messgröße in ein elektrisches Messsignal um. Weiterhin wird das Signal dank geeigneter Messschaltungen, Messverstärker und anderer Rechenglieder umgeformt und ein normiertes analoges Messsignal gewonnen. In dem digitalen Informationsverarbeitungssystem wird die Analog-Digital-Umwandlung benötigt. Dabei wird das analoge Signal bezüglich Zeit und Wert zuerst abgetastet und quantisiert, und anschließend in ein digitales Messsignal kodiert [PP94]. Dabei muss es so bemessen werden, dass das resultierende Raster der diskreten Werte die Messgenauigkeit nicht beeinträchtigt [WW10].

Für jede Analog-Digital-Umwandlung wird eine gewisse Zeit gebraucht (abhängig von den Charakteristiken des Umsetzers). Darüber hinaus sorgt der begrenzte Speicherplatz für eine Begrenzung der zeitkontinuierlich aufgezeichneten Digitalwerte [HHR12]. Deswegen wird man dazu gezwungen, das zeitkontinuierliche Signal über einen bestimmten Zeitraum in regelmäßigen Abständen abzutasten. Es muss berücksichtigt werden, dass der Informationsgehalt des Messsignals wegen der Alias-Effekte verfälscht wird. Um diese zu vermeiden, muss die Abtastfrequenz mindestens doppelt so groß wie die höchste auftretende Signalfrequenz gewählt werden: f<sub>Signal</sub> < f<sub>Abtast</sub> / 2. Dieses Theorem wird in unterschiedlichen Literaturquellen verschieden genannt [PP94][Hü96][BR13], da aber Shannon 1949 eine informationstechnische Begründung dafür formulierte [WW10], wird es hier Nyquist-Shannon-Theorem genannt. In vielen Messsystemen treten häufig höhere Schwingungsfrequenzen auf. Damit diese Frequenzen unterdrückt werden oder die Abtastfrequenz in Bezug zur Grenzfrequenz möglich gering bleibt, wird ein analoger Tiefpassfilter vor dem Abtast-Halteglied (als Antialiasing-Filter bekannt [Hü96][WW10]) geschaltet.

Eine weitere Schnittstelle zwischen dem Informationsverarbeitungssystem und der analogen Umgebung im Messsystem stellt die Digital-Analog-Umwandlung dar. Abhängig von der zu ermittelnden beziehungsweise zu verarbeitenden Information wird diese digital und/oder analog ausgegeben. [PP94][HHR12]

Wenn Stellsignale für die Aktoren des Messsystems erzeugt werden, wird der Wirkungskreis geschlossen (Messprozesssteuerung, Regelung). Der Wirkungskreis hat die Aufgabe, unerwünschte Störeinflüsse im Gesamtsystem zu unterdrücken, gezieltes Bewegungsverhalten im Messsystem zu realisieren und robuste Stabilität bei Parameterunbestimmtheiten- und –variationen zu ermöglichen [Ja10][RZ04].

Die oben beschriebenen Messglieder der Signalverarbeitungskette sind nicht ideal, wodurch die Messsignale häufig verfälscht werden [Hü96][RZ04]. Für diese Fälle wird eine korrigierende Signalverarbeitung durchgeführt, damit das ermittelte Messergebnis mit einer kleineren Messunsicherheit bestimmt wird. Hier können die Korrekturen z.B. als Kalibrierung, Linearisierung oder digitale Filterung durch einen Messrechner durch-

geführt werden. Die Digitalfilter können in unterschiedlichen Topologien aufgebaut werden (FIR-Filter "finite impulse response filter", IIR-Filter "infinite impulse response filter", WDF "Wellen-Digital-Filter"). In der Messtechnik kommt häufig der digitale Mittelwertfilter zum Einsatz [Ja10][Do08], wobei von einem Signal ein "gleitender Mittelwert" (moving average) gebildet wird. Laut [Be91] kann der Mittelwertfilter als FIR- und IIR-Filter realisiert werden. Grundsätzlich kann ein Digitalfilter hardwaremäßig beziehungsweise softwaremäßig umgesetzt werden. Die Implementierung durch Hardware ist die schnellste, jedoch sind die Kosten und die Realisierbarkeit von der Komplexität der Algorithmen abhängig. Die softwaremäßige Realisierung ist meist kostengünstiger, dabei wird der Digitalfilteralgorithmus durch einen Digitalrechner (z.B. Mikroprozessor, DSP) abgearbeitet [PP94][Ro91].

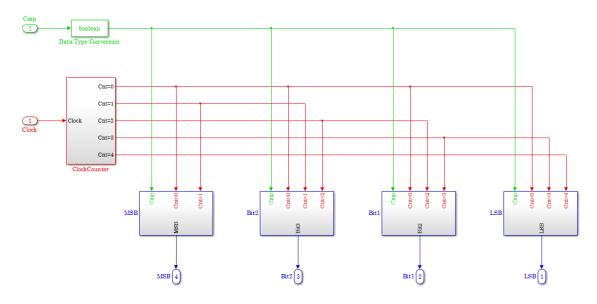

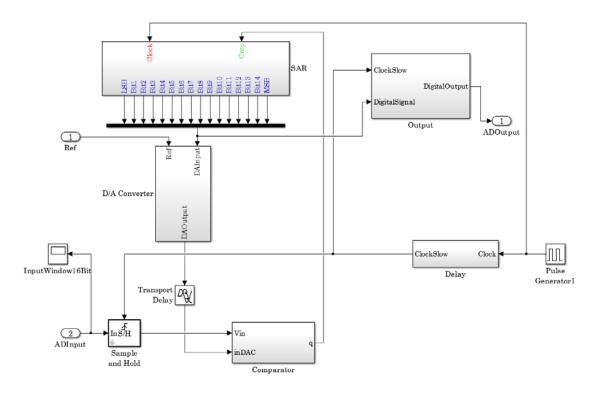

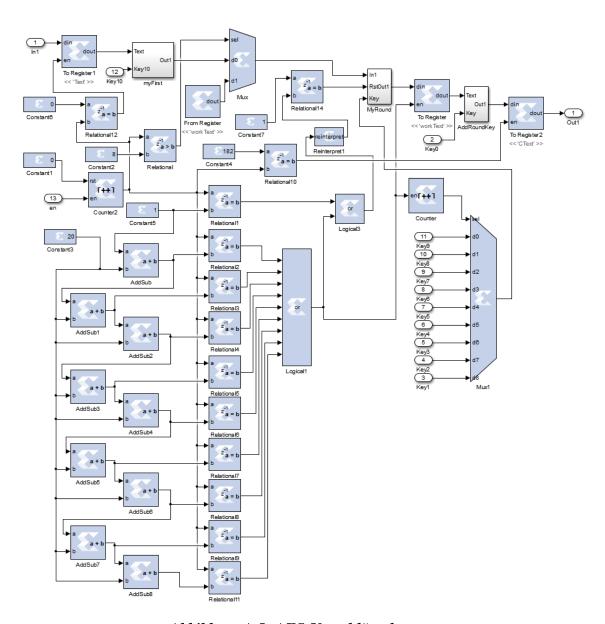

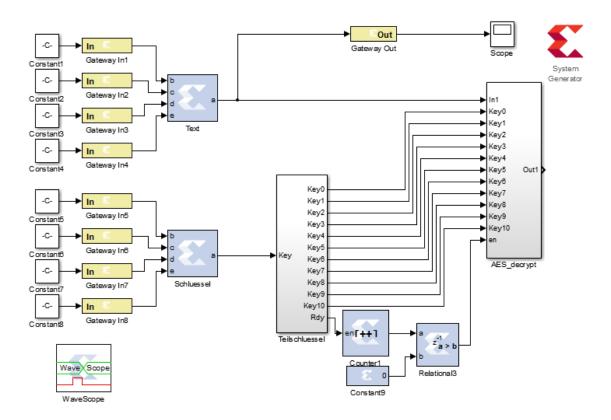

In der Praxis haben sich die Methoden von adaptiven Algorithmen bewährt [MB07]. Hierbei werden die Regler- und Filteralgorithmen an die störenden Einflüsse, sowie an die Messzeit im Signalverarbeitungssystem angepasst [Do08][Be91]. Es existiert eine Vielzahl von Algorithmen, die für die Adaptierung der Parameter verwendet werden können. Die Geschwindigkeit der Adaption ist von den eingesetzten Algorithmen und von den Realisierungsvarianten abhängig. Ein häufig verwendetes Beispiel eines adaptiven Filteralgorithmus ist der Kalman-Filter, der in mechatronischen Systemen als Störbeobachter beziehungsweise Zustandsbeobachter eingesetzt wird. Dabei können die nicht messbaren Störungen im System geschätzt werden [Am10][RZ04].