# Towards an Embedded Board-Level Tester Study of a Configurable Test Processor

### Dissertation

Zur Erlangung des akademischen Grades Doktor-Ingenieur (Dr.-Ing)

vorgelegt in der Fakultät für Informatik und Automatisierung der Technischen Universität Ilmenau

von Herrn Ing. Jorge Hernán Meza Escobar, geboren am 18.01.1984 in Cali, Kolumbien

Datum der Einrichtung: 15.06.2016 (vorliegende Revision vom 29.11.2016)

Datum der Verteidigung: 21.11.2016

Gutachter: 1. Prof. Dr.-Ing. habil. Andreas Mitschele-Thiel,

Technische Universität Ilmenau

2. Prof. Dr.-Ing. Sebastian Michael Sattler, Friedrich-Alexander Universität Erlangen-Nürnberg

3. Prof. Dr. Raimund-Johannes Ubar, Tallinn University of Technology

# **Acknowledgments**

First, I would like to express my deepest and sincere gratitude to my advisors Dr.-Ing. Heinz-Dietrich Wuttke and Prof. Dr.-Ing. habil. Andreas Mitschele-Thiel. Thank you for letting me be part of the ICS group, for the excellent scientific guidance of my thesis, and for your constructive reviews, suggestions, and discussions, which significantly improved this work.

I would also like to express my gratitude and appreciation to my whole family, especially to my parents Jorge and Leonor, my brother Kike, and my sister Leonor. Thank you for your support and for encouraging me to pursue my dreams. Special thanks go to Pamela for all her love, support, and encouragement. I would also like to thank my cousin Grace Lewis for her grammar and text corrections.

I would like to thank the HW/SW systems group, especially Steffen Ostendorff and Jörg Sachße. The embedded board-level tester and the test processor would surely not be able to work without your contributions! My special thanks go to Dr.-Ing. Karsten Henke and all ICS group members. Thanks for having an open ear for discussing various aspects of my theoretical and practical work.

I would like to thank the organizational and technical staff, Nicole Sauer, Nadine Wolf, and specially Jürgen Schmidt. I would also like to thank the reviewers for investing their time in reading and evaluating this work.

Finally, I would like to express my gratitude and recognize that this research would not have been possible without the financial assistance of the Thüringer Aufbaubank (TAB), the Zentrales Innovationsprogram Mittelstand (ZIM), and the TU Ilmenau. I am also very thankful to Göpel Electronic and Thomas Wenzel for the opportunity to develop this research with the collaboration of an industry partner.

# **Abstract**

The demand for electronic systems with more features, higher performance, and less power consumption increases continuously. This is a real challenge for design and test engineers because they have to deal with electronic systems with ever-increasing complexity maintaining production and test costs low and meeting critical time to market deadlines.

For a test engineer working at the board-level, this means that manufacturing defects must be detected as soon as possible and at a low cost. However, the use of classical test techniques for testing modern printed circuit boards is not sufficient, and in the worst case these techniques cannot be used at all. This is mainly due to modern packaging technologies, a high device density, and high operation frequencies of modern printed circuit boards. This leads to very long test times, low fault coverage, and high test costs.

This dissertation addresses these issues and proposes an FPGA-based test approach for printed circuit boards. The concept is based on a configurable test processor that is temporarily implemented in the on-board FPGA and provides the corresponding mechanisms to communicate to external test equipment and co-processors implemented in the FPGA. This embedded test approach provides the flexibility to implement test functions either in the external test equipment or in the FPGA. In this manner, tests are executed at-speed increasing the fault coverage, test times are reduced, and the test system can be adapted automatically to the properties of the FPGA and devices located on the board.

An essential part of the FPGA-based test approach deals with the development of a test processor. In this dissertation the required properties of the processor are discussed, and it is shown that the adaptation to the specific test scenario plays a very important role for the optimization. For this purpose, the test processor is equipped with configuration parameters at the instruction set architecture and microarchitecture level. Additionally, an automatic generation process for the test system and for the computation of some of the processor's configuration parameters is proposed. The automatic generation process uses as input a model known as the device under test model (DUT-M).

In order to evaluate the entire FPGA-based test approach and the viability of a processor for testing printed circuit boards, the developed test system is used to test interconnections to two different devices: a static random memory (SRAM) and a liquid crystal display (LCD). Experiments were conducted in order to determine the resource utilization of the processor and FPGA-based test system and to measure test time when different test functions are implemented in the external test equipment or the FPGA. It has been shown

VI Abstract

that the introduced approach is suitable to test printed circuit boards and that the test processor represents a realistic alternative for testing at board-level.

# Zusammenfassung

Der Bedarf an elektronischen Systemen mit zusätzlichen Merkmalen, höherer Leistung und geringerem Energieverbrauch nimmt ständig zu. Dies stellt eine erhebliche Herausforderung für Entwicklungs- und Testingenieure dar, weil sie sich mit elektronischen Systemen mit einer steigenden Komplexität zu befassen haben. Außerdem müssen die Herstellungs- und Testkosten gering bleiben und die Produkteinführungsfristen so kurz wie möglich gehalten werden.

Daraus folgt, dass ein Testingenieur, der auf Leiterplatten-Ebene arbeitet, die Herstellungsfehler so früh wie möglich entdecken und dabei möglichst niedrige Kosten verursachen soll. Allerdings sind die klassischen Testmethoden nicht in der Lage, die Anforderungen von modernen Leiterplatten zu erfüllen und im schlimmsten Fall können diese Testmethoden überhaupt nicht verwendet werden. Dies liegt vor allem an modernen Gehäuse-Technologien, der hohen Bauteildichte und den hohen Arbeitsfrequenzen von modernen Leiterplatten. Das führt zu sehr langen Testzeiten, geringer Testabdeckung und hohen Testkosten.

Die Dissertation greift diese Problematik auf und liefert einen FPGA-basierten Testansatz für Leiterplatten. Das Konzept beruht auf einem konfigurierbaren Testprozessor, welcher im On-Board-FPGA temporär implementiert wird und die entsprechenden Mechanismen für die Kommunikation mit der externen Testeinrichtung und Co-Prozessoren im FPGA bereitstellt. Dadurch ist es möglich Testfunktionen flexibel entweder auf der externen Testeinrichtung oder auf dem FPGA zu implementieren. Auf diese Weise werden Tests atspeed ausgeführt, um die Testabdeckung zu erhöhen. Außerdem wird die Testzeit verkürzt und das Testsystem automatisch an die Eigenschaften des FPGAs und anderer Bauteile auf der Leiterplatte angepasst.

Ein wesentlicher Teil des FPGA-basierten Testansatzes umfasst die Entwicklung eines Testprozessors. In dieser Dissertation wird über die benötigten Eigenschaften des Prozessors diskutiert und es wird gezeigt, dass die Anpassung des Prozessors an den spezifischen Testfall von großer Bedeutung für die Optimierung ist. Zu diesem Zweck wird der Prozessor mit Konfigurationsparametern auf der Befehlssatzarchitektur-Ebene Mikroarchitektur-Ebene ausgerüstet. Außerdem wird und ein automatischer Generierungsprozess für die Realisierung des Testsystems und für die Berechnung einer Untergruppe von Konfigurationsparametern des Prozessors vorgestellt. Der automatische Generierungsprozess benutzt als Eingangsinformation ein Modell des Prüflings (device under test model, DUT-M).

VIII Zusammenfassung

Das entwickelte Testsystem wurde zum Testen von Leiterplatten für Verbindungen zwischen dem FPGA und zwei Bauteilen verwendet, um den FPGA-basierten Testansatz und die Durchführbarkeit des Testprozessors für das Testen auf Leiterplatte-Ebene zu evaluieren. Die zwei Bauteile sind ein Speicher mit direktem Zugriff (static random-access memory, SRAM) und eine Flüssigkristallanzeige (liquid crystal display, LCD). Die Experimente wurden durchgeführt, um den Ressourcenverbrauch des Prozessors und Testsystems festzustellen und um die Testzeit zu messen. Dies geschah durch die Implementierung von unterschiedlichen Testfunktionen auf der externen Testeinrichtung und dem FPGA. Dadurch konnte gezeigt werden, dass der FPGA-basierte Ansatz für das Testen von Leiterplatten geeignet ist und dass der Testprozessor eine realistische Alternative für das Testen auf Leiterplatten-Ebene ist.

# **Table of Contents**

| List of | Tables                                            | XIII |

|---------|---------------------------------------------------|------|

| List of | Figures                                           | XV   |

| Acrony  | /ms                                               | XVII |

| 1 Int   | roduction                                         | 1    |

| 1.1     | Motivation                                        |      |

| 1.2     | Problem statement and research questions          |      |

| 1.3     | Publications related to this work                 |      |

| 1.4     | Structure of the dissertation and contributions   |      |

| 2 Ba    | ckground                                          | 7    |

| 2.1     | Testing, what is it?                              | 7    |

| 2.1.1   | Introduction                                      | 7    |

| 2.1.2   | Errors and defects                                | 8    |

| 2.1.3   | Validation, verification, and testing             | 9    |

| 2.1.4   | Fault and fault models                            | 9    |

| 2.1.5   | Diagnosis                                         | 15   |

| 2.1.6   | Test quality metrics and test costs               | 18   |

| 2.2     | Printed circuit board testing                     | 19   |

| 2.2.1   | Manufacturing process                             | 19   |

| 2.2.2   | Board-level testing                               |      |

| 2.2.3   | Board-level test techniques                       | 23   |

| 2.3     | Embedded board-level test techniques              |      |

| 2.3.1   | Processor-based testing                           | 29   |

| 2.3.2   | FPGA-based testing                                | 31   |

| 2.4     | Soft-core and test processors                     | 31   |

| 2.4.1   | Soft-core processors                              |      |

| 2.4.2   | Test processors                                   | 33   |

| 3 Pro   | ocessor in FPGA-based testing                     |      |

| 3.1     | FPGA-based testing                                |      |

| 3.1.1   | Building blocks                                   |      |

| 3.1.2   | Test scenario, application field, DUT, and faults |      |

| 3.1.3   | Test phases                                       |      |

| 3.1.4   | Design automation in FPGA-based testing           |      |

| 3.2     | FPGA-based testing in the literature              |      |

| 3 2 1   | Ad-hoc FPGA test instruments                      | 47   |

Table of Contents

| 3.2.2       | Generic FPGA test instruments               | 48  |

|-------------|---------------------------------------------|-----|

| 3.2.3       | Summary of embedded FPGA test instruments   | 50  |

| 3.3         | ROBSY approach                              | 50  |

| 3.3.1       | Modeling the test functionality             | 51  |

| 3.3.2       | FBTS architecture                           | 54  |

| 3.4         | Processor in the FPGA-based test system     | 58  |

| 3.4.1       | Processor impact                            | 58  |

| 3.4.2       | Analysis of L1                              | 61  |

| 3.4.3       | Analysis of L2                              | 65  |

| 3.4.4       | Analysis of L3                              |     |

| 3.4.5       | Analysis of L4 and L5                       | 67  |

| 3.4.6       | Analysis of interfaces I1, I2 and I3        | 68  |

| 3.5         | Summary                                     | 70  |

| 4 Co        | ncept of the ROBSY processor                | 71  |

| 4 00<br>4.1 | Introduction                                |     |

| 4.1         | General design aspects                      |     |

| 4.2.1       | ROBSY processor requirements                |     |

| 4.2.2       | Analysis of pre-designed processors         |     |

| 4.2.3       | Fundamental design choices                  |     |

| 4.3         | Processor specialization for testing        |     |

| 4.3.1       | Tailoring the processor for testing         |     |

| 4.3.2       | Test operations                             |     |

| 4.3.3       | Interfaces I2 and I3                        |     |

| 4.4         | Adaptation to the test scenario             |     |

| 4.4.1       | General adaptation mechanisms               |     |

| 4.4.2       | Adaptation mechanism of the ROBSY processor |     |

| 4.5         | Summary                                     |     |

|             |                                             |     |

|             | BSY processor                               |     |

| 5.1         | Introduction                                |     |

| 5.2         | Instruction set architecture                |     |

| 5.2.1       | Native data types                           |     |

| 5.2.2       | Programmer visible state and I/O            |     |

| 5.2.3       | Instruction set                             |     |

| 5.2.4       | Interrupts and exceptions                   |     |

| 5.3         | Microarchitecture                           |     |

| 5.3.1       | Top level view                              |     |

| 5.3.2       | Program, data, and stack memories           |     |

| 5.3.3       | Data controller                             |     |

| 5.3.4       | Stack controller                            |     |

| 5.3.5       | Central processing unit                     | 111 |

Table of Contents XI

| 5.4                                                                                   | Debug-Interface                                                                                                                                                                                                                                                                                                                                               | 116                                  |

|---------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| 5.4.1                                                                                 | Debug-commands                                                                                                                                                                                                                                                                                                                                                | 116                                  |

| 5.4.2                                                                                 | Access to the JTAG port                                                                                                                                                                                                                                                                                                                                       | 117                                  |

| 5.4.3                                                                                 | Structure of the debug-interface                                                                                                                                                                                                                                                                                                                              | 118                                  |

| 5.5                                                                                   | Configuration parameters                                                                                                                                                                                                                                                                                                                                      | 121                                  |

| 5.6                                                                                   | Summary                                                                                                                                                                                                                                                                                                                                                       | 122                                  |

| <b>6 A</b> u                                                                          | tomatic generation process                                                                                                                                                                                                                                                                                                                                    | 125                                  |

| 6.1                                                                                   | Introduction                                                                                                                                                                                                                                                                                                                                                  | 125                                  |

| 6.2                                                                                   | Overview of the automatic generation process                                                                                                                                                                                                                                                                                                                  | 125                                  |

| 6.3                                                                                   | ATE program generator                                                                                                                                                                                                                                                                                                                                         | 127                                  |

| 6.3.1                                                                                 | ATE/FBTS communication                                                                                                                                                                                                                                                                                                                                        | 127                                  |

| 6.3.2                                                                                 | Software compiler                                                                                                                                                                                                                                                                                                                                             | 129                                  |

| 6.3.3                                                                                 | Auxiliary software generator and supported ATE tools                                                                                                                                                                                                                                                                                                          | 129                                  |

| 6.4                                                                                   | FPGA based test system generator                                                                                                                                                                                                                                                                                                                              | 130                                  |

| 6.4.1                                                                                 | Processor/co-processor communication                                                                                                                                                                                                                                                                                                                          | 132                                  |

| 6.4.2                                                                                 | Reorganization of the configuration parameters                                                                                                                                                                                                                                                                                                                | 132                                  |

| 6.4.3                                                                                 | Embedded software generator.                                                                                                                                                                                                                                                                                                                                  | 135                                  |

| 6.4.4                                                                                 | Hardware generator                                                                                                                                                                                                                                                                                                                                            | 138                                  |

| 6.4.5                                                                                 | Synthesis tool                                                                                                                                                                                                                                                                                                                                                | 138                                  |

| 6.5                                                                                   | Summary                                                                                                                                                                                                                                                                                                                                                       | 138                                  |

|                                                                                       |                                                                                                                                                                                                                                                                                                                                                               |                                      |

| 7 Ex                                                                                  | perimental phase                                                                                                                                                                                                                                                                                                                                              | 141                                  |

| 7 Ex                                                                                  | perimental phaseIntroduction                                                                                                                                                                                                                                                                                                                                  |                                      |

|                                                                                       |                                                                                                                                                                                                                                                                                                                                                               | 141                                  |

| 7.1                                                                                   | Introduction                                                                                                                                                                                                                                                                                                                                                  | 141<br>141                           |

| 7.1<br>7.2                                                                            | Introduction  Experimental setup  Hardware setup  Software setup                                                                                                                                                                                                                                                                                              | 141<br>141<br>143                    |

| <b>7.1 7.2</b> 7.2.1                                                                  | Introduction Experimental setup Hardware setup                                                                                                                                                                                                                                                                                                                | 141<br>141<br>143                    |

| <b>7.1 7.2</b> 7.2.1 7.2.2                                                            | Introduction  Experimental setup  Hardware setup  Software setup                                                                                                                                                                                                                                                                                              | 141<br>141<br>143<br>144             |

| <b>7.1 7.2</b> 7.2.1 7.2.2 7.2.3                                                      | Introduction  Experimental setup  Hardware setup  Software setup  Processor and FBTS variants                                                                                                                                                                                                                                                                 | 141141143144145                      |

| <b>7.1 7.2</b> 7.2.1 7.2.2 7.2.3 7.2.4                                                | Introduction  Experimental setup  Hardware setup  Software setup  Processor and FBTS variants  Resource utilization and performance metrics                                                                                                                                                                                                                   | 141141143144145                      |

| 7.1 7.2 7.2.1 7.2.2 7.2.3 7.2.4 7.3                                                   | Introduction  Experimental setup  Hardware setup  Software setup  Processor and FBTS variants  Resource utilization and performance metrics  Devices under test                                                                                                                                                                                               | 141141143144145146                   |

| 7.1 7.2 7.2.1 7.2.2 7.2.3 7.2.4 7.3 7.3.1                                             | Introduction  Experimental setup  Hardware setup  Software setup  Processor and FBTS variants  Resource utilization and performance metrics  Devices under test  SRAM                                                                                                                                                                                         | 141141143145146146                   |

| 7.1 7.2 7.2.1 7.2.2 7.2.3 7.2.4 7.3 7.3.1 7.3.2                                       | Introduction  Experimental setup  Hardware setup  Software setup  Processor and FBTS variants  Resource utilization and performance metrics  Devices under test  SRAM  LCD                                                                                                                                                                                    | 141141143145146146148                |

| 7.1 7.2 7.2.1 7.2.2 7.2.3 7.2.4 7.3 7.3.1 7.3.2 7.4                                   | Introduction  Experimental setup  Hardware setup  Software setup  Processor and FBTS variants  Resource utilization and performance metrics  Devices under test  SRAM  LCD  Resource utilization  Effect of the dependent configuration parameters  Processor variants                                                                                        | 141141143145146148149151             |

| 7.1 7.2 7.2.1 7.2.2 7.2.3 7.2.4 7.3 7.3.1 7.3.2 7.4 7.4.1 7.4.2 7.4.3                 | Introduction  Experimental setup  Hardware setup  Software setup  Processor and FBTS variants  Resource utilization and performance metrics  Devices under test  SRAM  LCD  Resource utilization  Effect of the dependent configuration parameters  Processor variants  Layer partition                                                                       | 141141143144145146148149151          |

| 7.1 7.2 7.2.1 7.2.2 7.2.3 7.2.4 7.3 7.3.1 7.3.2 7.4 7.4.1 7.4.2 7.4.3 7.4.4           | Introduction  Experimental setup  Hardware setup  Software setup  Processor and FBTS variants  Resource utilization and performance metrics  Devices under test  SRAM  LCD  Resource utilization  Effect of the dependent configuration parameters  Processor variants  Layer partition  FPGA capacity                                                        | 141141143145146148149151156          |

| 7.1 7.2 7.2.1 7.2.2 7.2.3 7.2.4 7.3 7.3.1 7.3.2 7.4 7.4.1 7.4.2 7.4.3                 | Introduction  Experimental setup  Hardware setup  Software setup  Processor and FBTS variants  Resource utilization and performance metrics  Devices under test  SRAM  LCD  Resource utilization  Effect of the dependent configuration parameters  Processor variants  Layer partition  FPGA capacity  FBTS active time                                      |                                      |

| 7.1 7.2 7.2.1 7.2.2 7.2.3 7.2.4 7.3 7.3.1 7.3.2 7.4 7.4.1 7.4.2 7.4.3 7.4.4           | Introduction  Experimental setup  Hardware setup  Software setup  Processor and FBTS variants  Resource utilization and performance metrics  Devices under test  SRAM  LCD.  Resource utilization  Effect of the dependent configuration parameters  Processor variants  Layer partition  FPGA capacity  FBTS active time  Processor variants                 | 141141143144145146148149151156150    |

| 7.1 7.2 7.2.1 7.2.2 7.2.3 7.2.4 7.3 7.3.1 7.3.2 7.4 7.4.1 7.4.2 7.4.3 7.4.4 7.5       | Introduction  Experimental setup  Hardware setup  Software setup  Processor and FBTS variants  Resource utilization and performance metrics  Devices under test  SRAM  LCD  Resource utilization  Effect of the dependent configuration parameters  Processor variants  Layer partition  FPGA capacity  FBTS active time  Processor variants  Layer partition | 141141143145146148149151156159160163 |

| 7.1 7.2 7.2.1 7.2.2 7.2.3 7.2.4 7.3 7.3.1 7.3.2 7.4 7.4.1 7.4.2 7.4.3 7.4.4 7.5 7.5.1 | Introduction  Experimental setup  Hardware setup  Software setup  Processor and FBTS variants  Resource utilization and performance metrics  Devices under test  SRAM  LCD.  Resource utilization  Effect of the dependent configuration parameters  Processor variants  Layer partition  FPGA capacity  FBTS active time  Processor variants                 | 141141143145146148149151156159160163 |

XII Table of Contents

| 7.6.2                                  | Experimental results                    | 167                             |

|----------------------------------------|-----------------------------------------|---------------------------------|

| 7.6.3                                  | FPGA configuration time                 | 168                             |

| 7.7                                    | Comparison to other approaches          | 168                             |

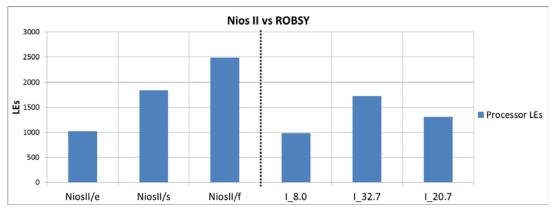

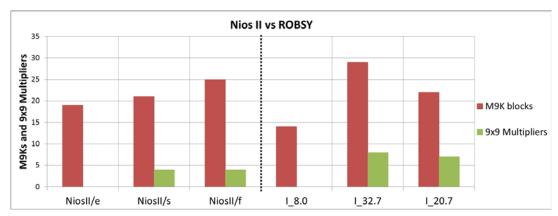

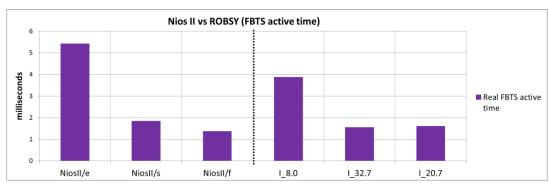

| 7.7.1                                  | ROBSY vs Nios II                        | 168                             |

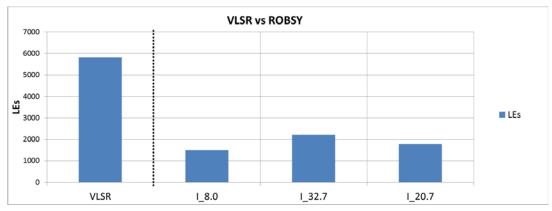

| 7.7.2                                  | ROBSY vs VLSR                           | 171                             |

| 7.8                                    | Summary                                 | 173                             |

| 7.8.1                                  | Resource utilization                    | 174                             |

| 7.8.2                                  | FBTS active time                        | 175                             |

| 7.8.3                                  | Test time                               | 177                             |

| 7.8.4                                  | Comparison to Nios II and VLSR          | 177                             |

| 7.8.5                                  | Synthesis tool                          | 178                             |

| 7.8.6                                  | Selection of a processor variant        | 179                             |

|                                        | 1                                       |                                 |

| 8 Co                                   | nclusions                               |                                 |

| 8 Co<br>8.1                            | -                                       | 181                             |

|                                        | nclusions Introduction                  | 181<br>181                      |

| 8.1                                    | nclusions                               | 181<br>181                      |

| 8.1<br>8.2                             | Introduction                            | 181<br>181<br>181<br>184        |

| 8.1<br>8.2<br>8.3                      | IntroductionSummary of the dissertation | 181<br>181<br>181<br>184<br>185 |

| 8.1<br>8.2<br>8.3<br>8.4               | Introduction                            |                                 |

| 8.1<br>8.2<br>8.3<br>8.4<br>8.5<br>8.6 | Introduction                            |                                 |

# **List of Tables**

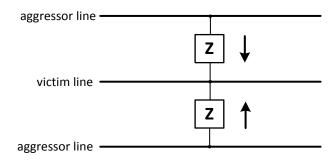

| Table 2.1: Effects of aggressor signals [22]                                                                                                | 15  |

|---------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 2.2: Test set for DUT                                                                                                                 | 17  |

| Table 2.3: Full response list fault dictionary                                                                                              | 17  |

| Table 2.4: Pass/fail two dimensional fault dictionary                                                                                       | 18  |

| Table 2.5: Comparison of different test techniques                                                                                          | 29  |

| Table 2.6: General purpose soft-core processors                                                                                             | 34  |

| Table 2.7: Test processors                                                                                                                  | 39  |

| Table 3.1: Properties of boundary scan, ad-hoc and generic FPGA test instruments                                                            | 50  |

| Table 3.2: Properties of the ROBSY approach                                                                                                 | 51  |

| Table 3.3: DUTs directly connected to FPGA                                                                                                  | 64  |

| Table 4.1: Walking one/zero, modified counting, and interleaved true/complement                                                             |     |

| sequences                                                                                                                                   | 84  |

| Table 4.2: Maximum aggressor fault sequences for glitches and delays                                                                        | 84  |

| Table 5.1: ROBSY processor instructions                                                                                                     | 100 |

| Table 5.2: Branching instructions                                                                                                           | 101 |

| Table 5.3: Procedure call instructions                                                                                                      | 101 |

| Table 5.4: STOP and NOP instructions                                                                                                        | 102 |

| Table 5.5: LOAD and STORE instructions                                                                                                      | 102 |

| Table 5.6: PUSH and POP instructions                                                                                                        | 102 |

| Table 5.7: ADD and SUB instructions                                                                                                         | 103 |

| Table 5.8: Logic instructions                                                                                                               | 104 |

| Table 5.9: Shift and rotate instructions                                                                                                    | 104 |

| Table 5.10: Test instructions                                                                                                               | 104 |

| Table 5.11: Sequence of patterns 8-bit LFSR with 0xB8 feedback polynomial                                                                   | 105 |

| Table 5.12: Exception codes                                                                                                                 | 108 |

| Table 5.13: Debug commands                                                                                                                  | 116 |

| Table 5.14: Configuration parameters                                                                                                        | 121 |

| Table 6.1: Reorganization of processor and debug-interface configuration parameters                                                         | 133 |

| Table 7.1: 112 possible processor variants                                                                                                  | 144 |

| Table 7.2: SRAM DUT-M (fault diagnosis) properties                                                                                          | 147 |

| Table 7.3: LCD DUT-M (LCD test) properties                                                                                                  | 148 |

| Table 7.4: SRAM DUT. Dependent configuration parameters (L4-L2)                                                                             | 150 |

| Table 7.5: LCD DUT. Dependent configuration parameters (L4-L2)                                                                              | 150 |

| Table 7.6: M9K blocks for stack, data, and program memories I <sub>16.0</sub> -I <sub>16.1</sub> /I <sub>16.8</sub> -I <sub>16.9</sub> (L4- | L2) |

|                                                                                                                                             | 153 |

XIV List of Tables

| Table 7.7: M9K blocks for stack, data, and program memories $I_{8.0}$ - $I_{8.1}/I_{8.8}$ - $I_{8.9}$ (L4-L2) | 154 |

|---------------------------------------------------------------------------------------------------------------|-----|

| Table 7.8: Dependent configuration parameters for all processor variants (L3)                                 | 156 |

| Table 7.9: Test time of ROBSY test system. SRAM DUT                                                           | 167 |

| Table 7.10: Test time of ROBSY test system. LCD DUT                                                           | 167 |

| Table 7.11: Properties of the Nios II cores.                                                                  | 168 |

| Table 7.12: ROBSY vs Nios II test time. SRAM DUT (L4-L2)                                                      | 171 |

| Table 7.13: ROBSY vs VLSR test time. SRAM DUT-M (all layer partitions)                                        | 172 |

| Table 7.14: ROBSY vs. VLSR test time. LCD DUT-M (all layer partitions)                                        | 173 |

# **List of Figures**

| Figure 1.1: Structure of the dissertation                                          | 4   |

|------------------------------------------------------------------------------------|-----|

| Figure 2.1: Development flow of an electronic system                               | 7   |

| Figure 2.2: Stuck-at-0 AND gate with truth table [17]                              | 11  |

| Figure 2.3: Wired AND/OR and dominant bridging fault models with truth table [17]  | 12  |

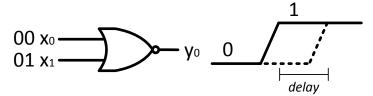

| Figure 2.4: Example of a delay fault [13]                                          | 13  |

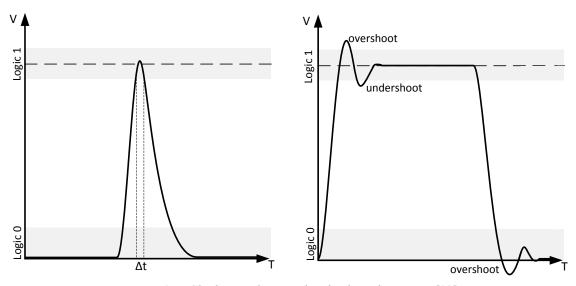

| Figure 2.5: Glitch, overshoot, and undershoot distortions [22]                     | 14  |

| Figure 2.6: Maximum aggressor fault model                                          | 15  |

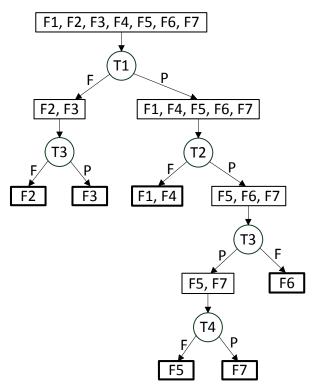

| Figure 2.7: Diagnostic tree [13]                                                   | 17  |

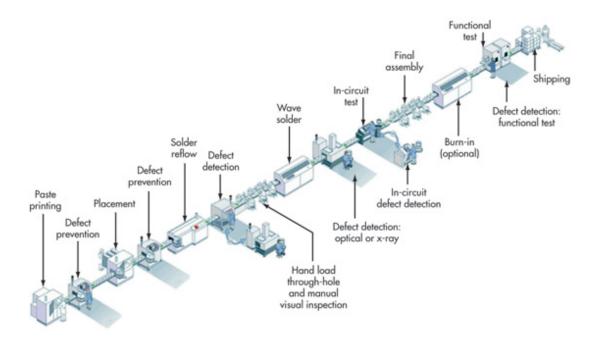

| Figure 2.8: Example of an assembly line [31]                                       | 20  |

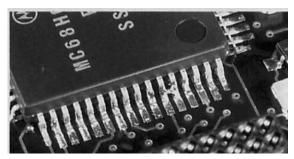

| Figure 2.9: Short defect [29] and crack in ball grid array solder joint [34]       | 22  |

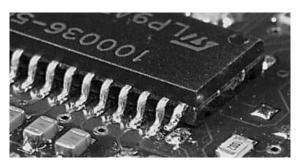

| Figure 2.10: Lifted lead and insufficient solder defects [29]                      | 22  |

| Figure 2.11: Misaligned and tombstone component defects [29]                       | 22  |

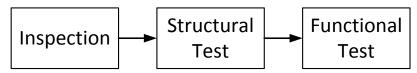

| Figure 2.12: General test strategy during PCB assembly                             | 23  |

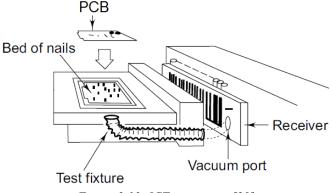

| Figure 2.13: ICT equipment [29]                                                    | 25  |

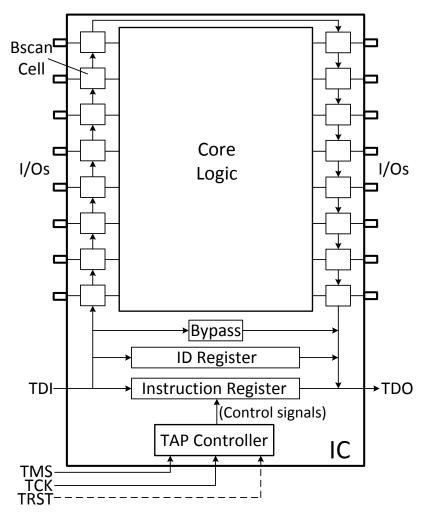

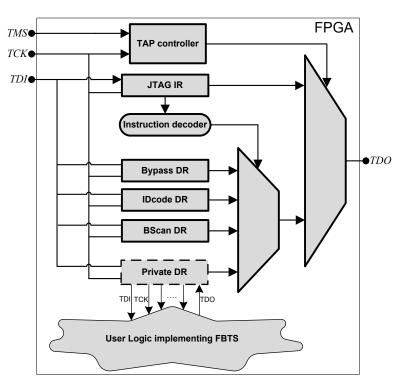

| Figure 2.14: Simplified architecture of an 11.49.1 compliant IC [37]               | 26  |

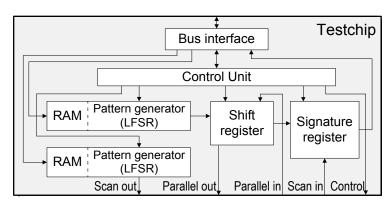

| Figure 2.15: Testchip architecture [76]                                            | 35  |

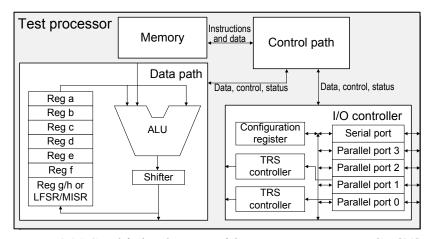

| Figure 2.16: Simplified architecture of the test processor presented in [81]       | 37  |

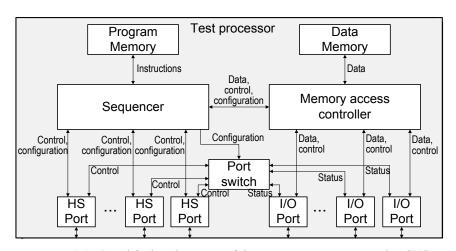

| Figure 2.17 Simplified architecture of the test processor presented in [89]        | 38  |

| Figure 3.1: FBT building blocks                                                    | 41  |

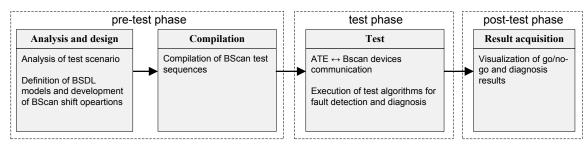

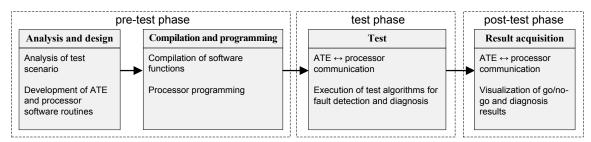

| Figure 3.2: FBT test phases                                                        | 43  |

| Figure 3.3: BScan test phases                                                      | 45  |

| Figure 3.4: PBT test phases                                                        | 45  |

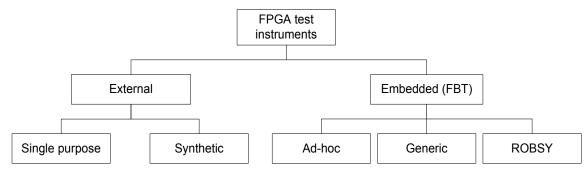

| Figure 3.5: FPGA test instruments classification                                   | 47  |

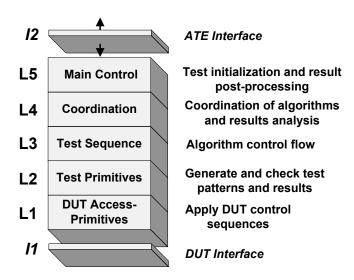

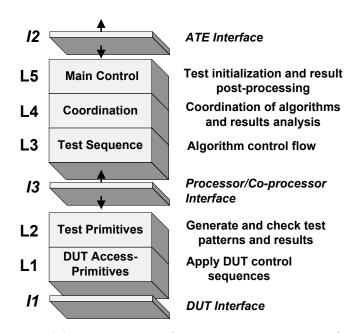

| Figure 3.6: Organization of the layers and interfaces                              | 52  |

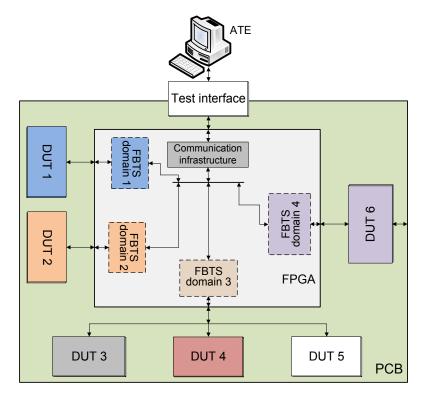

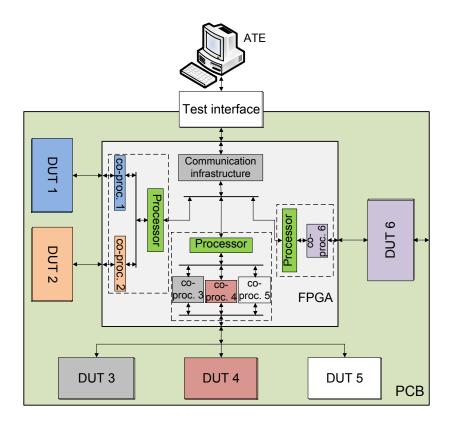

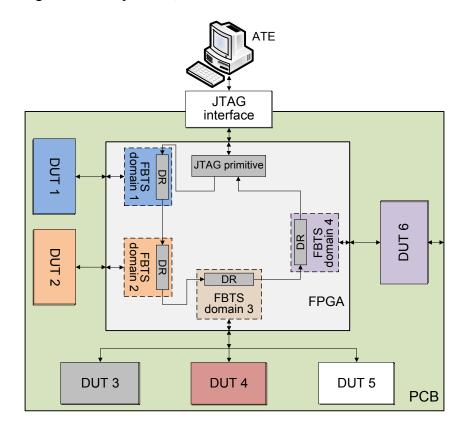

| Figure 3.7: FBTS domains                                                           | 55  |

| Figure 3.8: Layer concept with processor co-processor interface                    | 56  |

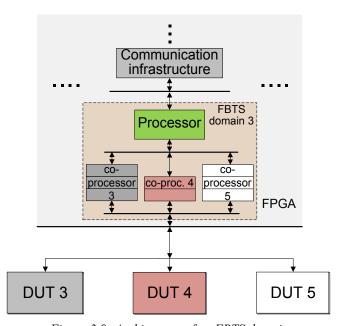

| Figure 3.9: Architecture of an FBTS domain                                         | 57  |

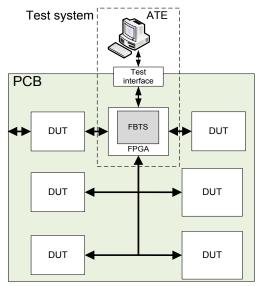

| Figure 3.10: Complete FBTS architecture                                            | 58  |

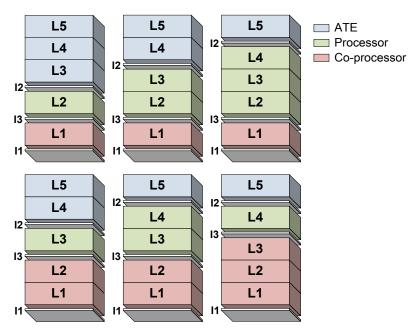

| Figure 3.11 ROBSY layer partitions                                                 | 69  |

| Figure 4.1 FBTS domains with DRs used for communication with ATE                   | 89  |

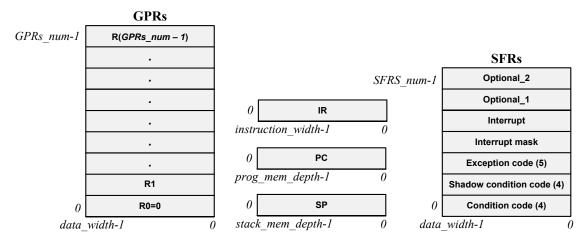

| Figure 5.1: ROBSY processor registers                                              | 98  |

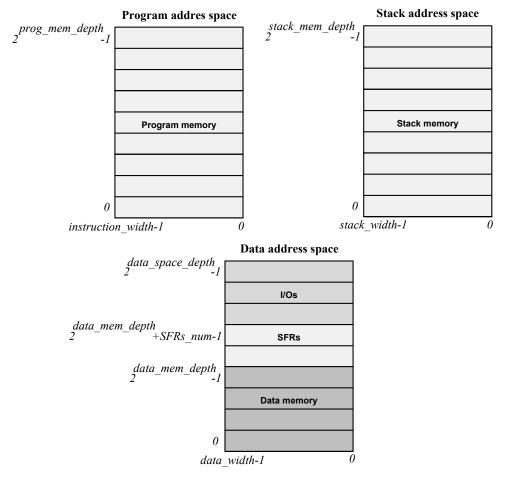

| Figure 5.2: ROBSY processor address spaces.                                        | 99  |

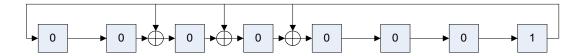

| Figure 5.3: 8-bit LFSR with 0xB8 feedback polynomial                               | 105 |

| Figure 5.4: Code for LFSR with 0x800B35 feedback polynomial and 8-bit data_width . | 105 |

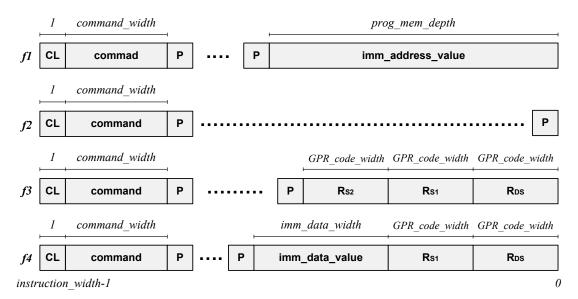

| Figure 5.5: Instruction formats                                                    | 107 |

XVI List of Figures

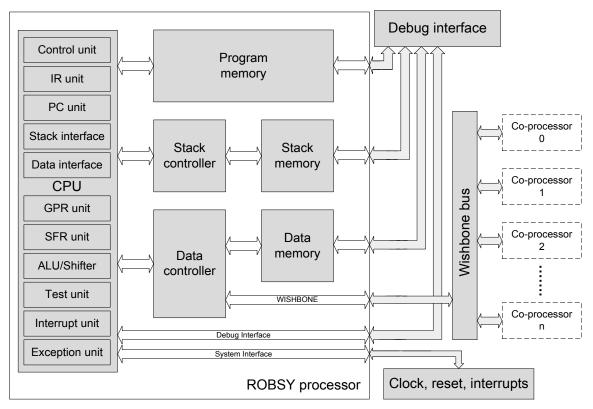

| Figure 5.6: ROBSY processor top level view                                                                   | 109 |

|--------------------------------------------------------------------------------------------------------------|-----|

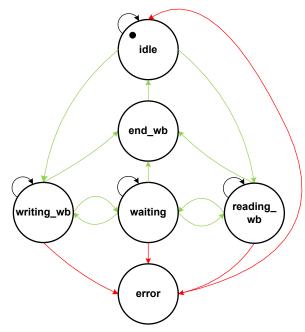

| Figure 5.7: Data controller finite state machine                                                             | 111 |

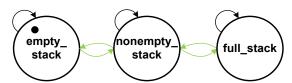

| Figure 5.8: Stack controller finite state machine.                                                           | 111 |

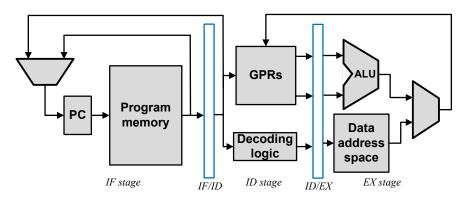

| Figure 5.9: Three-stage pipelined processor                                                                  | 112 |

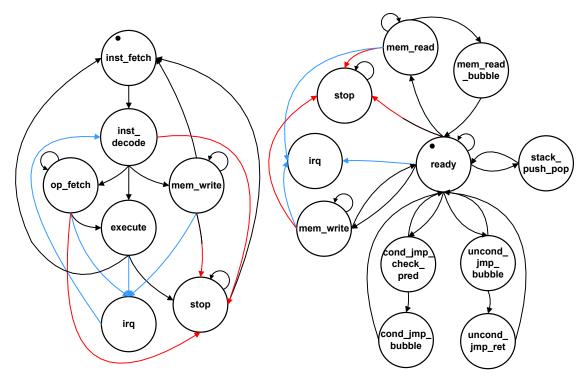

| Figure 5.10: FSM of multicycle (left) and pipeline (right) processor                                         | 113 |

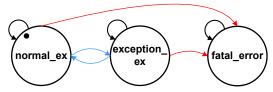

| Figure 5.11: FSM of exception module                                                                         | 115 |

| Figure 5.12: JTAG components and interconnections in an FPGA device                                          | 117 |

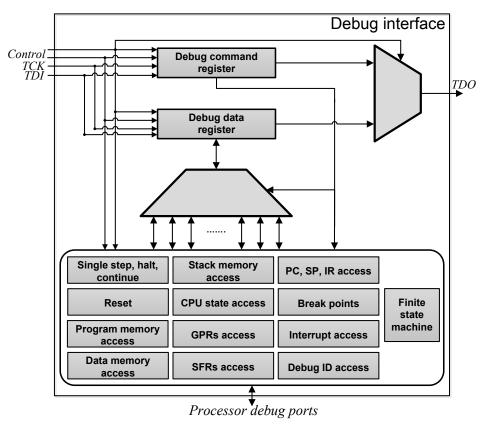

| Figure 5.13: Block diagram of the debug-interface                                                            | 118 |

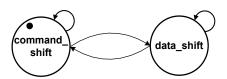

| Figure 5.14: Switching state machine                                                                         | 119 |

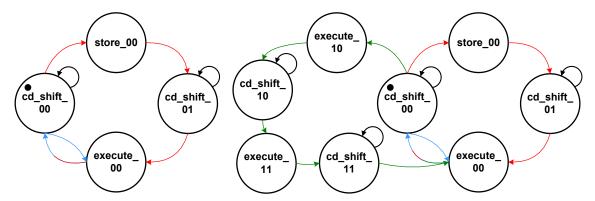

| Figure 5.15: FSM of debug-interface for multicycle (left) and pipeline(right) processor                      | 120 |

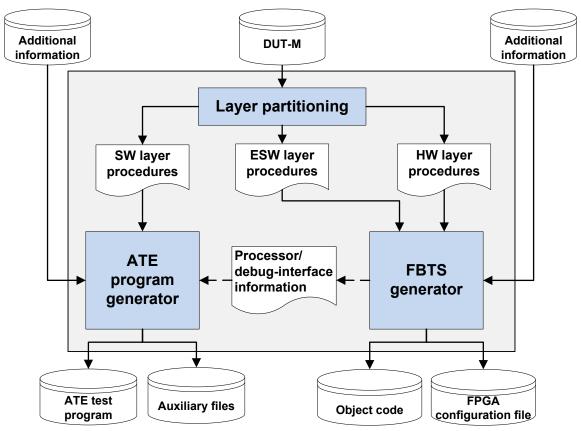

| Figure 6.1: Overview of automatic generation process for a single DUT-Model                                  | 126 |

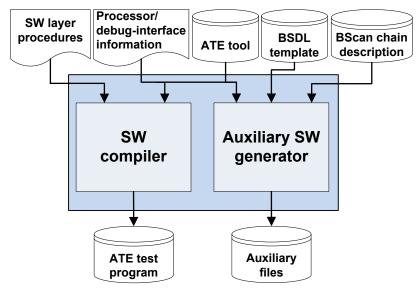

| Figure 6.2: ATE program generator                                                                            | 127 |

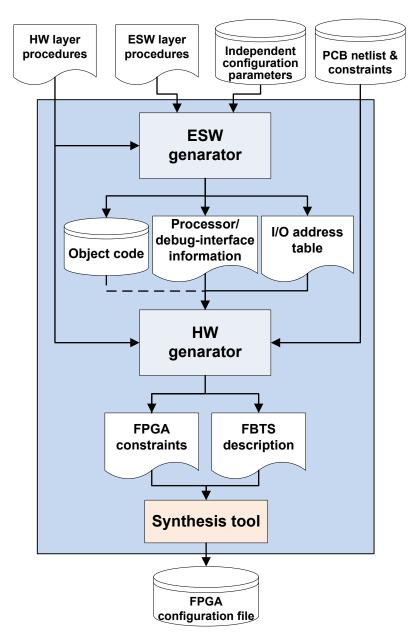

| Figure 6.3: FBTS generator                                                                                   | 131 |

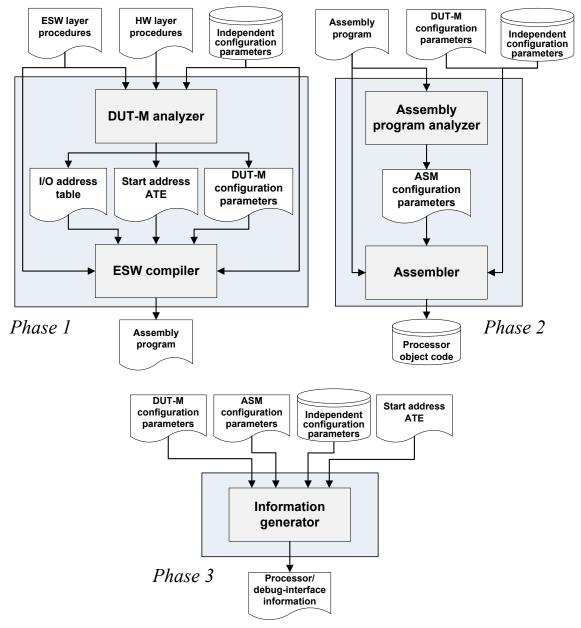

| Figure 6.4: Embedded software generator. Phase 1 (top left), 2 (top right), 3 (bottom)                       | 136 |

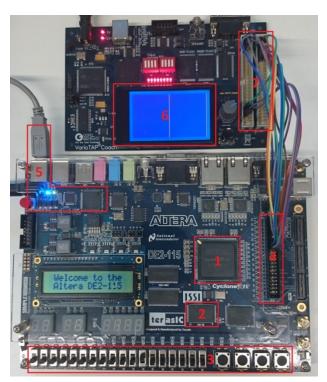

| Figure 7.1: Hardware setup (no ATE). VarioTap coach (top) and DE2-115 (bottom)                               | 142 |

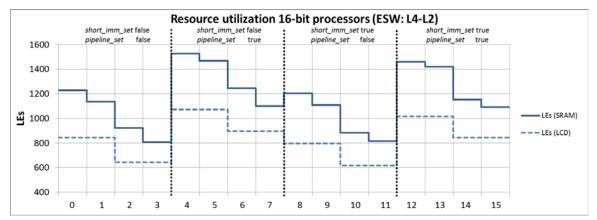

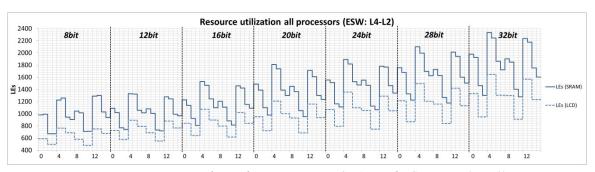

| Figure 7.2: Processor logic elements I <sub>16.0</sub> -I <sub>16.15</sub> . SRAM and LCD DUTs (L4-L2)       | 152 |

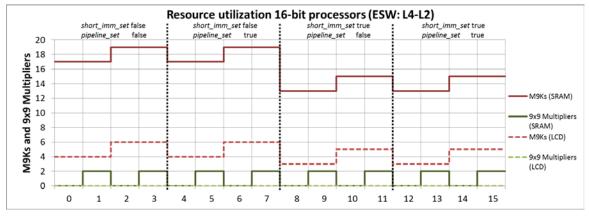

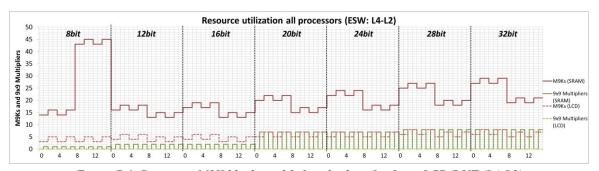

| Figure 7.3: Processor M9K blocks and 9x9 multipliers I <sub>16.0</sub> -I <sub>16.15</sub> . SRAM and LCD DU | Γs  |

| (L4-L2)                                                                                                      | 152 |

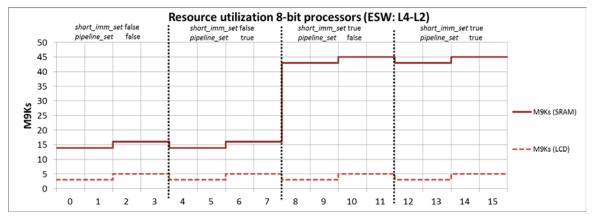

| Figure 7.4: Processor M9K blocks I <sub>8.0</sub> -I <sub>8.15</sub> . SRAM and LCD DUTs (L4-L2)             | 154 |

| Figure 7.5: Processor logic elements I <sub>8.0</sub> -I <sub>32.15</sub> . SRAM and LCD DUTs (L4-L2)        | 155 |

| Figure 7.6: Processor M9K blocks and 9x9 multipliers I <sub>8.0</sub> -I <sub>32.15</sub> . LCD DUT (L4-L2)  | 155 |

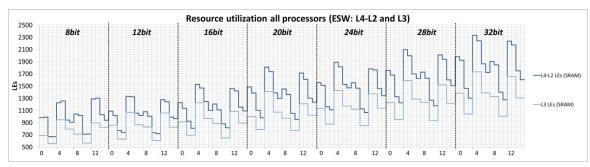

| Figure 7.7: Processors logic elements I <sub>8.0</sub> -I <sub>32.15</sub> . SRAM DUT (L4-L2 and L3)         | 157 |

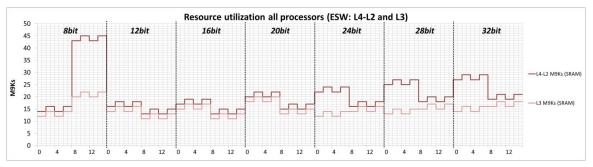

| Figure 7.8: Processors M9K blocks I <sub>8.0</sub> -I <sub>32.15</sub> . SRAM DUT (L4-L2 and L3)             | 157 |

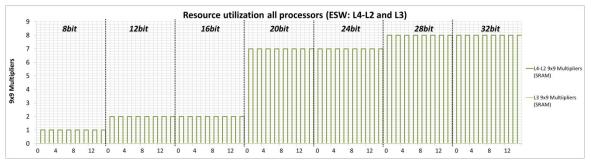

| Figure 7.9: Processors 9x9 Multipliers I <sub>8.0</sub> -I <sub>32.15</sub> . SRAM DUT (L4-L2 and L3)        | 157 |

| Figure 7.10: FBTS logic elements (average). SRAM and LCD DUTs (all layer partition                           | ıs) |

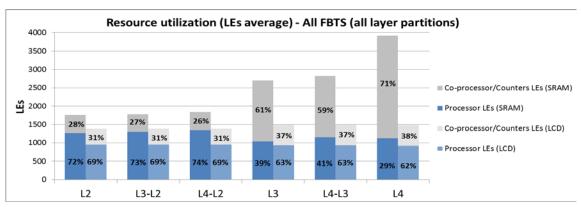

|                                                                                                              | 158 |

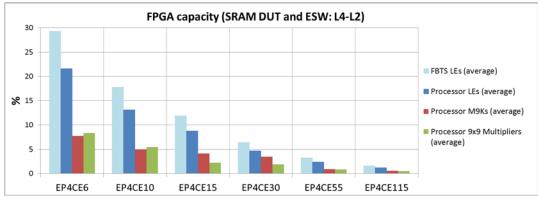

| Figure 7.11: FPGA capacity. SRAM DUT (L4-L2)                                                                 | 159 |

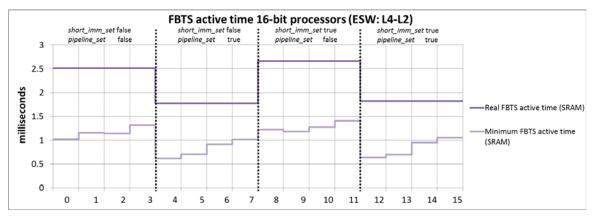

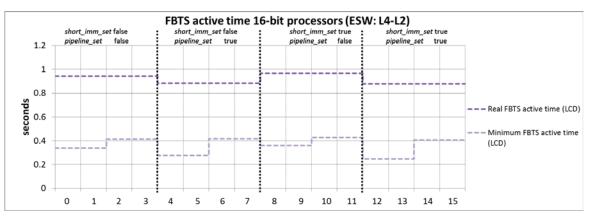

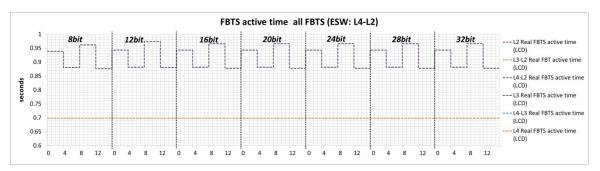

| Figure 7.12: FBTS active time I <sub>16.0</sub> -I <sub>16.15</sub> . SRAM DUT (L4-L2)                       | 160 |

| Figure 7.13: FBTS active time I <sub>16.0</sub> -I <sub>16.15</sub> . LCD DUT (L4-L2)                        | 161 |

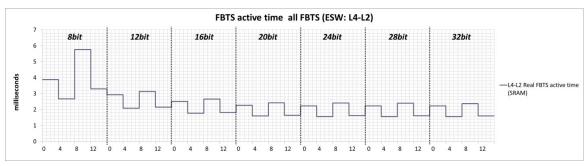

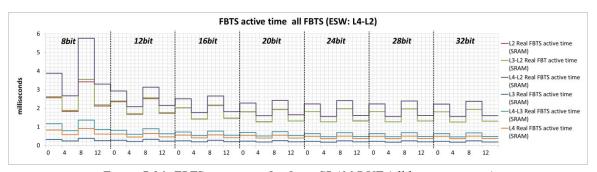

| Figure 7.14: FBTS active time I <sub>8.0</sub> -I <sub>32.15</sub> . SRAM DUT (L4-L2)                        | 162 |

| Figure 7.15: FBTS active time I <sub>8.0</sub> -I <sub>32.15</sub> . LCD DUT (L4-L2)                         | 162 |

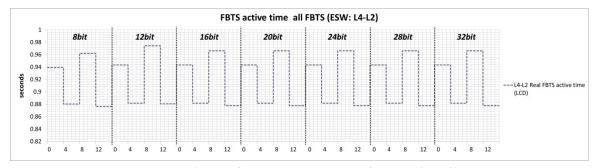

| Figure 7.16: FBTS active time I <sub>8.0</sub> -I <sub>32.15</sub> . SRAM DUT (all layer partitions)         | 163 |

| Figure 7.17: FBTS active time I <sub>8.0</sub> -I <sub>32.15</sub> . LCD DUT (all layer partitions)          | 164 |

| Figure 7.18: Nios II vs ROBSY logic elements. SRAM DUT (L4-L2)                                               | 170 |

| Figure 7.19: Nios II vs ROBSY M9Ks and 9x9 multipliers. SRAM DUT (L4-L2)                                     | 170 |

| Figure 7.20: Nios II vs ROBSY FBTS active time. SRAM DUT (L4-L2)                                             | 171 |

| Figure 7.21: VLSR vs ROBSY logic elements. SRAM DUT (L4-L2)                                                  | 172 |

# **Acronyms**

ACK Acknowledge

ALU Arithmetic logic unit

AOI Automated optical inspection

ATE External automatic test equipment

AXI Automated X-ray inspection

ASIC Application-specific IC

BGA Ball grid array

BIDIR Bidirectional

BILBO Built-in logic block observer

BIST Built-in self-test

BScan Boundary scan

CISC Complex instruction set computer

CPI Clock cycles per instruction

CPU Central processing unit

CS Chip select

DI Device interface

DDR Double data rate

DR Data register

DRAM Dynamic RAM

DUT Device under test

DUT-M DUT-model

DT Data transfer

EDA Electronic design automation

ESW Embedded software FBT FPGA-based testing

FBTS FPGA-based test system

FPGA Field programmable gate array

FPT Flying probe test

FSM Finite state machine

GPR General purpose register

HDL Hardware Description Language

HW Hardware I Index

I1 - I3 Interface 1 – Interface 3

I/O Input/output IC Integrated circuit

XVIII Acronyms

ICT In-circuit test

ILP Instruction level parallelism

IP Intellectual property

IPC Instructions per clock cycle

IR Instruction register

ISA Instruction set architecture

JTAG Joint test action group

L1 - L5 Layer 1 - Layer 5

LCD Liquid crystal display

LE Logic element

LFSR Linear feedback shift register

LSB Low significant bit LUT Look-up table

MISR Multiple input signature register

MSB Most significant bit

PBT Processor based testing

PC Program counter

PCB Printed circuit board

RAM Random access memory

RISC Reduced instruction set computer

ROBSY Reconfigurable on-board test system

RTL Register-transfer level

SDR Single data rate

SFR Special function register

SMT Surface mount technology

SoC System on chip

SP Stack pointer

SRAM Static RAM

SW Software

TAP Test access port

TCK Test clock

TDI Test data in

TDO Test data out

THT Through-hole technology

TMS Test mode select

TRST Test reset

VLIW Very large instruction word VLSR Variable length shift register

VHDL VHSIC HDL

VHSIC Very-high-speed integrated circuit

# 1 Introduction

### 1.1 Motivation

The world is more and more dependent on electronic systems. Today, they are a fundamental tool in medicine, healthcare, communication, automotive, navigation, space exploration, agriculture, etc. In all these fields, the demand for electronic systems with more features, higher performance, and less power consumption increases continuously. This is a real challenge for design and test engineers because they have to deal with electronic systems with ever-increasing complexity maintaining production and test costs low and meeting critical time to market deadlines.

For a test engineer, this means that manufacturing defects must be detected as soon as possible. Therefore, the manufacturing stage of every electronic system is escorted by several test phases hierarchically organized for early defect detection and diagnose. To fulfill this purpose, several test techniques have been developed and successfully used. But these techniques are not able to cope with test requirements of modern electronic systems, and in the worst case, they cannot be used at all.

At the board-level, this is mainly due to modern packaging technologies, a high device density, and the high operation frequencies of modern printed circuit boards. One example of this phenomenon is boundary scan (BScan) [1], which is a popular test technique developed thirty years ago and since then successfully used. Unfortunately, it is reaching its limits due to the properties of modern printed circuit boards. Basically, it is inadequate to handle defects with dynamic behavior because it cannot execute tests at the normal operation frequencies (at-speed test) of devices located at the board. Additionally, the high number of devices and pins per device results in very long test times and high test costs. Therefore, there is a growing interest in the research community and industry to investigate and develop new board-level test techniques that improve test quality metrics and reduce costs.

New developed test techniques and test standards tend to embed more of the test functions in the electronic system, whether the electronic system represents a printed circuit board (PCB) or a system entirely implemented in silicon such as a system on chip (SoC). In this way, access to internal structures and functions of the electronic system is enhanced, improving the observability, controllability, and test quality in a cost effective way.

2 1 Introduction

Two emerging embedded test techniques at the board-level have gained considerable importance. The first one corresponds to processor-based testing (PBT), where processors or microcontrollers located on the board are used to execute part of the test functions. The second technique is known as FPGA-based testing (FBT). Instead of processors or microcontrollers, this technique uses field programmable gate arrays (FPGAs) to implement part of the test functions. Both techniques are very attractive because they do not require the modification or addition of new components to the board, and allow the detection of defects with a dynamic behavior.

In the case of PBT, the difficulty lies in the development of mechanisms for the automatic generation of descriptions necessary to access different processors or microcontrollers from the external automatic test equipment (ATE). The access should be guaranteed independently if the processor or microcontroller is implemented as a stand-alone integrated circuit or as part of a SoC. In the case of FBT, the complexity lies in the development of the test system implemented in the FPGA, which is known as the FBT system (FBTS). For the development of such a system, it is necessary to provide an answer to the following questions:

- What is the structure of the FBTS?

- Which components are used for its implementation?

- How should the FBTS communicate with the ATE?

- Which mechanisms can be used to facilitate the work of test engineers?

In this dissertation the research is linked to the development and implementation of a configurable test processor as part of an FBT approach.

# 1.2 Problem statement and research questions

This dissertation targets the study and development of a configurable test processor as part of a new FBT approach. The FBT approach should be able to execute tests at-speed and in short time, adapt to the PCB and test requirements, and hide implementation details from test engineers in order to facilitate its utilization. The goal is to provide a better understanding of whether the use of a test processor as part of an FPGA-based testing approach is a good alternative to tackle test challenges imposed by modern PCBs, so that classical test techniques such as boundary scan can be complemented.

Although there are some FBT approaches found in the literature (Section 3.2), none of them makes use of a test processor or is able to provide all the advantages that the FBT

1 Introduction 3

approach proposed in this dissertation provides. Based on these considerations, the central research questions are defined as follows:

- Is it possible to design a resource and computational efficient FBT approach and obtain the advantages already mentioned based on a test processor?

- What are the architecture characteristics of an FBTS that use a test processor as central component?

- Which adaptation and abstraction mechanisms should be included in order to customize the FBTS to the test scenario and hide implementation details?

- Which instruction set architecture and microarchitecture features should be included in the test processor?

- What are the test functions that the test processor can efficiently execute in terms of resource utilization and execution time?

- Is it possible to use this approach in real manufacturing scenarios?

- Are the results concerning test quality metrics better in comparison to other FBT approaches?

- What are the limitations?

Literature research shows that these questions have not been answered in the related work so far, which ultimately motivates the development of this dissertation.

### 1.3 Publications related to this work

In the context of this work several papers have been published on national and international conferences. In [2, 3] the general concept of the FBT approach and targeted test processor is presented. The provided solution describes the layer concept and a first proposal for the FBTS architecture and automatic generation process. In [4] the concept is further developed and emphasis is given to the automatic generation of the complete test system. In [5] the main subject is the test processor and the use of configuration options at the instruction set architecture and microarchitecture level as a mechanism for the processor adaptation to the PCB and test requirements. In [6] the processor is used as part of a novel verification approach of register transfer level (RTL) designs. Finally, [7] presents results of the approach with focus on the test processor.

The publications cover basic aspects of the FBT approach proposed as part of this dissertation. This dissertation provides an extension of the work and a more detailed analysis of the FBTS, test processor, and automatic generation process. These aspects are extended with further improvements of the concept.

4 1 Introduction

# 1.4 Structure of the dissertation and contributions

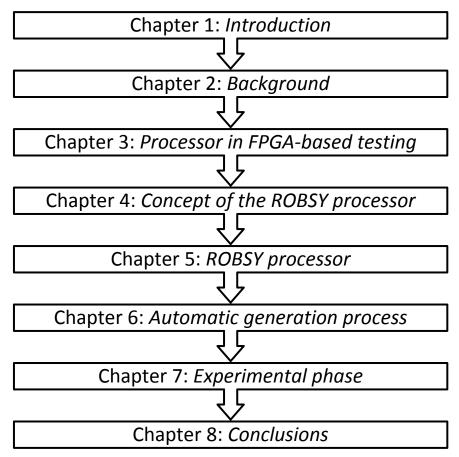

The structure of the dissertation is divided into eight chapters, as indicated in Figure 1.1.

Figure 1.1: Structure of the dissertation

Chapter 2 provides the theoretical basis of the dissertation. It presents an overview on testing, testing of printed circuit boards, and test techniques. Additionally, it provides information about the state of the art of soft-core processors and test processors.

Chapter 3 begins with a discussion about FPGA-based testing and the state of the art of FPGA-based testing approaches. The approaches are reviewed and classified under the aspects of external/embedded test instrumentation, application speed, test time, and design methodology. Based on the literature review, the FPGA-based testing approach proposed in this dissertation is presented. At the end of Chapter 3, an analysis of the use of a processor in FPGA-based testing is performed.

Chapter 4 presents the concept of the ROBSY (Reconfigurable On-Board test System) processor based on the analysis performed in Chapter 3. This chapter discusses the processor general design aspects, specialization for testing, and adaptation mechanisms to the PCB and test requirements.

1 Introduction 5

Chapter 5 presents the implementation details of the ROBSY processor. It shows its instruction set architecture, microarchitecture, and debug-interface. Additionally, Chapter 5 presents the configuration parameters supported by the processor.

Chapter 6 provides an overview of the automatic generation process for an FBTS composed of a processor/co-processor pair. The automatic generation process includes the generation of software for the ATE, embedded software for the ROBSY processor, and hardware descriptions that represent the co-processor. Furthermore, the automatic generation process is in charge of adapting the processor by defining the value of the configuration parameters known as dependent configuration parameters.

Chapter 7 presents the experimental results obtained with the proposed FBT approach. The chapter analyzes the implementation of test functions on the ATE and FPGA, as well as the effect of the processor configuration parameters known as the dependent and independent configuration parameters. It analyzes the resource utilization of the FPGA, the time that the FBTS is active during the whole test execution, and the total test time. At the end of the chapter the results obtained with the ROBSY test system are compared against the results obtained with a generic test instrument and with FBTS variants implemented based on the Nios II cores. The results show the advantages of the ROBSY approach and the ROBSY processor.

Finally, Chapter 8 summarizes the dissertation and provides an outlook on further research opportunities.

# 2 Background

# 2.1 Testing, what is it?

### 2.1.1 Introduction

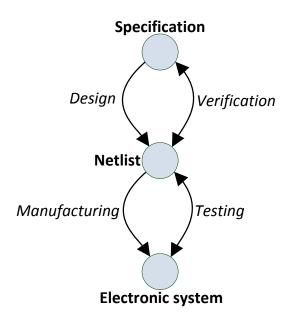

In order to provide a proper definition for the word testing, it is necessary to take a look at the general development flow of an electronic system presented in Figure 2.1. In the figure, the specification of the electronic system represents the starting point of the development flow, in which the requirements of the electronic system, as seen from its environment, are defined. This comprises the definition of the product's overall functionality, interfaces to the environment, performance requirements, etc. [8, 9].

Figure 2.1: Development flow of an electronic system

Based on the specification, the internal structure of the system is defined during the design stage. In this stage several solutions can be explored, based on different technologies, architectures, hardware/software partitions, and so on [10]. The outcome of the design stage is documented in a structural description or netlist of the physical objects and their interconnections. Depending on the level of abstraction, these objects are transistors, gates, integrated circuits (ICs), or even multiple printed circuit boards (PCBs).

The second stage is the fabrication of the electronic system, which is known as the manufacturing stage. Depending on the level of abstraction, the manufacturing stage

8 2 Background

might deal with the fabrication of ICs based on silicon wafers or the fabrication of PCBs, which involves the assembly of ICs in an insulated base with firmly attached conductors.

It is possible that the resulting electronic system behaves in an undesired way due to errors introduced during its development, or errors appearing during electronic system operation. In the first case, these errors were introduced during the elaboration of the specification, design or manufacturing stage. In the second case, these errors appear in the field.

In order to avoid or minimize the probability of incorrect behavior and detect possible causes as soon as possible, additional stages are included in the development flow, which are known as validation, verification, and testing [9].

### 2.1.2 Errors and defects

An error is essentially the observed effect of an incorrect behavior, which may be caused by diverse factors such as specification-errors, design-errors, fabrication-errors, fabrication-defects, or physical-failures [9, 11].

- Specification-errors occur due to an ambiguous or incomplete specification. In many cases, they are caused by an operation scenario not properly described in the specification, or even worse, an operation scenario not described at all [9].

- Design-errors are produced during the design of the electronic system. They are originated by an incorrect interpretation of the specification, violations of design rules, usage of defective design tools, etc. [9].

- Fabrication-errors and fabrication-defects appear during the manufacturing process. The former are directly attributable to a human act, such as the use of wrong devices, incorrect wiring, improper soldering, etc., while the latter are not directly attributable to a human act because they result from an imperfect manufacturing process [11].

- Physical-failures occur during the operation of the electronic system, and are caused due to wear out, aging, and environmental factors affecting the electronic system [11].

Fabrication-errors, fabrication-defects and physical-failures are collectively referred to in the literature as physical faults [11], manufacturing faults [9], or defects [12, 13]. They can be found anywhere: in a die, in one or multiple layers, in packages, in PCBs, etc. Additionally, they can be presented in arbitrary areas and can have different electrical properties, which means that they manifest themselves in different ways such as changing 2 Background 9

a logical value on a node, increasing the steady state supply current, changing timing properties, or causing discrepancy in other parameters.

In this dissertation, the term *defect* is adopted to refer to fabrication-errors, fabrication-defects, and physical-failures, and the term *error* is the observed incorrect behavior produced by a defect.

# 2.1.3 Validation, verification, and testing

There are different ways to look for errors and defects, depending on the electronic system development stage.

Validation is carried out to detect and minimize specification-errors. During the validation process, the specification is analyzed to determine if it describes the desired behavior and whether it is complete, unambiguous, and consistent [9].

As seen in Figure 2.1, verification is performed during the design stage. The goal is to continually prove if the structural model resulting from the design stage fulfills all the functional and nonfunctional requirements provided in the specification [9, 14]. There are different ways to perform verification, either using formal verification methods (model and equivalence checking) or functional verification.

In contrast, testing is the process responsible for detecting all defects (fabrication-errors, fabrication-defects, and physical-failures) introduced during the manufacturing process or operation of an electronic system [11, 12]. In this context, testing is an experiment in which the system is exercised and the resulting response is analyzed to ascertain whether it behaved correctly. If incorrect behavior is detected, a second goal of testing may be to diagnose the defect causing the misbehavior. Testing requires the generation, application, acquisition, and analysis of test patterns, which are defined depending on required test quality metrics and allowed costs (Section 2.1.6).

### 2.1.4 Fault and fault models

Ideally, a test should detect all defects produced in the manufacturing stage and let only functionally good devices pass. Unfortunately, the number of potential defects that appear during the manufacturing stage can be very large, and their effect on properties and behavior of the electronic system can be very complex and difficult to understand.

Faults and fault models are used to address this problem.

10 2 Background

A fault is defined as a representation of the defect at an abstract function level [13], which means that it is a representation of the effect of a defect on the operation of the system. Consequently, a fault model is a mathematical or formal description of a fault. Fault models bridge the gap between the physical reality and mathematical abstracts, and they reduce test complexity, given that [11]:

- Many defects can be represented by the same fault model.

- Some fault models can be used for different technologies because they are technology independent.

- Tests derived from fault models may be used for defects whose effect in the circuit behavior is not completely understood or is too complex to be analyzed.

Unsurprisingly, there is a trade-off when working with fault models. The more simple and abstract the fault model is, the more difficult it is to associate the fault with a real defect, which makes defect location and diagnosis more difficult. Therefore, one alternative is to work at different abstraction levels, starting with the development of tests for fault models at high abstraction levels, and then develop tests targeted at low-level faults that were not covered by the high-level fault models [15]. Which fault model is best and which type of testing is necessary depends on technology and defect manifestation.

In the next sections, fault models relevant for this thesis are presented: stuck-at, bridging, and dynamic fault models.

### 2.1.4.1 Stuck-at faults

The stuck-at fault is considered a static fault model because the defects that it represents are manifested at all frequencies. It is the logic-level fault model most commonly used in research as well as industry, being an industrial standard since 1959. Its death has been predicted but several reasons and properties have made the stuck-at fault model to continue to be used for testing [13]:

- Simplicity: It is easy to apply to a device under test (DUT).

- Logical behavior: Fault behavior is determined logically, so simulation is straightforward and deterministic.

- Measurability: The defect represented by a stuck-at fault is easy to detect.

- Adaptability: It can be used on transistors, gates, registers, systems, etc.

Stuck-at faults are mapped to interconnections between devices. Under faulty conditions, the affected line is assumed to be stuck-at a logic level (0 or 1) and the value cannot be altered by input stimuli. According to the value of the affected line, the fault is called

2 Background 11

either stuck-at-0 or stuck-at-1. Usually, open lines or lines shorted to ground or power behave like stuck-at faults [16].

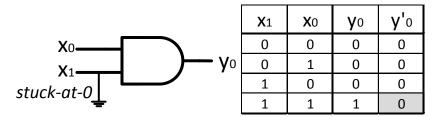

Figure 2.2 shows an example of a stuck-at-0 fault located at the input of an AND gate.

Figure 2.2: Stuck-at-0 AND gate with truth table [17]

In general, several stuck-at faults can be simultaneously present. A DUT with n lines can have  $3^n - 1$  possible stuck-at line combinations. This is because each line can be in one of the three states: stuck-at-1, stuck-at-0, or fault-free. Clearly, even a moderate value of n will generate an enormously large number of multiple stuck-at faults. However, it is a common practice to work with single stuck-at faults [11, 12, 17, 18]. In this case, an n-line DUT can have at most 2n single stuck-at faults.

### 2.1.4.2 Bridging faults

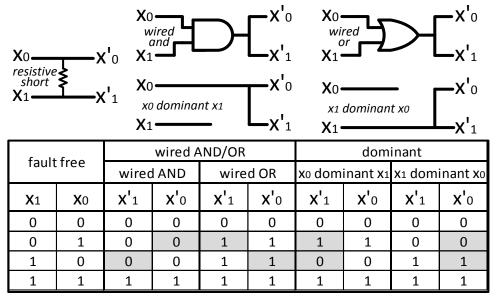

Same as the stuck-at fault model, a bridging fault is considered a static fault model because the defects that it represents are manifested at all frequencies. It is also a very common fault model and it is still one of the fault models most widely accepted in industry [16]. A bridging fault considers that two or more lines are unintentionally connected.

There are two bridging fault models that are frequently used in practice: the wired-AND/wired-OR bridging fault model and the dominant bridging fault model [17]. The wired-AND bridging fault is also known as 0-dominant bridging fault because a 0 on one of the faulty lines determines the logic value on both lines in the same way as a logic 0 at any input of an AND gate. Similarly, the wired-OR bridging fault is also known as 1-dominant bridging fault.

The dominant bridging fault model was developed to more accurately reflect the behavior of some shorts, in which the logic value at the destination end of the shorted lines is determined by the line with the strongest drive capability. As a consequence, the driver for one line "dominates" the driver for the other line. Figure 2.3 shows the four bridging fault models.

12 2 Background

Figure 2.3: Wired AND/OR and dominant bridging fault models with truth table [17]

In general, several bridging faults can be simultaneously present in the DUT. In this case, a DUT with n lines can have  $5^n - 1$  possible bridging fault combinations. However, in the same way as stuck-at faults, it is a common practice to work with single bridging faults [11, 12, 17, 18]. An n-line DUT can have at most 4n single bridging faults.

### 2.1.4.3 Dynamic faults

In contrast to stuck-at and bridging faults, dynamic faults represent defects that show up only at high frequencies. In order to detect this kind of fault, it is necessary to execute test at-speed, which means applying patterns at the operation frequency of the DUT [12]. Additionally, while stuck-at and bridging faults require the application of a single pattern for their detection, dynamic faults typically require the application of two patterns: the first one for value initialization and the second one for the activation of the fault. They can be separated into two main classes, known as delay faults and signal integrity faults.

### Delay faults

Delay fault models are associated to interconnection or component defects that cause the non-fulfillment of timing specifications. This means, defects that cause that a DUT whose operation is logically correct, to not perform at the required working frequency [13, 17]. In this case, an expected signal value is delayed and the actual measured output signal is therefore not correct within a pre-specified timing constraint. An example of this behavior is illustrated in Figure 2.4 using a NOR gate with a delay fault, whose output value changes from 0 to 1 after a larger time interval in comparison to the time interval defined in the timing specification.

2 Background 13

Figure 2.4: Example of a delay fault [13]

At the transistor level, defects modeled as delay faults can result from under- or overetching during the fabrication process, which produces transistors with channel widths that are much narrower or channel lengths that are much longer than intended, such that, some paths through the circuit may not meet performance specifications. Other causes are a drop in the power supply, shifts in the transistor threshold voltage, increment of parasitic capacitance, high resistance shorts, etc. [13].

At the gate level, delay faults are further categorized into specific delay fault models, such as gate-delay faults, transition-delay faults, path-delay faults, line-delay faults, and segment-delay faults [12, 13, 19, 20].

The gate-delay fault model is a quantitative model in which delays are represented by time intervals. Each gate has a pre-specified nominal delay, but a faulty gate is characterized by a considerably larger delay. Therefore, the gate delay fault is an added delay of certain magnitude in the propagation of a rising or falling transition from the gate inputs to the gate output. The number of gate-delay faults is twice the number of gates.

The transition-delay fault model is one of the basic delay fault models. Faults according to this model make slow signal changes on a line. There are two possible fault types, slow-to-rise and slow-to-fall. In this case, it is assumed that a defect on a line is large enough to affect any path that includes it. The total number of faults is twice the number of lines.