# Tilo Welker

Methoden und Technologien zur Optimierung der Entwärmung aktiver und passiver Komponenten auf keramischen Mehrlagensubstraten

# Methoden und Technologien zur Optimierung der Entwärmung aktiver und passiver Komponenten auf keramischen Mehrlagensubstraten

Tilo Welker

Universitätsverlag Ilmenau 2018

# **Impressum**

#### Bibliografische Information der Deutschen Nationalbibliothek

Die Deutsche Nationalbibliothek verzeichnet diese Publikation in der Deutschen Nationalbibliografie; detaillierte bibliografische Angaben sind im Internet über http://dnb.d-nb.de abrufbar.

Diese Arbeit hat der Fakultät für Elektrotechnik und Informationstechnik der Technischen Universität Ilmenau als Dissertation vorgelegen.

Tag der Einreichung: 19. Juni 2017

1. Gutachter: Prof. Dr.-Ing. Jens Müller

(Technische Universität Ilmenau)

2. Gutachter: Prof. Dr.-Ing. Christian Cierpka

(Technische Universität Ilmenau)

3. Gutachter: Prof. Dr.-Ing. Ralph Schacht

(Brandenburgische Technische Universität Cottbus-Senftenberg)

Tag der Verteidigung: 26. Februar 2018

Technische Universität Ilmenau/Universitätsbibliothek

# Universitätsverlag Ilmenau

Postfach 10 05 65 98684 Ilmenau

http://www.tu-ilmenau.de/universitaetsverlag

readbox unipress in der readbox publishing GmbH Am Hawerkamp 31 48155 Münster http://unipress.readbox.net

**ISBN** 978-3-86360-182-9 (Druckausgabe) **URN** urn:nbn:de:gbv:ilm1-2018000120

#### Vorwort

Die vorliegende Dissertation entstand während meiner Tätigkeit als wissenschaftlicher Mitarbeiter am Institut für Mikro- und Nanotechnologie (IMN) der Technischen Universität Ilmenau im Rahmen des vom BMWi geförderten Projektes iKersatec (Förderkennzeichen: 50YB1303). Ich danke allen Mitarbeitern des Instituts für die tolle Zusammenarbeit, die wissenschaftlichen Diskussionen, sowie die Unterstützung bei der Präparation und Durchführung von Experimenten. Den Projektpartnern des Projekts iKersatec gilt mein Dank für die konstruktiven Hinweise in den zahlreichen, fachlichen Diskussionen.

Besonders möchte ich mich bei folgenden Personen bedanken:

Herr Prof. Dr.-Ing. Jens Müller für die Betreuung und Begutachtung dieser Arbeit, insbesondere für die wertvollen Hinweise und Diskussionen. Die gewährten Freiheiten zum selbstständigen Arbeiten förderten die Entwicklung eigener Ideen, welche die vorliegende Arbeit erst ermöglichten. Die Unterstützung während der Erstellung der Arbeit, war für deren Gelingen unverzichtbar.

Herr Prof. Dr.-Ing. Christian Cierpka für das Interesse an dieser Arbeit, die konstruktiven Hinweise, sowie die Übernahme eines Gutachtens.

Herr Prof. Dr.-Ing. Ralph Schacht für das Interesse an dieser Arbeit und die Übernahme eines Gutachtens.

Herr Dr.-Ing. Karl-Heinz Drüe für die hilfreichen Hinweise, sowie die kritische Durchsicht des Manuskripts.

Herr Dipl.-Ing. (FH) Detlef Welker für die kritische Durchsicht des Manuskripts.

Herr Dipl.-Ing. Nam Gutzeit, Herr Dipl.-Ing. Michael Fischer, Herr Dipl.-Ing. (FH) Alexander Schulz, Frau Dr.-Ing. Heike Bartsch und Frau Dipl.-Ing. Sabine Oltmanns für die wertvollen wissenschaftlichen Diskussionen.

Frau Dipl.-Ing. (FH) Ina Koch und Herr Dipl.-Ing. Uwe Genatis für die unschätzbare Unterstützung bei der Substratfertigung.

Herr Alexander Schleicher für die gute Zusammenarbeit und Unterstützung bei der Bauteilmontage.

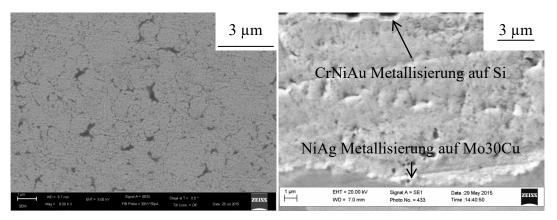

Frau Elvira Remdt und Frau Diana Roßberg für die ausgezeichnete Präparation von Querschliffproben und die Unterstützung bei REM Untersuchungen.

Herr Dipl.-Ing. (FH) Timmy Reimann für die Unterstützung bei der Materialcharakterisierung.

Herr M.Sc. Primin Rombach für die tolle Masterarbeit, auf deren Ergebnisse ich an gegebener Stelle verweise.

Frau Cathleen Kleinholz für die Unterstützung bei der Präparation und Durchführung der Scherfestigkeitsmessungen.

Insbesondere möchte ich meiner Familie und der Familie meiner Frau danken, die mich auf dem Weg zur Promotion aufgemuntert und motiviert haben. Ohne deren Unterstützung wäre diese Arbeit nicht möglich gewesen.

Schließlich möchte ich mich bei meiner Frau Kathleen und meinem Sohn Janick in ganz besondere Weise bedanken. Dem Anfertigen der Arbeit opferte ich einen großen Teil der gemeinsamen Zeit mit ihnen, was sie mit viel Geduld und Verständnis ertrugen. Danke Kathleen, danke Janick!

# Kurzfassung

Gegenstand dieser Arbeit ist der thermische Pfad in einem Mehrlagenmodul aus Niedertemperatur-Einbrand-Keramiken (engl.: low temperature co-fired ceramic, kurz: LTCC). Der thermische Pfad beschreibt dabei den Pfad der Wärme von einem verlustbehafteten Bauelement hin zu einer Wärmesenke. Ziel der Arbeit ist es durch neue Materialien, Technologien und Methoden den thermischen Pfad zu optimieren und so die thermische Performance des Mehrlagenmoduls zu verbessern. Der thermische Pfad kann in drei kritische Bereiche unterteilt werden.

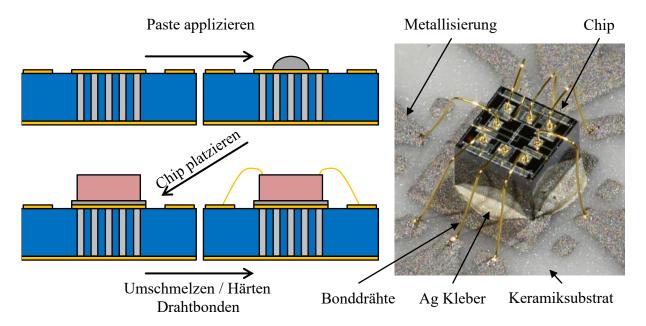

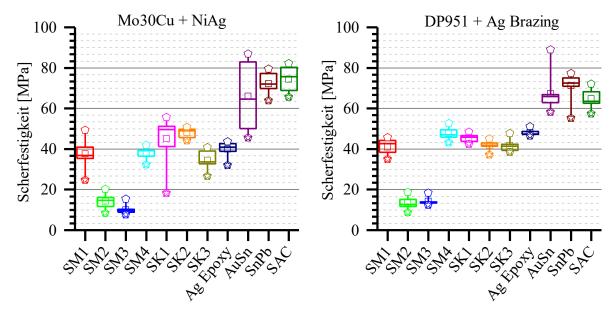

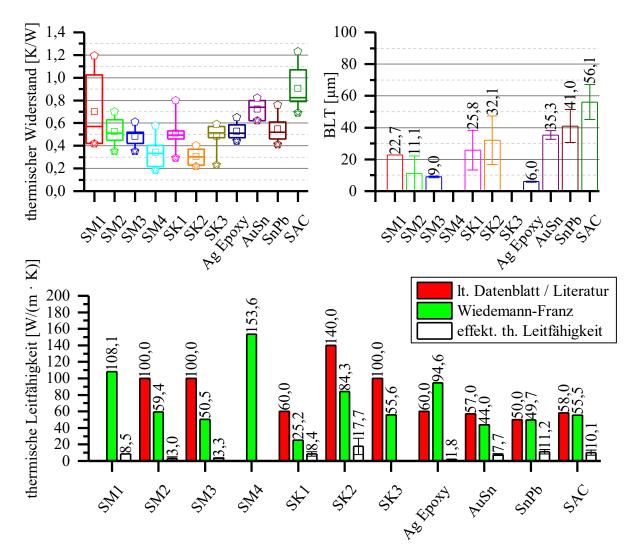

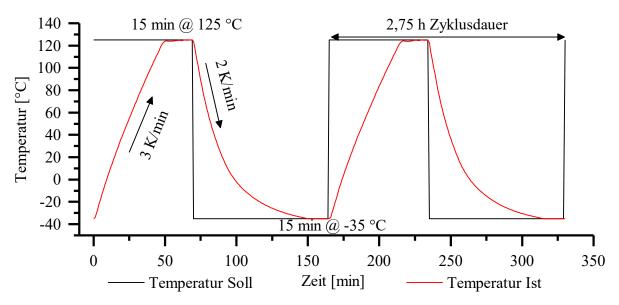

Der erste Bereich umfasst die Verbindung zwischen Chip und Substrat. Die hier eingesetzten Materialien stellen neben der mechanischen Fixierung auch den thermischen Kontakt zwischen Chip und Substrat her. Im Rahmen dieser Arbeit werden Silberpasten für die Chipmontage untersucht, die bei niedrigen Temperaturen sintern und eine thermisch hoch leitende Verbindung zwischen Chip und Substrat realisieren. Weiterhin werden reaktive Lote untersucht, die nach thermischer Aktivierung kurzzeitig einen starken thermischen Impuls generieren, wodurch das Fügen von Materialien mit unterschiedlichem thermischen Ausdehnungskoeffizient ermöglicht wird. Diese reaktiven Lote und die Silberpasten werden dabei mit den herkömmlichen Materialien der Chipmontage wie Loten und Klebern hinsichtlich ihres thermischen Widerstandes, der mechanischen Festigkeit und Zuverlässigkeit bewertet und verglichen.

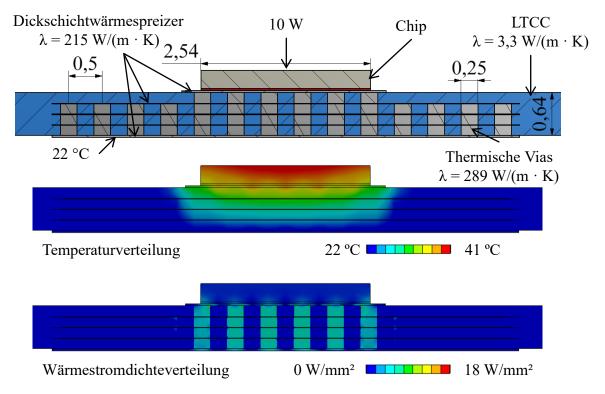

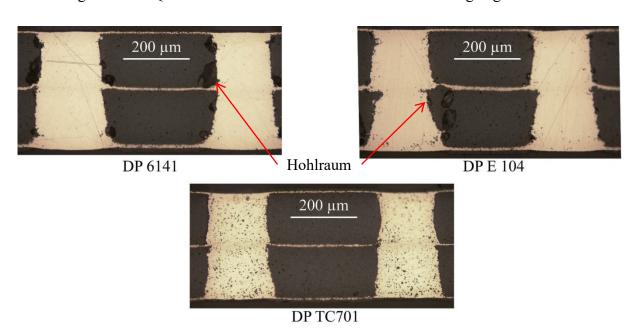

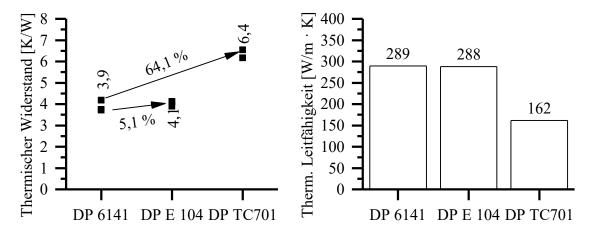

Der zweite Bereich umfasst das gesamte keramische Substrat. Um die geringe thermische Leitfähigkeit des Keramikgrundmaterials lokal zu verbessern, werden Metalle in Form von Metallzylindern in das Substrat integriert. Diese sog. thermischen Vias bestehen zumeist aus gold- oder silberbasierten Materialien und sind direkt in das Substrat unter die Chipbondfläche integriert. Gegenstand der Untersuchung ist hier der Einfluss der Viageometrie, des Viamaterials und des Sinterprozesses auf die thermische Performance und Hermetizität des Substrates.

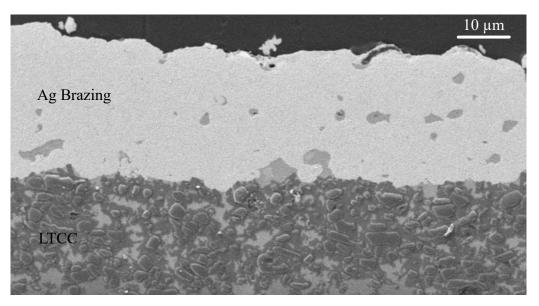

Weiterhin werden mittels neuen Silberfolien vollflächige Silberstrukturen in das Substrat integriert. Hierbei wird im Co-Fire Prozess das keramische Grundmaterial durch Silberfolie lokal substituiert, was Bereiche mit sehr hoher thermischer Leitfähigkeit im Substrat ermöglicht. Die thermische Performance solcher Silberstrukturen in LTCC Substraten wird anhand zweier Demonstratoren überprüft.

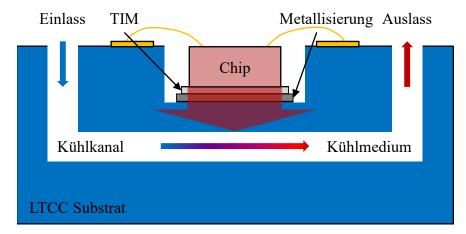

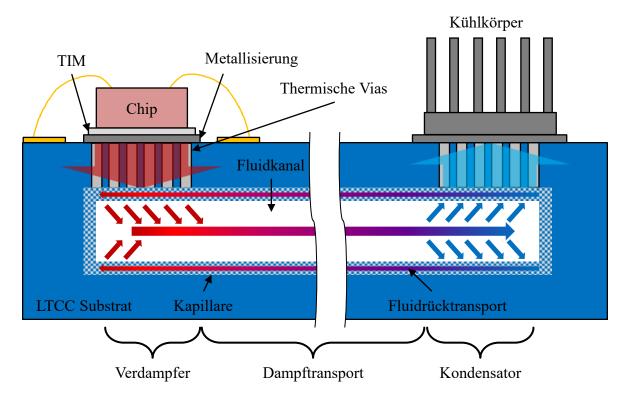

Der dritte Bereich umfasst die Wärmesenke. Im Rahmen dieser Arbeit wird die Möglichkeit diskutiert, fluidische Kanäle in das LTCC Substrat zu integrieren und damit eine aktive Kühlung zu realisieren. Die Untersuchungen umfassen das Design und die Fertigung des Kühlkanals und der fluidischen Schnittstellen, sowie die Bewertung der Kühlleistung dieser Methode.

#### **Abstract**

This thesis deals with the thermal path in a multilayer module based on low temperature cofired ceramic (LTCC). The thermal path describes the path of heat flowing from a heat generating component to a heat sink. The thesis focuses on new materials, technologies and methods, which improve the thermal performance of the multilayer module. The thermal path can be subdivided into three critical parts.

The first part contains the joining between the chip and the substrate. So called thermal interface materials (TIM) are used as bonding agent to ensure a strong and thermally conducting bond between chip and substrate. The thesis addresses the pressure less silver sintering technology, which provides a high thermally conducting bond between chip and substrate. Moreover reactive soldering is investigated as potential chip and substrate bonding technology. This technology utilizes a reactive multilayer foil, which reacts fast exothermically after a short thermal pulse. The delivered heat can be used to join materials with different coefficient of thermal expansion (CTE), like copper and LTCC or silicon. The thermal resistance, the mechanical strength and reliability of bonds based on reactive solders and silver pastes are characterized and compared to conventional bonding agents like solders and adhesives.

The second part addresses the entire ceramic substrate. To enhance the poor thermal conductivity of the ceramics metals in form of cylinders are integrated in the substrate. These so called thermal vias consist mostly of gold or silver based materials and are integrated below the chip bond area. The influence of the via geometry, via material and sinter process on the thermal performance and the hermeticity of the substrate are evaluated within the scope of this thesis. Furthermore new silver foils are integrated in the LTCC substrate during cofiring, to form a LTCC substrate with massive silver structures. Therefore, the LTCC is locally replaced by the silver foil, which forms areas with a very high thermal conductivity inside the substrate. The thermal performance of these silver structures inside LTCC substrates is investigated on the basis of two demonstrators.

The third part of the thermal path deals with the heat sink. The possibility to integrated fluidic channels inside the LTCC substrate, which can be utilized for active cooling with a coolant, is discussed within the scope of this thesis. The investigations cover the design and the fabrication of the fluidic channels and the fluidic interfaces. Moreover the thermal performance of these cooling concepts is evaluated.

# Inhaltsverzeichnis

| Vorwort   |                                                                      | VII |

|-----------|----------------------------------------------------------------------|-----|

| Kurzfassi | ung                                                                  | IX  |

| Abstract  |                                                                      | XI  |

| 1 Einle   | itung                                                                | 1   |

| 1.1 M     | otivation                                                            | 1   |

| 1.2 Zi    | elstellung der Arbeit                                                | 5   |

| 1.3 M     | ethodik der Arbeit                                                   | 6   |

| 1.3.1     | Versuchsplanung und Auswertung                                       | 6   |

| 1.3.2     | Design-, Realisierungs- und Bewertungsprozess                        | 7   |

| 2 Theo    | retische Grundlagen und Charakterisierungsmethoden                   | 9   |

| 2.1 Th    | neorie des Wärmetransports                                           | 9   |

| 2.1.1     | Joulesche Wärme und die Leistungsbilanz                              | 9   |

| 2.1.2     | Wärmestrahlung                                                       | 10  |

| 2.1.3     | Wärmeleitung                                                         | 11  |

| 2.1.4     | Konvektiver Wärmetransport                                           | 16  |

| 2.1.5     | Thermische Ersatzschaltbilder                                        | 22  |

| 2.1.6     | Temperaturfeldberechnung mittels der Finite – Elemente – Methode     | 23  |

| 2.2 M     | ethoden zur Bestimmung der thermischen Leitfähigkeit                 | 27  |

| 2.2.1     | Wiedemann-Franzsches Gesetz                                          | 27  |

| 2.2.2     | Laser Flash Analyse                                                  | 30  |

| 2.2.3     | Ermittlung der Wärmeleitfähigkeit nach ASTM D5470                    | 31  |

| 2.3 V     | ersuchsstand zur Bestimmung des thermischen Verhaltens               | 32  |

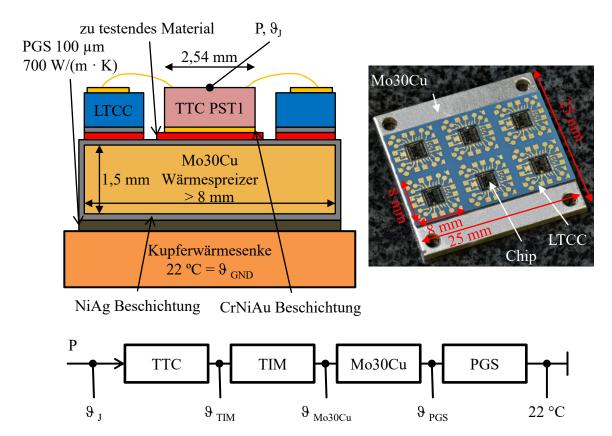

| 2.3.1     | Charakterisierung des thermischen Testchips PST1                     | 33  |

| 2.3.2     | Charakterisierung des thermischen Testchips G423B                    | 36  |

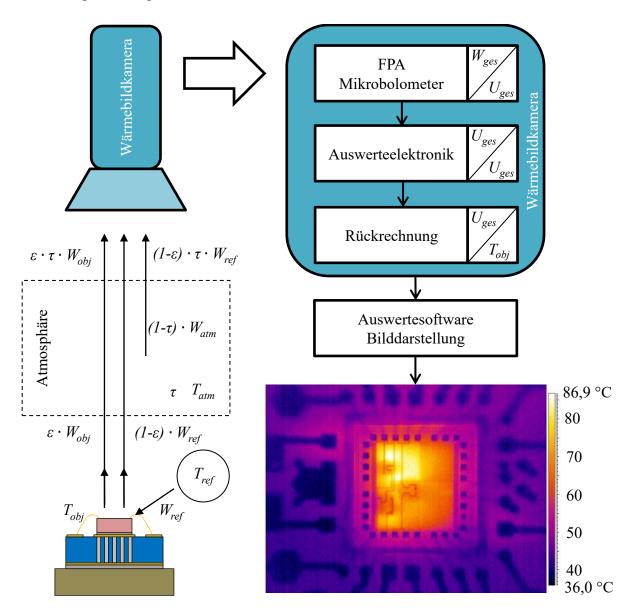

| 2.3.3     | Erfassung der Temperaturverteilung mittels Wärmebildkamera           | 37  |

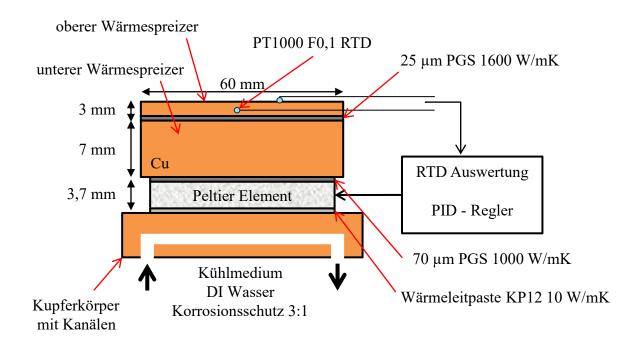

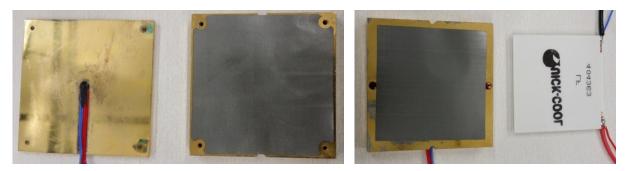

| 2.3.4     | Design und Steuerung der Wärmesenke                                  | 39  |

| 3 Tech    | nologische Grundlagen und Stand der Technik                          | 43  |

| 3.1 Er    | ntwurf und Herstellung von mehrlagigen keramischen Schaltungsträgern | 43  |

| 3.1.1     | Vorbehandlung, Stanzen und Viafüllen                                 |     |

| 3.1.2     |                                                                      |     |

| 3.1.3     | Laserstrukturierung                                                  |     |

| 3.1.4     | -                                                                    |     |

| 3.1.5     | Einbrand und Post-Fire Prozesse                                      |     |

| 3.2 Ve    | erfahren der Chipmontage und Verdrahtung                             | 49  |

|   | 3.2.1                                                                                                                | Fügen und Kontaktieren von Drahtbondchips                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 49                                                                                                           |

|---|----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

|   | 3.2.2                                                                                                                | Fügen von Chips mittels der Flip-Chip Technologie                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 53                                                                                                           |

|   | 3.3 Ent                                                                                                              | twärmungskonzepte in keramischen Packages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 55                                                                                                           |

|   | 3.3.1                                                                                                                | Chipmontage auf Wärmespreizer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 55                                                                                                           |

|   | 3.3.2                                                                                                                | Thermische Vias                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 57                                                                                                           |

|   | 3.3.3                                                                                                                | Dickschichtwärmespreizer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 59                                                                                                           |

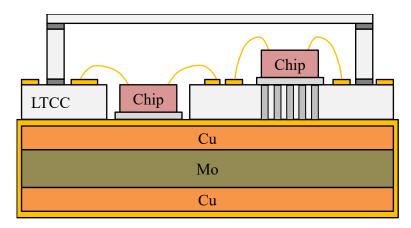

|   | 3.3.4                                                                                                                | LTCC – Metall Verbundsubstrat                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 64                                                                                                           |

|   | 3.3.5                                                                                                                | Aktive Kühlung durch substratintegrierte Kühlkanäle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 66                                                                                                           |

|   | 3.3.6                                                                                                                | Heatpipes in LTCC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 69                                                                                                           |

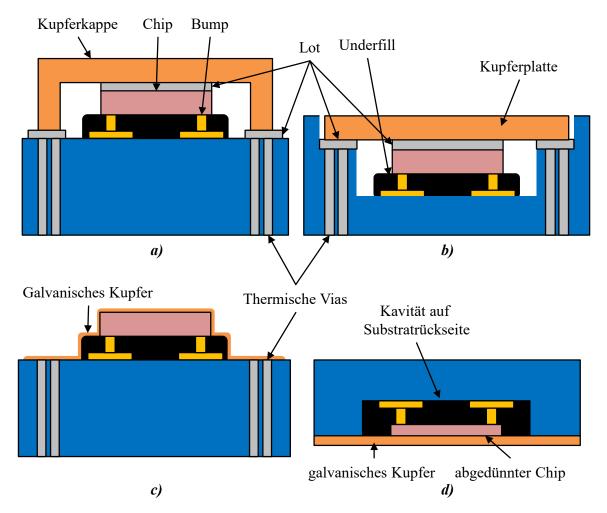

|   | 3.3.7                                                                                                                | Passive Entwärmung von Flip-Chips                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 71                                                                                                           |

| 4 | Chipn                                                                                                                | nontage auf Wärmespreizern mittels neuartiger Materialien                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 73                                                                                                           |

|   | 4.1 Dn                                                                                                               | ıckloses Niedertemperatursilbersintern                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 73                                                                                                           |

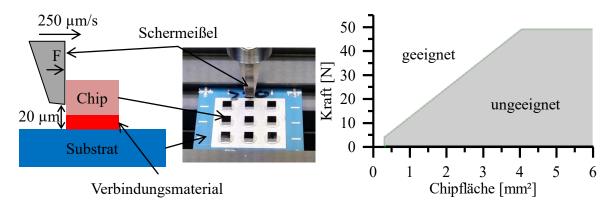

|   | 4.1.1                                                                                                                | Methodik zur Evaluierung der Chipmontage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                              |

|   | 4.1.2                                                                                                                | Ergebnisse der Untersuchungen und Bewertung                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                              |

|   | 4.1.3                                                                                                                | Zusammenfassung der Ergebnisse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                              |

|   | 4.2 Rea                                                                                                              | aktives Löten                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 100                                                                                                          |

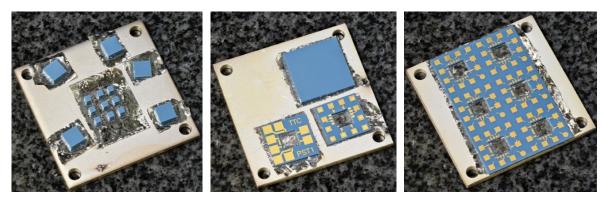

|   | 4.2.1                                                                                                                | Chipmontage auf Wärmespreizern                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 101                                                                                                          |

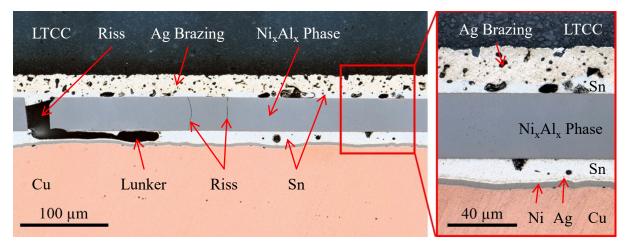

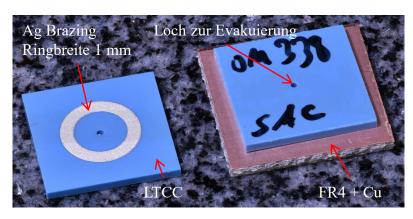

|   | 4.2.2                                                                                                                | LTCC Montage auf Kupferwärmespreizern                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                              |

|   | 4.2.3                                                                                                                | Zusammenfassung der Ergebnisse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 111                                                                                                          |

| 5 | Passiv                                                                                                               | ve Wärmeableitung im Schaltungsträger                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 113                                                                                                          |

|   | 5.1 The                                                                                                              | ermische Vias unter dem Aspekt der Hermetizität                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 113                                                                                                          |

|   |                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                              |

|   | 5.1.1                                                                                                                | Einflussfaktoren                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 113                                                                                                          |

|   | 5.1.1<br>5.1.2                                                                                                       | Einflussfaktoren Ermittlung der Hermetizität mittels Heliumlecktest                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                              |

|   | -                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 115                                                                                                          |

|   | 5.1.2                                                                                                                | Ermittlung der Hermetizität mittels Heliumlecktest                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 115<br>120                                                                                                   |

|   | 5.1.2<br>5.1.3<br>5.1.4                                                                                              | Ermittlung der Hermetizität mittels Heliumlecktest                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 115<br>120<br>122                                                                                            |

|   | 5.1.2<br>5.1.3<br>5.1.4                                                                                              | Ermittlung der Hermetizität mittels Heliumlecktest                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 115<br>120<br>122<br>125                                                                                     |

|   | 5.1.2<br>5.1.3<br>5.1.4<br>5.2 Sub                                                                                   | Ermittlung der Hermetizität mittels Heliumlecktest                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 115<br>120<br>122<br>125<br>125                                                                              |

|   | 5.1.2<br>5.1.3<br>5.1.4<br>5.2 Sub<br>5.2.1                                                                          | Ermittlung der Hermetizität mittels Heliumlecktest  Thermischer Widerstand alternierender Via Strukturen  Hermetizität von Vias im 0-Schrumpfprozess  estratintegrierte, dicke Silberwärmespreizer im Co-Fire Prozess  Materialanalyse der Silberfolie                                                                                                                                                                                                                                                                                                                                                                                                                                     | 115<br>120<br>122<br>125<br>125<br>127                                                                       |

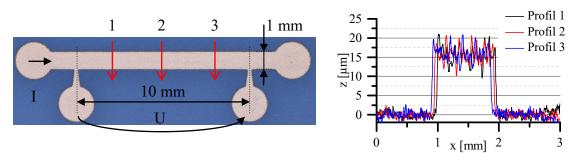

|   | 5.1.2<br>5.1.3<br>5.1.4<br>5.2 Sub<br>5.2.1<br>5.2.2                                                                 | Ermittlung der Hermetizität mittels Heliumlecktest                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 115<br>120<br>122<br>125<br>125<br>127<br>129                                                                |

|   | 5.1.2<br>5.1.3<br>5.1.4<br>5.2 Sub<br>5.2.1<br>5.2.2<br>5.2.3                                                        | Ermittlung der Hermetizität mittels Heliumlecktest                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 115<br>120<br>122<br>125<br>125<br>127<br>129<br>130                                                         |

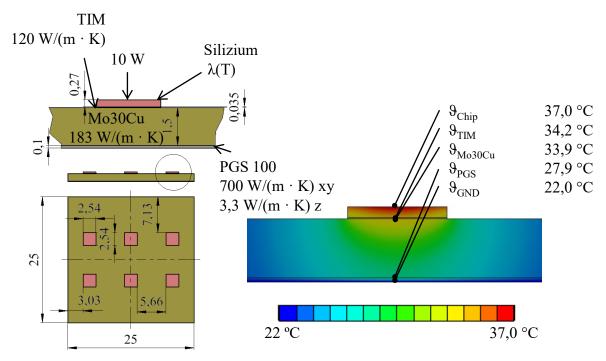

|   | 5.1.2<br>5.1.3<br>5.1.4<br>5.2 Sub<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4                                               | Ermittlung der Hermetizität mittels Heliumlecktest  Thermischer Widerstand alternierender Via Strukturen  Hermetizität von Vias im 0-Schrumpfprozess  estratintegrierte, dicke Silberwärmespreizer im Co-Fire Prozess  Materialanalyse der Silberfolie  Scherfestigkeit von geklebten bzw. gesinterten Chips auf dem Silbermaterial.  Ermittlung der Haftfestigkeit des LTCC – Ag Verbundes  Demonstrator Package zur Ermittlung der thermischen Performance                                                                                                                                                                                                                               | 115<br>120<br>122<br>125<br>125<br>127<br>129<br>130<br>139                                                  |

| 6 | 5.1.2<br>5.1.3<br>5.1.4<br>5.2 Sub<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6                             | Ermittlung der Hermetizität mittels Heliumlecktest  Thermischer Widerstand alternierender Via Strukturen  Hermetizität von Vias im 0-Schrumpfprozess  estratintegrierte, dicke Silberwärmespreizer im Co-Fire Prozess  Materialanalyse der Silberfolie  Scherfestigkeit von geklebten bzw. gesinterten Chips auf dem Silbermaterial.  Ermittlung der Haftfestigkeit des LTCC – Ag Verbundes  Demonstrator Package zur Ermittlung der thermischen Performance.  Hermetizität des LTCC – Ag Verbundes                                                                                                                                                                                        | 115<br>120<br>122<br>125<br>125<br>127<br>129<br>130<br>139                                                  |

| 6 | 5.1.2<br>5.1.3<br>5.1.4<br>5.2 Sub<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6                             | Ermittlung der Hermetizität mittels Heliumlecktest Thermischer Widerstand alternierender Via Strukturen Hermetizität von Vias im 0-Schrumpfprozess  Ostratintegrierte, dicke Silberwärmespreizer im Co-Fire Prozess  Materialanalyse der Silberfolie  Scherfestigkeit von geklebten bzw. gesinterten Chips auf dem Silbermaterial.  Ermittlung der Haftfestigkeit des LTCC – Ag Verbundes  Demonstrator Package zur Ermittlung der thermischen Performance  Hermetizität des LTCC – Ag Verbundes  Zusammenfassung der Ergebnisse                                                                                                                                                           | 115<br>120<br>122<br>125<br>125<br>127<br>129<br>130<br>139<br>139                                           |

| 6 | 5.1.2<br>5.1.3<br>5.1.4<br>5.2 Sub<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6                             | Ermittlung der Hermetizität mittels Heliumlecktest Thermischer Widerstand alternierender Via Strukturen Hermetizität von Vias im 0-Schrumpfprozess estratintegrierte, dicke Silberwärmespreizer im Co-Fire Prozess Materialanalyse der Silberfolie Scherfestigkeit von geklebten bzw. gesinterten Chips auf dem Silbermaterial. Ermittlung der Haftfestigkeit des LTCC – Ag Verbundes Demonstrator Package zur Ermittlung der thermischen Performance Hermetizität des LTCC – Ag Verbundes Zusammenfassung der Ergebnisse  e Wärmeableitung im Schaltungsträger sign, Fertigung und Charakterisierung.                                                                                     | 115<br>120<br>122<br>125<br>125<br>127<br>129<br>130<br>139<br>139                                           |

| 6 | 5.1.2<br>5.1.3<br>5.1.4<br>5.2 Sub<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6<br><b>Aktive</b>            | Ermittlung der Hermetizität mittels Heliumlecktest Thermischer Widerstand alternierender Via Strukturen Hermetizität von Vias im 0-Schrumpfprozess estratintegrierte, dicke Silberwärmespreizer im Co-Fire Prozess Materialanalyse der Silberfolie Scherfestigkeit von geklebten bzw. gesinterten Chips auf dem Silbermaterial. Ermittlung der Haftfestigkeit des LTCC – Ag Verbundes Demonstrator Package zur Ermittlung der thermischen Performance Hermetizität des LTCC – Ag Verbundes Zusammenfassung der Ergebnisse                                                                                                                                                                  | 115<br>120<br>122<br>125<br>125<br>127<br>129<br>130<br>139<br>139                                           |

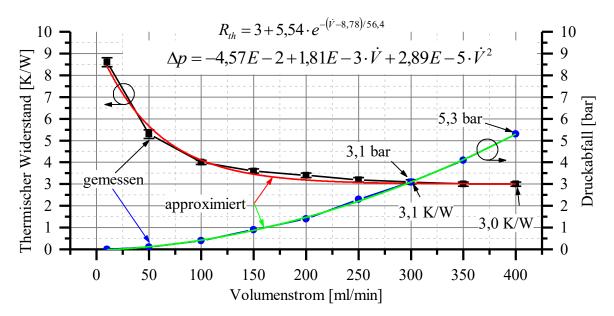

| 6 | 5.1.2<br>5.1.3<br>5.1.4<br>5.2 Sub<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6<br><b>Aktive</b><br>6.1 Des | Ermittlung der Hermetizität mittels Heliumlecktest                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 115<br>120<br>122<br>125<br>125<br>127<br>129<br>130<br>139<br>139<br>141<br>141<br>141                      |

| 6 | 5.1.2<br>5.1.3<br>5.1.4<br>5.2 Sub<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6<br><b>Aktive</b><br>6.1 Des | Ermittlung der Hermetizität mittels Heliumlecktest Thermischer Widerstand alternierender Via Strukturen Hermetizität von Vias im 0-Schrumpfprozess  Destratintegrierte, dicke Silberwärmespreizer im Co-Fire Prozess Materialanalyse der Silberfolie  Scherfestigkeit von geklebten bzw. gesinterten Chips auf dem Silbermaterial  Ermittlung der Haftfestigkeit des LTCC – Ag Verbundes  Demonstrator Package zur Ermittlung der thermischen Performance  Hermetizität des LTCC – Ag Verbundes  Zusammenfassung der Ergebnisse  e Wärmeableitung im Schaltungsträger  sign, Fertigung und Charakterisierung.  Integration von fluidischen Elementen in LTCC  Thermische Charakterisierung | 115<br>120<br>122<br>125<br>125<br>127<br>129<br>130<br>139<br>139<br><b>141</b><br>141<br>141<br>143<br>146 |

| 6.2.3      | Skalierbarkeit des Kühlkonzeptes                               | 160 |

|------------|----------------------------------------------------------------|-----|

| 6.2.4      | Elektrische Isolation zwischen Chip und Kühlmedium             | 163 |

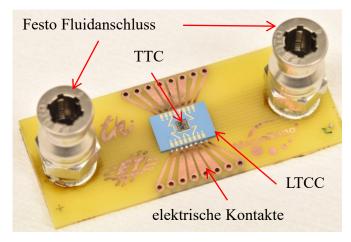

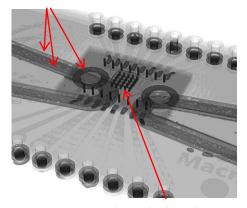

| 6.2.5      | LGA Package mit fluidischen Schnittstellen                     | 163 |

| 6.2.6      | Zusammenfassung der Ergebnisse                                 | 170 |

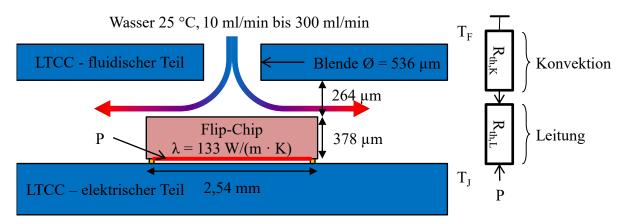

| 6.3 Kül    | ılkonzept für Flip-Chips                                       | 171 |

| 6.3.1      | Analytische Betrachtung                                        | 172 |

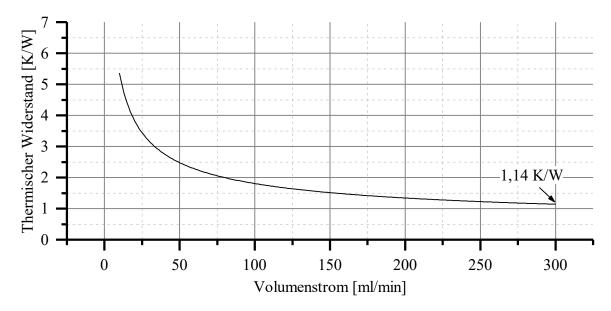

| 6.3.2      | CFD Simulation.                                                | 173 |

| 6.3.3      | Modulare Fertigung des Packages                                | 176 |

| 6.3.4      | Charakterisierung und Bewertung                                | 179 |

| 6.3.5      | Zusammenfassung der Ergebnisse                                 | 181 |

| 7 Zusan    | nmenfassung & Ausblick                                         | 183 |

| 7.1 Dru    | ckloses Niedertemperatursilbersintern                          | 183 |

| 7.2 Löt    | en mithilfe von reaktiven Materialen                           | 183 |

| 7.3 The    | rmische Vias unter dem Aspekt der Hermetizität                 | 184 |

| 7.4 Sub    | stratintegrierte, dicke Silberwärmespreizer im Co-Fire Prozess | 185 |

|            | ive Wärmeableitung im Schaltungsträger                         |     |

| Abbildung  | sverzeichnis                                                   | 189 |

| Tabellenve | erzeichnis                                                     | 201 |

| Symbolver  | zeichnis                                                       | 205 |

| Literaturv | erzeichnis                                                     | 213 |

| Thesen     |                                                                | 229 |

| Publikatio | nsverzeichnis                                                  | 231 |

# 1 Einleitung

#### 1.1 Motivation

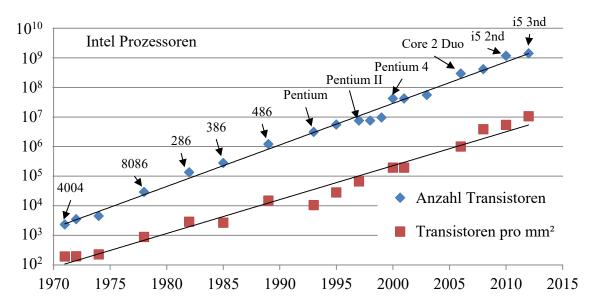

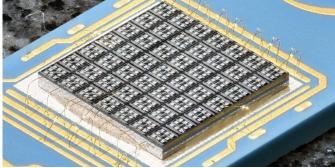

Seit der Erfindung des Transistors im Jahr 1947 durch John Bardeen, Walter H. Brattain und William B. Shockley [1] erlebt die Elektronik eine rasante Entwicklung. Bestanden elektronische Schaltungen zu Beginn noch aus vielen diskreten Einzelkomponenten, so stieg mit der Zeit das Maß an funktioneller Integration. Integrierte Schaltkreise aus den Jahren 1958 und 1959 von Jack Kilby und Robert Noyce enthielten vorerst einige wenige Transistoren und realisierten lediglich einfachste Funktionen [2], [3]. Mit Weiterentwicklung der Fertigungsprozesse stieg auch die Anzahl an möglichen Transistoren pro Fläche. Die ersten Mikroprozessoren aus dem Jahr 1970 enthielten bereits einige tausend Transistoren [4]. Im Jahr 1965 sagte Gordon Moore einen Trend voraus, wonach sich die Anzahl an Komponenten pro integriertem Schaltkreis jedes Jahr verdoppelt, welchen er 1975 auf eine Verdopplung aller zwei Jahre korrigierte [5]. Dieser Trend bestätigte sich in folgenden Jahren. 1993 enthielten komplexe Schaltkreise wie Prozessoren bereits mehrere Millionen Transistoren [4]. Die Verbesserung der Fertigungsverfahren führte zu immer kleineren Strukturbreiten, die eine höhere Anzahl an integrierten Komponenten pro Fläche ermöglichten. Im Jahr 2016 bestehen komplexe integrierte Schaltkreise Grafikprozessoren aus mehreren Milliarden Transistoren. Die Entwicklung der integrierten Schaltkreise ist am Beispiel der Intel Mikroprozessoren in Abbildung 1.1 dargestellt.

Abbildung 1.1: Entwicklung der integrierten Schaltkreise am Beispiel von Intel Mikroprozessoren. Daten aus [4].

Getrieben durch die Steigerung der Komplexität und Miniaturisierung integrierter Schaltkreise entwickelten sich parallel die Schaltungsträger und Verbindungstechnologien. Die Erfindung der Leiterplatte im Jahr 1943 durch Paul Eisler löste die bis dahin bestehende Freiluftverdrahtung ab [6]. Bauelemente wurden nun durch eine kupferkaschierte, isolierende

Platte gesteckt und auf einer Seite festgelötet. Die Platte übernahm neben der mechanischen Fixierung der Bauteile jetzt auch deren elektrische Verbindung. Die Forderung nach höheren Verdrahtungsdichten seitens der Halbleiterindustrie führte zu der Entwicklung komplexer, mehrlagiger Leiterplatten. Die Oberflächenmontagetechnik (engl. *surface mounted technology*, kurz SMT), entwickelt durch IBM im Jahr 1960, erlaubte zudem eine Miniaturisierung der Bauelemente und damit eine effektivere Flächenausnutzung des Schaltungsträgers. Mit der Laserstrukturierung von Bohrlöchern in Leiterplatten (*high density interconnect*, kurz HDI-Leiterplatten) wurden kleinere Bohrdurchmesser möglich, wodurch sich die Verdrahtungsdichte nochmals steigern ließ.

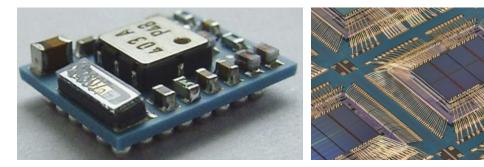

Die Erhöhung der Verdrahtungsdichten und die Minimierung der Strukturen tragen dabei maßgeblich zur Weiterentwicklung der Schaltungsträger- und Verbindungstechnologien bei. Daneben ist die Kostenreduktion ein weiterer wichtiger Treiber der Technologieentwicklung. So wird eine optimale Flächenausnutzung angestrebt, um die Kosten zu senken. Das wird u.a. durch die direkte Montage des Halbleiterchips auf dem Schaltungsträger erreicht (Nacktchipmontage, engl. *Chip-on-Board*, kurz: COB). Um den Integrationsgrad weiter zu erhöhen, werden passive und aktive Komponenten in den Schaltungsträger / das Bauteil integriert (engl. *System-in-Package*, kurz: SiP, Abbildung 1.2 links). Neue Technologien der 3D Integration wie das Stapeln einzelner Chips übereinander (Abbildung 1.2 rechts) oder das Vergraben des Chips im Schaltungsträger ermöglichen ein flexibleres Design und damit eine effizientere Flächenausnutzung.

Abbildung 1.2: Links: System-in-Package auf Basis eines keramischen Schaltungsträgers. Rechts: übereinander gestapelte Chips. Mit freundlicher Genehmigung der Micro Systems Engineering GmbH.

Das thermische Management gewinnt durch diesen Trend zunehmend an Bedeutung. Die Leistungssteigerung und Miniaturisierung der Bauelemente führt zu einer Erhöhung der Verlustleistungsdichte. Es muss daher mehr Wärme auf einer immer kleiner werdenden Fläche abgeführt werden. Dabei sollte die Bauteiltemperatur gering gehalten werden, da nach dem Gesetz von Arrhenius die Alterung einer Baugruppe durch die Erhöhung der Temperatur beschleunigt wird. Die sich hieraus ergebenden Anforderungen an den Schaltungsträger erfordern die Verbesserung von bestehenden und die Entwicklung von neuen Entwärmungskonzepten. Halbleitende Materialien mit hoher Bandlücke wie Siliziumcarbid (kurz: SiC) oder Galliumnitrid (kurz: GaN) erlauben zudem höhere Einsatztemperaturen der Schaltkreise im Vergleich zu Schaltkreisen aus Silizium [7], [8].

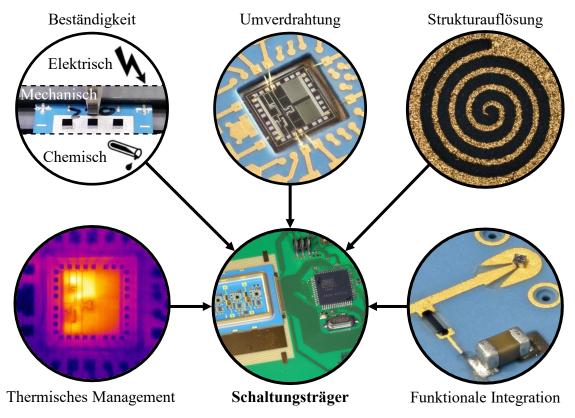

Höhere Einsatztemperaturen und längere Lebensdauer, wie sie z.B. der Satellitentechnologie gefordert Automobilindustrie und werden, steigern die Zuverlässigkeitsansprüche. Schaltungsträgermaterialien Andere wie Keramiken Verbindungstechnologien wie z. B. Niedertemperatursilbersintern (engl. low temperature silver sintering, kurz: LTSS) müssen eingesetzt werden, um diesen Anforderungen gerecht zu werden. In Abbildung 1.3 sind die Anforderungen an einen Schaltungsträger und dessen Aufgaben in einer Übersicht zusammengefasst.

Abbildung 1.3: Anforderungen an Schaltungsträger und deren Auswirkungen auf Schaltungsträger.

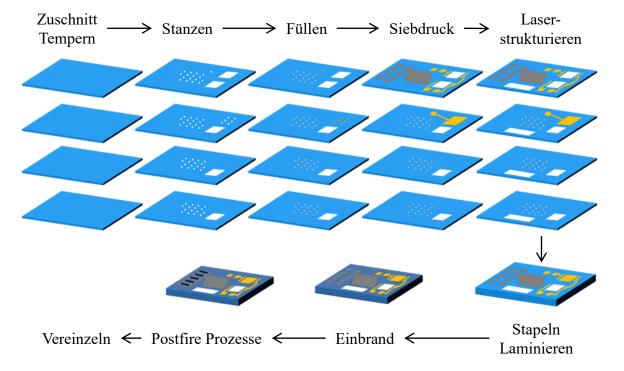

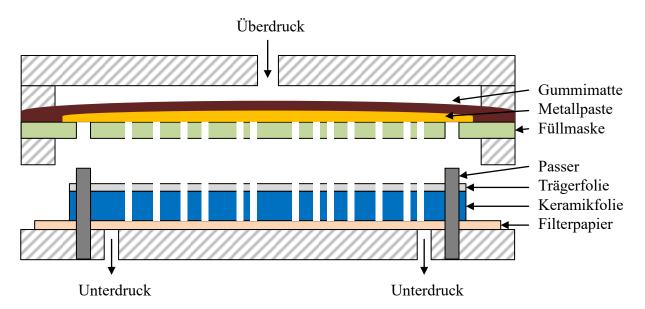

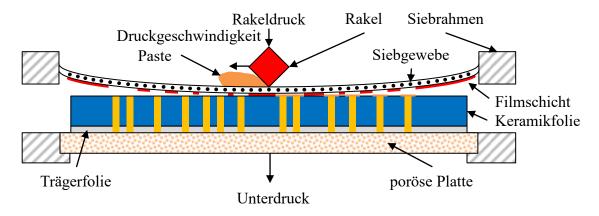

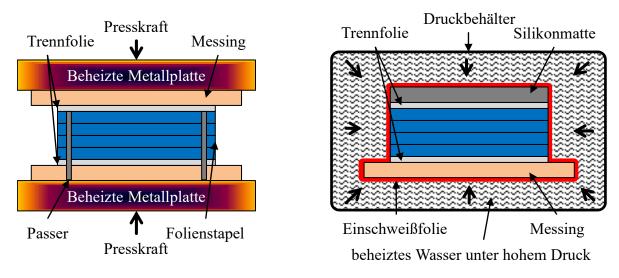

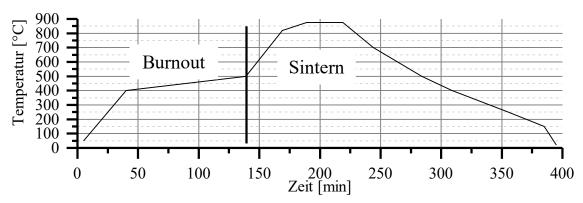

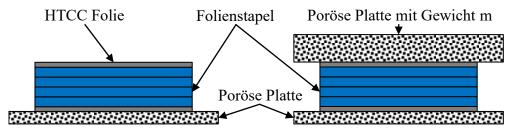

Niedertemperatur-Einbrand-Keramiken und deren Technologie (engl. Low Temperature Cofired Ceramics, kurz: LTCC) stellen eine Alternative zur Leiterplattentechnologie dar. Sie werden dort eingesetzt, wo Leiterplatten auf Basis organischer Materialien den Anforderungen nicht mehr gerecht werden können. Als Ausgangsmaterial dienen dabei keramik- und glasgefüllte organische Folien. Zur Erzeugung von Durchkontaktierungen werden Löcher in diese Folien gestanzt und diese dann mit Metallpaste aufgefüllt. Leiterzüge werden durch Siebdruck von Metallpasten auf der Vorder- bzw. Rückseite der Folien realisiert. Jede Lage des Schaltungsträgers wird dabei einzeln prozessiert. Anschließend werden die einzelnen Folien mittels Lamination zu einem Verbund verpresst. Daran schließt sich der Einbrand in einem Ofen an, wobei organische Bestandteile der Folie verbrennen und eine Sinterung stattfindet. Während dieses Prozesses versintert der sog. Grünling zu einem festen Glaskeramiksubstrat. Diese mehrlagigen, keramischen Schaltungsträger bieten neben einer hohen Strukturauflösung auch die Möglichkeit, passive Komponenten wie Widerstände, Induktivitäten und Kapazitäten direkt in den Schaltungsträger zu integrieren [9]. Dadurch

lässt sich das Maß an funktioneller Integration gegenüber der Leiterplatte nochmals steigern. Zudem weist das Grundmaterial ausgezeichnete Hochfrequenzeigenschaften auf. Ein Haupteinsatzgebiet der LTCC findet sich in Schaltungen für Hochfrequenzanwendungen. So Schaltungsträger wird dieses Material z.B. für Radaranwendungen als Satellitenkommunikationstechnik [10] eingesetzt. Ebenso wurden keramische Module für die Kommunikation in On-Board Entertainment Systemen entwickelt [11]. Auch sind miniaturisierte, hochfrequenztaugliche Bauelemente wie Filterstrukturen auf Basis dieser Technologie realisiert worden [12]. Darüber hinaus können keramische Schaltungsträger bei deutlich höheren Temperaturen als organische Schaltungsträger eingesetzt werden, sodass sie auch im Bereich der Hochtemperaturelektronik für die Automobilindustrie verwendet werden. Hier basieren die Schaltungen zur Motor-, ABS und Getriebesteuerung [13] bei einigen Fabrikaten auf keramischen Schaltungsträgern.

Das keramische Grundmaterial ist zudem temperaturstabil und beständig gegenüber einer Vielzahl an Chemikalien, sodass es auch zunehmend in den Bereichen der biologischen, medizinischen und chemischen Analyse verwendet wird. Die Systeme in diesen Anwendungsfeldern bestehen zumeist aus mikrofluidischen Modulen mit in den LTCC-Träger integrierten fluidischen Elementen wie Kanälen, Mischern und Reaktionskammern, sowie Sensoren für die Detektion verschiedenster physikalischer Größen wie z.B. Temperatur, Druck und Durchfluss [14]. Beispiele lassen sich hier in der Gasanalytik [15], [16], der Durchflussmessung in biologischen Mikrosystemen [17], sowie in der Analyse von biologischen Flüssigkeiten und Zellen [18], [19] finden.

Die hohe Zuverlässigkeit von LTCC-Schaltungsträgern ermöglicht den Einsatz im Medizinsektor. So basieren Schaltungen von einigen Herzschrittmachern auf LTCC-Trägern [20], [21].

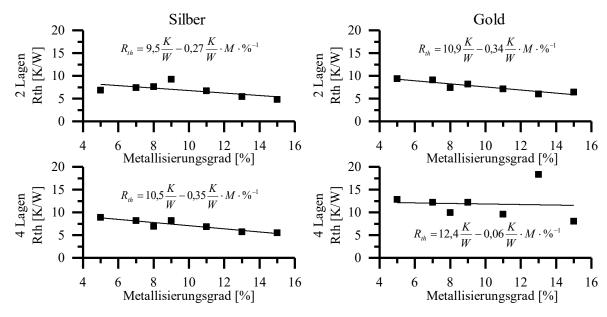

Das thermische Management ist in LTCC deutlich verbessert gegenüber einer epoxidbasierten Leiterplatte. Zum einen ist die thermische Leitfähigkeit des Grundmaterials ca. 10-mal höher als die der Leiterplatte. Zum anderen besteht die Möglichkeit den thermischen Pfad, also den Bereich zwischen Wärmequelle und –senke, zu optimieren. Durchkontaktierungen (engl. *Via*) können mit einer thermisch gut leitenden Silber- oder Goldpaste gefüllt werden, sodass die Wärme optimal durch das Substrat transportiert werden kann. Wärmespreizer werden hier mittels Siebdruck von Silber- oder Goldpasten realisiert und verteilen so die Wärme auf einer größeren Fläche. Kühlkanäle können direkt in den Schaltungsträger integriert werden und optimieren so die Entwärmung des Moduls.

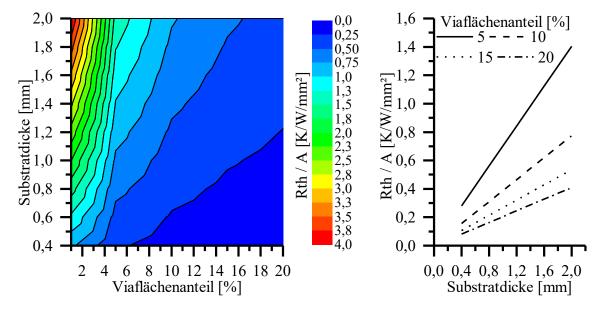

Die Forderung nach höheren Verlustleistungsdichten bringt jedoch auch diese Technologie an ihre Grenzen. Die erhöhte Wärmeleitfähigkeit der LTCC reicht nicht aus, um höhere Verlustleistungen sinnvoll abzuführen. Zudem lässt sich die Anzahl an thermischen Vias nicht beliebig erhöhen, da der Metallisierungsgrad technologisch auf etwa 20 bis 25 % begrenzt ist. Hier werden andere Substratmaterialien wie *Direct-Bonded-Copper* (kurz: DBC) oder Substrate mit Metallkern (*Insulated-Metal-Substrate*, kurz: IMS) eingesetzt. Diese Technologien bieten zwar eine deutlich höhere thermische Leitfähigkeit, sind jedoch in der Strukturauflösung und dem Funktionsintegrationsgrad stark eingeschränkt.

Die Motivation dieser Arbeit besteht darin, die technologischen Grenzen mit neuen Materialien und Prozessen zu überwinden und das Design des thermischen Pfades in LTCC

Modulen durch neue Kühlkonzepte zu optimieren. Hierdurch eröffnen sich der LTCC Technologie neue Einsatzmöglichkeiten in Anwendung mit höheren Verlustleistungsdichten, wie z. b. der Leistungselektronik oder Beleuchtungstechnologie. Die vielfältigen Einsatzgebiete der LTCC lassen sich hierdurch mit Anwendungen im Bereich hoher Verlustleistungsdichten kombinieren, woraus schließlich eine Vielzahl neuer Einsatzmöglichkeiten abgeleitet werden kann.

# 1.2 Zielstellung der Arbeit

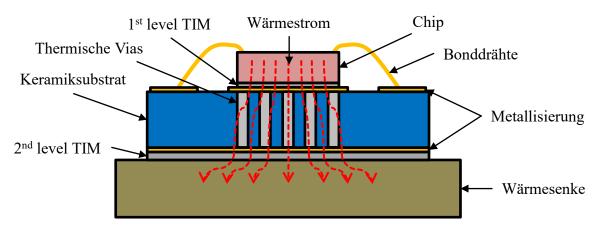

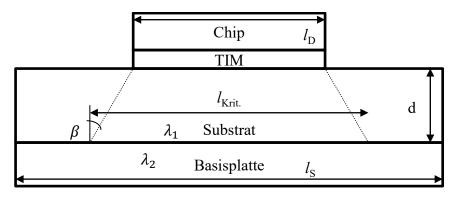

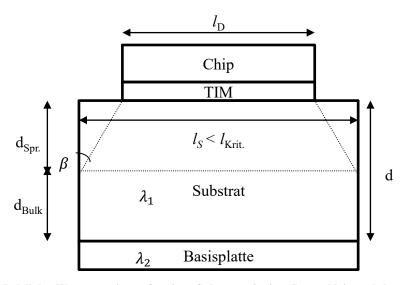

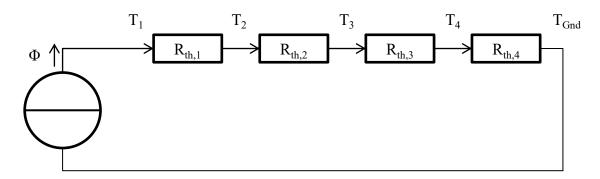

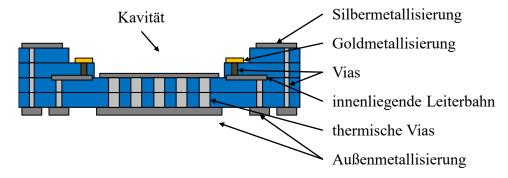

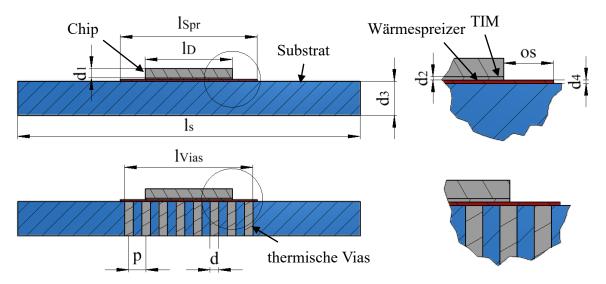

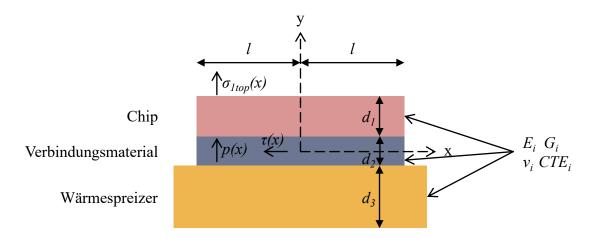

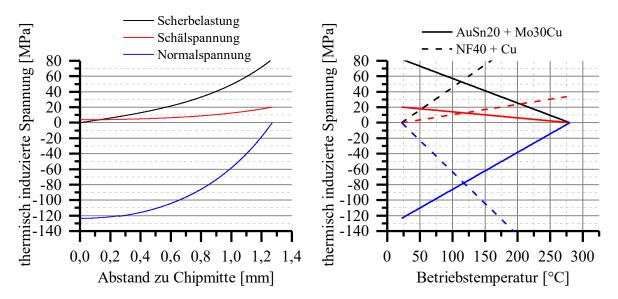

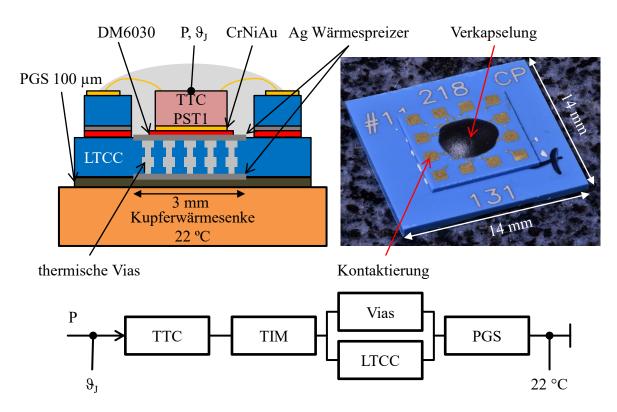

In Abbildung 1.4 ist schematisch ein typischer, mikroelektronischer Aufbau basierend auf keramischen Schaltungsträgern abgebildet. Der im Chip durch Verlustleistung freigegebene Wärmestrom wird in Richtung Wärmesenke abgeleitet. Der Weg des Wärmestroms durch den Aufbau wird thermischer Pfad genannt und bestimmt durch seinen thermischen Widerstand den Temperaturgradienten zwischen Chip und Wärmesenke und damit maßgeblich die Einsatzmöglichkeit und Leistungsfähigkeit des Aufbaus.

Abbildung 1.4: Schematischer Querschnitt eines typischen, mikroelektronischen Aufbaus auf Basis von keramischen Schaltungsträgern.

Diese Arbeit hat das Ziel, den thermischen Pfad zwischen Leistungsbauelement und Wärmesenke durch neue Materialien und Methoden derart zu verbessern, dass keramische Schaltungsträger auch in höheren Leistungsbereichen eingesetzt werden können. Der thermische Pfad lässt sich dabei in drei kritische Bereiche unterteilen.

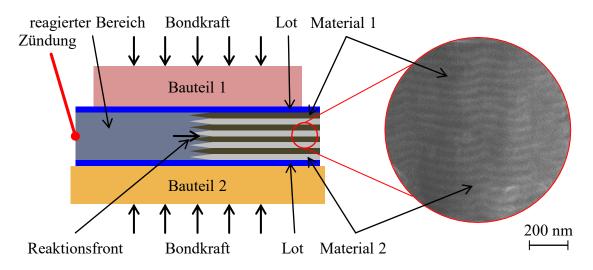

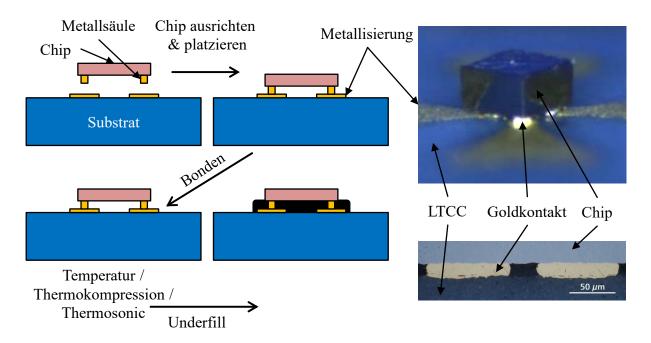

Der erste Bereich umfasst die Verbindung zwischen Chip und Substrat. Die hier eingesetzten Materialien werden als thermische Interface Materialien (engl. thermal interface material, kurz: TIM) bezeichnet und stellen neben der mechanischen Fixierung auch den thermischen Kontakt zwischen Chip und Substrat her. Im Rahmen dieser Arbeit werden Silberpasten für die Chipmontage untersucht, die bei niedrigen Temperaturen sintern und eine thermisch hoch leitende Verbindung zwischen Chip und Substrat realisieren. Weiterhin werden reaktive Lote untersucht, die nach thermischer Aktivierung kurzzeitig einen starken thermischen Impuls generieren, wodurch das Fügen von Materialien mit unterschiedlichem thermischen Ausdehnungskoeffizient ermöglicht wird. Diese reaktiven Lote und die Silberpasten werden

dabei mit den herkömmlichen Materialien der Chipmontage wie Loten und Klebern hinsichtlich ihres thermischen Widerstandes, der mechanischen Festigkeit und Zuverlässigkeit bewertet und verglichen.

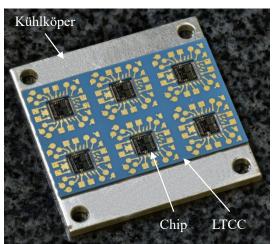

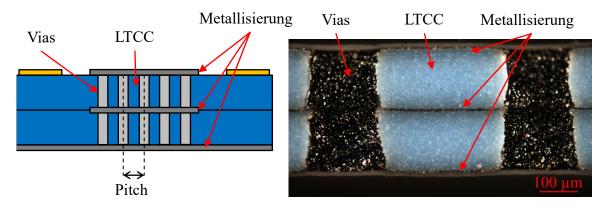

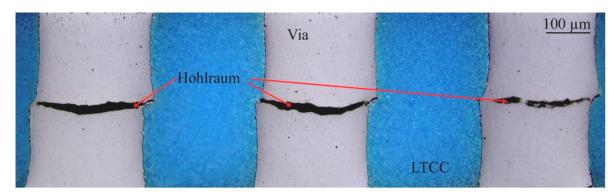

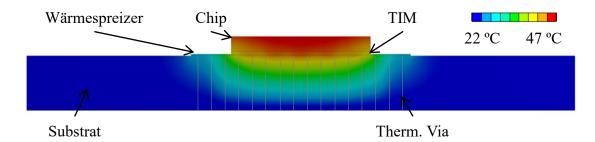

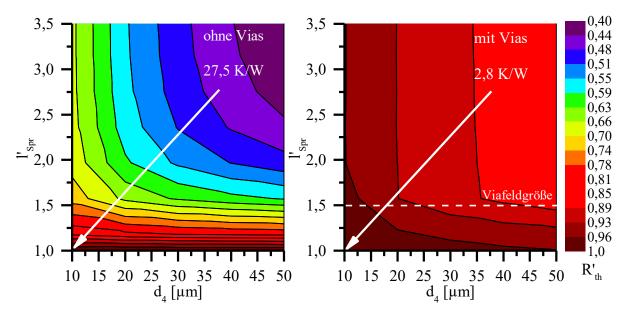

Der zweite Bereich umfasst das gesamte keramische Substrat. Das keramische Grundmaterial hat im Vergleich zu metallbasierten Schaltungsträgern wie DBC oder IMS Substraten eine niedrige thermische Leitfähigkeit. Daher müssen zusätzlich Materialien mit hoher thermischer Leitfähigkeit in das keramische Substrat integriert werden, um einen thermischen Pfad mit niedrigem thermischen Widerstand zu realisieren. Hierfür kommen thermische Vias zum Einsatz, die zumeist aus gold- oder silberbasierten Materialien bestehen und direkt in das Substrat unter die Chipbondfläche integriert werden. Thermische Vias können jedoch, bedingt durch ihre Materialzusammensetzung, zu Mikrokanälen entlang des thermischen Pfades führen, wodurch die Hermetizität des Substrates verringert wird. Ziel der Arbeit ist es hier, durch die Nutzung verschiedener Viaanordnungen die Hermetizität des Substrats zu verbessern. Weiterhin wird die Möglichkeit untersucht, mit neuen Silberfolien vollflächige Silberstrukturen in das Substrat zu integrieren. Hierbei wird das keramische Grundmaterial durch die Silberfolien lokal substituiert, was Bereiche mit sehr hoher thermischer Leitfähigkeit im Substrat ermöglicht. Außerdem wird der Einfluss der integrierten Silberstrukturen auf die Hermetizität des Substrates bewertet.

Der dritte Bereich umfasst die Wärmesenke. Hier kommen typischerweise im Verhältnis zum keramischen Modul große Metallplatten zum Einsatz, die die Wärme je nach Anwendung über Leitung, Konvektion oder Strahlung an die Umgebung abgeben. Die Verbindung des keramischen Moduls mit diesen Metallplatten erfolgt zumeist durch Löten, Kleben bzw. eine mechanische Fixierung. Unterschiede im thermischen Ausdehnungskoeffizienten zwischen den keramischen und den metallischen Werkstoffen stellen die Verbindungstechnologie hierbei vor besondere Herausforderungen. Im Rahmen dieser Arbeit wird die Möglichkeit diskutiert, fluidische Kanäle in das Substrat zu integrieren und damit eine aktive Kühlung zu realisieren. Die Untersuchungen umfassen das Design und die Fertigung des Kühlkanals und der fluidischen Schnittstellen, sowie die Bewertung der Kühlleistung dieser Methode.

#### 1.3 Methodik der Arbeit

#### 1.3.1 Versuchsplanung und Auswertung

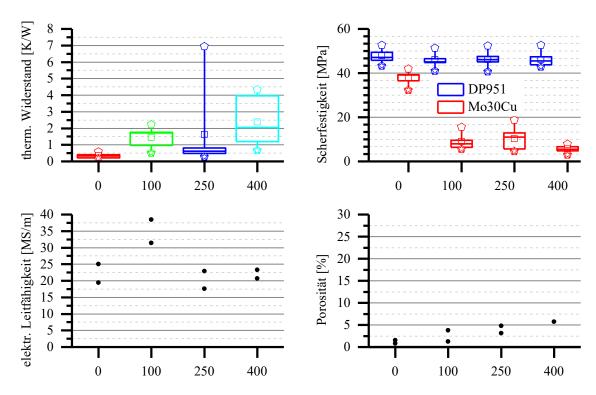

Die für die Arbeit notwendigen Versuche werden im Rahmen der statistischen Versuchsplanung durchgeführt. Mithilfe dieser Methodik werden Prozesse, Systeme oder Produkte hinsichtlich ihres Verhaltens auf Veränderungen der Einflussgrößen untersucht. Typischerweise wird dafür der Einfluss von Veränderungen der Eingangsvariablen auf die Zielgrößen bewertet. Die systematische Planung der Versuche (*Design-of-Experiment*, kurz: DOE) bietet dabei einen deutlich reduzierten Versuchsaufwand gegenüber der herkömmlichen "Trial-and-Error" Methode, sowie eine grobe Modellierung der Zusammenhänge basierend auf der statistischen Auswertung. Wo anwendbar, wird der voll faktorielle Versuchsplan

eingesetzt, der alle möglichen Kombinationen der Eingangsvariablen mit den dazugehörigen Faktorstufen enthält. Weiterhin wird die Reihenfolge der Abarbeitung einzelner Versuche zufällig gewählt, um so mögliche stochastische Fehler besser auf die einzelnen Versuche zu verteilen. [22]

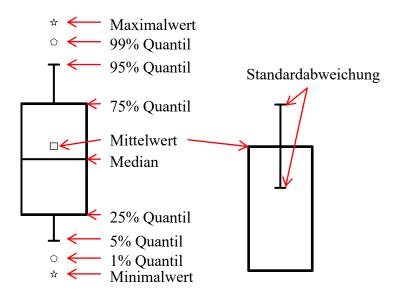

Wo mehr als ein Versuch pro Variation durchgeführt wird, erfolgt bei der statistischen Auswertung der Versuche mindestens die Angabe des Mittelwerts sowie der dazugehörigen Standardabweichung. Darüber hinaus werden an einigen Stellen sog. Boxplots (Abbildung 1.5) verwendet, die eine höhere statistische Aussagekraft als Mittelwert und Streuung besitzen.

Abbildung 1.5: Darstellung von Messdaten; Links: Boxplot mit allen relevanten Quantilen. Rechts: Säulendiagramm mit Standardabweichung.

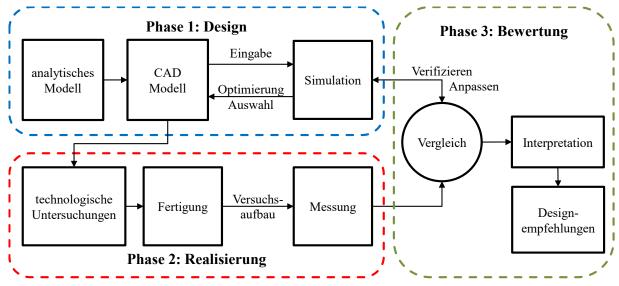

#### 1.3.2 Design-, Realisierungs- und Bewertungsprozess

Der Ablauf der Untersuchungen lässt sich in drei Phasen aufteilen und ist in Abbildung 1.6 schematisch dargestellt. Die erste Phase umfasst den Designprozess. Hier werden mit stark vereinfachten analytischen Modellen die Auswirkungen der Einflussgrößen auf die Zielgrößen abgeschätzt. Aufbauend auf diesen Erkenntnissen wird ein CAD Modell erstellt, welches der Ausgangspunkt für simulative Untersuchungen ist. Die Simulationen werden mit der Simulationsumgebung ANSYS Workbench durchgeführt und haben das Ziel, die Aussagen der analytischen Modelle zu verifizieren bzw. zu erweitern. Des Weiteren bieten die Simulationen die Möglichkeit vergleichsweise schnell und kostengünstig verschiedene thermische Designstrategien zu testen. Basierend auf den Simulationsergebnissen wird das CAD Modell hinsichtlich eines optimalen thermischen Designs angepasst bzw. die vielversprechendsten Designstrategien für weitere Untersuchungen ausgewählt.

Das optimierte CAD Modell stellt dann die Grundlage für die zweite Phase dar. Diese umfasst die Fertigung und die Messung. Da für die Realisierung einiger Kühlkonzepte Technologien und Prozesse erforderlich sind, die über den Stand der Technik hinausgehen, sind

technologische Untersuchungen im Rahmen der Fertigung notwendig. Diese haben das Ziel, die für die Realisierung des Kühlkonzeptes notwendigen Technologien, Materialien und Prozesse in die Fertigung der keramischen Schaltungsträger zu integrieren. Hierbei wird besonders auf Kompatibilität zu etablierten Fertigungstechnologien und –verfahren geachtet. Nach erfolgreicher Fertigung des Kühlkonzeptes erfolgt die elektrische und thermische Vermessung des Designs. Hierfür werden im Rahmen dieser Arbeit Versuchsaufbauten und Methoden entwickelt, die eine präzise Messung der thermischen Leistungsfähigkeit des zu testenden Kühlkonzeptes ermöglichen. Darüber hinaus sind die Versuchsaufbauten so gestaltet, das der Probenwechsel mit nur geringem Aufwand erfolgt, die Messdaten in einem automatisierten Verfahren aufbereitet und die relevanten thermischen Daten bereitgestellt werden. Der Zeitaufwand für die Vermessung wird hierdurch erheblich reduziert.

Die dritte Phase umfasst den Vergleich zwischen Simulation und Realisierung und nachfolgend die Bewertung bzw. Interpretation der Ergebnisse. Hierbei wird das Simulationsmodell mithilfe der gemessenen Daten verifiziert und gegebenenfalls angepasst. Neben Materialkennwerten wie der effektiven thermischen Leitfähigkeit einzelner Schichten kann hierbei auch die Geometrie des Simulationsmodells an die realen Abmaße der gefertigten Proben angeglichen werden. Abschließend werden die Messdaten bewertet und interpretiert. Die Effekte der Einflussfaktoren auf die Zielgrößen wie die thermische Leistungsfähigkeit werden hierbei ermittelt. Weiterhin können verschiedene Kühlkonzepte miteinander verglichen und Designempfehlungen abgeleitet werden.

Abbildung 1.6: Schematischer Ablauf und Zusammenhang des Design-, Realisierungs- und Bewertungsprozess.

# 2 Theoretische Grundlagen und Charakterisierungsmethoden

## 2.1 Theorie des Wärmetransports

#### 2.1.1 Joulesche Wärme und die Leistungsbilanz

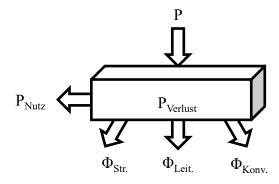

Die in einem elektrischen Bauteil eingebrachte Leistung P teilt sich in Nutzleistung  $P_{Nutz}$  und Verlustleistung  $P_{Verlust}$  auf. Die Verlustleistung beschreibt dabei den Teil der elektrischen Leistung, der aufgrund des ohmschen Widerstandes R des Bauteils dissipiert wird. Die sich aufgrund des äußeren Spannungsfeldes U bewegenden Valenzelektronen stoßen elastisch mit anderen Valenzelektronen zusammen und geben ihre Energie weiter. Treffen die Valenzelektronen auf Atomrümpfe, führt die Energieübertragung zu einer Erhöhung der Gitterschwingung, was einer Erhöhung der Temperatur gleichkommt. Hierbei wird kinetische Energie in thermische Energie umgewandelt. Diese Energie wird als Joulesche Wärme Q bezeichnet und ist als Produkt aus Leistung und Zeit definiert (2.1). [23]

$$Q = P_{Verlust} \cdot t = \frac{U^2}{R} \cdot t \tag{2.1}$$

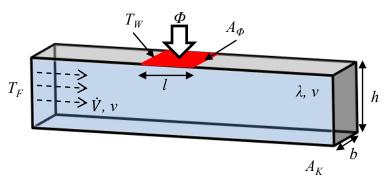

Diese thermische Energie wird in Form eines Wärmestroms übertragen, siehe Abbildung 2.1. Der Begriff des Wärmestroms  $\Phi$  beschreibt hier die Wärme Q, die in einer bestimmten Zeit t übertragen wird, vgl. Gl. (2.2). Mit (2.1) kann der Wärmestrom mit der Verlustleistung gleichgesetzt werden. Die Einheit des Wärmestroms ist [W]. [23]

$$\Phi = \frac{\delta Q}{\delta t} = P_{Verlust} \tag{2.2}$$

Je nach Umgebungsbedingungen wird der Wärmestrom über Wärmestrahlung, Wärmeleitung bzw. Konvektion an die Umgebung übertragen. Dabei ist die Summe aller Teilströme konstant und entspricht der im Bauteil umgesetzten Verlustleistung (2.3). [23]

$$P_{Verlust} = \Phi = \Phi_{Str.} + \Phi_{Leit.} + \Phi_{Konv.} \tag{2.3}$$

Abbildung 2.1: Schema der Wärme- und Leistungsbilanz in einem Körper.

## 2.1.2 Wärmestrahlung

Ein Körper mit einer bestimmten Temperatur T > 0~K gibt an seiner Oberfläche Wärme in Form von elektromagnetischen Wellen an die Umgebung ab. Für diese Art des Wärmetransportes ist kein Medium erforderlich, sodass die Übertragung auch im Vakuum stattfinden kann. Die dabei maximal mögliche Wärmestromdichte wird nach dem Stefan Boltzmann Gesetz (Gl. (2.4)) berechnet. Ein Strahler, der diese Wärmestromdichte erreicht, wird schwarzer Strahler genannt.  $\sigma$  bezeichnet hier die universelle Stefan-Boltzmann-Konstante. [23]

$$\dot{q} = \sigma \cdot T^4 \tag{2.4}$$

Reale Körper emittieren nicht mit der maximal möglichen Wärmestromdichte. Eine gute Approximation des Strahlungsverhaltens realer Körper ist der diffuse graue Strahler. Hier wird die Wärmestromdichte mit einem Korrekturfaktor  $\varepsilon(T)$  versehen, der die emittierte Strahlung des Körpers  $M_G$  ins Verhältnis zur emittierten Strahlung eines schwarzen Strahlers  $M_S$  gleicher Temperatur setzt, siehe Gl. (2.5) & (2.6). Dieser Korrekturfaktor wird Emissionsgrad genannt und ist bei einem grauen Strahler von dessen Oberflächeneigenschaften und der Oberflächentemperatur abhängig. [23]

$$\dot{q} = \varepsilon(T) \cdot \sigma \cdot T^4 \tag{2.5}$$

$$\varepsilon(T) = \frac{M_G}{M_S}, \qquad 0 < \varepsilon(T) < 1 \tag{2.6}$$

Die Integration über die Fläche A führt dann zu dem Wärmestrom  $\Phi_{Str.}$  Gl. (2.7). [23]

$$\Phi_{Str.} = \varepsilon(T) \cdot \sigma \cdot A \cdot T^4 \tag{2.7}$$

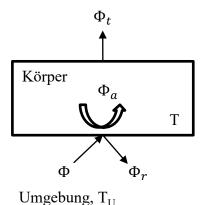

Befindet sich der Körper in einer Umgebung mit der Temperatur  $T_U$ , so gibt die Umgebung Wärmestrahlung an den Körper ab. Diese wird abhängig von dessen Oberflächen- und Materialeigenschaften absorbiert, reflektiert bzw. transmittiert, siehe Abbildung 2.2. [23]

Abbildung 2.2: Übersicht über Wärmestrahlung die auf einen Körper trifft.

Dabei werden die einzelnen Strahlungsanteile durch den Absorptionsgrad a, den Reflektionsgrad r und den Transmissionsgrad  $\tau$  bestimmt. Es gilt Gl. (2.8). Die Besonderheit des schwarzen Strahlers ist, dass er alle auftreffende Wärmestrahlung absorbiert. Reflexion und Transmission finden dadurch bei einem schwarzen Körper nicht statt. [23]

$$a + r + \tau = 1 \tag{2.8}$$

Die meisten Festkörper sind undurchlässig für Wärmestrahlung, sodass gilt:  $\tau = 0$  und r = 1 - a. Da der Körper eine gewisse Temperatur hat, gibt er an seiner Oberfläche Wärme in Form von Wärmestrahlung ab. Die Nettowärmestrahlung, die der Körper dabei an die Umgebung abgibt, wird nach Gl. (2.9) bestimmt. [23]

$$\Phi_{Str.} = \Phi_{Em.} - \Phi_a = \varepsilon(T) \cdot \sigma \cdot A \cdot T^4 - a \cdot \sigma \cdot A \cdot T_U^4$$

(2.9)

Für graue Strahler ist der Absorptionsgrad genauso groß wie der Emissionsgrad, sodass sich Gl. (2.9) vereinfacht und der Wärmestrom nach Gl. (2.10) berechnet werden kann. [23]

$$\Phi_{Str.} = \varepsilon(T) \cdot \sigma \cdot A \cdot (T^4 - T_U^4) \tag{2.10}$$

Dieser Gleichung ist leicht zu entnehmen, dass ein Körper bezogen auf die Wärmestrahlung nur dann eine Wärmequelle darstellt, wenn dessen Temperatur größer als die der Umgebung ist. Im anderen Fall agiert der Körper als Wärmesenke und entzieht der Umgebung thermische Energie.

Der thermische Widerstand für eine abstrahlende Oberfläche A wird nach Gl. (2.11) berechnet.

$$R_{th} = \frac{1}{\alpha_S \cdot A} \tag{2.11}$$

Die Wärmeübergangszahl  $\alpha_S$  wird dabei nach Gl. (2.12) berechnet.

$$\alpha_S = \varepsilon(T) \cdot \sigma \cdot \frac{(T^4 - T_U^4)}{(T - T_U)} \tag{2.12}$$

#### 2.1.3 Wärmeleitung

Der Begriff der Wärmeleitung umfasst den Wärmetransport innerhalb von Festkörpern, Flüssigkeiten und Gasen aufgrund eines Temperaturgradienten. Der Wärmetransport in Flüssigkeiten und Gasen erfolgt neben der Konvektion, auch durch Stöße von Teilchen. Die Übertragung der kinetischen Energie dieser Teilchen erfolgt dabei von Bereichen mit hohem zu Bereichen mit niedrigem Energieniveau. Dabei bestimmt die Temperatur die Höhe des Energieniveaus, sodass die Wärme entlang des Temperaturgradienten transportiert wird. Der Wärmetransport in Festkörpern erfolgt hauptsächlich durch Gitterschwingungen. Hierbei wird die thermische Energie durch Bewegung der Atome im Gitter transportiert. In elektrisch leitenden Festkörpern wird der Wärmetransport maßgeblich durch die Bewegung der freien

Elektronen bestimmt. Die allgemeine Wärmeleitungsgleichung (2.13) beschreibt die Änderung der Temperatur T über die Zeit t im instationären Fall bei Vorhandensein innerer Wärmequellen  $\dot{W}$ . [23]

$$\frac{\partial T}{\partial t} = \frac{\lambda}{\rho \cdot c_p} \cdot \nabla^2(T) + \frac{\dot{W}}{\rho \cdot c_p} \tag{2.13}$$

Die Proportionalitätsfaktoren  $\lambda$ ,  $\rho$  und  $c_p$  beschreiben dabei die stoffspezifischen Konstanten thermische Leitfähigkeit, Dichte und spezifische Wärmekapazität. In dieser Form gilt sie für inkompressible Festkörper, deren stoffspezifische Konstanten temperaturunabhängig sind. Im stationären Fall ist die Temperatur zeitlich unabhängig und das Fouriersche Gesetz kann angewendet werden, Gl. (2.14). Dieses Gesetz stellt den Zusammenhang zwischen der Wärmestromdichte  $\dot{q}$  und dem Temperaturfeld  $\nabla(T)$  her. Das Minuszeichen geht auf den zweiten Hauptsatz der Thermodynamik zurück, der besagt, dass Wärme nur in Richtung des Temperaturgefälles fließt. [23]

$$\dot{q} = -\lambda \cdot grad(T) = -\lambda \cdot \left(\frac{\partial T}{\partial x} \cdot \overrightarrow{e_x} + \frac{\partial T}{\partial y} \cdot \overrightarrow{e_y} + \frac{\partial T}{\partial z} \cdot \overrightarrow{e_z}\right)$$

(2.14)

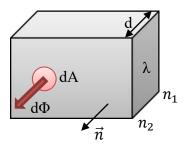

Der Wärmestrom  $d\Phi$  durch das Flächenelement dA ist nach folgender Gleichung definiert. [23]

$$d\Phi = -\lambda \cdot \frac{dT}{d\vec{n}} \cdot dA \tag{2.15}$$

Dabei steht der Wärmestrom senkrecht auf dem Flächenelement.  $\frac{dT}{d\vec{n}}$  beschreibt hierbei den Temperaturgradienten entlang der Flächennormale. In Abbildung 2.3 ist dies für einen einfachen Quader dargestellt.

Abbildung 2.3: Schema des Wärmestroms in einem Quader entlang der Flächennormale.

Nach Integration über die Fläche A ergibt sich Gl. (2.16).

$$-\lambda \cdot dT = \Phi \cdot \frac{d\vec{n}}{A} \tag{2.16}$$

Die Integration entlang der Flächennormale führt zu Gl. (2.17) und (2.18).

$$-\lambda \cdot \int_{T(n_1)}^{T(n_2)} dT = \frac{\Phi}{A} \cdot \int_{n_1}^{n_2} d\vec{n}$$

(2.17)

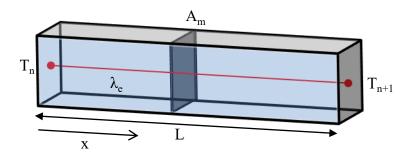

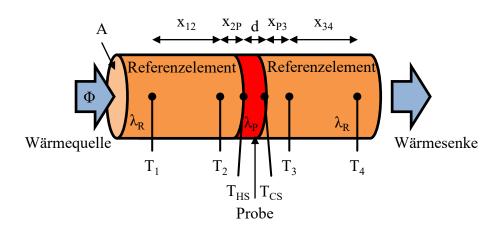

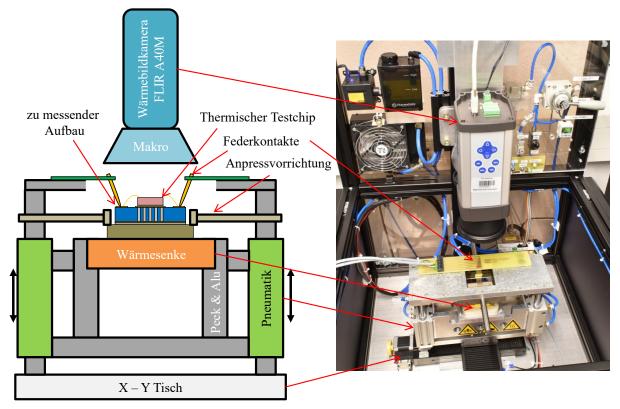

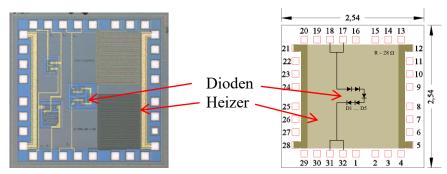

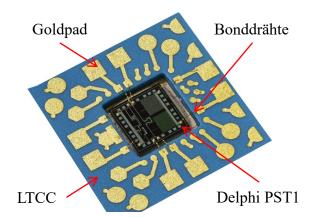

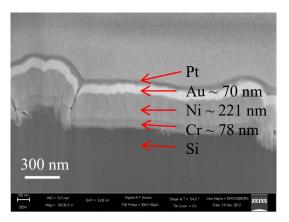

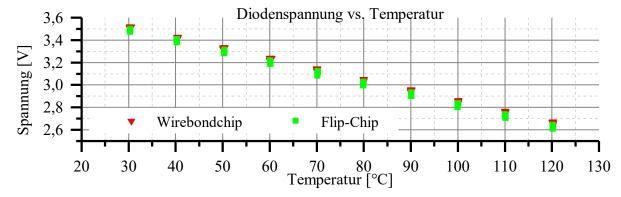

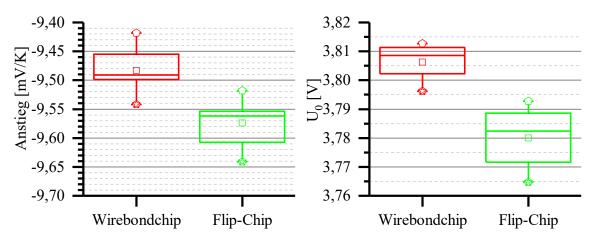

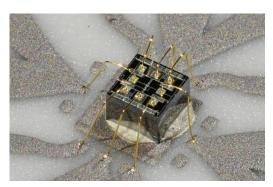

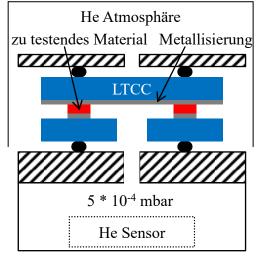

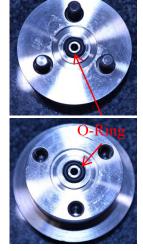

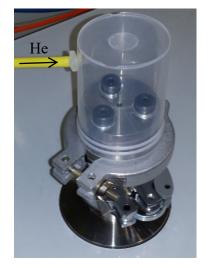

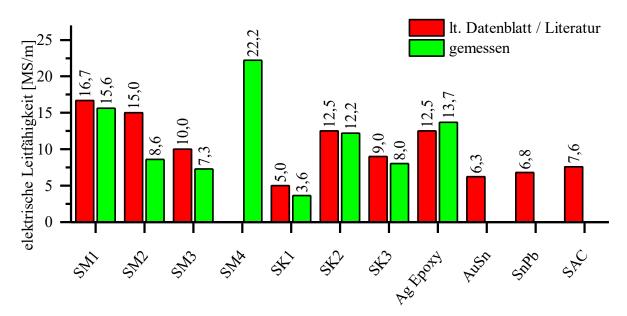

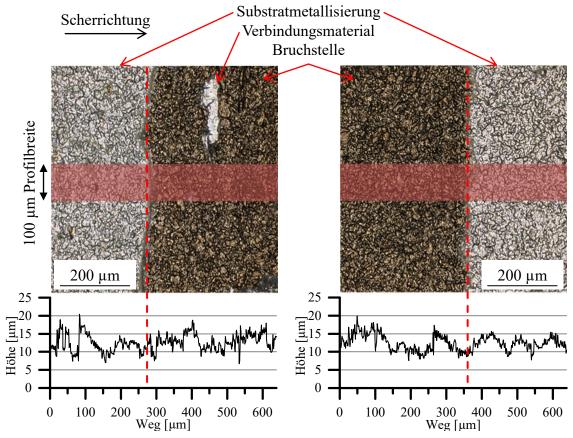

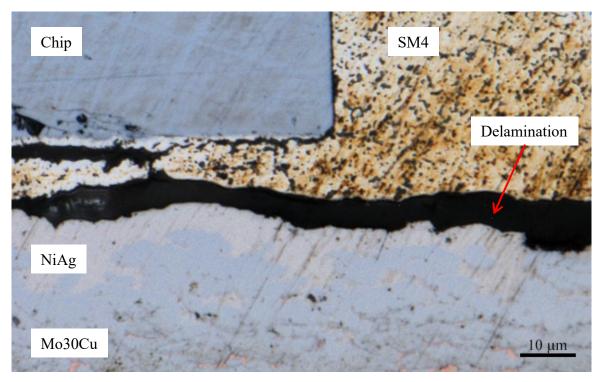

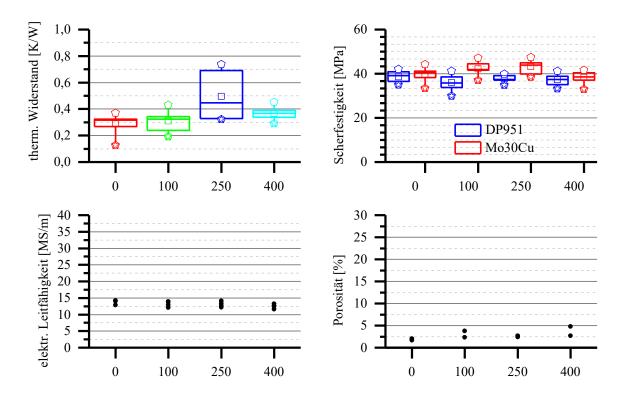

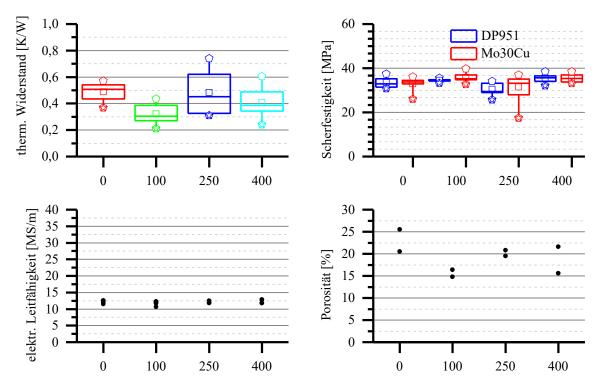

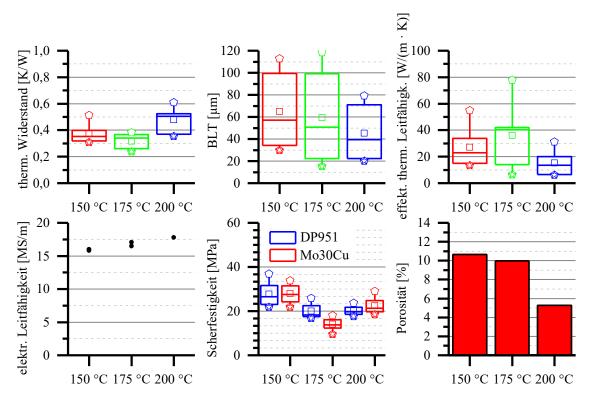

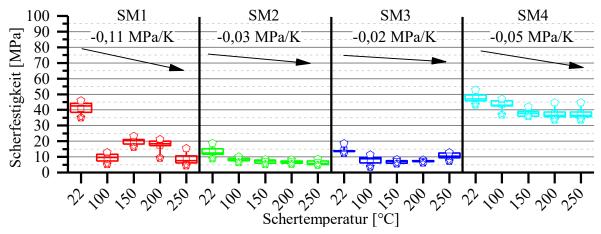

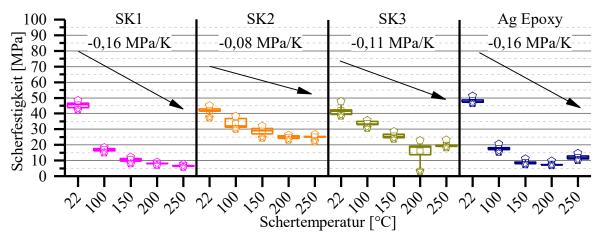

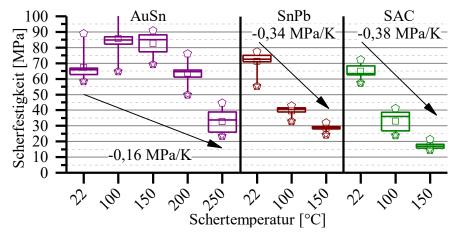

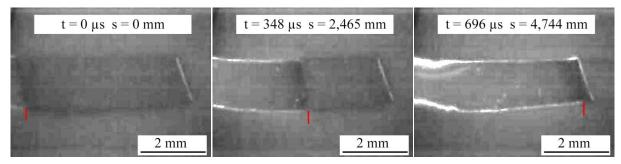

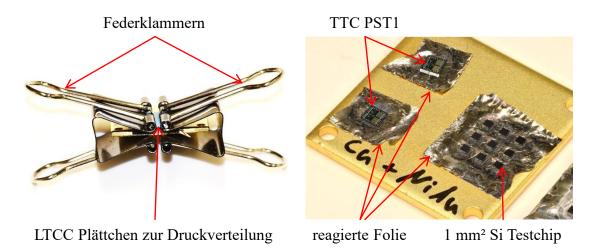

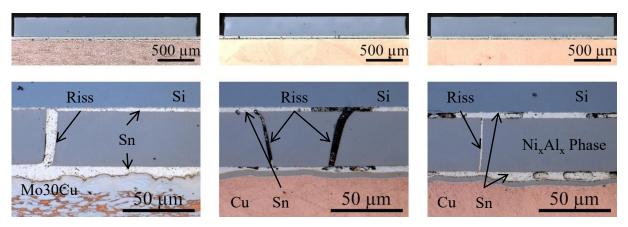

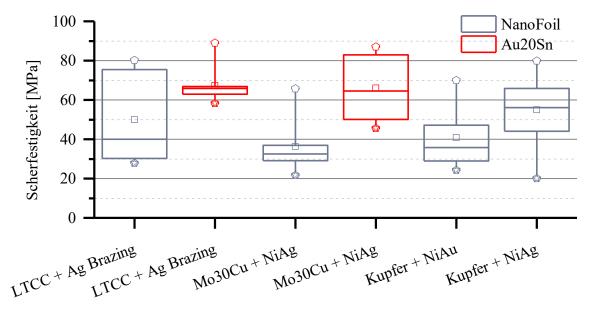

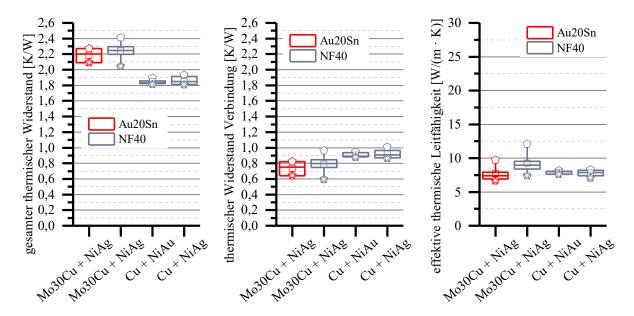

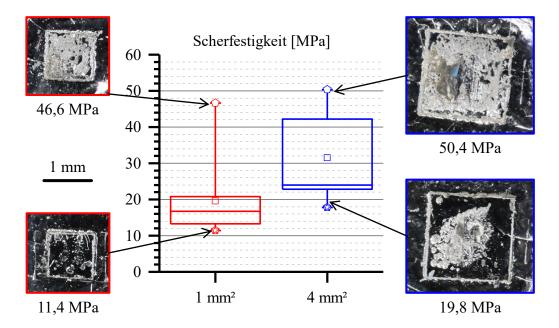

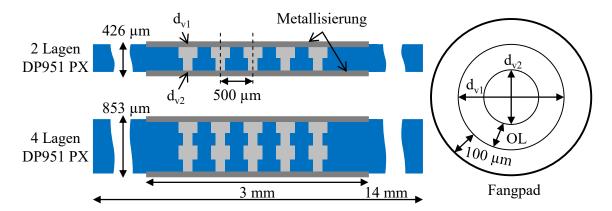

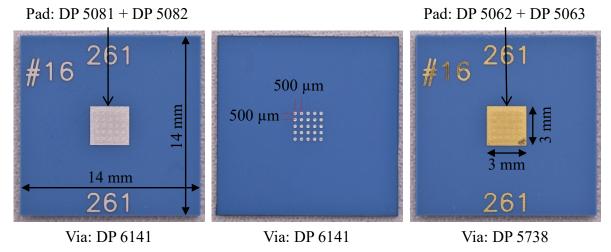

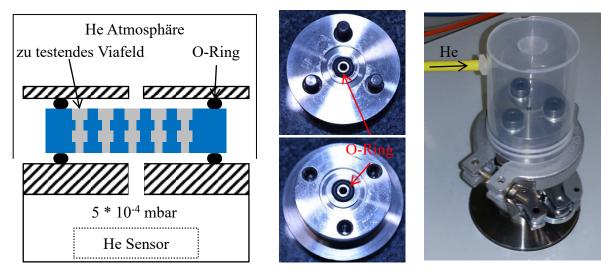

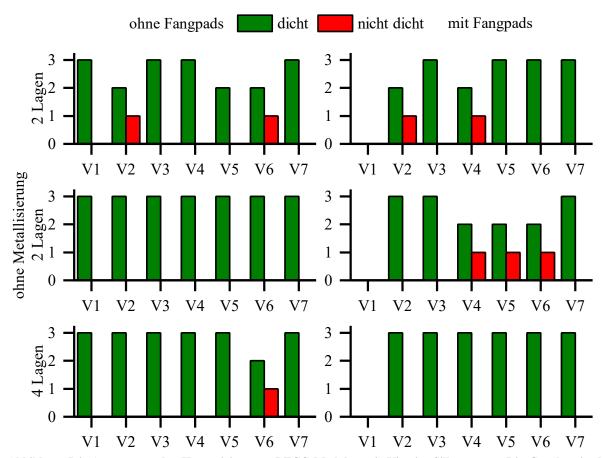

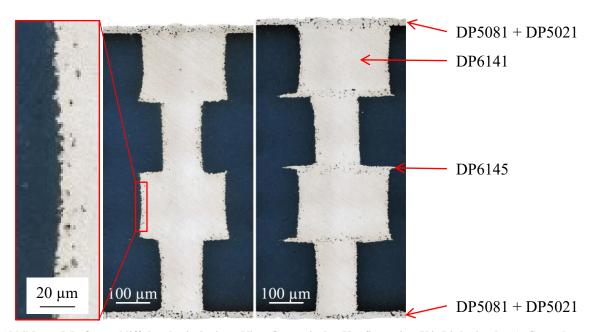

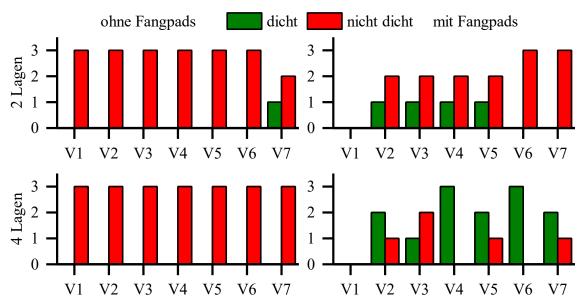

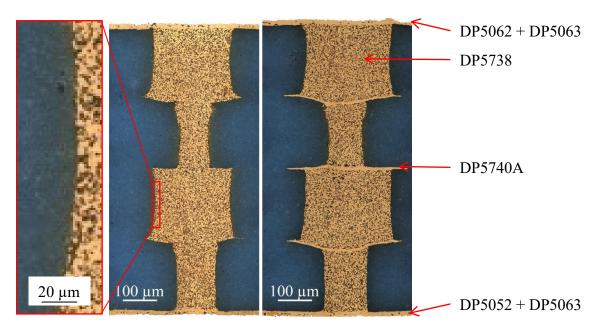

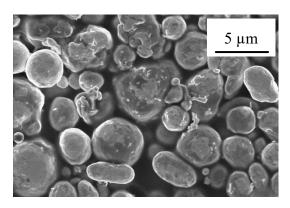

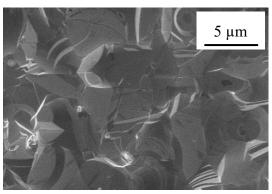

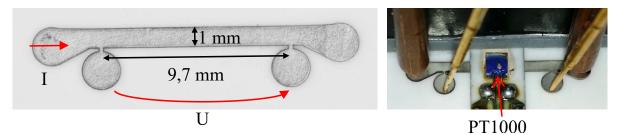

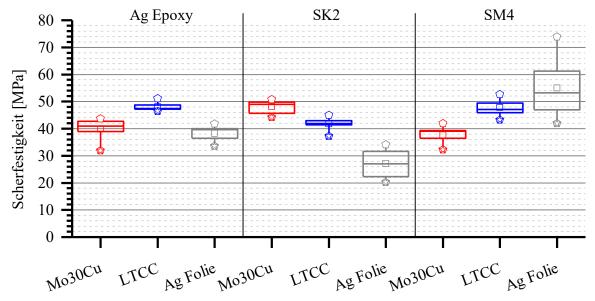

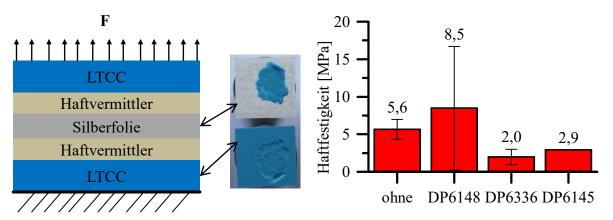

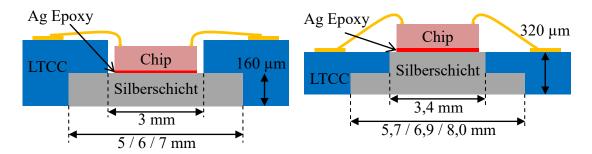

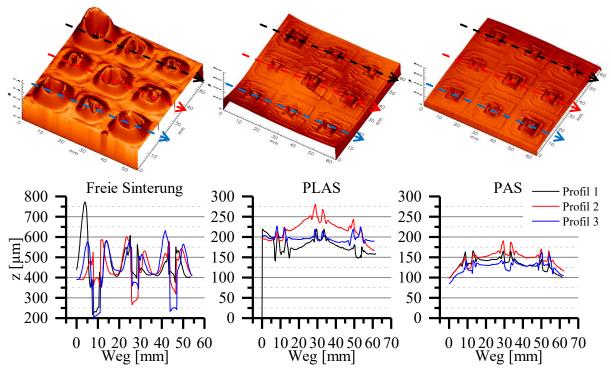

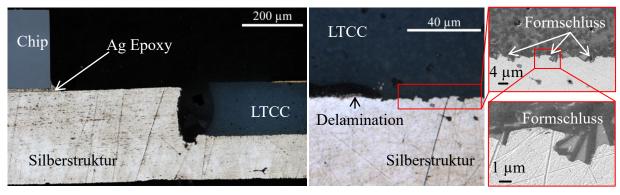

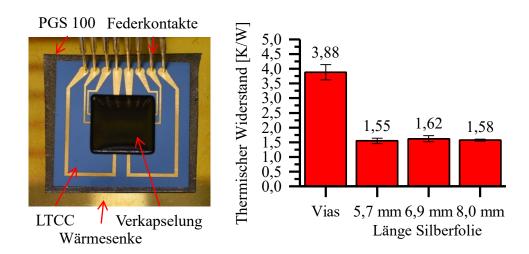

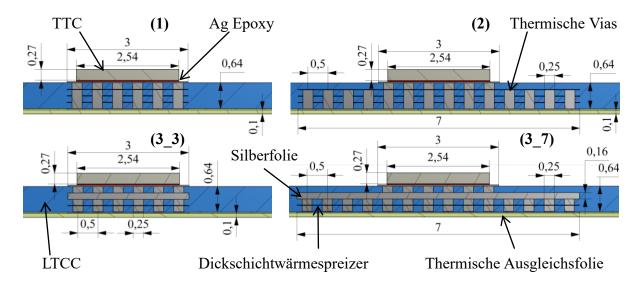

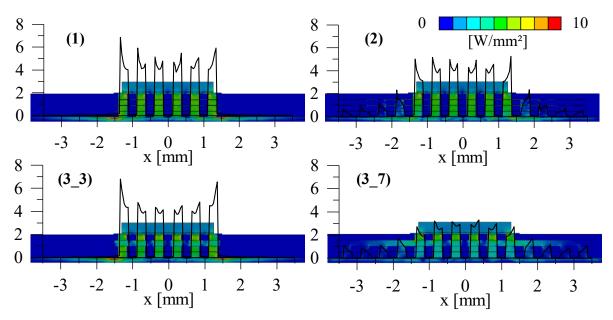

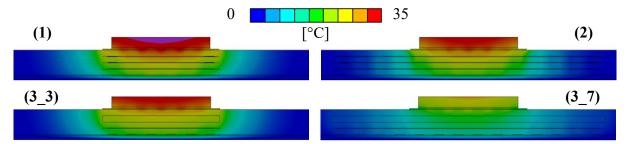

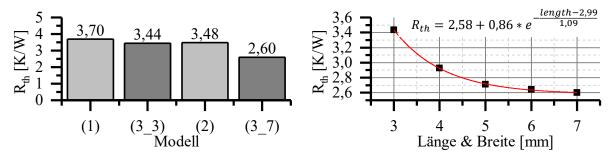

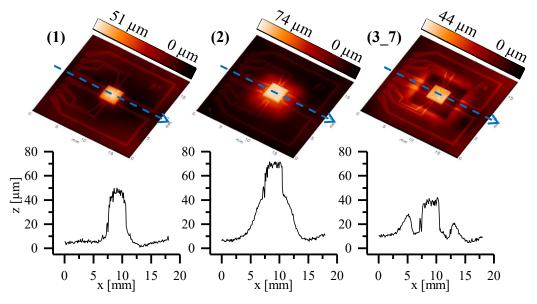

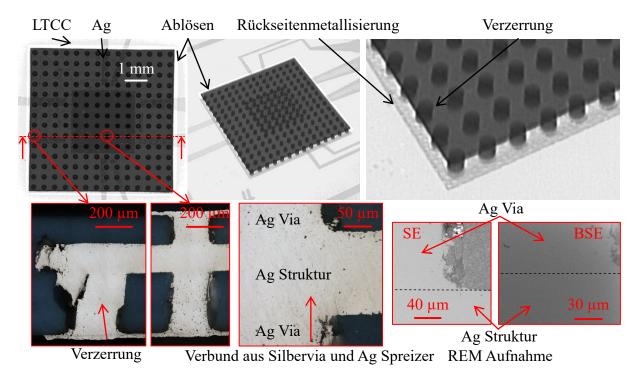

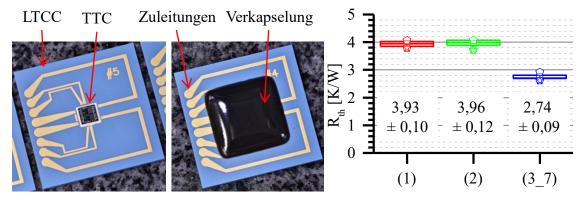

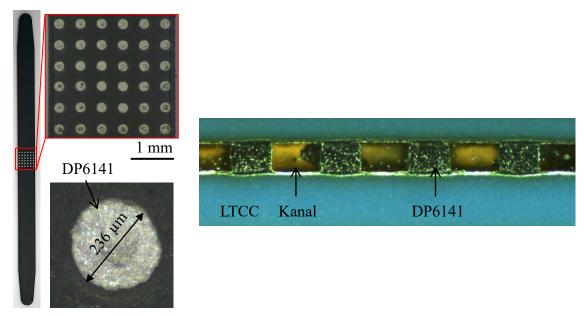

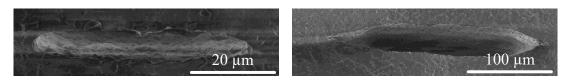

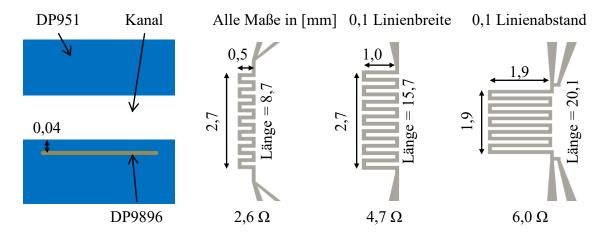

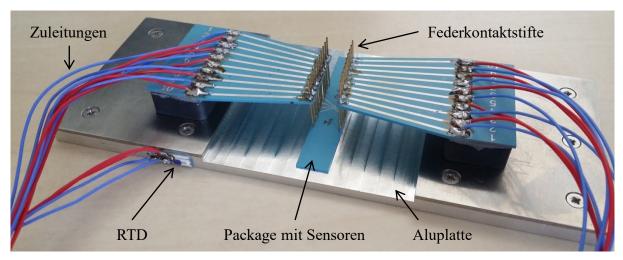

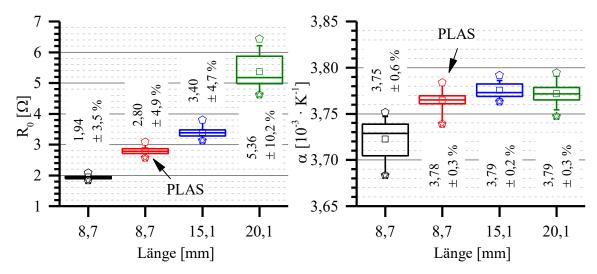

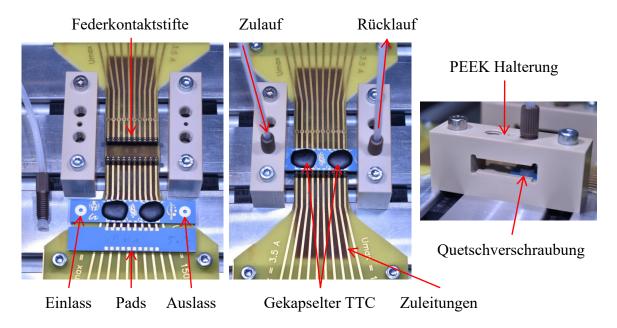

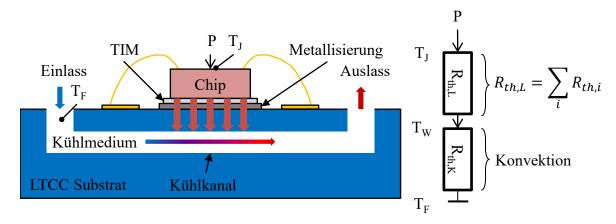

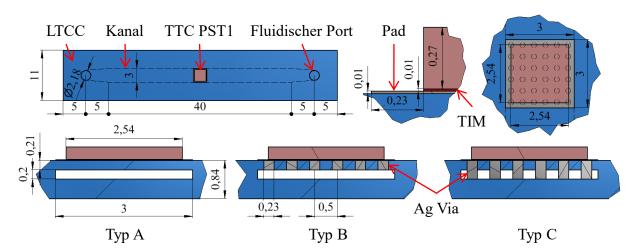

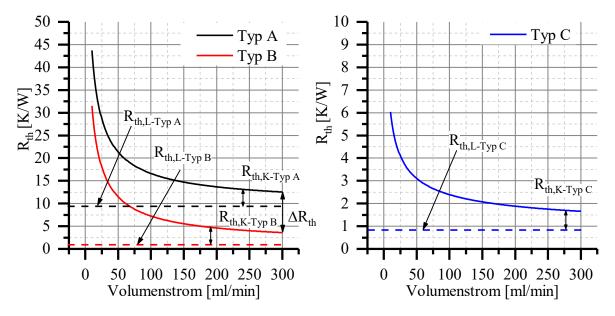

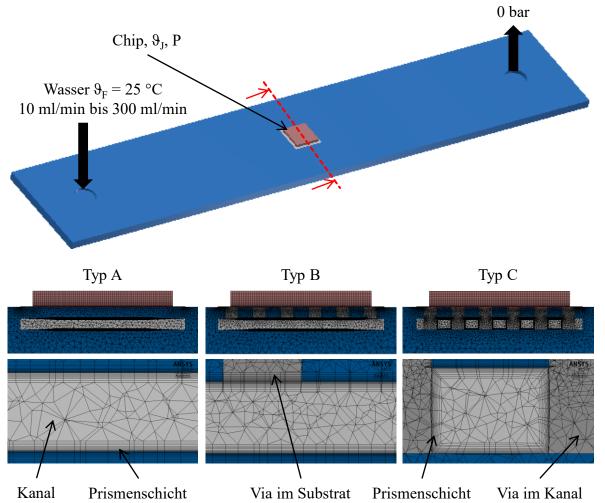

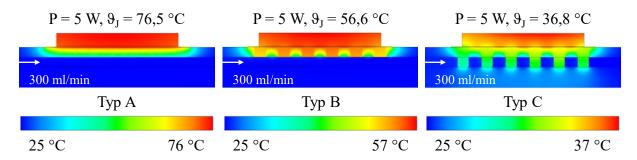

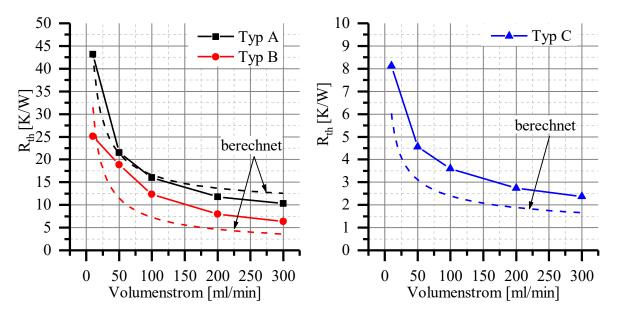

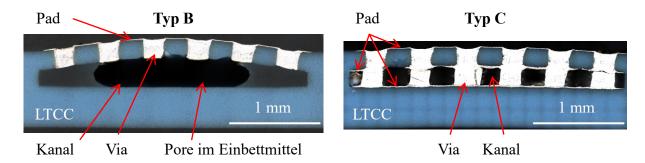

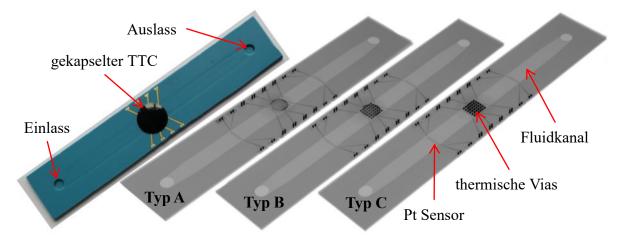

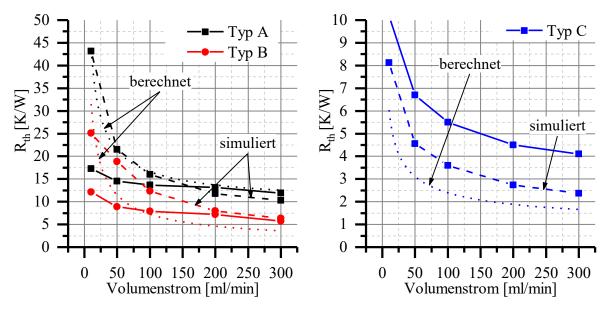

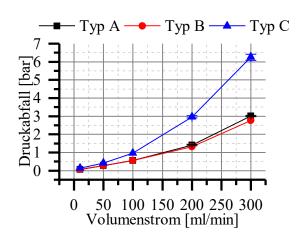

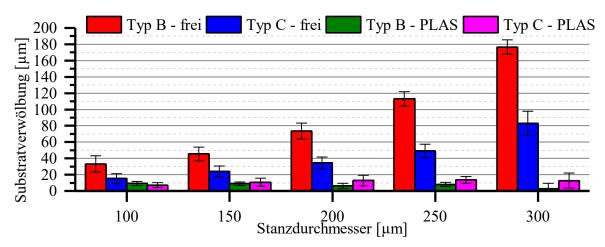

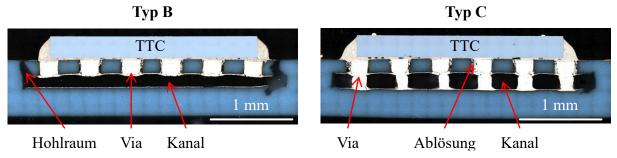

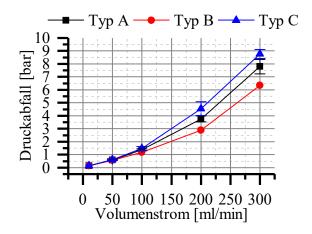

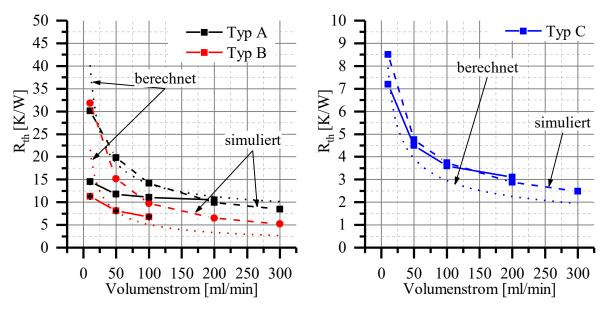

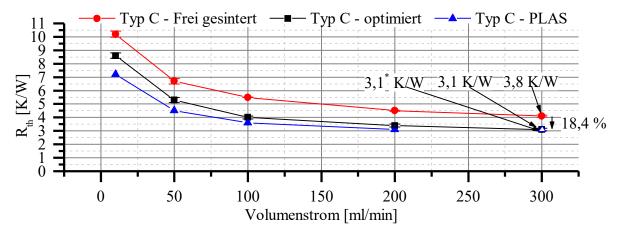

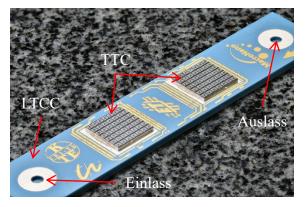

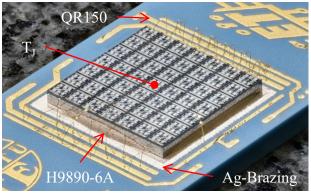

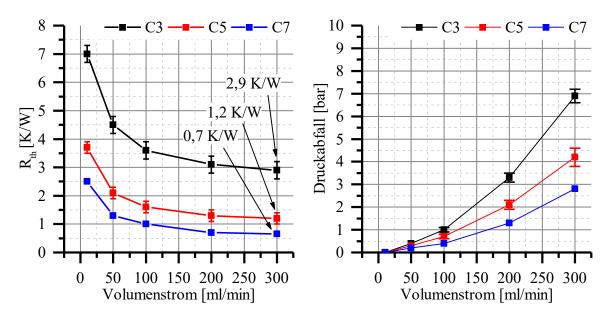

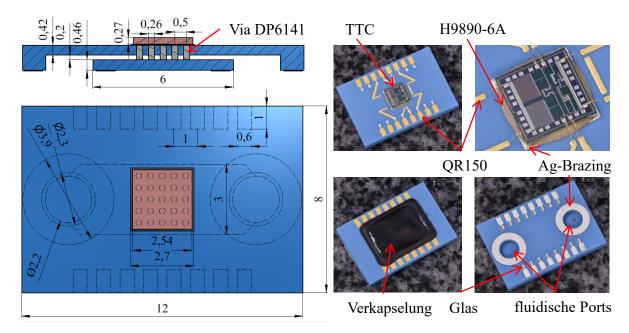

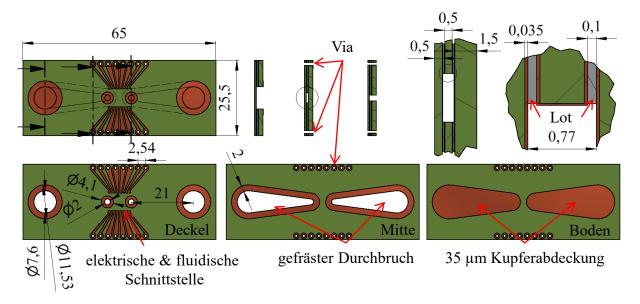

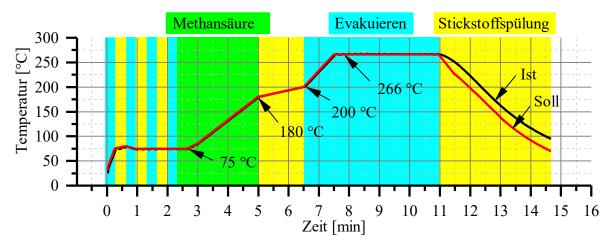

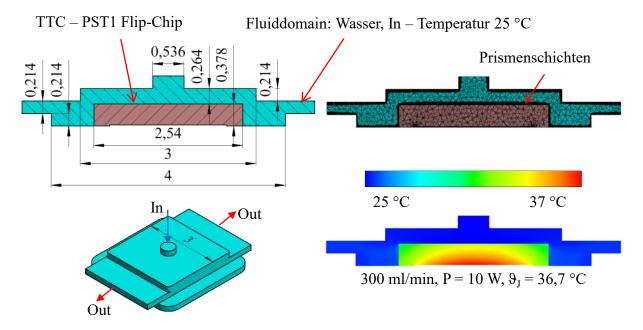

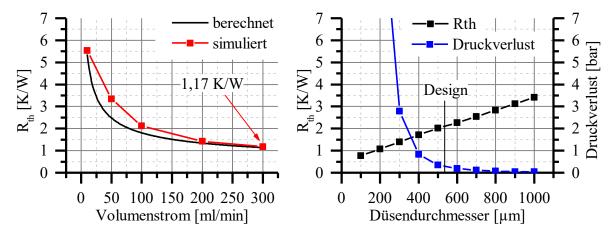

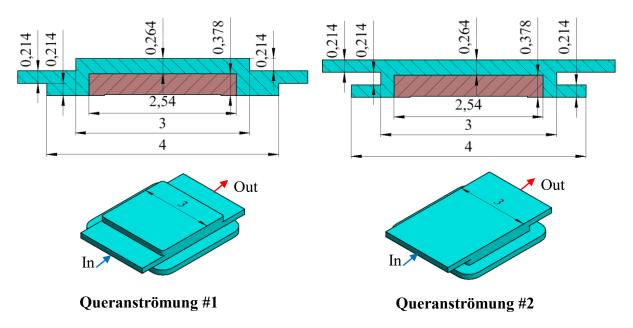

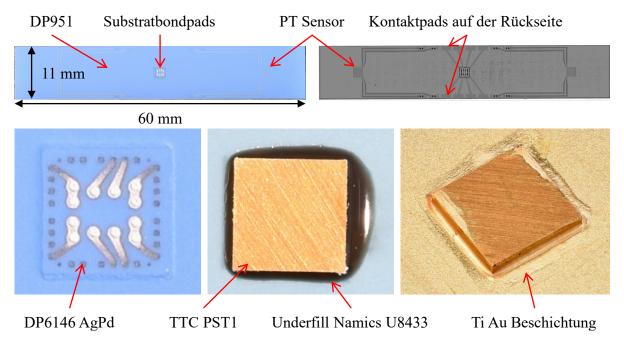

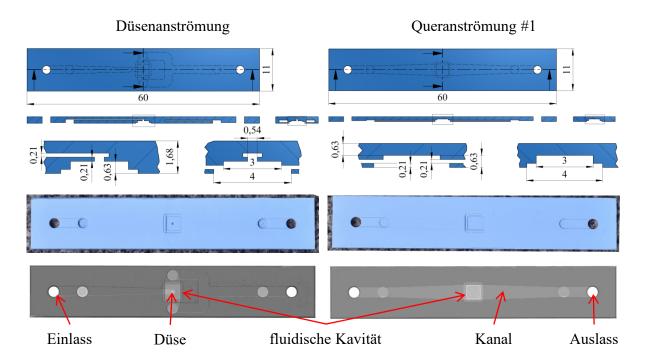

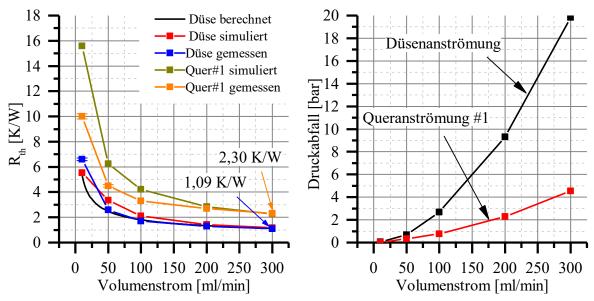

$$-\lambda \cdot \left(T(n_2) - T(n_1)\right) = \frac{\Phi}{A} \cdot (n_2 - n_1) \tag{2.18}$$