# Design, Implementation, and Test of a Tri-Mode Ethernet MAC on an FPGA

by Philipp Kerling

A thesis submitted in partial fulfillment for the degree of Bachelor of Science

at the Technische Universität Ilmenau Department of Electrical Engineering and Information Technology Electronic Measurement Engineering Group

2015-08-31

DOI: 10.22032/dbt.38245 URN:urn:nbn:de:gbv:ilm1-2019200167

### Abstract

Technische Universität Ilmenau Department of Electrical Engineering and Information Technology Electronic Measurement Engineering Group

#### Design, Implementation, and Test of a Tri-Mode Ethernet MAC on an FPGA

by Philipp Kerling

Ethernet is a mature communication technology with a sizable number of advantages for sensor networks and many other use cases. Applications interact with a media access control (MAC) sublayer to get packets from and to the network. This thesis presents the design, implementation, and test of an Ethernet MAC targeted at FPGAs in VHDL. It supports full-duplex interfacing with an Ethernet physical layer integrated circuit via the standard media-independent interface (MII) variants MII and GMII at link speeds of 10, 100, and 1000 Mb/s. In contrast to prior solutions, it is devised primarily with simplicity in mind, both in external usage and in internal operation. Users benefit from the straightforward FIFO interface offered while nevertheless being able to send and receive at almost full Gigabit Ethernet speed. The solution is designed for and verified on a Trenz Electronic GmbH GigaBee micromodule with a Xilinx Spartan-6 family FPGA.

Ethernet ist eine ausgereifte Kommunikationstechnologie mit vielen Vorteilen für Sensornetzwerke und einer Vielzahl anderer Einsatzbereiche. Anwendungen interagieren mit einer sogenannten Media-Access-Control-(MAC)-Unterschicht, um Pakete vom Netzwerk zu empfangen und zu versenden. Diese Arbeit stellt den Entwurf, die Implementierung und den Test einer in VHDL umgesetzten MAC-Schicht für Ethernet auf FPGAs vor. Die Kommunikation mit einem integrierten Schaltkreis, der die Bitübertragungsschicht von Ethernet umsetzt, erfolgt über das standardisierte Media-Independent Interface (MII) in den Varianten MII und GMII. Dabei werden Verbindungsgeschwindigkeiten von 10, 100 und 1000 Mb/s im Vollduplex-Modus unterstützt. Im Gegensatz zu bisherigen Lösungen liegt der Schwerpunkt des Entwurfs auf Einfachheit sowohl in der externen Benutzung als auch den internen Abläufen. Benutzern kommt die unkomplizierte FIFO-Schnittstelle zugute, mit der sie gleichzeitig bei nahezu voller Gigabit-Ethernet-Geschwindigkeit senden und empfangen können. Die MAC-Schicht wurde für ein GigaBee-Mikromodul der Trenz Electronic GmbH mit einem FPGA der Spartan-6-Familie von Xilinx entworfen und ebenfalls damit geprüft.

# Contents

| Ab  | Abstract i                                              |                |                                            |          |  |  |  |

|-----|---------------------------------------------------------|----------------|--------------------------------------------|----------|--|--|--|

| Lis | t of F                                                  | igures         |                                            | iv       |  |  |  |

| Lis | t of T                                                  | ables          |                                            | v        |  |  |  |

| Ab  | brevi                                                   | ations         |                                            | vi       |  |  |  |

| 1   | Intro                                                   | oductio        | n                                          | 1        |  |  |  |

| 2   | Func                                                    | damenta        | als                                        | 4        |  |  |  |

|     | 2.1                                                     | Ethern         | et (IEEE Std 802.3)                        | 4        |  |  |  |

|     |                                                         | 2.1.1          | Overview                                   | 4        |  |  |  |

|     |                                                         | 2.1.2          | Media-independent interface                | 7        |  |  |  |

|     |                                                         | 2.1.3          | Packet/frame structure                     | 9        |  |  |  |

|     | 2.2                                                     |                | are design with FPGAs                      | 11       |  |  |  |

|     |                                                         | 2.2.1          | Components                                 | 11       |  |  |  |

|     |                                                         | 2.2.2<br>2.2.3 | Clocking and metastability                 | 12<br>13 |  |  |  |

|     |                                                         | 2.2.5          |                                            | 15       |  |  |  |

| 3   | State                                                   | e of the       |                                            | 15       |  |  |  |

|     | 3.1                                                     | Existin        | g Ethernet MAC intellectual property cores | 15       |  |  |  |

|     | 3.2                                                     | Hardwa         | are platform                               | 17       |  |  |  |

| 4   | Desi                                                    | gn             |                                            | 19       |  |  |  |

|     | 4.1                                                     | Design         | trade-offs                                 | 19       |  |  |  |

|     | 4.2                                                     | Overvie        | ew                                         | 21       |  |  |  |

|     | 4.3                                                     | Compo          | nents                                      | 23       |  |  |  |

|     |                                                         | 4.3.1          | FIFOs                                      | 23       |  |  |  |

|     |                                                         | 4.3.2          | Framing                                    | 26       |  |  |  |

|     |                                                         | 4.3.3          | Media-independent interface                | 27       |  |  |  |

|     |                                                         | 4.3.4          | Media-independent interface input/output   | 28       |  |  |  |

|     |                                                         | 4.3.5          | Media-independent interface management     | 28       |  |  |  |

|     | 4.3.6 Media-independent interface management control 28 |                |                                            |          |  |  |  |

#### 5 Implementation

29

|        | 5.1         | (Gigabit) media-independent interface input/output | 29              |

|--------|-------------|----------------------------------------------------|-----------------|

|        |             | 5.1.1 Transmission                                 | 30              |

|        |             | 5.1.2 Reception                                    | 32              |

|        | 5.2         | Transmit FIFO                                      | 36              |

|        | 5.3         | Receive FIFO                                       | 37              |

|        | 5.4         | Frame check sequence calculation                   | 40              |

| 6      | Test        | and Results                                        | 42              |

|        | 6.1         | Functional verification                            | 42              |

|        | 6.2         | Benchmark                                          | 45              |

|        | 6.3         | Example application                                | 47              |

|        | 6.4         | FPGA resource and code statistics                  | 48              |

| 7      | Cond        | clusion                                            | 49              |

|        |             |                                                    |                 |

| A      | Timi        | ing Diagrams                                       | 52              |

| A      | Timi<br>A.1 | <b>ing Diagrams</b><br>Transmission                | <b>52</b><br>52 |

| A      |             |                                                    |                 |

| A<br>B | A.1<br>A.2  | Transmission                                       | 52              |

# List of Figures

| 2.1        | IEEE 802.3 simplified layer architecture in relation to the OSI reference model    | 5       |

|------------|------------------------------------------------------------------------------------|---------|

| 2.2<br>2.3 | Signals used by MII and GMII in full-duplex operation                              | 8<br>12 |

| 3.1        | Timing diagram of the OpenCores ethernet_tri_mode IP core RX user interface        | 16      |

| 3.2        | Trenz Electronic TE0603 baseboard with a GigaBee XC6SLX series module              | 10      |

|            | mounted on top                                                                     | 18      |

| 4.1        | Block diagram of the Ethernet MAC presented in this thesis                         | 22      |

| 4.2        | Ethernet simplified layer architecture in relation to the MAC implementation       |         |

| 4.3        | presented in this thesis                                                           | 24      |

| 4.5        | interface                                                                          | 25      |

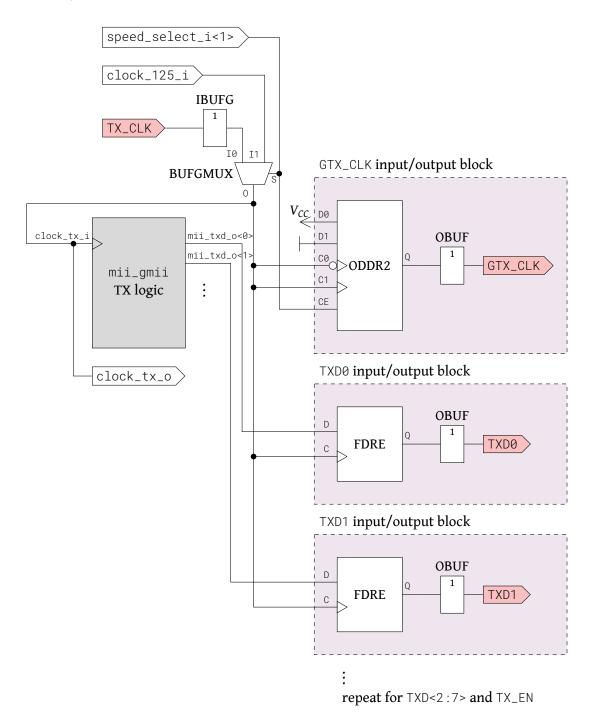

| 5.1        | Structure of the transmission part of mii_gmii_io on Spartan-6 family FPGAs        | 30      |

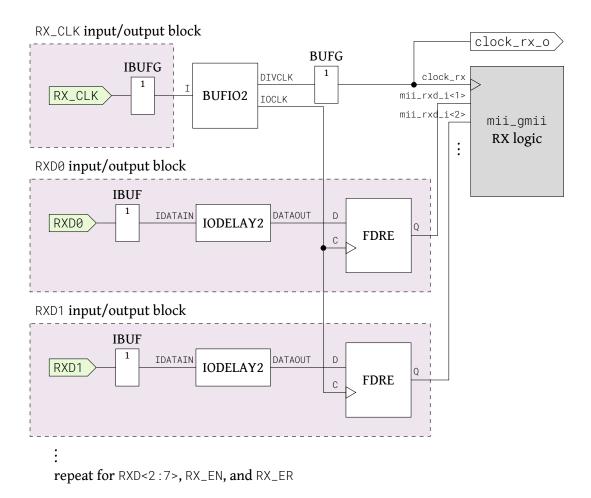

| 5.2        | Structure of the reception part of mii_gmii_io on Spartan-6 family FPGAs $\ . \ .$ | 35      |

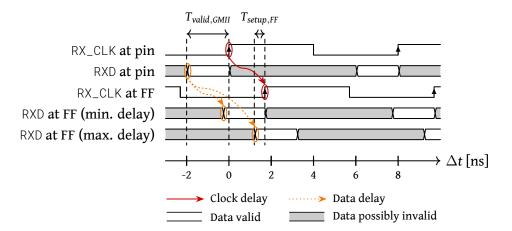

| 5.3        | Delay of clock and data signals on the GMII receive side at minimum clock          |         |

|            | delay                                                                              | 36      |

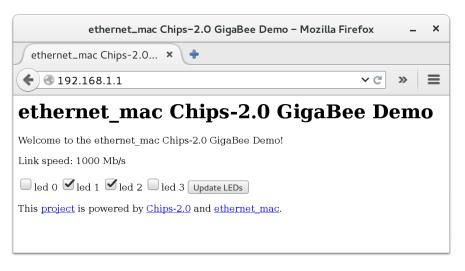

| 6.1        | Index page of the modified Chips webserver demo project using the MAC sub-         |         |

|            | layer presented in this thesis                                                     | 48      |

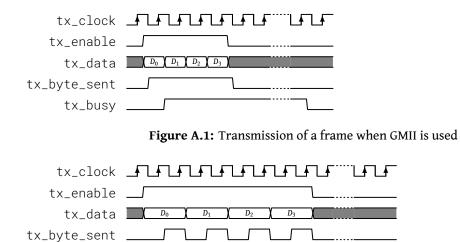

| A.1        | Transmission of a frame when GMII is used                                          | 52      |

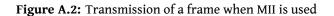

| A.2        | Transmission of a frame when MII is used                                           | 52      |

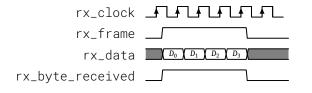

| A.3        | Reception of a frame when GMII is used                                             | 53      |

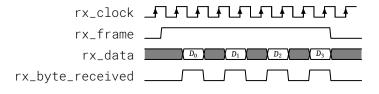

| A.4        | Reception of a frame when MII is used                                              | 53      |

# List of Tables

| 2.1 | Comparison of MII specifications                     | 7  |

|-----|------------------------------------------------------|----|

| 4.1 | Ports of the framing entity                          | 27 |

|     | Results of the MAC loopback benchmark                | 46 |

| 0.2 | on the Xilinx Spartan-6 family FPGA XC6SLX45-2FGG484 | 48 |

# Abbreviations

| CRC     | <b>c</b> yclic <b>r</b> edundancy <b>c</b> heck              |  |  |  |

|---------|--------------------------------------------------------------|--|--|--|

| CSMA/CD | carrier sense multiple access with collission detection      |  |  |  |

| DCM     | digital clock manager                                        |  |  |  |

| DDR     | double data rate                                             |  |  |  |

| DRAM    | <b>d</b> ynamic <b>r</b> andom <b>a</b> ccess <b>m</b> emory |  |  |  |

| FCS     | frame check sequence                                         |  |  |  |

| FF      | flip-flop                                                    |  |  |  |

| FIFO    | first-in-first-out                                           |  |  |  |

| FPGA    | field <b>p</b> rogrammable <b>g</b> ate <b>a</b> rray        |  |  |  |

| FWFT    | first-word fall-through                                      |  |  |  |

| GMII    | gigabit media-independent interface                          |  |  |  |

| HDL     | hardware description language                                |  |  |  |

| HTTP    | Hypertext Transfer Protocol                                  |  |  |  |

| IC      | integrated circuit                                           |  |  |  |

| IEEE    | Institute of Electrical and Electronics Engineers            |  |  |  |

| 10, I/O | input/output                                                 |  |  |  |

| ЮВ      | input/output block                                           |  |  |  |

| IP      | intellectual <b>p</b> roperty                                |  |  |  |

| IP      | Internet Protocol                                            |  |  |  |

| IPG     | interpacket gap                                              |  |  |  |

| ISO     | International Organization for Standardization               |  |  |  |

| LAN     | local <b>a</b> rea <b>n</b> etwork                           |  |  |  |

| LLC     | logical link control                                         |  |  |  |

| LSB     | least significant byte                                       |  |  |  |

| LUT     | look- <b>u</b> p <b>t</b> able                               |  |  |  |

| МАС       | media access control                                             |

|-----------|------------------------------------------------------------------|

| MAN       | <b>m</b> etropolitan <b>a</b> rea <b>n</b> etwork                |

| MII       | media-independent interface                                      |

| MIIM      | media-independent interface management                           |

| MSB       | <b>m</b> ost <b>s</b> ignificant <b>b</b> yte                    |

| OSI       | Open Systems Interconnection                                     |

| РНҮ       | <b>phy</b> sical (layer)                                         |

| PLD       | <b>p</b> rogrammable logic <b>d</b> evice                        |

| PLL       | phase-locked loop                                                |

| RAM       | random access memory                                             |

| RGMII     | reduced gigabit media-independent interface                      |

| RS        | <b>r</b> econciliation <b>s</b> ublayer                          |

| RTBI      | reduced pin count ten-bit interface                              |

| RX        | receive, reception                                               |

| SDR       | single <b>d</b> ata <b>r</b> ate                                 |

| SGMII     | serial gigabit media-independent interface                       |

| ТВІ       | ten-bit interface                                                |

| тср       | Transmission Control Protocol                                    |

| ТХ        | transmit, transmission                                           |

| UDP       | User Datagram Protocol                                           |

| USB       | Universal Serial Bus                                             |

| VHDL      | see VHSIC HDL                                                    |

| VHSIC HDL | Very High Speed Integrated Circuit Hardware Description Language |

|           |                                                                  |

### Chapter 1

## Introduction

Modern electronic sensors are very sophisticated pieces of equipment that can, among other things, improve the safety and security of human beings. The Electronic Measurement Engineering Group at Technische Universität Ilmenau has been researching the use of a not yet widely used radio sensor technology called ultra-wideband for a wide range of applications such as breast cancer detection [1], buried weapon detection [2], or vitality monitoring of senior citizens [3], with promising results.

In the latter use case described by Sachs and Herrmann, a network of ultra-wideband radar sensors monitors apartments of elderly people and aims to automatically detect when they e.g. fall over or exhibit anomalous breathing behavior. In contrast to previous solutions, the system provides data continuously and can operate without interaction with the subject, greatly improving practical usability in many dangerous situations.

The measurements from multiple sensors are fed into a central assistance system running on a personal computer that combines and interprets the individual sensor values, necessitating a feasible method of data exchange. The Electronic Measurement Engineering Group currently uses universal serial bus (USB) version 2.0 technology for this purpose, but has encountered considerable limitations with this approach. Most importantly, the maximum cable length (without signal repeaters) of 5 m [4] is impractical for devices distributed throughout e.g. an apartment and even though the standard allows for a maximum of 127 devices on one bus, performance problems were encountered when connecting several sensors.

It is desirable to replace USB with another standard connection technology that does not exhibit these problems, scales better to a higher number of sensor devices, and, at the same time, does not lower other factors such as the data rate below what is achievable with USB 2.0. The well-known Ethernet technologies for local area networks [5] provide for all of that. To be specific, they allow for cable lengths of up to 100 m at a data rate of 1000 Mb/s,

even higher than the 480 Mb/s signaling rate of USB 2.0. Ethernet is also a very mature technology, making related equipment available at low prices. As more than 95 percent of all wired local area networks already use it [6], measuring devices can be easily integrated there. The downside of this is that the implementation of standard protocols running on top of Ethernet such as the Internet Protocol is quite complex. Contrary to USB where integrated circuits providing the whole protocol stack such as the popular FX2 family by Cypress Semiconductor Corp. [7] exist, similar products for Ethernet are rare.

The preprocessing of sensor data is currently performed by field-programmable gate arrays (FPGAs), a special type of programmable circuits, on commercial off-the-shelf circuit boards. To not incur any additional cost, the FPGAs should take care of as much of the Ethernet communication process as possible. They can indeed handle at least part of it by addressing nodes on the network and encapsulating data into transmission units (packets). The other part consists of processing and generating the physical signals on the cable. Most FPGAs do not have the capability to perform this function, but special integrated circuits exist for this purpose. Communication with this circuit and the aforementioned packet encapsulation is the responsibility of a media access control (MAC) layer.

The goal of the present thesis is to design, implement, and test an Ethernet MAC on an FPGA that can then be used in ultra-wideband and other sensor devices to communicate with a central data capture and processing entity. The TE0600 FPGA board manufactured by Trenz Electronic GmbH [8] is used as primary target platform for implementation and verification purposes. It already includes an Ethernet physical layer chip. To maximize the suitability of the design for the UWB sensor network, it should:

- be easy to use, i.e. have a generic and familiar interface,

- be easy to understand and maintain (this also requires the source code to be readily available),

- be available free of charge,

- support the most common Ethernet link speeds of 10, 100, and 1000 Mb/s,

- be able to receive and transmit data at a rate very close to the maximum allowed by the Ethernet standard,

- communicate with a physical layer integrated circuit (IC) using the standard mediaindependent interface, and

- work on the TE0600 board, but also be designed with low-effort portability to other boards and FPGAs in mind.

Within the goals outlined above, portability to other FPGAs is considered secondary.

In contrast, objectives that are not the focus of the present thesis include:

- minimizing the FPGA resources used,

- supporting all possible Ethernet features such as flow control, multicast reception, and half-duplex connections, and

- implementing protocols on top of Ethernet.

For developing hardware structures for programmable logic devices, it needs to be possible to describe the functionality of digital electronic circuits using a formalized language. Every language that is primarily intended not for software development but this purpose is called a hardware description language (HDL). The two main competitors in this field are Verilog-HDL and Very High Speed Integrated Circuits Hardware Description Language (VHSIC HDL or VHDL) [9]. Only VHDL revision VHDL-93<sup>1</sup> as standardized in [10] will be considered for this MAC implementation. An explanation of the language is outside the scope of this thesis, so the reader is assumed to be familiar with at least the basic concepts of VHDL. A practically oriented introduction to the language offers Kafig, for instance, in [11], while a thorough discussion of all aspects can be found in "The Designer's Guide to VHDL" [12] by Ashenden.

In the present thesis, Chapter 2 will first of all introduce the primary technologies required, Ethernet and FPGAs, in more detail. We will then discuss prior implementations of Ethernet MACs on FPGAs and study the target hardware in Chapter 3, concluding the preliminary considerations. The next topic in Chapter 4 is the design of the MAC including an examination of the trade-offs that were made, followed by its implementation in Chapter 5. There, attention is drawn to a few points of special relevance to the core and the goals of this thesis. Chapter 6 shows how and with what results the functionality was tested before the presentation of the MAC sublayer ends in Chapter 7 with a resume of what was achieved and where to go from there.

<sup>&</sup>lt;sup>1</sup>VHDL-93 will be used because tool support for the more modern VHDL-2008, which allows for simpler constructs in many cases and would in theory be preferable, is still very limited.

### Chapter 2

## Fundamentals

First, we take a look at the Ethernet technologies for use in local and metropolitan area networks (LANs and MANs). They form the very foundation of the work presented in this thesis. The other building block is programmable hardware, introduced in the section directly following.

#### 2.1 Ethernet (IEEE Std 802.3)

The Ethernet family of technologies was standardized by the IEEE as IEEE Std 802.3<sup>™</sup> for the first time in 1983 [13] describing half-duplex communication over copper wire at a maximum data rate of 10 Mb/s. Since then, a lot of additional features have been added, including full-duplex operation and higher data rates of first 100 Mb/s (referred to as Fast Ethernet), then 1000 Mb/s (referred to as Gigabit Ethernet) and most recently up to 100 Gb/s, an astounding increase by four orders of magnitude. This has allowed Ethernet to become the dominant technology used in computer LANs worldwide: more than 95 percent of all wired local area networks use it [6]. The latest revision as of the writing of this thesis is IEEE Std 802.3-2012 [5], published 2012-12-28. All further references to the standard pertain to this revision.

#### 2.1.1 Overview

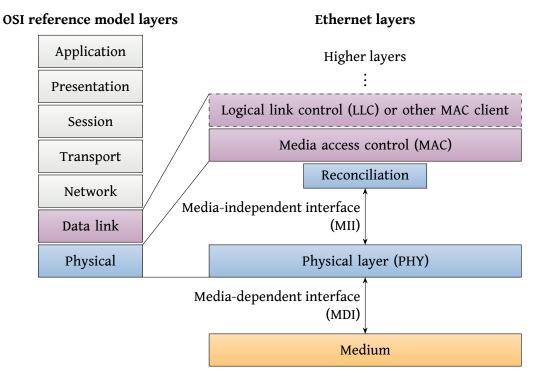

A layered architecture is described in the document which, at a high level of abstraction, differentiates between the physical layer (PHY) and the media access control (MAC) sublayer. The main responsibility of the physical layer is to transmit arbitrary opaque data over a physical medium while the media access control has to take care of encapsulating the payload into valid Ethernet frames, addressing nodes on the network, and error detection. This is intentionally very similar to the lower layers of the ISO Open Systems Interconnection model (OSI model, ISO/IEC 7498-1 [14]) which describes communication as interaction of abstract layers with well-defined responsibilities as shown in Figure 2.1. Layers communicate only with the layers directly above and below them. As long as the interfaces are compatible, the implementation of a layer can be freely exchanged with another one. The Ethernet PHY layer directly corresponds to the physical layer of the OSI model while the MAC sublayer together with the logical link control (LLC) sublayer form the OSI data link layer. The LLC sublayer (shown with dashed border in the figure) is not mandatory and not specified in IEEE Std 802.3.

Within the context of the standard, the operation of the MAC sublayer is always identical no matter what physical layer is used. Conceptually, it can only send and receive single bits, which makes an additional reconciliation sublayer located between the MAC sublayer and the physical layer necessary. Its only purpose is to translate this very generic interface to the media-independent interface (MII) accepted by a given physical layer. It is called mediaindependent because although it depends on the PHY implementation, usually all specified PHY variants that support the same transmission speed use the same MII. The interface between the physical layer and the physical medium is called media-dependent interface (MDI) accordingly. Throughout this thesis, the acronym PHY will be used not only to refer to the layer but also a device that implements Ethernet physical layer functionality.

**Figure 2.1:** IEEE 802.3 simplified layer architecture in relation to the OSI reference model. Adopted from [5, fig. 1-1].

The higher layers are usually comprised of members of the Internet protocol suite: the Internet Protocol (IP) for the network layer, the Transmission Control Protocol (TCP) or the User Datagram Protocol (UDP) for the transport layer, and arbitrary session, presentation, and application layer protocols such as the Hypertext Transfer Protocol (HTTP). As this thesis focuses on the data link layer, we will not discuss them further.

Of all physical layer technologies stated in IEEE Std 802.3, the ones most commonly used today are 100BASE-TX with a data rate of 100 Mb/s and 1000BASE-T with a data rate of 1000 Mb/s on copper wires [6]. The 10 Mb/s transmission that has initially spawned the Ethernet standardization is preserved under the name 10BASE-T but is not in wide usage any more. Since 10BASE-T, 100BASE-TX, and 1000BASE-T all share a shielded twisted pair copper wire as defined in the standard TIA/EIA-568-A as their physical medium, it is common for network devices to support multiple standards. A backwards-compatible auto-negotiation procedure is in place that ensures that link partners establish a connection at the fastest possible mode.

Although half-duplex operation with multiple devices on a shared bus was the initially predominant form of Ethernet setups, full-duplex operation has replaced it in most installations. It is safe to assume that Gigabit Ethernet is not practically used in half-duplex mode at all [6]. Using the same line for multiple nodes means that collisions are bound to occur when more than one node tries to access the shared medium at the same point in time. A complicated procedure called carrier sense multiple access with collision detection (CSMA/CD) is used in Ethernet to resolve such situations by detecting that a collision has occurred and retrying the transmission after a random amount of time [6]. In contrast, full-duplex Ethernet mandates that all connections are point-to-point with exactly two devices on the link where collisions are physically impossible. Central switches with multiple ports connect the nodes to form a network and replace the outdated bus topology. Larger commercially available switches usually have around 50 ports but can of course also be connected again to other switches. The benefit of this architecture is vastly improved performance both between two nodes and in the network as a whole. In full-duplex operation, almost the full 1000 Mb/s 1000BASE-T transmission speed can be achieved in each direction between two nodes transmitting to each other simultaneously. Using a single switch port per device also allows a different physical layer and thus data rate to be used for each node [5]. This is crucial as not all network participants may support the same and newest Ethernet technology.

#### 2.1.2 Media-independent interface

Since the goal of this thesis is to implement a media access control sublayer for Ethernet, the media-independent interface situated between the MAC and the physical layer is of special importance. If the MAC is separate from the PHY, the latter is usually implemented as an integrated circuit (IC) connected to the MAC unit via electrical wires on a printed circuit board. The electrical, signal timing, and signal functional characteristics of this connection are defined in the MII specifications.

A lot of different MII variants have been proposed both directly in IEEE Std 802.3 and by the telecommunication industry. They differ in their required number of signal lines, supported data rates, and interface clock speeds. An overview of the most important ones is provided in Table 2.1. Link speeds refer to the supported data rates on the physical layer while clock rate designates the maximum speed of the MII clock. Furthermore, double data rate (DDR) indicates transmission of data on both clock edges [15], thereby doubling the interface data rate but imposing stricter timing constraints on both sides. Using only one clock edge, in contrast, is called single data rate (SDR). All MIIs that do not use DDR transmit data on the rising clock edge only.

In order to support all common data rates of 10, 100, and 1000 Mb/s, either a single MII that supports all speeds such as RGMII or SGMII can be used, or switching between different MIIs that in sum can handle all cases such as MII plus GMII is necessary. The latter two interface variants are explained below in more detail.

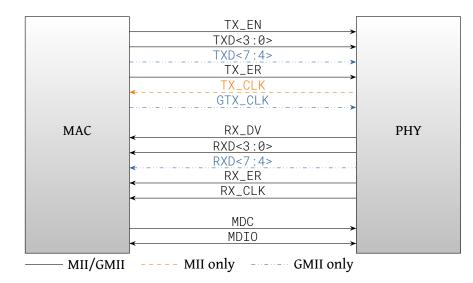

**Media-independent interface (MII)** (without any prefix) is the oldest of all mentioned variants and was specified for the Fast Ethernet family (100 Mb/s), but also supports operation at 10 Mb/s link speed. It offers full-duplex operation through completely separate data paths for receiving and transmitting data. The data buses called TXD and RXD are 4 bit wide each and synchronous to the rising edge of their respective clock TX\_CLK and RX\_CLK. The detailed timing characteristics are given in clause 22.3 of [5]. Both the RX and TX path clock

| Name  | # Pins | Link speeds [Mb/s] | Clock rate | DDR | Source           |

|-------|--------|--------------------|------------|-----|------------------|

| MII   | 16     | 10, 100            | 25 MHz     | No  | [5, clause 22]   |

| RMII  | 8      | 10, 100            | 50 MHz     | No  | [16]             |

| GMII  | 24     | 1000               | 125 MHz    | No  | [5, clause 35]   |

| SGMII | 4      | 10, 100, 1000      | 625 MHz    | Yes | [17]             |

| RGMII | 12     | 10, 100, 1000      | 125 MHz    | Yes | [18]             |

| TBI   | 24     | 1000               | 125 MHz    | No  | [5, clause 36.3] |

| Table 2.1: ( | Comparison | of MII s | pecifications |

|--------------|------------|----------|---------------|

|--------------|------------|----------|---------------|

MII: Media-independent Interface, RMII: Reduced media-independent interface, GMII: Gigabit mediaindependent interface, SGMII: Serial gigabit media-independent interface, RGMII: Reduced gigabit mediaindependent interface, TBI: Ten-bit interface. is sourced by the PHY. It has a frequency of 25 MHz at 100 Mb/s operation and 2.5 MHz at 10 Mb/s operation. Additionally, there are control signals for transmission error (TX\_ER, RX\_ER) and data validity indication (TX\_EN, RX\_DV) per direction as well as carrier sense and collision detection signals needed for CSMA/CD in half-duplex link modes. Lastly, the out-of-band MII management interface (MIIM) is included for exchanging configuration and status data with the PHY. It is a simple serial interface comprised of two wires with the clock signal MDC always provided by the MAC and the data signal MDIO by either entity as needed. A basic vendor-independent register set that every PHY that claims to support MII has to implement is given in Table 22-6 of the Ethernet standard [5]. It offers functionality for e.g. detecting whether a link has been established, perform a reset, or manually configure the link parameters speed and duplex mode. The current auto-negotiated link speed can be read indirectly by querying the capabilities of the link partner and choosing the fastest supported speed.

**Gigabit media-independent interface (GMII)** is the name of the MII variant for the Gigabit Ethernet family and can be seen mostly as an extension to the original Fast Ethernet MII. The data bus width is doubled to 8 bits and the clock rate quintupled to 125 MHz to account for the tenfold increase in data rate from 100 Mb/s to 1000 Mb/s. This means that timing margins are a lot smaller: the window during which data is guaranteed to be valid at the receiver is shortened from 20 ns with MII to 2 ns per clock cycle. For the TX path, the clock is now called GTX\_CLK and provided by the MAC instead of the PHY because wire propagation and processing delays at the MAC would make it difficult to achieve correct timing otherwise. This is called source-synchronous clocking [19]. The interface is otherwise functionally identical for normal data transfer and management. As can be seen in Figure 2.2 which provides an overview of signal connections needed, many pins can be shared in devices supporting both MII and GMII. There are three groups, from top to bottom: transmit direction

**Figure 2.2:** Signals used by MII and GMII in full-duplex operation. Adopted from [5, fig. 22-3] and [5, fig. 35-2].

signals synchronous to TX\_CLK (in 10/100 Mb/s mode) or GTX\_CLK (in 1000 Mb/s mode), receive direction signals synchronous to RX\_CLK, and the management signal synchronous to MDC. Even when the TX data lines are shared between both variants, their differing clock structure complicates the clock distribution and data output architecture in MACs.

#### 2.1.3 Packet/frame structure

As we have already discussed, the same conceptual media access control sublayer is used for all Ethernet variants. This also means that the Ethernet packet and MAC frame formats are identical no matter which transmission technology or speed is used, greatly simplifying devices that have to deal with more than one possible combination [6]. In the context of IEEE Std 802.3, a MAC frame contains all control and data information and an Ethernet packet "consists of a MAC frame [...] preceded by the Preamble and the Start Frame Delimiter" [5, clause 1.4.299]. These two added header fields have a combined length of 8 byte in total and their only purpose is synchronization at the physical layer [6]. When transmitting or receiving data, the full Ethernet packet is put on the media-independent interface sequentially. In the following chapters of this thesis, the general term packet (as opposed to Ethernet packet) will be used to denote MAC frames.

Besides the actual client data, the MAC frame contains the destination address, source address, a 2-byte length/type field that contains *either* the length of the frame *or* a MAC client protocol type indication exclusively, optional padding, and the 4-byte frame check sequence (FCS). Every Ethernet network interface controller has its own globally unique address with a length of 6 bytes. The FCS is a checksum calculated over the whole MAC frame minus the FCS itself according to a standard algorithm called cyclic redundancy check (CRC) defined in [5, clause 3.2.9]. Many common transmission errors at the physical layer like single flipped bits or sequences of corrupted bits can be detected with this checksum [20]. A general explanation of CRC calculation can be found e.g. from Halsall [21].

The achievable total performance of Ethernet is limited by the overhead introduced through the preamble and the interpacket gap (IPG) which requires a minimum duration of 96 bit times without activity after every packet transmitted. The maximum size of a normal Ethernet frame is 1518 bytes, but shorter frames are permitted down to a minimum of 64 bytes. When the payload is very short, the frame has to be padded to meet the requirement. As the overhead occurs per packet, data rate is at maximum when a lot of client data is transmitted in each one and at minimum when only short frames are sent. To illustrate the vast difference, we compare the achievable user data rate at 1 Gb/s link speed for both extremes. The static amount of bytes added by headers and the FCS in every MAC frame  $n_{Overhead, frame}$  is

$$n_{Overhead,frame} = 2n_{Address} + n_{Length/type} + n_{FCS}$$

= 2 · 6 + 2 + 4

= 18,

where  $n_x$  is the number of bytes needed for header element x, respectively. The only dynamic length field is the padding which has a byte length of

$$egin{aligned} n_{Padding} &= \max\{0, n_{Min.framesize} - n_{Overhead,frame} - n_{Data}\} \ &= \max\{0, 64 - 18 - n_{Data}\} \ &= \max\{0, 46 - n_{Data}\} \end{aligned}$$

depending on  $n_{Data}$ . Combined with the Ethernet packet preamble and the IPG they form the total amount of overhead bytes per packet  $n_{Overhead}$  as follows:

$$egin{aligned} n_{Overhead} &= n_{Preamble} + n_{SFD} + n_{Overhead,frame} + n_{Padding} + n_{IPG} \ &= 7 + 1 + 18 + \max\{0, 46 - n_{Data}\} + 12 \ &= 38 + \max\{0, 46 - n_{Data}\}. \end{aligned}$$

The achievable user data rate  $r(n_{Data})$  in the case of a continuous Gigabit Ethernet transmission of packets with  $n_{Data}$  bytes of payload is then

$$r(n_{Data}) = \frac{n_{Data}}{n_{Data} + n_{Overhead}} \cdot 1 \, \text{Gb/s} = \frac{n_{Data}}{n_{Data} + 38 + \max\{0, 46 - n_{Data}\}} \cdot 1 \, \text{Gb/s}.$$

Substituting one as the minimum number of bytes for  $n_{Data}$ , we get

$$r(1) = rac{1}{1+38+45} \, \mathrm{Gb/s} = rac{1}{84} \, \mathrm{Gb/s} pprox 11.9 \, \mathrm{Mb/s}.$$

In contrast, the maximum number of payload bytes is the maximum frame size of 1518 bytes minus  $n_{Overhead, frame}$ , resulting in 1500 bytes. The user data rate is then

$$r(1500) = rac{1500}{1500 + 38} \, \mathrm{Gb/s} = rac{1500}{1538} \, \mathrm{Gb/s} \approx 975.3 \, \mathrm{Mb/s}.$$

The difference is thus about two orders of magnitude, but the maximum rate achievable by using big packets is near the physical layer rate of 1000 Mb/s.

#### 2.2 Hardware design with FPGAs

After introducing the networking technology that has to be supported, we can now continue with a look at the general type of hardware on which the implementation takes place. A field programmable gate array (FPGA) is the most complex variant of a programmable logic device (PLD) and "contain[s] digital logic cells and programmable interconnect" [9]. The logic elements can be connected together to form a circuit that realizes arbitrary functions when programmed accordingly. This is conceptually similar to a microprocessor which can also perform a wide range of functionality but is limited to sequential execution of a piece of software and a specific set of instructions that can be processed. In contrast, an FPGA operates at a much lower abstraction level with inherent parallelism, leading to better performance. This also means that developing designs is vastly different from software programming and in many cases more complicated. In fact, microprocessors themselves can be implemented on FPGAs and it is common to do so in order to combine the benefits of both concepts [22]. The general components of an FPGA are outlined below, but if more information about the general design process is desired, [23] will offer a practical introduction.

#### 2.2.1 Components

The basic programmable logic functionality of FPGAs is realized not by simple boolean logic gates, but by a number of look-up tables (LUTs) and flip-flops contained in an array of slices. LUTs have multiple inputs and outputs and are dynamically programmed with the output values for every possible combination of input signal levels. Flip-flops are used as synchronous registers for intermediate storage of values. While the general idea is the same, the exact number and type of components in a slice varies between vendors [9]. Maxfield discusses logic slices and their internal operation in more detail in [22].

Interaction with the environment is required in any meaningful design, and an area that FPGAs excel in when compared to simpler PLDs. Larger devices provide a great number of package pins backed up by input/output (I/O) elements. They support different I/O standards and accommodate for high-speed buses with tight timing requirements by e.g. including flip-flops located very closely to the pins or providing special I/O clocking resources. A closer look at the I/O elements of the target device family of this thesis follows in Section 3.2.

As in most digital circuits, processing is done synchronously to a clock in many components of an FPGA. There is usually at least one system clock fed to the device that is used for general operation of the circuit and as a reference for synthesizing other frequencies if needed [9]. Additionally, I/O interfaces may require separate clocks if they do not use the same system clock as the FPGA does. Every clock signal spans a clock domain that encompasses all logic

elements that use it as their clock [19]. Those signals can usually only be routed on special clocking interconnect that is separate from the connections used for standard logic. It offers fast signal propagation with very low skew throughout the whole device or parts of it, but only reaches dedicated clock pins such as the clock inputs of D-type flip-flops.

To filter clocks that may contain jitter and derive new clocks with selectable phase shifts and frequency ratios, FPGAs include special digital and analog clocking components. A very common structure for analog frequency synthesis is the phase-locked loop (PLL) that can generate a wide range of output frequencies with defined phase relationships from a single clock input. The digital clocking resources, which fulfill a function similar to the PLLs, vary in their implementation, the FPGA vendor Xilinx for instance calls their equivalent digital clock managers (DCMs) in the Spartan device family [24].

FPGAs usually also include blocks of RAM to store larger amounts of data efficiently without using flip-flops. Additionally, digital signal processing blocks, memory controllers, and other circuitry realizing complex functions may be available [9].

A single aspect that typically does not warrant much attention when programming software but is of special importance in FPGA designs that perform high-speed interaction with external entities is the correct use of clock signals, which we will discuss next.

#### 2.2.2 Clocking and metastability

When using multiple clocks, passing signals between logic of different clock domains is a very complicated matter because if it is done wrong, non-repeatable failure conditions can occur that are very difficult to debug.

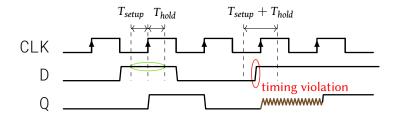

The root of this kind of problems lies in metastability, a physical phenomenon exhibited by a great number of digital devices. The D-type flip-flop for example samples its input pin D every time a rising edge is detected on the clock input CLK and then puts the value on its output pin Q. For correct behavior, it is essential that the D input stays stable for a minimum amount of time before the clock edge arrives (the setup time  $T_{setup}$ ) and after the clock edge has arrived (the hold time  $T_{hold}$ ) [25]. If these timing constraints are violated as shown in

Figure 2.3: Metastability in a D-type flip-flop. General idea adopted from [25, fig. 16.8].

Figure 2.3, the flip-flop may enter a metastable state, which means that the output lingers somewhere in between the voltage levels of a valid digital 0 and a valid digital 1 or even oscillates as discussed by Kleeman and Cantoni [26].

Chu claims in [25] that other gates and components that use the flip-flop output in some way can then interpret the output as either a logic 0 or 1 independently from each other, bringing the system to an invalid state from which it may not be able to recover. The metastable state can continue theoretically indefinitely, but it has been shown that the probability of the flip-flop resolving to a stable state increases exponentially over time. If there is no defined phase relation between clocks of different clock domains, it is impossible to correctly sample a signal from another domain without possibly violating the setup or hold time requirements of the D-FF in the target domain. Or as Kleeman et al. put it: "it is generally accepted that a perfect synchronizer cannot be physically realized." [26]

As the phenomenon cannot be prevented from occurring and will resolve by itself over time, the only direct solution is to give the FF enough time so that the probability of failure becomes small enough. The common way to do this is to add two (or more) chained flip-flops clocked in the target domain with the input of the first one connected to the signal to synchronize and the output of the last one used as synchronized signal. This structure protects the following combinatorial logic from intermittent invalid output states and gives the first flip-flop sufficient time to resolve to a valid state should timing requirements be violated. This simple approach introduces a delay of at least two clock cycles and can only be used for single independent signals as it can not be guaranteed that all individually synchronized signals become valid in the same clock cycle.

#### 2.2.3 First-in-first-out buffers

To effectively transfer data across clock boundaries, more sophisticated schemes have to be employed. A very straightforward and efficient option is to use an asynchronous first-infirst-out (FIFO) buffer. Data can be written into a FIFO and then read out only in the exact order it was written [25]. Being asynchronous means that there is a read and and a write side and that they can be used independently, concurrently, and have individual clocks. This makes the FIFO buffer an ideal candidate for cross-domain data transfer. Buffer empty and full indications can be provided for flow control.

Implementing this behavior correctly on hardware is rather complicated as can be seen in an exemplary design by Chu [25, pp. 652–660], but it is rarely necessary to do so. FPGA vendors provide automated generators tailored to their products with their design suites, usually free of charge. Xilinx for instance provides the "LogiCORE IP FIFO Generator" [27] that can generate FIFOs of almost arbitrary size and data bus width with or without separate clock domains for reading and writing. Optionally, counters that indicate the amount of data available for reading or writing can also be included. When both sides of the FIFO are clocked with the same clock speed and a continuous stream of data is written into it, the buffer can also be read continuously and at full speed after an initial delay of a few clock cycles depending on the implementation. A common variant called first-word fall-through (FWFT) or show-ahead [28] mode allows looking ahead to the next available data unit without explicitly reading it: the data, so to speak, "falls through" from the write to the read side.

### Chapter 3

## State of the Art

We have seen the fundamental technologies used in this thesis and what we must consider when using them. Next, it is essential to introduce existing solutions to our problem and how they relate to our goals. After that, studying the target platform and its specific FPGA will help in understanding the following chapters.

#### **3.1** Existing Ethernet MAC intellectual property cores

As the Ethernet technology is more than 20 years old, it is no surprise that a lot of MAC sublayers are already implemented in a wide range of technologies including FPGAs. When such a design is generic enough to be useful to a number of people, it is called an intellectual property core (IP core) that can be shared or sold. As many companies feel uncomfortable distributing the HDL code which shows off all their raw engineering ingenuity to potential competitors, a functionally equivalent but opaque (to humans, at the very least) list of gates and their connections can be offered instead.

Commercial Ethernet cores are available either directly from FPGA vendors such as Xilinx [29] and Altera [30] or third-party IP vendors such as Synopsys [31], mobiveil [32], and morethanIP [33]. They are available at least in a variant supporting 10/100/1000 speed operation, very feature-rich, and verified in tests and practice. However, they each come with one or more of the following downsides:

- The HDL source code is not available for inspection and modification, only an opaque netlist.

- Although the actual prices are usually not made public, high costs pose a problem especially for small or non-commercial projects including usage in research institutions.

- The interface offered to the application is tailored for integration into larger on-chip buses or microprocessors which makes it unnecessarily complex for simple applications.

- More features than needed are provided, increasing the complexity and resource usage of the FPGA design.

- Code that is specific to an FPGA family such as MII input/output meeting the timing required by the Ethernet standard and clocking is not included and would need to be developed by the user.

- A function to determine the current link speed automatically by reading MII management registers is missing.

At least the cost and intransparency arguments do not apply to cores from the Internet community platform OpenCores which aims to provide IP cores with full source code under open-source licenses. There are a few MAC implementations available, but only one that supports flexible operation at 10, 100, and 1000 Mb/s speed called ethernet\_tri\_mode [34]. It is written in Verilog and as a consequence may not be ideal for integrating into VHDL-based designs. Although it is possible to interface Verilog with VHDL code and vice-versa, keeping all components in the same language makes the source more consistent and thus easier to understand.

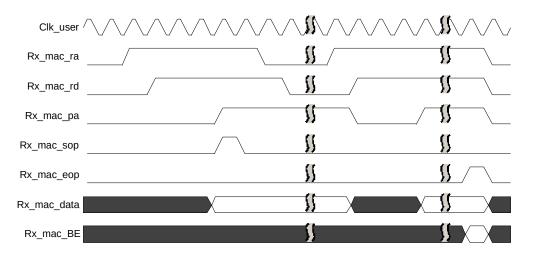

As can be seen in the official documentation [35], the user interface is documented only by two vague timing diagrams, one for transmission and one for reception, without any explanation of the signals involved. The fact that the user must resort to guesswork makes the core difficult to use. The RX part is included here without modification in Figure 3.1,

**Figure 3.1:** Timing diagram of the OpenCores ethernet\_tri\_mode IP core RX user interface. Source: [35]

the TX case is similar. The data bus Rx\_mac\_data is 32 bits wide. It is difficult to ascertain the meaning of the signals, but Rx\_mac\_sop is assumed to be the start of packet indicator while Rx\_mac\_eop looks like the end of packet indicator. They provide the actual length of the data only indirectly; the user needs to count how many bytes were transferred between assertion of the indicators if the size information is needed for further processing, which is very often the case. A look into the source code reveals that Rx\_mac\_BE serves as indicator for byte validity in the last 4-byte unit of packet data. As packets can have lengths that are not multiples of 4 bytes, the user has to put some effort into special handling of the last data unit. These considerations already show that the interface is more complex than it needs to be for general-purpose applications.

Another MAC implementation in the recent journal article "Design and Implementation of an Ethernet MAC IP Core for Embedded Applications" [36] has a similar aim of providing a flexible core for various applications. Because the full text could not be procured, only the abstract is considered here. It shows that the primary goal was to reduce FPGA resource usage and power consumption, which is deliberately not the case in the present thesis. The focus on ease of use and understanding here is a clear distinction from the work demonstrated in the article.

In summary, a sizable number of prior implementations exist but we have seen none that meet the goals of this thesis, especially being easy to use and understand and having the source code available free of charge.

#### 3.2 Hardware platform

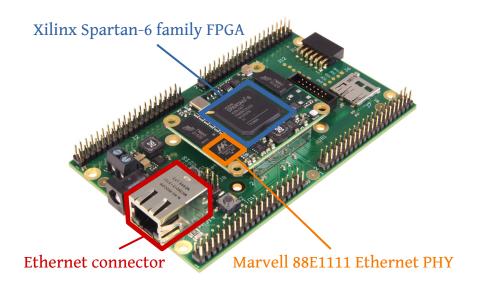

Section 2.2 provided a general introduction to field-programmable gate arrays that is now expanded upon by introducing the specific device and environment used during development of the MAC sublayer implementation presented in this thesis. The primary target platform is a GigaBee XC6SLX series industrial-grade FPGA micromodule manufactured by Trenz Electronic GmbH [8]. It includes a Xilinx Spartan-6 LX family FPGA at a system clock rate of 125 MHz and a 10/100/1000 tri-speed ethernet PHY chip Marvell Alaska 88E1111 [38] which supports a very wide range of interfaces: MII/GMII, RGMII, TBI, reduced pin count TBI (RTBI), and SGMII [39]. Which of those is used can be configured through the MII management interface. The smallest variant which is also the one used during development has a Xilinx XC6SLX45-2 FPGA and two 128 MiB dynamic random access memory (DRAM) ICs for data storage. As it is impractical to use the micromodule stand-alone, the optional baseboard TE0603 provides power supply circuitry and a standard Ethernet connector for testing purposes [40]. It can be replaced by a custom printed circuit board in actual applications. Figure 3.2 shows the two boards mated together.

**Figure 3.2:** A Trenz Electronic TE0603 baseboard with a GigaBee XC6SLX series module mounted on top. Source: [37] (component markings added).

The XC6SLX45 offers a total amount of 43,661 logic cells, 2,088 kB of block RAM storage, 8 digital clock managers (DCMs), and 4 phase locked loops (PLLs) [41]. All Spartan-6 family FPGAs have 16 global clock buffers called BUFGMUX that must be used to get clock signals onto the clocking interconnect, each of which can switch between two input clocks by way of a third select input. The switch can be performed free of glitches provided both clocks are continuously running [24].

Furthermore, there are flip-flop elements located directly besides every device pin in their designated input/output blocks (IOBs) to provide outputs with low skew called OLOGIC2 and capture inputs directly at their source called ILOGIC2 [42]. When combined with the possibility to also capture a clock right at the pin in a BUFIO2 element and use it to clock the FFs of neighboring data pins, input from high-speed data buses that supply their own clock signal can be easily implemented, eliminating delay and skew issues when the clock is first routed to a global buffer and then to a FF located arbitrarily in the device. The configurable delay element IODELAY2 again built into every IOB can be used to delay the clock, the data signal, or both in order to place the rising edge of the clock right in the middle of the valid data window. All I/O registers additionally provide double data rate ability. Buffers supporting a wide range of digital I/O standards are available. They drive either the general (input buffer IBUF, output buffer OBUF) or the clocking interconnect (input buffer IBUFG). There is no dedicated clock output buffer.

Up to this point, only preexisting technologies and products were introduced. Subsequently, this information is put to good use by moving on to the design and implementation of the FPGA-based Ethernet MAC sublayer.

### **Chapter 4**

### Design

The first step in developing the Ethernet MAC was to partition the task into smaller components (VHDL entities) with distinct responsibilities and define their interconnection. Special attention is drawn to a few key points that we will discuss first before we take a look at the resulting design in Section 4.2. A more thorough look at each component follows in Section 4.3.

#### 4.1 Design trade-offs

The interface offered to the user is of primary concern: to reach the goals of this thesis, it has to be fast enough to allow for symmetrical 1 Gb/s data transfer but also be easy to use, i.e. use simple signals and a common pattern that hardware developers are inherently familiar with. Furthermore, the users should be able to freely choose the clock they want to use for communicating with the MAC to avoid implementing clock domain crossing - the MAC should do that for them. A standard on-chip system bus like the Advanced eXtensible Interface (AXI) by ARM Limited [43] or Wishbone by OpenCores [44] is unfeasible because even though the concept is certainly well-known, it is over-sized for simple applications both in terms of signal count and complexity. Already less complex but similar in the overall idea is a block of RAM which acts as a buffer. To transmit a packet, the user could write it into the memory, but then the following questions have to be considered: how does the transmission logic know where the next packet lies in the buffer? How does it know that a packet is ready to send? How does the user know which packets in the buffer were sent and where he or she can write the next bulk of data? These are questions that can be answered, but in the course of doing so the naively suggested RAM interface will inevitably become more complex. If we think back to Section 2.2.3 though, we remember the FIFO interface and its characteristic of being very simple. It is also well-known, allows for high-speed data

transfer and, when backed by a standard implementation, offers easy clock domain crossing, making it ideal for the MAC sublayer presented in this thesis.

When describing an interface, not only the connections, but also the width and format of the data that is passed over them must be clear. To be able to construct a valid MAC frame, at least the destination address, source address, length/type, and client data is needed as we have seen in Section 2.1.3. The preamble and start frame delimiter can be skipped as they do not carry any information anyway. Theoretically speaking, these fields can be encoded in any fashion and order. But for both the user and the implementation of the media access control sublayer, keeping it plain and sticking to the format already defined in the Ethernet standard is the easiest option. There is also nothing to be gained by being fancy about the frame data representation. By sticking to the standard, the MAC can pass through most of the frame without any modification.

There is one complication concerning the frame trailer though: on the one hand, the user should not have to include the padding and frame check sequence on transmission. This problem can be solved when the data is defined to end right before padding and the MAC takes care of adding it. On reception on the other hand, the original length of the frame is not necessarily part of the header and thus unknown, so the padding cannot be removed in the general case. The FCS is a fixed-length field at the end of the packet and thus can always be stripped. Doing so makes the interface as symmetrical as possible. The user then has no possibility of verifying the integrity of a received packet, but that is also not necessary when the MAC takes proper care that erroneous packets are internally consumed and never reach the FIFO interface.

We have yet to examine the question of how many bits to transfer in one clock cycle, but as Ethernet counts data in multiples of bytes, making the interface 8 bit wide is the natural choice. A wider data bus allows for lower interface clock rates at identical data rates, but necessitates adaption logic to guarantee that byte units can be received and transmitted. In a general-purpose MAC, it is impossible to know the exact requirements of the user and what width would benefit his or her application, so the design has to cover all possibilities with the least common denominator of 1 byte. Width conversion logic can be easily added on top of the MAC FIFO interface by the user if there is a need for it.

A problem that still lingers in the FIFO architecture is that if only the data of packets is passed on, there is no way to know where they start and end. This is fixed by placing two bytes that indicate the size of the next packet in the buffer before each data part. Ethernet frames can be up to 1514 bytes long (excluding the frame check sequence), so one byte (maximum value 255) would not be enough for storing their size; the next possibility is using two bytes (maximum value 65535). As  $\lceil \log_2 1514 \rceil = 11$  bits are strictly needed for storing the maximally possible frame size, 5 of the 16 bits will inevitably remain unused but the wasted

space is so small that it is of no concern. It accounts for between 0.04 and 1.02 percent of the total stored data, depending on the packet size.

Nevertheless, we can see that there are in fact two limitations with this simple approach:

- 1. Packets must be delayed in the FIFO until they have been completely received so their size is known and can be put in front of the data.

- 2. The user needs to know the sizes of packets prior to starting transmission.

Both are rarely relevant in practice: a packet can usually not be acted upon as it is still being received since it could contain errors that are only detected when the frame check sequence that follows the data payload is verified. It is very important to understand that only the latency is different but that the achievable RX data rate is identical both when delaying the packet and when handing it to the user immediately. As for the second restriction, most users will want to use protocols that include further header checksums like UDP/IP instead of raw Ethernet frames. The IP header for example includes a field for the length of the packet, so to calculate its checksum the packet size again has to be known beforehand no matter how the MAC sublayer is designed.

One of the other choices to be made is whether to have completely separate modules in the transmit and receive paths or to combine some or all of them. Either option is feasible as there is zero interaction between both directions. However, the functionality is very similar, symmetrical even, so the code will be easier to understand if it is kept in one place. Splitting it per direction serves little purpose besides artificially increasing the component count, complicating the design. The single exception where it is worthwhile to make a separation are the FIFOs. The user might want to replace only one direction with a custom implementation.

These were the key points that we need to take into account when studying the MAC design in the following section.

#### 4.2 Overview

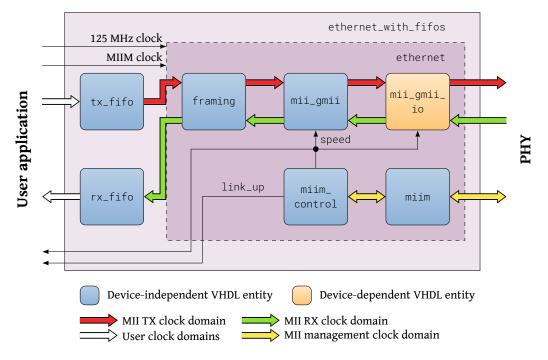

Figure 4.1 shows an overview of the MAC design. Every block corresponds to a VHDL entity with the indicated name. The arrows indicate conceptual flow of data and do *not* imply VHDL port directions. We shortly discuss the diagram beginning at the interface to the user application on the left-hand side and continuing rightwards from there until reaching the connection to the physical layer on the right-hand side.

Figure 4.1: Block diagram of the Ethernet MAC presented in this thesis

To not require users to learn the details of the MAC implementation and buffer packets themselves, FIFOs with standard interfaces are provided for both the transmit and receive data paths as previously discussed. As can be seen in the diagram, the two directions are completely independent from each other throughout the whole design. The first entity that implements actual Media Access Control sublayer functionality is the framing component. Functionality-wise, it performs the core operations that are expected from an Ethernet MAC like generating and verifying checksums and packet encapsulation. The following mii\_gmii module acts as transparent converter between the generic streams of packet data and the actual signals expected by the media-independent interfaces as well as switching between MII and GMII as needed based on the current link speed. The speed is periodically read out of the MII management interface by mim\_control which also takes care of the initial configuration of the PHY after reset. Only the high-level functionality is allotted to this module while the actual MIIM interface transactions are performed by miim. Lastly, due to the narrow timing requirements of the MII/GMII connections, it is not possible to directly connect them to the FPGA package pins. The device-specific I/O configuration needed in between is provided by mii\_gmii\_io.

Besides the clock pins used by the MII, the MAC requires the user to supply a 125 MHz reference clock to use as transmission clock in GMII mode, a clock for the MII management interface, and two FIFO clocks, one for each direction. The latter three of these clocks can be identical to simplify the user design. The reset\_generator entity (not shown in the figure) monitors the current link speed and issues a complete reset for the MII RX and TX clock domains when it changes. This guarantees a consistent system state after a potential transmission clock switch between MII and GMII. The reset indication is also provided to the user to ensure that no mismatched data is written to or read from the FIFOs. We will discuss the exact reasons why this procedure is necessary later when describing the IO implementation in Section 5.1.1.

As a convenience for using the MAC core, all mentioned components beginning at framing are preconnected to each other in a structural entity called ethernet which is then combined again with the FIFOs to form ethernet\_with\_fifos. The latter is a ready-to-use entity offering the FIFOs' interfaces on the user side and direct MII connections on the PHY side. It can be instantiated in custom designs that want to use Ethernet without much effort. It generally does not provide any benefit to bypass the FIFOs and directly connect to the framing component except in sufficiently sophisticated applications.

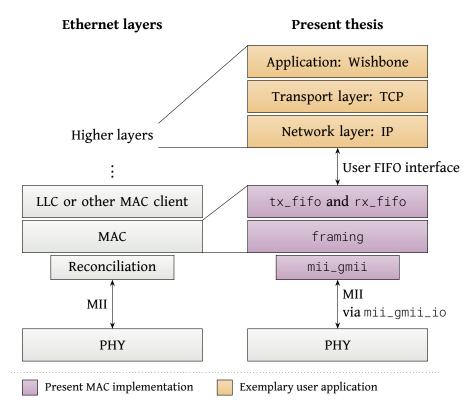

To clarify how the components relate to the layered architecture defined in the Ethernet standard as introduced in Section 2.1.1, Figure 4.2 shows the Ethernet layers and selected entities of the MAC design presented in this thesis side-by-side. The higher layers on the right-hand side are only exemplary and can be exchanged for arbitrary user application layers. Although the purposes of the reconciliation sublayer (RS) and the original Ethernet MAC sublayer correspond to the mii\_gmii and framing entities respectively, the interfaces between them differ. The standard e.g. suggests that the RS and the MAC sublayer communicate data one bit at a time, which is impractical for actual implementation on an FPGA. Similar considerations apply to the interface the MAC offers to higher layers. The logical link control (LLC) sublayer is designated optional by the standard and must be implemented by the user if needed.

#### 4.3 Components

Let us now take a closer look at each component and the input and output connections it exposes to its neighbors.

#### 4.3.1 FIFOs

The only modules that the user will normally interact with directly are the transmit and the receive FIFO buffer. Consistent with our prior considerations, both have a standard interface as seen for instance with Chu [25, p. 280] with a data width of 8 bits and only one side facing the user. The TX FIFO can be written, the RX FIFO can be read by the user. They both have

**Figure 4.2:** Ethernet simplified layer architecture in relation to the MAC implementation presented in this thesis. Ethernet side adopted from [5, fig. 1-1].

their own clock domain with the clock supplied by the user. The timing characteristics conform to the interface of first-word fall-through FIFOs generated by the Xilinx LogiCore IP FIFO generator [27].

To send a packet, first of all the FIFO must not be full. The application must put the 2-byte size of the packet into the buffer, most significant byte (MSB) first, then the least significant byte (LSB), after which precisely as many bytes of data as were indicated must follow. Keeping the structure identical to the Ethernet standard avoids unnecessary and costly rearrangements within the Ethernet packet when sending. As soon as the FIFO detects that the data for the next packet has been written completely, it starts passing the data on to the framing module.

Receiving a packet works analogously: framing writes an incoming packet to the buffer. After it has been received completely and without errors, the RX FIFO will indicate that it is not empty and the size and data can be read. As an added convenience, the FIFO will pretend to be empty for a few clock cycles after every packet even when technically more packets are available, so the user can sense the end of a transmission unit and does not need to count the data bytes while reading. During ongoing read-out of a packet, the FIFO never becomes empty. Although the interface is identical to that of a normal FIFO and the entity is called rx\_fifo, it cannot work like one internally. The packet size is known and written to the memory only after the last data byte has been received, but needs to be read out first, before the data, in clear violation of the first-in-first-out principle. Also, erroneous frames must be skipped without requiring the user to read them out.

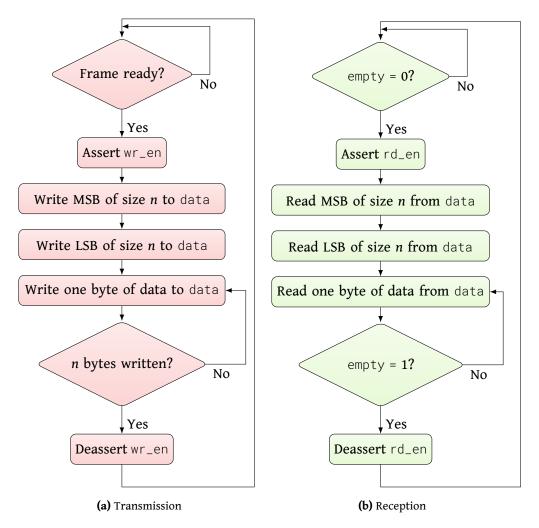

Figure 4.3 shows basic flowcharts for both transmission and reception of packets using the FIFO. The signal name wr\_en means "write enable" while rd\_en stands for "read enable". In the actual entities, the port names are additionally prefixed by the direction ( $tx_-$  or  $rx_-$ ). Although it is not shown for the TX case (Figure 4.3a) because it would considerably clutter the diagram, each write step can only occur when  $tx_full_0$  is not asserted. If it is, the user has to deassert  $tx_wr_en_i$  and delay the byte until the FIFO has space available again, or the write will be lost.

**Figure 4.3:** Flowcharts for packet transmission and reception on the MAC's FIFO user interface

#### 4.3.2 Framing

As the core part implementing actual MAC sublayer functionality, the framing component has the following responsibilities:

#### • Encapsulation of packets on transmission:

- Insertion of the preamble and start frame delimiter before transmitting the data

- Insertion of padding as required

- Calculation and insertion of the frame check sequence

- Enforcement of the interpacket gap

- Verification and decapsulation of packets on reception:

- Verification of the frame start which should be any number of preamble bytes followed by the start frame delimiter

- Verification of the frame check sequence

- Verification of the packet length which should be within the limits required by the Ethernet standard

All tasks are fulfilled by forwarding the data stream from the FIFO to mii\_gmii and viceversa, carefully inserting and removing data bytes as necessary. The interface offered to the FIFOs is almost identical to the one towards the mii\_gmii module. Table 4.1 lists all ports of the module. Transfer of a single byte of data can take a different amount of clock cycles depending on the underlying MII variant in use: only 4 bits can be transferred at a time with the Fast Ethernet MII for example, so it will take two cycles to completely send 8 bits. Since mii\_gmii does not buffer data, a new byte can only be placed on the line after the current one was processed. The next data unit should be placed on tx\_data in each clock cycle that has tx\_byte\_sent high when transmitting data, and read from rx\_data in each clock cycle that has rx\_byte\_received high when receiving data. The tx\_byte\_sent and rx\_byte\_received signals effectively act as a data strobe signal. Exemplary timing diagrams for packet transactions are found in Appendix A.

All differences between the two sides of framing are related to the interpacket gap (IPG) in frame transmission: tx\_busy exists only towards the FIFO and tx\_gap only towards mii\_ gmii. The busy indication is needed for signaling the FIFO to delay sending the next packet during the IPG while tx\_gap actively requests continued operation of tx\_byte\_sent without actually transmitting data on the media-independent interface.

Verification of incoming packets has two distinct ways in which errors are handled: should the frame beginning be invalid already, the remainder of the frame is silently skipped as no

| Port name                         | Function                                                   |  |  |

|-----------------------------------|------------------------------------------------------------|--|--|

| tx_reset_i                        | Active-high asynchronous reset of all TX functions         |  |  |

| tx_clock_i                        | Clock for all transmit signals                             |  |  |

| tx_enable_i                       | Active-high transmit enable                                |  |  |

| tx_data_i<7:0>                    | Data to transmit                                           |  |  |

| tx_byte_sent_o                    | Put next byte on tx_data when asserted                     |  |  |

| tx_busy_o                         | Start new packet only when deasserted                      |  |  |

| rx_reset_i                        | Active-high asynchronous reset of all RX functions         |  |  |

| rx_clock_i                        | Clock for all receive signals                              |  |  |

| rx_frame_o                        | Asserted as long as one continuous frame is being received |  |  |

| rx_data_o<7:0>                    | Data received                                              |  |  |

| rx_byte_received_o                | Asserted when rx_data is valid                             |  |  |

| rx_error_o                        | Active-high receive error indication                       |  |  |

| <pre>mii_tx_enable_o</pre>        | Function equivalent to tx_enable_i                         |  |  |

| mii_tx_data_o<7:0>                | Function equivalent to tx_data_i                           |  |  |

| <pre>mii_tx_byte_sent_i</pre>     | Function equivalent to tx_byte_sent_o                      |  |  |

| mii_tx_gap_o                      | Transmit IPG when asserted                                 |  |  |

| mii_rx_frame_i                    | Function equivalent to rx_frame_o                          |  |  |

| mii_rx_data_i<7:0>                | Function equivalent to rx_data_o                           |  |  |

| <pre>mii_rx_byte_received_i</pre> | Function equivalent to rx_byte_received_o                  |  |  |

| mii_rx_error_i                    | Function equivalent to rx_error_o                          |  |  |

| Table 4.1: | Ports | of the | framing | entity |

|------------|-------|--------|---------|--------|

data has left framing yet. If the FCS or length checks fail, a reception error is indicated by  $rx\_error\_o$ . In any case, the FCS is not stripped from the packet on reception since doing so would require delaying the data stream by the checksum length of 4 bytes. This would substantially increase the complexity of the receive state machine. Instead, the  $rx\_fifo$  entity is responsible for removing the FCS before it reaches the user.

#### 4.3.3 Media-independent interface

As the name mii\_gmii indicates, we have reached the first entity where actual communication with the physical layer device takes place. Because it primarily serves as a thin signal adaption layer, there is not much to do here, especially when GMII is used. Then the data received from framing can be passed on to the MII IO entity by directly mapping the ports. For MII though each data byte must be split into two 4-bit units on transmission and combined on reception. The MII signals CRS, COL, and TX\_ER are omitted from the MII/GMII ports because they are only useful in half-duplex modes.

#### 4.3.4 Media-independent interface input/output

The outputs and inputs of the mil entity on the MII side already conform to the functional characteristics of the Ethernet specification, but their timing has to be adapted. Getting this right is dependent on the concrete FPGA architecture and as a consequence put into a separate exchangeable entity named mil\_gmil\_io. The ports must then finally be connected to the pins of the device by the user where they will reach the PHY.

#### 4.3.5 Media-independent interface management

miim implements the standard management interface of MII. In addition to the actual MIIM MDC and MDIO signals for connection to the PHY, an interface to read and write single registers one at a time is provided. It runs in a user-supplied separate MIIM clock domain together with miim\_control.

#### 4.3.6 Media-independent interface management control