# Conceptual Design and Realization of a Dynamic Partial Reconfiguration Extension of an Existing Soft-Core Processor

by

Philipp Kerling

A thesis submitted in partial fulfillment for the degree of Master of Science

at

Technische Universität Ilmenau Department of Computer Science and Automation Software Architectures and Product Lines Group

> Examiner: Dr.-Ing. Detlef Streitferdt Supervisor: M.Sc. Michael Kirchhoff

> > February 12, 2019

DOI: 10.22032/dbt.38246 URN: urn:nbn:de:gbv:ilm1-2019200174

## Abstract

Technische Universität Ilmenau Department of Computer Science and Automation Software Architectures and Product Lines Group

# Conceptual Design and Realization of a Dynamic Partial Reconfiguration Extension of an Existing Soft-Core Processor

by Philipp Kerling

Many modern *field-programmable gate arrays* (FPGAs) support partial reconfiguration, which allows to dynamically replace only a part of a design at run time. In this thesis, partial reconfiguration capability is integrated with the *VHDL Integrated Softcore Architecture for Reconfigurable Devices* (ViSARD) developed at Technische Universität Ilmenau and conceived for hard real-time tasks requiring floating-point calculations with high precision. Specifically, its arithmetic logic unit is modified to allow exchanging floating-point arithmetic execution units. Design goals of the partial reconfiguration system are high speed, low latency, low resource overhead, and hard real-time capability. They are reached by implementing a custom partial reconfiguration controller loading partial bitstreams from external RAM over a standard AXI bus and extending the ViSARD appropriately. In a test design that switched between 3 different configurations each containing between 1 and 3 execution units, the proposed partial reconfiguration system achieved the maximum specified bitstream throughput on the target FPGA and allowed for roughly 40 % reduced look-up table usage.

Viele aktuelle Field Programmable Gate Arrays (FPGAs) unterstützen die Technik der partiellen Rekonfiguration (PR), durch die dynamisch zur Laufzeit ein Hardware-Design auch nur teilweise ausgetauscht werden kann. Die vorliegende Arbeit integriert PR-Funktionalität in die an der Technischen Universität Ilmenau für harte Echtzeitaufgaben mit hochpräzisen Fließkommaberechnungen entwickelte VHDL Integrated Softcore Architecture for Reconfigurable Devices (ViSARD). Zu diesem Zweck wird die arithmetisch-logische Einheit angepasst, um das Auswechseln von Fließkomma-Ausführungseinheiten zu ermöglichen. Ziele der Entwicklung des PR-Systems sind hohe Geschwindigkeit, niedrige Latenz, niedrige Ressourcenkosten und harte Echtzeitfähigkeit. Erreicht werden diese durch die Umsetzung einer eigenen Steuereinheit (partial reconfiguration controller), die partielle Bitströme aus externem RAM über einen standardmäßigen AXI-Bus lädt sowie die entsprechende Erweiterung der ViSARD. In einem Testdesign, das zwischen drei verschiedenen Konfigurationen mit je zwischen einer und drei Ausführungseinheiten wechselt, hat das entwickelte PR-System den maximal spezifierten Bitstromdurchsatz auf dem Ziel-FPGA erreicht und den Verbrauch an Lookup-Tabellen um etwa 40 % verringert.

## Acknowledgements

First and foremost, I would like to thank Dr. Streitferdt for the opportunity to write my graduation thesis at his chair.

I would furthermore like to extend my earnest appreciation to my advisor, Michael Kirchhoff, who has shaped my understanding of the academic world just as much as this thesis. A lot of very fruitful discussion went into both the theoretical and practical aspects of this work. His input on the meaningful presentation of results was especially valuable.

My friend Kathrin has invested a substantial amount of time into proofreading and giving me precious advice on scientific writing and consistency. I am deeply grateful for her help.

# Contents

| Ał  | ostrac  | t       |                                      | iii  |

|-----|---------|---------|--------------------------------------|------|

| Ac  | cknow   | ledgem  | ients                                | iv   |

| Li  | st of F | igures  |                                      | ix   |

| Li  | st of T | ables   |                                      | xi   |

| Ał  | hrevi   | ations  |                                      | xiii |

| 111 | JUICVI  | ations  |                                      | лш   |

| 1   | Intro   | oductio | n                                    | 1    |

| 2   | Fune    | damenta | als                                  | 5    |

|     | 2.1     | FPGAs   | s                                    | 5    |

|     |         | 2.1.1   | Overview                             | 6    |

|     |         | 2.1.2   | Components                           | 7    |

|     |         | 2.1.3   | Configuration                        | 9    |

|     | 2.2     | Digital | l hardware and systems design        | 11   |

|     |         | 2.2.1   | Key concepts and principles          | 12   |

|     |         | 2.2.2   | The Zynq-7000 SoC                    | 15   |

|     | 2.3     | Partial | l reconfiguration                    | 19   |

|     |         | 2.3.1   | Principle                            | 19   |

|     |         | 2.3.2   | Reconfiguration of Zynq-7000 devices | 21   |

|     |         | 2.3.3   | Limitations and trade-offs           | 24   |

|     | 2.4     | The Vi  | iSARD                                | 27   |

|     |         | 2.4.1   | Structure                            | 28   |

|     |         | 2.4.2   | Toolchain                            | 30   |

|     |         | 2.4.3   | Assembly language and assembler      | 30   |

|     |         | 2.4.4   | ALU/FPU operations                   | 32   |

| 3   | Desi    | •       |                                      | 37   |

|     | 3.1     | Partial | l reconfiguration controller         | 37   |

|     |         | 3.1.1   | Available options                    | 39   |

|     |         | 3.1.2   | Custom controller                    | 41   |

|     | 3.2     | ViSAR   | D                                    | 46   |

|   |      | 3.2.1          | Related work         47                                       |

|---|------|----------------|---------------------------------------------------------------|

|   |      | 3.2.2          | Integration                                                   |

|   |      | 3.2.3          | Assignment of execution units to reconfigurable partitions 51 |

|   |      | 3.2.4          | Pblock locations and shapes                                   |

|   |      | 3.2.5          | Examination of execution units for reconfiguration            |

|   |      | 3.2.6          | Impact on resource usage                                      |

|   |      |                |                                                               |

| 4 |      | lementa        |                                                               |

|   | 4.1  | -              | ations                                                        |

|   | 4.2  |                | osine execution unit                                          |

|   | 4.3  | Partial        | reconfiguration controller                                    |

|   |      | 4.3.1          | Interface                                                     |

|   |      | 4.3.2          | Bitstream storage format                                      |

|   |      | 4.3.3          | Data transfer architecture    68                              |

|   |      | 4.3.4          | Real-time capability    70                                    |

|   | 4.4  | Bitstre        | am packer                                                     |

|   | 4.5  |                | am preloader                                                  |

|   | 4.6  |                | D integration                                                 |

|   |      | 4.6.1          | Reconfigurable partition inside the ALU                       |

|   |      | 4.6.2          | Memory concatenator                                           |

|   | 4.7  |                | bitstream generation                                          |

|   | 1.7  | 4.7.1          | Module-based generation                                       |

|   |      | 4.7.2          | Xilinx compression   76                                       |

|   |      | 4.7.2          | Difference-based generation                                   |

|   |      | 4.7.4          | torCombitgen                                                  |

|   |      | 1./.1          | toreomongen                                                   |

| 5 | Test | and res        | ults 81                                                       |

|   | 5.1  | Simula         | tion of the partial reconfiguration controller                |

|   |      | 5.1.1          | Test setup                                                    |

|   |      | 5.1.2          | Results                                                       |

|   | 5.2  | Practic        | al verification of basic functionality                        |

|   |      | 5.2.1          | Test setup                                                    |

|   |      | 5.2.2          | Results                                                       |

|   | 5.3  | Two co         | ores with parallel calculation/reconfiguration                |

|   |      | 5.3.1          | Test setup         94                                         |

|   |      | 5.3.2          | Results                                                       |

|   | 5.4  |                | le execution units                                            |

|   | 011  | 5.4.1          | Test setup         97                                         |

|   |      | 5.4.2          | Results                                                       |

|   |      | 5.4.2<br>5.4.3 | Speed and timing         101           101         101        |

|   | 5.5  |                |                                                               |

|   | J.J  | Summa          | ary                                                           |

| 6 | Con  | clusion        | 109                                                           |

|   | 6.1  | Summa          | ary                                                           |

|   | 6.2  |                | work                                                          |

| A | Sour | ce code |                                                  | 115 |

|---|------|---------|--------------------------------------------------|-----|

|   | A.1  | PRC .   |                                                  | 115 |

|   | A.2  | bin_pa  | cker                                             | 115 |

|   | A.3  | mem_o   | concatenator                                     | 115 |

|   | A.4  | bin_pr  | ovider                                           | 115 |

| В | Test | setups  |                                                  | 117 |

|   | B.1  | Simula  | tion                                             | 117 |

|   |      | B.1.1   | Test bench (Verilog)                             | 117 |

|   |      | B.1.2   | Bitstream packing                                | 117 |

|   | B.2  | Basic t | est                                              | 117 |

|   |      | B.2.1   | Generation of test program and data memory files | 117 |

|   |      | B.2.2   | Bitstream generation Tcl script                  | 118 |

|   |      | B.2.3   | Bitstream packing                                | 118 |

|   |      | B.2.4   | U-Boot preparation commands                      | 119 |

|   |      | B.2.5   | Boot log                                         | 119 |

|   | B.3  | Multi-l | EU test                                          | 119 |

|   |      | B.3.1   | Generation of test program and data memory files | 119 |

|   |      | B.3.2   | Bitstream generation Tcl script                  | 120 |

|   |      | B.3.3   | Bitstream packing                                | 120 |

|   |      |         |                                                  |     |

### Bibliography

121

# **List of Figures**

| 2.1  | Generic FPGA architecture                                                          | 6  |

|------|------------------------------------------------------------------------------------|----|

| 2.2  | FPGA fabric with logic cells and interconnect                                      | 9  |

| 2.3  | Relation of FPGA functional and configuration layer                                | 10 |

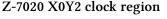

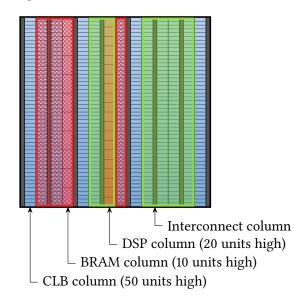

| 2.4  | Column layout inside the X0Y2 clock region of the Z-7020 FPGA (exemplary)          | 11 |

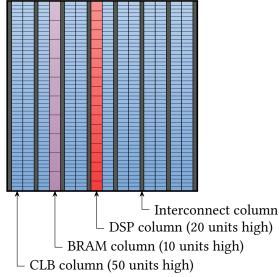

| 2.5  | Major steps in a typical FPGA design flow                                          | 13 |

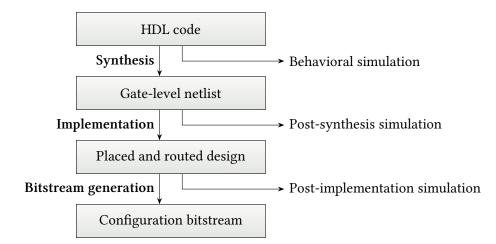

| 2.6  | AXI read channel architecture                                                      | 14 |

| 2.7  | Zynq-7000 SoC overview                                                             | 16 |

| 2.8  | Hardware used in this thesis                                                       | 18 |

| 2.9  | Overview of Z-7020 SoC used in this thesis                                         | 18 |

| 2.10 | Principle and model of partial reconfiguration                                     | 20 |

| 2.11 | ICAPE2 primitive for self-reconfiguration of 7 series devices                      | 21 |

| 2.12 | Xilinx design flow for partial reconfiguration                                     | 22 |

| 2.13 | Evolution of reconfiguration throughput of FPGA families supporting dynamic        |    |

|      | partial reconfiguration                                                            | 24 |

| 2.14 | 0 10                                                                               |    |

|      | Vivado design suite in partial reconfiguration-enabled projects                    | 27 |

| 2.15 | Schematic overview of the ViSARD structure                                         | 29 |

| 2.16 | ViSARD toolchain                                                                   | 30 |

| 2.17 | ViSARD instruction encoding                                                        | 32 |

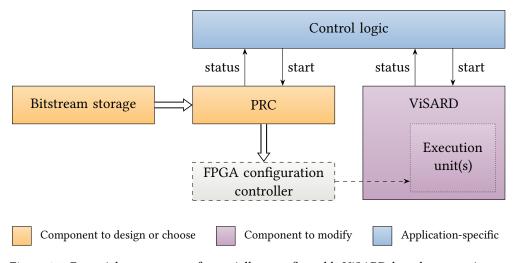

| 3.1  | Essential components of a partially reconfigurable ViSARD-based system             | 38 |

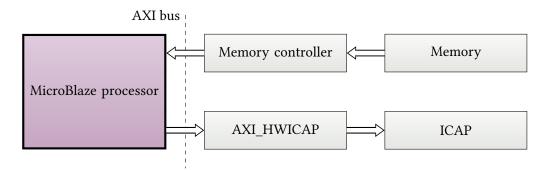

| 3.2  | Exemplary structure of a microprocessor-based partial reconfiguration system       |    |

|      | using the HWICAP solution by Xilinx                                                | 39 |

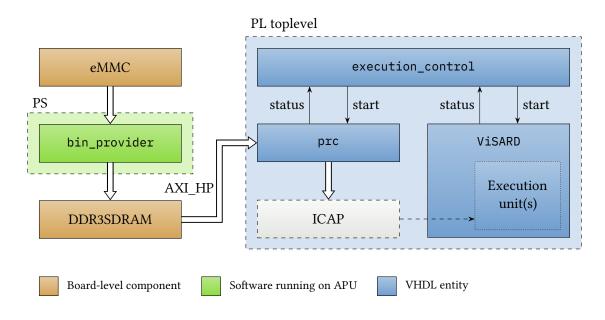

| 3.3  | Structure of the custom partial bitstream storage and delivery solution            | 44 |

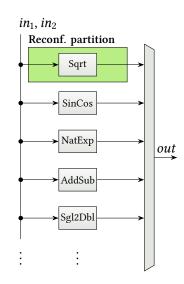

| 3.4  | Structure of the ViSARD ALU with one exemplary execution unit enclosed in          |    |

|      | a reconfigurable partition                                                         | 48 |

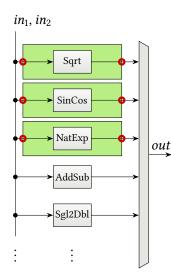

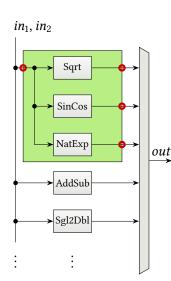

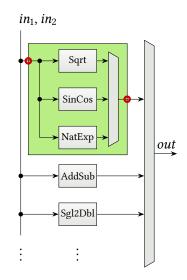

| 3.5  | Options of assigning execution units to reconfigurable partitions                  | 52 |

| 3.6  | Plot of total amount of partition pins in the design with increasing number        |    |

|      | of execution units for different options of assigning them to reconfigurable       |    |

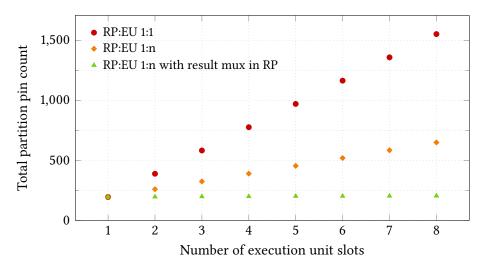

|      | partitions                                                                         | 53 |

| 3.7  | Valid and invalid exemplary Pblocks with regard to back-to-back violations . $\ .$ | 55 |

| 3.8  | Floating-point IP configuration example                                            | 57 |

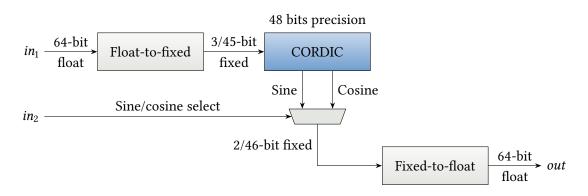

| 4.1  | Data flow inside the SinCos execution unit highlighting the data type conversions  | 64 |

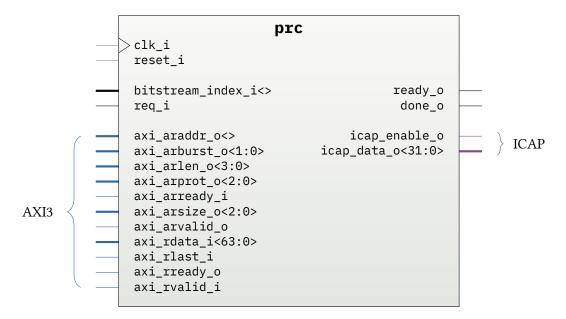

| 4.2  | Custom PRC ports                                                                   | 67 |

| 4.3  | Exemplary timing diagram of requesting partial bitstream transfers from the        |    |

|      | custom PRC                                                                         | 68 |

| 4.4  | Packed bitstream structure consisting of 2 partial bitstreams                      | 69 |

| Exemplary reconfigurable module entity containing the Sqrt, NatExp, and Mul-<br>tiply, execution units                                                                                         | 74                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Relation of full designs containing different RMs and partial bitstreams neces-<br>sary for switching between all possible configurations with difference-based<br>bitstream generation        | 78                    |

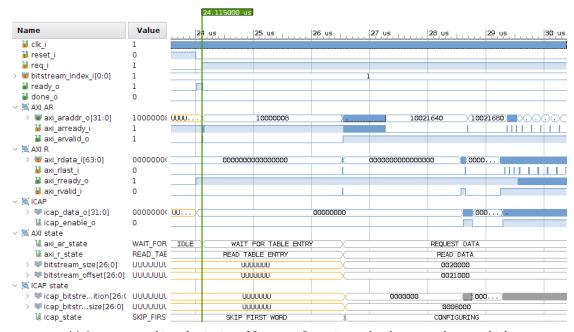

| Simulated waveforms showing the custom partial reconfiguration controller perform a reconfiguration                                                                                            | 84                    |

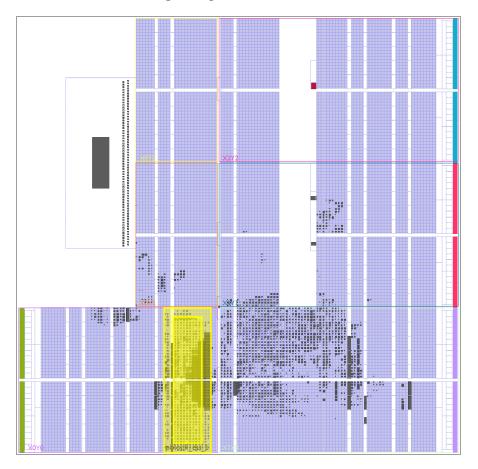

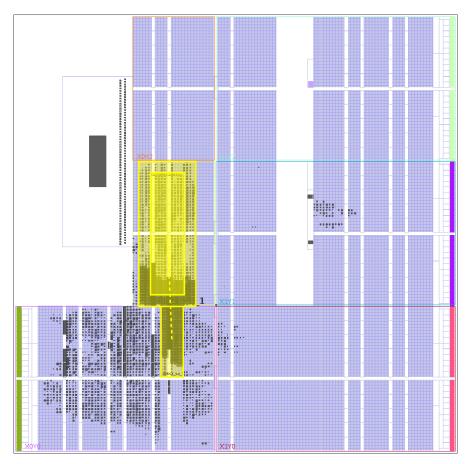

| Device overview highlighting the Pblock assigned to the reconfigurable parti-<br>tion of the execution units exchangeable in the basic test as seen in the imple-<br>mented full NatExp design | 86                    |

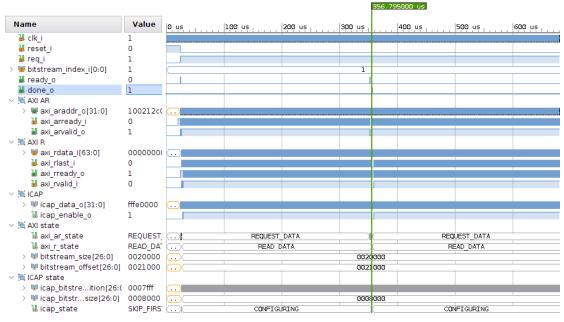

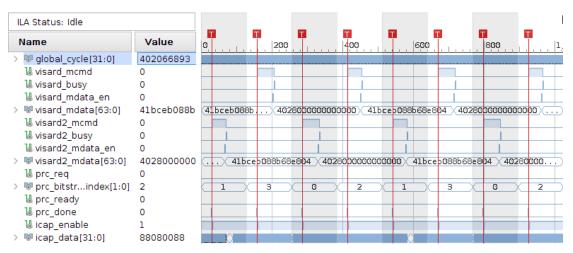

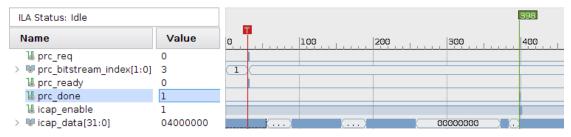

| Recorded waveforms showing basic partial reconfiguration of the ViSARD work-<br>ing in practice                                                                                                | 90                    |

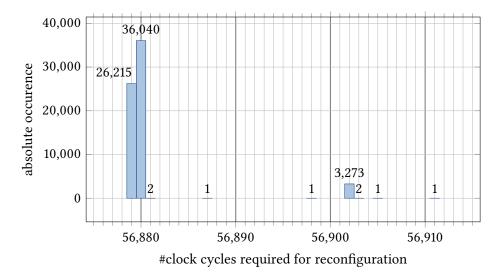

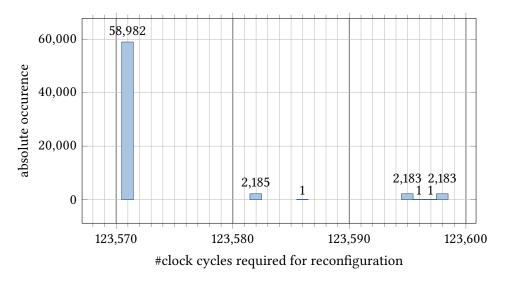

| Histogram of clock cycle count required for one exchange of EUs via partial reconfiguration in the basic test scenario                                                                         | 91                    |

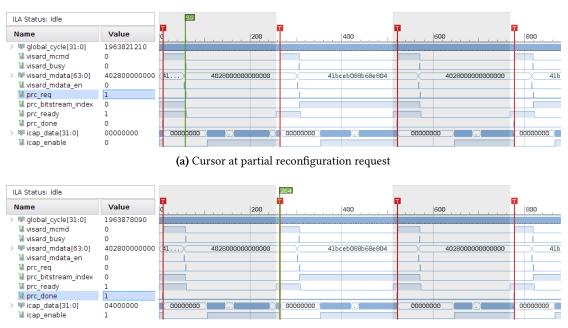

| Recorded waveform showing parallel reconfiguration and calculation of two ViSARD cores working in practice                                                                                     | 95                    |

| Recorded waveforms showing signal transitions during overlapping bitstream preloading and PR                                                                                                   | 96                    |

| Histogram of clock cycle count required for one exchange of EUs via partial reconfiguration in the multi-core test scenario                                                                    | 97                    |

| Device overview highlighting the Pblock assigned to the reconfigurable parti-<br>tion of the execution units exchangeable in the multi-EU test as seen in the                                  |                       |

| implemented full Divide designRecorded waveform showing multi-EU partial reconfiguration of the ViSARD                                                                                         | 98                    |

| working in practice                                                                                                                                                                            | 101                   |

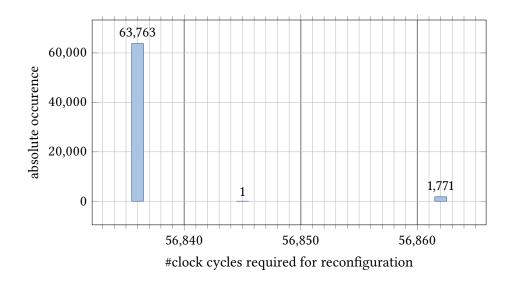

| Histogram of clock cycle count required for one exchange of EUs via partial reconfiguration in the multi-EU test scenario                                                                      | 101                   |

|                                                                                                                                                                                                | tiply execution units |

# **List of Tables**

| 2.1 | ViSARD operations and associated mnemonics                                    | 33  |

|-----|-------------------------------------------------------------------------------|-----|

| 3.1 | ViSARD execution units available in double precision and the mnemonics they   |     |

|     | handle                                                                        | 56  |

| 3.2 | Resource footprint of all double precision execution units                    | 59  |

| 4.1 | Custom PRC generics and their functions                                       | 66  |

| 5.1 | Drivers and descriptions of signals captured for demonstrating basic partial  |     |

|     | reconfiguration functionality                                                 | 90  |

| 5.2 | Primary resources used in the basic test design, by component                 | 92  |

| 5.3 | Basic test bitstream sizes generated by different methods                     | 93  |

| 5.4 | Combined resource usage of the EU configurations chosen for the multi-EU test | 99  |

| 5.5 | Primary resources used in the multi-EU test design, by component              | 102 |

| 5.6 | Multi-EU test bitstream sizes generated by different methods                  | 103 |

| 5.7 | Comparison of LUT and FF resources used in the multi-EU test design depend-   |     |

|     | ing on the location of the result multiplexer                                 | 104 |

| 5.8 | ICAP data throughput of the custom PRC obtained in practical tests            | 105 |

| 5.9 | Comparison of resource utilization and configuration throughput of the PRC    |     |

|     | presented in this thesis and other published PRC designs                      | 106 |

# Abbreviations

- ACP accelerator coherency port

- ALU arithmetic logic unit

- APU application processor unit

- ASIC application-specific integrated circuit

- ASSP application-specific standard part

- AXI Advanced eXtensible Interface

- BRAM block random-access memory

- CAP configuration access port

- CLB configurable logic block

- CORDIC coordinate rotational digital computer

- CPU central processing unit

- DAP debug access port

- DDR double data rate

DDR3 SDRAM double data rate type three synchronous dynamic random-access memory

- DMA direct memory access

- DPR dynamic partial reconfiguration

- DPRAM dual-port random-access memory

- DPRM dynamic partial reconfiguration manager

- DRAM dynamic random-access memory

| DSP digital signal processor                           |

|--------------------------------------------------------|

| ELF Executable and Linkable Format                     |

| EMIO extendable multiplexed input/output               |

| eMMC embedded MultiMediaCard                           |

| EU execution unit                                      |

| FAR Frame Address Register                             |

| FDRI Frame Data Register, Input                        |

| FF flip-flop                                           |

| FIFO first in, first out                               |

| FPGA field-programmable gate array                     |

| FPU floating point unit                                |

| FSM finite state machine                               |

| HDL hardware description language                      |

| HWICAP Hardware Internal Configuration Access Port     |

| I/D instruction/data                                   |

| I/O input/output                                       |

| IC integrated circuit                                  |

| ICAP Internal Configuration Access Port                |

| IDE integrated development environment                 |

| IEC International Electrotechnical Commission          |

| IEEE Institute of Electrical and Electronics Engineers |

| ILA Integrated Logic Analyzer                          |

| IOB input/output block                                 |

| IP intellectual property                               |

| ISO International Organization for Standardization     |

- LC logic cell

- LUT look-up table

- MIO multiplexed input/output

- MMC MultiMediaCard

- MMU memory management unit

- NaN not a number

- OCM on-chip memory

- OS operating system

- PCAP Processor Configuration Access Port

- PL programmable logic

- PLD programmable logic device

- PR partial reconfiguration

- PRC partial reconfiguration controller

- PS processing system

- QSPI quad serial peripheral interface

- RAM random-access memory

- RISC reduced instruction set computer

- RM reconfigurable module

- **ROM** read-only memory

- **RP** reconfigurable partition

- **RTOS** real-time operating system

- SD Secure Digital

- SDK software development kit

- SDRAM synchronous dynamic random-access memory

- SoC system on a chip

| SoM system on a module                                                         |

|--------------------------------------------------------------------------------|

| SRAM static random-access memory                                               |

| SSD solid-state drive                                                          |

| TFTP Trivial File Transfer Protocol                                            |

| Torc Tools for Open Reconfigurable Computing                                   |

| UART universal asynchronous receiver-transmitter                               |

| USB Universal Serial Bus                                                       |

| <b>VHDL</b> Very High Speed Integrated Circuit Hardware Description Language   |

| <b>ViSARD</b> VHDL Integrated Softcore Architecture for Reconfigurable Devices |

| VLIW very long instruction word                                                |

XML Extensible Markup Language

## **Chapter 1**

## Introduction

Digital electronic systems have become an integral part of all kinds of devices ranging from small accessories to industrial machines, replacing and surpassing analog components in many domains. Their easier large-scale integration and superior resilience to noise allowed to overcome many challenges that were previously thought impossible with traditional analog electronics. Most devices require computation in some way, which is commonly performed by digital computers. Both analog and digital systems can theoretically offer an unlimited amount of computational precision, but in practice it is much easier to achieve high precision digitally, which is why analog computers are virtually irrelevant today.

Computers consist of one or more programmable processing elements, exemplified by the *central processing unit* (CPU) prevalent in personal and industrial computers. Depending on the application, these elements can vary fundamentally in their characteristics and implementation. Simple control systems use low-end processing elements that are fine-tuned to their requirements, while the CPUs of modern personal computers are very generic and can perform a great range of calculations extremely quickly.

As this example shows, there is plenty possibility for variation among processing elements and looking for the best option to solve a given problem is highly beneficial in terms of power usage, size, weight, and manufacturing cost of a device.

Contrary to big CPUs that are commonly produced as fixed-function chips to be placed on circuit boards (called *hard cores*), *soft-core* processors are primarily designed to be used on another class of integrated circuits called *programmable logic devices* (PLDs). Much like a processing element, PLDs can be programmed to perform any kind of computation, but at the hardware instead of the software level.

The benefits of using a PLD as opposed to a custom chip include increased flexibility and reduced cost when producing a small to medium number of devices only. The flexibility is a result of a characteristic of many PLDs: They can be configured not only once, but reconfigured as many times as needed. This reconfiguration may be limited to a part of the PLD and be performed while other parts continue operating, which is referred to as *dynamic partial reconfiguration* (DPR).

The goal of this thesis is to enable an existing soft-core processor design intended for a specialized set of applications (specifically: the *VHDL Integrated Softcore Architecture for Reconfigurable Devices* (ViSARD) developed at the Computer Architecture and Embedded Systems Group of Technische Universität Ilmenau) to make use of DPR by designing and implementing an extension to the processor that swaps out *execution units* (EUs) which perform specific arithmetic operations such as addition, multiplication, or division. It is conceivable that at least some algorithms may be split (naturally or by reordering independent operations) into stages in which a distinct set of mathematical operations is required. For example, one part of an algorithm may need to do a lot of multiplications, while another part may not require any multiplication at all and instead has to calculate the sine of many values. With the current static design of the ViSARD, all EUs that the program needs at some point in its calculations must be present at all times, meaning that they always occupy space in the PLD the core runs on.

With *partial reconfiguration* (PR), only the EUs that the current part of the program needs must be available. It is unknown whether this optimization of the ViSARD leads to significant resource/area savings in practice, which is why this thesis will evaluate how equivalent PR and non-PR designs compare in terms of device utilization.

In order to maximize the benefit of partial reconfiguration, special weight is put on the efficiency of the proposed solution. Concretely, the PR system design

- must require a minimal amount of additional resources for implementing reconfiguration so they do not cloud the potential savings,

- must complete reconfiguration as fast as possible to allow for rapid switching between sets of EUs,

- must not compromise the hard real-time capability of the ViSARD by the introduction of PR,

- must be able to run on the hardware available for testing (the Trenz Electronic GigaZee containing a Xilinx Zynq-7000 *field-programmable gate array* (FPGA)), but be easily adaptable to other platforms and

- should be reasonably uncomplicated in order to facilitate further research.

These goals will guide the design, the implementation, and the test setups and the interpretation of their results. In detail, the thesis is structured as follows:

Chapter 2 introduces the main building blocks that all further work is built on. These are primarily FPGAs, the ViSARD, and more high-level topics of digital systems design that are relevant to the design and the implementation of the proposed partial reconfiguration system are explained.

Building upon this information, Chapter 3 describes both the final system and how it was reached including the evaluated alternatives. Main subjects are the *partial reconfiguration controller* (PRC) performing the reconfiguration and how PR was integrated into the ViSARD.

In order to consider the practical implementation of the proposed design, Chapter 4 goes on to explain how an actually working system was achieved based on the considerations in the preceding chapter. Besides the hardware components, utility programs developed for use on the computer of the designer that make the realization of PR-based ViSARD designs feasible are introduced.

Chapter 5 presents tests of the PRC and the whole system in simulation and on hardware by describing both their setup and their results. These tests allow conclusions to be drawn about the resource savings achieved by PR and whether the goals as outlined above were reached. Furthermore, different bitstream generation methods (module-based and difference-based) are compared in terms of their advantages and disadvantages and resulting bitstream sizes.

Finally, Chapter 6 sums up the main findings and contributions of the present research and offers some possibilities for further consideration.

Floating-point numbers in this thesis follow the IEEE-754 standard [IEE08] and are always given in double precision (64 bits). The ViSARD itself allows selectable single or double precision, but only the latter is evaluated here as far as PR is concerned.

Multiples of byte units follow the international standard ISO/IEC 80000-13 [Int11] in combination with ISO/IEC 80000-1 [Int08], so for example 1 *kB* (kilobyte) equals 1,000 bytes, while 1 *KiB* (kibibyte) equals 1,024 bytes.

## **Chapter 2**

## **Fundamentals**

The purpose of this chapter is to introduce the devices and techniques used in this thesis, concentrating on the aspects that are fundamentally important: The first section will be about *field-programmable gate arrays* (FPGAs) (the type of device that this thesis is implemented on) and their components. After that, selected topics of digital hardware and systems design will be presented before giving an in-depth explanation of partial reconfiguration and finishing the chapter with a description of the *VHDL Integrated Softcore Architecture for Reconfigurable Devices* (ViSARD). Since it is not possible to describe everything from the ground up within the scope of this master's thesis, the reader is assumed to be familiar with the basic concepts of digital electronics such as Boolean logic.

### 2.1 FPGAs

Almost all modern electronic devices consist of one or more silicon *integrated circuits* (ICs). These are typically off-the-shelf components that are produced in large quantities in order to be profitable. They can have very generic functions such as in the case of a microprocessor or be designed for a narrower purpose, which makes them *application-specific standard parts* (ASSPs). Additionally, *application-specific integrated circuits* (ASICs) are specially constructed for one specific application and usually manufactured in smaller batches, so the production costs are very high. Prototyping new circuits is especially expensive when multiple iterations of troubleshooting and production are needed. In order to allow for a more flexible approach to development and manufacturing, simple *programmable logic devices* (PLDs) were sold as an alternative in as early as the 1970s. FPGAs are the most advanced type of PLDs and can be summarized as "digital ICs that contain configurable (programmable) blocks of logic along with configurable interconnects between these blocks" [Max08]. [Max08; Tar17]

#### 2.1.1 Overview

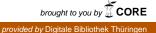

At the highest level, FPGAs consist of a "regular array of basic programmable *logic cells* (LCs) and a programmable interconnect matrix surrounding the logic cells" [Gro08]. Additionally, the pins of the device are connected to programmable *input/output* (I/O) cells that allow them to be used with various I/O standards for extra flexibility in communicating with other parts of a hardware system. This basic architecture is shown in Figure 2.1. Many additional components exist that will be explained in detail below.

**Figure 2.1:** Generic FPGA architecture. The programmable interconnect provides flexible connections between the logic cells and to the I/O cells. Additional components omitted for clarity. Adopted from [Gro08, fig. 1.16].

The logic elements can be connected together to form a circuit that realizes arbitrary functions when programmed accordingly. This is conceptually similar to a microprocessor which can likewise perform a wide range of functionality but is limited to sequential execution of a piece of software and a specific set of instructions that can be processed. In contrast, an FPGA operates at a much lower abstraction level with inherent parallelism, leading to better performance. This means that developing designs is vastly different from software programming and in many cases more complicated. In fact, microprocessors themselves can be implemented on FPGAs and it is common to do so in order to combine the benefits of both concepts. [Ker15; Max08]

Various companies are presently manufacturing FPGA devices, with the most relevant of them being Xilinx and Intel (formerly Altera). Naming of components varies between them: Xilinx, for instance, calls their logic cell equivalent *slice*, while Intel calls their equivalent *adaptive logic module* (ALM). Due to the hardware available for implementation, this thesis will focus on Xilinx devices. [Tar17; Xil16a; Max08]

FPGAs are used e.g. for faster and cheaper prototyping of ASICs, but in modern electronics development they are not limited to that. Owing to their flexibility, low cost (compared to ASICs), and short time-to-market, they can be found not only in low-volume order-made devices and systems, but also in end-user products. Typical applications include communication devices, automotive equipment like driver assistance systems, and other systems that require high-performance digital signal processing. Compared to *central processing units* (CPUs), FPGAs are often used to implement algorithms and systems that would be difficult or too expensive to realize in software in an efficient manner. [Max08]

#### 2.1.2 Components

The following subsections will offer a rudimentary introduction to major components of FPGAs. A concise, but comprehensive description of these devices, the associated trade-offs and design flows can be found in the excellent book "FPGAs: Instant Access" by Maxfield [Max08], for example.

#### Logic cells

The basic building block of any FPGA, the logic cell, consists of at least one multi-input *look-up table* (LUT) that has one *flip-flop* (FF) register connected to it. A LUT is a simple digital logic element that is programmed with the desired output value for every possible combination of input values, so it can be used to realize arbitrary combinatorial binary logic functions. The flip-flop is a storage element that samples its input value at a clock edge and outputs it steadily for the duration of the whole clock cycle, even when the input changes intermittently. Via the routing fabric of the FPGA, the output of the flip-flop can in turn be connected to the input of another LUT. The combination and interconnection of these elements facilitates the building of arbitrary synchronous logic circuits such as state machines. Other architectures (e.g. using multiplexers instead of LUTs) are possible, but not discussed here. [Max08]

FPGA manufacturers usually build a hierarchy using these basic elements. Xilinx slices in 7 series devices, for example, contain 4 6-input LUTs and 8 flip-flops. Two slices are combined to form one *configurable logic block* (CLB). Slices also contain programmable multiplexers to allow for e.g. bypassing the flip-flop in the output path. [Xil16a]

#### **Embedded memory**

For storing larger amounts of data that would need too many flip-flops, the FPGA may include embedded *random-access memory* (RAM) modules called *block random-access memory* (BRAM). They can be combined to form larger memories and are typically realized as *static random-access memory* (SRAM), so they do not have any access latency and are very fast. Their number and size varies depending on the manufacturer and architecture of the device. [Max08]

#### Embedded multipliers/adders

Furthermore, advanced FPGAs will also contain embedded binary multipliers and adders as separate hardwired components. The reason for this is that realizing these functions in programmable logic is inherently slow. These are mainly useful for digital signal processing applications, which is why these blocks are called *digital signal processor* (DSP) slices at least by Xilinx. [Max08; Xil18a]

#### **Embedded processors**

Virtually every algorithm can be implemented in hardware (as digital logic), in software (as instructions run on a microprocessor), or using a mixture of both. The decision of which option to use to implement a given task typically requires, inter alia, a trade-off involving criteria such as performance requirements, economical constraints, and developer skills. In many cases, it is beneficial to combine digital logic and processors in order to get the best of both concepts. [Max08]

FPGA suppliers try to make it as easy as possible to take advantage of this combination without increasing system complexity too much by integrating embedded microprocessors in their devices. This is achieved in the following two ways:

- Hard-core processors are hardwired CPU cores integrated in FPGAs as separate blocks adjacent to or inside the fabric of programmable logic. They are mostly included in more expensive high-end chips. If the core is not a component of the FPGA, but plays a considerable role in the overall system, the device is referred to as system on a chip (SoC). [Max08]

- *Soft-core processors* are instantiated by the designer as entities in the programmable logic design. They get translated to FPGA resources like LCs and interconnect together with the rest of the design. Their performance and efficiency are usually inferior to equivalent hard cores, but they can be used in every project independent of the concrete FPGA chosen as long as it has enough resources. Another advantage is the possibility to adapt the soft core to the specific requirements of the use case, which is not possible with a hardwired CPU. As a consequence, it can be more efficient to use a specially parametrized soft core as opposed to a general-purpose hard core. The cores themselves may be provided by the FPGA supplier or obtained separately. [Max08]

#### **Routing resources**

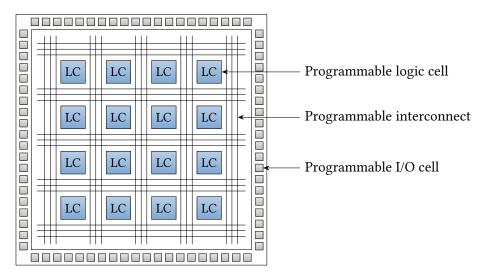

Interconnections between the logic elements are provided by the routing fabric of the FPGA. A typical structure can be seen in Figure 2.2. Routing resources are arranged in horizontal and vertical lines, forming a grid with LCs inside it. The interconnect boxes contain programmable switch matrices that can form connections between the lines entering and exiting on each side with varying degrees of flexibility according to the concrete FPGA architecture. This way, connections across the whole device are possible. [FMM12]

Figure 2.2: FPGA fabric with logic cells and interconnect (zoomed-in version of Figure 2.1). Adopted from [Max08, fig. 2-1].

#### Utilization

To any designer, the amount of resources used on the FPGA is of great importance. If the device is not utilized to a satisfying degree, it effectively means that money could be saved by choosing a smaller one. The prime measurement for resource utilization is the absolute amount or percentage of component instances used by a given design. The components most interesting to consider for this were outlined above: logic slices (possibly broken down to LUTs and flip-flops), BRAM, and DSP slices. Due to timing restrictions and the limited availability of routing resources, a logic utilization of 100 % is not practical [DeH99].

### 2.1.3 Configuration

The programmability of FPGAs is realized by configuration cells inside the components that e.g. indicate to a LUT to which inputs it should respond with a logic one or to a routing matrix which lines to connect. This section will introduce both the general concept and specifics of Xilinx 7 series devices, since the FPGA this thesis was implemented on belongs to this family.

#### Overview

Most commercially available devices use configuration cells based on SRAM technology, allowing for an unlimited number of reconfigurations. The downside is that the configuration is volatile, i.e. it must be programmed into the FPGA after each power cycle. [Max08]

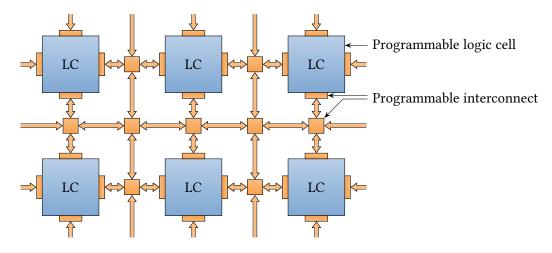

A dedicated *configuration controller* on the device accepts configuration data from inside or outside the chip and feeds it into the SRAM cells inside the device (Figure 2.3). These cells are typically organized in larger registers, so they cannot be accessed individually, but only in chunks. Modern FPGAs contain millions of such cells. Conceptually, an FPGA can be imagined to contain two layers: A functional layer consisting of all logic cells, interconnect, and functional units such as DSPs and below it a configuration layer consisting of 1-bit cells defining the operation and interconnection of the functional layer. The configuration data for SRAM devices is called *configuration bitstream* and is encoded in supplier/device-specific proprietary formats. [Max08; VF18; BLC07]

**Figure 2.3**: Relation of FPGA functional and configuration layer. The exemplary 3-input 1output LUT on the functional layer requires one configuration cell per possible input combination for a total of  $2^3 = 8$  cells on the configuration layer to fully define its behavior. The configuration controller can usually access these cells in chunks, but not individually.

#### **Specifics of Xilinx 7 series devices**

Logic elements in Xilinx 7 series FPGAs are tiled into 1 to 24 *clock regions* (depending on the device) that each contain a grid of CLBs 50 units high. Every clock region is interspersed with configuration cell register chains that run vertically through them from one end to the other (the direction may vary). One such register is the smallest addressable unit in the configuration memory of the FPGA and is called a *configuration frame*. All frames have the same length of

3,232 bits (404 bytes), but may contain different information such as LUT configuration, BRAM content, or routing matrix data.

The layout of different types of logic components within a clock region is columnar, with columns of DSP (each 20 units high) and BRAM (each 10 units high) resources inserted into the CLB grid. Additionally, interconnect resources for routing usually exist in-between every pair of columns. The exact configuration differs between clock regions and devices, but columns always run through the whole FPGA in the vertical direction, across clock regions. Figure 2.4 shows an exemplary column layout for illustration. [Xil18b; Xil18c; VF18]

Figure 2.4: Column layout inside the X0Y2 clock region of the Z-7020 FPGA (exemplary).

The format of the bitstream data is rudimentarily documented in [Xil18c]. It consists of 4-byte command words instructing the configuration controller to read or write one of its registers optionally followed by the data to write, again as 4-byte words. To program all configuration cells in the most basic fashion, the *Frame Address Register* (FAR) is set to zero (i.e. first frame in first clock region) and all configuration data is written to the *Frame Data Register, Input* (FDRI) in one batch. The controller will automatically cycle through all configuration cells in an undocumented order without requiring the FAR to be updated. To program a specific part of the device, the FAR register can instead be set to the address of the frame to write.

### 2.2 Digital hardware and systems design

Since the basic description of the hardware is concluded, the introduction moves one level of abstraction higher to the logic and systems to be implemented on top of FPGAs. This section begins with an outline of important concepts in digital systems design that are required for

the understanding of this thesis. Most of these topics are introduced in "FPGAs: Instant Access" [Max08]. More details regarding system level design and related topics are available in "Digital Systems Design with FPGAs and CPLDs" by Grout [Gro08]. Subsequently, the hard-ware used for implementation is introduced both on the device level (the Xilinx Zynq-7000) and the board level (the Trenz Electronic GigaZee).

#### 2.2.1 Key concepts and principles

#### Hardware description languages

For developing hardware designs for PLDs, it needs to be possible to describe the functionality of digital electronic circuits using a formalized language – due to the enormous size and complexity of FPGAs, manually configuring every logic slice is not feasible for all but the most simple designs. Every language that is primarily intended not for software development but for designing hardware is called a *hardware description language* (HDL). The two main alternatives in this field are Verilog-HDL and *Very High Speed Integrated Circuit Hardware Description Language* (VHDL), of which only the latter will be used here. The reader is assumed to be familiar with at least the basic concepts of VHDL. A practically oriented introduction to the language offers Kafig, for instance, in [Kaf11], while a thorough discussion of all aspects can be found in "The Designer's Guide to VHDL" [Ash08] by Ashenden. [Ker15; Gro08]

This thesis makes use of features added in the VHDL-2008 revision of the language standard as they allow for more concise and consistent code.

#### **Design flow**

As the HDL code cannot be directly put on the FPGA, the *design flow* when working with systems including FPGAs requires a transformation of this code into valid device-specific configuration data (Section 2.1.3). Major steps of this process (as seen in Figure 2.5) are: *Synthesis* which takes the HDL files and produces a *netlist* describing logic gates and their interconnections implementing the desired functionality, *implementation* which *places* the gates into logic cells and *routes* the required connections, and *bitstream generation* which produces the final configuration to program the actual FPGA device with.

#### Pipelining

An important concept to understand when working on hardware designs is *pipelining*. As combinatorial functions get more complex, they will span more and more LUTs and slices. Every

**Figure 2.5:** Major steps (synthesis, implementation, and bitstream generation) in a typical FPGA design flow, starting with code and ending with a bitstream to program the device. Simulation is possible after each step. Inspired by [Smi10, fig. 3-10; Gro08, fig. 1.20].

connection between those elements and every pass through a basic element such as a LUT takes some time and adds up to the total delay of the circuit, i.e. the time difference between changing an input value and the correct response appearing on the final output. The maximum frequency for which the combinatorial function can be correctly performed is approximately inversely proportional to this delay. [Max08]

Pipelining means that additional register (flip-flop) stages are inserted between stages of combinatorial logic. This breaks up the logic into smaller parts that can operate more efficiently and at higher maximum frequency, but it adds to the latency of the circuit. It will take as many clock cycles as there are stages until the output corresponding to a specific input value is ready to be consumed. Similarly to a car manufacturing line, a new operation can be started in every clock cycle, so the throughput is still high [Max08]. This technique can only be applied to combinatorial functions that have distinct separable stages. FPGA manufacturers such as Xilinx highly recommend pipelining, since it is cheap (their FPGAs include lots of flip-flops in slices anyway) and improves performance [Xil16a].

#### **Intellectual property**

As in software programming, it is common to use preexisting functional blocks in hardware designs. These are referred to as *intellectual property* (IP) or IP cores. They can for example be offered by companies for purchase, be included with the design suite of the FPGA supplier, or be available for free on the internet on web pages such as OpenCores [Oli18]. Furthermore, core generators may allow customizing the IP for the respective application by including or excluding certain features or allowing to set performance characteristics such as latency. [Max08]

#### **Bus systems**

Connecting functional blocks inside an FPGA or SoC would be very difficult without some standard protocols for communication. This is even more important for IP cores, since they need to be used in a variety of applications and system designers cannot be expected to learn a new method of communication for every core. Standard on-chip bus systems include *Advanced eXtensible Interface* (AXI) [ARM11] and AXI4-Stream [ARM10] by ARM Limited and Wishbone by OpenCores [Ope10]. Xilinx has decided to adopt AXI buses in their products (devices as well as IP) [Xil12].

In AXI terminology, each bus has a *master* and a *slave* side, with the master issuing read and write commands and the slave answering. Reading and writing uses separate channels, and each of these channels is further divided into an address and a data channel, plus one response channel for the writing direction for a total of 5 channels. The reading part of the interface is shown in Figure 2.6. The master initiates read transactions by specifying the initial read address and additional transfer parameters and the slave answers with the requested data (or an error indicator). The width of the address and data signal vectors can be chosen according to the application: Address width is arbitrary, while data width is limited to powers of two between a minimum of 8 and a maximum of 1,024 bits. [ARM11]

Figure 2.6: AXI read channel architecture. The master sends read requests on the read address channel which are answered by the slave in the form of (potentially multiple) data replies on the read data channel. Adopted from [ARM11, fig. A1-1].

Reads and writes are performed in bursts, i.e. each transaction has a burst length associated with it that specifies how many successive transfers are requested. In many cases, this is more efficient than requesting each transfer separately due to the reduced amount of round-trips and increased opportunity for pipelining and buffering. All channels include handshake signals that indicate when the source is sending valid data and when the sink is ready to accept it. The master does not need to wait for the response to a transaction to arrive to issue the next one, it can immediately signal a new request that the slave will process when ready, possibly in parallel to other ones. [ARM11]

#### **Real-time systems**

Practical systems, especially in digital signal processing applications, often have requirements concerning the time the system is allowed to take to react or perform certain operations. A system capable of achieving this is called a *real-time system*. Predictability of all components involved is key to achieve this, but fulfilling this may reduce the performance of the system on average.

Depending on the consequences that missing the deadline for finishing a real-time task would have, they are further categorized. Missing the deadline of a *hard real-time* task is most severe and will cause the system to behave erroneously, while the delayed response of a *firm real-time* task means that the result cannot be used any more. The third and final category of *soft real-time* tasks produces results that would at most cause decreased performance if not available by their deadline. Examples of systems with hard real-time requirements are safety-critical devices such as brake control in automotive vehicles or measurement instruments that need to process incoming sensor data without losing any information. [But11]

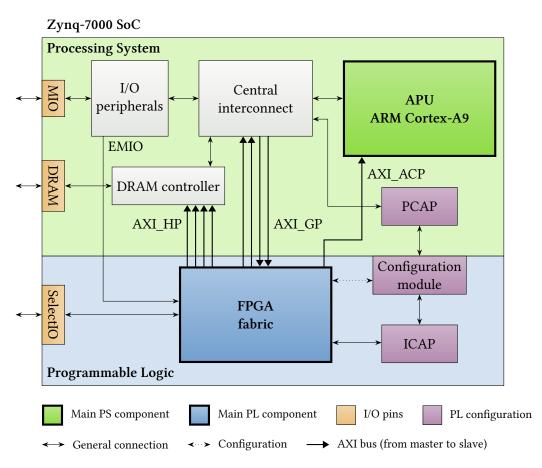

#### 2.2.2 The Zynq-7000 SoC

The Xilinx Zynq-7000 family, to which the device used for practical implementation in this thesis belongs, is comprised of SoCs that include an ARM Cortex-A9 based hard-core processor and a Xilinx 7 series based FPGA, with the ARM core being the central component and the FPGA acting as slave. The processor (also referred to as *application processor unit* (APU)), peripherals, and bus interconnect including memory controllers form the *processing system* (PS). The FPGA fabric and all supporting circuitry such as clock managers and the configuration module are in entirety called *programmable logic* (PL). [Xil18r]

#### Overview

A high-level overview of the SoC is shown in Figure 2.7. The FPGA is programmed by writing bitstream data to the PL configuration module via the *Processor Configuration Access Port* (PCAP) from the PS. Access to the module is also possible from the logic fabric using the *Internal Configuration Access Port* (ICAP). Furthermore, a *dynamic random-access memory* (DRAM) controller is included in the PS to easily access external *double data rate* (DDR) memory from both parts of the SoC. Communication between them is possible using a number of dedicated AXI buses. Moreover, both the PS and PL include their own separate I/O blocks and associated device pins, called *multiplexed input/output* (MIO) for the PS and SelectIO for the PL. A part of the functions of the MIO pins can be redirected to the PL using the *extendable multiplexed input/output* (EMIO) interface, but the reverse is not possible. [Xil18s]

Figure 2.7: Zynq-7000 SoC overview highlighting interconnections between processing system and programmable logic. APU: Application processor unit, EMIO: Extendable multiplexed input/output, ICAP: Internal Configuration Access Port, MIO: Multiplexed input/output, PCAP: Processor Configuration Access Port. Adopted from [Xil18s, fig. 1-1] (reduced to components relevant for this thesis).

In detail, the AXI buses crossing between the PS and PL part of the SoC are (as seen from the PL side, from left to right in Figure 2.7): [Xil18s]

- 4x AXI\_HP: 32-bit or 64-bit high performance/bandwidth master ports that can access only the DRAM controller and a small amount of *on-chip memory* (OCM) inside the APU,

- 4x AXI\_GP: 32-bit general purpose ports (2x master, 2x slave), and

- 1x AXI\_ACP: 64-bit cache coherent master port (accelerator coherency port (ACP)).

Xilinx recommends to use the AXI\_HP port for "high performance *direct memory access* (DMA) for large datasets", the AXI\_ACP for "high performance DMA for smaller, coherent datasets", and the AXI\_GP port for "PL to PS control functions [and] PS I/O peripheral access" [Xil18s].

#### Development

The digital logic development solution offered by Xilinx for all of their recent products starting with 7 series FPGAs and the Zynq-7000 SoC is the Vivado *integrated development environment* (IDE), part of the Vivado Design Suite. In addition to the hardware design, systems including the Zynq-7000 have to consider the software that is to run on the APU. At the very least, the PS is responsible for (initially) programming the PL. The Vivado Design Suite includes a separate *software development kit* (SDK) environment called Xilinx SDK (XSDK) including a complete toolchain (C/C++ compiler, debugger, utilities, and libraries) and an IDE based on the open-source Eclipse C/C++ Development Toolkit. [Xil18n; Xil15b]

One of the first and main points to consider is what kind of *operating system* (OS) to run on the processor. Generally speaking, the options are to run a bare-metal system (i.e. without any OS), a *real-time operating system* (RTOS), or a fully-fledged Linux OS. Xilinx facilitates each of these options by e.g. providing low-level drivers and an SDK for developing bare-metal applications and Linux drivers for easily using a high-level operating system. Using Linux will typically allow for easier development due to the abundance of available libraries and tools, but it does not directly support real-time constraints and increases system complexity. [Xil15b]

Using the Xilinx SDK environment, even applications running without an OS can be created with little effort. If the Zynq-7000 was configured in the hardware design in the Vivado design suite by way of the Processing System IP [Xil17e], the SDK will automatically pick up all important parameters such as the peripherals enabled and their memory mappings, so the designer does not have to set up anything manually. It will also generate boot loader code for initialization of the PS and its controllers and peripherals after power-up. The boot loader can be programmed to the start-up flash memory on the system board. [Xil15b]

#### Hardware used in this thesis

The hardware available for implementation in the present thesis is the TE-0720 GigaZee *system on a module* (SoM) by Trenz Electronic (Figure 2.8a) in combination with a TE-0703 carrier board (Figure 2.8b). The main module is equipped with a Xilinx Zynq-7000 family Z-7020 SoC, a Gigabit Ethernet transceiver, a 32 MB *quad serial peripheral interface* (QSPI) flash memory for storing the boot loader and system software, a 4 GB *embedded MultiMediaCard* (eMMC) for

(a) TE0720 SoM (top view). Source: [Treb]

(b) TE0703 carrier board (top view). Source: [Trea]

Figure 2.8: Hardware used in this thesis: TE0720, to be mounted on top of TE0703 (scale differs)

additional data storage, and 1 GB of *double data rate type three synchronous dynamic randomaccess memory* (DDR3 SDRAM). The FPGA inside the Z-7020 is based on the low-end Artix-7 series and provides 53,200 LUTs, 106,400 flip-flops, 4.9 Mb of BRAM, and 220 DSP slices. Power supply to the SoM and connection to Xilinx programming tools via a *Universal Serial Bus* (USB) cable are provided by the carrier board. [Tre17; Tre16; Xil18r]

The Z-7020 PL is divided into 6 clock regions as seen in the device overview in Figure 2.9. The layout of logic columns is not completely homogeneous across the device due to the differing sizes of the clock regions (see Figure 2.4 for the layout of the X0Y2 clock region as an example).

| PS  | X0Y2 | X1Y2 |

|-----|------|------|

| 10  | X0Y1 | X1Y1 |

| X0Y | 0    | X1Y0 |

**Figure 2.9**: Overview of Z-7020 SoC used in this thesis. The programmable logic is divided into 6 clock regions. The upper left corner is taken up by the processing system.

### 2.3 Partial reconfiguration

Configuration of FPGAs was already briefly explained in Section 2.1.3 when introducing their components, but there is a more advanced technique called *partial reconfiguration* (PR) that is a fundamental building block of this thesis. This section introduces the principle of reconfiguration including its further classification and focuses on partial reconfiguration, starting with its benefits and use cases. After discussing how this technique applies to Zynq-7000 devices, important considerations for PR designs are listed. For further reading and gaining a deeper understanding of this topic, a comprehensive book on this topic written by Koch in 2013 [Koc13] is recommended. A compact overview of the historical and recent developments in this field is offered in the summary "FPGA Dynamic and Partial Reconfiguration" [VF18] published in 2018.

### 2.3.1 Principle

First of all, the term *reconfiguration* refers to changing the configuration of an FPGA that is already configured. *Global reconfiguration* exchanges the whole design, while *partial reconfiguration* only exchanges the configuration in some part(s) of the FPGA. Typically, global reconfiguring leads to a complete loss of internal state and necessitates a shutdown/initialization cycle of the logic running on the device. This is not the case with partial reconfiguration, as the part of the FPGA that is not exchanged (referred to as the *static logic*) retains all state. Only the actually reconfigured part (referred to as the *dynamic logic*) needs to be reinitialized if necessary. When the reconfiguration is classified as *dynamic partial reconfiguration* (DPR), the static logic will even continue to run normally and can perform tasks unrelated to the units that are being exchanged. The opposing concept, i.e. stopping the whole FPGA for the duration of the configuration change, is called *static partial reconfiguration*. Alternative terms for these concepts are *active* (i.e. dynamic) and *passive* (i.e. static) reconfiguration. [Di<sup>+</sup>12; Koc13; VF18]

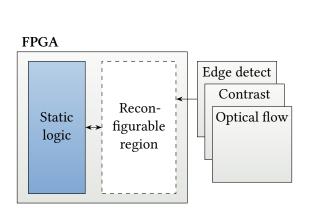

Partial reconfiguration can be beneficial for a number of reasons: Digital signal processing and cryptography applications may include parameters that can be modeled as connections in digital circuits that do or do not exist, i.e. they are practically equivalent to configuration bits in LCs. Partial reconfiguration can program those bits at run time in order to parametrize the module. This will typically result in lower resource usage than traditional means to achieve the same purpose such as additional input signals to the algorithm. Furthermore, reconfiguration of FPGA-based systems on a module level allows sharing of resources that are never used at the same time. This basic principle is illustrated in Figure 2.10a. An in-vehicle driver assistance unit will usually have to use image filters in order to process and act upon incoming picture data from various cameras. It might need an edge detection filter, a contrast enhancement filter, and an optical flow analysis filter, for example, as described in [Cla11]. Each is only usable in a specific driving situation, so they are never needed at the same time and having them occupy valuable FPGA resources permanently would be wasteful. An FPGA design with improved resource utilization using PR would be partitioned into static logic that is not reconfigured and dynamic logic in the form of one (or more) reconfigurable regions into which modules can be inserted at run time. When a module is to be exchanged, the surrounding system is tasked with sending a configuration bitstream to the configuration module of the FPGA. The component responsible for this task is typically called partial reconfiguration controller (PRC) (not to be confused with the previously introduced configuration controller that is a component of the FPGA hardware). If the PRC is operating from within the FPGA as part of the static logic, the process is classified as *self-reconfiguration*. From a high-level point of view, the reconfigurable region is like a stack of multiplexers for all signals going into and out of it (Figure 2.10b). Exchanging a module is equivalent to changing the selection of these multiplexers all at once.

Edge detect Contrast Optical flow Surrounding (static) system

Configuration module

(a) Principle of partial reconfiguration: A distinct region of the FPGA is designated as a reconfigurable region into which one of multiple implementations (in this example, of an image filter) can be inserted.

(b) Model of partial reconfiguration: The FPGA configuration module controls multiplexers on the reconfigurable region boundary that switch between multiple possible implementations all having the same interface. The whole operation is controlled by the surrounding (static) system.

Figure 2.10: Principle and model of partial reconfiguration. Adopted from [Koc13, fig 1.13].

In order to smoothly exchange these modules, all of them must have a compatible interface. On the HDL level, this typically means that all ports going in and out must be identical in name, type, and width. On the device level, in every module these ports must be routed to the same locations on the boundary of the dynamic logic area. Otherwise, the routes from and to the static design will not match up with the ones inside the dynamic logic and cause severe design malfunction akin to the likely crash of a software application when trying to load a software component that does not implement the expected interface.

Hardware and tools supporting DPR are at present only provided by Xilinx and Intel/Altera. A number of other FPGA manufacturers such as National Semiconductor, Lattice Semiconductor, and Atmel have previously offered this feature, but have since ceased to do so. Of the two remaining options, Xilinx FPGAs remain the most popular choice due to the company's long history of PR support initially offered already in 1995 in its XC6200 series. [VF18; Xil95]

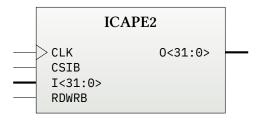

#### 2.3.2 Reconfiguration of Zynq-7000 devices

The FPGA inside the Zynq-7000 SoC is fully equipped for dynamic partial reconfiguration. It offers both external and internal interfaces connected to the PL configuration module that accept partial configuration bitstreams. In the context of this thesis no external components can be added, so only the internal ports are of interest. These are the PCAP for (re)configuring the FPGA from the PS and the ICAP for reconfiguring from within the FPGA design (see also Figure 2.7). They cannot both be used at the same time; which one of them is active is controlled by multiplexers accessible to the APU.

The primitive to instantiate for self-reconfiguration in HDL designs is called ICAPE2 for all Xilinx 7 series devices. Its input and output ports are documented in [Xil18i, p. 333] and are reproduced in Figure 2.11. For self-reconfiguration, the configuration data must be streamed to the 32-bit configuration input port I with the CLK port acting as clock while both the enable input CSIB and the read/write select input RDWRB are held low. Although the last part is not specifically documented, it can be inferred from the description of the equivalent RDWR\_B configuration pin on the device itself [Xil18c, p. 28]. The output port 0 is optionally used when reading data back from the FPGA e.g. for verifying the configuration. There are no handshake signals since the operation of the ICAP is completely deterministic and predictable. One 4-byte unit of data from a configuration bitstream is accepted on the input port in any given clock cycle.

Figure 2.11: ICAPE2 primitive for self-reconfiguration of 7 series devices. Ports are inputs on the left-hand side and outputs on the right-hand side. Angle brackets indicate ranges of vector ports. Adopted from [Xil18i, p. 333].

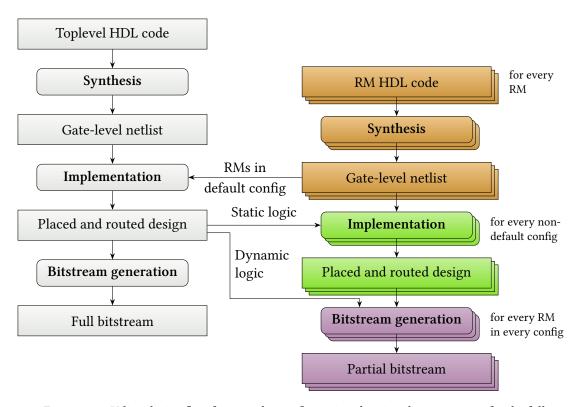

The Xilinx synthesis and implementation tools and the Vivado IDE support partial reconfiguration in principle when a separate PR license has been purchased. There are, however, a number of limitations which are outlined further below. The workflow is described in detail in the Vivado partial reconfiguration user guide [Xil18m] and a hands-on tutorial [Xil18k] is also offered. The basic idea is that entities in the design hierarchy can be marked as *reconfigurable partitions* (RPs), which turns them into slots to which multiple different implementations (that are referred to as *reconfigurable modules* (RMs)) must be assigned.

The complete tool flow is illustrated in Figure 2.12: The IDE will first run synthesis for every RM declared. After that, it will implement a complete design including one initial (default) RM of choice for each reconfigurable partition and write a full bitstream using the traditional non-PR flow, with the primary difference being that for the RM instances, the gate-level netlists of the preceding synthesis runs are used. After that, for each non-default *configuration* (assignment of RMs to RPs specified by the designer), implementation is run reusing the static part of the initial design results. Finally, a partial bitstream per RM in every configuration (including the default one) is written.

**Figure 2.12**: Xilinx design flow for partial reconfiguration showing the major steps for the full initial design (left-hand side) and all reconfigurable modules and configurations (right-hand side). The process for the full bitstream is identical to the non-PR case (cf. Figure 2.5). For PR, synthesis is performed for every reconfigurable module, while implementation is performed for every non-default configuration and partial bitstream generation for every RM in every configuration.

The designer manually has to select and specify an area of resources (called *Pblock*) on the FPGA per RP that forms the reconfigurable region on the device. Only resources (concretely: CLBs, DSP slices, and BRAM) contained in the Pblock assigned to a reconfigurable partition are available for implementation of each individual module. Consequentially, the size of the Pblock has to be determined such that for each resource it includes at least the maximum amount used in any of the modules assigned to an RP. In terms of pure logic usage, this will usually be the most complicated (i.e. largest) module. Short of a small number of hardware constraints that may not be violated, the Pblock location within the device is up to the discretion of developer. A possible approach to guide the Pblock layout is to implement the design statically once using the largest module per reconfigurable partition and create Pblocks approximately where the reconfigurable module logic ended up being placed by the tools. [Xil18m]

Each signal crossing a reconfigurable partition boundary from static to dynamic design or viceversa is referred to as *partition pin* in Xilinx documentation. The locations of partition pins are determined automatically (although they can be specified manually) and are fixed after the initial design run. In earlier PR workflows, it was necessary to insert logic elements such as LUTs or flip-flops into the dynamic logic that would form the endpoint for routes from the static region. These elements were called *proxy logic*. The Vivado Design Suite has overcome this requirement and made these techniques obsolete, so the partition pins supposedly do not generate any logic overhead. [Koc13; Xil18m]

The Xilinx tools ensure adherence to a set of strict rules guaranteeing that the PR design works in practice. For the purposes of this thesis, the following restrictions are especially relevant: [Xil18m]

- Optimization algorithms may not cross the boundaries of reconfigurable partitions and their associated Pblocks.

- Logic elements of the static design may not be placed into the area of a reconfigurable partition to ensure that all resources in the partition are available for implementing the function of the modules and that the static logic is unaffected by switching between modules.

- Similarly to routes to partition pins, routes of the static design that run through a reconfigurable Pblock (called *feed-through routes* [RFG16]) must be fixed after the initial implementation and stay exactly the same in all modules. Otherwise, the static design would cease functioning as soon as an incompatible implementation has been loaded.

- Routes of reconfigurable modules must be contained entirely within their Pblocks.

These rules are followed by the Xilinx tools, but they must in principle be implemented by any synthesis software supporting partial reconfiguration.

#### 2.3.3 Limitations and trade-offs

Partial reconfiguration as a technique is not very widely employed in commercial applications yet [Koc13; VF18]. This section will discuss some possible reasons and which important tradeoffs have to be made when considering whether to use PR in a design.

Multiplexing FPGA resources in the time domain on the one hand allows significant area and power savings, reduces cost by potentially allowing a smaller device to be chosen, and increases design flexibility. On the other hand, there are a number of considerations to make:

• Reconfiguring the logic takes a certain amount of time. At the most basic level, the time required for exchanging a module equals its partial bitstream size times the average configuration throughput. This throughput is limited by the lower of two parameters: The maximum throughput allowed by the configuration controller of the device (as indicated in its data sheet) and the maximum rate at which the supporting system can supply configuration data to this controller. Ideally, the bitstreams can be read and buffered at speeds exceeding the limit of the configuration controller to make sure that the system achieves the full potential of partial reconfiguration on the chosen FPGA.

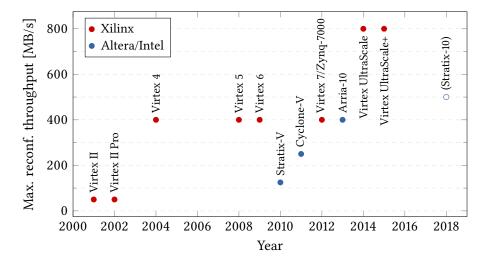

As far as the device throughput limit is concerned, Figure 2.13 shows the evolution of DPR throughput in commercial FPGAs of the biggest suppliers Xilinx and Intel/Altera during the past 20 years up to the newest devices at the time of the writing of this thesis (Virtex UltraScale+, Intel Stratix-10). It can be seen that speeds of the Virtex family did not improve at all for 10 years between 2004 and 2014.

**Figure 2.13**: Evolution of reconfiguration throughput of Xilinx and Altera/Intel FPGA families supporting dynamic partial reconfiguration. Adopted from [Bio<sup>+</sup>16, fig. 1]. For Xilinx, speeds are comparable for different families of the same generation. Intel figures are from [Alt18b; Alt18a; Int18b; Int18c; Int18a]. Stratix-10 devices are not generally available yet [VF18], so their reconfiguration throughput must be considered preliminary.

At the same time, FPGAs grew larger in size and consequently needed a greater amount of configuration data. To illustrate: The FPGA part of the Z-7020 used in this thesis has a total bitstream size of 4.05 MB, while it takes up 55.92 MB for the biggest Virtex-7 device. Reconfiguring 10 % of the devices at the maximum throughput of 400 MB/s would take 4.05 MB : 10 : 400 MB/s = 1.0 ms and 55.92 MB : 10 : 400 MB/s = 14.0 ms, respectively. To put this into a larger context, a system that processes a video stream in real time at 50 frames per second must finish each frame in at most 20 ms. Consequentially, a reconfiguration of 10 % of the device resources would be permissible only one time per frame for the big Virtex-7 FPGA. [Xil18q; Xil17f; Xil18c]

The latest UltraScale and UltraScale+ generation devices including the Zynq UltraScale SoCs have achieved significant progress by doubling the previous maximum throughput to 800 MB/s. The largest Virtex UltraScale device uses full bitstreams sized 128.97 MB, so a 10 % reconfiguration in this case would take 128.97 MB : 10 : 800 MB/s = 16.1 ms. Despite the vastly improved throughput, it still takes longer than for the previous generation due to the even larger increase in configuration data size. It is currently unclear whether reconfiguration throughput will be further improved for upcoming generations or if it will stay the same for a longer period of time again. [Xil18g; Xil18h; Xil18o]

The size of any partial bitstream is approximately proportional to the area the reconfigurable partitions contained in it occupy on the chip. Partitions of increased size and number will naturally lead to longer reconfiguration times. Finally, how often reconfiguration needs to be performed also influences the overall performance. Depending on the concrete usage scenario, a moderate throughput supported by a simple system design might be completely sufficient and not require the developer to reach the maximum speed of the device or buy a newer, more expensive FPGA. [Xil18m]

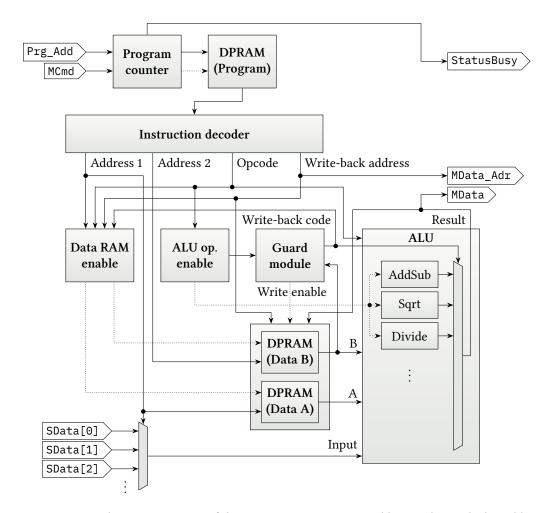

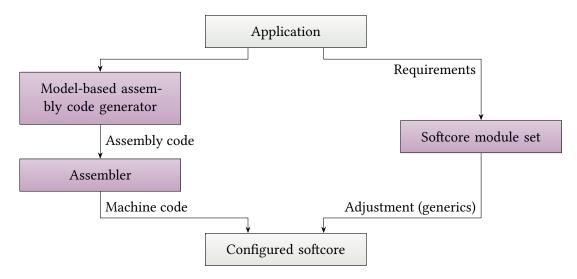

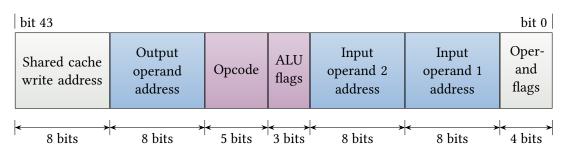

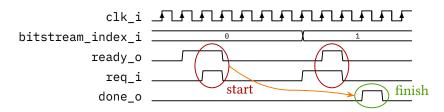

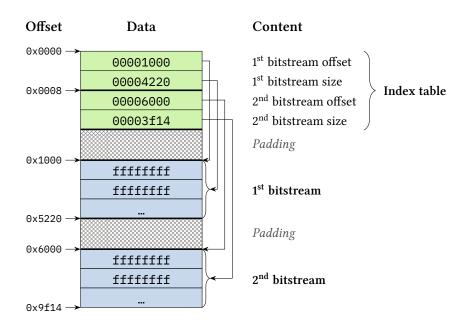

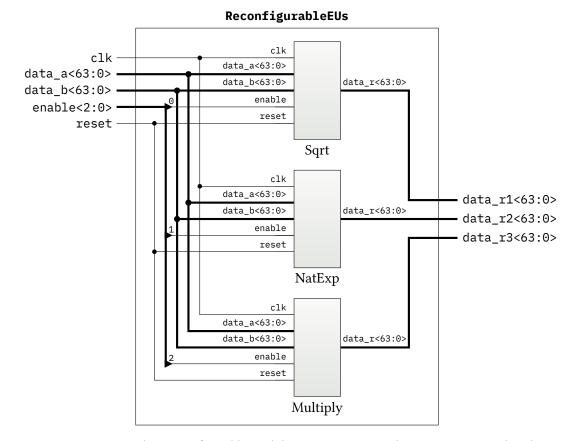

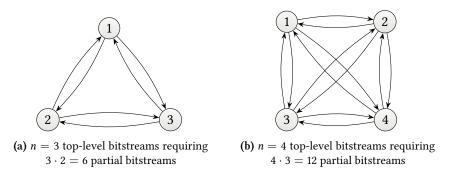

- Reconfiguring the logic requires energy. This aspect will not be considered further in this thesis. For observations on the energy cost of partial reconfiguration, see e.g. [NL16] which claims that the power consumption overhead is very small and [Bec<sup>+</sup>16] which presents measurement results for a Zynq-7000 SoC.