### GENERALIZED DATABASE INDEX STRUCTURES ON MASSIVELY PARALLEL PROCESSOR ARCHITECTURES

# DISSERTATION SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF

DOKTOR-INGENIEUR (DR.-ING.)

by Dipl.–Inf. Felix Beier

## TECHNISCHE UNIVERSITÄT ILMENAU FACULTY OF COMPUTER SCIENCE AND AUTOMATION

SUBMISSION DATE: 4TH OF DECEMBER, 2018 PHD THESIS DEFENSE: 15TH OF APRIL, 2019

#### READING COMMITTEE:

- 1. Univ.-Prof. Dr.-Ing. Habil. Kai-Uwe Sattler

- 2. Univ.-Prof. Dr.-Ing. Habil. Wolfgang Lehner

- 3. Dr. Götz Graefe

URN:NBN:DE:GBV:ILM1-2019000101

### **Abstract**

Index structures are ubiquitous in database management systems as well as in other applications that require efficient access methods in order to identify entries in large data volumes, which match specific search criteria. Height-balanced search trees represent one of the most important classes of indexes. They can be configured with various strategies for structuring the indexed search space for a given data set and for pruning it when different kinds of search queries are answered. In order to facilitate the development of application-specific tree variants, index frameworks, such as GiST (Generalized Search Tree), exist that provide a reusable library of commonly shared tree management functionality. By specializing internal data organization strategies, the framework can be customized to create an index that is efficient for an application's data distribution and data access characteristics. Because the majority of the framework's code can be reused, development and testing efforts are significantly lower, compared to an implementation from scratch. However, none of the existing frameworks supports the execution of index operations on massively parallel processor architectures, such as GPUs.

Enabling the use of such processors for generalized index frameworks is the goal of this thesis. By compiling state-of-the-art techniques from a wide range of CPU- and GPU-optimized indexes, a GiST extension is developed that abstracts the physical execution aspect of generic, tree-based search queries. Tree traversals are broken-down into vectorized processing primitives that can be scheduled to one of the available (co-)processors for execution. Further, a CPU-based implementation is provided as well as a new GPU-based algorithm that, unlike prior art in this area, does not require that the index is fully stored inside a GPU's main memory buffer, which is rather limited in size. The applicability of the extended framework is assessed for image rendering engines and, based on microbenchmarks, the parallelized algorithm performance is compared for different CPU and GPU generations. It will be shown that cases exist, where the GPU clearly outperforms the CPU and vice versa, depending on runtime-specific workload parameters.

In order to leverage the strengths of each processor type for mixed workload scenarios, an adaptive scheduler is presented that can be used to schedule index operations on a hybrid system, where multiple different processor devices exist. After an initial calibration phase that is used to train the scheduler's decision model, it is able to use this model to estimate total execution costs for a given operation and select the best device for it. With the help of a tree traversal simulation that models various query workloads, different scheduling strategies are evaluated. It will be shown that the adaptive scheduler can be used to make near-optimal decisions, increasing query throughputs by an order of magnitude and more, depending on the workload.

## Zusammenfassung

Index Strukturen sind allgegenwärtig in Datenbanksystemen und anderen Anwendungen, die eine effiziente Möglichkeit benötigen um in großen Datensätzen nach Einträgen zu suchen, die bestimmte Suchkriterien erfüllen. Suchbäume nehmen dabei einen bedeutende Rolle ein, da sie mit verschiedensten Strategien konfiguriert werden können um den Suchraum zu strukturieren und damit später die für ein Suchergebnis irrelevante Bereiche von der Bearbeitung ausschließen zu können. Die Entwicklung von anwendungsspezifischen Indexen wird durch Frameworks wie GiST unterstützt, welche wiederverwendbare Algorithmen zur Verwaltung von Baumstrukturen zu Verfügung stellen. Diese Frameworks können über interne Schnittstellen spezialisiert werden um Indexe zu modellieren, die speziell auf die Datenverteilung und Zugriffsmuster einer Anwendung zugeschnitten sind. Da dabei ein Großteil des Codes wiederverwendet werden kann, reduziert diese Art der Implementierung Entwicklungs- und Testkosten erheblich im Vergleich zu einer Neuimplementierung. Jedoch unterstützt keines der heute bereits existierenden Frameworks die Verwendung von hochgradig parallelen Prozessorarchitekturen wie GPUs.

Solche Prozessoren für generische Index Frameworks nutzbar zu machen, ist Ziel dieser Arbeit. Dazu werden Techniken aus verschiedensten CPU- und GPU-optimierten Indexen analysiert und für die Entwicklung einer GiST-Erweiterung verwendet, welche die für eine Suche in Suchbäumen nötigen Berechnungen abstrahiert. Traversierungsoperationen werden dabei auf vektorisierte Primitive abgebildet, die auf parallelen Prozessoren implementiert werden können. Die Verwendung dieser Erweiterung wird beispielhaft an einem CPU Algorithmus demonstriert. Weiterhin wird ein neuer GPU-basierter Algorithmus vorgestellt, der im Vergleich zu bisherigen Verfahren, ein dynamisches Nachladen der Index Daten in den Hauptspeicher der GPU unterstützt, da dieser in der Größe sehr beschränkt ist. Die Praktikabilität des erweiterten Frameworks wird am Beispiel von Anwendungen aus der Computergrafik untersucht und die Performanz der verwendeten Algorithmen mit Hilfe eines Benchmarks auf verschiedenen CPU-und GPU-Modellen analysiert. Dabei wird gezeigt, unter welchen Bedingungen die parallele GPU-basierte Ausführung schneller ist als die CPU-basierte Variante – und umgekehrt.

Um die Stärken beider Prozessortypen in einem hybriden System ausnutzen zu können, wird ein Scheduler entwickelt, der nach einer Kalibrierungsphase die erwarteten Ausführungszeiten einer Operation auf allen Prozessoren abschätzen und somit den geeignetsten Prozessor wählen kann. Mit Hilfe eines Simulators für Baumtraversierungen werden verschiedenste Scheduling Strategien verglichen. Dabei wird gezeigt, dass die Entscheidungen des kalibrierten Schedulers kaum vom Optimum abweichen und, abhängig von der simulierten Last, die erzielbaren Durchsätze für die parallele Ausführung mehrerer Suchoperationen durch hybrides Scheduling um eine Größenordnung und mehr erhöht werden können.

## **Danksagung**

An dieser Stelle möchte ich mich ganz herzlich bei allen bedanken, die mich bei der Erstellung der Arbeit unterstützt haben.

Allen voran meinem Doktorvater, Kai-Uwe Sattler, dessen Tür immer offen war um meine Fragen zu besprechen. Er sorgte auch stets für die nötige Motivation neben meiner regulären Arbeit und selbst nach Rückschlägen am Ball zu bleiben und die Dissertation erfolgreich fertigzustellen.

Weiterhin möchte ich auch Goetz Graefe und Ilia Petrov danken, die sich die Zeit genommen haben frühe Versionen meiner Dissertation zu lesen und mir wertvolles Feedback dazu zu geben. Insbesondere Goetz' Anmerkungen haben dafür gesorgt, den Fokus der Arbeit zu schärfen.

Ich möchte auch allen danken, die an zahlreichen Experimenten und Publikationen mitgewirkt haben: Sebastian Breß für die Arbeit am Scheduler, Hannes Rauhe für zahlreiche Experimente mit der GPU und Jens Teubner für seine Beiträge zum Hardware Kapitel.

Auch zahlreiche Studenten standen mir bei meinen Experimenten zur Seite: Torsten Kilias bei der Entwicklung der GiST Erweiterung, Daniel Löber bei der Parallelisierung der Nachbarschaftssuche; Steffen Hirte bei der Integration von GiST in POV Ray; Tafil Kaijtazi bei der Integration von GiST in Ogre3D.

Mein Dank gilt auch meinen ehemaligen Kollegen der TU Ilmenau: Stephan Baumann und Stefan Hagedorn für die vielen fachlichen Diskussionen im Eckbüro; Heiko Betz, Matthias Baag, Martin Sauerbrey und Peter Henkel für die Betreuung der Recheninfrastruktur; Markus Färber und Beat Brüderlin für ihre Unterstützung bei Computergrafik-Fragen; und natürlich den vielen anderen guten Geistern der Uni und des Fachgebietes Datenbanken & Informationssysteme.

Danke auch an meine IBM Kollegen, die mich unterstützt haben: insbesondere an Knut Stolze für die langjährige Zusammenarbeit und die Arbeit an zahlreichen Publikationen und Patenten; Oliver Draese und Jürgen Schimpf für ihre Unterstützung bei meiner Bewerbung um den IBM PhD Fellowship Award; meinen Managerinnen Corinna Peters und Anja Nicolussi, die mir so manches Mal geholfen haben Zeit für die Fertigstellung der Dissertation freizuschaufeln.

Zu guter Letzt gilt mein Dank natürlich meiner Familie und meinen Freunden, die mir im privaten Bereich den stets Rücken freigehalten haben. Insbesondere meine Partnerin, Linda Stocker, hat mir auf den "letzten Metern" sehr geholfen die Arbeit zügig zum Abschluss zu bringen.

#### Danke!

## **Contents**

| Al | bstrac            | ct                             |                  |  |   |  | iii |  |

|----|-------------------|--------------------------------|------------------|--|---|--|-----|--|

| Zι | isammenfassung iv |                                |                  |  |   |  |     |  |

| Da | anksaş            | ngung                          |                  |  |   |  | v   |  |

| 1  | Introduction      |                                |                  |  |   |  |     |  |

|    | 1.1               | Motivation                     |                  |  | ٠ |  | 2   |  |

|    |                   | 1.1.1 Search Operations in Lar | ge Data Sets     |  | ٠ |  | 2   |  |

|    |                   | 1.1.2 The Need for Index Fran  | neworks          |  | ٠ |  | 4   |  |

|    |                   | 1.1.3 Hardware-Accelerated Se  | earch Operations |  | ٠ |  | 7   |  |

|    | 1.2               | Contributions of this Thesis   |                  |  | ٠ |  | 8   |  |

|    | 1.3               | Focus of this Thesis           |                  |  | • |  | 9   |  |

|    | 1.4               | Structure of this Thesis       |                  |  |   |  | 9   |  |

| 2 | Bac | kgroun  | d – Parallel Processors and Coprocessors | 11 |

|---|-----|---------|------------------------------------------|----|

|   | 2.1 | Paralle | el Processor Architectures               | 12 |

|   |     | 2.1.1   | Multi-core CPUs                          | 13 |

|   |     | 2.1.2   | GPU Architecture                         | 15 |

|   |     |         | 2.1.2.1 Device Architecture              | 16 |

|   |     |         | 2.1.2.2 Processor Architecture           | 16 |

|   |     |         | 2.1.2.3 Memory Architecture              | 17 |

|   |     | 2.1.3   | Many-core CPUs                           | 20 |

|   |     | 2.1.4   | Field-Programmable Gate Arrays           | 21 |

|   | 2.2 | Hybrid  | d Systems                                | 23 |

|   |     | 2.2.1   | Processor Characteristics                | 24 |

|   |     | 2.2.2   | Memory Bus Systems                       | 24 |

|   |     | 2.2.3   | Hardware Limits                          | 26 |

|   |     | 2.2.4   | Other Aspects                            | 27 |

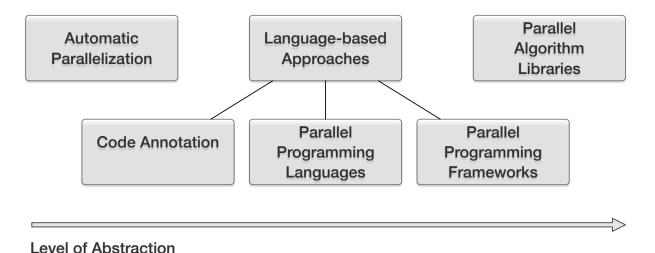

|   | 2.3 | Paralle | el Programming Models                    | 28 |

|   |     | 2.3.1   | Automatic Parallelization                | 29 |

|   |     | 2.3.2   | Parallel Programming Languages           | 29 |

|   |     | 2.3.3   | Parallel Programming Libraries           | 30 |

|   | 2.4 | The C   | UDA/OpenCL Programming Model             | 30 |

|   |     | 2.4.1   | Platform Model                           | 31 |

|   |     | 2.4.2   | Execution Model                          | 33 |

|   |     | 2.4.3   | Memory Model                             | 34 |

|   |     | 2.4.4   | Development Model                        | 36 |

|   |     | 2.4.5   | Comparison of CUDA and OpenCL            | 39 |

|   | 2.5 | Summ    | nary                                     | 41 |

| 3 | Rela | lated Work |                                                                  |               | 43 |

|---|------|------------|------------------------------------------------------------------|---------------|----|

|   | 3.1  | A Surv     | rvey of Index Processing Techniques on Different Processor Types |               |    |

|   |      | 3.1.1      | Indexing on CPUs                                                 |               | 45 |

|   |      |            | 3.1.1.1 Data Structure Organization                              |               | 45 |

|   |      |            | 3.1.1.2 Data Access Patterns                                     |               | 46 |

|   |      |            | 3.1.1.3 Parallelization of Index Operations                      |               | 47 |

|   |      | 3.1.2      | Indexing on GPUs                                                 |               | 47 |

|   |      |            | 3.1.2.1 Data Structure Organization                              |               | 47 |

|   |      |            | 3.1.2.2 Data Access Patterns                                     |               | 48 |

|   |      |            | 3.1.2.3 Parallelization of Index Operations                      |               | 50 |

|   |      | 3.1.3      | Indexing on Other (Co-)Processors                                |               | 51 |

|   |      | 3.1.4      | Indexing on Hybrid Systems                                       |               | 51 |

|   |      |            | 3.1.4.1 Static Scheduling                                        |               | 52 |

|   |      |            | 3.1.4.2 Dynamic Scheduling                                       |               | 53 |

|   |      | 3.1.5      | Summary – Common Implementation Techniques brid) CPU/GPU Systems | ` •           | 53 |

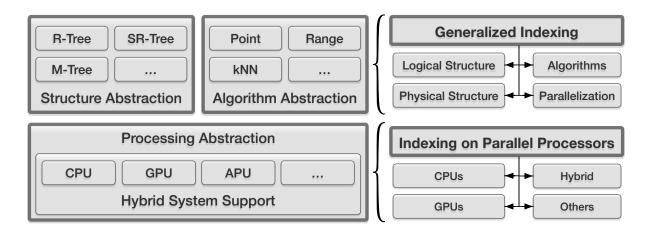

|   | 3.2  | Genera     | alized Indexing                                                  |               | 56 |

|   |      | 3.2.1      | Logical Structure Abstraction                                    |               | 57 |

|   |      | 3.2.2      | Physical Structure Abstraction                                   |               | 58 |

|   |      | 3.2.3      | Abstraction of Index Algorithms                                  |               | 59 |

|   |      | 3.2.4      | Transaction Support                                              |               | 60 |

|   |      | 3.2.5      | Parallelization of Index Algorithms                              |               | 60 |

|   | 3.3  | Discus     | ssion – Generalizing "Processing" in Generalized Inc             | ex Structures | 61 |

| 4 | Gen | eralized | l Processing in Generalized Index Structures                                          | 65 |

|---|-----|----------|---------------------------------------------------------------------------------------|----|

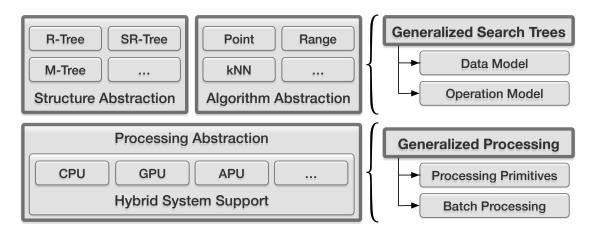

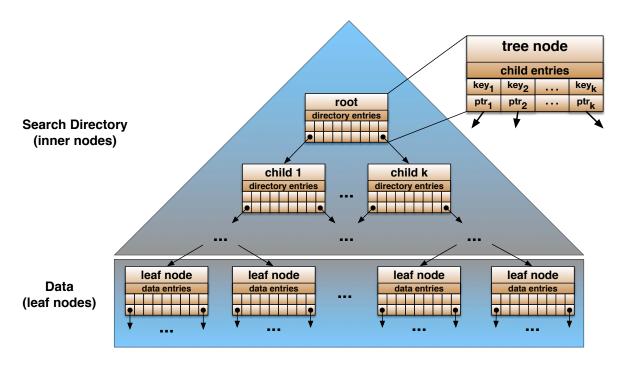

|   | 4.1 | Genera   | alized Search Trees                                                                   | 66 |

|   |     | 4.1.1    | Tree Data Model                                                                       | 66 |

|   |     | 4.1.2    | Tree Operations                                                                       | 67 |

|   |     |          | 4.1.2.1 Query Operations                                                              | 69 |

|   |     |          | 4.1.2.2 Tree Maintenance Operations                                                   | 71 |

|   |     |          | 4.1.2.3 Index Specialization                                                          | 73 |

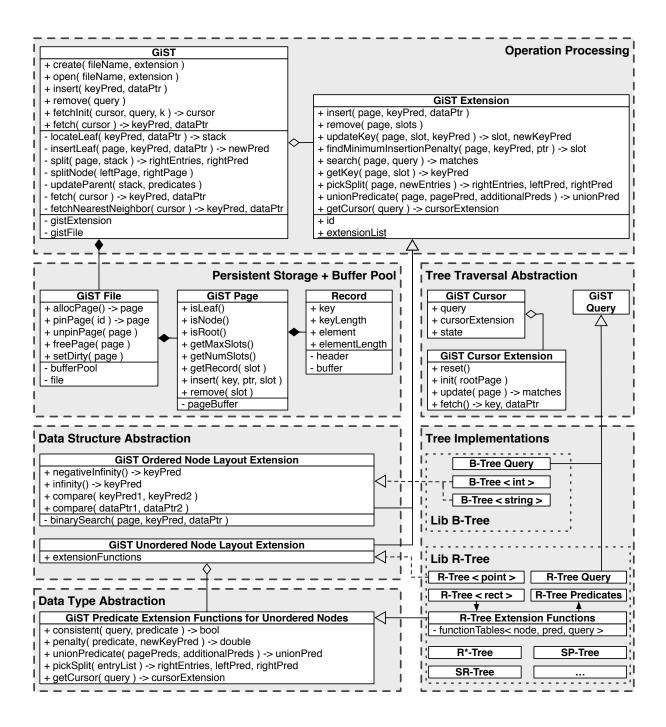

|   |     | 4.1.3    | GiST Architecture                                                                     | 74 |

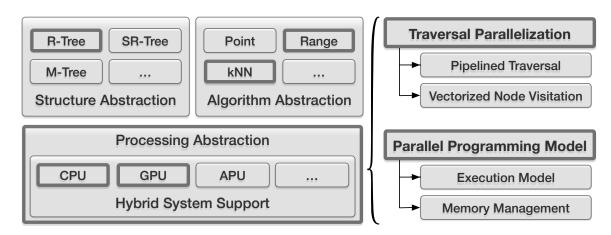

|   | 4.2 | Proces   | ssing Abstraction in Generalized Search Trees                                         | 76 |

|   |     | 4.2.1    | Index Structure Modifications                                                         | 78 |

|   |     | 4.2.2    | Index Operation Modifications                                                         | 78 |

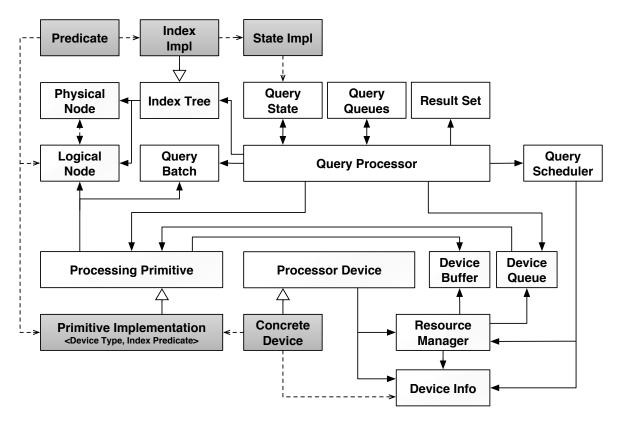

|   | 4.3 | Impler   | menting a Processing Abstraction Layer in GiST                                        | 80 |

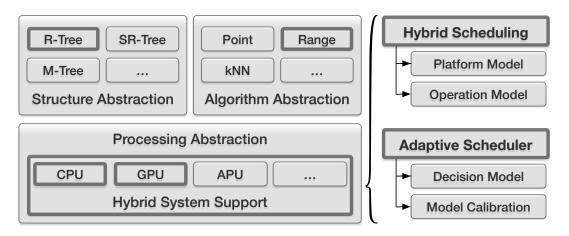

|   |     | 4.3.1    | Architecture Overview                                                                 | 80 |

|   |     | 4.3.2    | Index Components                                                                      | 82 |

|   |     | 4.3.3    | Query Components                                                                      | 83 |

|   |     | 4.3.4    | Processing Components                                                                 | 84 |

|   | 4.4 |          | ation – Applicability of the Extended Indexing Framework in Computer ics Applications | 85 |

|   |     | 4.4.1    | Framework Integration into Image Rendering Engines                                    | 85 |

|   |     | 4.4.2    | Profiling of Search Operations                                                        | 87 |

|   | 4.5 | Summ     | ary                                                                                   | 92 |

| 5 | A Pa | arallel I | Execution Model for Generalized Search Trees             | 93  |

|---|------|-----------|----------------------------------------------------------|-----|

|   | 5.1  | Paralle   | elizing Search Operations in Generalized Trees           | 94  |

|   |      | 5.1.1     | Parallel Search Tree Traversal                           | 94  |

|   |      | 5.1.2     | Vectorized Processing of Stateless Queries               | 95  |

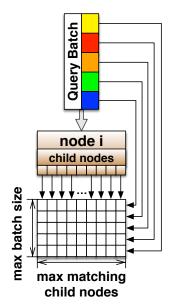

|   |      | 5.1.3     | Vectorized Processing of Stateful Queries                | 96  |

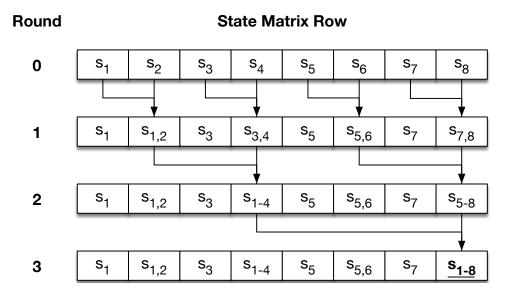

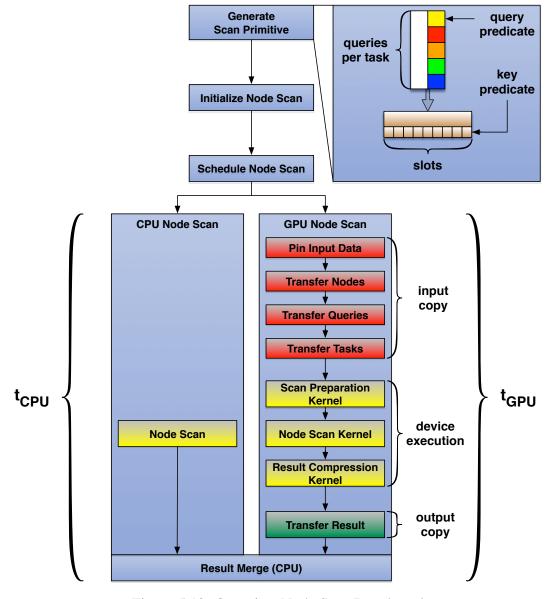

|   | 5.2  | Paralle   | el GiST Traversals with CUDA                             | 99  |

|   |      | 5.2.1     | Host Execution Model                                     | 99  |

|   |      | 5.2.2     | Device Execution Model                                   | 102 |

|   |      | 5.2.3     | Host Memory Management                                   | 107 |

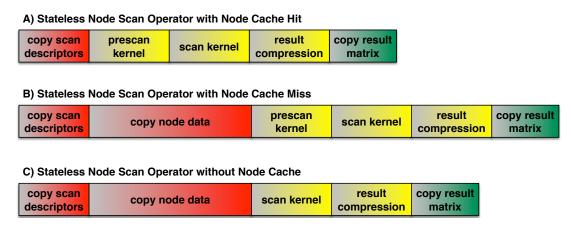

|   |      | 5.2.4     | Device Memory Management                                 | 108 |

|   |      |           | 5.2.4.1 Device Buffers                                   | 108 |

|   |      |           | 5.2.4.2 Scan Preparation                                 | 110 |

|   |      |           | 5.2.4.3 Shared Memory Buffering                          | 113 |

|   | 5.3  | Evalua    | ation – Parallel Search Tree Traversals on CPUs and GPUs | 113 |

|   |      | 5.3.1     | Setup – Node Scan Benchmark                              | 114 |

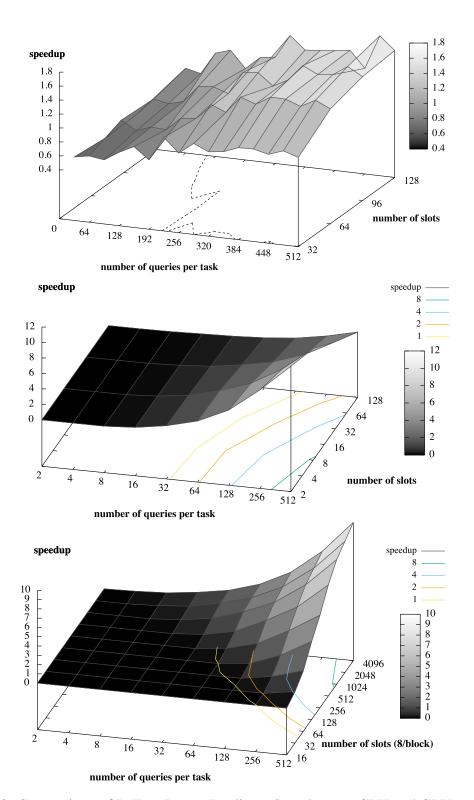

|   |      | 5.3.2     | CPU / GPU Speedup Analysis                               | 116 |

|   |      |           | 5.3.2.1 Comparison of Stateless Search Operations        | 116 |

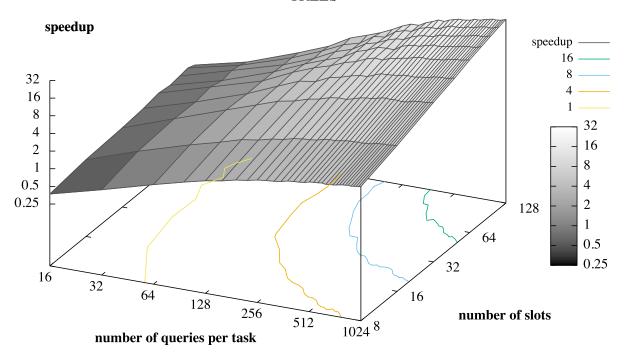

|   |      |           | 5.3.2.2 Comparison of Stateful Search Operations         | 119 |

|   |      | 5.3.3     | Query Throughput Analysis                                | 120 |

|   |      | 5.3.4     | Profiling Node Scan Phases                               | 122 |

|   |      | 5.3.5     | CPU / GPU Data Transfers                                 | 125 |

|   | 5 4  | Summ      | arv                                                      | 128 |

| 6 | Sche | eduling | in Hybrid  | CPU-GPU Architectures                                                       | 131 |

|---|------|---------|------------|-----------------------------------------------------------------------------|-----|

|   | 6.1  |         | 1          | on Scheduler for Hybrid                                                     | 132 |

|   |      | 6.1.1   | Platform   | Model                                                                       | 132 |

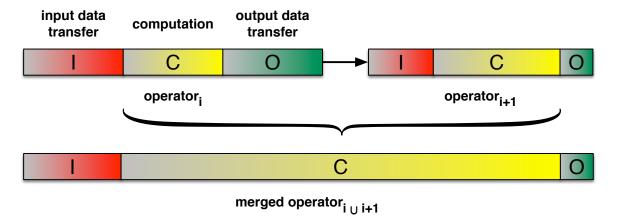

|   |      | 6.1.2   | Index Op   | eration Model                                                               | 133 |

|   |      | 6.1.3   | Index Op   | eration Scheduler                                                           | 136 |

|   | 6.2  | A Self- | -Tuning Sc | heduler Implementation                                                      | 137 |

|   |      | 6.2.1   | _          | and – A Hardware-Oblivious Operation Scheduling Framework d CPU/GPU Systems | 138 |

|   |      | 6.2.2   | An Adapt   | tive Index Operation Scheduler                                              | 140 |

|   |      | 6.2.3   | Decision   | Model                                                                       | 141 |

|   |      | 6.2.4   | Model M    | aintenance                                                                  | 142 |

|   | 6.3  | Evalua  | tion of Ge | neralized Query Traversals on a Hybrid CPU/GPU Platform .                   | 143 |

|   |      | 6.3.1   | Index Tra  | versal Workload Simulation                                                  | 144 |

|   |      | 6.3.2   | Decision   | Model Accuracy                                                              | 151 |

|   |      | 6.3.3   | Hybrid So  | cheduling Strategies                                                        | 152 |

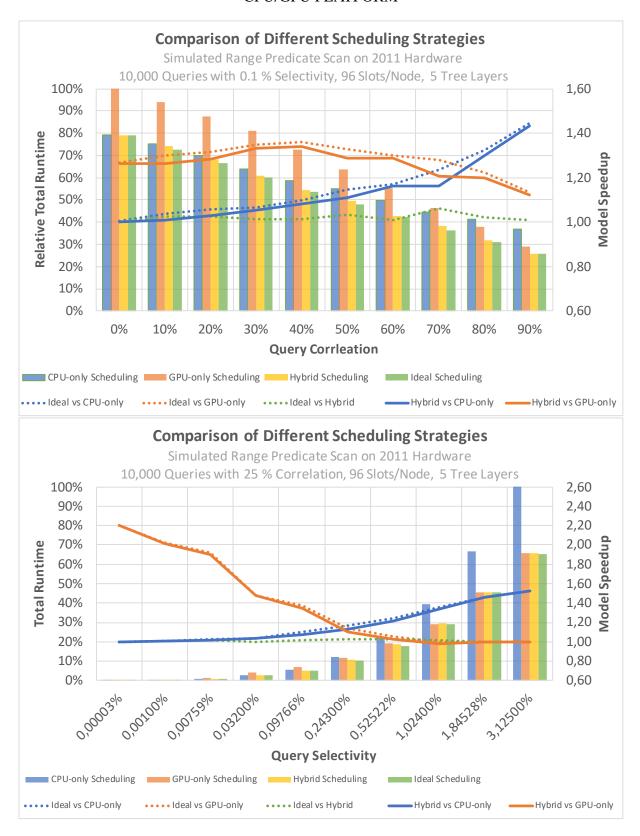

|   |      |         | 6.3.3.1    | Runtime Impact of Hybrid Decision Models                                    | 153 |

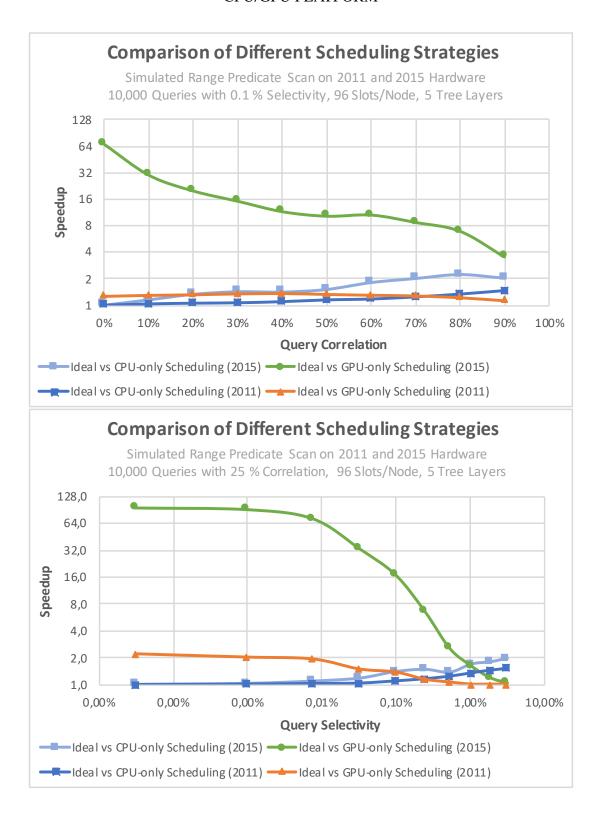

|   |      |         | 6.3.3.2    | Runtime Impact of Different Hardware Platforms                              | 157 |

|   |      |         | 6.3.3.3    | Runtime Impact of Batch Processing Strategies                               | 160 |

|   |      |         | 6.3.3.4    | Runtime Impact of Tree Parameters                                           | 166 |

|   |      |         | 6.3.3.5    | Runtime Impact of Query Parameters                                          | 172 |

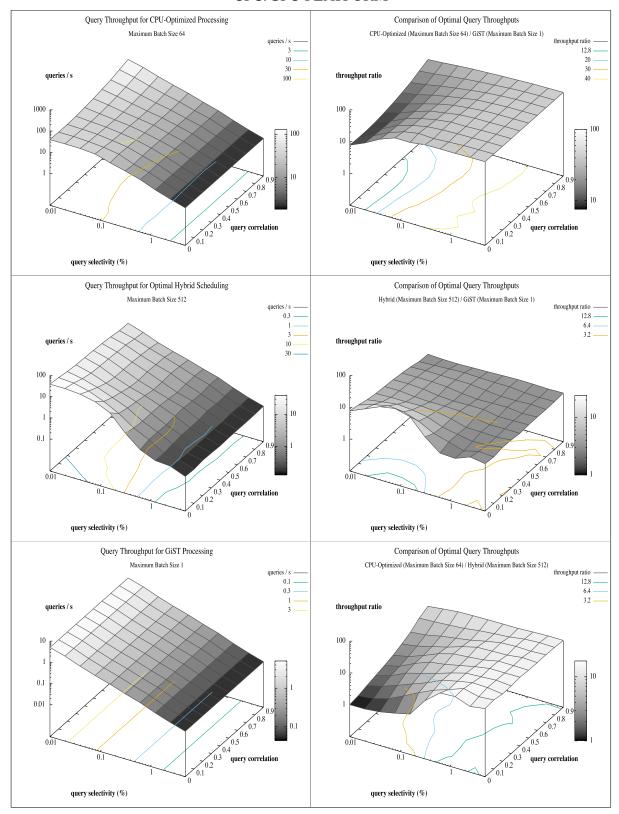

|   |      | 6.3.4   | CPU-Opt    | imization & Comparison with GiST                                            | 178 |

|   |      | 6.3.5   | Discussion | on of Hybrid Scheduling Evaluation Results                                  | 182 |

|   | 6.4  | Summ    | ary        |                                                                             | 183 |

| 7 | Con  | clusion | and Outlo  | ook                                                                         | 185 |

|   | 7.1  | Conclu  | ision      |                                                                             | 185 |

|   | 7.2  | Outloo  | k          |                                                                             | 186 |

| A | Glos | sary of | CUDA an    | d OpenCL Terminology                                                        | 187 |

|   | A.1  | Platfor | m & Hard   | ware-Related Terms                                                          | 188 |

|   | A.2  | Interac | tion betwe | en Host and Devices                                                         | 189 |

|   | A.3  | Execut  | ion Model  | Terminology                                                                 | 190 |

|   | A.4  | Memo    | ry Model T | Terminology                                                                 | 191 |

## Acronyms

**ADT** Abstract Data Type

**ALM** Adaptive Logical Module

**ALU** Arithmetic Logical Unit

**AoS** Array of Structures

**API** Application Programming Interface

**APU** Accelerated/Advanced Processing Unit

**ART** Adaptive Radix Tree

**AVX** Advanced Vector Extensions

**BFS** Breadth-First Search

**BVH** Bounding Volume Hierarchy

**CAD** Computer-Aided Design

**CAM** Computer-Aided Manufacturing

**CC-GiST** Cache-Conscious Generalized Search Tree

**CPU** Central Processing Unit

**CUDA** formerly Compute Unified Device Architecture

**DAG** Directed Acyclic Graph

**DBMS** Database Management System

**DFS** Depth-First Search

**dGPU** dedicated Graphics Processing Unit

**DMA** Direct Memory Access

**DPP** Data-Parallel Processor

**DSP** Digital Signal Processor

**FAST** Fast Architecture Sensitive Tree

**FPGA** Field-Programmable Gate Array

**GiST** Generalized Search Tree

**GPGPU** General-Purpose computation on Graphics Processing Units

**GPU** Graphics Processing Unit

**HT** HyperTransport

**ICD** Installable Client Driver

**iGPU** integrated Graphics Processing Unit

**JIT** Just In Time

LLVM LLVM compiler infrastructure project, formerly Low Level Vir-

tual Machine

MBR Minimum Bounding Rectangle

MIC Intel Many Integrated Core Architecture

**MPI** Message Passing Interface

**NUMA** Non-Uniform Memory Access

**Ogre 3D** Object-Oriented Graphics Rendering Engine

**OpenCL** Open Computing Language

**OpenGL** Open Graphics Library

**PCIe** Peripheral Component Interconnect Express

**POD** Plain Old Data Type

**POV-Ray** Persistence of Vision Raytracer

**QPI** Intel QuickPath Interconnect

**SaIL** Spatial Index Library

**SHM** Shared Memory

**SIMD** Single Instruction Multiple Data

**SIMT** Single Instruction Multiple Thread

**SM** Streaming Multiprocessor, sometimes SMX

**SMT** Simultaneous Multi-Threading

**SoA** Structure of Arrays

**SoC** System on Chip

**SP-GiST** Space Partitioning-Generalized Search Tree

**SPH** Space Partitioning Hierarchy

**SPMD** Single Program Multiple Data

SSE Streaming SIMD Extensions

**TD** Tag Directory

**VPU** Vector Processing Unit

VRAM Video RAM

**XXL** eXtensible and fleXible Library

## **List of Figures**

| 1.1  | History of Multidimensional Access Methods                | 5  |

|------|-----------------------------------------------------------|----|

| 1.2  | Overview of Contributions                                 | 8  |

| 2.1  | Overview of Parallel Processing Background Information    | 11 |

| 2.2  | Overview of Programmable Parallel Processor Architectures | 12 |

| 2.3  | Architecture of a modern multi-core CPU                   | 13 |

| 2.4  | Architecture of a dedicated GPU device                    | 15 |

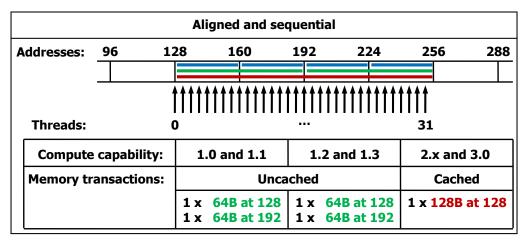

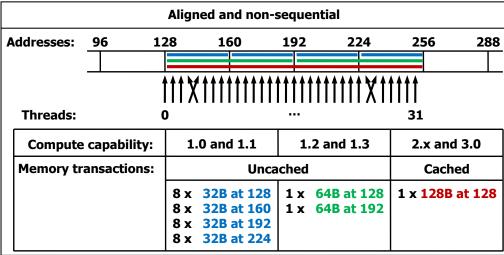

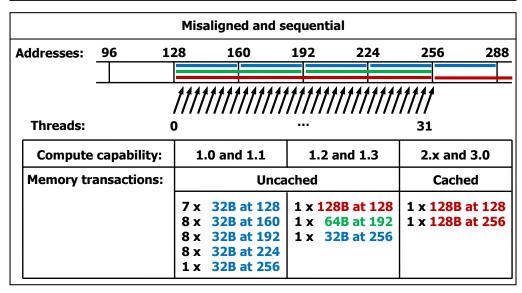

| 2.5  | Memory Access Patterns on a CUDA-capable GPU              | 18 |

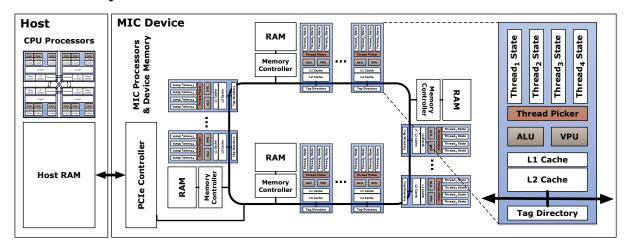

| 2.6  | Simplified architecture of an Intel MIC device            | 20 |

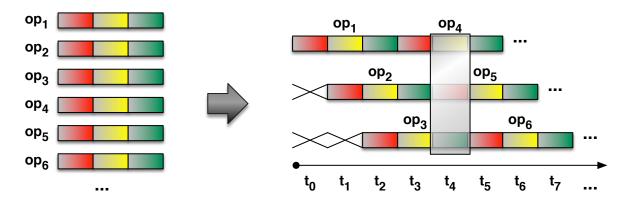

| 2.7  | Comparison of SIMD and Pipeline Parallelism               | 22 |

| 2.8  | Branching in SIMD and Pipeline Parallelism                | 22 |

| 2.9  | Pipelining of multiple Operations on GPUs                 | 25 |

| 2.10 | Overview Parallel Programming Models                      | 28 |

| 2.11 | Platform Model in OpenCL & CUDA                           | 32 |

| 2.12 | Execution Model in OpenCL & CUDA                          | 33 |

| 2.13 | Memory Model in OpenCL & CUDA                             | 35 |

| 2.14 | Development Model in OpenCL & CUDA                        | 37 |

| 3.1  | Overview of Related Work                           | 43  |

|------|----------------------------------------------------|-----|

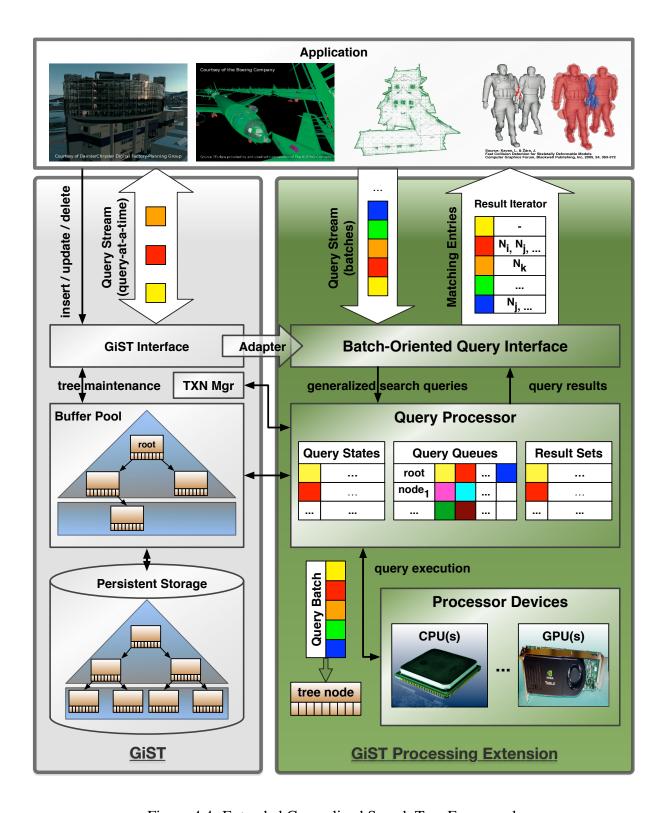

| 4.1  | Overview of the Index Processing Abstraction Layer | 65  |

| 4.2  | Logical Data Model of a Generalized Search Tree    | 67  |

| 4.3  | GiST Architecture Overview                         | 75  |

| 4.4  | Extended Generalized Search Tree Framework         | 77  |

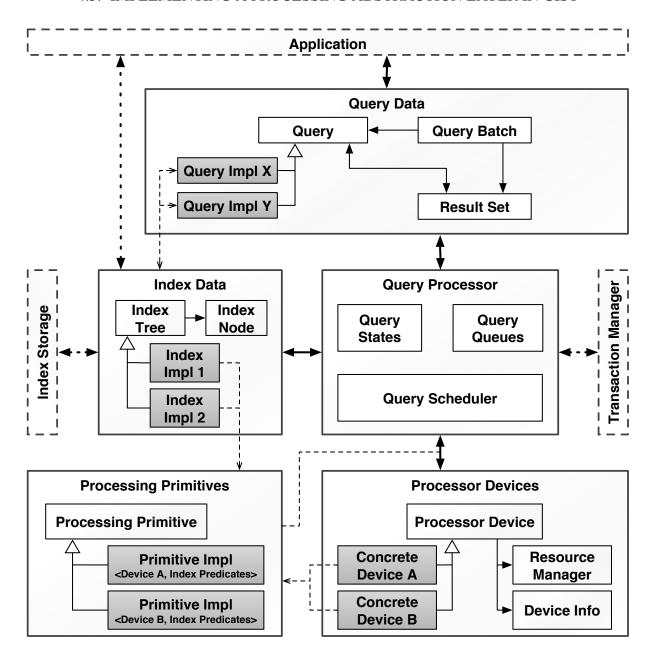

| 4.5  | Architecture Overview                              | 81  |

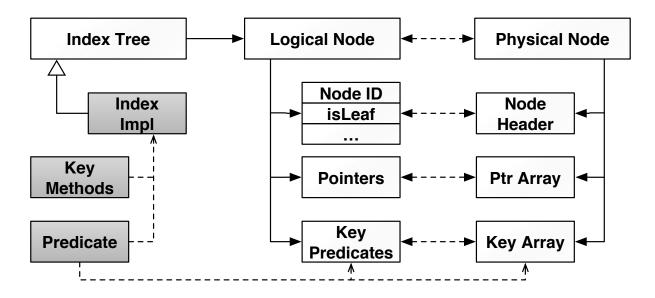

| 4.6  | Index Structure Components                         | 82  |

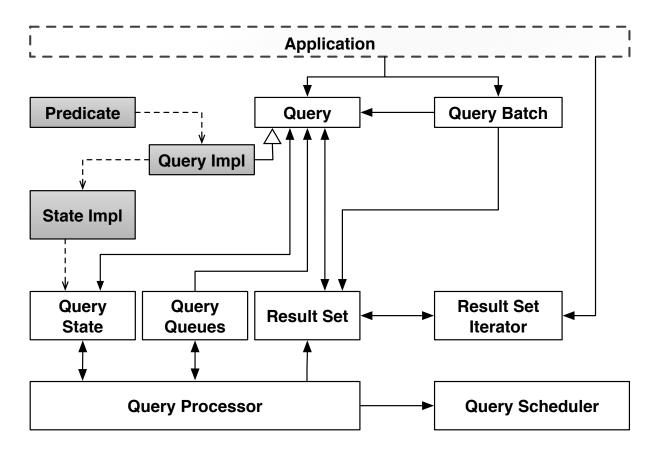

| 4.7  | Query Components                                   | 83  |

| 4.8  | Processing Components                              | 84  |

| 4.9  | Level-of-Detail Stanford Bunny                     | 86  |

| 4.10 | Ogre Head                                          | 87  |

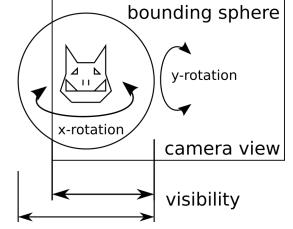

| 4.11 | Ogre Visibility Experiment                         | 87  |

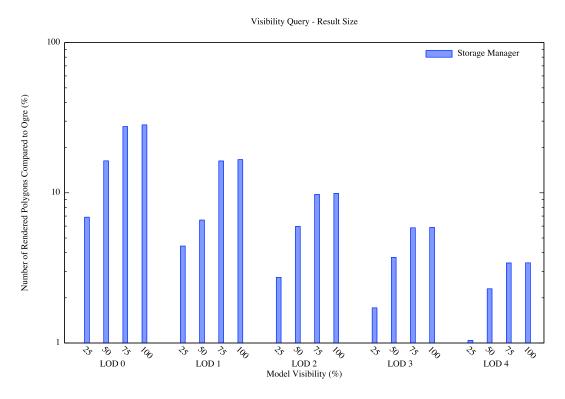

| 4.12 | Query Result Sizes with Varying Visibility         | 88  |

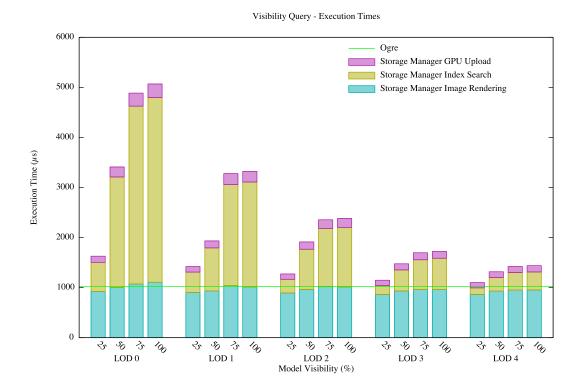

| 4.13 | Rendering Times with Varying Visibility            | 89  |

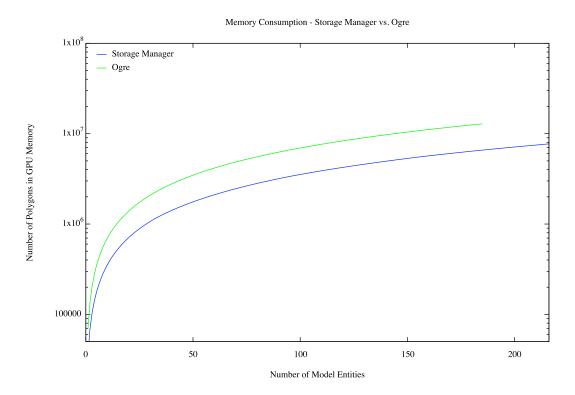

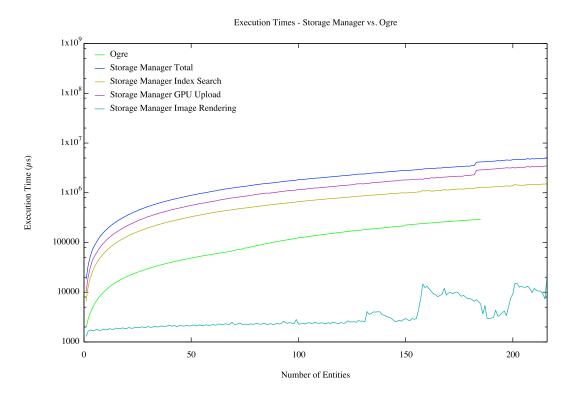

| 4.14 | Scalability Experiment: Memory Consumption         | 90  |

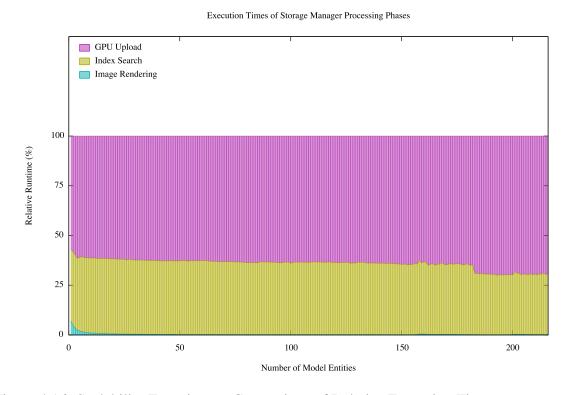

| 4.15 | Scalability Experiment: Absolute Execution Times   | 91  |

| 4.16 | Scalability Experiment: Relative Execution Times   | 91  |

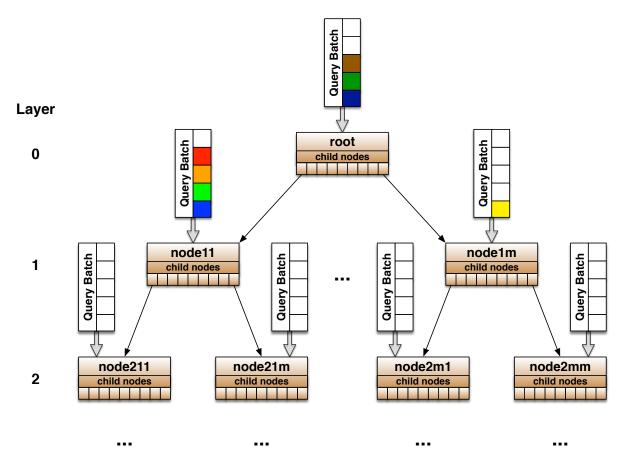

| 5.1  | Overview of the Parallel Index Execution Model     | 93  |

| 5.2  | Task & Pipeline Parallelism in Index Search        | 95  |

| 5.3  | SIMD Parallelism in Node Scan Primitives           | 96  |

| 5.4  | Parallel Query State Aggregation                   | 99  |

| 5.5  | Index Node Scan Mapping to CUDA                    | 102 |

| 5.6  | Coalesced Memory Transactions                      | 104 |

| 5.7  | Result Matrix Offsets for Inner and Leaf Node Scans                                                    | 105 |

|------|--------------------------------------------------------------------------------------------------------|-----|

| 5.8  | Result Post-Processing (Inner Node)                                                                    | 106 |

| 5.9  | Index Data Management on Host and Device                                                               | 107 |

| 5.10 | Device Buffers                                                                                         | 109 |

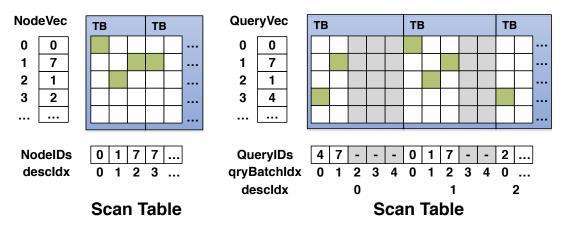

| 5.11 | Scan Preparation Phase                                                                                 | 111 |

| 5.12 | Overview Node Scan Benchmark                                                                           | 115 |

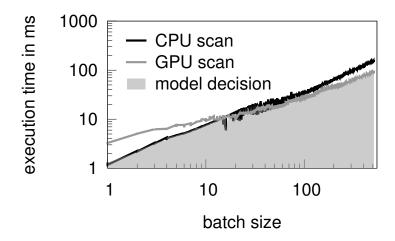

| 5.13 | Comparison of R-Tree Range Predicate Speedups                                                          | 118 |

| 5.14 | Comparison of R-Tree Nearest Neigbor Search on CPU and GPU                                             | 120 |

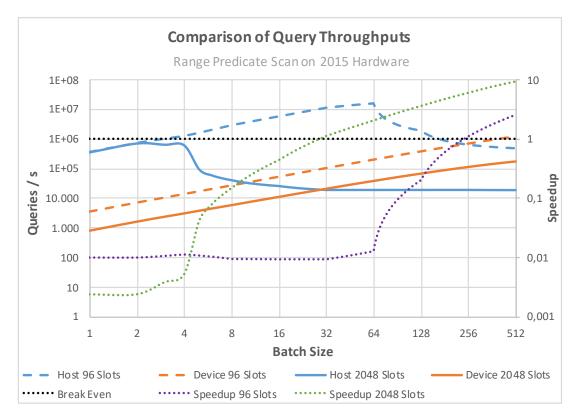

| 5.15 | Comparison of R-Tree Range Predicate Scan Throughputs                                                  | 121 |

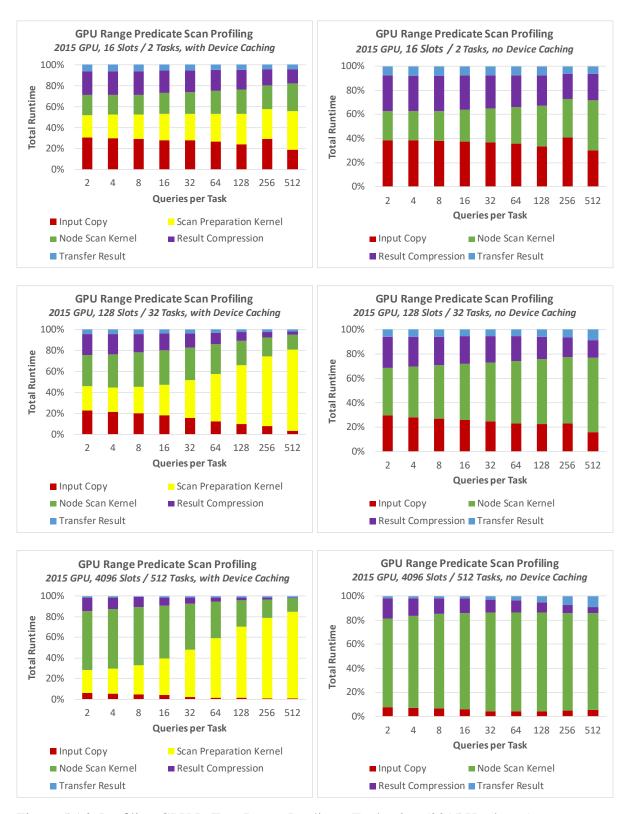

| 5.16 | Profiling GPU R-Tree Range Predicate Evaluation                                                        | 123 |

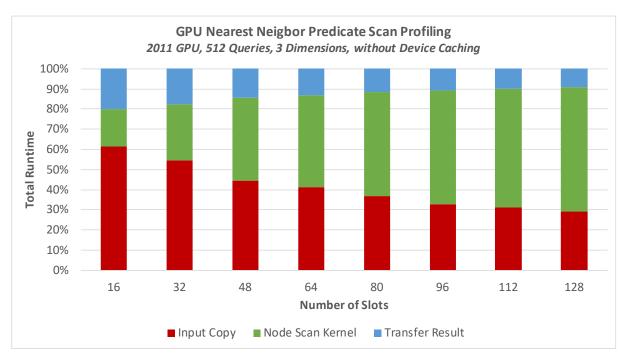

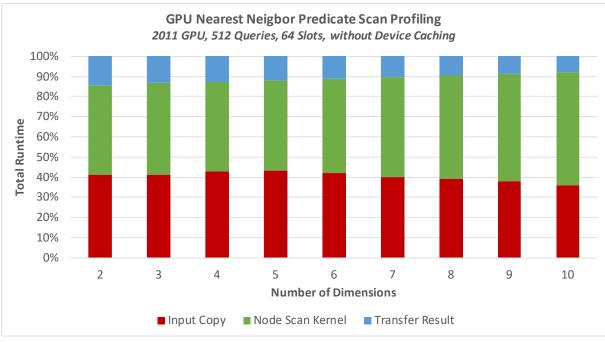

| 5.17 | Profiling GPU R-Tree Nearest-Neighbor Predicate Evaluation                                             | 126 |

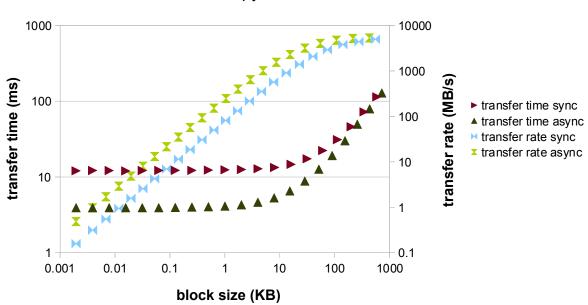

| 5.18 | $Host \rightarrow Device\ Data\ Transfer\ Benchmark\ for\ PCIe\ 2.0\ Bus \qquad . \ . \ . \ . \ . \ .$ | 127 |

| 6.1  | Overview of the Hybrid System Scheduler                                                                | 131 |

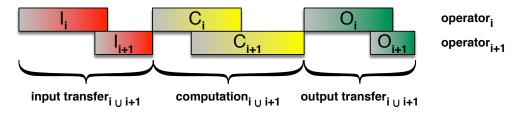

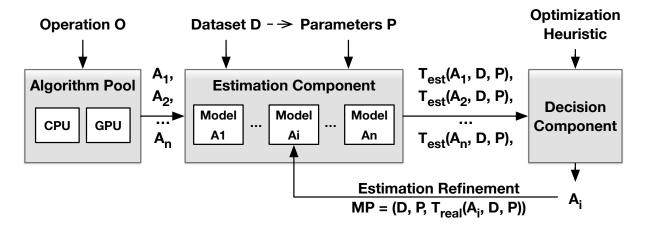

| 6.2  | Abstract Operator Model for Single Processing Primitives                                               | 133 |

| 6.3  | Operator Models For Stateless Node Scan Primitive                                                      | 135 |

| 6.4  | Operator Streaming Model for Multiple Processing Primitives                                            | 136 |

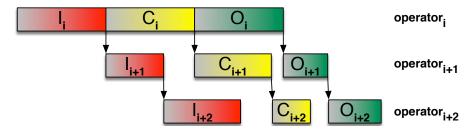

| 6.5  | Scheduler for Generalized Index Queries                                                                | 137 |

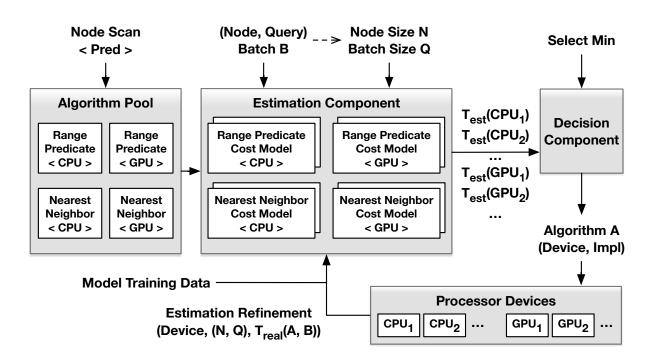

| 6.6  | Self-Tuning Operation Scheduler for Hybrid Platforms                                                   | 138 |

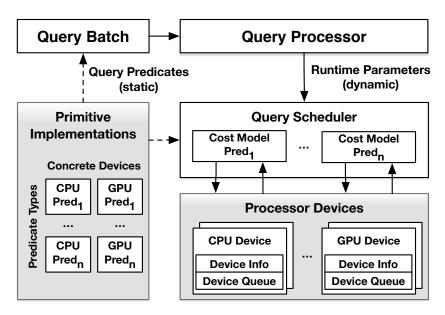

| 6.7  | Self-Tuning Index Operation Scheduler for Hybrid Platforms                                             | 139 |

| 6.8  | Simplified Black-Box Primitive Operator Model                                                          | 141 |

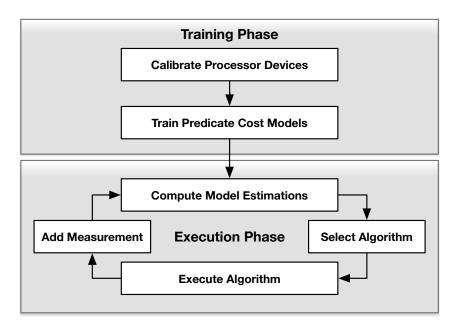

| 6.9  | Self-Tuning Scheduler Workflow                                                                         | 142 |

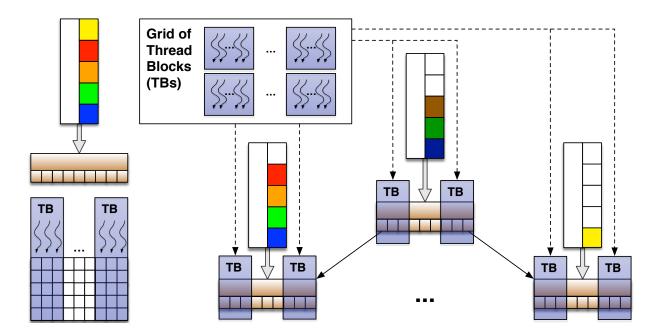

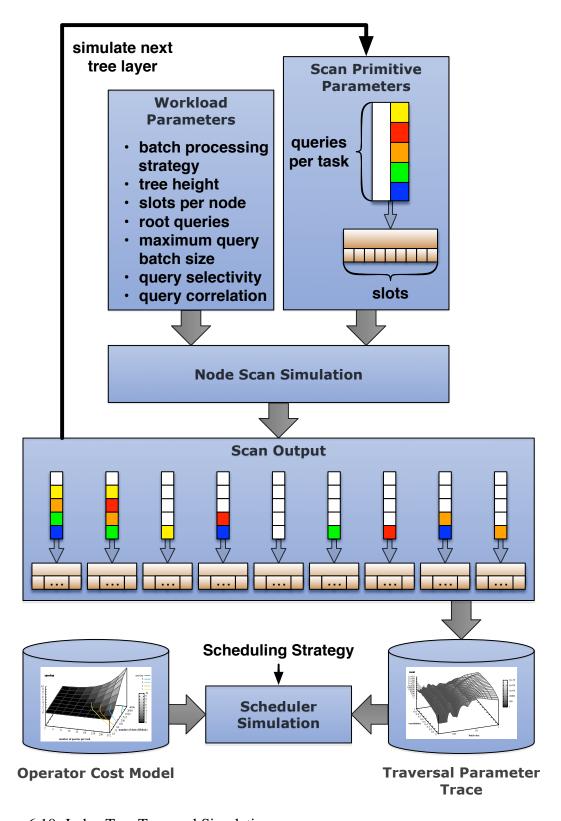

| 6.10 | Index Tree Traversal Simulation                                                                        | 145 |

|      |                                                                                                        |     |

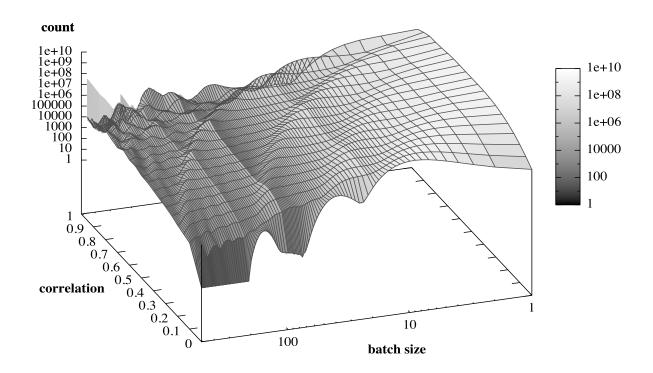

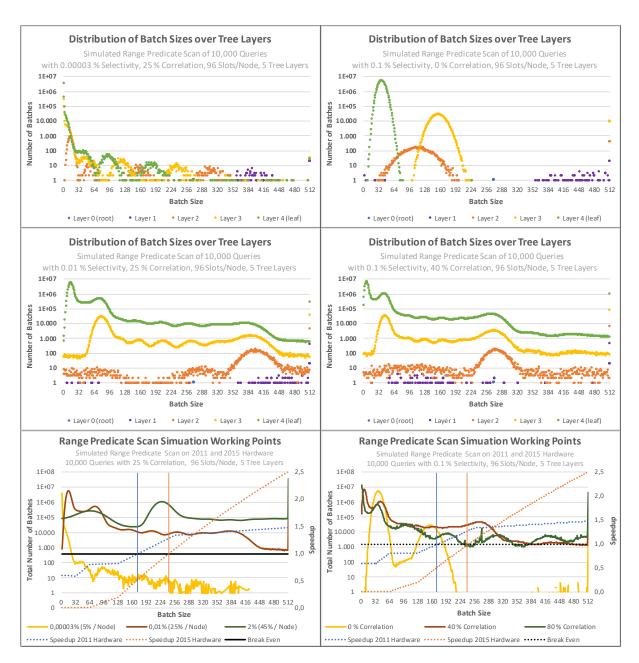

| 6.12 | Tree Traversal Simulation: Impact of Query Selectivity and Correlation             | 150 |

|------|------------------------------------------------------------------------------------|-----|

| 6.13 | Range Predicate Regression Model Decisions                                         | 151 |

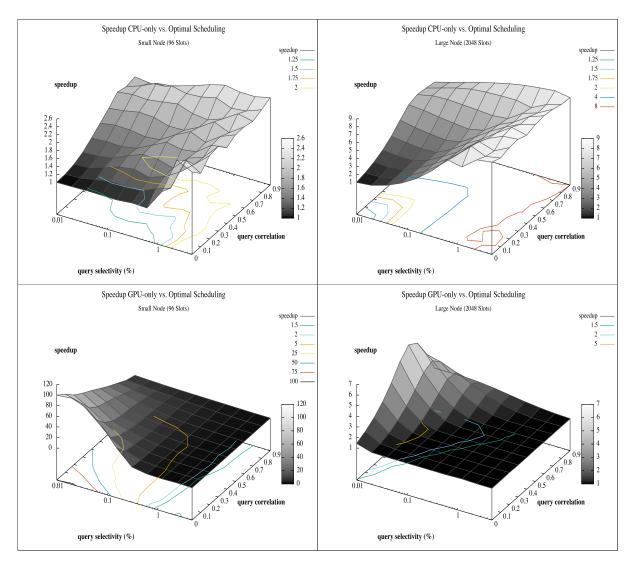

| 6.14 | Comparison of Different Scheduling Strategies on 2011 Hardware                     | 155 |

| 6.15 | Comparison of CPU, GPU, and hybrid Scheduling Strategies on 2011 and 2015 Hardware | 159 |

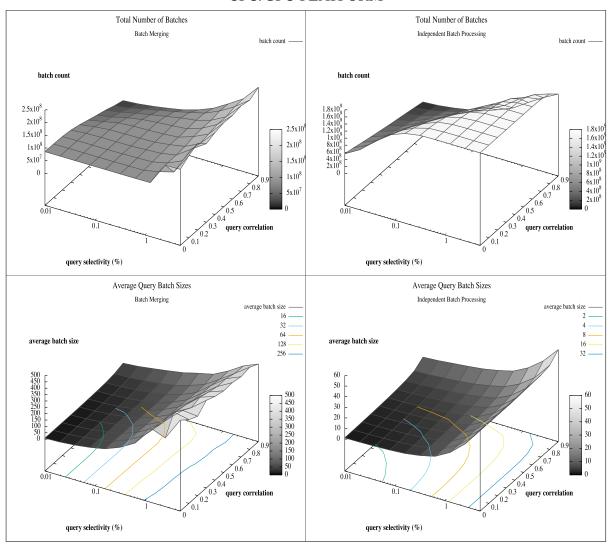

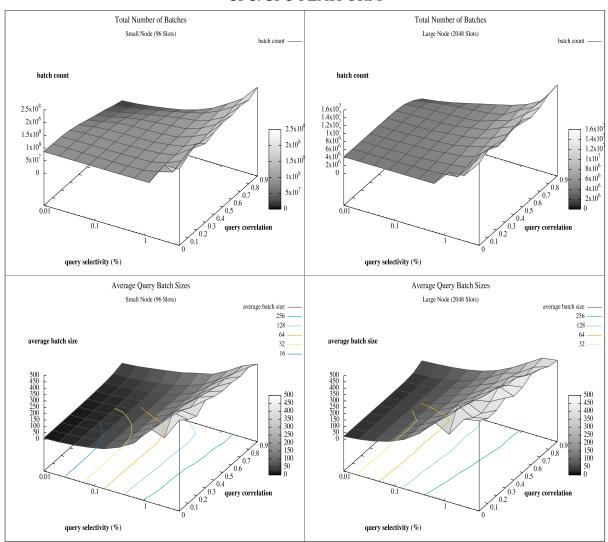

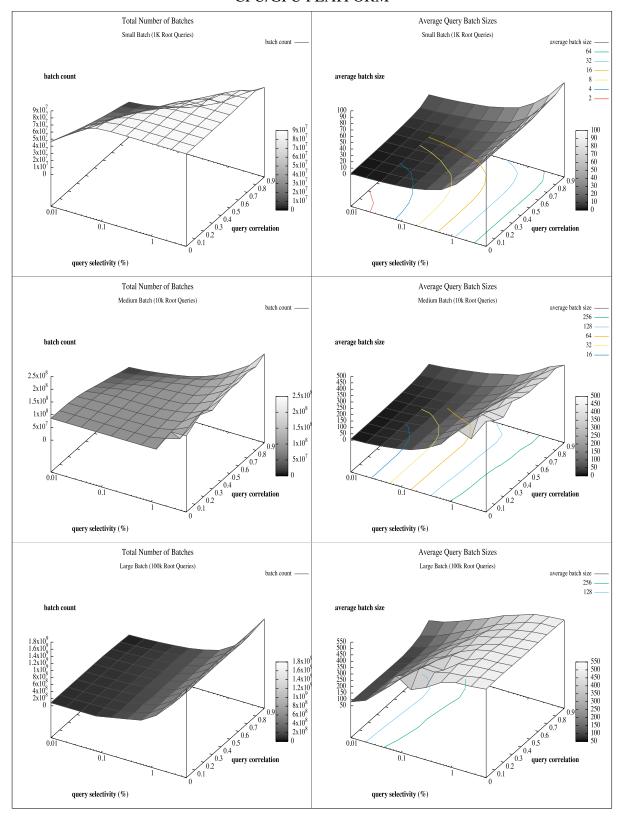

| 6.16 | Batch Processing Strategies: Total Batch Distribution Metrics                      | 161 |

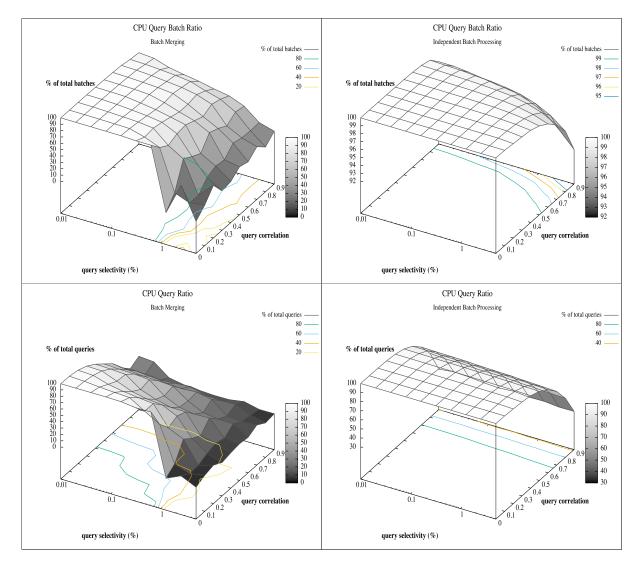

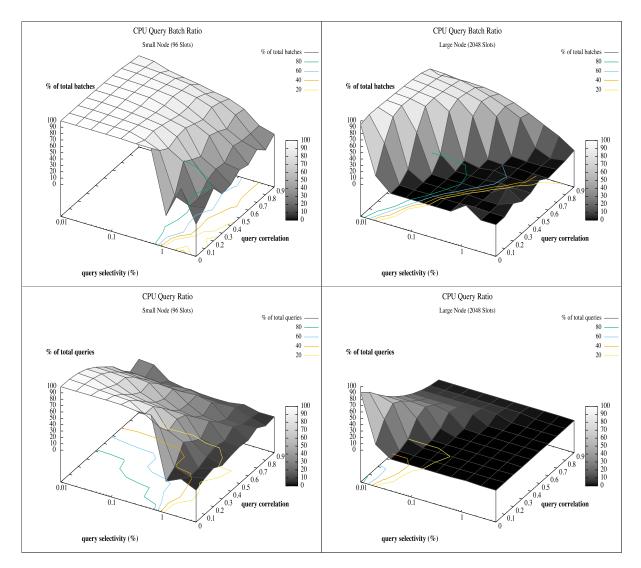

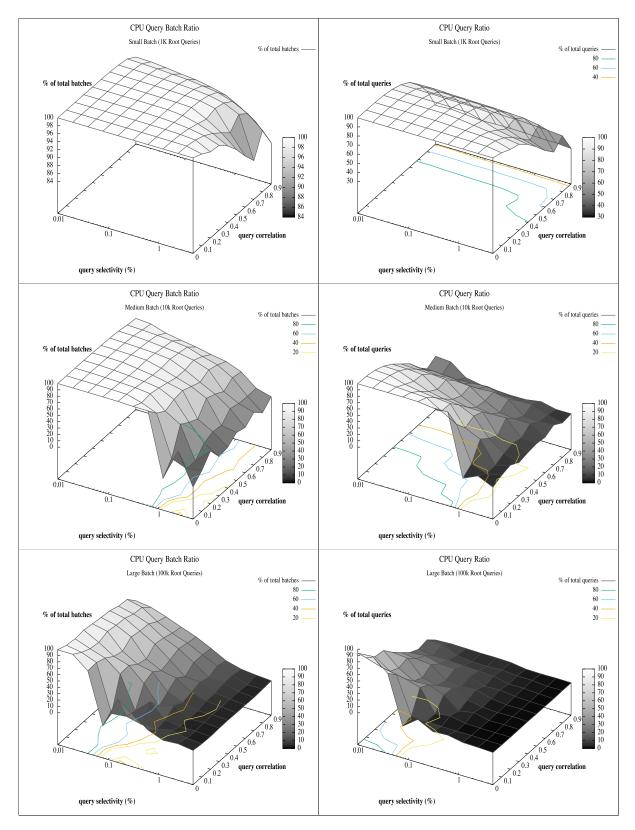

| 6.17 | Batch Processing Strategies: CPU Batch Distribution Metrics                        | 162 |

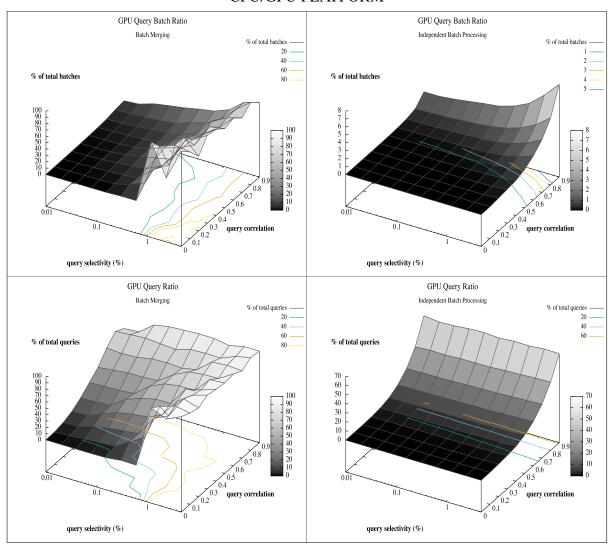

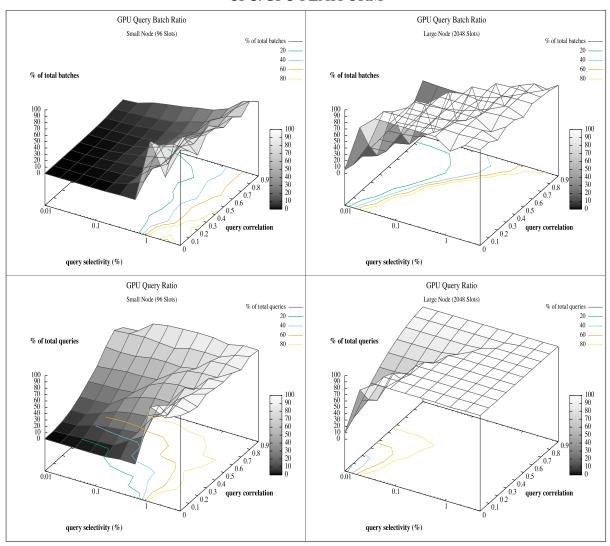

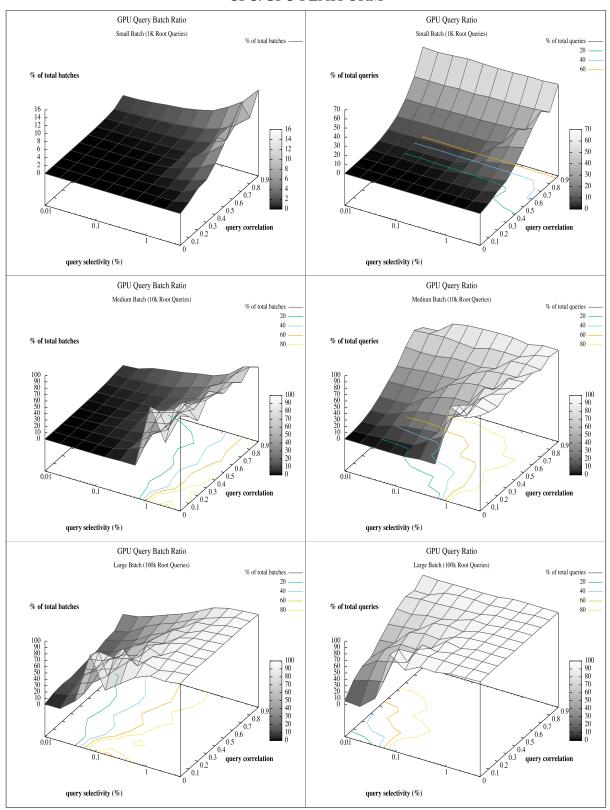

| 6.18 | Batch Processing Strategies: GPU Batch Distribution Metrics                        | 163 |

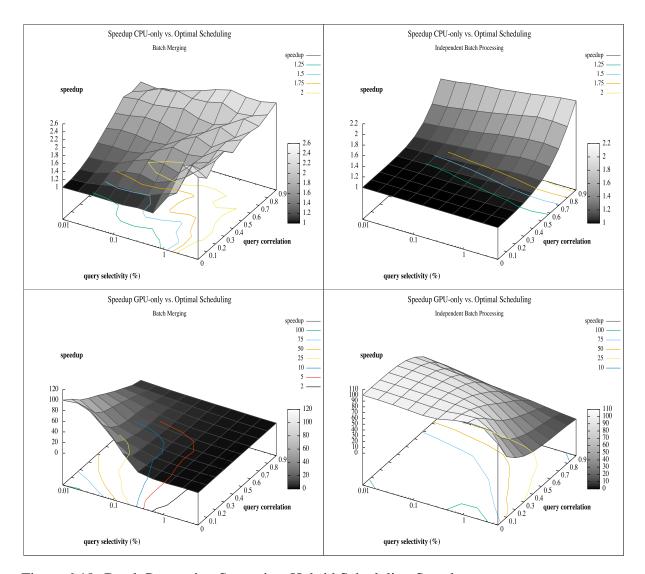

| 6.19 | Batch Processing Strategies: Hybrid Scheduling Speedups                            | 164 |

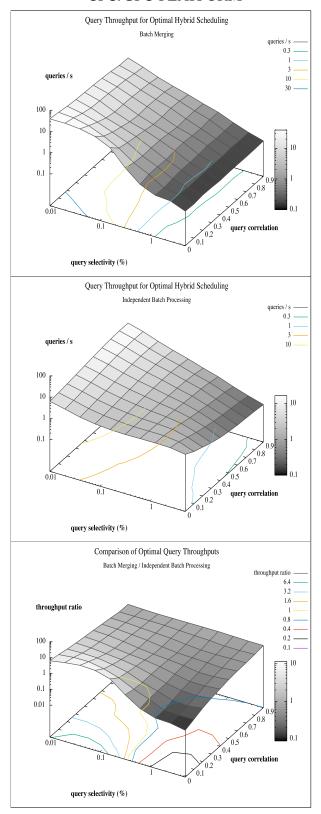

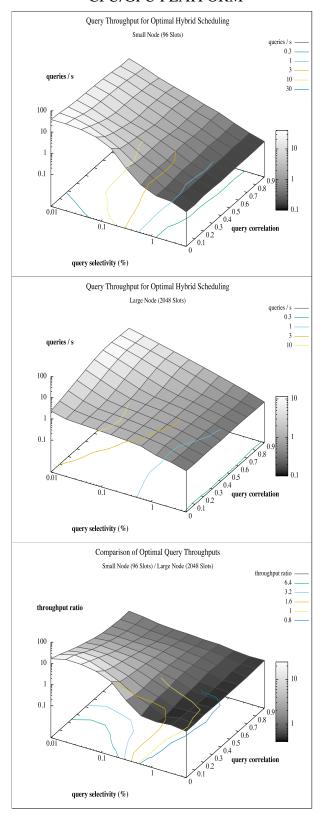

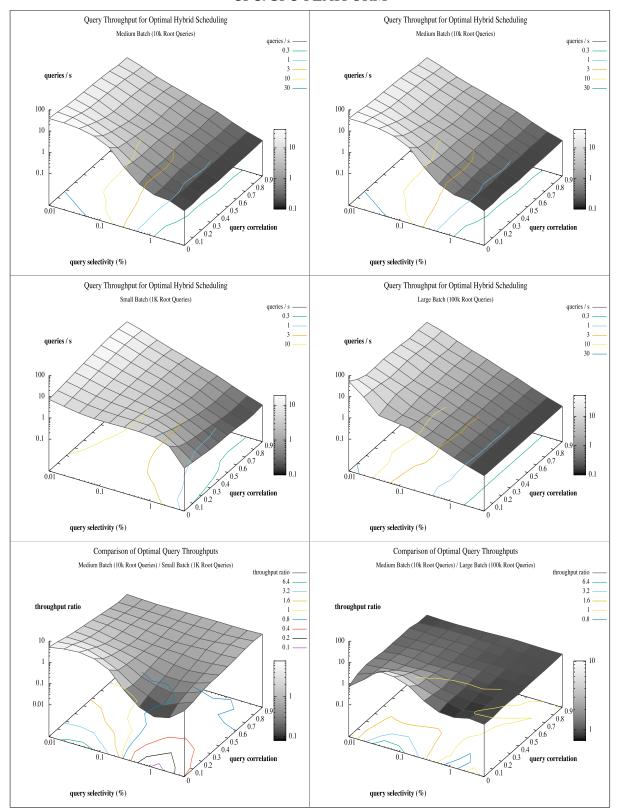

| 6.20 | Batch Processing Strategies: Query Throughputs                                     | 165 |

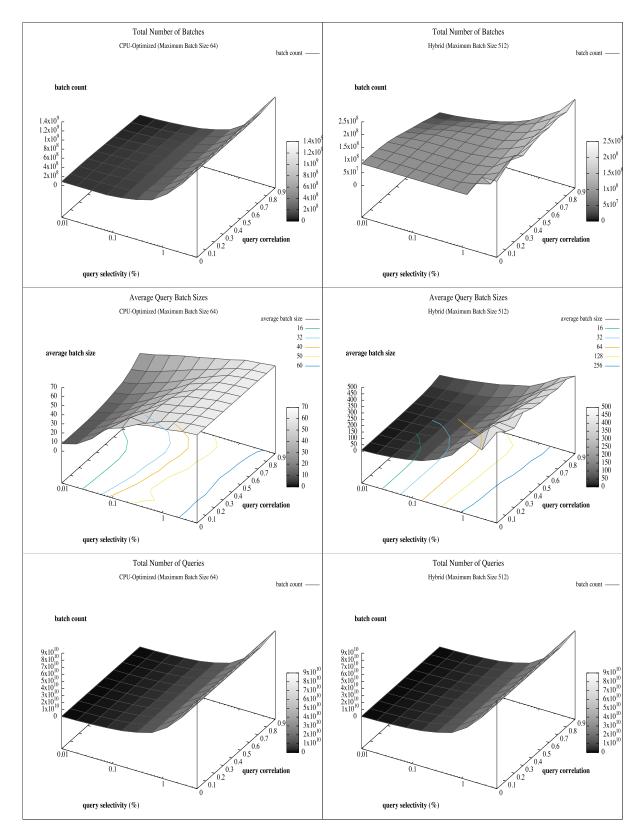

| 6.21 | Tree Parameters: Total Batch Distribution Metrics                                  | 167 |

| 6.22 | Tree Parameters: CPU Batch Distribution Metrics                                    | 168 |

| 6.23 | Tree Parameters: GPU Batch Distribution Metrics                                    | 169 |

| 6.24 | Tree Parameters: Hybrid Scheduling Speedups                                        | 170 |

| 6.25 | Tree Parameters: Query Throughputs                                                 | 171 |

| 6.26 | Query Parameters: Total Batch Distribution Metrics                                 | 173 |

| 6.27 | Query Parameters: CPU Batch Distribution Metrics                                   | 174 |

| 6.28 | Query Parameters: GPU Batch Distribution Metrics                                   | 175 |

| 6.29 | Query Parameters: Query Throughputs                                                | 177 |

| 6.30 | Maximum Batch Size: Query Batch Distribution                                       | 180 |

| 6.31 | Maximum Batch Size: Query Throughputs                                              | 181 |

## **List of Tables**

| 3.1 | Index Frameworks and Extensions            | 62  |

|-----|--------------------------------------------|-----|

| 4.1 | Generalized Search Tree Operations         | 68  |

| 4.2 | Ogre Model Polygons                        | 86  |

| 5.1 | Hardware Specification for Microbenchmarks | 115 |

## **Algorithms and Program Code**

| 4.1 | GiST Stateless Search                  | 59         |

|-----|----------------------------------------|------------|

| 4.2 | GiST Stateful Search                   | 70         |

| 4.3 | GiST Insertion                         | 71         |

| 5.1 | Parallel Stateless Node Scan Primitive | 96         |

| 5.2 | Sequential Stateful Node Scan Primtive | 97         |

| 5.3 | Parallel Stateful Node Scan Primtive   | )7         |

| 5.4 | Parallel Query State Update            | <b>)</b> 7 |

| 5.5 | Host Thread                            | )()        |

| 5.6 | Query Result Merge                     | )()        |

| 5.7 | Node Scan Kernel (Stateless Queries)   | )4         |

| 5.8 | Scan Preparation                       | 1          |

| 6.1 | Index Query Simulation                 | 16         |

| 6.2 | <i>createRootBatches</i> ()            | ١7         |

| 6.3 | <i>createChildBatches</i> ()           | ١7         |

## Chapter 1

### Introduction

Index structures are mandatory for implementing efficient search operations on large data volumes in traditional relational DBMS (Database Management System) applications. Efficient indexing is also important for applications from other domains, which do not necessarily use traditional DBMSs for storing and processing the available information, for example, computer graphic or other multi-media data applications, and scientific data management.

One challenge in these domains is that mature, well-understood index structures that are ubiquitous in the relational world for supporting various filter operations on potentially multidimensional data sets are not always working properly due to certain data characteristics. Therefore, numerous specialized indexes have been developed that are carefully designed for the workload characteristics of the application. Among these indexes, tree-based structures represent the most prominent class. Because a lot of tree management and traversal functionality is common between different instances of this index class, frameworks have been developed that generalize these aspects and provide a common implementation that can be shared between implementing indexes variants. By specializing custom extension points that configure the actual behavior of an index structure, a lot of development efforts can be saved, which fosters rapid prototyping that is required to identify the best structure(s) for a domain-specific use case.

The latest developments in hardware architectures present a new challenge in this context. Due to physical limitations, processor clock frequencies cannot be increased any further, which, from a software perspective, up to that time led to transparent performance gains, without the need to adjust existing code. Instead, hardware manufacturers now focus on increasing the number of processors as well as the bandwidth of interconnecting memory bus systems, providing an infrastructure that can be used by the software to gain speedups through parallelism. This trend has been picked-up by research and industry to develop new, parallelized indexing algorithms that can efficiently utilize new hardware resources, like multi-core CPUs (Central Processing Units) or GPUs (Graphics Processing Units). This hardware combination is of particular interest here, since CPUs and GPUs are already commonly used in multi-media and scientific data management domains, e. g., for rendering visual representations of the data or for running simulations.

#### CHAPTER 1. INTRODUCTION

The plethora of new hardware-conscious index structures led to a situation, which is comparable to the numerous, logically differing index types, before their implementations have been unified in generic frameworks. Therefore, this thesis addresses the following research questions:

- (1) How can parallel (co-)processor support be integrated into index implementations, without re-inventing the wheel for existing tree-based index structures?

- (2) How do generic index algorithms need to be adapted so that they can be accelerated by processing them on parallel hardware architectures, CPUs and GPUs in particular?

- (3) How can different (co-)processor types be combined in a hybrid system in order to leverage their respective strengths for specific, workload-dependent characteristics?

#### 1.1 Motivation

Section 1.1.1 presents some use cases in more detail to emphasize the importance that these challenging questions are addressed. Typical operations on the application data are discussed as well as their requirements for index structures. Section 1.1.2 highlights the role of index frameworks when it comes to developing actual indexes. The motivation for considering current hardware developments in this context is covered in Section 1.1.3. These dimensions will be combined in this thesis in order to extend the index framework idea for hardware aspects.

#### 1.1.1 Search Operations in Large Data Sets

An effective filtering mechanism is mandatory for many applications that operate on large data sets, because it helps to limit processing to those partitions that are required for executing a certain operation. Index structures are the method of choice in almost every case as they are well-understood and ubiquitous in data management applications such as relational DBMSs. In its simplest form, an index supports search queries for one-dimensional data, e. g., filtering records by a specific attribute. However, there are many applications that operate on more complex structures. CAD (Computer-Aided Design), CAM (Computer-Aided Manufacturing), or geographic/cartographic applications [80], applications that do text processing, genome or image databases [33], and many more were among the first applications that required special search structures for multi-dimensional data.

For example, in the field of computer graphics, 2D images have to be created from 3D models in order to display them on a screen. The source models, usually, consist of billions of triangles as the most common geometric primitive, which are augmented by additional properties, such as surface textures, material properties like opacity or color, and many others. Ray tracing [70, 132] is a well-known technique for this image rendering process that can simulate real-world conditions pretty well, including physical effects, like reflection or refraction. During

#### 1.1. MOTIVATION

this process, the path of light is simulated by rays that are "shot" into the scene. A ray is generated for each pixel in the final image that starts at the virtual camera position. In order to calculate the pixel color, each ray requires a search operation (point query) to determine its intersection point with visible objects in the underlying data model. For each intersection point, another query is required to calculate the incidence of light, originating from simulated light sources in the scene. To obtain photo-realistic images, this process can be repeated recursively to refine the initial results by considering the impact of neighboring objects on the pixel color. For example, additional reflection and refraction rays can be simulated, which originate from each intersection point at the hit object's surface. However, this refinement leads to a potentially exponential growth in the number of search operations.

Another class of rendering algorithms relies on projections of the virtual scene into the camera coordinate system. These algorithms are, usually, employed for interactive CAD/CAM applications [39]. Unlike ray tracing, whose physical simulation of light is rather time consuming and, mostly, calculated offline, CAD software requires user interactions with the scene, e.g., to control the camera or to manipulate objects. Therefore, for each operation, the projections must be calculated in real-time, i.e., only low latencies are acceptable until an image frame is rendered as user feedback. This is a rather challenging task, because the underlying models, such as air planes or power plants, may consist of billions of geometric primitives and additional meta data, like part numbers, part types, material properties, etc. Overall model sizes of tens to hundreds of GB are not uncommon in this domain. In order to reduce the amount of data that needs to be passed through the graphical rendering pipeline, systems implementing these projection-based algorithms rely on visibility-based filtering and incremental refinement of rendering results after each simulation step. Therefore, efficient searches (range queries) are required, which quickly return object candidates that might be visible in the current camera view. Complex occlusion and opacity effects are calculated later, using this significantly reduced data volume as input. Additional filters can be applied in order to reduce data volumes further, for example, distance-based predicates (clipping planes) or predicates that select certain parts in the model, e.g., electric wires, parts that belong to an engine, etc. Such filter combinations lead to *n*-dimensional predicates, where n > 3.

The aforementioned use cases required direct filtering on the underlying base model. Other uses cases, such as collision detection that is an important building blocks for physical simulations [100,121], require filtering as part of a (spatial) join operation between several models. In order to determine whether two or more 3D models collide, their boundaries need to be tested for intersection. In order to speedup the process, potentially colliding geometric primitives can be filtered within each simulation step by using spatial access methods.

The last related class of operations that shall be discussed here, is the simulation of distance-based interactions between objects in a virtual scene. For example, earth quake simulations [122] can use 3-dimensional geometries with varying data distributions so that certain conditions of the ground, like density, can be modeled. Shock waves are simulated by calculating the impact of a modified, e. g., shifted, primitive upon its neighbors within a certain range. A similar task is required in the *Blue Brain Project* [146] whose objective is to understand how the net of interconnected neurons in a brain works. Neurons, which are, again, modeled by geometric

#### CHAPTER 1. INTRODUCTION

primitives, like cylindric shapes, are used in simulations to calculate how electric current propagates through synapses as the interconnecting points between them. These simulations require spatial filtering techniques [190, 193] that allow selection of specific primitives in conjunction with filtering of neighboring objects.

Summarizing the main characteristics of these sample use cases, one can clearly see that the aforementioned applications need to cope with huge volumes of high-dimensional data. They require efficient filtering techniques in order to reduce the amount of data that actually needs to be passed to the complex and time-consuming algorithms. Access methods that shall be used therefor need to be flexible in terms of the data elements which shall be handled as well as in terms of supported search space pruning criteria. This flexibility is particularly important, because properties of the analyzed data set might not be known a priori and, sometimes, require explorative analysis with customizable search algorithms [11].

#### 1.1.2 The Need for Index Frameworks

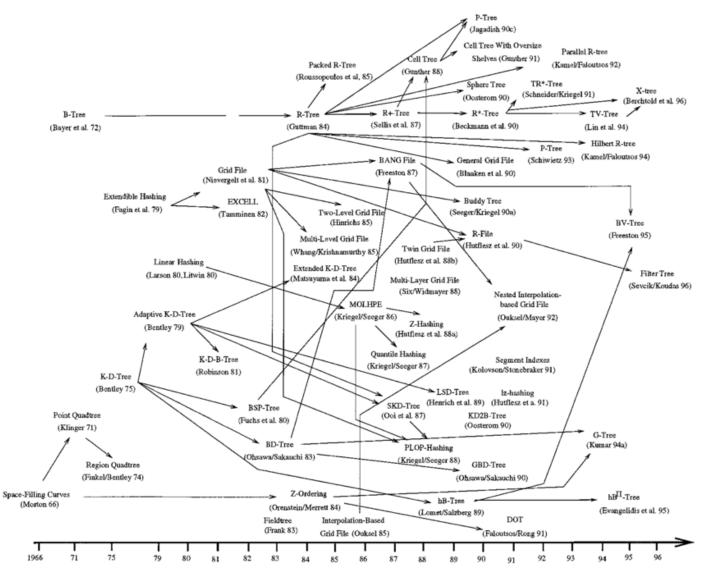

In order to speed up data access and filtering, the applications mentioned in Section 1.1.1, usually, make use of (multi-dimensional) index structures, like search trees. However, the effort for implementing and testing them is quite significant. A common approach to reduce this implementation complexity is to reuse existing implementations in the application's data management layer. Relational general purpose DBMSs provide industrial-strength implementations of common bounding volume data structures, such as B-Trees [20,48] or R-Trees [81], that can easily be used via declarative interfaces if the application's data model has been mapped to the relational model before. But the latter usually does not happen in practice. Instead, software solutions are built use case-driven, including a custom data management layer that has been tailored towards the needs of the application. For example, partitioning trees like Octrees [150] or k-d-Trees [25] are widely used in computer graphics applications. Thus, each domain, somehow independently, developed its own solutions that work quite well for their requirements. The somehow aged, but nevertheless telling Figure 1.1, compiled by Gaede/Günther [64], illustrates how many index variants exist, each claiming superior performance for a particular workload.

This development is quite natural, but generates a lot of implementation overheads. Even if the code for specific indexes is provided as reusable library, there are often cases where it needs to be adjusted, because of some application-specific workload characteristics that have not been considered in the original library design, effectively leading to a new index variant. For example, the visibility-guided image rendering algorithm in Interviews3D [39] augments nodes in a k-d-Tree [25] by dynamic state information that encodes whether the scene partition covered by that node was visible in the last frame or not, e. g., in case if it has been occluded before. This "visibility band" inside the tree can be leveraged to reduce the overhead for object filter algorithms by limiting them to the changes that occurred since the last frame, which are expected to be rather small compared to a full traversal of the entire scene hierarchy.

Figure 1.1: History of Multidimensional Access Methods Source: [64]

#### CHAPTER 1. INTRODUCTION

A second example is the access method that was developed for the *Blue Brain Project* [11, 190, 193]. The initial approach of using a standard R-Tree implementation failed because of the very dense data distribution that caused a lot of overlaps among the MBRs (Minimum Bounding Rectangles) inside R-Tree nodes, effectively turning each tree traversal into a full scan of the whole data set. As a solution, FLAT [193] has been created, a new specialized index structure that makes use of this density by linking nearby nodes with each other. The tree traversal method has also been modified. An initial tree descending algorithm yields starting points which are then processed in a subsequent neighbor exploring phase to do the final filtering.

There are many other examples where certain data properties, like the "the curse of dimensionality" led to the development of new index structures [26, 44, 133]. Such tailor-made solutions work pretty well, at least initially, where the application is in a prototype phase and non-performance related requirements are less important. However, once the application grows and is geared towards commercial use, other functional aspects, like concurrency handling or durability guarantees, need to be addressed, too. While concurrent updates were completely ignored in FLAT, they became particular important for the commercial Interviews3D product. Without correct synchronization mechanisms, concurrent operations executed by multiple end users on a shared data model are not feasible without unintended side effects.

In order to facilitate the development of indexes that correctly implement such complex algorithmic logic, several index frameworks have been proposed [59, 82, 86]. By generalizing common logic that is shared between a majority of index structures and providing it as customizable library code, the use of such frameworks can save development time and testing efforts. Examples for such generalizable index algorithms are:

- clustering of "similar" (key, value)-records inside tree nodes for search space pruning

- management of tree nodes when over- or underflows occur in internal data structures upon record insertion or removal

- tree traversals for answering search queries with correct concurrency control handling

- serialization of in-memory tree data to persistent storage devices with internal buffering mechanisms

Extension points are provided by these libraries to allow injection of index-specific information that distinguishes the various existing index variants from each other. By, for example, defining custom key data types that are stored inside tree nodes, a similarity metric for clustering nearby entries, node visitation strategies for tree traversals, or special query predicates for modeling different kinds of search operations, the aforementioned algorithms can be customized by index developers to parameterize the framework for a specific use case without the need to change any of the shared code.

Summing this up, one can clearly see the need to define custom index structures for different use cases that need to cope with large data sets and non-standard data accesses. Index frameworks are useful to implement such indexes, because they reduce development efforts for complex algorithms that are generalizable and share code between different implementations. A flexible framework design is required to allow efficient prototyping for specific applications, providing extension points that can be used to customize a concrete implementation.

#### 1.1.3 Hardware-Accelerated Search Operations

Many of the motivating applications from Section 1.1.1 run workloads that offer great potential for parallelization. For example, ray tracing generates many independent search queries in each iteration, collision detection requires distance calculations and intersection tests for many geometric primitives that are involved in a spatial join, and physical simulations need to examine many neighboring data elements in order to calculate their mutual interactions in each simulation step. Therefore, exploiting this potential on modern parallel processor architectures represents the second dimension that motivates the research of this thesis.

Parallel processor architectures gained considerable attention recently. The many-cited end of Moore's Law [119, 188, 200], caused by physical limitations, such as thermal effects, energy constraints, etc., that prevent a further increase of a processor's clock frequency in order to improve application performance, let to a strong industry focus on the development of processors that are comprised of many independent cores. A multitude of different processor architectures have been developed, each following a slightly different approach of handling parallelism. Multi-core CPUs, for example, are designed for task parallelism and efficiency of sequential steps by embedding complex algorithms, like branch prediction or out-of-order processing, on the chip. GPUs clearly focus on data parallelism with huge arrays of simple processor cores, while FPGAs (Field-Programmable Gate Arrays) can be used to embed any algorithm directly in hardware and handle pipeline parallelism in streaming tasks pretty well. Oftentimes, a parallel processor is used as coprocessor in conjunction with another processor for sequential tasks. Developer toolchains, which are mostly provided by hardware manufactures, simplify the management of these processors by abstracting many low-level details, such as the creation and management of parallel tasks, and support software developers to model, implement, and tune parallel algorithms.

Of course, these new tools have been picked-up by the database community to analyze how the new methodology can be leveraged for the development of index structures that make use of the abundance of available processing resources. Well-known indexes, like B-Trees or R-Trees, have been analyzed to speed up lookups with parallelized search operations [104,141,167,179], to optimize data layouts for efficient memory access [171], or to revise existing structures so that they can be used on different processor device types [111,194]. Likewise, research in other domains, e. g., computer graphics, has been conducted [62,90,143], where, naturally, the use of coprocessors like GPUs is already state of the art since decades.

Parallelizing (indexing) algorithms for modern (co)processor architectures is a challenging task because of the many subtleties that need to be considered when an algorithm is tuned for a specific architecture. Designing efficient data structure layouts for given access patterns is equally important as mapping algorithms to fine-granular, independent units of work that can be scheduled to the available processors. While the former are implementation and tuning tasks that are supported by vendor-provided toolchains, the latter requires a different way of algorithmic thinking [192], which can also be considered the main challenge here. According to *Amdahl's Law* [15], which can also be applied to modern parallel processor architectures [88], the parallelization is an important challenge to solve because the ratio of sequential to parallelized code significantly impacts an application's overall scalability. Therefore, this challenge shall, to some extend, be addressed for the field of tree-based index structures in the following.

#### 1.2 Contributions of this Thesis

The overall goal of this thesis is to develop and evaluate a framework for implementing index structures that utilize the parallel processing resources provided by modern computation hardware. The framework offers extension points that can be specialized by an index developer in order to define different kinds of search trees as basic data structures for custom traversal operations. The framework itself handles tree management operations, automatically parallelizes traversal algorithms, and schedules them to available processor devices in the runtime system. Using the framework bridges the gap between existing generic index structures that are flexible and highly specialized implementations that have been tuned for specific processing devices.

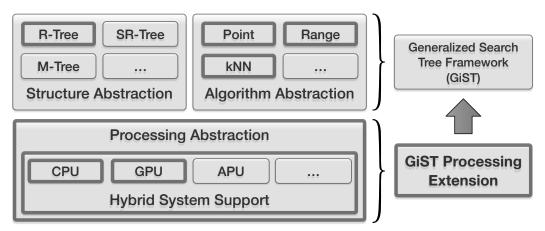

Figure 1.2: Overview of Contributions

More specifically, the following main contributions are made by this thesis (cf. Figure 1.2):

- 1. The well-known GiST framework for modeling height-balanced search trees is extended by a processing abstraction layer. Based on GiST's generic data structure and algorithm abstraction layers that allow to model many index structures on a logical level, generic index processing primitives are defined that can be executed on arbitrary processor devices.

- 2. A sample implementation of this physical execution layer is developed that allows to schedule index operations to CPUs and GPUs.

- 3. A new out-of-core GPU-based algorithm is developed using the CUDA (formerly Compute Unified Device Architecture) programming model. Unlike prior art, the implementation does not require that the index data is fully stored in a GPU's main memory, but can be fetched on-demand.

- 4. Based on the generic index operation model, an adaptive scheduler is developed that allows to leverage the strengths of CPUs and GPUs in a hybrid system. The scheduler can be calibrated for arbitrary runtime system setups, without changes in the underlying framework implementation.

- 5. Finally, R-Tree range and nearest neighbor search algorithms are evaluated to assess parallelization benefits for both processor architectures and to compare different scheduling strategies with the original GiST baseline.

#### 1.3 Focus of this Thesis

During the development of the indexing framework, the following assumptions have been made that limit the scope of this thesis:

- The thesis focuses on systems consisting of CPUs and GPUs that are attached as dedicated

accelerator cards via PCIe (Peripheral Component Interconnect Express) bus, because

such setups are widely used in practice and were also available for experimental evaluations. Integrating other processor types should be simple by choosing an OpenCL-based

implementation of the algorithms, because many device types support this standard.

- It is assumed that index structures reside in main memory of the host system that interacts with coprocessor devices, i. e., disk I/O costs are ignored for query processing. In practice, this should not be a strong limitation, because upper tree layers, which are responsible for search space pruning, consume only fractions of an index' data volume and, therefore, can be usually buffered in-memory [75].

- The thesis focuses on query processing only. Tree modification operations and the implementation of concurrency control mechanisms are assumed to be provided by the underlying GiST framework. Therefore, the solution is applicable to rather static indexes that are used for analytic workloads and are refreshed in bulk.

- The thesis focuses rather on generality and extensibility of the resulting index framework than on tuning it for a specific use case. Index structures that that are implemented via the framework will, most likely, be outperformed by fine-tuned implementations. However, considering industrial hardware development cycles, it is rather unlikely that existing software will always be kept up-to-date to fully exploit all new features and capabilities (Wirth's Law [197]). Therefore, lowering development overheads with generic frameworks will likely be a better solution than adapting a large code base of fine-tuned structures in a long-term view.

#### 1.4 Structure of this Thesis

An overview of current parallel processor architectures is given in Chapter 2. Architectural differences are discussed as well as parallel programming models, which are used in the following chapters to parallelize index operations. Chapter 3 covers prior art in this area. Common implementation techniques of parallelized indexes are discussed, as well as existing frameworks that allow to generalize index implementations. Further, the gap between these two research areas is highlighted in order to motivate the case for generalized parallel processing in index frameworks. In Chapter 4, the processing abstraction layer is developed. Further, existing applications from the computer graphics domain are profiled in order to assess potential benefits of parallelized index searches. Tree-based search operations are parallelized in Chapter 5. Moreover, a GPU-based implementation is presented that extends prior art by out-of-core processing capabilities, which is mandatory for scaling indexed data volumes that can be processed, and for leveraging multiple processor devices for the execution. Chapter 6 discusses how different device types can be integrated into the framework and how a scheduler can be implemented that dynamically selects the best processor type for a specific task execution. Chapter 7 summarizes this work and highlights next steps for future research directions.

#### CHAPTER 1. INTRODUCTION

## Chapter 2

# **Background – Parallel Processors and Coprocessors**

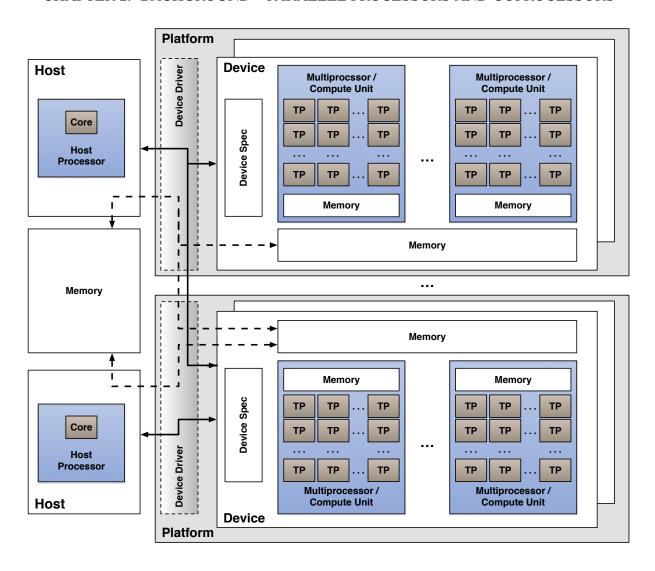

Figure 2.1: Overview of Parallel Processing Background Information

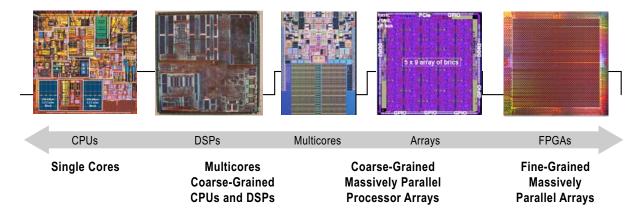

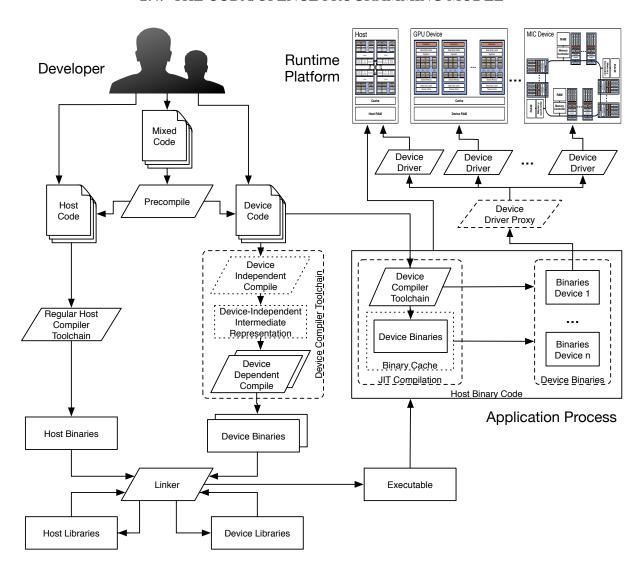

Before deep-diving into the parallelization internals of the indexing framework, this chapter provides some background information on parallel processor architectures (Section 2.1) and hybrid systems that are comprised of multiple different processor types (Section 2.2). This will provide a solid foundation for understanding the rationale behind some algorithmic design decisions that have been made while implementing the framework. Multi-core CPUs and GPUs are in the focus of these sections, because they were used for experimental evaluations.

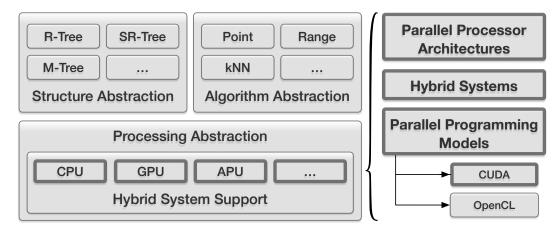

The second part of this chapter (Section 2.3 and Section 2.4) discusses parallel programming models that provide useful abstractions for low-level hardware details when algorithms shall be implemented for these platforms. The focus in the following clearly lies on the CUDA and OpenCL (Open Computing Language) models, because they currently represent the de facto standards when algorithms for hybrid CPU-GPU systems are developed. CUDA has also been used for implementing the indexing algorithms that are subject of the following chapters.

#### 2.1 Parallel Processor Architectures

Figure 2.2: Overview of Programmable Parallel Processor Architectures Source: [185]

It is observable that processors' clock frequencies are no longer increasing since several years. The reason for this is the often-cited "power wall" [35, 148, 188, 200], i. e., an exponentially growing energy consumption with increasing frequencies and the thereby arising thermal issues [119, 185, 192]. Instead, it can be observed that the number of cores are increasing in computer systems in order to gain performance by leveraging parallel computing. Further, sizes of caches within systems are increasing, as well as throughputs of interconnects between different kinds of memories and processing units [152] to keep cores busy by fetching data fast enough and avoid stalls through memory access. The latter is also known as the "memory wall" in literature [198].

There are various ways how the ever-increasing number of transistors can be wired in order to design processor architectures that fit special problem classes. A coarse-granular overview of some architectures is illustrated in Figure 2.2, which has been taken verbatim from [185]. Some of them are discussed in [129] and in more detail in the following sections, ranging from architecture of modern multi- and many-core CPUs over GPUs to FPGAs. Single-core CPUs are not considered here, because this thesis focuses on parallel hardware. Neither are DSPs (Digital Signal Processors), since these are special-purpose processors, designed for high-performance signal processing workloads that are not considered relevant for the indexing use case.

Multi-core CPUs, which are covered in Section 2.1.1, are commonly available as commodity hardware and, with a higher number of cores, also in the high-end server segment. They resemble the heart of most computer systems and are a good fit for general purpose tasks. A lot of effort was spent by vendors to, e. g., optimize CPU architectures for sequential tasks that involve divergent branches. Most of the currently available processor types also offer some capabilities for data-parallel SIMD (Single Instruction Multiple Data) processing.

The other extreme are processors that are optimized for SIMD tasks, such as GPUs, which are discussed in detail in Section 2.1.2. GPUs consists of large arrays of simple cores and, thus, can be classified as very large vector processors. They are best-suited for computationally intensive tasks that can be subdivided into a lot of fine-granular subtasks, preferably without any branch divergence among them.

#### 2.1. PARALLEL PROCESSOR ARCHITECTURES

Many-core processors, which are briefly broached in Section 2.1.3, can be classified somewhere in between CPUs and GPUs. They are sold as devices having many CPU cores with separate memories and offer a much higher degree of parallelism than CPUs, but are more flexible than simple GPU cores. These devices are comparable to parallel processor arrays and allow to implement a SoC (System on Chip) design where, unlike GPU devices, the entire program runs on the device without the need to synchronize with a host system.

Section 2.1.4 briefly discusses FPGAs, which are important coprocessors in many use cases. For example, they are used in commercial database management systems, such as IBM Netzza [63], to implement (de-)compression and filter algorithms near the data source before the data is streamed into main memory for further processing. FPGAs are freely programmable circuits that allow to embed the circuit corresponding to a specific problem directly on the chip – even logic implemented in CPUs, which also allows a SoC design on these devices. FPGAs are very energy efficient and can benefit from different kinds of parallelism. But they require workloads where many inputs are "streamed" through the device for producing outputs.

#### 2.1.1 Multi-core CPUs

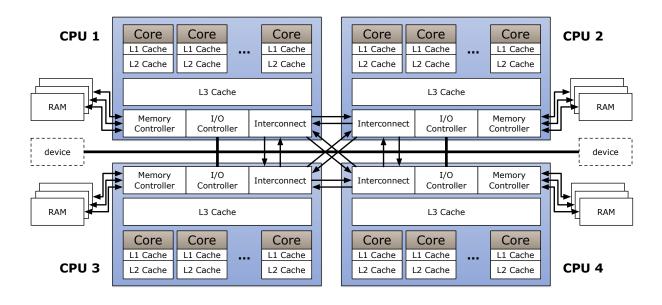

Figure 2.3: Architecture of a modern multi-core CPU

Multi-core CPUs represent the most common parallel processor architecture. A basic overview of their most important components is illustrated in Figure 2.3, which was compiled from many different sources and specifications of the largest vendors of CPU hardware [42, 49, 91, 95, 98, 175, 191, 196]. Of course, these specifications differ between different vendors, CPU families, and models, but the basic concepts remain the same. Those concepts shall be discussed here, including their consequences for algorithm design.

#### CHAPTER 2. BACKGROUND - PARALLEL PROCESSORS AND COPROCESSORS

A modern multi-core CPU consists of several processor chips having multiple cores on a single die, ranging from 2 and 4 cores for commodity hardware, like the Intel Core i5 processor, over 12 cores, e.g., in IBM POWER8 processors, to 18 cores in Intel Xeon E7 processors for highend server hardware. Each core can be managed independently from the others and operates at very high clock rates, usually between 2 and 5 GHz. High frequencies are automatically used for workload peaks to boost computation performance if certain conditions are met, e.g., temperature values comply with the hardware specifications [94]. Depending on the hardware architecture, each core can process multiple hardware threads simultaneously. While Intel refers to this feature as hyper-threading and in its current processor families supports up to two concurrent hardware threads per core [93, 175], IBM names this capability SMT (Simultaneous Multi-Threading) and supports four hardware threads per core in the POWER7 architecture and up to eight in the POWER8 architecture [91, 191].

CPU cores communicate via an internal bus system with all other components on the same die. Communication between different processors is done via an interconnect bus (QPI (Intel QuickPath Interconnect) by Intel [95] and HT (HyperTransport) by AMD, IBM, Apple, and Nvidia [49]). The communication with peripheral devices is implemented by an I/O controller via another bus system, most commonly PCIe [40, 72, 196] or NVLink, which provides even higher connection throughputs [163]. Coprocessors, like dGPUs (dedicated Graphics Processing Units) or FPGAs, are attached via this infrastructure, or, in case of iGPUs (integrated Graphics Processing Units)/ APUs (Accelerated/Advanced Processing Units), reside on the same chip. Both variants will be briefly discussed in Section 2.2. Further, there are usually several other specialized accelerators integrated on a CPU chip, which can be leveraged for dedicated tasks, like video de-/encoding or de/-encryption algorithms. But these accelerators are not considered here, because, unlike CPUs or GPUs, they cannot be programmed for general purpose tasks.

A significant amount of CPU chip space is spent on caches, which are managed by the hardware itself. Typically, L1 and L2 caches are privately accessible per CPU core while the L3, and sometimes a L4 cache, are shared between all cores residing on the same die. These caches form hierarchies, increasing in size and having higher access latencies with each additional layer. Main memory is attached via independent modules that are connected via a memory controller to the available processors. Access latencies and achievable transfer bandwidths from/to these memory modules are better when they are directly accessed from cores that reside on the same chip where the modules are connected to. Indirect access through the processor interconnect shows higher latencies and lower transfer bandwidths, which can have significant impact on application performance. This property is commonly referred to as NUMA (Non-Uniform Memory Access) effect in literature [127], but of less importance in the following.

In addition to caches, registers, and arithmetic-logical function units within the cores, a large number of transistors is used to optimize processing pipelines on each core. CPU cores are implemented as superscalar processors that can execute multiple instructions at once and comprise complex logic to overlap different operation phases (instruction loading, decoding, operand fetch, execution, result writing), predicting a program's control flow with branch prediction, and allowing out-of-order-execution of independent operations. Since these features are purely implemented in hardware, they mostly remain hidden from programmers. But for highly-tuned systems, e. g., database management systems, algorithms are carefully designed to exploit these optimizations in order to deliver maximum performance [34, 169, 212].

#### 2.1. PARALLEL PROCESSOR ARCHITECTURES

Another feature that all modern CPU families offer is the capability to execute SIMD operations, i. e., calculate the results of the same operation on multiple input data elements within a single step. Therefore, the input operands must be fetched into wide vector registers before an SIMD operation can be executed, yielding all results at once. The data must be properly aligned in memory for being able to fetch and store them with a single vector read / vector write memory transaction. These SIMD features are made accessible to the programmer via specialized processor instructions. However, each vendor offers different instruction sets for different architectures, which complicates the development of portable algorithms that exploit these features for maximum performance [54]. Some examples for SIMD instruction sets are:

- MMX, different SSE (Streaming SIMD Extensions) versions, or AVX (Advanced Vector Extensions) on x86-based processors

- AltiVec or Cell SPU on the POWER family

- VFP or NEON on ARM

#### 2.1.2 GPU Architecture

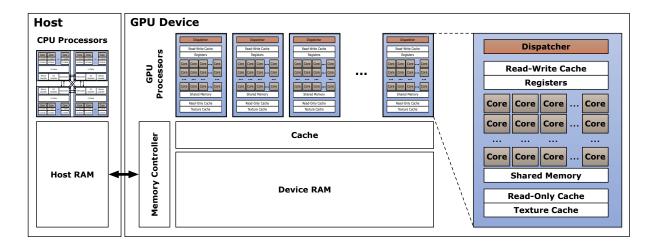

Figure 2.4: Architecture of a dedicated GPU device

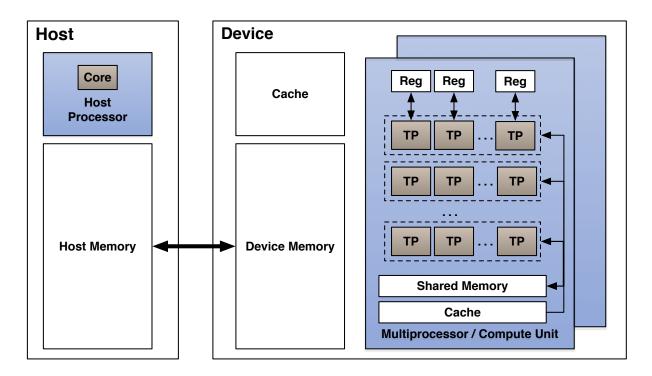

Figure 2.4 illustrates a simplified architecture of a dedicated GPU device that is capable to execute general purpose tasks in parallel, i. e., general data-parallel programs which differ from the classic graphic processing pipeline. This model is often referred to as GPGPU (General-Purpose computation on Graphics Processing Units) in literature and by the industry. Current major vendors of such GPU devices are Nvidia and AMD/ATI. Their officially provided references and white papers have been used to compile Figure 2.4 [9, 10, 155, 157, 159, 161, 162]. Of course, some details, like the actual on-/off-chip cache organization, the hardware queuing capabilities, the memory access mechanisms, or the dispatcher behavior, are vendor- and device model/type-specific. But the given overview shall be sufficient to highlight architectural differences compared to a multi-core CPU described in the previous section and their implications on how the programming model has to be adapted for this hardware platform, which will be covered later in Section 2.4.

#### 2.1.2.1 Device Architecture

A dedicated GPU *Device* is attached to the *Host* via an I/O bus system, like a PCIe or NVLink bus. The host uses a device driver to control all operations that are executed by the device, such as resource allocations, memory copy operations, Kernel executions, and synchronization barriers. Device operations are sent through the bus as well as all data that is exchanged between those systems. All data that is produced by the host system and acts as input for an offloaded GPU kernel has to be copied to the Device Memory. Output data that is generated by GPU kernels and requires further processing on the host has to be copied in the opposite direction.<sup>1</sup> Physically, an PCIe bus link comprises several lanes, which are composed of multiple electrically connected pins that allow full duplex, parallel point-to-point data transfers between the communication endpoints [40]. According to PCIe specifications, 2.5 Gb/s can be transferred via PCIe v1, 5.0 Gb/s via PCIe v2, and 8 Gb/s via PCIe v3 bus links per lane and direction [72]. However, the effective bandwidth for transferred data does also depend on the CPU and chipset which is used [9] and is much lower due to encoding overheads required by the physical interconnect, e.g., PCIe protocol overheads (packets with header information, sequence numbers, error correction codes, package acknowledgements etc.), and other overheads caused by additional communication layers in the application's stack [72]. As later experiments will show (cf. Section 5.3.5), these overheads significantly reduce the achievable transfer bandwidth between a host system and a GPU device, which might become an issue in case of transfer-bound applications. This bottleneck can be mitigated, e.g., by implementing caching techniques to store and reuse data on the device's main memory. In the case of GPUs that are integrated on the CPU die (cf. Section 2.2), CPU host and GPU device share the same main memory and data transfer operations can be omitted. However, memory access still has to be appropriately synchronized through the memory controller, which leads to additional overheads.

#### 2.1.2.2 Processor Architecture

Similar to a CPU processor, a processor on a GPU comprises several cores on a die.<sup>2</sup> Compared to a CPU system, a GPU not only comprises a much higher number of cores per processor, but, usually, also a higher number of processors on the device. For example, Nvidia's Kepler architecture implements 192 CUDA cores per SM (Streaming Multiprocessor, sometimes SMX) [161] and 26 of such SMs are available on a Tesla K80 device [164]. In contrast to CPUs, GPUs are operated at much lower clock frequencies of less than 2 GHz. However, due to the large number of cores, more instructions can be executed simultaneously. Further, GPU processors and cores cannot be operated completely independent from each other. These aspects have to be considered when algorithms are implemented for this architecture.

<sup>&</sup>lt;sup>1</sup> Note that the requirement for such memory copy operations is dictated by this system architecture. Terms like "Unified Memory" or "Shared Virtual Memory" that are oftentimes found in programming references or other vendor publications (cf. Section 2.4.3) do only refer to the virtual memory model that is presented to the programmer, i. e., how virtual memory addresses are mapped to the physical host/device address space. Such a model merely simplifies programatic memory management operations but, nevertheless, still requires physical data transfers to be executed implicitly by the device driver under the hood.

<sup>&</sup>lt;sup>2</sup> Nvidia refers to a GPU processor as Streaming Multiprocessor, sometimes SMX, while a single core is referred to as *CUDA core* [157, 161]. AMD uses the term DPP (Data-Parallel Processor) for a multiprocessor, while a single core is referred to as *compute unit* [10].

#### 2.1. PARALLEL PROCESSOR ARCHITECTURES

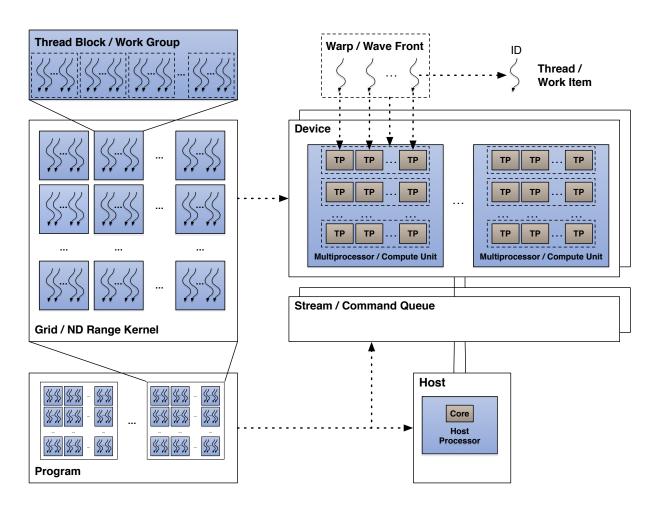

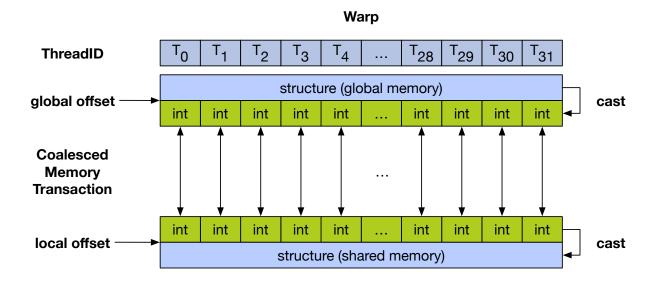

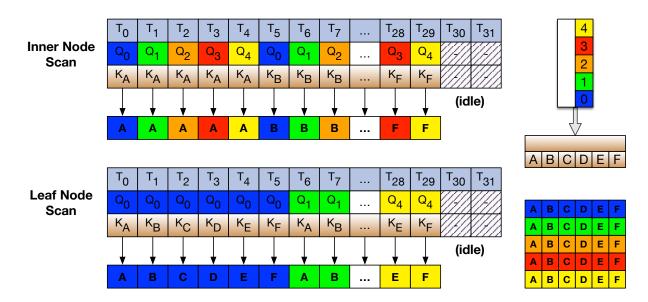

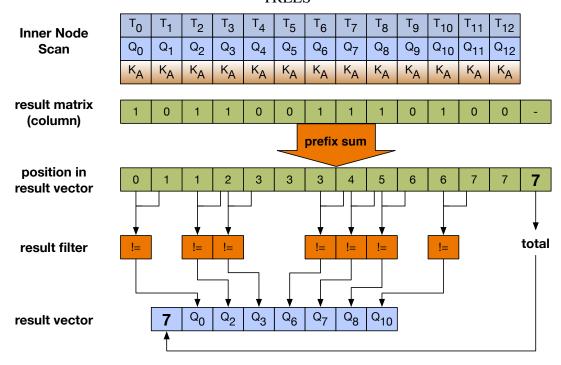

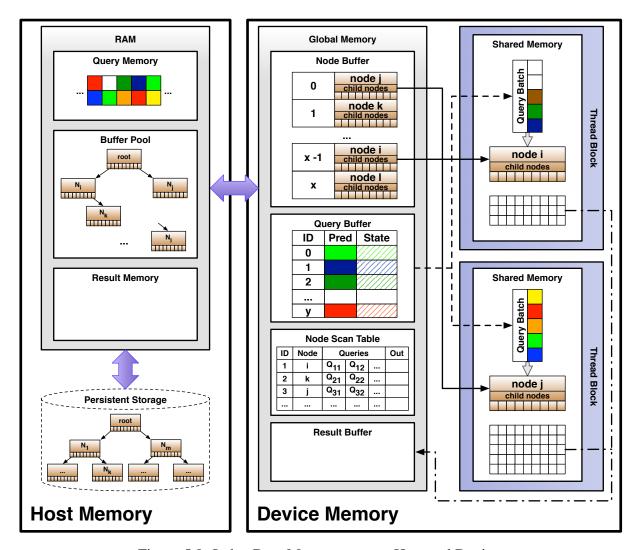

A GPU multiprocessor acts as SIMD/SPMD (Single Program Multiple Data) vector-processor for large data-parallel tasks, which are consistently referred to as *GPU Kernel* or simply *Kernel* in literature (cf. Section 2.4.2) and are scheduled to the available cores on the device. While the GPU architecture allows communication and synchronization between the cores of the same multiprocessor, this is not the case for communication between different multiprocessors. This must be considered when *Kernel* algorithms are designed. Unlike CPU threads, which can be scheduled separately to each core, GPU hardware threads are dispatched in *thread groups*, which represent the smallest available dispatch unit on a GPU. Within such a group, also called *Warps* in Nvida terminology [160] and *Wave Fronts* by AMD [9], all threads operate in lockstep mode. That is, they share the instruction counter and, hence, execute the same instruction at the same time, but usually on different data partitions. Which data element shall be processed by a thread is indicated by a unique and possibly multi-dimensional *index*, i. e., a counter that is automatically calculated as offset for each kernel thread. These indexes are stored in special hardware registers and can be queried by each thread through dedicated program instructions.