## Alma Mater Studiorum – Università di Bologna

## DOTTORATO DI RICERCA IN

## Ingegneria Elettronica, delle Telecomunicazioni e Tecnologie dell'Informazione

## Ciclo XXXI

**Settore Concorsuale:** Area 09 (Ingegneria Industriale e dell'Informazione) – 09/E3 Elettronica

Settore Scientifico Disciplinare: Area 09 (Ingegneria Industriale e dell'Informazione) – ING-INF/01 Elettronica

## POWER AND THERMAL MANAGEMENT RUNTIMES FOR HPC APPLICATIONS IN THE ERA OF EXASCALE COMPUTING

Presentata da: Dott. Daniele Cesarini

**Coordinatore Dottorato**

Prof. Alessandra Costanzo

Supervisore

Prof. Luca Benini

**Co-supervisore**

Dr. Andrea Bartolini

Esame finale anno 2019

The computer is incredibly fast, accurate, and stupid. Man is incredibly slow, inaccurate, and brilliant. The marriage of the two is a force beyond calculation. L. Cherne

#### Abstract

In the scope of technical and scientific computing the rush towards larger simulations, with higher complexity and accuracy, has been so far assisted by a steady downsizing of micro-processing units, which has allowed increasing the compute capacity of generalpurpose architectures at constant power. As side effects of the end of Dennard's scaling, this process is now hitting its ultimate power limits and is just about to come to an end. Today is not more possible to maintain the expected grow of supercomputers performance without increase the power consumption. Thus, power and thermal walls stand in front of the evolution of supercomputers towards the exaflops era. These technological walls are big challenges to face for assuring a constant grow of performance in scientific applications. Next generation architectures for high-performance computing systems implement hardware and software components to address power and thermal issues for increasing performance and efficiency. The continuous grow of power consumption at peak performance of supercomputers, start to require to well-defined power budget at design time which should considers the worst-case power consumption of the computing resources to avoid outages. But supercomputers rarely cause the worst-case power consumption during their life limiting the performance achievable in normal conditions. Power capping mechanisms are necessary to aggregate more computing units to target the "average-case power consumption" of the system by limiting the performance at execution time when peak power consumption is demanded. Power capping systems can be implemented using hardware or software mechanisms, but they have different advantages and challenges which need to be explored. Another drawback of the end of the Dennard's scaling is that power density of high-end processors starts to increase at every technologically steps leading to overheating and thermal gradient on the same die. As result, thermal-bound machines show performance degradation and heterogeneity which limits the peak performance of the system. Thermal management solutions are needed in order to avoid thermal hazards which make the system too unreliable to use. Power capping and thermal controls are both safety mechanisms, but none of them address energy efficiency in applications. It is well known that in large application runs, the time spent by the application in the communication is not negligible and impacts the power consumption of the system. Today's supercomputer can leverage on low power states to reduce the power consumption during communication, but due to the time scale at which communication happens, transitioning in low power

states during communication's idle times may introduce overheads. As a matter of fact, there is no known low-overhead mechanism for reducing the power consumption during communication slacks. In this thesis have been developed software strategies in order to face the main bottlenecks of power and thermal issues that affects supercomputers of next generation. It targets scientific applications which are the principal candidates that are negatively affected from the power and thermal constraints of supercomputers. To respond to the above challenges, this work shows that propagating workload requirements from application to the runtime and operating system level is the key to provide efficiency. But this is possible only if the proposed software methodologies have little or no overhead in term of application performance. The run-times libraries developed in this work respect this constraint, and to prove it, they have been largely tested in real production HPC systems with widely used scientific applications and datasets. Moreover, in this thesis has been shown that hardware mechanisms to enforce a power cap at execution time can induce overhead due the unawareness of the application workload. While software policies, which can be integrated in the application, can take advantage on relaxing the power constraint consistently with the application's workload. While, in thermal-bound HPC machines, workload-aware runtimes can leverage hardware knobs to guarantee the best operating points in term of performance and power saving without violating thermal constraints independently for each computing unit. To conclude, it has been proposed a methodology and a runtime for identifying and automatically reducing the power consumption of the computing elements during communication and synchronization primitives filtering out phases which would detriment the time to solution of the application. The experimental results show a significant step forward respects to the current state-of-the-art solutions in power and thermal control of HPC systems.

# Contents

|   | Ack          | nowledgements                                              | 13 |  |

|---|--------------|------------------------------------------------------------|----|--|

| 1 | Introduction |                                                            |    |  |

|   | 1.1          | Scientific Applications in the Era of Exascale Computing   | 15 |  |

|   | 1.2          | Energy and Power Walls                                     | 15 |  |

|   | 1.3          | Time Constraints in Power-limited HPC Systems              | 16 |  |

|   | 1.4          | Thermal Capacitance and Heterogeneity in HPC Compute Nodes | 17 |  |

|   | 1.5          | Parallelization and Energy Efficiency                      | 19 |  |

|   | 1.6          | Contributions and Organization                             | 20 |  |

| 2 | Stat         | te of the Art                                              | 22 |  |

|   | 2.1          | Power Capping                                              | 22 |  |

|   | 2.2          | Dynamic Thermal Control                                    | 23 |  |

|   | 2.3          | Energy-aware MPI                                           | 24 |  |

| 3 | HP           | C Power Capping                                            | 29 |  |

|   | 3.1          | Overview                                                   | 29 |  |

|   | 3.2          | HPC Architectures and Power Management Systems             | 30 |  |

|   |              | 3.2.1 HPC Architectures                                    | 30 |  |

|   |              | 3.2.2 Power Management in HPC Systems                      | 30 |  |

|   |              | 3.2.3 Hardware Power Controller                            | 32 |  |

|   | 3.3          | Benchmarking Scenario                                      | 34 |  |

|   |              | 3.3.1 Architecture Target                                  | 34 |  |

|   |              | 3.3.2 Application Target                                   | 34 |  |

|   |              | 3.3.3 Monitoring Framework                                 | 35 |  |

|   | 3.4          | Experimental Results                                       | 37 |  |

|   |              | 3.4.1 Methodology                                          | 37 |  |

|   |              | 3.4.2 System Analysis                                      | 37 |  |

|   |              |                                                            |    |  |

|   |     | 3.4.3  | Application Analysis                                                                                                      | 9  |

|---|-----|--------|---------------------------------------------------------------------------------------------------------------------------|----|

|   | 3.5 | Summ   | nary on HPC Power Capping                                                                                                 | 2  |

| 4 | HP  | C Opti | mal Thermal Control 4                                                                                                     | 4  |

|   | 4.1 | Overv  | iew4                                                                                                                      | :4 |

|   | 4.2 | Work   | load and Thermal Modelling of HPC                                                                                         | :5 |

|   |     | 4.2.1  | Power and Thermal Management                                                                                              | :5 |

|   |     | 4.2.2  | Thermal Model                                                                                                             | :6 |

|   |     | 4.2.3  | Power Model                                                                                                               | :7 |

|   |     | 4.2.4  | Workload Model                                                                                                            | :7 |

|   | 4.3 | Optin  | nal Thermal Control                                                                                                       | 9  |

|   |     | 4.3.1  | Task Criticality Generator                                                                                                | 2  |

|   |     | 4.3.2  | The First Step Problem - FSP                                                                                              | 3  |

|   |     | 4.3.3  | The i-th Step Problem - ISP                                                                                               | 5  |

|   | 4.4 | Exper  | imental Results                                                                                                           | 7  |

|   |     | 4.4.1  | Emulation Framework                                                                                                       | 7  |

|   |     | 4.4.2  | Energy-aware MPI Wrapper                                                                                                  | 8  |

|   |     | 4.4.3  | Evaluation of Prediction Horizons                                                                                         | 9  |

|   |     | 4.4.4  | Evaluation of the Task Criticality Generator 6                                                                            | 0  |

|   |     | 4.4.5  | Performance Gain                                                                                                          | 2  |

|   |     | 4.4.6  | Overhead Time                                                                                                             | 4  |

|   | 4.5 | Summ   | nary on HPC Optimal Thermal Control 6                                                                                     | 5  |

| 5 | Ene | rgy-aw | are MPI Runtime 6                                                                                                         | 6  |

|   | 5.1 | Overv  | iew                                                                                                                       | 6  |

|   | 5.2 | Backg  | $round \dots \dots$ | 8  |

|   |     | 5.2.1  | Wait-mode/C-state MPI library                                                                                             | 9  |

|   |     | 5.2.2  | DVFS/P-state MPI library                                                                                                  | 1  |

|   |     | 5.2.3  | DDCM/T-state MPI library                                                                                                  | 2  |

|   | 5.3 | Frame  | ework                                                                                                                     | 3  |

|   |     | 5.3.1  | Profiler Module                                                                                                           | 5  |

|   |     | 5.3.2  | Event Module                                                                                                              | 7  |

|   | 5.4 | Exper  | imental Results                                                                                                           | 8  |

|   |     | 5.4.1  | Framework Overheads                                                                                                       | 9  |

|          |              | 5.4.2   | DVFS Overheads and Time Region Analysis | 81 |

|----------|--------------|---------|-----------------------------------------|----|

|          |              | 5.4.3   | Single-node Evaluation                  | 84 |

|          |              | 5.4.4   | HPC Evaluation                          | 86 |

|          | 5.5          | Summ    | ary on Energy-aware MPI Runtime         | 90 |

| 6        | Con          | clusion |                                         | 91 |

| Glossary |              |         |                                         | 94 |

| Bi       | Bibliography |         |                                         |    |

# **List of Figures**

| 3.1 | Example of how vary the power/voltage respect to the frequency for          |    |

|-----|-----------------------------------------------------------------------------|----|

|     | different P-state level in Intel architectures                              | 31 |

| 3.2 | Power domain identification of Intel RAPL                                   | 33 |

| 3.3 | Phases of computation and communication identified by application-          |    |

|     | aware monitoring Runtime                                                    | 36 |

| 3.4 | Time window of 50 seconds of the system monitor, every value is aver-       |    |

|     | aged over 1-second-interval window                                          | 38 |

| 3.5 | Sum of RAPL and application time grouped for frequency operational          |    |

|     | intervals                                                                   | 40 |

| 3.6 | Time gain of FF w.r.t RAPL grouped for frequency operational intervals.     | 41 |

| 3.7 | Average CPI and number of SIMD instructions retired grouped for             |    |

|     | frequency operational intervals                                             | 41 |

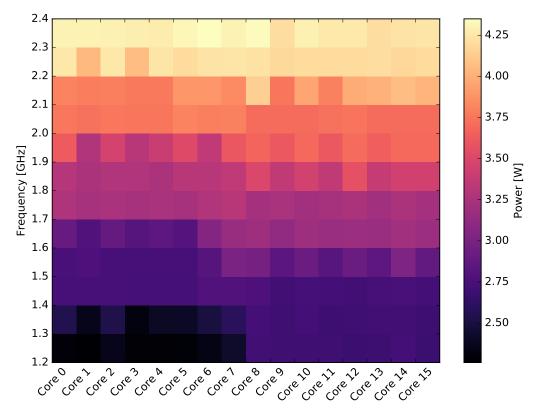

| 4.1 | Average power consumption of cores at all available frequency levels.       | 48 |

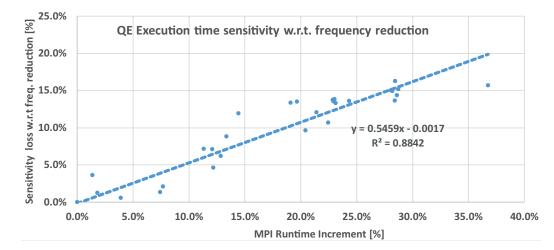

| 4.2 | Sensitivity loss with respect to the reduction of frequency compared        |    |

|     | with the increment of the time spent into MPI library                       | 49 |

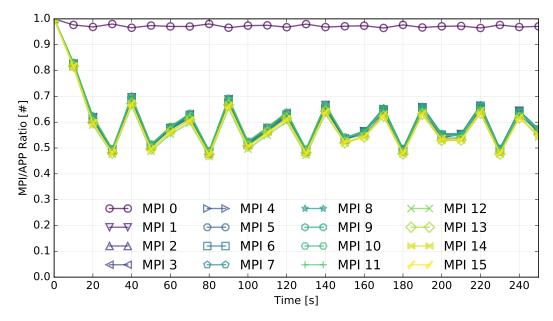

| 4.3 | Ratio of the time spent in application phases and MPI phases for each       |    |

|     | core and every 10 seconds                                                   | 50 |

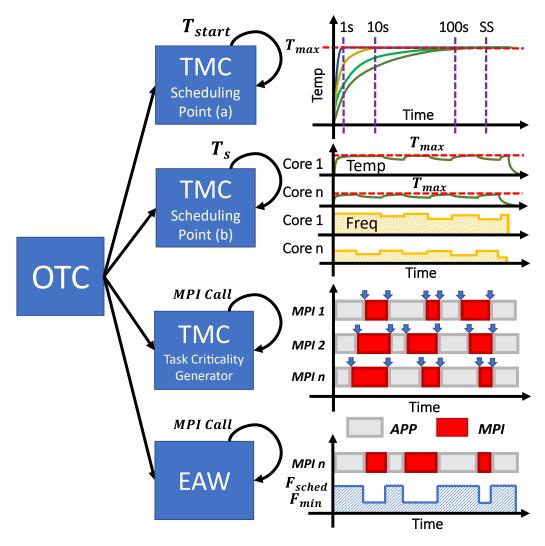

| 4.4 | Optimal thermal controller at node level                                    | 51 |

| 4.5 | General HPC application section with the naming convention used to          |    |

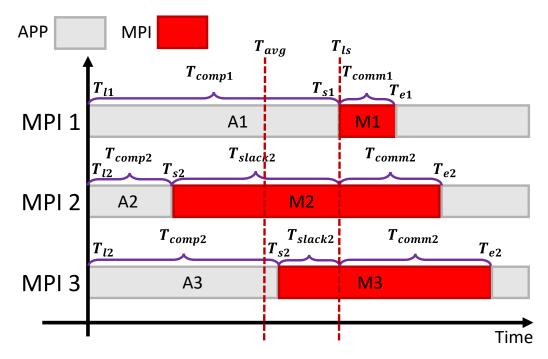

|     | calculate the criticality for each MPI task. $\ldots$ . $\ldots$ . $\ldots$ | 52 |

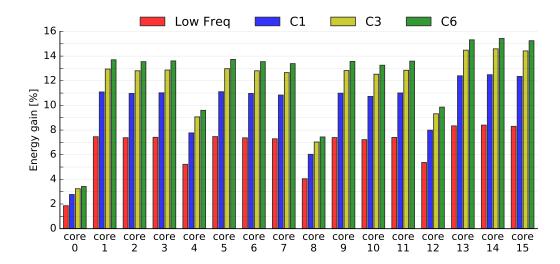

| 4.6 | Energy saving of MPI with <i>reactive policy</i> with respect to the MPI    |    |

|     | busy-waiting                                                                | 58 |

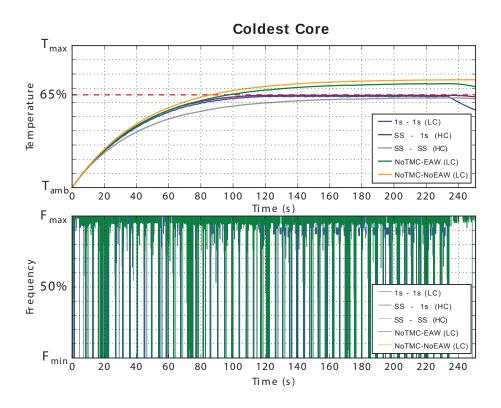

| 4.7 | Temperature and frequency evolution for the coldest core of the system      |    |

|     | - core $\#0$                                                                | 60 |

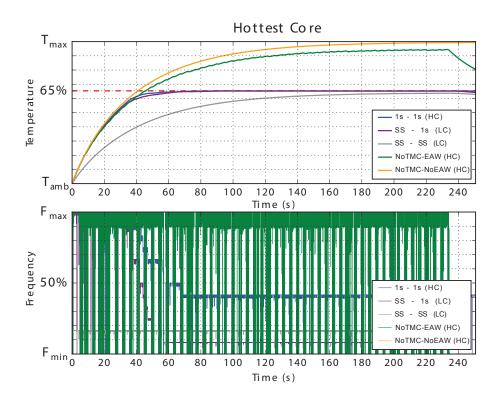

| 4.8 | Temperature and frequency evolution for the hottest core of the system      |    |

|     | - core $#14$                                                                | 61 |

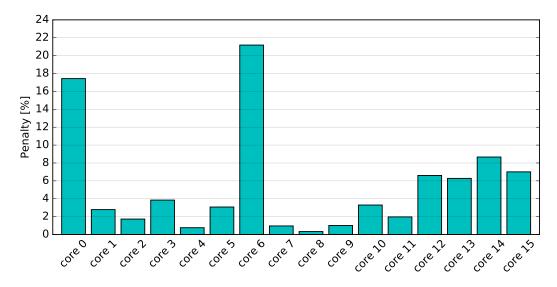

| 4.9  | Execution time penalty in benchmarks with equal per-task criticality        |        |

|------|-----------------------------------------------------------------------------|--------|

|      | level with respect to the benchmark with the TMC criticality generator.     |        |

|      | Every run identify on which core was pinned the highest critical task       | 62     |

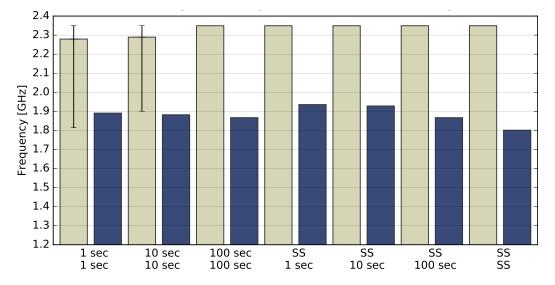

| 4.10 | 0 Comparison between average core's frequency (dark bars) and the fre-      |        |

|      | quency of the highest critical core (light bars) using different configu-   |        |

|      | ration for the optimization problem                                         | 63     |

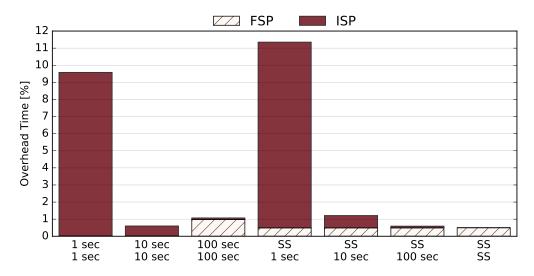

| 4.11 | 1 Cumulative overhead induces by the optimization problem using dif-        |        |

|      | ferent configurations for the optimization problem                          | 64     |

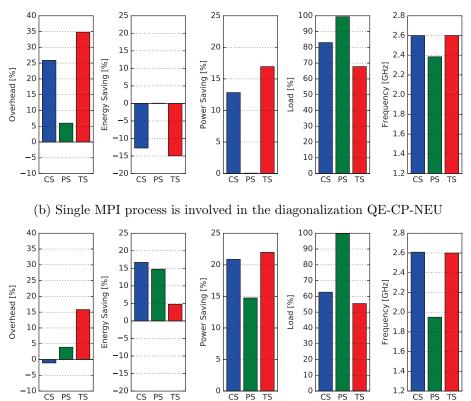

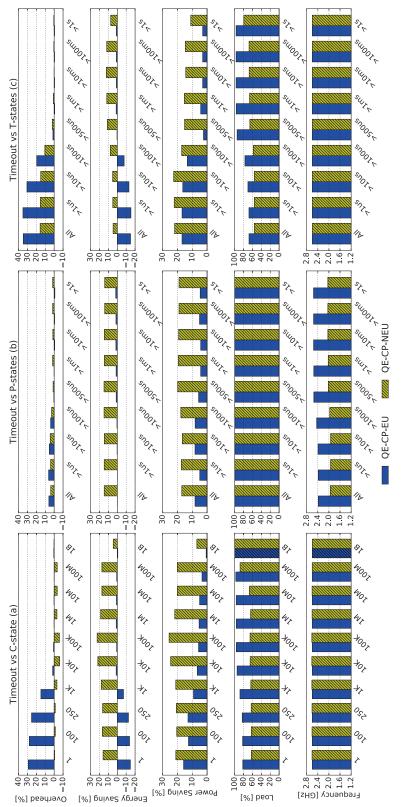

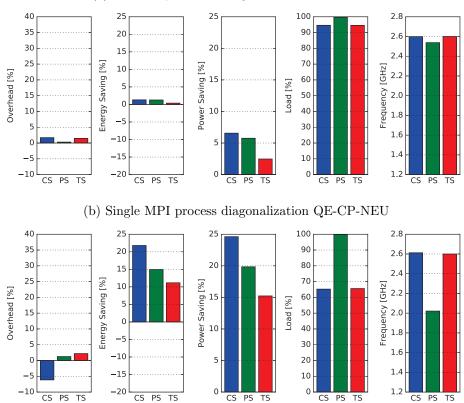

| 5.1  | Overhead, energy/power saving, average load and frequency for QE-           |        |

|      | CP-EU (a) and QE-CP-NEU (b). Legend: C-state $(CS)$ , P-state $(PS)$        |        |

|      | and T-state $(TS)$ mode. Baseline is busy-waiting mode (default mode)       |        |

|      | of MPI library.                                                             | 70     |

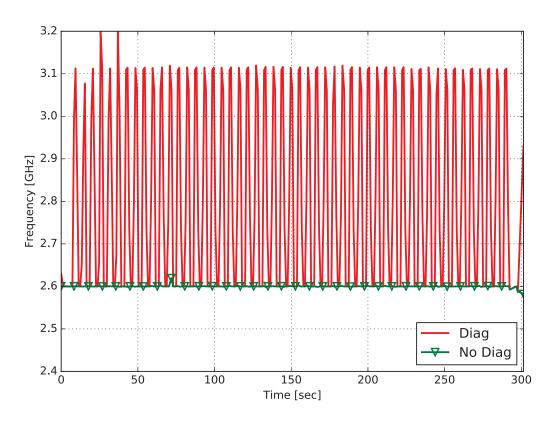

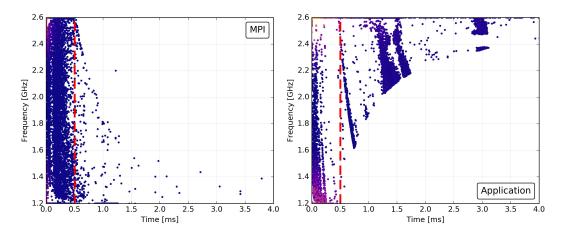

| 5.2  | Time plot of frequency for QE-CP-NEU identifies the frequency of the        |        |

|      | MPI process working on the diagonalization, $No \ Diag$ is the average      |        |

|      | frequency of MPI processes not involved in the diagonalization. $\ . \ .$ . | 71     |

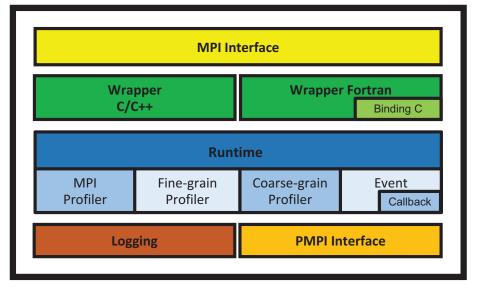

| 5.3  | Logical view of all the components of COUNTDOWN. $\ldots$                   | 74     |

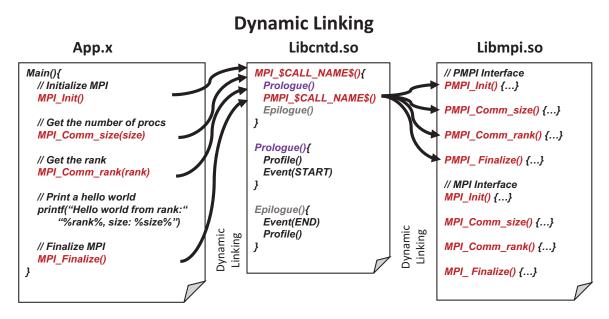

| 5.4  | Dynamic linking events when COUNTDOWN is injected at loading                |        |

|      | time in the application                                                     | 75     |

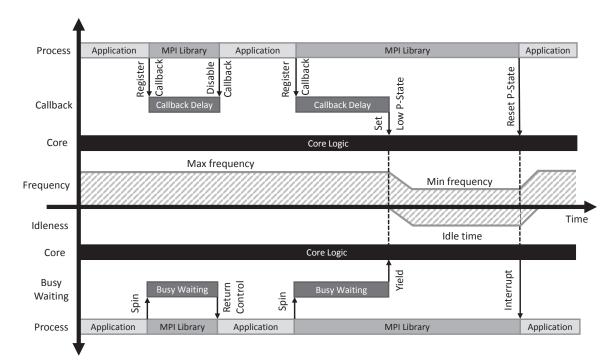

| 5.5  | On the upper side is depicted the timer strategy utilized in COUNT-         |        |

|      | DOWN, while in the lower side is depicted the idle-wait mode with           |        |

|      | timer implemented in the Intel MPI library.                                 | 77     |

| 5.6  | Impact of MPI phases duration on the overheads, energy and power            |        |

|      | savings of C/P/T-state for QE-CP-EU and QE-CP-NEU                           | 80     |

| 5.7  | Average frequency and time duration of Application/MPI phases of            |        |

|      | the single node benchmark for QE-CP-EU. The lighter zones identify          |        |

|      | higher point density.                                                       | 83     |

| 5.8  | Time and average frequency of Application/MPI phases of the single          |        |

|      | node benchmark for QE-CP-EU                                                 | 83     |

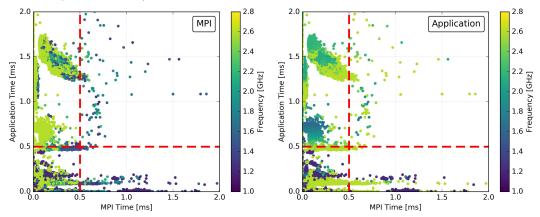

| 5.9  | Overhead, energy/power saving, average load and frequency using COUNT       | -<br>- |

|      | DOWN for QE-CP-EU (a) and QE-CP-NEU (b). Legend: C-state                    |        |

|      | (CS), P-state $(PS)$ and T-state $(TS)$ mode. Baseline is busy-waiting      |        |

|      | mode of MPI library.                                                        | 85     |

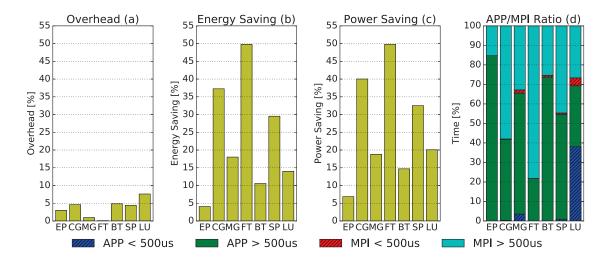

| 5.10 | Experimental results of NAS parallel benchmarks using COUNTDOWN.    |    |

|------|---------------------------------------------------------------------|----|

|      | Baseline is busy-waiting mode (default mode) MPI library            | 87 |

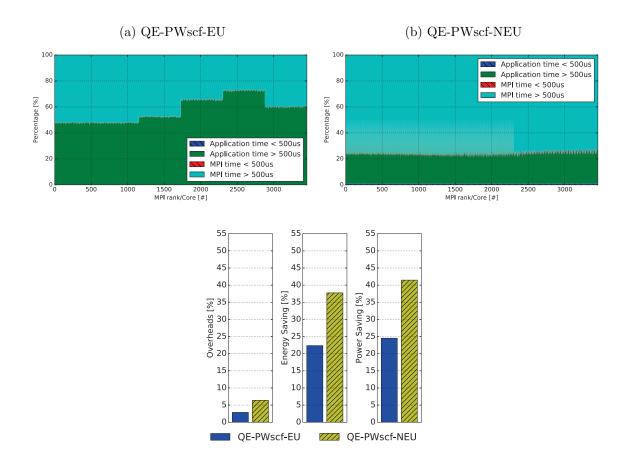

| 5.11 | (a,b) Sum of the time spent in phases longer and shorter than 500us |    |

|      | for QE-PWscf-EU and QE-PWscf-NEU.                                   | 89 |

|      |                                                                     |    |

# Acknowledgements

It is a great pleasure to express my thanks to the many people who contributed and make possible my Ph.D. and this doctoral dissertation.

Firstly, I would like to express my sincere gratitude to my advisor Prof. Luca Benini for the continuous support of my Ph.D study and research's activity, for his motivation, and immense knowledge. His guidance helped me in all the time during my Ph.D. and writing of this thesis. I owe a great debt of gratitude for enlightening me the first glance of research. I could not have imagined having a better advisor and mentor for my Ph.D study.

My special thanks go to the Dr. Andrea Bartolini who have been my co-advisor during these years of doctoral study. Andrea has been a mentor and a friend, from whom I have learnt the vital skills and discipline of academic research. His professional guidance and careful scrutiny of my research work has been invaluable. Thank you again Andrea!

I would like to express my thanks to the dissertation committee: Dr. Carlo Cavazzoni and Prof. Mathieu Luisier, for their insightful comments and appreciations, but also for the hard question which helped me to make this thesis considerably better.

I again want to thank the Prof. Luisier who provided me a great opportunity to join his team at ETH Zurich as Ph.D visiting student, and who gave access to the laboratory, research facilities and financial support.

I would like to thank to all the CINECA staff, in particular to the Dr. Cavazzoni and Dr. Piero Bonfà. Without their precious support and possibility to use the HPC systems of CINECA, it would not be possible to conduct this research.

I thank my fellow labmates for their technical helps and friendship, I have appreciated a lot the fun we have had in these years. I list them in alphabetic order: Alessandro Capotondi, Andrea Borghesi, Andrea Marongiu, Davide Rossi, Federico Pittino, Francesco Beneventi, Francesco Conti, Francesco Paci, Giuseppe Tagliavini, Igor Loi, Manuele Rusci, Marco Balboni, Simone Benatti and Thomas Bridi. Also I thank my colleagues and friends at ETH Zurich: Abbas Rahimi, Antonio Libri, Antonio Pullini, Daniele Palossi, Frank Gurkaynak, Lukas Cavigelli, Mario Osta, Renzo Andri and Sara Fiore. Also, I thank Angela Cavazzini for the invaluable help to fill-out the bureaucracy documents during these years.

I would also like to acknowledge the support and encouragement of all my friends (in no particular order): Lorenzo Monachini, Mariani's family, Vittorio Muzioli, Davide Medici, Luca Moretti, Denis Billi, Nannuzi's family, Mambelli's family, Re's family, Leonelli's family, Marsili's family, Battagli's family, Federico Ricci, Irene Menghi, Sara Valentini, Marco Lessi, Pablo Montemaggi, Giovanni Campana, Ferrante's family, Mariotti's family, Bertelli's family, Zangoli's families, Mariangela Leone and all the friends of SdC. Moreover, I want to thank my friends of "Meeting di Rimini" that accompanied me during these years: Andrea Battagli, Marco Pacelli, Sandro Ricci, Emanuele Forlani, Matteo Turchi, Eugenio Andreatta, Stefano Pichi Sermolli, Federico Prinetto, Michele Arduini, Stefano Re, Andrea Acquaviva and all the voluntaries.

Last but not the least, I must express my very profound gratitude to all my parents and in particular to my family: My father Massimo, my mother Silvia and my sister Elena for providing me with unfailing support and continuous encouragement throughout my years of study and through the process of researching. This achievement would not have been possible without you.

> Thank you all! Daniele

# Chapter 1

# Introduction

## 1.1 Scientific Applications in the Era of Exascale Computing

In the past four decades scientific applications in many fields have evolved from simple homebrewed codes to complex community projects steadily growing thanks to a distributed, and often loosely coordinated, effort from a variety of groups, laboratories, and institutions. This lively and creative anarchy was facilitated by the smooth progress of hardware architecture, which did not require major disruptions of the programming models. Notwithstanding its benefits, this loosely coordinated development model also had a strong and detrimental impact on the long-term sustainability of software projects, which is becoming particularly critical in the proximity of the next hardware revolution that will occur with the transition to exascale computing. The slowing down of Moore's law and the end of the Dennard's scaling [1, 2] in CMOS technology sets new thermal and power challenges in forthcoming machines which would disrupt the typical programming model adopted so far by scientific community.

#### 1.2 Energy and Power Walls

While Moore's law is approaching its end, Dennard's scaling has already run out of steam. This has caused a constant increase of the power density required to operate each new processor generation at its maximum performance: causing de facto, the total power consumption of each device to limit the practical achievable performance. In addition of the detrimental effect of power density on the final performance, total power consumption needs to be delivered and removed through cooling consuming additional power. All these issues impact on the total power budget available to the data centres, which limits the computing capacity [3]. As a matter of fact, energy and power walls are the key challenges to be faced in order to deliver the planned performance growth in future.

The effects of energy and power walls are already visible today in the Top500[4] and Green500[5] lists. Until June 2013, every new most powerful supercomputer in the world (1st in the Top500 list) has marked an increase in its power consumption. Reaching with Tianhe-2, 17.8 MWatts of IT peak power consumption, which increases to 24MWatts when considering also the cooling power [6]. This has set the record for the power consumption of a single supercomputer installation, reaching a power provisioning around 20MWatts [7]. The total cost of ownership TCO of a supercomputer is moving from architecture to the power budget, this has set a new practical limit. The fact is that to maintain the performance grown of the past decades, is nowadays possible only increasing the power budget: as a matter of fact, supercomputers are becoming power limited [8]!

#### 1.3 Time Constraints in Power-limited HPC Systems

As it previously seen, supercomputer power consumption is a critical aspect and imposes to target a well-define power budget for the system at design time. The power design must consider the worst-case power consumption of the computing resources of a supercomputer. However, supercomputer workloads rarely cause worst-case power consumption during their life making worst-case design approaches a bad choice which decreases the average supercomputing performance. Power capping approaches support the design for "the average power consumption case" by packing more computing capacity, with a feasible power budget under average workload and dynamically reducing the performance during the execution of workloads with peak power consumption.

At the basis of these approaches there is the capability of computing elements to trade off performance with power consumption. Dynamic and voltage frequency states (DVFS, also known as performance states or P-states [9])) allow the reduction of the power consumption during active computation. Dynamic power management policies take advantage of these HW states to create feedback loops adapting the performance to workload phases aiming to reduce the energy consumption or ensure a specific power and thermal budget. Pure software implementations of these policies have clear software advantages but need to be executed on the same computational resources, interrupting the application flow and causing overheads.

Recently vendors have added HW components to implement these policies in hardware allowing a more fine-grain control. Intel Running Average Power Limits (RAPL) technology can enforce in hardware a given power limit. This is done exploiting power sensors and power management knobs. Current RAPL implementations aim to enforce a constant power consumption within a ten-milliseconds time window. However this is far below the timescale of supercomputing centres where the power budget must be respected in large time windows coming from the power grid and supplier [10, 11].

## 1.4 Thermal Capacitance and Heterogeneity in HPC Compute Nodes

Power capping mechanisms are very effective to control the power consumption during supercomputers' life. But the trend of increasing supercomputers' power consumption has also seen as collateral effects of the rapid increase of CPU's power density that in turn have limited the achievable performance caused by higher temperatures. Power capping mechanisms do not guarantee a safe and reliable use of high-performance computing (HPC) nodes from a thermal point of view, which need specific thermal policies and controllers to avoid overheating and thermal hazards.

The maximum safe temperature at which the processing elements of HPC nodes can run depends on the cooling technologies. For instance, Intel Xeon E5-26XX v3 server class processors have specifications on the maximum silicon temperature ranging from  $69^{\circ}C$  to  $101^{\circ}C$  according to the package thermal resistance (cost) and the nominal thermal design power (TDP)<sup>1</sup>. To enforce a safe working temperatures, HPC nodes use active-cooling solutions which translate in additional power consumption.

Dynamic thermal management (DTM) has been studied to limit the cooling effort by controlling and reducing the heat generation. This is achieved monitoring the HW thermal sensors and the application workload reacting on DVFS states. New

<sup>&</sup>lt;sup>1</sup>Intel Xeon®Processor E5 v3 Family Thermal Guide

generation multi-core CPUs, which are used in HPC systems, can apply a different voltage and frequency to each core independently [12]. This opens new scenarios for fine-grain DVFS control in DTM solution. Operating systems (OS) use feedback loops between sensors and DVFS states of each core to scale down frequency states to avoid thermal hazards.

Cooling and heat generation are rapidly becoming new key limiters for high performance processors, especially for HPC data centres which typically are hosted clusters of thousands of compute nodes. Each compute node could be equipped with tens of computing units, thus scientific applications can take advantage of these parallel architectures to speed up the execution of large-scale simulations and workloads. The message-passing interface (MPI) programming model is the de facto standard in HPC programs for splitting the workload in tasks that execute in parallel in the compute nodes of the HPC machine. During the execution of an MPI-based application, the tasks alternate phases of computation with phases of communications. A critical design parameter in MPI applications is the balancing of the workload between the tasks, and the minimization of the waiting time for each tasks in the synchronization points [13, 14]. Critical tasks in a specific code segment, are the ones which carry on the most workload and arrive late at a synchronization point. In practice, they limit the application speed in the specific code segment. HPC application developers and users parameterize the application to balance the workload. This intended to limit the slowdown induced by critical tasks. DTM techniques can create local unbalance between cores to maximize processor's throughput. This can be significantly detrimental for application performance as it may slow down critical tasks in parallel applications.

Several solutions explore proactive techniques for DTM strategies to improve performance in thermal-bound systems [15, 16, 17, 18]. DTM strategies take advantages of the heterogeneity in the thermal dissipation of cores, which is related to chip and board design, and manufacture, to maximize the performance. However, these approaches often result in a performance unbalance between the cores. Coldest cores run faster than hottest cores.

#### 1.5 Parallelization and Energy Efficiency

Power capping and thermal control systems are both safety mechanisms to avoid critical situations in HPC machines but none of them impact on the energy efficiency of the application and today the power consumption is one of the most important key limiting factor in HPC systems.

It is known that a significant amount of time in large scale HPC applications is wasted in communication synchronization-related idle times. A typical HPC application is composed of several processes running on a cluster of nodes which exchange messages through a high-bandwidth, low-latency network. These processes can access the network sub-system through the MPI library. Usually when the scale of the application increases, the time spent by the application in the MPI becomes not negligible and impacts the overall power consumption.

Low power design strategies enable computing resources to trade-off performance and power consumption through low power states. These states obtained by DVFS states (P-state), clock gating or throttling states (T-states), and idle power saving states, which switch off unused resources (C-states) [9]. Power states transitions are controlled by hardware policies, OS policies, and with an increasing emphasis in recent years, at user space by the final users [19, 20, 21, 22] and at execution time [23, 24].

While OS policies focus to maximize the utilization of the computing resources increasing the processor's speed proportionally to the processor's utilization — two main families of power control policies are emerging in scientific computing. The first is based on the assumption that performance penalty can be tolerated to reduce the overall energy consumption [19, 25, 20, 21]. The second is based on the assumption that it is possible to slow down the speed of a processor only when it does not execute critical tasks: to save energy without penalizing application performance [23, 24, 26, 22]. Both approaches are based on the concept of application slack/bottleneck (memory and network communication) that can be opportunistically exploited to reduce power and to save energy. However, there are drawbacks which limit of usage of these concepts in a production environment. The first approach causes overheads in the application time-to-solution (Tts) limiting the supercomputer throughput and capacity. The second approach depends on the capability of predicting the critical tasks in advance with severe performance loss in case of mispredictions.

By default, when processes are waiting in synchronization primitives, the MPI

libraries use a busy-waiting mechanism. However, during MPI primitives the workload is primarily composed of wait times and memory/network accesses for which running an application in a low power mode may result in lower CPU power consumption with limited or even no impact on the execution time.

MPI libraries implement idle-waiting mechanisms, but these are not used in practice to avoid performance penalties caused by the transition times to enter and exit of low-power states [27]. As a matter of fact, there is no known low-overhead and reliable mechanism for reducing selectively the energy consumption during MPI communication slack.

### 1.6 Contributions and Organization

This thesis faces the power and thermal issues which will affect the next generation of supercomputers leveraging to the typical programming models adopted so far by scientific community. The presented SW approaches avoid to change the source code of scientific applications leaving users and developers to focus only to the usability and on the functionality of the applications. To make this possible, the proposed run-time libraries are able to extract application requirements at execution time and propagating them to the OS and HW level.

In the thesis is shown how i) using SW strategies for relaxing the power capping constraint in HPC systems can have benefit in performance instead to force a constant power consumption through HW mechanisms. ii) it has been developed an optimal thermal control for scientific applications to address thermal capacitance and heterogeneity in thermal-bound HPC nodes, and iii) it has been developed an MPI-aware runtime to save energy in large-scale scientific applications.

This thesis is organized as followed:

- In Chapter 2 are presented the state-of-the-art works in the research fields of power capping systems, dynamic thermal control and power/energy management approaches for scientific computing systems.

- In Chapter 3, it has been shown a novel exploration work on power capping mechanisms for power constrained HPC nodes and it is shown how scientific applications can have performance benefits relaxing the power constraint using large time windows.

- In Chapter 4, it has been developed a an optimal thermal management runtime for scientific applications in order to face thermal hazards and heterogeneity in HPC processors.

- In Chapter 5, it has been developed a run-time library, analysis tool and methodology to save energy in scientific applications by leveraging on the communication slack for real-production HPC systems.

- The conclusion of this thesis are presented in Chapter 6 with a summary of the outcomes.

# Chapter 2

## State of the Art

## 2.1 Power Capping

Several approaches in the literature have proposed mechanisms to constrain the power consumption in large-scale computing infrastructures. These can be classified into two main families. Approaches in the first class use predictive models to estimate the power consumed by a job before its execution. At job scheduling time, this information is used to allow into the system jobs that satisfy the total power consumption budget. HW power capping mechanisms like RAPL are used to ensure that the predicted budget is respected during all the application phases and to tolerate prediction errors in the job average power consumption estimation [28, 29, 30]. Approaches in the second class distribute a slice of the total system power budget to each active computing element. The per-compute power budget is ensured to hardware power capping mechanisms like RAPL. The allocation of the power budget to each compute node can be done statically or dynamically [31, 22, 32, 33]. It is the goal of the runtime to trade off power reduction with application performance loss. Eastep et al. propose GEOPM [22], an extensible and plug-in based framework for power management in large parallel systems. GEOPM is an open-source project and it exposes a set of APIs that programmers can insert into applications to combine power management strategies and HPC workload. A plugin of the framework target power constraint systems aiming to speed up the critical path migrating power to the CPU's executing the critical path tasks. Authors in [34] quantitatively evaluated RAPL as a control system in term of stability, accuracy, settling time, overshoot, and efficiency. While the work proposed in Chapter 3 evaluates the proprieties of RAPL mechanism

with respect to a software-based power capping mechanism and shows how vary the performance penalty in different application workload.

#### 2.2 Dynamic Thermal Control

Different works were focused on thermal-aware workload allocation based on DVFS strategies. Those techniques include: (i) on-line optimization policies [35, 36, 37, 38], which are based on predictive models and embedded sensors to read the current temperatures on the system; (ii) scheduling approaches for off-line allocation [39, 40] which rely on simplified thermal models, usually embedded in the target platform [36] or simulating chip temperature [41].

Today's thermal management works range from mobile to large scale parallel machine, like supercomputer and HPC systems. Xie et. al. [42] show that mobile systems are thermally constraint. Interestingly, thermal constraints come from user experience and not from silicon limits. Conficoni et al. [43] show that the power cost of HPC cooling depends on several factors, for instance IT power consumption, the cooling control policies, and the ambient temperature. On the other hand, the power consumption is intertwined with workload execution and computation phases [44, 45], which can produce high thermal heterogeneity between nodes and CPUs. For this reason, over-provisioning cooling design can cause severe inefficiencies.

Wang et. al. [46] show that fan power can account for up to 23% of typical server power and scales super-linearly with node utilization. Authors in [47] extract a predictive thermal model directly from the multicore device correlating power, performance and thermal sensors implemented in hardware. They show that the thermal evolution of a multicore device can be modeled with a linear state-space representation. The leakage-power dependency from temperature can be modeled as a perturbation of the state matrix of the thermal model. Due to different materials present in the heat dissipation path, the thermal transient is multi-modal with time constants that vary from ms to tens of seconds. Beneventi et al. [48] shows in an Intel based computing nodes with 36 physical cores, that the increased number of processors integrated in the same die generates significant thermal gradients and this thermal heterogeneity can be exploited by thermal-aware MPI task allocation to reduce the fan speed and power without impacting the application performance. To find a close form solution of the fast mapping problem under thermal constraint, Hanumaiah [49] assumes the absence of direct thermal exchange from the hot to the cold cores of the same die. Mutapcic et al. [40] formulate a convex optimization problem to control the speed of the processor, which is subject to environment thermal constraints. They solve it with a specialized algorithm. However, their optimization algorithm does not cover the case of a higher number of cores than the number of tasks (some cores remain in idle state).

Predictive controls are often based on thermal and optimization models which can guarantee a safe-working condition applying performance constraints to the systems. Rudi et al. [50] have developed an integer linear programming (ILP) model for task allocation and frequency selection to avoid thermal hazards in many-core architectures. This thermal control is able to leverage on the idleness of the cores when tasks are less than the number of available cores allocating tasks on the coldest cores and leaving hottest ones in idle states. The limit of [50] is the task allocation, which is not handled by the systems.

## 2.3 Energy-aware MPI

Several works developed mechanisms and strategies to maximize the energy savings at the expense of performance. These works focus on operating the processors at a reduced frequency for the entire duration of the application [19, 20, 21]. The main drawback of these approaches is the negative impact on the application performance which is detrimental to the data centre cost efficiency.

Fraternali et al. [19, 25] analyzed the impact on frequency selection on a green HPC machine which can lead a significant global energy reduction in real-life applications, but can also induce significant performance penalties. Auweter et al. [20] developed a energy-aware scheduler that relies on a predictive model to predict the wall-time and the power consumption at different frequency levels for each running applications in the system. The scheduler uses this information to select the frequency to apply to all the nodes executing the job to minimize the energy-to-solution allowing unbounded slowdown in the Tts. The main drawback of this approach is the selection of a fixed frequency for the entire application run which can cause a significant penalty on CPU-bound applications. Hsu et al. [21] present a different approach where users

can specify a maximum-allowed performance slowdown for their applications while the proposed power-aware runtime reduces frequency on time windows, respecting the user's specified constraint. For this purpose, the proposed runtime estimates the instruction throughput dependency over frequency and minimizes the frequency while respecting the user's maximum-allowed performance slowdown. Similarly to the previous approach, an energy gain is possible only by degrading the performance of the application.

The main drawback of the works mentioned so far is that they lead to a systematic increase of Tts, which may be acceptable for the user, but it is not easily acceptable by the facility manager, since it reduces the data centre cost efficiency and TCO [51]. For this reason, there is a trend in the literature towards HPC energy reduction methodologies with negligible or low impact on Tts of the running applications.

Sundrival et al. [52, 53, 54, 55] analyze the impact of fine-grain power management strategies in MVAPICH2 communication primitives, with a focus on send/receive [52], AlltoAll [53], and AllGather communications [54]. In [52] the authors propose an algorithm to lower the P-state of the processor during send and receive primitives. The algorithm dynamically learns the best operating points for the different send and receive calls. In the [54, 53, 55] works, the authors proposes to lower also the T-state during the send-receive, AllGather and AlltoAll primitives as this increases the power savings. In these works, authors discover that the overhead of this solution is more prominent when these communication patterns are intra-node. Moreover, the overhead of the proposed strategy decreases with message dimension. Authors shows that this overhead is different within the different kernels implementing the communication primitives, thus they propose a low power implementation of the studied MVAPICH2 primitives where P-state and T-state are lowered in specific stages of these primitives. These approaches show that power saving can be achieved by entering in a low power mode during specific communication primitives. To be effective, these predicting algorithms needs to be aware of the internal logic of the communication primitive, thus they depend on a specific MPI implementation. Differently, the work in Chapter 5 shows that important savings can be achieve without impacting the implementation of the communication primitives.

Rountree et al. [56] analyzes the energy savings which can be achieved on MPI parallel applications by slowing down the frequencies of processors which are not in the critical path. Authors of the paper define tasks as the region of code between

two MPI communication calls. In this thesis, tasks are refer to phases. The critical path is defined as the chain of the tasks which bounds the application execution time. Indeed, cores executing tasks in the critical path will be the latest ones to reach the MPI synchronization points, forcing the other cores to wait. In [56] authors propose a methodology for estimating offline the minimum frequency at which the waiting cores can execute without affecting the critical path and the Tts.

A later work of the same authors [23], implements an online algorithm to identify the task and the minimum frequency at which it can be executed without worsening the critical path. In a similar way, Kappiah et al. [26] developed Jitter, an online runtime based on the identification of the critical path on the application among compute nodes involved in the application run. Liu et al. [57] use a similar methodology as Kappiah et al. [26] but they apply it to a multi-core CPU.

The authors of [58], as in [56, 23], focus on saving power by entering in a low power state for processes which are not in the critical path. The authors propose an algorithm to save energy by reducing the application unbalance. This is based on measuring the start and end time of each MPL\_barrier and MPL\_Allreduce primitives to compute the duration of application and MPI code. Based on that the authors propose a feedback loop to lower the P-state and T-state if in previous compute and MPI region the overhead was below a given threshold. The algorithm is based on the assumption that the duration of current application and MPI phases will be the same of the previous ones.

To save energy during MPI phases, Lim et at. [59] propose to reduce core's frequency in "long" MPI phases. Subsequent short MPI phases are grouped together and treated as a single long MPI phase. They use an algorithm to select the best P-state to be applied according to the micro-operation throughput in the MPI phase. Similarly to [56, 23], this approach is based on the assumption that the duration and instruction composition of current MPI phase will be the same as the previous ones. Moreover, by treating short MPI phases as a single long one, the application phases between them is executed at reduced frequency, leading to Tts overheads.

Li et al. [60] use a similar approach to [59] to reduce power consumption in synchronization points. This work focuses on collective barriers for parallel applications in shared-memory multiprocessors. Differently from the previous approaches, instead of using P-state, they use C-state and specific hardware extensions to account for their transitioning (sleep and wake-up) times. As in the previously described approaches, this runtime uses a history-based prediction model to identify the duration of the next barriers.

The authors of [61] show that the approaches in [56, 23] and the ones which estimate the duration of MPI and communication phases based on a last-value prediction [59, 60] can lead to significant misprediction errors. The authors propose to solve this issue by estimating the duration of the MPI phases with a combination of communication models and empirical observation specialized for the different groups of communication primitives. If this estimated time is long enough, they will reduce the P-state. In Chapter 5, is shown the proposed approach of this thesis and how this can be achieved without a specific library implementation and communication models.

Li et al. [24] analyzed hybrid MPI/OpenMP applications in term of performance and energy saving and developed a power-aware runtime that relies on dynamic concurrency throttling (DCT) and DVFS mechanisms. This runtime uses a combination of a power model and a time predictor for OpenMP phases to select the best cores' frequency when application manifests workload imbalance.

The works in the second group, namely [26, 57, 24, 59, 60], have in common the prediction of future workload imbalances or MPI phases obtained by analyzing previous communication patterns. However, this approach can lead to frequently mispredictions in irregular applications [62] which cause performance penalties. The methodology proposed in Chapter 5, differs from the above approaches (and complements them) because it is purely reactive and does not rely on assumptions and estimation of the future workload unbalance.

The power management literature has analyzed in depth the issue of prediction inaccuracy and predictive model overfitting [63]. One key outcome form of this work proposed in 5, is that timeout-based policies are effective if predictions are not available (e.g. when data is being collected for building a predictive model), and are also essential in mitigating miss-prediction overheads. Timeout-based power management policies are simple to calibrate, as they only require to find a timeout threshold that prevents power state changes when the duration of the slow-down (or shut-down) phase is not long enough to amortize power state transition overhead. In the following Chapters, it is shown how to identify the critical timeout threshold in the specific context of MPI applications running on HPC machines.

In a similar manner, another plugin of GEOPM [22] can selectively reduce the frequency of the processors in specific regions of codes flagged by the user by differ-

entiating regions in CPU, memory, IO, or disk bound. Today, GEOPM is capable of identifying MPI regions and to reduce the frequency based on MPI primitive type. However, it cannot differentiate between short and long MPI and thus cannot control the overhead caused by the frequency changes and runtime in short MPI primitives. The methodology proposed in this thesis addresses this limitation and can be integrated in future releases of GEOPM, as its design principles are completely compatible with it (i.e. no application code modifications are required).

# Chapter 3

# **HPC Power Capping**

### 3.1 Overview

As explained in Section 1.3, leveraging on power capping mechanisms to aggregate more computing units in power-constrained systems adds both advantages and challenges. In this exploration work are evaluated the impact of HW power capping mechanisms on a real scientific application composed by parallel execution. By comparing a HW capping mechanism against static frequency allocation schemes, it can be seen that a speed up can be achieved if the power constraint is enforced in average, during the application run, instead of on short time periods. RAPL, which enforces the power constraint on a few milliseconds time scale, fails on sharing power budget between more demanding and less demanding application phases.

In detail, it has been analyzed the efficacy (measured as application Tts) of power capping to maintain the same power budget using (i) RAPL controller and (ii) a simple fixed frequency allocation that statically assigns cores' frequency for the entire application time. In the first case, RAPL imposes the power constraint every ten milliseconds modulating the operating point (i.e. clock frequency) to workload changes with a similar time granularity. On the contrary, the second set-up uses fixed frequency for the entire application time selected to obtain for the entire duration of the application the same average power consumption as RAPL. This work has been presented to the scientific community in [45].

# 3.2 HPC Architectures and Power Management Systems

#### 3.2.1 HPC Architectures

A typical HPC system is composed of tens to thousands compute nodes interconnected with a low-latency high-bandwidth network. Compute nodes are usually organized in sub-clusters allocated at execution time from the system scheduler according to the users' request. Sub-clusters have a limited lifetime, after which resources are released to the system scheduler. Users request resources through a batch queue system, where they submit applications jobs. Even a single node can be split in multiple resources shared among users. The single indivisible units in an HPC system are: CPUs, memory and possibly accelerators (GPGPU, FPGA, many-core accelerator, etc.).

HPC applications typically is based on a single program multiple data (SPMD) execution model, where the same executable is instanced multiple time on different computing element of the cluster; each instance works on a partition of the global workload and communicates with other instances to orchestrate subsequent computational steps. For this reason, an HPC application can be seen as the composition of several tasks executed in a distributed environment which exchanges messages among all the instances. Achieving high-performance communication on distributed applications in large clusters is not an easy task. The MPI runtime responds to these demands by abstracting the level of network infrastructure using a simple but high-performance interface for communication which can scale up on thousands of nodes.

HPC machines are extreme energy consumers and the server rooms require a proportioned cooling system to avoid overheating. The extreme working conditions of this machines bring a lot of inefficiencies in terms of energy and thermal control, that turn in computational performance degradation. HW power managers are becoming a fundamental component to control power utilization using different strategies in order to reduce energy waste and, at the same time, assure a safe thermal environment.

#### 3.2.2 Power Management in HPC Systems

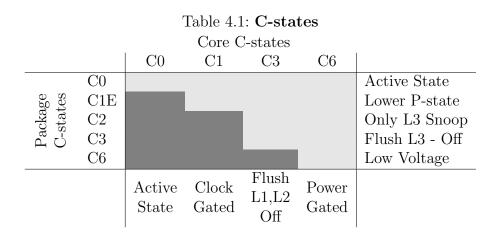

Nowadays, operating systems can communicate with different hardware power managers through an open standard interface called advanced configuration and power interface (ACPI) [9]. This work focuses on ACPI implementation of Intel architectures, since most of the HPC machines are based on Intel CPUs. Intel implements the ACPI specification defining different component states where a CPU can use to reduce power consumption. Today's CPU architectures are composed of multiple processing elements (PE) that can communicate through a on-chip network subsystem. Intel architecture optimizes ACPI using different power saving levels for cores and uncore components. The ACPI standard defines P-state to select DVFS operating points targeting the reduction of active power, while also defines specific idle states to manage power consumption during inactivity time of the CPU. In this work, it has been only considered P-states to manage DVFS control knobs, this because tipycal HPC applications do not manifest idle time during the execution.

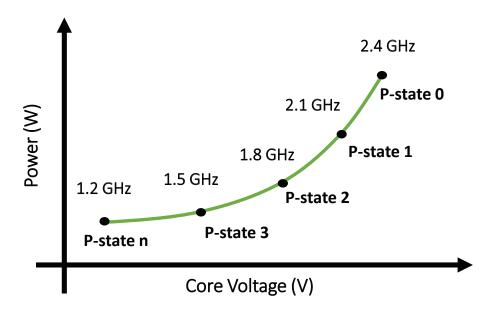

Figure 3.1: Example of how vary the power/voltage respect to the frequency for different P-state level in Intel architectures

Intel P-states show in Figure 3.1 defining a number of levels which are numbered from 0 to n, where n is the lowest frequency and 0 is the highest frequency with the possibility to take advantage of *Turbo Boost technology*. *Turbo Boost* is an Intel technology that enables processors to increase their frequency beyond the nominal via dynamic control of clock rate. The maximum turbo frequency is limited by the power consumption, thermal limits and the number of cores that are currently using turbo frequency. Since Haswell architecture, Intel cores allow independent per-core P-state.

#### Linux Power Management Driver

Intel P-states are managed by the OS power governor implemented in the Linux kernel driver. By default on Linux system, Intel architectures are managed by a kernel module called *intel\_pstate* developed by Intel. But *intel\_pstate* driver does not support a governor that allows users to select per-core fixed frequency. Differently, the standard power management driver of Linux *acpi-cpufreq* does it. *acpi-cpufreq* is similar to Intel driver but implement a large set of governors. The available governors are:

- 1. *powersave*: this governor runs the CPU always at the minimum frequency.

- 2. *performance*: runs the CPU always at the maximum frequency.

- 3. userspace: runs the CPU at user specified frequencies.

- 4. ondemand: scales the frequency dynamically according to current load [64].

- 5. conservative: similar to ondemand but scales the frequency more gradually.

It has been used *acpi-cpufreq* driver with *userspace* governor that allows to select per-core fixed frequency.

#### 3.2.3 Hardware Power Controller

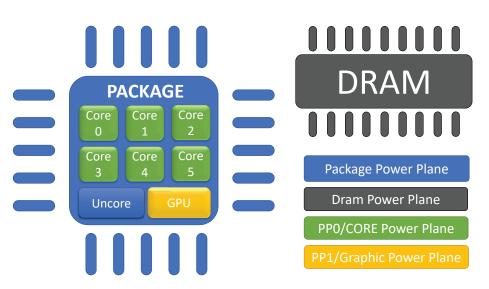

Today's CPU architectures implement reactive HW controller to maintain the processor always under an assigned power budget. The HW controller tries to maximize the overall performance while constraining the power consumption and maintaining a safe silicon temperature. Intel architectures developed its own HW power controller called Running Average Power Limit (RAPL) depicted in Figure 3.2. RAPL is a control system, which receives as input a power limit and a time window. As consequent, RAPL continuously tunes the P-states to ensure that the limit is respected in the specified time window. RAPL can scale down and up cores' frequencies when the power constraint is not respected overriding the selected P-state. RAPL power budget and time window can be configured writing a model-specific register (MSR). Maximum and minimal values for both power budget and time window are specified in a read-only architectural register. Values for both power and time used in RAPL

Figure 3.2: Power domain identification of Intel RAPL

are represented as multiple of a reference unit contained in a specific architectural register. At the machine startup, RAPL is configured using maximum power budget of the CPU with a 10ms time window. RAPL also provides 32bit performance counters for each power domain to monitor the energy consumption and the total throttled time. RAPL implements four power domains which can be independently configured:

- 1. *Package Domain*: this power domain limits the power consumption for the entire package of the CPU, this includes cores and uncore components.

- 2. *DRAM Domain*: this power domain is used to power cap the DRAM memory. It is available only for server architectures.

- 3. *PP0/Core Domain*: is used to restrict the power limit only to the cores of the CPU.

- 4. *PP1/Graphic Domain*: is used to power limit only the graphic component of the CPU. It is available only for client architectures due Intel server architectures do not implement graphic component into the package.

In the experimental result, the exploration focus on the package domain of RAPL controller because core and graphic domains are not available for Intel Xeon processors while DRAM domain is left for future exploration works. Also the time windows of package domain (which can be set in a range of 1ms to 46ms in target system) was

tested to check its impact on application performance. The experimental results show that this parameter does not lead to noticeable changes in the results obtained. For this reason, results report only the default 10ms time window configuration.

## 3.3 Benchmarking Scenario

#### 3.3.1 Architecture Target

The architecture target used in the experimental Section is a Tier-1 high-performance computing infrastructure based on IBM NeXtScale cluster. Each node of the system is equipped with 2 Intel Haswell E5-2630 v3 CPUs, with 8 cores with 2.4 GHz nominal clock speed and 85W TDP [12]. As regards the software infrastructure, SMP CentOS Linux distribution version 7.0 with kernel 3.10, runs on each node of the system. The experimental tests have been conducted using the complete software stack of Intel systems for HPC production environment. In particular, the Intel *MPI Library 5.1* has been used as communication library and Intel *ICC/IFORT 16.0* has been used as the toolchain. This Tier-1 supercomputer is currently classified in the Top500 supercomputer list [4]. The analysis focuses on a single node of the cluster.

#### 3.3.2 Application Target

The thesis work is focused on a widely used scientific application, QuantumESPRESSO (QE) [65]. QE has been selected as principal benchmark because is a paradigmatic suite of scientific applications largely used in several HPC centres. QE shows several architectural bottlenecks of typical HPC applications, like CPU, memory and IO boundness. Moreover, the collaboration with the developers has been a key factor in the correctness of use and in the tuning of the application. The QE version used in the experimental Sections of this thesis is v5.4.0.

In detail, QE is an integrated suite of scientific codes for electronic-structure calculations and materials modelling at the nanoscale. It is an open source package for research in molecule dynamics simulations and it is freely available to researchers around the world under the terms of the GNU General Public License. QE is commonly used in high-end supercomputers and it is based on main computational kernels, which include dense parallel linear algebra (LA) and 3D parallel fast Fourier transform (FFT). Moreover, most of application workload is based on LA and FFT mathematical kernels, which makes the exploration work relevant for many HPC codes. In the following experimental Section of this Chapter, it has been selected the QE Car-Parrinello (CP) simulation, which prepares an initial configuration of a thermally disordered crystal of chemical element by randomly displacing the atoms from their ideal crystalline positions. The dataset used for this simulation is a silicon atom (SiO2) due it is one of the common chemical element occurs in nature.

#### 3.3.3 Monitoring Framework

In this Section, it is described in detail the monitoring framework used to profile the application and the system. The monitoring framework is composed of two monitoring tools. The first one can monitor several hardware performance counters with a regular time stamping. The second monitoring tool is synchronized with parallel phases of the application allowing to isolate performance and architectural metrics for each program phase. However, due to the higher number of monitoring points per time unit, it access only on a sub-set of performance counters of the first tool to avoid excessive overhead. The monitoring framework have a minimal overhead, less than 1% with respect to application execution time.

#### System-aware Monitoring Tool

The system-aware monitoring tool is based on Examon [66]. This monitoring tool can be used to read periodically per-core frequency, CPI and scalar/vector instructions retired. In addition, it can monitor for each socket the DRAM memory bandwidth and package power consumption using RAPL performance counters. This monitor is a simple daemon process that can access to the performance counters of the CPU using MSR read/write operations. The daemon starts at a given  $T_{samp}$  rate and in the following benchmarks are used  $T_{samp}$  of 1 second.

#### Application-aware Monitoring Runtime

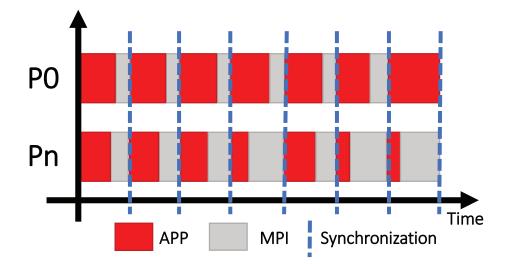

To extract application-based behaviours, it has been developed a monitor runtime to extract system information synchronously with the application flow. The runtime is a simple wrapper of the MPI library where every MPI function has been enclosed

Figure 3.3: Phases of computation and communication identified by application-aware monitoring Runtime

by an epilogue and a prologue function using the MPI standard profiling interface (PMPI). PMPI APIs allow to intercept all the MPI library functions without modify the application source code. The runtime is integrated in the application at linked time. Hence, Application-aware Monitoring Runtime is able to extract information distinguishing application and MPI phases as shows in Figure 3.3. The monitor runtime uses *RDPMC* and *RDTSC* assembly instructions to access respectively the time stamp counter (TSC) and Intel performance monitoring unit (PMU) counters with an overhead of few hundreds of cycles for each counter access. PMU counters are programmable through standard MSR operations which require administrative permissions and are costly in terms of access overhead. However, the counter value can be read using the *RDPMC* instruction directly from user space without involving syscalls. To monitor frequency, CPI, and scalar/vector instructions retired has been programmed the per-core PMU registers. The monitor runtime intercept all MPI calls of the application even in application regions where the density of the calls are very high. For this reason is not possible to use MSR operations to access low level performance counters through syscalls, which can cause high-performance penalty.

# 3.4 Experimental Results

# 3.4.1 Methodology

The QE-CP has been run with a configuration of 16 MPI processes with a one-toone bind to each core of the HPC node. This allocation is able to load as much as possible the node. Different configurations are compared for power capping in the test environment. Initially, the power budget has been split in an equal manner on both sockets, RAPL has been set to maintain 48W on each socket, for a global power envelope of 96W. This test shows that the cores' frequency on different sockets are heterogeneous, suggesting that the two sockets have different inherent power efficiency. To have the same frequency among all the cores, the tested computing node needs of 11.31% higher power on socket 0. As consequence of this result, a set of benchmarks has been run using the OS power manager to fix the same frequency for all the cores while monitoring the power consumption of each socket during an application run. These per-socket power budgets are set to power constraints the node to obtain the same frequency among all the cores. The tests has been executed again using RAPL to impose these per-socket power caps and leave RAPL decides the actual frequency.

Table 3.1 shows the results of experimental set using different levels of power caps. In the first column are reported the target frequencies used to extract the power limits specified in the second column. Second and third columns show the sum of power consumption of both sockets using fixed frequency (FF) allocation and RAPL mechanisms for power capping. it can be seen that the power consumption is the same, so the power cap is respected, and the tests are comparable. In the frequency columns are reported the average frequencies for the entire application among all the cores. These columns show that RAPL has an average frequency of 11.14% higher than FF but, it is possible to see at the execution time (reported in next columns), FF has a lower execution time, in average 2.87% faster than RAPL. In the next Sections, the exploration shows why FF has a lower execution time respect to RAPL which, in contrast, has a higher average frequency.

# 3.4.2 System Analysis

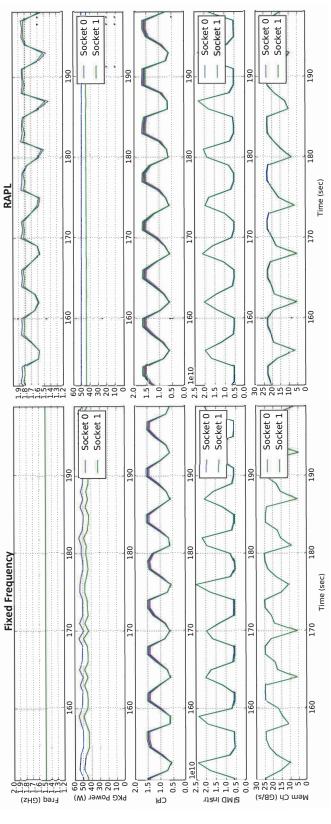

First, It is clearly shown the correct behavior of power capping logic by looking at the core's frequencies and package power consumption (first two top plots). In the

| Iable 3.1: Quantum ESFRESSO - Fower Capping | Frequency Execution Time | RAPL   FF vs RAPL | 5.10%                 | 0.11%                                       | 2.75%                                         | 3.53%                                                                 |

|---------------------------------------------|--------------------------|-------------------|-----------------------|---------------------------------------------|-----------------------------------------------|-----------------------------------------------------------------------|

|                                             |                          | RAPL              | 328.16sec             | 274.42sec                                   | $247.60sec \mid 254.59sec$                    | $231.19sec \mid 239.65sec \mid$                                       |

|                                             |                          | FF                | 311.43sec $328.16sec$ | 274.11sec 274.42sec                         | 247.60sec                                     | 231.19sec                                                             |

|                                             |                          | RAPL   FF vs RAPL | -15.11%               | -16.22%                                     | -9.86%                                        | -3.37%                                                                |

|                                             |                          | RAPL              | 1766MHz               | 2144MHz                                     | 2323MHz                                       | 2476MHz                                                               |

|                                             |                          | FF                | 1499MHz $1766MHz$     | 1797MHz $2144MHz$                           | 2094MHz $2323MHz$                             | $2.4 \text{ GHz} \mid 134.44W \mid 131.32W \mid 2392MHz \mid 2476MHz$ |

|                                             | Power                    | RAPL              | 94.81W                | 110.63W                                     | 120.71W                                       | 131.32W                                                               |

|                                             |                          | FF                | 1.5  GHz $95.56W$ $9$ | $1.8 \mathrm{~GHz}$   $111.86W$   $110.63W$ | $2.1 \mathrm{~GHz} \mid 122.87W \mid 120.71W$ | 134.44W                                                               |

|                                             |                          |                   | $1.5~{ m GHz}$        | $1.8~\mathrm{GHz}$                          | $2.1~{ m GHz}$                                | $2.4~{ m GHz}$                                                        |

Table 3 1. Onantim FSPRFSSO - Power Canning

FF plot on the left part of Figure 3.4, cores' frequency are fixed at 1.5GHz while package power consumption floats around the average value as effect of the different application phases. In contrast, RAPL (on the right) maintains constant the power consumption for both sockets while cores' frequency changes following the current application phase. Table 3.1 reports a similar average power consumption for both cases, thus the power cappers are working as expected. Both benchmarks show a lower CPI when the memory bandwidth is low and SIMD instructions retired are high. In these phases, RAPL imposes lower core's frequency than the FF case as effect of the higher power demand of SIMD instructions. On the other hand, RAPL assigns higher core's frequency than FF when CPI is high and this happens when the application is moving data from/to memory as proved by the high memory traffic/bandwidth reported by the Mem Ch[GB/s] plot. In these phases, the number of SIMD instructions retired are lower and, as already pointed out and shown in the RAPL plot, the cores' frequency selected by RAPL increases above average due the higher available power budget. However, increasing cores' frequency when the application is memory bound does not reflect in a consequent performance gain due the higher CPI and sub-linear dependency of application speed-up with frequency in these phases.

Figure 3.4 shows a time window of the system-aware monitoring tool for both power capping mechanisms while QE-CP iterates on the same computational kernel. The test reports the case of a power constraint relative to 1.5 GHz for FF and RAPL. So, the results are comparable directly.

Hence, FF is more efficient of RAPL (shorter execution time) for two reasons: i) FF executes with higher instruction per seconds when application has high SIMD instructions density. ii) RAPL instead reduces the core's frequency in the same phase to avoid excessive power consumption. On the contrary, RAPL increases the core's frequency during memory bound phases obtaining a similar average power as the FF case.

#### 3.4.3 Application Analysis

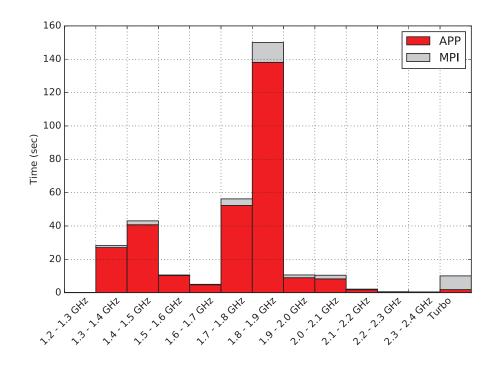

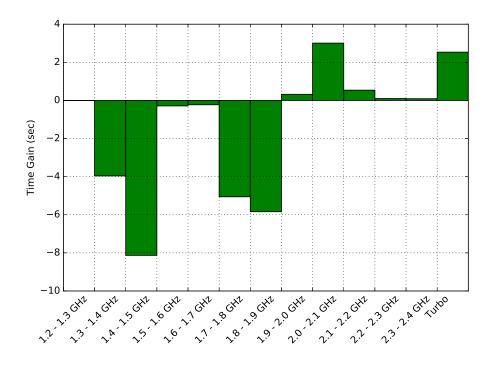

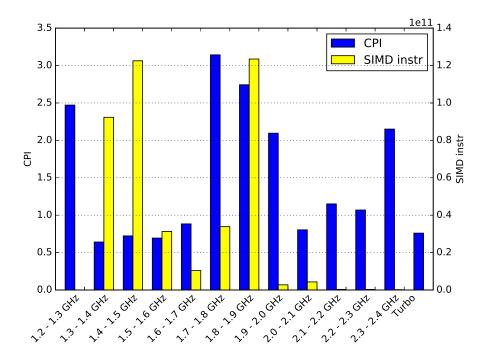

In this Section, it shows what happen in the system through the application-aware monitoring runtime. This runtime is able to recognize application phases marked by global synchronization points as depicted in Figure 3.4. In the Figures 3.5, 3.6, and 3.7 are reported the average values of performance counters of RAPL gathered

into frequency operational intervals. In Figure 3.5 is depicted the amount of time for computation (APP) and for communication (MPI) phases. Figure 3.6 shows the time gain for the FF respect to RAPL distributed on different frequency operational intervals. Negative values mean seconds of application time saved by FF with respect to RAPL. Figure 3.7 shows the values for CPI and SIMD instructions retired for the same phases that RAPL executes at a given frequency.

To explain the behavior that characterizes FF and RAPL, it should be taken a look at all the three plots together. Starting from Figure 3.6, it is possible to recognize that in the frequency intervals 1.3 to 1.5 GHz and 1.7 to 1.9 GHz, FF obtains its highest speed up. The first gaining interval is justified by the high number of SIMD instructions retired and by the lower CPI with respect to other application phases. Indeed from Figure 3.7, it can be noticed that most of the SIMD instructions are executed with these lower frequencies by RAPL.

Figure 3.5: Sum of RAPL and application time grouped for frequency operational intervals.

In the interval 1.7 to 1.9GHz, the CPI is higher and the SIMD instructions retired are not negligible. From Figure 3.5, it is possible to recognize that most the application time is spent in this frequency range with a lower SIMD instructions density

Figure 3.6: Time gain of FF w.r.t RAPL grouped for frequency operational intervals.

Figure 3.7: Average CPI and number of SIMD instructions retired grouped for frequency operational intervals.

respect to the 1.3 to 1.5 GHz interval. Hence, high CPI, low density of SIMD instructions and high frequency suggest memory bound phases as shown by previous Section. Interesting these phases run at higher frequency than the FF but leads to a performance penalty. This suggests side effects of high frequency in terms of memory contentions.

In the interval 2.0 to 2.1GHz, RAPL has a performance gain with respect to FF. This behavior is explained by the CPI and the number of SIMD instructions retired during this phase. In this interval, RAPL has a low CPI and does not perform SIMD instructions, so this phase scales its execution with the frequency. RAPL can dynamically manages the available power budget made available by the low SIMD instructions and can increase the frequency. This leads to a consequent performance increment.

In the turbo frequency interval, RAPL performs better than FF as it is an MPI reduction phase where only the root process is active. During the reduction, all the processes except the root MPI remain in a barrier to wait the termination of the root. This is explained by the high MPI runtime time (figure 3.5) presents at this frequency interval. Hence, RAPL can use the power budget released by the processes in barriers to speed up the root process leading to a performance gain.

# 3.5 Summary on HPC Power Capping

In this work, it has been presented a novel exploration on power capping mechanisms for power constrained HPC nodes. Differently from state-of-the-art works, the analysis focus on power capping strategies used in real HPC system nodes. In details, it explored the characteristics of Intel RAPL and a fixed frequency allocation during the execution of a real scientific HPC application which is performance constrained by the power budget assigned to the node.