1

# Control and Experimental Validation of the Series Bridge Modular Multilevel Converter for HVDC Applications

Carlos Martínez Diez, Alessandro Costabeber, *Member, IEEE*, Francesco Tardelli, *Member, IEEE*, David Trainer and Jon Clare, *Senior Member, IEEE*

Abstract—The Series Bridge Converter (SBC) is a modular multilevel converter recently developed to enhance power density in high voltage, high power applications. The Modular Multilevel Converter (MMC) is a well established solution, widely researched and exploited in practical HVDC connections thanks to its high power quality and high efficiency. However, the main limitation of the MMC is the relatively large energy storage, also due to the fact that power ripples in the sub-module capacitors include a component at the fundamental AC frequency. As a result, volume becomes critical in applications such as offshore or city centre in-feeds where space is restricted and expensive. The SBC offers a more compact footprint by exploiting a series connection on the DC side and by operating the sub-modules with rectified waveforms, thus moving the minimum component of the instantaneous power to twice the AC fundamental and reducing capacitors size. The drawback of the converter is a more complex energy control compared to the MMC. This paper proposes the first experimental validation of the SBC, using a 2kW laboratory-scale prototype. Since the basic converter design has been discussed in previous papers, the focus of this work is on converter control design and experimental validation.

Index Terms—HVDC transmission, Modular multilevel converters, AC-DC power converters.

#### I. INTRODUCTION

OWADAYS, with the increasing demand of electricity and the growing market share of renewables, new technologies are being researched in order to improve the AC electrical transmission systems and guarantee seamless integration of the new resources. High Voltage Direct Current (HVDC) transmission has been developed since the 1950s for its advantages in terms of cost and efficiency over the more traditional AC transmission systems for long distance transmission [1]. However, HVDC has been increasingly deployed in the last few decades to support the expansion of the transmission networks driven by the requirements to connect a growing number of far-offshore wind farms [2] and enabled by the developments on Voltage Source Converters (VSCs). Off-shore energy transmission is one of the applications where HVDC has been proved most useful, considering the additional challenge posed by undersea cables. However, the scope of HVDC is not limited to off-shore systems but it represents an enabling technology for the development of the European and global Super-grid [3], [4] and to support the dramatic growth of the Chinese energy market [5].

The authors are with the Faculty of Engineering, The University of Nottingham, Nottingham NG7 2RD, UK, e-mail: jon.clare@nottingham.ac.uk

In off-shore applications, the size of platform has a significant economic impact on the overall system cost [6]. In addition, HVDC converters are likely to be installed in densely populated regions, such as urban areas, where space is limited and expensive. Therefore, there is a widespread interest in minimising the footprint - in terms of volume and weight - of HVDC converters, to drive the cost down and increase the number of connections.

In HVDC systems, Voltage Source Converters (VSCs) are widely used, especially since the introduction of the new modular multilevel topologies, which provide an enhanced voltage and current waveform quality and a more compact footprint compared to the firstly used Line Commutated Converters (LCC) [7], that are nowadays used mainly in bulk power transmission where high efficiency, cost and reliability take priority on power quality, size and controllability.

The first Modular Multilevel Converter (MMC) was introduced in [8], [9] and has been successfully used in many HVDC installations [10]. The concept of the MMC relies on the series connection of either half-bridge or full-bridge sub-modules (SMs) equipped with floating capacitors to synthesize the multilevel output voltage waveform. A breed of new converter topologies derived from the MMC were later introduced [11], aiming at improving different aspects of the converter design and operation, still relaying on the same fundamental power conversion principle. Among them, the Series connected MMC [12] features three single phase MMC converters connected in series on the DC side, hence reducing the number of switching devices. The middle SM MMC [13] includes an additional SM interconnecting the upper and lower arms in each converter phase which also results in fewer SMs compared with the traditional MMC but the addition of the middle SM adds an extra degree of freedom to balance the SM voltages. The modular concept of the MMC has also been extended to other new converter topologies in the recent years like the Hexverter [14], featuring six identical branches of series connected H-bridge SMs arranged in an hexagonal manner, or like the Alternating Arm Converter (AAC) [15] which combines the MMC concept with a two-level converter concept. In the case of the AAC, each phase consists of two arms (array of full-bridge SMs) a director switch and a small inductor. Each arm is capable of producing a maximum voltage equal to half the DC voltage  $(V_{DC}/2)$  and therefore, for the same ratings of the MMC, the AAC requires half the number of SMs. Additionally, the full-bridge SMs provide the

converter with a DC fault ride-through capability.

Besides the AAC, one of the new modular multilevel converter topologies that features a compact footprint is the Parallel Hybrid Converter (PH-M2C) [16], [17] due to the series connection of the three phases on the DC side of the converter. Each phase features a series connection of half-bridge SMs named Chain-Link (CL), which generates a rectified sinusoidal waveform that will be unfolded by the corresponding H-bridge in each phase to provide a sinusoidal voltage waveform on the grid side. The CLs are connected in series on the DC side adding to a total DC voltage with a ripple at 6 times the grid frequency. This series connection on the DC side gives a reduction in the overall number of SMs, and at the same time has lower requirements in terms of SM capacitance, since the instantaneous power ripple through the SM capacitors has a fundamental component at twice the fundamental AC frequency. The size of a PH-M2C is about 50% of a similarly rated classic MMC, making it very attractive for off-shore applications. The main drawbacks of the PH-M2C are the  $6^{th}$ harmonic DC voltage ripple that requires additional filtering and the fact that the AC and DC side voltages are tightly coupled, and only limited reactive power control can be achieved through third harmonic injection [18].

The concept of the SBC [19], [20] has been derived as an evolution of the PH-M2C topology, with the addition of an array of series full-bridge SMs (SFBs) in between the CLs and H-bridges. The SFBs allow decoupling the AC and DC side voltages to achieve full reactive power control. Furthermore, they are used to achieve a ripple free DC voltage.

The SBC maintains the advantages that the former PH-M2C topology introduces and it is fully modular so it has the same inherent advantages as the MMC with regard to redundancy, noting that in a full-scale application the unfolding bridges will require series connection of devices for which redundant operation is well established [21], [22]. In [23], a detailed comparison between a conventional half-bridge (HB) MMC and the SBC is provided. It is concluded that for the same power rating (20MW), the SBC provides a significant footprint reduction (51%) and the valve voltage rating is 63% lower. Reference [24] also includes a comparison between the PH-M2C topology and other converter topologies also used for HVDC applications, highlighting the advantages of the PH-M2C converter with regards to the number of semiconductors and SM capacitance requirements.

However, the addition of the SFBs into the converter topology adds more complexity to the system, in particular making the internal energy control and balancing more challenging. The aim of this paper is to provide a detailed analysis of the basic energy management concept introduced in [20], with a focus on the control design and experimental validation of the topology and the proposed control.

The rest of the paper is organised as follows: Section II summarises the operating principle of the SBC and the basic equations describing the wave-shaping; Section III focuses on the energy management problem and Section IV describes in detail the choice of an additional  $2^{nd}$  harmonic voltage used as control variable to ensure energy control; Section V describes the design of the basic control loops required for

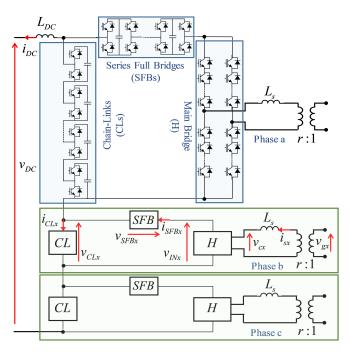

Fig. 1: Series Bridge Converter topology.

the practical operation of the converter; Finally, Section VI discusses the experimental prototype and shows experimental results matching the design requirements.

# II. CONVERTER TOPOLOGY AND OPERATING PRINCIPLE

The SBC topology is shown in Fig. 1. The converter can be considered as a set of three single-phase converters connected in series on the DC side. Each of the phases consists of a shunt connected array of series half-bridge SMs named Chain-Link (CL). Ideally, the CL in each phase synthesizes a multilevel rectified waveform. Each CL provides one third of the total DC voltage  $v_{DC}$  and, as a consequence, the peak value of the CL voltage waveform is imposed according to (1). It is worth noting that assuming equally split DC voltages amongst the series connected CLs implies that the power provided by each phase on the DC side is exactly 1/3 of the total DC power, thus forcing each of the three phases to exchange the same amount of power on the AC side to achieve per-phase and global power balance.

$$\hat{V}_{CL_x} = \frac{\pi}{2} \overline{V}_{CL_X} = \frac{\pi}{6} V_{DC} \tag{1}$$

In each phase, a group of series connected full-bridge SMs named Series Full Bridge (SFB) is connected to the positive terminal of the CL. The SFBs are introduced to decouple the AC and DC side voltages. In fact, the peak voltage of each CL is fixed by the DC link voltage as discussed above and therefore, without the addition of the SFB, the CL voltage will be directly unfolded by the main bridge in each phase resulting in an AC voltage with the same peak value. The voltage decoupling allows reactive power control in the converter and additionally, the SFBs can be used to achieve a ripple-free DC voltage, as discussed in the next section. The sum of CL and SFB voltages in each phase is unfolded by a main H-bridge

(H) at the zero crossing of the voltage to produce a sinusoidal waveform on the AC side. The outputs of the unfolding H-bridges are connected to the secondaries of three single phase transformers through an inductor  $L_s$ .

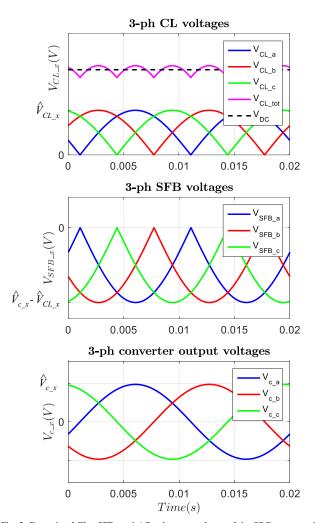

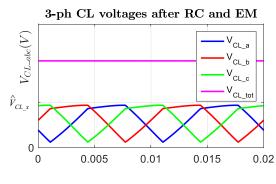

Averaged voltage waveforms (no switching considered) according to the discussion above are shown in Fig. 2, which illustrates qualitatively the basic concept of the wave-shaping for the SBC. Note that in this basic mode the DC ripple is yet to be cancelled. In addition, it will be shown in the following section that substantial modifications to the voltages shown here will be required to guarantee power balance and provide controllability of the energy stored in the converter.

Fig. 2: Example of CLs, SFBs and AC voltage waveforms of the SBC converter. These waveforms correspond to the converter operation at nominal active power and unity power factor, assuming a 50Hz grid frequency.

# III. SBC VOLTAGE WAVE-SHAPING, ENERGY MANAGEMENT AND DC RIPPLE CANCELLATION

For the following analysis the voltage and current sign convention depicted in Fig. 1 is used throughout. All phase shifts are expressed relative to the grid voltage of phase a. In addition, unity turns-ratio is assumed for the transformer, i.e. r=1 in Fig. 1. For clarity the CLs and SFBs are modelled as ideal controllable voltage sources (discrete levels are not

considered) and the discussion concerning power balance will neglect the internal loss of the converter. Accordingly, the following variables can be defined for the generic phase x: grid voltage  $v_{g_x}$ , grid current  $i_{s_x}$ , converter AC voltage  $v_{c_x}$ , converter voltage before unfolding with the main H-bridge  $v_{IN_x}$ , CL voltage  $v_{CL_x}$  and SFB voltage  $v_{SFB_x}$ . These quantities for phase a are given in equations (2) to (7) respectively. The corresponding waveforms for the other two phases can be obtained from those in phase a by shifting through  $120^{\circ}$ .

$$v_{q_a} = \hat{V}_q \sin(\omega t) \tag{2}$$

$$i_{s_a} = \hat{I}_s \sin(\omega t + \phi) \tag{3}$$

$$v_{c_a} = \hat{V}_c \sin(\omega t + \delta) \tag{4}$$

$$v_{IN_a} = \hat{V}_c \left| \sin(\omega t + \delta) \right| = v_{CL_a} + v_{SFB_a}$$

(5)

$$v_{CL_a} = \hat{V}_{CL} \left| \sin(\omega t + \delta) \right| \tag{6}$$

$$v_{SFB_a} = \left(\hat{V}_c - \hat{V}_{CL}\right) \left|\sin(\omega t + \delta)\right| \tag{7}$$

If the SBC is operated according to the waveforms expressed in (2-7), global and per-phase power balance can be achieved if the total DC power  $P_{DC}$  is equal to the total AC power  $P_{AC}$  and by ensuring that each phase processes 1/3 of the power, i.e.  $P_{AC_x} = P_{DC}/3$ . Depending on the operating mode of the converter, the DC power could be imposed by a DC load/generator and therefore  $\hat{V}_c$  and  $\delta$  will be controlled to balance the powers. Instead, if the AC power is imposed,  $v_{DC}$  will be controlled to ensure power balance. For simplicity only the first case will be considered in the rest of this paper.

In the SBC however, achieving global power balance between the AC and the DC side is not enough to guarantee power balance in the individual CLs and SFBs, even in the case where no loss or components asymmetries are considered. This is due to the fact that the capacitors in the CLs and in the SFBs represent two independent energy storage elements in each phase. It is easy to show that, with the ideal waveshaping proposed in Section II, the average powers in the CLs and SFBs in steady state are non-zero, and their value is a function of the operating point. It will be demonstrated later in Section V that if global and per-phase power balance are achieved, i.e.  $P_{AC_x} = P_{DC}/3$ , the average power  $\overline{P_{CL_x}}$  in each CL is, as expected, equal and opposite to the one in the corresponding SFB,  $\overline{P_{SFB_x}}$ :

$$\overline{P_{CL_{\alpha}}} = -\overline{P_{SFB_{\alpha}}} \tag{8}$$

As a consequence, the ideal wave-shaping discussed so far does not guarantee correct operation of the converter. Indeed, a mechanism is needed to shift power between the CLs and SFBs so that the average powers in steady state can be zero and the energy stored in the CLs and SFBs can be actively controlled.

#### A. Energy management

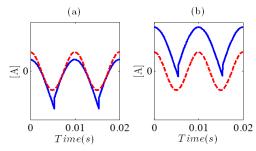

The solution to overcome this limitation is based on the observation that the CL and SFB currents in each phase have different DC values but exactly the same AC current components, which are even harmonics of the AC grid frequency, generated by the rectification action of the main H-bridge. Observing the Fourier series of the currents, it can be easily shown that the  $2^{nd}$  harmonic component (100Hz) is dominant.

Accordingly, to manage the energy stored in the individual CLs and SFBs and to guarantee zero average power in steadystate, a  $2^{nd}$  harmonic voltage component can be added to the SFB voltage and subtracted from the CL voltage of each phase. The  $2^{nd}$  harmonic voltage will interact with the  $2^{nd}$ harmonic current component to generate the additional power terms needed in CLs and SFBs to make their average power zero and therefore enable control of the stored energy. It is important to note that the addition of the  $2^{nd}$  harmonic voltage components does not affect the AC operating point of the converter. In fact, in the voltages on the DC inputs of the main H-bridges,  $v_{IN_x}$ , the  $2^{nd}$  harmonic voltage components cancel since they are added in phase opposition in  $v_{CL_x}$  and  $v_{SFB_x}$ . On the DC side, the  $2^{nd}$  harmonic voltage components added to  $v_{CL_x}$  cancel since they form a symmetrical three phase system. It is also important to realise that the current flowing in the CLs and SFBs is not affected at all by the added  $2^{nd}$  harmonic voltage and the only impact on losses results from the need to have enough cells to meet the peak voltage generation requirement [23].

#### B. DC ripple cancellation

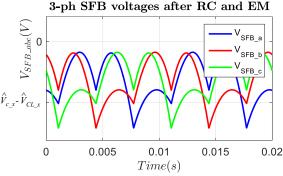

As discussed in the previous section and as shown in Fig. 2, the basic voltage wave-shaping causes a voltage ripple at 6 times the grid frequency to appear at the DC side of the converter. This ripple was a limitation in the PH-M2C since the CL voltages were directly generating the AC converter voltages. However, in the SBC the SFBs can be exploited also to cancel the DC ripple. In fact, the CL voltage waveforms can be pre-distorted by subtracting one third of the  $6^{th}$  harmonic ripple from the rectified sine wave in each phase, so that the sum of the three waves on the DC side will be ideally ripple free. The rectified sine voltage waveforms expected across the DC terminals of the main H-bridges  $v_{IN_x}$  are then restored by cancelling with the SFBs the ripple components added to the CLs.

Fig. 3: Example of CL (a) and SFB (b) current waveforms. The solid line represents the instantaneous current, the dashed waveform represents the fundamental component.

#### C. Final voltage wave-shaping

Following the previous discusion, the CL and SFB voltage waveforms are initially shaped to provide the required P and Q on the AC side, as well as the DC power to guarantee global power balance. These waveforms are then modified to achieve energy management between CL and SFB in each phase and to cancel the  $6^{th}$  harmonic DC ripple. To do so the CL and SFB voltages in each phase can be defined as in (9) and (10) respectively.  $v_{CL_x}^{RC}$  is the ripple compensation term corresponding to one third of the total DC voltage ripple.  $v_{CL_x}^{EM}$  is the  $2^{nd}$  harmonic voltage component for energy management that will make the CL and SFB average powers equal to zero in steady state and will provide controllability of the stored energy. Finally,  $k_{CL_x}$  is selected to define the DC voltage contribution of each phase, considered here to be  $v_{DC}/3$ .

$$v_{CL_x}^{FIN} = \underbrace{k_{CL_x} v_{IN_x}}_{v_{CL_x}} + v_{CL_x}^{RC} + v_{CL_x}^{EM}$$

(9)

$$v_{SFB_x}^{FIN} = \underbrace{(1 - k_{CL_x})v_{IN_x}}_{v_{SFB_x}} - v_{CL_x}^{RC} - v_{CL_x}^{EM}$$

(10)

It is worth noting that the two added components,  $v_{CL_x}^{EM}$  and  $v_{CL_x}^{RC}$  are a function of the operating point, i.e. for fixed DC and AC voltages, they change with a change in the active and reactive power exchanged by the converter. The ripple contribution  $v_{CL_x}^{RC}$  is relatively small and does not affect the original wave-shaping much. Conversely, the energy management component  $v_{CL_x}^{EM}$  can substantially modify the appearance of the voltage waveforms, as it will be shown in the following section. If the DC ripple cancellation can be enforced in open loop, the energy management must be driven by a closed loop system that controls the amplitude of the  $2^{nd}$  harmonic voltage, to ensure that CL and SFB energy storage is maintained as the converter operating point varies.

### IV. CHOICE OF THE SECOND HARMONIC VOLTAGE

This section provides a deeper analysis of the  $2^{nd}$  harmonic voltage used to drive the CL and SFB average powers to zero in steady state and to achieve controllability of the energy stored in each CL and SFB. In order to understand the implications of adding such an AC component, the equations governing the  $2^{nd}$  harmonic voltage and resulting power in steady state must be analysed first.

The current flowing through the SFBs can be defined from the grid current and the AC converter voltage sign as in (11). The Fourier series is shown in (12), from which the  $2^{nd}$  harmonic component can be obtained by making n=1. Accordingly, the  $2^{nd}$  harmonic of the SFB current is as given in (13). The generic  $2^{nd}$  harmonic voltage component that will be added to the CL and SFB voltages can be defined as in (14) for the CL voltage case.  $\gamma_x$  is the second harmonic voltage angle.

$$i_{SFB_x} = i_{s_x} sign(V_{c_x}) \tag{11}$$

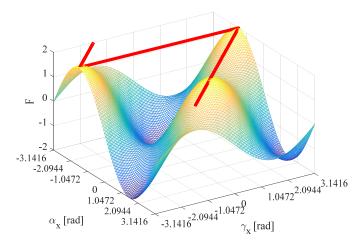

Fig. 4: Non-linear  $2^{nd}$  harmonic power function  $F(\alpha_x, \gamma_x)$  as a function of the  $2^{nd}$  harmonic voltage phase  $\gamma_x$  and the difference between the converter voltage and grid current phases  $\alpha_x$ .

$$i_{SFB_{x}} = \frac{2\hat{I}_{s}}{\pi} \cos(\delta_{x} - \phi_{x}) + \sum_{n=1}^{\infty} \frac{4\hat{I}_{s}}{\pi (1 - 4n^{2})} \cos(\delta_{x} - \phi_{x}) \cos(2n\omega t + 2n\delta_{x}) + \sum_{n=1}^{\infty} \frac{4\hat{I}_{s}}{\pi (1 - 4n^{2})} 2n \sin(\delta_{x} - \phi_{x}) \sin(2n\omega t + 2n\delta_{x})$$

(12)

$$i_{SFB_x}^{2\omega} = \frac{-4\hat{I}_s}{\pi} \left( \frac{1}{3} \cos(\delta_x - \phi_x) \cos(2\omega t + 2\delta_x) + \frac{2}{3} \sin(\delta_x - \phi_x) \sin(2\omega t + 2\delta_x) \right) = i_{CL_x}^{2\omega}$$

(13)

$$V_{CL_x}^{EM} = \hat{V}_{2\omega_x} \sin(2\omega t + 2\delta_x + \gamma_x)$$

(14)

The average CL power contribution due to the added  $2^{nd}$  harmonic voltage, shown in (15), is calculated from (13) and (14) and it can be simplified as shown in (16), where  $\delta_x - \phi_x = \alpha_x$ . It can be noted that the resulting expression depends on the active and reactive power operating conditions through  $\alpha_x$  and  $\hat{I}_s$  and on the choice of the  $2^{nd}$  harmonic voltage amplitude  $\hat{V}_{2\omega_x}$  and angle  $\gamma_x$  which represent the control variables for the energy management. It can be seen from (16) that the power component added to the CL by the  $2^{nd}$  harmonic voltage is directly proportional to the amplitude  $\hat{V}_{2\omega_x}$  and is related to the angle  $\gamma_x$  through the non-linear function  $F(\alpha_x, \gamma_x)$ .

$$\overline{P}_{CL_x}^{2\omega} = \overline{V_{CL_x}^{EM} i_{CL_x}^{2\omega}} = -\frac{2}{3\pi} \hat{I}_s \hat{V}_{2\omega_x}$$

$$\left[\cos(\delta_x - \phi_x)\sin(\gamma_x) + 2\sin(\delta_x - \phi_x)\cos(\gamma_x)\right] \quad (15)$$

$$\overline{P}_{CL_x}^{2\omega} = -\frac{2}{3\pi} \hat{I}_s \hat{V}_{2\omega_x} \underbrace{\left[\cos(\alpha_x)\sin(\gamma_x) + 2\sin(\alpha_x)\cos(\gamma_x)\right]}_{F(\alpha_x, \gamma_x)}$$

(16)

By plotting  $F(\alpha_x, \gamma_x)$  as shown in Fig. 4, it can be seen that the value taken by the function oscillates between +2 and -2, depending on the operating point (which is defined by the application requirements), and on the choice of  $\gamma_x$  which is a degree of freedom. It is now important to consider the choice of  $\gamma_x$ . The power that must be generated by the second harmonic voltage to achieve power balance in the CLs and SFBs is given in (8) and only depends on the operating point of the converter. Considering that energy management is achieved by adding another component to the CL and SFB voltage wave-shaping, it is important to minimise the amplitude of that component to minimise the impact on the converter sizing. It is clear from (16) that for a given  $2^{nd}$  harmonic power needed for balancing,  $V_{CL_x}^{EM}$  is minimum when the function  $F(\alpha_x, \gamma_x)$ is maximum. For this reason, the angle  $\gamma_x$  is changed as a function of the operating point to make sure the maximum is tracked. The locus of the maximum is highlighted with the red line in Fig. 4, shifted to F=2 for visibility purposes. It can be easily shown that the locus can be described in the  $(\alpha_x, \gamma_x)$  plane by:

$$\gamma_x = \frac{\pi}{2} - \alpha_x \tag{17}$$

By substituting the constraint (17) into (16), the function  $F(\alpha_x, \gamma_x)$  becomes solely a function of  $\alpha_x$ , turning F into a variable gain that depends on the active and reactive powers exchanged by the converter with the grid. The resulting power equation is shown in (18).

$$\overline{P}_{CL_x}^{2\omega} = -\frac{2}{3\pi} \hat{I}_s \hat{V}_{2\omega_x} \left[ 1 + \sin^2(\alpha_x) \right]$$

(18)

By imposing the constraint (17), the only variable available for energy control is the amplitude of the  $2^{nd}$  harmonic voltage  $\hat{V}_{2\omega_x}$ . All the other parameters in (18) depend on the operating point, resulting in a variable gain for the energy management. However, considering that the energy control will be a relatively slow control loop, the variable gain can be easily compensated with feed-forward. On a final note, it is worth emphasising that the  $2^{nd}$  harmonic voltage is added to shift power between the CL and SFB in each phase and that the amount of required voltage changes with the operating point of the converter. As a result, the wave-shaping originally shown in Fig. 2 will change, as shown in the example in Fig. 5.

#### V. SBC ENERGY CONTROL

The analysis given so far has highlighted that the basic wave-shaping originally discussed in Section II does not guarantee operability of the SBC, since the steady state average powers in the CLs and SFBs would be non-zero even under global power balance conditions. Subsequently, it has then been shown that the addition of  $2^{nd}$  harmonic voltage components, with opposite phase in the CLs and SFBs, provides a mean of exchanging power between CLs and SFBs without affecting the AC or the DC operating points.

The analysis provided above and the subsequently energy control that will be addressed in the following sections only account for balanced grid conditions. In the presence of

Fig. 5: Example of CLs and SFBs voltage waveforms with DC ripple cancellation (RC) and  $2^{nd}$  voltage for energy management (EM) when the converter operates at nominal active power and zero reactive power.

unbalanced grid conditions some augmentation of the basic scheme will be required to achieve proper operation - this is not discussed further here.

The goals of the energy control loops are to maintain the global energy storage of the converter, maintain the correct share of energy between different phases and ultimately to guarantee that each CL and SFB stores the desired amount of energy. In order to set up a simple control system that fulfils all those requirements, it is important to understand the basic power flows within the converter that affect energy distribution.

To simplify the notation, in the following analysis the components related with the DC ripple compensation will be ignored, in the understanding that the modifications to powers caused by the ripple compensation voltage terms are relatively small since they are related with interactions of 6n harmonics.

The architecture of the control system depends on the application of the converter. For brevity, in this paper the control of the converter is discussed for an application where the DC voltage  $v_{DC}$  is constant and the DC power depends on the DC load/source. This is the typical arrangement found in the onshore converter of a point-to-point HVDC link for offshore wind farms or in MVDC grid forming converters in marine DC systems [25]. This operating mode will be generally referred as DC grid forming converter. The choice does not constrain generality, since the proposed methodology for analysis and design can be easily extended to other operating conditions.

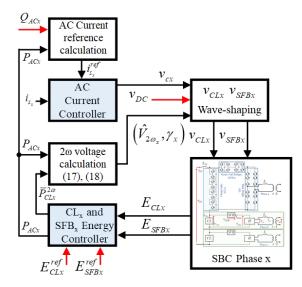

The control diagram in Fig. 6 shows the different elements of the control system for each phase of a DC grid forming SBC. The details of operation and design of the different control loops will be discussed in the rest of this section, with

Fig. 6: Per-phase control architecture for the DC grid forming SBC. Red arrows indicate external references.

a focus on the energy controllers in charge of maintaining CLs energies  $E_{CL_x}$  and SFB energies  $E_{SFB_x}$  at the reference values, corresponding to a desired voltage reference in each SM capacitor. Please note that the energy has been used as a control variable only for ease of explanation, SM voltage control can also be defined in the same way by using the linearised transfer function between average power and capacitor voltages. The AC current control included in Fig. 6 will be designed in Section VI. However, its contribution is neglected in the analysis and design of the energy controllers which are assumed to be much slower than the inner current loop. Similarly, the effects of modulation and cell sorting are not considered here and will be briefly discussed in the experimental results in Section VI.

The first step for the analysis and design of the energy controllers is to understand the power flows in the CLs and SFBs in each phase. The analysis starts assuming that the basic voltage wave-shaping of Fig. 2 is used, i.e. the  $2^{nd}$  harmonic discussed in Section IV is not considered yet. Under this assumption, CL and SFB voltages in each phase can be expressed in Fourier series form as shown in (19) and (20) for a generic operating point.

$$v_{CL_x} = \frac{2\hat{V}_{CL}}{\pi} \left( 1 + \sum_{n=1}^{\infty} \frac{2\cos(2n\omega t + 2n\delta_x)}{(1 - 4n^2)} \right)$$

(19)

$$v_{SFB_x} = \frac{2(\hat{V}_c - \hat{V}_{CL})}{\pi} \left( 1 + \sum_{n=1}^{\infty} \frac{2\cos(2n\omega t + 2n\delta_x)}{(1 - 4n^2)} \right)$$

(20)

The CL current equation in each phase can be derived from the corresponding SFB current expression shown in (12) by looking at Fig. 1:

$$i_{CL_x} = i_{SFB_x} - I_{DC} \tag{21}$$

Note that the currents in the CLs and SFBs are only a function of the DC and AC operating conditions, and will

not change with the addition of the  $2^{nd}$  harmonic voltage components for energy management. The average CL and SFB powers in each phase can be defined as (22) and (23).

$$\overline{P}_{CL_x} = -\frac{2I_{DC}\hat{V}_{CL}}{\pi} + \frac{\hat{I}_{s_x}\hat{V}_{CL}}{2}\cos(\phi_x - \delta_x)$$

(22)

$$\overline{P}_{SFB_x} = \frac{\left(1 - \frac{\hat{V}_{CL}}{\hat{V}_{c_x}}\right) \hat{I}_{s_x} \hat{V}_{c_x}}{2} \cos(\phi_x - \delta_x) \qquad (23)$$

Remembering that  $\hat{V}_{CL_x}=\frac{\pi}{6}v_{DC},\,P_{DC_x}=\frac{1}{3}v_{DC}i_{DC}$  and  $P_{AC_x}=\frac{1}{2}\hat{V}_{c_x}\hat{I}_{s_x}cos(\phi_x-\delta_x)$ , (22) and (23) can be rewritten as:

$$\overline{P}_{CL_x} = -P_{DC_x} + \frac{\pi}{6} \frac{v_{DC}}{\hat{V}_{c_x}} P_{AC_x}$$

(24)

$$\overline{P}_{SFB_x} = P_{AC_x} - \frac{\pi}{6} \frac{v_{DC}}{\hat{V}_{c_x}} P_{AC_x}$$

(25)

From (24) and (25) it can be seen that if the power balance per-phase is respected, i.e.  $P_{AC_x} = P_{DC_x}$ , the sum of CL and SFB powers is zero in each phase, but the individual components are generally different from zero. The addition of the  $2^{nd}$  harmonic power contribution for energy management turns (24) and (25) into the final power equations:

$$\overline{P}_{CL_x}^{FIN} = -P_{DC_x} + \frac{\pi}{6} \frac{v_{DC}}{\hat{V}_{C_x}} P_{AC_x} + \overline{P}_{CL_x}^{2\omega}$$

(26)

$$\overline{P}_{SFB_x}^{FIN} = P_{AC_x} - \frac{\pi}{6} \frac{v_{DC}}{\hat{V}_c} P_{AC_x} - \overline{P}_{CL_x}^{2\omega}$$

(27)

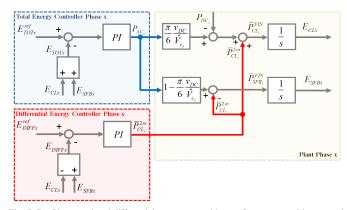

With the addition of the power contribution of the  $2^{nd}$ harmonic voltage, in (26) and (27) the component  $P_{CL_{T}}^{\omega}$ represents the additional degree of freedom needed to control the two energies stored in the CLs and SFBs in each phase. From a control point of view, and considering the DC grid forming operating mode,  $v_{DC}$  is constant,  $P_{DC_x}$  is a function of the DC power, imposed by the DC load/source,  $P_{AC_x}$  is the first control variable and  $\overline{P}_{CL_x}^{2\omega}$  is the second control variable in each phase. Considering that  $\overline{P}_{CL_x}^{FIN}$  and  $\overline{P}_{SFB_x}^{FIN}$  together drive the energy stored in the CL and SFB in each phase, it is clear that the two state variables are tightly coupled, and are therefore the states of a MIMO dynamic system. This can be also seen in Fig. 7 showing the simplified energy control scheme for each phase, where the current control has been neglected for simplicity. The proposed per-phase energy controller is divided into two loops, a total energy loop taking care of the overall energy storage  $E_{TOT_{\pi}}$  in the CLs and SFBs and therefore driving the AC power demand  $P_{AC_x}$ , and a differential energy loop ensuring that the energy difference  $E_{DIFF_{x}}$  is maintained at the desired value. Please note that the differential energy reference is generally different from zero, since the number of SMs in the CLs and SFBs is generally different. Define  $V^i_{SM_{CLx}}$  and  $V^j_{SM_{SFBx}}$  as the capacitor voltage in the i-th SM in the CLs and SFBs, and  $C_{CL}$  and  $C_{SFB}$  as the capacitance in the j-th SM in the CLs and SFBs respectively.  $N_{CL}$  and  $N_{SFB}$  are the number of SMs in the CLs and SFBs:

Fig. 7: Per-Phase total and differential energy control loops. Current control is assumed ideal for simplicity.

$$E_{CL_x} = \sum_{i=1}^{N_{CL}} 0.5 C_{CL} (V_{SM_{CL_x}}^i)^2$$

(28)

$$E_{CL_x}(s) = \frac{1}{s} \overline{P}_{CL_x}^{FIN}(s)$$

(29)

$$E_{SFB_x} = \sum_{j=1}^{N_{SFB}} 0.5 C_{SFB} (V_{SM_{SFB_x}}^j)^2$$

(30)

$$E_{SFB_x}(s) = \frac{1}{s} \overline{P}_{SFB_x}^{FIN}(s)$$

(31)

$$E_{TOT_x} = E_{SFB_x} + E_{CL_x} \tag{32}$$

$$E_{DIFF_x} = E_{SFB_x} - E_{CL_x} \tag{33}$$

Observing Fig. 7 it can be seen that the resulting energy loops are a non-linear MIMO system, since the gains of the plant include the peak AC converter voltage  $V_{c_x}$ , that in the assumption of a small phase angle  $\delta_x$  between converter and grid voltage becomes a function of the reactive power reference of the phase,  $Q_{AC_x}$ . However, it can be easily seen that if only the total energy controller is considered, the non linear gain cancels, and the control loops simplify to the one shown in Fig. 8. The figure clearly shows that the total energy stored in the phase only depends on  $P_{AC_x}$ , and does not see the action of the differential energy control. The DC power component of the phase,  $P_{DC_x}$ , acts as an external perturbation that can be easily compensated, also adding a feed-forward term. The total energy control represents the outer loop of the control system, and is therefore the slowest one. When looking at the equivalent block diagram for the differential energy controller, shown in Fig. 9 the decoupling feature is lost, since the action of the total energy controller acts as a perturbation for the differential loop. The proposed solution is to simply assume that the differential controller is designed for a bandwidth higher than that of the total energy controller, so that the component  $P_{AC_x}$  generated by the total energy controller is seen as a constant during transients of the differential loop. Under this assumption, the perturbations to the differential loop are only  $P_{DC_x}$  and  $Q_{AC_x}$  through  $\hat{V}_{c_x}$ .

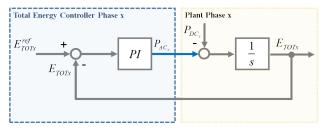

Fig. 8: Per-phase total energy control loop.

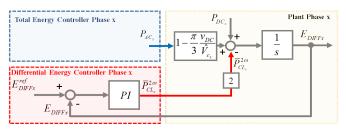

Fig. 9: Per-phase differential energy control loop.

These are however external perturbations that do not affect stability of the controllers.

From an intuitive perspective, if the differential energy controller acts more quickly than the total energy controller, the power that is absorbed from the AC side  $P_{AC_x}$  to maintain the total energy storage, is quickly redistributed by the differential energy controller between CLs and SFBs to maintain their energy difference constant  $E_{DIFF_x}$ .

According to the discussion above, the plants used to design the two Proportional-Integral (PI) controllers for the total and differential loops in Fig. 8 and 9 are simply:

$$G_{TOT}(s) = \frac{1}{s} \quad G_{DIFF}(s) = \frac{2}{s}$$

(34)

In order to design the energy controllers, the only design criteria is that the differential energy controller must be faster than the total energy controller.

#### A. Energy controllers design

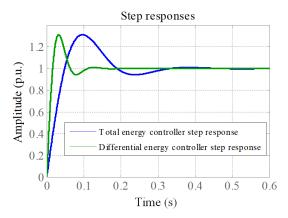

According to the discussion in the previous paragraphs, the selected bandwidths for the total energy and the differential energy control loops in each phase are:  $BW_{E_{TOT}}=5Hz$ ,  $BW_{E_{DIFF}}=15Hz$ . The other design criteria for the PI controllers is a phase margin of  $m_{E_{TOT}}=m_{E_{DIFF}}=50^\circ$ . The proportional and integral gains of the two PI controllers have been designed according to the specifications, considering the simple plants in (34). The step responses of the two loops are shown in Fig. 10.

#### B. AC current control

In the discussion about the architecture and the design of the energy controllers, current control has been neglected for simplicity, since its bandwidth is expected to be much higher than that of the energy loops. Also the current control is performed on a per-phase basis. For that purpose, the proportional resonant controller introduced in [26] has been used, with the transfer function defined as:

Fig. 10: Step responses of the designed total (blue) and differential (green) energy controllers

$$C_{I_{s_x}}(s) = \frac{(L_s + R_s)(2\omega_c s + \omega_c^2)}{s^2 + \omega_s^2}$$

(35)

Where  $L_s$  and  $R_s$  are AC inductor and resistor and  $\omega_s$  is the grid pulsation. Instead,  $\omega_c=1/\tau_c$  where  $\tau_c$  represents the desired time constant of the first order envelope of the grid current amplitude in response to a current reference amplitude step, as discussed in [26]. The controller in this paper has been designed for  $\omega_c=2\pi500[rad/s]$ .

A final remark is related with the grid synchronization. A traditional single-phase Phase-Locked-Loop (PLL) like the one described in [27] has been implemented in the experimental converter. The PLL gives the frequency of phase a of the grid voltage. The voltage references for the other phases are calculated by phase-shifting from phase a.

#### VI. SBC EXPERIMENTAL RESULTS

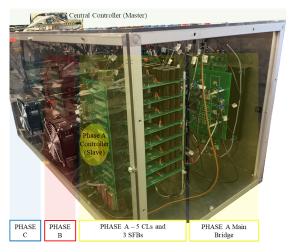

A small-scale low-voltage prototype of the SBC has been developed in order to experimentally validate the proposed control scheme and to show the converter voltage and current waveforms during normal operation, transferring active and reactive power. The converter has been designed for an AC peak phase voltage of 95V, a DC voltage of 200V and a maximum power rating of 2 kVA. In the experimental results presented, the converter has been operated as a rectifier connected to a resistive load on the DC side, and therefore behaves as DC grid forming converter, for consistency with the theoretical analysis proposed in the previous sections. On the AC side the converter is connected to a three phase VARIAC via three single phase transformers with unity turn ratio.

Each phase of the converter includes 8 SMs, divided into 5 half-bridge SMs for each CL and 3 full-bridge SMs in each SFB. The nominal operating voltage of the SMs is 40V. The switching devices are Infineon IPB072N15N3 MOSFET, rated for 150V and 100A. The use of MOSFET devices in the low power prototype avoids the problem of unrealistically high device voltage drops compared to the low cell voltage that would occur if IGBT devices were used. The three main H-bridges operate at higher voltage have been implemented using commercial IGBT power modules, Semikron SKM75GB12V.

Fig. 11: Laboratory prototype of the SBC

| TARI | E i | T٠ | SBC | rio | parameters |

|------|-----|----|-----|-----|------------|

|      |     |    |     |     |            |

| Parameter                             | Value                 |

|---------------------------------------|-----------------------|

| Grid voltage (phase to neutral, peak) | $V_{grid} = 95V$      |

| Single phase transformer turns ratio  | r = 1                 |

| Grid side inductance                  | $L_s = 12.5mH$        |

| Grid side resistance                  | $R_s = 1\Omega$       |

| DC voltage                            | $V_{DC} = 200V$       |

| DC side inductor                      | $L_{DC} = 37.5mH$     |

| DC side resistor                      | $R_{DC} = 36.5\Omega$ |

| CL SM capacitor                       | $C_{CL} = 4mF$        |

| SFB SM capacitor                      | $C_{SFB} = 4mF$       |

| Number of CL SMs                      | $N_{CL} = 5$          |

| Number of SFB SMs                     | $N_{SFB} = 3$         |

| PWM frequency                         | $f_{PWM} = 8kHz$      |

| Cell sorting frequency                | $f_{sorting} = 800Hz$ |

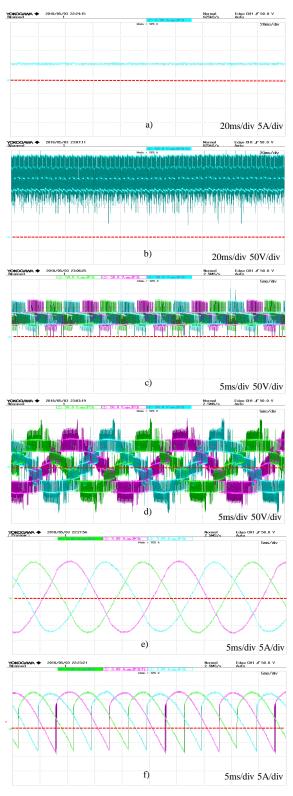

The other parameters of the system are summarised in TA-BLE I. The experimental rig is shown in Fig. 11 noting that it is constructed to allow easy access for measurements and for reconfigurability rather than for compactness. Due to the large number of waveforms that must be logged simultaneously, results have been recorded using a YOKOGAVA DCM2024, 200 MHz 2.5 GSa/s oscilloscope combined with data sampled at  $f_{log}=2kHz$  and stored by the master control board. Some of the oscilloscope screen-shots have be replotted in Matlab to improve readability. The source and the processing used for each of the results in this section is clearly indicated in the figure captions.

The control has been implemented using micro-controllerunits (MCUs) arranged in a master-slave architecture, where a local slave MCU (Texas Instruments F28377s) in each phase monitors the individual SM voltages and communicates to the master (Texas Instruments F28379d) only the sum of the voltages. The master controller implements the AC current control, total energy control, differential energy control and CL-SFB wave-shaping for each of the phases and dispatches the modulation signals for the three slaves. The three slaves perform level-shifted PWM modulation for the local CL and SFB, as well as the sorting algorithm for cell balancing.

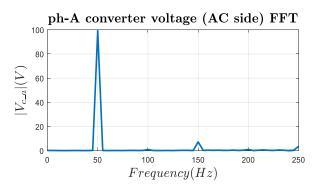

Fig. 12: Fast Fourier Transformation (FFT) of phase a AC side converter voltage when the converter operates at  $P_{DC}=1.1kW$  and  $Q_{AC}=300 {\rm VAr}$ . Data logged in the master controller at  $f_{log}=2kHz$ .

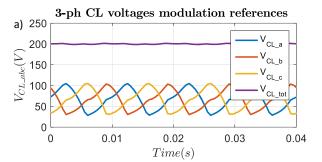

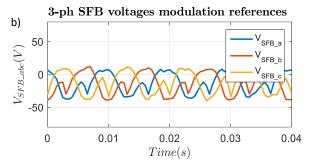

Fig. 13: Steady-state CL (a) and SFB (b) modulation signals sent by the the master controller to the slaves when the converter operates with  $P_{DC}=1.1kW$  and  $Q_{AC}=300 {\rm VAr}$ . Data logged in the master controller at  $f_{log}=2kHz$ .

# A. Steady-State results

The first set of results to validate the operation of the SBC and the control discussed in this paper relate to steady state operation. In all the results presented in this subsection, the converter is operating at nominal DC voltage  $V_{DC}=200V$  with a DC load resistor  $R_{DC}=36.5\Omega$ . This corresponds to a total power delivered to the DC side of the converter  $P_{DC}=1.1kW$ . In addition, a total reactive power  $Q_{AC}=300\text{VAr}$  is exchanged with the AC grid. According to the sign conventions adopted throughout the paper, this means that the converter is seen as an inductive load by the AC grid. It will be shown in the transient results that positive  $Q_{AC}$  is more demanding than the negative case since the energy management requires higher second harmonic voltage to balance CLs and SFBs in each phase.

Fig. 12 presents the FFT of the phase a of the AC side converter voltages to show the  $2^{nd}$  harmonic cancellation of

Fig. 14: SBC voltage and current waveforms when operating at  $P_{DC}=1.1kW$  and  $Q_{AC}=300\mathrm{VAr.}$  (a) DC current  $(I_{DC})$ , (b) DC voltage  $(V_{DC})$ , (c) CL voltages  $(V_{C\_abc})$ , (d) AC side converter voltages  $(V_{c\_abc})$ , (e) AC side currents  $(I_{s\_abc})$  and (f) SFB currents  $(I_{SFB\_abc})$ . Data recorded with a YOKOGAVA DCM2024, 200 MHz 2.5 GSa/s oscilloscope.

the voltage components added to the CL and SFB voltages to achieve energy balance as explained in this paper.

Fig. 13 shows the CL and SFB voltage demands sent by the central controller to the slaves in the three phases. Note that, as already shown qualitatively in Fig. 5, the actual voltage wave-shaping is less intuitive than the simple rectified sinewaves on which the basic concept of the converter is based, mainly because of the additional ripple cancellation and energy management components. Fig. 14 shows oscilloscope screenshots of DC voltage and current, CL voltages, AC converter voltages, AC converter currents and SFB currents. The SFB voltages are not shown since the relatively low amplitude of their voltage demand shown in Fig. 14 makes the PWM waveforms difficult to read. It is important to note that the small-scale prototype is using a small number of SMs for CLs and SFBs, affecting the fidelity of the instantaneous voltage waveforms which accordingly contain significant switching related components. However, in a full scale HVDC converter the larger number of SMs will guarantee high fidelity voltage waveforms.

The SM voltage waveforms in steady state are not shown for brevity, since the collective information on their state will be provided in the following sub-section where energy transients are discussed.

#### B. Energy transients

The aim of this sub-section is to validate the total and differential energy controllers shown in Fig. 7. The role of the energy controllers is to keep the energy stored in the CLs and SFBs to the desired reference value. According to (28) and (30) and based on the parameters of the experimental prototype discussed earlier in this section, the reference energies for each CL and SFB are  $E_{CL_x}^{ref}=16J$  and  $E_{SFB_x}^{ref}=9.6J$ . These references correspond to a total energy reference per-phase of  $E_{TOT_x}^{ref}=25.6J$  and a differential energy reference per-phase of  $E_{DIFF_x}^{ref}=6.4J$ . To confirm the correctness of modelling and control design, two main transients are shown.

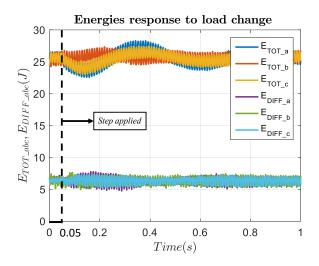

Fig. 15: Total and differential energies response to a DC load step from  $P_{DC}=800W$  to  $P_{DC}=1.1kW$  when  $Q_{AC}=300\mathrm{VAr}$ . Data logged in the master controller at  $f_{loa}=2kHz$ .

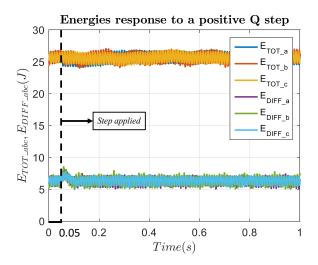

Fig. 16: Total and differential energies response to a reactive power step from  $Q_{AC}=0$ VAr to  $Q_{AC}=300$ VAr when  $P_{DC}=800W$ . Data logged in the master controller at  $f_{log}=2kHz$ .

First, from Fig. 8 and Fig. 9 it can be observed that a change in the DC load power affects both the differential and the total energy control. However, if  $P_{DC}$  acts directly in the total energy loop, its action is actually mitigated in the differential energy loop. In fact, the gain  $1 - (\pi v_{DC})/(3V_{c_x})$ in Fig. 9 can be approximated as  $1 - (\pi v_{DC})/(3V_{c_x}) \approx -1$  if the change of  $V_{c_x}$  with reactive power is neglected. As a result, the perturbation seen by the differential loop is  $P_{DC_x} - P_{AC_x}$ where  $P_{AC_x}$  is the response of the total energy control, that in steady state is  $P_{AC_x} = P_{DC_x}$ . This attenuation of the load step perturbation, combined with the higher bandwidth of the differential controller, lead to the fact that a DC power step only marginally affects the differential control and can be used to test the response of the total energy controller. Fig. 15 shows the response of total and differential energies to a DC load step from  $P_{DC}=800W$  to  $P_{DC}=1.1kW$ , while keeping  $Q_{AC} = 300 \text{VAr}$ . The step change is imposed at t = 0.05s and the results confirm the impact on the total energy control with virtually no impact on the differential control as expected. The response of the total energy controller brings the total energies back to steady state in about 0.5s as expected from the designed response in Fig. 10.

The second observation from Fig. 8 and 9 is that a step in the reactive power  $Q_{AC}$  only affects the differential energy controller by changing the amplitude of the AC converter voltage  $\hat{V}_{c_x}$  and therefore changing the gain  $1-(\pi v_{DC})/(3\hat{V}_{c_x})$ . This results in a step perturbation seen by the differential loop. This has been evaluated starting from  $P_{DC}=800W$  and  $Q_{AC}=0$ VAr and applying a step to  $Q_{AC}=300$ VAr. The step change is imposed at t=0.05s in Fig. 16 and it is clear from the results that the major impact of this transient is now on the differential energy controllers with very little impact on the total energy controllers as expected. The differential energy control brings the energies back to steady state in about 0.1s as expected from the designed response in Fig. 10 (i.e much faster than the total energy response).

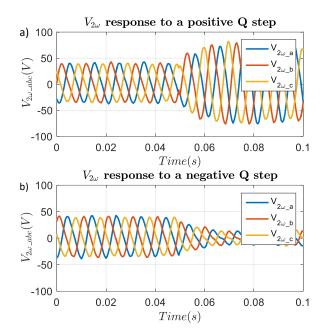

Fig. 17:  $2^{nd}$  harmonic voltages starting from  $P_{DC}=800W$  and  $Q_{AC}=0$ VAr and applying a positive reactive power step  $P_{DC}=800W$ ,  $Q_{AC}=300$ VAr (a) and a negative reactive power step  $P_{DC}=800W$ ,  $Q_{AC}=-300$ VAr (b). Data logged in the master controller at  $f_{log}=2kHz$ .

Finally, Fig. 17 shows how the amount of  $2^{nd}$  harmonic voltage needed for energy management changes when changing the operating point of the converter, as discussed in (18) and (26, 27). With the converter operating at fixed  $P_{DC}=800W$ , the figure shows the response of the  $2^{nd}$  harmonic voltage  $V_{CL_x}^{EM}$  to a transient  $Q_{AC}=0$ VAr to  $Q_{AC}=300$ VAr and a transient from  $Q_{AC}=0$ VAr to  $Q_{AC}=-300$ VAr. The envelope followed by  $V_{CL_x}^{EM}$  corresponds to the dynamic response of the differential energy loop, since  $\hat{V}_{2\omega_x}$  is directly calculated from the  $2^{nd}$  harmonic power demand  $\overline{P}_{CL_x}^{2\omega}$ , controlled by the differential energy loop.

# VII. CONCLUSION

This paper has presented the first experimental validation of the SBC through a 2kVA small-scale prototype. The SBC exploits the series connection of SMs on the DC side and the internal operation with current and voltage waveforms at twice the AC grid frequency to reduce the converter footprint. This makes the SBC attractive in HVDC but the same operating principles could be exploited also in other applications such as MVDC and MV motor drives. However, operation requires careful consideration for the choice of the wave-shaping that enables DC ripple cancellation and energy management between the CLs - series connection of half-bridge SMs - and the SFBs - series connection of full-bridge SMs - in each phase. The paper discussed in detail the generation of the voltage references for the CLs and SFBs and then focused on the definition and design of a simple but effective control system to maintain the energy stored in the converter at the desired reference. The experimental results demonstrated the expected converter waveforms when the converter is operated in DC grid forming mode, imposing the DC voltage and exchanging the desired reactive power with the AC grid. A DC load step change as well as a reactive power reference step change have been performed, confirming good agreement with the theoretical expectations.

#### REFERENCES

- [1] N. R. W. Jos Arrillaga, Y. H. Liu, Flexible Power Transmission: The HVDC Options, Wiley, Ed. Wiley, 2007.

- [2] D. V. Hertem, O. Gomis-Bellmunt, and J. Liang, HVDC Technology and Technology for Offshore Grids. IEEE-Wiley, 2016. [Online]. Available: https://ieeexplore.ieee.org/xpl/articleDetails.jsp?arnumber=7435071

- [3] P. Fairley, "Germany jump-starts the supergrid," *IEEE Spectrum*, vol. 50, no. 5, pp. 36–41, May 2013.

- [4] C. W. Gellings, "A globe spanning super grid," *IEEE Spectrum*, vol. 52, no. 8, pp. 48–54, August 2015.

- [5] X. Dong and M. Ni, "Ultra high voltage power grid development in china," in *IEEE PES General Meeting*, July 2010, pp. 1–8.

- [6] P. Bresesti, W. L. Kling, R. L. Hendriks, and R. Vailati, "HVDC connection of offshore wind farms to the transmission system," *IEEE Transactions on Energy Conversion*, vol. 22, no. 1, pp. 37–43, March 2007

- [7] O. E. Oni, I. E. Davidson, and K. N. I. Mbangula, "A review of lcc-hvdc and vsc-hvdc technologies and applications," in 2016 IEEE 16th International Conference on Environment and Electrical Engineering (EEEIC), June 2016, pp. 1–7.

- [8] DE Patent DE10 103 031B4, 2001.

- [9] A. Lesnicar and R. Marquardt, "An innovative modular multilevel converter topology suitable for a wide power range," in 2003 IEEE Bologna Power Tech Conference Proceedings,, vol. 3, June 2003, pp. 6 pp. Vol.3–.

- [10] H. Knaak, "Modular multilevel converters and hvdc/facts: A success story," in *Proceedings of the 2011 14th European Conference on Power Electronics and Applications*, Aug 2011, pp. 1–6.

- [11] A. Dekka, B. Wu, R. L. Fuentes, M. Perez, and N. R. Zargari, "Evolution of topologies, modeling, control schemes, and applications of modular multilevel converters," *IEEE Journal of Emerging and Selected Topics* in *Power Electronics*, vol. 5, no. 4, pp. 1631–1656, Dec 2017.

- [12] Q. Hao, B. Ooi, F. Gao, C. Wang, and N. Li, "Three-phase series-connected modular multilevel converter for hvdc application," *IEEE Transactions on Power Delivery*, vol. 31, no. 1, pp. 50–58, Feb 2016.

- [13] K. Wang, Y. Li, Z. Zheng, and L. Xu, "Voltage balancing and fluctuationsuppression methods of floating capacitors in a new modular multilevel converter," *IEEE Transactions on Industrial Electronics*, vol. 60, no. 5, pp. 1943–1954, May 2013.

- [14] L. Baruschka and A. Mertens, "A new three-phase ac/ac modular multilevel converter with six branches in hexagonal configuration," *IEEE Transactions on Industry Applications*, vol. 49, no. 3, pp. 1400–1410, May 2013.

- [15] M. M. C. Merlin, T. C. Green, P. D. Mitcheson, D. R. Trainer, R. Critchley, W. Crookes, and F. Hassan, "The alternate arm converter: A new hybrid multilevel converter with dc-fault blocking capability," *IEEE Transactions on Power Delivery*, vol. 29, no. 1, pp. 310–317, Feb 2014.

- [16] E. Amankwah, A. Watson, R. Feldman, J. Clare, and P. Wheeler, "Experimental validation of a parallel hybrid modular multilevel voltage source converter for hvdc transmission," in 2013 Twenty-Eighth Annual IEEE Applied Power Electronics Conference and Exposition (APEC), March 2013, pp. 1607–1614.

- [17] US Patent 9 065 299B2, 2015.

- [18] R. Feldman, M. Tomasini, E. Amankwah, J. C. Clare, P. W. Wheeler, D. R. Trainer, and R. S. Whitehouse, "A hybrid modular multilevel voltage source converter for hyde power transmission," *IEEE Transactions on Industry Applications*, vol. 49, no. 4, pp. 1577–1588, 2013.

- [19] US Patent 20170077834A1, 2017.

- [20] E. Amankwah, A. Costabeber, A. Watson, D. Trainer, O. Jasim, J. Chivite-Zabalza, and J. Clare, "The series bridge converter (sbc): Design of a compact modular multilevel converter for grid applications," in *IECON 2016 - 42nd Annual Conference of the IEEE Industrial Electronics Society*, Oct 2016, pp. 2588–2593.

- [21] J. F. Chivite-Zabalza, D. R. Trainer, J. C. Nicholls, and C. Davidson, "Balancing algorithm for a self-powered, high voltage switch, using series connected igbts for hvdc applications," *IEEE Transactions on Power Electronics*, 2018.

- [22] B. Jacobson, P. Karlsson, G. Asplund, L. Harnefors, and T. Jonsson, "Vsc-hvdc transmission with cascaded two-level converters," CIGRE 2010, 2010.

- [23] O. Idehen, D. Trainer, K. Vershinin, H. Dang, S. Brehaut, and E. Farr, "The series bridge converter: A compact and economic vsc-hvdc converter," 15th IET International Conference on AC and DC Power Transmission (ACDC 2019), pp. 1–6, 2019.

- [24] P. Wheeler, A. Watson, J. Clare, E. Amankwah, and R. Feldman, "Power electronic converters for hvdc renewable energy applications," 2015 CHILEAN Conference on Electrical, Electronics Engineering, Information and Communication Technologies (CHILECON)), pp. 425– 428, 2015

- [25] H. Li and D. Boroyevich, "Guest editorial special issue on emerging electric ship mvdc power technology," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 5, no. 1, pp. 1–4, March 2017.

- [26] A. Kuperman, "Proportional-resonant current controllers design based on desired transient performance," *IEEE Transactions on Power Electronics*, vol. 30, no. 10, pp. 5341–5345, Oct 2015.

- [27] H. Awad, J. Svensson, and M. Bollen, "Tuning software phase-locked loop for series-connected converters," *IEEE Transactions on Power Delivery*, vol. 20, pp. 300–308, 2005.

Carlos Martínez Diez received his bachelors degree in industrial engineering in the speciality of electronics in 2012 from the University of Oviedo, Spain. In 2014, he received his masters degree from the University of Oviedo in electrical energy conversion and power systems. From March to August 2014, he did his masters thesis at the University of Wisconsin-Madison in sensorless control for permanent magnet synchronous machines (PMSMs). In November 2018, he was awarded the PhD degree from the University of Nottingham, UK in power electron-

ics. From September 2018 until June 2019, he worked as a post-doctoral researcher at the University of Nottingham in modular multilevel converters. In June 2019, he started working as senior power electronics engineer at Huawei Technologies Sweden. His research interests include power converter topologies for HVDC transmission and electric vehicle applications.

Alessandro Costabeber received the MSc degree (Hons) in electronic engineering and the PhD degree in information engineering from the University of Padova, Padua, Italy, in 2008 and 2012, respectively. His Ph.D. thesis was on energy efficient architectures and control for future residential microgrids. In 2014, he joined as a Lecturer in power electronics with the Power Electronics and Machine Control Research Group, University of Nottingham, Nottingham, U.K. His current research interests include modular multilevel converters for HVDC, high-

power density converters, and control and stability analysis of ac and dc microgrids. Dr. Costabeber received the IEEE Joseph John Suozzi INTELEC Fellowship Award in Power Electronics in 2011.

Francesco Tardelli received his masters degree in electrical engineering from the University of Pisa (Italy) in 2014, and the PhD in electrical and electronic engineering from the University of Nottingham (UK) in 2018. From 2018-2019 he was a post-doctoral research fellow in the Power Electronics, Machines and Control Group at The University of Nottingham. In 2019 he joined Amantys Power Electronics Limited (part of the group Maschinenfabrik Reinhausen GmbH) and he is currently working on Modular Multilevel Converters for MV applications.

His research interests include modular multilevel converter topologies, control systems applied to power conversion and control and modelling of power converters.

David Trainer received his BSc (Hons) and PhD degrees from Staffordshire Polytechnic, UK, in 1985 and 1991, respectively. Between 1985 and 1998 he worked for GEC on the development of advanced thyristor valves for HVDC power transmission and later pioneered the use of GTO based modular multilevel converter (M2C) technology for reactive power compensation. In 1998, David joined Goodrich working on the development of electric actuation systems for civil and defence aerospace. In 2004 he joined Rolls-Royce to support more electric

engine development in the strategic research centre. In 2008, David joined Alstom to work on the development of high-power voltage source converters for HVDC power transmission leading the development of new converter technologies. In 2018, David re-joined Rolls-Royce as the global technology lead for power electronics and is focussing mainly on aerospace and marine electric propulsion systems and electric starter-generators. He is an Honorary Professor of electrical power conversion at The University of Nottingham, UK.

Jon Clare was born in Bristol, UK, in 1957. He received the BSc and PhD degrees in electrical engineering from the University of Bristol, Bristol, UK, in 1979 and 1990, respectively. From 1984 to 1990, he was a Research Assistant and Lecturer with the University of Bristol, where he was involved in teaching and research on power electronic systems. Since 1990, he has been with the Faculty of Engineering at the University of Nottingham, UK. He is currently Professor of Power Electronics and is the Head of the Electrical and Electronic Engineering

Department. He is a member of the Power Electronics, Machines and Control Research Group at Nottingham. His research interests are in power-electronic converters and their applications and control. Jon Clare is the recipient of a Royal Society Wolfson Research Merit Award.