The 9th International Conference on Power Electronics, Machines and Drives (PEMD 2018)

# New modulation scheme for bidirectional qZS deliver on 21st June 2018 Accepted on 21st June 2018 Accepted on 27th July 2018 E-First on 1st April 2019 doi: 10.1049/joe.2018.8020

Fatma A. Khera<sup>1,2</sup> , Christian Klumpner<sup>1</sup>, Pat W. Wheeler<sup>1</sup>

<sup>1</sup>Power Electronics, Machines and Control Research Group, Department of Electrical and Electronic Engineering, University of Nottingham, Nottingham, UK

**Abstract:** This study proposes a dedicated modulation scheme for a bidirectional quasi-Z-source (qZS) modular multi-level converter. The operation principle and a suitable pulse-width modulation method are proposed. The relation between the modulation index and shoot-through duty ratio is derived. A formula for calculating the required value of qZS capacitance is given. The simulation results presented in the study validate the operation and the performance of the proposed topology.

#### 1 Introduction

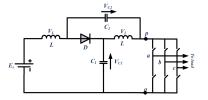

Multi-level inverters (MLIs) are preferred due to their attractive features compared with two-level voltage source inverters (VSIs) [1] such as better AC voltage quality, low voltage stress on semiconductors, possibility to produce significantly higher voltages than a single-switch voltage rating. The modular multi-level converter (MMC) is a relatively new competitive concept which has been proposed in 2002 [2]. It provides several features such as modularity, voltage, and power scalability and failure management capability in the case of device failures [3]. These advantages favour the MMC for various applications, such as an interface between high-voltage direct current (HVDC) [4] and flexible AC transmission (FACT) systems [5], driving medium-voltage (MV) motors [3], and connecting renewable energy sources such as photovoltaics [6] and wind energy system [7] to MV grids. The output voltage of most renewable energy sources fluctuates with working conditions; therefore, having a converter that can adapt to these fluctuation by being able not only to step down but also to step up the voltage in order to regulate the voltage at the DC-link terminals may be quite useful. Power converter topologies based on the use of the impedance network concept have been proposed in [8] which proposes the implementation of a quasi-Z-source (qZS) MMC. The basic structure of the quasi-Z-source inverter (qZSI) as proposed in [9] is shown in Fig. 1. The operating principle of the qZS network relies on producing a short circuit

Fig. 1 Equivalent circuit of the quasi-Z-source inverter (qZSI)

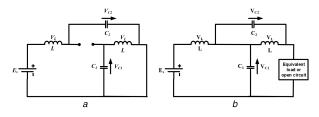

**Fig. 2** Equivalent circuit of qZSI (a) Shoot-through (ST) mode, (b) Non-shoot-through (NST) mode

www.ietdl.org

(shoot through, ST) at inverter DC-link terminals in order to increase the stored energy in the inductors that is later transferred in the qZS capacitors and, finally, this extra voltage adds up to the DC source voltage and provides voltage boosting capability.

There are two operation modes for the qZS network which are ST and non-ST (NST) modes. In the ST mode, the DC-link terminals are shorted by gating both the upper and lower devices of at least one inverter leg, which forces the qZS diode *D* to become reverse biased and therefore behave like an open circuit as shown in Fig. 2*a*. Hence, the stored energy in the capacitors begins to transfer into the inductors. In the NST mode, the inverter operates by producing active and null voltage states [10] and then *D* will be forward biased as shown in Fig. 2*b*; the stored energy in the inductors begins to transfer to the load, which sees  $V_{po} = V_{c1} + V_{c2}$  as its DC-link voltage, and qZS capacitors begin to charge.

Khera *et al.* [8] proposed the integration of the qZS network with a single-phase MMC to provide voltage boost capability. The proposed circuit faces some limitations which were identified in the same paper, and a solution was proposed by modifying the qZS-MMC to be a bidirectional one (BqZS-MMC).

This paper gives a detailed circuit analysis of the proposed BqZS-MMC. The equivalent circuit of the qZS-MMC with the proper implemented sinusoidal pulse-width modulation (SPWM) boosting scheme is presented which can be extended to any number of output voltage levels. The relation between the modulation index and ST duty ratio for any number of voltage levels is derived. A guideline for choosing the value of qZS capacitance is proposed. Finally, the operation and analysis of the proposed modulation scheme are validated using results simulation from a MATLAB/PLECS model.

### 2 Operation principles of the bidirectional quasi-Z-source modular multi-level converter

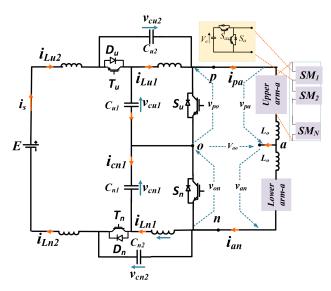

The topology of a single-phase qZS-MMC is shown in Fig. 3. The MMC leg consists of the upper and lower arms where each arm consists of series-connected sub-modules (SMs), and an arm inductor ( $L_o$ ). Each SM has a half-bridge inverter configuration with one DC-link capacitor. The two switches ( $S_a$  and  $S_{ax}$ ) in SM are controlled by complementary gating signals. When  $S_a$  is on, the SM capacitor is bypassed and the SM terminal voltage is zero. If  $S_a$  is off,  $S_{ax}$  is on; therefore, SM terminal voltage is  $V_c$  and the SM capacitor reads to be charged by a fraction of the DC bus voltage E/N, where N is the number of SMs per arm. Therefore, the output voltage ( $V_{ao}$ ) swings between  $-V_{pn}/2$  and  $V_{pn}/2$  and each arm should aim to produce the

Fig. 3 Typical topology of an N-cell single-phase MMC

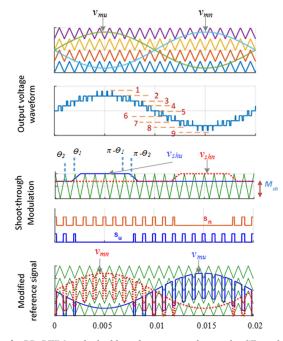

**Fig. 4** *PD-PWM* with double reference waveforms, the ST modulation signals and the generated pulses for the RNIC technique

reference output voltage potential, as average over one switching period. Output inductors  $L_o$  have the role to limit the current ripple caused by the momentary mismatch of voltage produced by the two arms, and also enable the control of circulating current needed to replenish the energy in the SM capacitors. The modulation scheme for generating these states will be explained in Section 4.

The output voltage equation as a function of the upper arm, lower arm, and the DC-link voltages is given by

$$v_{ao} = \frac{v_{an} - v_{pa}}{2} + \frac{v_{po} - v_{on}}{2} \tag{1}$$

From (1), if the upper qZS network is shorted via  $S_u$ , i.e.  $v_{po} = 0$ , the upper arm voltage  $v_{pa}$  should be reduced to keep the required output voltage at a certain level which can be achieved by reducing the number of inserted cells in the upper arm by N/2. The same procedure is followed if the lower qZS network is shorted via  $S_n$ . In this study, phase disposition SPWM (PD- SPWM) is used to control the MMC arms [11].  $S_u$  and  $S_n$  have been modulated using the proposed technique as follows.

## 3 MMC capacitors voltage balancing and modulation scheme

#### 3.1 Capacitor voltage balance

MMC requires a voltage balancing strategy to balance and keep the SM capacitor voltages at their desired average values. The implementation of balancing strategies depends on the presence of the redundant states in the MMC arm [10]. The redundant switching state with the strongest effect in facilitating voltage balancing is always selected. The MMC arm capacitor balancing can be achieved by different strategies [10]. The most widely used balancing strategy is based on the sorting method [6] which is summarised in four steps as follows:

(1) Measure and sort the upper and lower capacitor voltages.

(2) From modulation scheme, determine the number of inserted cells ( $n_p$  and  $n_n$ ) from the upper and lower arms, respectively.

(3) If the upper (lower) arm current is positive where the current direction as shown in Fig. 3 is considered as positive, choose the  $n_p$  ( $n_n$ ) cells with a lower voltage to be inserted. Therefore, the corresponding cell capacitor is charged and its voltage increases.

(4) If the upper (lower) arm current is negative, choose the  $n_p$  ( $n_n$ ) cell with a higher voltage to be inserted. Therefore, the corresponding cell capacitor is discharged and its voltage decreases.

#### 3.2 Modulation scheme

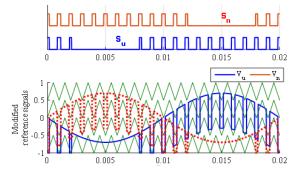

To synthesise *n*-level voltage waveform at the converter AC side where *n* equal 2N-1, phase disposition SPWM (PD-SPWM) with two complementary reference signals ( $v_{mn}$  and  $v_{mu}$ ) is used in this study to control the BqZS-MMC as indicated in Fig. 4. Each carrier is responsible for producing the gating signals of two cells (one from upper and one from lower arm). The reference signals are compared against the carriers to define which leg switches are conducting. The upper (lower) qZS networks can be in the ST mode if the number of upper (lower) inserted cells equals or is higher than N/2. Therefore, the number of inserted cells can be reduced by N/2 to obtain the required voltage level. According to this concept, this modulation scheme can be named as the reduced number of the inserted cell (RNIC) technique. By considering N=4, the number of output voltage level will be 9 as clarified in Fig. 4. Table 1 lists the available voltage levels when N=4 by clarifying the number of inserted SMs in both the upper and lower arms for each level before and after introducing ST intervals and which qZS-network switches  $S_u$  and  $S_n$  should be gated. Su can be shorted during all output voltage levels except levels 1, 2, and 3 (7, 8, and 9 for  $S_n$ ) as shown in Table 1 and Fig. 4, because at these levels, the number of inserted cells from the upper (lower) arm is  $<\!\!2$ (N/2). Therefore, ST signals of  $S_{\mu}$  at levels 1, 2, and 3 are set to zero.

Fig. 4 shows the output voltage waveform, ST signals, and the gating signals for both  $S_u$  and  $S_n$ . The upper ST signal ( $V_{\text{sh-}u}$ ) is defined by

$V_{\rm sh\ u} =$

$$\begin{cases} M_{\rm sh} & 0 < \omega t \le \theta_2; \pi - \theta_2 < \omega t \le 2\pi \\ N/2 \times M_{\rm sh} \sin wt & \theta_2 < \omega t \le \theta_1; \pi - \theta_1 < \omega t \le \pi - \theta_2 \\ 1 & \theta_1 < \omega t \le \pi - \theta_1 \\ 1 - M_{\rm sh} & \pi < \omega t \le 2\pi \end{cases}$$

(2)

where  $M_{\rm sh}$  is the ST modulating signal height as shown in Fig. 4. In the range from  $\Theta 1$  to  $\pi$ - $\Theta_1$ , the number of inserted SMs per arm became lower than N/2, where the ST interval should set at zero, and  $\Theta 1$  is defined by

Table 1

Available voltage levels with clarifying the number of inserted SMs in both the upper and lower arms

| Level number | Voltage level         | Number of SMs inserted $N = 4$ (upper, lower) |       | (S <sub>u</sub> , S <sub>n</sub> ) |

|--------------|-----------------------|-----------------------------------------------|-------|------------------------------------|

|              |                       | before                                        | after |                                    |

| 1            | -V <sub>pn</sub> /2   | 4, 0                                          | 2, 0  | (1, 0)                             |

| 2            | -3 V <sub>pn</sub> /8 | 4, 1                                          | 2, 1  | (1, 0)                             |

|              |                       | 3, 0                                          | 1, 0  |                                    |

| 3            | -V <sub>pn</sub> /4   | 3, 1                                          | 1, 1  | (1, 0)                             |

| 4            | -V <sub>pn</sub> /8   | 3, 2                                          | 3, 0  | (0, 1)                             |

|              |                       | 2, 1                                          | 0, 1  | (1, 0)                             |

| 5            | 0                     | 2, 2                                          | 0, 2  | (1, 0)                             |

|              |                       |                                               | 2, 0  | (0, 1)                             |

| 6            | V <sub>pn</sub> /8    | 1, 2                                          | 1, 0  | (0, 1)                             |

|              |                       | 2, 3                                          | 0, 3  | (1, 0)                             |

| 7            | V <sub>pn</sub> /4    | 1, 3                                          | 1, 1  | (0, 1)                             |

| 8            | 3 V <sub>pn</sub> /8  | 1, 4                                          | 1, 2  | (0, 1)                             |

|              |                       | 0, 3                                          | 0, 1  |                                    |

| 9            | V <sub>pn</sub> /2    | 0, 4                                          | 0, 2  | (0, 1)                             |

**Fig. 5** Modified output voltage reference waveforms according to the ST pulses for the RNIC technique

$$\theta_1 = \sin^{-1}(2/NM_{\rm sh})$$

$$\theta_2 = \sin^{-1}(2/N)$$

(3)

The lower ST signal  $V_{\text{sh-}n}$  waveform is of the same shape as  $V_{\text{sh-}u}$  but shifted by 180° as shown in Fig. 4. The pulses of  $S_u$  and  $S_n$  are generated if the carrier signal  $C_{\text{sh}}$  is higher than  $V_{\text{sh-}u}$  and  $V_{\text{sh-}n}$ , respectively. According to  $V_{\text{sh-}u}$  and  $V_{\text{sh-}n}$  signals, the output voltage reference waveforms ( $V_{mu}$  and  $V_{mn}$ ) for the upper and lower arms are modified as shown in Fig. 5 in order to provide a reduction in the number of inserted cells during these intervals by two cells (N/2). From (2), the instantaneous value of the duty ratio is given by

$$d_{sh\_u} = \begin{cases} 1 - M_{sh} & 0 < \omega t < \theta_2; \pi - \theta_2 < \omega t < 2\pi \\ 1 - N/2 \times M_{sh} \sin wt & \theta_2 < \omega t < \theta_1; \pi - \theta_1 < \omega t < \pi - \theta_2 \\ 0 & \theta_1 < \omega t < \pi - \theta_1 \end{cases}$$

(4)

By integrating (4), the average ST duty ratio  $D_{\rm sh}$  can be calculated which is given by

$$D_{\rm sh} = (\pi + 2\theta_2)(1 - M_{\rm sh})/2\pi + (\theta_1 - \theta_2)/\pi + NM_{\rm sh}(\cos\theta_1 - \cos\theta_2)/\pi$$

(5)

From (5), The DC-link voltage can be expressed by

$$V_{pn} = 1/(1 - 2D_{sh}) \times E$$

=  $\frac{\pi}{2\theta_1 + M_{sh}(2N(\cos\theta_1 - \cos\theta_2) - 2\theta_2 - \pi)}E$  (6)

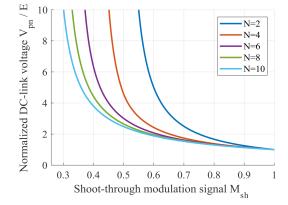

Fig. 6 Normalised DC-link voltage  $V_{pn/E}$  versus ST modulation index  $M_{sh}$

Fig. 6 shows the normalised peak DC-link voltage versus ST duty ratio  $M_{\rm sh}$  when N=2, 4, 6, 8, and 10. By increasing the number of SM, higher  $M_{\rm sh}$  is required at the same DC-link voltage. The qZS-capacitor voltages are given by

$$V_{cu1} = V_{cn1} = (1 - D_{sh})V_{pn}/2;$$

$$V_{cu2} = V_{cu2} = D_{sh}V_{nn}/2$$

(7)

For N of SMs per arms, the SM capacitor voltages are given by

$$V_{c-\rm arm} = V_{pn}/N \tag{8}$$

From (8), the peak value of the fundamental output voltage is given by  $\$

$$V_m = MNV_{c-\text{arm}}/2 = GE/2 \tag{9}$$

Where G is given as a function of  $D_{sh}$  (or  $M_{sh}$ ) and the output voltage modulation index M is given by

$$G = M/(1 - 2D_{\rm sh}) = 3\pi M/[(4\pi + 6\sqrt{3} - 12\cos\theta_1)M_{\rm sh} - 6\theta_1]$$

(10)

#### 4 Choosing values of a passive element

According to [8], using an IGBT in antiparallel to the diode D in the BqZS-network allows the converter to operate with small values of inductance without disturbing the operation of the circuit, being able to completely avoid the undesirable operation modes found in [8], consequently, eliminating any drops in the DC-link voltages that affected the output harmonic distortion. However, the

*J. Eng.*, 2019, Vol. 2019 Iss. 17, pp. 3836-3841 This is an open access article published by the IET under the Creative Commons Attribution License (http://creativecommons.org/licenses/by/3.0/)

3838

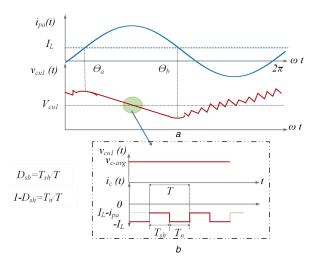

Fig. 7 Waveforms of qZ-MMC circuit

(a) Upper arm current  $(i_{pa})$  and the qZS capacitor voltage  $V_{cu1}$ , (b) A zoom in of the capacitor voltage  $V_{cu1}$  and capacitor current  $i_c$

| Table 2 ZSI simula  | ation m | odel parameters      |           |

|---------------------|---------|----------------------|-----------|

| source voltage E    | 3 kV    | load inductance and  | 14 mH, 13 |

| -                   |         | resistance           | Ω         |

| qZS-network         | 10 mH   | qZS-network          | 3.3 mF    |

| inductances         |         | capacitances         |           |

| MMC-arm inductance  | 5 mH    | MMC-arm capacitances | 3.3 mF    |

| switching frequency | 2 kHz   | output frequency fo  | 50 Hz     |

qZS-inductance value should be chosen for limiting the ripples to a reasonable level (20%) to reduce the current stress on the converter devices.

The inductance value of the four inductors is chosen according to [12]. The arm inductance and SM capacitance are calculated according to the relevant study and the relations given in [13]. In this section, the general relation for determining the proper qZScapacitance value has been obtained. According to [8], the qZScapacitor voltages  $V_{cu1}$  and  $V_{cu2}$  ( $V_{cn1}$  and  $V_{cn2}$ ) decrease when the arm current value  $i_{pa}$  ( $i_{na}$ ) is higher than the average value of the inductor current *I*L during both ST and NST modes as indicated in Fig. 7. The interval when the arm current is higher than the average inductor current ranges between  $\theta_a$  and  $\theta_b$ , where  $\theta_a$  and  $\theta_b$  are the two instants when the arm current is equal to  $I_{\rm L}$ . The upper and lower arm currents can be expressed by

$$i_{pa} = i_a/2 + i_{2f} + I_{dc}; \quad i_{na} = -i_a/2 + i_{2f} + I_{dc}$$

(11)

where  $I_{dc}$  is the DC component in arm currents which is responsible for transferring real active power from the supply to the load. The  $i_{2f}$  is the second-order harmonic usually present in any single-phase converters and  $i_a$  is the AC load current component. In the following analysis, the value of the second-order harmonic is not a significant as ia, so i2f is not considered and set to zero in (11). From the power balance equation, the maximum value of the load current  $I_a$  can be calculated by

$$I_a = \frac{2EI_L}{V_m \cos \Phi} \sin(\omega t - \Phi)$$

(12)

where  $\Phi$  is the load displacement angle,  $I_{dc}$  is the DC component in the arm current which can be calculated as a function of the average value of the qZS-inductor current by

$$I_{\rm dc} = \frac{1 - 2D_{\rm sh}}{1 - D_{\rm sh}} I_L \tag{13}$$

Substituting (12) and (13) into (11), and equating the resultant equation by  $I_L$ ,  $\theta_a$ , and  $\theta_b$  can be calculated by

$$\theta_a = \sin^{-1} \left( \frac{D_{\rm sh}}{2(1 - 2D_{\rm sh})} \cos \Phi \right) + \Phi$$

$$\theta_b = \pi - \sin^{-1} \left( \frac{D_{\rm sh}}{2(1 - 2D_{\rm sh})} \cos \Phi \right) + \Phi$$

(14)

The capacitance  $C_{u1}$  can be obtained by

$$C_{u1} = \frac{I_c \Delta t}{\Delta v_{Cu1}} \tag{15}$$

According to Fig. 7,  $\Delta t$  and  $\Delta v_{cu1}$  can be defined as

$$\Delta v_{cu1} = k_{\rm v} V_{cu1} \& \Delta t = \frac{\theta_b - \theta_a}{2\pi} * \frac{1}{f_{\rm o}}$$

(16)

where  $V_{cu1}$  is the average value of the qZS capacitor voltage,  $k_V$  is the ratio between peak-to-peak capacitor voltage  $\Delta v_{cu1}$  and  $V_{cu1}$ , and  $f_0$  is the output load frequency. The capacitor current  $I_c$  during the interval from  $\theta_a$  to  $\theta_b$  is given by

$$i_{\rm c}(t) = \begin{cases} I_L - i_{pa} & \text{non-shoot-throughmode} (1 - D_{\rm sh}) \\ -I_L & \text{shoot-throughmode} D_{\rm sh} \end{cases}$$

(17)

The average value of  $i_c(t)$  over a switching period is given by

$$I_{c-sw} = -D_{sh}I_L + (1 - D_{sh})(I_L - i_{pa}(t))$$

(18)

Substituting (11)–(13) into (18), and integrating from  $\theta_a$  to  $\theta_b$ , the average value of  $i_c$  over the interval from  $\theta_a$  to  $\theta_b$  is given by

$$I_{\rm c} = \frac{4(1 - 2D_{\rm sh})\cos(\theta_2 - \Phi)}{\cos\Phi(\theta_2 - \theta_1)}I_L$$

(19)

Substituting (7) and (19) into (15), the minimum required capacitance to provide a  $k_v$  voltage ripple can be obtained as

$$C_{u1} \ge \frac{4(1 - 2D_{\rm sh})^2 \cos(\theta_b - \Phi)P}{\pi k_{\rm v} f_0 \cos \Phi (1 - D_{\rm sh})E^2}$$

(20)

#### 5 Simulation results

To verify the validity of the proposed modulation scheme for the BqZS-MMC, a simulation model is implemented in MATLAB/PLECS for the proposed configuration shown in Fig. 2 with a number of SMs equal to 6. The parameters used in the simulation models are given in Table 2. The simulation study has been carried out using a passive (R+L) load and considering that all system components and switches are ideal.

The optimum qZS-capacitors ( $C_{u1}$  and  $C_{n1}$ ) were calculated in order to provide the voltage ripple factor *k*v of ~10%. Based on the parameters in Table 2, the required value of the qZS capacitor is ~3.15 mF which is calculated by (20).

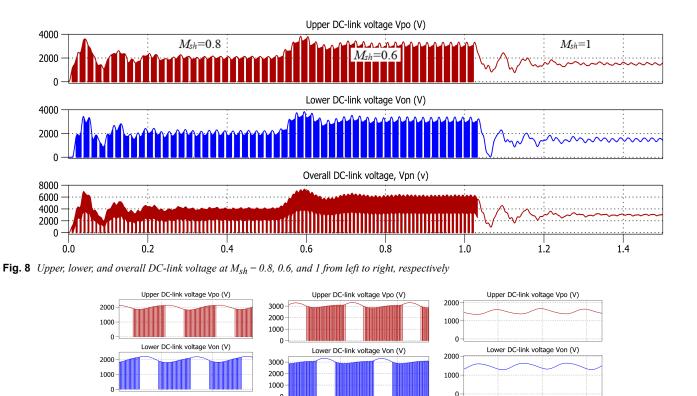

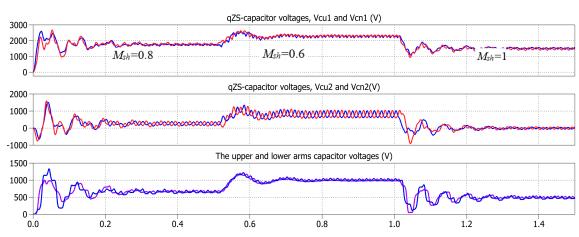

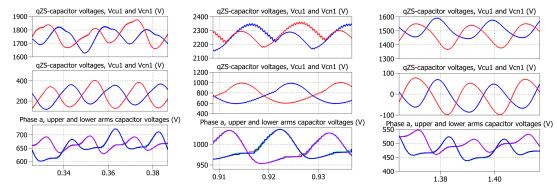

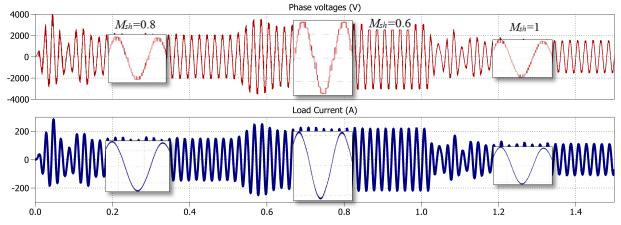

The converter modulation index M is set at 1 and the ST modulation index  $M_{\rm sh}$  is set to 0.8 (boost), 0.6 (boost), and 1, (buck) and consequently the ST duty ratio  $D_{\rm sh}$  is equal 0.124, 0.256, and zero, respectively. Figs. 8 and 9 show the upper, lower, and overall DC-link voltage, and their zooming. By lowering  $M_{\rm sh}$  from 0.8 to 0.6, the peak value of the overall DC-link voltage is increased from 4 to 6.2 kV. Also, to check the operation in the buck mode,  $M_{\rm sh}$  is set at 1, where the peak value of the overall DC-link voltage becomes 3 kV that is equal to the DC source voltage E.

The simulation results of the qZS-network capacitor ( $V_{cu1}$ ,  $V_{cn1}$ ,  $V_{cu2}$ , and  $V_{cn2}$ ) and arm capacitor voltages are shown in Fig. 10, and Fig. 11 illustrates their zooming. These capacitors are charged according to the relations given in (7) and (8). The ripple factor  $k_v$

1.40 0.84 0.86 **Fig. 9** Zooming of the upper, lower, and overall DC-link voltage at  $M_{sh} = 0.8$ , 0.6, and 1 from left to right, respectively

erall DC-link voltage, Vpn (v

0.42

0.40

4000

2000

0

0

6000

4000

2000

0

Overall DC-link voltage, Vpn (v)

Fig. 10 qZS-network capacitor and arm capacitor voltages at M = 0.8, 0.6, and 1 from left to right, respectively

of  $V_{cu1}$  and  $V_{cn1}$  is ~10% which confirm the validity of the proposed capacitance formula. Load voltage and current are shown in Fig. 12. For the proposed BqZS-MMC, by lowering  $M_{\rm sh}$  from 0.8 to 0.6, the peak value of the output voltage fundamental component is increased from 2 to 3.1 kV. However, for traditional MMC, the peak value of the output voltage is limited to the halfvalue of the supply voltage (E/2 = 1500 V). The output current shown in Fig. 12 does not show low-order harmonics, which is a sign that the proposed modulation works as expected.

#### 6 Conclusion

This paper proposed a modulation scheme for a bidirectional qZS MMC topology that is able to achieve buck and boost voltage capabilities. The relation between the modulation index and average ST duty ratio has been derived and verified by simulation at different modulation indices in both the buck and boost modes. An analytical design methodology for calculating the required values of qZS capacitors has been proposed, and the resulting ripples in the simulation match the ripple imposed in the design.

Overall DC-link voltage, Vpn (v)

1.42

1.44

4000

2000

0

**Fig. 11** Zooming of the qZS-network capacitor and arm capacitor voltages at  $M_{sh} = 0.8$ , 0.6, and 1 from left to right, respectively

Fig. 12 Load voltage and current at  $M_{sh} = 0.8$ , 0.6, and 1 from left to right, respectively

#### 7 References

- [1] Abu-Rub, H., Holtz, J., Rodriguez, J., et al.: 'Medium-voltage multilevel converters-state of the art, challenges, and requirements in industrial applications', *IEEE Trans. Ind. Electron.*, 2010, **57**, pp. 2581–2596

- [2] Lesnicar, A., Marquardt, R.: 'An innovative modular multilevel converter topology suitable for a wide power range'. 2003 IEEE Bologna Power Tech Conf. Proc., Bologna, Italy, 2003, vol. 3, p. 6

- Conf. Proc., Bologna, Italy, 2003, vol. 3, p. 6

[3] Debnath, S., Qin, J., Bahrani, B., *et al.*: 'Operation, control, and applications of the modular multilevel converter: A review', *IEEE Trans. Power Electron.*, 2015, 30, pp. 37–53

- [4] Saeedifard, M., Iravani, R.: 'Dynamic performance of a modular multilevel back-to-back HVDC system'. 2011 IEEE Power and Energy Society General Meeting, Detroit, USA, 2011, pp. 1–1

- [5] Lawan, A.U., Abbas, H., Khor, J.G., et al.: 'Dynamic performance improvement of MMC inverter with STATCOM capability interfacing PMSG wind turbines with grid'. 2015 IEEE Conf. on Energy Conversion (CENCON), Johor Bahru, Malaysia, 2015, pp. 492–497

- [6] Guruambeth, R., Ramabadran, R.: 'Fuzzy logic controller for partial shaded photovoltaic array fed modular multilevel converter', *IET Power Electron.*, 2016, 9, pp. 1694–1702

- [7] Nakanishi, T., Orikawa, K., Itoh, J.I.: 'Modular multilevel converter for wind power generation system connected to micro-grid'. 2014 Int. Conf. on

Renewable Energy Research and Application (ICRERA), Milwaukee, USA, 2014, pp. 653–658

- [8] Khera, F.A., Klumpner, C., Wheeler, P.W.: 'Operation principles of quasi Z-source modular multilevel converters'. 2017 IEEE 3rd Annual Southern Power Electronics Conf. (SPEC), Puerto Varas, Chile, 2017

- [9] Anderson, J., Peng, F.Z.: 'A class of quasi-Z-source inverters'. 2008 IEEE Industry Applications Society Annual Meeting, Edmonton, Canada, 2008, pp. 1–7

- [10] Adam, G.P., Anaya-Lara, O., Burt, G.M., et al.: 'Modular multilevel inverter: Pulse width modulation and capacitor balancing technique', *IET Power Electron.*, 2010, 3, pp. 702–715

- [11] Shi, X., Wang, Z., Tolbert, L.M., et al.: 'A comparison of phase disposition and phase shift PWM strategies for modular multilevel converters'. 2013 IEEE Energy Conversion Congress and Exposition, Denver, USA, 2013, pp. 4089–4096

- [12] Rajakaruna, S., Jayawickrama, L.: 'Steady-state analysis and designing impedance network of Z-source inverters', *IEEE Trans. Ind. Electron.*, 2010, 57, pp. 2483–2491

- [13] Zygmanowski, M., Grzesik, B., Nalepa, R.: 'Capacitance and inductance selection of the modular multilevel converter'. 2013 15th European Conf. on Power Electronics and Applications (EPE), Lille, France, 2013, pp. 1–10