## **Ruben Emanuel Estrela Monteiro**

Licenciado em Ciências da Engenharia Electrotécnica e de Computadores

# Wideband Low Noise Oscillator suitable for Injection Locking

Dissertação para obtenção do Grau de Mestre em

Engenharia Electrotécnica e de Computadores

Orientador: Doutor Luís Augusto Bica Gomes de Oliveira, Prof. Auxiliar, Faculdade de Ciências e Tecnologia da Universidade Nova de Lisboa

Júri

Presidente: Prof. Doutor Fernando José Almeida Vieira do Coito Arguente: Prof. Doutor João Pedro Abreu de Oliveira Vogal: Prof. Doutor Luís Augusto Bica Gomes de Oliveira

Setembro, 2018

#### Wideband Low Noise Oscillator suitable for Injection Locking

Copyright © Ruben Emanuel Estrela Monteiro, Faculdade de Ciências e Tecnologia, Universidade NOVA de Lisboa.

A Faculdade de Ciências e Tecnologia e a Universidade NOVA de Lisboa têm o direito, perpétuo e sem limites geográficos, de arquivar e publicar esta dissertação através de exemplares impressos reproduzidos em papel ou de forma digital, ou por qualquer outro meio conhecido ou que venha a ser inventado, e de a divulgar através de repositórios científicos e de admitir a sua cópia e distribuição com objetivos educacionais ou de investigação, não comerciais, desde que seja dado crédito ao autor e editor.

"One, remember to look up at the stars and not down at your feet. Two, never give up work. Work gives you meaning and purpose and life is empty without it. Three, if you are lucky enough to find love, remember it is there and don't throw it away."

- Stephen Hawking

### ACKNOWLEDGEMENTS

Esta obra é o produto final de um conjunto de contribuições, sejam elas directas ou indirectas. E como ninguém faz nada sozinho neste mundo, tenho o dever de agradecer às pessoas e entidades que me possibilitaram chegar a este patamar.

Começo por agradecer à Faculdade de Ciências e Tecnologia da Universidade Nova de Lisboa, por me ter proporcionado ao longo de todo o curso um ambiente académico salutar que me permitiu adquirir competências técnicas importantes, bem como aprender bastante sobre mim próprio.

Em particular, agradeço ao Professor Luís Oliveira por ter aceite ser o meu orientador e me ter sugerido um tema de tese tão interessante e actual. Quero ainda agradecerlhe por toda a sua disponibilidade, apoio e pelo entusiasmo contagiante que demonstra ao discutir temas relacionados com a Microelectrónica, criando assim um ambiente de trabalho enriquecedor.

Agradeço também a todos os professores da área de Electrónica com que me cruzei no meu percurso académico, pois através do seu método de ensino conseguiram-me transmitir uma paixão pelo assunto.

Ao longo deste curso, cruzei-me com muitos colegas que contribuíram positivamente para o meu sucesso académico, por isso agradeço também a todos eles.

Por último, mas definitivamente não menos importantes, agradeço a todos os membros da minha Família que me apoiaram ao longo desta escalada. Em particular, agradeço ao meu Pai pela estabilidade e exemplo que traz para a minha vida, à maninha por todos os bons momentos e à minha namorada Marta Terroso por ser a Luz que ilumina sempre o meu caminho.

## ABSTRACT

There is a growing need to design compact and low power transceiver circuits. The increasingly crowded frequency spectrum leads to increased challenges associated with transceiver design. In particular, it becomes imperative that the oscillator circuits have a low phase noise.

RC oscillators have the ability to produce wideband oscillations with reduced area and low power consumption. However, a serious drawback is its high phase noise, which leads to poor circuit performance.

To improve the performance of an RC oscillator, it is common for it to be integrated into a frequency synthesizer. The most common approach of a synthesizer is the Phase-Locked Loop (PLL). This approach leads to an increase in the area and complexity of the circuit. Another approach to a synthesizer is an Injection-Locked Oscillator (ILO), which achieves similar performances to a PLL without the disadvantages referred to above.

In this thesis, an ILO based on an RC oscillator, using a Spin Torque Oscillator (STO) as a reference generator, is presented. The circuit is implemented in two different Complementary Metal-Oxide-Semiconductor (CMOS) technologies: 130 nm CMOS and 180 nm CMOS. The STO used as reference has characteristics similar to a nanometric device developed at the International Iberian Nanotechnology Laboratory (INL). In addition, the ILO operates in a wide frequency band ranging from 100 MHz to 3 GHz, has a power consumption ranging from 2.94 mW to 6.81 mW for 130 nm CMOS technology, whereas in 180nm CMOS technology it consumes between 4.86 mW and 13.96 mW.

Thus, the work developed in the course of this thesis serves as proof of concept for the manufacture of a fully integrated hybrid ILO using the STO technology in conjunction with CMOS circuits.

**Keywords:** CMOS, RC Oscillator, Injection Locking, Phase Noise, Radio Frequency, Wideband.

## Resumo

É cada vez maior a necessidade de projetar circuitos transceptores compactos e de baixa potência. O espectro de frequências cada vez mais sobrelotado leva a que haja desafios acrescidos associados ao projecto dos transceptores. Em particular, torna-se imperativo que os circuitos osciladores tenham um baixo ruído de fase.

Os osciladores RC têm a capacidade de produzir oscilações com uma grande largura de banda enquanto apresentam baixos consumos de potência e áreas reduzidas. Porém, uma desvantagem séria é o seu elevado ruído de fase, que leva a baixos desempenhos do circuito.

Para melhorar o desempenho de um oscilador RC, é comum este ser integrado num sintetizador de frequência. A abordagem mais comum de um sintetizador é a malha de captura de fase (PLL). Esta abordagem implica um aumento na área e complexidade do circuito. Outra abordagem para um sintetizador é um oscilador sincronizado por injeção (ILO), que atinge desempenhos semelhantes a uma PLL sem as desvantagens referidas anteriormente.

Nesta tese, é proposto um ILO, baseado num oscilador RC, que usa um nano-oscilador por trasferência de spin (STO) como gerador de referência. O circuito é implementado em duas tecnologias distintas: CMOS 130nm e CMOS 180 nm. O STO usado como referência tem caracteristicas semelhantes a um dispositivo nanométrico desenvolvido no Laboratório Ibérico Internacional de Nanotecnologia (INL). Para além disso, o ILO opera numa banda larga de frequências desde os 100 MHz até aos 3 GHz, tem consumo de potência de 2.94 mW a 6.81 mW para a tecnologia CMOS 130 nm, enquanto que na tecnologia CMOS 180 nm consome entre 4.86 mW a 13.96 mW de potência.

Assim sendo, o trabalho desenvolvido no decorrer desta tese serve de prova de conceito para o fabrico de um ILO híbrido e totalmente integrado que use a tecnologia do STO em conjunto com circuitos CMOS.

**Palavras-chave:** CMOS, Oscilador RC, Sincronização por Injeção, Ruído de fase, Radio-frequência, Banda Larga.

## Contents

| Li | List of Figures xvii |         |                                         |       |

|----|----------------------|---------|-----------------------------------------|-------|

| Li | List of Tables xxi   |         |                                         |       |

| Ac | crony                | ms      |                                         | xxiii |

| 1  | Intr                 | oductio | )n                                      | 1     |

|    | 1.1                  | Backg   | round and Motivation                    | 1     |

|    | 1.2                  | Main (  | Contributions                           | 3     |

|    | 1.3                  | Thesis  | Organization                            | 4     |

| 2  | Bac                  | kgroun  | d on RF receivers using CMOS technology | 5     |

|    | 2.1                  | Types   | of MOSFET                               | 6     |

|    | 2.2                  | MOSF    | ET Large-Signal Behaviour               | 6     |

|    |                      | 2.2.1   | Basic Operation                         | 6     |

|    |                      | 2.2.2   | Channel-Length Modulation               | 11    |

|    |                      | 2.2.3   | Body Effect                             | 12    |

|    |                      | 2.2.4   | NMOS-PMOS Duality                       |       |

|    | 2.3                  | MOSF    | ET Small-Signal Modelling               | 13    |

|    |                      | 2.3.1   | Low-Frequency Small-Signal Model        | 13    |

|    |                      | 2.3.2   | High-Frequency Small-Signal Model       | 14    |

|    | 2.4                  | Noise   |                                         | 15    |

|    |                      | 2.4.1   | Thermal Noise                           | 15    |

|    |                      | 2.4.2   | Flicker Noise                           | 17    |

|    |                      | 2.4.3   | Noise Figure                            | 18    |

|    | 2.5                  | Receiv  | ver Architectures                       | 19    |

|    |                      | 2.5.1   | Heterodyne Receiver                     | 19    |

|    |                      | 2.5.2   | Homodyne Receiver                       | 21    |

|    |                      | 2.5.3   | Low-IF Receiver                         | 22    |

| 3  | CM                   | OS Osc  | illators                                | 25    |

|    | 3.1                  | Basic ( | Concepts                                | 25    |

|    |                      | 3.1.1   | Positive Feedback Loop                  | 25    |

|   |            | 3.1.2 Barkhausen Criterion                                                                 |

|---|------------|--------------------------------------------------------------------------------------------|

|   |            | 3.1.3 Phase Noise                                                                          |

|   |            | 3.1.4 Quality Factor                                                                       |

|   |            | 3.1.5 Tuning Range 32                                                                      |

|   | 3.2        | Harmonic Oscillators                                                                       |

|   | 3.3        | RC Oscillators                                                                             |

|   |            | 3.3.1 Relaxation Oscillators 37                                                            |

|   |            | 3.3.2 Ring Oscillators                                                                     |

|   |            | 3.3.3 Two-Integrator Oscillator 41                                                         |

|   | 3.4        | State of the Art of CMOS Oscillators 43                                                    |

| 4 | Inio       | ction Locking 42                                                                           |

| 4 | 4.1        | Frequency Synthesizers                                                                     |

|   | 4.1        |                                                                                            |

|   |            | I I I I I I I I I I I I I I I I I I I                                                      |

|   | 4.2        | 4.1.2       Injection-Locked Oscillator       48         Injection Locking Effect       49 |

|   | 4.2<br>4.3 | Synchronization Models                                                                     |

|   | 4.5        | •                                                                                          |

|   |            | 4.3.1Frequency-domain Models504.3.2Phase-domain Models55                                   |

|   |            |                                                                                            |

| 5 | Ref        | erence Signal Generators 59                                                                |

|   | 5.1        | Crystal Oscillator                                                                         |

|   | 5.2        | Spin Transfer Torque Nano-Oscillator62                                                     |

|   |            | 5.2.1Spin Transfer Torque62                                                                |

|   |            | 5.2.2 Magnetoresistance 63                                                                 |

|   |            | 5.2.3 Types of Spin Torque Oscillators64                                                   |

|   | 5.3        | Discussion                                                                                 |

| 6 | Inje       | ction Locked RC Oscillator with STO as reference generator 67                              |

|   | 6.1        | Chosen Topology for the RC Oscillator                                                      |

|   | 6.2        | Proposed Circuits                                                                          |

|   |            | 6.2.1 Free-Running Oscillator                                                              |

|   |            | 6.2.2 Injection-Locked Two-Integrator Oscillator                                           |

|   |            | 6.2.3 Injection Block                                                                      |

|   |            | 6.2.4 Reference Generator                                                                  |

|   |            | 6.2.5 Design Guidelines                                                                    |

|   | 6.3        | Circuit Simulations                                                                        |

|   | 6.4        | Discussion                                                                                 |

| 7 | Con        | clusions and Future Work 85                                                                |

|   | 7.1        | Conclusions                                                                                |

|   | 7.2        | Future Work   86                                                                           |

|   |            |                                                                                            |

| Bi | Bibliography                                                                |    |

|----|-----------------------------------------------------------------------------|----|

| Ι  | Procedures to ensure convergence of the PSS analysis of an Injection-Locked |    |

|    | Oscillator in SpectreRF                                                     | 93 |

# List of Figures

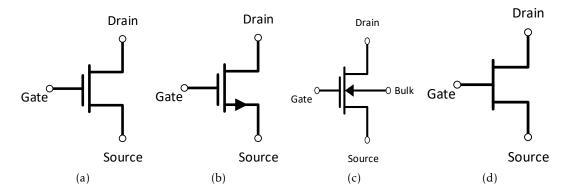

| 2.1  | Commonly used symbols for NMOS transistors (adopted from [18])                   | 6  |

|------|----------------------------------------------------------------------------------|----|

| 2.2  | Commonly used symbols for PMOS transistors (adopted from [18])                   | 7  |

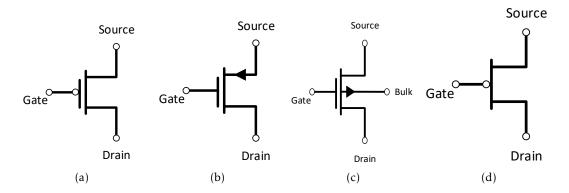

| 2.3  | $i_D - v_{GS}$ curve of an NMOS transistor                                       | 8  |

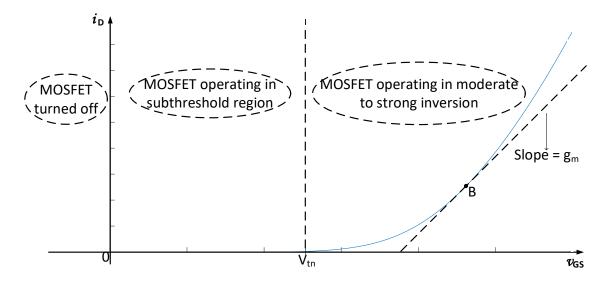

| 2.4  | $i_D - v_{Dsat}$ curve of an NMOS transistor                                     | 9  |

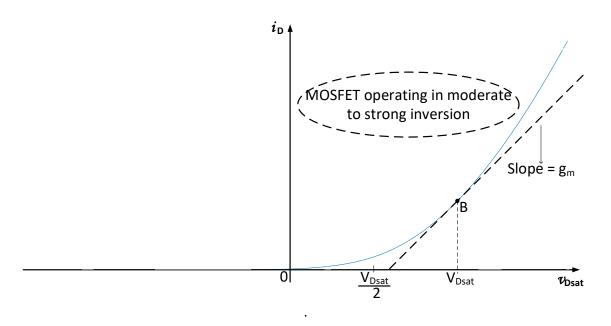

| 2.5  | $i_D - v_{DS}$ curve of an NMOS transistor                                       | 10 |

| 2.6  | Low-frequency small-signal model for NMOS transistor (adapted from [19]).        | 13 |

| 2.7  | High-frequency small-signal model for an NMOS transistor.                        | 14 |

| 2.8  | Models of a resistor thermal noise (adopted from [21])                           | 16 |

| 2.9  | Thermal noise model for MOSFET (adopted from [21]).                              | 16 |

| 2.10 | Power spectrum of noise in a MOSFET (adapted from [21])                          | 18 |

| 2.11 | Noisy two-port network representation (adopted from [21])                        | 18 |

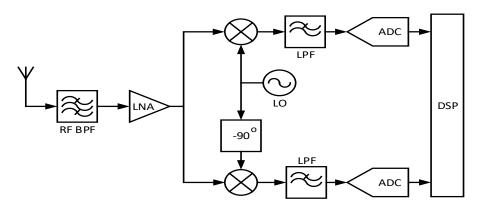

| 2.12 | Heterodyne receiver architecture (adapted from [2])                              | 19 |

| 2.13 | Image rejection in heterodyne receivers (adapted from [2])                       | 20 |

| 2.14 | Homodyne receiver architecture (adapted from [2])                                | 21 |

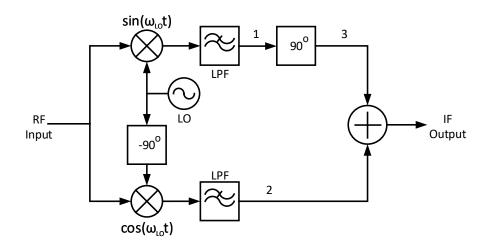

| 2.15 | Hartley image rejection architecture for Low-IF Receiver(adopted from [2]).      | 23 |

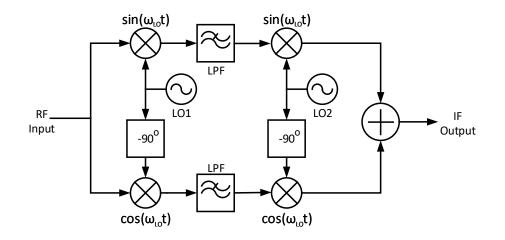

| 2.16 | Weaver image rejection architecture for Low-IF Receiver (adopted from [2]).      | 24 |

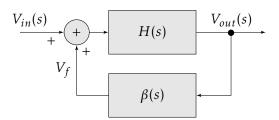

| 3.1  | Sinusoidal oscillator's feedback loop.                                           | 26 |

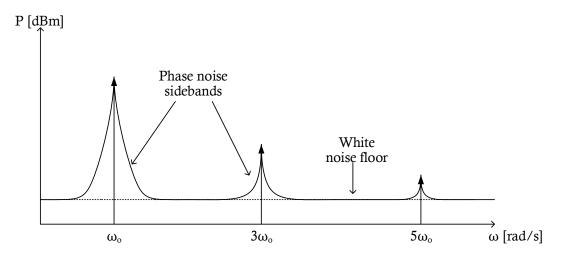

| 3.2  | Real oscillator frequency spectrum (adapted from [24]).                          | 27 |

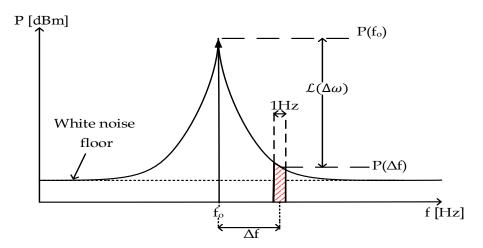

| 3.3  | Phase noise to carrier ratio definition                                          | 27 |

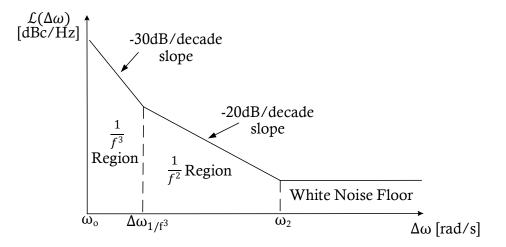

| 3.4  | Asymptotic single-sideband phase noise (adapted from [2])                        | 28 |

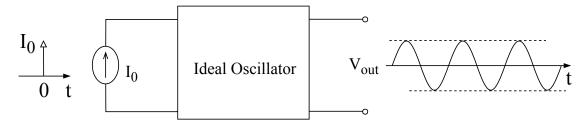

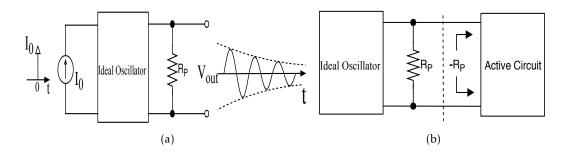

| 3.5  | Ideal oscillator operation (adapted from [1]).                                   | 29 |

| 3.6  | High-level models for real oscillators: (a) Lossy oscillator operation (adapted  |    |

|      | from [1]), (b) Loss cancellation by an active circuit (adapted from [1])         | 30 |

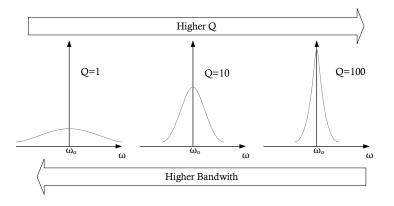

| 3.7  | Variation of the carrier spectrum depending on the value of Q                    | 30 |

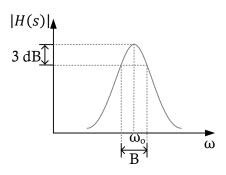

| 3.8  | Definition of Q of a second-order system according to its bandwidth (adapted     |    |

|      | from [2])                                                                        | 31 |

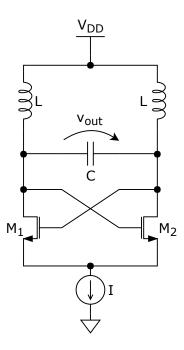

| 3.9  | Cross-coupled oscillator.                                                        | 33 |

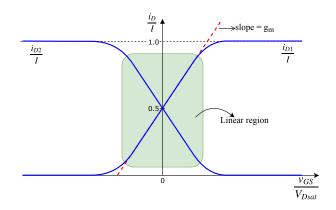

| 3.10 | Voltage to current transfer function of a differential pair (adapted from [19]). | 34 |

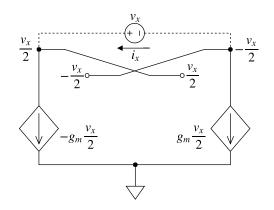

| 3.11 | Small-signal model of a cross-coupled differential pair.                         | 34 |

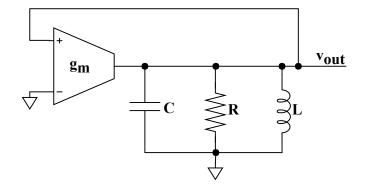

| 3.12 | LC Oscillator behavioral model (adapted from [2])                                | 34 |

| 3.13 | Non-linear oscillator behavioral model (adapted from [16])                       | 36 |

| 3.14 | Schmitt-trigger transfer function (adapted from [19]).                                                                                             | 36 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.15 | CMOS Relaxation oscillator.                                                                                                                        | 37 |

| 3.16 | CMOS Inverting Schmitt-trigger transfer function (adapted from [2])                                                                                | 38 |

| 3.17 | Relaxation oscillator waveforms.                                                                                                                   | 38 |

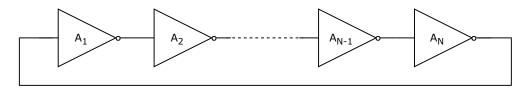

| 3.18 | Ring oscillator (adopted from [21])                                                                                                                | 39 |

| 3.19 | Ring oscillator high-level model.                                                                                                                  | 40 |

| 3.20 | CMOS Ring oscillator.                                                                                                                              | 40 |

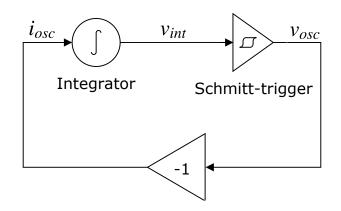

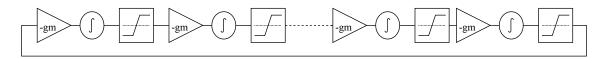

| 3.21 | Two-integrator oscillator high level model                                                                                                         | 41 |

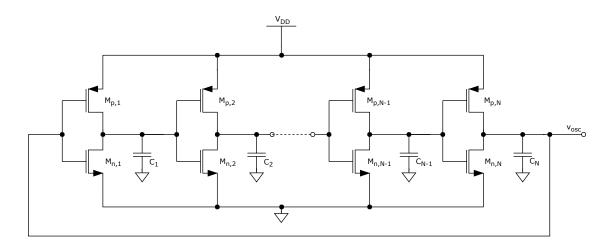

| 3.22 | CMOS Two-integrator oscillator.                                                                                                                    | 42 |

| 3.23 | Two-integrator oscillator linear model (adopted from [2])                                                                                          | 43 |

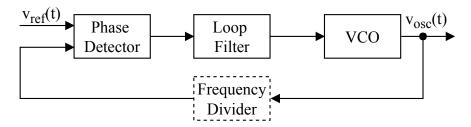

| 4.1  | PLL Block diagram.                                                                                                                                 | 48 |

| 4.2  | Frequency synthesizer with direct injection into a VCO.                                                                                            | 49 |

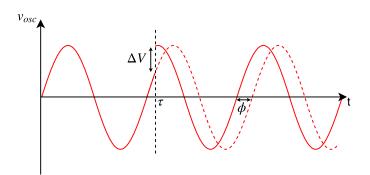

| 4.3  | Oscillator phase-shift due to charge variation at instant $\tau$ (adopted from [16]).                                                              | 49 |

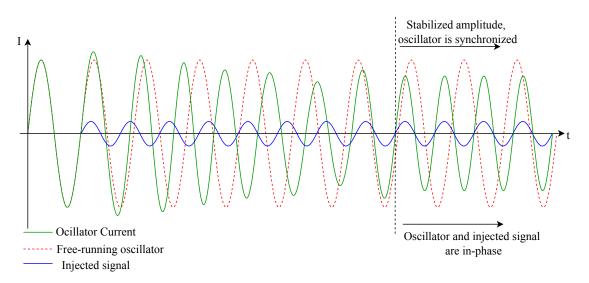

| 4.4  | Syncronization of an oscillator using a periodic stimulus (adapted from [16]).                                                                     | 50 |

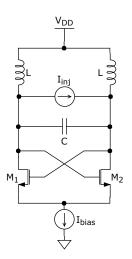

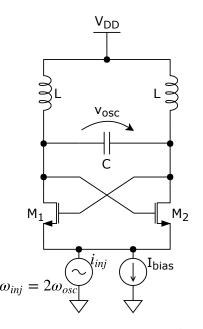

| 4.5  | Injection-locked LC oscillator (adapted from [45]).                                                                                                | 51 |

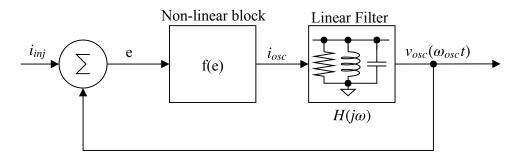

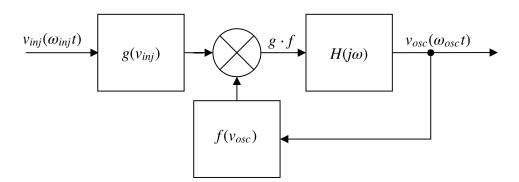

| 4.6  | Injection-locked LC oscillator high-level model (adapted from [46])                                                                                | 51 |

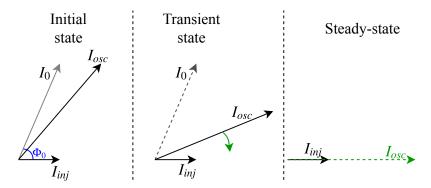

| 4.7  | Phasor diagram illustrating synchronization of an ILO (adapted from [16]).                                                                         | 52 |

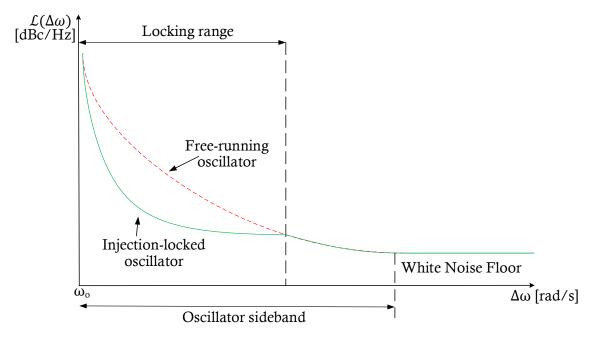

| 4.8  | Phase noise improvement within the locking range (adapted from [16])                                                                               | 53 |

| 4.9  | Miller injection model (adapted from [46]).                                                                                                        | 54 |

| 4.10 | Injection-locked divider (adapted from [45]).                                                                                                      | 56 |

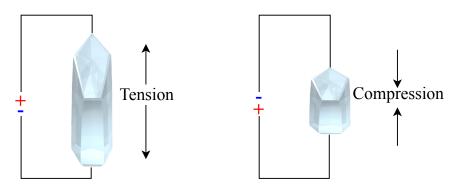

| 5.1  | Piezoelectric phenomena on a crystal (adopted from [16])                                                                                           | 59 |

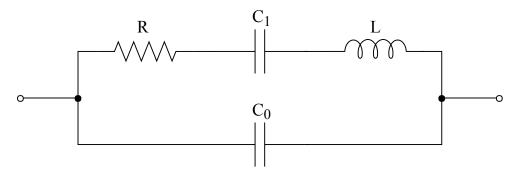

| 5.2  | Electrical symbol for a crystal.                                                                                                                   | 60 |

| 5.3  | Electrical model of a crystal.                                                                                                                     | 60 |

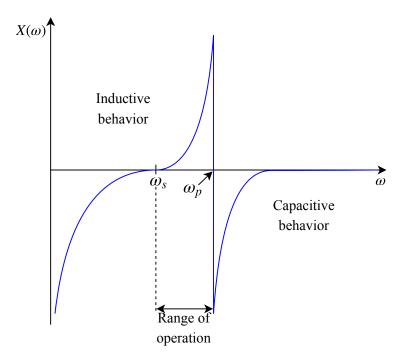

| 5.4  | Crystal reactance vs frequency (adapted from [16])                                                                                                 | 61 |

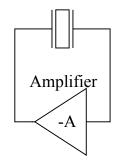

| 5.5  | Crystal oscillator high-level model.                                                                                                               | 61 |

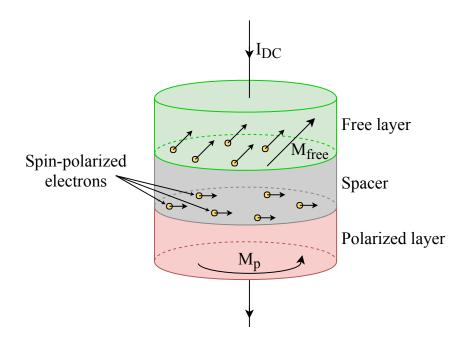

| 5.6  | Spin torque oscillator physical struture (adapted from [12])                                                                                       | 63 |

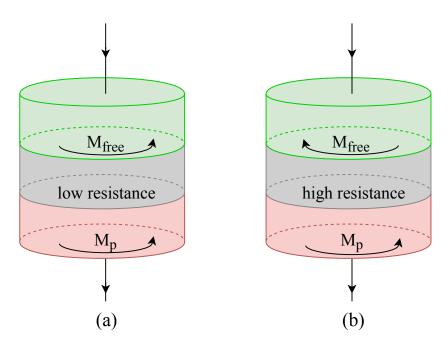

| 5.7  | Magnetoresistance effect: (a) Parallel state; (b) Anti-parallel state (adapted                                                                     |    |

|      | from [12])                                                                                                                                         | 64 |

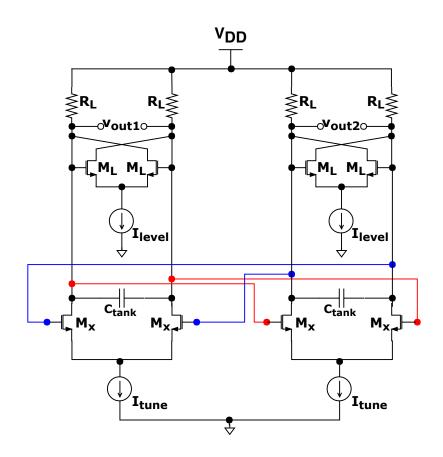

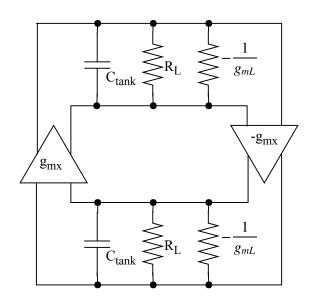

| 6.1  | Free-running oscillator implementation.                                                                                                            | 69 |

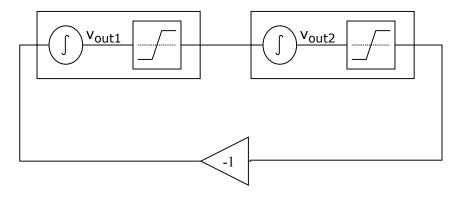

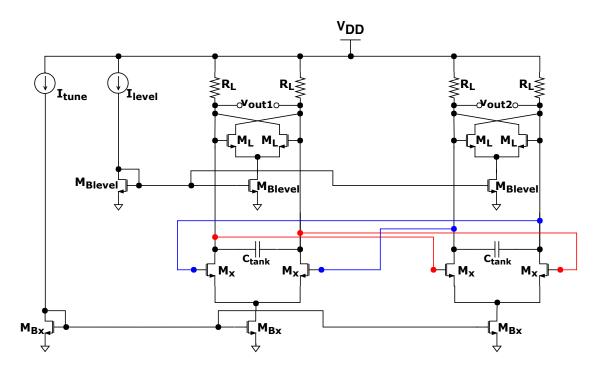

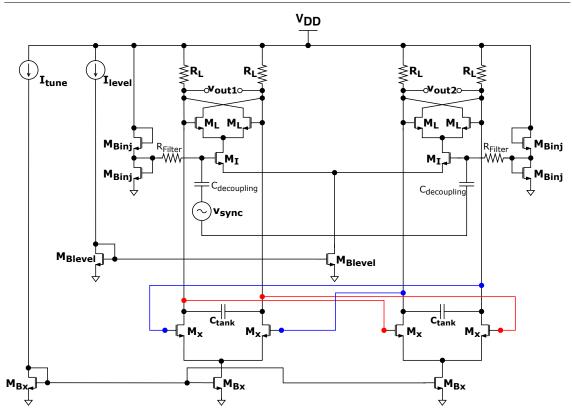

| 6.2  | Two-integrator injection-locked oscillator                                                                                                         | 70 |

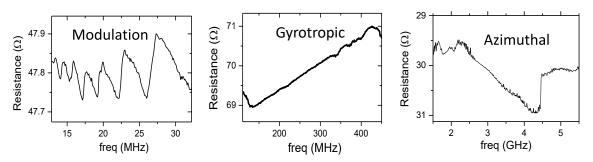

| 6.3  | Operation modes of a spintronic-based frequency sensor developed at INL.                                                                           | 72 |

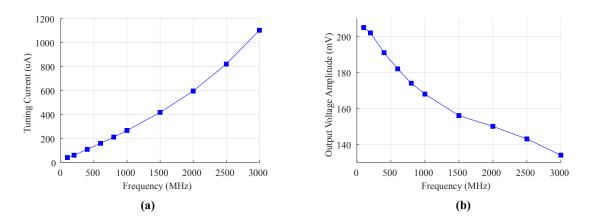

| 6.4  | Voltage and current variation according to the frequency of the free-running oscillator implemented in 130 nm CMOS: (a) Tuning Current, (b) Output |    |

|      | Voltage.                                                                                                                                           | 75 |

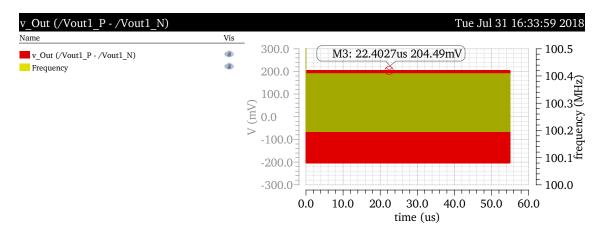

| 6.5  | Free-running oscillator transient response in 130 nm CMOS technology: single output voltage at $f_{100} = 100$ MHz                                 | 76 |

|      | output voltage at $f_{osc} = 100 \text{ MHz}$ .                                                                                                    | 76 |

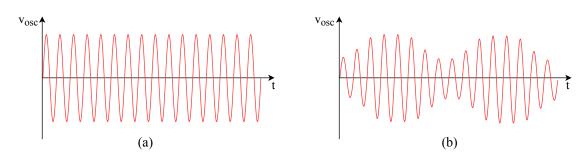

| 6.6  | Output of the oscillator under injection: (a) Successful synchronization, (b) Failed synchronization (adapted from [16]).                          | 76 |

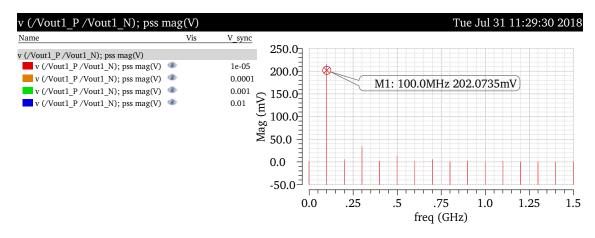

| 6.7  | PSS analysis of the ILO in 130 nm CMOS technology: single output voltage at          |    |

|------|--------------------------------------------------------------------------------------|----|

|      | $f_{osc} = 100 \text{ MHz}.$                                                         | 77 |

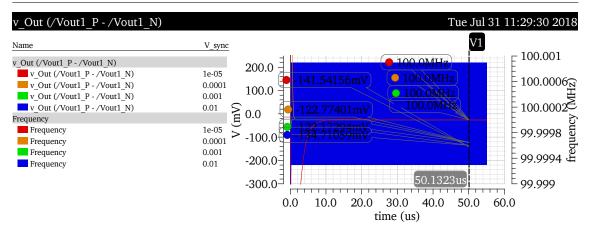

| 6.8  | ILO transient response in 130 nm CMOS technology: single output voltage at           |    |

|      | $f_{osc} = 100 \text{ MHz.}$                                                         | 78 |

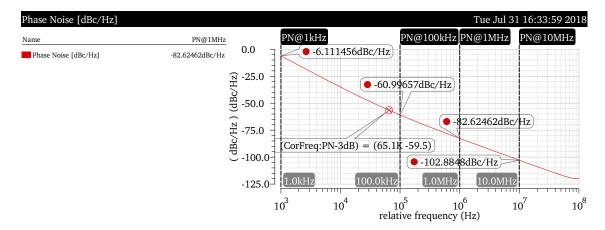

| 6.9  | Free-running oscillator phase noise in 130 nm CMOS technology: single out-           |    |

|      | put voltage at $f_{osc} = 100 \text{ MHz}$ .                                         | 78 |

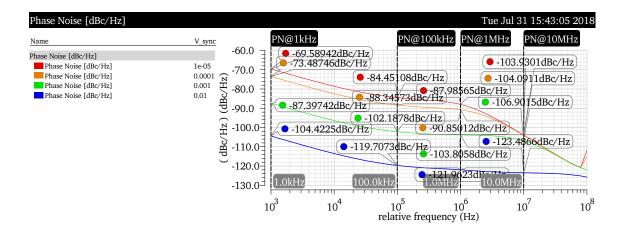

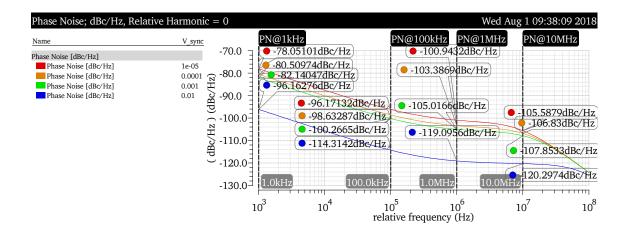

| 6.10 | ILO phase noise in 130 nm CMOS technology: single output voltage at $f_{osc}$ =      |    |

|      | 100 MHz                                                                              | 79 |

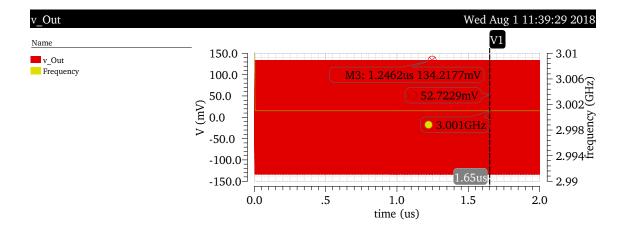

| 6.11 | Free-running oscillator transient response in 130 nm CMOS technology: single         |    |

|      | output voltage at $f_{osc} = 3$ GHz.                                                 | 79 |

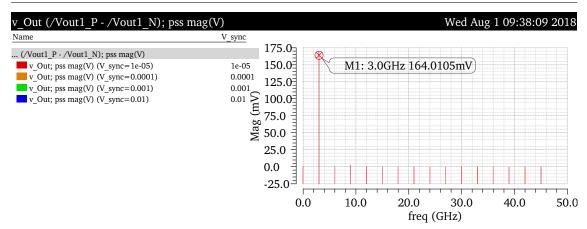

| 6.12 | PSS analysis of the ILO in 130 nm CMOS technology: single output voltage at          |    |

|      | $f_{osc} = 3 \text{ GHz}.$                                                           | 80 |

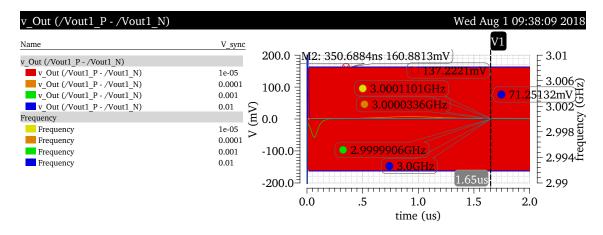

| 6.13 | ILO transient response in 130 nm CMOS technology: single output voltage at           |    |

|      | $f_{osc} = 3 \text{ GHz}.$                                                           | 80 |

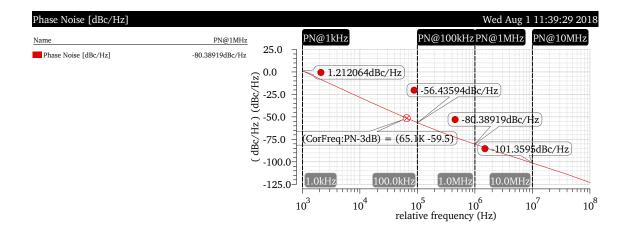

| 6.14 | Free-running oscillator phase noise in 130 nm CMOS technology: single out-           |    |

|      | put voltage at $f_{osc} = 3$ GHz.                                                    | 81 |

| 6.15 | ILO phase noise in 130 nm CMOS technology: single output voltage at $f_{osc}$ =      |    |

|      | 3 GHz.                                                                               | 81 |

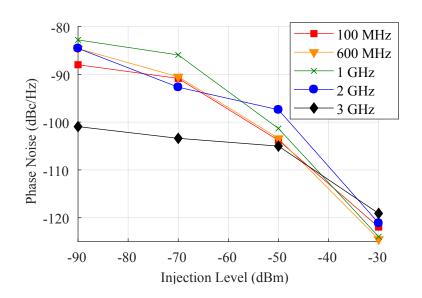

| 6.16 | Phase Noise at 1 MHz offset frequency vs Injection Level for the ILO in 130          |    |

|      | nm CMOS                                                                              | 82 |

|      |                                                                                      |    |

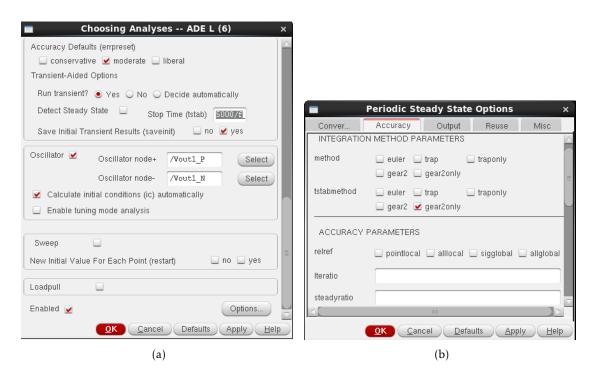

| I.1  | Changing simulator tolerances in SpectreRF: (a) Access to the simulator op-          |    |

|      | tions, (b) Changing tolerance options                                                | 94 |

| I.2  | Configuring the PSS analysis of the free-running oscillator operating at $f_{osc}$ = |    |

|      | 3 GHz: (a) Basic configuration (b) Changing accuracy options.                        | 95 |

| I.3  | Configuring the PSS analysis of the ILO operating at $f_{osc} = 600$ MHz: (a) Basic  |    |

|      | configuration (b) Changing accuracy options.                                         | 96 |

# LIST OF TABLES

| 3.1 | Performance comparison for state-of-the-art CMOS LC oscillators              | 44 |

|-----|------------------------------------------------------------------------------|----|

| 3.2 | Performance comparison for state-of-the-art CMOS RC oscillators              | 44 |

| 5.1 | Reference generators comparison                                              | 65 |

| 6.1 | Comparison of the operation modes of a spintronic-based frequency sensor     |    |

|     | developed at INL                                                             | 72 |

| 6.2 | Free-running oscillator sizing on 130nm CMOS technology.                     | 74 |

| 6.3 | Injection-locked oscillator sizing on 130nm CMOS technology                  | 74 |

| 6.4 | Free-running oscillator sizing on 180 nm CMOS technology                     | 75 |

| 6.5 | Injection-locked oscillator sizing on 180nm CMOS technology.                 | 75 |

| 6.6 | Phase noise at 1 MHz offset frequency: Comparison between free-running       |    |

|     | oscillator and ILO                                                           | 82 |

| 6.7 | Figure of Merit comparison between the free-running oscillator and the ILO.  | 83 |

| I.1 | Values of the steadyratio parameter of the PSS analysis at several operating |    |

|     | points of the ILO.                                                           | 97 |

## ACRONYMS

| AC     | Alternating Current.                             |

|--------|--------------------------------------------------|

| ADC    | Analog to Digital Converter.                     |

| BPF    | Band-Pass Filter.                                |

| CCO    | Current Controlled Oscillator.                   |

| CMOS   | Complementary Metal-Oxide-Semiconductor.         |

| CNR    | Carrier to Noise Ratio.                          |

| CS BPF | Channel Select Band-Pass Filter.                 |

| DC     | Direct Current.                                  |

| DSP    | Digital Signal Processing.                       |

| FoM    | Figure of Merit.                                 |

| GMR    | Giant Magnetoresistance.                         |

| GSM    | Global System for Mobile communications.         |

| HF     | High Frequency.                                  |

| I/Q    | In-Phase and Quadrature.                         |

| IF     | Intermediate Frequency.                          |

| ILO    | Injection-Locked Oscillator.                     |

| INL    | International Iberian Nanotechnology Laboratory. |

| IR BPF | Image Rejection Band-Pass Filter.                |

| ISM    | Industrial, Scientific and Medical.              |

| LF     | Loop Filter.                                     |

| LNA    | Low Noise Amplifier.                             |

#### ACRONYMS

| LO      | Local Oscillator.                                  |

|---------|----------------------------------------------------|

| LPF     | Low-Pass Filter.                                   |

| LTE     | Long-Term Evolution.                               |

| MOS     | Metal-Oxide-Semiconductor.                         |

| MOSFET  | Metal-Oxide-Semiconductor Field-Effect Transistor. |

| MTJ STO | Magnetic Tunnel Junction Spin Torque Oscillator.   |

| NF      | Noise Figure.                                      |

| NMOS    | N-Channel Metal-Oxide-Semiconductor.               |

| PD      | Phase Detector.                                    |

| PLL     | Phase-Locked Loop.                                 |

| PMOS    | P-Channel Metal-Oxide-Semiconductor.               |

| PSD     | Power Spectral Density.                            |

| PSS     | Periodic Steady-State.                             |

| QAM     | Quadrature Amplitude Modulation.                   |

| RF      | Radio Frequency.                                   |

| RMS     | Root Mean Square.                                  |

| SHF     | Super High Frequency.                              |

| SNR     | Signal-to-Noise Ratio.                             |

| SoC     | System on a Chip.                                  |

| SSB     | Single-Sideband.                                   |

| STO     | Spin Torque Oscillator.                            |

| STT     | Spin Transfer Torque.                              |

| SV STO  | Spin Valve Spin Torque Oscillator.                 |

| TMR     | Tunneling Magnetoresistance.                       |

| UHF     | Ultra High Frequency.                              |

| UMTS    | Universal Mobile Telecommunications System.        |

| VCO     | Voltage Controlled Oscillator.                     |

| VCRO    | Voltage Controlled Ring Oscillator.                |

VHF Very High Frequency.

## INTRODUCTION

#### **1.1 Background and Motivation**

Connectivity is a growing need in today's society, especially through wireless technologies, which forces the industry to produce compact devices with greater autonomy. To meet these requirements, it becomes imperative that the electronic circuits which allow the transmission and reception of signals, known as transceivers, have lower areas along with lower power consumption and voltage supply. Therefore, it is desirable to use CMOS technology, which enables design of circuits that possess such characteristics while also being able to operate at high frequencies [1]. CMOS technology is also advantageous to fully integrate the transceiver, allowing manufacturers to put the entire electronic System on a Chip (SoC).

In a transceiver there are two types of circuit that are constantly switched: transmitter and receiver. The transmitter's main features are modulation, upconversion and power amplification while the receiver is responsible for low noise amplification, downconversion and demodulation. Due to the wide variety of existing communication standards, the frequency spectrum is overcrowded. This makes the receiver's Radio Frequency (RF) blocks specifications more demanding than the transmitter's, since requirements such as integrability, band selectivity and interference rejection become critical on the receiving end. For this reason, receivers are the most critical circuits of transceivers, which explains the major concern in the scientific research of receiver improvements. Commonly, transceiver designers define RF front-end as being a part of the receiver circuit that processes the incoming signal in its analog form, thus being the interface between the antenna and the Analog to Digital Converter (ADC).

As previously mentioned, upconversion and down-conversion are processes of frequency translation that are inherent to any transceiver. These operations are performed by mixers, which are blocks that generally have two inputs: the signal to be down-converted or up-converted and a periodic wave generated by a Local Oscillator (LO). For this reason, in addition to mixers, oscillators are key building blocks for any transceiver.

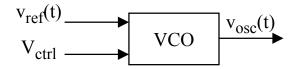

An oscillator is a circuit whose main function is to convert a Direct Current (DC) power at its input into an Alternating Current (AC) signal, which has a periodic waveform [2]. According to its output, an oscillator can be classified as quasi-linear or harmonic, if it produces a sine wave, or it can be a strongly non-linear or relaxation oscillator, if it generates a non-sinusoidal wave. It is also common to classify these types of circuits according to the networks of passive elements that they use to obtain oscillations. If the circuit uses passive networks made up of inductors and capacitors then this is known as an LC oscillator. If the passive networks are constituted by resistors and capacitors, then the circuit is an RC oscillator. In addition, it is common practice to design the oscillator so that its output frequency is controlled within a certain range by an input voltage. In these cases the circuit is known as a Voltage Controlled Oscillator (VCO).

The growing demand for wireless communication among a wide variety of mobile electronic devices means that integrability, low cost and low power consumption are increasingly critical requirements. To meet these needs, RC oscillators are the most suitable topology to implement the LO because of their small areas and wide tuning range.

The main constraint on the performance of oscillators is their phase noise, which means that the focus of research over the last few years has been an attempt to improve it through various techniques such as the use of a noise filter in harmonic oscillators [3], class-D oscillator topologies [4, 5], as well as coupled quadrature oscillators [6, 7] and complementary VCO with implicit common-mode resonance [8].

The techniques described above were applied to LC oscillators, which are the ones with the best phase noise performance. As for RC oscillators, the most common method to reduce their phase noise is the use of frequency synthesizers.

A widely known frequency synthesizer structure is the PLL, where the VCO is enclosed in a feedback loop, along with other blocks, in order to minimize the phase difference between a reference signal and the VCO output. Since it is a feedback loop, the design of a PLL must be careful and complex in order to avoid stability issues and high synchronization times. Furthermore, the implementation of this frequency synthesizer leads to an increase in both the circuit die area and the power consumption of the transceiver [1].

Frequency synthesizers based on injection locking are another type of phase noise improvement technique for RC oscillators. In these synthesizers, the direct injection of the reference signal into a VCO node is sufficient for synchronization, achieving a performance comparable to that of a PLL without having the same disadvantages [9, 10]. The main advantage of this type of synthesizer is that it is a simple structure that requires neither additional blocks nor feedback and the concerns associated with it. However, a drawback to this approach is that, unlike a PLL, the reference signal must operate in the

same frequency range as the VCO.

The generation of the reference signal can be performed by a crystal oscillator [11] or by a STO [12]. Crystal-based wave generators produce a fixed frequency, which leads to a low flexibility of the synthesizer. For this reason, an ILO with a crystal reference generator does not have considerable advantages over a PLL, which can be programmed to perform frequency hopping by adjusting a frequency division block present in its feedback loop. In addition, crystal oscillators have a reduced frequency of operation, up to a few hundred MHz, making it impossible to use them as a reference for an ILO operating in the GHz range.

On the other hand, the reference signal generator may be an STO, which is a relatively new nanostructure under ongoing research [13–15]. The manufacture of these nanostructures is compatible with CMOS processes. In addition, an STO is capable of producing oscillations in the GHz frequency range with large tunability. For these reasons, the use of an STO as a reference generator has the potential to allow implementation of a fully integrated ILO with high phase noise performance and wide tuning range.

This thesis aims to implement a CMOS ILO based on an RC oscillator, as presented in [16]. In this work, it is considered that the reference signal is based on an STO with characteristics similar to those of a frequency sensor developed at the INL, located in Braga (Portugal) [17]. The referred frequency sensor is a nanometric device that generates a DC voltage proportional to the frequency of an RF signal that is transmitted through the device. In addition, this structure shows an adjustable frequency range starting from hundreds of MHz ([100-600 MHz] for operation in the gyrotropic mode), up to a few GHz ([1-12 GHz] for operation in azimuthal mode), while it has a power consumption ranging from 1 $\mu$ W to 15 $\mu$ W.

#### **1.2 Main Contributions**

This work presents the design of a fully integrated ILO with an STO as a reference generator. The proposed circuit was implemented in two different CMOS technologies:

- 130 nm CMOS with a 1.2 V supply voltage, which is a low cost technology.

- 180 nm CMOS with a 1.8 V supply voltage, since this technology is compatible with the manufacturing process of the STO under consideration [13, 14].

These oscillators feature high phase noise performance and a wide tuning range of [100 MHz - 3 GHz], covering the whole Global System for Mobile communications (GSM) frequency band and the vast majority of the Universal Mobile Telecommunications System (UMTS) and the Long-Term Evolution (LTE) bands. The reference signal used in simulations has similar characteristics to those of a nanometric device developed at the INL. Thus, this work serves as proof of concept for the manufacture of a hybrid circuit with this technology in conjunction with CMOS devices.

### **1.3 Thesis Organization**

This dissertation is structured in seven chapters, including this introduction, organized as follows:

#### Chapter 2 – Background on RF receivers using CMOS technology

This chapter presents a brief review of the most important concepts of the Metal-Oxide-Semiconductor Field-Effect Transistor (MOSFET) theory, thus providing the reader with a basis for understanding one of the basic functional units of most RF circuits. Furthermore, the different types of noise present in receivers and how to measure its impact on circuit performance are concepts presented in this chapter. In addition, an overview of the main wireless receiver architectures is provided.

#### Chapter 3 – CMOS Oscillators

This chapter presents fundamental concepts about the operation of oscillator circuits, including the main parameters for measuring their performance. An overview of the main CMOS oscillator implementations is also provided, concluding with a reference to the state-of-the-art oscillators for each topology type (LC and RC).

#### **Chapter 4 – Injection Locking**

The main techniques of phase noise reduction are referred to in this chapter, starting with a greater focus on the most efficient technique: the use of frequency synthesizers. Subsequently, the phenomenon of injection locking is further explored and discussed.

#### **Chapter 5 – Reference Signal Generators**

In this chapter, the two types of circuits that produce reference signals for frequency synthesizers are described: the crystal oscillator and the STO. In addition, both types of reference generator are discussed, in order to identify the most suitable for the implementation of a fully integrated wideband ILO.

#### Chapter 6 – Injection Locked RC Oscillator with STO as reference generator

This chapter presents the design of an ILO based on an RC oscillator. This ILO uses an STO as a reference generator.

Two different implementations of the ILO are made using 130 nm CMOS and 180 nm CMOS technologies. In addition, for each of these technologies, an implementation of the free-running RC oscillator is made.

Moreover, the results of the simulations applied to the implemented circuits are presented and discussed.

#### Chapter 7 – Conclusions and Future Work

In this last chapter the conclusions of the work developed in the course of this thesis are drawn. Some suggestions are also given to further complement what has been achieved in this research topic.

Снартек

# BACKGROUND ON RF RECEIVERS USING CMOS TECHNOLOGY

When a system uses air as its communication channel, it must be taken into account that, due to the characteristics of the channel, the received signals will be greatly attenuated and will suffer strong interferences. This means that in a wireless communication system, the receiving antenna will pick up a signal with extremely low amplitude and a considerable amount of noise. All of these constraints have a greater impact on receiver design than on the transmitter. In addition, it is common in these systems for signals to propagate at high frequencies, allowing the size reduction of antennas and more information to be transmitted using higher bandwidth. Thus, the RF front-end is a crucial part of a receiver, since it is responsible for amplifying the received signal with minimal introduction of noise and for downconverting this signal, so that it can be processed by a digital system. For these reasons, the main functional blocks of a wireless receiver are the Low Noise Amplifier (LNA), the LO and the mixer.

The reception of highly noisy signals leads to specific problems in the design of the receiver LO, since it must be designed to have a narrow spectral component so that the receiver has good channel selectivity and good interference rejection [1].

As mentioned in the introductory chapter, CMOS technology enables the design of low-area circuits capable of operating at high frequencies, together with low power consumption [1]. It is these advantages that make this the most popular technology for designing RF microcircuits. Consequently, the MOSFET is one of the basic functional units of the vast majority of RF circuits. Therefore, this chapter starts with a review of the basic concepts that involve MOSFET operation. Furthermore, this chapter has the following main objectives: an introduction to noise and its impact on the performance of RF circuits implemented with CMOS technology. Finally, an overview of the main architectures of wireless receivers is presented.

### 2.1 Types of MOSFET

There are two types of Metal-Oxide-Semiconductor (MOS) transistors: n-channel devices (N-Channel Metal-Oxide-Semiconductor (NMOS)), which use electrons to conduct current, and p-channel devices (P-Channel Metal-Oxide-Semiconductor (PMOS)) that use holes for the same effect. In addition, NMOS transistors conduct with a positive gate voltage, whereas PMOS devices conduct with a negative gate voltage. Since these transistors have complementary characteristics, microcircuits that use both NMOS and PMOS devices are called CMOS circuits.

There are many symbols that are used to represent a MOSFET according to the type of channel it has. Fig. 2.1 illustrates some symbols that are commonly used to represent NMOS transistors.

Figure 2.1: Commonly used symbols for NMOS transistors (adopted from [18]).

As shown by Fig. 2.1(c), a MOSFET is a four-terminal device, with the Bulk being a terminal that represents the device's substrate. In NMOS transistors, their  $p^-$  type substrate is normally connected to the lowest potential in the circuit. In such cases the Bulk terminal is normally omitted, as shown in Figs. 2.1(a), 2.1(b) and 2.1(d). Likewise, PMOS devices have a n<sup>-</sup> type substrate, which is usually connected to the highest voltage in the microcircuit. Fig. 2.1(b) is the most commonly used symbol for NMOS transistors in analog design. In this representation, an arrow points outward on the source terminal indicating the direction of current in this transistor's channel.

Fig. 2.2 illustrates some symbols that are widely used to represent PMOS transistors.

### 2.2 MOSFET Large-Signal Behaviour

#### 2.2.1 Basic Operation

It is possible to understand the basic operation of the MOSFET by simply studying the behavior of an NMOS transistor.

Figure 2.2: Commonly used symbols for PMOS transistors (adopted from [18]).

The voltage between the gate and the source terminals,  $V_{GS}$ , is an important parameter in the definition of the current conduction state of an NMOS transistor. For values of  $V_{GS}$ satisfying the condition  $V_{GS} \leq 0$ , it is assumed that the transistor is off and there is no current flowing between drain and source.

The gate-source voltage, at which the concentration of electrons immediately under the gate is equal to the concentration of holes in the substrate  $p^-$ , further away from the gate, is widely known as the transistor threshold voltage and denoted  $V_{tn}$  (for NMOS transistors). When  $0 < V_{GS} \le V_{tn}$ , small amounts of subthreshold current can flow from drain to source, as this region is in depletion [19]. Under these conditions, the transistor is in weak inversion and is said to be operating in the subthreshold region.

When  $V_{GS} > V_{tn}$ , a channel is created in the substrate region located between drain and source. This channel is formed by inverting the substrate surface of type  $p^-$  to type  $n^-$ . Thus, the induced channel is also known as the inversion layer [19]. Under these conditions, a positive current,  $I_D$ , flows from drain to source and as  $V_{GS}$  increases in value so does the charge density in the channel. For this reason, there is usually a distinction between moderate inversion ( $V_{GS} > V_{tn}$ ) and strong inversion ( $V_{GS} >> V_{tn}$ ).

The charge density in the channel is proportional to the difference  $V_{GS} - V_{tn}$ , which is often referred to as the effective voltage or the overdrive voltage. In this thesis, the effective voltage will be denoted, as indicated in Eq. (2.1), as  $V_{Dsat}$  (representing the  $V_{DS}$ saturation voltage).

$$V_{Dsat} \equiv V_{GS} - V_{tn} \tag{2.1}$$

In Fig. 2.3 the characteristic  $i_D - v_{GS}$  of a 65 nm technology NMOS transistor is shown in blue. The NMOS transistor whose characteristic is studied in Fig. 2.3 has the following channel dimensions: a channel width,  $W = 4\mu m$ , and a channel length,  $L = 2\mu m$ . Furthermore, it was simulated with Cadence<sup>®</sup> SpectreRF and BSIM3v3 MOSFET models. This characteristic was obtained by setting the voltage between the drain and source,  $V_{DS} = 1.2V$ . The study of Fig. 2.3 allows to understand the  $i_D$ - $v_{GS}$  characteristic of a generic NMOS transistor, where the modes of operation of the device corresponding to each range of  $V_{GS}$  values are indicated.

Figure 2.3:  $i_D - v_{GS}$  curve of an NMOS transistor.

In this figure, there is also a graphical representation of the transistor transconductance,  $g_m$ , which can be understood as the slope of the straight line tangent to the  $i_D - v_{GS}$ curve at the bias point, B. Thus,  $g_m$  is defined in Eq. (2.2).

$$g_m = \frac{\partial i_D}{\partial v_{GS}} \tag{2.2}$$

Rearranging the graph of Fig. 2.3 to analyze  $i_D$  as a function of  $v_{Dsat} = v_{GS} - V_{tn}$ , results in Fig. 2.4, where it is possible to verify that the tangent of bias point B crosses the horizontal axis near  $\frac{V_{Dsat}}{2}$ .

A simpler MOSFET model than the BSIM3v3 used to simulate the NMOS studied in Fig. 2.4 and which is widely used in the community of CMOS circuit designers is known as the quadratic model, since it takes a quadratic variation between  $i_D$  and  $v_{GS}$ . In addition, the quadratic model assumes the approximation defined in Eq. (2.3).

$$g_m = \frac{I_D}{\frac{1}{2}V_{Dsat}}$$

(2.3)

In fact,  $g_m$  is one of the key parameters in transistors design, since it is a factor of great importance in defining the intrinsic gain of a transistor [19].

The gain of a system translates into the ratio between the amplitude of the output signal and the amplitude of the input signal, measuring the ability of the system to affect the amplitude of an input signal, ideally without the introduction of distortions [19].

If the system under discussion produces at its output a signal of amplitude equal to that of the input signal, the system has unity gain. If the system outputs a higher amplitude signal than the input signal, then the gain of this system is greater than unity,

Figure 2.4:  $i_D - v_{Dsat}$  curve of an NMOS transistor.

the input signal is said to be amplified, and the system can be classified as an amplifier. When the amplitude of the input signal is greater than that of the output signal, then the input signal is said to be attenuated and the system has a gain that is less than unity.

Usually, in RF electronic circuits, three different types of gain are considered: current gain (defined in Eq. (2.4), voltage gain (see Eq. (2.5)) and power gain (expressed by Eq. (2.6)).

$$A_i = \frac{i_{out}}{i_{in}} \tag{2.4}$$

$$A_v = \frac{v_{out}}{v_{in}} \tag{2.5}$$

$$A_P = \frac{P_{out}}{P_{in}} \tag{2.6}$$

The Gain is a feature of great importance in transceiver subcircuits responsible for compensating the losses and noise introduced by the channel. This is especially critical in the case of wireless systems, where air is the channel used and the amplitudes of received signals are very weak, usually in the microvolt range.

For clarity, the gain is usually expressed in dB. In these cases, the voltage and current gains expressed in dB,  $A_{v,i}|_{dB}$ , are defined as in Eq. (2.7) while the power gain in dB,  $A_p|_{dB}$ , is expressed in Eq. (2.8).

$$A_{v,i}|_{dB} = 20\log|A_{v,i}| \tag{2.7}$$

$$A_p|_{dB} = 20\log|A_p| \tag{2.8}$$

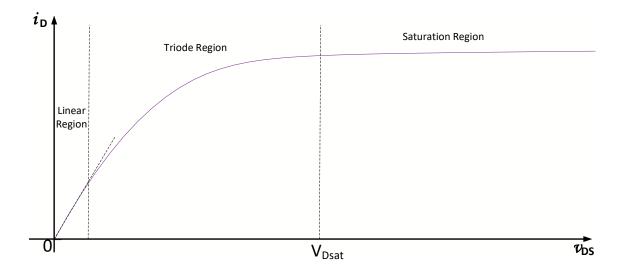

Figure 2.5:  $i_D - v_{DS}$  curve of an NMOS transistor.

As soon as the inversion layer is created ( $V_{GS} > V_{tn}$ ), the current in the channel,  $I_D$ , is able to flow with significant values. Under these conditions, the  $I_D$  value varies nonlinearly as a function of  $V_{DS}$ . Considering this, the quadratic model for MOSFET predicts a linear approximation by sections to the  $i_D - v_{DS}$  characteristic as described in Fig. 2.5. The graph shown in this figure was obtained using the same transistor as in Fig. 2.3 and considering  $V_{GS} > V_{tn}$ .

By making these approximations, the model predicts three regions of operation of the NMOS transistor, dependent on the value of  $V_{DS}$ , such that in each operating region  $I_D$  is approximated by an equation:

1. For  $V_{DS} \approx 0^+$ , the NMOS transistor operates in the linear region, where the device exhibits a resistive behavior and the channel current assumes the expression given by Eq. (2.9).

$$I_D = \mu_n C_{ox} \frac{W}{L} V_{Dsat} V_{DS}$$

(2.9)

Where:

$\mu_n$  – mobility coefficient of n-type carriers (electrons);

$C_{ox}$  – Gate-oxide capacitance per unit area. This is a technology-dependent parameter described by Eq. (2.10).

$$C_{ox} = \frac{K_{ox}\varepsilon_0}{t_{ox}} \tag{2.10}$$

Where:

$K_{ox}$  – relative permittivity of SiO<sub>2</sub>;

$\varepsilon_0$  – permittivity of free space;

$t_{ox}$  – thickness of the thin oxide under the gate.

For simplicity, it is common to use the transconductance parameter,  $k_n$ , defined in Eq. (2.11).

$$k_n = \mu_n C_{ox} \tag{2.11}$$

2. When  $V_{DS}$  increases to values close to  $V_{Dsat}$ ,  $0^+ < V_{DS} < V_{Dsat}$ , then  $I_D$  is described by Eq. (2.12) and the transistor is said to be operating in the triode region.

$$I_D = k_n \frac{W}{L} V_{Dsat} V_{DS} - \frac{(V_{DS})^2}{2}$$

(2.12)

3. With the increase in  $V_{DS}$  value,  $I_D$  increases until the channel becomes pinched off near the drain terminal. The pinch-off occurs at approximately  $V_{DS} = V_{Dsat}$  [18].

When  $V_{DS} > V_{Dsat}$ , the current  $I_D$  stops increasing due to the channel pinch-off and the NMOS transistor operates in the saturation region. In this operating zone, also known as active region,  $I_D$  is approximated by Eq. (2.13).

$$I_D = \frac{k_n}{2} \frac{W}{L} (V_{Dsat})^2$$

(2.13)

#### 2.2.2 Channel-Length Modulation

Apparently, according to Eq. (2.13),  $I_D$  is independent of  $V_{DS}$ . This only remains true for a first-order approximation, since the largest source of error is due to the reduction of the channel length, L, with increasing  $V_{DS}$  values. The increase of  $V_{DS}$  to values larger than  $V_{Dsat}$  causes the depletion region around the drain junction to increase its width in a square root relationship with respect to  $V_{DS}$  [18]. This expansion in width of the drain depletion region results in the reduction of the effective channel length. Consequently, the decrease in effective channel length causes the drain current  $I_D$  to increase, resulting in a phenomenon known as channel-length modulation.

In order to take into account the channel-length modulation effect, and thus obtaining a more accurate approximation,  $I_D$  in the saturation zone must be defined as shown in Eq. (2.14).

$$I_D = \frac{k_n}{2} \frac{W}{L} (V_{Dsat})^2 (1 + \lambda V_{DS})$$

(2.14)

Where  $\lambda$  is a device parameter, dependent on both the technology used to manufacture the transistor and the channel length, L, selected by the circuit designer. The value of  $\lambda$  is much larger for current submicron technologies than for older technologies [19].

### 2.2.3 Body Effect

The large signal equations described so far assume that the source terminal is at the same voltage as the body (the substrate or bulk in an NMOS device). Nonetheless, there are often situations where the source is at a different voltage than the body. In these situations, the value of  $I_D$  in the saturation zone is affected, since the potential difference between body and source influences the amount of charge in the channel and conduction through it.

The influence of the body potential on the channel is termed the body effect and is modeled as a slight increase in threshold voltage,  $V_{tn}$ . The body effect must be considered since it is often important in analog circuit design.

When considering the body effect, it is possible to show that the threshold voltage of an NMOS transistor becomes defined by Eq. (2.15) [18].

$$V_{tn} = V_{tn0} + \gamma \left( \sqrt{V_{SB} + |2\phi_F|} - \sqrt{|2\phi_F|} \right)$$

(2.15)

Where:

$V_{tn0}$  – threshold voltage with zero  $V_{SB}$  (source-to-body voltage);

$\gamma$  – body-effect constant, measured in  $\sqrt{V}$  and defined in Eq. (2.16);

$\phi_F$  – Fermi potential of the body, as explained in Eq. (2.17).

$$\gamma = \frac{\sqrt{2qN_AK_S\varepsilon_0}}{C_{ox}} \tag{2.16}$$

Where:

*q* – electron charge;

$N_A$  – number of acceptors;

$K_s$  – relative permittivity of silicon;

$$\phi_F = \left(\frac{kT}{q}\right) \times \ln\left(\frac{N_A}{n_i}\right) \tag{2.17}$$

Where:

$n_i$  – carrier concentration of intrinsic silicon;

- *k* Boltzmann's constant;

- T temperature in Kelvin.

### 2.2.4 NMOS-PMOS Duality

Once the large-signal behavior of an NMOS transistor is understood, it is possible to understand the large-signal operation of a PMOS device considering three essential differences:

1. PMOS use holes to conduct channel current,  $I_D$ . Holes have an electrical charge symmetrical to that of the electrons used in NMOS devices. In practical terms, this

means that, for a PMOS transistor, the positive current  $I_D$  is considered to flow from source to drain, in the opposite direction to that defined by the current in an NMOS device;

- 2. PMOS devices conduct with a negative gate-to-source voltage. In fact, this is done considering that  $V_{tp}$  is negative and reversing the direction of all the voltages contained in the equations applied to the large-signal behavior of NMOS transistors. Thus, the condition required for conduction on a PMOS device becomes  $V_{GS} < V_{tp} \Leftrightarrow V_{SG} > |V_{tp}|$ , where  $V_{tp}$  is now a negative quantity;

- 3. The holes used in PMOS devices are substantially slower than the electrons used in NMOS. This is described by the hole mobility constant,  $\mu_p$ , which ranges from  $0.25\mu_n$  to  $0.5\mu_n$  [19].

# 2.3 MOSFET Small-Signal Modelling

### 2.3.1 Low-Frequency Small-Signal Model

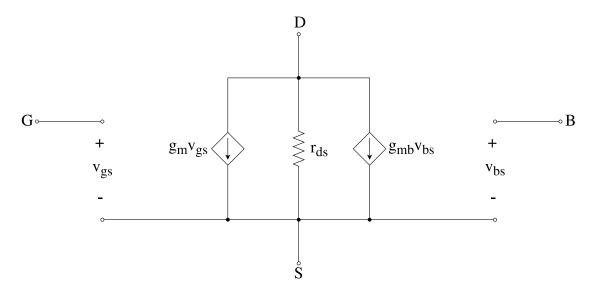

Considering the changes to be made to convert the large signal equations of an NMOS transistor to those of a PMOS device, the same can be done with respect to the small-signal behavior of a transistor. In this regard, the most widely used low-frequency small-signal model for an NMOS transistor operating in the saturation region is depicted in Fig. 2.6.

Figure 2.6: Low-frequency small-signal model for NMOS transistor (adapted from [19]).

The most important component of this model is the voltage-controlled current source,  $g_m v_{gs}$ . To model the implications of the body effect, there is another voltage-controlled current source,  $g_{mb}v_{bs}$ , where  $g_{mb}$  represents the body transconductance and is defined in Eq. (2.18).

$$g_{mb} = \frac{\partial i_D}{\partial v_{BS}} \tag{2.18}$$

Typically,  $g_{mb}$  has values in the range from  $0.1 \times g_m$  to  $0.3 \times g_m$  [19].

Through Eq. (2.14), it is known that there is a linear dependence of the drain current relative to  $V_{DS}$ . This dependence was modeled by a finite resistance between drain and source, rds, given by Eq. (2.19) [19].

$$r_{ds} = \frac{|V_A|}{I_D} \tag{2.19}$$

Where  $V_A = 1/\lambda$ .

#### 2.3.2 High-Frequency Small-Signal Model

Due to the topology of the transistor, a MOSFET model closer to reality must take into account the parasitic capacitances between its terminals, namely:  $C_{gd}$ ,  $C_{db}$ ,  $C_{bs}$  and  $C_{gs}$ . These capacitances must be considered, especially when the device is subject to higher frequency signals. Thus, Fig. 2.7 represents the high-frequency small-signal model for an NMOS transistor.

Figure 2.7: High-frequency small-signal model for an NMOS transistor.

Among the parasitic capacitances of this model,  $C_{gs}$  is the one with the highest value. It is possible to demonstrate that  $C_{gs}$  is given by Eq. (2.20) [18].

$$C_{gs} = \frac{2}{3} W L C_{ox} + W L_{ov} C_{ox}$$

(2.20)

Where  $L_{ov}$  is the effetive overlap distance and is usually empirically derived.

As for the  $C_{gd}$  capacitance, which is sometimes referred to as the Miller capacitance, its value is expressed by Eq. (2.21) and is important when there is a large voltage gain between gate and drain [18].

$$C_{gd} = WL_{ov}C_{ox} \tag{2.21}$$

The capacitances  $C_{db}$  and  $C_{bs}$  are defined by complex technology-dependent equations (see [18]). The precise definitions of these capacitances will not be part of the scope of this thesis.

### 2.4 Noise

Noise is a process that is present in all electronic circuits and has a random nature. This is because it represents external interferences to the circuit as well as physical phenomena related to the nature of the materials. Since noise is detrimental to circuit's performance, it is crucial to analyze and minimize its impact, which can be done through statistical models and methods created for this purpose [20].

### 2.4.1 Thermal Noise

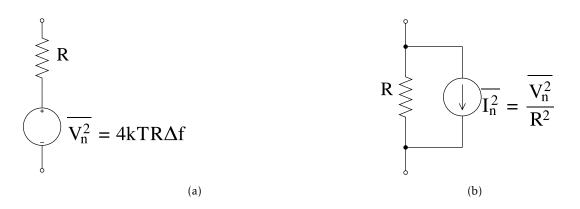

One of the main sources of noise in CMOS circuits is thermal noise, which is the result of thermal excitation of the charge carriers present in a conductor. This type of noise occurs in all elements that, operating at a temperature above absolute zero, have a resistive behavior (including semiconductors).

The spectrum of this type of noise is white (flat) and is proportional to the absolute temperature [18].

The average thermal noise power generated in a resistor is defined by Eq. (2.22).

$$\overline{V_n^2} = 4kTR\Delta f \tag{2.22}$$

Where:

k – Boltzmann's constant;

*T* – absolute temperature in Kelvin;

$\Delta f$  – system bandwidth, which is usually assumed to be  $\Delta f = 1Hz$  so that the noise power is expressed per unit of bandwidth.

Thus, based on Eq. (2.22) thermal noise in a resistor can be modeled in two ways, as illustrated by Fig. 2.8.

Firstly, thermal noise in a resistor can be modeled by a Thevenin equivalent, comprising a voltage source with a Power Spectral Density (PSD) of  $\overline{V_n^2}$  in series with a noiseless resistor (see Fig. 2.8(a)). On the other hand, the Norton equivalent, consisting of a current source with a PSD of  $\overline{I_n^2}$  in parallel with the same noiseless resistor, may serve the same purpose (see Fig. 2.8(b)) [1].

Figure 2.8: Models of a resistor thermal noise (adopted from [21]).

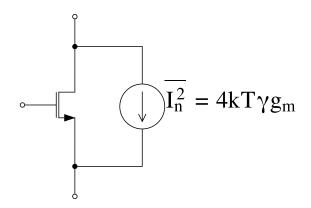

As discussed in the previous chapter, the linear dependence of the drain current of a MOSFET relative to  $V_{DS}$  indicates that there is a resistive component in the behavior of these devices, which is modeled by the  $r_{ds}$  resistor present in its small signal models. Therefore, due to the movement of carriers in the channel, MOS transistors also exhibit thermal noise which can be modeled by a MOSFET with a current source connected between its drain and its source [20], as depicted in Fig. 2.9.

Figure 2.9: Thermal channel noise model for a MOSFET (adopted from [21]).

The average thermal noise current generated by a MOSFET is defined by Eq. (2.23).

$$\overline{I_n^2} = 4kT\gamma g_m \tag{2.23}$$

Where  $\gamma$  is called the excess noise factor. For long-channel transistors  $\gamma = 2/3$ , although this value is higher for short-channel devices [22].

If the MOSFET is operating in the deep triode region, then it acts as a resistor controlled by the gate-source voltage,  $V_{GS}$ . In this case,  $V_{DS} \approx 0$ ,  $\gamma = 1$  and the resistor that the transistor represents in this region has the value:  $R_{on} \approx r_{ds} = 1/g_{ds}$ . Thus, similarly to the case of resistors, the thermal noise current generated by a MOSFET operating in this region is given by Eq. (2.24).

$$I_n^2 = 4kTg_{d0} (2.24)$$

Where  $g_{d0}$  is the drain-to-source conductance,  $g_{ds}$ , for  $V_{DS} = 0$ .

### 2.4.2 Flicker Noise

The other main source of noise in CMOS circuits is the flicker noise. This is a type of noise that is present in all active devices when a DC current is flowing and it originates from a phenomenon that occurs at the interface between the silicon substrate (Si) and the gate (SiO<sub>2</sub>). With the movement of charge carriers at the Si-SiO<sub>2</sub> interface, the random phenomenon occurs, which leads to some of carriers being trapped and others being released, introducing a "flicker"noise into the drain current [20].

The flicker noise of a MOSFET is theoretically modeled as a voltage source in series with its gate, having a PSD as exposed by Eq. (2.25).

$$\overline{V_{nf}^2} \approx \frac{K_f}{C_{ox}WLf}$$

(2.25)

Where  $K_f$  is a process dependent constant, although it is independent of the biasing conditions.

From Eq. (2.25), it can be seen that this PSD is linearly dependent on 1/f, and it is for this reason that flicker noise is also commonly called 1/f noise. Furthermore, this equation also shows that the flicker noise is inversely proportional to transistor's dimensions. Finally, it is important to note that the constant  $K_f$  has a lower value for p-channel devices, which results in PMOS transistors having lower flicker noise than NMOS devices.

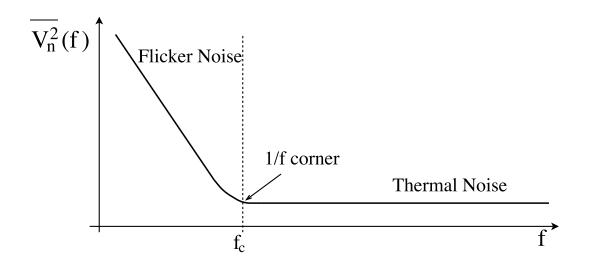

Combining the two main sources of noise in CMOS circuits presented so far, it is possible to conclude that the power spectrum of noise in a MOSFET is illustrated by Fig. 2.10.

In Fig. 2.10 the 1/f corner is shown, which indicates that for frequencies higher than the corner frequency,  $f_c$ , the thermal noise becomes the most important contribution for this PSD.

To find the value of the corner frequency,  $f_c$ , it is first necessary to convert the flicker noise voltage into a current, as indicated by Fig. 2.8(b), replacing  $R = (1/g_m)$ . After this, the flicker noise current that resulted from this conversion is equated to the current given by Eq. (2.23), resulting in the expression shown in Eq. (2.26).

$$f_c = \frac{K_f}{WLC_{ox}} \frac{g_m}{4KT\gamma}$$

(2.26)

Figure 2.10: Power spectrum of noise in a MOSFET (adapted from [21]).

### 2.4.3 Noise Figure

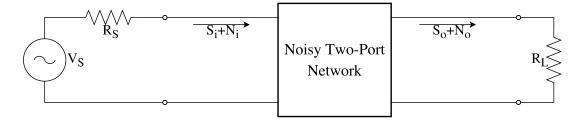

The noise factor is the most widely used measure to determine the noise generated by a circuit and, to understand it, the system must be interpreted as a two-port network as shown in Fig. 2.11.

Figure 2.11: Noisy two-port network representation (adopted from [21]).

The noise factor, F, is defined by the ratio depicted in Eq. (2.27).

$$F = \frac{N_o}{N_i G_A} \tag{2.27}$$

Where:

$N_o$  – available power noise at the circuit's output;

$N_i$  – available power noise at the circuit's input, wich is defined as the noise power resulting from a matched resistor at  $T_o = 290K$  [23];

$G_A$  – available power gain of the circuit.

If the output and input ports are adapted then the power gain of the system is given by Eq. (2.28).

$$G_A = \frac{S_o}{S_i} \tag{2.28}$$

By making this substitution in Eq. (2.27), it is possible to conclude that *F* measures the degradation of the two-port network's Signal-to-Noise Ratio (SNR), as demonstrated in Eq. (2.29).

$$F = \frac{S_i/N_i}{S_o/N_o} = \frac{SNR_i}{SNR_o}$$

(2.29)

It is common for the noise factor to be expressed in dB and when this happens it acquires the name of Noise Figure (NF), defined by Eq. (2.30).

$$NF = 10\log\frac{SNR_i}{SNR_a} \tag{2.30}$$

In an ideal case, where the network would be noiseless, then the noise factor would have the value F = 1, resulting in a noise figure of NF = 0dB.

# 2.5 Receiver Architectures

Within the different approaches that exist to implement receivers, there are three main architectures that will be addressed in this section: heterodyne, homodyne and low-IF.

#### 2.5.1 Heterodyne Receiver

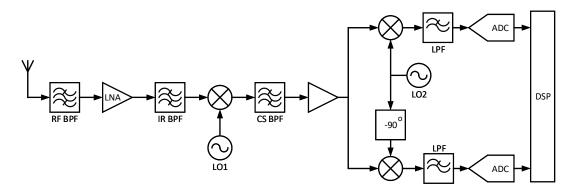

The heterodyne receiver, which consists of a two-step down-conversion of the received signal, is shown in Fig. 2.12.

Figure 2.12: Heterodyne receiver architecture (adapted from [2]).

This is a widely adopted architecture in wireless communication receivers, also known as the Intermediate Frequency (IF) receiver.

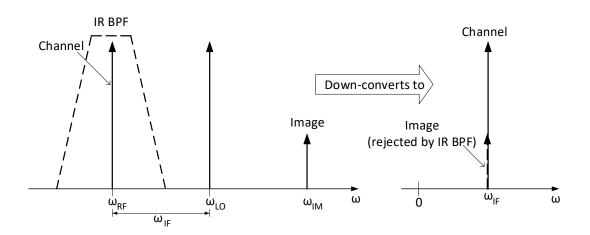

From the information captured by the antenna, the Band-Pass Filter (BPF) selects the frequency band that contains the signal of interest. After this signal is amplified by the LNA, it will be filtered by the Image Rejection Band-Pass Filter (IR BPF), whose function is to eliminate the image that can be generated in the down-conversion process. The need for this filter arises from the fact that two different input frequencies can generate the same IF (see Fig. 2.13).

Figure 2.13: Image rejection in heterodyne receivers (adapted from [2]).

The down-conversion process, performed by the Mixer, is possible thanks to an inherent property of multiplying two sinusoidal signals, also known as mixing. Thanks to this property, the output signal of the mixer,  $v_{IF}(t)$ , results from the multiplication of the two pure sinusoidal waves at its input,  $v_{LO}(t)$  and  $v_{RF}(t)$ . This mathematical relation is given by Eq. (2.31).

$$v_{IF}(t) = v_{RF}(t) \cdot v_{LO}(t) = \frac{1}{2} V_{RF} V_{LO} \left[ \cos(\omega_{RF}t - \omega_{LO}t) + \cos(\omega_{RF}t + \omega_{LO}t) \right]$$

(2.31)

Where:

$v_{RF}(t) = V_{RF} \cos(\omega_{RF}t)$  is the receiver's input signal;  $v_{LO}(t) = V_{LO} \cos(\omega_{LO}t)$  is the sine wave produced by the LO; And  $\omega_{IF} = \omega_{RF} - \omega_{LO}$ .

Through Eq. (2.31) it is possible to clarify the importance of the IR BPF eliminating a signal  $v_{IM} = V_{IM} \cos(\omega_{IM} t)$  before it reaches the input of the mixer. This is because, if  $\omega_{IM} = 2\omega_{LO} - \omega_{RF}$  then the mixing between  $v_{IM}$  and  $v_{LO}$  will generate two signals at the frequencies  $\omega_1 = \omega_{LO} - \omega_{RF}$  and  $\omega_2 = 3\omega_{LO} - \omega_{RF}$ . Meaning that  $|\omega_1| = |\omega_{IF}|$ . Thus, if the IR BPF was not present in this architecture, the signal with frequency  $\omega_1$  would deteriorate to the signal of interest by overlapping the frequency  $\omega_{IF}$ .

The choice of IF is an important point to consider in the design of this architecture, since there is a trade-off between a high IF that facilitates the design of the IR BPF and a low IF that facilitates the suppression of interferers [2]. It is also important to note that the filters mentioned here require a high quality factor, only possible to achieve with reactive components, making it difficult to implement this architecture as a good solution for applications where low-cost and low-area are the main priorities.

Subsequent to the first mixing procedure, the Channel Select Band-Pass Filter (CS BPF) eliminates the interferers that are down-converted along with the signal of interest, which is then amplified. After this amplification, the information is again down-converted generating an In-Phase and Quadrature (I/Q) signal at a baseband frequency, which is

then cleared of interferers by the Low-Pass Filter (LPF). Finally, the signal is converted to the digital domain by the ADC so that it can proceed to Digital Signal Processing (DSP). Therefore, a key advantage of this architecture is the compatibility it has with modern modulation schemes that require I/Q signals for full recovery of the information.

### 2.5.2 Homodyne Receiver

In the homodyne receiver architecture, after the RF signal is picked up by the antenna, filtered by the RF BPF and amplified by the LNA, there is a single down-conversion from the RF frequency to the baseband. This is achieved by using a LO to generate a signal with the same frequency as the RF input. Therefore, this topology is also called the direct-conversion or zero-IF receiver and is illustrated in Fig. 2.14.

Figure 2.14: Homodyne receiver architecture (adapted from [2]).

The fact that only one LPF is required to make a correct channel selection and that there is no external IR BPF leads to quality factor requirements for these filters that are less demanding. In addition, these characteristics allow the receiver full integration, making this architecture a solution for obtaining low-cost, low-area and low-power receivers. However, as will be evidenced by the disadvantages briefly presented below, this topology is a less appropriate solution than the heterodyne receiver in applications whose demands are more stringent [2].

Firstly, it is important to note that this circuit is more vulnerable to flicker noise, since this type of noise can corrupt the baseband signals used in this receiver.

Another drawback of this circuit relates to mismatches between the I/Q mixers and errors in the 90° phase shift circuit. This leads to imbalances in the gain and phase outputs of the I/Q mixers, which can corrupt the signal constellation used in modern modulation schemes such as Quadrature Amplitude Modulation (QAM). To overcome this problem it is necessary to implement high frequency blocks with very high precision, which is a difficult task.

It is also important to note the problem that arises if two interferers, with frequencies  $\omega_1$  and  $\omega_2$  such that  $\omega_2 - \omega_1 \approx 0$ , are close to the channel of interest. In this case, the

mixing of these interferers results in a second-order term that will be down-converted to near the baseband, distorting the signal.

Another problem that can occur in this receiver is the coupling of the LO signal to the antenna that will eventually radiate this information, a phenomenon known as LO leakage. This is due to the capacitances and resistances between the LO and RF ports of the mixer and the LNA ports. This means that this problem has the potential to interfere with other receivers using the same wireless standard unless a differential LO is used and the mixer outputs cancel common mode components [2].

As a consequence of LO leakage, a phenomenon known as LO self-mixing occurs. In this process a DC component is generated at the mixer's output, which can saturate baseband circuits and prevent signal detection [2]. Therefore, in order to overcome this limitation, the homodyne receiver requires DC offset removal techniques.

Finally, it should be noted that, in order to create the necessary conditions for converting the baseband signal of interest to the digital domain, the LPF must be highly linear and have low noise contributions. These requirements, which enable the LPF to suppress out-of-channel interferers, are difficult to implement.

### 2.5.3 Low-IF Receiver

The low-IF receiver has a design approach that blends the characteristics of the two receiver topologies previously mentioned, in order to combine the advantages of each of them in a single architecture. On the one hand, the low-IF receiver has the high performance and flexibility that are typical in the heterodyne architecture, on the other hand it can be fully integrated as the homodyne receiver.

Like the heterodyne architecture, the low-IF receiver also avoids the problems related to direct conversion mentioned in the previous subsection by using an intermediate frequency, which in this case has a low value. However, the use of an IF implies that the low-IF receiver will also have to deal with the image problem described by Fig. 2.13. To overcome this limitation while avoiding the use of a high quality factor IR BPF, the low-IF receiver requires special techniques to cancel the image frequency. To accomplish this purpose, there are two main image rejection architectures, one proposed by Hartley and the other suggested by Weaver.

The Hartley architecture is illustrated in Fig. 2.15, consisting of a solution that begins by mixing the I/Q outputs of the LO with the RF signal. Thereafter, the resulting signal is filtered by the LPF and one of the I/Q outputs is then shifted 90° and added to the other output signal. This last operation results in an IF signal with no image frequency.

The reason why the output of this architecture has no image frequency is explained mathematically. First, assume that the RF input signal with an associated image frequency is described by Eq. (2.32).

$$x_{RF}(t) = V_{RF}\cos(\omega_{RF}t) + V_{IM}\cos(\omega_{IM}t)$$

(2.32)

Figure 2.15: Hartley image rejection architecture for Low-IF Receiver (adopted from [2]).

Thus, at point 1 of Fig. 2.15, there is the signal  $x_1(t)$ , described by Eq. (2.33), and at point 2 the signal is defined by Eq. (2.34)

$$x_1(t) = -\frac{V_{RF}}{2} \sin \left[ (\omega_{RF} - \omega_{LO}) t \right] + \frac{V_{IM}}{2} \sin \left[ (\omega_{LO} - \omega_{IM}) t \right]$$

(2.33)

$$x_{2}(t) = \frac{V_{RF}}{2} \cos \left[ (\omega_{LO} - \omega_{RF}) t \right] + \frac{V_{IM}}{2} \cos \left[ (\omega_{LO} - \omega_{IM}) t \right]$$

(2.34)

At point 3, the signal expressed in Eq. (2.33) is shifted by 90°, which is equivalent to a substitution of  $[\sin(\alpha)]$  for  $[-\cos(\alpha)]$ , resulting in the signal given by Eq. (2.35).

$$x_{3}(t) = \frac{V_{RF}}{2} \cos \left[ (\omega_{RF} - \omega_{LO}) t \right] - \frac{V_{IM}}{2} \cos \left[ (\omega_{LO} - \omega_{IM}) t \right]$$

(2.35)

The result of the sum between  $x_1(t)$  and  $x_3(t)$  is an IF output with no image frequency component, defined by Eq. (2.36).

$$x_{IF}(t) = V_{RF} \cos\left[\left(\omega_{RF} - \omega_{LO}\right)t\right]$$

(2.36)

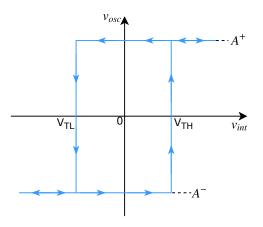

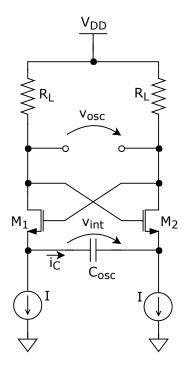

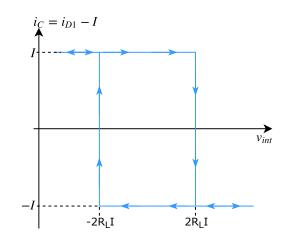

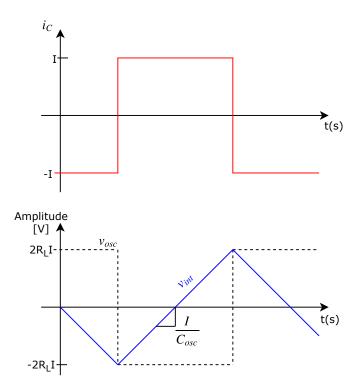

This circuit has two major limitations that can lead to incomplete image cancellation: high sensitivity to LO quadrature errors and mismatches between the two I/Q signal paths.