# Renata Santos Leitão

Licenciada em Ciências da Engenharia Electrotécnica e de Computadores

# Design of a Limiting Amplifier for an Optical Receiver

Dissertação para obtenção do Grau de Mestre em Engenharia Electrotécnica e de Computadores

Orientador: Prof. Dr. Nuno Filipe Silva Veríssimo Paulino, Prof. Auxiliar, Universidade Nova de Lisboa

Júri

Presidente:Prof. Dr. Rodolfo Alexandre Duarte Oliveira, FCT-UNLArguente:Prof. Dr. Luís Augusto Bica Gomes de Oliveira, FCT-UNLVogal:Prof. Dr. Nuno Filipe Silva Veríssimo Paulino, FCT-UNL

Março, 2018

## Design of a Limiting Amplifier for an Optical Receiver

Copyright © Renata Santos Leitão, Faculdade de Ciências e Tecnologia, Universidade NOVA de Lisboa.

A Faculdade de Ciências e Tecnologia e a Universidade NOVA de Lisboa têm o direito, perpétuo e sem limites geográficos, de arquivar e publicar esta dissertação através de exemplares impressos reproduzidos em papel ou de forma digital, ou por qualquer outro meio conhecido ou que venha a ser inventado, e de a divulgar através de repositórios científicos e de admitir a sua cópia e distribuição com objetivos educacionais ou de investigação, não comerciais, desde que seja dado crédito ao autor e editor.

To Joaquim and António

### ACKNOWLEDGEMENTS

Firstly, I would like to thank Professor Nuno Paulino for his advising and supervising, counseling, and unconditional support throughout the development of this thesis. Furthermore, for all his patience, help, and especially all the knowlegde he was able to pass on to me. I would also like to express my gratitude to CERN and give thanks for the opportunity of being part of this project. Especially, to Paulo Moreira and Szymon Kulis for all the support, guidance and supervising they provided me during this project. I would also like to thank my colleagues from the project, Inês Martins and João Carvalho, for all the support, patience and friendship shown throughout this work, even when things sometimes got complicated. A special thank you to Inês for many interesting and helpful discussions.

On a more personal note, I would like to thank my family, especially my mother, my father and my grandmothers for all the support, caring and love demonstrated not only during this work, but also during my entire academic journey. Also, my uncle, for all the conversations and counselling that were so essential. I would like to thank Miguel for his support, encouragement, and for always telling me that I could do it. Last but not least, I would like to thank all my closest friends that were always present both in the good and bad moments.

## ABSTRACT

The HEP experiments that take place at CERN's LHC demand a multi-gigabit optical link for an efficient transmission of the resulting generated data. An optoelectronic link arises as the best solution given its possibility of working at high data rates and due to fiber's imunnity to electromagnetic noise. The design of this optical link is particularly demanding due to the stringent data rate specifications (5Gb/s), the BER specification (10<sup>-</sup>12) and the constraints imposed by radiation. In HEP, radiation is always a constraint so, the Optical Receiver circuit must be hardened in order to tolerate that kind of environment radiation-tolerant.

The core of a standard optoeletronic receiver includes a Photodiode, a Transimpedance Amplifier (TIA) and a Limiting Amplifier (LA). This thesis proposes the study and implementation of one of these blocks (LA), as the main focus, as well as the analysis and design of all three other blocks.

The two major design constraints regarding the LA are the bandwidth and minimising its power consumption, which were overcome by using two bandwidth enhancement techniques. The circuit yields a bandwidth of 4.8 GHz with a power consumption under 19 mW.

Another fundamental block is the Output Buffer. The major request for this block was maintaining relatively low transition times and improving the signal's integrity. It has a differential output swing around 400 mV with Pre-emphasis levels larger than 130%.

The third block is the Received Signal Strength Indicator (RSSI). From a system point of view it is useful to have a measure of the input signal's power so that the communication channel is used in its full potential. With a power consumption smaller than  $600 \mu$ W the RSSI presents an input dynamic range larger than 50 dB. The fourth block implements a Squelch function, in order to suppress unwanted output toggling due to noise.

All these elements were developed in a TSMC 65 nm CMOS process with a 1.2 V supply voltage.

**Keywords:** CERN, LHC, Optical Receiver, Radiation-tolerant, LA, RSSI, Output Buffer, Squelch.

# Resumo

As experiências de física de alta energia, que ocorrem no LHC do CERN, exigem uma ligação de alta velocidade, para uma transmissão eficiente dos dados gerados pelas mesmas. Um canal de transmissão optoeletrónico surge como sendo a melhor solução devido à possibilidade de trabalhar com altos ritmos de transmissão e à imunidade ao ruído eletromagnético da fibra ótica. Este projeto é exigente devido às especificações associadas ao ritmo de transmissão (5Gb/s) e ao BER (10<sup>-12</sup>) bem como às restrições impostas pela radiação. Dado que, neste tipo de ambiente, a radiação é sempre um constrangimento, o Recetor Ótico deverá ser capaz de tolerar e apresentar imunidade à mesma.

O núcleo do Recetor Ótico inclui um Fotodíodo, um Amplificador de Transimpedância e um Amplificador Limitador. Esta tese propõe o estudo e implementação de um destes elementos de base, o Amplificador Limitador, como elemento principal, e de outros três blocos.

Os dois principais requisitos da especificação do Amplificador Limitador foram a largura de banda e a minimização do consumo de potência, objetivos cumpridos usando uma combinação de técnicas de aumento de largura de banda. Apresenta uma largura de banda de 4.8 GHz com um consumo de potência inferior a 19 mW.

Outro bloco essencial é o Buffer de Saída. O requisito principal neste bloco foi alcançar tempos de transição baixos, aumentando a integridade do sinal. O Buffer apresenta uma excursão sinal diferencial que ronda os 400 mV com níveis de *Pre-emphasis* superiores a 130%.

O terceiro bloco é um Indicador de Potência de Sinal Recebido. Com um consumo inferior a  $600 \,\mu\text{W}$  apresenta uma gama dinâmica superior a  $50 \,\text{dB}$ . O quarto elemento assegura uma função de *Squelch*, suprimindo o ruído na saída, quando não há transmissão.

Todos estes elementos foram desenvolvidos em tecnologia CMOS 65 nm da TSMC com uma tensão de alimentação de 1.2 V.

**Palavras-chave:** CERN, LHC, Recetor Ótico, Tolerante à radiação, Amplificador Limitador, Indicador de Força de Sinal Recebido, Buffer de Saída, *Squelch*.

# Contents

| Li | List of Figures xv |          |                                           |     |  |

|----|--------------------|----------|-------------------------------------------|-----|--|

| Li | ist of Tables xix  |          |                                           |     |  |

| A  | Acronyms           |          |                                           | xxi |  |

| 1  | Intr               | oductio  | on                                        | 1   |  |

|    | 1.1                | Motiva   | ation                                     | 2   |  |

|    | 1.2                | Thesis   | Organization                              | 4   |  |

| 2  | Lite               | rature's | s Review                                  | 7   |  |

|    | 2.1                | Limiti   | ing Amplifier                             | 7   |  |

|    |                    | 2.1.1    | Performance Parameters                    | 8   |  |

|    |                    | 2.1.2    | Cascade of Gain Stages                    | 10  |  |

|    |                    | 2.1.3    | AM/PM Conversion                          | 16  |  |

|    |                    | 2.1.4    | Broadband Techniques                      | 16  |  |

|    |                    | 2.1.5    | Offset Cancelation Techniques             | 30  |  |

|    | 2.2                | Outpu    | at Buffer with Pre-emphasis Capability    | 32  |  |

|    | 2.3                | Receiv   | ved Signal Strength Indicator and Squelch | 34  |  |

|    | 2.4                | Radiat   | tion Effects on CMOS Technology           | 34  |  |

|    |                    | 2.4.1    | TID Effects on Modern CMOS Process        | 35  |  |

| 3  | Imp                | lement   | tation in CMOS                            | 41  |  |

|    | 3.1                | Limiti   | ing Amplifier                             | 41  |  |

|    |                    | 3.1.1    | Modelation                                | 41  |  |

|    |                    | 3.1.2    | Gain Cell                                 | 53  |  |

|    |                    | 3.1.3    | Replica Bias                              | 56  |  |

|    |                    | 3.1.4    | Limiting Chain                            | 61  |  |

|    |                    | 3.1.5    | Simulation Results                        | 63  |  |

|    | 3.2                | Receiv   | ved Signal Strength Indicator             | 68  |  |

|    |                    | 3.2.1    | Full-Wave Rectifier                       | 70  |  |

|    |                    | 3.2.2    | PVT Independent Bias                      | 76  |  |

|    |                    | 3.2.3    | Simulation Results                        | 82  |  |

|    |       | 3.2.4   | Layout                                | 84  |

|----|-------|---------|---------------------------------------|-----|

|    | 3.3   | Squelc  | h                                     | 86  |

|    |       | 3.3.1   | Comparator                            | 88  |

|    |       | 3.3.2   | Squelch's Logic                       | 92  |

|    |       | 3.3.3   | Simulation Results                    | 96  |

|    | 3.4   | Outpu   | t Buffer with Pre-emphasis Capability | 98  |

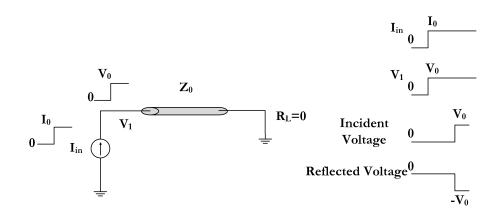

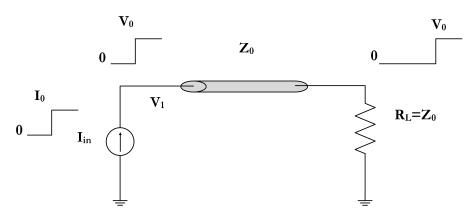

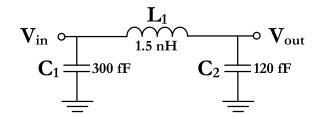

|    |       | 3.4.1   | Transmission Lines                    | 99  |

|    |       | 3.4.2   | Impedance Matching                    | 101 |

|    |       | 3.4.3   | Differential Signaling                | 102 |

|    |       | 3.4.4   | Double-termination Output Buffer      | 103 |

|    |       | 3.4.5   | Pre-emphasis Capability               | 104 |

|    |       | 3.4.6   | Simulation Results                    | 114 |

| 4  | Con   | clusion | as and Future Work                    | 119 |

|    | 4.1   | Conclu  | usions                                | 119 |

|    | 4.2   | Future  | e Work                                | 122 |

| Bi | bliog | raphy   |                                       | 123 |

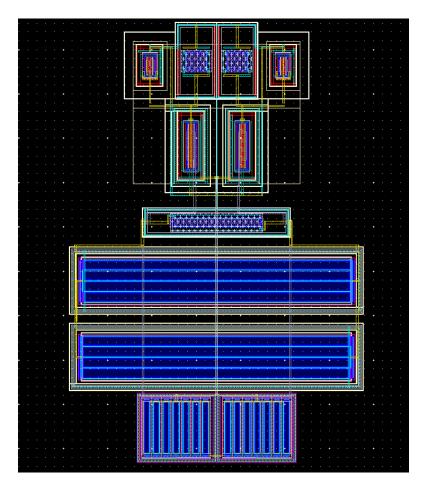

| A  | Layo  | outs    |                                       | 127 |

# List of Figures

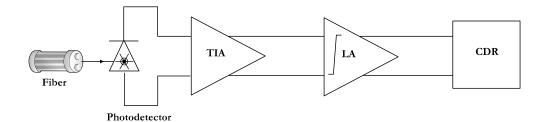

| 1.1  | Simplified block diagram of a standard Optical Receiver.                                                  | 2  |

|------|-----------------------------------------------------------------------------------------------------------|----|

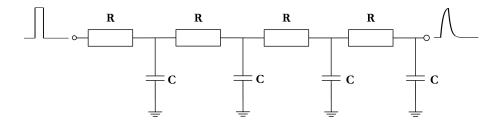

| 1.2  | Softening of the edges in an electrical line - RC model for lossy line                                    | 2  |

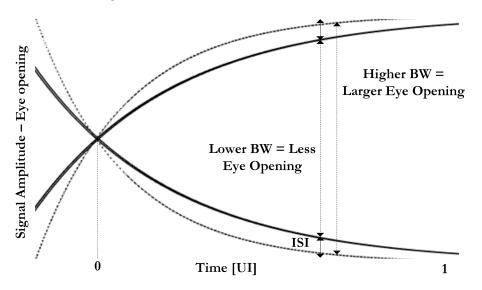

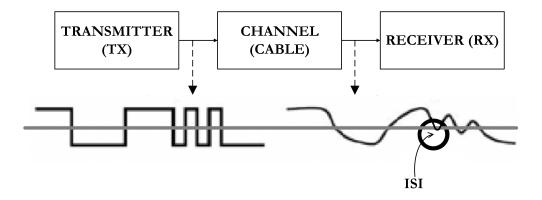

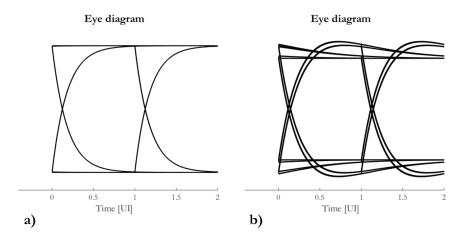

| 2.1  | Eye diagram for two different bandwidths and resulting ISI                                                | 8  |

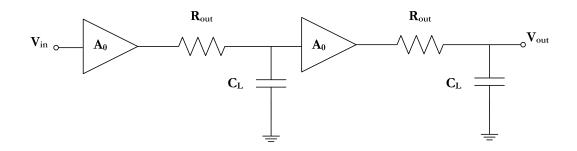

| 2.2  | Simplified small signals' model of a cascade of two gain stages                                           | 10 |

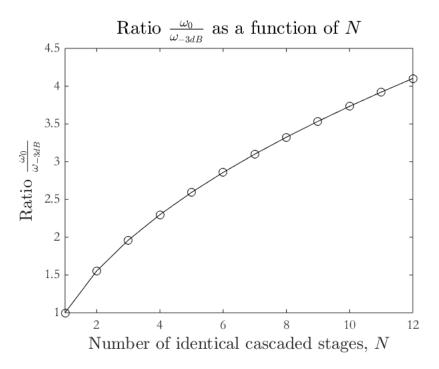

| 2.3  | Ratio $\frac{\omega_0}{\omega_{-3dR}}$ as a function of the number of cascaded stages, $N. \ldots \ldots$ | 12 |

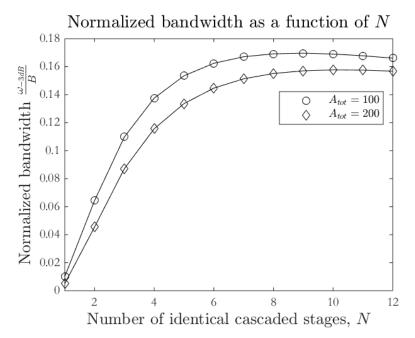

| 2.4  | Normalized bandwidth as a function of the number of cascaded stages for                                   |    |

|      | $A_{tot} = 100 \text{ and } A_{tot} = 200$                                                                | 13 |

| 2.5  | Non-linear behavior in a cascade of differential pairs                                                    | 14 |

| 2.6  | Differential pair.                                                                                        | 15 |

| 2.7  | Delay in a differential pair.                                                                             | 15 |

| 2.8  | Effect of random amplitude noise on jitter                                                                | 16 |

| 2.9  | a) Common source stage without Inductive Peaking. b) Common source stage                                  |    |

|      | with Inductive Peaking                                                                                    | 17 |

| 2.10 | Differential pair with active inductive load.                                                             | 18 |

| 2.11 | a) Active inductor. b) Small signals' model of an active inductor                                         | 18 |

| 2.12 | a) Frequency response of the normalized impedance of an active inductor                                   |    |

|      | (simplified). b) Frequency response of the normalized impedance of an active                              |    |

|      | inductor (complete)                                                                                       | 19 |

| 2.13 | Differential pair with Capacitive Degeneration.                                                           | 20 |

| 2.14 | a) Frequency response of the normalized equivalent transconductance, $G_m$ . b)                           |    |

|      | Frequency response of the voltage gain                                                                    | 21 |

| 2.15 | Gain stage with Negative Miller Capacitance.                                                              | 22 |

| 2.16 | Two-stage amplifier with negative miller capacitors.                                                      | 22 |

| 2.17 | AC half-circuit of a source-coupled differential pair.                                                    | 23 |

| 2.18 | Source-coupled differential pair with cascode transistors                                                 | 23 |

| 2.19 | Single-ended Cherry-Hooper amplifier                                                                      | 24 |

| 2.20 | Gilbert gain cell                                                                                         | 25 |

| 2.21 | Inversely scaled differential pairs (by a factor of <i>k</i> )                                            | 26 |

| 2.22 | $f_T$ Doubler                                                                                             | 27 |

| 2.23 | Input capacitance of $f_T$ Doubler                                                                        | 28 |

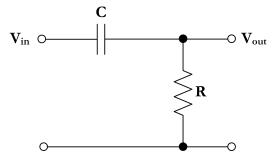

| 2.24 | AC coupling circuit.                                                                                      | 30 |

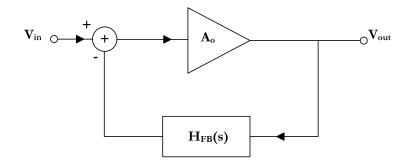

| 2.25 | DC offset cancelation loop.                                                       | 31 |

|------|-----------------------------------------------------------------------------------|----|

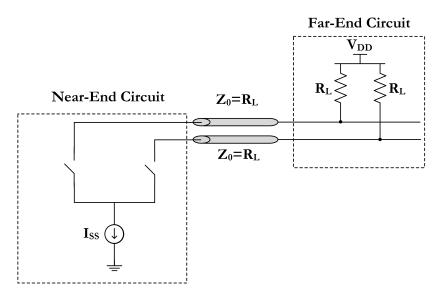

| 2.26 | "Open-drain" Output Buffer, transmission line and off-chip load                   | 32 |

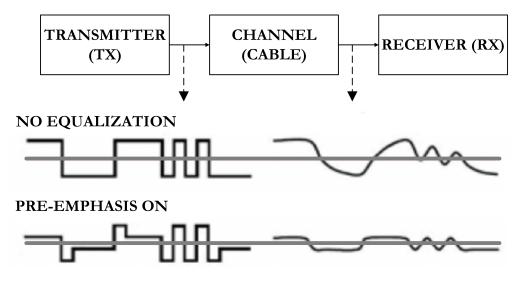

| 2.27 | Effect of low-pass line in an electrical signal and impact in ISI                 | 33 |

| 2.28 | Signal with and without Pre-emphasis                                              | 33 |

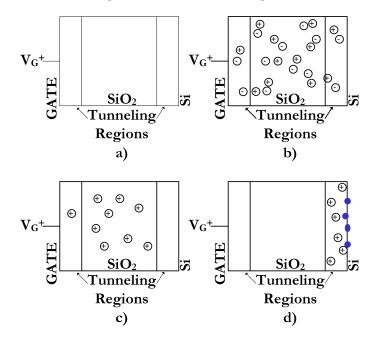

| 2.29 | Charge distribution in a gate oxide at three times after exposure to a pulse of   |    |

|      | irradiation                                                                       | 35 |

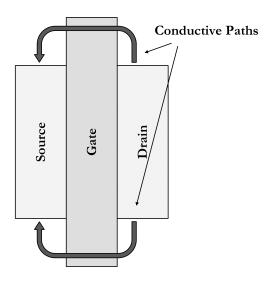

| 2.30 | Parasitic conductive paths                                                        | 37 |

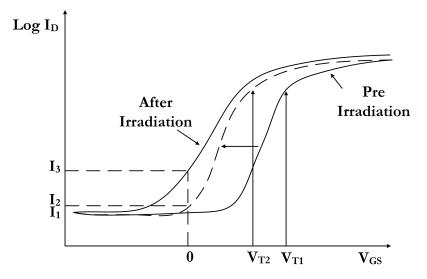

| 2.31 | Increase of the subthreshold current in a NMOS as consequence of the decrease     |    |

|      | of the effective threshold voltage                                                | 38 |

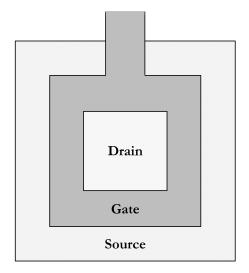

|      | MOSFET with an enclosed layout.                                                   | 38 |

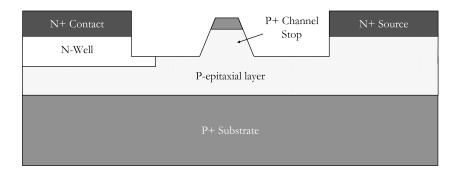

| 2.33 | Cross-section of a CMOS process with a p+ channel stop designed into the          |    |

|      | FOX isolation.                                                                    | 39 |

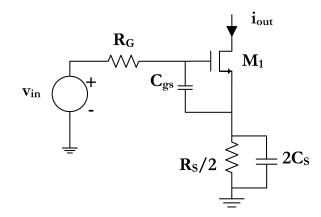

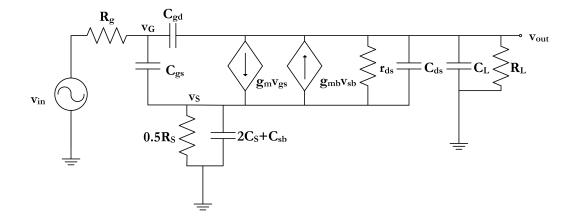

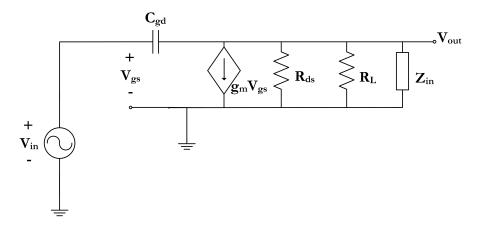

| 3.1  | Equivalent half-circuit of a capacitive degenerated differential pair             | 42 |

| 3.2  | Equivalent half-circuit of the load effect created by a capacitive degenerated    |    |

|      | differential pair.                                                                | 43 |

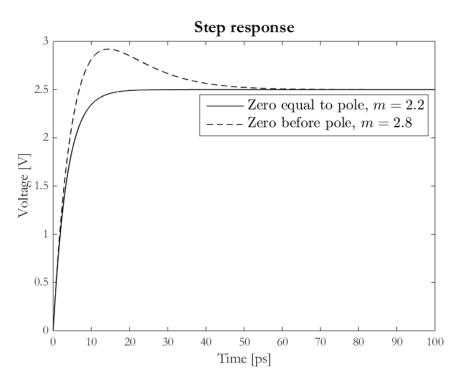

| 3.3  | Step responses of a capacitive degenerated differential pair as a function of the |    |

|      | transconductance's zero position.                                                 | 45 |

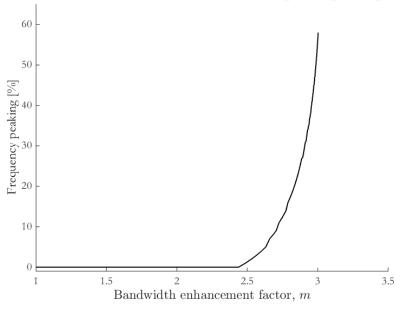

| 3.4  | Tradeoff between the bandwidth enhancement factor, <i>m</i> , and frequency peak- |    |

|      | ing                                                                               | 46 |

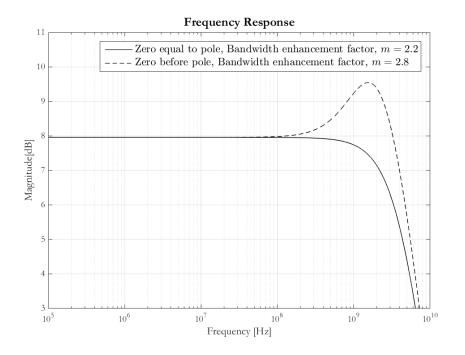

| 3.5  | Frequency response of a capacitive degenerated differential for two different     |    |

|      | positions of the transconductance's zero.                                         | 47 |

| 3.6  | Eye diagrams of the output signals of a capacitive degenerated differential       |    |

|      | pair as a function of the transconductance's zero position, with the zero: a)     |    |

|      | matching the dominant pole b) before the dominant pole.                           | 47 |

| 3.7  | Small signals' model for the equivalent half-circuit of capacitive degenerated    |    |

|      | differential pair.                                                                | 48 |

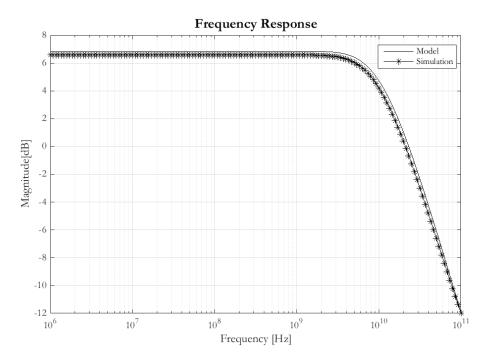

| 3.8  | Modeled and simulated frequency response of a capacitive degenerated differ-      |    |

|      | ential pair.                                                                      | 48 |

| 3.9  | Small signals' model of the equivalent half-circuit of a differential pair em-    |    |

|      | ploying NMC technique                                                             | 50 |

| 3.10 | Small signals' model of the equivalent half-circuit of a simple differential pair |    |

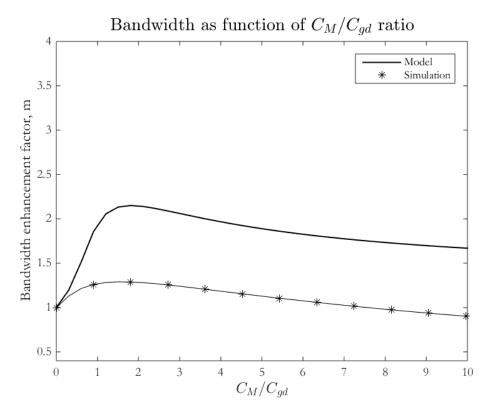

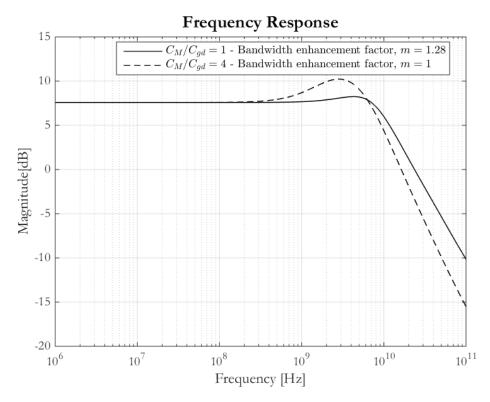

|      | loaded by a differential pair employing NMC                                       | 51 |

| 3.11 | Variation of a bandwidth enhancement factor, $m$ , as a function of the ratio     |    |

|      | $C_M/C_{gd}$                                                                      | 51 |

|      | Different frequency responses for different $C_M/C_{gd}$ ratios                   | 52 |

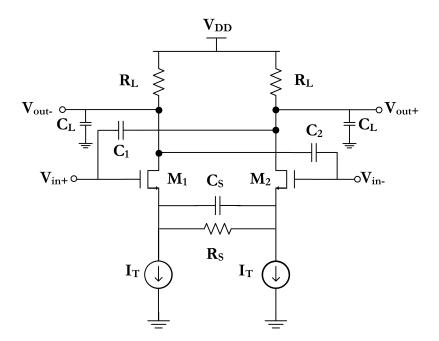

|      | Simplified schematic of each Limiting Amplifier's gain cell                       | 53 |

|      | Degeneration's capacitor implemented with a PMOS transistor                       | 54 |

|      | Degeneration's capacitors implemented with PMOS transistors                       | 54 |

|      | Crossed-coupled capacitors, $C_1$ and $C_2$ , implemented with PMOS transistors.  | 55 |

| 3.17 | Complete architecture of each Limiting Amplifier's gain cell                      | 56 |

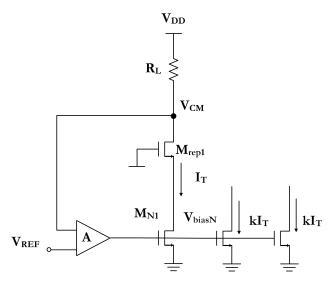

| 3.18 | Replica bias' architecture.                                                       | 57 |

|------|-----------------------------------------------------------------------------------|----|

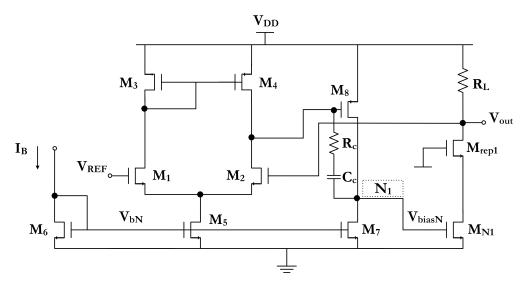

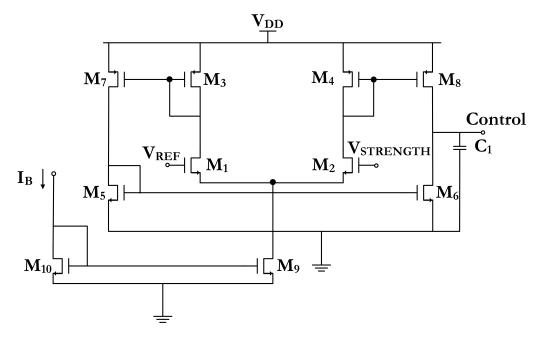

| 3.19 | Schematic of the replica bias' amplifier.                                         | 59 |

|      | Layout of the replica bias' amplifier.                                            | 60 |

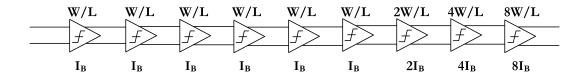

| 3.21 | Cascade of limiting stages and scaling factors                                    | 61 |

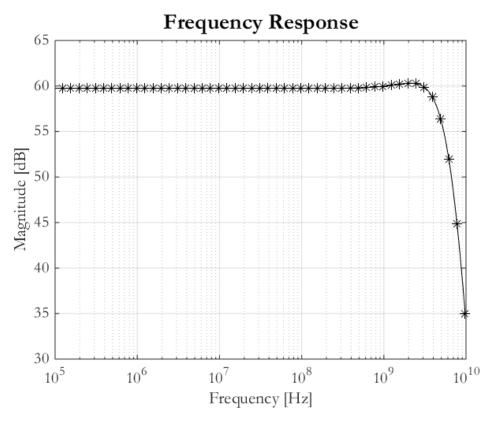

| 3.22 | Frequency response of the overall Limiting Amplifier.                             | 63 |

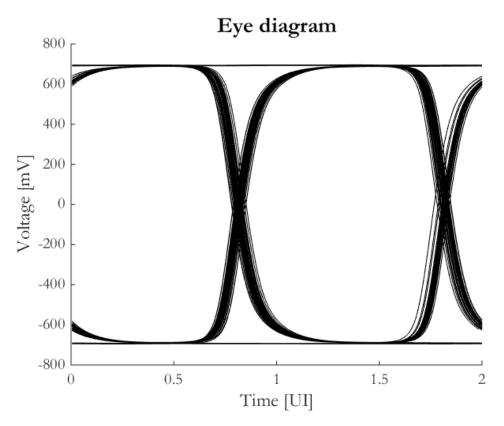

| 3.23 | Eye diagram of the last Limiting stage for an input PRBS at 5Gb/s for the         |    |

|      | minimum input signal's amplitude                                                  | 65 |

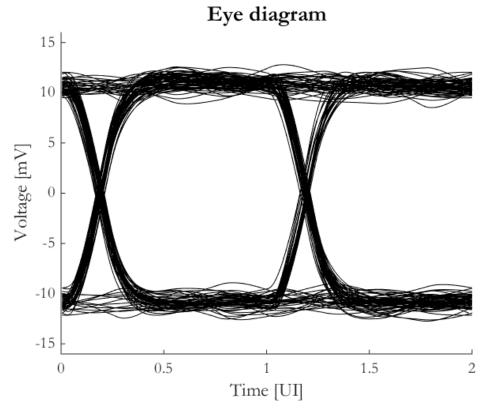

| 3.24 | Eye diagram of the first Limiting stage for an input PRBS at 5Gb/s for the        |    |

|      | minimum input signal's amplitude                                                  | 66 |

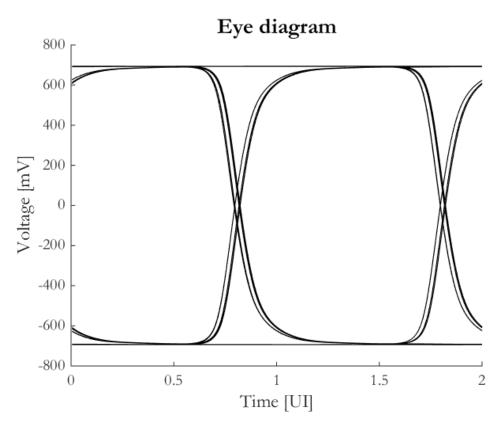

| 3.25 | Eye diagram of the last Limiting stage for an input PRBS at 5Gb/s for the         |    |

|      | maximum input signal's amplitude                                                  | 67 |

| 3.26 | RSSI's architecture.                                                              | 68 |

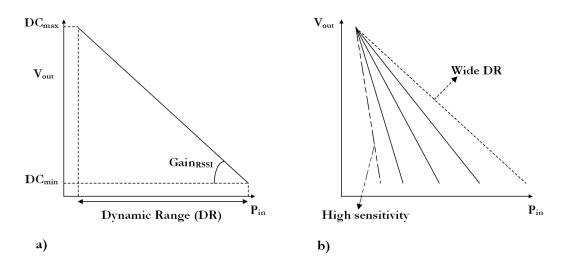

| 3.27 | Tradeoff between Dynamic Range and detection sensitivity                          | 69 |

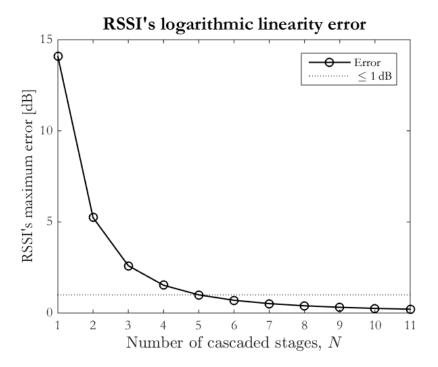

| 3.28 | RSSI's logarithmic linearity error as a function of the LA's number of cascaded   |    |

|      | stages                                                                            | 70 |

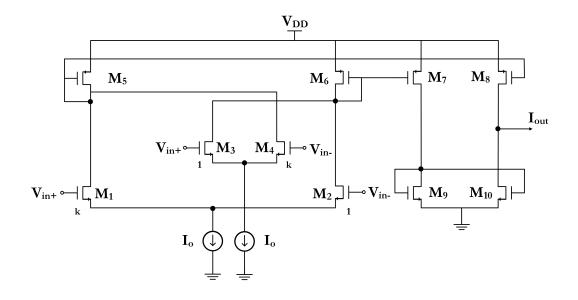

| 3.29 | FWR's architecture.                                                               | 71 |

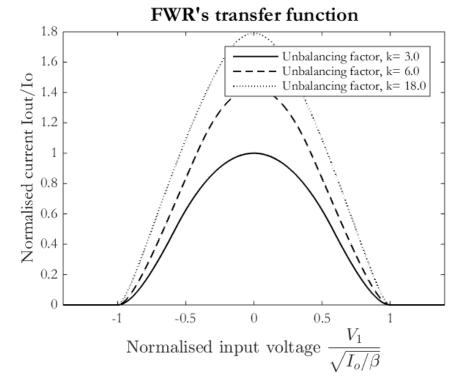

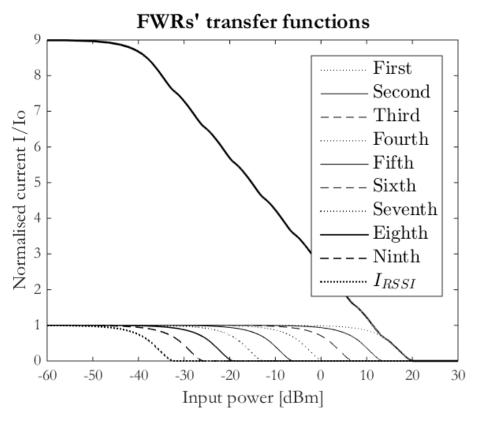

| 3.30 | FWR's transfer function for different values of the unbalancing factor, $k$       | 73 |

| 3.31 | Modeled RSSI's and FWRs' transfer functions                                       | 74 |

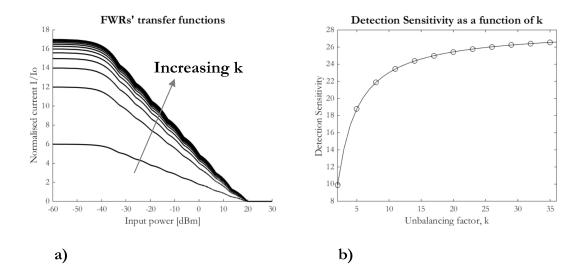

| 3.32 | a) FWR's transfer functions for different values of the unbalancing factor, $k$ . |    |

|      | b) Detection sensitivity as a function of the unbalancing factor, <i>k</i>        | 75 |

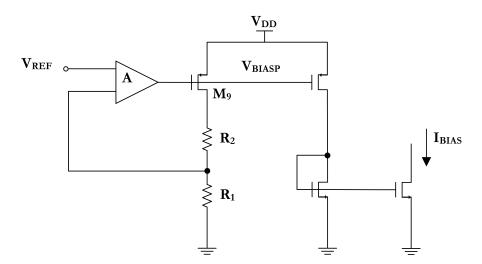

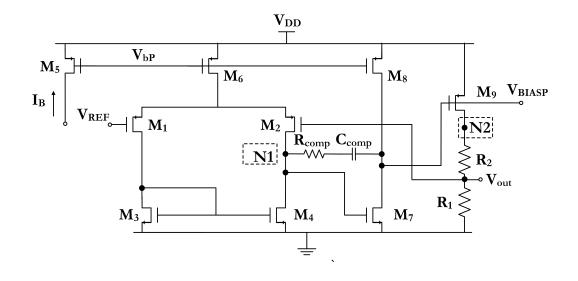

| 3.33 | RSSI's PVT independent bias circuit.                                              | 76 |

| 3.34 | RSSI's bias circuit amplifier.                                                    | 78 |

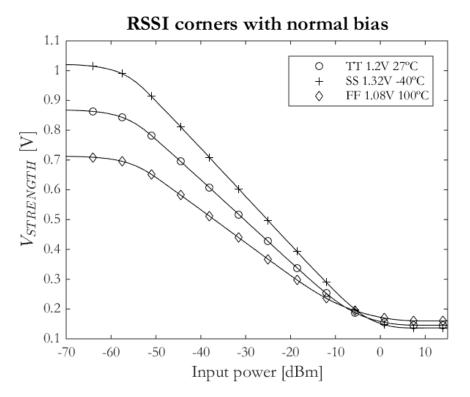

| 3.35 | Variation of the RSSI's transfer function across corners using a normal bias      |    |

|      | circuit                                                                           | 80 |

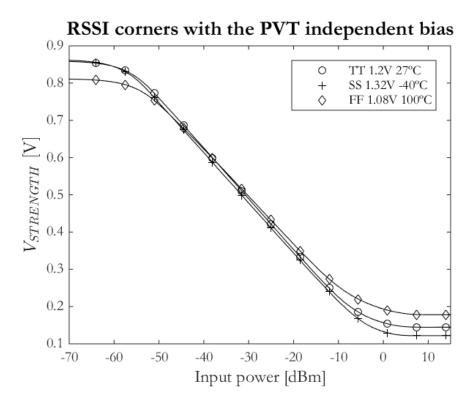

| 3.36 | Variation of the RSSI's transfer function across corners using the proposed       |    |

|      | PVT independent bias circuit.                                                     | 81 |

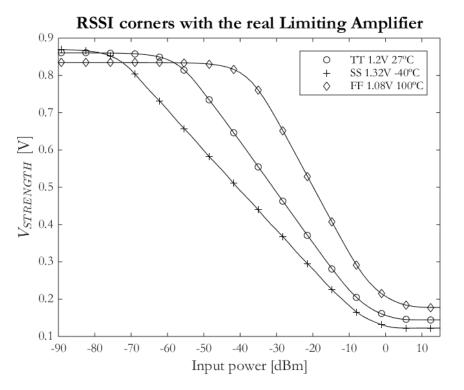

| 3.37 | Variation of the RSSI's transfer function across corners using the proposed       |    |

|      | PVT independent bias circuit with the real LA.                                    | 82 |

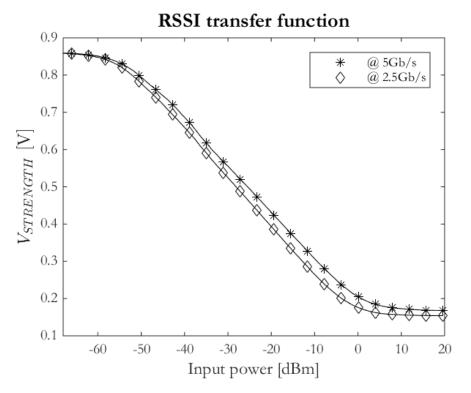

| 3.38 | RSSI's transfer function at 5 and 2.5Gb/s                                         | 83 |

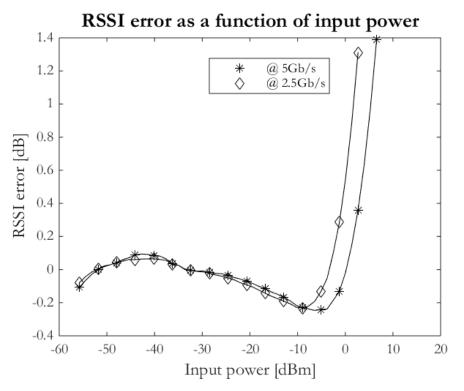

| 3.39 | RSSI's logarithmic error at 5 and 2.5Gb/s                                         | 84 |

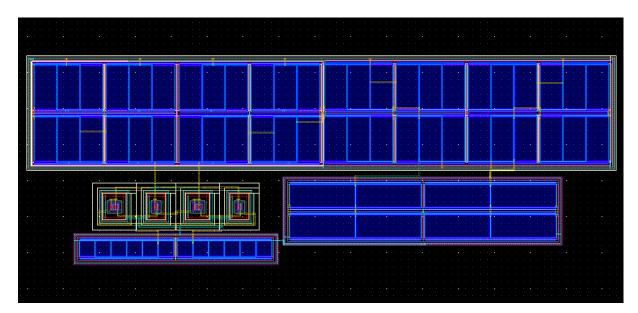

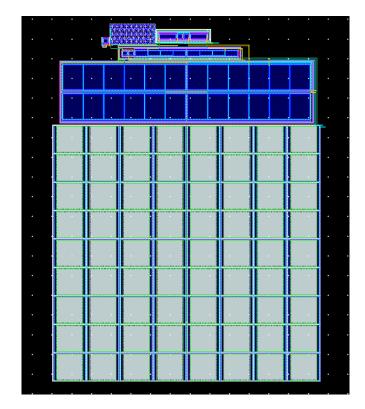

| 3.40 | Layout of the RSSI's FWR.                                                         | 84 |

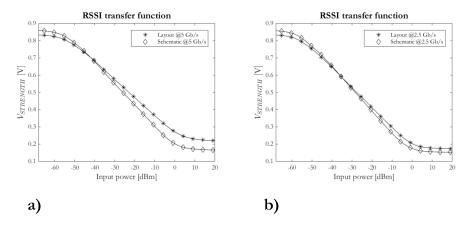

| 3.41 | RSSI's transfer function at a) 5Gb/s and b) 2.5Gb/s - layout vs schematic         | 85 |

| 3.42 | Squelch's working principle.                                                      | 87 |

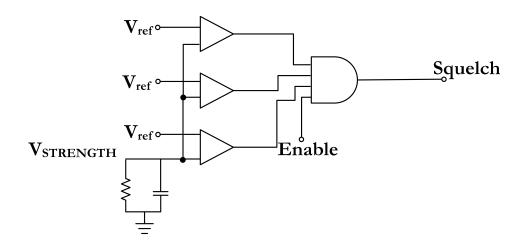

| 3.43 | Simplified Squelch's architecture using redundancy techniques                     | 88 |

| 3.44 | Squelch's comparator.                                                             | 89 |

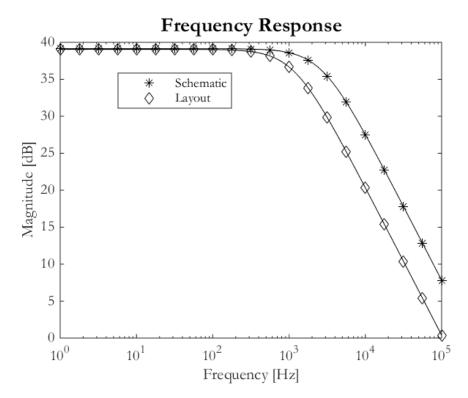

| 3.45 | Layout of the Squelch's comparator                                                | 91 |

| 3.46 | Frequency response of the Squelch's comparator - layout vs schematic              | 91 |

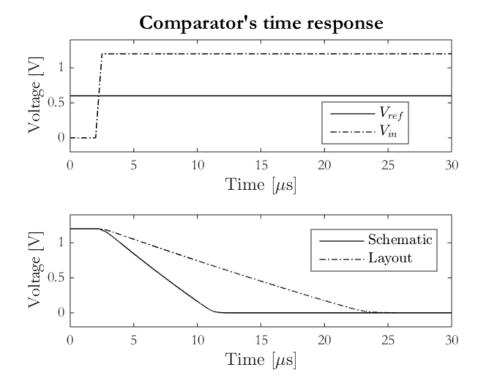

|      | Time response of the Squelch's comparator - layout vs schematic                   | 92 |

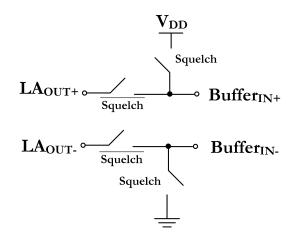

| 3.48 | Unbalancing of the Output Buffer.                                                 | 93 |

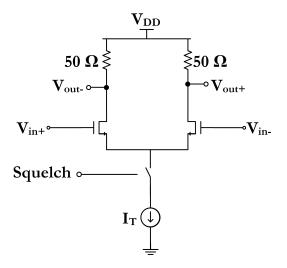

| 3.49 | Disconnection of the Output Buffer's current source.                              | 94 |

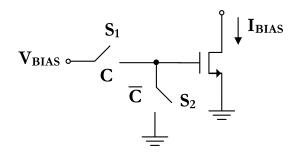

| 3.50 | Switches for the Output Buffer's bias current's control                           | 94 |

| 3.51 | Implementation of the switches for the Output Buffer's bias current's control.                    | 95  |

|------|---------------------------------------------------------------------------------------------------|-----|

| 3.52 | Squelch's transient simulations.                                                                  | 96  |

| 3.53 | Variability of the Squelch's input referred threshold due to the variations of                    |     |

|      | the RSSI's transfer function across corners                                                       | 97  |

| 3.54 | CML "open-drain" Output Buffer                                                                    | 98  |

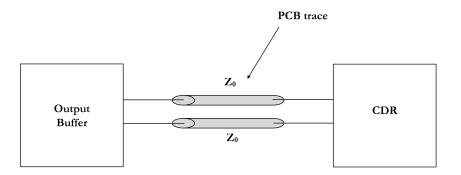

| 3.55 | PCB transmission line connecting the Output Buffer and the CDR                                    | 99  |

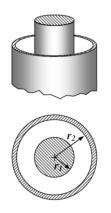

| 3.56 | Coaxial Cable.                                                                                    | 100 |

| 3.57 | T line with short load                                                                            | 101 |

| 3.58 | Matched T line.                                                                                   | 102 |

| 3.59 | Effects of package parasitics.                                                                    | 102 |

| 3.60 | Double-termination Output Buffer                                                                  | 104 |

| 3.61 | Simplified schematic of the Output Buffer with Pre-emphasis capability                            | 105 |

| 3.62 | High level Pre-emphasis scheme.                                                                   | 105 |

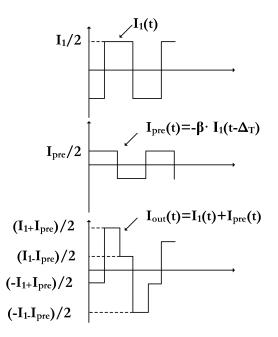

| 3.63 | Waveforms of the currents involved in the Pre-emphasis function                                   | 106 |

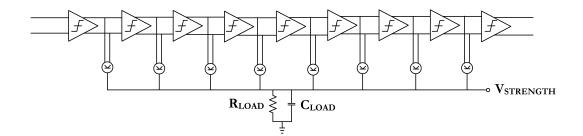

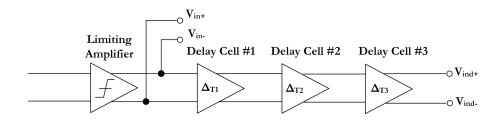

| 3.64 | Chain of delays for the Pre-emphasis circuit                                                      | 107 |

| 3.65 | Schematic of first and second delay cell.                                                         | 108 |

| 3.66 | PMOS switches for the first delay cell.                                                           | 108 |

| 3.67 | Schematic of the third delay cell.                                                                | 109 |

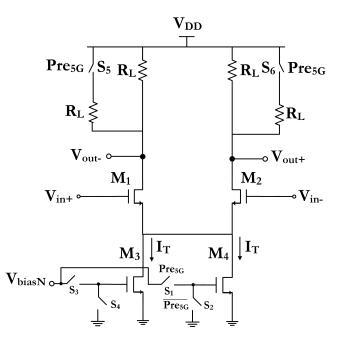

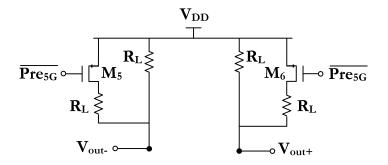

| 3.68 | Output buffer with tunable Pre-emphasis capability.                                               | 112 |

| 3.69 | Control logic used to generate the control signals for the main buffer and Pre-                   |     |

|      | emphasis' current sources.                                                                        | 113 |

| 3.70 | $Complete \ schematic \ of \ the \ Output \ Buffer \ with \ tunable \ Pre-emphasis \ capability.$ | 113 |

| 3.71 | Output buffer's differential output for a 2.5 Gb/s PRBS sequence at the input                     |     |

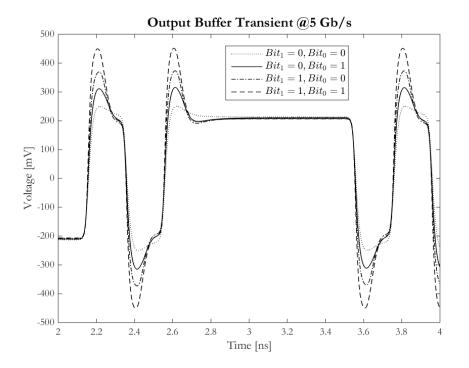

|      | of LA for different combination of the control bits ( $Pre_{5G} = 0$ V)                           | 115 |

| 3.72 | Output buffer's differential output for a 5 Gb/s PRBS sequence at the input of                    |     |

|      | LA for different combinations of the control bits ( $Pre_{5G} = 1.2$ V)                           | 116 |

| 3.73 | Electrical model of the package parasitics.                                                       | 116 |

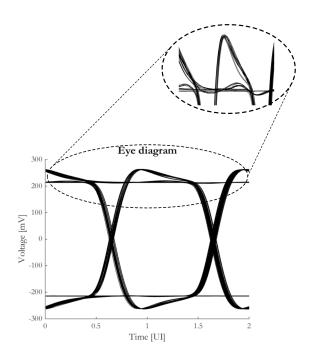

| 3.74 | Eye diagram of the Output Buffer considering the package parasitics for a 5                       |     |

|      | Gb/s PRBS sequence at the input of LA                                                             | 117 |

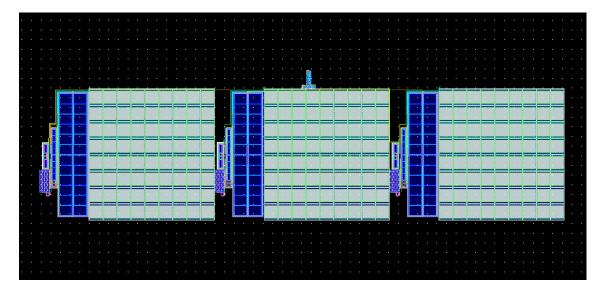

| A.1  | ,                                                                                                 | 127 |

| A.2  | Layout of the overall Squelch block.                                                              | 128 |

# LIST OF TABLES

| 2.1  | Comparison of bandwidth enhancement techniques                                | 29  |

|------|-------------------------------------------------------------------------------|-----|

| 2.2  | Comparison of referenced LAs/VGAs.                                            | 29  |

| 3.1  | Comparison of results obtained by the mathematical model vs simulation re-    |     |

|      | sults for a capacitive degenerated differential pair.                         | 48  |

| 3.2  | Variation of the frequency peaking against the TT process for two different   |     |

|      | implementations of the degeneration's capacitor, $C_S$                        | 55  |

| 3.3  | Components' dimensions of the Limiting Amplifier's gain cell                  | 56  |

| 3.4  | Components' dimensions of the replica bias' amplifier                         | 59  |

| 3.5  | Estimated and simulated results of the replica bias' amplifier                | 60  |

| 3.6  | Schematic vs layout simulation results of the replica bias' amplifier         | 61  |

| 3.7  | Simulation results of the overall Limiting Amplifier.                         | 63  |

| 3.8  | Limiting Amplifier's simulation results across the most relevant PVT corners. | 64  |

| 3.9  | Bandwidth enhancement factor for different broadband techniques               | 64  |

| 3.10 | Simulation results concerning the time response of the LA at 5Gb/s            | 65  |

| 3.11 | Components' dimensions of the RSSI                                            | 75  |

| 3.12 | Components' dimensions of the RSSI's bias circuit amplifier                   | 79  |

| 3.13 | Estimated and simulated results of the RSSI bias circuit's amplifier          | 79  |

| 3.14 | Variations on the detection sensitivity across corners using the proposed PVT |     |

|      | independent bias vs a normal bias circuit                                     | 81  |

| 3.15 | RSSI's simulation results for two different working frequencies               | 83  |

| 3.16 | Components' dimensions of the Squelch's comparator.                           | 89  |

| 3.17 | Estimated and simulated results of the Squelch's comparator                   | 90  |

| 3.18 | Component's dimensions of the switches for the Output Buffer's bias current's |     |

|      | control                                                                       | 95  |

| 3.19 | Variation of the Squelch's threshold across different corners                 | 97  |

| 3.20 | Components' dimensions of the first and second delay cell                     | 109 |

| 3.21 | Components' dimensions of the third delay cell.                               | 110 |

| 3.22 | Delays produced by the adjustable delay circuit as a function of the control  |     |

|      | signal <i>Pre</i> <sub>5G</sub>                                               | 110 |

| 3.23 | Main buffer and Pre-emphasis' currents according to the control bits          | 111 |

| 3.24 | Truth table of the control signals and correspondent currents as a fuction of  |     |

|------|--------------------------------------------------------------------------------|-----|

|      | the control bits for Squelch=0 V                                               | 112 |

| 3.25 | Components' dimensions of the Output Buffer with Pre-emphasis capability.      | 114 |

| 3.26 | Simulated Pre-emphasis' levels according to the control bits at 2.5 Gb/s       | 115 |

| 3.27 | Simulated Pre-emphasis' levels according to the control bits at 5 Gb/s         | 116 |

| 3.28 | Simulation results concerning the time response of the Output Buffer at 5Gb/s. | 117 |

| 3.29 | Output Buffer's simulation results - power consumption and Return Loss         | 118 |

|      |                                                                                |     |

| 4.1  | Comparison of referenced LAs/VGAs with this work                               | 120 |

# ACRONYMS

- **AC** Alternating Current.

- AM Amplitude Modulation.

- BER Bit Error Ratio.

- CDR Clock and Data Recovery.

- **CERN** Conseil Européen pour la Recherche Nucléaire.

- CML Current-Mode Logic.

- CMOS Complementary Metal-Oxide-Semiconductor.

- CMRR Common-Mode Rejection Ratio.

- DC Direct Current.

- DR Dynamic Range.

- FOX Field Oxides.

- FWR Full-Wave Rectifier.

- **GBW** Gain–Bandwidth Product.

- HBD Hardness-by-Design.

- **HEP** High Energy Physics.

- **ISI** Intersymbol Interference.

- JTOL Jitter Tolerance.

- KCL Kirchhoff's Current Law.

- KVL Kirchhoff's Voltage Law.

## ACRONYMS

| LA Limiting Amplifier.                                    |

|-----------------------------------------------------------|

| LHC Large Hadron Collider.                                |

| MOM Metal Oxide Metal.                                    |

| MOSFET Metal-Oxide Semiconductor Field-Effect Transistor. |

| NMC Negative Miller Capacitance.                          |

| NMOS Negative Channel Metal-Oxide Semiconductor.          |

| PCB Printed-Circuit Board.                                |

| <b>PM</b> Phase Modulation.                               |

| PMOS Positive Channel Metal-Oxide Semiconductor.          |

| PRBS Pseudo-Random Binary Sequence.                       |

| <b>PVT</b> Process Voltage and Temperature.               |

| RC Resistor-Capacitor.                                    |

| RSSI Received Signal Strength Indicator.                  |

| SEE Single-Event Effects.                                 |

| SNR Signal-to-Noise ratio.                                |

| SRF Self-Resonant Frequency.                              |

| TIA Transimpedance Amplifier.                             |

| TID Total Ionizing Dose.                                  |

| VGA Variable Gain Amplifier.                              |

|                                                           |

|                                                           |

|                                                           |

|                                                           |

## INTRODUCTION

This Chapter's purpose is to contextualize the Limiting Amplifier sub-block and its function in an Optical Receiver to be implemented in a 65 nm Complementary Metal-Oxide-Semiconductor (CMOS) technology with a 1.2 V power supply for a high-speed optical link (as well as other sub-blocks such as: a Received Signal Strength Indicator, a Squelch circuit and an Output Buffer with Pre-emphasis capability). It will be explained what motivated this project in the first place, and the main goals to be achieved during this work.

The European Organization for Nuclear Research, known as *Conseil Européen pour la Recherche Nucléaire* (CERN) performs experiences at the Large Hadron Collider (LHC), so the need for a way to efficiently transfer the huge amount of data generated by these experiences to the counting room is imminent. Due to the radioactive nature of these experiences the most practical way to do this is using optical fiber, since it has a high tolerance to radiation and is practically immune to magnetic fields and electromagnetic noise. Therefore, it is necessary to have a high speed radiation-tolerant Optical Receiver, and the most economical way to do it is having all the blocks embedded in the same Integrated Circuit (IC). Albeit there are many CMOS Optical Receivers in the market, they cannot be used in this particular situation since they are not radiation-hardened. This receiver requires a very large bandwidth in order to fulfill the data acquisition system requirements.

The core of the Optical Receiver consists of three major sub-blocks: the Photodiode and the corresponding bias circuit, the Transimpedance Amplifier and the respective Offset Cancelation block, and finally, the Limiting Amplifier. Fig 1.1 shows a simplified schematic of the Optical Receiver's architecture.

Without going into many details about the function and the design of each sub-block, a brief explanation will be given. The Photodiode is responsible for detecting the light

Figure 1.1: Simplified block diagram of a standard Optical Receiver.

signal in the fiber, working in the reverse bias region in order to maximize its sensitivity, which is made possible due to the existence of a biasing circuit (which includes a step up voltage converter to produce a 2 V power supply) that adjusts the voltage across the photodiode in order to maintain it in this region. The TIA converts the input current from the Photodiode into a voltage signal, and cancels the offset of the signal to avoid saturation in the following amplification stages. After that, the Limiting Amplifier provides additional voltage gain, boosting the signal swing in order to achieve a clear digital signal, so it can be properly detected by the Clock and Data Recovery (CDR).

### 1.1 Motivation

In order to conveniently transmit the data originated from the LHC experiments to the counting room, it is necessary to have a communication channel that allows for high data rates, and must consequently have a sufficiently large bandwidth. When a signal is propagating in an electrical line (e.g. coaxial cable) it will start with sharp rising and falling "edges" but, as the distance increases, these edges will be softened due to the loss-related distortion and dispersion. This phenomenon is illustrated in Fig. 1.2.

Figure 1.2: Softening of the edges in an electrical line - RC model for lossy line.

The "softening" of the edges makes precise extraction of timing information harder. In optical fibers, for the same communication distances this effect is not as noticeable, since the dispersion and loss is smaller than in electric wires [1]. This makes optical communication suited for higher data rates, which are necessary to fulfill the data acquisition system requirements for the LHC experiments.

There is also a major advantage that makes optical fiber the most efficient type of communication channel for this particular application. It can be used in environments with large Electromagnetic Interference and Radio-Frequency Interference which is the case of the surrounding environment of the LHC, where radiation is not the only source for disturbance or system failures: the electromagnetic environment in the tunnel and service areas is rich in interference sources [2]. Hence, the use of optical fiber implies the existence of an Optical Receiver, which consists of the blocks mentioned earlier plus an off-chip CDR circuit (which is not to be implemented in this project). Although there are many wideband Optical Receivers available in the market there is a need for a special circuit. Due to the beam interactions with residual gases, collimators or other equipment in the experiences, there is a lot of ionizing radiation with a broad energy spectrum. This ionization can permanently damage the electronic components by altering the device parameters. For example, it can change the value of the transistors' threshold voltages and leakage currents and, in the case of the Photodiode, it can brutally increase its Direct Current (DC) leakage current, leading to a decrease in the Photodiode bias voltage (due to high voltage drops in the biasing circuit). The permanent changes in the electronic devices caused by radiation are called Total Ionizing Dose (TID) effects. Additionally, radiation can also cause exceptional and isolated events. These are called Single-Event Effects (SEE), such as: Single-Event Upsets (SEUs), Single-Event Functional Interrupts (SEFIs), Single-Event Transients (SETs), and Single-Event Latchups (SELs) [3].

For these reasons, the associated electronic components need to be capable of sustaining high radiation doses  $(2 \text{ MGy}^1)$  [4] and survive in this environment. In order to use microelectronics in this kind of environment, it is mandatory to mitigate the radiation effects. This can be achieved by using the Hardness-by-Design (HBD) methodology, thus making the circuit radiation-hardened. HBD techniques can be done at the transistor level, the component level, and the system level, guarantying TID and SEE toleration.

These "special" conditions create the necessity for a more complex Optical Receiver with some particular design constraints, and singular specifications that make it different from the other products available in the market. This constitutes the main motivation for this investigation project.

<sup>&</sup>lt;sup>1</sup>The gray (symbol: Gy) is a derived unit of ionizing radiation dose in the International System of Units (SI). It is defined as the absorption of one joule of radiation energy per kilogram of matter.

In this context, the Limiting Amplifier appears as a fundamental block for the Optical Receiver's body. Its main function is to create a clear digital signal at a fixed swing (independent of the input voltage swing) that can be adequately detected by the CDR circuit. The correct operation of this block is of the utmost importance for the overall system performance, since it has to satisfy the input sensitivity of the attached Clock and Data Recovery circuit for proper data reconstruction. In other words, the amplitude of the LA's output signal has to be greater than this value (CDR's input sensitivity), and the rise and fall time both have to allow correct detection of the zero crossings. So, the incorrect or poor behaviour/operation of the Limiting Amplifier can negatively impact the system performance, increasing the Bit Error Ratio (BER)<sup>2</sup>, therefore causing incorrect bit detections [5], Chapter 7.

### **1.2 Thesis Organization**

This thesis is organized in four Chapters. Them being: Introduction, Literature's Review, Implementation in CMOS and Conclusions and Future Work.

The first one (namely this one) contextualizes the overall Optical Receiver and its necessity. It briefly explains why optical communication is suited for this application. It also defines the functions and responsibilities of each core block in the overall Optical Receiver.

The second Chapter is the Literature's Review and its purpose is to study and understand the major issues and constrains when designing a Limiting Amplifier. It also presents some possible techniques used to overcome those issues - bandwidth enhancement techniques. Practical examples of application of this techniques are provided as well as a comparision chart. In addition to that, each of the other blocks and their tasks are shortly discussed. Furthermore, and due to the environment in which the Optical Receiver will work, the effects of radiation in modern CMOS process are also addressed, especially the TID effects.

The third Chapter is the Implementation in CMOS and it covers the design and implementation of all four blocks. It is devided in four sections, one for each block. Which one contains a theoretical analysis of the block, - for some blocks mathematical models were also developed and presented, as well as a comparison with real simulation results - the schematics of all the master circuits used and its components' dimensions, the relevant electric simulations regarding that particular block and also the layout of some integrant sub-blocks.

The last Chapter presents the most relevant conclusions regarding each Chapter and the four blocks designed. The aspects that could have been improved or made differently are also addressed in this Chapter.

<sup>&</sup>lt;sup>2</sup>Bit Error Ratio is defined as  $\frac{\#bit\,errors}{\#bits\,received}$

Lasty, the Appendix includes some layouts that were executed and that are not going to be discussed in detail during this thesis.

Снартек

# LITERATURE'S REVIEW

### 2.1 Limiting Amplifier

The current signal originated in the Photodiode is converted into a voltage signal by the TIA. However, this signal typically suffers from a low output swing (only a few milivolts for the minimum input current -  $10 \,\mu$ A) which is clearly not sufficient to satisfy the sensitivity of the CDR. Therefore, the Limiting Amplifier or Limiter<sup>1</sup> has to boost the signal's swing, bringing it to logic levels with an amplitude of around 500 mV. Then, the CDR receives this boosted signal and decides the binary nature of the voltage, and thusly of the input optical signal.

LAs have to provide high voltage gain and a large bandwidth. An open-loop configuration of a cascade of broadband stages is typically used to fulfil these requirements. Altough, sometimes, the use of some broadband techniques is required, in order to increase the bandwidth of each stage (since in a cascade of broadband stages the bandwidth decreases with the number of stages limiting the overall LA bandwidth). This subject is going to discussed in more detail, since the last amplification stages work in large signal mode, invalidating the concept of small-signal bandwidth (the large-signal speed in a cascade of gain stages is limited by the speed of a single gate, and not by the complete cascade). Sometimes the LA also incorporates an Offset Cancelation block so is does not saturate due to the DC component, avoiding a premature detection of the signal.

LAs must often drive off-chip loads, so it is necessary to use an Output Buffer for impedance matching<sup>2</sup> (typically 50  $\Omega$ ) while providing large currents and reasonable

<sup>&</sup>lt;sup>1</sup>In optical communications it is commonly known as a Limiting Amplifier, in RF community it is called a Limiter.

<sup>&</sup>lt;sup>2</sup>Impedance matching is the practice of designing the input impedance of an electrical load, or the output impedance of its corresponding signal source to maximize the power transfer, or minimize signal reflection from the load.

output swings to the load.

Automatic Gain Control (AGC) is another method that allows to keep constant signal amplitude independent of the input swing. However, compared with LAs, Automatic Gain Control needs more setting-up time, more complex analog circuits and larger chip area. For these reasons, Limiting Amplifiers are more commonly used for wideband Optical Receivers.

#### 2.1.1 Performance Parameters

Let us now discuss the main performance parameters that must be taken into account when designing a Litimiting Amplifier for an Optical Receiver. As mentioned before, the LA plays an important role on the Optical Receiver, allowing for the correct detection of the signal, and so it must satisfy the demanded requirements.

#### 2.1.1.1 Bandwidth

Limiting Amplifiers are designed to have greater bandwidth than the TIAs (a common value is  $1.5B_{TIA}$ ), because they need to be capable of clipping the signal provenient of the TIA, and generate a signal with high slew rate and near to zero transition times. Typically, a Limiting Amplifier's bandwidth is designed to be equal to the data rate, which implies that the bandwidth of each stage (LAs are usually built as a cascade of gain cells) has to be bigger than this value. If the LA's bandwidth were to be lower than the signal's bandwidth, this would affect the edge timing and amplitude at the sampling instant, lowering the eye opening and contributing to Intersymbol Interference (ISI) [5]. This effect is illustrated in Fig. 2.1.

Figure 2.1: Eye diagram for two different bandwidths and resulting ISI. Adapted from [5], Chapter 3.

An eye diagram is a useful tool for understanding signal impairments in the physical layer of high-speed digital data systems, verifying transmitter output compliance, and revealing the amplitude and time distortion elements that degrade the BER for diagnostic purposes. By taking high-bandwidth instantaneous samples of a high-speed digital signal, an eye diagram is the sum of samples from superimposing the 1s, 0s, and corresponding transition measurements [6]. The data rate is used to trigger the horizontal sweep, and represented in UI, which stands for Unit Interval and is defined as the minimum time interval between condition changes of a data transmission signal, also known as the pulse time or symbol duration time. In this context, the eye opening corresponds to one bit period and is typically called the UI width of the eye diagram.

#### 2.1.1.2 Noise

The referred input noise is relevant in Limiting Amplifiers for three main reasons. Firstly, the large bandwidth of these amplifiers yields a large integrated noise. Secondly, the design of TIAs with high transimpedance gain is more difficult at high speeds, making the noise contribution of the LA more significant. Lastly, the amplitude noise in the Limiting Amplifiers is modulated as phase errors (due to the non-linear behavior of this amplifier) causing jitter noise (this will be discussed in more detail in Section 2.1.3) and consequently impacting the signal detection. The amplitude noise can also affect the vertical opening of the eye diagram, reducing its quality factor, and therefore increasing the BER. The smaller the eye width at the sampling instant, the bigger the probability of a 1 bit to mistaken by a 0 and vice-versa.

#### 2.1.1.3 Gain

The first amplifier stage (assuming a cascade of gain stages) must employ a large gain, in order to minimize the noise contribution of the following stages. If the TIA's noise is already large sometimes a downscaling technique is used, as a way to reduce the noise and the loading effect.

#### 2.1.1.4 Drive Capability

The Output Buffer is responsible for driving the output loads, delivering large currents to off-chip  $50 \Omega$  loads. These large currents force the transistors of the Output Buffer to have large dimensions, leading to large gate capacitances. Therefore, the buffer will exhibit a high input capacitance heavilly loading the preceding stage, possibly becoming the bottleneck for the bandwidth in the communication channel. This means that the last gain stage has to be able to drive a large capacitive load, while mantaining a wide bandwidth.

#### 2.1.1.5 Jitter

Jitter is one of the most important performance parameters in Limiting Amplifiers. Due to the non-linear behaviour of the last LA's stages (working in large signal operation), the amplitude variations (such as amplitude noise) are modulated as time shifts, resulting in an Amplitude Modulation (AM)-Phase Modulation (PM) conversion. This causes a deviation of the zero crossings from the ideal position, which is defined as jitter.

#### 2.1.1.6 Offset Voltage

Typically, an offset cancellation circuit is added to the first amplifying stages to prevent the offset (due to the device mismatch) from saturating the amplifier, thusly preventing incorrect signal detection.

#### 2.1.2 Cascade of Gain Stages

Let us consider a simple open-loop configuration where N broadband gain stages are placed in cascade in order to provide large output swing and large voltage gain. Each amplifier block can be seen as an ideal voltage amplifier with gain  $A_0$  followed by an Resistor–Capacitor (RC) circuit (composed by an output resistor  $R_{out}$  and a load capacitor,  $C_L$ ). Such an architecture is depicted in Fig. 2.2. It is important to understand that this model only provides a small signals' analysis of the Limiting Amplifier, which is not enough to understand its behaviour (the saturation effect is not taken into consideration) and it is necessary to study the large-signal operation of the Limiting Amplifier, since the last stages of amplification tend to work in this mode of operation (mostly when the input current is above the minimum value).

Figure 2.2: Simplified small signals' model of a cascade of two gain stages.

The corresponding transfer function, for a cascade of two stages, is given by expression 2.1.

$$H(s) = \left(\frac{A_0}{1 + \frac{s}{\omega_0}}\right)^2 \tag{2.1}$$

where  $\omega_0 = (R_{out}C_L)^{-1}$  is the frequency (in rad/s) of the poles and corresponds to the -3dB<sup>3</sup> bandwidth of each amplification stage. One can assume that the -3dB bandwidth of the system is a reasonable measure of its speed (and consequently, of the maximum bit rate). Replacing  $s = j\omega_{-3dB}$  in expression 2.1 and solving for  $\omega_{-3dB}$ :

$$\left| \left( \frac{A_0}{1 + \frac{\omega_{-3dB}}{\omega_0}} \right)^2 \right| = \frac{A_0^2}{2} \Leftrightarrow \left( \frac{A_0}{\sqrt{1 + \left(\frac{\omega_{-3dB}}{\omega_0}\right)^2}} \right)^2 = \frac{A_0^2}{2}$$

(2.2)

The -3dB bandwidth of the system,  $\omega_{-3dB}$ , is given by expression 2.3.

$$\omega_{-3dB} = \omega_0 \sqrt{\sqrt{2} - 1} \tag{2.3}$$

By scaling this logic to the N identical stages is possible to obtain a generic expression of the -3dB bandwidth of the system as a function of the number of stages, given by expression 2.4.

$$\omega_{-3dB} = \omega_0 \sqrt{\sqrt[N]{2} - 1} \tag{2.4}$$

Fig. 2.3 illustrates the ratio between the bandwidth of each stage, and the total bandwidth as a function of the number of cascaded stages. In other words, how large each stage's bandwidth has to be, in order to achieve a determinated value for the overall system's bandwidth.

One can see that, beyond 5 cascaded stages, the bandwidth required by an individual stage to achieve a given system's bandwidth is almost 3 times bigger, suggesting that it may be unpractical to build a Limiting Amplifier with more than 5 stages (depending on the gain specifications). Analyzing expression 2.4 it is possible to conclude that, in order to have a given system bandwidth, each stage of amplification must accomplish a larger bandwidth (e.g., for N = 3 the bandwidth of each stage has to be almost twice the overall bandwidth).

The DC gain of the cascade can be defined as  $A_{tot} = A_0^N$  (where  $A_0$  is the gain of each stage, considering equal gain for all the stages) which means that it may be useful to to distribute the gain over a large number of stages. On the other hand, when using low gain in the first stages (as a way to maximize the bandwidth) the last stages accumulate all the noise, resulting in an increased Signal-to-Noise ratio (SNR).

<sup>&</sup>lt;sup>3</sup>The -3dB bandwidth is defined as the separation between zero frequency - where the amplitude spectrum attains its peak value - and the positive frequency at which the amplitude spectrum drops to  $\frac{1}{\sqrt{2}}$  of its peak value. Or, alternately, drops to half of its peak power.

Figure 2.3: Ratio  $\frac{\omega_0}{\omega_{-3dB}}$  as a function of the number of cascaded stages, *N*.

There is a clear tradeoff between gain and bandwidth, if each stage of amplification has a small gain and a very large bandwidth, then N has to be large enough to fulfil both the overall gain specifications,  $A_{tot}$ , and the bandwidth requirements at the same time. This hints that there is an optimum value for N (for a specific system gain,  $A_{tot}$ ) that allows the maximization of the overall system bandwidth. Let us define  $B = A_0\omega_0$ as the Gain–Bandwidth Product (GBW) which is considered to be constant for a certain technology (for a given power consumption). So, for N stages  $A_{tot} = \left(\frac{B}{\omega_0}\right)^N$  and  $\omega_0 = \frac{B}{\sqrt[N]{A_{tot}}}$ . Replacing these parameters in expression 2.4, is possible to obtain:

$$\omega_{-3dB} = B \frac{\sqrt{\sqrt[N]{2} - 1}}{\sqrt[N]{A_{tot}}}$$

(2.5)

As demonstrated in [7], Chapter 5, the optimal value the number of cascaded stages,  $N_{opt}$ , is given by:

$$N_{opt} = 2\ln A_{tot} \tag{2.6}$$

One should note that this value is independent from the GBW and of the technology for that matter. The optimum gain per stage is given by  $A_0 = \sqrt{e}$  as derived in [5], Chapter 7.

Fig. 2.4 shows the evolution of the normalized bandwidth  $\frac{\omega_{-3dB}}{B}$  as a function of N for two different system gains,  $A_{tot} = 100$  and  $A_{tot} = 200$ . For  $A_{tot} = 100$  the maximum bandwidth is achieved for N = 9 and for  $A_{tot} = 200$  for N = 10. There is a common result for both graphics: for  $N \ge 6$  the increase in the bandwidth is not significant (smaller than 10% in both cases). This is the main reason why typically, amplifiers with more than 5 stages are not implemented (also because low gain stages contribute to more noise in the latter stages). Let us also define  $\omega_{-3dB}$  as  $2\pi R_b$ , where  $R_b$  denotes the bit rate. From the graph in Fig. 2.4 we see that the maximum bandwidth is of approximately 0.17B (for  $A_{tot} = 100$ ) and 0.16B (for  $A_{tot} = 200$ ) which implies that B has to be greater than  $2\pi \times (6R_b)$  (approximately for both cases). But, as mentioned before, this value does not need to be as large, because the latter stages have larger input swings and, for that reason, the Limiting Amplifier works in large-signal mode. In other words, when the input signal's amplitude is sufficiently large, one branch of the circuit is OFF while the other carries the total current, experiencing a fully switched state. In this mode of operation the small signals' analysis is not valid. Note: a differential topology is assumed in further calculations.

Figure 2.4: Normalized bandwidth as a function of the number of cascaded stages for  $A_{tot} = 100$  and  $A_{tot} = 200$ .

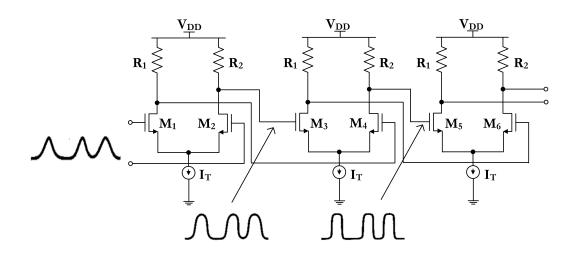

This means that each LA's stage can work in two distinct operation regimes: one is a linear region where both transistors are ON and can be defined by the small signals' model of the circuit, and a non-linear region or saturation regime where one of the transistors is OFF and the other one drives all the current, where a small signals' analysis cannot be applied. Fig. 2.5 illustrates this effect in a cascade of differential pairs, manifesting itself strongly in the third stage.

# CHAPTER 2. LITERATURE'S REVIEW

Due to the existence of non-linear behaviour, and the fact that one transistor will completely steer all the tail current  $I_T$ , the last two stages experience different zero crossing time instants. This proves that the small signals' model is not valid in this regime of operation.

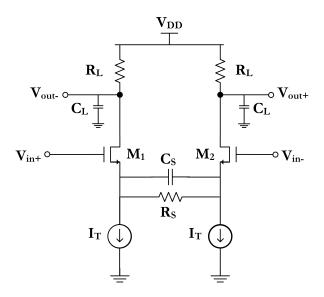

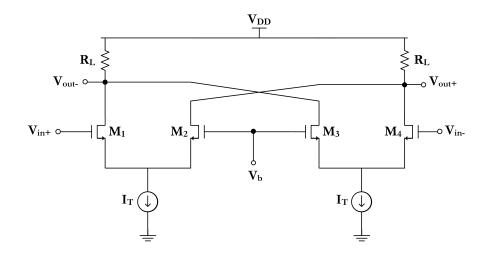

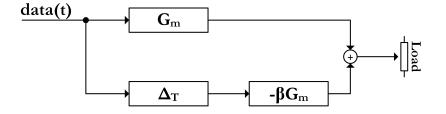

Figure 2.5: Non-linear behavior in a cascade of differential pairs. Adapted from [7], Chapter 5.

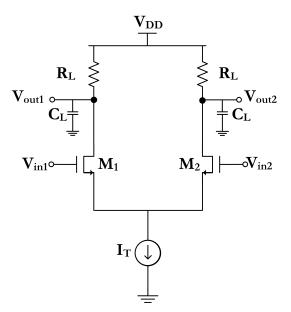

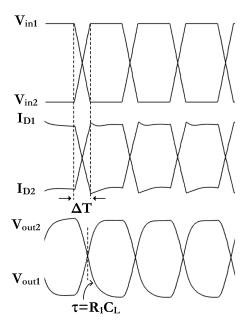

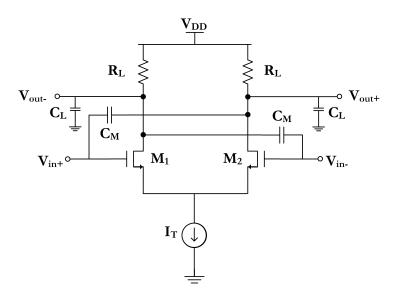

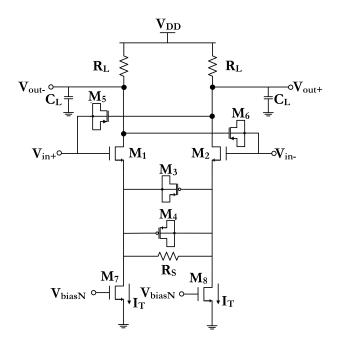

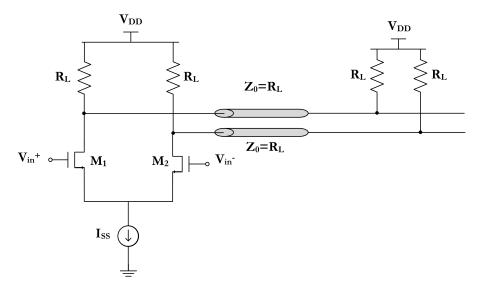

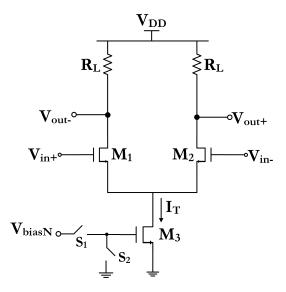

Let's consider a simple differential pair as represented in Fig. 2.6. Now, let us consider that  $V_{in1}$  and  $V_{in2}$  are large enough, and that the circuit displays a very large transconductance in equilibrium, so that it will work in large signal operation even around the zero crossing times of the input signal (defined by  $\Delta T$ ). As a consequence,  $M_1$  and  $M_2$  will be able to drive the tail current,  $I_T$ , during  $\Delta T$  creating a "sharper" signal. However, the speed of the output signal is limited by a time constant  $\tau = R_1C_1$  creating a delay on the time response. The input signals,  $V_{in1}$  and  $V_{in2}$ , as well as the drain currents of  $M_1$  and  $M_2$  ( $I_{D1}$  and  $I_{D2}$ ), and the output voltages ( $V_{out1}$  and  $V_{out2}$ ) are represented in Fig. 2.7.

This means that, in a cascade of identical stages (assuming of course, a differential architecture), when one amplifier saturates, the rise and fall times of the output signal are limited only by its time constant, and what occurs in previous stages does not influence the rise and fall times. In other words, the speed is bound only by one stage, similar to what happens in a cascade of digital gates [5], Chapter 3.

Figure 2.6: Differential pair.

Figure 2.7: Delay in a differential pair. Adapted from [7], Chapter 5.

# 2.1.3 AM/PM Conversion

There is also an interesting phenomenon illustrated in Fig. 2.7. There is an AM to PM conversion. The amplitude variations are being converted to a time delay, which is equivalent to a phase error (this effect is due to the saturation of the differential pair which resembles a non-linear low-pass circuit). Observing Fig. 2.7, one can see that the drain currents  $I_{D1}$  and  $I_{D2}$  cross the zero at the same time as the input signals. But the output voltages are experiencing a delay in the zero crossing instant, when compared to the input waves. Although the currents do not suffer from phase modulation, the variation of the input signal's amplitude (assuming a sinusoidal wave) passing through a frequency-dependent load (RC circuit) causes phase deviation in the first and third harmonics of the output voltage [7], Chapter 5.

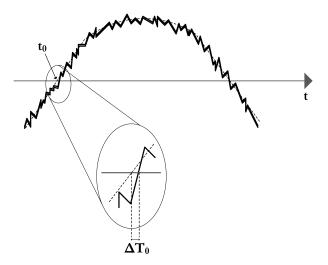

This effect can prove itself really harmful when the input signal contains random amplitude noise, causing the output signal to have random shifts in its zero crossings leading to excessive jitter noise. Fig. 2.8 illustrates the contribution of the amplitude noise in the unwanted phase errors, where the amplitude noise causes a delay,  $\Delta T_0$ , from the ideal zero crossing instant,  $t_0$ . Jitter plays an important role for the correct operation of the Clock and Data Recovery circuit. The total amount of jitter that the CDR can tolerate before the synchronization in lost (meaning, before the maximum BER is exceeded) is called Jitter Tolerance (JTOL).

Figure 2.8: Effect of random amplitude noise on jitter. Adapted from [7], Chapter 2.

# 2.1.4 Broadband Techniques

Sometimes a cascade of simple differential pairs with resistive loads is not enough to satisfy the system's stringent bandwidth requirements, resulting in the need for some bandwidth enhancement techniques. In this Chapter, the state of the art of these techniques and architectures will be discussed, as well as both their advantages and disadvantages.

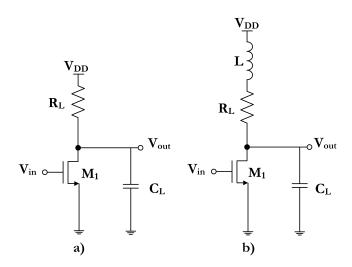

# 2.1.4.1 Inductive Peaking

The bandwidth of a gain stage is always bounded by the capacitive load, usually at the output node, that along with  $R_L$  consists in a large time constant. For a simple common-source stage, as illustrated in Fig. 2.9 a), the pole at the output is defined by  $\omega_0 = \frac{1}{R_L C_L}$ . It is possible to include an inductor at the output node, Fig 2.9 b), in order to partially cancel the load capacitance, and consequently extend the bandwidth.

Figure 2.9: a) Common source stage without Inductive Peaking. b) Common source stage with Inductive Peaking.

However, implementing an inductor in an integrated circuit can be a challenging task. On-chip inductors have an higher quality factor (Q), low noise and low voltage headroom consumption, albeit occupying a large area and leading to more parasitic capacitances. Furthermore, it is usually difficult to realize a spiral inductor with a high inductance but keeping the Self-Resonant Frequency (SRF)<sup>4</sup>, well outside the pass-band at the same time [8].

The inductive load can be done by on-chip spiral inductors (passive inductors) [9], conventional active inductors [10], [8], [4] and conventional active inductors using a voltage boosting technique [11].

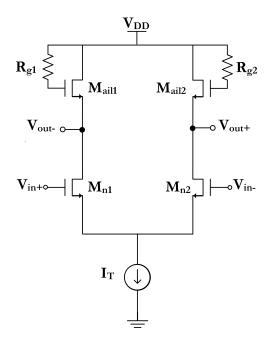

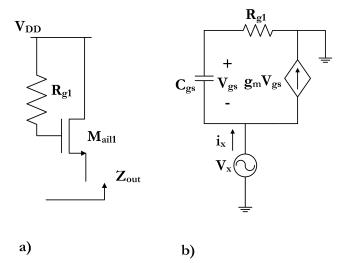

When chip area is an important factor, inductors can be implemented by active devices, having a lower Q but being able to work at higher frequencies. Active inductors require a large voltage headroom which can make its implementation very hard for low supply voltages. Reference [8] presents a differential topology with inductive loads in every LA stage, known as shunt peaking. This architecture is presented in Fig. 2.10. In this topology the active inductors are implemented by the transistor and resistor pairs:  $[M_{ail1}, R_{g1}]$  and  $[M_{ail2}, R_{g2}]$ .

<sup>&</sup>lt;sup>4</sup>At frequencies below the SRF, the model appears to be inductive; at frequencies above the SRF it appears to be capacitive and at the SRF it is resistive.

Figure 2.10: Differential pair with active inductive load. Adapted from [8].

The active inductor circuit is represented in Fig. 2.11 a). Fig. 2.11 b) represents the simplified equivalent small signals' model (neglecting the body effect, the gain-drain and bulk-source capacitance, and channel-length modulation). Applying Kirchhoff's Current Law (KCL) to the node  $V_x$  in Fig. 2.11 b) and solving for  $V_x$  it is possible to calculate the impedance seen from the source of the transistor by doing  $Z_{out}(s) = \frac{V_x}{t_x}$ :

$$Z_{out}(s) = \frac{R_{g1}C_{gs} + 1}{g_m + C_{gs}s}$$

(2.7)

Figure 2.11: a) Active inductor. b) Small signals' model of an active inductor.

The frequency response of the equivalent normalized impedance is represented in Fig. 2.12 a). It is possible to see that the frequency behaviour almost equals the one of a passive inductor - except for the existence of a pole. The reader should note that neglecting the effect of the other parasitic capacitances and the body effect eliminates the existence of a second pole, that would cause a decrease in the impedance at higher frequencies, as depicted in Fig. 2.12 b).

Figure 2.12: a) Frequency response of the normalized impedance of an active inductor (simplified). b) Frequency response of the normalized impedance of an active inductor (complete).

Reference [8] shows that it is possible to obtain a flat frequency response for the shunt peaking amplifier, as well as an increase of about 70% in the bandwidth before the peaking occurs. Another advantage of this particular topology is that the DC gain exhibits an extremely weak dependence on process, temperature and bias, because the ratio of the Negative Channel Metal-Oxide Semiconductor (NMOS) transistors  $M_{n1}$  and  $M_{ail1}$  determines the gain.

A different topology for the gain cell is presented in [10]. The active inductor is implemented by a simple high-Q two-transistor but, instead of being connected in series - like it is commonly done with a Positive Channel Metal-Oxide Semiconductor (PMOS) active load - it is connected at the output node supressing the load capacitance effect, therefore increasing the bandwidth. The peculiarity of this circuit is that transistors that implement the inductors are biased using a controlled voltage which allows to tune the inductance by changing this parameter. Hence, obtaining different frequency responses for different values of the biasing voltage without degenerating the voltage headroom of the active inductor [10]. This gain cell was used in a fully differential Limiting Amplifier for an Optical Receiver implemented in a  $0.18 \,\mu$ m CMOS technology.

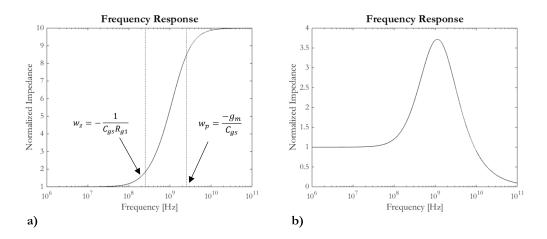

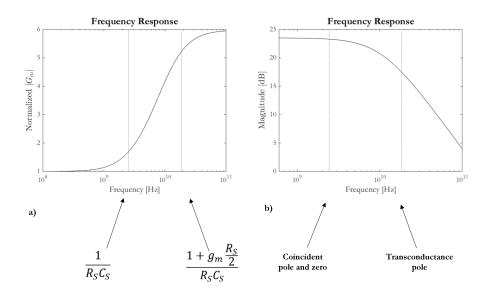

# 2.1.4.2 Capacitive Degeneration

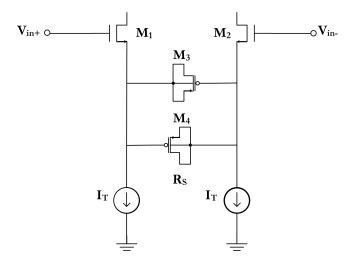

Capacitive Degeneration is another bandwidth enhancement technique that consists in degenerating the transistors of a differential pair by placing a capacitor and a resistor in parallel, connected between the sources of the transistors, Fig. 2.13. This causes an increase in the effective transconductance of the circuit at higher frequencies, compensating for the decrease in the voltage gain due to the pole at the output node.

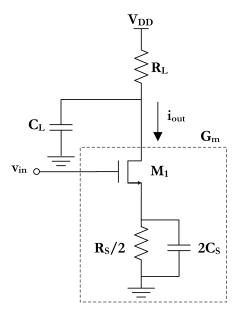

Figure 2.13: Differential pair with Capacitive Degeneration.

Aplying a single-ended analysis in this circuit (considering the half-circuit), it is possible to calculate the transfer function for the equivalent transconductance,  $G_m$ , and the corresponding poles and zeros, as demonstrated in [12]:

$$G_m(s) = \frac{g_m(R_S C_S s + 1)}{R_S C_S s + 1 + g_m \frac{R_S}{2}}$$

(2.8)

The corresponding zero and pole are given by Eq. 2.9 and Eq. 2.10, respectively.

$$\omega_z = \frac{1}{R_S C_S} \tag{2.9}$$

$$\omega_p = \frac{1 + g_m \frac{R_s}{2}}{R_s C_s}$$

(2.10)

The zero of the effective transconductance can be placed in order to cancel the output node pole, therefore extending the circuit's bandwidth up to the transconductance pole. This is the key idea behind this technique, and surely this increase in the bandwidth implies a decrease in the DC gain by the same amount. Fig. 2.14 a) illustrates the frequency response of the normalized equivalent transconductance, and the position of the corresponding zero and pole. Fig. 2.14 b) represents the frequency response of the voltage gain, when the degeneration zero is matched to the dominant pole at the output node.

Figure 2.14: a) Frequency response of the normalized equivalent transconductance,  $G_m$ . b) Frequency response of the voltage gain.

Capacitive Degeneration can also be used to cancel DC offset locally, instead of placing Alternating Current (AC) coupling between each stage (which occupies a lot of chip area) or using external feedback loops that can bring stability issues specially in high frequency circuits. This particular application of Capacitive Degeneration was used in [13], where the DC offset is reduced whithout impacting the high frequency gain.

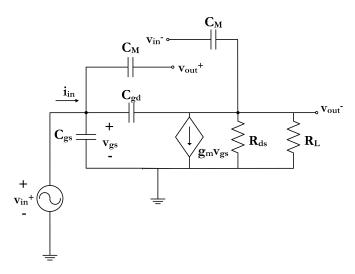

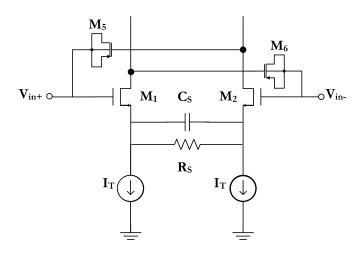

#### 2.1.4.3 Negative Miller Capacitance

The ideia behind Negative Miller Capacitance (NMC) is exploiting the Miller<sup>5</sup> effect to reduce the input capacitance of one amplifier stage, thus reducing the load effect in the previous stage and improving the overall bandwidth. Fig. 2.15 shows a gain stage employing NMC technique.

It it possible to perceive, by observation only, that the capacitors  $C_M$  are connected to the opposite output node, thusly suffering from a 180° phase shift between the signals in both nodes, and adding up to the gain-drain overlap parasitic capacitance of transistor  $M_1$  and  $M_2$  with a negative sign.

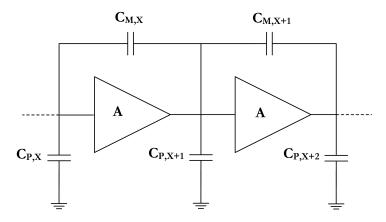

For better understanding of this effect, let us consider a high level schematic of a two-stage amplifier with negative miller capacitors, Fig. 2.16. Where  $C_{P,X}$  is the input capacitance of each stage and  $C_{M,X}$  are the capacitors used to take advantage of the Miller effect, and A is the voltage gain of the amplifier. The effective capacitance seen at the input of each stage is given by:

$$C_{effec,X} = C_{P,X} + (1 - A)C_{M,X}$$

(2.11)

<sup>&</sup>lt;sup>5</sup> Miller effect is when a capacitor is connected between the input and output of a high-gain inverting amplifier, appearing to be much larger at the input than it actually is.

Figure 2.15: Gain stage with Negative Miller Capacitance.

Figure 2.16: Two-stage amplifier with negative miller capacitors.

This means that if A is bigger than 1, the Miller capacitance -  $(1 - A)C_{M,X}$  - becomes negative, decreasing the effective capacitance seen at the input node and therefore reducing the load effect in the preceding stage and increasing the bandwidth.

The problem with this technique is that it is normally used to cancel the gate-drain overlap capacitance, which in deep submicron technologies working at high speed, tends to be smaller than 50 fF, making it difficult to create a capacitor that could accurately equal this value.

References [14], [15] and [13] are examples of the utilization of this technique in LAs.

# 2.1.4.4 Miller-Effect Suppression using Cascode Transistor

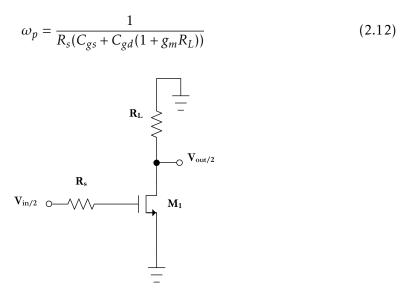

In a source-coupled differential pair, which AC half-circuit is illustrated in Fig. 2.17, the Miller effect is responsible for bringing the input pole to lower frequencies, making it the dominant pole, thusly limiting the bandwidth. As demonstrated in [16] Chapter 4, the dominant pole is given by:

Figure 2.17: AC half-circuit of a source-coupled differential pair.

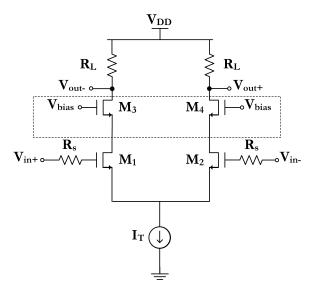

Miller effect increases the gate-drain overlap capacitance by  $1 + g_m R_L$ , this effect is more critical for high voltage gain amplifiers. One way to mitigate this effect is using cascode transistors, as depicted in Fig. 2.18.

Figure 2.18: Source-coupled differential pair with cascode transistors.

To understand this technique let us consider the left equivalent AC half-circuit of Fig. 2.18. The impedance seen from the source of the cascode transistor  $M_3$  is essencially  $\frac{1}{g_{m3}}$ , which means that the voltage gain from the input to  $M_1$ 's drain is  $\frac{g_{m1}}{g_{m3}}$ . If  $M_1$  and  $M_3$  have equal dimensions, this value is equal to 1, and the capacitance perceived by the input would be smaller and given by the following expression:

$$C_{in} = C_{gs} + C_{gd} \left( 1 + \frac{g_{m1}}{g_{m3}} \right)$$

(2.13)

If  $M_1$  is equal to  $M_3$  then expression 2.13 can be approximated to  $C_{gs} + 2C_{gd}$ . This value being much smaller than the one in a normal source-coupled differential pair, therefore killing the Miller effect. This way, the load effect in the preceding stage is reduced, allowing for an increase in the system's bandwidth. This practice has two major disadvantages: the decrease in the voltage headroom - which makes it hard to implement for low supply voltages - and the addition of a high frequency pole by transistor  $M_3$ .

Reference [17] shows an example of utilization of a cascode structure in a output stage for a power amplifier in 250 nm SiGe BiCMOS technology. In reference [18] a cascode structure is used in a pre-amplifier (equivalent to a transimpedance amplifier) for an Optical Receiver, decreasing the input capacitance.

#### 2.1.4.5 Cherry-Hooper Amplifier

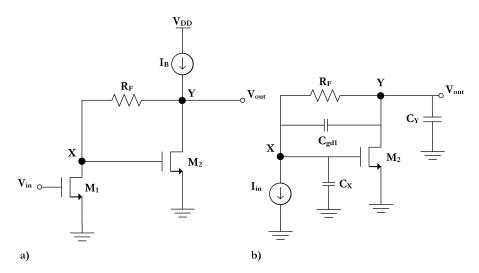

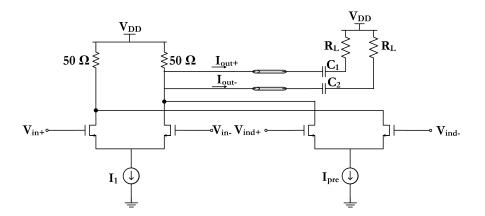

The Cherry-Hooper amplifier takes advantage of local feedback to improve speed which is a suitable solution for wideband multi-stage amplifiers. It allows for an independent tuning of the gain and bandwidth of the amplifier. Its basic architecture is composed by two stages, the first one converts the input signal to a current and the second one, that has a shunt feedback resistor, converts that current into a voltage. Fig. 2.19 a) shows a single-ended version of a Cherry-Hooper amplifier.

Figure 2.19: Single-ended Cherry-Hooper amplifier: a) complete b) simplified. Adapted from [7], Chapter 5.

By observation of Fig. 2.19 a) it is possible to comprehend that the feedback path is established by resistor  $R_F$  that senses the voltage at the output node, Y, and "responds" with a proportional current to node X. One should note that there are two paths to the output, one through  $M_2$  and the other through  $R_F$ , which means that it is important to minimize the signal flowing through the feedback resistor, since it opposes the one created by  $M_2$ . Let us consider a simplified schematic of the circuit, as represented in Fig. 2.19 b). Where  $I_B$  is considerer an ideal current source (infinite impedance) and  $I_{in}$  represents the drain current of transistor  $M_1$ . It is possible to determine the two poles of this circuit, as demonstrated in [7], Chapter 5 (assuming they are equal):

$$\omega_{p1} = \omega_{p2} = \frac{2g_{m2}}{C_X + C_Y + g_{m2}R_F C_{gd2}}$$

(2.14)

So, these poles will be in much higher frequencies than the ones without feedback,  $\omega_{p1} = (R_F C_X)^{-1}$  and  $\omega_{p2} = (R_F C_Y)^{-1}$ , since  $R_F$  is typically much larger than  $g_{m2}^{-1}$ . Although differential Cherry-Hooper structures allow for high frequency operation it struggles with low supply voltages.

References [19], [20], [4] and [13] are examples of the utilization of this circuit topology in multi-stage amplifiers. Reference [19] presents an architecture of a modified Cherry-Hooper with source-follower feedback (the feedback path is implemented by a source-follower instead of a simple resistor) fabricated in a 0.35  $\mu$ m CMOS technology. They were able to obtain a gain of 9.4 dB and 880 MHz bandwidth while consuming 6.0 mA from a 3.3 V supply.

#### 2.1.4.6 Gilbert Gain Cell

The Gilbert Gain cell was invented by Barrie Gilbert in 1968, and was developed to be specifically used in cascaded amplifiers as a gain cell. The purpose was to develop a cascadable circuit form (a "gain cell") that could provide DC-coupled temperature-insensitive sub-nanosecond current gain with the virtual absence of voltage swings, and theoretically perfect transfer function characteristic [21]. The Gilbert gain cell is represented in Fig. 2.20 (with Bipolar Junction Transistors).

Figure 2.20: Gilbert gain cell. Adapted from [21].

This topology has many advantages. First, the "inner" stage can operate with a voltage gain smaller than 1, yet the outer stage can achieve a gain greater than unity. Also, this cell is perfectly suited for cascade assemblies, since the output of one stage can directly drive the next. And lastly, the bias voltage circuit for each stage has to supply only the base current for that stage, which is not signal dependent. Therefore, this cell may be used in low-power applications where 0.5/1V is sufficient.

Reference [22] is an example of this circuit's employment as a Variable Gain Amplifier (VGA) inserted in a Automatic Gain Control block to be used in an 3.3 GHz Optical Receiver implemented in standard 0.18 µm CMOS.

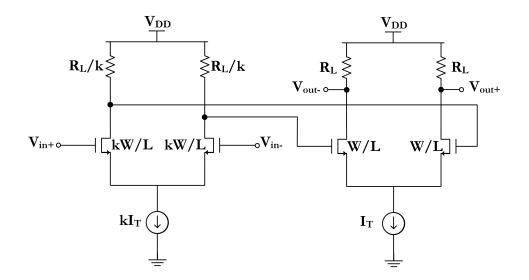

#### 2.1.4.7 Inverse Scaling Technique

Inverse Scaling is a technique where the dimensions of the transistors (the  $\frac{W}{L}$  ratio) and the tail current are scaled down from one stage to the other, whereas the load resistor's dimensions are scaled up. Fig. 2.21 illustrates this procedure.

Figure 2.21: Inversely scaled differential pairs (by a factor of *k*).

This technique concedes an increase in the bandwidth while keeping the GBW constant. This is because the GBW of each stage is defined as  $\frac{g_m}{C_{tot}}$  where  $C_{tot}$  is the load capacitance of each stage [5]. By reducing the dimensions of the driven stage (compared to the driving stage) the transconductance is reduced by the scaling factor , k - as are the input capacitances - thus diminishing the load effect in the previous stage, and enabling a bandwidth enhancement.

In reference [11] this technique is used in a Limiting Amplifier cascade for a 3 GHzOptical Receiver implemented in a  $0.25 \,\mu\text{m}$  CMOS process. A cascade of 4 gain stages scaled by a factor of 2 allowed a reduction in the power consumption by about 50% without compromising the noise and offset characteristics of the amplifier (this is because the noise and offset are mainly moduladed by the first amplifying stage, which is not scaled).

# **2.1.4.8** $f_T$ **Doublers**

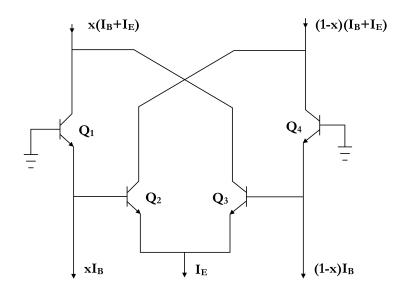

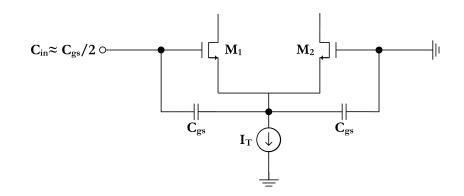

As mentioned before - in a cascade of identical amplifiers - the load effect from a certain stage exerted in the previous one is the most limiting factor when it comes to the overall system's bandwidth. Mainly for Output Buffers that must provide large currents to off-chip loads.  $f_T^6$  Doublers are a way to reduce the input capacitance of an amplifier without altering the corresponding voltage gain. Fig. 2.22 illustrates this circuit (considering that all the transistors have the same dimensions).

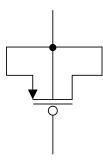

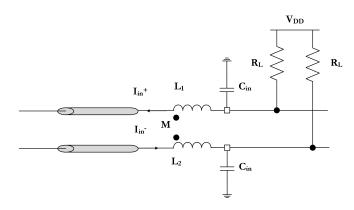

Figure 2.22:  $f_T$  Doubler. Adapted from [7], Chapter 5.

One can see that the small signals' gain remains the same as in a source-coupled different pair, but the input capacitance is reduced by half of its value. Let us consider the left half of the  $f_T$  Doubler, as represented in Fig. 2.23. In a small signals' analysis, only one of the transistors,  $M_1$  in this case, has an AC signal at its gate. Whereas the other one,  $M_2$ , has its gate grounded. Therefore, the effective capacitance seen from the gate of transistor  $M_1$  is the series connection of the two identical parasitic capacitances,  $C_{gs}$ .

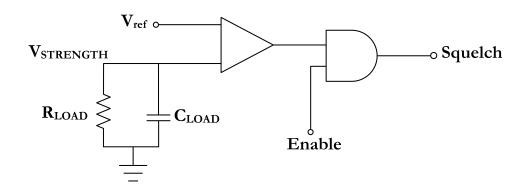

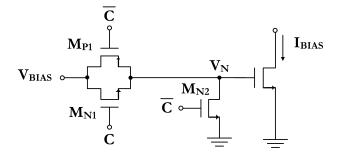

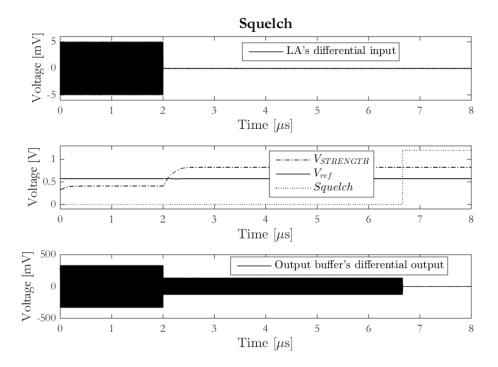

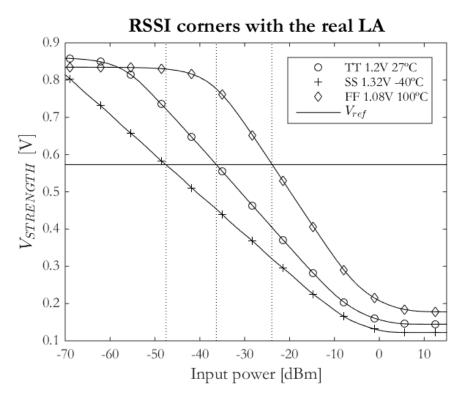

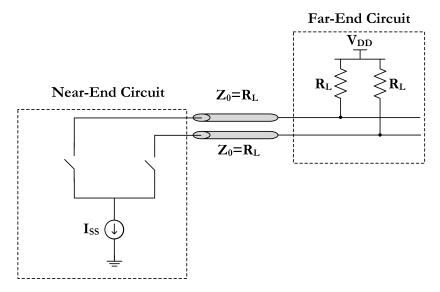

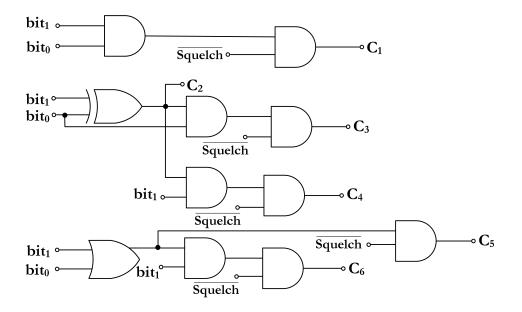

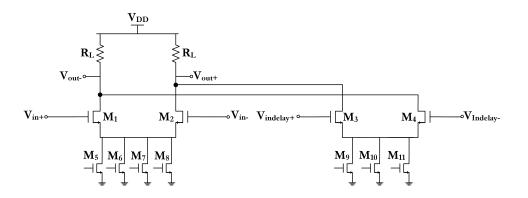

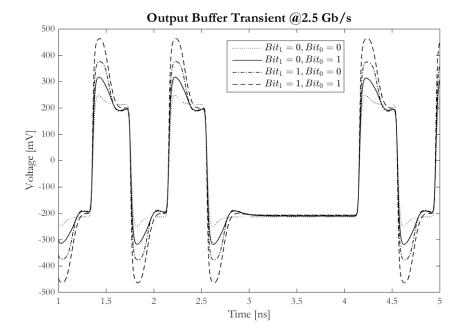

The input capacitance is reduced to  $\frac{C_{gs}}{2}$  and that is why this circuit is called  $f_T$  Doubler, because the transit frequency will double its value (ignoring the gate-drain parasitic capacitance).