# Automatic Synthesis of Application-specific Processors

#### CHARLES MUTIGWE

Thesis submitted in fulfilment of the requirements for the Degree

### DOCTOR TECHNOLOGIAE: ENGINEERING: ELECTRICAL

in the

School of Electrical and Computer Systems Engineering Faculty of Engineering and Information Technology

at the

Central University of Technology, Free State

Promoter: Prof. F. Aghdasi, Ph.D. (Eng.)

Co-promoter: Prof. J. Kinyua, Ph.D. (Eng.)

BLOEMFONTEIN October, 2012

# DECLARATION WITH REGARD TO INDEPENDENT WORK

| I, CHARLES MUTIGWE, identity number and student number                                |

|---------------------------------------------------------------------------------------|

| 207072035, do hereby declare that this research project submitted to the Central      |

| University of Technology, Free State for the Degree DOCTOR TECHNOLOGIAE:              |

| ENGINEERING: ELECTRICAL, is my own independent work; and complies with                |

| the Code of Academic Integrity, as well as other relevant policies, procedures, rules |

| and regulations of the Central University of Technology, Free State; and has not      |

| been submitted before to any institution by myself of any other person in fulfilment  |

| (or partial fulfilment) of the requirements for the attainment of any qualification.  |

|                                                                                       |

|                                                                                       |

|                                                                                       |

|                                                                                       |

|                                                                                       |

|                                                                                       |

|                                                                                       |

| SIGNATURE OF STUDENT DATE                                                             |

|                                                                                       |

I would like to dedicate this thesis to my parents and my grandmother who, by word and example, have inspired me to never stop learning and to always strive for academic excellence.

#### Acknowledgements

I would like express my deepest thanks to my advisors, Professor Farhad Aghdasi and Professor Johnson Kinyua, for their support, guidance and understanding during my doctoral studies. I thank them for giving me this wonderful opportunity to pursue the idea of automatic generation of processors and for agreeing to continue advising me after they both left CUT. I would like to thank Prof. Aghdasi for helping me secure funding for the first 3 years of my studies.

As a part-time student not based in South Africa or in my home country, Zimbabwe, the administrative requirements associated with continued enrollment at CUT were many and quite demanding. In this regard, I am especially grateful to my brother, Bruce, who is based in Bulawayo, Zimbabwe, for the many trips to Harare that he made on my behalf, and for all the other necessary administrative documents he helped me to secure. He was very supportive of my studies in other ways, including as a 'bouncing board' for some of my ideas. I would also like to thank the many dedicated administrative staff at CUT who helped me successfully navigate the administrative maze.

Above all, I am grateful to my wife, Sabely, my daughter, Chelsea and my son, Simbarashe who have all patiently put up with and supported me through the seemingly endless years spent on this research project.

#### Summary

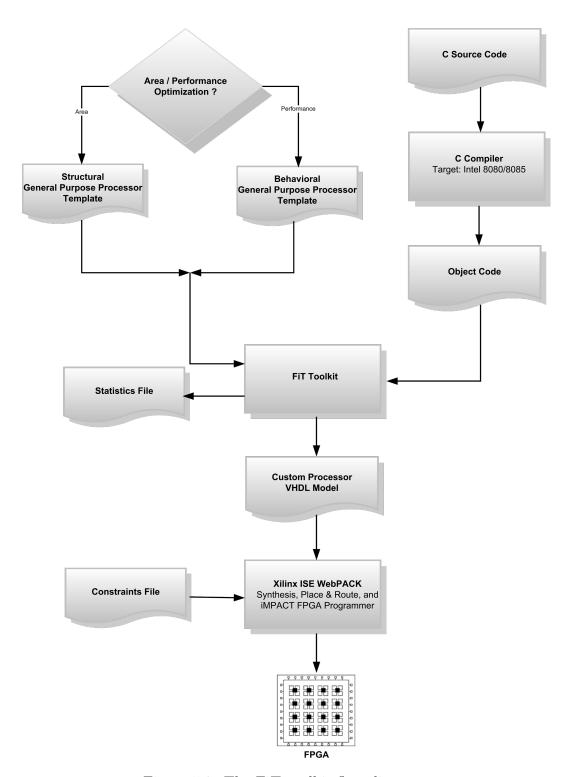

This thesis describes a method for the automatic generation of application specific processors. The thesis was organized into three separate but interrelated studies, which together provide: a justification for the method used, a theory that supports the method, and a software application that realizes the method. The first study looked at how modern day microprocessors utilize their hardware resources and it proposed a metric, called core density, for measuring the utilization rate. The core density is a function of the microprocessor's instruction set and the application scheduled to run on that microprocessor. This study concluded that modern day microprocessors use their resources very inefficiently and proposed the use of subset processors to execute the same applications more efficiently. The second study sought to provide a theoretical framework for the use of subset processors by developing a generic formal model of computer architecture. To demonstrate the model's versatility, it was used to describe a number of computer architecture components and entire computing systems. The third study describes the development of a set of software tools that enable the automatic generation of application specific proces-The FiT toolkit automatically generates a unique Hardware Description Language (HDL) description of a processor based on an application binary file and a parameterizable template of a generic microprocessor. Area-optimized and performance-optimized custom soft processors were generated using the FiT toolkit and the utilization of the hardware resources by the custom soft processors was characterized. The FiT toolkit was combined with an ANSI C compiler and a third-party tool for programming field-programmable gate arrays (FPGAs) to create an unconstrained C-to-silicon compiler.

#### **Opsomming**

Hierdie tesis beskryf 'n metode vir die outomatiese generasie van die aansoek spesifieke verwerkers. Die tesis is georganiseer in drie afsonderlike maar verwante studies, wat saam verskaf: 'n regverdiging vir die metode wat gebruik word om 'n teorie wat die metode ondersteun, en 'n sagteware program wat die metode besef. Die eerste studie het gekyk na hoe die hedendaagse mikroverwerkers gebruik hulle hardeware hulpbronne en dit 'n statistiek, die sogenaamde kern digtheid voorgestel, vir die meet van die benutting koers. Die kern digtheid is 'n funksie van die mikroverwerker se opdrag stel en die aansoek wat geskeduleer is om uit te voer op daardie mikroverwerker. Hierdie studie het tot die gevolgtrekking gekom dat die moderne dag mikroverwerkers gebruik om hul hulpbronne baie ondoeltreffend en voorgestel dat die gebruik van die subset verwerkers dieselfde toepassings meer doeltreffend uit te voer. Die tweede studie het probeer om 'n teoretiese raamwerk vir die gebruik van die subset verwerkers deur die ontwikkeling van 'n generiese formele model van die rekenaar argitektuur te verskaf. Die model se veelsydigheid te demonstreer, is dit gebruik om 'n aantal van rekenaarargitektuur komponente en die hele rekenaar stelsels te beskryf. Die derde studie beskryf die ontwikkeling van 'n stel van sagteware gereedskap wat in staat stel om die outomatiese generasie van die aansoek spesifieke verwerkers. Die Fit toolkit genereer outomaties 'n unieke Hardware Beskrywing Taal (HDL) beskrywing van 'n verwerker wat gebaseer is op 'n aansoek binre ler en 'n parameterizable sjabloon van 'n generiese mikroverwerker. Area-new en prestasie-optimale persoonlike sagte verwerkers is gegenereer deur gebruik te maak van die Fit toolkit en die benutting van die hardeware hulpbronne deur die persoonlike sagte verwerkers is gekenmerk. Die Fit toolkit is gekombineer met 'n ANSI C compiler en 1/3-party hulpmiddel vir die programmering van veldprogrammeerbare hek skikkings (FPGAs) te skep van 'n onbeperkte C-tot-silikon samesteller.

# Contents

| $\mathbf{C}$ | ontei | nts                                    | vi        |

|--------------|-------|----------------------------------------|-----------|

| Li           | st of | Figures                                | ix  xi  1 |

| Li           | st of | Tables                                 | xi        |

| 1            | Inti  | roduction                              | 1         |

|              | 1.1   | Introduction                           | 1         |

|              | 1.2   | Problem Description                    | 2         |

|              | 1.3   | Motivation for the Research            | 3         |

|              | 1.4   | Research Objectives                    | 4         |

|              | 1.5   | Research Methodology                   | 5         |

|              | 1.6   | Limitations of the Research            | 6         |

|              | 1.7   | Thesis Organization                    | 6         |

| 2            | Rel   | ated Work                              | 8         |

|              | 2.1   | Introduction                           | 8         |

|              | 2.2   | Instruction Set Usage                  | 8         |

|              | 2.3   | Formal Models of Computer Architecture | 11        |

|              | 2.4   | Soft Processors                        | 15        |

|              | 2.5   | Subset Processors                      | 16        |

|              | 2.6   | Summary                                | 18        |

| 3            | Inst  | truction Set Usage Analysis            | 19        |

|              | 2 1   | Introduction                           | 10        |

#### CONTENTS

|   | 3.2  | Instruction Sets and Core Density   | 20                |

|---|------|-------------------------------------|-------------------|

|   |      | 3.2.1 Introduction                  | 20                |

|   |      | 3.2.2 Instruction Sets and Hardware | 21                |

|   |      | 3.2.3 Instruction Subsets           | 23                |

|   |      | 3.2.4 Core Density                  | 25                |

|   | 3.3  | ISA Usage Experiments               | 28                |

|   |      | 3.3.1 Architectures and Compilers   | 28                |

|   |      | 3.3.2 Benchmark Applications        | 29                |

|   |      | 3.3.3 Method                        | 29                |

|   | 3.4  | Results and Discussion              | 30                |

|   |      | 3.4.1 Compilers                     | 30                |

|   |      | 3.4.2 Optimizations                 | 32                |

|   |      | 3.4.3 Instruction Set Usage         | 33                |

|   |      | 3.4.4 Top N Instructions            | 37                |

|   | 3.5  | Significance of this Study          | 39                |

| 4 | ۸ (  | omputer Architecture Model          | 41                |

| 1 | 4.1  | -                                   | <del></del><br>41 |

|   | 4.2  |                                     | 42                |

|   | 1.2  |                                     | $\frac{12}{47}$   |

|   | 4.3  |                                     | 50                |

|   | 1.0  |                                     | 50                |

|   | 4.4  | -                                   | 52                |

|   |      |                                     | 53                |

|   |      |                                     | 54                |

|   |      |                                     | 55                |

|   |      |                                     | 55                |

|   |      | -                                   | 56                |

|   | 4.5  |                                     | 57                |

|   | 4.6  |                                     | 59                |

| = | Ма   | ahing Draggars to Applications      | ይሶ                |

| 5 |      |                                     | <b>60</b><br>60   |

|   | ·) [ | THEOUTICHOH                         | 1 11 1            |

#### CONTENTS

|              | 5.2   | Toolkit Description                                | 62 |

|--------------|-------|----------------------------------------------------|----|

|              |       | 5.2.1 General-Purpose Processor Templates          | 63 |

|              |       | 5.2.2 Operation                                    | 64 |

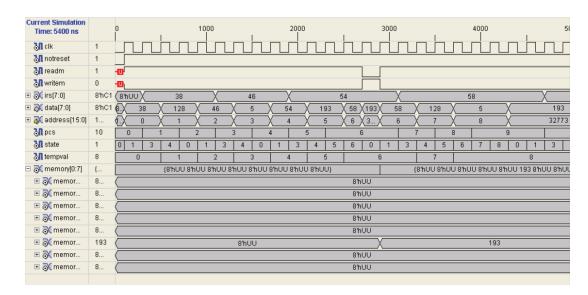

|              |       | 5.2.3 Verification                                 | 66 |

|              | 5.3   | Benchmarks                                         | 66 |

|              | 5.4   | Results                                            | 68 |

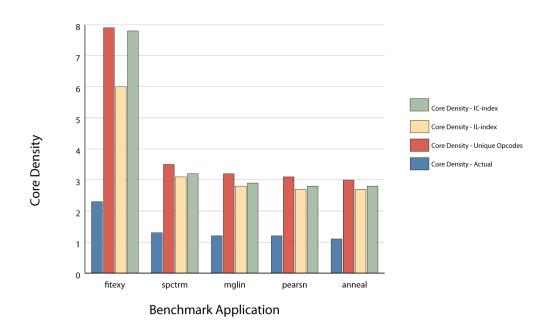

|              |       | 5.4.1 Area-Optimized Custom Soft Processors        | 69 |

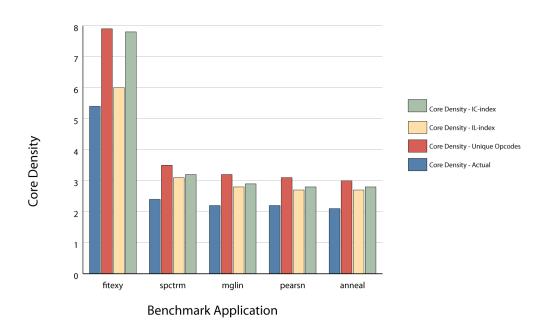

|              |       | 5.4.2 Performance-Optimized Custom Soft Processors | 71 |

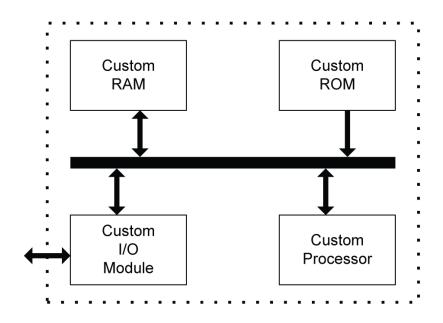

|              | 5.5   | Application                                        | 72 |

|              | 5.6   | Significance of this Study                         | 73 |

| 6            | Cor   | clusion and Future Research                        | 75 |

|              | 6.1   | Summary                                            | 75 |

|              | 6.2   | Contributions                                      | 76 |

|              | 6.3   | Future Research                                    | 77 |

|              |       | 6.3.1 Extending the Study on Instruction Set Usage | 78 |

|              |       | 6.3.2 Extending the Computer Architecture Model    | 78 |

|              |       | 6.3.3 Extending the FiT Toolchain                  | 78 |

|              | 6.4   | List of Scientific Publications                    | 79 |

| $\mathbf{R}$ | efere | ces                                                | 80 |

| $\mathbf{A}$ | NNE   | KURE A                                             | 87 |

|              | .1    | Processor Module                                   | 87 |

|              | .2    | ROM Module                                         | 95 |

|              | 3     | SRAM Module                                        | 98 |

# List of Figures

| 2.1 | Instructions (%) responsible for 80% and 90% of instruction exe- |    |

|-----|------------------------------------------------------------------|----|

|     | cutions                                                          | 10 |

| 2.2 | A VM that supports multiple OS environments                      | 14 |

| 3.1 | Transforming a fixed ISA processor into an exact ISA processor   | 20 |

| 3.2 | The Instruction Vector                                           | 22 |

| 3.3 | Opcode extraction and analysis process for each application      | 31 |

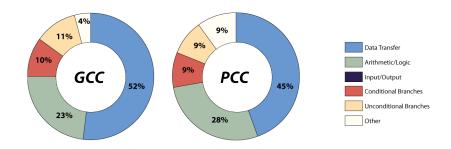

| 3.4 | Instruction usage by instruction type and compiler               | 32 |

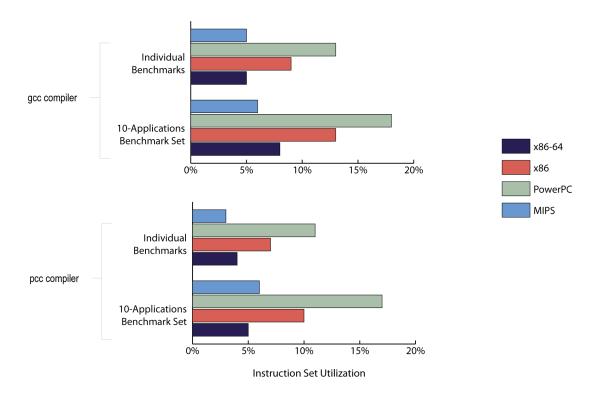

| 3.5 | Average ISA utilization by target architecture and compiler      | 33 |

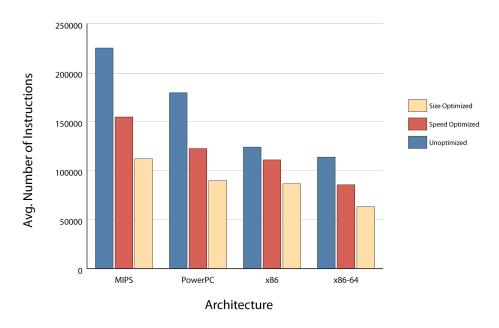

| 3.6 | Average instruction counts by compiler target and optimization   | 34 |

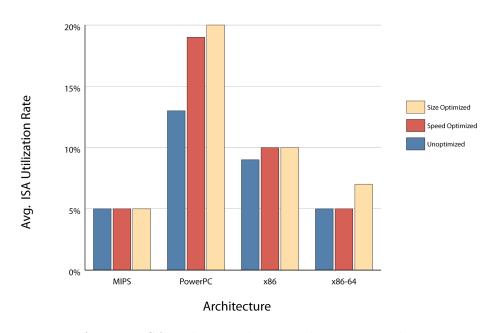

| 3.7 | Average ISA utilization by compiler target and optimization      | 34 |

| 3.8 | TopN opcodes used as a percentage of total opcodes used          | 38 |

| 4.1 | Instruction to resources relation                                | 43 |

| 4.2 | Resources to data relation                                       | 45 |

| 4.3 | Graphical representation of the triplet model                    | 46 |

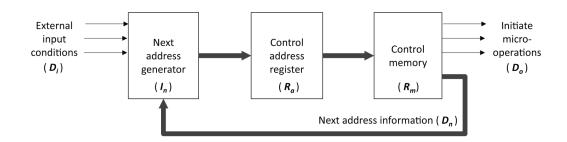

| 4.4 | The k85 microprocessor architecture block diagram                | 48 |

| 4.5 | Tree-based representation of the generic model                   | 51 |

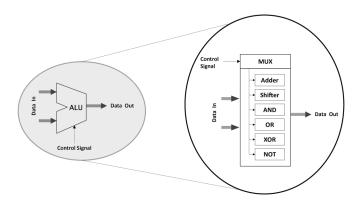

| 4.6 | The arithmetic logic unit (ALU)                                  | 51 |

| 4.7 | Microprogramming control unit organization                       | 54 |

| 5.1 | The Xilinx Spartan 3E Development Board                          | 62 |

| 5.2 | The k85 microprocessor architecture block diagram                | 63 |

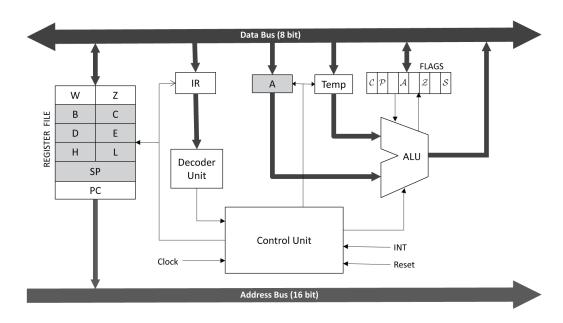

| 5.3 | The FiT toolkit flow diagram                                     | 65 |

| 5.4 | Timing diagram for the Processor, ROM, and SRAM modules          | 66 |

#### LIST OF FIGURES

| 5.5 | Running a 'Hello World!' application                            | 67 |

|-----|-----------------------------------------------------------------|----|

| 5.6 | Core densities for area-optimized custom soft processors        | 70 |

| 5.7 | Core densities for performance-optimized custom soft processors | 71 |

| 5.8 | Custom 8085-based microcontroller                               | 72 |

| 5.9 | C-to-silicon Compiler.                                          | 73 |

## List of Tables

| 2.1 | Top 10 instructions for the x86                                  | 11 |

|-----|------------------------------------------------------------------|----|

| 2.2 | Mix of instructions for TMS320C540x DSP                          | 12 |

| 3.1 | Architectures Studied                                            | 28 |

| 3.2 | C Benchmark Applications                                         | 29 |

| 3.3 | Java Benchmark Applications                                      | 30 |

| 3.4 | Number of instructions (opcodes) used                            | 35 |

| 3.5 | Application Core Densities                                       | 36 |

| 3.6 | JVM instruction-set usage statistics                             | 38 |

| 3.7 | Core densities using the Top25 opcodes                           | 39 |

| 5.1 | FiT Benchmark Applications                                       | 68 |

| 5.2 | Results for the complete 8085 ISA opcode set                     | 69 |

| 5.3 | Average core densities of area-optimized custom soft processors  | 70 |

| 5.4 | Average core densities of performance-optimized custom soft pro- |    |

|     | cessors                                                          | 72 |

### Chapter 1

### Introduction

#### 1.1 Introduction

As the number of transistors on a silicon chip continue increase exponentially, as predicted by Moore's Law, the design of electronic systems is moving away from the situation where discrete chips were assembled on a circuit board to one where entire systems or networks of systems are placed on a single chip. The design of these systems-on-chip (SoCs) and networks-on-chip (NoCs) demands new ways of viewing the electronic systems design process and new design tools. The research described in this work focuses on one aspect of designing SoCs and that is the automated design systems based on one class of microprocessors.

We believe that the work presented in this thesis contributes a small, but important, step in facilitating the paradigm shift that is required to design the SoCs of the future. This work not only provides a reference implementation and a theoretical framework for some new designs, but it also shows the shortcomings of existing microprocessor implementations.

In this chapter we begin by looking at the problems that the research presented in this thesis attempts to answer. Using some scenarios, we highlight real computer engineering issues that motivated our research. This is followed by a description of the objectives of the research. Next, the research methodologies that were used are outlined and then a description of the research's limitations is given. The chapter concludes with a summary of how the rest of the thesis is organized.

#### 1.2 Problem Description

The basic question addressed by this work is, how can the properties of an application be used to automatically generate an optimized custom processor, which will later be used to execute the application? Application properties, in this context, means the assembly instructions used by the application - their usage frequencies, their length in bits and their cycle times. Optimized, in this context, means that for an application set to run on the processor, each resource in the processor is scheduled at least once for the successful execution of the application. In other words, there are no unused resources in the processor. The microprocessor generating system developed to answer this question is easily extended to synthesize microcontrollers, and this leads to a more general question related to the program-store von Neumann model [1]: can a generic program-architecture-store model be developed to represent these microcontrollers that have a one-to-one relation between the application and the processor?

Other sub-questions arising from these, which are addressed as part of this work, are:

- How are processors generated automatically?

- How efficiently do applications use the resources on traditional microprocessors?

- How efficiently do applications use the resources on the microprocessors that are generated as part of this work?

- Can the processor generating system developed be extended into an unconstrained C-to-silicon compiler?

Any effective answer to the last sub-question is of much interest to the electronic design automation (EDA) community [2].

#### 1.3 Motivation for the Research

Consider the following scenarios, which are typical of those that have motivated this research.

- Platform Vendor versus App Developers: A device platform vendor may want to provide some performance guarantees for applications hosted on the device, while at the same time improving the platform's popularity by courting as many third-party developers to write apps for the platform. The third-party developers may each optimize the performance and functionality of their applications without regard to any other applications that may be co-located on the device. If the device is implemented with a limited number of microprocessors and uses context-switching-based multitasking, then as the number of applications hosted on the devices rises, clearly the performance guarantees are in jeopardy. For example, early releases of the iPhone did not permit any apps to run in the background, causing outcries from the developer community [3]. iPhone multitasking was introduced with OS 4.0. However, even with this release, applications are categorized and then the allocation of computing resources to these categories is prioritized [4].

- Application Isolation: According to some estimates, 80 percent of automobile innovations come from computer systems [5]. Premium-class automobiles now use around 100 million lines of code, and that number is expected to reach 300 million in the near future [6]. As the amount of software increases, so does the complexity of the systems. Complexity leads to reliability concerns. The challenge is to continue to increase the functionality by adding new software applications (i.e. more lines of code), while improving reliability by minimizing the potential for unwanted interactions between these applications.

- Legacy Application Support: The obsolescence of technology is one of the primary drivers for modernizing legacy information systems [7]. However, according to Sneed [8], more than 50 percent of these modernization projects fail; he recommends an upgrade method that minimizes the risks

of failure. The proposed method leaves the data and the business processes unchanged, and focuses on updating the technology components piecemealwise.

• Time to Market: Raising the level of programming abstraction improves the productivity and performance of the applications developers [9, 10] by allowing developers to more easily describe what a desired application should do, instead of having them focus on the details of how it should do it. The productivity of the product developers is important since, according to Cohen et al. [11], many technology-driven firms now compete on product-development cycle time.

The two common themes running through the examples are: complexity, and features. Each example involves the relationship between a computer system's complexity and its supported feature set. The features are encapsulated in software applications. As more applications are scheduled to run on a computer system, the complexity of the system increases due to (1) the interaction among the applications and (2) the varying demands made by each application to the shared computing resources. One way, which is the focus of this work, to manage the latter cause of computer system complexity is to try and guarantee computing resources for each application. The main resource in most modern computer systems is the microprocessor, so the general direction of this work is to show how we can transparently allocate to each application a dedicated microprocessor whose resources are tailored to the application.

#### 1.4 Research Objectives

The objectives of our research were to:

1. Study how existing microprocessors utilize their hardware resources when running software applications. The results of this study should help identify any inefficiencies or missing features that require further research.

- 2. Create and evaluate a tool to automatically generate custom microprocessors. This tool is a new, practically useful system to perform tasks that previously could not be achieved.

- 3. Develop a formalism to model computer architecture. The practical applications of the computer architecture models are that they enable us to better understand, control and modify our custom microprocessors.

#### 1.5 Research Methodology

In this section we use the terminology by Amaral *et al.* [12] to describe the research methods used in this work.

The experimental methodology was used to measure how existing microprocessors utilize their hardware resources as a function of the microprocessors' instruction sets. Industry standard benchmarks from the Standard Performance Evaluation Corp. [13, 14] were used to provide the source code. The most popular open source compilers were used to compile the source code and to profile compiler outputs.

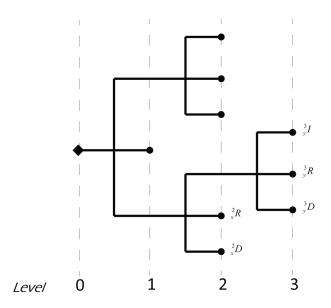

The model methodology was used to develop the 'instructions-resources-data triplet model, which is an abstract model of real and virtual computer architectures. The triplet model was constructed from first principles as a recursive, set-theoretic model. The triplet model was used to describe custom microprocessors, which were the primary focus of this research. However, the triplet model is generic enough and is able to model general computer components and general computing systems, as shown by the examples that were given in this work.

The build methodology was used to build, in the C programming language, a software application that demonstrated the feasibility of automatically generating custom microprocessors. We called this software application the FiT toolkit. The automatically generated custom microprocessors were then implemented on a reconfigurable computing device. The utilization of hardware resources by the automatically generated custom microprocessors was then studied using the

experimental methodology. Third-party tools provided by Xilinx Corp. [15], the vendor of the reconfigurable computing device, were used to study the generated custom microprocessors.

#### 1.6 Limitations of the Research

While the method of generating custom microprocessors presented in this work raises the abstraction level and so improves the productivity of system designers. The quality of the custom microprocessors that are produced may depend on the quality of the executable file that is generated by the compiler. We tested for this dependence using two popular optimizing compilers and found it not to exist, however in order to be more conclusive, tests using a more diverse set of compilers are needed.

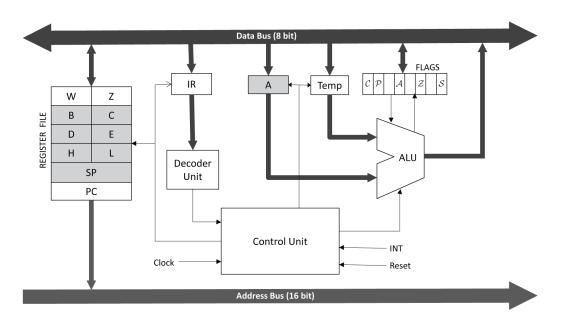

The example applications of the formal model and the FiT toolkit that were both developed as part of this research target the k85 microprocessor. The k85 is a very simple microprocessor that is code-compatible with the first popular microprocessors, the Intel 8080 and 8085. This research needs to be extended to target modern microprocessors, which are much more complex than the k85.

#### 1.7 Thesis Organization

The rest of this thesis is organized around three self-contained studies. The studies are related and they are arranged so as to build upon one another.

Chapter 2 reviews previous work on instruction set usage, formal models of computer architecture, and subset processors.

Chapter 3 presents the first study in which the core density metric is developed and compared to another instruction set usage measure. The study then describes the instruction set usage experiments. The results of the experiments are also discussed and compared to instruction set usage results from other researchers.

We propose the use of subset processors in order to generate application-specific systems that have an optimal core density.

Chapter 4 presents the second study where a generic computer architecture model is developed. We give a number of examples to demonstrate how the model can be used to describe computer components as well as complete computer systems. In this study the computer architecture model is used to describe the subset processors that were proposed in the previous study.

Chapter 5 presents the third study, which describes the FiT toolchain. FiT is an application-specific processor generator that accepts an application binary file as an input, and automatically creates an HDL specification for an 8-bit subset processor. The HDL processor specifications are then realized on an FPGA development board. Two approaches to generating the sub-set processors are presented and compared as to their hardware resource utilization. In the study, we use some scripts to combine the FiT toolchain, an ANSI C compiler from the Amsterdam Compiler Kit and the Xilinx ISE WebPACK to create a C-to-silicon compiler. This C-to-silicon compiler takes an application described in unconstrained ANSI C and automatically implements the application in hardware as a microcontroller that is driven by an 8-bit subset processor.

Chapter 6 summarizes the findings of this research, highlights the contributions of this research and presents some recommendations for future research work.

### Chapter 2

### Related Work

#### 2.1 Introduction

The research presented in this work is focused in the area of customizable processors, also referred to as application-specific instruction processors (ASIPs). Several researchers have described ASIPs as the next evolutionary step for microprocessors [16, 17]. The general research approaches in this area have been to construct one or more of the following [18]: (i) Parameterizable processors (ii) Extensible processors (iii) Custom processor development tools. As part of this research, a custom processor development tool for parameterizable processors was created.

In this chapter we review earlier work that laid the foundation for our research on a particular group of ASIPs called subset processors. We also note any gaps in the earlier work that have directed our research.

### 2.2 Instruction Set Usage

Foster et al. [19] describe two types of instruction set usage analyses. In the first type, the static case, the frequency counts of the instructions used to specify the

logic of the problem are collected and analyzed. In the second type, the dynamic case, the frequency counts of the instructions used to execute the logic of the problem are collected and analyzed [20]. Foster *et al.* [19] proposed two measures for instruction usage.

The first measure is based on information theory and it calculates the average number of bits of information contained in each opcode for each application that is analyzed. It states that if there are T instructions and  $p_i$  is the probability that the i-th instruction is used, then the average number of bits of information contained in each instruction, I, is

$$I = -\sum_{i=1}^{T} p_i(\log_2 p_i). \tag{2.1}$$

$I_{max}$  the maximum value of I occurs when the usage of any instruction is equally probable and it is

$$I_{max} = log_2 T. (2.2)$$

The relative difference between I and  $I_{max}$  is a measure of the utilization of any particular set of instructions.

The second measure estimates the effort needed to recode an application when the number of opcodes available to the compiler or assembly programmer is reduced to the N most popular ones after an initial unconstrained compilation. To arrive at this measure the instructions used in the application are ordered from the most frequently used to the least frequently used. Let  $C_k$  equals the number of times the k-th instruction was used where  $C_k \geqslant C_{k+1}$  for all k and let P equal the total number of instructions in the original application. The fraction of all instruction occurrences included in the set N is given by the function f(N) where

$$f(N) = \frac{1}{P} \sum_{k=1}^{N} C_k \tag{2.3}$$

and g(N) defined as:

$$g(N) = 1 - f(N) (2.4)$$

is then a measure of the effort needed to recode the original application onto a machine that only uses the top N opcodes. Both of the measure mentioned above applied to static and dynamic instruction usage. Foster  $et\ al.$  also found that the hand-assembled code has higher static opcode usage than machine-compiled code, and that there are no significant differences in dynamic opcode usage between the hand-assembled and machine-compiled code.

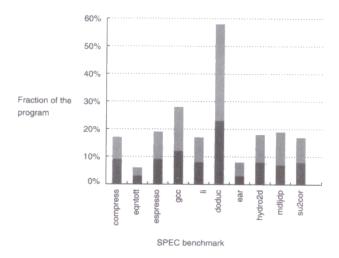

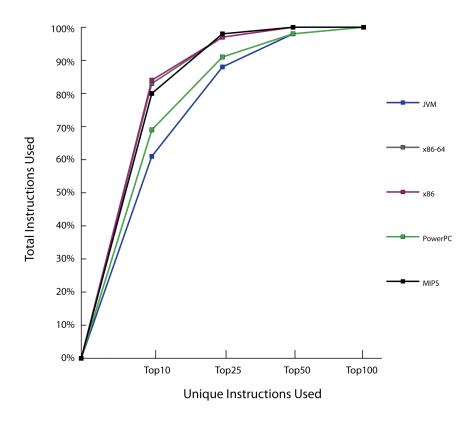

Hennessy and Patterson [21, 22] conducted instruction set usage experiments on several Complex Instruction Set Computing (CISC) and Reduced Instruction Set Computing (RISC) ISAs using the SPEC CPU92 benchmark applications. They found that on average 90% of the instruction execution comes from 10% of the instructions in the integer programs and 14% of the instructions in the floating-point programs. Fig. 2.1 (sourced from [21]) shows the percentage of instructions that are responsible for 80% and for 90% of the instruction executions. The total bar height indicates the fractions of instructions that account for the 90% of the instruction executions and the dark portion indicates the fraction of instructions responsible for the 80% of the instruction executions. For the x86 architecture Hennessy and Patterson [22] found that the top 10 instructions were responsible for 96% of the instructions that were executed as shown in Table 2.1. These 10

Figure 2.1: Instructions (%) responsible for 80% and 90% of instruction executions.

Table 2.1: Top 10 instructions for the x86.

| Rank | 80x86 instruction      | Integer average     |  |

|------|------------------------|---------------------|--|

|      |                        | (%  total executed) |  |

| 1    | load                   | 22%                 |  |

| 2    | conditional branch     | 20%                 |  |

| 3    | compare                | 16%                 |  |

| 4    | store                  | 12%                 |  |

| 5    | add                    | 8%                  |  |

| 6    | and                    | 6%                  |  |

| 7    | sub                    | 5%                  |  |

| 8    | move register-register | 4%                  |  |

| 9    | call                   | 1%                  |  |

| 10   | return                 | 1%                  |  |

|      | Total                  | 96%                 |  |

instructions represent 25 opcodes in the x86 ISA. Using the TI TMS320C540x Digital Signal Processor (DSP), Hennessy and Patterson [22] found that the top 20 instructions account for 97.2% of all the instructions executed as shown in Table 2.2.

Other empirical studies by Adams and Zimmerman [20], and Huang and Peng [23] on the x86 instruction set architecture (ISA); and El-Kharashi *et al.* [24] on the Java Virtual Machine (JVM) have also shown that modern applications spend 80-90% of their time accessing only 10-20% of the ISA.

#### 2.3 Formal Models of Computer Architecture

The term computer architecture was first used to describe the attributes of the IBM System/360 as seen by the programmer [25, 26]. Today this aspect of a computer's design is commonly known as its Instruction Set Architecture (ISA). Over time, the concept of computer architecture has grown to be more encompassing. Mudge [26] defines computer architecture as the ISA together with its implementation using hardware components. He adds that computer architecture influences and is influenced by the existing technology, the applications targeted

Table 2.2: Mix of instructions for TMS320C540x DSP.

| Instruction                     | Percent |

|---------------------------------|---------|

| store mem16                     | 32.2%   |

| load mem16                      | 9.4%    |

| add mem16                       | 6.8%    |

| call                            | 5.0%    |

| push mem16                      | 5.0%    |

| subtract mem16                  | 4.9%    |

| multiple-accumulate (MAC) mem16 | 4.6%    |

| move mem-mem 16                 | 4.0%    |

| change status                   | 3.7%    |

| pop mem16                       | 2.8%    |

| conditional branch              | 2.6%    |

| load mem32                      | 2.5%    |

| return                          | 2.5%    |

| store mem32                     | 2.0%    |

| branch                          | 2.0%    |

| repeat                          | 2.0%    |

| multiply                        | 1.8%    |

| NOP                             | 1.5%    |

| add mem32                       | 1.3%    |

| subtract mem32                  | 0.9%    |

| Total                           | 97.2%   |

to run on the computer, and other constraints such as costs, compatibility and the marketplace. Hennessy and Patterson [27] define computer architecture as the design specifications for a computer, which include the description of its: (i) ISA, (ii) microarchitecture, also known as computer organization, and (iii) hardware. These design specifications (or blueprints), when implemented, should result in a computer that maximizes performance while subject to constraints, such as costs and power. In this work we used the definition of computer architecture by Hennessy and Patterson. When dealing with physical machines, the 'program' and 'data' components of our proposed model relate to the ISA part of this definition, while the 'resources' part of our model relates to the microarchitecture and the hardware descriptions.

A constructive computation-based theoretical framework for modeling the underlying structures of computer architecture is presented by Albrecht [28]. While this framework is generic, it has some limitations in that it is not intuitive and it is mainly focused on modeling the operations of the components. Furthermore, it is only accessible to computer architects with advanced mathematical training in formal models.

Within the literature, the architecture of physical computers and the architecture of virtual computers are treated as a separate subjects [27, 29]. Given the growing importance of virtualization in the computer industry, we are of the view that a framework which seamlessly handles both physical and virtual computer architectures will be advantageous. Chen et al. [30] proposed a Virtual Machine (VM) model that extends an existing model that is used for real machines. They model both the source computer system and the destination computer system (virtual machine) as Turing Machines,  $M^S$  and  $M^T$ , such that

$$M^S = \left(S^s, I^S, \delta^S, s_o{}^S, S_f{}^S\right) \tag{2.5}$$

where

- $S^S$  denotes the set of all the states the source machine (computer system) may have,

- $I^S$  denotes the set of all the instructions the source machine can provide.

- $\delta^S: S \times I \mapsto S \times I$  is the execution operator of an instruction of I,

- $s_o^S$  denotes the initial state of a machine, and

- $S_f^S$  denotes the set of all the possible final states of a machine.

For  $M^T$ , simply change all the superscripts in Equation (2.5) from 'S' to 'T'. To handle the emulation they extend the execution operator to

$$\delta: S \times \{I\} \mapsto S \times I. \tag{2.6}$$

This results in a state machine-based model that does not easily lend itself to modeling the architectures such as those of application-specific processor cores on a reconfigurable computing fabric, since the set of all states may be too large to easily display and keep track of.

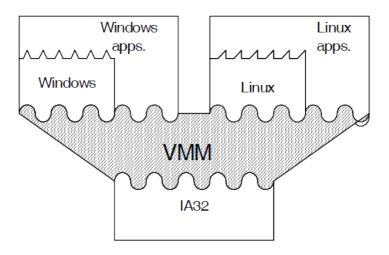

Smith and Nair [29] model virtual machines graphically. Fig. 2.2 shows an example of one of their models for a system VM that supports multiple Operating System (OS) environments on the same hardware. Such models are most useful when working with a small set of virtual machines or when the level of virtualization is low. These graphical models cannot be used to analyze virtual machines algebraically or recursively.

Figure 2.2: A VM that supports multiple OS environments.

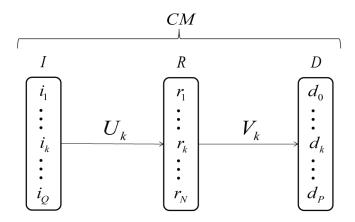

Reconfigurable computing refers to "systems incorporating some form of (runtime) hardware programmability, - customizing how the hardware is used using a number of physical control points. These control points can then be changed periodically in order to execute different applications using the same hardware" [31]. We are looking for a computer architecture model that is generic enough to take into account the possible use of reconfigurable computing resources. Sima et al. [32] put forward an architectural-based taxonomy for field-programmable devices. Their taxonomy introduced a recursive formalism (similar to Flynn's requestor/server formalism [33]) that is based on microcode in order to abstract away any references to a particular ISA. This formalism defines a computing machine (CM) as a doublet, consisting of a microprogram  $(\mu P)$ , and a set of resources (R). That is

$$CM = (\mu P, R). \tag{2.7}$$

Our proposed computer architecture model extends this formalism in Equation (2.7) by adding a third component that will be used to model the data processed by the computing machine. This data component will facilitate the modeling of virtual devices and operations on inputs with different data types.

#### 2.4 Soft Processors

A soft processor is a hardware description language (HDL) model of a microprocessor core that is implemented on a reconfigurable device. In a soft processor a HDL, such as VHDL or Verilog, is used to describe the structure and behavior of the microprocessor. Vendor-specific logic synthesis and place & route tools are then used to implement HDL model on a reconfigurable device, such as an FPGA. Most of the complex soft processors that have been implemented using VHDL and Verilog models have been based on the RISC architecture. In a RISC ISA, the reduced number of instructions and their fixed format lend themselves to a simpler design for the microprocessors control unit [34, 35]. One of the earliest complete VHDL models of a commercial processor was LEON, which modeled the SPARC V8 microprocessor [36]. The LEON required 5,300 look-up tables

(LUTs) to implement on a Xilinx XCV300E-8 FPGA. Other RISC-based VHDL models of complete 32-bit and 64-bit microprocessors continue to be developed and used as research tools [37, 38]. Lu et al. developed a complete VHDL model of the CISC-based Pentium microprocessor, which was implemented on an FPGA and used to replace the original microprocessor on a motherboard [39]. Lu et al. were able to install and run Windows XP and other applications on this soft processor-driven computer system. However, given the complexity of the x86 architecture, 65,612 LUTs were required to implement the Pentium VHDL model on a Xilinx Virtex-4 FPGA. In all the cases above the resources required to implement each soft processor, as measured by the number of LUTs used, are fixed. However, as we will show in Chapter 3 most of these resources will not be used by the applications running on the soft processors and so in order to more efficiently utilize the limited resources on the reconfigurable devices any unused resources should not be implemented.

#### 2.5 Subset Processors

The study of subset processors is part of the broader study of ASIPs. Jain et al. [40], in their overview of the issues and techniques in ASIP design note that the techniques for instruction set generation fall into one of two categories: instruction set synthesis or instruction selection from a pre-existing superset of instructions. Our FiT toolkit uses the instruction selection technique. Soft processors have size, performance and power disadvantages when compared to their packaged counterparts. Bilski et al. [41] discuss some of ways that these shortcomings were mitigated in the design of the Xilinx MicroBlaze soft processor. They did this as follows:

- Limited the number of pipe stages to three, because adding more pipe stages increased the number and size of the multiplexors in the processor.

- Matched the supported number logic instructions in the MicroBlaze's instruction set to the input size of the Look-Up Tables (LUT), which in the case of the Xilinx devices was 4.

- Implemented all timing-critical functions using a carry chain in order to reduce logic delays.

- Used the shift register mode of the LUT to implement First-In First-Out (FIFO) and instruction fetch buffers, whenever possible.

As a result of their optimizations the MicroBlaze has a fixed floor plan and any customizations, such as those proposed in Chapter 3, would disturb the optimal floor plan. Customization in the MicroBlaze is achieved by adding or removing carefully selected pre-configured modules, such as the floating-point unit. These result in predetermined optimal fixed floor plans.

Other soft processors, such as the NIOS II from Altera [42], support extending the instruction set by allowing users to create custom instructions. FiT does not use a fixed floor plan scheme. To facilitate portability, the HDL model of our custom soft processors does not take advantage of any vendor-dependent optimizations or pre-compiled synthesis libraries. As will be discussed in Chapter 3, we do not use instruction set extensions, as these increase the core density and require that the source code or the tools that compile the source code be updated to handle the new instructions.

Bush [43], in his Ph.D. thesis, proposed the synthesis of subset processors. However, since this was incidental to his primary research focus, he did not address the theory and applications of subset processors. However, more recently Yiannacouras et al. [44] have taken a more substantive stab at the subject; they have proposed a method similar to ours which they referred to as ISA subsetting, together with an application called the SPREE toolkit that generated subset processors. Unlike FiT, SPREE only uses a single structural processor template, similar to the one described in Section 5.2.1 and it does not have an automated end-to-end flow using either the source code or the object code as input to generate the custom soft processor. Yiannacouras et al. [44], also did not provide an overarching theoretical framework for subset processors.

#### 2.6 Summary

Earlier research on instruction set usage showed low instruction set utilization, however this research failed to show the relationship between instruction set utilization and microprocessor hardware utilization. While, previous work on subset processors lacked a theoretical framework, which made the analysis and comparison of subset processors difficult. To overcome these problems this work established the relationship between instruction set utilization and microprocessor hardware utilization and proposed a way to measure the relationship. Our work, also developed a theoretical framework for subset processors. The FiT toolkit was created to automatically synthesize custom subset processors that are based on our theoretical framework. These custom subset processors optimize the hardware utilization.

### Chapter 3

### Instruction Set Usage Analysis

#### 3.1 Introduction

The instruction set of a processor serves as an interface between the processor's hardware and the software applications seeking to run on that hardware. To the software engineer, the instruction set exposes a processor's functionality, while to the hardware engineer it is a measure of the hardware resources that will need to be implemented in the processor. Given two processors with the same bus size, but with different architectures, the one with a larger instruction set will expose more features or operations to the software applications. In addition, it will often require more hardware resources (as will be shown later in this study) and design effort to implement.

The software applications that execute on a processor are created by compiling source code that is written in a high-level programming language, such as C or Java, or they are hand-crafted using assembly instructions and an assembler. In both cases, the end result is an object file consisting of an ordered sequence of operations that are to be performed by the processor.

A number of empirical studies on instruction set usage, including the one presented in this work, have shown that most of the instructions in any instruction set are rarely used by the applications [19, 24, 20, 23]. If a processor's instruction

set is a measure of the hardware resources needed to implement the processor, then these results from the empirical studies suggest that most of the hardware resources on processors with a fixed instruction set architecture (ISA) are highly underutilized.

In this chapter we discuss the relationship between a processors instruction set and the hardware resources needed to support that instruction set, and define the core density measure. We also describe our instruction set usage experiments, present the results of these experiments and discuss their implications.

#### 3.2 Instruction Sets and Core Density

#### 3.2.1 Introduction

In this study we attempt to make a direct connection between instruction set usage and processor hardware requirements. We conducted instruction set usage experiments across a variety of existing ISAs using the SPEC CPU2006 [13] and SPECjvm2008 benchmark [14] applications written in C and Java. For the C applications, we used two compilers and it took into account different compiler optimizations. The results from these experiments confirm those of previous

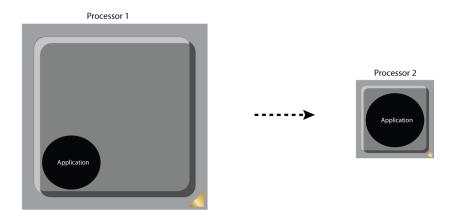

Figure 3.1: Transforming a fixed ISA processor into an exact ISA processor.

studies. We describe a way to measure the resource underutilization using a single instruction set usage measure, *core density*, in place of the two measures by Foster *et al.* We then propose a more efficient method of allocating hardware resources to support a given instruction set. The proposed technique generates application-specific processors that we term *exact processors*, where each processor's resources are mapped one-to-one to the processing needs of the applications that are set to execute on the processor, as shown by Processor 2 in Fig. 3.1.

#### 3.2.2 Instruction Sets and Hardware

A processor instruction is a directive to the processor that specifies the following: the instruction format; the operation to be performed, also known as the opcode; the source operands; the result operand; and the next instruction to be executed [45]. The instruction layout is illustrated in Fig. 3.2.

The instruction format is often expressed implicitly. The opcode encodes the type of transformation that is to be performed. There are four basic types of transformations for discrete information [46]:

- data transfer in space (for example, from one register to another),

- data transfer in time (storage),

- arithmetic operations, and

- logical operations.

The addresses of the source operands, result operand, and the next instruction may be expressed in several ways: by coordinate addresses, by implication, as immediate variables, or by association [45]. From now onwards, the terms instruction and opcode will be used interchangeably.

Let R be all of the hardware resources of the processor represented as functional units and I be the processor instruction set, where

$$R = \{r_1, \dots, r_M\}$$

and  $I = \{i_1, \dots, r_N\}.$  (3.1)

Let P be the power set of R. For any i where  $i \in I$ , let  $R_i$  represent the set of resources needed to implement the instruction where

$$R_i \in P$$

and  $R_i \subset R$ . (3.2)

Let  $R_I$  represent the resources needed to implement all the instructions in I, then

$$R_I = \bigcup_{i=1}^N R_i. \tag{3.3}$$

Resources that are not directly related to the implementation of any instruction will be referred to as a constant  $M_{const}$ , where

$$M_{const} = |R - R_I|. (3.4)$$

One example of such a resource is the hardware needed to implement pipelining.

As the number of shared resources decreases, that is as

$$\left| \bigcap_{i=1}^{N} R_i \right| \to 0, \tag{3.5}$$

the processor's performance improves. An example of this relationship is the improved performance of directly-implemented processors versus their microprogrammed versions.

With regards to hardware requirements, in directly-implemented processors there is a one-to-one function f, such that  $f: I \mapsto P$ . As the number of instructions in I increases, so does  $|R_I|$ .

Figure 3.2: The Instruction Vector.

In the case of microprogrammed processors, f is not one-to-one; several instructions may map onto one set of resources. However, each instruction represents a distinct operation, and this distinction is captured in the microinstructions used to describe it. All the sets of microinstructions and the lookup tables matching them to their corresponding instructions are stored in the control memory. Wisniewska et al. [47] found that as the number of microinstructions was increased by a factor of 3, the amount of control memory required to store them increased by a multiple of 54, suggesting an exponential growth in hardware requirements. Jian-Lun [48] notes that for some processors (including the Intel x86), the control memory takes up 50% of the area on the chip.

We conclude that regardless of whether a processor is directly-implemented or it is microprogrammed,

$$|I| \propto |R_I|. \tag{3.6}$$

#### 3.2.3 Instruction Subsets

Applications that execute on a processor use a set of instructions, which we will refer to as the *application instruction set*. Let A represent this set. The application instruction set is a subset of the processor instruction set, that is

$$A \subset I.$$

(3.7)

The number of possible application instruction sets, N, is

$$N = 2^{|I|}. (3.8)$$

The resources required to implement  $R_A$  the application-specific processor for A are,

$$R_A = \bigcup_{i=1}^{|A|} R_i \tag{3.9}$$

where,

$$R_A \subset R_I. \tag{3.10}$$

From Equation (3.7), we have

$$|A| \leqslant |I| \tag{3.11}$$

and from Equation (3.10), we have

$$|R_A| \leqslant |R_I|. \tag{3.12}$$

The results of the experiments presented below show that for the benchmark applications,

$$A \ll I. \tag{3.13}$$

Now using Equations (3.6), (3.12) and (3.13) we have

$$|R_A| \ll |R_I|. \tag{3.14}$$

That is, the average application-specific processor requires much less hardware resources than the processor that implements the complete instruction set. The next Section describes a measure that can be used to compare the resources between the two processors in Equation (3.14).

We will refer to the processor that implements the complete processor instruction set as a general-purpose core (GPC), while the processor that implements only the application instruction sets that will target it, we will call an exact processor core (EPC). There is another type of core that allows for run-time extensions to the GPC, which we will refer to as the extensible processor core (XPC). The Xtensa processor from Tensilica provides an example of an XPC [49]. Since, in every case, the  $GPC \subseteq XPC$ , the ISA utilization of the XPC is at best only equal to that of the GPC. Therefore, we will only address the relationship between the GPC and the EPC in this study.

#### 3.2.4 Core Density

Given a set of applications that have been compiled to run on a given ISA, we define the applications' core density  $(\eta)$  as

$$\eta = \frac{\text{Amount of hardware resources needed to implement a GPC}}{\text{Amount of hardware resources needed to implement an EPC}}$$

(3.15)

For example, assume that we have an application that uses 22% of the target ISA and  $M_{const} = \emptyset$ , then the application's core density  $\eta = 100/22 = 4.5$ . That is, the hardware resources of four and a half EPC modules are equivalent to the resources of a single GPC module that implements the target ISA.

Before discussing the relationship between our core density metric and the first measure on opcode usage proposed by Foster *et al.* [19], we will briefly describe the latter. The number of bits,  $B_{op}$ , used to encode any opcode from the instruction set I has to be

$$B_{op} \geqslant log_2|I|. \tag{3.16}$$

Let  $p_k$  represent the probability that the k-th opcode is used by the processor, then the average number of bits of information contained in each opcode,  $b_I$ , is

$$b_I = -\sum_{k=1}^{|I|} p_k(\log_2 p_k) \tag{3.17}$$

If all opcodes are equally probable, then

$$p_k = \frac{1}{|I|}$$

and  $b_{I-max} = log_2|I|$  (3.18)

From Equations (3.16) and (3.18) we see that

$$b_{I-max} \leqslant B_{op} \tag{3.19}$$

According to Foster *et al.* [19], the relative difference between  $b_I$  and  $b_{I-max}$  is a measure of the utilization of any particular set of opcodes.

Now, let us consider an application with an instruction set A that is set to execute on the application-specific processor, in this case:

$$b_A = b_{A-max} \tag{3.20}$$

since all the opcodes in A are utilized, and thus are equally probable. Also,

$$b_{I-max} = \alpha b_{A-max} \tag{3.21}$$

where  $\alpha \geqslant 1$ , since  $|I| \geqslant |A|$  more bits are required to represent each opcode in the processor instruction set than in the application instruction set. The core density,  $\eta$ , is given by

$$\eta = \frac{\alpha |I| + M_{const}}{\alpha |A| + M_{const}} = \frac{\alpha(2^{b_I}) + M_{const}}{\alpha(2^{b_A}) + M_{const}}$$

(3.22)

and from Equations (3.20), (3.21) and (3.22) we have

$$\eta = \frac{\alpha(2^{b_I}) + M_{const}}{\alpha(2^{(\frac{b_{I-max}}{\alpha})}) + M_{const}}.$$

(3.23)

From Equation (3.23) we see that core density and the first measure in Foster *et al.* [19] are both related to  $b_I$  and  $b_{I-max}$ .

The second measure proposed by Foster et al. [19] estimates the effort needed to recode an application when the number of opcodes available to the compiler is reduced after an initial unconstrained compilation. Let us consider an application instruction set, A, and a compiler that is constrained to use only the N most frequently used opcodes in A to recompile the application. We will call the resulting application instruction set  $A_c$ . Clearly  $A_c \subseteq A$  and  $|A_c| = N$ . The second metric proposed by Foster et al. [19] measures the effort required to recompile the code that uses instructions in set A to code that only uses instructions in set  $A_c$ . They determined that the effort required is proportional to  $e^{-\beta N}$ , where  $\beta$  is a constant.

Jones [50] and others have demonstrated abstract processors that have an in-

struction set consisting of only one opcode. In other words, a compiler can be constrained until N=1 if the compiler supports this universal opcode.

To illustrate the process of constraining a compiler, let us look at an example. Suppose we have an application, which when compiled by an unconstrained compiler has an application instruction set,  $A_3$ , consisting of three opcodes; IF...THEN, NOT, and OR, with the first opcode in this list as the most frequently used. For ease of manipulation, we will represent these opcodes by the logic symbols  $\Rightarrow$ ,  $\neg$ , and  $\vee$ , respectively. So,

$$A_3 = \{ \Rightarrow, \neg, \vee \} \tag{3.24}$$

We further suppose that our compiler is set to recognize the following equivalences:

$$(p \Rightarrow q)$$

iff  $(\neg p \lor q)$

$\neg p$  iff  $(p \Rightarrow false)$  (3.25)

If the compiler is now constrained to N=1, then using the equivalences in Equation (3.25) the object code using  $A_3$  can be recompiled into code that uses application instruction set  $A_1$ , where

$$A_1 = \{ \Rightarrow \}. \tag{3.26}$$

Note that the transformation from  $A_3$  to  $A_1$  often comes at the cost of more instructions (larger program size) and/or slower execution, since the opcodes that are stripped out of  $A_3$  implement their operations faster than the transformed IF...THEN instruction. We will discuss later how by increasing  $\eta$ , this performance penalty can be mitigated.

The core density for an application using a compiler that is constrained to only use the N most popular opcodes and targeting a processor with an instruction set I is

$$\eta = \frac{\alpha |I| + M_{const}}{\alpha N + M_{const}} \tag{3.27}$$

Table 3.1: Architectures Studied

| Architecture | Machine Type | Implementation | Unique Opcodes |

|--------------|--------------|----------------|----------------|

| JVM          | Stack        | Software       | 204            |

| MIPS64       | Register     | Hardware       | 1182           |

| PowerPC      | Register     | Hardware       | 533            |

| x86          | Register     | Hardware       | 659            |

| x86-64       | Register     | Hardware       | 1101           |

## 3.3 ISA Usage Experiments

In our experiments we only considered opcodes and their static usage. We varied four factors; the benchmark applications, the ISA of the target processors, the compilers, and the compiler optimizations. Below is a description of how the experiments were setup.

#### 3.3.1 Architectures and Compilers

A virtual machine with 64-bit version of the Linux (kernel 2.6.32) Ubuntu 10.40 LTS distribution was used as the platform for all the experiments. We used the GNU Compiler Collection (gcc) and the Portable C Compiler (pcc) to build the C benchmark applications. For the Java applications we used the pre-compiled class files that came with the JVM benchmark applications. We also used the GNU Compiler for Java (gcj) to compile the JVM benchmark applications' source code to directly target the x86-64 platform.

We used gcc version 4.4.3 with the m32 flag set and pcc version 1.0 as the native C compilers. The crosstool-ng was used to build the gcc cross-compilers for the MIPS64, PowerPC, and x86-64 architectures, which we will refer to as the hardware processors. We determined the number of unique opcodes for each of the hardware processors in Table 3.1 from the manufacturers' product manuals.

Table 3.2: C Benchmark Applications

| Application  | Description                                                         | Type           |

|--------------|---------------------------------------------------------------------|----------------|

| 401.bzip2    | Data compression tool                                               | Integer        |

| 403.gcc      | C language optimizing compiler                                      | Integer        |

| 429.mcf      | Combinatorial optimization tool for single-depot vehicle scheduling | Integer        |

| 433.milc     | Quantum chromodynamics simulation tool                              | Floating Point |

| 456.hmmer    | Gene sequence database search application                           | Integer        |

| 458.sjeng    | Game playing (chess & variants) and pattern recognition application | Integer        |

| 464.h264ref  | Video compression                                                   | Integer        |

| 470.lbm      | Computational fluid dynamics using Lattice<br>Boltzmann method      | Floating Point |

| 482.sphinx3  | Speech recognition system                                           | Floating Point |

| 999.specrand | Pseudorandom number generator                                       | Floating Point |

#### 3.3.2 Benchmark Applications

The benchmark applications were divided into two categories: the C applications and the Java applications. The ten C benchmark applications are listed in Table 3.2 and they are all part of the SPEC CPU2006 benchmark suite [13]. The applications in this category are further divided, according to their primary computation type, into two groups: floating-point or integer.

The eight Java benchmark applications are listed in Table 3.3 and they are all part of the SPECjvm2008 benchmark suite [14]. Only the class files from this benchmark suite have been used; we did not compile any of the source code.

#### 3.3.3 Method

All the C applications were compiled three times with the gcc compilers, and with each compilation a different optimization scheme was used together with the -S option to generate assembler files instead of binary files. In the first iteration there is no optimization, in the second the applications were optimized for size (-Os flag), and in the final iteration they were optimized for speed (-O3 flag). All

Table 3.3: Java Benchmark Applications

| Application | Description                                                       |

|-------------|-------------------------------------------------------------------|

| Compiler    | Compiles a set of .java files using the OpenJDKfront end compiler |

| Compress    | Compresses data using a modified Lempel-Ziv method (LZW)          |

| Crypto      | Encrypt & decrypt samples using AES, DES and RSA protocols        |

| MPEGaudio   | MP3 audio decoding                                                |

| Serial      | Serializes and deserializes primitives and objects                |

| Startup     | Starts each benchmark for one operation                           |

| Sunflow     | Tests graphics visualization                                      |

| XML         | XML.transform and XML.validation                                  |

the C applications were also compiled twice with the pcc compilers, and with each compilation a different optimization option was used. In the first pcc iteration there was no optimization; in the second, the applications were optimized for speed (-O flag).

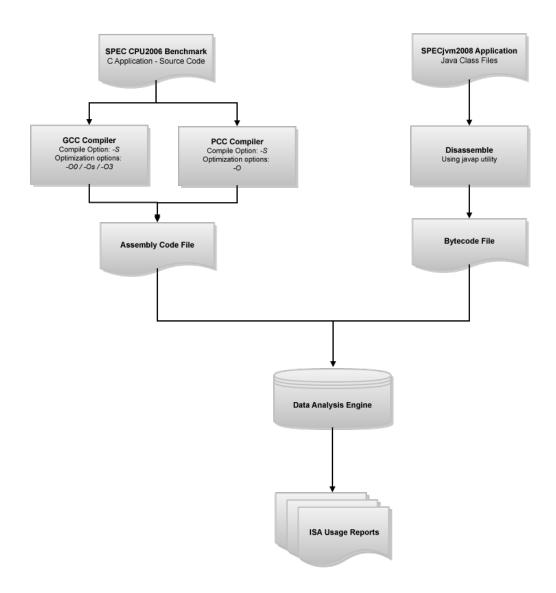

In the case of the Java applications, the classfiles shown in step 3 of Fig. 3.3, provide the starting point for the data generation process. The classfiles were disassembled using the javap utility into JVM assembly files.

The opcodes are extracted by parsing the assembly files for each run and collating them into a single flat file. The data analysis of the raw data files and the generation of the tables and charts were performed using Microsoft Excel.

## 3.4 Results and Discussion

In this Section we present the results of the ISA utilization experiments and discuss their implications.

## 3.4.1 Compilers

For the physical architectures, the same source code was used with the gcc and pcc compilers. These two compilers follow different compilation strategies, as

Figure 3.3: Opcode extraction and analysis process for each application.

Figure 3.4: Instruction usage by instruction type and compiler.

displayed by the relative differences in the instruction types of the compiled code in Fig. 3.4.

However, with regards to the relationship between instruction set utilization and architecture, the choice of compiler did not make a difference, as seen in Fig. 3.5. The average utilization for all the applications in the C benchmark set is 2% higher that when the applications are considered individually. The PowerPC and x86 architectures have higher utilization rates compared to the MIPS and x86-64 architectures. The latter architectures have larger instruction sets.

Given the relative invariance of the instruction set utilization when different compilers are used, we will, for the remainder of the study, only considers benchmark data generated using the gcc compiler.

## 3.4.2 Optimizations

The impact of the compiler optimizations on the size of the application is shown in Fig. 3.6. The optimization for speed reduced the average application size for all the hardware processors when compared with the un-optimized applications. The optimization for size results are as expected; across all the platforms, the size of the applications is significantly reduced when compared to both the un-optimized case and the case in which the applications are optimized for speed. No compiler optimization experiments were performed for the software processor since, for this processor, we only used the class files that were provided with the SPECjym2008 benchmark suite.

While the compiler optimizations affect the program size, we observed that they did not have a significant impact on ISA utilization, as shown in Fig. 3.7. With the exception of the PowerPC architecture, the differences between any pair of results in the ISA utilization-versus-compiler optimizations all fall within a 3% margin. The margin for the PowerPC architecture is 6%. Based on this observation, from this point forward we will only discuss the results for the applications that were optimized for size.

#### 3.4.3 Instruction Set Usage

The number of instructions used by each application is shown in Table 3.4 for the hardware processors and in Table 3.6 for the JVM or the software processor. The x86 and the x86-64 platforms are what were traditionally called CISC-based architectures that use more instructions than the other two hardware processors,

Figure 3.5: Average ISA utilization by target architecture and compiler.

Figure 3.6: Average instruction counts by compiler target and optimization.

Figure 3.7: Average ISA utilization by compiler target and optimization.

Table 3.4: Number of instructions (opcodes) used

| Application\Architecture       | MIPS    | PowerPC | x86     | x86-64  |

|--------------------------------|---------|---------|---------|---------|

| 401.bzip2                      | 17,543  | 15,104  | 12,465  | 10,095  |

| 403.gcc                        | 801,853 | 630,836 | 616,909 | 438,257 |

| 429.mcf                        | 2,371   | 2,135   | 2,003   | 1,562   |

| 433.milc                       | 27,755  | 21,279  | 20,954  | 16,191  |

| 456.hmmer                      | 68,736  | 56,292  | 57,601  | 43,726  |

| 458.sjeng                      | 29,999  | 25,391  | 19,620  | 14,331  |

| 464.h264ref                    | 124,775 | 107,945 | 98,543  | 77,030  |

| 470.lbm                        | 3,953   | 2,274   | 2,275   | 1,875   |

| 482.sphinx3                    | 42,780  | 35,486  | 34,450  | 27,557  |

| 999.specrand                   | 150     | 121     | 108     | 77      |

| Average number of instructions | 111,992 | 89,686  | 86,493  | 63,070  |

traditionally called RISC-based. This result is at odds with one of the widely held views that CISC-based applications require fewer instructions than RISC-based ones. However, there may be two potential explanations for this result. Firstly, the distinction between RISC and CISC in most modern processors is no longer clear-cut. For example, RISC architecture should have fewer opcodes, but a look at the number of opcodes for each processor in Table 3.1 reveals that the MIPS64 processor has more opcodes than the x86-64. Secondly, the discrepancy may be due to the fact that the compiler produces more compact code for the CISC-based processors. The CISC-based processors have been more popular in the market place and hence more resources may have been committed to optimizing compilers for the processors.

In order to estimate  $M_{const}$ , we assume that 50% of the processor consists of instruction-dependent hardware. This estimate is in line with findings of Jian-Lun [48]. Using this approximation,  $\eta$  reduces to

$$\eta = \frac{|I|}{|A|}.\tag{3.28}$$

The ISA utilization results for the hardware processors, expressed in terms of core density, are presented in Table 3.5.

Table 3.5: Application Core Densities

| $\fbox{ Application \backslash Architecture }$ | MIPS  | PowerPC | x86   | x86-64 |

|------------------------------------------------|-------|---------|-------|--------|

| 401.bzip2                                      | 20.38 | 5.03    | 10.14 | 19.32  |

| 403.gcc                                        | 16.42 | 3.37    | 7.40  | 13.59  |

| 429.mcf                                        | 30.31 | 8.20    | 16.07 | 29.76  |

| 433.milc                                       | 20.74 | 5.38    | 8.45  | 18.35  |

| 456.hmmer                                      | 16.19 | 4.26    | 7.57  | 13.43  |

| 458.sjeng                                      | 17.91 | 5.03    | 9.98  | 18.35  |

| 464.h264ref                                    | 16.19 | 3.73    | 7.01  | 13.59  |

| 470.lbm                                        | 23.64 | 8.46    | 12.43 | 25.60  |

| 482.sphinx3                                    | 16.65 | 4.33    | 8.04  | 14.68  |

| 999.specrand                                   | 39.40 | 15.68   | 24.41 | 47.87  |

| Average $\eta$                                 | 21.78 | 6.35    | 11.15 | 21.45  |

| $\eta/10	ext{-App Set}$                        | 15.76 | 3.05    | 6.72  | 11.35  |

| Max. $\eta/10$ -App Set                        | 39.40 | 15.68   | 24.41 | 47.87  |

Considering the case of the x86-64 processor, we note that if it were executing any one of the ten applications, its average core density would be 21.5. However, if it were only executing the 999 specrand benchmark application its core density would be 47.9. This indicates that for this application, the traditional processor model (or GPC) fails to utilize more than 98% of the processor resources, since only 1 exact core is required. However, resources equivalent to 48 exact cores are deployed in an existing traditional processor. Based on these results, a multicore solution may be pursued in order to improve utilization and performance by several orders of magnitude, while using the same hardware resources as a traditional processor. For example, consider an embedded system that executes only the sphinx3 application. By designing an EPC for this application, forty eight such cores can be deployed using the same amount of hardware resources as one existing x86-64 processor. We also note that when using the exact processor model, resources do not need to be optimized for the average case; they can be optimized for the individual case and the resource utilization rate of a multi-core system is equal to the average of the resource utilization rates of its component cores. So, by using exact cores whose individual resource utilization rates have been maximized, the resulting multi-core system will have the maximum resource utilization rate.

If however, all ten applications were to run on the x86-64 processor, then let S be the set of all the applications. That is

$$S = \left\{ \frac{401.bzip2, 403.gcc, 429.mcf, 433.milc, 456.hmmer,}{458.sjeng, 464.h264ref, 470.lbm, 482.sphinx3, 999.specrand} \right\}.$$

The application instruction set for S is

$$\bigcup_{k \in S} A_k.$$

(3.29)

where  $A_k$  is the application instruction set of the k-th application generated by the compiler targeting the x86-64 processor. So for S, the core density, shown in the row for  $\eta/10$ -App Set in Table 3.5, is determined as

$$\eta = \frac{|P_{x86-64}|}{|\bigcup_{k \in S} A_k|} = 11.4. \tag{3.30}$$

This indicates that as more varied applications run on the processor, the utilization rate of the resources improves. However, even in this case, more than 90% of the processor's resources are not utilized.

Instruction-set usage statistics for the software processor are presented in Table 3.6. The average core density for the software processor is lower than that for the hardware processors, indicating better resource utilization by this processor. This may be due to the fact that the JVM has the least number of unique opcodes of all the processors in this study. As the number of opcodes in a processor approaches 1, the core density also approaches 1. In other words, ISA utilization approaches 100%.

## 3.4.4 Top N Instructions

The top 25 instructions account for more than 89% of all the instructions used by the applications, as shown in Fig. 3.8. This result confirms the locality of reference property of applications and is in line with the results of Adams and Zimmerman [20], and Hennessy and Patterson [22].

Table 3.6: JVM instruction-set usage statistics

| Application             | Core Density | Opcodes Used | Top50 Opcodes |  |

|-------------------------|--------------|--------------|---------------|--|

| Compiler                | 2.83         | 1357         | 98%           |  |

| Compress                | 2.49         | 1041         | 97%           |  |

| Crypto                  | 3.52         | 939          | 100%          |  |

| MPEGaudio               | 4.43         | 149          | 100%          |  |

| Serial                  | 2.58         | 2041         | 97%           |  |

| Startup                 | 4.16         | 363          | 100%          |  |

| Sunflow                 | 6.38         | 57           | 100%          |  |

| XML                     | 2.76         | 1645         | 96%           |  |

| Average                 | 3.64         | 949          | 98%           |  |

| $\eta$ /10-App Set      | 1.77         |              |               |  |

| Max. $\eta$ /10-App Set | 6.38         |              |               |  |

Figure 3.8: TopN opcodes used as a percentage of total opcodes used.

Selecting for the constrained compiler, we get the core densities shown in Table 3.7, and these core densities are in the range of the maximum cases in Table 3.5 and Table 3.6.