# Development of High-Speed Silicon Devices and Their Design with Advanced Physical Models

Hiroshi Goto

January 1999

# Abstract

In the field of high-speed silicon devices, silicon bipolar junction transistors (BJTs) had played a major role from the 1970s to the end of the 1980s. However, in the 1990s complementary metal-oxide-semiconductor (CMOS) field effect transistors (FETs) have been replacing their position. This dissertation explains the reasons why BJTs were suitable for high-speed operation. This is concluded from the development of technologies for BJTs and the analyses of devices fabricated with these technologies. At the same time it clarifies why they were replaced by CMOS transistors. The BJT's high driving capability and large power dissipation were the both sides of a sword.

In the case of high-speed CMOS devices, the driving current of MOSFET should be large enough, and device design must be based on precise comprehension of carrier transport in MOSFETs. Therefore, we need accurate device model as well as rigid device-structure information obtained by experiments. This dissertation describes the device design methodology not only based on inverse modeling to extract device structures consistent with all kinds of experimental results but also based on simulations by generalized hydrodynamic model and full-band Monte Carlo model. The background and concept of the methodology is also discussed, and its necessity in future development is clarified. Moreover, hot carrier modeling is discussed by employing full-band Monte Carlo device simulation. Also, this dissertation clarifies the fact there is no experimental evidence for the difference between the surface and bulk impact ionization mechanism in silicon. The reported difference in the literature was only caused by an unsound application of the local field model and was just an artifact.

Finally, by using these sophisticated models, the saturation drain current as well as hot carrier effects of subquarter micron MOSFETs are analyzed. MOSFET design strategy for the 0.1  $\mu$  m regime is discussed and the importance of shallow junction for source/drain extension is also clarified.

# Acknowledgments

I greatly acknowledge Professor Dr. Mitiko Miura-Mattausch for supporting the preparation of this doctoral dissertation that is submitted to Hiroshima University in Japan. I express my best thanks to my coworkers at Fujitsu Limited, especially Dr. Christoph Jungemann, who was with Fujitsu Kawasaki in Japan from April, 1995 to March, 1997 as a post-doctoral visiting researcher and mainly contributed to the development of the full-band Monte Carlo device simulator FALCON, and Mr. Seiichiro Yamaguchi for the major contribution to the development of the inverse modeling assisting program MOSFIT. I also acknowledge my current and former colleagues, Mr. Kaina Suzuki for the development of the two-dimensional process simulator FIPS2, Mr. Yoji Nagase for the development of the ac analysis routine for the two-dimensional device simulator BIP2DAN, and Mr. Kenji Hashimoto for the development of the transient analysis routine of the same program. In addition I owned quite much to the people who worked together since my joining Fujitsu Limited in Kawasaki, to develop not only bipolar device technologies such as IOP-II, U-FOX, ESPER, but also quarter and subquarter micron CMOS technologies. Finally, I specially acknowledge my wife for her daily support to my work these ten years.

To my wife and children

# **Table of Contents**

| Abstract                                                            | ii  |

|---------------------------------------------------------------------|-----|

| Acknowledgments                                                     | iii |

| Chapter 1 Introduction                                              |     |

| <ul><li>1.1 Motivation</li><li>1.2 Scope and Organization</li></ul> |     |

| Chapter 2 Development of High-Speed Silicon Bipolar Devices         |     |

| 2.1 Historical Back Ground                                          |     |

| 2.2 Trench Isolation Techniques                                     |     |

| 2.2.1 Introduction                                                  | 5   |

| 2.2.2 Trench Isolation by Oxide and Polysilicon                     | 7   |

| 2.2.3 Trench Isolation with Thick Field Oxide                       | 12  |

| 2.2.4 Benefits and Device Performance.                              | 15  |

| 2.2.5 Limiting Aspects and Recent Improvements                      | 18  |

| 2.2.6 Conclusion                                                    | 19  |

| 2.3 Polysilicon Self-Aligned Structures                             |     |

| 2.3.1 Introduction                                                  | 19  |

| 2.3.2 Double Polysilicon Self-Aligned Structure                     | 19  |

| 2.3.2.1 One-Mask Process                                            | 20  |

| 2.3.2.2 Two-Mask Process                                            | 25  |

| 2.3.2.3 Three-Mask Process                                          |     |

| 2.3.3 Single Polysilicon Self-Aligned Structure                     | 29  |

| 2.3.4 Sidewall Base Contact Structures                              | 30  |

| 2.3.5 Polysilicon Emitter and Emitter-Base Heterojunction           |     |

| 2.3.6 Conclusion                                                    | 37  |

| 2.4 Physics-Based Bipolar Transistor Design                         |     |

| 2.4.1 Introduction                                                  | 37  |

| 2.4.2 Two-Dimensional Process/Device Simulation System              |     |

| 2.4.3 Simulation of Pedestal-Collector Transistors                  |     |

| 2.4.3.1 Process Simulation.                                   |    |

|---------------------------------------------------------------|----|

| 2.4.3.2 Device Simulation                                     | 41 |

| 2.4.4 Favorable Process Condition for Pedestal Collector      | 44 |

| 2.4.5 Application to ECL Circuits                             | 46 |

| 2.4.6 Conclusion                                              | 46 |

| Chapter 3 Performance Estimation of High-Speed Bipolar Device | 47 |

| 3.1 Introduction.                                             |    |

| 3.2 Strategy to Estimate ECL-Circuit Performance              |    |

| 3.3 Optimization of ECL-Circuit Performance                   |    |

| 3.4 Favorable Silicon BJT Features and Its Limitation         |    |

| 3.5 Conclusion                                                |    |

| Chapter 4 Design Concept for High-Speed CMOS Device           | 60 |

| 4.1 Introduction                                              |    |

| 4.2 Requirements for High-Speed CMOS Device                   |    |

| 4.3 Quarter and Subquarter Micron CMOS Technologies           |    |

| 4.3.1 Quarter Micron CMOS Technology                          |    |

| 4.3.2 Subquarter Micron CMOS Technology                       |    |

| 4.4 Conclusion                                                |    |

| Chapter 5 Inverse Modeling Technique for MOSFET Design        | 65 |

| 5.1 Introduction                                              |    |

| 5.2 Inverse Modeling Procedure                                |    |

| 5.3 Extraction of a Deep Submicron MOSFET Structure           |    |

| 5.4 Saturation Drain Current and Substrate Current            | 77 |

| 5.5 Device Characteristic Prediction                          | 79 |

| 5.6 Conclusion                                                | 80 |

| Chapter 6 Carrier Transport in MOSFETs                        | 81 |

| 6.1 Introduction                                              | 81 |

| 6.2 Modeling of Carrier Transport in MOSFETs                  | 82 |

| 6.2.1 Particle-Based Model                                    | 82 |

| 6.2.1.1 Full-Band Monte Carlo Device Simulator - FALCON       | 83 |

| 6.2.1.2 Simulation Results by FALCON                     |     |

|----------------------------------------------------------|-----|

| 6.2.2 Fluid-Based Model                                  |     |

| 6.2.2.1 Hydrodynamic Model versus Energy Transport Model |     |

| 6.2.2.2 Generalized Hydrodynamic Model                   |     |

| 6.2.2.3 Guarantee of Simulation Accuracy by GHDM         | 89  |

| 6.3 Impact Ionization in MOSFETs                         | 90  |

| 6.3.1 Impact Ionization Models                           | 91  |

| 6.3.2 Surface Impact Ionization                          | 92  |

| 6.4 Conclusion                                           | 98  |

| Chapter 7 Physics-Based MOSFET Design                    | 99  |

| 7.1 Introduction                                         | 99  |

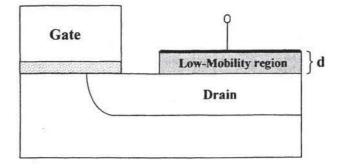

| 7.2 Hot Carrier Effects of nMOSFET                       | 100 |

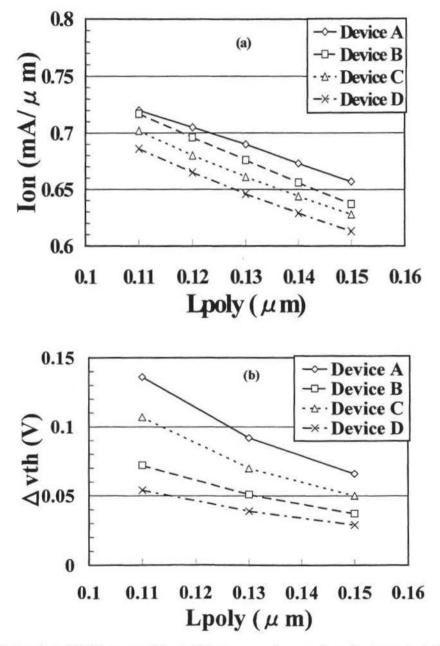

| 7.3 Physics-Based MOSFET Design                          | 104 |

| 7.4 Conclusion                                           |     |

| Chapter 8 Conclusion                                     | 107 |

| 8.1 Summary                                              | 107 |

| 8.2 Future Work                                          | 108 |

| Bibliography                                             | 110 |

| List of | f Papers |  |

|---------|----------|--|

|---------|----------|--|

# List of Tables

| able 2.1 Typical address access time of linear shrunk 1kb ECL RAMs using IOP-II17 |

|-----------------------------------------------------------------------------------|

| able 2.2 Calculated device parameters and BV <sub>CEO</sub>                       |

| able 5.1 Extracted parameters for each device and measurement data                |

| able 5.2 Extracted doping and structure-related parameters for a deep submicron   |

| nMOSFET (Lpoly=0.19 $\mu$ m). Gate oxide thickness is 6.3 nm and contact          |

| resistance is $160 \Omega \ \mu \ m$                                              |

# List of Figures

| Fig. 2.1 Fabrication process steps of a typical trench isolation technique                                                  |

|-----------------------------------------------------------------------------------------------------------------------------|

| Fig. 2.2 Unfavorable trench shapes caused by trench etching.                                                                |

| (a) Black silicon (b) Sub-trench (c) Bowing (d) Laterally etched undercut9                                                  |

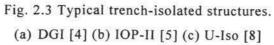

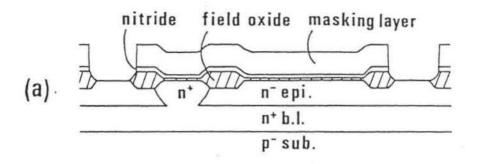

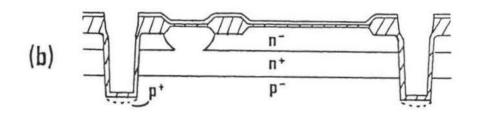

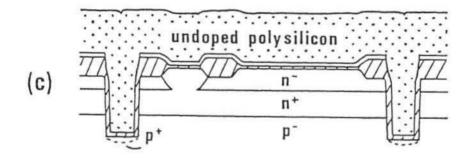

| Fig. 2.3 Typical trench-isolated structures.                                                                                |

| (a) DGI [4] (b) IOP-II [5] (c) U-Iso [8]11                                                                                  |

| Fig. 2.4 Fabrication process steps of U-FOX                                                                                 |

| Fig. 2.5 Fabrication process steps of [10]14                                                                                |

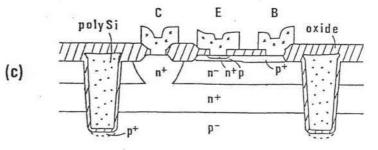

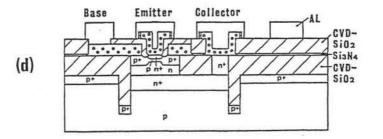

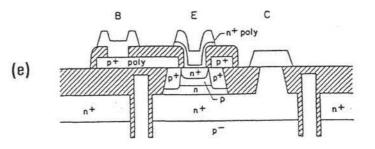

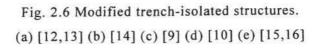

| Fig. 2.6 Modified trench-isolated structures.                                                                               |

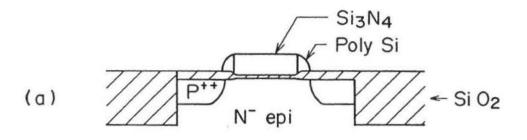

| (a) [12,13] (b) [14] (c) [9] (d) [10] (e) [15,16]16                                                                         |

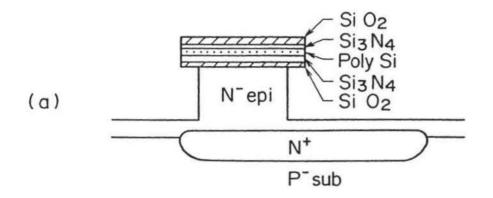

| Fig. 2.7 SST-1A fabrication steps [31]21                                                                                    |

| Fig. 2.8 Cross-sectional view of the SST-1B transistor with selectively implanted pedestal                                  |

| collector [32]                                                                                                              |

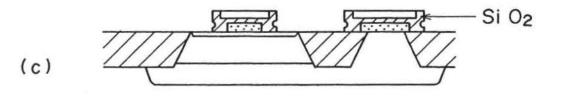

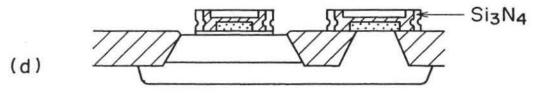

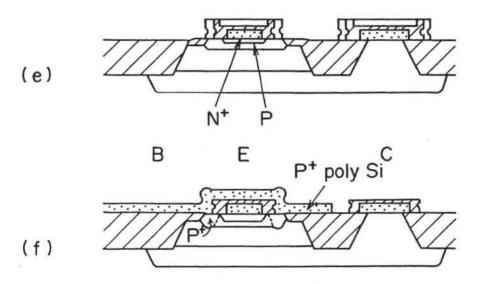

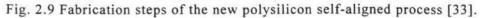

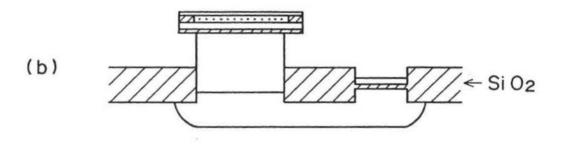

| Fig. 2.9 Fabrication steps of the new polysilicon self-aligned process [33]24                                               |

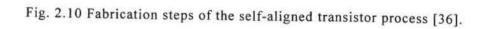

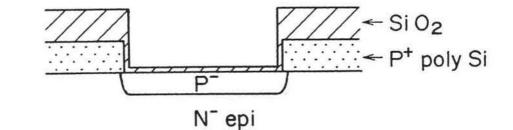

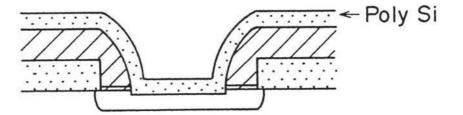

| Fig. 2.10 Fabrication steps of the self-aligned transistor process [36]26                                                   |

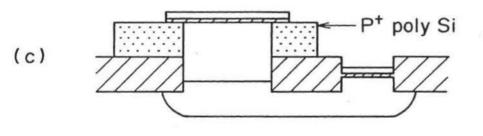

| Fig. 2.11 Fabrication steps of the double polysilicon self-aligned process using coupling                                   |

| base implantation [52]                                                                                                      |

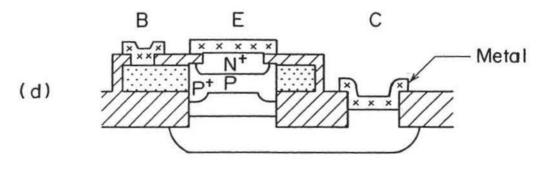

| Fig. 2.12 Fabrication steps of the single polysilicon self-aligned process [66]31                                           |

| Fig. 2.13 Fabrication steps of the SICOS process [67]                                                                       |

| Fig. 2.14 Fabrication steps of the SICOS process modified by the TOSS process [69]34                                        |

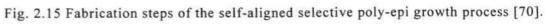

| Fig. 2.15 Fabrication steps of the self-aligned selective poly-epi growth process [70]36                                    |

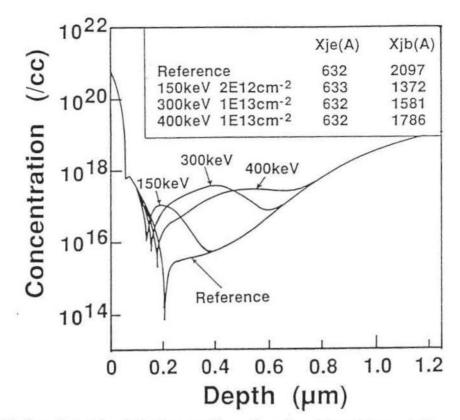

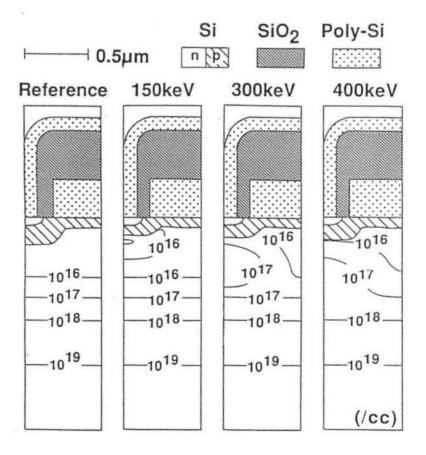

| Fig. 2.16 One-dimensional doping profiles of analyzed transistors at the center of                                          |

| emitter40                                                                                                                   |

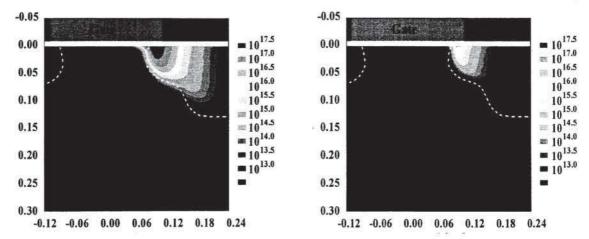

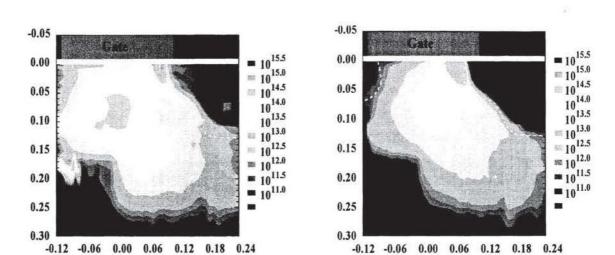

| Fig. 2.17 Two-dimensional doping distributions with concentration equi-contour lines40                                      |

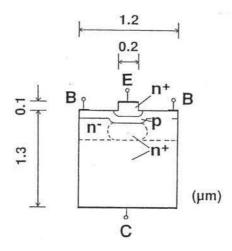

| Fig. 2.18 Schematic cross section of an analyzed transistor. The device length is $1.0 \mu$ m41                             |

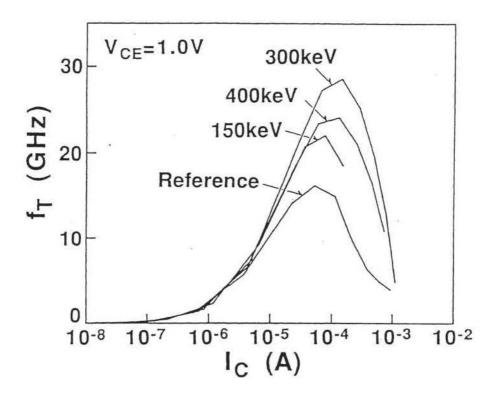

| Fig. 2.19 Cutoff frequency $(f_T)$ versus collector current $(I_c)$ characteristics                                         |

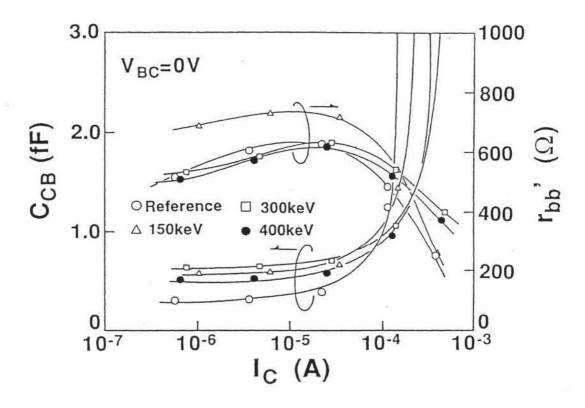

| Fig. 2.20 AC base resistance $(r_{bb})$ and base-collector capacitance $(C_{cb})$ versus collector                          |

| current (I <sub>c</sub> ) characteristics                                                                                   |

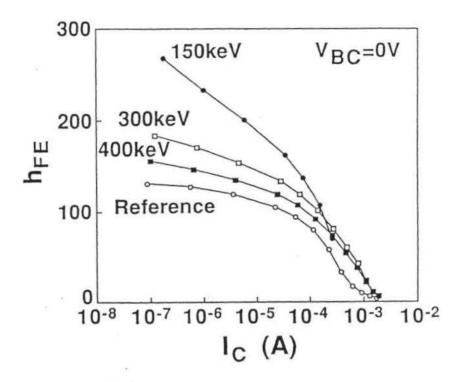

| Fig. 2.21 Current gain $(h_{FE})$ versus collector current $(I_c)$ characteristic                                           |

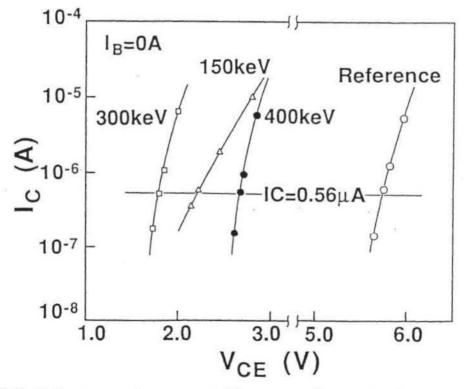

| Fig. 2.22 Collector-to-emitter current $(I_c)$ versus collector-to-emitter voltage $(V_{CE})$ where                         |

| the base currents terminate                                                                                                 |

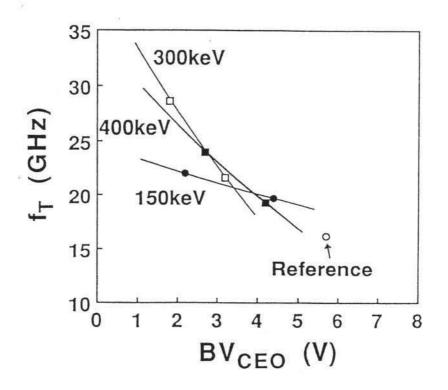

| Fig. 2.23 Relationship between $BV_{CEO}$ and $f_T$ for different phosphorus-ion-implanting                                 |

| conditions. Dose conditions; 150KeV with $2 \times 10^{12}$ /cm <sup>2</sup> , $1 \times 10^{12}$ /cm <sup>2</sup> ; 300KeV |

| with $1 \times 10^{13}$ /cm <sup>2</sup> , $2 \times 10^{12}$ /cm <sup>2</sup> ; 400KeV | with $1 \times 10^{13}$ /cm <sup>2</sup> , $2 \times 10^{12}$ /cm <sup>2</sup> 45 |

|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

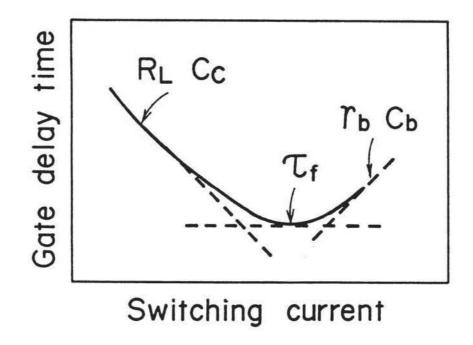

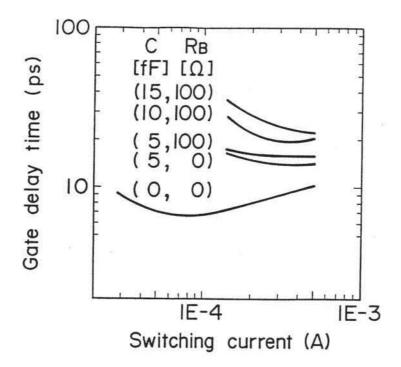

| Fig. 3.1 Gate delay time versus switching current per gate (arbitrary unit)48              |

|--------------------------------------------------------------------------------------------|

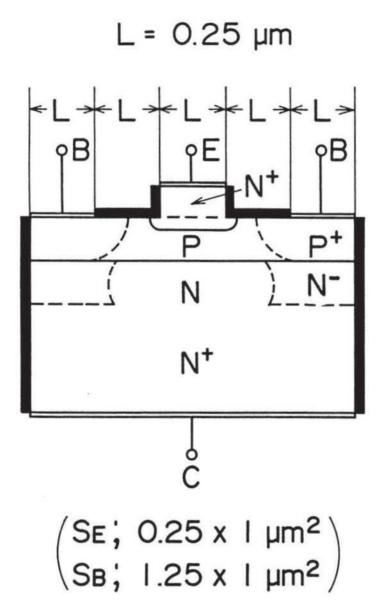

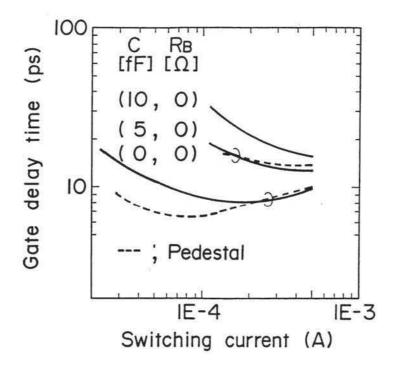

| Fig. 3.2 Schematic cross-section of the analyzed transistor                                |

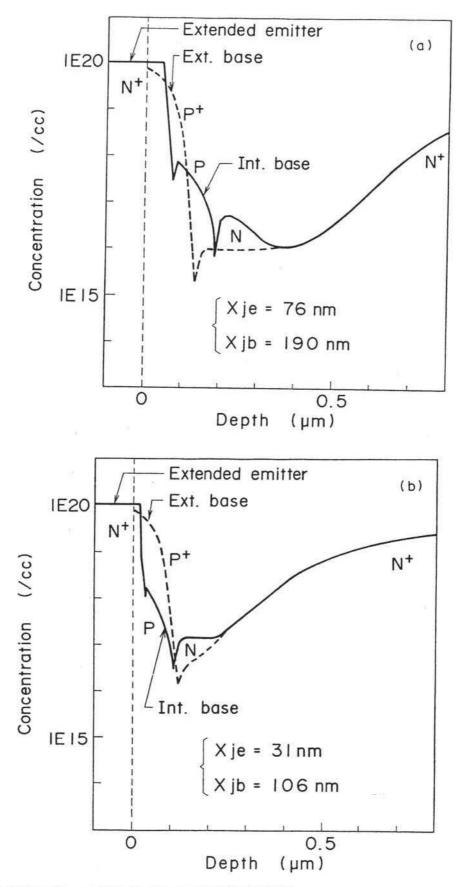

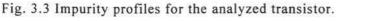

| Fig. 3.3 Impurity profiles for the analyzed transistor.                                    |

| (a) Selectively implanted pedestal collector profile.                                      |

| (b) Gradient collector profile                                                             |

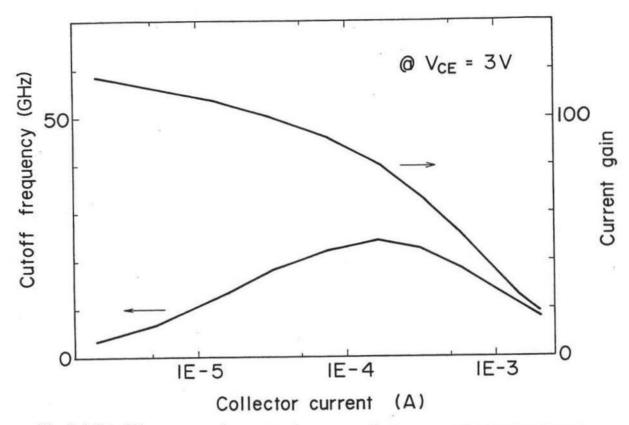

| Fig. 3.4 Cutoff frequency and current gain versus collector current (pedestal collector)52 |

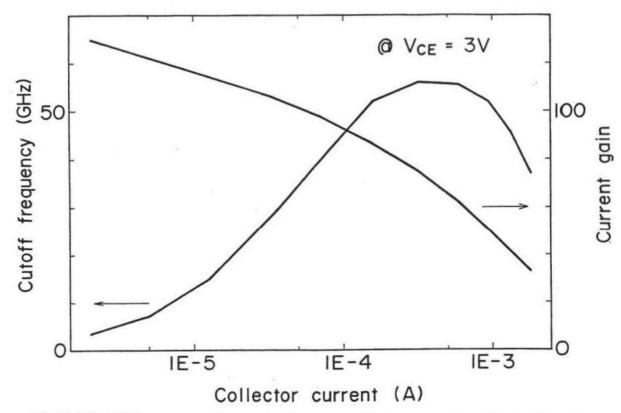

| Fig. 3.5 Cutoff frequency and current gain versus collector current (gradient collector)52 |

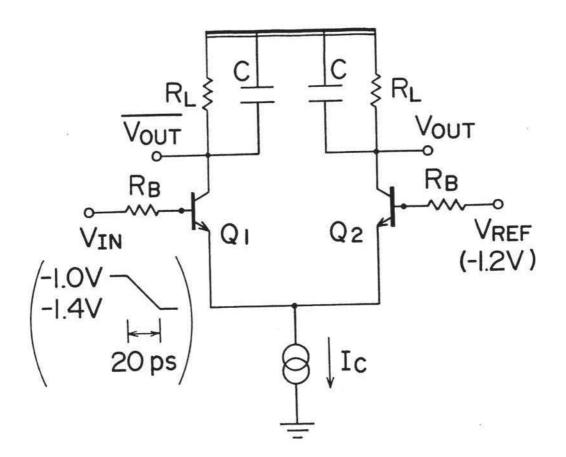

| Fig. 3.6 Analyzed circuit diagram                                                          |

| Fig. 3.7 Gate delay time versus switching current per gate (pedestal collector)55          |

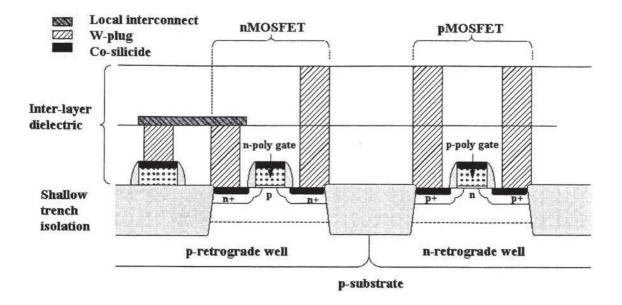

| Fig. 3.8 Gate delay time versus switching current per gate (gradient collector)            |

| Fig. 3.9 Schematic cross-section of the favorable BJT structure                            |

|                                                                                            |

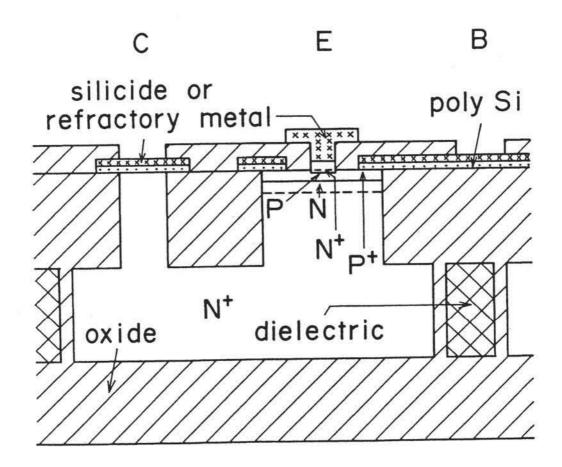

| Fig. 4.1 Cross-sectional structure of dual-gate CMOS device with CoSi <sub>2</sub> after   |

| contact plug formation                                                                     |

|                                                                                            |

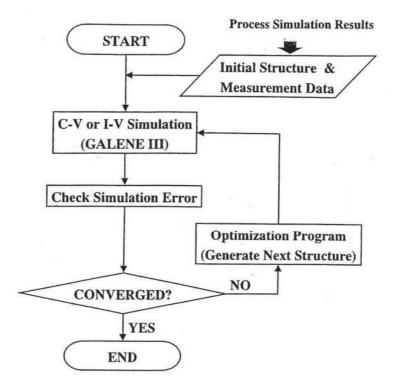

| Fig. 5.1 Flowchart of the "MOSFIT" program                                                 |

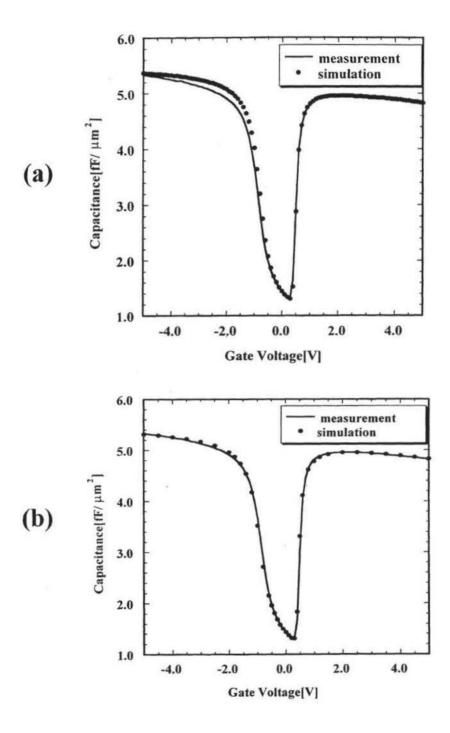

| Fig. 5.2 C-V characteristics of a large-area nMOSFET comparing measurement and             |

| simulation results after the gate oxide thickness and doping profile of polysilicon        |

| gate are determined.                                                                       |

| (a) Classical calculation. (b) Quantum mechanical calculation                              |

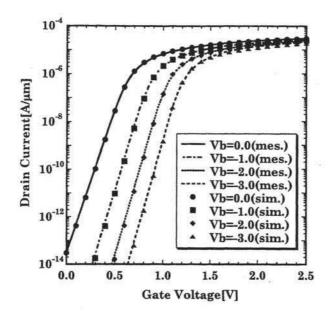

| Fig. 5.3 Subthreshold Id-Vg characteristics of a 1.0- $\mu$ m nMOSFET comparing            |

| measurement and simulation results after the channel doping profile is extracted.          |

| (Lines: measurement results, symbols: simulation results)                                  |

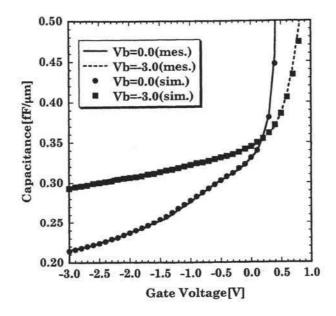

| Fig. 5.4 Cgd-V characteristics of a finger gate nMOSFET comparing measurement and          |

| simulation results after the source/drain doping profile is extracted. (Lines:             |

| measurement results, symbols: simulation results)                                          |

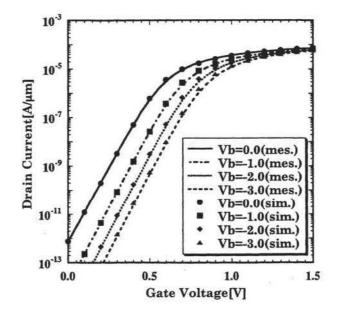

| Fig. 5.5 Subthreshold <i>Id-Vg</i> characteristics of a 0.19- $\mu$ m nMOSFET comparing    |

| measurement and simulation results after the channel doping profile is extracted.          |

| (Lines: measurement results, symbols: simulation results)                                  |

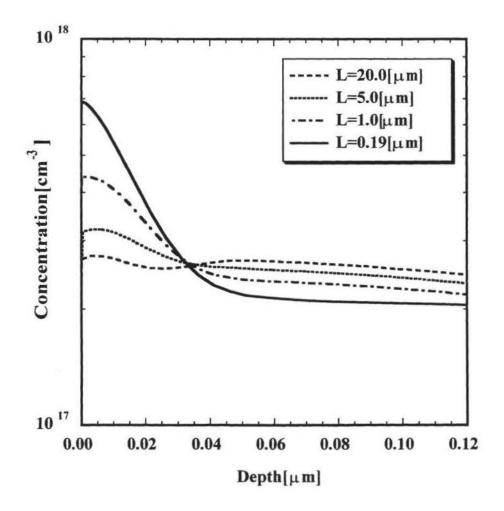

| Fig. 5.6 Mid-channel doping profiles depending on the gate length                          |

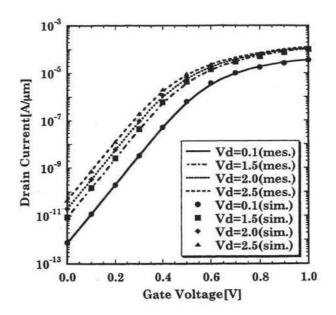

| Fig. 5.7 DIBL effect for a $0.19-\mu$ m nMOSFET comparing measurement and simulation       |

|                                                                                            |

| results after the channel doping profile and gate length are determined. (Lines:           |

х

| measurement results, symbols: simulation results)                                                   |

|-----------------------------------------------------------------------------------------------------|

| Fig. 5.8 Implementation of the source/drain contact resistance for linear Id-Vg                     |

| calculation                                                                                         |

| Fig. 5.9 Linear Id-Vg characteristics comparing measurement and simulation results                  |

| including source/drain contact resistance                                                           |

| Fig. 5.10 Final two-dimensional structure and doping profile of a 0.19- $\mu$ m nMOSFET.            |

| (Unit; $\mu$ m for axes and cm <sup>-3</sup> for contour lines)                                     |

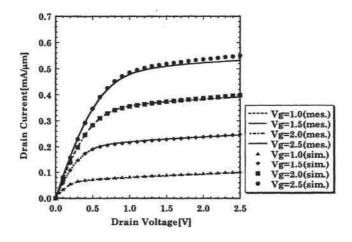

| Fig. 5.11 Id-Vd characteristics comparing measurement and simulation results using the              |

| GHDM by GALENE-III for a 0.19- $\mu$ m nMOSFET. (Lines: measurement results,                        |

| symbols: simulation results)                                                                        |

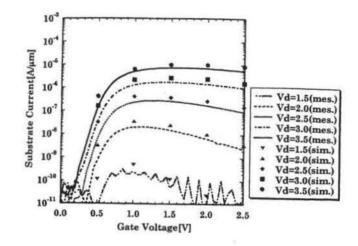

| Fig. 5.12 Substrate current characteristics comparing measurement and simulation results            |

| using the full-band MC simulator FALCON for a 0.19- $\mu$ m nMOSFET. (Lines:                        |

| measurement results, symbols: simulation results)                                                   |

| Fig. 5.13 Id-Vd characteristics comparing measurement and predicted simulation results              |

| using the GHDM by GALENE-III for a different 0.19- $\mu$ m nMOSFET of which                         |

| source/drain doping concentration is scaled to one-tenth. (Lines: measurement                       |

| results, symbols: simulation results)79                                                             |

| Fig. 5.14 Substrate current characteristics comparing measurement and predicted                     |

| simulation results using the full-band MC simulator FALCON for a different 0.19-                    |

| $\mu$ m nMOSFET of which source/drain doping concentration is scaled to one-tenth.                  |

| (Lines: measurement results, symbols: simulation results)                                           |

|                                                                                                     |

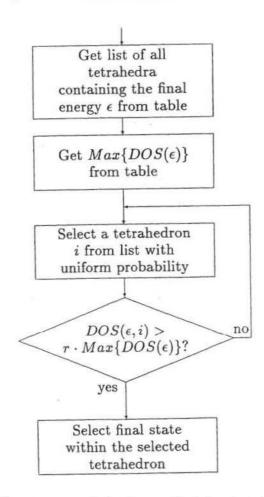

| Fig. 6.1 Flowchart of the acceptance/rejection method for the selection of the final state          |

| after scattering (random number r uniformly distributed in [0,1])                                   |

| Fig. 6.2 Substrate current and CPU times for (a) a 0.18 $\mu$ m nMOSFET and (b) a 1.0 $\mu$ m       |

| nMOSFET for different drain voltages. (Lines: experiment, Symbol: FB-MC                             |

| simulation)                                                                                         |

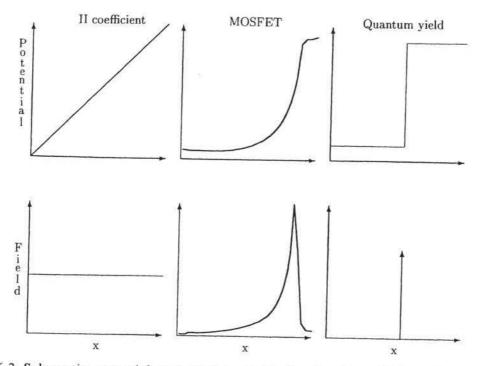

| Fig. 6.3 Schematic potential and electric fields for the II coefficient (left), at the $Si/SiO_2$ - |

| interface of a MOSFET (center) and for the quantum yield experiment (right)91                       |

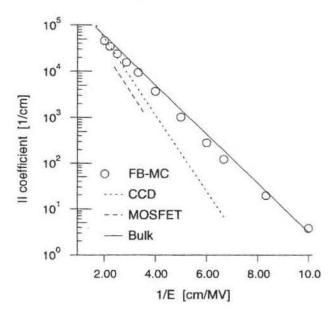

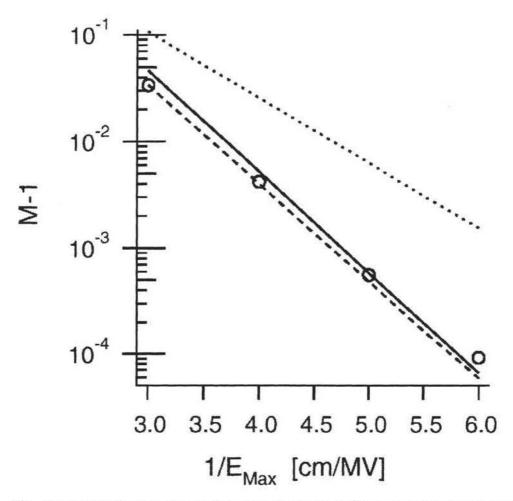

| Fig. 6.4 II coefficient versus inverse electric field for bulk silicon (solid line) as              |

| given by van Overstratton, for MOSFETs (dashed line) and CCDs (dotted                               |

| line) by Slotboom [133] and FB-MC results (symbol)93                                                |

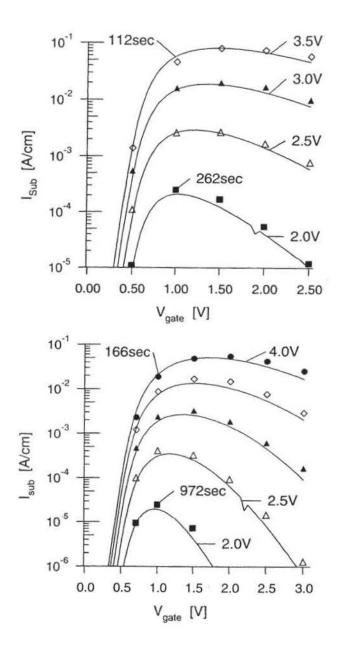

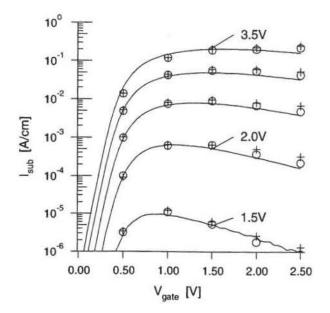

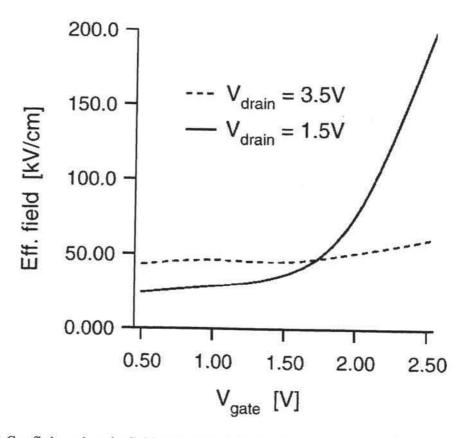

| Fig. 6.5 Substrate current versus gate voltage for the shallow source/drain extension $0.16 \mu$    |

m-nMOSFET (Vd=1.5,2.0,2.5,3.0,3.5V). (Lines: measurement, O: FB-MC with

surface roughness scattering, + FB-MC without surface roughness scattering) ....93

- Fig. 6.7 Multiplication factor for case *B* of the CCD, measured (solid line) [133], calculated with the LF model based on bulk parameters (dotted line), based on surface parameters (dashed line) and FB-MC results (symbol)......96

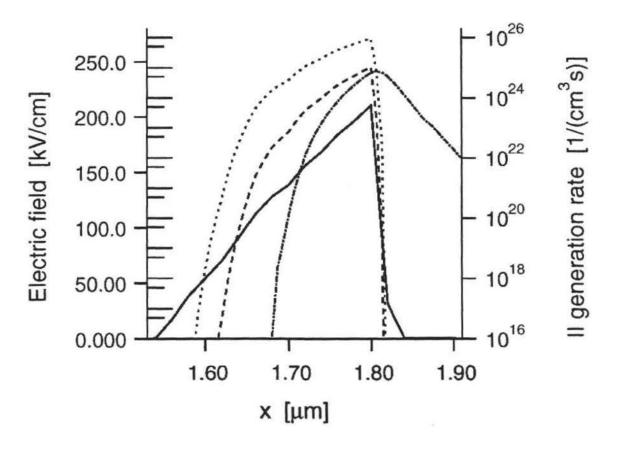

- Fig. 6.8 Confining electric field averaged with the II generation rate for the 0.16 μ mnMOSFET......97

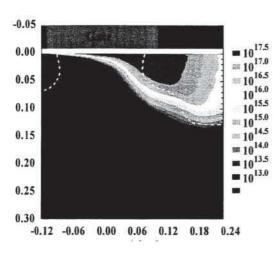

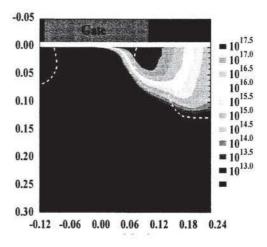

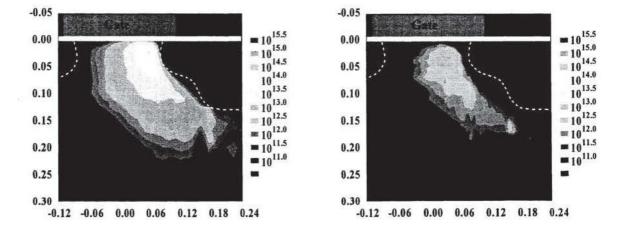

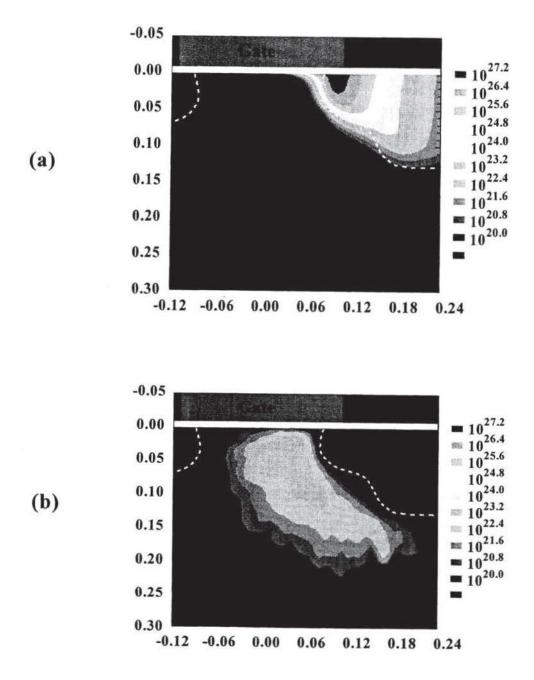

- Fig. 7.3 II generation rate caused by (a) electron and (b) hole. (Vd=2.5V, Vg=1.5V, axes unit:  $\mu$  m, contour line unit: s<sup>-1</sup>cm<sup>-3</sup>, dashed line denotes pn-junction).....103

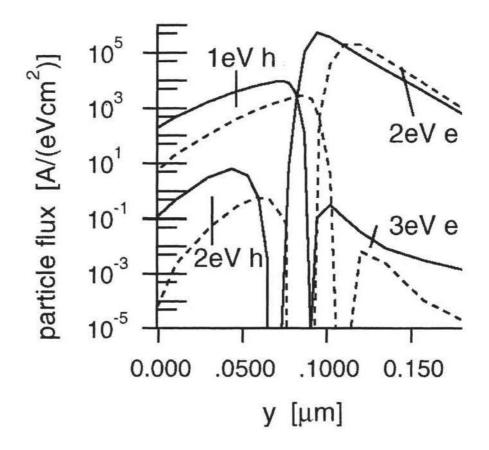

- Fig. 7.4 Currents of electrons and holes with certain energies hitting the Si/SiO<sub>2</sub> interface for the 0.18  $\mu$  m- (dashed line) and 0.16  $\mu$  m- (solid line) nMOSFETs.....104

# Chapter 1 Introduction

#### **1.1 Motivation**

In the field of high-speed silicon devices, silicon bipolar junction transistors (BJTs) had played a major role from the 1970s to the end of the 1980s. However, in the 1990s complementary metal-oxide-semiconductor (CMOS) field effect transistors (FETs) have been replacing their position. This dissertation tries to clarify the reason why BJTs were suitable for high-speed operation through the development of silicon bipolar device technologies and physics-based device analyses. This dissertation also reveals the reason why they were replaced by CMOS transistors. Then, to achieve high-speed CMOS transistors, this dissertation makes clear the needs for the device design methodology based on accurate physical device modeling as well as the importance of inverse modeling to determine device structure consistent with all experimental results. Also is made distinct the necessity for both particle-based full-band Monte Carlo and fluid-based generalized hydrodynamic models for accurate device simulation. Finally, the MOSFET design strategy for deep submicron regime will be discussed.

# 1.2 Scope and Organization

Chapter 2 describes the development of high-speed silicon bipolar technology and physics-based BJT design. In the case of BJTs, it was easy to reduce base width by employing a successive p-type and n-type diffusion technique that can result in the base thickness of 50nm or so. By introducing various kinds of self-alignment techniques such as deep trench isolation and double polysilicon self-aligned structures, BJTs enjoyed the benefit of short transit time i.e. high cutoff frequency caused by the thin base without needing sophisticated lithography tools. As a result, they achieved more competitive position to compound semiconductor devices and conquered the major position in the field of high-speed *l*arge scale *integrations* (LSIs).

Chapter 3 discusses circuit performance for high-speed BJT and clarifies its advantages and limiting factors. The most effective circuit to explore the high-speed performance of BJT is *e*mitter-*c*oupled *l*ogic (ECL). In the case of

ECL, emitter-coupled pair transistors are switched in accordance with input signal applied to base without bringing them into the saturation operation mode. This means each transistor benefits from quick discharging and switching. By using drift-diffusion-based device/circuit mixed simulator, the ultimate performance of an ECL-like circuit was investigated for double polysilicon self-aligned BJTs. As a result, it was found that the circuit delay was no more limited by cutoff frequency or the forward transit time of the BJT itself, but parasitic capacitance associated with a collector pull-up resistor. In other words, collector-substrate capacitance and loaded capacitance including an emitter follower input capacitance limit the circuit delay. Therefore, the reduction of base-collector and/or collector-substrate capacitance is more effective than the increment of cutoff frequency. On the other hand, in the case of ideal condition without any parasitic capacitance with the collector pull-up resistor, the switching current of around 100  $\mu$  A for each gate is still needed to achieve minimum gate delay. This indicates that, in the case of one-million-gate circuit, the chip will dissipate 100A in total, far beyond the practical air-cooling limit. Accordingly, BJTs were not able to enjoy the progress of microfabrication technology brought by deep submicron lithography.

Chapter 4 points out the reason why CMOS transistors replaced BJTs even in the high-speed field. CMOS transistor is an ideal device from the viewpoint of power dissipation because it dissipates power only when switching. The major drawback to the CMOS transistor was the larger channel length that was defined by minimum lithographic pattern. In the 1980s the channel length was from one to two orders larger than the base width of BJT, bringing MOSFETs lower cutoff frequency and larger transit time than bipolar devices. However, the dramatic progress of optical lithography has made it possible to realize deep submicron channel length. This results in higher driving current as well as shorter switching time even by CMOS circuits. Microprocessor is the main device benefited by this advantage, and high-speed LSIs have been realized. Fundamental technological features for high performance CMOS devices are retrograde well, dual-gate surface channel MOSFETs and a salicide structure. The former two features can realize high freedom for choosing supply voltage and threshold voltage design independently on the well structure especially in lower supply voltage regimes. The latter feature reduces parasitic resistance and, if combined with shallow trench isolation, parasitic capacitance associated with source/drain junction can be reduced. From the device-design point of view, optimization for higher driving current with lower off-leakage current as well as hot-carrier-induced degradation immunity is the most important concern.

Chapter 5 describes the requirement of precise knowledge of the device that is made by split lot experiments to design MOSFET effectively. For this purpose, inverse modeling is a powerful technique. The concept of inverse modeling, the procedure and application to quarter micron nMOSFETs are demonstrated. By using inversely modeled information, driving current and hot carrier properties can be predicted and successfully designed.

Chapter 6 discusses what kind of device model should be used to describe carrier transport in high-field regime to analyze driving current or the saturation drain current of MOSFETs. We must use accurate device model for this operation regime. To this end drift-diffusion model is not enough because this model assumes equilibrium carrier transport inside device. Not only fluid-model-based generalized hydrodynamic model but also particlebased first-principle model using ensemble full-band Monte Carlo simulation is inevitable. The background and concept of these approaches are also discussed and clarified. Moreover, hot carrier property and its model hierarchy is discussed based on the full-band Monte Carlo simulation analysis. Also is studied the previously proposed surface impact ionization model different from the bulk, and it is demonstrated that there is no experimental evidence for the difference between the surface and bulk impact ionization in silicon. The difference was only caused by an unsound application of local field model and just was an artifact.

Finally, in Chapter 7, by employing these sophisticated models, the saturation drain current as well as the hot carrier effects of subquarter micron MOSFETs are studied. Then, MOSFET design strategy for the 0.1- $\mu$  m regime is discussed, and the importance of shallow junction for source/drain extension is demonstrated.

In Chapter 8 as conclusion, the summary and future works for the sub-0.1  $\mu$  m regime are pointed out.

## Chapter 2 Development of High-Speed Silicon Bipolar Devices

#### 2.1 Historical Background

To achieve high-speed operation, silicon bipolar devices have conquered numerous process-technological obstacles. Since the discovery of pointcontact transistor by Bardeen and Brattain in 1947 and the invention of bipolar junction transistor by Shockley in 1948, several valuable process innovations have been introduced. The first notable step was the development of integrated circuits and a planar technique by the end of the 1950s. Isolation of pn-junction and new epitaxial growth techniques had triggered a rapid progress of bipolar ICs in the industry. Around 1970, two new process techniques had been developed. One was the LOCOS (local oxidation of silicon) technique [1]. By employing LOCOS isolation instead of junction isolation, dimensions of isolation regions were drastically reduced and the packing density was much improved. The other was the DOPOS (doped polysilicon) technique, which was the first polysilicon emitter process [2]. The DOPOS technique used impurity-doped polysilicon not only as an emitter diffusion source but also as an emitter electrode. The DOPOS made possible the achievement of much narrower and shallower emitters than those realized by a conventional washed emitter technique, which had been the ultimate refinement of the planar technique. In the 1970s, polysilicon techniques were further improved so as to achieve various applications for bipolar devices. A polysilicon self-aligned (PSA) process technique was one of the most sophisticated example [3]. The PSA technique used a polysilicon base electrode as well as a graft base diffusion source, exactly as the polysilicon emitter. Another notable property of the PSA technique was the application of the LOCOS technique to polysilicon films. By employing the PSA technique, the first fully self-aligned device structure that did not use tight lithographic design rules was demonstrated.

In the early 1980s, new etching techniques were demonstrated; namely the anisotropic dry etching techniques, such as reactive ion etching (RIE). By using this technique, first, steep and narrow grooves or trenches were easily realized for much improved isolation. Trench isolation began to replace conventional oxide isolation, resulting in higher packing densities and smaller

collector-substrate capacitance. Second, the so-called sidewall spacer technique was developed, allowing self-aligned compact isolation between stacking conducting layers of materials such as doped polysilicon. By combining the sidewall spacer techniques and the polysilicon base and emitter, double polysilicon self-aligned processes emerged. A submicron distance between the emitter and the base electrode was easily realized to achieve lower base-collector capacitance and lower base resistance than with any previous device structure. Anisotropic dry etching was also used to form steep and narrow monosilicon mesas to act as intrinsic base and emitter regions. By introducing sidewall contacted polysilicon base electrodes to the mesas, a new, sophisticated device structure was proposed. A sidewall base electrode contact structure (SICOS) was another approach to achieve fully self-aligned process. The SICOS was intended to realize an ideal one-dimensional device structure suitable for upward operation. Other sidewall base contact structures were also demonstrated by selective epitaxial growth as well as simultaneous epitaxial polysilicon growth in steep grooves.

Self-aligned processes as well as polysilicon emitter have been standard techniques for high performance silicon bipolar IC fabrication. Great efforts have been spent to improve these techniques and many researchers have been investigating the underlying device physics.

#### **2.2 Trench Isolation Techniques**

## 2.2.1 Introduction

Isolation is one of the key techniques in integrated circuit processes. When the first integrated circuit was invented by Kilby, two transistors and some resistors made in a monolithic germanium chip were partially separated by a slot and air. However, with the advent of the planar technique, pnjunction isolation became the major technique because Kilby's non-planar structure was unfavorable for wiring process. Another approach was also tried to improve the surface topography of air-isolated devices. This is the socalled dielectric isolation utilizing groove etching. Air isolation slots were replaced by dielectric substrates in which active semiconductor islands were sustained. The dielectric isolation achieved rather planar surfaces, but it was too complicated for conventional devices. Only for very high voltage devices has this technique been used.

After the LOCOS technique was developed, pn-junction isolation was gradually replaced by oxide isolation. At the same time there was a revival of groove isolation. In this case only laterally isolated regions were formed by grooves filled with dielectric materials, and the substrate was isolated by pnjunction. Grooves were formed by anisotropic chemical etching. Both of these isolation techniques achieved higher packing density than pn-junctionisolated devices. The scaling concept was also employed to achieve large scale integration and high performance devices. When the devices are scaled, not only active regions but also inactive regions such as the isolation should be reduced. In the case of LOCOS isolation, the so-called bird's beak enlarges the inactive regions. The length of the bird's beak is dependent on the thickness of oxide and cannot be reduced proportionally to the scaling ratio. This was the ultimate limitation of oxide isolation. On the other hand, the groove isolation utilized anisotropically etched V-shaped grooves for isolation using alkaline etchant applied to (100) silicon surface. The Vgroove's depth is 70% of its width, so the reduction of isolation regions is limited by the groove depth necessary to keep enough breakdown voltage.

In order to overcome these problems of conventional isolation techniques, the bird's beak free and width-independent isolation scheme was most important, the result was the advent of trench isolation. This is a new technology employing novel etching techniques such as RIE to form narrow and steep U-shaped grooves, or trenches for isolation, but its root is based on the classical idea of dielectric isolation.

Though a practical trench isolation technique was first disclosed in 1978[4], we demonstrated its application to practical devices for the first time early in the 1980s[5]. Since the first application of trench isolation to 1kb ECL static RAMs in 1982 [5], many bipolar devices have been fabricated by various kinds of trench isolation techniques. In the case of bipolar devices, some trench isolation techniques have been used in volume production since the early stage of the development, though trench isolation for MOS devices are only introduced recently as a shallow trench isolation technique.

In the following subsections, process technologies, device structures, application to devices and benefits and limiting aspects of trench isolation for

bipolar devices will be discussed.

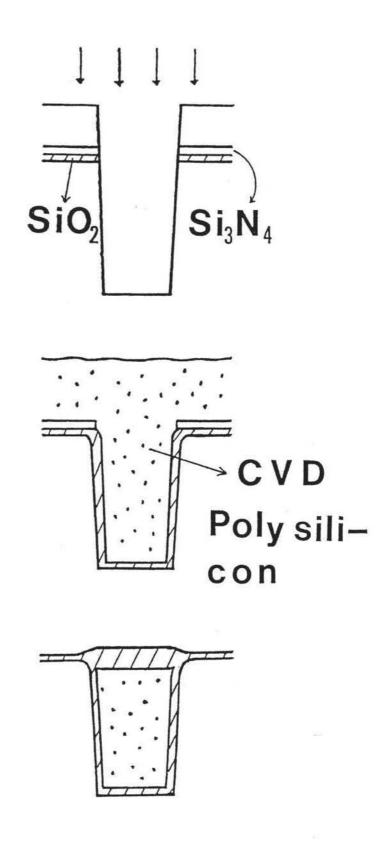

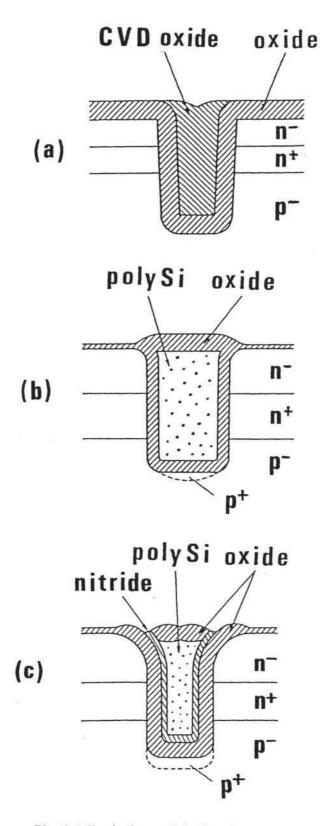

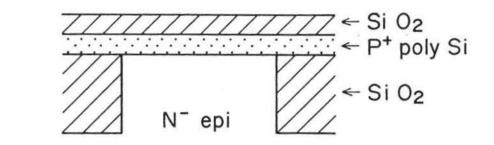

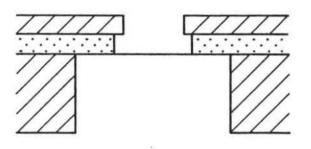

#### 2.2.2 Trench Isolation by Oxide and Polysilicon

Typical trench isolation techniques consist of three major process steps [5]. These are trench etching, trench filling and planarization. Figure 2.1 shows an example of process steps. As usual, an  $n^+$  buried layer and an  $n^-$  epitaxial layer are formed on a p-type substrate. On the  $n^-$  epitaxial layer, a nitride layer with thin pad oxide is deposited and a masking layer for trench etching is also deposited. After the isolation pattern is formed, trench etching follows using anisotropic dry etching such as RIE. The trenches penetrate both the epitaxial and buried layers to reach the p-type substrate. The inside of the trenches is then oxidized to accomplish electrical isolation. After that, trenches are buried with undoped polysilicon. Excess polysilicon is polished off until the nitride layer appears. Finally the surface of polysilicon is oxidized for capping. The trenches are filled with oxide and polysilicon.

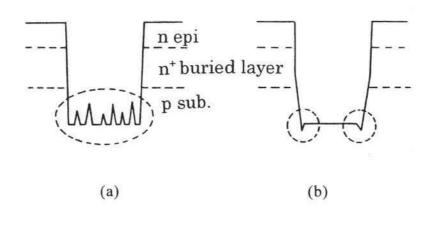

Trench etching is one of the most important processes in trench isolation techniques. The typical structure of narrow and deep trenches for isolation is achieved by anisotropic plasma etching. RIE is widely used for this purpose. The etching conditions should be carefully optimized to avoid unfavorable trench shapes. Figure 2.2 shows examples of maladapted trench structures. Figure 2.2(a) shows so-called 'black-silicon' or needle-like silicon residues, and sub-trench at the corners of bottom edges of trenches is shown in Fig. 2.2(b). Figure 2.2(c) is the case of laterally-etched undercut that occurs at the highly doped  $n^+$  buried layer. All of these unfavorable shapes cause large leakage current between isolated elements. Figure 2.2(d) shows bowing. In this case the trenches are not completely buried by filler materials and voids occur in isolation regions. These voids may become sharp crevices after the planarization step finishes. They cause bad metallization step coverage.

These trench shapes are strongly dependent on gas species, pressure, flow rates and power in RIE processes [6,7]. These etching conditions are not universal, so they should be optimized according to etching systems.

Trench filling and planarization processes are also important. Trenches should be filled completely with filler materials. If not, nonplanar surfaces occur after excess filler materials are removed. The filler materials should

Fig. 2.1 Fabrication process steps of a typical trench isolation technique.

Fig. 2.2 Unfavorable trench shapes caused by trench etching.(a) Black silicon (b) Sub-trench (c) Laterally etched undercut (d) Bowing

also be deposited as uniformly as possible. There are variety of filler materials such as CVD (chemical vapor deposition) oxide, CVD nitride and undoped polysilicon. When CVD oxide is used, trench shapes, especially the sidewall taper should be optimized because CVD oxide does not show good step coverage inside trenches [4]. Until now, instead of CVD oxide, bias sputtered oxide, ECR (electron cyclotron resonance) plasma enhanced CVD oxide and boron-phosphorus silicate glass have been tried. Nevertheless, low-pressure CVD polysilicon shows excellent step coverage although it is not a complete insulator. Undoped polysilicon is widely used as the filler material. CVD nitride is a good insulator, but because of its high tension it is impossible to fill trenches completely. Nitride is often used as a spacer

between thermal oxide of trench surfaces and undoped polysilicon. Excess filler materials are removed to attain a planar surface by controlled etch-back techniques or chemical-mechanical polishing (CMP) technique. This planarization process requires high uniformity. In our experience, polishing techniques are superior to controlled etch-back processes, resulting in recent large stream of CMP process as a major planarizing technique.

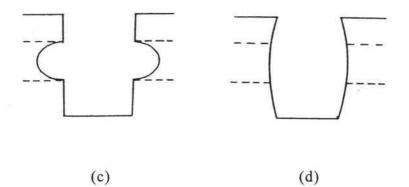

Figure 2.3 shows the typical trench-isolated structures. Figure 2.3(a) is called DGI (deep groove isolation) [4]. Trenches are etched by RIE using Cl<sub>2</sub>/Ar gas mixture. Trench surfaces are oxidized and filled with CVD oxide. Excess oxide was removed by a controlled etch-back technique. Figure 2.3(b) shows our IOP-II (isolation by oxide and polysilicon; second version) [5]. Trenches are etched by RIE and filled with oxide and polysilicon. Excess polysilicon is removed by a chemical-mechanical polishing technique. IOP-II is an advanced version of conventional IOP using V-grooves, and only V-groove etching was replaced by trench etching. Figure 2.3(c) exhibits U-Iso (Ugroove isolation) [8]. In this case, the trench is not U-shaped but Y-shaped. The trench etching process consists of two steps. First, anisotropic chemical etching of (100) surface is employed to form an overhung structure using a nitride layer with side-etched pad oxide as a mask. Then anisotropic dry etching such as reactive sputter etching using a CCl<sub>4</sub>/O<sub>2</sub> gas mixture follows for trenches to penetrate an n<sup>+</sup> buried layer. The inside of the trenches is oxidized and the second nitride layer is deposited to cover the trench surface. Trenches are filled with undoped polysilicon. Excess polysilicon is removed by a controlled etch-back technique.

The above-mentioned trench-isolated structures may be called the first generation. In these trench isolation techniques, one attempts to reduce only the isolation regions; other inactive regions such as field regions for wiring or shallow isolation for base and collector-reach-through regions are not taken into account. As far as memory devices are concerned, there is no serious problem. However, for high performance logic devices, those parasitic inactive regions are fatal disadvantages for switching speeds. In order to overcome these disadvantages of the first generation, some process modification followed. In the next subsection, process technologies and device structures of advanced trench isolation techniques, which may be called the second generation, will be described.

#### 2.2.3 Trench Isolation with Thick Field Oxide

Process modifications for the second generation may be roughly divided into two types. One is the combination of LOCOS or ROX (recessed oxide) with deep trenches, and the other is the combination of shallow trenches with deep ones. For instance, Figure 2.4 shows the process steps of our U-FOX (U-groove isolation with thick field oxide, renamed from IOP-L) or an advanced version of IOP-II, combining LOCOS with trench isolation [9]. After the formation of an n<sup>-</sup> epitaxial layer by conventional means, its surface is selectively oxidized except base, collector-reach-through regions and so on, using the LOCOS technique. Then a new nitride layer and a masking layer for trench etching are deposited. They are removed at the isolation regions and trench etching follows. After the trenches have been etched, their surfaces are oxidized and filled with undoped polysilicon. Excess polysilicon is polished off until the polysilicon not on the isolation regions is completely removed. Then capping oxidation is performed. This process step sequence, or the trench etching after the field LOCOS formation is favorable to the other option, or the LOCOS-after-trench process, avoiding nonplanar surface topography as well as stress induced crystalline defects caused by capping oxidation. The detail will be discussed later again.

To compare our U-FOX process with other approaches, another technique is shown in Fig. 2.5 [10]. In this technique, deep trenches for device isolation are first etched, using a thick oxide layer as a mask. Then the masking layer is selectively removed by the second isolation patterns, which contain base- and collector-reach-through isolation and field regions. Again trench etching is performed to give no penetrating shallow trenches. Deep trenches penetrate the  $n^+$  buried layer to reach also the p-type substrate. Both deep and shallow trenches are buried with CVD oxide. The CVD oxide itself does not achieve good step coverage in the trenches, but by optimizing the distances between deep trenches in shallow ones, voids in the deep trenches are elaborately covered by over-grown oxide. Excess oxide is removed by a controlled etch-back technique in just the same way as reported for simplified *buried oxide* (BOX) isolation for MOS devices [11].

Fig. 2.4 Fabrication process steps of U-FOX.

Fig. 2.5 Fabrication process steps of [10].

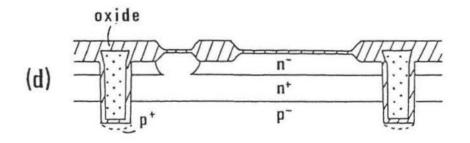

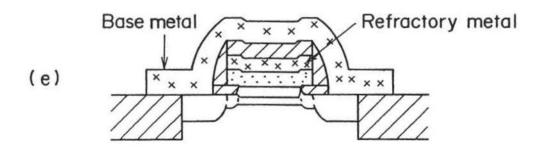

There are also some structural modifications of these techniques. Figure 2.6 shows structural variations of modified trench-isolated devices in the second generation. Figure 2.6(a) is an example of deep trench isolation combined with recessed oxide. The recessed oxide is formed by recessing silicon, using RIE followed by oxidation. Deep trenches are then etched, covered with a thin thermal oxide layer and filled with CVD oxide. In some cases there are voids in the middle of isolation regions [12,13]. Figure 2.6(b) is an example of a dual-depth trench-isolated structure [14]. Shallower trenches, filled with oxide, nitride, and polysilicon isolate transistors and Schottky barrier diodes, and they may be able to isolate base and collectorreach-through regions. Figure 2.6(c) shows our U-FOX structure. LOCOS technique is used for base and collector-reach-through isolation and field

oxide for wiring regions. Figure 2.6(d) is the final structure of the technique mentioned above [10]. Figure 2.6(e) is a modification of Fig. 2.6(a). As a filler material for deep trenches, CVD oxide is replaced by selective episilicon [15,16]. In this case, trenches of variable width can be filled and planarized at the same process step. There are other variations on advanced trench-isolated structures [17,18]. In ref. [17], field oxidation, as well as capping oxidation of trench-filling polysilicon, performed after excess polysilicon is removed by a controlled etch-back technique. In order to bury the crevices which occur along the trench-edge surface, an etch-back technique of reflow glass is used The final device structure resembles Fig. 2.6(d). In ref. [18], vertical pnp transistors are formed as well as conventional npn transistors, and new advantageous device structure is achieved. The main drawbacks to these techniques are rather complicated dual-depth trench etching process, poor step coverage of CVD oxide inside trenches and larger collector-substrate parasitic capacitance caused by selective epi-trench filling process.

## 2.2.4 Benefits and Device Performance

The trench isolation techniques mentioned above have a number of advantages, and bipolar devices using them have achieved higher performance than conventionally isolated devices

First, higher packing density than in conventional isolation is achieved because the trench depth is almost independent of its width and the bird's beak is reduced much more than in LOCOS. The  $p^+$  channel stop layers are completely separated from  $n^+$  buried layers. Therefore, even if the trench width is reduced, there is enough space that a depletion layer can sustain high breakdown voltage. Also, the complete separation of the channel stop layers and the  $n^+$  buried layers makes collector-substrate parasitic capacitance smaller. Because the  $n^+$  buried layer islands are self-aligned to isolation trenches, there is no mask alignment step between a buried layer and an isolation pattern, and planar collector-substrate pn-junction is achieved, which is also favorable for the reduction of its parasitic capacitance.

Table 2.1 is an example of device performance demonstrated by 1kb ECL (emitter coupled logic) static RAM (random access memory) using our IOP-II [5]. The V-groove-based IOP device was shrunk at the ratios of 0.8, 0.7 and 0.6. Trench width can be shrunk by the same factor as the active regions, from  $5\mu$  m of the V-groove to 4, 3.5 and  $3\mu$  m of the trenches, respectively. Because of this linear shrink, the typical access time can be reduced in proportion to the shrinking factor. Our IOP-II also realized various ECL static RAMs from 4kb to 64kb generations for high-speed cache RAM applications [19-24]. On the other hand, the advantage of trench isolation was shown using ring oscillator circuits by other researchers. The basic gate delay of an ECL circuit using with trench isolation was nearly 30% improved compared with oxide isolation [8]

| Shrink ratio | Isolation width ( $\mu$ m) | Access time (ns) | Technology     |

|--------------|----------------------------|------------------|----------------|

| 1.0          | 5.0                        | 7.4              | IOP(V-groove)  |

| 0.8          | 4.0                        | 5.8              | IOP-II(Trench) |

| 0.7          | 3.5                        | 4.8              | IOP-II(Trench) |

| 0.6          | 3.0                        | 4.4              | IOP-II(Trench) |

Table 2.1 Typical address access time of linear shrunk 1kb ECL RAM using IOP-II.

Not only trench structures but also the modification in the second generation have much improved device performance. By introducing thick field oxide for wiring regions, parasitic capacitance between wiring layers and substrate have been reduced. This approach is suitable for logic devices. As well as the reduction of wiring-substrate capacitance, base-collector parasitic capacitance is also reduced because LOCOS or shallow-trench-filled oxide surrounds the base region to achieve a so-called walled base structure. In the case of our U-FOX structure, the wiring delay time of 50ps/mm was achieved for the first and second metallization layers using a 1.6-um wide wiring pattern. A loaded gate delay of 323ps (basic delay=177 ps, FI=FO=3, wiring length=2mm) using an ECL circuit was obtained at a switching current of 0.2mA/gate [9]. The U-FOX structure made possible 3000- and 10,000-gate ECL logic LSIs for the Fujitsu mainframe computer FACOM-M780.

Other examples demonstrated by trench isolation techniques are listed in ref [25].

2.2.5 Limiting Aspects and Recent Improvements

Trench isolation is now a must for high performance bipolar devices. In the early stage of the development, there were several problems, and those were broadly divided into two categories. One was the structural problem and the other was the electrical problem. They were often strongly related and the former, in particular, is apt to influence the latter. As previously described in subsection 2.2.2, if the trench etching process is not optimized, trench shapes may change variously. The structural problems without electrical ones are usually bad step coverage of metallization layers caused by voids or sharp crevices on isolation regions. To avoid these problems trench shape should not show bowing or overhung and over etching in etchback processes to remove the excess filler materials should be carefully controlled. Other maladapted trench structures such as black silicon, subtrench, laterally-etched undercut of highly doped buried layers often accompany crystalline defects. These crystalline defects cause large leakage current between isolated elements. Thus, trench-etching processes should be optimized thoroughly to achieve the best conditions.

The most serious problem was how to get rid of isolation leakage caused by crystalline defects. The crystalline defects often occur at stressconcentrated places such as sharp-edged corners caused by unfavorable trench structures. However, even if the trench shapes show the ideal structure, crystalline defects may sometimes appear. They seem to be influenced by ion-implantation-induced damages and inadequate subsequent heat processes. The use of Y-shaped trenches instead of U-shaped trenches is one way to avoid stress-concentrated right-angled corners around top edges of trenches at the expense of packing density [26]. In relation to trench isolation combined with LOCOS, some process modifications were also proposed. One is the nitride liner between the oxide of the trench surface and filled polysilicon [27], and another was the combination of selective polysilicon oxidation (SEPOX) with trenches, which was applied to a CMOS static RAM [28]. In both of these techniques, selective oxidation of field regions is performed at the same time as capping oxidation. Without these modifications large stress occurs at the top corner of trenches when single crystalline silicon and filled polysilicon are oxidized simultaneously, and they causes crystalline defects. Most recent approach to avoid large stress by capping oxidation is to use soft reflow glass to fill the trench. Boron-phosphorus silicate glass can be used for such purpose [29]

#### 2.2.6 Conclusion

Trench isolation is one of the key techniques in high performance bipolar devices. It realizes higher packing density and smaller collectorsubstrate parasitic capacitance than conventional isolation techniques. It also reduces wiring-substrate and base-collector parasitic capacitance with process modifications such as combining thick field oxide for wiring regions.

# 2.3 Polysilicon Self-Aligned Structures

## 2.3.1 Introduction

As described in the historical background section, self-aligned techniques using polysilicon is another key feature to realize high performance silicon BJTs. These self-aligned techniques consist of double polysilicon and/or single polysilicon processes. Moreover, polysilicon emitter is also important to achieve shallow emitter that results in high cutoff frequency. The polysilicon emitter is a root for wide-gap emitter, or emitterbase heterojunction BJT. In this section, these self-aligned and polysiliconrelated device structures will be discussed.

#### 2.3.2 Double Polysilicon Self-Aligned Structure

In this subsection, various kinds of double-polysilicon self-aligned processes and related device structures are discussed. The double polysilicon self-aligned processes are roughly divided into three classes depending on the number of masks used to form the emitter and base regions. A one-mask process can define not only the emitter and intrinsic base region, but also the extrinsic (graft) base region by using the same mask. A super self-aligned technology (SST) is a typical example of this type [30]. In the case of a twomask process, the extrinsic base regions are defined by a mask different from that of the emitter and intrinsic base region. Until now, these processes are widely used in advanced bipolar IC production. Finally, Three-mask processes use different masks to define the emitter, intrinsic base and extrinsic base regions, respectively.

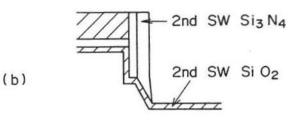

#### 2.3.2.1 One-Mask Process

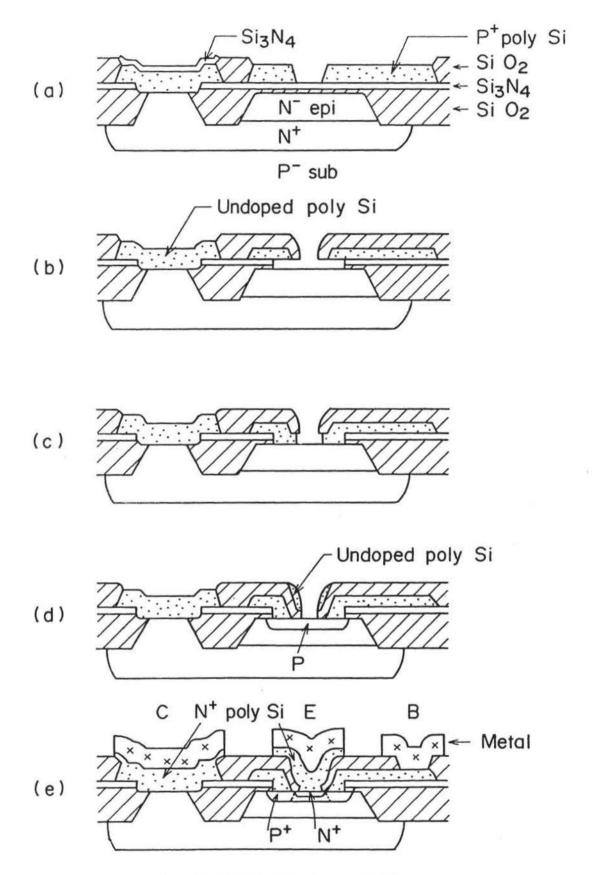

A typical and the most successful one-mask process is the so-called SST. The first version of this process was reported in 1980 [30], and some process improvements have since been introduced. Major improvement was reported in 1983 such as advanced SST [31]. Figure 2.7 shows the fabrication steps of the SST-1A (an advanced version of SST-1) process. After growing n-type epitaxial layer on a p-type substrate and oxide isolation formation, an oxide layer, a nitride layer and a polysilicon layer are deposited consecutively. The polysilicon layer is selectively oxidized (above the oxide isolation regions). The polysilicon in the area corresponding to the transistor emitter regions is etched away (Fig. 2.7(a)), and then oxidized. The nitride is side-etched followed by etching of the underneath oxide (Fig. 2.7(b)). New polysilicon is deposited to fill the overhung space and to connect the first polysilicon to the epitaxial layer. The excess polysilicon is etched away (Fig. 2.7(c)). Thermal oxide is grown and the intrinsic base region is formed by boron ion implantation through the oxide. Then CVD oxide and polysilicon are deposited. The emitter window is opened by dry etching (Fig. 2.7(d)). Finally, the emitter area is diffused through the arsenic-implanted polysilicon layer (Fig. 2.7(e)).

Fig. 2.7 SST-1A fabrication steps [31].

Fig. 2.8 Cross-sectional view of the SST-1B transistor with selectively implanted pedestal collector [32].

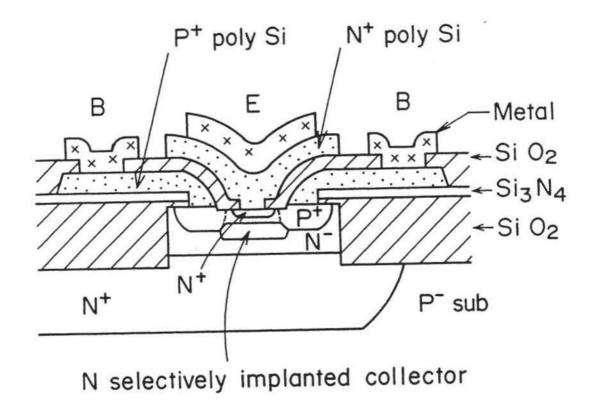

In the SST process, all the active regions are defined by a single mask pattern. The extrinsic base region is determined by the side-etched area in the nitride layer under the base-electrode polysilicon. The distance between the emitter and the base electrode is about the thickness of the CVD oxide and polysilicon. The emitter-window width can easily be made narrower than the original mask feature to achieve a submicron width. As a result, the base-collector parasitic capacitance and extrinsic base resistance of the SST transistor are dramatically reduced. In addition to obtaining a higher cutoff frequency, a selectively implanted pedestal collector process is used along with a low energy ion implantation for the intrinsic base region. Figure 2.8 shows the schematic cross-section of the improved structure. By using this improved process, named SST-1B, a peak cutoff frequency of 25.7 GHz (Vce=3V) was obtained, and a minimum basic gate delay time of 20.5 ps by an NTL circuit was demonstrated at a power dissipation of 2.32 mW/gate. At the same time, a minimum basic gate delay time of 34.1 ps by an ECL circuit at a

power dissipation of 7.54 mW/gate was also reported [32]. The drawback to the SST process is that there is a slight difficulty in defining a walled-base structure to reduce the parasitic base-collector capacitance. If the walled-base structure is required, a tight alignment control is needed between the fieldoxidation and the intrinsic-base masks at the expense of the one-mask selfalignment advantage.

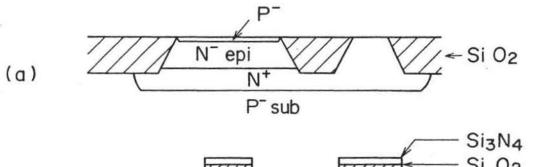

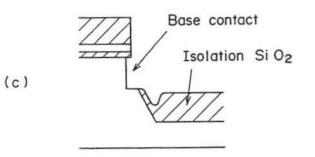

Another successful one-mask process was demonstrated by depositing the emitter polysilicon prior to the deposition of the base-electrode polysilicon [33]. Figure 2.9 shows the fabrication steps of this polysilicon self-aligned technology. After LOCOS isolation, the intrinsic base region is first implanted (Fig. 2.9(a)). Then, heavily implanted n-type polysilicon, CVD oxide and nitride layers are deposited and successively etched where the intrinsic base and emitter region are defined (Fig. 2.9(b)). To isolate the sidewall of the n-type polysilicon, the second CVD oxide is deposited, followed by reactive ion etching (Fig. 2.9(c)). A second nitride is deposited and reactively etched to form a vertical nitride layer (Fig. 2.9(d)). By using the first and second nitride as a mask, the surface of the extrinsic base area is locally oxidized, while the emitter is also driven into the intrinsic base region (Fig. 2.9(e)). The base contact window is opened by removing the nitride layer. Then p-type doped polysilicon is deposited, which acts as the base electrode as well as the graft base diffusion source (Fig. 2.9(f)). By using this technique, a basic gate delay of 52 ps at a power dissipation of 0.16 mW/gate employing a CML circuit was demonstrated. This process has the same advantages as those of the one-mask process, but there are some drawbacks such as higher emitter series resistance caused by the polysilicon emitter electrode without metallization, furthermore, this is an unwalled base structure.

Other one-mask processes have been reported based on the same fabricating sequence as the SST, for instance, as the side frame self-aligned (SFS) technology [34], or the selective diffusion by exdiffusion (SDX) technology [35]

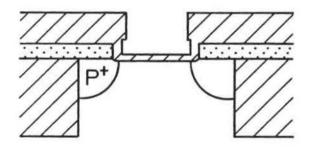

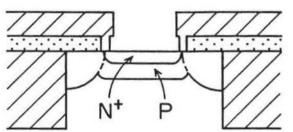

# 2.3.2.2 Two-Mask Process

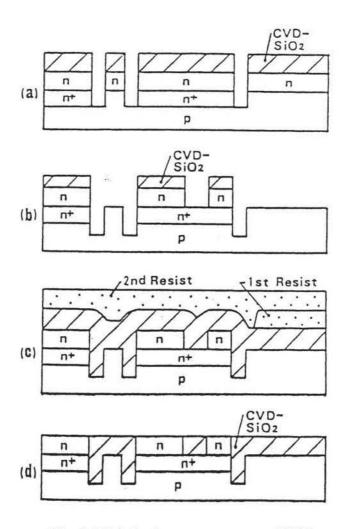

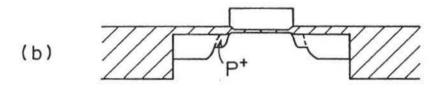

Two-mask processes have been widely used to achieve the double polysilicon self-aligned structures. The first and simplest example was reported in 1980 as a self-aligned transistor [36]. Figure 2.10 shows its fabrication steps. P-type boron doped polysilicon and CVD oxide layers are deposited on an n-type epitaxial layer after conventional recessed oxide isolation. The recessed oxide isolation defines not only collector reachthrough regions but also the total base regions (Fig. 2.10 (a)). The CVD oxide and polysilicon layers are preferentially etched by using an intrinsic-basewindow opening mask (Fig. 2.10(b)). The surface of the epitaxial layer and the sidewall of polysilicon are oxidized, while the extrinsic (graft) base is diffused from the boron-doped polysilicon (Fig. 2.10(c)). The intrinsic base region is opened by RIE. Finally, the intrinsic base is ion-implanted, and the emitter is also diffused into the same region (Fig. 2.10(d)). Since this early development, numerous process modifications and improvements have been introduced by a number of researchers. These processes have been given various names such as SAPT [17], OXIS-III [37], SDD [38], MOSAIC-III [39], ESPER [40], BSA [41] and many others [42-47].

The two-mask process uses different masks for the extrinsic (graft) base and intrinsic base. Therefore, the walled-base structure can be easily obtained without using a complicated side-etching technique, although this is at the expense of alignment tolerance. Other properties of the two-mask processes are fundamentally the same as those of the one-mask process. The most significant and careful process control is required for the intrinsic-base formation, the sidewall spacer etching, and the intrinsic base diffusion. There are two options for the intrinsic base diffusion step and the sidewall-spaceretching step. One is to have the intrinsic base implantation prior to the sidewall spacer formation, and the other is to reverse the sequence of the two steps. In the case of the first process sequence, the intrinsic base region is implanted just adjacent to the extrinsic base. Because the extrinsic base is already diffused vertically and laterally toward the intrinsic base region, the requisite low resistance cross-linking region between the intrinsic base and the extrinsic base is stably obtained. Moreover, the lateral-encroachment of the extrinsic base region can be covered by the sidewall spacer, which

(a)

(c)

eliminates any emitter-base tunneling leakage current and ensures a high emitter-base reverse breakdown voltage. However, attention should be paid to the sidewall-spacer-etching step to avoid overetching, because the intrinsic base region is damaged and the base depth might be changed.

In the second process sequence, overetching of the sidewall spacer does not damage the intrinsic base region, but the extrinsic base diffusion must be carefully controlled. Too much lateral encroachment of the extrinsic base results in highly doped pn-junction at the emitter periphery, causing not only reverse, but also forward tunneling leakage current [48]. Also caused is unfavorable degradation of dc current gain as well as that of transient characteristics [49,50]. However, the peripheral punchthrough occurs when the cross-linking region between the intrinsic and extrinsic base is not satisfactorily diffused [51].

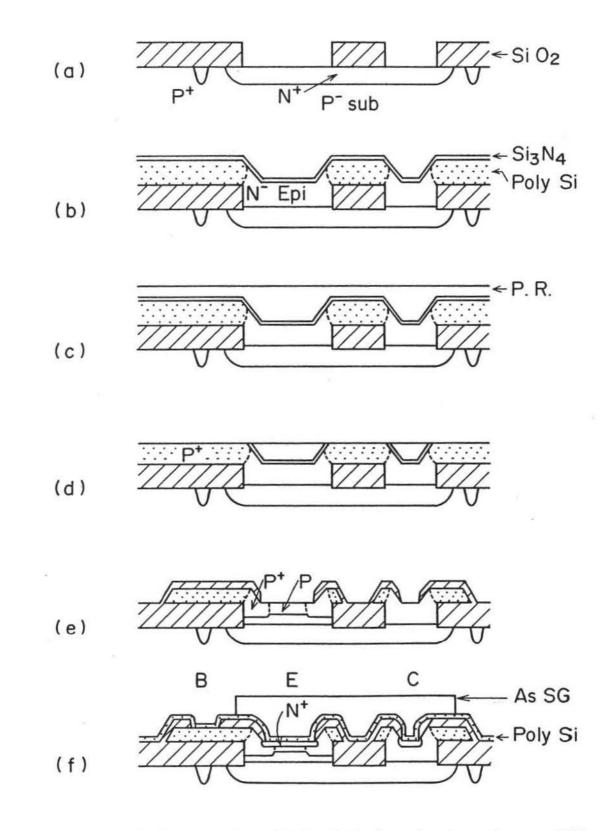

To avoid these contradictory problems, some process modifications have been reported to combine light-coupling ion implantation and base diffusion through polysilicon [47,52]. The coupling base is lightly implanted after etching the CVD oxide and the base polysilicon (Fig. 2.11(a)). Then, CVD oxide is deposited and etched by reactive ion etching to form the sidewall spacer, and another polysilicon layer is deposited (Fig. 2.11(b)). The intrinsic base is implanted and diffused through the polysilicon, while the extrinsic base is also driven in (Fig. 2.11(c)). By using this technique, a cutoff frequency of more than 30 GHz and a minimum basic gate delay of 24 ps at a switching current of 2.2 mA/gate by an LCML circuit have been reported [47]. The drawback to this coupling base technique is its process complexity and the difficulty in controlling the intrinsic base-emitter depth because the boron diffusion for the intrinsic base and the arsenic diffusion for the emitter require different annealing conditions due to the difference between the respective diffusion coefficients.

Some authors have investigated reliability of two-mask double polysilicon self-aligned devices. They reported gain degradation under reverse emitter-base bias and high current forward base-emitter bias stress conditions when transistors are irradiated by laser, X-ray and electron beams [53-56]. Although not all the degradation mechanisms are understood, if the ideal factor of the base current is kept unity, the electrical characteristics are found to be unchanged under high-current stresses. This fact suggests that if the cross-linking region between the intrinsic and extrinsic base is well controlled, the transistors have enough reliability to operate under normal bias and environmental conditions.

(b)

Fig. 2.11 Fabrication steps of the double polysilicon self-aligned process using coupling base implantation [52].

Although the two-mask process requires alignment tolerance between the field isolation and emitter opening masks, resulting in a little larger base area than that of the one-mask process, good circuit performance was obtained. For example, our ESPER process realized basic gate delay of 38.8ps by ECL circuit at a switching current of 1.28mA/gate [40]. In our case, the double polysilicon self-aligned process was combined with the U-FOX structure. By using this technology, 15,000 gate ECL array LSI with a loaded gate delay of 220 ps (basic delay=80 ps, FI=FO=3, wiring length=2 mm) and 64kb-RAM with 3,000 gate ECL array LSI (SRAM access time=1.15 ns) for the Fujitsu mainframe computer FACOM-M1800 and super computer VP2000 series were realized [57]. In addition to them experimental 50,000 gate sea-of-gate ECL array and 100,000 gate ECL standard cell LSIs were also demonstrated [58,59]

#### 2.3.2.3 Three-Mask Process

There have not been so many examples of the three-mask process reported to date. This is not only because total active base area obtained by the three-mask process is slightly reduced but also as a result of the number of process steps being increased. However, the first double-polysilicon self-aligned process was demonstrated by a three-mask process named APSA, an advanced version of PSA [60]. Historically, this process has some value, but because of the drawbacks to the three-mask process, few efforts have been made to improve it. Only one approach was reported as a salicide base contact technology (SCOT) [61].

### 2.3.3 Single Polysilicon Self-Aligned Process

Basically single polysilicon process originated from the DOPOS technique [2]. At the early stage of development, some process improvements attained to achieve self-aligned isolation between emitter and base electrodes, such as stepped electrode transistor (SET) or elevated electrode IC (EEIC) [62,63]. In these processes, an overhang polysilicon emitter structure isolated the emitter polysilicon and the base electrode metallization. Another approach was also reported to use the sidewall spacer technique just as in double polysilicon self-aligned processes. This self-aligned process employed the sidewall spacer between the emitter polysilicon and the base electrode getween the aluminum base electrode [64]. All of these are two-mask processes, and the distance between the emitter and the base electrodes is defined by self-aligned techniques. However, the disadvantages of these processes are nonplanar surface topographies of the SET or the EEIC and a high emitter series resistance caused by the absence of emitter metallization. Because of these

disadvantages, development efforts essentially instead focused on improving the double-polysilicon self -aligned processes.

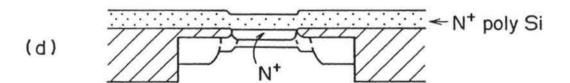

A single polysilicon three-mask process has also been reported [65]. It was demonstrated as an example to avoid cross-linking problem of double polysilicon self-aligned processes. Figure 2.12 shows the process steps [66]. After conventional oxide isolation, a nitride layer is preferentially patterned at the portion of intrinsic-base and emitter defining region. By using the nitride layer as a mask, the epitaxial layer is slightly oxidized, and a polysilicon sidewall spacer is formed. Highly doped extrinsic base regions are implanted (Fig. 2.12(a)). After the polysilicon sidewall spacer is removed, the cross-link base regions are lightly implanted (Fig. 2.12 (b)). After removal of the nitride, intrinsic base is implanted (Fig. 2.12 (c)). Emitter is diffused from an arsenic doped polysilicon layer (Fig. 2.12(d)). The emitter polysilicon is covered with a silicide layer and an oxide layer on top. Another mask is used to define the emitter electrode, which is covered by the capping oxide and new sidewall spacers. The base contact window is opened at the same time when the sidewall spacer is etched (Fig. 2.12(e)). By using this process, a basic gate delay of 49.8 ps for an ECL circuit was demonstrated at a switching current of 0.65 mA [65].

In this three mask process, the cross-link region is made before the intrinsic base implantation, and only the emitter drive-in heat step is required after the intrinsic base formation. Therefore, the cross-link problem induced by the double polysilicon process is eliminated. However, this process requires different masks for the intrinsic base region and base contact window opening. Furthermore, the somewhat higher series resistance of the emitter electrode is a drawback, although a silicide layer is deposited on the emitter polysilicon.

# 2.3.4 Sidewall Base Contact Structures

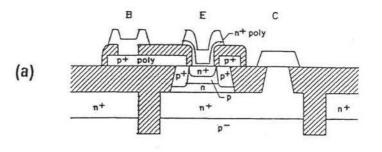

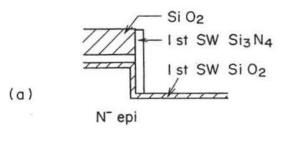

Sidewall base contact structures were intended to achieve an ideal, onedimensional transistor structure eliminating any parasitic capacitance and resistance. A sidewall base contact structure was first reported as SICOS in 1981 [67]. Since that time, much process modification had been reported. Figure 2.13 shows the fabrication steps of the original SICOS. First, a

Fig. 2.12 Fabrication steps of the single polysilicon self-aligned process [66].

mesa-etched region is formed by reactive ion etching, using a multilayered structure, successively including an oxide, a nitride, a polysilicon, a nitride and a CVD oxide layer (Fig. 2.13(a)). After a slight sideetching of the mesa, another nitride layer is deposited and a spacer is formed at the sidewall edge. Then, the silicon surface is oxidized and the nitride spacer is removed (Fig. 2.13(b)). Another polysilicon layer is deposited and preferentially etched where the base electrode is positioned (Fig. 2.13(c)). Finally the graft base is diffused from the second polysilicon, which is boron-doped by ion implantation. The intrinsic base is implanted through the first oxide on the mesa and emitter is also diffused through another polysilicon layer (Fig. 2.13(d)).

The advantage of the SICOS is the nearly one-dimensional device structure in addition to its full one-mask self-alignment feature. Consequently, excellent upward operation has been reported since the early stage of the development. However, there has been a serious drawback to this process. This is encroachment of the extrinsic (graft) base, which occurs not only laterally but also vertically towards the buried collector layer. The lateral encroachment is the same problem as experienced by the double polysilicon self-aligned processes, whereas the vertical encroachment is specific to the SICOS structure. To reduce the extrinsic base resistance, the sidewall contact area should be kept large, and the graft base should also be satisfactory diffused. Therefore, the graft base is deeper than the intrinsic base region and the collector-base junction area is much larger than the original dimension on the mask. Hence, the collector-base junction capacitance can not be decreased while maintaining low base resistance. Moreover, the vertical encroachment of the extrinsic base causes the reduction of the base-collector reverse breakdown voltage.

Great efforts had been paid to remove these complications. A *self*aligned *e*dge *c*ontact *t*echnology (SELECT) was applied to the original SICOS [68], whereby a basic gate delay of 48 ps was demonstrated by an ECL circuit at a switching current of 0.58 mA. Another approach was also reported, the *t*wo-step *o*xidation of the *s*idewall *s*urface (TOSS) [69]. Figure 2.14 shows the improved process steps, which determines the base contact width. The mesa is covered by a nitride frame (Fig. 2.14(a)). Then, the second mesa etching is performed by an is otropic chemical etching.

Fig. 2.13 Fabrication steps of the SICOS process [67].

The sidewall is again covered by nitride (Fig. 2.14(b)). Finally, isolation is achieved by LOCOS, followed by the nitride removal (Fig. 2.14(c)). These process options have been introduced to control the sidewall contact width to prevent the vertical encroachment. Nevertheless, these process modifications result in process complexity and a higher base resistance. This situation seems to show that practical bipolar transistors are basically two-dimensional three terminal devices, which never operates in one-dimensional mode because two opposite conductive carriers must pass orthogonally to each other. Therefore, to optimize the device structure, two-dimensional feature, or the equivalent distributed circuit characteristics should always be taken into account.

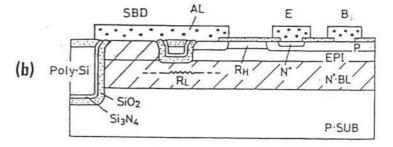

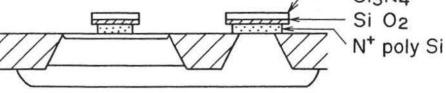

The other unique self-aligned approach for obtaining a sidewall base contact structure was demonstrated by a selective epitaxial growth technique. Strictly speaking, it was an epitaxial polysilicon simultaneous growth technique [70]. Figure 2.15 shows the process steps. After an n<sup>+</sup> buried layer is diffused, CVD oxide is deposited and active areas are opened by conventional lithography and etching (Fig. 2.15(a)). Then, an n-type epitaxial layer and a simultaneously grown polysilicon layer are continuously deposited. The surface of the epitaxial polysilicon-layer is covered by nitride (Fig. 2.15(b)). By using a controlled planarization technique, the nitride and the polysilicon on the field oxide are removed followed by base-electrode boron-ion-implantation (Fig. 2.15(c), (d)). Hence, the polysilicon surface is locally oxidized. The nitride at the intrinsic base region is removed and the intrinsic base is implanted (Fig. 2.15(e)). The emitter is diffused through a polysilicon layer from an arsenic doped spun-on-glass layer (Fig. 2.15(f)). By using this process, a basic gate delay of 83 ps was demonstrated by an LCML circuit at a 1 mW/gate power dissipation. Although the elegant feature of the technique was realized, this structure has the same problems as those of the SICOS. Moreover, the peripheral area of the selective epitaxial region has numerous crystalline defects, which must be eliminated to suppress no leakage current. Finally, there also seems to be some difficulty in achieving a one-dimensional device structure using selective epitaxial techniques.

#### 2.3.5 Polysilicon Emitter and Emitter-Base Heterojunction

In addition to various kinds of self-aligning techniques, two notable process techniques have also been employed or investigated in modern silicon bipolar devices. One is polysilicon emitter, which is the basic concept for self-aligned transistor structures, and the other is emitter-base heterojunction. Polysilicon emitter can enhance the dc gain even with shallow base-emitter junction. Nevertheless, the mechanism of the gain enhancement is not perfectly understood, and much discussion had been reported at conferences or in scientific papers. Although to describe all of these is beyond the scope of this dissertation, the important point is that, by using polysilicon emitter, the current gain is no longer considered to be the limiting figure of merit for silicon bipolar transistors with shallow base-emitter junctions.

Silicon-based heterojunction BJTs (HBTs), or the widegap emitter and/or narrow gap base have also been proposed to enhance the polysilicon emitter effect. Silicon-germanium for the narrow gap base is now becoming the most promising candidate, and a sophisticate process technology combining selective ultra high vacuums (UHV) CVD epitaxial base with double-polysilicon self-aligned structure has also been proposed [71,72].

## 2.3.6 Conclusion

The double polysilicon self-aligned structure is also another must for high-speed silicon bipolar LSIs. By employing this structure, BJTs had achieved high-speed performance more competitive than compound semiconductor devices without using tight lithographic design rules. BJTs also utilized full advantage of polysilicon material properties, that have recently been merged to silicon-based heterojunction BJTs.

## 2.4 Physics-Based Bipolar Transistor Design

# 2.4.1 Introduction

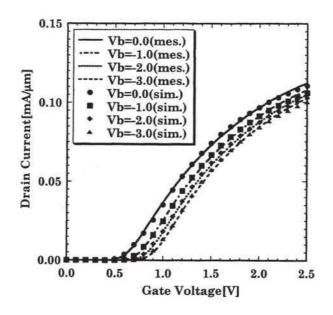

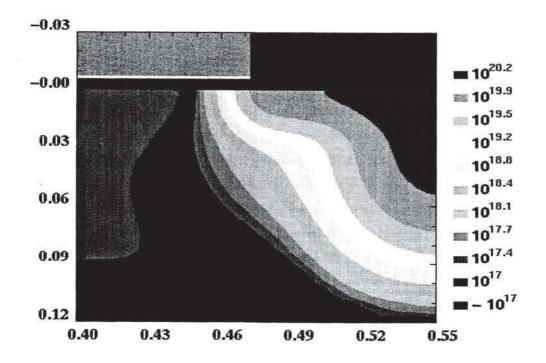

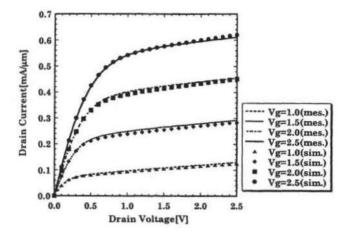

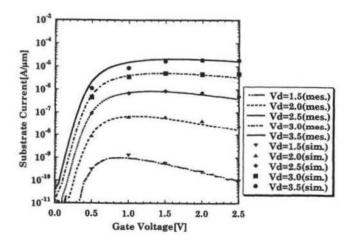

In order to extract ultimate high-speed performance of silicon BJTs, well-balanced optima of device parameters such as cutoff frequency, base resistance and base-collector capacitance have major concerns. For example, by combining double polysilicon self-aligned processes, a pedestal-collector transistor has revived to improve cutoff frequency using a selective-ion-implantation technique [32,73-77]. The transition was able to achieve satisfactorily high cutoff frequency without so much increase of base resistance and base-collector capacitance because a pedestal collector is self-aligned to an intrinsic base region.