## OpenAIR@RGU

# The Open Access Institutional Repository at Robert Gordon University

http://openair.rgu.ac.uk

**Citation Details**

Citation for the version of the work held in 'OpenAIR@RGU':

GOLI, M., 2015. Autonomic behavioural framework for structural parallelism over heterogeneous multi-core systems. Available from *OpenAIR@RGU*. [online]. Available from: http://openair.rgu.ac.uk

### Copyright

Items in 'OpenAIR@RGU', Robert Gordon University Open Access Institutional Repository, are protected by copyright and intellectual property law. If you believe that any material held in 'OpenAIR@RGU' infringes copyright, please contact <u>openair-help@rgu.ac.uk</u> with details. The item will be removed from the repository while the claim is investigated.

## Autonomic Behavioural Framework for Structural Parallelism over Heterogeneous Multi-Core Systems

Mehdi Goli

A thesis submitted in partial fulfilment of the requirements of the Robert Gordon University for the degree of Doctor of Philosophy May 2015

### Abstract

With the continuous advancement in hardware technologies, significant research has been devoted to design and develop high-level parallel programming models that allow programmers to exploit the latest developments in heterogeneous multi-core/many-core architectures.

Structural programming paradigms propose a viable solution for efficiently programming modern heterogeneous multi-core architectures equipped with one or more programmable Graphics Processing Units (GPUs). Applying structured programming paradigms, it is possible to subdivide a system into building blocks (modules, skids or components) that can be independently created and then used in different systems to derive multiple functionalities.

Exploiting such systematic divisions, it is possible to address extra-functional features such as application performance, portability and resource utilisations from the component level in heterogeneous multi-core architecture. While the computing function of a building block can vary for different applications, the behaviour (semantic) of the block remains intact. Therefore, by understanding the behaviour of building blocks and their structural compositions in parallel patterns, the process of constructing and coordinating a structured application can be automated.

In this thesis we have proposed Structural Composition and Interaction Protocol (SKIP) as a systematic methodology to exploit the structural programming paradigm (Building block approach in this case) for constructing a structured application and extracting/injecting information from/to the structured application. Using SKIP methodology, we have designed and developed Performance Enhancement Infrastructure (PEI) as a SKIP compliant autonomic behavioural framework to automatically coordinate structured parallel applications based on the extracted extra-functional properties related to the parallel computation patterns.

We have used 15 different PEI-based applications (from large scale applications with heavy input workload that take hours to execute to small-scale applications which take seconds to execute) to evaluate PEI in terms of overhead and performance improvements. The experiments have been carried out on 3 different Heterogeneous (CPU/GPU) multi-core architectures (including one cluster machine with 4 symmetric nodes with one GPU per node and 2 single machines with one GPU per machine). Our results demonstrate that with less than 3% overhead, we can achieve up to one order of magnitude speed-up when using PEI for enhancing application performance.

To my beloved, friend and guide, Chariji

## Acknowledgements

First and foremost, I would like to thank my father who was my main motivator in perusing my education to the highest degree.

I would like to thank my wife who has been with me through all difficult periods that I went through during these years and her advice for handling those difficult situations.

I would like to thank my family as well who patiently tolerated the hard situation of minimum contact and support from me through these years.

I would like to thank my supervisory team for their efficient advice and support, both morally and technically, without which it would not have been possible for me to complete the PhD.

## Declaration

I declare that this thesis was composed by myself, that the work contained herein is my own except where explicitly stated otherwise in the text, and that this work has not been submitted for any other degree or professional qualification except as specified.

(Mehdi Goli)

### Nomenclature

ACG Abstract Computation Graph

AMD Advanced Micro Devices

**API** Application Program Interface

APUs Accelerated Processing Units

**CPU** Central Processing Unit

CUDA Compute Unified Device Architecture

DSL Domain Specific Language

DSRI Dynamic Skeleton Runtime Interface

**DSP** Digital signal processing

FF FastFLow

FIFO First-in First-out

**FP** Functional Programming

FPGA Field-Programmable Gate Array

GPGPU General Purpose Graphics Processing Unit

GPU Graphics Processing Unit

**GS** Group Size

HAL High-Level Abstraction Layer

HFastFlow Heterogeneous FastFLow

Intel TBB Intel Threading Building Block

LDS Local Data Share

MCTS Monte Carlo Tree Search

MD Molecular Dynamic

MISD Multiple Instruction Single Data

MPI Message Passing Interface

**ODVL** OpenCL Device Virtualisation Layer

OpenCL Open Computing Language

**OpenMP** Open Multi-Processing

**PE** Processing Element

PEI Performance Enhancement Infrastructure

PETs Performance Enhancement Tools

**POSIX** Portable Operating System Interface

RISC-Pb<sup>2</sup>l Reduced Instruction Set Computing based Parallel Building Block Library

**RPC** Remote Procedure Call

SIMD Single Instruction Multiple Data

SKIP Structural Composition and Interaction Protocol

SMs Streaming Multi-Processors

SMTWTP Single Machine Total Weighted Tardiness ProblemUCT Upper Confidence bounds applied to TreesUML Unified Modelling LanguageURNG Uniform Random Number Generator

ZMQ Zero Message passing Queue

# **Table of Contents**

| 1 | Intr | oduction                                                                                        | 1  |

|---|------|-------------------------------------------------------------------------------------------------|----|

|   | 1.1  | Contributions                                                                                   | 5  |

|   | 1.2  | List of Publications and Authorship                                                             | 9  |

|   | 1.3  | Research Method                                                                                 | 11 |

|   | 1.4  | Thesis Architecture                                                                             | 12 |

| 2 | Rev  | iew of Literature                                                                               | 15 |

|   | 2.1  | Preliminaries                                                                                   | 15 |

|   |      | 2.1.1 Control Systems                                                                           | 16 |

|   |      | 2.1.2 OpenCL                                                                                    | 16 |

|   | 2.2  | Abstraction Mechanism                                                                           | 18 |

|   |      | 2.2.1 Traditional Low-level Library Model                                                       | 18 |

|   |      | 2.2.2 Structured High-level Parallel Programming Model                                          | 18 |

|   | 2.3  | Parallel Applications Optimisation                                                              | 25 |

|   |      | 2.3.1 Scheduling System Over Heterogeneous Multi-core Architecture                              | 25 |

|   |      | 2.3.2 Auto-Tuning Parallel Applications' Performance                                            | 27 |

|   | 2.4  | Research Gap                                                                                    | 29 |

| 3 | SKI  | P Methodology for Coordinating Structural Parallel Programming                                  | 33 |

|   | 3.1  | Controlling Parameters                                                                          | 33 |

|   | 3.2  | Extending RISC-pb <sup>2</sup> l Over Heterogeneous Architectures $\ldots \ldots \ldots \ldots$ | 34 |

|   | 3.3  | Structural Composition and Interaction Protocol (SKIP)                                          | 38 |

|   | 3.4  | SKIP Compliant Autonomic Behavioural Framework                                                  | 45 |

|   | 3.5  | Summary                                                                                         | 47 |

| 4 | Perf | formance Enhancement Infrastructure                                                             | 49 |

|   | 4.1  | FastFlow Expansions                                                                             | 50 |

|   |      | 4.1.1 OpenCL Back-end                                                                           | 50 |

|   |      | 4.1.2 Adaptive Load-balancer                                                                    | 53 |

|   |      | 4.1.3 Memory Management                                                                         | 54 |

|   |      | 4.1.4   | Efficient Idling                         |

|---|------|---------|------------------------------------------|

|   | 4.2  | HFastI  | Flow Instrumentation                     |

|   |      | 4.2.1   | Controlling Parameters                   |

|   |      | 4.2.2   | Performance Metrics                      |

|   |      | 4.2.3   | Structural Meta-data                     |

|   | 4.3  | High-I  | Level Abstraction Layer (HAL)            |

|   |      | 4.3.1   | SKIP Adaptor                             |

|   |      | 4.3.2   | Dynamic Structural Runtime Interface     |

|   |      | 4.3.3   | ODVL: OpenCL Device Virtualisation Layer |

|   | 4.4  | Perform | mance Enhancement Tools (PETs)           |

|   |      | 4.4.1   | Sensor Analyser                          |

|   |      | 4.4.2   | Adaptive Workload Distribution           |

|   |      | 4.4.3   | OpenCL Scheduler                         |

|   |      | 4.4.4   | Static Structural Configuration          |

|   | 4.5  | Summ    | ary                                      |

| 5 | Eval | uation  | of OpenCL Based Applications 85          |

|   | 5.1  | Applic  | ation Suite                              |

|   |      | 5.1.1   | Sobel Filter                             |

|   |      | 5.1.2   | Bilateral Denoise                        |

|   |      | 5.1.3   | Gaussian Noise                           |

|   |      | 5.1.4   | Uniform Random Noise Generator (URNG)    |

|   |      | 5.1.5   | Recursive Gaussian                       |

|   |      | 5.1.6   | Separable Convolution                    |

|   | 5.2  | Evalua  | ntion                                    |

|   |      | 5.2.1   | Performance Overhead of PEI              |

|   |      | 5.2.2   | OpenCL Back-end                          |

|   |      | 5.2.3   | Workload Distribution                    |

|   |      | 5.2.4   | Phase Changing Prediction                |

|   |      | 5.2.5   | Multi-tenant Application                 |

|   | 5.3  | Summ    | ary                                      |

| 6 | Eval | uation  | of Generic Applications 119              |

|   | 6.1  | Homog   | geneous Application                      |

|   |      | 6.1.1   | <i>N</i> -body Simulation                |

|   |      | 6.1.2   | Mandelbrot                               |

|   |      | 6.1.3   | Quick Sort                               |

|   |      | 6.1.4   | Fibonacci                                |

|   |             | 6.1.5    | Stencil                                                   | . 126 |

|---|-------------|----------|-----------------------------------------------------------|-------|

|   |             | 6.1.6    | N-queens                                                  | . 127 |

|   | 6.2         | Hetero   | geneous Applications                                      | . 130 |

|   |             | 6.2.1    | Custom Implementation of EISPACK Routines                 | . 130 |

|   |             | 6.2.2    | SMTWTP                                                    | . 133 |

|   |             | 6.2.3    | Molecular Dynamics                                        | . 134 |

|   | 6.3         | Applic   | ation Evaluation                                          | . 136 |

|   |             | 6.3.1    | Performance Overhead                                      | . 136 |

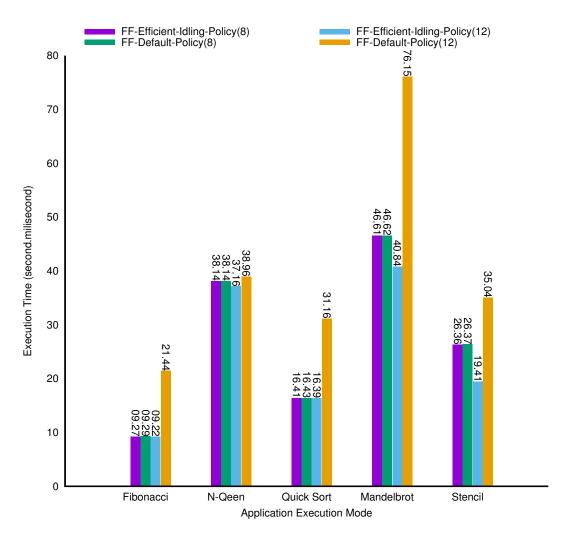

|   |             | 6.3.2    | Efficient Idling                                          | . 144 |

|   |             | 6.3.3    | Memory Management                                         | . 146 |

|   |             | 6.3.4    | Static Structural Configuration                           | . 147 |

|   | 6.4         | Summa    | ary                                                       | . 152 |

| 7 | Con         | clusion  | & Future Work                                             | 155   |

|   | 7.1         | Consol   | lidation of Research                                      | . 155 |

|   | 7.2         | Resear   | ch Impact                                                 | . 160 |

|   | 7.3         | Ongoir   | ng Research and Future Work                               | . 163 |

| A | Valio       | lation o | of RISC-pb <sup>2</sup> l Grammar                         | 167   |

|   | A.1         |          | on-based Parallel Patterns                                | . 167 |

|   |             | A.1.1    | Embarrassingly Parallel Patterns                          | . 167 |

|   |             | A.1.2    | Reduction                                                 | . 168 |

|   |             | A.1.3    | Pipe                                                      | . 168 |

|   |             | A.1.4    | Divide & Conquer                                          | . 169 |

|   |             | A.1.5    | Stencil                                                   | . 170 |

|   | A.2         | Genera   | al Purpose Computing Models                               | . 171 |

|   |             | A.2.1    | <i>BSP</i>                                                | . 171 |

|   |             | A.2.2    | Map-Reduce                                                | . 172 |

|   |             | A.2.3    | MDF                                                       | . 173 |

|   | A.3         | Domai    | n Specific pattern                                        | . 174 |

|   |             | A.3.1    | GSP                                                       | . 174 |

|   |             | A.3.2    | OB                                                        | . 175 |

|   |             | A.3.3    | NPP                                                       | . 176 |

| B | The         | Structu  | ral Representation of Application Suite                   | 177   |

|   | <b>B</b> .1 | Unifor   | m Random Noise Generator                                  | . 177 |

|   |             | B.1.1    | Demonstration of URNG with RISC-pb <sup>2</sup> l Grammar | . 177 |

|   |             | B.1.2    | SKIP-compliant Object Representing the URNG Application   | . 177 |

|   |             |          |                                                           |       |

|   | <b>B</b> .2 | Recurs                                                                                                                       | vive Gaussian                                                                                                                                                                                                                      |

|---|-------------|------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |             | B.2.1                                                                                                                        | Demonstration of Recursive Gaussian with RISC-pb <sup>2</sup> l Grammar 178                                                                                                                                                        |

|   |             | B.2.2                                                                                                                        | SKIP-compliant Object Representing the Recursive Gaussian Applica-                                                                                                                                                                 |

|   |             |                                                                                                                              | tion                                                                                                                                                                                                                               |

|   | B.3         | Separa                                                                                                                       | ble Convolution                                                                                                                                                                                                                    |

|   |             | B.3.1                                                                                                                        | Demonstration of Separable Convolution with RISC-pb <sup>2</sup> l Grammar $180$                                                                                                                                                   |

|   |             | B.3.2                                                                                                                        | SKIP-compliant Object Representing the Separable Convolution Ap-                                                                                                                                                                   |

|   |             |                                                                                                                              | plication                                                                                                                                                                                                                          |

|   | B.4         | Bilater                                                                                                                      | al Denoise                                                                                                                                                                                                                         |

|   |             | <b>B.4.1</b>                                                                                                                 | Demonstration of Bilateral Denoise with RISC-pb <sup>2</sup> l Grammar $\ldots \ldots 182$                                                                                                                                         |

|   |             | B.4.2                                                                                                                        | SKIP-compliant Object Representing the Bilateral Denoise Application 182                                                                                                                                                           |

|   | B.5         | Sobel                                                                                                                        | Filter                                                                                                                                                                                                                             |

|   |             | B.5.1                                                                                                                        | Demonstration of Soble Filter with RISC-pb <sup>2</sup> l Grammar $\ldots \ldots \ldots 184$                                                                                                                                       |

|   |             | B.5.2                                                                                                                        | SKIP-compliant Object Representing the Soble Filter Application 184                                                                                                                                                                |

|   | B.6         | Gaussi                                                                                                                       | an Noise                                                                                                                                                                                                                           |

|   |             | B.6.1                                                                                                                        | Demonstration of Gaussian Noise with RISC-pb <sup>2</sup> l Grammar $\ldots \ldots 185$                                                                                                                                            |

|   |             | B.6.2                                                                                                                        | SKIP-compliant Object Representing the Gaussian Noise Application . 185                                                                                                                                                            |

| С | The         | SKIP (                                                                                                                       | Compliant Objects 187                                                                                                                                                                                                              |

| U |             |                                                                                                                              | 2                                                                                                                                                                                                                                  |

|   | C.1         | Sensor                                                                                                                       | Files 187                                                                                                                                                                                                                          |

|   | C.1         | Sensor<br>C.1.1                                                                                                              | Files    187      Bilateral-Denoise    187                                                                                                                                                                                         |

|   | C.1         |                                                                                                                              | Bilateral-Denoise                                                                                                                                                                                                                  |

|   | C.1         | C.1.1                                                                                                                        | Bilateral-Denoise187Recursive Gaussian190                                                                                                                                                                                          |

|   | C.1         | C.1.1<br>C.1.2                                                                                                               | Bilateral-Denoise187Recursive Gaussian190Gausian-Noise193                                                                                                                                                                          |

|   | C.1         | C.1.1<br>C.1.2<br>C.1.3                                                                                                      | Bilateral-Denoise187Recursive Gaussian190                                                                                                                                                                                          |

|   | C.1         | C.1.1<br>C.1.2<br>C.1.3<br>C.1.4                                                                                             | Bilateral-Denoise187Recursive Gaussian190Gausian-Noise193Sobel Filter195                                                                                                                                                           |

|   | C.1<br>C.2  | C.1.1<br>C.1.2<br>C.1.3<br>C.1.4<br>C.1.5<br>C.1.6                                                                           | Bilateral-Denoise187Recursive Gaussian190Gausian-Noise193Sobel Filter195separable-Convolution196                                                                                                                                   |

|   |             | C.1.1<br>C.1.2<br>C.1.3<br>C.1.4<br>C.1.5<br>C.1.6                                                                           | Bilateral-Denoise187Recursive Gaussian190Gausian-Noise193Sobel Filter195separable-Convolution196URNG198                                                                                                                            |

|   |             | C.1.1<br>C.1.2<br>C.1.3<br>C.1.4<br>C.1.5<br>C.1.6<br>Actuat                                                                 | Bilateral-Denoise187Recursive Gaussian190Gausian-Noise193Sobel Filter195separable-Convolution196URNG198or Files200                                                                                                                 |

|   |             | C.1.1<br>C.1.2<br>C.1.3<br>C.1.4<br>C.1.5<br>C.1.6<br>Actuat<br>C.2.1                                                        | Bilateral-Denoise187Recursive Gaussian190Gausian-Noise193Sobel Filter195separable-Convolution196URNG198or Files200Bilateral-Denoise200                                                                                             |

|   |             | C.1.1<br>C.1.2<br>C.1.3<br>C.1.4<br>C.1.5<br>C.1.6<br>Actuat<br>C.2.1<br>C.2.2                                               | Bilateral-Denoise187Recursive Gaussian190Gausian-Noise193Sobel Filter195separable-Convolution196URNG198or Files200Bilateral-Denoise200Gaussian-Noise201                                                                            |

|   |             | C.1.1<br>C.1.2<br>C.1.3<br>C.1.4<br>C.1.5<br>C.1.6<br>Actuat<br>C.2.1<br>C.2.2<br>C.2.3                                      | Bilateral-Denoise187Recursive Gaussian190Gausian-Noise193Sobel Filter195separable-Convolution196URNG198or Files200Bilateral-Denoise200Gaussian-Noise201Recursive-Gaussian202                                                       |

|   |             | C.1.1<br>C.1.2<br>C.1.3<br>C.1.4<br>C.1.5<br>C.1.6<br>Actuat<br>C.2.1<br>C.2.2<br>C.2.3<br>C.2.4                             | Bilateral-Denoise187Recursive Gaussian190Gausian-Noise193Sobel Filter195separable-Convolution196URNG198or Files200Bilateral-Denoise200Gaussian-Noise201Recursive-Gaussian202Sobel-Filter204                                        |

|   |             | C.1.1<br>C.1.2<br>C.1.3<br>C.1.4<br>C.1.5<br>C.1.6<br>Actuat<br>C.2.1<br>C.2.2<br>C.2.3<br>C.2.4<br>C.2.5<br>C.2.6           | Bilateral-Denoise187Recursive Gaussian190Gausian-Noise193Sobel Filter195separable-Convolution196URNG198or Files200Bilateral-Denoise200Gaussian-Noise201Recursive-Gaussian202Sobel-Filter204Separable-Convolution204                |

| D | C.2<br>C.3  | C.1.1<br>C.1.2<br>C.1.3<br>C.1.4<br>C.1.5<br>C.1.6<br>Actuat<br>C.2.1<br>C.2.2<br>C.2.3<br>C.2.4<br>C.2.5<br>C.2.6<br>Constr | Bilateral-Denoise187Recursive Gaussian190Gausian-Noise193Sobel Filter195separable-Convolution196URNG198or Files200Bilateral-Denoise200Gaussian-Noise201Recursive-Gaussian202Sobel-Filter204Separable-Convolution204Sobel-Filter204 |

| D | C.2<br>C.3  | C.1.1<br>C.1.2<br>C.1.3<br>C.1.4<br>C.1.5<br>C.1.6<br>Actuat<br>C.2.1<br>C.2.2<br>C.2.3<br>C.2.4<br>C.2.5<br>C.2.6<br>Constr | Bilateral-Denoise187Recursive Gaussian190Gausian-Noise193Sobel Filter195separable-Convolution196URNG198or Files200Bilateral-Denoise200Gaussian-Noise201Recursive-Gaussian202Sobel-Filter204Separable-Convolution204URNG205         |

| Bił | Bibliography 219 |                                                        |     |  |  |

|-----|------------------|--------------------------------------------------------|-----|--|--|

|     | E.1              | <i>N</i> -body Simulation                              | 215 |  |  |

| E   | Impl             | ementation of N-body Simulation under Three Frameworks | 215 |  |  |

|     | D.9              | <i>MD</i>                                              | 212 |  |  |

|     | D.8              | getSolution component for <i>SMTWTP</i>                | 211 |  |  |

|     | D.7              | EISPACK Routine                                        | 211 |  |  |

|     | D.6              | N-queen                                                | 210 |  |  |

|     | D.5              | Stencil                                                | 210 |  |  |

|     | D.4              | Fibonacci                                              | 209 |  |  |

|     | D.3              | Quick sort                                             | 209 |  |  |

# **List of Figures**

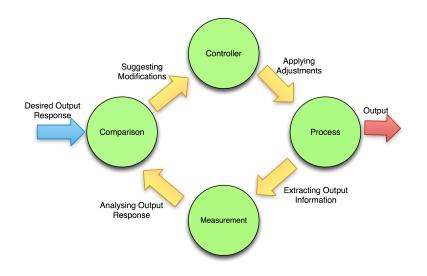

| 2.1  | Feedback control system                                                          | 16  |

|------|----------------------------------------------------------------------------------|-----|

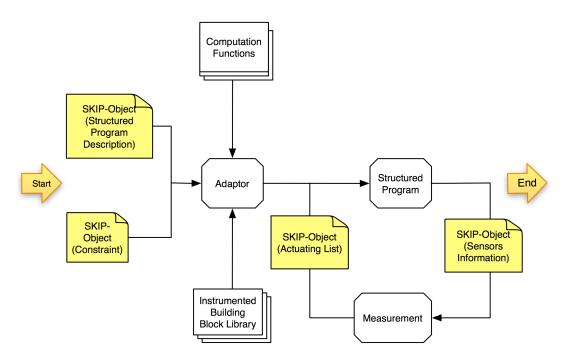

| 3.1  | Schematic view of construction and execution of a structured program using       |     |

|      | SKIP compliant autonomic behavioural system                                      | 45  |

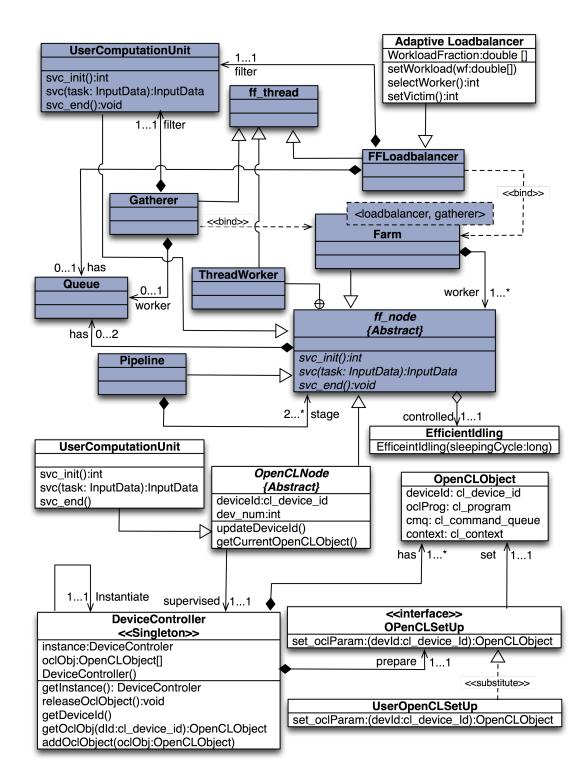

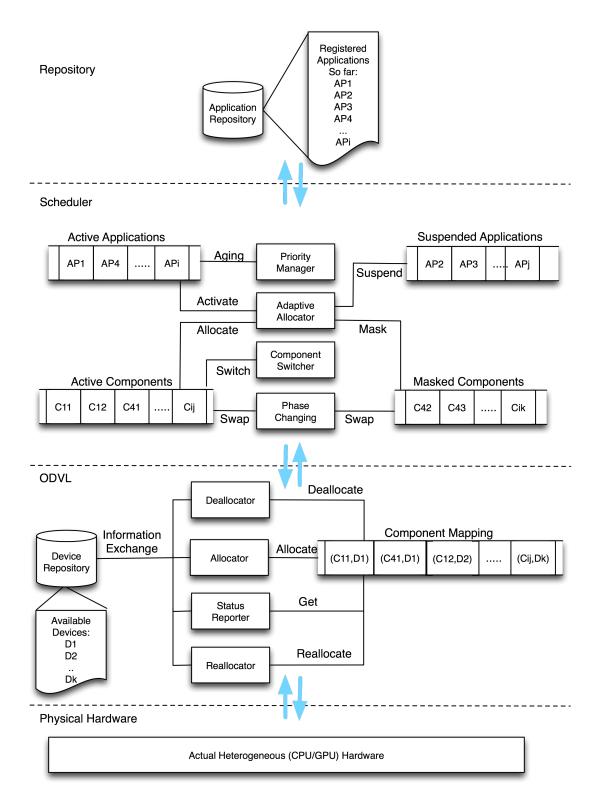

| 4.1  | A UML class diagram for instrumented FastFlow                                    | 51  |

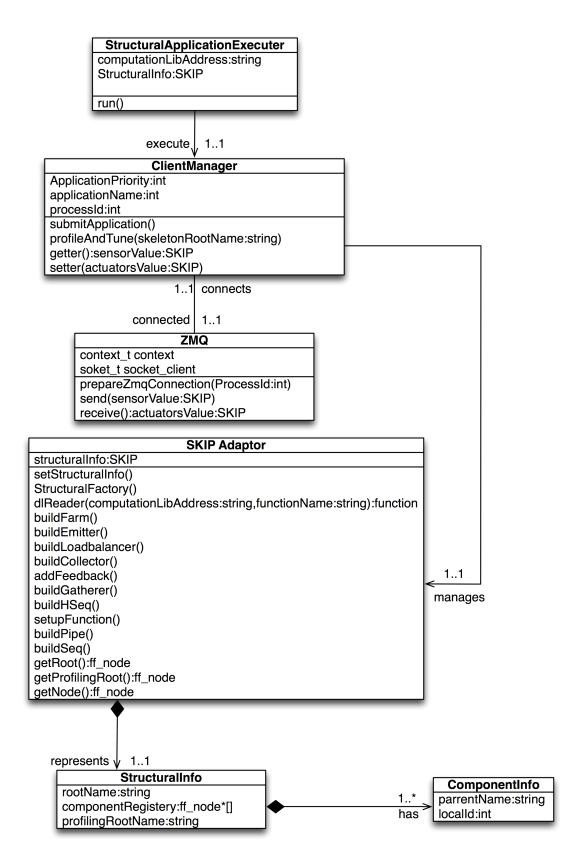

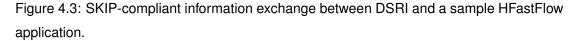

| 4.2  | A class diagram representing the DSRI client                                     | 64  |

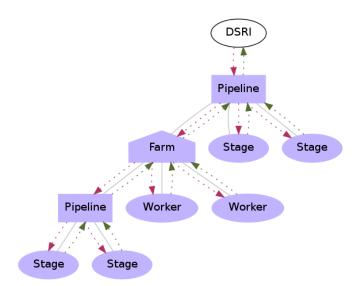

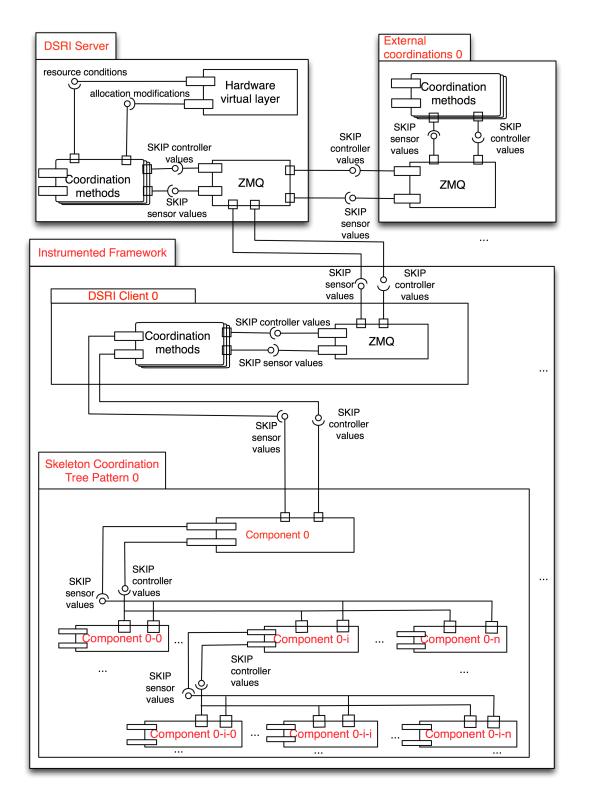

| 4.3  | SKIP-compliant information exchange between DSRI and a sample HFastFlow          |     |

|      | application.                                                                     | 65  |

| 4.4  | A class diagram representing the DSRI Server                                     | 67  |

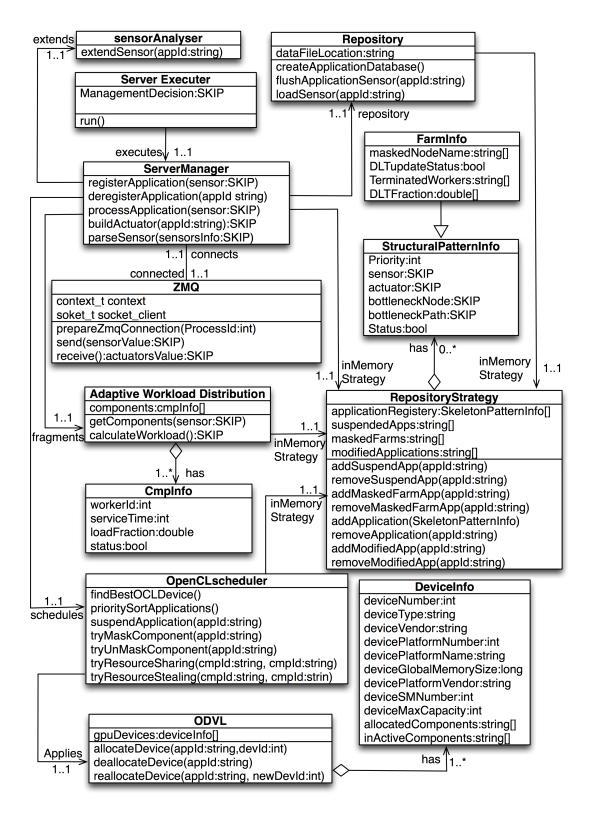

| 4.5  | An architectural view of the Proposed OpenCL Scheduler                           | 73  |

| 4.6  | A component diagram representing the physical view of the autonomous be-         |     |

|      | havioural framework                                                              | 82  |

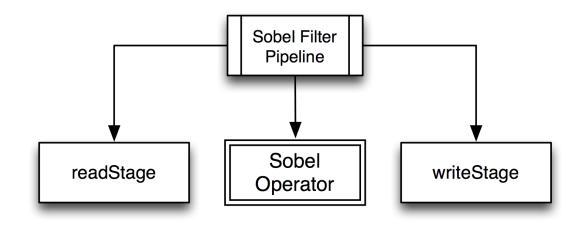

| 5.1  | The structural composition of components for sobel filter                        | 88  |

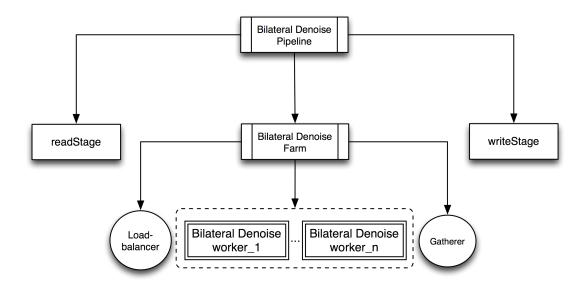

| 5.2  | The structural composition of components for Bilateral Denoise                   | 89  |

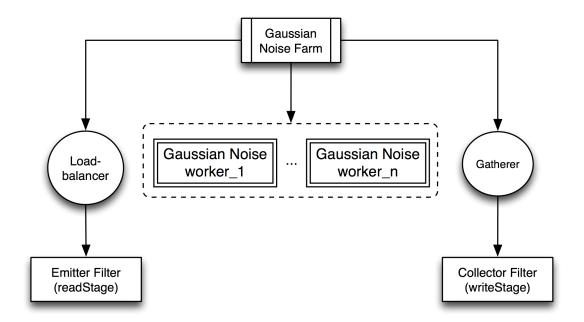

| 5.3  | The structural composition of components for Gaussian Noise                      | 90  |

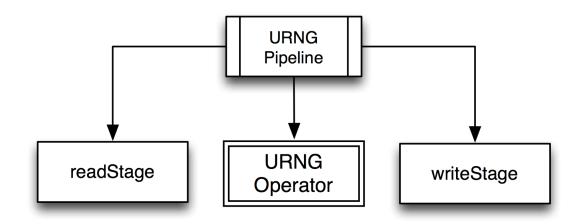

| 5.4  | The structural composition of components for URNG                                | 91  |

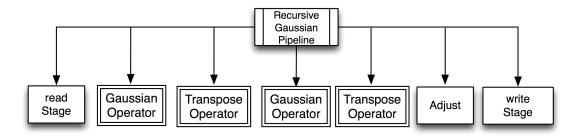

| 5.5  | The structural composition of components for Recursive Gaussian                  | 92  |

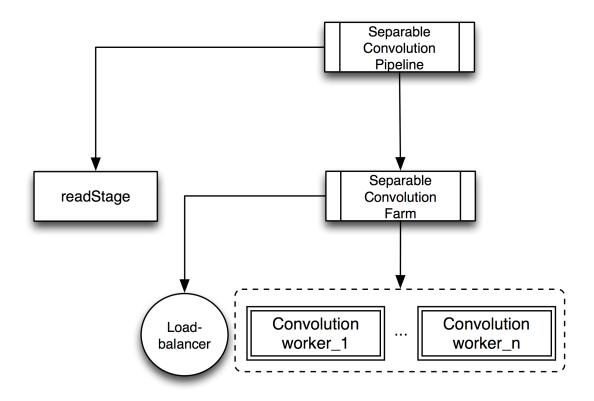

| 5.6  | The structural composition of components for Simple Convolution                  | 93  |

| 5.7  | The upper-bound overhead of performance metrics tracing for image process-       |     |

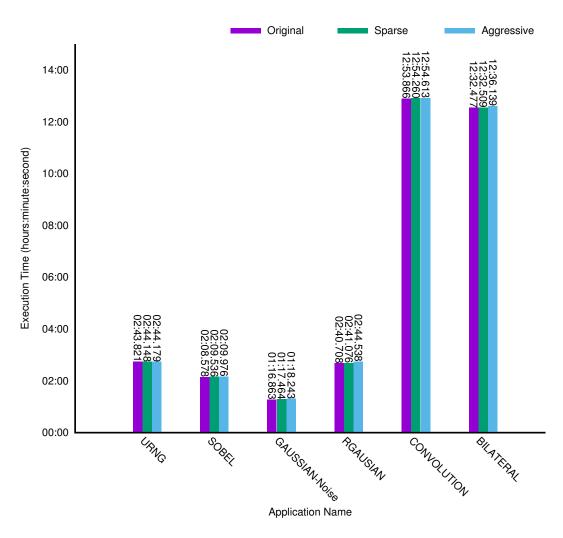

|      | ing applications                                                                 | 96  |

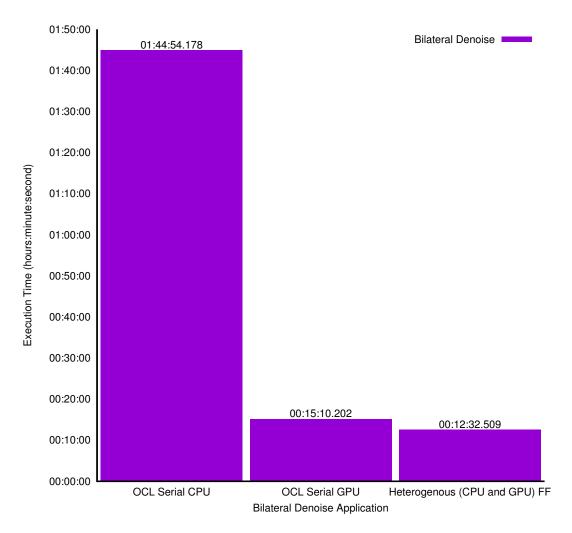

| 5.8  | Execution of Bilateral denoise using OpenCL back-end                             | 99  |

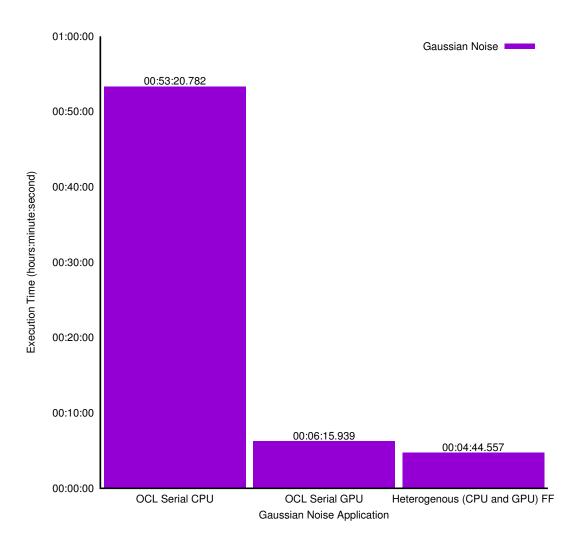

| 5.9  | Execution of Gaussian noise using OpenCL back-end                                | 100 |

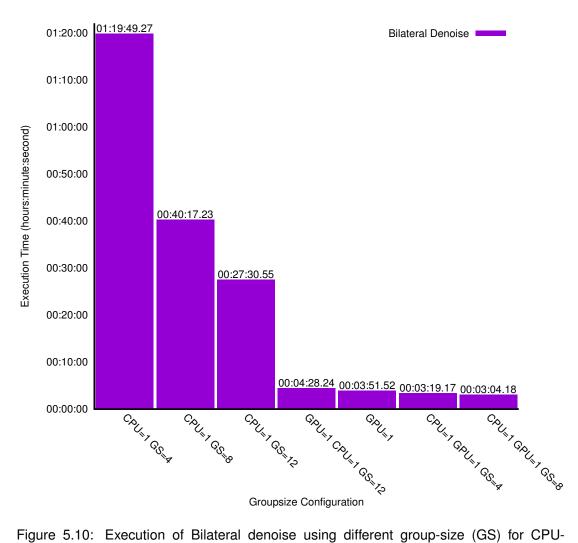

| 5.10 | Execution of Bilateral denoise using different group-size (GS) for CPU-allocated |     |

|      | OpenCL workers                                                                   | 102 |

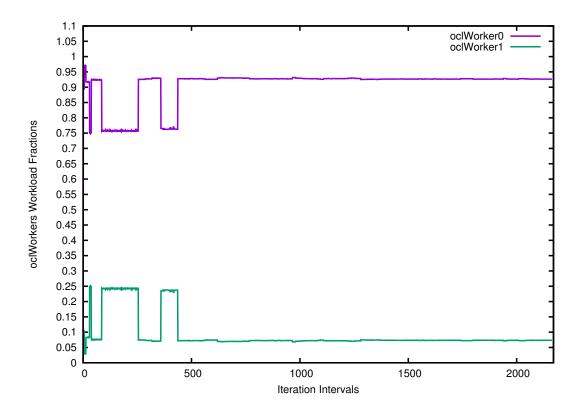

| 5.11 | The variation of workload distribution for CPU/GPU workers for different in-     |     |

|      | put stream sizes using the ad-hoc policy                                         | 104 |

| 5.12 | The variation of workload distribution for CPU/GPU workers for different in-     |     |

|      | put stream sizes using the average policy                                        | 105 |

| 5.13 | The execution time of the bilateral denoise application for different load-balancers,                                                                                                       |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | different queue sizes and different input image stream sizes                                                                                                                                |

| 5.14 | The execution time of the recursive Gaussian application for different alloca-                                                                                                              |

|      | tion policies                                                                                                                                                                               |

| 5.15 | The static structural configuration approach for recursive Gaussian 109                                                                                                                     |

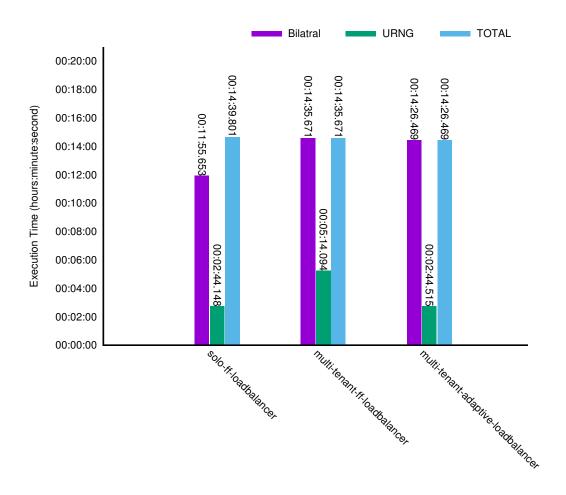

| 5.16 | The concurrent execution of the URNG and Bilateral denoise applications $\ldots$ 112                                                                                                        |

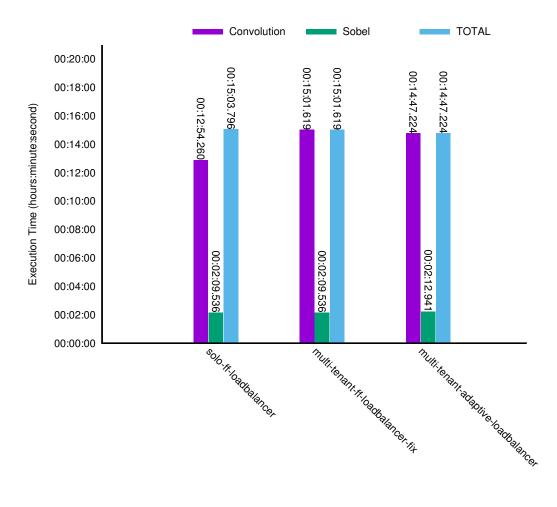

| 5.17 | The concurrent execution of the sobel filter and convolution applications $\ldots$ . 113                                                                                                    |

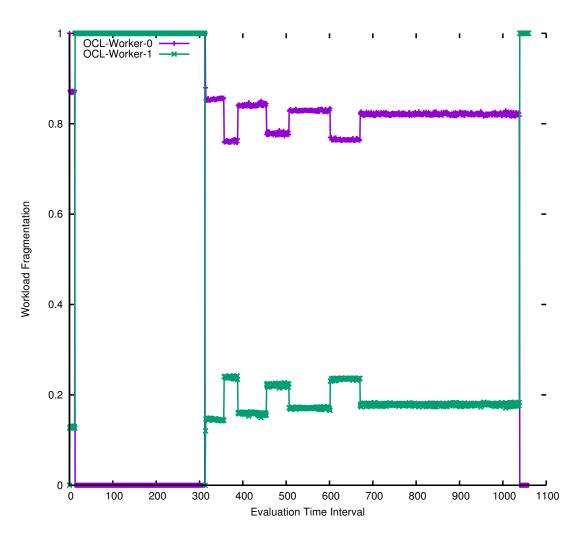

| 5.18 | The visual demonstration of the concurrent execution intervals for the sobel                                                                                                                |

|      | filter and convolution applications                                                                                                                                                         |

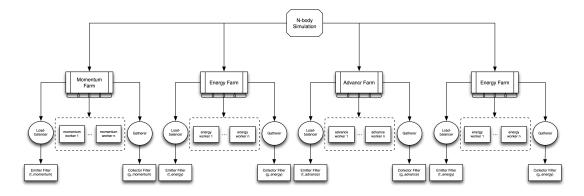

| 6.1  | The structural composition of components for the <i>N</i> -body simulation                                                                                                                  |

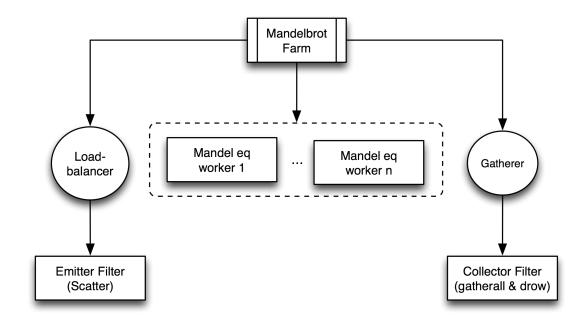

| 6.2  | The structural composition of components for Mandelbrot $\ldots \ldots \ldots \ldots \ldots 123$                                                                                            |

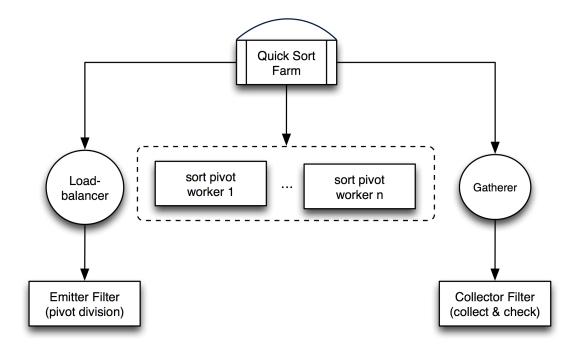

| 6.3  | The structural composition of components for quick sort $\ldots \ldots \ldots \ldots \ldots 124$                                                                                            |

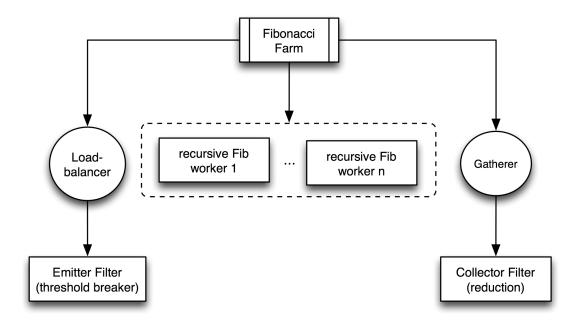

| 6.4  | The structural composition of components for Fibonacci                                                                                                                                      |

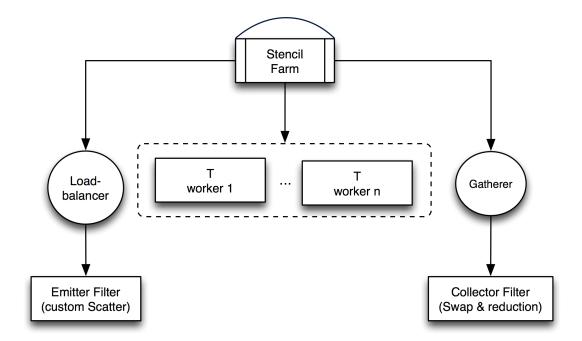

| 6.5  | The structural composition of components for stencil $\ldots \ldots \ldots$ |

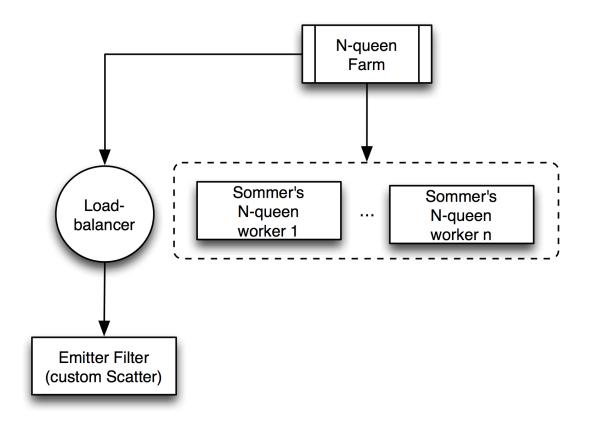

| 6.6  | The structural composition of components for <i>N</i> -queen                                                                                                                                |

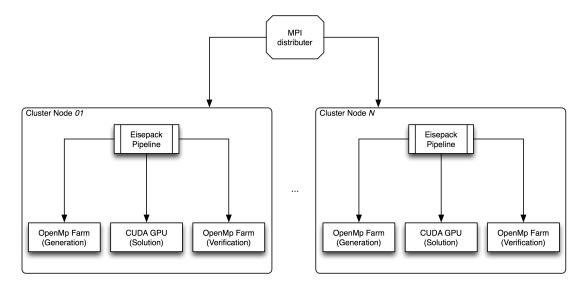

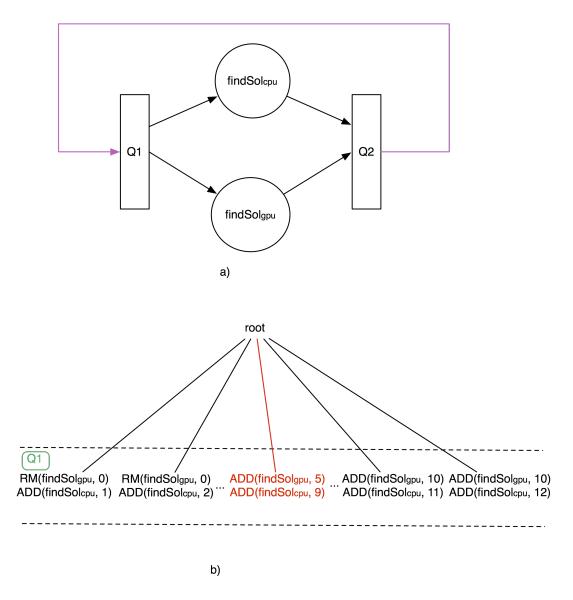

| 6.7  | The structural composition of components for EISPACK                                                                                                                                        |

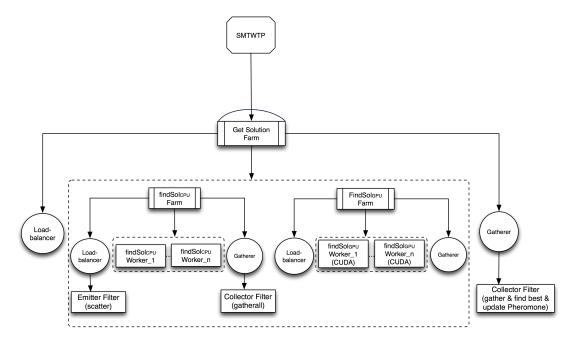

| 6.8  | The structural composition of components for SMTWTP                                                                                                                                         |

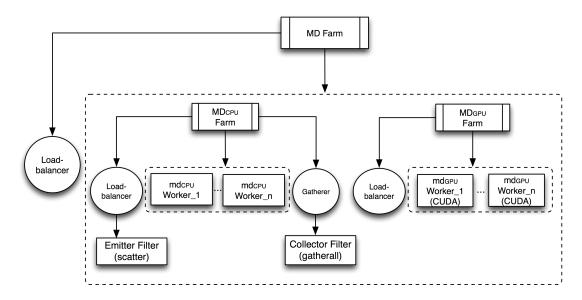

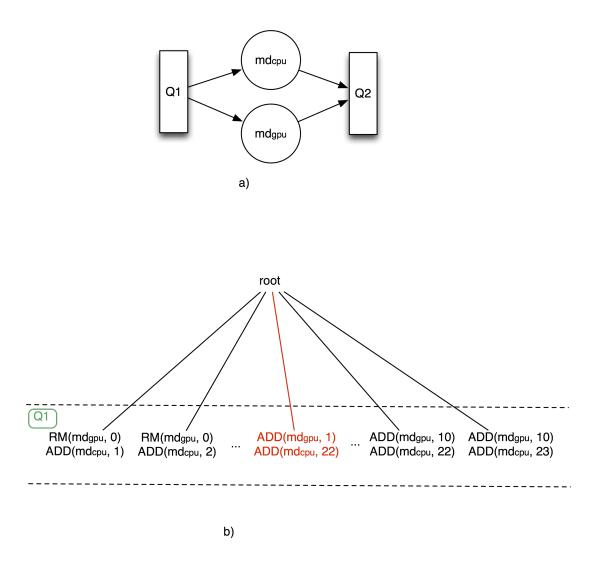

| 6.9  | The structural composition of components for <i>MD</i>                                                                                                                                      |

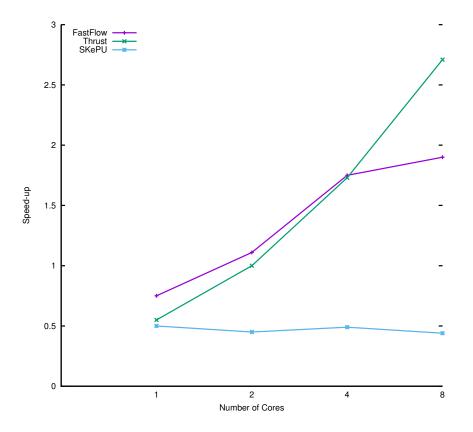

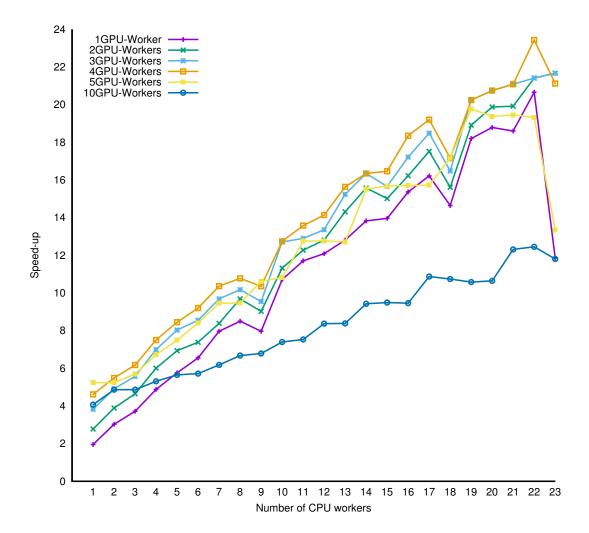

| 6.10 | Speed-up graph for N-body simulation using FastFlow, Thrust and SkePU                                                                                                                       |

|      | (Problem size: 1024 bodies)                                                                                                                                                                 |

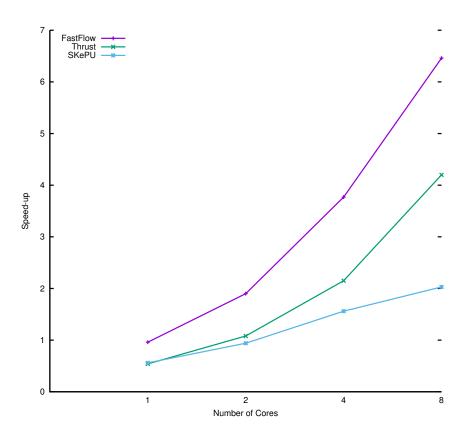

| 6.11 | Speed-up graph for N-body simulation using FastFlow, Thrust and SkePU                                                                                                                       |

|      | (Problem size: 8192 bodies)                                                                                                                                                                 |

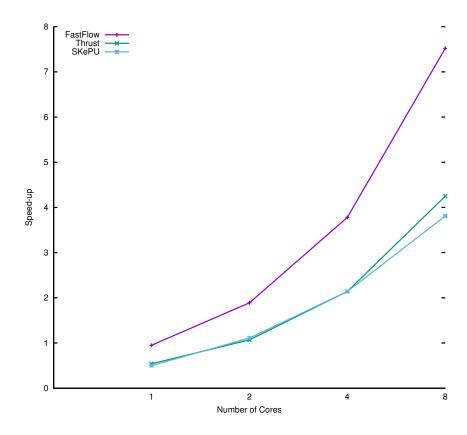

| 6.12 | Speed-up graph for N-body simulation using FastFlow, Thrust and SkePU                                                                                                                       |

|      | (Problem size: 65536 bodies)                                                                                                                                                                |

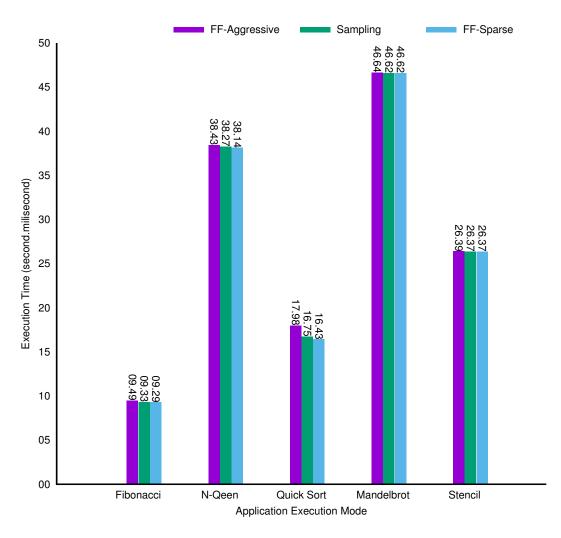

| 6.13 | The upper-bound overhead of performance metrics tracing for FastFlow bench-                                                                                                                 |

|      | mark applications                                                                                                                                                                           |

| 6.14 | The applications' runtime with and without using efficient idling technique $\ . \ . \ 145$                                                                                                 |

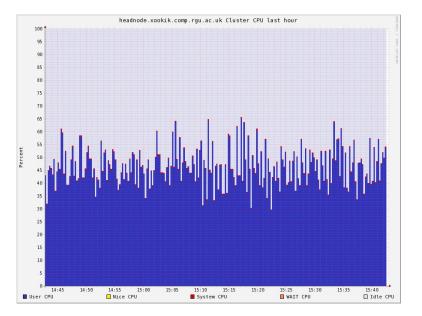

| 6.15 | The overall cluster CPU usage percentage over one hour of execution for the                                                                                                                 |

|      | EISPACK application                                                                                                                                                                         |

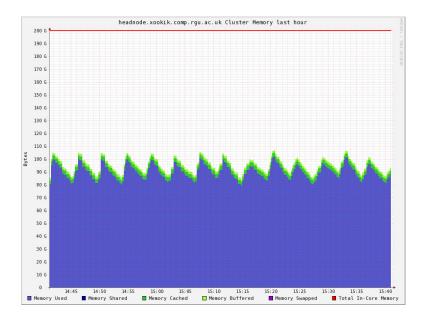

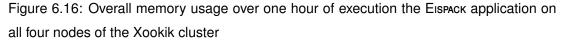

| 6.16 | Overall memory usage over one hour of execution the EISPACK application $\ldots$ 147                                                                                                        |

| 6.17 | The static structural configuration results for SMTWTP application                                                                                                                          |

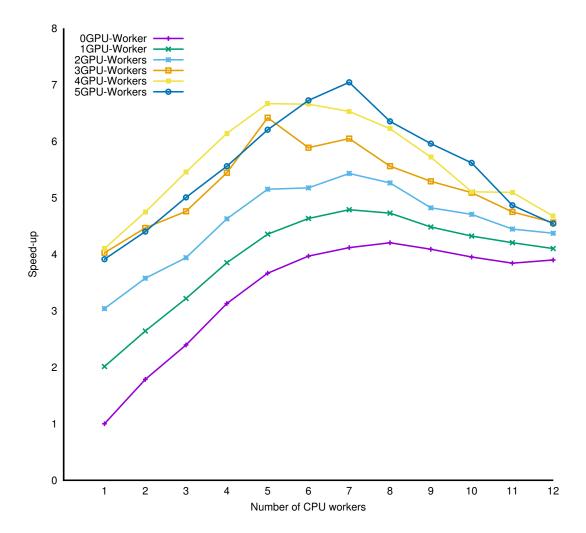

| 6.18 | Speed-up graph for SMTWTP configurations                                                                                                                                                    |

| 6.19 | The static structural configuration results for MD application $\ldots \ldots \ldots \ldots 150$                                                                                            |

| 6.20 | Speed-up graph for the molecular dynamics configurations                                                                                                                                    |

| 7.1  | Deployment diagram for distributed PEI                                                                                                                                                      |

| E.1 | The visual representation of the intermediate grid for calculating the gravita- |       |

|-----|---------------------------------------------------------------------------------|-------|

|     | tional computation of the <i>N</i> -body algorithm                              | . 216 |

# **List of Tables**

| 2.1 | An example set of well-known patterns                                                    | 20  |

|-----|------------------------------------------------------------------------------------------|-----|

| 2.2 | Base building blocks for parallel instruction                                            | 21  |

| 2.3 | Correspondence between the RISC-pb <sup>2</sup> l building block and FastFlow components | 23  |

| 3.1 | Control-required Conditions                                                              | 35  |

| 3.2 | Structural meta-data                                                                     | 39  |

| 3.3 | Control parameters                                                                       | 40  |

| 3.4 | Performance metrics                                                                      | 41  |

| 3.5 | Constraint configurations                                                                | 42  |

| 4.1 | Control parameters                                                                       | 57  |

| 4.2 | Performance metrics                                                                      | 58  |

| 4.3 | Structural meta-data                                                                     | 59  |

| 4.4 | SKIP adaptor functions to generate the HFastFlow structured application                  | 62  |

| 4.5 | Constraint configurations                                                                | 68  |

| 5.1 | Summary of Applications Characteristics                                                  | 86  |

| 5.2 | The correspondence between structural tree notations and HFastFlow components            | 87  |

| 5.3 | Hardware Specification Table for the Titanic machine and the Xookik cluster .            | 94  |

| 5.4 | Input stream specification for image processing applications                             | 97  |

| 5.5 | The execution times and GPU utilisation for the Sobel Filter application $\ldots$ .      | 98  |

| 5.6 | Workload fraction in proportion with the computing power for each OpenCL                 |     |

|     | component of the Bilateral Denoise                                                       | 103 |

| 5.7 | The bilateral application execution and different runtime for each component             | 104 |

| 5.8 | The runtime for concurrent execution of the Sobel Filter application and URNG            |     |

|     | on a node of the Xookik cluster                                                          | 111 |

| 5.9 | The runtime for concurrent execution of the Sobel Filter application and URNG            |     |

|     | on the Titanic machine                                                                   | 111 |

| 6.1 | Summary of Homogeneous Applications Characteristics                                      | 120 |

| 6.2 | Summary of Heterogeneous Applications Characteristics                            |

|-----|----------------------------------------------------------------------------------|

| 6.3 | Intel Westmere E5620 quad core processor for one of the worker node in Eddie 136 |

| 6.4 | List of the software used to evaluate the framework overhead on the Scalability  |

|     | of applications                                                                  |

| 6.5 | The detailed execution times of the FastFlow farm for calculating the gravita-   |

|     | tional force                                                                     |

| 6.6 | The detailed execution times of each function for calculating the SKePU grav-    |

|     | itational force                                                                  |

| 6.7 | Software Specification FastFlow benchmark applications                           |

| 6.8 | Active execution times on individual GPUs and total programme runtime for        |

|     | the EISPACK application                                                          |

# Listings

| 3.1 | A grammar for automatically generating RISC-pb <sup>2</sup> l based structured program- |    |

|-----|-----------------------------------------------------------------------------------------|----|

|     | ming                                                                                    | 36 |

| 3.2 | SKIP definition for building block grammar                                              | 42 |

## **Chapter 1**

## Introduction

Before 1990, there were very few parallel computers, which were only used for the most critical problems. However, the availability of parallel computers has changed dramatically since the mid 1990s. With the appearance of multiple processor cores and multi threading support, parallel computers are becoming ubiquitous. Now, almost all university computer science departments have at least one parallel computer. Virtually all oil companies, auto mobile manufacturers, drug development companies and special effects studios use parallel computing.

Although computing in less time is beneficial, and may enable problems to be solved that cannot be otherwise, it comes at a cost. Writing software to run on parallel computers can be difficult. Only a small minority of programmers have experience with parallel programming. If all these computers that are designed to exploit parallelism are going to achieve their potential, more programmers need to learn how to write parallel programmes. They need to deal with more complexities such as synchronising multiple processes/threads, handling communication between processes/threads, preventing deadlocks, and, even more, after all of these, programmers need to think about optimisation in order to achieve the best performance. Otherwise, the result might be even worse than running a programme in sequential mode.

Recent revolutions in underlying hardware have also had an important effect on parallel programming algorithms. With the appearance of the general purpose graphical processing unit (GPGPU), a new parallel programming environment is required to support the execution of the programme in a hybrid (multi-core CPU/GPGPU) environment. Several environments such as CUDA C and OpenCL are available, allowing the programmer to develop applications which can take advantage of both CPUs and GPUs.

One the one hand, GPUs have been shown to have orders of magnitude faster than CPUs for different application domains. In [1] there is an order of magnitude speed-up for a computationally intensive portion of the Weather Research and Forecast (WRF) model on a variety of NVIDIA Graphics Processing Units (GPU). In [2] with the use of a GPU accelerator the k nearest neighbor search (KNN) algorithm has been speed-up for two orders of magnitude.

In [3], one order of magnitude speed-up has been achieved for the GPU-based implementation of the video feature tracking and matching technique.

In [4], an image correlation as a fundamental component of many real-time imaging and tracking systems has been implemented on a graphics processing unit (GPU) with one order of magnitude speed-up over the CPU version.

On the other hand, GPUs make the complexities of parallel programming even harder than before. A programmer needs to take care of the following:

- Using different parallelisation techniques such as tiling to achieve maximum reasonable speed-up and resource utilisation.

- Managing the usage of shared memories registers, global memories, constant memories and providing coalesce memory access to hide the memory latency, while in multi-core systems such optimisations are automatically handled by compilers.

- Minimising the data transfer cost between GPU memory and CPU memory to minimise the I/O time and reduce the processing elements' idle time.

Things can be even more complex if we have more than one GPU-device due to the need for extra efforts such as the coordination of tasks and distribution of data among GPUs based on their memory limitations, the speed of processing elements, and I/O bus speed between GPUs and CPUs.

One of the major problems in parallel programming is the lack of abstraction. The CUDA and OpenCL environments supporting hybrid (CPU and GPU) executions are low-level and they do not provide a high-level abstraction for the programmer to hide the above-mentioned complexities. Several high-level approaches are offered to tackle the abstraction issues by providing high-level techniques such as compiler based directive languages [5, 6, 7] or structured parallel programming [8, 9, 10, 11].

Although compiler based directive languages are providing an abstraction mechanism, they are highly inflexible, both in terms of not allowing dynamic adaptation in their execution environment, and in terms of making it difficult to introduce the high-level changes to programme structure.

As a well-known example of structured programming, *algorithmic skeletons* have long been considered a viable way of introducing high-level abstraction into parallel programming that hides the complexity of recurring patterns of coordination and communication logic behind a generic reusable application interface [12, 13].

Moreover, the building block based approach is another example of structured programming that supports the modelling and implementation of high-level structured parallel programming frameworks. It has been demonstrated that such approach can not only support skeleton based structured programming, but also general purpose programming models and domain specific patterns [14, 15].

Beside synchronisations and communications, another coordination problem can be optimising the scheduling mechanism in hybrid environments. Several researchers have demonstrated that operating systems provide a robust scheduling mechanism to support multi-threading and separate the coordination of allocating different threads to different resources from the programmer [16, 17, 18, 19, 20]. However, executing applications over heterogeneous multicore/many-core resources requires an explicit scheduling system in order to optimise performance and resource utilisation.

In [21] an extension of the OpenMP approach has been provided that spreads the compiler provided parallel computation across the heterogeneous cores to optimize performance and power consumption. In [22] a uniform interface is designed for task schedulers, offering low level scheduling mechanisms such as work stealing. Depending on the application, a user can select the most appropriate strategy at runtime, as all strategies implement the same interface.

In [23, 24] a scheduling approach has been designed which allocates incoming streams to a set of available CPUs and GPUs with a determined order to guarantee that no deadlines will be missed. In [25, 26] two different scheduling algorithms have been provided to extend the execution of an OpenCL programme written on a single device on both CPU and GPU in order to fully utilise all available OpenCL-enabled devices in a system. In [27] automatic adaptive mapping has been developed to dynamically map computation units on processing elements executing on both CPU and GPU.

Such a scheduling system can be considered as glue between the device scheduler and the operating system scheduler to optimise the allocation patterns of heterogeneous applications. Several approaches have emerged to tackle the problem of scheduling over heterogeneous multi-core architectures such as heuristic approaches, source-to-source compiler based optimisation and historical information generated from previous executions [28, 29, 30, 31].

Moreover, *autonomic management* can be considered as a viable solution to overcome the rapidly growing complexity of computing systems management and to reduce the barrier that complexity poses to further growth. **Autonomic management** refers to the self-managing characteristics of computing resources and adapting to unpredictable changes while hiding intrinsic complexity to operators and users[32].

By applying **autonomic management** in the parallel computing area, the self-managing characteristics can be considered as extra-functional and non-functional features such as performance, portability, security, fault-tolerance and power-management. In this case, applying autonomic management on a skeleton based framework to control a set of extra-functional and non-functional features has been called *behavioural skeletons*. Therefore, a **behavioural skeleton** is a skeleton with an associated autonomic manager taking care of extra-functional and non-functional properties related to skeleton implementation. It can be constructed as a combination of parallel patterns and rule-based control systems. Such a system delivers the implementation of an autonomic mechanism while managing one or more extra-functional or non-functional properties related to the parallel computation patterns [33].

In [34, 35, 36, 37] different behavioural modelling frameworks have been introduced on grid systems for autonomic management where the quality of a service goal can be defined for throughput under varying conditions of resource availability.

In [38], an investigation into key technologies has been performed to provide a new paradigm for developing autonomic grid applications. The proposed paradigm can be used to develop applications that are context aware and capable of self-configuring, self-composing, self-optimising and self-adapting.

In [39], an extension of the Fractal component model has been proposed to allow the modular development of adaptation policies and their dynamic weaving into running applications. These policies detect the evolutions of the execution context and adapt the base programme by reconfiguring it.

In principle, considering the abstraction and autonomic coordination over a set of extrafunctional features as two of the major challenges in the parallel computing area, it is expected that an efficient parallel programming model:

- Should provide a reasonable level of abstraction to hide the difficulty of communication and synchronisation over heterogeneous multi-core environments; and

- Must provide an autonomic management to optimise execution of parallel applications on a set of available heterogeneous resources over a set of predefined extra-functional features.

The challenge is, therefore, to produce and support such a programming paradigm that satisfies the above two conditions.

Although different behavioural skeletons automate the coordination of heterogeneous parallelism, they typically support non-functional properties, such as quality of service in grid computing systems. To the best of our knowledge, the autonomic management approach has not been applied to heterogeneous multi-core architecture for both extra-functional and nonfunctional properties.

Moreover, the existing autonomic management approaches for parallel programming have mainly been applied to algorithmic skeleton and have not considered other structured programming models. In [14, 15] it has been demonstrated that the intrinsic characteristics of structured parallelism through the building block approach place this paradigm in a preponderant position to support a reasonable level of abstraction by implicitly providing the communication and synchronisation for a parallel application. Also, it has been demonstrated that this approach

#### 1.1. Contributions

supports not only common patterns in algorithmic skeletons, but also other approaches such as the Google Map-Reduce model and domain specific parallel programming models. Therefore, our behavioural framework uses RISC-Pb<sup>2</sup>l building block approach presented in [14, 15] as a structured parallel programming approach to support abstraction.

Thus, in this thesis we develop a behavioural RISC-Pb<sup>2</sup>l framework that supports autonomic management over heterogeneous multi-core architecture for both extra-functional and non-functional properties.

To develop the autonomic behavioural framework over heterogeneous multi-core architecture, this thesis presents SKIP as a generic strategy that targets the autonomic coordination on structural parallelism over heterogeneous multi-core architectures. Applying the SKIP methodology, it would be possible to turn an existing structural parallel framework into a SKIP compliant autonomic behavioural framework with minimum modifications. Therefore, it would be possible for such a framework to interact with a set of SKIP compliant coordination engines to support autonomic coordination over heterogeneous multi-core architectures.

SKIP (*Structural Composition and Interaction Protocol*) is a generic methodology to instrument the structural programming for further autonomic coordination over one or more aspects of extra-functional properties related to parallel computation patterns on heterogeneous multi-core architectures.

Exploiting the SKIP interaction mechanism, a SKIP-compliant behavioural framework can automatically detect any variation regarding the selected extra-functional or non-functional properties and enhance it. Such variation can be a change in data input size, application priority or termination of a component in an application. Once such variation is detected, the automatic coordination is applied through a set of SKIP-compliant coordination engines to optimise the performance.

### 1.1 Contributions

In this thesis we have designed and implemented an autonomic behavioural framework called performance enhancement infrastructure (PEI) supporting automatic coordination management for structured parallel applications over heterogeneous multi-core architectures.

The framework is composed of the following three main parts:

- Structured Parallel Programming Model: Separates coordination from computation and hides the synchronisation and communications between application components from end-users.

- 2. **High-Level Abstraction Layer (HAL)** supports autonomic management for structured applications over heterogeneous multi-core architectures;

- 3. **Performance Enhancement Tools (PETs)** which are a set of coordination engines that support scheduling, load balancing and static configuration of an application structure for a specific heterogeneous multi-core architecture. We have designed and developed these coordination engines as part of the key optimisation objectives for ParaPhrase project [40].

- **Structured Parallel Programming Model:** We have selected the existing RISC-Pb<sup>2</sup>l building block approach as the structured parallel programming model. We have:

- extended the RISC-Pb<sup>2</sup>1 by adding a new heterogeneous block that enables the coordination of application over heterogeneous multi-core architecture;

- designed a grammar for the extended RISC-Pb<sup>2</sup>1 that detects the set of parallel programming patterns supportable by RISC-Pb<sup>2</sup>1 building block library for heterogeneous multi-core architecture. The grammar checks the correction and validation of the application structure generated by RISC-Pb<sup>2</sup>1 library;

- used FastFlow [41] as an existing RISC-Pb<sup>2</sup>l framework for homogeneous multicore system; and,

- expanded FastFlow by implementing a GPU back-end that supports application execution over heterogeneous multi-core architectures. This expansion is the implementation of the new heterogeneous building block called HFastFlow.

**High-Level Abstraction Layer (HAL):** Engulfing a structured parallel programming framework, this layer delivers three interfaces:

- 1. *User-level interface*: Determines a set of extra-functional and non-functional properties that allows the end-user to descriptively define the structural composition of its application. It also allows the end-user to descriptively determine the constraint configuration of the application and the underlying architecture.

- 2. *System level interface*: Determines a set of extra-functional and non-functional properties that are *i*) monitored on the structured parallel framework; *ii*) monitored on the underlying resources; *iii*) addressed by coordination engines.

- 3. *Autonomic manager interface*: Is a bridge between the end-user, the structured framework, the coordination engines, and the underlying hardware. It can automatically apply the specific coordination decisions to adapt to the changes happening on both the application status or the underlying hardware status.

In order to develop HAL, we have:

### 1.1. Contributions

- determined a set of controlling parameters that can affect application coordination. This has been provided by investigating a set of existing structured parallelism framework that support coordination over heterogeneous architectures;

- designed SKIP as a generic methodology that enables autonomic management for structured parallel programming model over heterogeneous multi-core architectures. SKIP determines both user-level and system level interfaces required to provide an autonomic management over a structured parallel application;

- fused SKIP with the RISC-Pb<sup>2</sup>l grammar to generate the high-level abstraction layer for RISC-Pb<sup>2</sup>l building block approach;

- instrumented HFastFlow by adding a set of actuators and sensors to exchange the extra-functional and non-functional properties determined in SKIP. This instrumentation represents the implementation of the SKIP fusion on RISC-Pb<sup>2</sup>1;

- designed and implemented a SKIP adaptor that auto-generates a RISC-Pb2l application from a descriptive structural composition file provided by the end-user; and,

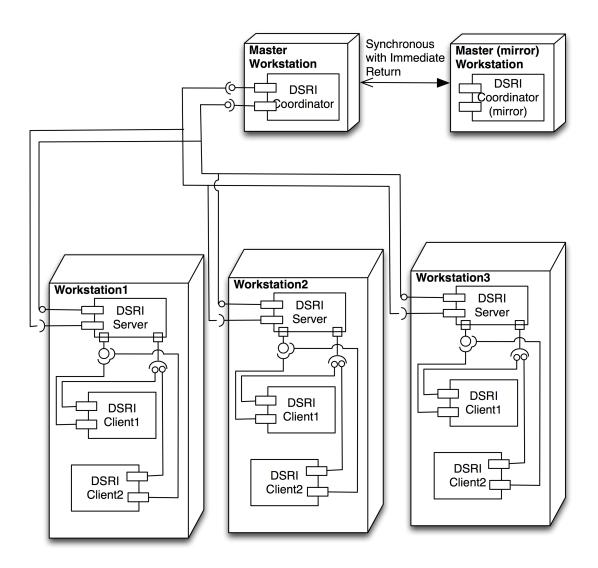

- designed and implemented a dynamic skeleton runtime interface (DSRI) to provide the autonomic management on HFastFlow for heterogeneous multi-core architecture.

- **Performance Enhancement Tools (PETs):** We have designed and implemented a set of coordination engines in order to verify the suitability of HAL for orchestrating structured parallel applications over heterogeneous architecture. These engines interact with HFast-Flow through the autonomic manager (DSRI) to optimise performance of the application and its resource utilisation over heterogeneous architectures. The coordination engines we have designed and implemented in this thesis are as follows.

- A scheduling mechanism to allocate/reallocate different components of applications on the underlying heterogeneous devices. It can dynamically remap heterogeneous software components to the available CPU/GPU devices based on the following information provided by the high-level abstraction layer: *i*) the extra-functional properties of the software components; *ii*) the hardware performance characteristics; and *iii*) information that is obtained from monitoring the dynamic system load. The provided system is capable of dealing with components from multiple applications and remapping them to the best available hardware, thus ensuring optimal use of the available hardware resources.

- A load-balancing technique that auto-tunes the workload fraction over different heterogeneous components with regards to their computational power. The technique

will also respond to sudden changes on the input workload size and if required, automatically tunes the workload fraction for application components.

- A static structural configuration technique to tune an application structure for a specific heterogeneous architecture. As an external coordination method, the static structural configuration tries to automatically tune a structured application and to map its components to the available resources for a given architecture in order to maximise the application throughput.

- An efficient idling technique to enhance utilisation of the resources for any CPU slot allocated to a component. The efficient utilisation of a resource depends on the availability of a task in a component queue for the allocated slot for the component.

- A memory management technique that dynamically controls the memory usage for heavy workload applications in order to prevent queue overflows for application components in HFastFlow.

- **PEI Evaluation:** In order to verify the efficiency of PEI, we have used 15 high-level structured applications classified into *two categories*.

The first category consists of 6 different *image processing applications* using the OpenCL back-end that we have designed and implemented in PEI. These applications are presented in Chapter 5, section 5.1. Each application in this category receives a stream of 6144 images as the input to process. This category has been designed to verify the efficiency of coordination engines regarding the structural extension to the FastFlow framework for targeting heterogeneous multi-core architectures. These applications have been executed on 2 different heterogeneous multi-core architectures, operating on different workload varieties from small-scale data to relatively large-scale data. The result are:

- less than 3% performance overhead for using PEI to enhance the performance of image processing applications;

- up to one order of magnitude speed-up over serial CPU version when OpenCL back-end is applied;

- up to 1.68 times speed-up over serial GPU version when OpenCL back-end is applied;

- up to 38% increase in GPU utilisation;

- up to 9 times speed-up when using the adaptive load-balancer instead of the Fast-Flow round-robin load-balancer;

- up to one order of magnitude speed-up when applying our dynamic scheduling over the FastFlow round robin technique;

- up to 5 times speed up when applying the static structural configuration; and

• no drop in performance when executing multiple applications concurrently.

The second category consists of 9 *existing FastFLow applications that do not use the extended OpenCL back-end*. This category has been designed to attest the efficiency of the proposed approach over a set of existing applications in the FastFlow framework.

This category includes an *N*-body simulation, 5 standard FastFlow benchmarks the EISPACK routine, a Molecular Dynamic (MD), and SMPWTP application. All applications are comprehensively described in Chapter 6. The results are:

- less than 3% performance overhead when using PEI to enhance the performance of FastFlow benchmark applications;

- up to 2 times speed-up more than Thrust and SkePU for the *N*-body simulation on large input data sizes;

- up to 2 times speed-up when using our efficient idling technique for FastFlow benchmark applications;

- up to 20 times speed-up when applying static structural configuration for molecular dynamic on Titanic machine;

- up to 5 times speed-up when applying static structural configuration for SMTWTP application on Titanic machine; and,

- Efficiently controlling the memory usage for EISPACK a known large-scale application with a heavy input workload.

### 1.2 List of Publications and Authorship

This research has been supported by the European Commission under the 7<sup>th</sup> Framework Programme through the Specific Targeted Research Project 'ParaPhrase': Parallel Patterns for Adaptive Heterogeneous Multicore Systems" http://paraphrase-ict.eu/, contract no.: 288570. The ParaPhrase project has produced a new structured design and implementation process for heterogeneous parallel architectures, where developers exploit a variety of parallel patterns to develop component based applications that can be mapped to the available hardware resources and, if required, dynamically re-mapped to meet application needs and hardware availability.

Some of the results of this research have been consistently published in high-impact outlets. For each publication below, we briefly explain the main contribution of the paper and the relationship to this thesis.

[1] Mehdi Goli, Horacio Gonzalez-Velez: N-body computations using skeletal frameworks on multicore CPU/graphics processing unit architectures: an empirical performance evaluation. Concurrency and Computation: Practice and Experience 26(4): 972-986, 2014.

In this paper we have developed *N*-body-simulation applications on three different structured frameworks, namely, FastFlow, Thrust, SKePU. We have compared the performance overhead and speed-up of *N*-body-simulation for 1024, 8192 and 65535 bodies on these three frameworks. The results have been added to chapter 6.

[2] Mehdi Goli, Michael T. Garba, Horacio Gonzalez-Velez: Streaming Dynamic Coarse-Grained CPU/GPU Workloads with Heterogeneous Pipelines in FastFlow. HPCC-ICESS. 445-452, 2012.

In this paper we have investigated the generality and scalability of FastFlow to parallelise an existing application called *EI*-routine. Moreover, we have efficiently controlled the memory usage for the EISPACK application as a large-scale application with a heavy input workload. The result for the memory management technique has been added to chapter 6. We have also determined the necessity of GPU-back-end support in FastFlow to further coordinate an application over heterogeneous architecture.

- [3] Mehdi Goli, Horacio Gonzalez-Velez: Heterogeneous Algorithmic Skeletons for Fast Flow with Seamless Coordination over Hybrid Architectures. PDP 148-156, 2013. In this paper we have expanded FastFlow by implementing an OpenCL-based GPU backend that supports application execution over heterogeneous multi-core architecture. This expansion has been added to chapter 4, while the implementation of the new heterogeneous building block is presented in chapter 3.

- [4] Mehdi Goli, John McCall, Horacio Gonzalez-Velez, and Marco Aldinucci. Performance Enhancement Infrastructure for Skeleton-based Parallel Programming Frameworks In CSRD Springer, submitted, 2014.

In this paper we have implemented the PEI framework and evaluated its overhead and efficiency to coordinate a set of FastFlow benchmark application. The PEI implementation has been added in chapter 4 and its evaluation has been added to chapter 6.

[5] Mehdi Goli, John McCall, Christopher Brown, Vladimir Janjic, Kevin Hammond: Mapping parallel programmes to heterogeneous CPU/GPU architectures using a Monte Carlo Tree Search. IEEE Congress on Evolutionary Computation 2013: 2932-2939.

Our contribution to this paper was to develop a static-structural configuration technique to tune an application structure for a specific heterogeneous architecture. Furthermore, for the specified architecture, the algorithm statically maps application components to the available CPUs/GPUs. The static structural configuration technique is a Monte-Carlo Tree Search (MCTS)-based algorithm which has been added to chapter 4

### 1.3. Research Method

[6] Christopher Brown, Vladimir Janjic, Kevin Hammond, Kamran Idrees, Colin Glass, Amer Wafai, Mehdi Goli, and John McCall. Bridgind the divide: a new methodology for semi-automatic programming of heterogeneous parallel machines. In CSRD Springer, submitted, 2014.

In this paper we have integrated our MCTS-algorithm with the refactoring technique provided by other Paraphrase partners to automate the process of static skeleton trimming and component mapping for an application generated by the refactoring tool. We have evaluated our MCTS-approach over two parallel applications (namely molecular dynamic and SMTWTP) generated by the refactoring tool. The evaluation results have been added to chapter 6.

### 1.3 Research Method

The discipline of computer science has roots in three other disciplines: mathematics, natural science and engineering. Theory, abstraction and design are three paradigms proposed by The ACM Task Force on the core of computer science [42] to characterise research work in computer science.

Theory originates from mathematics where the objects of study are identified, and their relationships are hypothesised, proved and later interpreted. Abstraction is ingrained in experimental scientific methods where a hypothesis is formed, models are built to predict and in the end, experiments are carried out to evaluate built models. Finally, the results are analysed. Design has its essence in engineering where requirements are specified, and a solution is designed, built and tested to ensure that it satisfies the given requirements.

As pointed out in [42], all three paradigm are equally important and are often intertwined together in computer science. Moreover, all three paradigms model a process which can be repeated and iterated multiple times until the desired outcome is achieved. The research presented in this thesis mainly follows the abstraction and design paradigms.

The proposed autonomic behavioural model represents an abstract paradigms that instruments structural parallel applications for further autonomic coordination over one or more aspects of more extra-functional properties of parallel computation patterns on heterogeneous multi-core architectures. The design and development of the behavioural model followed by different evaluations regarding the feasibility and efficiency of the framework that represents the design paradigm.

### 1.4 Thesis Architecture

This thesis has been organised into seven chapters and four appendices. In the following section we provide a brief description of each chapter.

- 1. **The Introduction** presents an overall description of our approach by introducing structured parallelism as a way to employ autonomic interaction with structured applications and states the hypothesis, followed by the enumeration of the objectives and structure of the thesis.

- 2. The Review of Literature presents an outline of the structured parallelism paradigm and its related approaches, with strong emphasis on heterogeneous systems in order to put the contribution of this thesis into context. This chapter ends with the identification of the specific research gap addressed by this work.

- 3. The SKIP Methodology This chapter presents the SKIP Methodology for designing a behavioural system that supports autonomic management (including monitoring and coordination processes of instrumented components) on RISC-Pb21-applications during their lifecycles. Through this chapter we have:

- (a) expanded the RISC-Pb<sup>2</sup>l building block approach to support heterogeneous architecture;

- (b) presented a grammar for RISC-Pb<sup>2</sup>l building block approach on heterogeneous architecture;

- (c) introduced SKIP to enable autonomic management for structured parallel programming model over heterogeneous multi- core architectures;

- (d) fused SKIP with the provided RISC-Pb<sup>2</sup>l grammar to instrument the building block approach for structural constructing and interacting with RISC-Pb<sup>2</sup>l-applications.

- (e) designed a SKIP compliant behavioural system to support autonomic coordination for RISC-Pb2l-applications on heterogeneous multi-core architectures.

- 4. The Implementation of the SKIP-Compliant Behavioural Framework In this chapter we have proposed PEI as the implementation of SKIP-compliant behavioural system that is proposed by the SKIP methodology. This chapter is composed of four different parts, namely:

- i FastFlow expansion (GPU back-end) to support heterogeneous architecture;

- ii FastFlow instrumentation with actuators and sensors;

- iii Implementation of HAL which support autonomic management over HFastFlow framework; and,

- iv Implementation of coordination engines that deliver autonomic adjustment related to the determined extra-functional properties.

- 5. The Evaluation of OpenCL Based Applications represents the evaluation of the SKIPcompliant behavioural framework on a set of applications using our structural expansion on FastFlow over heterogeneous systems. It contains the application definition, assessment and discussion about the applicability of different coordination methods targeting different extra-functional properties.

- 6. The Evaluation of Generic Applications represents the evaluation of the SKIP-compliant behavioural framework on a set of existing FastFlow applications which does not use our structural expansion for FastFlow over heterogeneous systems. It contains the application definition, assessment and discussion about the applicability of some coordination methods that are suitable for those applications.

- 7. **Conclusion & Future Work** The conclusion furnishes a description of the research area covered by the thesis. It explains the ongoing related research studies regarding our investigation. It concludes by discussing possible avenues for future work.

- 8. Appendix: Validation of RISC-pb<sup>2</sup>l Grammar This appendix chapter explains the validation of the provided RISC-pb<sup>2</sup>l grammar for the set of supported patterns presented.

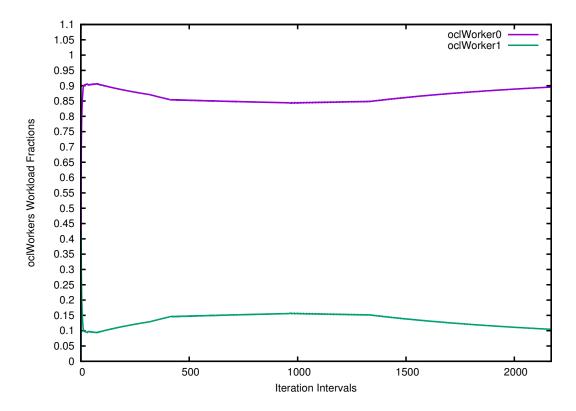

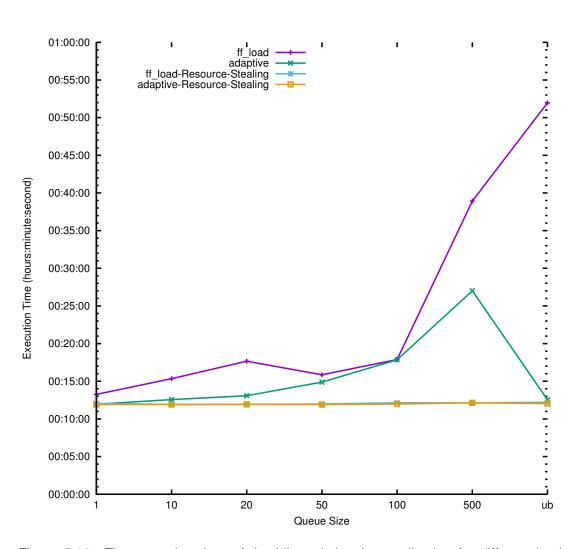

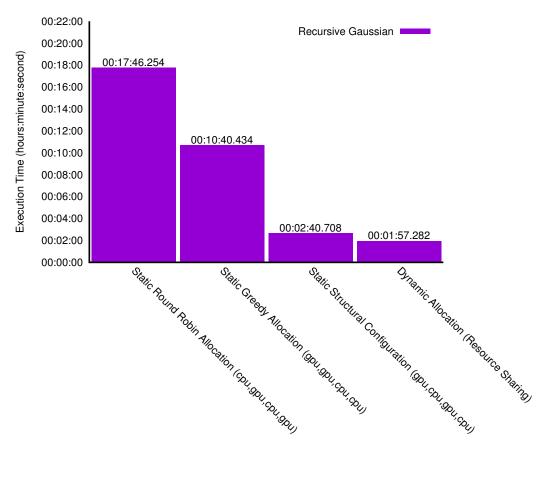

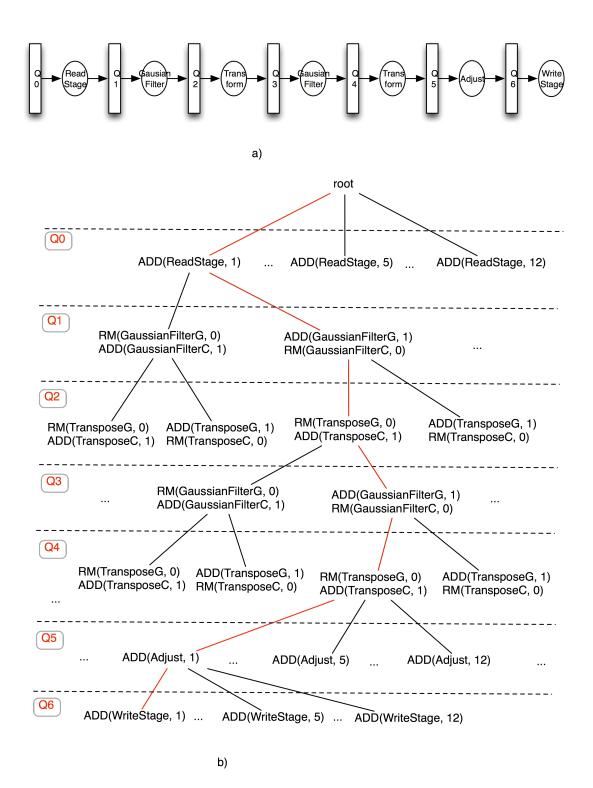

- Appendix: The Structural Representation of the Application Suite This appendix chapter demonstrates the structural representation of designed applications through the RISC-pb<sup>2</sup>l grammar and SKIP methodology.